# Bayesian neuromorphic computing based on resistive memory

Thomas Dalgaty

### ▶ To cite this version:

Thomas Dalgaty. Bayesian neuromorphic computing based on resistive memory. Micro and nanotechnologies/Microelectronics. Université Grenoble Alpes [2020-..], 2020. English. NNT: 2020GRALT087. tel-03466542

# HAL Id: tel-03466542 https://theses.hal.science/tel-03466542

Submitted on 6 Dec 2021

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# THÈSE

Pour obtenir le grade de

## DOCTEUR DE L'UNIVERSITÉ GRENOBLE ALPES

Spécialité : NANO ELECTRONIQUE ET NANO TECHNOLOGIES Arrêté ministériel : 25 mai 2016

Présentée par

# **Thomas DALGATY**

Thèse dirigée par  ${\bf Barbara} \ {\bf DE} \ {\bf SALVO}$  , Directeur de Recherche et codirigée par  ${\bf Elisa} \ {\bf VIANELLO}$

et Jérôme CASAS, Enseignant-Chercheur, Université de Tours

préparée au sein du Laboratoire CEA/LETI dans l'École Doctorale Electronique, Electrotechnique, Automatique, Traitement du Signal (EEATS)

# Calcul neuromorphique Bayésien basé sur la mémoire résistive

# Bayesian neuromorphic computing based on resistive memory

Thèse soutenue publiquement le **27 novembre 2020**, devant le jury composé de :

Madame BARBARA DE SALVO INGENIEUR HDR, CEA GRENOBLE, Directrice de thèse Madame ELISABETTA CHICCA PROFESSEUR, UNIVERSITE DE GRONINGUE - PAYS-BAS, Rapporteure Monsieur LUCA BENINI PROFESSEUR, ETH ZURICH - SUISSE, Rapporteur Monsieur JEAN-MICHEL PORTAL PROFESSEUR DES UNIVERSITES, AIX-MARSEILLE UNIVERSITE, Président Monsieur DAMIEN QUERLIOZ CHARGE DE RECHERCHE HDR, CNRS DELEGATION ILE-DE-FRANCE SUD, Examinateur Monsieur GIACOMO INDIVERI

PROFESSEUR, UNIVERSITE DE ZURICH - SUISSE, Examinateur

# Abstract

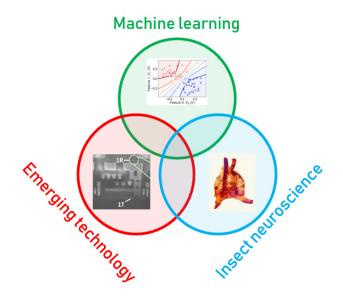

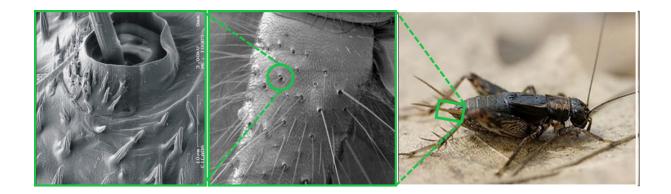

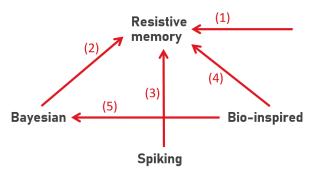

Artificial intelligence is a field that, historically, has benefited from the combination of ideas from across inter-disciplinary boundaries which have improved models of AI and the algorithms that operate on them. Biological nervous systems in particular have inspired various model topologies and algorithmic tricks that have led to leaps in performance. In contrast, as computing power and memory availability have increased relentlessly since the 1950's, models of artificial intelligence have largely failed to recognise the constraints imposed by, or incorporate the opportunities offered by, the underlying computing hardware. While this is not immediately apparent in the cloud computing setting; the mismatch between model, algorithm and hardware is the limiting factor that currently curtails the efficient application of locally-adaptive artificially intelligent systems at the edge. In this thesis, the interdisciplinary boundary between machine learning, emerging technologies and biological nervous systems will be explored with the objective of proposing a new, hardware-focussed, approach for the application of energy efficient and locally-adaptive edge neuromorphic computing systems. Resistive memories are a leading candidate as an enabling technology for AI to greatly reduce its energy requirements. This is largely owed to the efficient and parallelised implementation of the dot-product operation that pervades machine learning as well as its material-level compatibility with advanced CMOS processes. However, until now, the application of RRAM has been confined predominantly to implementations of gradient-based machine learning algorithms, namely backpropagation, to train RRAM-based multi-layer perceptron models. The fundamental properties of RRAM though, predominantly their conductance variability, are, on the contrary, not compatible with learning algorithms based on the descent of error gradients. This thesis recognises that, in contrast, the intrinsic properties of this technology can be harnessed through Bayesian approaches to machine learning where, like device conductance states, model parameters are described as random variables. RRAM-based implementations of Markov Chain Monte Carlo sampling algorithms are implemented and applied to the training of RRAM-based models. An RRAM-based computing hardware capable of supporting such models is also proposed. Inspired by the organisational principles of animal nervous systems, whereby memory and processing are distributed and arguably indistinguishable, this thesis proposes analogue circuit solutions for biological models of neurons and synapses and for a system-level architecture to interconnect such elements. Reflecting the role played by ion-channels embedded in biological neuronal membranes, these circuits co-localise memory and computation by incorporating resistive memory devices directly into the circuits themselves; determining model parameters and the interconnectivity between these elements locally. Relative to similar approaches, this obviates the need for volatile on-chip working memory and the use of analogue-to-digital conversion, both entailing significant energy demands. In recognition of the efficient solutions animals like insects have uncovered throughout the course of evolution, their nervous systems are used to guide the development of model architectures. Based on recent neurophysiological studies, models inspired by the cricket cercal system and the fruit fly motion detection system are proposed. To achieve an equivalent performance to the cercal system model, multi-layer perceptrons require between one and two orders of magnitude more memory elements; offering a means of scaling the proposed MCMC sampling algorithms to more complex tasks. It is also discussed how the 'small-worldness' of networks of neurons found in animal nervous systems can provide a solution to the spatial connectivity constraints inherent to the proposed RRAM-based computing fabric.

**Key words**: Bayesian, machine learning, resistive memory, neural networks, electronic circuits, bioinspiration.

# Résumé

L'intelligence artificielle (IA) est un domaine qui, historiquement, a grandement bénéficié de l'association d'idées interdisciplinaires, pour améliorer ses modèles ainsi que ses algorithmes. Les systèmes nerveux biologique ont ainsi été une source d'inspiration de valeur pour les topologies des modèles et des techniques algorithmiques, et ont été à l'origine de sauts en performances. Cependant, même si la puissance du calcul et la quantité de la mémoire ont augmenté sans cesse, les modèles de l'IA ont largement échoué à s'adapter aux opportunités et aux contraintes apportées par les technologies silicium. Ce constat est relativement masqué dans le cas du calcul dans le cloud, mais constitue le facteur limitant pour le calcul au niveau edge à faible puissance. Cette thèse explore la frontière interdisciplinaire entre l'apprentissage automatique, les technologies émergentes et les systèmes nerveux biologique, avec l'objectif de proposer une nouvelle approche de l'IA, focalisée sur le hardware, pour réaliser des systèmes calcul neuromorphiques à faible consommation et adaptifs localement au niveau edge. Les mémoires résistives jouent un rôle prometteur pour la réduction de la consommation d'énergie de l'IA. Elles permettent en effet de réaliser efficacement et de manière parallélisée l'opération de produit scalaire, extrêmement importante dans l'IA, et elles sont compatibles avec les technologies CMOS avancées. Jusqu'ici, l'utilisation de RRAM a été majoritairement confinée à des algorithmes basés sur les gradients, notamment la rétro-propagation, pour l'apprentissage de perceptrons multicouches. Cependant, les caractéristiques des RRAM, notamment la variabilité de leur conductance, ne sont pas compatibles avec les besoins de ces algorithmes d'apprentissage basé sur la descente de gradients. Ce travail de thèse propose à l'inverse d'utiliser ces caractéristiques fondamentales des RRAM comme un avantage pour la modélisation Bayésienne, où des paramètres des modèles sont, comme les états de conductance de RRAM, décrits par des variables aléatoires. Des implémentations ex-situ et in-situ de méthodes Monte Carlo par chaînes de Markov (MCMC) basées sur les RRAM sont proposées et appliquées à l'entrainement des modèles. De plus, un hardware de calcul basé sur les RRAM est aussi proposé, permettant de mettre en application ces modèles. Inspirées par les systèmes nerveux animaux, où les éléments du calcul et de la mémoire sont distribués et co-localisés, des solutions en circuit analogiques sont proposées pour modéliser des neurones et des synapses biologiques ainsi qu'une architecture au niveau du système pour les interconnecter. Reflétant le rôle joué par les canaux ioniques, noyé dans les membranes neuronales, les circuits incorporent la RRAM au sein des circuits et déterminent localement leurs paramètres et leur inter-connectivite. Contrairement aux autres approches, ce système ne nécessite ni mémoires vives statiques (SRAM), ni convertisseurs analogiques-numériques qui nécessitant une consommation énergétique élevée. Enfin, en reconnaissant les solutions efficaces qu'ils ont trouvé au cours de l'évolution, les systèmes nerveux des insectes, nous servent de guider le développement d'architectures de modèles d'IA. En s'appuyant sur les résultats récents d'études neurophysiologiques sur les insectes, deux modèles sont proposés : un inspiré par le système cercal du grillon et l'autre par le système de détection de mouvement de la mouche. Pour obtenir une performance égale au modèle cercal, nous observons que les modèles de perceptrons multicouches nécessitent entre une et deux fois plus des paramètres synaptiques - ce qui ouvre la possibilité d'appliquer le MCMC à base de RRAM à des tâches complexes. Les caractéristiques 'small-world' des réseaux des neurones biologiques sont également abordées : elles peuvent offrir une solution pour outrepasser les contraintes de connectivites spatiales liées à l'architecture proposée.

**Mots clés**: Bayésien, apprentissage automatique, mémoire résistive, réseaux de neurones, circuits électroniques, bio-inspiration.

# **Acknowledgements**

This thesis was carried out in collaboration with various partner Universities and is composed of adapted versions of the papers and patents written with them in which I was the first author - those listed in the following page. Reflecting this, the thesis is written using 'we' instead of 'I' throughout. Specifically, I would like to thank Damien Querlioz at Université Paris-Saclay and his students Clement Turck and Kamel-Eddine Harabi for their collaboration in chapter 3, Giacomo Indiveri and Melika Payvand from the Institute of neuroinformatics, a joint laboratory between the University of Zurich and the ETH Zurich, for their collaboration in chapter 4 and to Jerome Casas, Claudio Lazzari, Teresita Insausti and Thomas Steinmann at Université de Tours as well as to John P. Miller from Montana state University for their collaboration in chapter 2. This is of course in addition to my many colleagues in CEA who have contributed to this work over the course of my PhD and are far too numerous to be listed here.

# List of publications and patents

### First author publications

- *T. Dalgaty et al.*, In-situ learning using intrinsic memristor variability via Markov chain Monte Carlo sampling, **Nature electronics**, *2021*

- *T. Dalgaty et al.*, Bio-inspired architectures substantially reduce the memory requirements of neural networks, **Frontiers in neuroscience**, *2021*

- *T. Dalgaty et al.*, Ex-situ transfer of Bayesian neural networks to resistive memory based inference hardware, **Advanced intelligent systems**, *2021*

- *T. Dalgaty et al.*, Hybrid neuromorphic circuits exploiting non-conventional properties of RRAM for massively parallel plasticity mechanisms, **APL Materials**, *2019*

- *T. Dalgaty et al.*, Hybrid CMOS-RRAM Neurons with intrinsic plasticity, **ISCAS, Sapporo, Japan**, 2019

- *T. Dalgaty et al.*, Insect-inspired neuromorphic computing, **Current opinions in insect science**, 2018

- *T. Dalgaty et al.*, Insect-inspired elementary motion detection embracing resistive memory and spiking neural networks, **Living machines**, **Paris**, **France**, *2018*

- *T. Dalgaty et al.*, A Mosaic of neuromorphic memory for in-memory small-world neural networks, **In** redaction, *2021*

## Subsidiary author publications

- *Y. Demirag et al.*, PCM-trace: Scalable Synaptic Eligibility Traces with Resistivity Drift of Phase-Change Materials, **ISCAS, Daegu, South Korea**, *2021*

- *M. Payvand et al.*, Analog weight updates with compliance current modulation of binary ReRAMs for on-chip learning, **ISCAS**, **Seville**, **Spain**, *2020*

- *E. Esmanhotto et al.*, High-Density 3D Monolithically Integrated Multiple 1T1R MultiLevel-Cell for Neural Networks, **IEDM, San Francisco, United States**, *2020*

- *F. Pebay-Peyroula et al.*, Entropy source characterisation in HfO2 RRAM for TRNG applications, **DTIS, Marrakesh, Morocco**, *2020*

- *D.R.B Ly et al.* Novel 1T2R1T RRAM-based TCAM for large scale pattern recognition, **IEDM, San Francisco, United States**, *2019*

- *E. Donati et al.*Processing ECG signals using reservoir computing on an event-based neuromorphic system, **BioCAS, Cleveland, United States**, *2018*

- *E. Vianello et al.* Metal-oxide resistive memory and phase change memory as artificial synapses in spiking neural networks, **ICECS**, **Bordeaux**, **France**, *2018*

- *D.R.B Ly et al.* Role of synaptic variability in spike-based neuromorphic circuits with unsupervised learning, **ISCAS, Florence, Italy**, *2018*

## Book chapters

• Synaptic realizations based on memristive devices, Memristive Devices for Brain-Inspired Computing, **Woodhead Publishing**, *2020*

## Patents

- Odd-even memory array architecture for MCMC sampling 2021

- Temporal difference reinforcement learning algorithm using volatile conductance states 2020

- Phase change memory based spike-time-dependent plasticity algorithm, 2020

- Volatile memory based three-factor learning algorithm, 2020

- Neuromorphic event-based routing architecture based on resistive memory, 2019

- Resistive memory based Markov Chain Monte Carlo sampling 2019

- Resistive memory based Bayesian neural network architecture and model transfer technique 2019

- Hybrid CMOS-RRAM neuron circuit 2018

# Contents

| 1 | Introduction                              |        |                                                      |    |  |  |  |  |

|---|-------------------------------------------|--------|------------------------------------------------------|----|--|--|--|--|

|   | 1.1                                       | A brie | f history of artificial intelligence                 | 12 |  |  |  |  |

|   |                                           | 1.1.1  | Pre-history                                          | 12 |  |  |  |  |

|   |                                           | 1.1.2  | 1950's, 60's and 70's                                | 15 |  |  |  |  |

|   |                                           | 1.1.3  | 1980's and 90s                                       | 19 |  |  |  |  |

|   |                                           | 1.1.4  | 21 <sup>st</sup> Century                             | 20 |  |  |  |  |

|   | 1.2                                       | Hardw  | vare in artificial intelligence                      | 23 |  |  |  |  |

|   |                                           | 1.2.1  | LISP machines                                        | 23 |  |  |  |  |

|   |                                           | 1.2.2  | Field programmable gate arrays                       | 24 |  |  |  |  |

|   |                                           | 1.2.3  | Graphics and tensor processing units                 | 24 |  |  |  |  |

|   |                                           | 1.2.4  | Neuromorphic processors                              | 24 |  |  |  |  |

|   |                                           | 1.2.5  | Memory technologies                                  | 27 |  |  |  |  |

|   | 1.3                                       | Challe | nges in applying artificial intelligence             | 30 |  |  |  |  |

|   |                                           | 1.3.1  | Training energy consumption                          | 31 |  |  |  |  |

|   |                                           | 1.3.2  | Bringing learning to the edge                        | 31 |  |  |  |  |

|   |                                           | 1.3.3  | Ethical application of Al                            | 32 |  |  |  |  |

|   | 1.4                                       | Scope  | of this thesis                                       | 34 |  |  |  |  |

| 2 | Bio-inspired neural network architectures |        |                                                      |    |  |  |  |  |

|   | 2.1                                       | Chapt  | er introduction                                      | 37 |  |  |  |  |

|   | 2.2                                       | Model  | of the cricket cercal system escape response         | 37 |  |  |  |  |

|   |                                           | 2.2.1  | Introduction                                         | 37 |  |  |  |  |

|   |                                           | 2.2.2  | Model definition                                     | 39 |  |  |  |  |

|   |                                           | 2.2.3  | Model evaluation                                     | 47 |  |  |  |  |

|   |                                           | 2.2.4  | Universal approximator benchmarking                  | 48 |  |  |  |  |

|   |                                           | 2.2.5  | Model interpretation                                 | 51 |  |  |  |  |

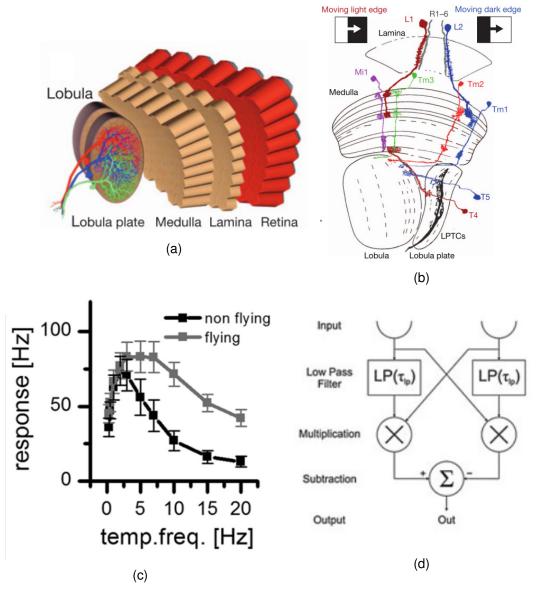

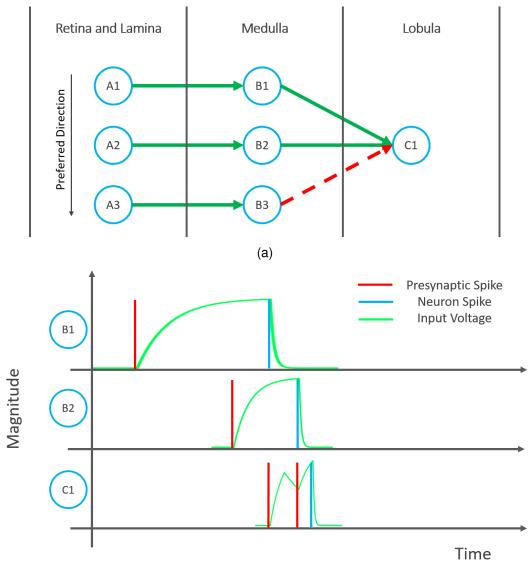

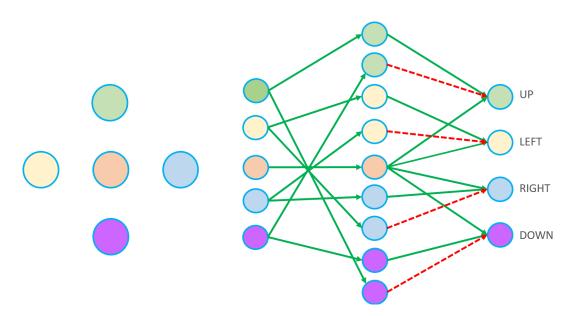

|   | 2.3                                       | Model  | of the Drosophila elementary motion detection system | 57 |  |  |  |  |

|   |                                           | 2.3.1  | Introduction                                         | 57 |  |  |  |  |

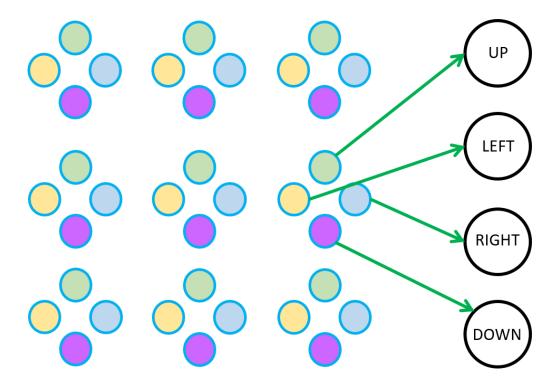

|   |                                           | 2.3.2  | Model definition                                     | 59 |  |  |  |  |

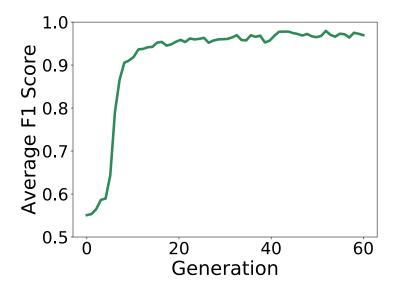

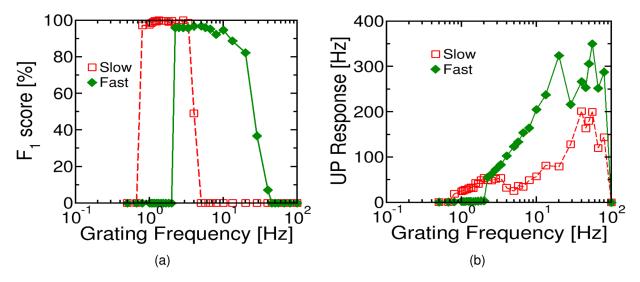

|   |                                           | 2.3.3  | Model evaluation                                     | 62 |  |  |  |  |

|   | 2.4                                       | Chapt  | er discussion                                        | 65 |  |  |  |  |

| 3 | Bayesian machine learning with resistive memory |         |                                                                 |     |  |  |  |  |  |  |  |

|---|-------------------------------------------------|---------|-----------------------------------------------------------------|-----|--|--|--|--|--|--|--|

|   | 3.1                                             | Chapte  | er introduction                                                 | 69  |  |  |  |  |  |  |  |

|   | 3.2                                             | In-situ | resistive memory based Markov Chain Monte Carlo                 | 69  |  |  |  |  |  |  |  |

|   |                                                 | 3.2.1   |                                                                 | 69  |  |  |  |  |  |  |  |

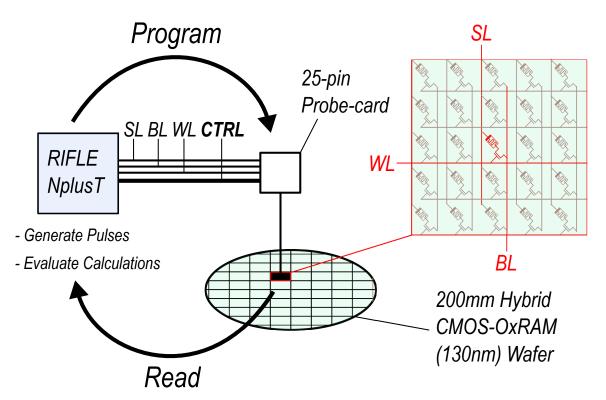

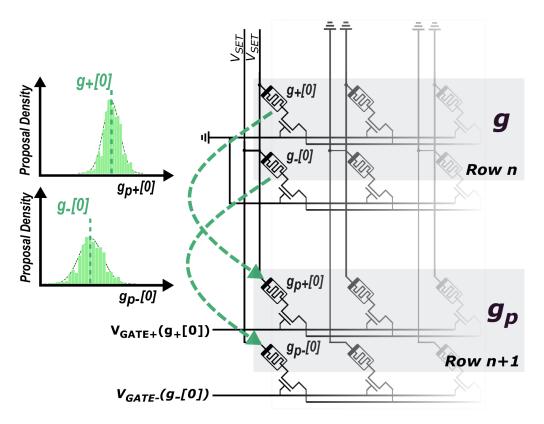

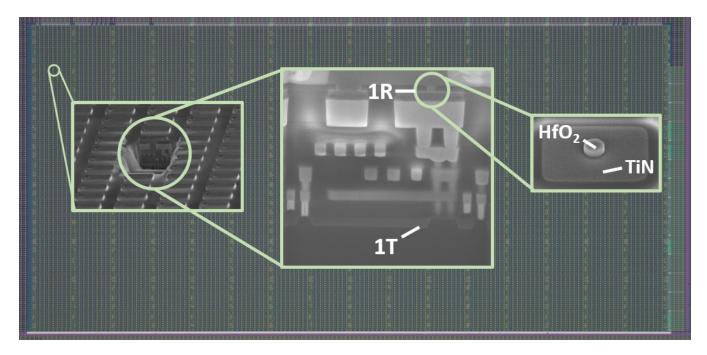

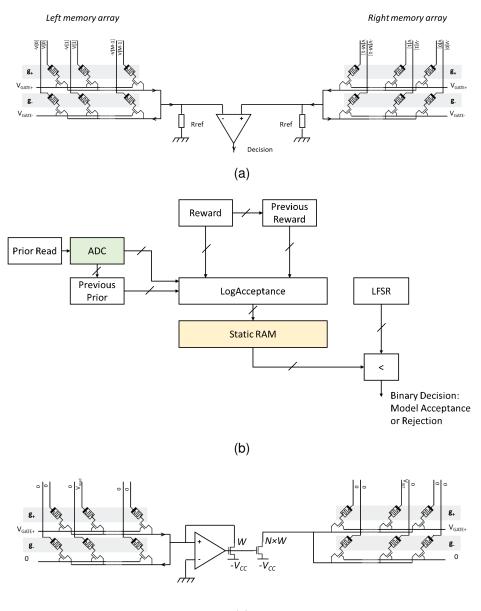

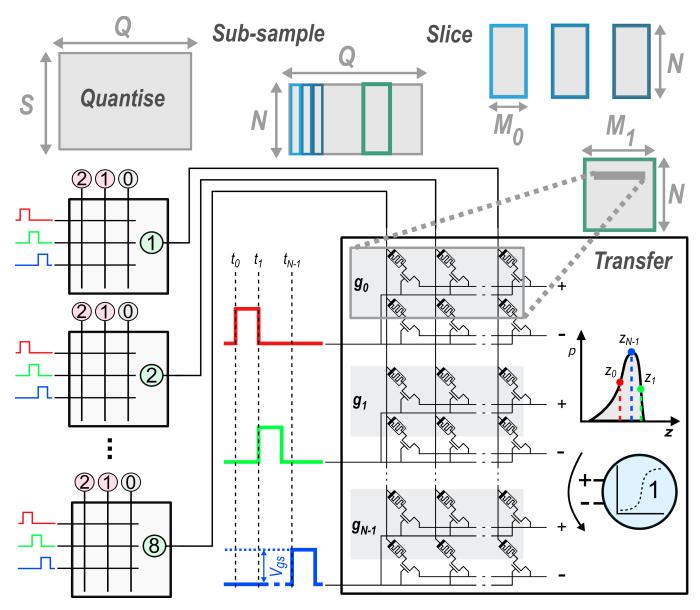

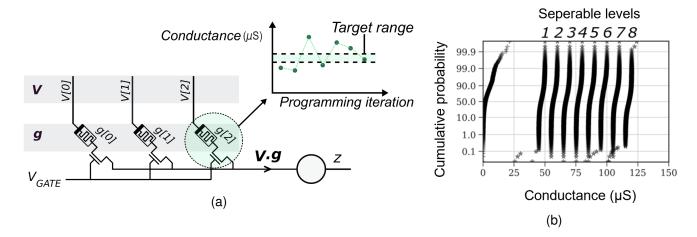

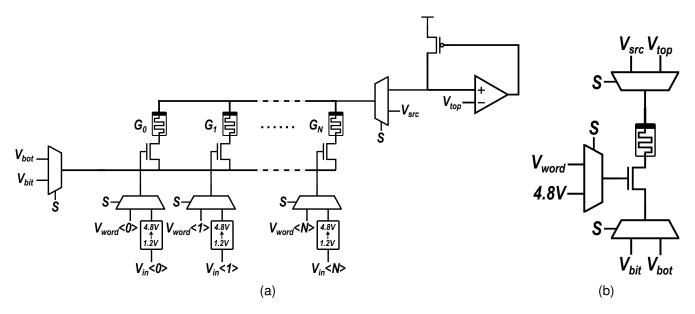

|   |                                                 | 3.2.2   | In-memory implementation                                        | 71  |  |  |  |  |  |  |  |

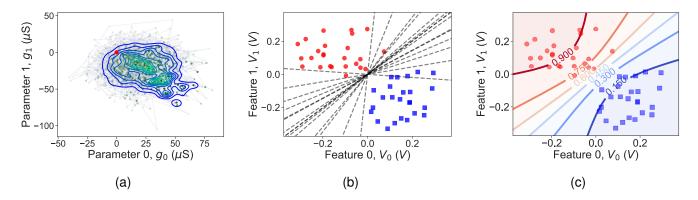

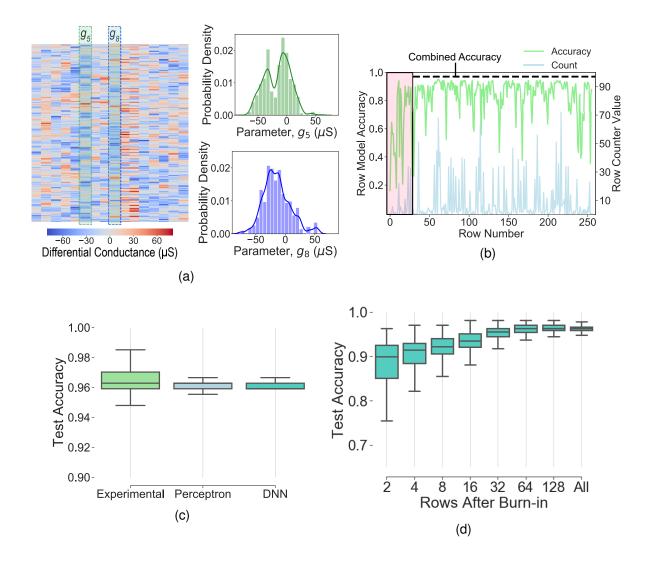

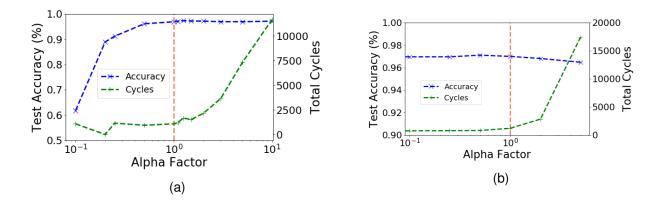

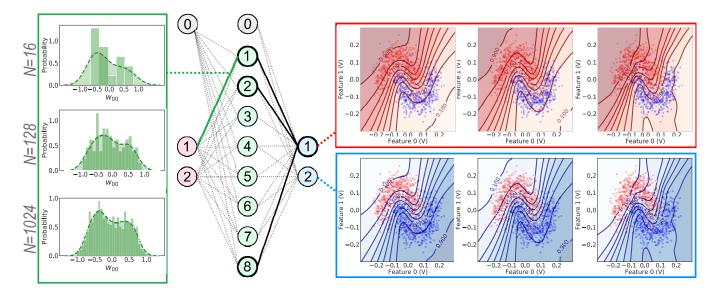

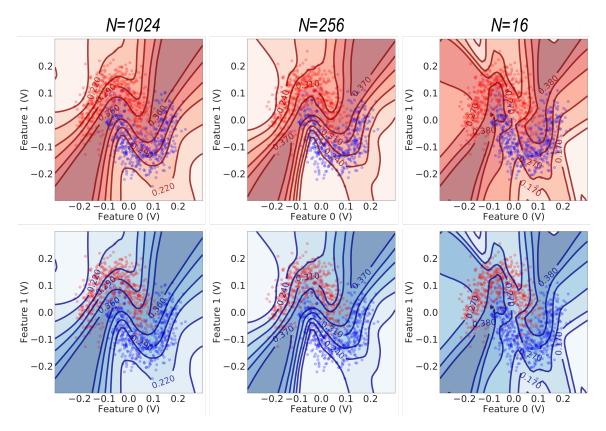

|   |                                                 | 3.2.3   | Application to supervised learning                              | 80  |  |  |  |  |  |  |  |

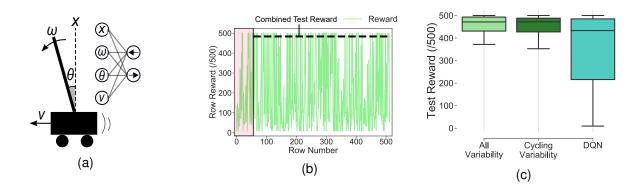

|   |                                                 | 3.2.4   | Application to reinforcement learning                           | 87  |  |  |  |  |  |  |  |

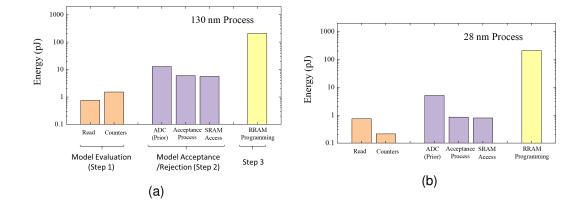

|   |                                                 | 3.2.5   | System level energy estimation                                  | 91  |  |  |  |  |  |  |  |

|   | 3.3                                             | Ex-situ | u transfer of a Bayesian neural network                         | 96  |  |  |  |  |  |  |  |

|   |                                                 | 3.3.1   | Section introduction                                            | 96  |  |  |  |  |  |  |  |

|   |                                                 | 3.3.2   | Expectation-maximisation based parameter decomposition          | 97  |  |  |  |  |  |  |  |

|   |                                                 | 3.3.3   | Ex-situ training of an RRAM-based Bayesian neural network       | 100 |  |  |  |  |  |  |  |

|   |                                                 | 3.3.4   | Transfer to resistive memory based inference hardware           | 102 |  |  |  |  |  |  |  |

|   |                                                 | 3.3.5   | Allowing a model to say 'I don't know'                          | 106 |  |  |  |  |  |  |  |

|   | 3.4                                             | Chapt   | er discussion                                                   | 109 |  |  |  |  |  |  |  |

|   | •                                               |         |                                                                 |     |  |  |  |  |  |  |  |

| 4 | <b>A</b> no                                     |         | Neumann neuromorphic computing fabric           er introduction | 113 |  |  |  |  |  |  |  |

|   | 4.1                                             | •       |                                                                 |     |  |  |  |  |  |  |  |

|   | 4.2                                             | 4.2.1   | CMOS-RRAM analogue circuit models                               |     |  |  |  |  |  |  |  |

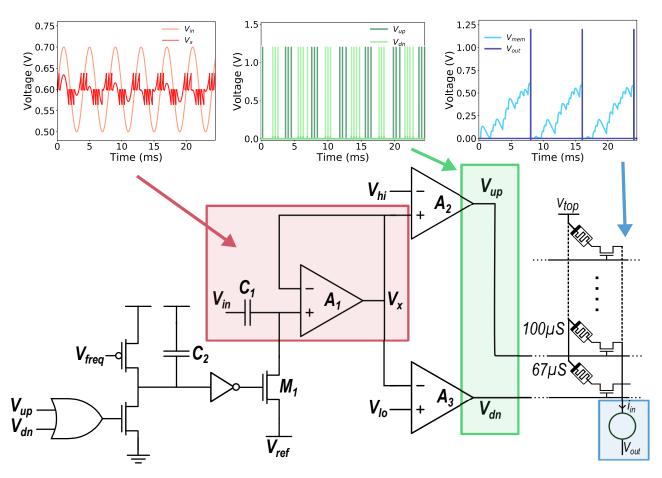

|   |                                                 | 4.2.1   | An OxRAM based intrinsic plasticity algorithm                   |     |  |  |  |  |  |  |  |

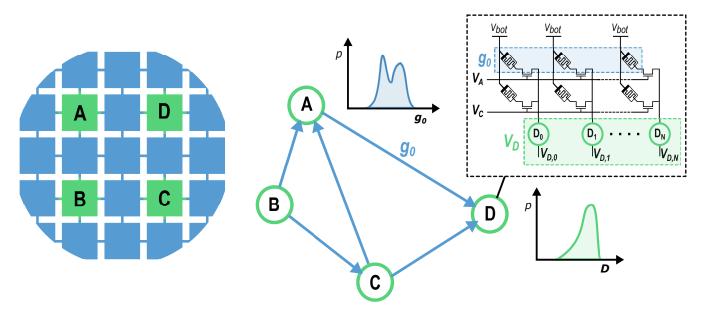

|   | 4.3                                             |         | morphic event routing architecture                              |     |  |  |  |  |  |  |  |

|   | <del>т.</del> 0                                 | 4.3.1   |                                                                 |     |  |  |  |  |  |  |  |

|   |                                                 | 4.3.2   | Neuron and routing tiles                                        |     |  |  |  |  |  |  |  |

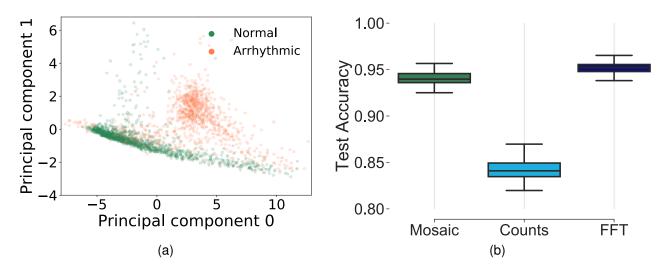

|   |                                                 | 4.3.3   | Application to reservoir computing                              |     |  |  |  |  |  |  |  |

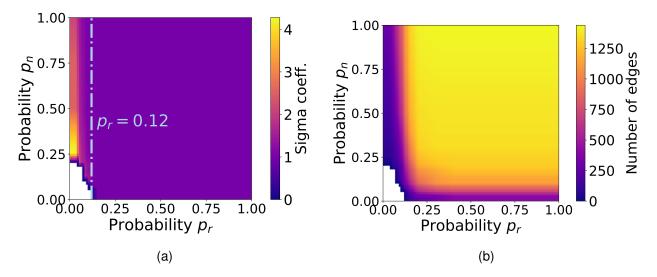

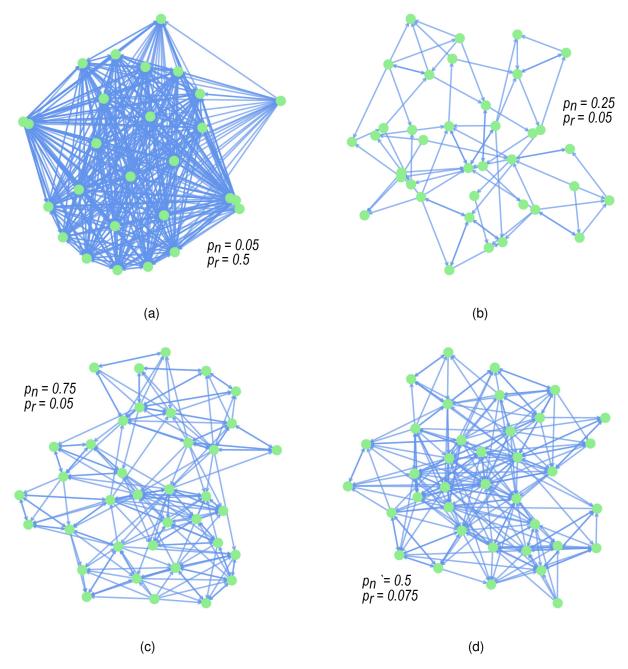

|   |                                                 | 4.3.4   | Small world graph properties                                    |     |  |  |  |  |  |  |  |

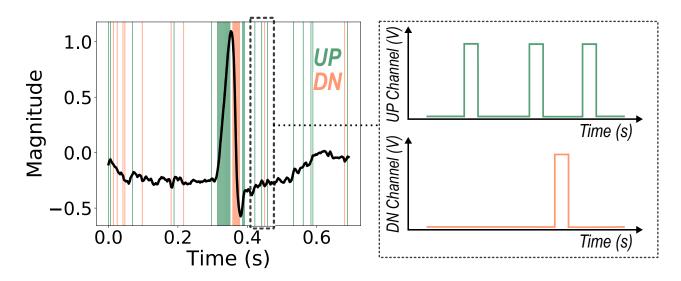

|   |                                                 | 4.3.5   | Heartbeat arrhythmia detection                                  |     |  |  |  |  |  |  |  |

|   | 44                                              |         |                                                                 |     |  |  |  |  |  |  |  |

|   |                                                 |         |                                                                 |     |  |  |  |  |  |  |  |

| 5 | Con                                             | clusior |                                                                 | 161 |  |  |  |  |  |  |  |

|   | 5.1                                             |         | on of a Bayesian neuromorphic computing system                  |     |  |  |  |  |  |  |  |

|   | 5.2                                             | Perspe  | ectives and future work                                         | 164 |  |  |  |  |  |  |  |

| 6 | Appendices 169                                  |         |                                                                 |     |  |  |  |  |  |  |  |

|   | 6.1                                             |         | ndix - Additional circuits and layouts                          | 169 |  |  |  |  |  |  |  |

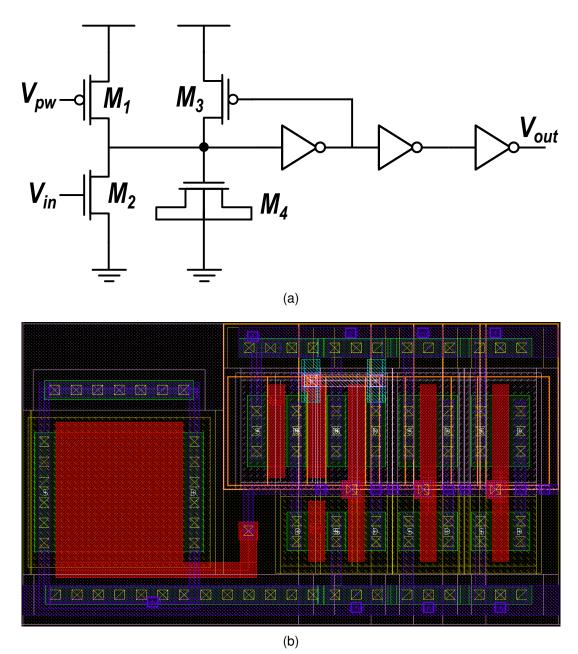

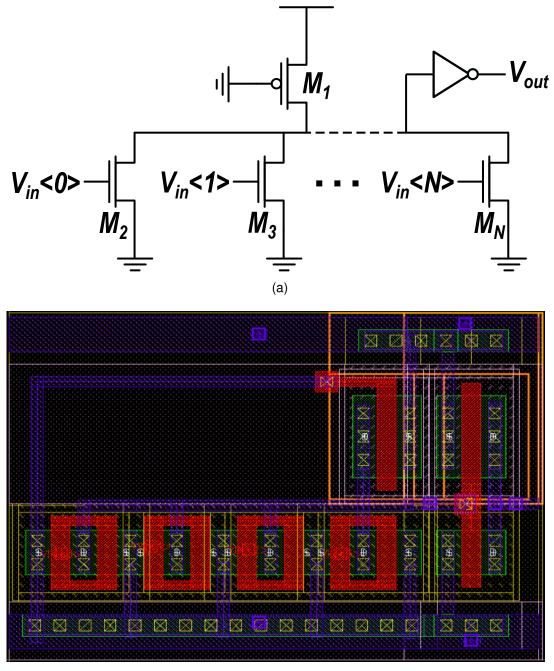

|   |                                                 | 6.1.1   | Inverter unit cell                                              |     |  |  |  |  |  |  |  |

|   |                                                 | 6.1.2   | Thick oxide inverter unit cell                                  |     |  |  |  |  |  |  |  |

|   |                                                 | 6.1.3   | Starved inverter                                                |     |  |  |  |  |  |  |  |

|   |                                                 | 6.1.4   | Operational amplifier                                           |     |  |  |  |  |  |  |  |

|   |                                                 | 6.1.5   | Pulse extender                                                  |     |  |  |  |  |  |  |  |

|   |                                                 | 6.1.6   | Half OR                                                         |     |  |  |  |  |  |  |  |

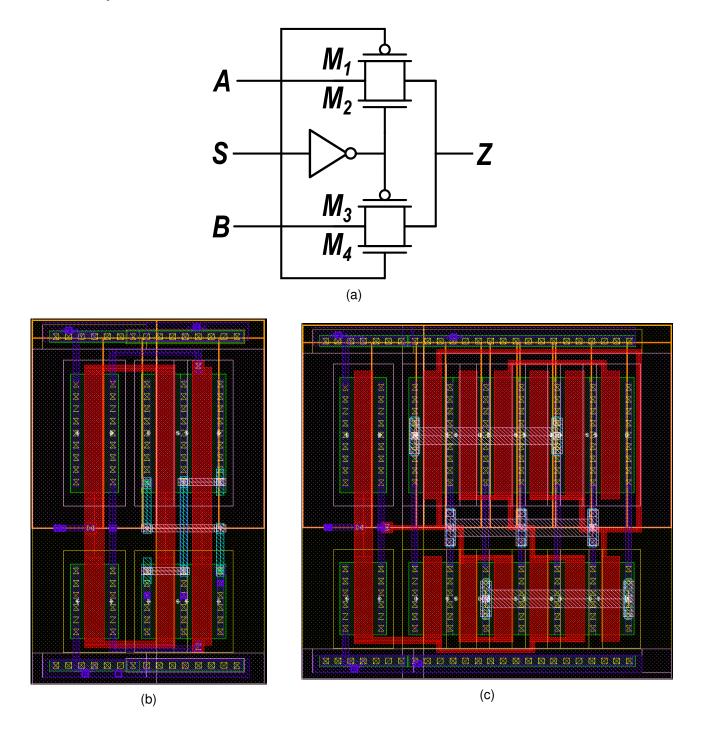

|   |                                                 | 6.1.7   | Multiplexer                                                     |     |  |  |  |  |  |  |  |

|   |                                                 |         | ,                                                               | . • |  |  |  |  |  |  |  |

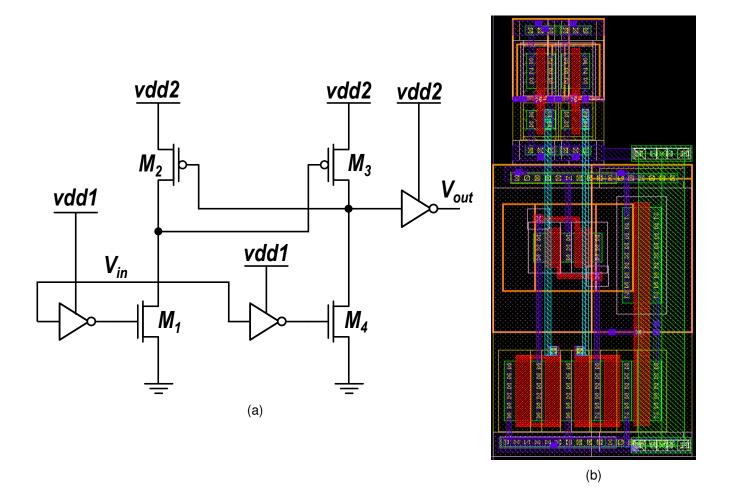

|      | 6.1.8 Level shifter                                                 | 77             |

|------|---------------------------------------------------------------------|----------------|

|      | 6.1.9 CMOS neuron                                                   | 78             |

|      | 6.1.10 CMOS synapse                                                 | 79             |

|      | 6.1.11 Delta modulator layout                                       | 30             |

|      | 6.1.12 1T1R cell                                                    | 31             |

|      | 6.1.13 Column circuit layout                                        | 32             |

|      | 6.1.14 Hybrid synapse layout                                        | 33             |

|      | 6.1.15 Hybrid neuron layout                                         | 34             |

| 6.2  | Appendix - Note on MOS capacitors                                   | 35             |

| 6.3  | Appendix - Resistive memory experiments 18                          | 37             |

| 6.4  | Appendix - Implementation of RRAM-based MCMC simulator              | 38             |

| 6.5  | Appendix - Note on implementation of neural network models          | <del>)</del> 0 |

| 6.6  | Appendix - Pre-processing of the electrocardiogram dataset          | <b>)</b> 1     |

| 6.7  | Appendix - Cercal system statistical model response                 | )2             |

| 6.8  | Appendix - Observed shift of the OxRAM normal random variable       | <del>)</del> 6 |

| 6.9  | Appendix - Cercal system model input neuron circuit implementation  | <del>)</del> 7 |

| 6.10 | Appendix - Robustness of TAG model to random parameter permutations | <del>)</del> 8 |

| 6.11 | Appendix - Measurements of fabricated CMOS neuron circuits          | )2             |

# Chapter 1

# Introduction

The human species, homo-sapiens, emerged an estimated 300,000 years ago. As modern humans we share, in large part, the same genes as our ancestors and our bodies and brains remain relatively unchanged. We have little common ground however in terms of how we live our lives and how we see the world. We can attribute this difference, despite our similarities, to our innate drive and ability to invent tools and ideas that have incrementally impacted how we are able to interact with the world over these millennia. This encompasses pre-historic inventions such as stone daggers for hunting and techniques to start fires; those from antiquity like religion, philosophy and bronze; all along the winding road of inventions through printing, economics and 5G telecommunications networks that have led us to this modern age. This thesis is concerned with another invention which, at the time of writing, is anticipated to give rise to a further incremental step on this path - artificially intelligent systems. Artificial intelligence (AI) is a scientific and engineering field concerned with the development of computer models that reproduce certain intelligent behaviours observed in animals such as reasoning, planning or learning. Since AI models and computers are fundamentally inter-twined, the term 'computer' is not only reserved for the computing machines with which we are today familiar, but importantly extends to any engineerable system that harnesses physical principles for computation. These computer models, other than developing theories of psychology and cognition, can also be applied in an engineering sense to solve practical problems. For example, the replacement or augmentation of human labour in monotonous or dangerous tasks, in complex tasks like medical diagnosis as well as applications which are otherwise unsuitable for humans such as the 'mining' of, or pattern extraction from, large and high-dimensional datasets.

The potential of the current generation of approaches in AI has been recognised both by governments and large technology corporations, which are jointly driving the rapid growth of its commercial application [1, 2]. However, lurking in the shadow of numerous grand success stories, there are fundamental drawbacks and limitations which, to support the anticipated growth, must be confronted. Principally there are environmental issues, concerning the spiralling quantities of energy demanded by state of the art AI models [3, 4] for incremental performance gains [5], the 'cloud-centric' application of AI instead of in distributed and resource constrained 'edge' environments [2] and ethical issues regarding the lack of model interpretability [6] and the absence of model uncertainty quantification in many cases [7, 8]. The progress in the field can be attributed predominantly to progress in underlying computing hardware, rather than a revolution from the algorithmic or modelling perspective, applied to 'connectionist', or 'neural network', AI models. This thesis explores how, in a similar spirit, an emerging technology called resistive memory can be married together with neural network models. It proposes a new, hardware-focused, approach that requires extremely low quantities of energy with respect to existing solutions. Additionally, in recognising the important role it has played in the development of the field via the tricks discovered by evolution, biological nervous systems will be used as a means of inspiration to guide the direction of the work.

Before introducing the content of this thesis in more detail, it will first be instructive to briefly recount the history of artificial intelligence, the computer hardware that has been used as a substrate in AI and elaborate upon some of the predominant problems faced by field which this work aims to address, in order to better understand its place and contribution.

## 1.1 A brief history of artificial intelligence

Although artificial intelligence would appear to be something new, being formally named in 1956 [9], the seeds that would go on to become the roots of the field were gradually sewn in the centuries before - during an AI 'pre-history'.

#### 1.1.1 Pre-history

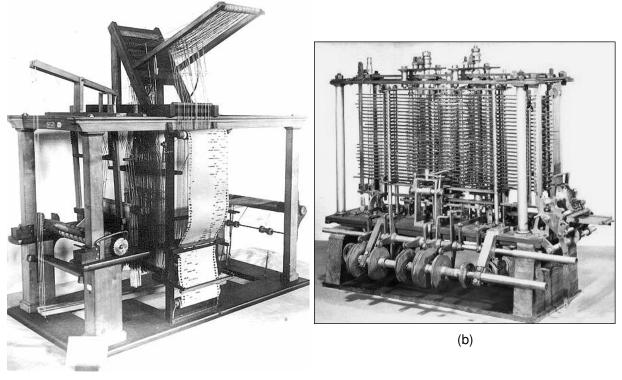

The link between artificial intelligence and computer science is unshakeable - if intelligence were to be implemented artificially, on what other substrate besides a 'computer' could it be realised? The first system bearing the hallmarks of computer would appear in 1804 in France - the Jacquard loom [10]. The loom was a fabric weaving machine, programmable via hole punched paper cards which determined routines to be executed with the apparatus (Fig. 1.1a). Some decades later, in 1832, Charles Babbage who was an admirer of the Jacquard loom, proposed a mechanical computer he called the Analytical engine (Fig. 1.1b), featuring an arithmetic logic unit, memory and a means of realising conditional flows and loops [11] - although it would never be built. George Boole would go on to formalise the mathematics of the logical manipulation of symbols (which had been evolving from the time of the ancient Greek philosopher Aristotle) in 1854 [12], before Alan Turing would take such concepts of logic and combine them with Babbage's ideas and propose the first digital computer system during the second world in 1936 [13]. The ideas of Turing would then be taken forward by the likes of the Hungarian scientist John von Neumann [14] who led the effort to manufacture the first binary stored-program Electronic Discrete Variable Automatic Computer (EDVAC) (Fig. 1.1c) architecture which remains widespread today. Largely it has been the manipulation of models, residing in the memory of the computer, by mathematical algorithms, which execute in the computers arithmetic centres, of these 'von Neumann' computers that has been the principal means of implementing and applying AI ever since.

(a)

Figure 1.1: **Early computer systems.** (a) A photo of a Jaquard loom. The hole punch card can be seen as a vertically running white sheet on the front face of the apparatus. (b) A model of the analytical engine proposed, but never built, by Charles Babbage. (c) Jon von Neumann stands next to a portion of the Electronic Discrete Variable Automatic Computer (EDVAC). (d) The beast robot consisting of large metal drum which, inside, contained a small network of transistors that controlled its movement.

Parallel to the development of the ideas that lead to modern digital computers, several important mathematical theories would also be developed during these centuries that would go on to lay the foundations of AI. In 1805, one year after the invention of the Jacquard loom and also in France, the mathematician Adrien-Marie Legendre published a paper on the least-squares regression method [15] which remains, two centuries later, one of the central concepts of subsets of approaches to AI based on the minimisation of an error metric of a model given some data. Later, an iterative method for solving such problems would be proposed by Augustine-Louis Cauchy in 1847 called gradient-descent [16]. At the time of writing, gradient-descent is arguably the most important algorithm in modern day artificial intelligence and, in a broader sense, the field of mathematical optimisation.

Remarkably, some decades even before Adrien-Marie, an English reverend and mathematician named Thomas Bayes wrote down a novel interpretation on probability theory [17]. What would come to be known as Bayes' rule described how, instead of calculating probabilities based on frequency of past events, a posterior probability could be updated through the product of a prior belief on this probability and the likelihood of a set of observations. Bayes actually did not publish this work during his lifetime, and his manuscripts were encountered by chance after his death in 1761 while his family were sorting through his possessions. Had they not been discovered, the French mathematician Laplace would also independently arrive at the same set of conclusions as Bayes half a century later in 1820 [18]. These techniques set the foundations for a statistical approach to artificial intelligence called Bayesian inference whereby a posterior probability is iteratively updated as new evidence becomes available [17]. A Russian mathematician Andrei Markov, also working in the field of probability theory one and a half centuries after Thomas Bayes, published several works describing what have become known as Markov chains [19]. Markov chains describe a random and 'memoryless' process whereby new states of an arbitrary system results from random permutations to its current state, offering a way to model systems with apparently stochastic characteristics. Markov chains and Bayes' theorem would eventually be married together in several works in the follow century, beginning with an article from Nicholas Metropolis and Stanislav Ulam on the Monte Carlo method [20, 21], and later expanded upon by Wilfried Keith Hastings [22], that set the groundwork for 'Markov chain Monte Carlo' (MCMC) sampling algorithms. Crucially, Markov chain Monte Carlo would allow for Bayesian inference to applied to problems where, in the majority of cases, conjugate likelihood and prior distribution pairs did exist and did not permit an analytical solution to the posterior [23]. At the time of writing, MCMC is considered to be of the most important and influential computer algorithms ever proposed [24], with a marked impact upon countless scientific and commercial fields artificial intelligence among them.

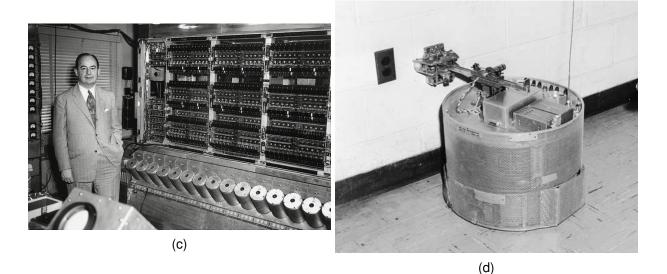

In the early 20<sup>th</sup> century, prompted by experimental results such as the measurement of action potentials propagating down the giant axon of the squid to trigger an escape response [25], a group of scientists who called themselves Cyberneticians, would begin to build 'bottom-up' models of animal nervous systems [26]. An early contribution to the field was made by Americans Warren McCulloch and Walter Pitts in 1943 when they proposed a model of a neuron that was activated as a function of a weighted sum of its input [27]. This would be followed with another model proposed by Alan Hodgkin and Andrew Huxley, based on their own experiments they conducted with the squid giant axon, that expanded on the ideas of the McCulloch-Pitts model by incorporating dynamical properties of neuronal membranes and the 'spiking' activation behaviour observed in the squid axon [28]. They would go onto receive the Nobel prize for their work in 1963. At the same time, a Canadian scientist named Donald Hebb proposed that neurons, described by such models, could organise themselves via correlative rules based on their co-activation as a means of adaptation and learning in the nervous system - an idea that would come to be called Hebbian

learning [29]. Successive works on the visual systems of *Drosophila* [30] and cats [31], would go onto recognise that networks of these neuronal elements were were capable of computing certain functions defined by their topology - respectively motion and edge detection. An early Cybernetic system, brought to life by a hard-wired network of neuronal like transistors, was the 'beast' robot - assembled by scientists at John Hopkins University [32]. The beast, a big metal can on wheels (Fig. 1.1d), was equipped with ultrasonic sensors on it's exterior which were connected to a small network of analogue logic circuits - culminating in no more than some dozens of transistors. The outputs of these gates controlled the wheels of the robot and, it is said, it would wander aimlessly around the corridors of the University avoiding obstacles and turning corners. When the beast was low on battery it would find, and plug itself into, an electrical socket. Then, when fully charged and ready to wander anew, it would un-plug itself and once again be on its way. The behaviour of the system has since drawn comparisons with the feeding and survival behaviours of simple uni-cellular organisms such as Paramecium [33] as well as multi-cellular organisms equipped with simple nervous systems such as the *C. Elegans* worm [34].

Figure 1.2: **Types of neuron models.** (a) The McCulloch-Pitts neuron model whereby the sum of the multiplication of the elements of an input vector **X** and a synaptic weight vector **w** is output by the neuron. (b An electrical circuit model for a neuron proposed by Hodgkin and Huxley that describes how parameters, such as the neuron membrane voltage  $V_c$ , evolves in time.)

#### 1.1.2 1950's, 60's and 70's

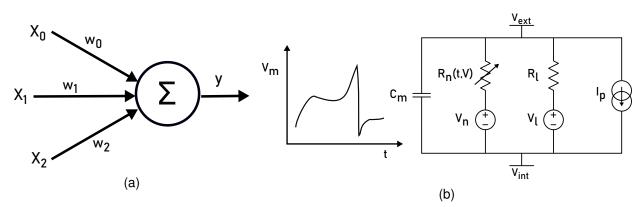

The first general purpose model inspired by biological neural networks was the perceptron [35], proposed in 1958 by Frank Rosenblatt. The perceptron is composed of layers (i.e. a multi-layer perceptron) of McCulloch-Pitts neurons. Each layer is networked by a so-called fully-connected matrix of synaptic edges, weights or parameters. Perceptrons allowed neurons to be leveraged as single linear units, in that they define a linear hyper-plane through their input feature space, which, through their combination in a network permitted non-linear functions to be implemented. An intuitive example of the utility of such networks is the three neuron, six synapse network which implements the non-linear XOR logic function [35] - something that cannot be solved with a single linear neuron alone. The parameters of early perceptrons were determined by optimisation techniques such as the Widrow-Hoff delta learning rule [36]. This was a first example of a supervised 'machine learning' algorithm whereby the model would learn, not in biologically-plausible fashion as Hebb had envisaged [29], but rather using iterative mathematical operations implemented in the arithmetic centres of von Neumann computers. In their rule, the difference between a 'teacher' signal and the actual output of the neuron units would be multiplied by the activation of the input neurons and a learning rate constant to provide the updates that were required to applied on the intermediate synaptic weight matrix. However, the delta rule could only be used to parameterise synapses in a two layer perceptron. A technique called automatic differentiation, proposed in 1970 by a Finnish master student called Seppo Linnainmaa [37], would facilitate, although not until one decade later, the 'training' of multi-layer perceptrons. In the meantime, another type machine learning approach, inspired by Darwinian theories of evolution, was developed and applied to the optimisation of models, such as the multi-layer perceptron, called genetic and evolutionary algorithms [38]. Such algorithms operate by mixing together properties of a previous 'generation' of candidate models, selecting the best according to some fitness metric and then 'breeding' together the parameters of the best, or the 'fittest', models to produce a new generation of models, and so on.

As an alternative to the 'black-box' optimisation of perceptrons, another prominent early direction of exploration was into models of symbolic reasoning. A first, extremely famous, example of such a model was the chess playing program developed by American electrical engineer Claude Shannon - the same Shannon who would later make even greater contributions to information theory - in the year 1950 [39]. Shannon's program searched a 'tree' of possible moves from a current game state using a search algorithm called minimax. After searching the tree to a certain depth, or a number of moves in the future, the algorithm 'backs-up' possible eventual outcomes to the top of tree and permits a decision to be taken regarding the optimal move (Fig. 1.3b). Some years later Arthur Samuel would augment Shannon's approach with a technique called 'rote' learning (this time using the game of draughts) where the algorithm would back-up and assign to nodes a measure of value based on the time to reward [40]. This concept of assigning value based on a temporal difference would set a foundation for a great number of algorithms that would be proposed in later decades. Another tree-based model, the goal-tree, was developed by James Slagle in 1963 [41], which took an initially complex integration problem and proceeded to use a set of pre-defined heuristic transformations to expand, therein constructing a tree, and simplify the original problem into a final form, at the terminal tree leaf nodes, that could be easily solved with another set of simple mathematical rules. Goal-trees were later applied to a set of problems known as 'block worlds', whereby the computer model was tasked with arranging scattered blocks on a table into a specific, user defined, arrangement - a non-trivial task requiring the computer model to reason and plan. In this case, based on a limited set of pre-defined logical rules and block manipulation functions, the computer would proceed to heuristically build a goal-tree and define a sequence of block manipulations required to obtain the required arrangement [42]. One feature of goal trees was that, after performing a set of actions, the computer model could be queried to explain it's reasoning by backing-up the tree it has just built - offering an interpretation of its actions. A related AI model, based on logical relations between 'symbols', were semantic networks, often called knowledge graphs, applied by Ross Quillan in 1966 [43] as a knowledge inference engine. Semantic networks are composed of nodes representing entities, and edges between the nodes explaining their relation or interaction and set the basis for the 'knowledge graphs' that underpin search engines like Google. For example, a directed edge in a semantic network 'is a' could connect the node 'cat' to the node 'animal'. In 1970, Patrick Winston would propose 'arch', or 'one-shot', learning whereby, an algorithm constructs a semantic network by inter-connecting symbols through specific relations consistent with examples presented to the model - building a comprehensive description of an object based on very few observations, or very few shots. An arch, for example, can be characterised by a horizontal block that is related to two vertical blocks below in that they support it, and those two vertical blocks were related to each other in that they do not touch each other (Fig. 1.3c) [44]. Unlike the delta learning algorithm used to train perceptrons, which required many training examples to produce incremental changes to model parameters, arch learning is capable of constructing and augmenting a number of relations between nodes from single examples. Additionally, like goal-trees, the resulting semantic graph also benefits from a means of interpretability. The culmination of these, and many other related ideas from this epoch that have not been discussed (such as constraint propagation [45, 46]), would ultimately lead to what were marketed as expert systems [47] in the 1980's. These systems incorporated knowledge into a hand-crafted logical model using control flow statements like if, then and else. Despite their perceived lack of elegance from AI practitioners, expert systems would ultimately mark the first time that an AI system was massively commercialised and applied to real-world problems.

Many of these approaches to machine learning, such as the application of the Widrow-Hoff delta rule to the perceptron, can be labelled as 'supervised' algorithms. Modern day machine learning is often split into three such categories - supervised, unsupervised and reinforcement learning. Ideas pertaining to the latter two were also proposed during these decades. Unsupervised learning algorithms, those without a teaching signal or labelled data, can trace their roots back to a paper in 1967 by Thomas Cover proposing the nearest neighbour algorithm [48]. Unsupervised learning algorithms, instead of learning to produce a desired output, looked for underlying structure in a set of data and use mathematical constructs, like euclidean distance from a common centroid or a parametric probability distribution, to group together similar data-points. (Fig. 1.3d). A few years earlier, in 1964, a Scottish computer scientist called Donald Michie, described the first reinforcement learning approach with his 'tabular' approach to noughts and crosses (tic-tac-toe) [49]. Perhaps for want of a computer, Michie demonstrated his idea using a set of 304 drawers, each containing coloured beads, and required a human operator to correctly move the beads between the drawers based on a small set of rules. Each drawer corresponded to one of the 304 possible game states of noughts and crosses and the colour of beads in each drawer corresponded to the possible actions taken from that state. For each step of the game, a bead was randomly sampled from the drawer of the current state by the operator and a nought or cross was placed accordingly. If the actions that were taken during a round of the game resulted in a loss, Michie's model would be 'punished' whereby the all of the drawn beads that were played in that losing game were removed from their drawers. In the event of winning a game, the model was 'rewarded' by placing three extra beads of the colours that were drawn in the respective drawers. This had the effect that, with an increasing number of iterations, the model would have a higher probability of choosing actions in game states it had already visited that would lead to an eventual victory.

Figure 1.3: **Examples of computer models applied in artificial intelligence.** (a) The perceptron model composed of an input layer of neurons, representing the input data points, and an output layer of neurons each of which corresponds to a prediction, normally a label, about the input. These outputs, y, are inferred using the dot product between the data X and the weight matrix W and then the weight vector can be updated, or trained, through the multiplication of the difference between a teacher signal t and the actual outputs y with the input data X and a learning rate  $\alpha$ . (b) A search tree model whereby each green circle represents a node, a specific state in a game of chess for example, and each blue branch that extends downwards a possible decision taken from that node. Blue upward pointing arrows provide a notion of backing-up the search tree, such that information about future states can inform what decision is taken in the current state - drawn as the green node at the top of the tree. (c An example of arch learning, using the task of learning the properties of an arch - drawn as the blue rectangular blocks. Arch learning allows the construction of a semantic network with relations (blue directed arrows) between nodes (green circles) that characterise the object to be recognised. (d) An example of a nearest neighbours unsupervised learning model whereby the distance between the centroid of a data cluster (green and blue crosses) and a new data point (white circle) can be used to determine to which cluster it belongs.

#### 1.1.3 1980's and 90s

The 1980's began with a proposal for what would become a hugely important neural network architecture, named the 'neocognitron' by Japanese computer scientist Kunihiko Fukushima [50]. The modelling approach known at the time of writing as convolutional neural networks would descend from this idea. In his paper, Fukushima draws heavily upon research into the architectural mechanisms uncovered in the visual cortex of the cat several decades earlier [31]. This 'bio-inspired' neural network architecture employed a combination of fixed and modifiable synapses which, contrary to later approaches with convolutional neural networks, would be trained using an unsupervised machine learning algorithm. Later in 1986, the automatic differentiation technique originally proposed in 1970 [37], was famously applied to train a multi-layer perceptron model - solving the credit assignment problem between network layers that had previously limited perceptron models [51]. This technique came to be known as backpropagation. Three years later, the 'universal approximation theorem' was presented by George Cybenko stating that a finite hidden layer of fully-connected neurons of such a multi-layer perceptron model was capable of approximating any continuous function [52]. The combination of backpropagation with universal approximators gave rise to tremendous expectation about the potential of such a modelling approach, although it would take further decades of innovation, by in large at the hardware level, before that potential would finally be realised. Backpropagation was extended to the setting of recurrent neural networks simultaneously by several scientists towards the end of the 1980s using a technique called backpropagation through time [53], whereby recurrent connections between neurons were defined, not with cyclic loops that were forbidden by backpropgation, but by 'unrolling' the network into several timesteps. In 1997 an important recurrent neural network architecture was proposed called the long short term memory network [54]. Somewhat like the neocognitron, long short term memory networks, incorporated specific connectivity patterns which permitted, for example, architectural mechanisms enabling functionality such as 'forgetting' which proved useful in the tasks related to time-series data.

In the 1990's Christopher Watkins would take forward the ideas of Donald Michie, thankfully this time with a digital computer, and Arthur Samuel and propose the reinforcement learning approach known as Q-learning [55]. Instead of a set of drawers containing beads, Q-learning uses a state-action 'Q-table'. Each cell of a Q-table contains a Q-value corresponding to the expected, temporally discounted, future reward based on taking optimal actions from that state. The Q-learning algorithm explores these states through interaction with an environment and uses the Bellman equation from dynamic programming [56] to populate, or learn, the state-value pairs in each cell. Around the same time, Richard Sutton would formalise the work of Arthur Samuel into what is now called temporal difference learning [57]. Temporal difference learning algorithms are characterised by a temporally decaying parameter called an eligibility trace that tracks the time since, for example, a particular state has been visited. This approach was applied in the 1994 by engineers working at IBM whereby a temporal-difference model learned, from self-play, to play the game of backgammon, eventually obtaining a 'master level' of performance [58]. IBM would also produce DeepBlue two years later that, despite being unsuccessful the first time around, would go on to beat the reigning world chess champion in 1997. DeepBlue employed a search-tree algorithm, largely similar to the minimax algorithm used by Shannon four decades before, called alpha-beta [59]. The success therein was not a substantial modelling innovation but rather the development of a massively

parallelised computer architecture that allowed faster and deeper search to be performed. With DeepBlue, IBM would go on to set two trends in artificial intelligence in the subsequent decades - that of applying 'brute force' computing to AI and also the use of public competitions as a marketing strategy of large corporations.

Similarly to how the neocognitron took architectural inspiration from biology, an American scientist called John Hopfield would, in 1982, take inspiration from the dynamical properties of biological neural networks and propose a new idea for how memories could be stored and accessed in a recurrently connected population of neurons [60]. The neurons of early 'Hopfield networks' were McCulloch-Pitts neurons which output either +1, if it's weighted input exceeded a threshold, or -1 otherwise. Under the condition of symmetrical connectivity, it was proven that, upon presentation of a static input pattern, the state of the network would tend towards a stable attractor of +1 and -1 activations - serving as an activation 'barcode' that represented a memory. New attractors could be formed in Hopfield networks through the Hebbian modification of synaptic parameters based on the co-activation of the pre- and post-synaptic neurons pairs. Two years later Hopfield networks would be implemented using neurons implementing a sigmoid activation function [61] and later with dynamical, Hodgkin-Huxley, neuron models [62] culminating in a research field dedicated to investigating 'attractor networks'. In the 1990's American physicist Carver Mead would draw analogues between the modulation of conductivity in neuronal ion channels in biological neuronal membranes and transistors [63] giving rise to a new field called 'neuromorphic' computing. Neuromorphic computing would concern itself with the bottom-up emulation of biological neural networks and biological Hebbian learning mechanisms, attractor networks for example, using sub-threshold analogue transistor circuit models of neurons and synapses.

These two decades also saw the proposal and demonstration of many other important supervised and unsupervised learning models and algorithms such as the self-organising map proposed in 1990 by Finnish scientist Teuvo Kohonen [64]. Additionally, in 1995, Vladimir Vapnik published a paper that combined a linear classification approach he had been developing since the 1960's called support vector machines [65], with a set of mathematical tricks called kernel methods that were also originally proposed in the 1960's [66]. The incorporation of the kernel trick into the support vector machine permitted an implicit projection of data, which was perhaps not linearly separable in its original space, into new space where it becomes separable using linear support vector machine classifier [67]. Another important idea, called boosting, was developed during the 1990's [68]. Boosting recognised the predictive power of a large ensemble of individually weak predictive models which, while alone were perhaps only slightly better than random guessing, together allowed particular subsets of models to specialise in the detection of specific features of a complex dataset. Boosting was combined with decision trees by Tim Kam Ho in 1995 to realise the important random decision forest machine learning algorithm [69].

#### 1.1.4 21<sup>st</sup> Century

In the current epoch it is perhaps not yet clear which new ideas will stick or not. At the time of writing, it seems like a period with little in the way of fundamentally new or radical ideas in how to build models of artificial intelligence and instead one where existing ideas have been supercharged by ever increasing computational resources. The key piece of computing hardware would become the graphics processing

units, the first of which was launched by NVIDIA, rather appropriately, at the turn of the century in 1999 [70]. Graphics processing units would ultimately pave the way for 'deep' multi-layer perceptron models to be trained using the backpropagation algorithm to achieve state of the art performance across a wide range of application domains. The approach was re-branded as 'deep learning' in order to distance it from previous failures regarding the optimisation of multi-layer perceptron models using backpropagation [71]. If artificial intelligence were a garden, deep learning is a massive Sycamore tree that is blocking out the light for a lot of the smaller, more fragile, plants. The first great success of deep learning was the application of a deep convolutional network model, named AlexNet, in the annual ImageNet image classification competition held in 2012 where it achieved a resounding victory [72]. AlexNet, a somewhat monstrous evolution of the 1980's neocognitron counting 60,000,000 free synaptic parameters, proposed a regularisation technique called dropout that prevented the model, which with the large number of parameters had so many degrees of freedom, from over-fitting. Dropout, another concept loosely inspired from biology, simply requires that, upon successive forward propagations, synaptic parameter values be temporarily set to be zero with some probability such that they do not contribute to the models prediction.

The next year, a British artificial intelligence company called DeepMind would demonstrate a deep reinforcement learning approach, called Deep-Q learning, that learned to play Atari games from experience [73] where a deep convolutional neural network model was employed as an approximation of the Q-table proposed in the 1990's [55]. Again it was a bio-inspired idea, based on theories of the mammalian hippocampus, called experience replay was the would prove to be the trick that would enable the Deep-Q model to obtain such an 'expert-level' of performance. Echoing the marketing strategy of IBM's DeepBlue in the 1990's, DeepMind famously defeated the European champion of 'Go' with their Alpha-Go deep re-inforcement learning model in 2016 [74]. Similarly to DeepBlue, Alpha-Go was based on a search-tree algorithm called Monte Carlo tree search [75] combined with of value and policy encoding deep learning models.

Deep learning models have also had a profound impact in natural language processing. Initially, this was thanks to deep recurrent neural network models, the long short term memory network for example. However, in 2014 'attention' models were proposed which would come to dominate natural language processing. Attention provided an architectural mechanism allowing models to focus on particular parts of a data sequence - whether it being an a certain area of an image or particular word in a phrase - similar in concept to the mammalian fovea. Initially deep attention models were incorporated into an architecture composed of recurrent neural networks [76]. In 2017 however, engineers working at Google proposed an attention model called Transformer. Transformer improved on the previous state of the art using an attention architecture that did not feature any recurrence [77] - leading many in the field to claim that recurrent neural networks were now redundant in such applications.

Another important deep learning architecture was proposed in 2014 called the generative adversarial neural network [78]. These models are actually a composite of two competing deep neural networks. The first neural network, the generator, is fed with noise it then uses to produce a 'fake' output data point - a fake image for example. The second network, the discriminator, is tasked with distinguishing this fake from a real data point. The two models are optimised simultaneously using backpropagation, whereby the objective of the discriminator is to minimise the error in the detection of the real data points while the generator is trained to maximise the error of the discriminator. Interestingly, the generator uses a de-convolutional neural network architecture to generate the fake images [79] - effectively a convolutional network flipped back-to-front.

Despite the truly seismic success of deep learning, serious concerns about model size, therein the number of synaptic parameters in the model, as well as the computational resources required to optimise all of those parameters during training throw its practicality into question [3, 4]. At the time of writing the largest models make use of a few hundred billion synaptic parameters [80]. This is particularly relevant in the context of memory and energy constrained 'edge' computing applications and has led to research into deep learning architectures and algorithms that allow model size to be significantly reduced. One such model, proposed in 2016, is SqueezeNet [81]. SqueezeNet offers a 50x reduction in model size with respect to the sixty million parameter AlexNet while being able to obtain an equivalent performance. The principal innovation of SqueezeNet was the proposal of the 'fire' module. Each fire module in the architecture is composed of a layer of point-wise convolutional filters followed by an expansions layer containing more point-wise filters but also larger convolutional kernels.

Another direction of research, resonating more with the ideas of John Hopfield and attractor networks, called reservoir computing emerged at the beginning of the 21<sup>st</sup> century. Reservoir computing is based on the idea that static, randomly recurrently connected neurons could project an input time-series into a new, possibly higher dimensional, space where temporal information pertaining to different classes of data points could be integrated into linearly separable neuron activation patterns. The two main approaches in reservoir computing are echo state networks [82], which employ neurons with continuous activation functions, and liquid-state machines [83], that use spiking neuron models. The two approaches can therefore be broadly dichotomised into favouring either the McCulloch-Pitts or Hodgkin-Huxley paradigms. Both approaches have been applied to problems in temporal pattern recognition, although their achievements have been largely overshadowed by the achievements of deep learning models applied to the same tasks. Despite being unable to match the performance of deep learning models based on graphics processing units, 'non-von Neumann' reservoir computing models implemented on an emerging class of computer called a 'neuromorphic processor', offers the prospect of a more energy efficient solution. Rooted in the ideas outlined by Carver Mead in the 1980's [63], the first system bearing the hallmarks of a neuromorphic processor was demonstrated in 2006 and consisted of an array of programmable analogue silicon spiking neuron circuits which could be inter-connected through further circuits models of the synaptic connections between neurons [84]. A more developed system, supported by an additional digital 'event routing' protocol was proposed in 2014 [85] and would be followed by a similar chip in 2015 which incorporated additional circuit implementations of bio-inspired Hebbian learning algorithms [86]. Fully digital neuromorphic processors were then released released by IBM in 2015 [87] and then Intel in 2018 [88] confirming the interest of large corporations in the development of neuromorphic, event-based, hardware. Such systems are referred to as non-von Neumann since they offer a means of distributed memory and parallelised computing, similar to the computation of the animal nervous systems on which the chips are based, in contrast to the centralised and sequential nature of the computing machines developed by the likes of Alan Turing and John von Neumann. However, it is important to note that both Turing and particularly von Neumann [14] also argued in favour of such brain-inspired computing solutions in the 1940's and 50's.

## 1.2 Hardware in artificial intelligence

Artificially intelligent computer models are intrinsically tied to computing hardware. It is no coincidence that the fathers of computer science, like Alan Turing, Donald Michie and Claude Shannon, were also the pioneers that developed early concepts in AI that still persist to this day. At the time of writing, the predominant computing architecture is the von Neumann stored-program computer. Von Neumann machines are coarsely defined as having separate memory and processing centres. Information encoded as strings of binary bits, describing either variables or arithmetic and logic instructions, are stored as digital words in the memory centre. The processing unit fetches these variables and instructions from defined addresses in memory, performs an operation on the variables as defined by the corresponding instruction and then writes the result back to another pre-defined location in the memory. Relative to the modern computers available at the time of writing, early systems were almost unimaginably constrained in terms memory and speed. Around the time that Arthur Samuel wrote his draughts playing program [40] for example, the state of the art computer was the IBM 1401. It disposed a mere 4kb of 8-bit memory and was clocked at a frequency of 87kHz. This permitted the equivalent of approximately one thousand operations per second [89]. You can imagine how aware of the underlying hardware the early AI practitioners had to be. As time progressed however, von Neumann computers would become faster and leverage more memory as well as benefit from architectural innovations such as parallelisation, cache memory [90] and multi-threading [91], such that gradually less and less thought was given to the underlying computation. However, for memory intensive techniques in AI, such as deep learning, computing hardware has once again become a limiting factor. This is not due to memory capacity, which continues to increase year on year, nor is it due to a limit in clock speed. The problem arises from the time and energy incurred in the transportation information between memory and processing centres. In reference to this, the term 'von Neumann bottleneck' was coined in 1978 [92]. This has driven the pursuit of alternative, non-von Neumann, hardware paradigms wherein the objective has been to reduce as much as possible the physical distance separating memory and processing - ideally to zero.

### 1.2.1 LISP machines

In the first decades of AI research and application, the go-to language for the implementation of tree, logic and knowledge based models was LISP [93]; deriving its name from LISt Processor in reference to the data structure and syntactic style central to by the language - the linked list. As a result of its popularity, a special purpose computer called a LISP machine was developed in the 1970's [94] whereby dedicated circuits allowed the acceleration of various LIPS specific operations and memory structures. These machines offered a speed-up of several factors compared to equivalent programs implemented on general purpose machines. However, as the use of the LISP language, and the approach to AI which it facilitated, declined during the 1980's and 90's, many LISP machine manufacturers would ultimately go out of business and general purpose von Neumann computers would go on to serve as the predominant substrate for AI.

#### 1.2.2 Field programmable gate arrays

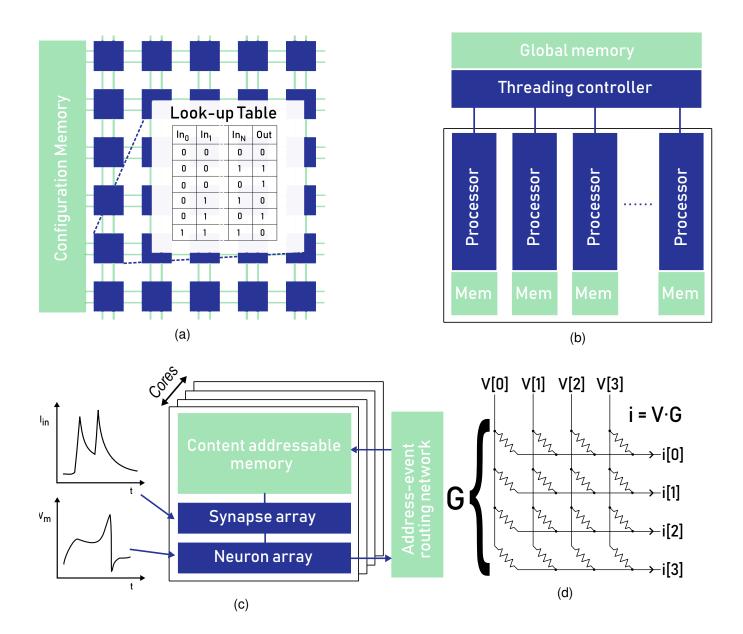

The earliest example of a non-von Neumann computing hardware is the field programmable gate array (FPGA), proposed in 1985 by the American company Xilinx [95]. FPGAs are effectively a two-dimensional array of configurable logic blocks (Fig 1.4a). Each block can be configured independently to implement basic logic operations, typically using a look-up table. The connections between neighbouring blocks can also be configured offering the possibility of realising large reconfigurable digital circuits. FPGAs distribute blocks of memory over the periodic 2D array which are responsible for storing the information which determines the logic and inter-connectivity for a subset of blocks. Naturally a body of work has focused on the implementation neural network architectures and deep learning algorithms, such as backpropagation [51], on FPGAs [96]. In particular the parallelisation of the dot(inner)-product operation, which underpins the forward and backward propagations required in deep learning, has been investigated. However, when benchmarked against application-specific integrated circuits (ASICs) implementing neural networks [97], FPGAs are generally acknowledged to incur penalties an order of magnitude greater in silicon area, power consumption and latency [98].

#### 1.2.3 Graphics and tensor processing units

Graphics and, more recently proposed tensor, processing units (GPU/TPUs) represent an evolution of central processing units (CPUs) through the incorporation of a parallelised architecture and multi-threading that allows the acceleration of mathematical operations, namely operations on matrices (Fig. 1.4b). Originally proposed, as suggested by the name, to accelerate the processing of images and video by NVIDIA in 1999 [70], the GPU has also been leveraged to accelerate AI models based on the manipulation of large matrices - principally deep learning [71]. Like CPUs, current GPUs [99], are configured to execute stored programs through the use of an interface called Compute Unified Device Architecture (CUDA) which provides access to the arithmetic units of the GPU from a high-level programming language and, although memory and processing and more distributed with respect to a CPU, they are still considered as von Neumann computers. Recently Google released the TPU that, unlike the GPU which is intended to be applied to a broad class of applications, is targeted solely on accelerating inference and learning algorithms related to deep learning [100]. While GPUs and TPUs achieve extremely high throughput and accelerate significantly deep learning models, they require a large amount of energy - a typical GPU at the time of writing will consume on the order of hundreds of Watts of power [101]. Their application is therefore largely limited to cloud computing and data centre settings. This however restricts the class of tasks to which such GPU-based AI models can address - in particular applications at the edge where energy and memory resources are constrained and perhaps intermittent.

#### 1.2.4 Neuromorphic processors

The energy requirements of GPUs and TPUs, when applied to artificial intelligence, are often contrasted with the estimated energy requirements of animal nervous which are capable of performing the same task (while of course performing countless other parallel tasks) but requiring many orders of magnitude less energy. This has driven interest in the field of neuromorphic computing [63], which aims to develop

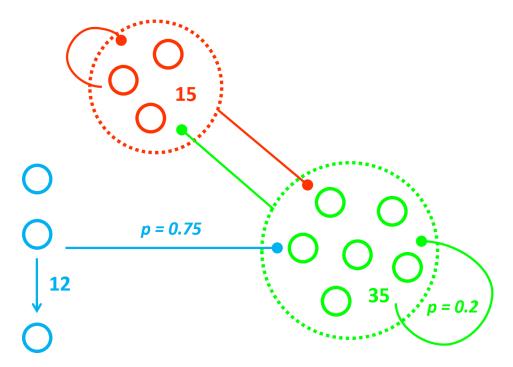

computing systems that imitate the bottom-up computational primitives of animal nervous systems in configurable, often self-configuring, silicon chips. It is believed that such a bottom-up approach, emulating the massive parallelism and distributed computation of the biological system, will lead to the realisation of a more energy efficient hardware that could support AI models which can be applied in the energy constrained setting of the edge. Numerous analogue circuits modelling the dynamical properties of biological neurons [102, 103] and synapses [104] have been proposed, leading to the first re-configurable arrays of such models in 2006 [84]. Later systems would be composed of multiple 'neuromorphic cores' [86, 85] that make use of content addressable memories [105] and a routing protocol called address event representation (AER) [106] to send information between neurons on the same core and between cores (Fig. 1.4c). AER assigns an address to each neuron and, since neuromorphic processors implement spiking neuron models like that proposed by Hodgkin and Huxley [28], transmit events from a source address neuron to, potentially, multiple target address neurons asynchronously.

Neuromorphic processors have also been realised using digital, instead of analogue, circuit models of neurons and synapses [87, 88]. The digital approach is appealing since, as technology nodes scale down, digital circuits become more energy efficient whereas analogue circuits face increasing design challenges and are not able to extract an equivalent benefit [107]. Furthermore, due to the increased mismatch between transistor dimensions and properties in more advanced nodes, large behavioural differences can exist between analogue circuit models that would ideally behave identically. To mitigate this, the dimensions of the transistors composing analogue circuit models are generally increased well above the minimum feature size of the node [108] - negating somewhat the benefit of using the more advanced technology nodes.

Other than providing a silicon substrate for defining dynamical neural network topologies, neuromorphic processors also support biologically-plausible learning and adaptation algorithms, such as Hebbian spike-timing-dependent-plasticity [109] for long-term memory formation as well as circuits implementing short-term plasticity [110] and also spike frequency adaptation [111]. At the time of writing, the field of neuromorphic computing, in particular the development of neuromorphic processors, is still emerging and currently faces a broad spectrum of challenges ranging from conceptual ones, regarding how to transfer results from computational neuroscience into neuromorphic computing models, to technical ones such as addressing bandwidth limitations and reducing levels of static power consumption due the AER based communication protocol [112]. The field would do well however, to appreciate the long timescales observed throughout the history of AI between the emergence of new ideas and their successful implementation.

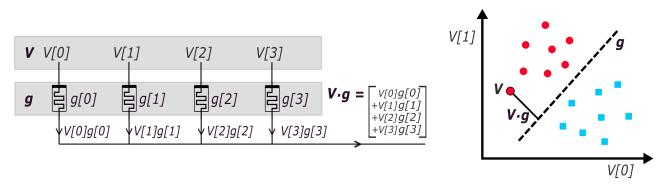

Figure 1.4: **Computing hardware supporting AI computer models.** (a) A field programmable gate array (FPGA) is composed of an array of configurable logic blocks (blue squares) which receive and send digital signals with their neighbouring blocks. The logic of each block is generally implemented using a look-up table. The logic of the look-up table and block inter-connectivity is determined using a memory that is generally shared by a subset of of blocks (b) Graphics processing units are generally composed of multiple processors, each with their own local memory, that execute in parallel on multiple cores. Their execution is determined by a global threading controller and a global memory. (c) Neuromorphic processors are composed of multiple neuron cores, each containing an array of neurons and synapses that, with either analogue or digital circuits, model their dynamical properties. A content addressable memory is used to interconnect neurons on the same core as well as neurons on other cores which communicate through a global address-event representation (AER) interface. (d) A dot(inner)-product operation can be implemented by applying features (V[0], V[1], V[2] and V[3]) of a voltage vector **V** of the columns of a cross-point array of resistive (conductive) elements **G**. The currents (i[0], i[1], i[2], i[3]) that flow out of each row correspond to the vector **i**.

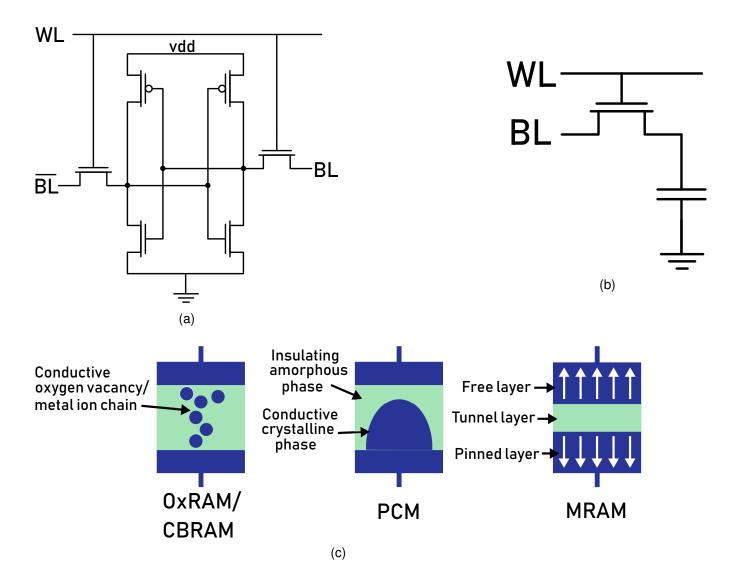

#### 1.2.5 Memory technologies

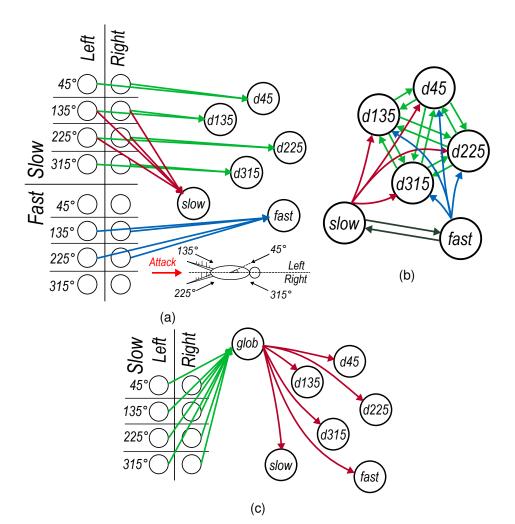

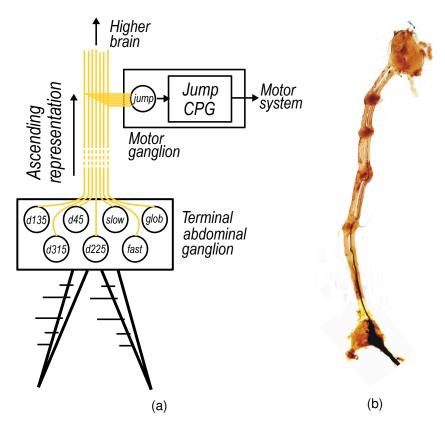

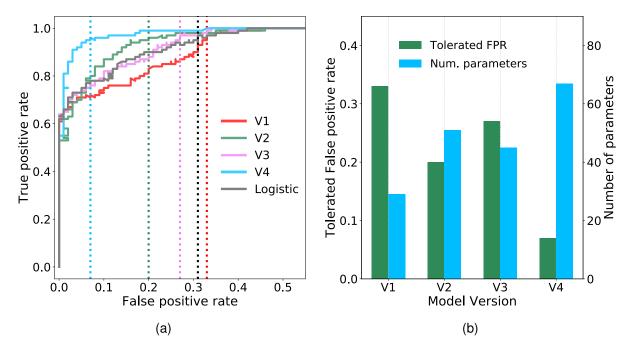

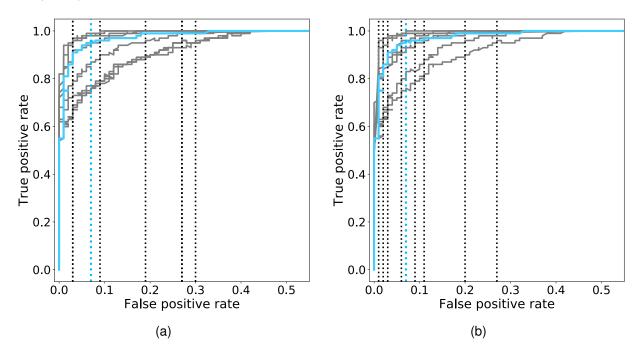

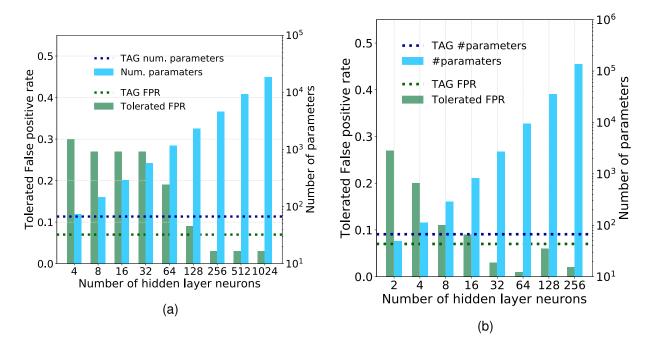

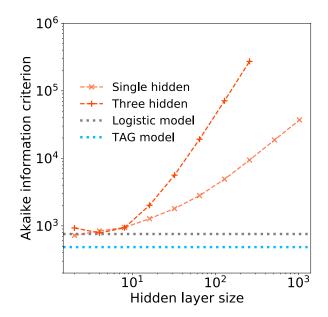

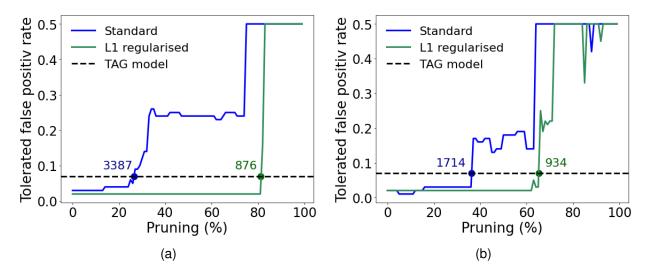

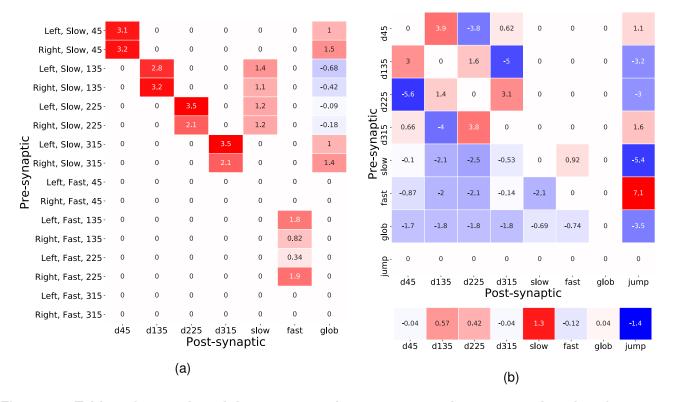

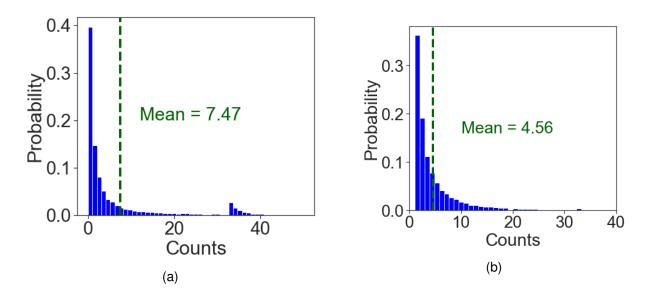

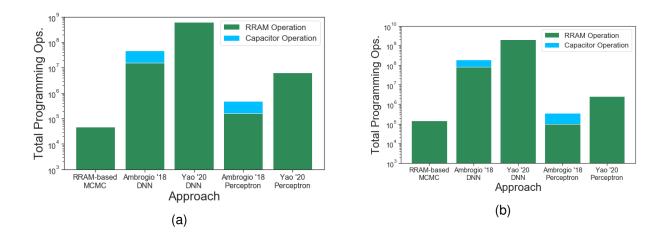

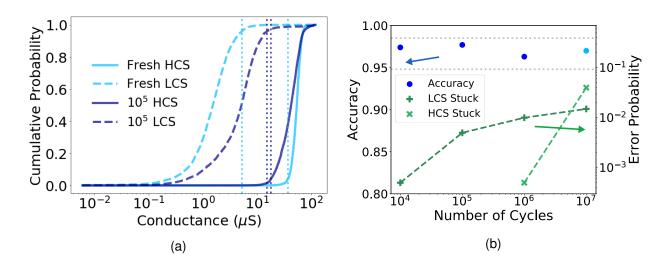

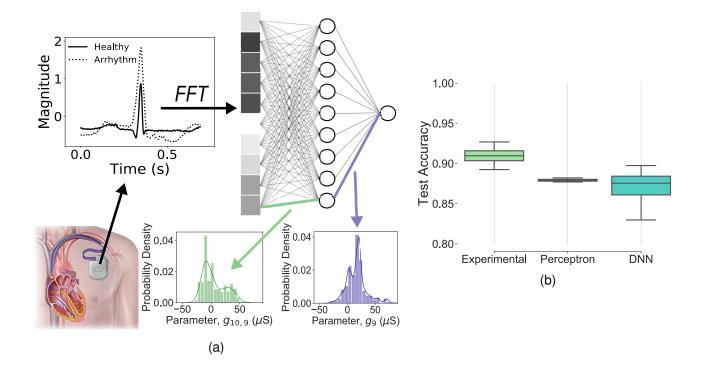

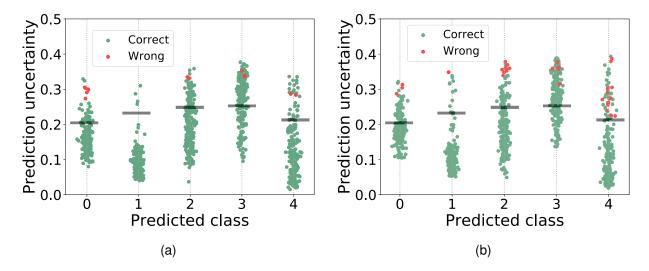

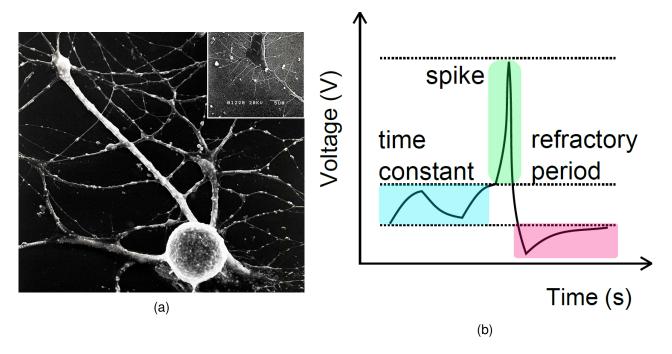

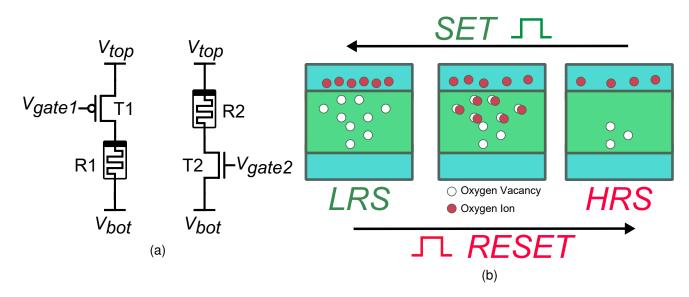

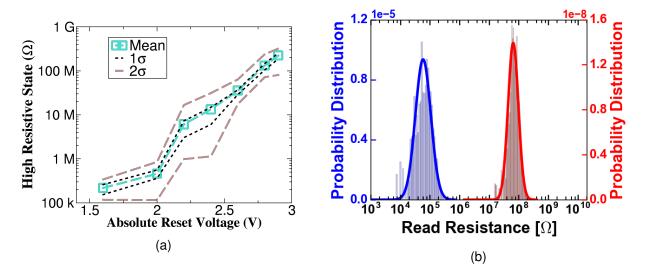

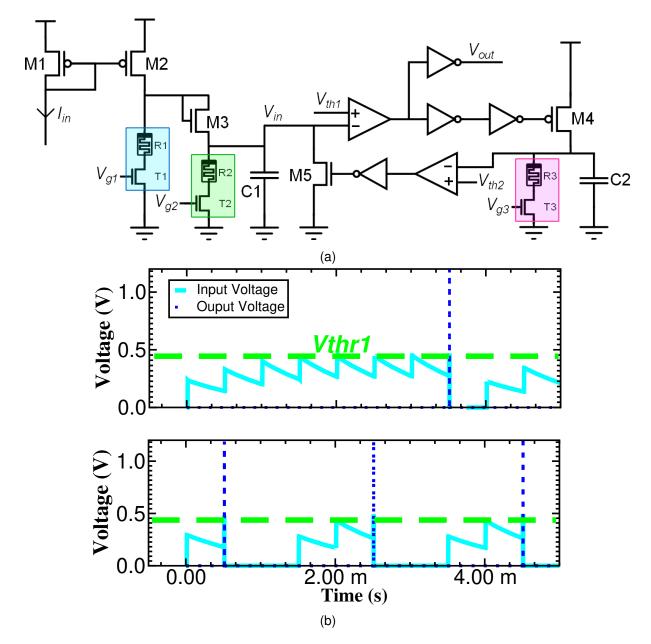

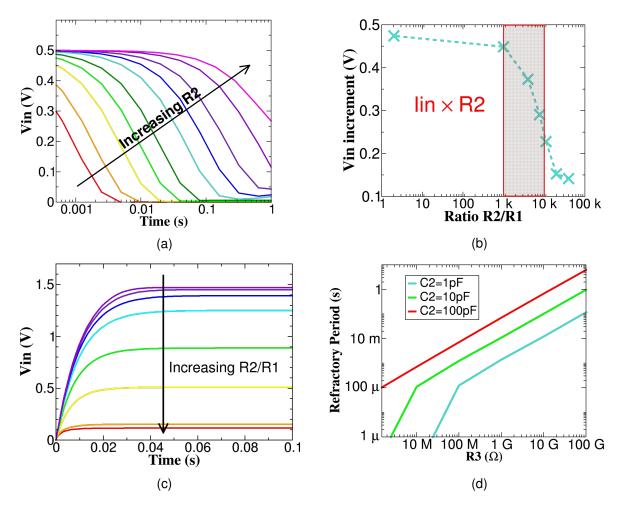

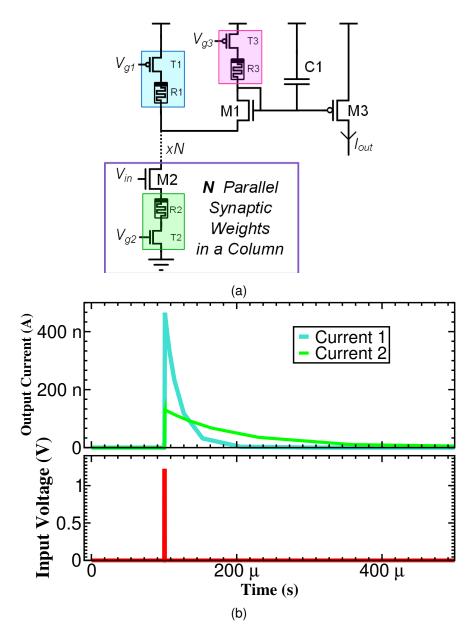

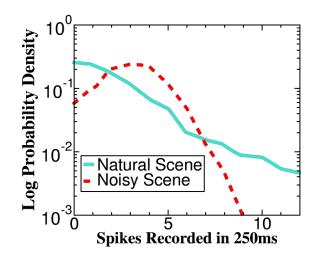

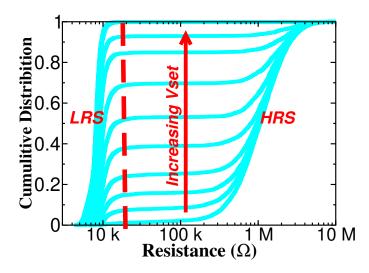

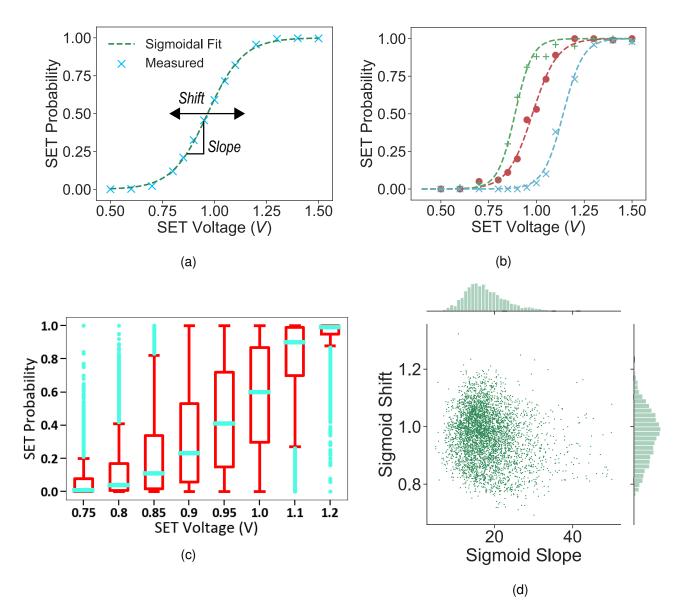

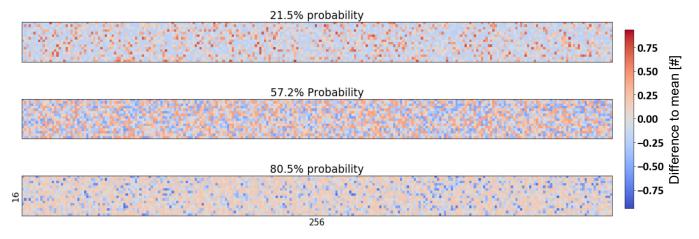

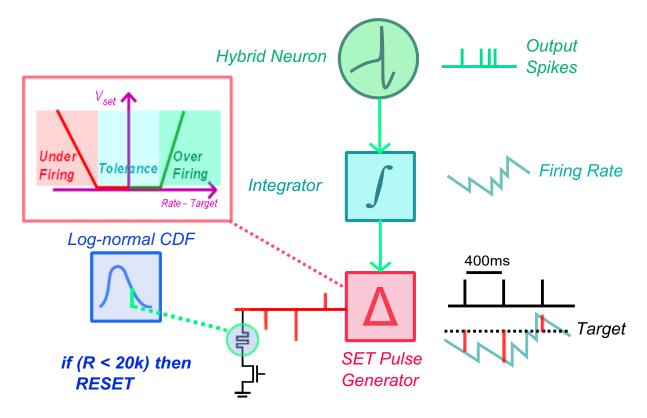

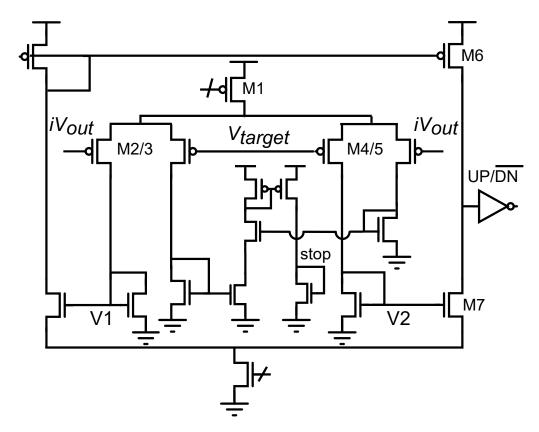

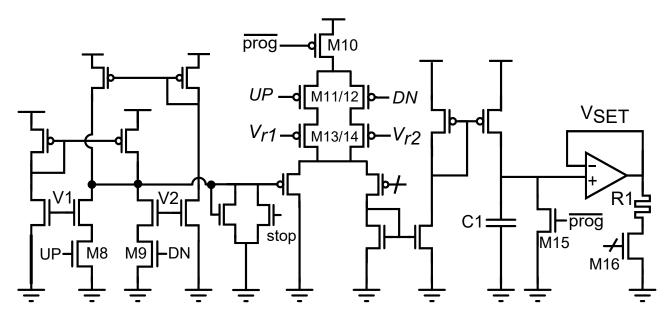

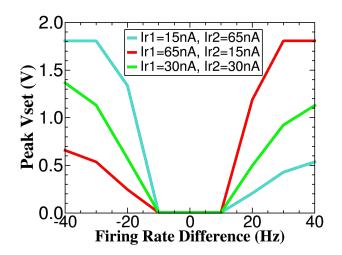

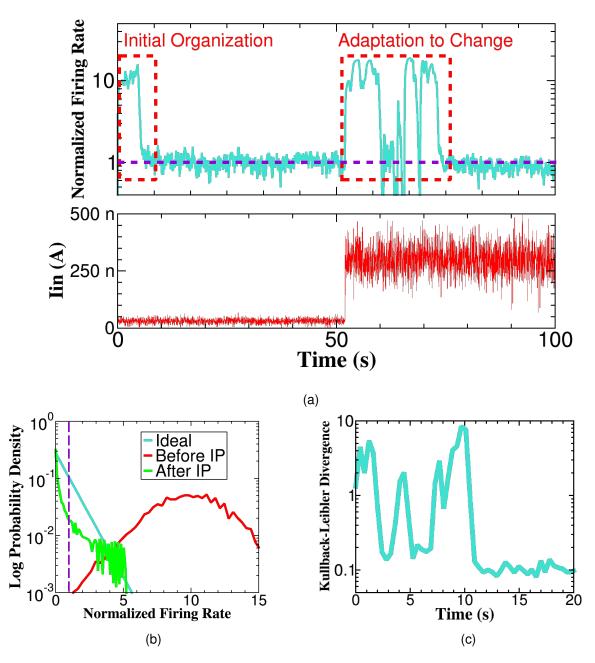

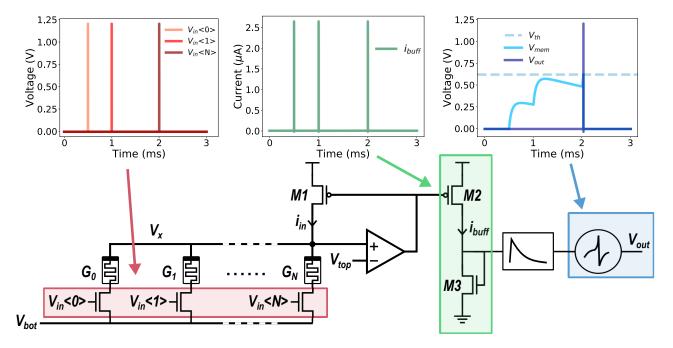

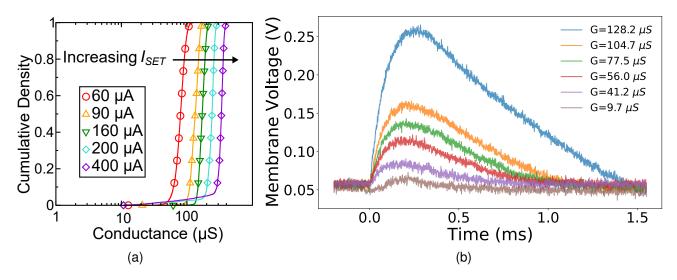

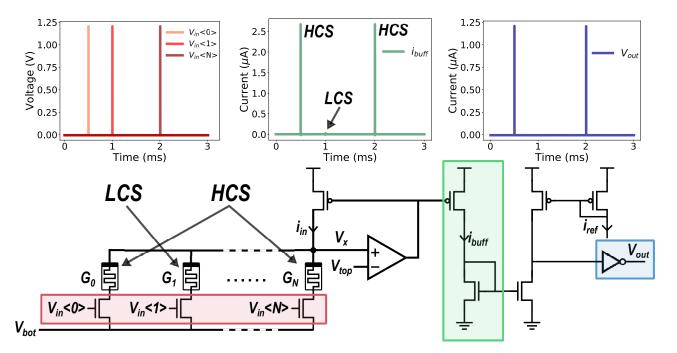

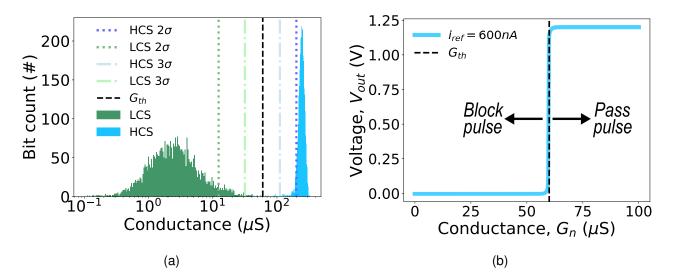

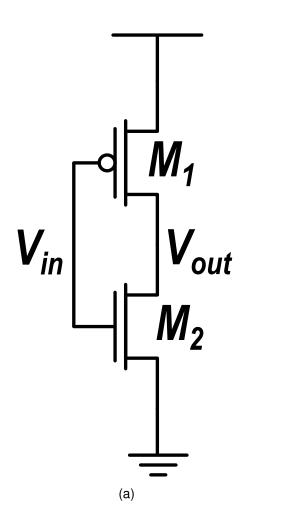

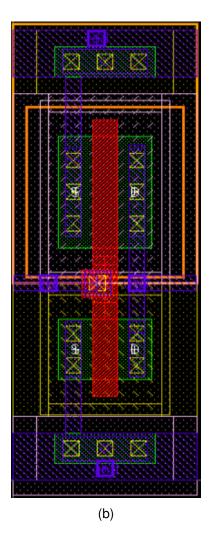

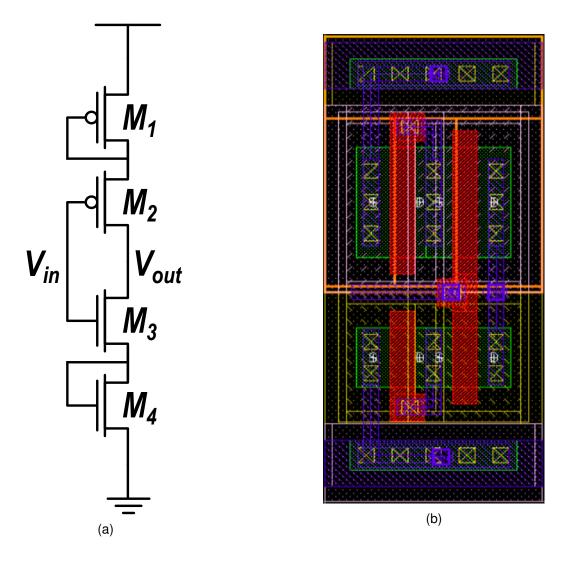

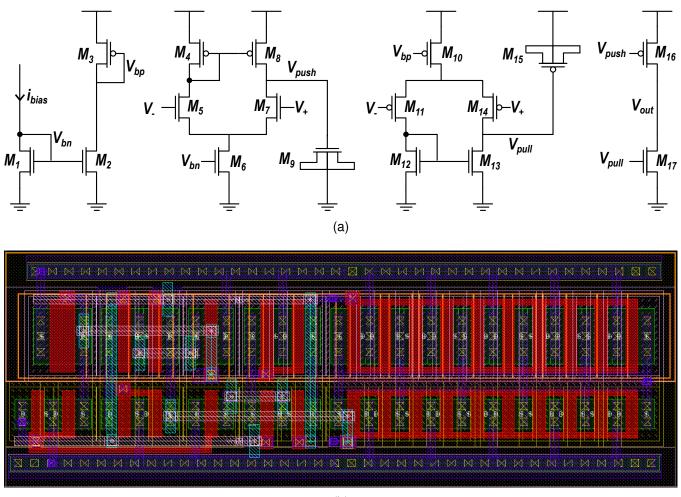

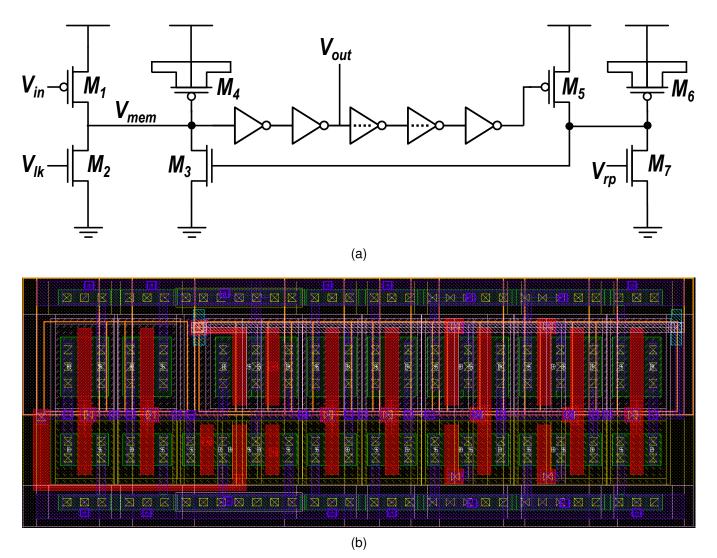

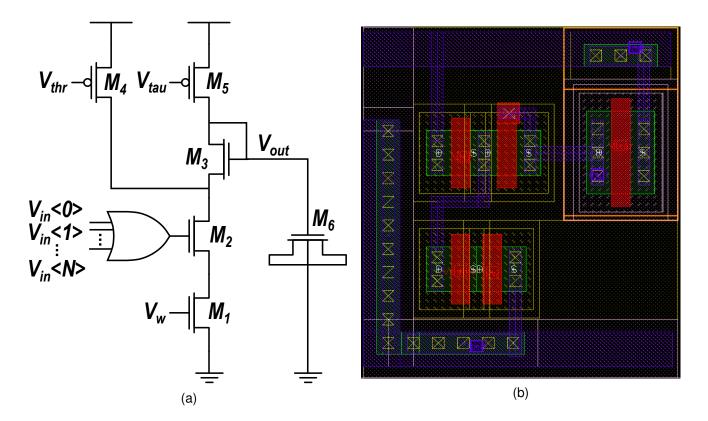

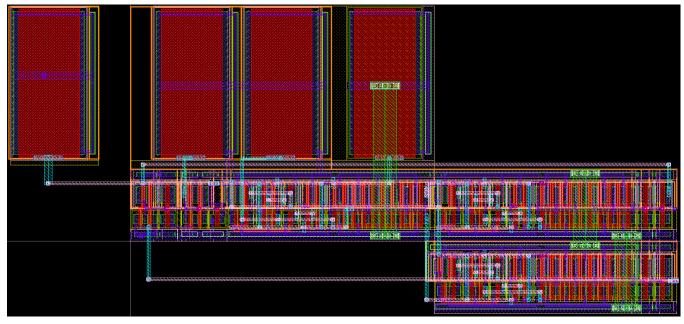

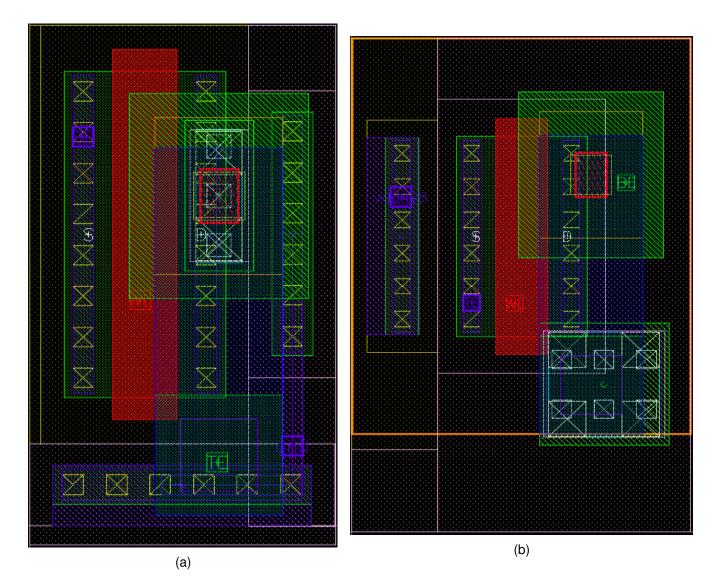

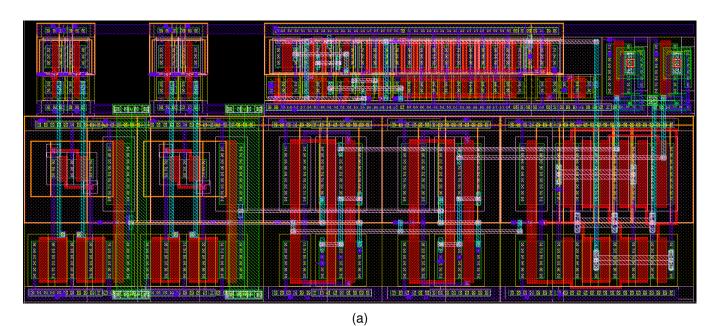

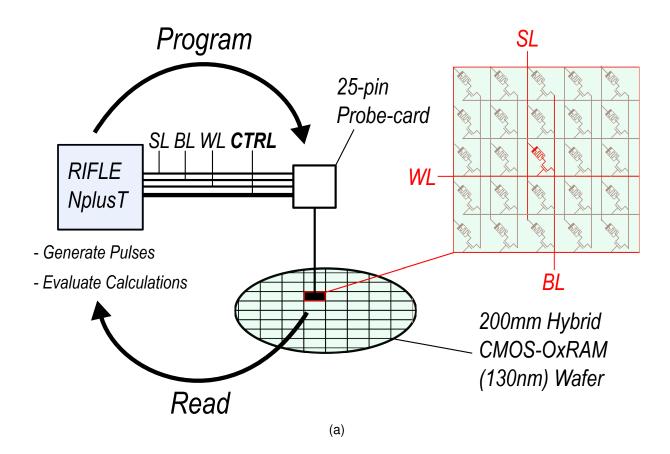

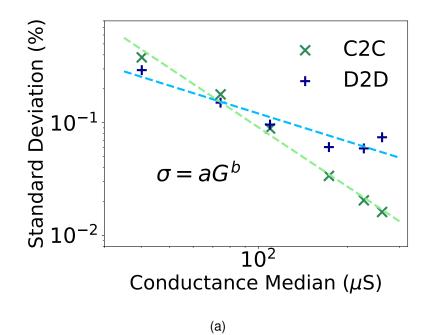

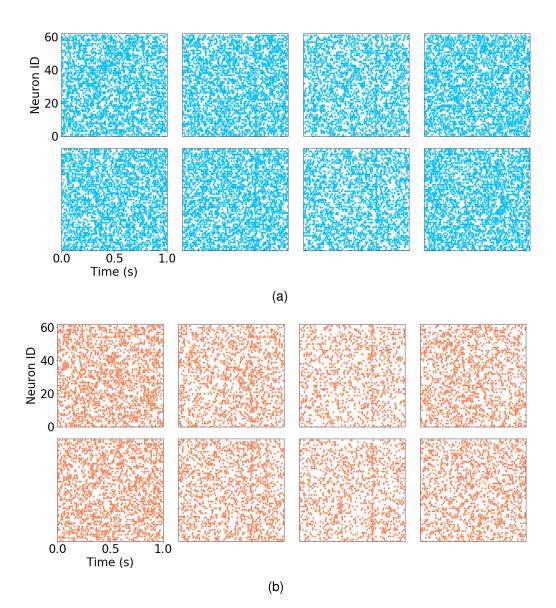

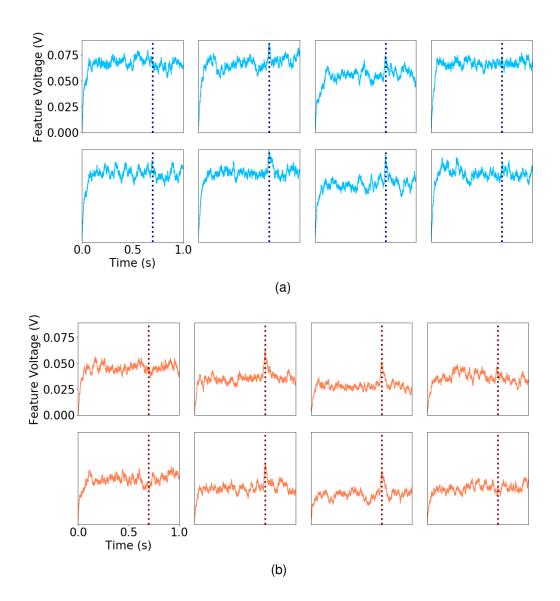

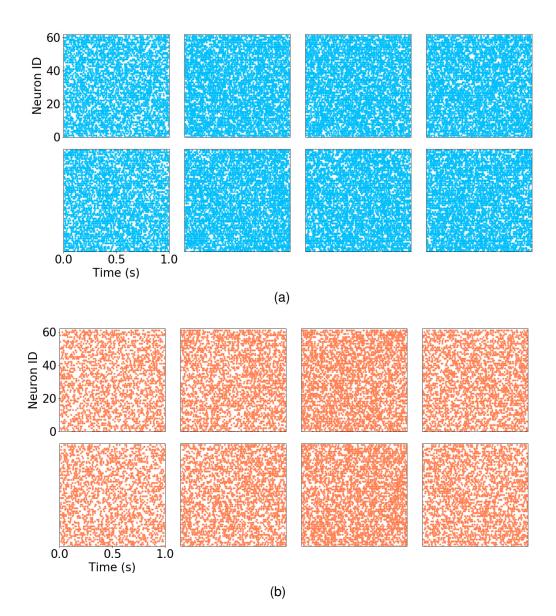

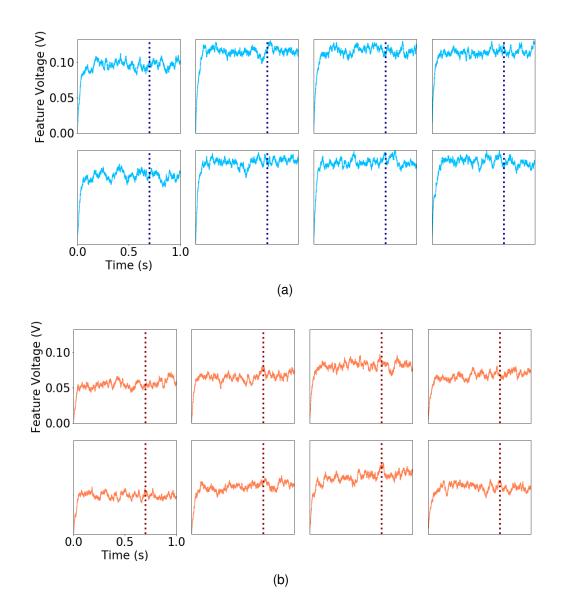

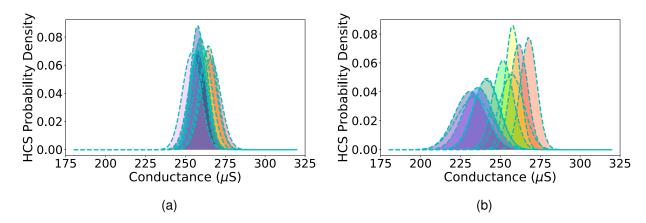

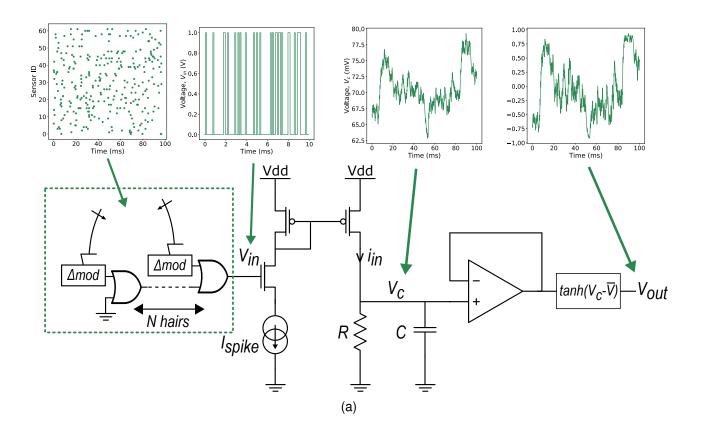

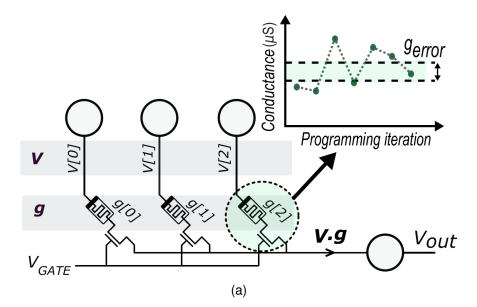

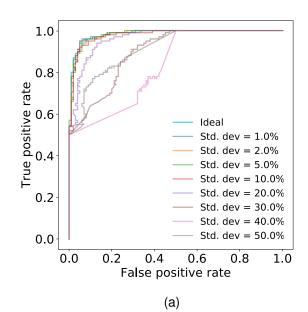

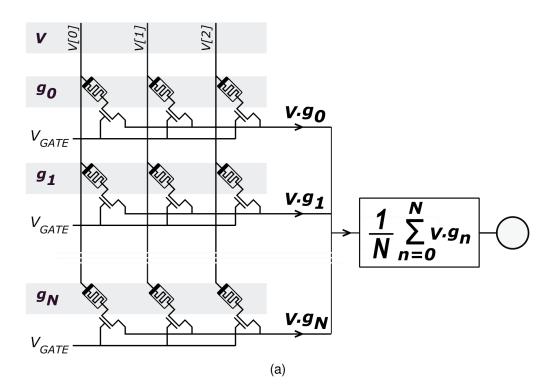

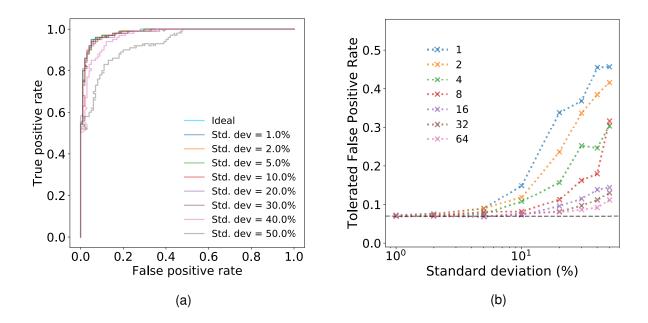

Computing hardware is dominated by memory. This is as true for the distinct memory centres of von Neumann chips as it is for the distributed memory blocks in FPGAs and neuromorphic processors. Models of artificial intelligence also hinge on memory which provides structure and brings them to life - whether it being the giga-bytes of memory required to define the synaptic weights of AlexNet [72] or the transient memories that are accessed through attractors in Hopfield networks [60, 61]. Memory is a concept that unifies concepts of learning, behaviour and planning in psychology but at the same time is something entirely tangible from a technological perspective. The right kind of memory technology could be the spark that illuminates new opportunities and methods for constructing the next generation of non-von Neumann machines that can support models of artificial intelligence more efficiently than those that exist today.