## Étude et conception d'une nouvelle architecture de déphaseur actif à 24 GHZ en technologie BiCMOS SIGE: C 0,25 $\mu$ m pour la formation de faisceaux

Bhanu Pratap Singh Jadav

#### ▶ To cite this version:

Bhanu Pratap Singh Jadav. Étude et conception d'une nouvelle architecture de déphaseur actif à 24 GHZ en technologie BiCMOS SIGE: C 0,25  $\mu$ m pour la formation de faisceaux. Electronique. Université de Poitiers, 2019. Français. NNT: 2019POIT2320 . tel-03463684

## HAL Id: tel-03463684 https://theses.hal.science/tel-03463684

Submitted on 2 Dec 2021

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

## **THÈSE**

Pour l'obtention du Grade de

## DOCTEUR DE L'UNIVERSITÉ DE POITIERS

FACULTÉ DES SCIENCES FONDAMENTALES ET APPLIQUÉES (Diplôme National - Arrêté du 25 mai 2016)

Ecole Doctorale : Sciences et Ingénierie des Systèmes, Mathématique, Informatique (SISMI)

SECTEUR DE RECHERCHE : ÉLECTRONIQUE, MICROÉLECTRONIQUE ET NANOÉLECTRONIQUE

PRÉSENTÉE PAR:

#### BHANU PRATAP SINGH JADAV

\*\*\*\*\*\*\*

ANALYSIS AND DESIGN OF A NEW 24 GHZ ACTIVE PHASE SHIFTER, INTEGRATED IN A BICMOS SIGE:C 0.25 μm TECHNOLOGY FOR BEAMFORMING APPLICATIONS

\*\*\*\*\*\*\*

DIRECTEUR DE THÈSE : **Jean-Marie PAILLOT**CO-ENCADRANT : **David CORDEAU**

\*\*\*\*\*\*\*

Soutenue le 13 Décembre 2019 devant la Commission d'Examen

\*\*\*\*\*\*\*

#### **JURY**

Rapporteurs:

Jean-Baptiste BEGUERET

Tchanguiz RAZBAN HAGHIGHI

Professeur à l'Université de Bordeaux Professeur à l'Université de Nantes

Examinateurs:

Julien SARRAZIN David CORDEAU Jean-Marie PAILLOT Maître de conférences HDR à Sorbonne Université Maître de conférences HDR à l'Université de Poitiers

Professeur à l'Université de Poitiers

## **ACKNOWLEDGEMENTS**

With immense pleasure and heartfelt gratitude, I would like to sincerely acknowledge the much-appreciated love, support and invaluable contributions extended to me throughout my PhD journey.

In this regard, I would like to express my initial thanks to Mr Dominique BAILLARGEAT, Professor at the University of Limoges and former Director of the XLIM laboratory, for having welcomed me to laboratory xlim and to finance a part of my thesis.

I would like to convey my sincere gratitude towards the Director of my thesis, Mr Jean-Marie Paillot, Professor at the University of Poitiers and Director of the University Institute of Technology of Angoulême, for offering me the opportunity to pursue PhD under his supervision. He has been generous in his encouragement and for his timely feedback. His energy and liveliness have been inspirational. I am grateful to him for inspiring my interests in the subject and his support throughout this entire period.

I am thankful also to my co-director Mr David Cordeau, Maître de Conference HDR at the University of Poitiers, for his critical feedback and the many detailed explanation of the integrated circuit designing from the initial phases of the thesis. The quality of his supervision, involvement and valuable scientific advices were instrumental in defining the path of my research.

I would like to express my appreciation to the committee members, Professor Jean-Baptiste Beguret, Professor Tchanguiz Razban Haghighi and Professor Julien Sarrazin, for accepting the request to validate my thesis and participate in my oral defence. I am also thankful for their insightful comments and positive suggestions.

A special thanks to Sébastien Soubie, Computer Technician at the IUT Angoulême, "the Genius" of the laboratory, for his high availability, his good humour, his kindness, his efficiency and his precious help.

I remain thankful to all these people for their support and involvement in my work, despite unforgiving deadlines and commitments.

Along with them, my sincere thanks to Smail Bachir, Claude Duvanaud, Fabrice Wateau, Regis Lucas, Emilie Remond and Thami Zeghloul who were always ready to provide academic assistance whenever needed. My sincere thanks also go to Nelly Gilley, for her care, guidance, understanding and moral support. Despite her busy schedule, she always kept a

watchful eye over me and provided me with her valuable advice whenever needed to balance my work life and personal life.

A special mention of thanks to my friends Amit Karel, Arjun Maheshwari, Parth Raj Singh and Shubham Maheshwari for their unconditional friendship and moral support during my PhD. The years would not have passed without the friendship and lighter moments with my laboratory colleagues, Mariem, Serguei, Abdu, Mohamed, Younes, Tayeb, Maissa and Bogdon. My colleagues played a significant role during my PhD by sharing their knowledge and experience. A special thank also goes to Marion Giraud, Jean Marie Barth, Catherine Martinon, Françoise Mercier, Pratik Purkayastha, Rachid Chowdury and Celine Chowdury for introducing me to the French culture, cuisine and becoming my family in France.

I owe my deepest gratitude towards my mother Bhragulata Jadav, my father Hukam Singh Jadav, my lovely sister Bhanu Priya Jadav and my brother-in-law Digvijay Singh Chauhan for their belief in me, their eternal support and understanding of my goals and aspirations. Their infallible love and support has always been my support.

In the end, I would like to extend my warm and heartfelt gratitude towards each and everyone who has impacted this work for their constant love, support and encouragement.

| List  | of figu                                                                                               | ires      |                                                  | V  |

|-------|-------------------------------------------------------------------------------------------------------|-----------|--------------------------------------------------|----|

| List  | of tabl                                                                                               | es        |                                                  | ix |

| List  | of Abl                                                                                                | oreviatio | ns                                               | xi |

| Gene  | ral In                                                                                                | troductio | on                                               | 1  |

| Chap  | oter I:                                                                                               | Introduc  | tion to the research work                        | 6  |

| Intro | ductio                                                                                                | on        |                                                  | 10 |

| 1     | 5G: 7                                                                                                 | The futur | re vision                                        | 11 |

|       | 1.1                                                                                                   | Key cap   | pabilities of 5G                                 | 12 |

|       | 1.2                                                                                                   | Applica   | tions of the 5G                                  | 14 |

|       | 1.3                                                                                                   | Spectru   | m for 5G                                         | 15 |

|       | 1.4                                                                                                   | Researc   | ch challenges in 5G and motivation of the thesis | 15 |

| 2     | Bean                                                                                                  | nforming  | g of Antenna array                               | 16 |

|       | 2.1                                                                                                   | Princip   | le of the antenna array                          | 16 |

|       | 2.2                                                                                                   | Uniforn   | n linear antenna array                           | 18 |

|       | 2.3                                                                                                   | Uniforn   | n planar antenna array                           | 19 |

|       | 2.4                                                                                                   | Control   | ling the shape of the radiation pattern          | 21 |

| 3     | Principle and state of the art of different methods to control the radiation pattern phase synthesis. |           |                                                  |    |

|       | 3.1                                                                                                   | Phase s   | ynthesis by Vector Modulators                    | 23 |

|       |                                                                                                       | 3.1.1     | Limitations                                      | 24 |

|       | 3.2                                                                                                   | Phase s   | ynthesis by using Coupled Oscillator Arrays      | 25 |

|       |                                                                                                       | 3.2.1     | Theory of oscillator                             | 25 |

|       |         |           | 3.2.1.1     | Oscillator's principle                  | 26                       |

|-------|---------|-----------|-------------|-----------------------------------------|--------------------------|

|       |         |           | 3.2.1.2     | Starting of oscillations                | 27                       |

|       |         | 3.2.2     | Coupled     | d Oscillator Arrays (COAs)              | 28                       |

|       |         | 3.2.3     | Limitati    | ions                                    | 31                       |

|       | 3.3     | Phase     | synthesis l | by Injection locked Oscillator Array (l | LOAs) 32                 |

|       |         | 3.3.1     | Injection   | n locking phenomenon                    | 33                       |

|       |         | 3.3.2     | Limitati    | ions of ILOs                            | 36                       |

|       | 3.4     | Contro    | olling the  | shape of the radiation pattern of a     | n antenna array through  |

|       | injec   | ction loc | ked oscilla | ator array                              | 39                       |

| 4     | The     | objectiv  | e of the di | ssertation                              | 41                       |

| 5     | Con     | clusion.  |             |                                         | 43                       |

| Cha   | pter II | : Behavi  | ioural and  | alysis of triple-push VCO and design o  | of a new triple-push VCC |

|       |         |           |             |                                         | 44                       |

| Intro | oductio | on        |             |                                         | 48                       |

| 1.    | Trip    | le-push ( | Oscillators | s                                       | 49                       |

|       | 1.1.    | Triple-   | push Osci   | illator principle                       | 50                       |

|       | 1.2.    | Oscilla   | ition mode  | es analysis in a triple-push oscillator | 51                       |

|       | 1.3.    | Differe   | ent archite | ctures of the triple-push               | 53                       |

| 2.    | Desi    | gn of the | e different | tial elementary VCO                     | 55                       |

|       | 2.1.    | Resona    | ance tank   | design                                  | 57                       |

|       | 2.2.    | Active    | part desig  | gn                                      | 62                       |

|       | 2.3.    | The lay   | yout of the | e VCO                                   | 63                       |

| 3.    | Desi    | gn of the | e different | tial triple-push VCO                    | 67                       |

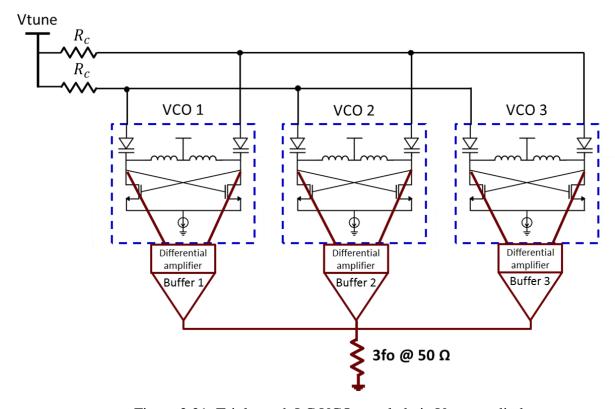

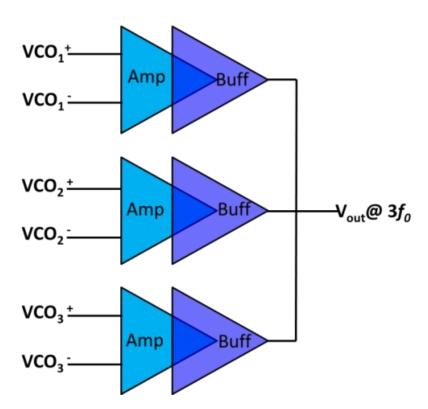

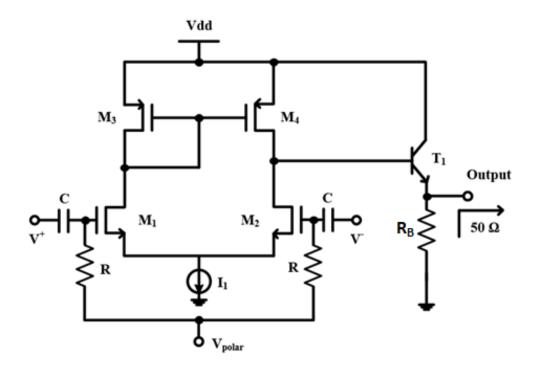

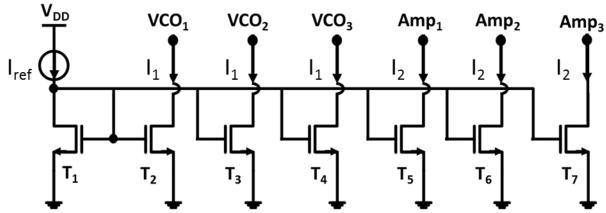

|       | 3.1.    | Design    | of the ou   | tput stage amplifier and buffer         | 68                       |

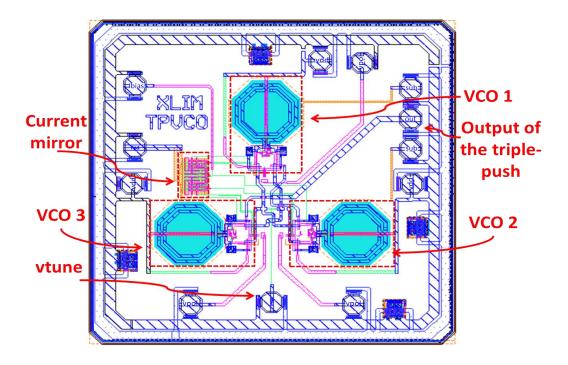

|       | 3.2.    | The lay   | yout of the | e Triple-Push VCO                       | 71                       |

|       | 3.3.    | The Po    | st layout   | simulation results of the TPVCO         | 72                       |

| 4     | Con     | clusion   |             |                                         | 76                       |

| Chapter III: Injection locked triple-push VCO based active phase shift | <i>er</i> 78                                                                        |  |  |  |  |  |

|------------------------------------------------------------------------|-------------------------------------------------------------------------------------|--|--|--|--|--|

| Introduction                                                           | 82                                                                                  |  |  |  |  |  |

| 1. The Injection locking phenomenon in a triple-push Voltage Cont      | The Injection locking phenomenon in a triple-push Voltage Controlled Oscillator. 83 |  |  |  |  |  |

| 2. The 120° phase shifter                                              | 84                                                                                  |  |  |  |  |  |

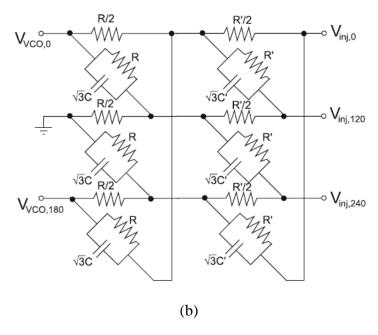

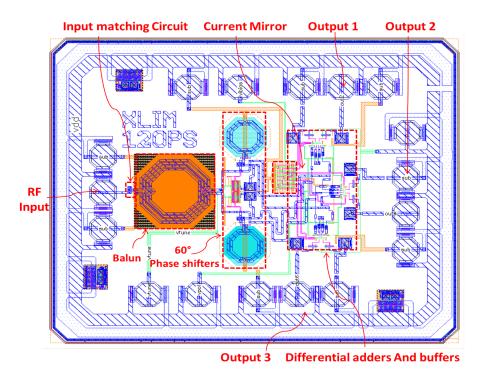

| 2.1. Design of a new 120° phase shifter at 8 GHz                       | 86                                                                                  |  |  |  |  |  |

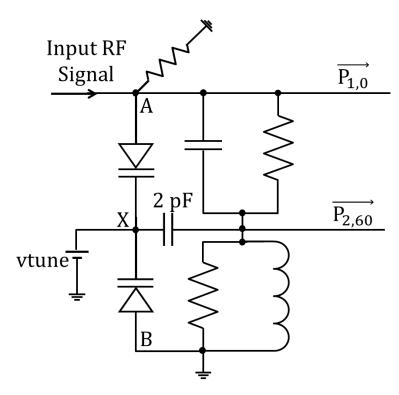

| 2.1.1. Analysis and design of the 60° phase shifters                   | 86                                                                                  |  |  |  |  |  |

| 2.1.2. Design of the 120° phase shifter by using differen              | tial adders88                                                                       |  |  |  |  |  |

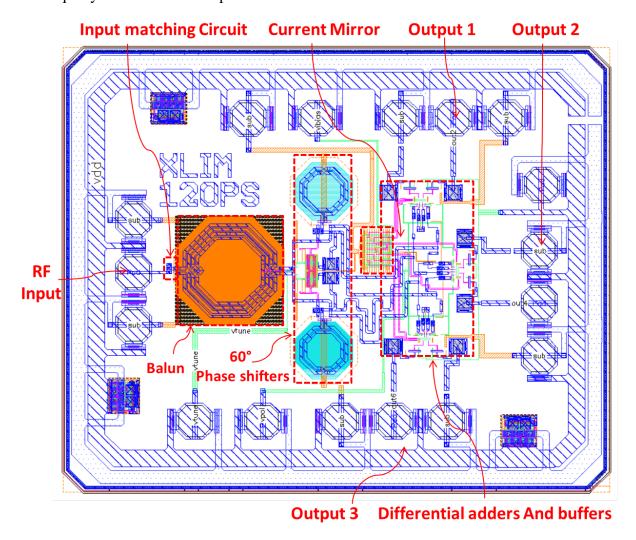

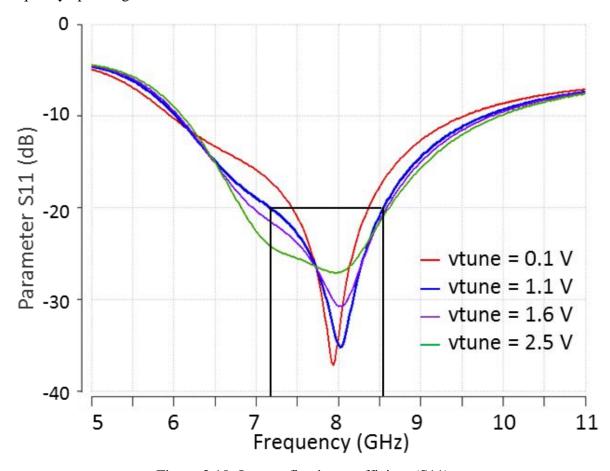

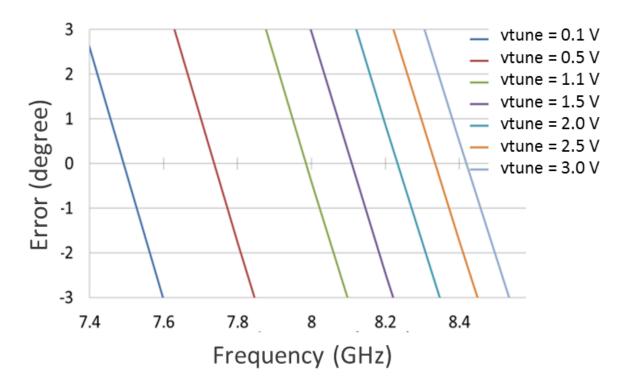

| 2.2. Post-layout simulation results of the 120° phase shifter          | 92                                                                                  |  |  |  |  |  |

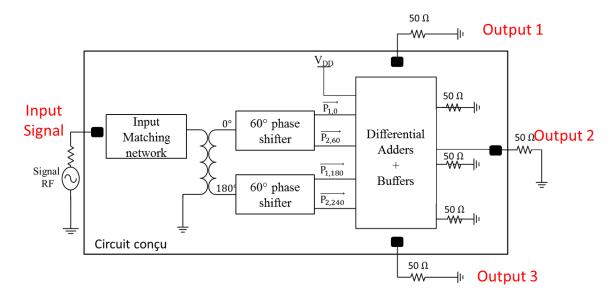

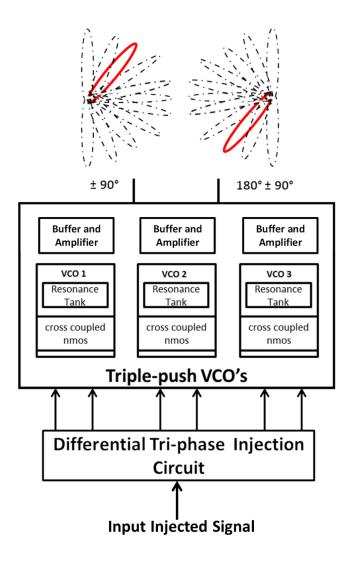

| 3. Injection-locked triple-push VCO based RF active phase shifter.     | 97                                                                                  |  |  |  |  |  |

| 3.1. The architecture of the Injection Locked Triple-push VCO          | (ILTPVCO) 100                                                                       |  |  |  |  |  |

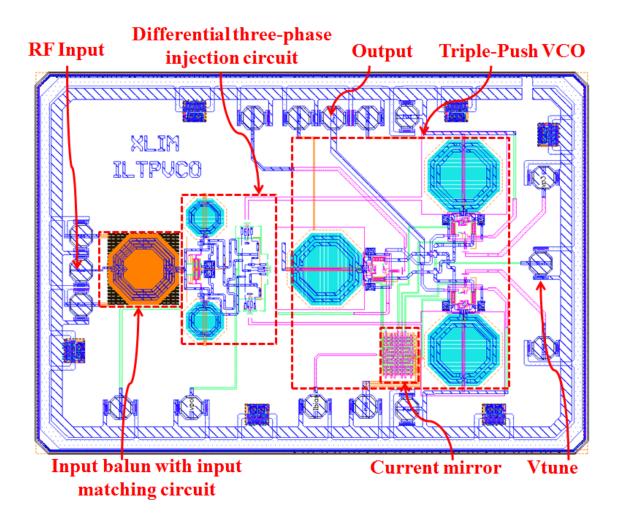

| 3.2. The layout of the IL TP VCO                                       | 103                                                                                 |  |  |  |  |  |

| 3.3. Post layout simulation results                                    | 104                                                                                 |  |  |  |  |  |

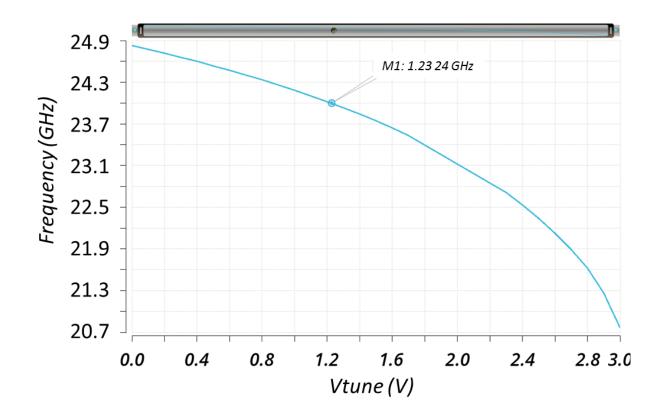

| 3.3.1. The performances of the active phase shifter with               | out injection 104                                                                   |  |  |  |  |  |

| 3.3.2. The performances of the active phase shifter with               | injection 105                                                                       |  |  |  |  |  |

| 4. Resume of the phase shifter results                                 | 108                                                                                 |  |  |  |  |  |

| 5. Conclusion                                                          | 110                                                                                 |  |  |  |  |  |

| Final Conclusion                                                       | 111                                                                                 |  |  |  |  |  |

| List of scientific publications                                        | 115                                                                                 |  |  |  |  |  |

| Résumé en français                                                     | 116                                                                                 |  |  |  |  |  |

| eferences 126                                                          |                                                                                     |  |  |  |  |  |

## **List of figures**

| Figure 1.1: Advancement of the 'G' Technology [source: www.softwaretestinggenius.           | .com].  |

|---------------------------------------------------------------------------------------------|---------|

|                                                                                             | 11      |

| Figure 1.2: Enhancement of key capabilities from IMT-Advanced to IMT 2020 [4]               | 13      |

| Figure 1.3: 5G Spectrum GSMA Public Policy Position, November 2018.                         | 15      |

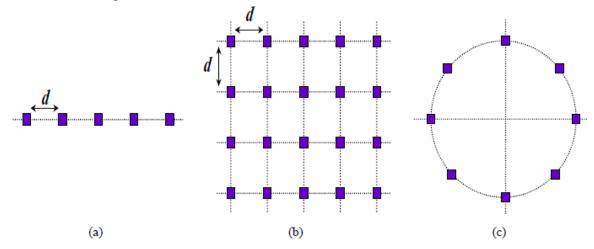

| Figure 1.4: Examples of geometric configurations of the antenna array: (a) linear, (b) p    | olanar, |

| and (c) circular                                                                            | 17      |

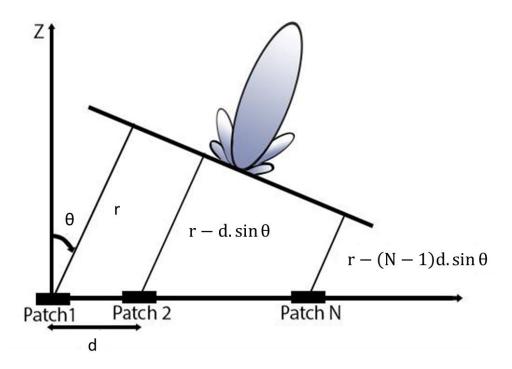

| Figure 1.5: Representation of a uniform linear array                                        | 19      |

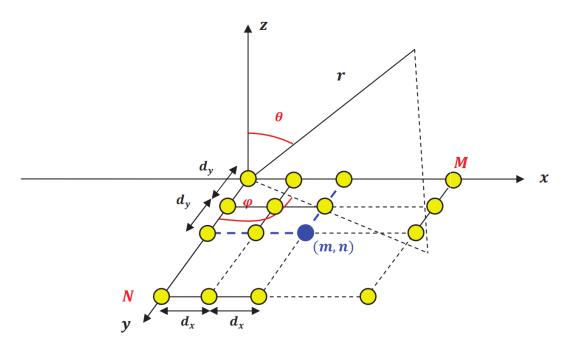

| Figure 1.6: Rectangular planar antenna array.                                               | 20      |

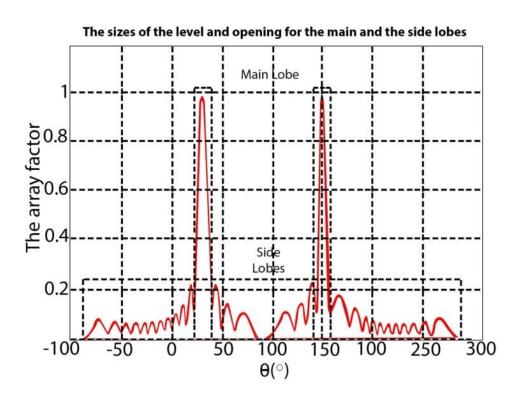

| Figure 1.7: Main lobe and side lobes level of the radiation pattern of an antenna array     | 21      |

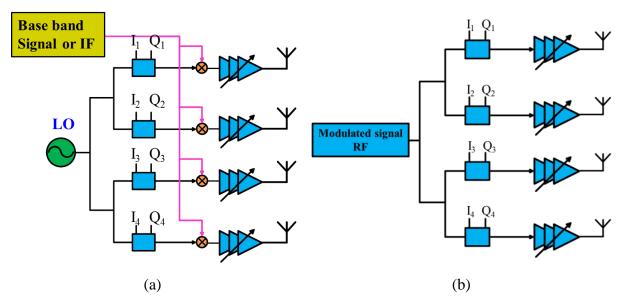

| Figure 1.8: Vector modulator architecture used on (a) LO path; (b) RF path                  | 23      |

| Figure 1.9: Block diagram of a common vector modulator-based active phase shifter [20       | ]24     |

| Figure 1.10: Examples of different periodic signals                                         | 25      |

| Figure 1.11: Linear model of an oscillator                                                  | 26      |

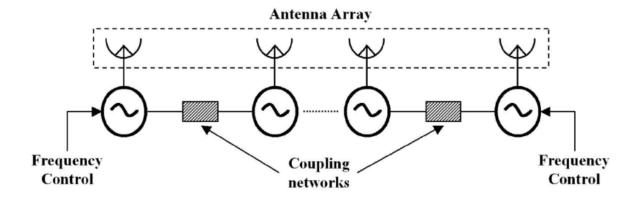

| Figure 1.12: Block diagram of an array of N coupled oscillators                             | 29      |

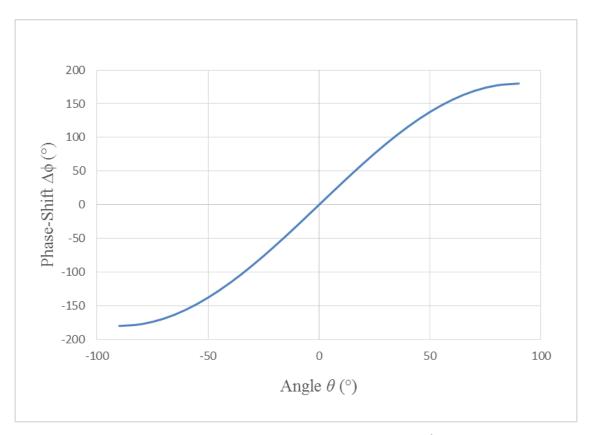

| Figure 1.13: Phase-Shift versus the angle $\theta$                                          | 29      |

| Figure 1.14: Two resistively coupled oscillators                                            | 30      |

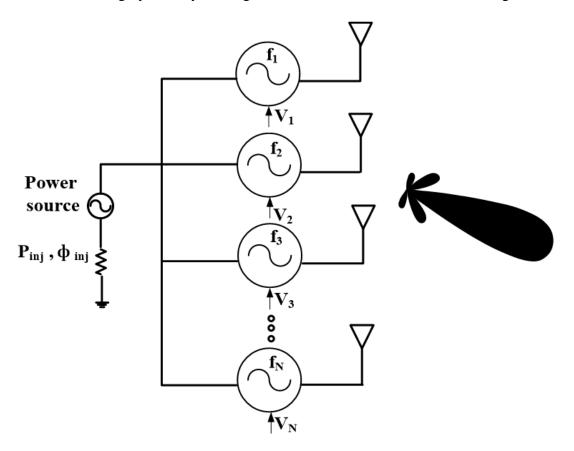

| Figure 1.15: General architecture of a phased-array transmitter using an ILOA               | 32      |

| Figure 1.16: Simplified model of (a) LC oscillator (b) LC oscillator under injection        | 33      |

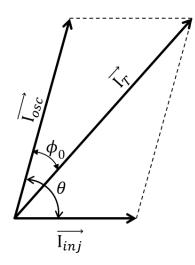

| Figure 1.17: Phasor diagram of the ILO of figure 1.16 (b)                                   | 34      |

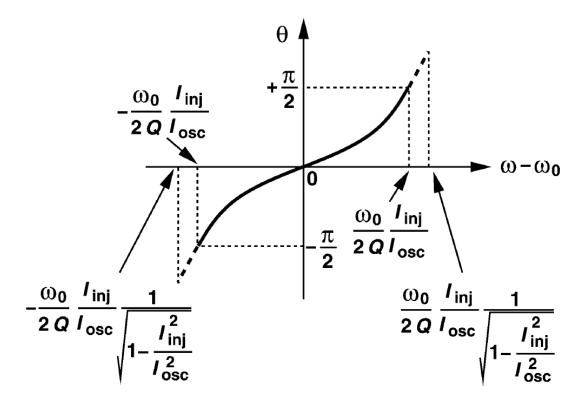

| Figure 1.18: Phase shift in an injection locked oscillator [40].                            | 36      |

| Figure 1.19: Phase variation in an ILO                                                      | 37      |

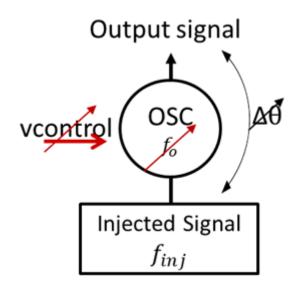

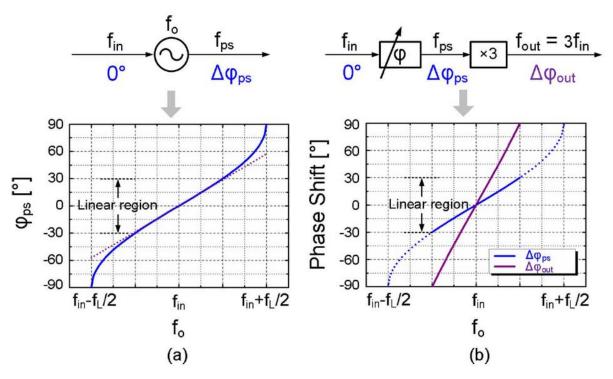

| Figure 1. 20: (a) Phase shift variation of an injection locked oscillator, (b) Linear Phase | e shift |

| variation by using a frequency tripler [22].                                                | 38      |

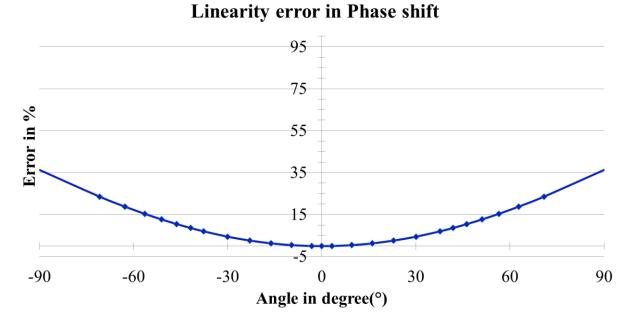

| Figure 1.21: Calculated linearity error of the phase shift obtained by injection locking    | in the  |

| oscillator.                                                                                 | 38      |

| Figure 1.22: Block diagram of an antenna array controlled by an ILOA.                       | 39      |

| Figure 1.23: Injection locking in a planar antenna array                                    | 40      |

| Figure 1.24: Schematic of a hybrid antenna array                                            | 41      |

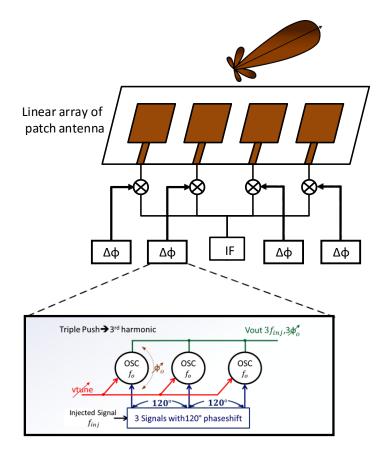

| Figure 1 25: The architecture of the proposed active phase shifter.                         | 42      |

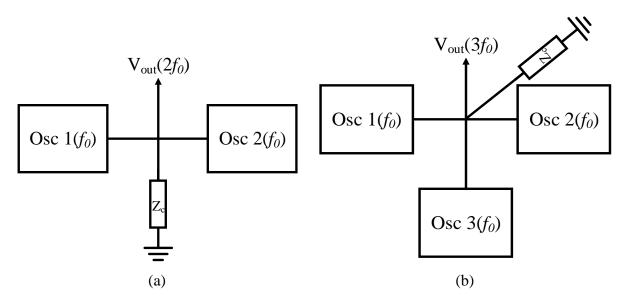

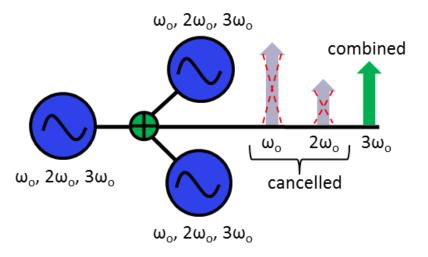

| Figure 2.1: Design of (a) Push-push oscillator and (b) Triple-push oscillator               | 49      |

## List of Figures

| Figure 2.2: Triple-push oscillator operation                                                          |

|-------------------------------------------------------------------------------------------------------|

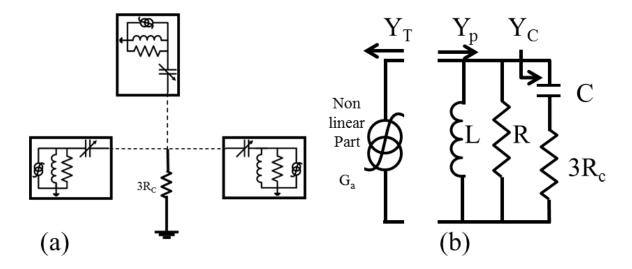

| Figure 2.3: Triple-push equivalent circuit model in the odd mode                                      |

| Figure 2.4: Triple-push equivalent circuit model in even mode                                         |

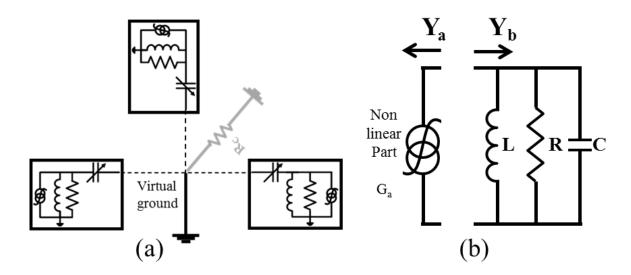

| Figure 2.5: Different modes of oscillations for the triple-push oscillator53                          |

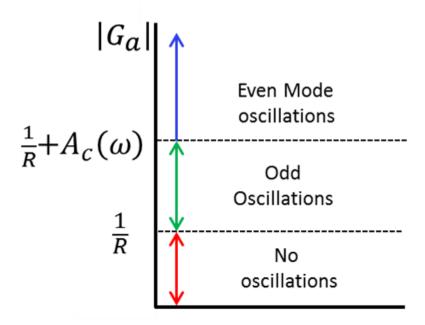

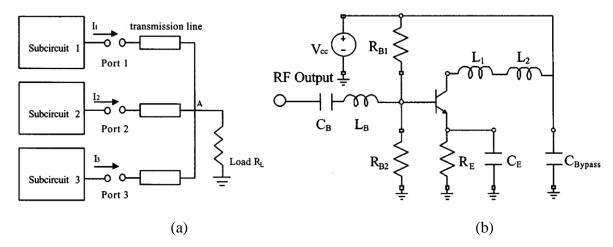

| Figure 2.6: (a)Triple-push architecture by Yu-Long Tang and Huei Wang [47], (b)                       |

| Architecture of the subcircuit oscillator                                                             |

| Figure 2.7: Triple-push architectures (a) by B Çatli and M M Hella [52], (b) by C C Li, C C           |

| Chen, B J Huang, P C Huang, K Y Lin, and H Wang [54]54                                                |

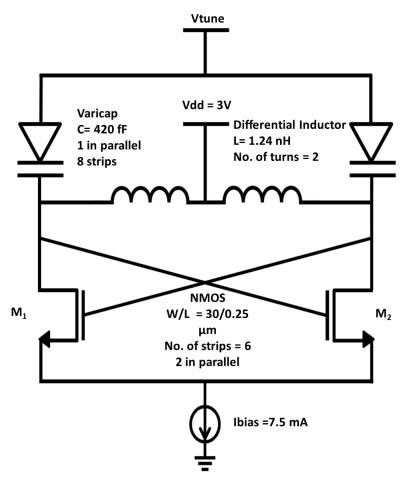

| Figure 2.8: Schematic of the differential LC VCO                                                      |

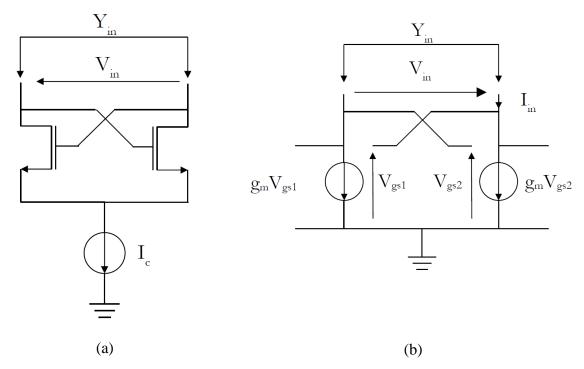

| Figure 2.9: (a) Admittance $Y_{in}$ presented to the resonance tank, (b) Schematic for the small-     |

| signal and low-frequency analysis of the cross-coupled NMOS differential pair. 57                     |

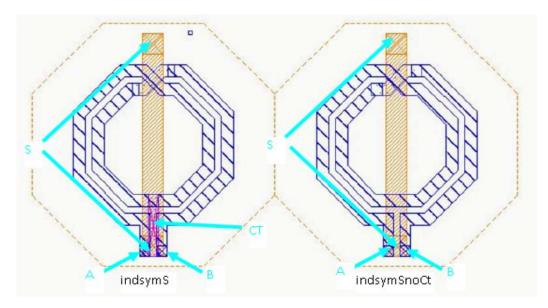

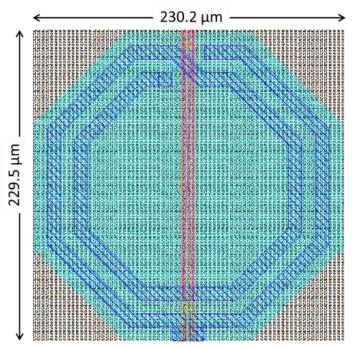

| Figure 2.10: Layouts of the shielded octagonal inductors with and without center tap 58               |

| Figure 2.11: Layout view of the octagonal differential inductor in QUBiC4X library 59                 |

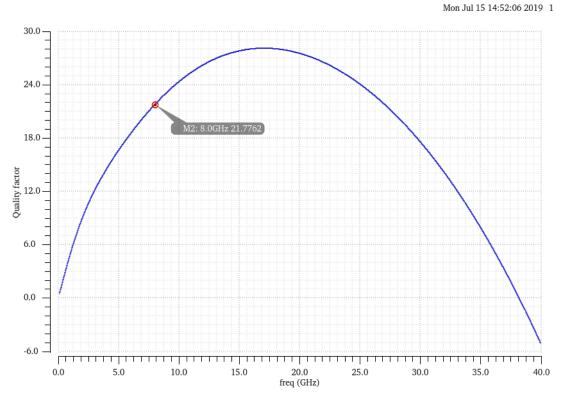

| Figure 2.12: The simulated Quality factor of the differential inductor                                |

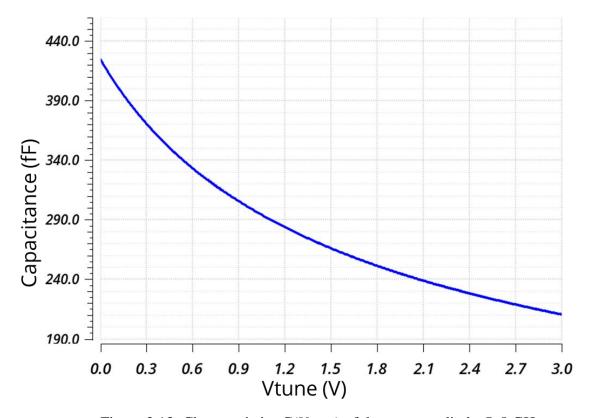

| Figure 2.13: Characteristics C(Vtune) of the varactor diode @ 8 GHz60                                 |

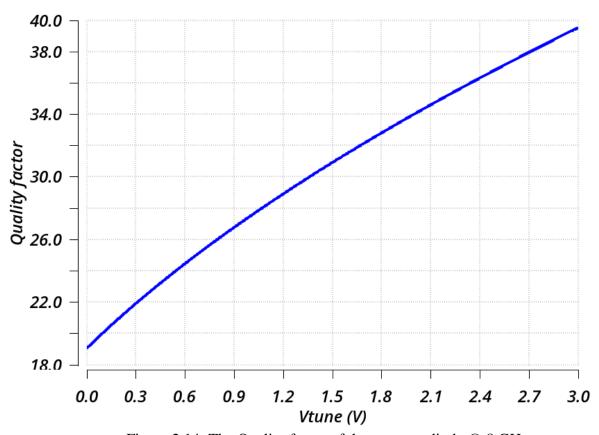

| Figure 2.14: The Quality factor of the varactor diode @ 8 GHz                                         |

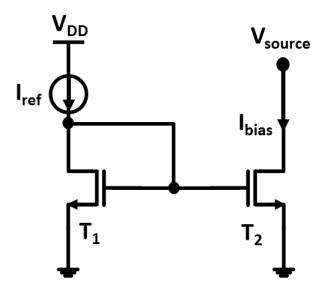

| Figure 2.15: Architecture of the current mirror for a single LC VCO                                   |

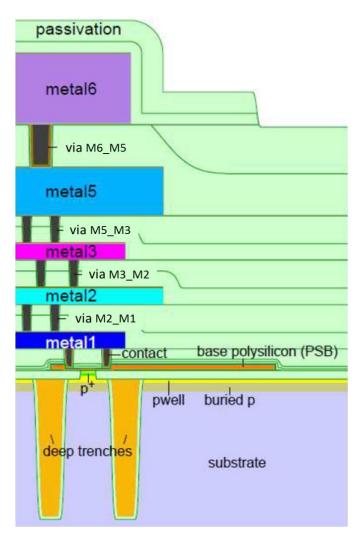

| Figure 2.16: Cross-section view of the QUBiC4X technology of NXP semiconductors 64                    |

| Figure 2.17: Layout of the LC VCO in the cadence design system                                        |

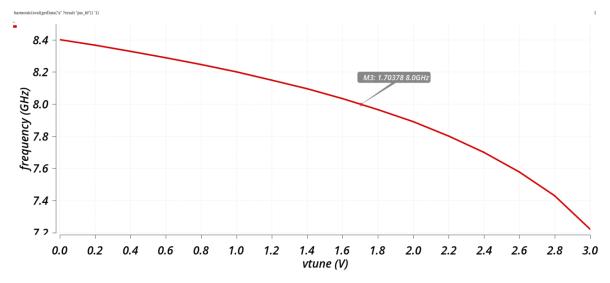

| Figure 2.18: Post layout simulation results of the output frequency vs the tuning voltage. $\dots$ 65 |

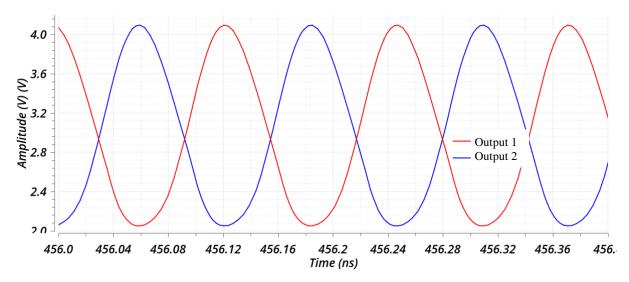

| Figure 2.19: Post layout time-domain simulation analysis of LC VCO at 8 GHz for $Vtune=1.7$           |

| V66                                                                                                   |

| Figure 2.20: Simulated phase noise of the VCO for a tuning voltage of 1.7 V                           |

| Figure 2.21: Triple-push LC VCO coupled via Varactor diodes                                           |

| Figure 2.22: Architecture of the differential amplifier and output buffer                             |

| Figure 2.23: Current mirror of the Triple-Push VCO providing biasing current for the three            |

| VCOs and the three output stage amplifiers69                                                          |

| Figure 2.24: The layout of the triple-push VCO implemented in the QUBiC4X 0.25 $\mu m$                |

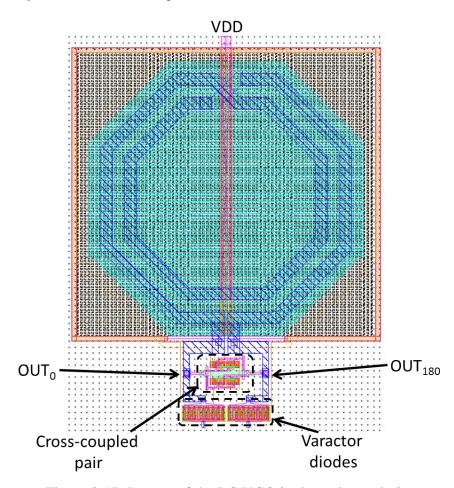

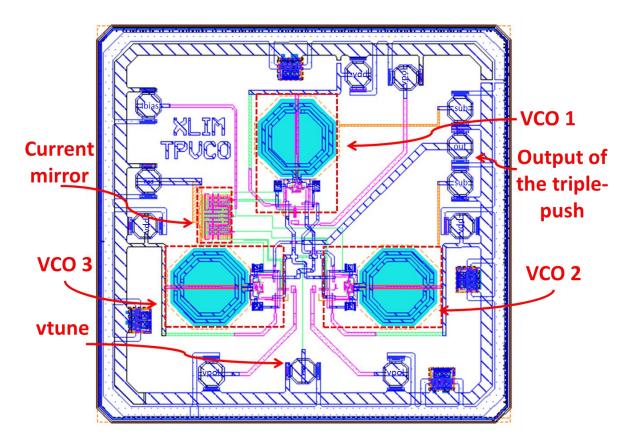

| SiGe:C BiCMOS process of NXP Semiconductors71                                                         |

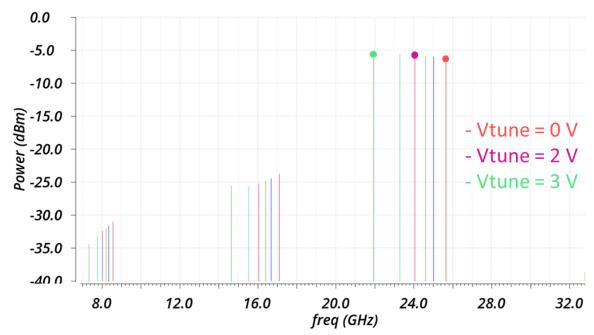

| Figure 2.25: Post layout simulation of the output frequency vs the tuning voltage72                   |

| Figure 2.26: Post Layout simulation results of the output power, second harmonics and                 |

| fundamental as a function of the tuning voltage in CADENCE®73                                         |

## List of Figures

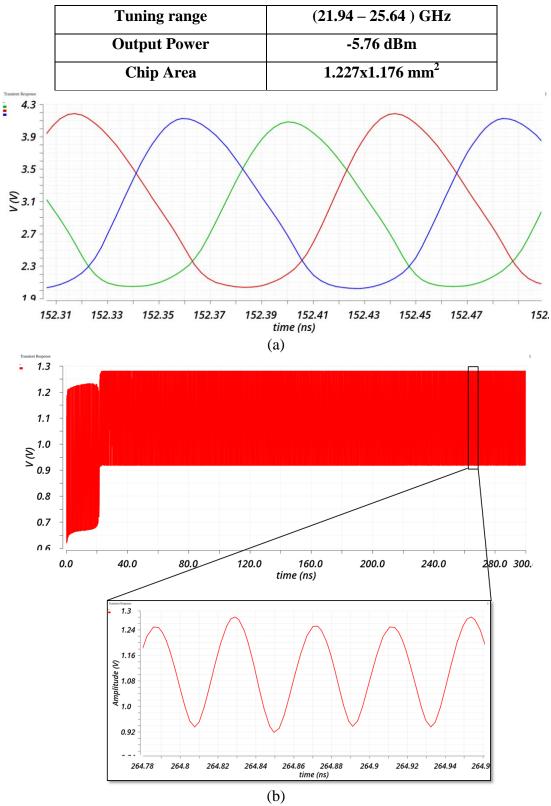

| Figure 2.27: Time-domain post-layout analysis of the triple-push VCO (a) Output of the three                                         |

|--------------------------------------------------------------------------------------------------------------------------------------|

| VCO at 8 GHz and at 120° to each other, (b) Output of the triple-push VCO in                                                         |

| odd mode at 24 GHz for <i>Vtune</i> = 2 V74                                                                                          |

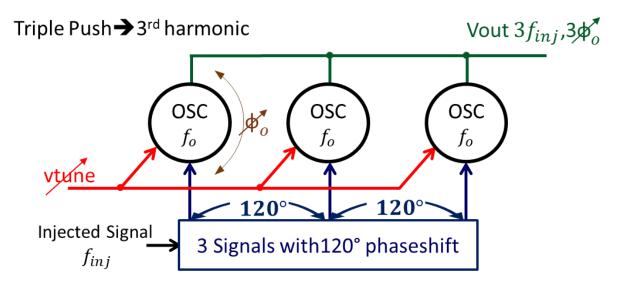

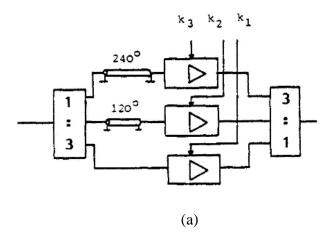

| Figure 3.1: The principle of injection locking in a triple-push oscillator                                                           |

| Figure 3.2: Architecture of a 120° phase shifter proposed by (a) W. Mielke [63], (b) Andrea                                          |

| Bevilacqua et Pietro Andreani [64] and (c) T. Chi, J. Luo, S. Hu, and H. Wang                                                        |

| [65]                                                                                                                                 |

| Figure 3.3: complete 120° phase shifter architecture.                                                                                |

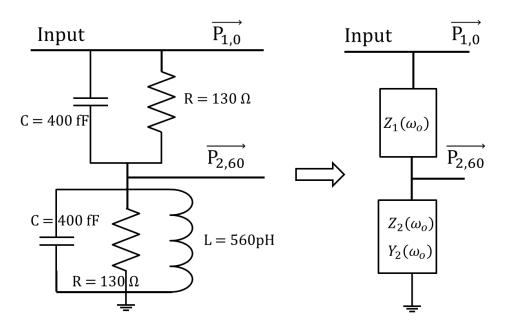

| Figure 3.4: Schematic of the 60° phase shifter                                                                                       |

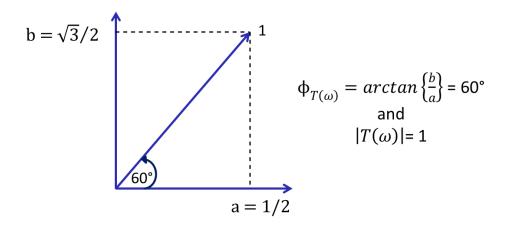

| Figure 3.5: Construction of the vector $P_2$ from the algebraic notation $a + jb$ for a phase of 60                                  |

| and a module of 1                                                                                                                    |

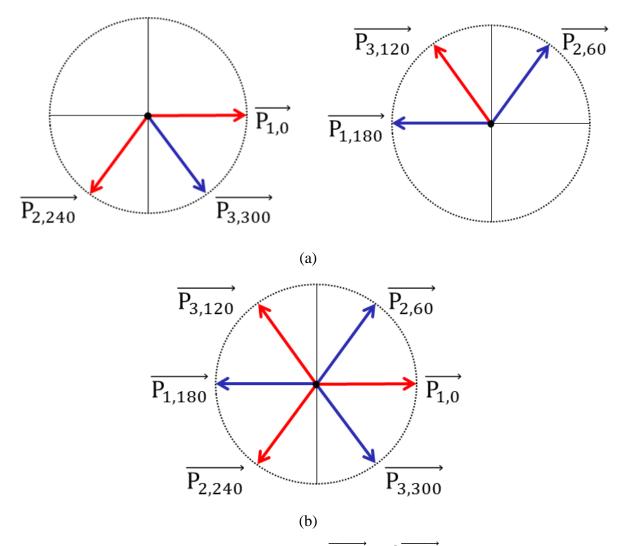

| Figure 3.6: (a) Phase construction of $\overrightarrow{P_{3,300}}$ and $\overrightarrow{P_{3,120}}$ , (b) Complete phasor diagram 89 |

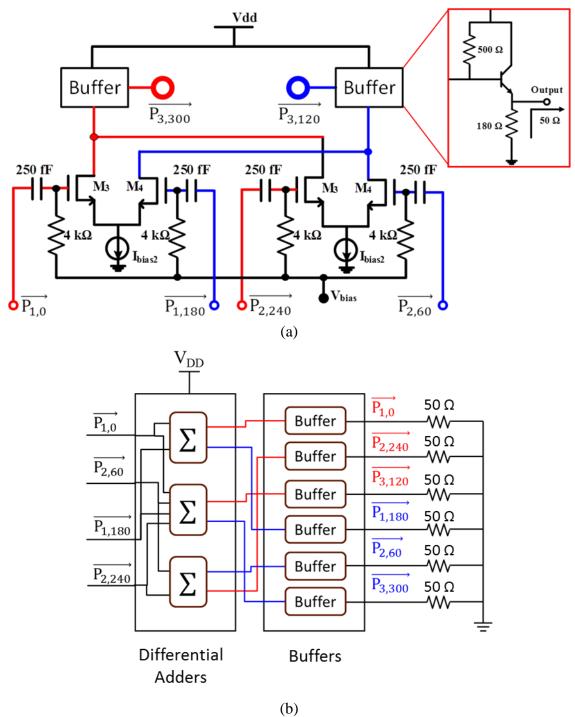

| Figure 3.7: (a) Architecture of the differential adder, (b) Block diagram of the three                                               |

| differential adders connected to six output buffers                                                                                  |

| Figure 3.8: Electrical circuit diagram of the $60^{\circ}$ phase shifter tunable at 8 GHz                                            |

| Figure 3.9: The layout of the 120° phase shifter                                                                                     |

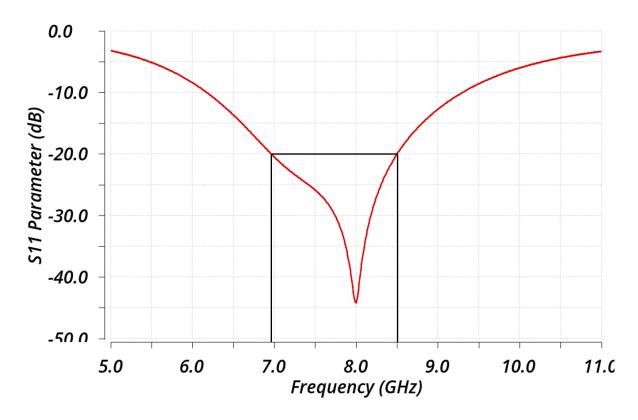

| Figure 3.10: Input reflection coefficient (S11)                                                                                      |

| Figure 3.11: Phase error at the output of the $60^{\circ}$ phase shifter                                                             |

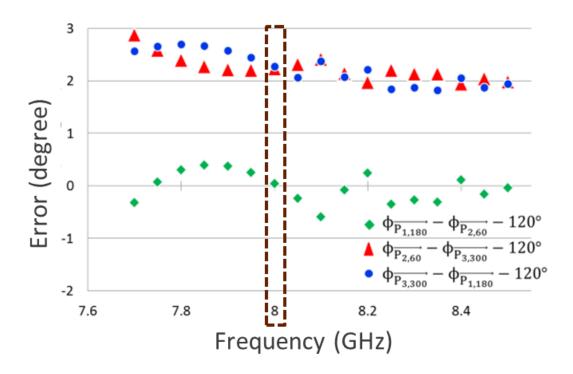

| Figure 3.12: Phase errors between the three output signals                                                                           |

| Figure 3.13: Amplitude errors between the three output signals                                                                       |

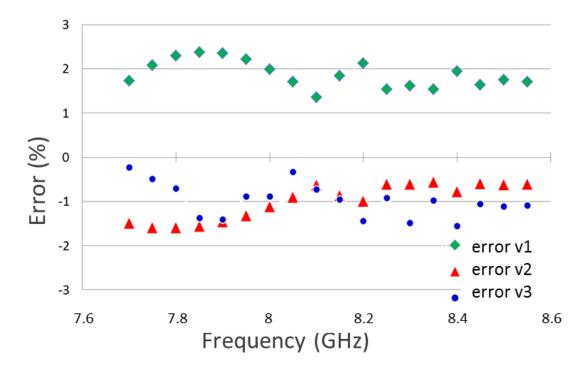

| Figure 3.14: Different architectures for implementing the RF phase shift: (a) on the RF path                                         |

| (b) on the IF path; (c) on the LO path; (d) in digital baseband                                                                      |

| Figure 3.15: The architecture of the phased antenna array for the beamforming application in                                         |

| LO path99                                                                                                                            |

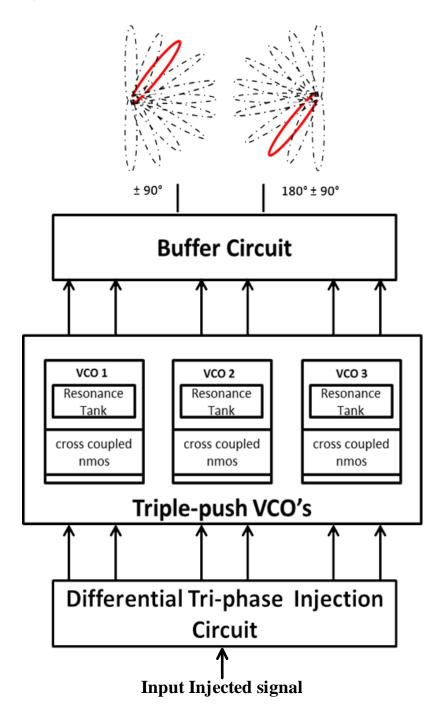

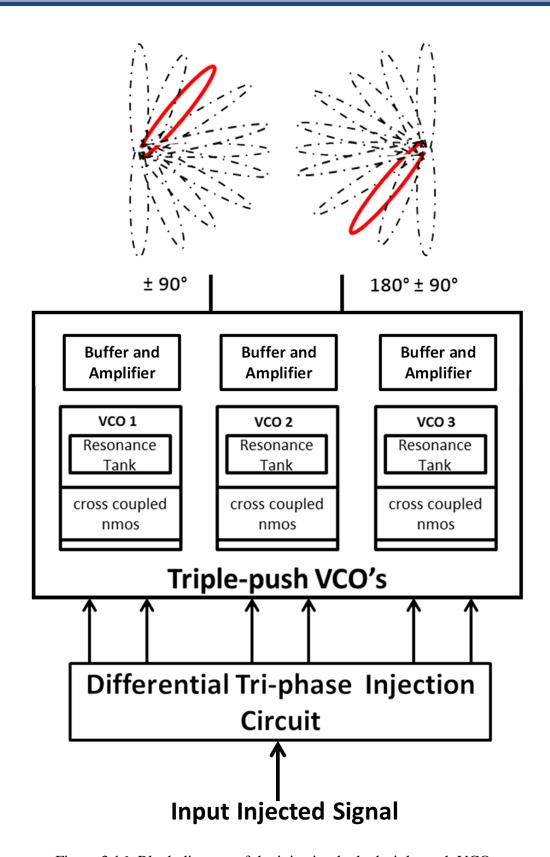

| Figure 3.16: Block diagram of the injection locked triple-push VCO                                                                   |

| Figure 3.17 : The layout of the injection locked triple-push VCO                                                                     |

| Figure 3.18: Frequency vs <i>Vtune</i> for the global circuit without injection                                                      |

| Figure 3.19: Input reflection coefficient (S11)                                                                                      |

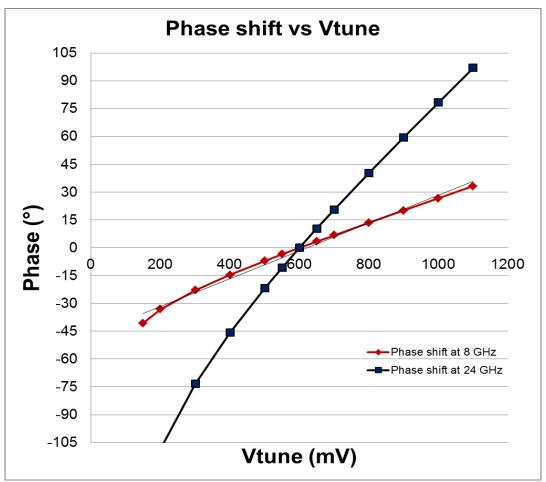

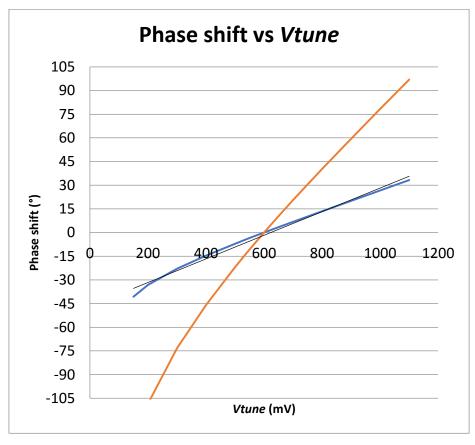

| Figure 3.20: Post layout simulation of the phase shift obtained between the injection signal                                         |

| and output of one VCO with respect to Vtune and corresponding phase shift                                                            |

| obtained at the output of the triple-push VCO                                                                                        |

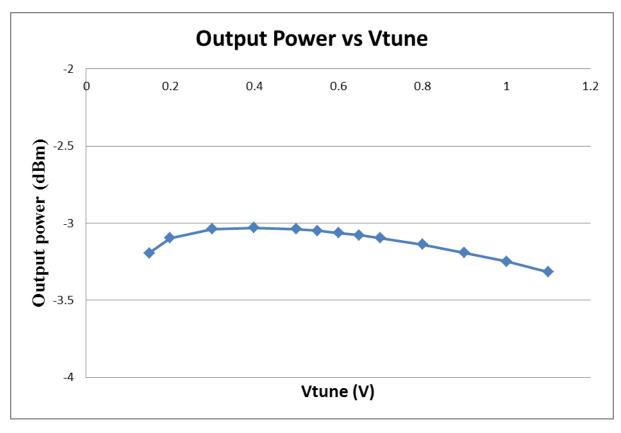

| Figure 3.21: Post layout simulation result of the output power with respect to <i>Vtune</i> 108                                      |

## List of tables

| Table 1.1: Generation of wireless technology [1].                                             |

|-----------------------------------------------------------------------------------------------|

| Table 2.1: Physical characteristics of the Inductor                                           |

| Table 2.2: Summary of simulated varactor performances                                         |

| Table 2.3: Dimensions of the transistors of the current mirror                                |

| Table 2.4: Current mirror transistors' size for the complete triple-push VCO                  |

| Table 2.5: Comparison with other triple-push VCOs between 20-30 GHz                           |

| Table 2.6: Summary of the triple-push VCO performances                                        |

| Table 2.7: Rejection of the fundamental and second harmonic as a function of the temperature  |

| 75                                                                                            |

| Table 2.8: Rejection of the fundamental and second harmonic as a function of the supply       |

| voltage75                                                                                     |

| Table 2.9: Rejection of the fundamental and second harmonic as a function of the process      |

| variations                                                                                    |

| Table 3.1: Summary of performances of the differential 120° tunable active phase shifter at 8 |

| GHz                                                                                           |

| Table 3.2: Static parameters of the overall circuit                                           |

| Table 3.3: Post layout results of the active phase shifter                                    |

| Table 3.4: Comparison of the performances of the developed system with the literature 109     |

## **List of Abbreviations**

**ADC** Analog to Digital Convertor

**AR** Augmented Reality

**BiCMOS** Bipolar Complementary Metal-Oxide Semiconductor

**CAD** Computer Aided Design

**CDMA** Code Division Multiple Access

**COAs** Coupled Oscillator Arrays

**DAMPS** Digital Advanced Mobile Phone Service

**DRM** Design Rule Manual

**EVDO** Evolution Data Optimised

**GSM** Global System for Mobile Communications

**GSMA** Global System for Mobile Communications

**HB** Harmonic Balance

**HSPA** High Speed Packet Access

**ICT** Information and Communication Technologies

**IEEE** Institute of Electrical and Electronics Engineers

**IF** Intermediate Frequency

**ILOAs** Injection locked Oscillator Arrays

**ILOs** Injection Locked Oscillators

**ILTPVCO** Injection Locked Triple-Push Voltage Controlled Oscillator

**IMT** International Mobile Telecommunications

**IoT** Internet of Things

ITU International Telecommunication Union

#### List of Abbreviations

**LO** Local oscillator

LTE Long Term Evolution

MIM Metal Insulator Metal

MIMO Multiple Input Multiple Output

NMOS Negative Channel Metal Oxide Semiconductor

**PMOS** Positive Channel Metal Oxide Semiconductor

**PSS** Periodic Steady State Simulation Analysis

**PVT** Process Voltage and Temperature

**QoE** Quality of Experience

**QoS** Quality of Service

**RAT** Radio Access Technologies

**RF** Radio Frequency

SiGe Silicon Germanium

SMS Short Message Service

**TPO** Triple-Push Oscillator

**TPVCO** Triple-Push Voltage Controlled Oscillator

**UMTS** Universal Mobile Telecommunications System

**V2I/V2V** Vehicle to Infrastructure/Vehicle to Vehicle

VCO Voltage Controlled Oscillator

**VR** Virtual Reality

**WiMAX** Worldwide Interoperability for Microwave Access

WRC World Radiocommunication Conference

G technology, i.e. fifth generation of wireless communication technology, arriving in 2020, is going to change the perception of the whole world towards technology advancement. It is the future of the next/new generation mobile network/wireless systems which will become the backbone of the Internet of Things (IoT), providing broadband and media everywhere, smart vehicles transport, critical services and infrastructure control, critical control of remote devices, human-machine interaction, sensors network etc... A new architecture, new communication technologies and new hardware with advanced high-tech software will implement this transformation to provide access to information and sharing of data anytime and anywhere. 5G key capabilities, recommended by the International Telecommunication Union (ITU), will be able to provide peak data rate up to 10 Gbits/sec per user/device with a latency of under 1 msec, ultra-high reliability (>99.999%) and high connection density. To support increased traffic capacity and enable the transmission bandwidths needed to support very high data rates, 5G will extend the range of frequencies used for mobile communications. According to a June 2019 report from Ericsson, 5G will reach 45% population coverage and 1.9 billion subscriptions by 2024, making it the fastest generation ever to be rolled out on a global scale. Even though the spectrum of 5G is not fixed, it is expected to be up to 300 GHz. Once 5G is deployed in 2020, the most critical challenge will be to control the massive traffic. The transmission of the signals with minimum losses and interference is going to be one of the most important factors.

Research for different challenges of 5G technologies has already started. One of the research challenges in 5G is beamforming and how to perform it at millimetre wave frequencies. It plays vital role in many applications for the transmission of data. In case of broadband and media, it creates new opportunities for mobile broadband evolution, enhances transmission in crowded areas, and improves the QoS (Quality of Service). For the Smart vehicles and transport, it provides improved fleet monitoring, navigation and augmented reality by orchestration of fast data and input interfaces with small latency. Critical controls of remote devices have significant benefits of efficiently controlling in hazardous environment by directing the signals at required positions, thereby increasing the efficiency and reducing cost. Human machine interaction will be reliable and precise especially for smart houses, child monitoring and remote health care. Indeed, it will improve the requirements for indoor and outdoor communication scenarios.

In this context, it seems interesting to develop an integrated circuit in the millimetre wave domain to control the transmission of signals. Associated to an antenna array, this circuit allows to perform beamforming, i.e. it allows the orientation and control of the radiation pattern in the desired direction. In millimetre waves, the ability to steer the beam allows to compensate for the losses due to the increase in frequency. This new circuit ensures a tunable RF phase shift between the input and the output. It is based on an original Injection Locked Triple-Push Voltage Controlled Oscillator (ILTPVCO) at 8 GHz. In these conditions, the frequency of the output signal is at 24 GHz. The objective of this dissertation is to present the analysis and the design of this fully integrated active RF phase shifter implemented in the QUBiC4X 0.25 µm SiGe:C BiCMOS process of NXP semiconductors.

This manuscript is composed of three chapters:

The first chapter begins with the introduction of the future vision of 5G, its applications, the spectrum of the 5G and different research challenges in 5G. A brief description of the beamforming basics using different methods to control the shape of the radiation pattern is discussed. Indeed, the control of the radiation pattern by amplitude and/or phase synthesis is first treated. Then, the state of the art of different phase synthesis techniques is reviewed. More specifically, the control of the radiation pattern by phase synthesis with external commanding through oscillators is illustrated.

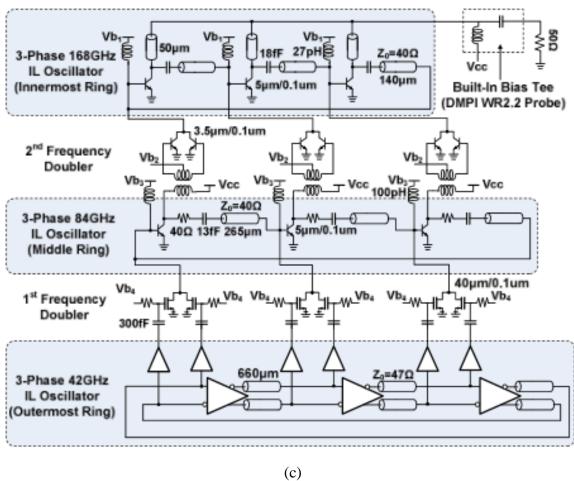

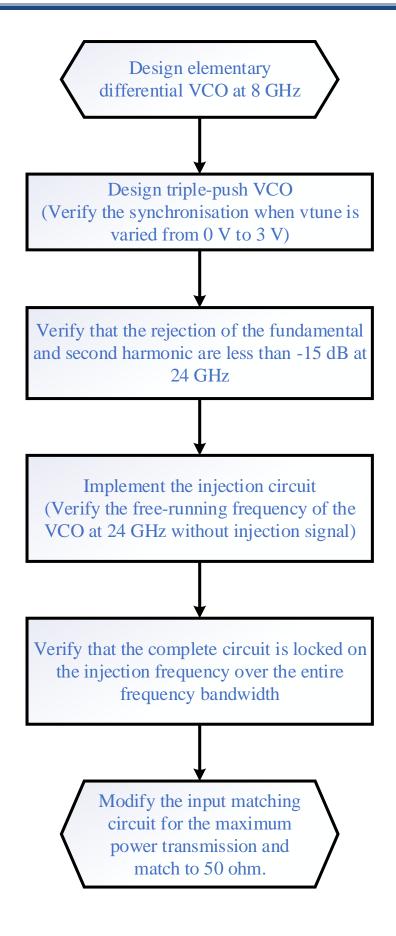

The second chapter presents the design and implementation of a differential triple-push VCO. The chapter starts with the brief theory of the triple-push oscillator and its mode analysis. Different triple-push oscillators around 20-40 GHz designed previously are reviewed, and different architectures of previous triple-push oscillators are analysed. A new architecture of a differential triple- push VCO is proposed here. It consists of operating the coupling through the varactor diodes and isolating the output 3<sup>rd</sup> harmonic from the coupling circuit. The circuit is implemented in the QUBiC4X 0.25 µm SiGe:C BiCMOS process of NXP semiconductors and the post layout simulation results are presented.

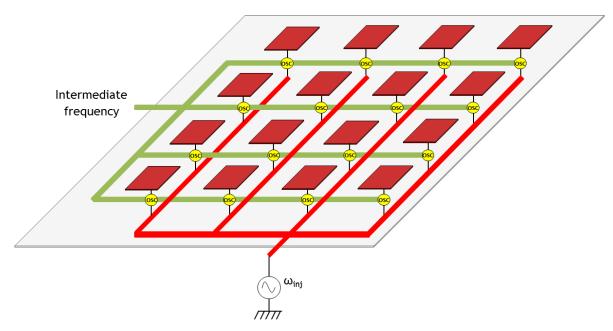

The third chapter presents the proposed original architecture of an active RF phase shifter using an Injection Locked Triple-Push Voltage Controlled Oscillator (ILTPVCO). The chapter begins with the introduction of the 120° injection circuit. A novel architecture of a differential tunable 120° phase shifter at 8 GHz and integrated in the 0.25 µm BiCMOS SiGe:C technology is presented with the post-layout simulation results. In the second part, we

present the design and implementation of the new active phase shifter architecture designed with the combination of the  $120^\circ$  phase shifter and the triple-push VCO at a frequency of 24 GHz fully integrated on a silicon substrate using the  $0.25~\mu m$  BiCMOS SiGe:C process of NXP semiconductors . Then the post-layout simulation results of the circuit are presented in order to evaluate the performances of the proposed active phase shifter and to validate the concept of this new architecture.

# Chapter I: Introduction to the research work

| Chap  | ter I: | Introduc                     | tion to the research work                                              | 6    |  |  |

|-------|--------|------------------------------|------------------------------------------------------------------------|------|--|--|

| Intro | ductio | n                            |                                                                        | 10   |  |  |

| 1     | 5G: T  | The future vision            |                                                                        |      |  |  |

|       | 1.1    | Key cap                      | pabilities of 5G                                                       | 12   |  |  |

|       | 1.2    | Applica                      | tions of the 5G                                                        | 14   |  |  |

|       | 1.3    | Spectru                      | m for 5G                                                               | 15   |  |  |

|       | 1.4    | Researc                      | h challenges in 5G and motivation of the thesis                        | 15   |  |  |

| 2     | Beam   | mforming of Antenna array 1  |                                                                        |      |  |  |

|       | 2.1    | Principl                     | e of the antenna array                                                 | 16   |  |  |

|       | 2.2    | Uniform linear antenna array |                                                                        |      |  |  |

|       | 2.3    | Uniform                      | n planar antenna array                                                 | 19   |  |  |

|       | 2.4    | Control                      | ling the shape of the radiation pattern                                | 21   |  |  |

| 3     | Princ  | iple and                     | state of the art of different methods to control the radiation pattern | ı by |  |  |

|       | phase  | synthes                      | is                                                                     | 22   |  |  |

|       | 3.1    | Phase sy                     | ynthesis by Vector Modulators                                          | 23   |  |  |

|       |        | 3.1.1                        | Limitations                                                            | 24   |  |  |

|       | 3.2    | Phase sy                     | ynthesis by using Coupled Oscillator Arrays                            | 25   |  |  |

|       |        | 3.2.1                        | Theory of oscillator                                                   | 25   |  |  |

|       |        |                              | 3.2.1.1 Oscillator's principle                                         | 26   |  |  |

|       |        |                              | 3.2.1.2 Starting of oscillations                                       | 27   |  |  |

|       |        | 3.2.2                        | Coupled Oscillator Arrays (COAs)                                       | 28   |  |  |

## Chapter I : Introduction to the research work

|   |                                   | 3.2.3      | Limitations                                                       | 31   |

|---|-----------------------------------|------------|-------------------------------------------------------------------|------|

|   | 3.3                               | Phase s    | synthesis by Injection locked Oscillator Array (ILOAs)            | 32   |

|   |                                   | 3.3.1      | Injection locking phenomenon                                      | 33   |

|   |                                   | 3.3.2      | Limitations of ILOs                                               | 36   |

|   | 3.4                               | Contro     | olling the shape of the radiation pattern of an antenna array thr | ough |

|   | injec                             | ction locl | ked oscillator array                                              | 39   |

| 4 | The objective of the dissertation |            |                                                                   | 41   |

| 5 | Conclusion                        |            |                                                                   | 43   |

#### **Introduction**

The objective of this first chapter is to present the framework of my thesis work and the different basic concepts involved in this dissertation. This chapter begins with the introduction of the future vision of 5G, its applications, the spectrum associated with 5G and different research challenges that need to be addressed from a research perspective. First, the principle and different types of antenna arrays, as well as the main characteristics of linear and planar antenna arrays, are presented. Then, the different techniques of the radiation pattern synthesis will be described. In addition, a state of the art of the different architectures for implementing phase shifts, used in the literature, is established. Subsequently, the emphasis is placed on the phase synthesis technique using an "Injection-Locked Oscillator Array" (ILOA). This technique is based on the use of a "slave oscillator" which, once synchronised to the injection frequency of the "master oscillator", generates a phase difference between the injected signal (master oscillator) and the output signal of the "slave oscillator". This phase difference is controlled by modifying the free-running frequency of the "slave oscillator" via its control voltage, referred to here as *Vtune*. Thus, to control an antenna array, it is sufficient to place a network of slave oscillators each associated with an antenna (or a group of antennas), all of them synchronised by an injection signal, in this case the LO signal. The independent control of the free-running frequencies (different Vtune) allows an independent control of the phase shift between each output signal and the injected signal. In the end, the objective of the thesis is presented, followed by the conclusion.

#### 1 5G: The future vision

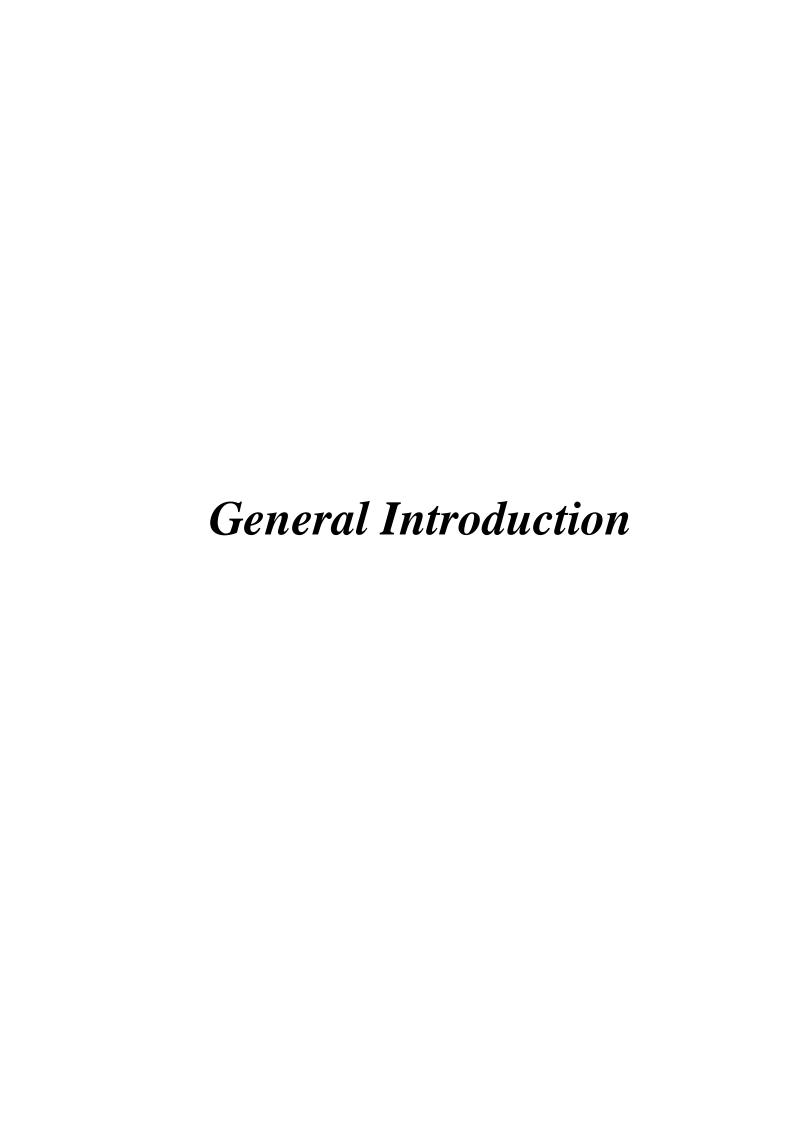

The fifth-generation, abbreviated as 5G, is the future of the next/new generation mobile networks/wireless systems. The arrival of 5G technology in 2020 has already boosted the major transformation in the wireless industry, which will completely change the communication system in the whole world (figure 1.1). In the coming years, sharing of data and access to information would be possible anytime and anywhere to anyone and anything. It would be able to provide very high data rates (typically of Gbps), very low latency (<1ms), ultra-high reliability (>99.999%), energy efficiency and extreme divide densities and will be accomplished by the development of LTE in combination with new radio access technologies (RAT). 5G will enhance the work and play in the cloud capacities, wireless connectivity of wearables, self-driving cars, smart homes, traffic safety/control, industrial process, automation, and very-high-speed media delivery. In short, it will accelerate the rapid development of the Internet of Things (IoT).

Rather than based on one specific radio-access technology, 5G is a portfolio of access and connectivity solutions addressing the demands and requirement of mobile communication beyond 2020. Table 1.1 summarises the generation of wireless technology.

Figure 1.1: Advancement of the 'G' Technology [source: www.softwaretestinggenius.com].

Table 1.1: Generation of wireless technology [1].

| Generation           | Requirements                                                                     | Comments                         |

|----------------------|----------------------------------------------------------------------------------|----------------------------------|

| 1G                   | <ul><li>No official requirements.</li></ul>                                      | > Deployed in the 1980s.         |

| 16                   | •                                                                                | Deployed in the 1980s.           |

|                      | > Analog technology.                                                             |                                  |

| <b>2G</b>            | No official requirements.                                                        | > First digital systems.         |

|                      | Digital technology.                                                              | Deployed in the 1990s.           |

|                      |                                                                                  | New services such as SMS and     |

|                      |                                                                                  | low-rate data.                   |

|                      |                                                                                  | > Primary technologies include   |

|                      |                                                                                  | IS-95 CDMA (CDMA One), IS-       |

|                      |                                                                                  | 136 (DAMPS), and GSM.            |

| 3G                   | > ITU's IMT-2000 required 144                                                    | > First deployment in 2000.      |

|                      | Kbps mobile, 384 Kbps                                                            | > Primary technologies include   |

|                      | pedestrian, 2 Mbps indoors.                                                      | CDMA2000 1X/EVDO and             |

|                      |                                                                                  | UMTS-HSPA. WiMAX.                |

| 4G (Initial          | > ITU's IMT-Advanced                                                             | > First deployment in 2010. IEEE |

| Technical            | requirements include the ability                                                 | 802.16m and LTE Advanced         |

| <b>Designation</b> ) | to operate in up to-40-MHz                                                       | meet the requirements.           |

|                      | radio channels and with very                                                     |                                  |

|                      | high spectral efficiency.                                                        |                                  |

| 4G (Current          | > Systems that significantly                                                     | > Today's HSPA+, LTE, and        |

| Marketing            | exceed the performance of                                                        | WiMAX networks meet this         |

| <b>Designation</b> ) | initial 3G networks.                                                             | requirement.                     |

|                      | > No quantitative requirements.                                                  |                                  |

| 5G                   | > ITU IMT-2020 has defined                                                       | > First standards-based          |

|                      | technical requirements for 5G,                                                   | deployments in 2019 and 2020.    |

|                      | and 3GPP is developing                                                           |                                  |

|                      | specifications.                                                                  |                                  |

| 5G                   | > ITU IMT-2020 has defined technical requirements for 5G, and 3GPP is developing |                                  |

## 1.1 Key capabilities of 5G

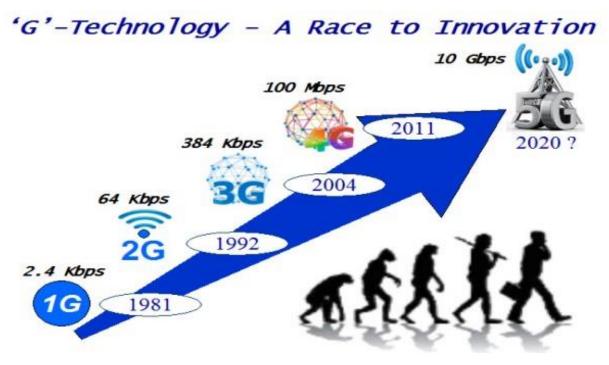

The expected enhanced key capabilities of 5G recommended by the International Telecommunication Union (ITU) are [2] [3]:

- ➤ Peak data rate: Under ideal conditions, it is expected to be 10 Gbits/sec per user/device. (20 Gbits/s under certain conditions).

- ➤ User experienced data rate: Up to 100 Mbit/s or Gbit/s in hotspots cases.

- ➤ Latency: <1 ms.

- ➤ Mobility: Up to 500 Km/hr with acceptable QoS (accommodate high-speed trains).

- ➤ Connection density: 10 times higher than 4G. 10<sup>6</sup>/km<sup>2</sup>.

- > Spectrum efficiency: 3 times more than 4G.

- > Energy efficiency: 100 times as compared to 4G.

- Area traffic capability: Support up to 10 Mbit/s/m<sup>2</sup> area traffic capacity. Greater than 100 times current 4G.

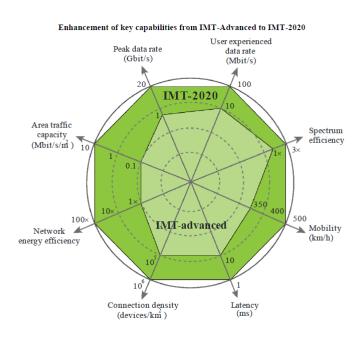

The comparisons of the key capabilities of the IMT-2020 with IMT-Advanced are shown in figure 1.2. IMT-2020 will mainly boost the development of the Internet of Things (IoT). It will provide a broad platform for the smart wearable devices, applications, machines and other connected objection without the intervention of the humans. IMT-2020 would provide sustained and affordable future without increasing the cost energy consumption, network equipment cost, and deployment cost [2].

Figure 1.2: Enhancement of key capabilities from IMT-Advanced to IMT 2020 [4].

#### 1.2 Applications of the 5G

Many Information and Communication Technologies (ICT) industrial bodies have already set the requirements in terms of what 5G is [2] [4]. As mentioned in the previous section, 5G will become a cornerstone in many of the economic sectors [5] [6] [7]. Some of the economic domains where 5G technology is going to play a significant role are as follows:

- Agriculture: Advancement in sensors and actuators to measure soil quality, prediction of climatic change, monitoring of cultivation, and livestock movements.

- Automobiles: Improvement in the autonomous vehicle control (self-driving), intelligent traffic control/safety, quality of life, V2V (vehicle-to-vehicle) and V2I (vehicle-to-infrastructure) communications.

- ➤ Construction/Building: Development of smart cities with remote accessibility, safety, monitoring, energy efficiency.

- ➤ Energy utilities: 5G could efficiently address oil supply unbalance and instability, fracking advancements and carbon constraints, as well as new decentralised business models, and renewable energy generation challenges of the energy utility industries.

- ➤ Finance (including banking): Security, fraud detection, and analytics improvement for financial activities such as trading, banking, and shopping.

- ➤ Health: Transforming healthcare with 5G is going to be a significant boom in global health which includes exercising at home, remote diagnosis and robotic-assisted surgery, wireless connectivity of health monitoring devices, continuous consumer health sensing, and medical alert.

- ➤ Manufacturing: With the introduction of wireless 5G technologies, industrial process control can be made more efficient, reliable, and accurate. Sufficiently low latency and ultra-reliable operation will enhance the factory cell automation and be associated with cloud robotics.

- ➤ Media on demand: High frequency with large bandwidth will provide an excellent user experience for viewing 3D and 4K formats on a mass scale. Future smartphone users will popularly enjoy Virtual Reality (VR) and Augmented Reality (AR).

➤ Public safety: Emergency communications for police, fire, rescue, ambulance, and medical emergency services needs a better reliable and available network. 5G radio access will multiply the efficiency in case of emergency during natural disasters natural calamities.

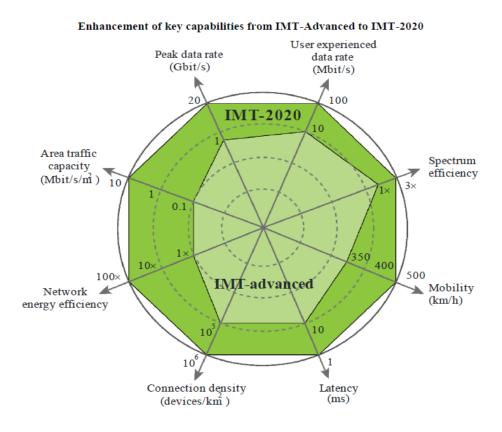

# 1.3 Spectrum for 5G

The spectrum of the 5G is not definitely fixed until now. WRC-19 (World Radiocommunication Conference) will take place from 28 October to 22 November 2019, and it will have a significant impact on the future of the 5G spectrum. In order to support increased traffic capacity and to enable the transmission bandwidths needed to support very high data rates, 5G will extend the range of frequencies used for mobile communications. 5G research targets a range between 300 MHz to 300 GHz [8] [9]. WRC-19 is vital for establishing international agreement of 5G bands above 24 GHz. 5G needs a significant amount of new harmonised mobile spectrum. Indeed, 5G needs spectrum within three key frequency ranges to deliver widespread coverage and support all user cases. The three estimated ranges are Sub-1 GHz, 1-6 GHz, and above 6 GHz (figure 1.3).

Figure 1.3: 5G Spectrum GSMA Public Policy Position, November 2018.

#### 1.4 Research challenges in 5G and motivation of the thesis

Currently, many types of research are going on future 5G technology [10] [11]. Some of the delicate open research challenges are:

- ➤ Introduction of the mm-wave spectrum;

- Unavailability of the popular channel model;

- > Site-Specific propagation;

- ➤ Antenna array design;

- Beamforming and beam training;

- ➤ Massive MIMO;

- ➤ Novel multiplexing;

- ➤ Non-orthogonality;

- ➤ Low latency and QoE;

- > Energy efficiency;

- > 5G Applications and standardisation.

There are several applications ready to implement in 5G technology. Moreover, once 5G is deployed in 2020, the most critical challenge would be to control the massive traffic. One of the research challenges in 5G is beamforming and how to perform it at millimetre wave frequencies. In this context, it seems interesting to study a system that is able to perform beamforming for the 5G standard. In this dissertation, an active phase shifter is designed in the millimetre wave to orientate and control the radiation pattern in the desired direction.

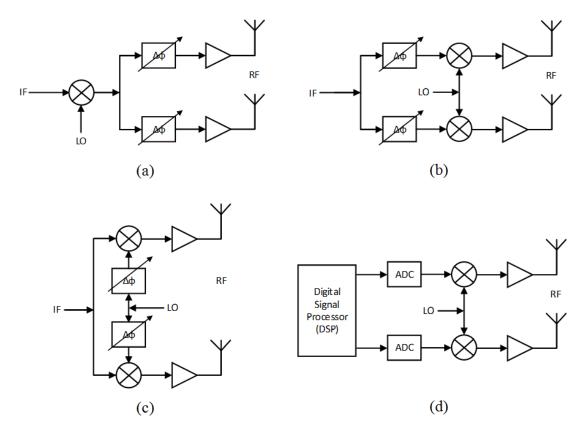

The active phase shifter is intended to be applied in the LO path for the application of the beamforming in 5G technology. A solution, among others, to focus the EM wave is to use Injection Locked Voltage Controlled Oscillators (ILVCO) which are associated with an antenna array. In this context, the main goal of this thesis will consist in the study and the design of an active phase shifter for phased array systems based on an original injection-locked triple-push VCO at 24 GHz integrated on silicon technology.

# 2 Beamforming of Antenna array

# 2.1 Principle of the antenna array

An antenna array is defined as a set of N distributed radiating elements in space. The amplitude and/or phase of the injected signal on each of these elementary antennas can be controlled to command the shape of the radiation pattern of the antenna array and to command its orientation. In particular, it is possible to choose these commands in order to create several lobes simultaneously or a single lobe in the direction of the incident signal and a zero in the direction of an interference wave. The number and type of elementary antennas constituting the array, as well as their geometric layout, represent the main characteristics of an antenna array. The main types of antennas used in antenna arrays are dipoles, monopoles, loop, slots,

horns, and microstrip patch antennas. For the reason of simplicity, implementation and manufacturing, identical elements are generally chosen. For the same reasons, equidistant uniformly spaced linear networks are mostly encountered in practice. The distance d between two antennas is called "step" of the network. The possible geometric configurations of the antenna array are of great variety, in general, they can be:

- linear: the antennas are aligned on a straight line,

- > planar: the antennas are arranged on a plane,

- > circular: the antennas are arranged on a circle,

- > volume: the antennas are distributed in a volume.

The first three types of geometric arrangements are the most commonly used, as they are illustrated in figure 1.4.

Figure 1.4: Examples of geometric configurations of the antenna array: (a) linear, (b) planar, and (c) circular.

Antenna arrays contribute to the improvement of the communication system performances while increasing the channel capacity, providing a wider band of coverage, and minimising the multipath fading and the interference between channels. Besides these advantages, the following properties describe a few assets of antenna arrays:

➤ The decrease of electromagnetic pollution: the shape of the radiation pattern can be optimised in order to reduce the side lobes. Similarly, the radiation pattern can be steered in the desired direction, and therefore, any radiations in useless directions are minimised.

A better quality of the transmission/reception: the emitted power can be focused in the desired direction, and therefore, the wasted power in useless directions is reduced. One of the advantages resulting from this decrease is also the distribution of the power on all the power amplifiers constituting the transmission network. Similarly, for the reception, the noise provided by the interfering signals is minimised, leading to a reduced Bit Error Rate (BER), which is the priority of any transmission architecture.

#### 2.2 Uniform linear antenna array

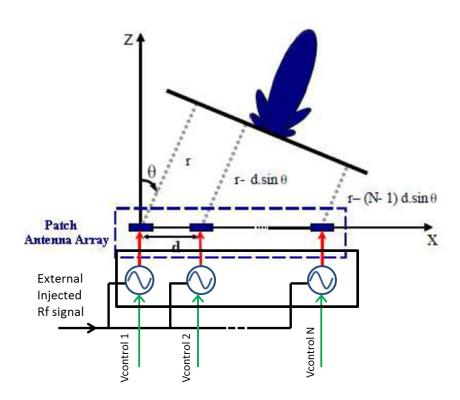

The radiation pattern of an antenna array is based on the basic physical structure of elementary antennas and the geometry of the array, and also on their control signals [12] [13]. When the elementary sources of a linear array are excited with the same amplitude, the antenna array is considered to be uniform and therefore is called equi-amplitude. In figure 1.5, we consider a uniform linear antenna array made of N identical equidistant elements with a distance d between them along an axis x, commanded by N sources with a mutual phase gradient of  $\Delta \varphi$  between them. The maximum distance between the reference antenna and the observation plane is represented by r, and  $\theta$  is the angle of the main lobe direction.

Under these conditions, the total electrical field radiated by the antenna array, in the far-field, is given by:

$$E_{tot} = E_0 \times A(\Psi) \tag{1}$$

where,

- $E_0$  represents the electrical field radiated by one elementary antenna. It is called "element factor" and depends only on the physical characteristics of the elementary antenna;

- $A(\Psi)$  is the array factor and depends on the geometry of the array and the amount of the amplitude and phase of the signal applied to each elementary antenna. This array factor has the following formula:

$$A(\Psi) = \frac{1}{N} exp(j(N-1)\Psi/2) \frac{sin(N\Psi/2)}{sin(\Psi/2)}$$

(2)

where

$$\Psi = \frac{2\pi d}{\lambda} \times \sin(\theta) - \Delta \phi$$

and  $\lambda$  is the wavelength

Figure 1.5: Representation of a uniform linear array

Therefore the total radiation pattern of the antenna array is defined by the product of the magnitude of the electrical field radiated by an elementary antenna and the one of the array factor, the latter being given by the following expression:

$$|A(\Psi)| = \frac{1}{N} \left| \frac{\sin(N\Psi/2)}{\sin(\Psi/2)} \right| \tag{3}$$

The total radiation pattern of the array depends more and more on the array factor and a little on the radiation pattern of each elementary antenna when the number N of the elementary antennas increased. In addition, we show that the maximum of the expression (3) occurs when  $\Psi$  is zero. As a consequence, the direction of the maximum radiation is given by:  $\Delta \varphi = \frac{2\pi d}{\lambda} \times \sin(\theta_0).$

Therefore, from the direction of the desired radiation pattern  $\theta$ , the phase shift  $\Delta \varphi$  applied between the radiating sources can be determined.

#### 2.3 Uniform planar antenna array

A planar antenna array is a 2-D (two-dimensional) array obtained by arranging its antenna elements on a plane. The shape can be rectangular, circular, etc... Figure 1.6

illustrates a uniform rectangular planar array represented in 2-D. This array consists of  $N_x$  x  $N_y$  elements placed in the XY plane with respective spacing's  $d_x$  and  $d_y$  between the antenna elements.

In the same way, as in the case of a linear antenna array, the main lobe of the radiation pattern is steered in the desired direction but with additional angular freedom in this case (azimuth as well as elevation). Indeed, the variation of the radiation pattern with a linear array is only possible in the alignment of radiating sources while with a planar array scanning is possible in all desired angular directions [14].

Figure 1.6: Rectangular planar antenna array.

The array factor  $AF_{plan}$  is the product of the two uniform linear network factors: one in the x-direction  $(AF_x)$  and another in the y-direction  $(AF_y)$  [15].

$$AF_{plan} = AF_x * AF_y = \sum_{m=0}^{N_x} e^{j(m-1)\psi_x} * \sum_{n=0}^{N_y} e^{j(n-1)\psi_y}$$

(4)

with

$$\psi_x = \frac{2\pi d_x}{\lambda}\sin\theta\cos\varphi - \Delta\varphi_x$$

and  $\psi_y = \frac{2\pi d_y}{\lambda}\sin\theta\sin\varphi - \Delta\varphi_y$

where  $\Delta \varphi_x$  and  $\Delta \varphi_y$  are the mutual phase gradient between the antenna elements in x and y directions, respectively.

The magnitude of the array factor is defined as:

$$\left| AF_{plan}(\psi) \right| = \left( \frac{1}{N_x} \left| \frac{\sin\left(\frac{N\psi_x}{2}\right)}{\sin\left(\frac{\psi_x}{2}\right)} \right| \right) \left( \frac{1}{N_y} \left| \frac{\sin\left(\frac{N\psi_y}{2}\right)}{\sin\left(\frac{\psi_y}{2}\right)} \right| \right)$$

(5)

Therefore, as in the case of a linear array, the maximum radiation direction  $(\theta_0, \varphi_0)$  is obtained when the inter-element phase shifts at x and y are equal to:

$$\Delta \varphi_x = rac{2\pi d_x}{\lambda} \sin heta_0 \cos heta_0 \quad , \quad \Delta \varphi_y = rac{2\pi d_y}{\lambda} \sin heta_0 \sin heta_0$$

## 2.4 Controlling the shape of the radiation pattern

As mentioned above, an antenna array allows the distribution of the radiated energy in space to be controlled in order to optimise the link budget. This distribution is obtained by forming and controlling the radiation pattern. To achieve this, it is necessary to establish a control law consisting of injecting amplitude and/or phase weighting to the signals applied on each radiating elementary elements of the antenna array. This defines the required height and/or opening of the side lobes relative to those of the main lobes (figure 1.7).

Figure 1.7: Main lobe and side lobes level of the radiation pattern of an antenna array.

The higher the sidelobe level, the lower the power assigned to the main lobe; hence, power is wasted. In a radiation pattern, it is necessary to reduce the side lobes levels for an imposed opening of the main lobe in order to concentrate power in the desired direction and thus minimise losses in other directions [16]. Under these conditions, three different types of synthesis can be considered:

#### Amplitude synthesis

This technique allows the synthesis of directional and symmetric lobes with the possibility of controlling the level of the side lobes [17] [18]. With the analysis techniques (Chebyshev, Fourier,...), the network coefficients can be determined. However, the applications for this type of synthesis are limited.

#### Amplitude and phase synthesis

This technique can be used to synthesise both directional lobes and side lobes whose levels are strongly controlled [17] [18]. This technique is useful for adaptive antenna applications but its implementation is complicated and expensive because it requires phase and amplitude synthesis methods, as the name implies.

#### Phase synthesis

This technique can be used to synthesise both directional lobes and side lobes that are "moderately controllable" [17] [18]. Nevertheless, the level received or transmitted in the direction of the useful radiation as well as the interference radiation can be controlled. Thus, this synthesis technique offers a good trade-off between the directivity of the radiation pattern and the low computing time as well as the reduced implementation costs compared to the two previous solutions. Phase synthesis is also referred to as "phased array antenna".

# 3 Principle and state of the art of different methods to control the radiation pattern by phase synthesis.

In this context, to control the radiation pattern by phase synthesis, several solutions using passive or active phase shifters can be used to achieve the electronic modification of the radiation pattern of a phased antenna array. Passive phase shifters present excellent linearity but suffer specifically from large chip area, significant insertion loss and amplitude variations [18] [19]. On the other hand, active phase shifters offer a high level of integration, no insertion losses and smaller amplitude variations, but they require large power consumption

compared to the passive ones. A variety of integrated active phase shifter architectures have been proposed in the literature [20] [21] [22]. In the following section, the state of the art of different phase shifters using vector modulator, coupled oscillators arrays and injection locked oscillator arrays is discussed.

#### 3.1 Phase synthesis by Vector Modulators

A vector modulator is an RF/microwave circuit which can be used to perform beamforming of the antenna array by controlling both the amplitude and the phase of the signals applied on each element of the antenna array. Hence, vector modulators can provide an active solution for the beamforming on the LO path as well as on the RF path (figure 1.8).

Figure 1.8: Vector modulator architecture used on (a) LO path; (b) RF path

The vector modulator allows the sidelobe level reduction while the antenna radiation pattern can be precisely positioned in any direction. Phase shift ranging from 0° to 360° can be obtained in steps that depend on the phase tracking accuracy. For instance, in the adaptive beam shaping system presented in [23], the alignment of the beam in the azimuthal direction is performed by vector modulators. The main constraints for vector modulators are:

- ➤ Phase/Amplitude accuracy over the system bandwidth and the phase shift range

- Minimum variation of the amplitude between the phase states

- ➤ Minimal insertion loss

#### > Low power consumption.

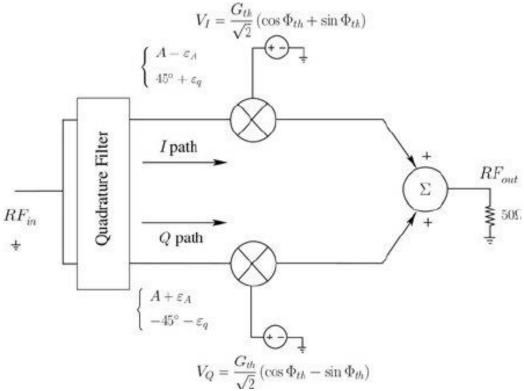

Vector modulator controls the signal into the desired vector location through command signals  $V_I$  and  $V_Q$  as illustrated in figure 1.9 where  $\Phi_{th}$  is the synthesised phase shift and  $G_{th}$  is the gain of the active phase shifter [20].

Figure 1.9: Block diagram of a common vector modulator-based active phase shifter [20].

#### 3.1.1 Limitations

In the past, some active solutions using vector modulators as active phase shifters have been presented [24] [25] [26] [27], but none of these works presents the measurement results of the entire system including the antenna array. Indeed, an effective solution using vector modulators associated with a linear antenna array to perform beamforming has been presented in [20]. However, this type of synthesis is complicated and costly as it requires amplitude and phase control. Moreover, other recent works based on the vector-sum technique have been developed in order to obtain high phase resolution and accuracy [28] [29] [30]. Nevertheless, this solution suffers mainly from the complexity of the control circuit in order to obtain the desired phase resolution performances.

# 3.2 Phase synthesis by using Coupled Oscillator Arrays

# 3.2.1 Theory of oscillator

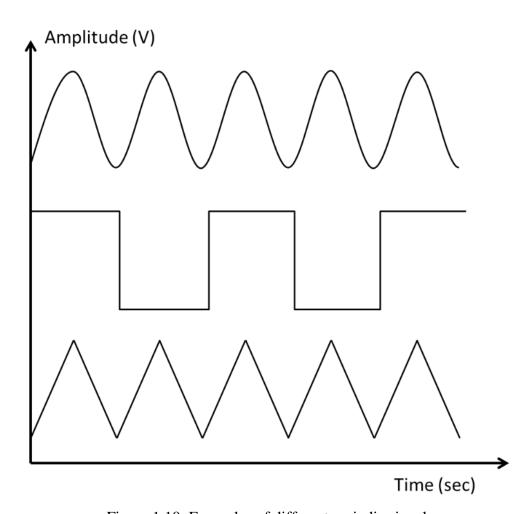

An electrical oscillator is an autonomous system that generates a signal with a fixed period (in the case of a simple oscillator) or variable (in the case of a voltage-controlled oscillator or VCO). An oscillator converts the direct current (DC) provided by a power supply into a continuously repeating alternative current (AC) signal. The signal shape can be sinusoidal, square or triangular, as shown in figure 1.10, or a distorted combination of the previous three.

Figure 1.10: Examples of different periodic signals

Oscillators are used in many applications, like a clock, frequency generators, tuneable radio transmitters, the local oscillators. In all the radio frequency applications, it is necessary to have sinusoidal references of high spectral purity (low phase noise). This is one of the

essential characteristic of an oscillator. Indeed, this phase noise will determine the stability of the periodicity of the oscillations provided.

# 3.2.1.1 Oscillator's principle

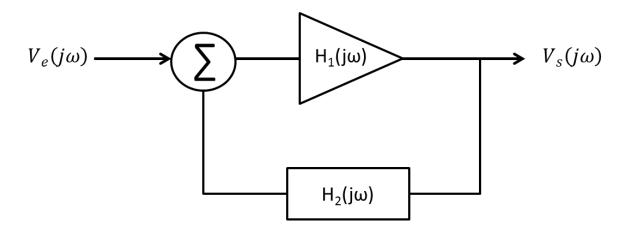

An electronic oscillator is composed of a passive resonant circuit and an active circuit. Generally, the passive circuit is inductance-capacitance (LC) type, which determines the oscillation frequency of the oscillator and the active circuit is based on transistors. From a dynamic point of view, this system is autonomous and balanced, as shown in figure 1.11, where  $H_1(j\omega)$  represents the transfer function of the active part and  $H_2(j\omega)$  represents the transfer function of the resonator.

Figure 1.11: Linear model of an oscillator

This block diagram involves a linearization of the behaviour of the active part. It explains the conditions of existence of the oscillations and the starting conditions of oscillations.

The transfer function of this positive feedback system can be written as:

$$H(j\omega) = \frac{V_s(j\omega)}{V_e(j\omega)} = \frac{H_1(j\omega)}{1 - H_1(j\omega) H_2(j\omega)}$$

(6)

The existence of oscillations is determined by the instability of the system. In the above system, the instability is represented by the poles of the closed-loop function  $H(j\omega)$ . To find the poles of the equation, we equate the denominator to zero and look for the cases where denominator vanishes. Hence, we have:

$$1 - H_1(j\omega) H_2(j\omega) = 0 \tag{7}$$

To guarantee the existence of oscillations, the following are the two parts of the solution of the complex equation:

$$|H_1(j\omega) H_2(j\omega)| = 1 \text{ and } Arg(H_1(j\omega) H_2(j\omega)) = 2\pi n$$

(8)

where  $n \in natural numbers$ .

These two conditions are popularly known as the Barkhausen stability criterion.

#### 3.2.1.2 Starting of oscillations

When the electronic oscillator is switched on, the Barkhausen criterion is not enough to start the oscillations. In other words, in the real world, we cannot guarantee the starting of oscillations even if (7) is strictly verified. We have two cases:

• Case 1:

$$|H_1(j\omega) H_2(j\omega)| < 1$$

(9)

In this situation, any existing oscillations are damped and vanish over time. The output of the system is made of hazardous oscillations of small amplitude. We deal with a system whose active part does not bring enough energy to compensate for the losses of the resonator.

• Case 2:

$$|H_1(j\omega) H_2(j\omega)| > 1$$

(10)

In this situation, the active part provides more energy than the resonator losses. Hence the oscillations amplify in time and do not vanish. Without further indications, it is clear that such a situation is not possible in the real world since the amplitude of the oscillations only increases, tending towards infinity.

#### Limitations of oscillators

We have just seen that to guarantee the starting of the oscillations in the system, it is necessary that the active part of the oscillator provides little more energy than the losses presented by the resonance tank. However, when the amplitude of the oscillations becomes large, the components that constitute the active part eventually move from their linear operating range to a non-linear region, hence resulting in a reduction of the gain of the active part. This shifting to non-linear behaviour implies the generation of the harmonic components. The non-linear behaviour of the oscillators is explained by the non-linear Van der Pol equations [31]. The reduction in the gain will be carried out until the criterion

presented in the (7) is satisfied. Finally, to guarantee the starting and the maintenance of the oscillations in an electronic oscillator, the active part must provide an amount of energy slightly higher than the losses of the resonator and enough to keep the components of the active part in the linear region. The maximum oscillation frequency that can be reached by the fundamental frequency oscillators is basically limited by the components used in the active part of the oscillator. The transistor-based active component limits the oscillation frequency when the maximum available gain reaches unity. Harmonic oscillators are one of the better solutions to use at high frequency as they are not limited by the active component's constraints.

# 3.2.2 Coupled Oscillator Arrays (COAs)

R. York & al. introduced a new technique based on the synchronisation property of the coupled oscillators to steer the radiation pattern of an antenna array [32]. The synchronisation requirements can be satisfied by coupling the oscillators together by a coupling circuit. A constant phase gradient  $\Delta \phi$  can be obtained between the adjacent elements by controlling the free-running frequencies of the outermost oscillators. In [21], it is shown that the theoretical limit of the phase shift that can be obtained by detuning the two end oscillators of the array by equal amounts but in opposite directions is only  $\pm$  90°. Nevertheless, the measurement results performed in [33] [34] shows that the maximum value of the phase shift  $\Delta \phi$  decreases by increasing the number of coupled oscillators. For a linear array (figure 1.12), a phase shift  $\Delta \phi$  between adjacent elements results in steering the beam to an angle  $\theta$  off broadside, which is given by:

$$\theta = \arcsin\left(\frac{\lambda}{2\pi d}\Delta\phi\right) \tag{11}$$

where d is the distance separating two antenna elements and  $\lambda$  is the free-space wavelength. In the case of differential oscillators, the theoretical limit of the phase shift is within  $\pm 180^{\circ}$  due to the differential nature of the oscillator array providing a more efficient beam-scanning architecture (figure 1.13).

An analysis of N coupled Van der Pol oscillators has been performed by Liao and York in [35].

$$\theta_i = \omega_i t + \phi_i \tag{12}$$

Figure 1.12: Block diagram of an array of N coupled oscillators

Figure 1.13: Phase-Shift versus the angle  $\theta$

According to this analysis, it is possible to write the phase dynamics for an array of N elements as follows:

$$\frac{d\theta_i}{dt} = \omega_i - \frac{\omega_i}{2Q} \sum_{j=1}^{N} Im \left\{ k_{ij} \frac{A_j}{A_i} e^{J(\theta_j - \theta_i)} \right\}$$

(13)

where for the  $i^{th}$  oscillator,  $\theta_i = \omega_i t + \phi_i$  is the instantaneous phase,  $\omega_i$  is the free-running pulsation and  $\emptyset_i$  is the initial phase. Furthermore,  $k_{ij}$  is the coupling coefficient between the  $i^{th}$  and  $j^{th}$  oscillator and Q is the resonator's quality factor.

Considering that  $y_{ijN}$  are the admittance parameters of the coupling matrix Y for an array of N coupled oscillators and if  $G_L$  is the conductance associated with the losses of the tank for one oscillator, then, we can write:  $k_{ij} = y_{ijN}/G_L$ . Under certain conditions, all of the oscillators are synchronised to the same pulsation  $\omega_0$ , and the magnitude variations are nearly zero, which occurs when:

$$\frac{dA_i}{dt} = 0 \text{ and } \frac{d\theta_i}{dt} = \omega_0 \ i = 1, 2, \dots, N$$

(14)

By substituting (14) in (13) and considering that  $k_{ij}$  is real, we obtain

$$\omega_0 = \omega_i - \frac{\omega_i}{2Q} \sum_{j=1}^N k_{ij} \frac{A_j}{A_i} sin(\theta_j - \theta_i)$$

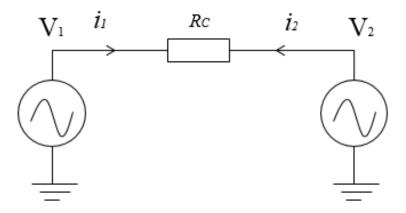

(15)