## Data Placement Strategies for Heterogeneous and Non-Volatile Memories in High Performance Computing

Andrès Rubio Proaño

#### ▶ To cite this version:

Andrès Rubio Proaño. Data Placement Strategies for Heterogeneous and Non-Volatile Memories in High Performance Computing. Distributed, Parallel, and Cluster Computing [cs.DC]. Université de Bordeaux, 2021. English. NNT: 2021BORD0224. tel-03431281

### HAL Id: tel-03431281 https://theses.hal.science/tel-03431281

Submitted on 16 Nov 2021

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# THÈSE PRÉSENTÉE

## POUR OBTENIR LE GRADE DE

## **DOCTEUR**

## DE L'UNIVERSITÉ DE BORDEAUX

# ÉCOLE DOCTORALE DE MATHÉMATIQUES ET D'INFORMATIQUE

INFORMATIQUE

#### Par Andrès RUBIO PROAÑO

Stratégies de Placement de Données pour Mémoires Hétérogènes et Non-Volatiles en Calcul Haute Performance

Sous la direction de : Brice GOGLIN

Soutenue le 7 Octobre 2021

#### Membres du jury:

| Mme Rosa Badia     | Directrice de recherche, Barcelona Supercomputing Center | Examinatrice |

|--------------------|----------------------------------------------------------|--------------|

| M. Thierry Gautier | Chargé de Recherche, Inria                               | Rapporteur   |

| M. Brice Goglin    | Directeur de recherche, Inria / LaBRI                    | Directeur    |

| M. Raymond Namyst  | Professeur, Université de Bordeaux                       | Président    |

| M. François Trahay | Maître de conférence, Institut Polytechnique de Paris    | Rapporteur   |

**Titre** Stratégies de placement de données pour les systèmes à mémoires hétérogènes dans le calcul haute performance.

Résumé Les systèmes mémoire des plates-formes de calcul haute performance ont subi des changements majeurs ces dernières années. En plus de la mémoire principale, du stockage et de plusieurs niveaux de caches, les serveurs sont à accès non-uniforme (NUMA) et peuvent disposer de plusieurs types de mémoire. Par exemple, les mémoires à haut débit (HBM) embarquées dans le processeur ainsi que les mémoires non volatiles (NVDIMM) ont été introduites dans la hiérarchie. Ces changements sont nécessaires pour rapprocher les données du traitement et donc avoir de meilleures performances. Cependant, ils obligent les développeurs à adapter leurs applications pour fonctionner correctement sur ces différents systèmes hétérogènes, ce qui rend le développement beaucoup plus complexe. En pratique, le simple fait de décider d'allouer un tampon de données sur le bon type de mémoire dans ces systèmes hétérogènes est difficile et critique pour les performances de l'application.

Cette thèse a été réalisée à Inria Bordeaux - Sud-Ouest et au LaBRI. Après avoir présenté l'état de l'art des architectures mémoire, nous avons caractérisés les différents types de mémoires à l'aide d'attributs simples. Nous avons fourni une interface que la bibliothèque hwloc expose aux applications pour comprendre l'organisation mémoire et allouer des tampons. Nous avons ensuite proposé une méthodologie pour que les développeurs puissent adapter leurs applications à l'utilisation appropriée de systèmes à mémoire hétérogènes. Comme l'accès à différents plates-formes hétérogènes n'est pas toujours possible, nous avons identifiés de nombreuses stratégies permettant la simulation des performances de mémoire hétérogène, et l'émulation de topologie de la mémoire différentes. Enfin, nous avons conçu une stratégie visant à faciliter le partage des plates-formes à mémoire non-volatile et hétérogènes entre des tâches HPC co-exécutées sur les mêmes serveurs.

Mots-clés Calcul haute performance, systèmes à mémoire hétérogène, modèles de programmation parallèle, programmation par tâches, calcul distribué, supports d'exécution

Laboratoire d'accueil Inria Bordeaux Sud-Ouest, 200 Avenue de la Vieille Tour, 33400 Talence

**Title** Data-Placement Strategies for Heterogenous Memory Systems in High Performance Computing.

Abstract Memory systems in High-Performance Computing (HPC) systems have undergone major changes in recent years. Beside main memory, storage and multiple levels of caches, servers come with non-uniform memory access (NUMA) and may contain different kinds of memory. For instance, high bandwidth memory (HBM) embedded on the processor package and non-volatile memory (NVDIMM) have been introduced into the hierarchy. These changes are necessary to bring the data closer and closer to processing and therefore have better performance. However, they require developers to adapt their applications to work properly on different heterogeneous memory systems, causing software development to become much more complex. In practice, the simple fact of deciding to allocate a data buffer on the appropriate memory in a heterogeneous system becomes difficult and critical to application performance.

This thesis has been carried out at Inria Bordeaux - Sud-Ouest and LaBRI. After a presentation of the state of the art of memory architectures, we have characterised the memories through simple attributes. We have provided an interface that the hwloc library exposes to applications to understand the memory topology and allocate buffers. Then, we proposed a strategy to help developers adapt their applications for the proper use of heterogeneous memory systems. As accessing different heterogeneous platforms is not always possible, we identify several ways to simulate the performance of heterogeneous memory and to emulate different memory topologies. Finally, we built a strategy that eases the sharing of platforms with heterogeneous and non-volatile memory between HPC tasks co-scheduled on the same nodes.

**Keywords** High performance computing, heterogeneous memory systems, parallel programming models, task-based programming, distributed computing, run-time systems

**Hosting Laboratory** Inria Bordeaux Sud-Ouest, 200 Avenue de la Vieille Tour, 33400 Talence

**Título** Estrategias de emplazamiento de datos para sistemas de memoria heterogéneos en computación de alto rendimiento.

Resumen Los sistemas de memoria en los sistemas de Computación de Alto Rendimiento han experimentado cambios importantes en los últimos años. Además de la memoria principal, el almacenamiento y varios niveles de cachés, los servidores vienen con acceso a memoria no uniforme (NUMA) y pueden contener diferentes tipos de memoria. Por ejemplo, la memoria de alto ancho de banda (HBM) incorporada en el paquete del procesador y la memoria no volátil (NVDIMM) se han introducido en la jerarquía. Estos cambios son necesarios para acercar cada vez más los datos al procesamiento y, por lo tanto, tener un mejor rendimiento. Sin embargo, requieren que los desarrolladores adapten sus aplicaciones para que funcionen correctamente en diferentes sistemas de memoria heterogéneos, lo que hace que el desarrollo de software se vuelva mucho más complejo. En la práctica, el simple hecho de decidir asignar un búfer de datos en la memoria adecuada en un sistema heterogéneo se vuelve difícil y crítico para el rendimiento de la aplicación.

Esta tesis se ha realizado en Inria Bordeaux - Sud-Ouest y LaBRI. Después de una presentación del estado del arte de las arquitecturas de memoria, hemos caracterizado las memorias a través de atributos simples. Hemos proporcionado una interfaz que la biblioteca hwloc expone a las aplicaciones para comprender la topología de la memoria y asignar búferes. Luego, propusimos una estrategia para ayudar a los desarrolladores a adaptar sus aplicaciones para el uso adecuado de sistemas de memoria heterogéneos. Dado que no siempre es posible acceder a diferentes plataformas heterogéneas, identificamos varias formas de simular el rendimiento de la memoria heterogénea y de emular diferentes topologías de memoria. Finalmente, creamos una estrategia que facilita el intercambio de plataformas con memoria heterogénea y no volátil entre tareas de HPC coprogramadas en los mismos nodos.

Palabras Clave Computación de alto rendimiento, sistemas heterogéneos de memoria, modelos de programación paralela, programación basada en tareas, computación distribuida, sistemas de tiempo de ejecución

**Laboratorio Antitrión** Inria Bordeaux Sud-Ouest, 200 Avenue de la Vieille Tour, 33400 Talence

# Acknowledgments

I begin by thanking Jesus for his wonderful work on the cross, for allowing me to have an unforgettable experience during these three years of the thesis, and for putting the right people in order to finish this process successfully.

I thank the members of the jury who have taken the time to read my thesis. Thanks to Thierry and François for having read the manuscript in a very attentive way. To Rosa and Raymond for their valuable input as examiners.

I have no way of thanking Brice Goglin who has not only guided me in the completion of the thesis but has also been attentive at each stage of my adaptation in France. Thank you for all your help and for all that I have been able to learn from you.

I thank my beautiful and beloved wife Eilen Gordillo Proaño for accompanying me during these three years of the thesis. You could even be my co-worker during the lockdown. I love you and I will always love you.

I thank all my colleagues from the TADaaM team, Emmanuel, François, Alexandre, Francielli, Guillaume A and Guillaume. To my colleagues from the open space Valentin Honoré, Nicolas Vidal, Valentin Hoyet, Adrien Guilbaud, Florian Reynier, Philippe Swartvagher, Clément G, Clément B, Luan and Alexis. To my colleagues at HiePACS Alena and Esragul.

Thanks to the support of my parents, Mercedes Proaño and Xavier Rubio. I have no way of paying you for everything you have done for me. To my brother José Rubio Proaño and my sister-in-law María José Alcivar for all your love. To my in-laws Freddy Gordillo and Nery Proaño for always being aware of us. To my sister-in-law Valeska Gordillo for always brightening our days. To my siblings-in-law Ámbar Gordillo, Thiago Gordillo and Esteban Pérez. And to my beautiful niece, Agustina Pérez Gordillo.

To my beautiful Rubio Villegas family, especially my beloved grandparents Miguel Rubio Arteaga and Rosa Villegas Chávez who are in the presence of God and who have always driven me to be better.

To my beautiful Proaño Durán family, especially my beloved grandparents José Proaño Guevara and Luz Durán Merino for being that instrument to reach the feet of Christ.

# Résumé étendu en français

L'humanité est confrontée au problème de créer une civilisation plus intelligente. Pour y parvenir, il est nécessaire de comprendre et de résoudre différents problèmes sociaux et scientifiques qui nous permettent d'avoir de nouveaux niveaux d'efficacité et d'optimisation. Ces problèmes nécessitent généralement de résoudre des tâches trop complexes. Par exemple, simuler la dynamique moléculaire pour créer de nouveaux matériaux.

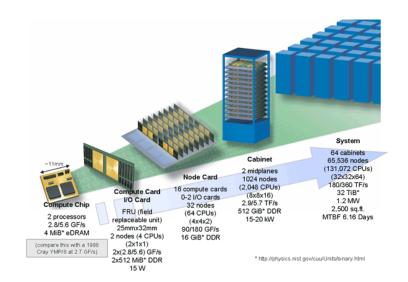

En ce sens, le calcul haute performance est devenu un élément clé pour résoudre plusieurs de ces problèmes à travers des modèles, des simulations et des analyses. Mais pour devenir de plus en plus efficaces, ces systèmes doivent constamment évoluer.

Aujourd'hui, la tendance est de se rapprocher de l'exascale dans les systèmes et ainsi de résoudre les problèmes beaucoup plus gros et plus rapidement. Cependant, pour atteindre cet objectif, nous devons tout améliorer, du matériel aux applications. C'est là que l'hétérogénéité devient l'un des facteurs les plus récents permettant des systèmes plus rapides. Elle permet de travailler avec différents types d'applications où il peut être combiné, des processeurs pour les ordinateurs petits/complexes et des GPU pour les ordinateurs grands/simples. L'hétérogénéité n'a pas seulement approchée les processeurs, mais ces dernières années, elle a commencé à apparaître dans les systèmes de mémoire.

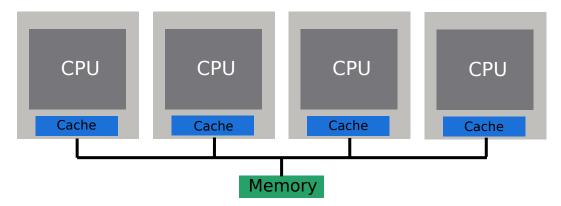

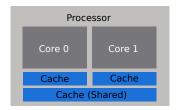

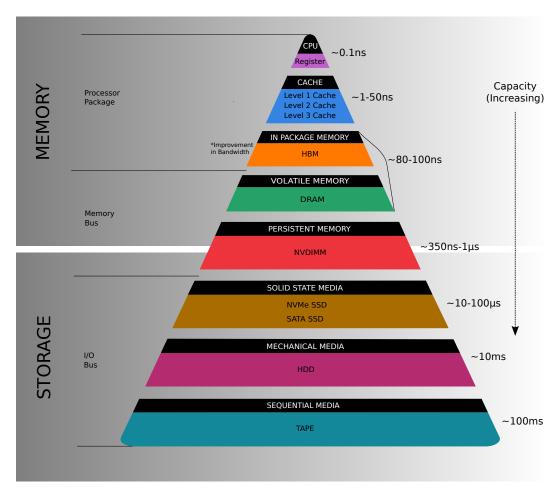

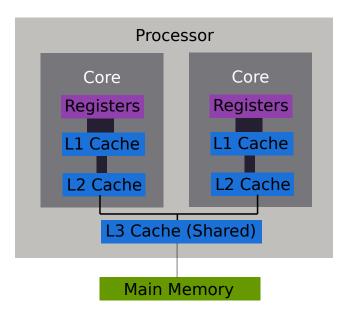

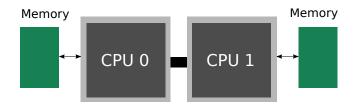

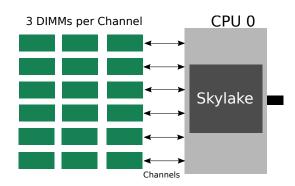

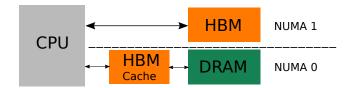

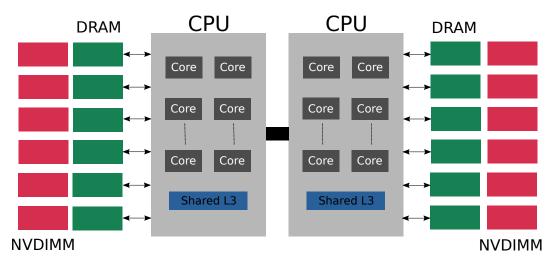

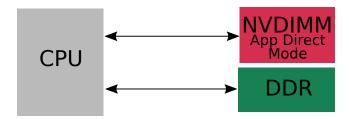

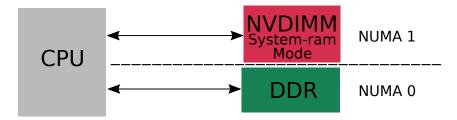

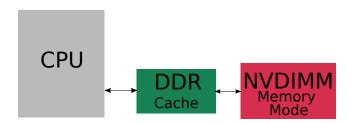

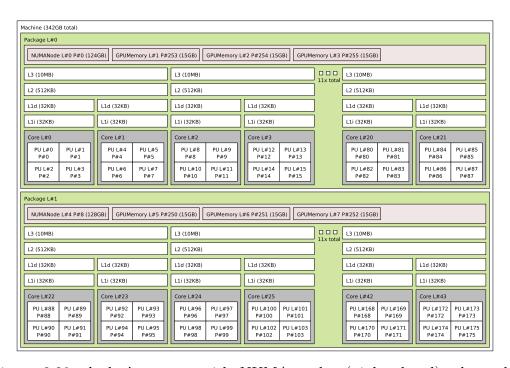

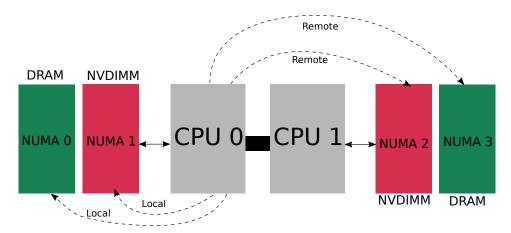

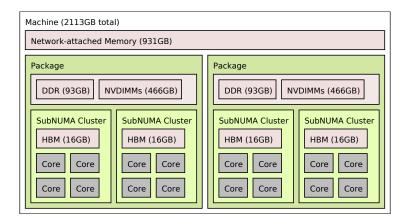

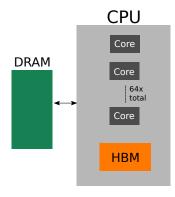

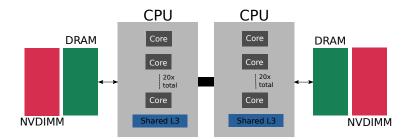

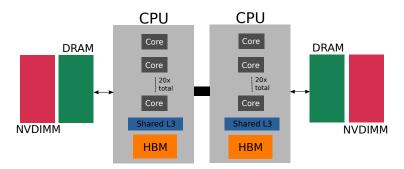

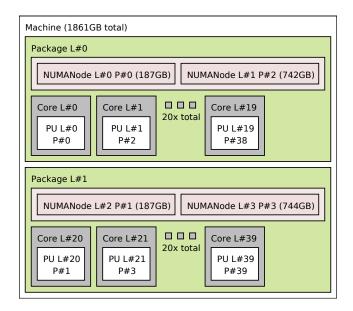

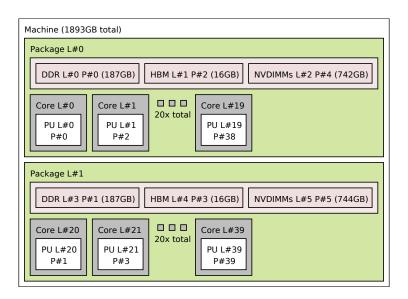

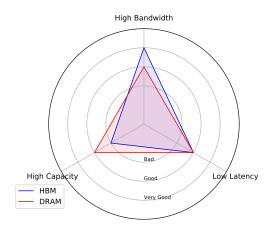

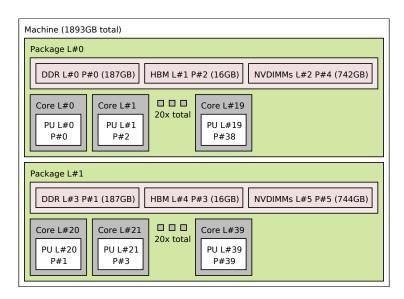

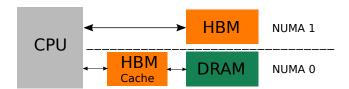

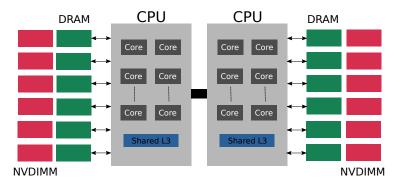

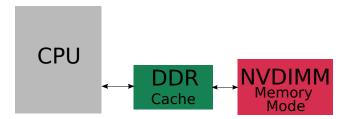

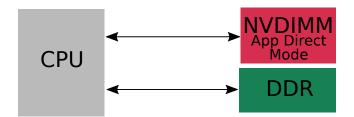

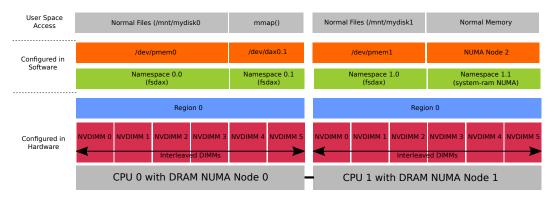

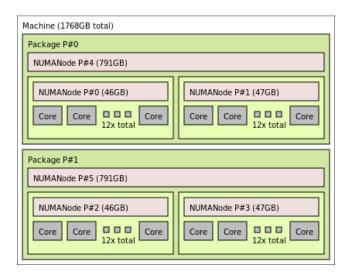

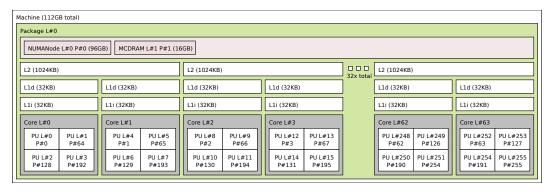

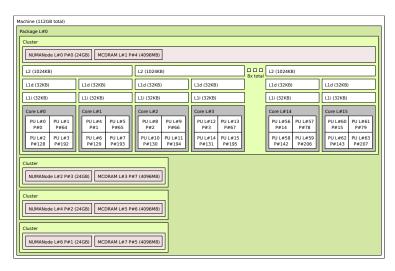

Actuellement, nous pouvons déjà trouver des systèmes de mémoire qui contiennent plusieurs types de mémoire coexistants. Les systèmes de mémoire dans le calcul haute performance (HPC) ont subi des changements majeurs ces dernières années. Outre la mémoire principale, le stockage et plusieurs niveaux de cache, les serveurs sont livrés avec un accès mémoire non uniforme (NUMA) et peuvent contenir différents types de mémoire. Par exemple, la mémoire à bande passante élevée (HBM) intégrée au processeur et la mémoire non volatile (NVDIMM) ont été introduites dans la hiérarchie.

Ces changements sont nécessaires pour rapprocher de plus en plus les données du traitement et donc avoir de meilleures performances. Cependant, ce saut nécessite que les développeurs prennent en compte le fait qu'ils doivent développer ou modifier des applications pour s'adapter au système de mémoire hétérogène. Cela pose la question principale qui est de savoir où allouer mes objets mémoire.

Avant de répondre à la question principale, il fallait d'abord être capable

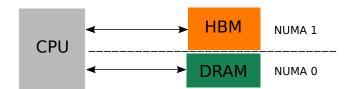

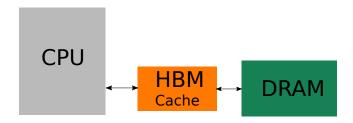

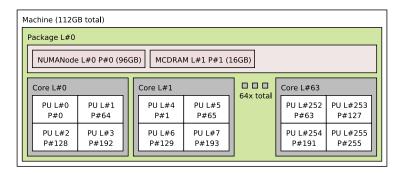

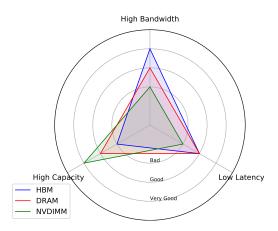

d'identifier quel type de mémoire nous avons dans le matériel. Comme mentionné, la gestion de la mémoire dans HPC devient de plus en plus difficile en raison de l'hétérogénéité réelle du système de mémoire. En ce sens, nous considérons que pour mieux prendre en charge ces nouveaux systèmes de mémoire, il est crucial d'identifier les types de mémoire et d'exposer leurs caractéristiques, afin que les couches logicielles supérieures puissent avoir une idée de l'endroit où allouer les tampons critiques pour les performances. Les systèmes de mémoire hétérogènes ne sont pas de forme unique et varient d'une plate-forme à l'autre, maintenant toujours une interaction d'au moins deux acteurs de mémoire différents, c'est-à-dire des systèmes qui combinent par example, HBM + DRAM.

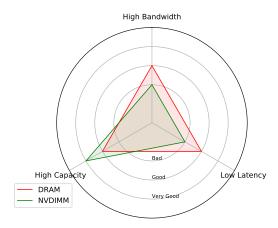

En fait, identifier les types de mémoire consiste à comprendre quels nœuds NUMA sont de quel type. Pour ce faire, nous considérons que le système de mémoire est un élément clé dans la prise de conscience de la topologie pour avoir une allocation appropriée des tampons mémoire, et pour cela, chaque type de mémoire peut être caractérisé par certains attributs de mémoire tels que la bande passante, la latence, capacité, persistance, énergie, etc. Ces attributs nous permettent non seulement d'identifier le type de mémoire mais nous permettent également d'avoir un ordre sur le système de mémoire hétérogène. Dans ce travail, nous assignons un ensemble d'attributs à chaque dispositif mémoire, compte tenu de l'hétérogénéité du système. Ces attributs nous aident à les classer en fonction des métriques intuitives déjà mentionnées pour aider à la sélection du bon périphérique de mémoire en fonction d'un cas d'utilisation. Avec ces classements des périphériques mémoire disponibles, une application peut le choisir pour allouer ses données.

Ensuite, pour ouvrir ces idées aux développeurs, nous avons étendu une interface de programmation de la bibliothèque hwloc qui permet de récupérer la meilleure cible mémoire en fonction de l'attribut que l'on se demande d'utiliser. Il comprend des fonctions qui nous permettent d'identifier la meilleure cible mémoire étant donné un attribut mémoire et un initiateur (ensemble de cœurs accédant aux données). Il permet également de récupérer des informations sur les valeurs d'attributs, et il nous donne la possibilité d'ajouter nos propres attributs de mémoire.

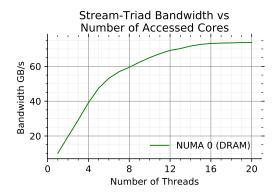

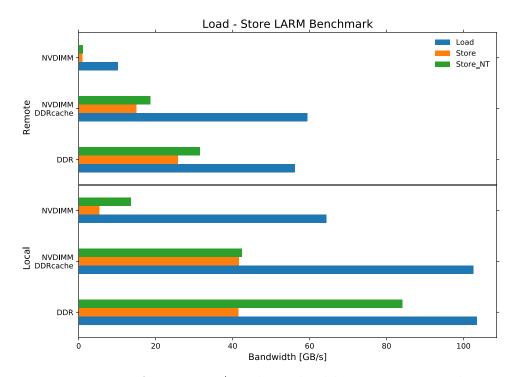

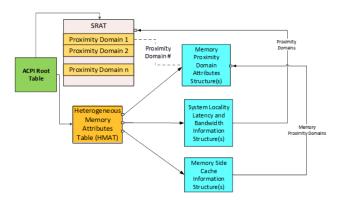

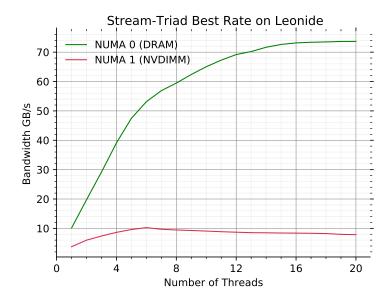

Les valeurs d'attributs proviennent de deux sources principales. Le premier, correspond à l'utilisation des tables matérielles ACPI HMAT, dans lesquelles nous pouvons trouver des informations relatives à la localité, la latence et la bande passante. Cependant, cette table n'est pas encore implémentée dans tous les systèmes. L'alternative, la plus utilisée pour le moment, consiste à mesurer expérimentalement les valeurs des attributs. Cela nous permet de caractériser les performances matérielles mais surtout d'obtenir un ordre (étant donné un attribut) sur un système de mémoire hétérogène.

Une conséquence malheureuse de l'évolution et de l'hétérogénéité croissante des systèmes mémoire est la nécessité d'adapter les applications HPC

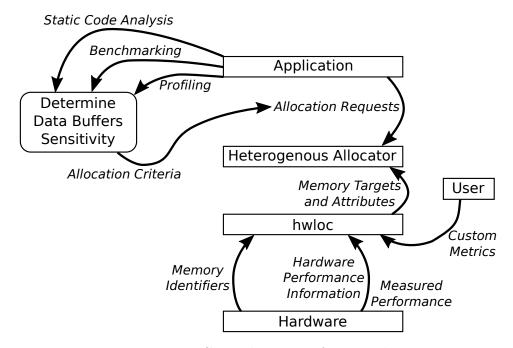

afin qu'elles puissent exploiter correctement le système mémoire. Une première étape a été effectuée lors de l'identification et de la caractérisation du système de mémoire, cependant, cela ne répond pas aux considérations que le développeur devrait avoir lorsqu'il travaille avec une application avec des charges gourmandes en mémoire. En fait, comment le développeur peut-il savoir si une application ou ses buffers internes ont une certaine affinité avec un attribut mémoire? En d'autres termes, pour savoir si l'attribut est critique pour la performance. Les applications HPC sont conçues pour prendre en charge un type de mémoire, cependant, nous considérons qu'étant donné que les applications peuvent être sensibles à la latence, la bande passante ou la capacité, il est important d'allouer au moins leurs principaux tampons au bon endroit. Nous proposons une stratégie qui met en œuvre des étapes pour fournir aux développeurs un environnement à haute productivité pour prendre en charge des systèmes de mémoire hétérogènes de manière portable. Dans cette stratégie, nous considérons qu'avant d'effectuer une demande d'allocation, nous avons besoin d'une étape intermédiaire pour déterminer la sensibilité de l'application et/ou de leurs buffers pour finalement obtenir un critère d'allocation. Nous considérons qu'il existe des développeurs très expérimentés qui sont capables de deviner si les performances d'accès à une zone sont plutôt limitée par la latence ou la bande passante, tout cela grâce à des années de travail d'optimisation de cache, de préchargement d'affinité, de tuilage, etc., un niveau de subjectivité basé sur l'expérience d'un individu. Compte tenu de cela, un cadre plus productif est nécessaire pour les non-experts en architectures matérielles et en optimisation de code.

Ensuite, nous considérons que nous devons analyser le comportement des applications pour déterminer la sensibilité des applications et de leurs buffers internes. Nous avons identifié trois options principales pour déterminer la sensibilité d'une application en évaluant, en profilant et en effectuant une analyse de code statique.

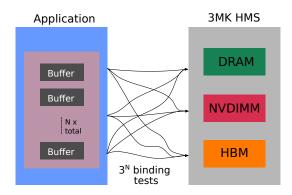

Avec le benchmarking, nous considérons que nous pouvons identifier la sensibilité d'une application en comparant différentes exécutions des applications en forçant l'ensemble du processus sur différents types de mémoire ou en forçant chacun des tampons sur différents types de mémoire. Cette approche pour déterminer les sensibilités est encore largement utilisée dans la littérature pour montrer la sensibilité de certains repères à certains attributs. Cependant, la complexité des applications pourrait imposer de nombreuses exécutions différentes. Pour cette raison, nous étudions également le profilage.

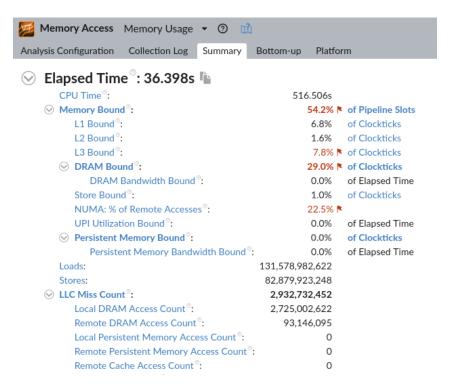

Le profilage est une stratégie plus complexe qui effectue une analyse de l'exécution à l'aide de compteurs matériels et/ou d'instrumentation pour identifier en détail les problèmes liés à la mémoire tels que les goulots d'étranglement, les points chauds, etc. Il peut également être utilisé pour déterminer la sensibilité d'une application dans laquelle selon le profileur, nous pouvons avoir des métriques pertinentes qui nous donnent des indices que les

applications pourraient avoir une certaine sensibilité en termes de latence ou de bande passante. De plus il est possible d'identifier très facilement les principaux tampons de l'application qui rencontrent des problèmes et d'identifier ces tampons dans le code source.

La troisième option consiste à étudier le code source lors de la compilation, dans lequel nous pourrions fournir au compilateur des informations supplémentaires lors de l'exécution, par exemple, ce qui se passera dans le futur avec un tampon. Les compilateurs tentent depuis longtemps de réduire la latence d'accès à la mémoire en insérant des instructions de pré-chargement pour des applications spécifiques et/ou des plates-formes spécifiques. Nous pensons que ce type de travail devrait permettre aux compilateurs de détecter la sensibilité à la latence ou à la bande passante des noyaux et ainsi fournir des conseils de sensibilité aux systèmes d'exécution. Par exemple, les accès en continu/linéaires à des tampons contigus peuvent être détectés et marqués comme sensibles à la bande passante sans que l'utilisateur n'ait besoin de comparer ou de profiler manuellement l'application.

Ensuite, les développeurs doivent préparer les applications et les runtimes pour travailler sur les différents systèmes de mémoire hétérogènes, mais il est clair qu'ils n'ont pas toujours accès à des machines avec des scénarios de mémoire différents. C'est pourquoi les outils nécessaires doivent être fournis afin que les développeurs puissent préparer leurs applications à affronter différents systèmes de mémoire hétérogènes. En fait, les développeurs peuvent facilement travailler avec le système de mémoire hétérogène KNL très connu car la configuration reste toujours la même. Cependant, cela change avec les NVDIMM dans les plates-formes génériques, où le nombre ou les types de mémoires peuvent changer de manière significative. Par conséquent, il est nécessaire de tester le runtime/les applications sur une grande variété de configurations matérielles pour s'assurer que notre logiciel est portable.

Tout d'abord, nous avons abordé les scénarios dont le développeur a besoin pour tester les performances de son application déjà développée sur une mémoire hétérogène spécifique. Et deuxièmement, nous avons abordé différents outils, avec lesquels nous pouvons exposer des configurations de mémoire à des applications qui ne correspondent pas précisément à l'environnement physique, c'est-à-dire que nous présentons des outils qui peuvent être utiles pour émuler des systèmes de mémoire hétérogènes. En fait, cela n'expose pas une véritable performance hétérogène, mais dans ce cas, il s'agit d'exposer le système de mémoire hétérogène comme le ferait un système réel.

Lorsqu'on parle de simulation de performances, on fait référence au fait de simuler le comportement que doit avoir une certaine application lorsqu'elle fait face à un scénario mémoire très éventuellement difficile d'accès pour le développeur. Par exemple, le cas d'un futur système à venir avec un système de mémoire hétérogène différent. Nous avons identifié des options qui nous permettent de modifier les performances des applications. Premièrement, l'accès mémoire

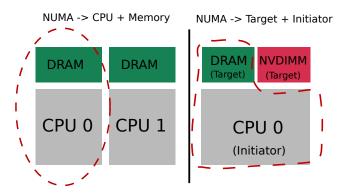

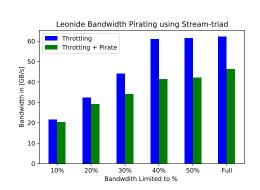

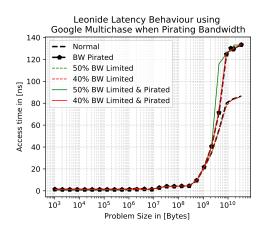

non uniforme (NUMA) a été généralisé dans les machines multi-sockets, dans lesquelles chaque socket a un contrôleur mémoire associé. En raison de la distance relative entre les processeurs et les dispositifs de mémoire, l'accès à la mémoire n'est pas uniforme. Depuis la naissance des systèmes NUMA, diverses études ont été menées pour tenter de minimiser l'impact de cette situation. Deuxièmement, la technologie Intel Resource Director (Intel RDT) est un outil qui permet de surveiller l'allocation de cache et de mémoire. Il est exposé en tant qu'interface utilisateur pour le contrôle des ressources par le noyau Linux. Intel RDT est capable de partitionner certaines ressources telles que la hiérarchie du cache et pour notre intérêt particulier la bande passante. Et troisièmement, le piratage de mémoire est une méthode de simulation de performances qui permet de contrôler la quantité de mémoire disponible pour l'application en la co-exécutant avec une application qui lui vole de la bande passante.

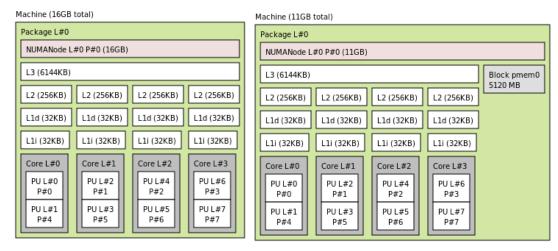

D'un autre côté, l'émulation d'un système de mémoire permet aux développeurs de préparer leurs applications pour les systèmes de mémoire de nouvelle génération. L'émulation de ces systèmes consiste à chercher en quelque sorte à exposer des dispositifs de mémoire qui ne sont pas physiquement situés dans les nœuds comme s'ils étaient présents. En émulation, on ne peut pas changer les performances comme dans la section précédente. Son utilisation est principalement dédiée à l'exposition de différents systèmes HMS pour préparer ou adapter des applications pour accéder à différents types de mémoire. C'est-àdire, tester les heuristiques et les algorithmes développés pour sélectionner la cible appropriée pour chaque tampon. L'émulation peut être effectuée à l'aide de plusieurs options, et nous les avons classées en émulation matérielle, émulation de système d'exploitation et émulation logicielle. L'émulation du HMS via le matériel fait référence à l'utilisation d'un périphérique matériel réel pour imiter la fonction d'un autre HMS. Une autre manière d'émuler des systèmes de mémoire hétérogènes consiste à utiliser des systèmes d'exploitation. Enfin, étant donné que la plupart des environnements d'exécution et des applications HPC peuvent lire la topologie matérielle, l'exposition de différentes topologies modifiera leur comportement. hwloc est souvent utilisé comme couche intermédiaire entre la découverte du matériel et de la topologie dans HPC, nous pouvons donc utiliser hwloc pour « mentir » aux applications.

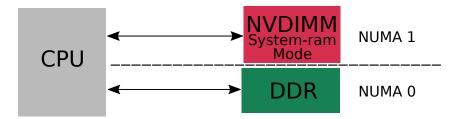

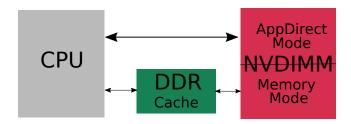

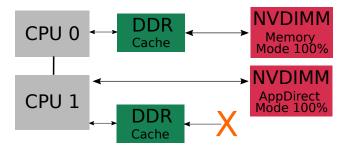

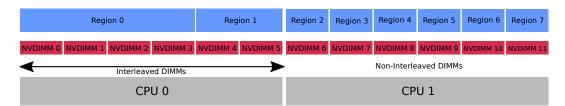

Enfin, nous nous sommes également penchés sur le problème de la coprogrammation. Les nœuds de calcul sont de plus en plus complexes, avec des dizaines de cœurs. La co-ordonnancement permet d'optimiser l'utilisation de ces nœuds là où les applications sont capables d'utiliser des ressources matérielles distinctes pour éviter la sous-utilisation des nœuds disponibles. La coplanification de plusieurs tâches sur de tels nœuds est une stratégie utile pour s'assurer que tous les cœurs sont utilisés dans les centres HPC. Cependant, le partage de nœuds entre plusieurs tâches entraîne également des problèmes tels que des conflits dans le sous-système de mémoire ou une pollution du cache. Le partitionnement des ressources est un moyen intéressant d'éviter de tels problèmes grâce aux fonctionnalités du système d'exploitation telles que les Cgroups dans le noyau Linux. L'émergence des DIMM à mémoire non volatile apporte de nouvelles stratégies pour la gestion des données dans les applications HPC. En fait, ils prennent en charge plusieurs configurations matérielles et logicielles allant d'énormes capacités volatiles au stockage hautes performances, qui peuvent être utilisées comme tampons pour absorber les pics de stockage, ou pour la récupération après une panne.

Cette thèse a été réalisée à Inria Bordeaux - Sud-Ouest et au LaBRI. Après une présentation de l'état de l'art de l'architecture mémoire, nous avons caractérisé les mémoires par des attributs simples. Nous avons fourni une interface que la bibliothèque hwloc expose aux applications pour comprendre la topologie de la mémoire et allouer des tampons. Ensuite, nous avons proposé une stratégie pour aider les développeurs à adapter leurs applications au bon usage de systèmes de mémoire hétérogènes. Comme l'accès à différentes platesformes hétérogènes n'est pas toujours possible, nous identifions plusieurs façons de simuler les performances de la mémoire hétérogène et d'émuler différentes topologies de mémoire. Enfin, nous avons construit une stratégie qui facilite le partage de plateformes à mémoire hétérogène et non volatile entre les tâches HPC co-planifiées sur les mêmes nœuds.

# Contents

| 1 | Intr | oduction, Context and Motivations         | 1 |

|---|------|-------------------------------------------|---|

|   | 1.1  | Benefits of High-Performance Computing    | 1 |

|   | 1.2  | Heterogeneous perspective of HPC          | 2 |

|   | 1.3  | Outline of the manuscript                 | 3 |

| 2 | Me   | mory Systems in HPC                       | 5 |

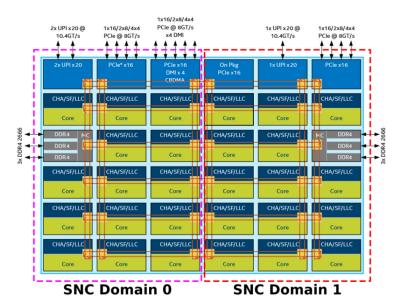

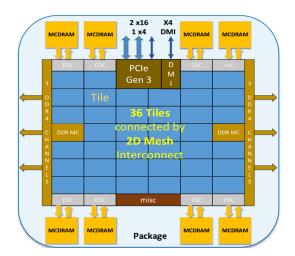

|   | 2.1  | HPC Architecture                          | 6 |

|   | 2.2  | Memory Hierarchy                          | 9 |

|   |      | 2.2.1 Registers                           | 1 |

|   |      | 2.2.2 Cache Memory Hierarchy              | 1 |

|   |      | · · · · · · · · · · · · · · · · · · ·     | 1 |

|   |      |                                           | 2 |

|   | 2.3  | New Memory Technologies                   | 5 |

|   |      | 2.3.1 HBM                                 | 5 |

|   |      |                                           | 7 |

|   |      |                                           | 9 |

|   |      |                                           | 1 |

|   | 2.4  | Impact of the Memory Subsystem            | 3 |

|   |      | 2.4.1 Combining different kinds of memory | 3 |

|   |      | · · · · · · · · · · · · · · · · · · ·     | 4 |

|   |      | 2.4.3 Summary                             | 5 |

|   | 2.5  | Software State of the art                 | 6 |

|   |      | 2.5.1 Managing Heterogeneous Memory 2     |   |

|   |      | 2.5.2 hwloc                               |   |

|   | 2.6  | Statement of the Problem                  |   |

| 3 | Nav  | vigating Complex Memory Spaces 3          | 1 |

|   | 3.1  | Exposing Memory Characteristics           | 3 |

|   |      | 3.1.1 Identifying Memories                | 5 |

|   |      | 3.1.2 Characterising Memories             | 5 |

|   | 3.2  | Memory Attributes                         | 6 |

|   |      | 3.2.1 Bandwidth                           | 6 |

|   |      | 3.2.2 Latency 3                           | 7 |

|                               | 3.3<br>3.4<br>3.5   | Attribu 3.4.1 3.4.2 3.4.3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Capacity                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 38<br>39<br>40<br>42<br>45<br>45<br>46<br>48<br>52                                                  |

|-------------------------------|---------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|

| 4                             | Pre                 | paring                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | HPC Applications to Complex Heterogeneous                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                     |

|                               | Me                  | mory S                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | ystems                                                                                                                                                                                                                                                                                                                                                                                                                                                      | <b>53</b>                                                                                           |

|                               | 4.1                 | Hetero                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | geneous Memory Allocator                                                                                                                                                                                                                                                                                                                                                                                                                                    | 54                                                                                                  |

|                               | 4.2                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | ion Criteria                                                                                                                                                                                                                                                                                                                                                                                                                                                | 56                                                                                                  |

|                               |                     | 4.2.1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Benchmarking                                                                                                                                                                                                                                                                                                                                                                                                                                                | 57                                                                                                  |

|                               |                     | 4.2.2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Profiling                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 58                                                                                                  |

|                               |                     | 4.2.3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Static Code Analysis                                                                                                                                                                                                                                                                                                                                                                                                                                        | 60                                                                                                  |

|                               | 4.3                 | Use Ca                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | se                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 61                                                                                                  |

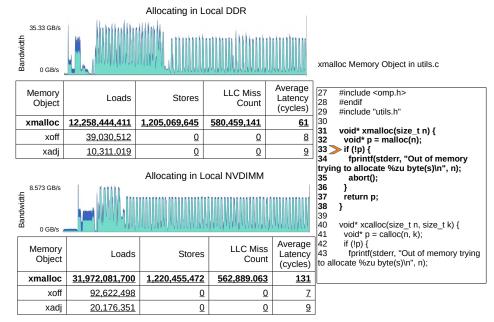

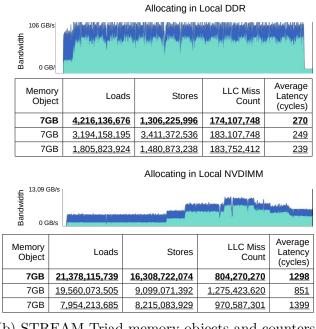

|                               |                     | 4.3.1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Benchmarking                                                                                                                                                                                                                                                                                                                                                                                                                                                | 61                                                                                                  |

|                               |                     | 4.3.2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Profiling                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 63                                                                                                  |

|                               |                     | 4.3.3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 63                                                                                                  |

|                               |                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                     |

| 5                             | Soft                | ware                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Tools for the development on Heterogeneous                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                     |

| 5                             |                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Tools for the development on Heterogeneous                                                                                                                                                                                                                                                                                                                                                                                                                  | 67                                                                                                  |

| 5                             | Me                  | mory                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | _                                                                                                                                                                                                                                                                                                                                                                                                                                                           | <b>67</b>                                                                                           |

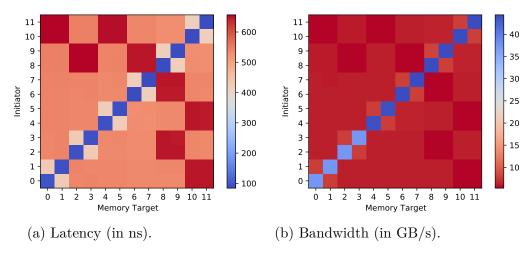

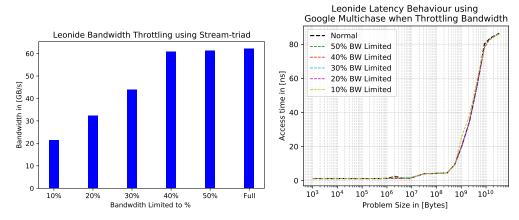

| 5                             | Me                  | <b>mory</b><br>Perforn                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | nance Simulation                                                                                                                                                                                                                                                                                                                                                                                                                                            | <b>67</b> 68 69                                                                                     |