# Development and validation of a predictive model to ensure the long-term electromagnetic compatibility of embedded electronic systems

Chaimae Ghfiri

## ▶ To cite this version:

Chaimae Ghfiri. Development and validation of a predictive model to ensure the long-term electromagnetic compatibility of embedded electronic systems. Electromagnetism. INSA de Toulouse, 2017. English. NNT: 2017ISAT0033. tel-02062116

# HAL Id: tel-02062116 https://theses.hal.science/tel-02062116

Submitted on 8 Mar 2019

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

## En vue de l'obtention du

# DOCTORAT DE L'UNIVERSITÉ DE TOULOUSE

Délivré par :

| Présentée et soutenue par :                   |  |

|-----------------------------------------------|--|

| le                                            |  |

| Titre:                                        |  |

|                                               |  |

|                                               |  |

|                                               |  |

| École doctorale et discipline ou spécialité : |  |

| Unité de recherche :                          |  |

| Directeur/trice(s) de Thèse :                 |  |

|                                               |  |

| Jury:                                         |  |

## **Acknowledgments**

First and foremost, I would like to express my sincere gratitude to my supervisors who guided me through these last three years and contributed in the achievement of this project. Special thanks to Alexandre Boyer for being my major advisor on various technical and scientific topics and for his availability throughout this period, thank you for your support, motivation and your professionalism. Also, I would like to thank my supervisor Sonia Ben Dhia who, despite her many responsibilities, managed to follow this project and gave me relevant advice and technical recommendations. And thank you to André Durier for his support and encouragement.

I am also grateful to the IRT Saint-Exupéry administrative collaborators, Gilbert Casamatta and Ariel Sirat for allowing me to realize this project and the trust they had toward my skills. Thank you to Régine Sutra Orus for her openness and willingness to discuss and give professional and personal advice. And thank you to all the project members.

Thank you to the Professors Fabian Vargas and Bernd Deutschmann for accepting to review this manuscript, the time they afford to do this and for being a part of the thesis committee.

During this Ph.D. period, I was also supported by my colleagues Mustafa Zerarka, Samuel Pin, Siham Hairoud and Omar Chihani, to whom I would like to express my gratitude. Thank you to Alain Bensoussan who was my reference and my main advisor on the various aspects of reliability and who did not hesitate to share his experience and skills with me, thank you for your generosity. I also would like to thank Sebastien Serpaud for the technical support and the interesting discussions we have had. Thank you to Huang He for introducing me the EMC laboratory at INSA. I won't forget the interns Nathan Prim, Manuel Gonzalez Sentis and Yevgeniy Nurseitov who have performed remarkable work in this project. Thank you to Olivier Crepel for the discussions and Christian Marot for the technical support. My excuses go to those I did not mention, I would like them to know that I really consider their support and for that I am sincerely grateful.

And last but no means least, many thanks to my supporting club; my parents, my lovely siblings and fiancé for being there all along this period to provide me the emotional and moral assistance despite the long distance separating us. I am really grateful to my best friend Amine for his support and all my friends. My special gratitude goes to my uncle and second father Said Ghfiri to whom I owe realizing my project. Thank you to every member of my family.

### **Abstract**

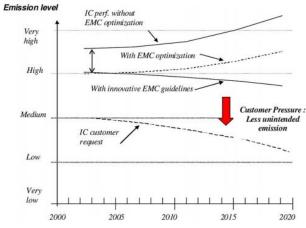

With the technological evolution of integrated circuits (ICs) through the transistors scaling, which leads to the multiplication of the number of transistors within a chip, the requirements in terms of emission and immunity levels become more restrictive in the aeronautic, space and automotive industries. Moreover, since the evolution of Electromagnetic Compatibility (EMC) levels of electronic equipment after aging must meet the EMC long-term robustness requirements, the EMC margins defined by the manufacturers are often overestimated and the filtering systems designed by the equipment manufacturer could be oversized.

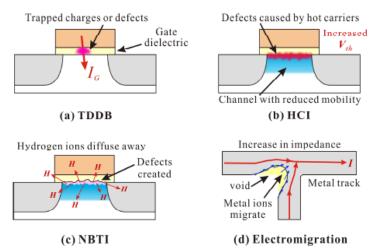

Therefore, for the integrated circuits dedicated to embedded applications, it is necessary to study the different aspects of EMC modeling as well as the reliability the modeling. These last years, several standards have been proposed for the construction of predictive EMC models such as ICEM-CE/RE (Integrated Circuit Emission Model for Conducted and Radiated Emission) and ICIM-CI (Integrated Circuit Immunity Model for Conducted Immunity). On the other hand, to integrate the effect of aging in EMC models, it is important to study the main intrinsic degradation mechanisms that accelerate the aging of ICs, such as HCI (Hot Carrier Injection), TDDB (Time Dependent Dielectric Breakdown), EM (Electromigration) and NBTI (Negative Bias Temperature Instability). For this purpose, there are existing models for the reliability prediction, such as the MIL-HDBK-217 standard and the FIDES standard. However, these models could take into account only the activation of one degradation mechanism. The combination of several degradation mechanisms could be critical for the IC performances and could contribute in the evolution of EMC level.

This dissertation introduces the different aspects of EMC and reliability modeling. This work deals with the construction of a conducted emission model of an FPGA and the proposition of new modeling methodologies. Furthermore, the reliability of the tested FPGA is described using a new predictive model, which takes into account the activation of the different degradation mechanisms. The reliability model has been combined with the EMC model for the long-term conducted emission level prediction.

## Résumé

Avec l'avancement technologique des circuits intégrés à travers la miniaturisation des tailles des transistors et leur multiplication au sein d'une même puce, l'intégration des circuits dans des systèmes embarqués complexes, principalement dans l'industrie aéronautique, spatiale et automobile, rencontre de plus en plus d'exigences en termes de respect des niveaux d'émission et d'immunité. De plus, étant donné que l'évolution des niveaux de Compatibilité Electromagnétique (CEM) des équipements électroniques doit respecter ces exigences à longterme, les marges définis par les industriels sont souvent surestimés et les systèmes de filtrages établis par les équipementiers peuvent être surdimensionnés.

De ce fait, pour les circuits intégrés dédiés aux applications embarquées, il est nécessaire d'étudier les deux aspects qui concernent la modélisation CEM ainsi que la modélisation de la fiabilité. Ces dernières années, des standards ont été proposés et permettent la construction de modèles CEM prédictifs tel que ICEM-CE/RE (Integrated Circuit Emission Model for Conducted and Radiated Emission) et ICIM-CI (Integrated Circuit Immunity Model for Conducted Immunity). De plus, pour intégrer l'effet du vieillissement dans les modèles CEM, il faut étudier les principaux mécanismes de dégradation intrinsèques aux circuits intégrés qui accélèrent leur vieillissement tels que le HCI (Hot Carrier Injection), TDDB (Time Dependent Dielectric Breakdown), EM (Electromigration) et NBTI (Negative Bias Temperature Instability). Des modèles standardisés sont utilisés dans les différents domaines industriels qui permettent la construction de modèle de fiabilité tels que le standard MIL-HDBK-217 et le standard FIDES. Cependant, ils ne permettent de prendre en compte qu'un seul mécanisme de dégradation à la fois.

Ce manuscrit de thèse introduit ces aspects de modélisation CEM et de fiabilité. Il traite également la construction d'un modèle d'émission conduite d'un FPGA avec la proposition de nouvelle méthodologie de modélisation. Ensuite, l'étude de la fiabilité du FPGA est décrite à travers l'utilisation d'un nouveau modèle permettant la prise en compte des différents mécanismes de dégradations et a été combiné au modèle CEM pour la prédiction des niveaux d'émissions conduite à long-terme.

## **TABLE OF CONTENTS**

| Abstract                                                                             | i    |

|--------------------------------------------------------------------------------------|------|

| Résumé                                                                               | ii   |

| TABLE OF CONTENTS                                                                    | I    |

| LIST OF FIGURES                                                                      | IV   |

| LIST OF TABLES                                                                       | XI   |

| List of acronyms                                                                     | XIII |

| General introduction                                                                 | 1    |

| Thesis context                                                                       | 1    |

| Scope of this dissertation                                                           | 3    |

| References                                                                           | 5    |

| Chapter I. Effect of ICs reliability issues on long-term electromagnetic robustness  | 6    |

| 1. Overview on EMC of integrated circuits                                            | 6    |

| 1.1. Evolution of CMOS technology                                                    | 6    |

| 1.2. Electromagnetic compatibility of integrated circuits for embedded applications. | 9    |

| 2. Integrated circuits reliability issues                                            | 19   |

| 2.1. Introduction                                                                    | 19   |

| 2.2. Impact of technology scaling on the long-term reliability of ICs                | 20   |

| 2.3. Degradation mechanisms                                                          | 22   |

| 3. Aging effect on EMC                                                               | 36   |

| 3.1. Electromagnetic robustness of ICs                                               | 36   |

| 3.2. Aging effect on electromagnetic emissions (EME) of ICs                          | 40   |

| 3.3. Aging effect on electromagnetic susceptibility (EMS) of ICs                     | 42   |

| 3.4. EMC modelling taking into account the aging                                     | 45   |

| 4. Conclusion                                                                        | 48   |

| 5. References                                                                        | 49   |

| Chapter II. Electromagnetic compatibility modeling of integrated circuits            | 53   |

| 1. General overview on EMC and SI modeling                                           | 54   |

| 1.1. Introduction                                                            | 54           |

|------------------------------------------------------------------------------|--------------|

| 1.2. IBIS model                                                              | 57           |

| 1.3. ICEM-CE model                                                           | 59           |

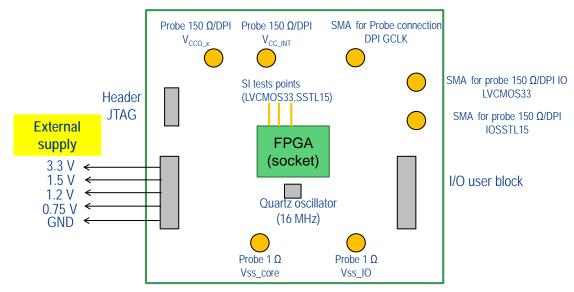

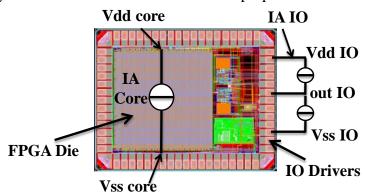

| 2. Presentation of the circuit under test                                    | 67           |

| 2.1. The circuit under test                                                  | 67           |

| 2.2. Description of the test boards                                          | 68           |

| 3. Construction of an ICEM-CE model of a FPGA                                | 70           |

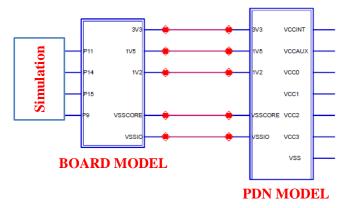

| 3.1. Experimental protocol for the construction of the PDN model             | 70           |

| 3.2. Construction of the PDN model                                           | 75           |

| 3.3. Modeling of ELECIS-F board                                              | 81           |

| 3.4. Construction of the internal activity of the FPGA                       | 85           |

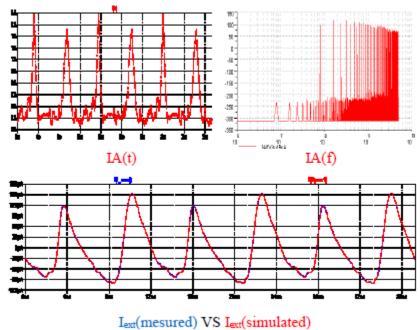

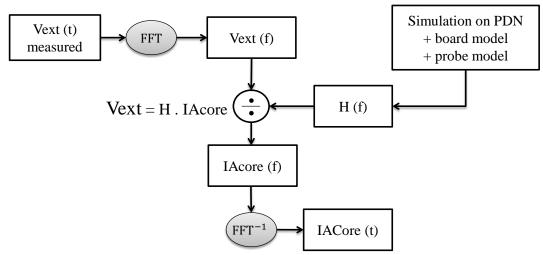

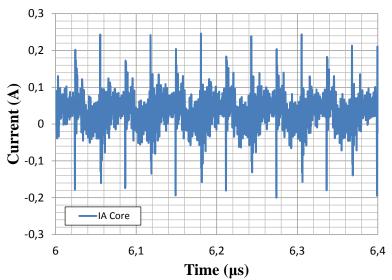

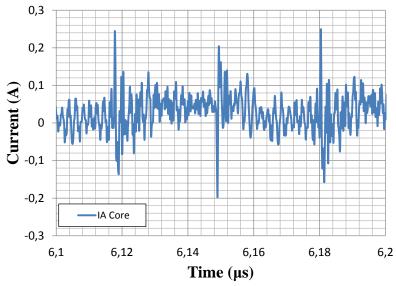

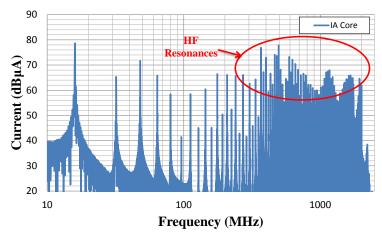

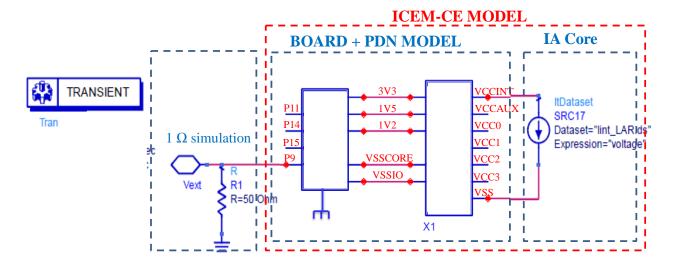

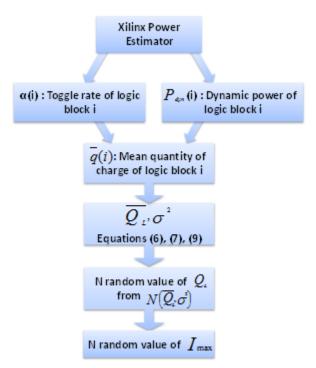

| 4. New methodology for the IA core construction                              | 100          |

| 4.1. Influence of the instantaneous current consumption waveform on emission | spectrum 101 |

| 4.2. Presentation of the IA construction methodology                         | 102          |

| 4.3. Statistical method for construction of a random IA                      | 104          |

| 4.4. Validation of the IA core model                                         | 106          |

| 4.5. Comparison between the inverse method and the new methodology for IA    | construction |

|                                                                              | 113          |

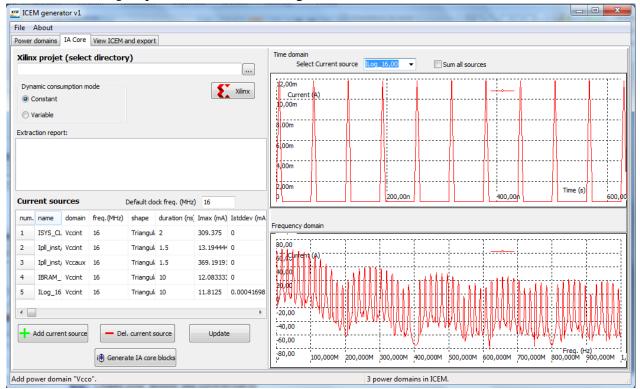

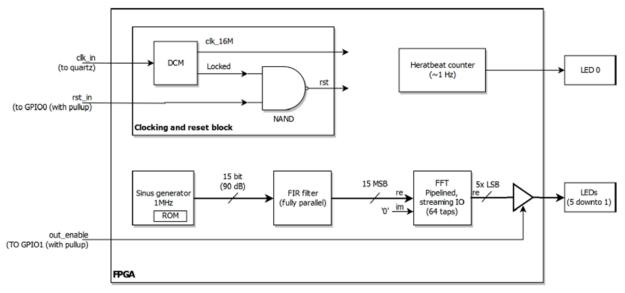

| 5. Presentation of ICEM Generator tool                                       | 115          |

| 5.1. ICEM GENERATOR tool                                                     | 115          |

| 5.2. Validation of ICEM GENERATOR tool                                       |              |

| 6. Conclusion                                                                | 119          |

| 7. References                                                                | 121          |

| Chapter III. Predictive reliability modeling                                 | 123          |

| 1. Historical perspective of reliability prediction                          | 123          |

| 1.1. General purpose of reliability prediction                               | 123          |

| 1.2. History of reliability prediction approach                              | 125          |

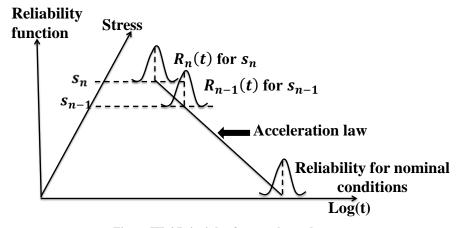

| 2. Acceleration models for reliability prediction                            | 131          |

| 2.1. General overview on accelerated tests                                   | 131          |

| 2.2. Scale reliability laws                                                  | 133          |

| 2.3. Accelerated lifetime models                                             | 134          |

| 3. The Multiple Temperature Operational Life (MTOL) method                  | 137 |

|-----------------------------------------------------------------------------|-----|

| 3.1. Introduction to MTOL model                                             | 137 |

| 3.2. Presentation of the MTOL method                                        | 138 |

| 3.3. Presentation of MSTORM tool                                            | 143 |

| 4. Conclusion                                                               | 148 |

| 5. References                                                               | 149 |

| Chapter IV. Long-term electromagnetic robustness                            | 151 |

| 1. General overview on reliability accelerated testing                      | 151 |

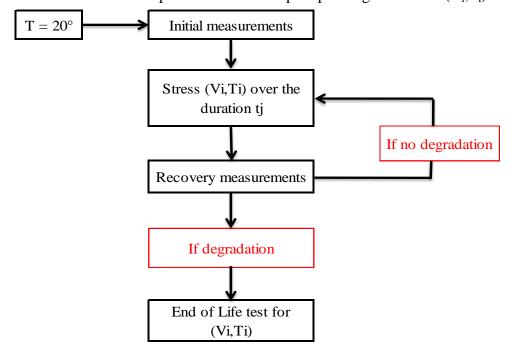

| 2. Methodology of accelerated life testing                                  | 153 |

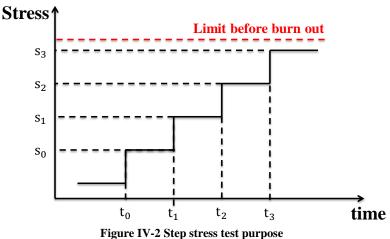

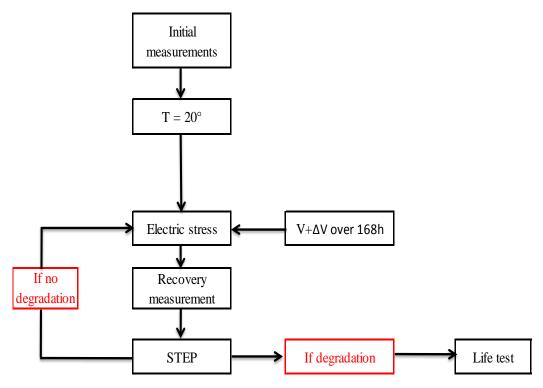

| 2.1. Step-Stress Accelerated Life Test (SSALT)                              | 153 |

| 2.2. Multiple High Temperature Operating Life test (M-HTOL)                 | 156 |

| 2.3. Experimental tests strategy                                            | 158 |

| 3. Experimental results of accelerated life test                            | 160 |

| 3.1. Experimental results of SSALT                                          | 160 |

| 3.2. Experimental results of M-HTOL                                         | 167 |

| 4. Reliability model construction                                           | 176 |

| 4.1. Methodology of reliability model construction                          | 176 |

| 4.2. Construction and validation using MSTORM model                         | 181 |

| 4.3. Conclusion on reliability model construction                           | 188 |

| 5. Long-term electromagnetic robustness: Study of ICEM-CE model after aging | 189 |

| 5.1. IA Core block construction after aging                                 | 189 |

| 5.2. IA IO block construction                                               | 193 |

| 6. Conclusion.                                                              | 197 |

| 7. References                                                               | 199 |

| General Conclusion                                                          | 200 |

| ANNEX 1 - EMC requirements in the standards                                 | 205 |

| 1. EMC requirements at equipment level                                      | 205 |

| 2. EMC requirements at component level                                      | 208 |

| ANNEX 2 - Overview on the IRIS Standard                                     | 210 |

## LIST OF FIGURES

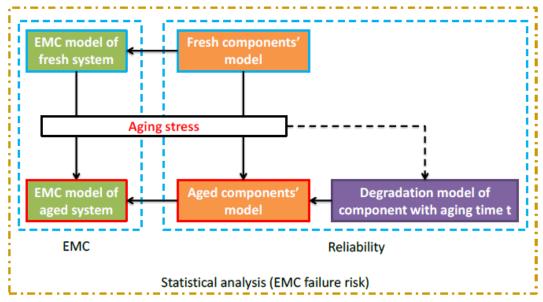

| Figure 1 Long-term electromagnetic robustness                                                                                 |

|-------------------------------------------------------------------------------------------------------------------------------|

| Figure 2 Workflow of long-term electromagnetic robustness prediction                                                          |

| Figure I-1 Reduction of the gate length of CMOS process over the years7                                                       |

| Figure I-2 Evolution of ICs characteristics with the technology scaling [15]7                                                 |

| Figure I-3 Evolution of the leakage power and the dynamic power with technology scaling for                                   |

| different temperatures and constant die size [3]8                                                                             |

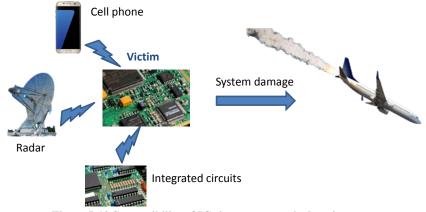

| Figure I-4 Elements contributing in an EMC9                                                                                   |

| Figure I-5 EMC issues of integrated circuits [1]                                                                              |

| Figure I-6 Sources of EME in an aeronautical system                                                                           |

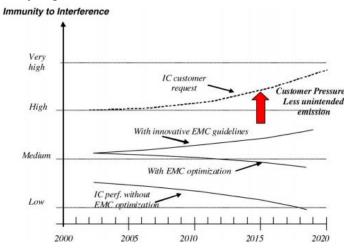

| Figure I-7 Evolution of the emission level requirements with the technology evolution [32]12                                  |

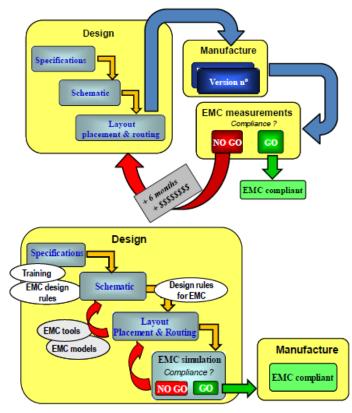

| Figure I-8 IC design flow with taking into account EMC compliance in the design (top), taking                                 |

| EMC compliance in the design (bottom) [1]                                                                                     |

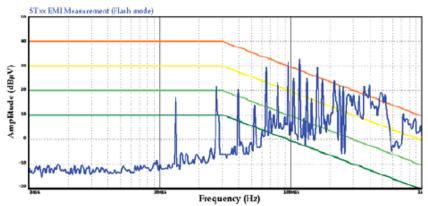

| Figure I-9 Emission spectrum of the STXX microcontroller generated by the flash unit [28]14                                   |

| Figure I-10 Susceptibility of ICs in an aeronautical environment                                                              |

| Figure I-11 Evolution of the immunity level requirements with the technology evolution [32]17                                 |

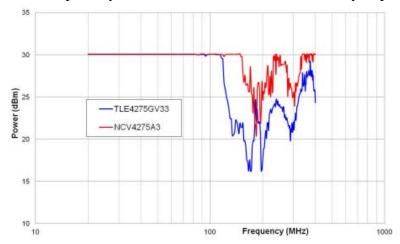

| Figure I-12 Immunity level of two different LDOs [68]                                                                         |

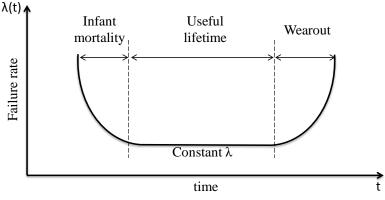

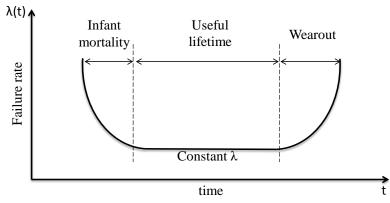

| Figure I-13 Bathtub curve                                                                                                     |

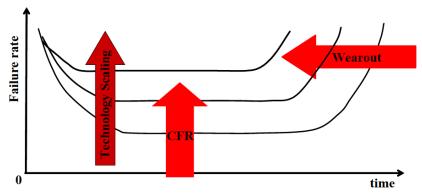

| Figure I-14 Evolution of the bathtub curve with the technology scaling [3]21                                                  |

| Figure I-15 Trends of power supply and threshold voltage and gate oxide thickness with the                                    |

| evolution of CMOS channel length [23]                                                                                         |

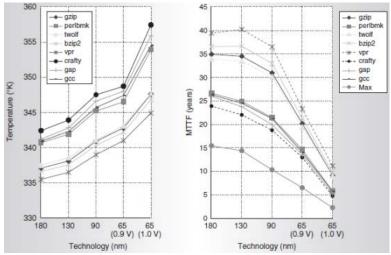

| Figure I-16 Maximum temperature reached for different structure (Left), MTTF evolution with                                   |

| the technology scaling (right) [39]                                                                                           |

| Figure I-17 Illustration of the degradation mechanisms: TDDB, HCI, EM, NBTI [24]23 $$                                         |

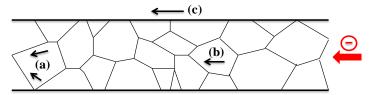

| Figure I-18 Illustration of various diffusion processes within the lattice of an interconnection: (a)                         |

| grain boundary diffusion, (b) bulk diffusion, and (c) surface diffusion24                                                     |

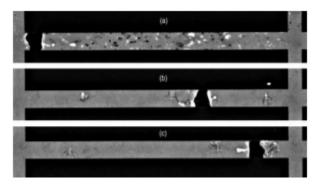

| Figure I-19 Voids induced by electromigration in the metallization of interconnections and vias                               |

| [43]                                                                                                                          |

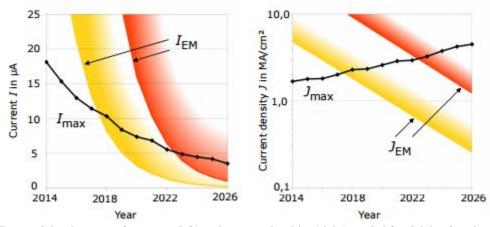

| Figure I-20 Expected development of currents (left) and current densities (right) needed for                                  |

| driving four inverter gates, according to ITRS 2011 [27]. EM degradation needs to be considered                               |

| when crossing the yellow barrier of currents ( $I_{\text{EM}}$ ) and current densities ( $J_{\text{EM}}$ ). The solutions are |

| not known in the red area                                                                                                     |

| Figure I-21 Impact ionization in the vicinity of the drain caused by a hot carrier [43]26                                     |

| Figure I-22 Drain Avalanche Hot Carrier (DAHC) mechanism                                                                      |

| Figure I-23 Channel Hot Electron mechanism                                                                                    |

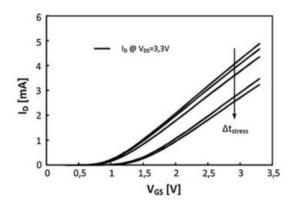

| Figure I-24 Characteristics of transfers of the drain current with respect to the variation of the                            |

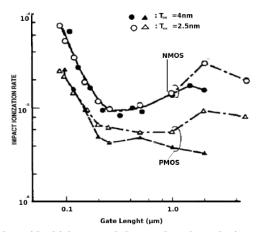

| gate voltage (Ids / Vgs) (a), with respect to the variation of the drain voltage (Ids / Vds) (b)28 $$                         |

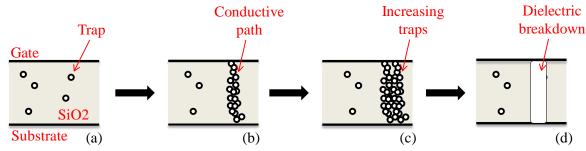

| Figure I-25 Effect of the oxide thickness and the gate length on the impact ionization rate $[56]$ . 29                       |

| Figure I-26 Steps of creation of the degradations in the dielectric of a MOSFET generated by the                              |

| TDDB mechanism30                                                                                                              |

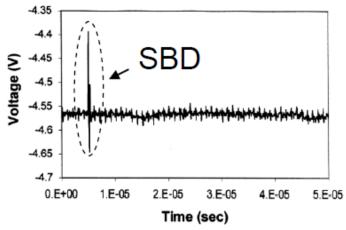

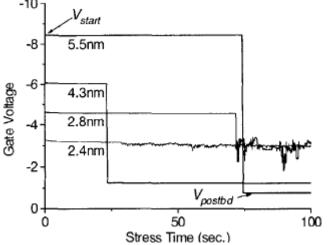

| Figure I-27 Appearance of an SBD on the gate voltage [46]                                       | 31           |

|-------------------------------------------------------------------------------------------------|--------------|

| Figure I-28 Breakdown on the gate voltage for different oxide thickness [47]                    | 31           |

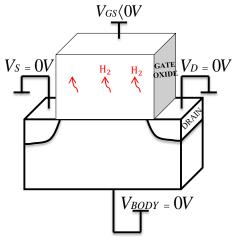

| Figure I-29 Electric configuration of the NBTI mechanism activation                             | 33           |

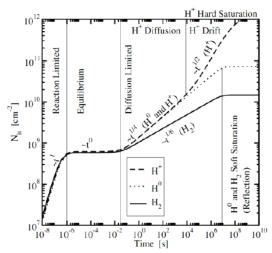

| Figure I-30 Illustration of the five stages of a RD model                                       | 34           |

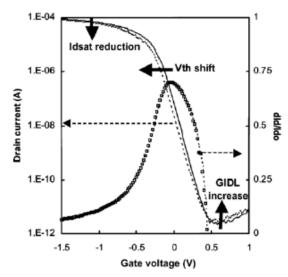

| Figure I-31 Principal degradation induced by the NBTI on transistors [52]                       | 34           |

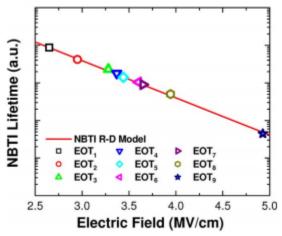

| Figure I-32 NBTI lifetime evolution with the increase of the electric field [54]                |              |

| Figure I-33 Long-term electromagnetic robustness (EMR) [58]                                     | 37           |

| Figure I-34 Electromagnetic robustness characterization methodology [57]                        | 39           |

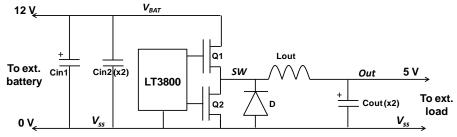

| Figure I-35 Electrical diagram of the studied DC-DC converter in [62]                           | 40           |

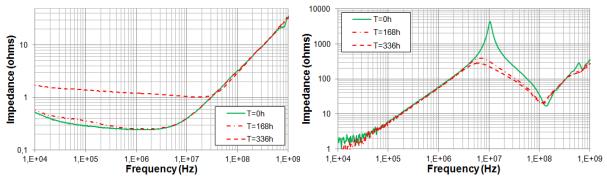

| Figure I-36 Impedance evolution before and after aging on an electrolytic capacitor (le         | eft) and the |

| output inductor (right) [62]                                                                    | 41           |

| Figure I-37 Evolution of the I(V) characteristics of the Schottky diode (left) and a            | TVS diode    |

| (right) [62]                                                                                    | 41           |

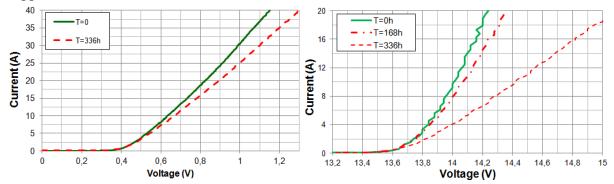

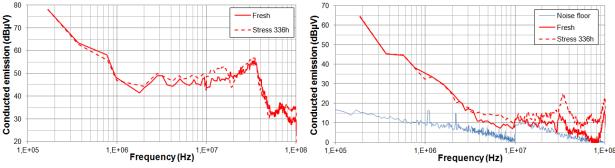

| Figure I-38 Conducted emission at the input (left) and the output (right) of the DC-DC          | Converter    |

| before and after aging [62]                                                                     | 42           |

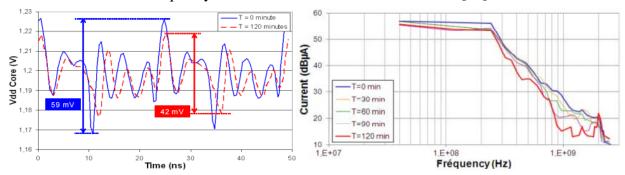

| Figure I-39 Evolution of the core power voltage (left) and the spectral current of cond         | acted noise  |

| (right) after aging [63]                                                                        | 42           |

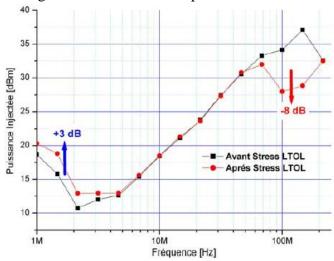

| Figure I-40 The conducted immunity level of a 65 nm integrated circuit before and               | after aging  |

| [30]                                                                                            | 43           |

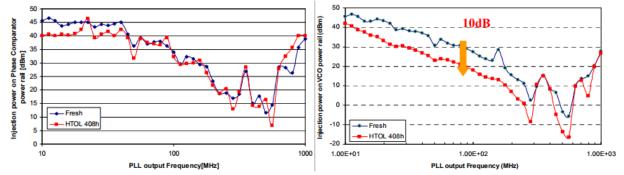

| Figure I-41 PLL susceptibility threshold with an injection on Phase comparator (left)           | and VCO      |

| power rails (right) before and after ageing [67]                                                | 44           |

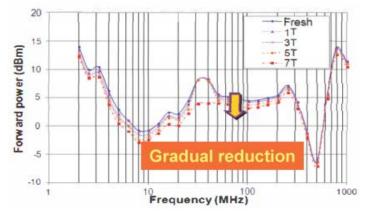

| Figure I-42 Evolution of the forward power before and after aging [68]                          | 44           |

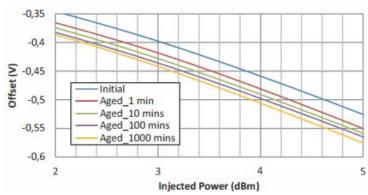

| Figure I-43 Drift in the offset voltage with the injected voltage before and after aging [      | 58]45        |

| Figure I-44 Workflow of electromagnetic robustness model extraction [71]                        | 45           |

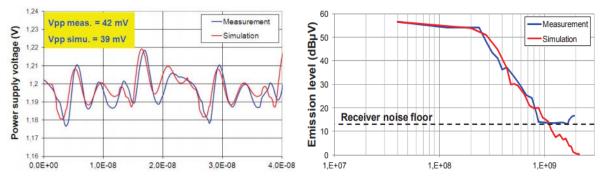

| Figure I-45 ICEM-CE model of a 90 nm IC digital core [63]                                       | 46           |

| Figure I-46 Comparison between the measurement and simulation of power supp                     | oly voltage  |

| fluctuation (left) and CE after 120 min under electrical stress of 3,6 V [63]                   | 47           |

| Figure II-1 Design flow of an electronic circuit taking into account the EMC performance        |              |

| Figure II-2 The different level of EMC modeling: system level (a), PCB level (b),               | integrated   |

| circuit level (c)                                                                               | 56           |

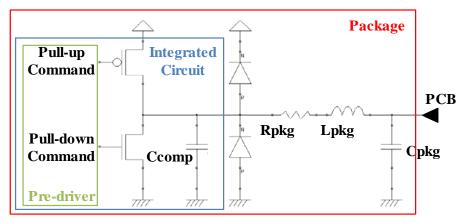

| Figure II-3 IBIS model of an input                                                              | 58           |

| Figure II-4 IBIS model of an output                                                             |              |

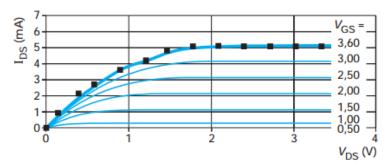

| Figure II-5 I(V) curve for the simulation of an output response [11]                            | 59           |

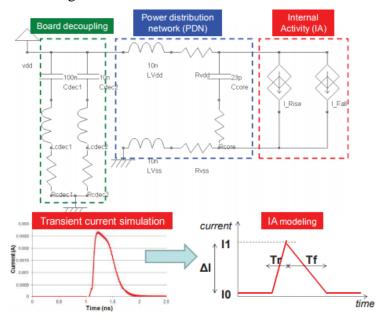

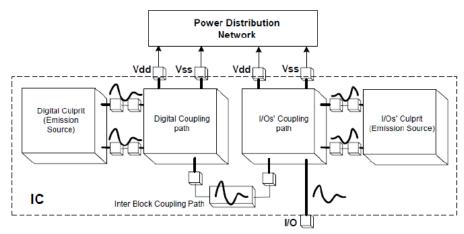

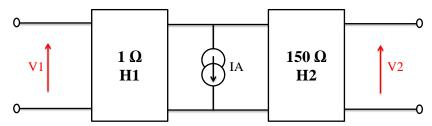

| Figure II-6 Presentation of the noise source and the coupling path of an IC                     |              |

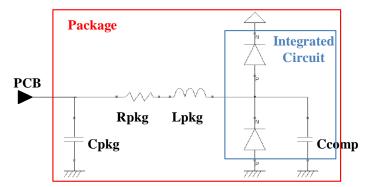

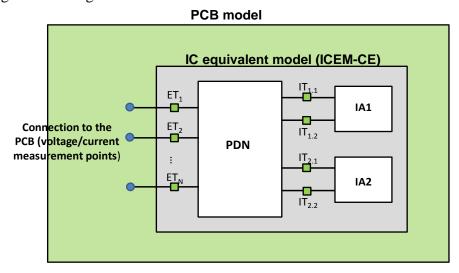

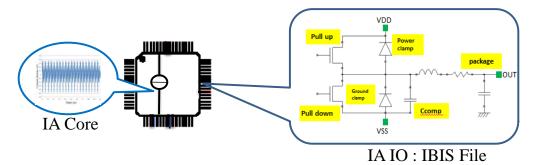

| Figure II-7 Presentation of the ICEM-CE macro-model                                             |              |

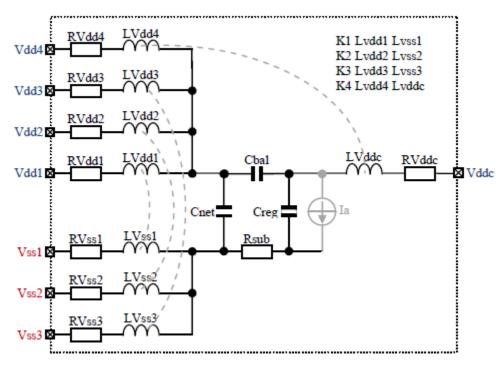

| Figure II-8 PDN model of a microcontroller DSPIC [13]                                           |              |

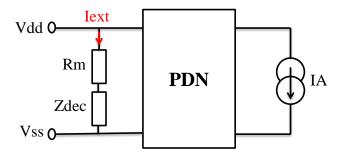

| Figure II-9 IA construction based from the external current measurement                         | 63           |

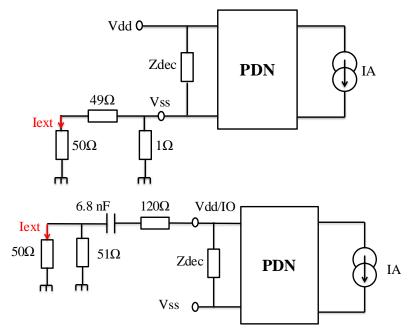

| Figure II-10 IEC 61967-4 measurement methods: 1 $\Omega$ method (top) 150 $\Omega$ method (both |              |

| Figure II-11 IA construction and comparison between the measured and simulate                   | ed external  |

| current [13]                                                                                    | 64           |

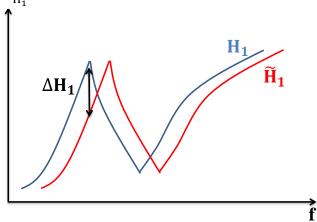

| Figure II-12 Simplified illustration of the link between the transfer functions and the ex          | ternal  |

|-----------------------------------------------------------------------------------------------------|---------|

| voltages measured with the $1/150~\Omega$ methods                                                   | 65      |

| Figure II-13 Illustration of the induced absolute error on the transfer function                    | 66      |

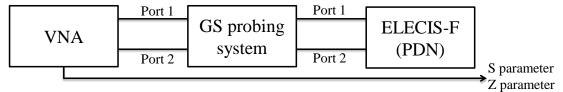

| Figure II-14 Block diagram of ELECIS-F demonstrator                                                 | 69      |

| Figure II-15 The designed demonstrator ELECIS-F                                                     | 69      |

| Figure II-16 test board for PDN extraction: bottom side (left), top side (right)                    | 70      |

| Figure II-17 Description of the workflow for S parameter measurements of the FPGA                   |         |

| Figure II-18 S parameter measurements with a GS probing system: on the pins of the la               | FPGA    |

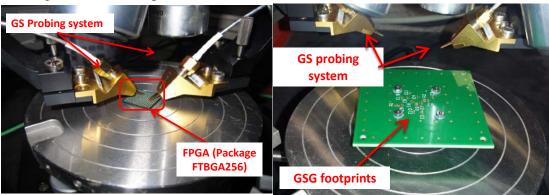

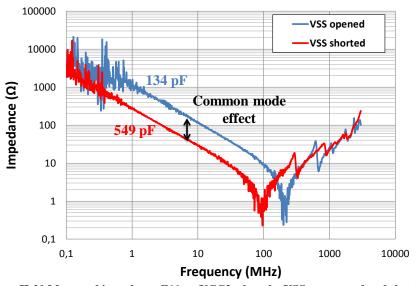

| (left), on test board for PDN extraction (right)                                                    | 71      |

| Figure II-19 Set up for S parameter measurements using a bias tee                                   | 72      |

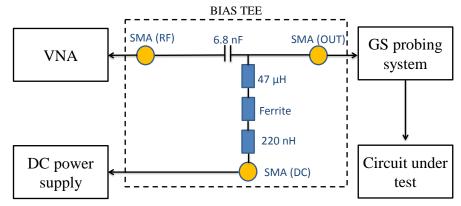

| Figure II-20 Measured impedance Z11 on VCC3 when the VSS are opened and shorted                     | 73      |

| Figure II-21 Measured impedance Z21 on power and unpowered FPGA when the two por                    |         |

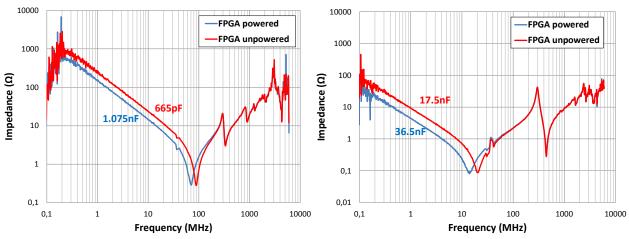

| VCC0 (left), VCCINT (right)                                                                         |         |

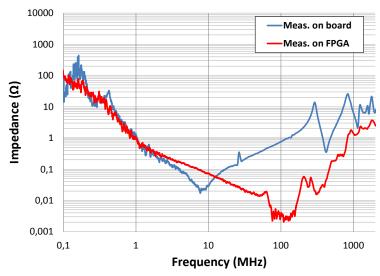

| Figure II-22 Measured impedance Z21 on board and directly on the FPGA package when the              | _       |

| 1 is on VCC1 and the port 2 on VCC3                                                                 |         |

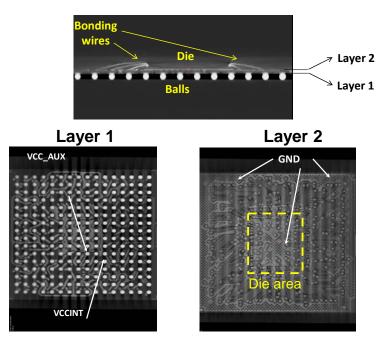

| Figure II-23 X-ray images of the FPGA mounted on FTBGA256                                           |         |

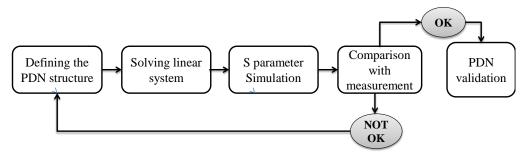

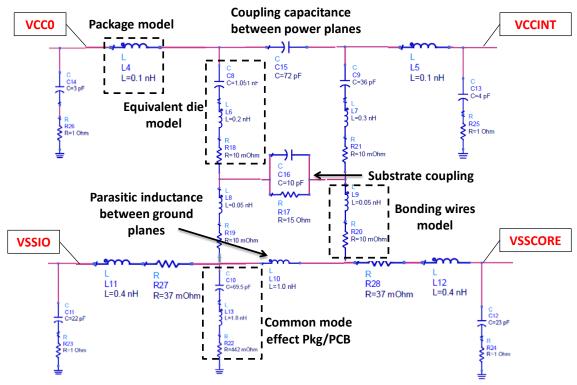

| Figure II-24 Workflow of construction of the PDN model                                              |         |

| Figure II-25 Simplified view of the PDN model between VCCO/VSSIO and VCCINT/VC                      |         |

| Figure II-26 General structure of the PDN of the tested FPGA                                        |         |

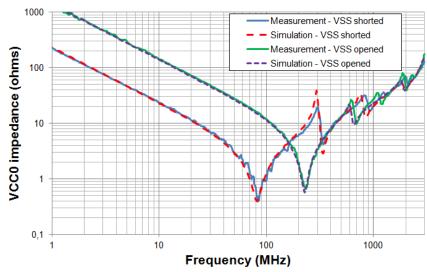

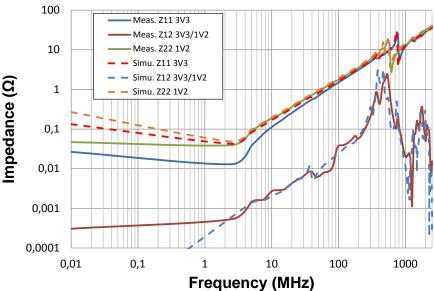

| Figure II-27 Comparison between the measurement and the simulation of the impedance 2               |         |

| VCC0 when the VSS are opened and when the VSS are shorted                                           |         |

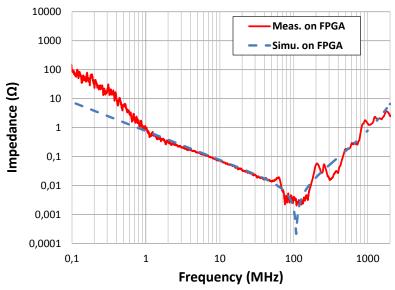

| Figure II-28 Comparison between the measurement and simulation performed on the FPO                 |         |

| the impedance Z21 when the port 1 is VCC1 and the port 2 is VCC3                                    |         |

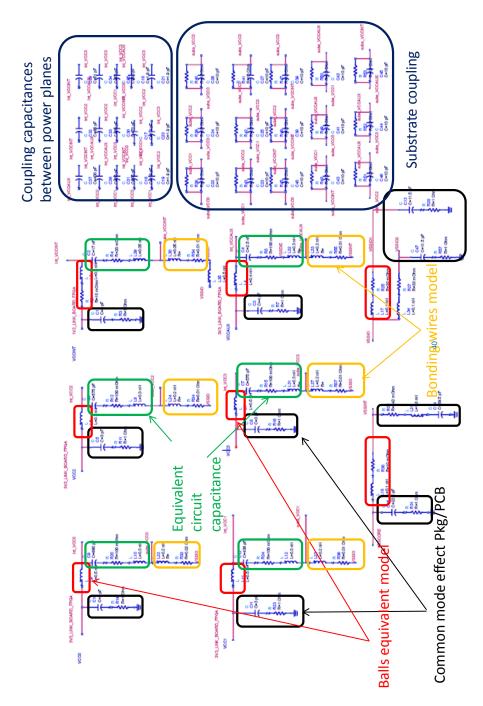

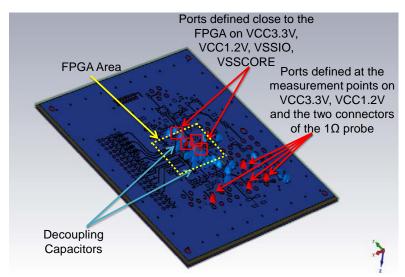

| Figure II-29 General methodology for the PCB modeling                                               |         |

| Figure II-30 ELECIS-F modeling with CST Studio Suite                                                |         |

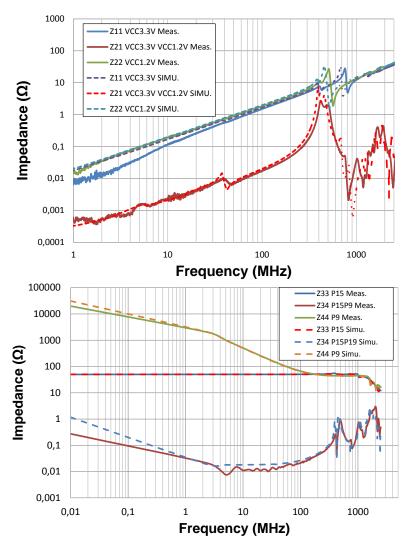

| Figure II-31 Comparison between the measured and simulated impedance between 3.3 V at               |         |

| V (up) and between P15 and P9 (down)                                                                |         |

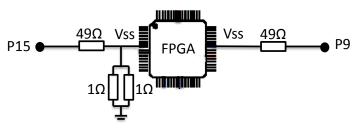

| Figure II-32 Definition of the SMA connectors P15 and P9 on ELECIS-F                                | 84      |

| Figure II-33 SPICE model for S parameter simulation on ELECIS-F and the FPGA equi model             |         |

| Figure II-34 Comparison between the measured and simulated impedance of the board and               |         |

| model between the power planes 3.3 V and 1.2 V                                                      |         |

| Figure II-35 Regions of the internal activity of a FPGA: Core and IOs                               |         |

| Figure II-36 Workflow of construction of the IA Core using the inverse method                       |         |

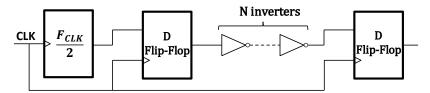

| Figure II-37 Structure of the test configuration: Delay lines                                       |         |

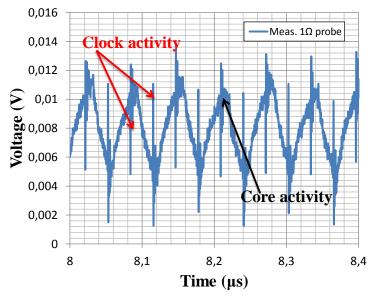

| Figure II-38 Measured external voltage using the 1 $\Omega$ probe for the test configuration: Delay | y lines |

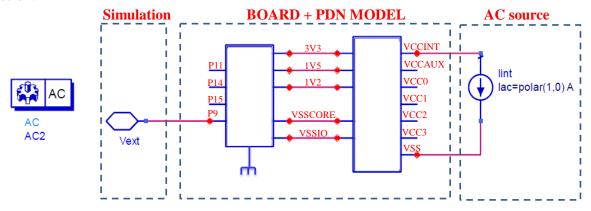

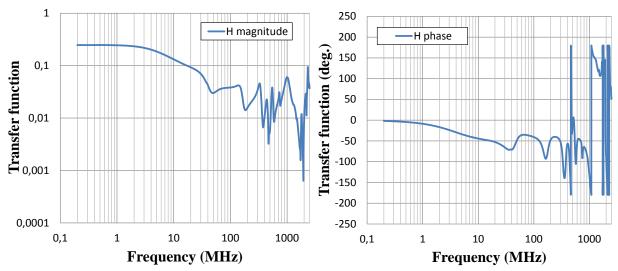

| Figure II-39 Schematic for AC simulation to compute the transfer function                           |         |

| Figure II-40 The obtained magnitude and phase of the transfer function by AC simulation             |         |

| Figure II-41 The extracted IA Core for the configuration delay lines using the inverse method                  |

|----------------------------------------------------------------------------------------------------------------|

| based on 1 $\Omega$ measurement                                                                                |

| Figure II-42 Zoom on the extracted IA Core using the inverse method in the time domain90                       |

| Figure II-43 The extracted IA Core for the delay lines configuration in the frequency domain90                 |

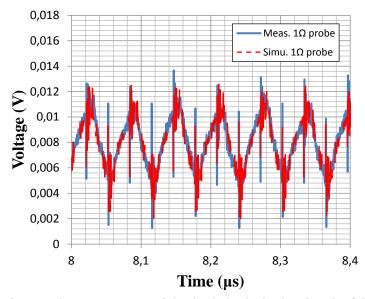

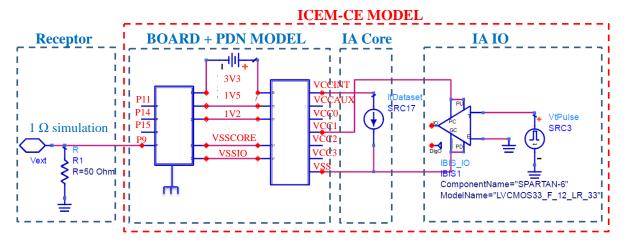

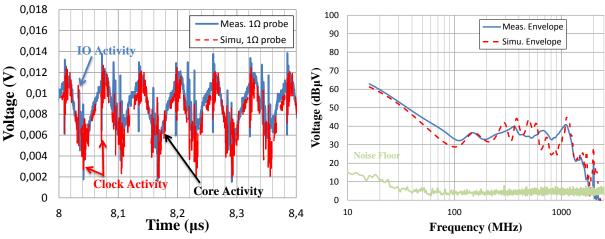

| Figure II-44 Constructed ICEM-CE model for transient simulation using a 1 $\Omega$ probe91                     |

| Figure II-45 Comparison between the measurement and the simulation in the time domain of the                   |

| external voltage using the 1 $\Omega$ probe91                                                                  |

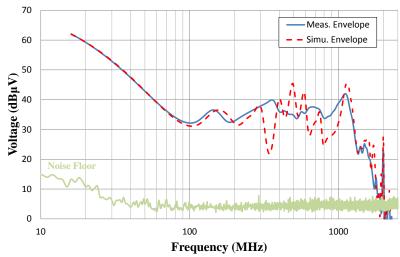

| Figure II-46 Comparison of the measured and simulated envelope in the frequency domain of the                  |

| external voltage using the 1 $\Omega$ probe                                                                    |

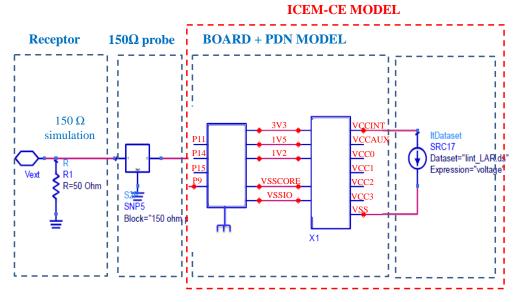

| Figure II-47 Schematic for transient simulation on ICEM-CE model using a 150 $\Omega$ probe92                  |

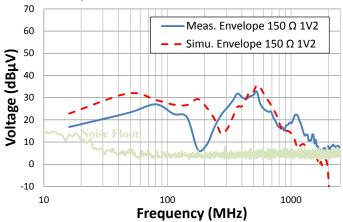

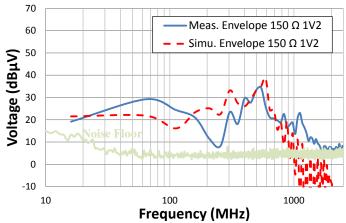

| Figure II-48 Comparison between the measurement and the simulation of the spectral envelope of                 |

| external voltage using the 150 $\Omega$ probe                                                                  |

| Figure II-49 Schematic of ICEM-CE integrating IA Core and IA IO94                                              |

| Figure II-50 Extracted IA IO in the time domain (left) and the frequency domain (right)95                      |

| Figure II-51 Comparison between the simulated and measured CE using the 1 $\Omega$ probe in the                |

| time domain (left) and frequency domain (right)96                                                              |

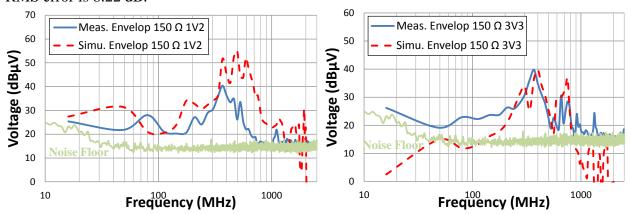

| Figure II-52 Comparison between the measured and simulated CE using the 150 $\Omega$ probe on the              |

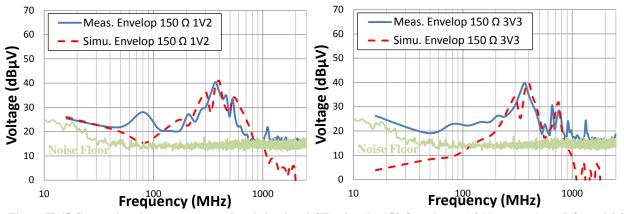

| power planes 1.2 V (left) and 3.3 V (right) in the frequency domain                                            |

| Figure II-53 Presentation of the IA Core and IA IO blocs of the ICEM-CE model98                                |

| Figure II-54 Schematic of ICEM-CE model with the IA IO bloc                                                    |

| Figure II-55 Comparison in the time and frequency domain of the external voltage using a 1 $\Omega$            |

| probe when an IO is activated                                                                                  |

| Figure II-56 Comparison between the measured and simulated CE using the 150 $\Omega$ probe on the              |

| power planes 1.2 V (left) and 3.3 V (right)99                                                                  |

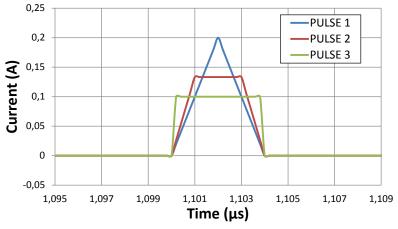

| Figure II-57 The generated pulses for IA construction                                                          |

| Figure II-58 The CE simulation for each pulse in the time domain (left) and the frequency                      |

| domain (right)                                                                                                 |

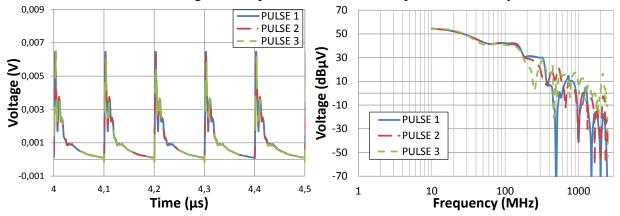

| Figure II-59 Workflow of construction of the IA Core with a deterministic approach104                          |

| Figure II-60 Workflow of construction of the IA Core with the statistical approach106                          |

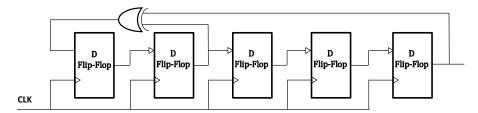

| Figure II-61 Structure of the 5-bits PRNG configuration                                                        |

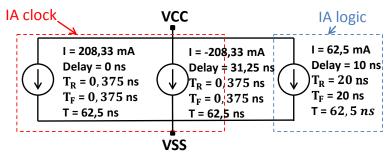

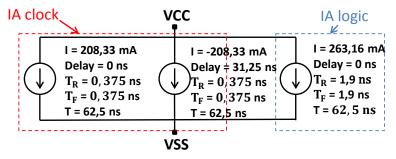

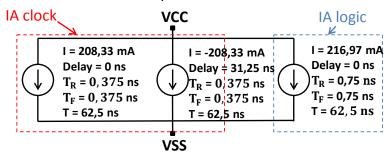

| Figure II-62 Construction of IA Core bloc using current sources for the delay lines case study 107             |

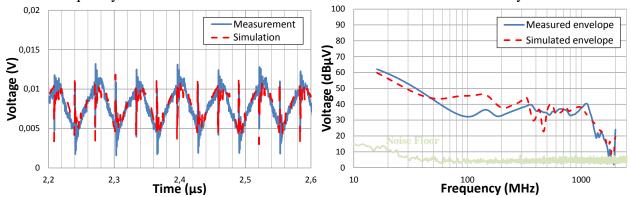

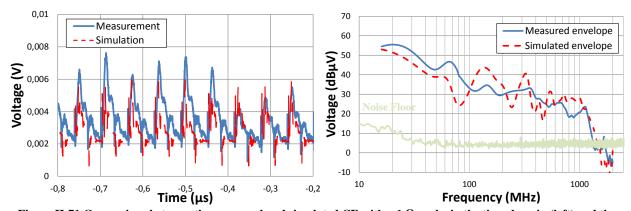

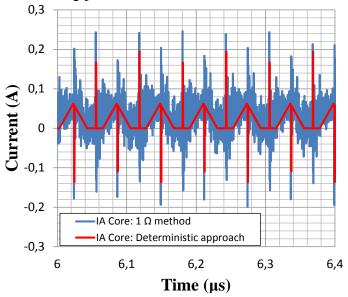

| Figure II-63 Comparison between the measured and simulated CE with the 1 $\Omega$ probe in the time            |

| domain (left) and the frequency domain (right) for the delay line108                                           |

| Figure II-64 Comparison between the measured and simulation CE with a 150 $\Omega$ probe on 1.2 $\mbox{\em V}$ |

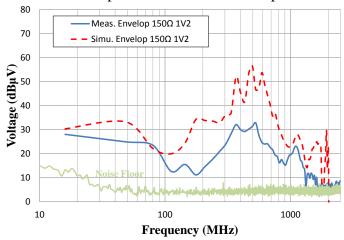

| in the frequency domain for the delay line configuration                                                       |

| Figure II-65 Comparison between measured and simulated CE using the 150 $\Omega$ probe on 1.2 V                |

| power plane (left) and 3.3 V power plane (right) for the delay line configuration109                           |

| Figure II-66 IA Core construction for the 7-bits counter configuration                                         |

| Figure II-67 Comparison between the measured and simulated CE with the 1 $\Omega$ probe in the time            |

| domain (left) and the frequency domain (right) for the 7-bits counter configuration using the                  |

| deterministic approach                                                                                         |

| Figure II-68 Comparison between the measured and simulated CE with the 1 $\Omega$ probe in the time           |

|---------------------------------------------------------------------------------------------------------------|

| domain (left) and the frequency domain (right) for the 7-bits counter configuration using the                 |

| statistical approach111                                                                                       |

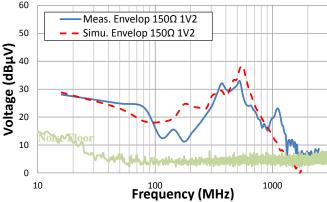

| Figure II-69 Comparison between measured and simulated CE using the 150 $\Omega$ probe on 1.2 V               |

| power plane for the 7-bits counter configuration                                                              |

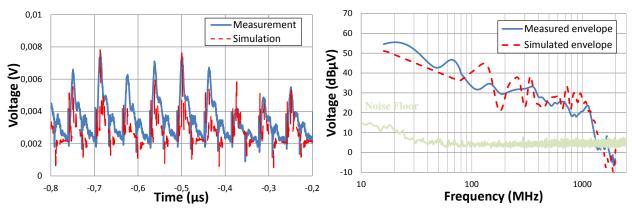

| Figure II-70 IA Core construction for the PRNG test configuration                                             |

| Figure II-71 Comparison between the measured and simulated CE with a 1 $\Omega$ probe in the time             |

| domain (left) and the frequency domain (right) for the PRNG using the deterministic approach                  |

| Figure II-72 Comparison between the measured and simulated CE with a 1 $\Omega$ probe in the time             |

| domain (left) and the frequency domain (right) for the PRNG using the statistical approach113                 |

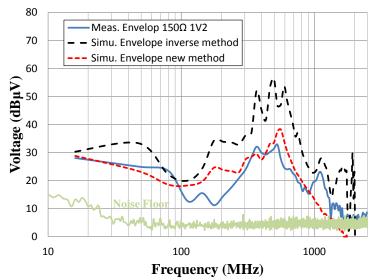

| Figure II-73 Comparison between measured and simulated CE using the 150 $\Omega$ probe on 1.2 V               |

| power plane for the 5-bits PRNG configuration                                                                 |

| Figure II-74 Comparison between the IA core generated with the inverse method and with the                    |

| deterministic approach for the delay line configuration                                                       |

| Figure II-75 Comparison between the measured and simulated CE with an extracted IA Core                       |

| following the inverse method and the new approach for the delay line configuration                            |

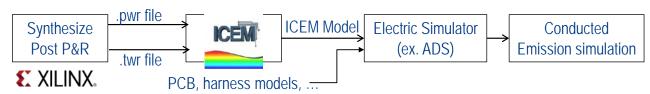

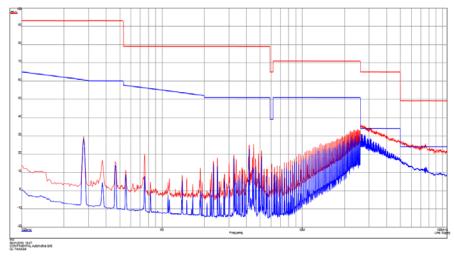

| Figure II-76 Workflow of CE simulation using ICEM GENRATOR                                                    |

| Figure II-77 ICEM GENERATOR tool window                                                                       |

| Figure II-78 On-chip power consumption and resources utilization estimated by XPA117                          |

| Figure II-79 Industrial application design block diagram                                                      |

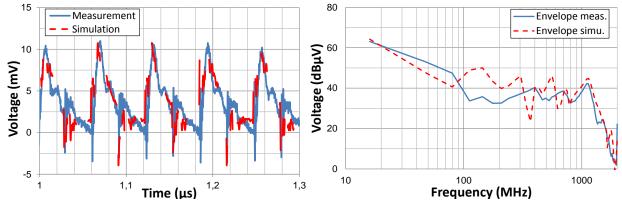

| Figure II-80 Comparison between the measured and simulation CE using a 1 $\Omega$ probe in the time           |

| domain (left) and frequency domain (right) for the FFT test configuration118                                  |

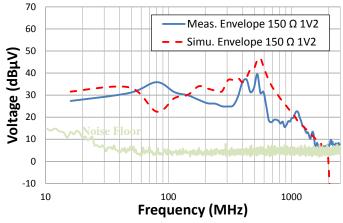

| Figure II-81 Comparison between the measurement and simulation of CE on 1.2 V power plane                     |

| using the 150 $\Omega$ probe for the industrial application                                                   |

| Figure III-1 Bathtub curve principle                                                                          |

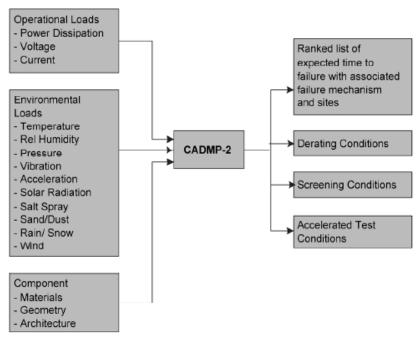

| Figure III-2 Inputs and outputs of CADMP-2 tool [1]129                                                        |

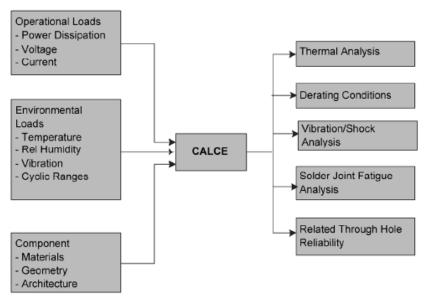

| Figure III-3 Inputs and outputs of CALCE tool [1]                                                             |

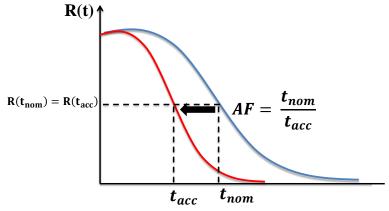

| Figure III-4 Principle of an accelerated test                                                                 |

| Figure III-5 Principle of standard Accelerated Life Model                                                     |

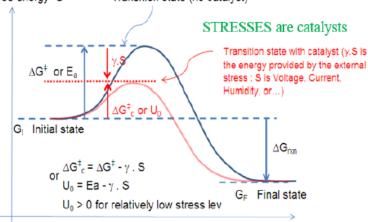

| Figure III-6 External stress effect on the activation energy [20]                                             |

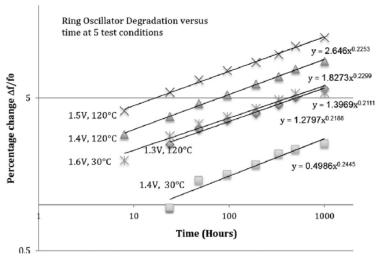

| Figure III-7 Accelerating test results at different stress conditions [28]141                                 |

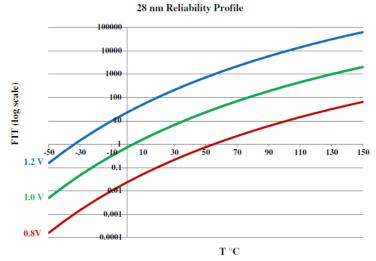

| Figure III-8 Reliability curve for different voltages for 28 nm technology [11]142                            |

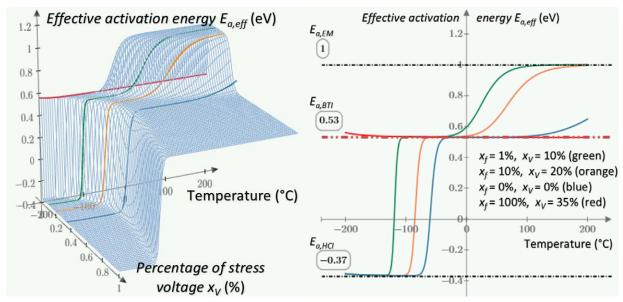

| Figure III-9 Effective activation energy of 28 nm technology using M-STORM model (left) 3D                    |

| plot for $E_{a,eff}$ ( $x_f = 10\%$ , $x_V$ , T), or (right) 2D plot for same various percentage of stress    |

| conditions ( $x_f = F/F_{max}$ and $x_V = V/V_{br}$ ) and temperature ( $F_{max} = 12$ GHz, $V_{br} = 3.3V$ ) |

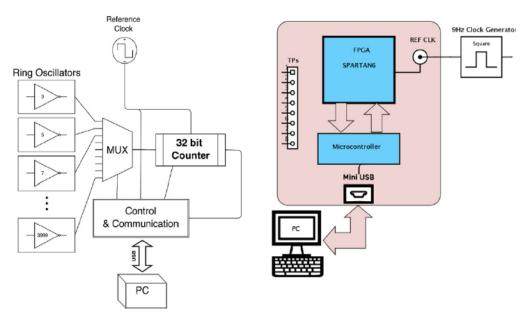

| Figure III-10 Test set-up and the control and communication interface for accelerated tests [11]              |

| 145                                                                                                           |

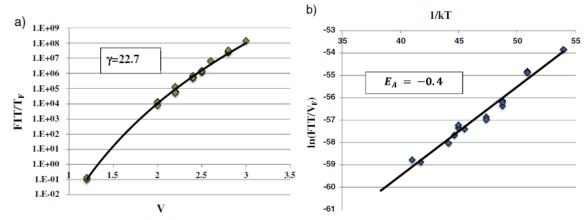

| Figure III-11 Plotted results of $\gamma$ (a) and $E_a$ (b) for HCI mechanism [11]145                         |

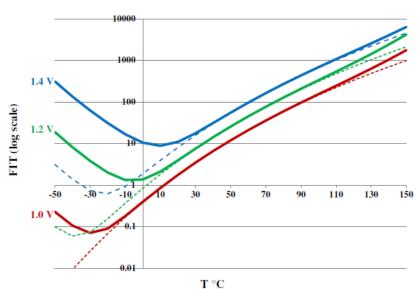

| Figure III-12 Reliability curve for different voltages and frequencies from 10 MHz (dashed lines)             |

| to 2 GHz (solid lines) [11]                                                                                   |

| Figure IV-1 Workflow of EMC level prediction using the MSTORM reliability model              | 152    |

|----------------------------------------------------------------------------------------------|--------|

| Figure IV-2 Step stress test purpose                                                         | 153    |

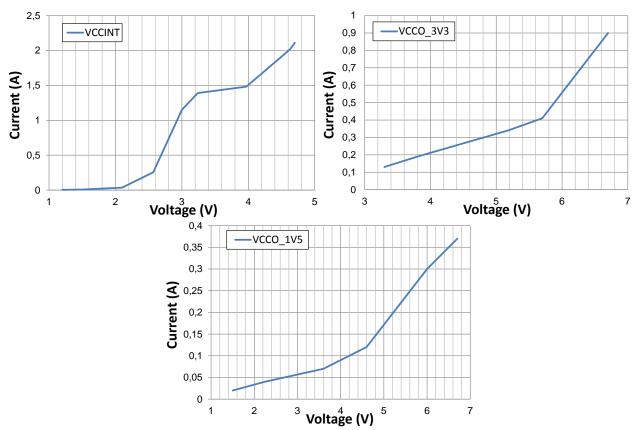

| Figure IV-3 Evolution of the current consumption with the increase of the voltage on the dif | ferent |

| power domains of the FPGA                                                                    | 155    |

| Figure IV-4 Step Stress workflow description                                                 | 156    |

| Figure IV-5 Presentation of the workflow of the Life test                                    | 157    |

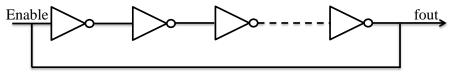

| Figure IV-6 Design principle of the ring oscillator configuration                            | 159    |

| Figure IV-7 Designed PCB for burn-in tests for several FPGAs                                 | 160    |

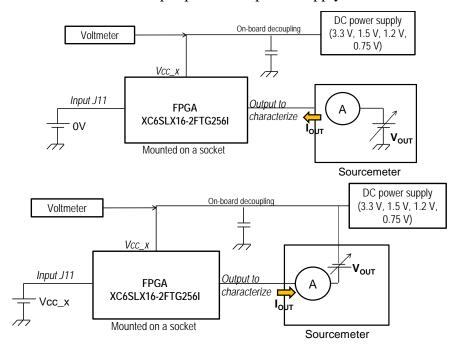

| Figure IV-8 Experimental set-up for static measurements                                      | 161    |

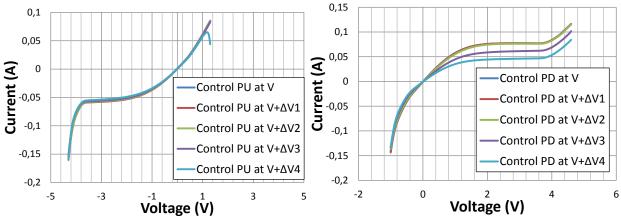

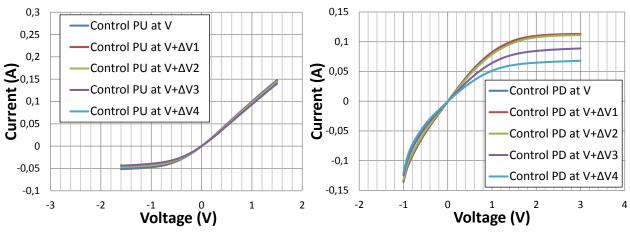

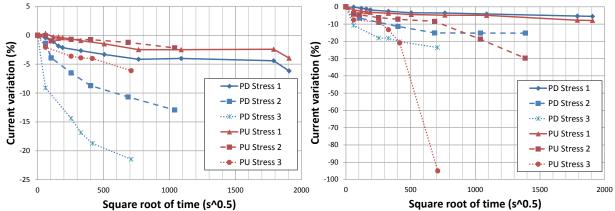

| Figure IV-9 Pull-up and pull-down Static measurement on the LVCMOS33 pin of C1SE             | 162    |

| Figure IV-10 Pull-up and pull-down Static measurement on the SSTL15 pin of C1SE              | 162    |

| Figure IV-11 Current variation for the pull-down devices of the tested FPGAs for LVCM        |        |

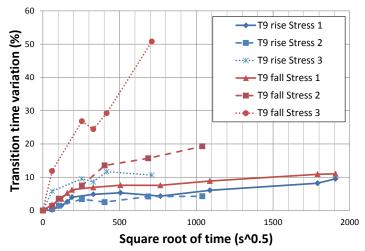

| (left) and SSTL15 (right) IOs                                                                |        |

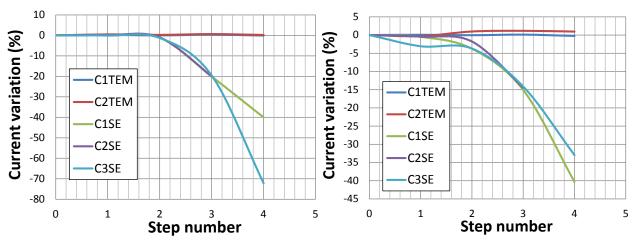

| Figure IV-12 Experimental set-up for signal integrity measurements                           | 163    |

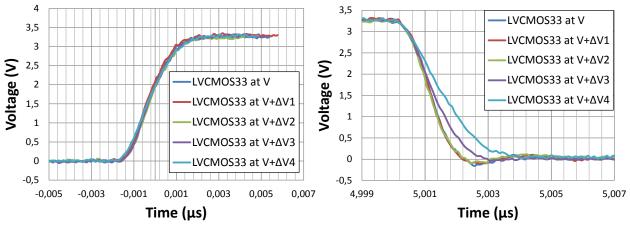

| Figure IV-13 Rising and falling edges evolution at the different steps for C1SE LVCM         |        |

| output                                                                                       | 164    |

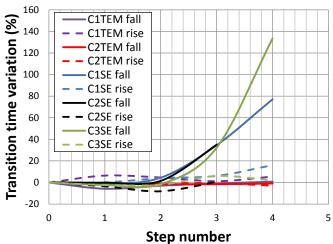

| Figure IV-14 Transition time variation during the step stress for the tested components      |        |

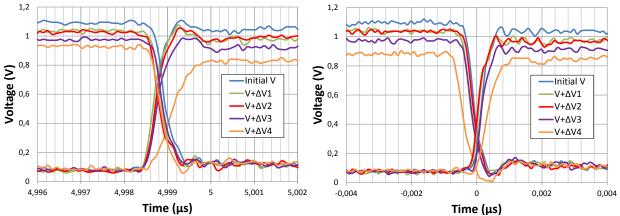

| Figure IV-15 Time profile of the differential outputs E1/E2 on the rising edge (left) and f  |        |

| edge (right) of E2                                                                           |        |

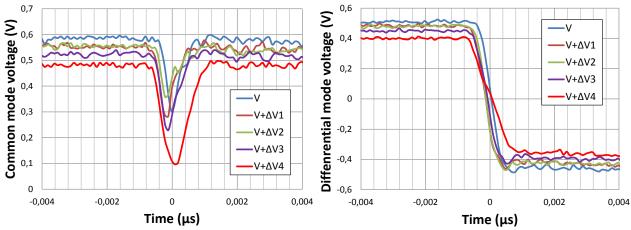

| Figure IV-16 Common mode (left) and differential mode (right) voltages on the falling ed     |        |

| E2 for the component C1SE                                                                    | 166    |

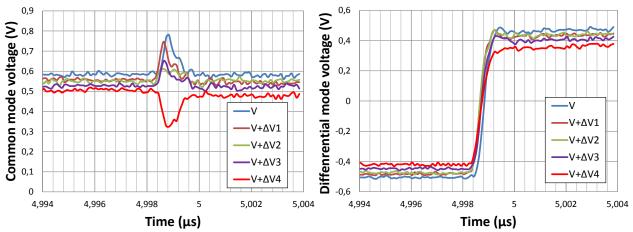

| Figure IV-17 Common mode (left) and differential mode (right) voltages on the rising edge    |        |

| for the component C1SE                                                                       |        |

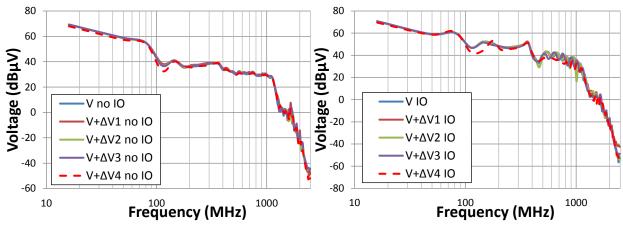

| Figure IV-18 CE measurements using the 1 $\Omega$ probe on C1SE for the delay line configu   |        |

| with no activated IO (left), with one activated IO (right)                                   |        |

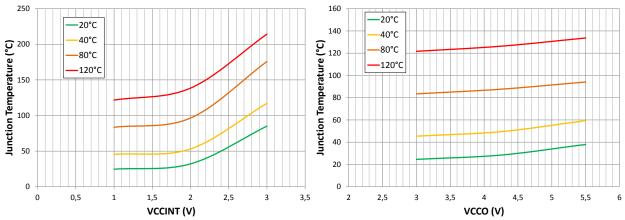

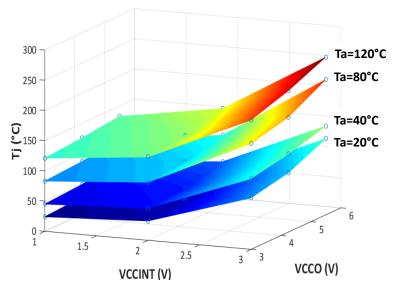

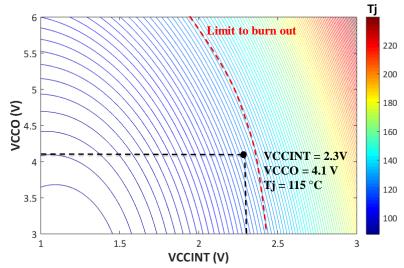

| Figure IV-19 Evolution of the junction temperature according the power supply voltage VC     |        |

| (left) and VCCO (right) for different ambient temperatures                                   |        |

| Figure IV-20 Evolution of the junction temperature according VCCINT, VCCO                    |        |

| Figure IV-21 Junction temperature evolution at an ambient temperature 70 °C                  |        |

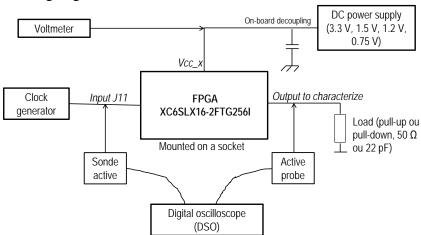

| Figure IV-22 Current variation on PD and PU devices of LVCMOS33 (left) and SSTL15 (          |        |

| output buffers for the different stresses                                                    |        |

| Figure IV-23 Transition time variation of LVCMOS33 output buffer for the different stresse   | s.172  |

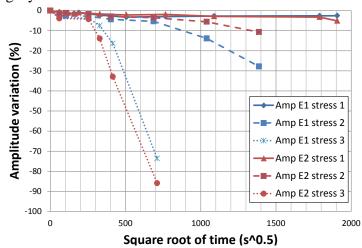

| Figure IV-24 Amplitude variation on differential pins (DIFF_SSTL15) for the different st     |        |

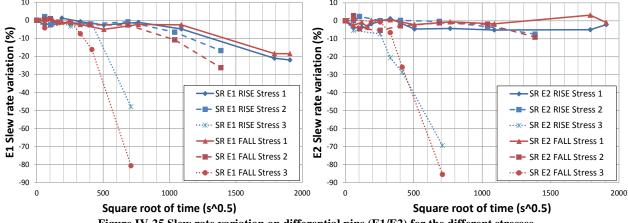

|                                                                                              |        |

| Figure IV-25 Slew rate variation on differential pins (E1/E2) for the different stresses     |        |

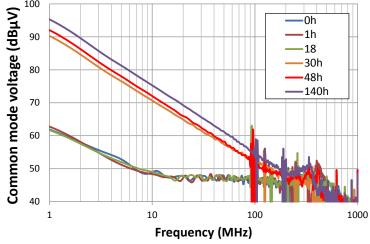

| Figure IV-26 Common mode voltage in frequency domain of one stressed FPGA at the             |        |

| conditions N° 3                                                                              |        |

| Figure IV-27 Average common mode voltage level evolution between [1,100] MHz for             |        |

| different stresses                                                                           |        |

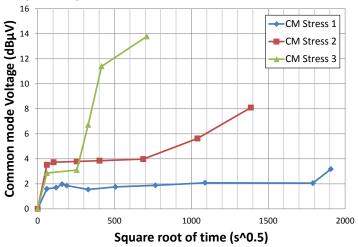

| Figure IV-28 Average RO frequency variation for the different stresses                       | 175    |

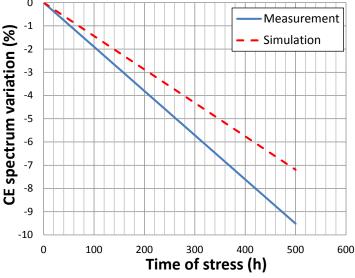

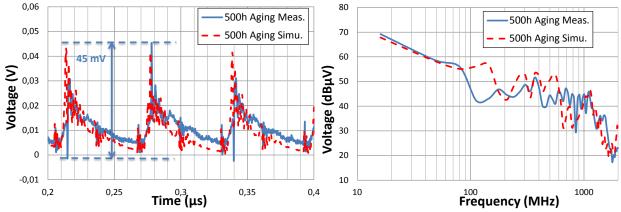

| Figure IV-29 Initial and after 500 h aging CE measurement in the time and frequency de          | omain   |

|-------------------------------------------------------------------------------------------------|---------|

| using the 1 $\Omega$ probe at the stress conditions number 2                                    | 175     |

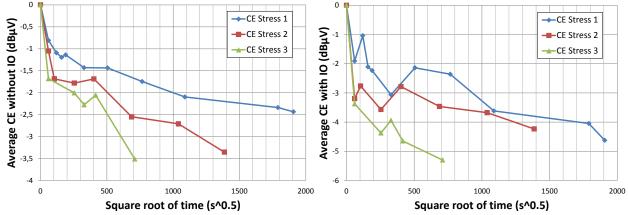

| Figure IV-30 Evolution of the average CE variation without activated IOs (left) and             | with    |

| activated IOs (right) at the different stress conditions                                        | 176     |

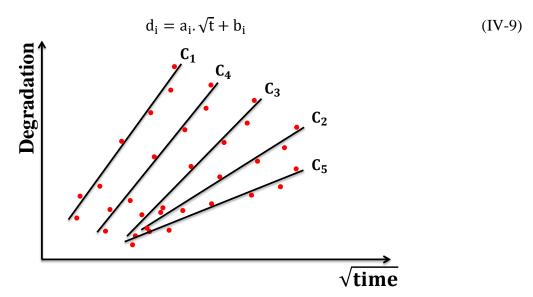

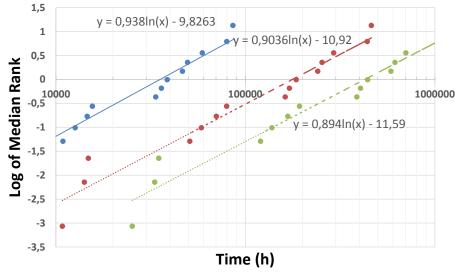

| Figure IV-31 Illustration of the drift plot according to time for different stressed components |         |

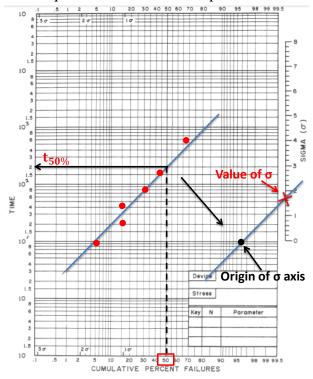

| Figure IV-32 Log-normal plot to compute $t_{50\%}$ and $\sigma$                                 |         |

| Figure IV-33 Student's t distribution adapted to confidence level and the sample size [80]      | 179     |

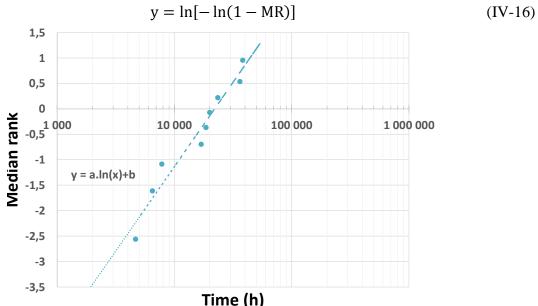

| Figure IV-34 Degradation data plot using Weibull's distribution                                 | 180     |

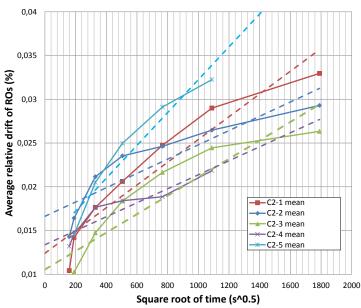

| Figure IV-35 Average relative drift calculated on the three ROs at the first stress conditio    | ns for  |

| the five tested components                                                                      | 181     |

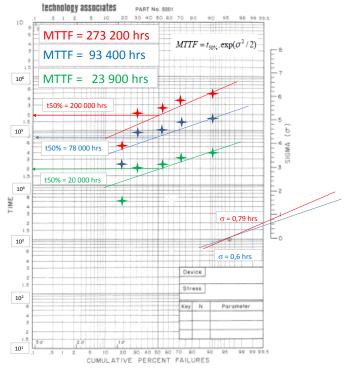

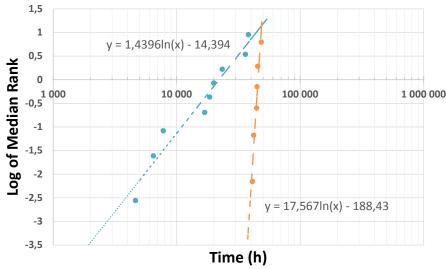

| Figure IV-36 MTTF calculation using the log-normal plot for the stress conditions 1             |         |

| Figure IV-37 Log-normal plot of degradation data for the stress conditions 2 and 3              | 183     |

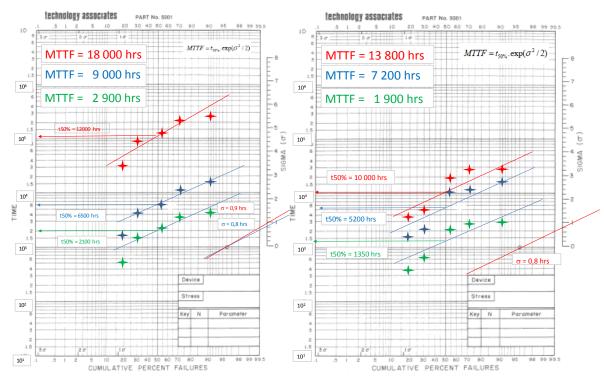

| Figure IV-38 Weibull's distribution for the stress conditions 1 at 10 %, 20 % and 30 % dr       | ifts of |

| the ROs output frequencies                                                                      | 185     |

| Figure IV-39 Weibull plot for the stress conditions 2 for 30 % drift                            | 185     |

| Figure IV-40 Calculated FITs with Weibull's distribution (red and blue points) for the three    | stress  |

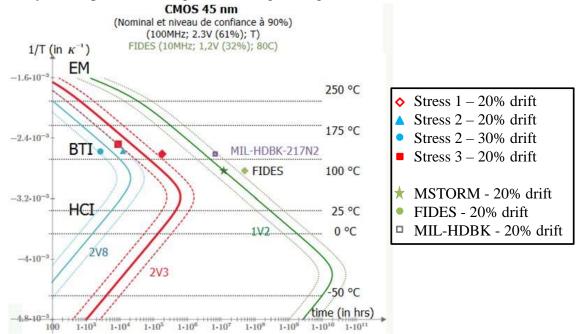

| conditions placed on the MSTORM model for 2.8 V and 2.3 V on VCCINT                             | 187     |

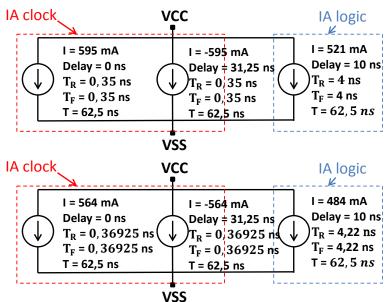

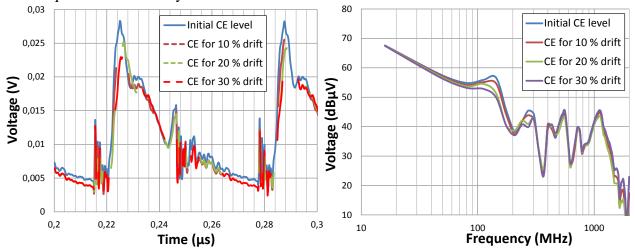

| Figure IV-41 Internal activity of the Core block construction before (up) and after (down)      | aging   |

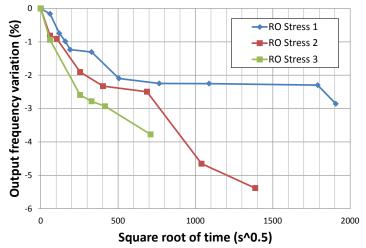

|                                                                                                 | 190     |

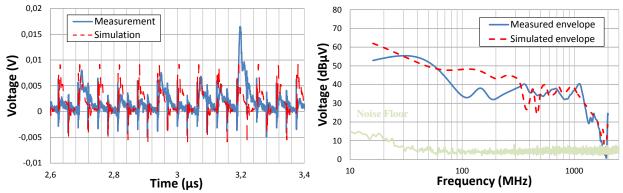

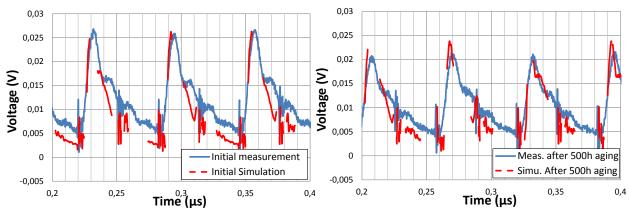

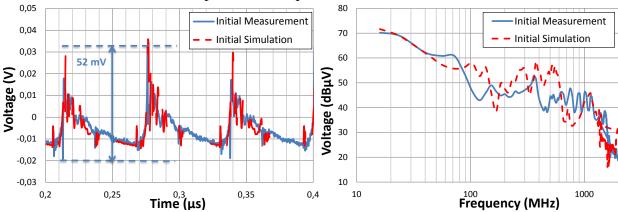

| Figure IV-42 Comparison between the measured and simulated CE using the $\Omega$ probe          | at the  |

| initial measurements and after 500 h aging under the stress conditions 2 in the time domain.    | 191     |

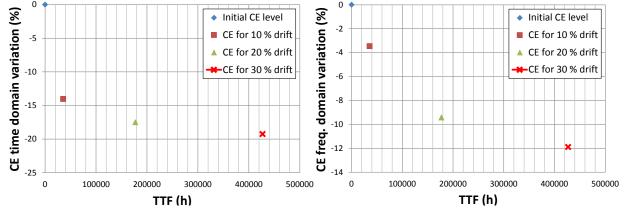

| Figure IV-43 Comparison between the variation of the measured and simulated CE spe              | ectrum  |

| from the initial state and after 500 h aging under the stress conditions 2                      | 191     |

| Figure IV-44 Prediction of CE level in the time and frequency domain for different propagation  | gation  |

| delay drift percentage                                                                          | 192     |

| Figure IV-45 TTF prediction for CE variation in the time and frequency domain for diff          | ferent  |

| degradation criteria                                                                            | 192     |

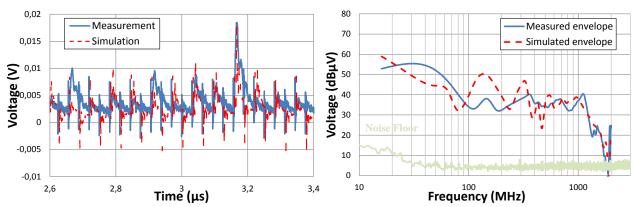

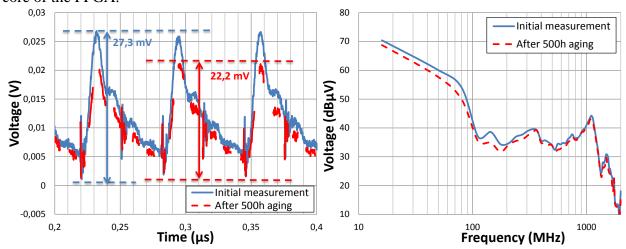

| Figure IV-46 Comparison between measured and simulated CE using the 1 $\Omega$ probe before     | aging   |

| when the IOs are activated                                                                      | 193     |

| Figure IV-47 Comparison between the measured and simulated CE using the 1 $\Omega$ probe after  | er 500  |

| h aging under test conditions 2                                                                 | 194     |

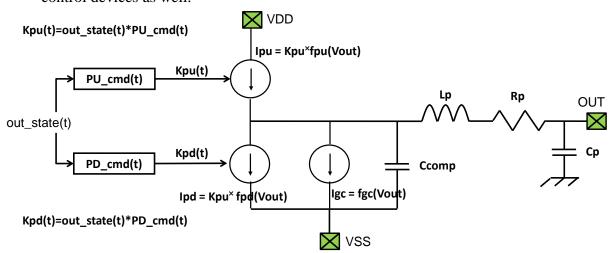

| Figure IV-48 3-state output buffer equivalent model                                             | 195     |

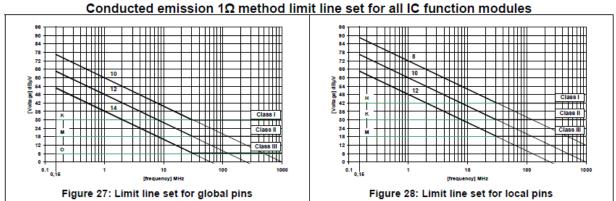

| Figure 49 Conducted Emission (voltage method) measurements in Narrow Band (blue                 | e) and  |

| Broad Band (red) compared with limits given by Renault 3600808 specification                    | 208     |

| Figure 50 Example of requirements for CE level using the 1 $\Omega$ method                      | 208     |

| Figure 51 Requirements classes for immunity tests                                               |         |

| Figure 52 Power and Ground clamp model in an IBIS file                                          | 211     |

| Figure 53 Pull-up and Pull-down I(V) characteristics of an output                               | 212     |

| Figure 54 Timing profile characteristics of an output                                           |         |

## LIST OF TABLES

| Table I-1 Excerpt of 2003 ITRS technology scaling from 90nm to 22nm [27]                  | 12          |

|-------------------------------------------------------------------------------------------|-------------|

| Table I-2 Examples of EMC standards for automobile, aeronautic, and military applicati    | ons13       |

| Table I-3 Standards for conducted and radiated emissions measurements at IC level         | 14          |

| Table I-4 IEC standards for EMI modelling at IC level                                     | 15          |

| Table I-5 Standards for conducted and radiated susceptibility measurements at IC          | 18          |

| Table I-6 Standard for IC immunity modelling                                              | 19          |

| Table I-7 Operating temperature range of COTS components in industrial application [3     | 6]20        |

| Table I-8 Scaling impact on the degradation mechanisms and stresses accelerating the m    | echanism    |

|                                                                                           | 36          |

| Table II-1 Selected pins for S parameter measurements                                     |             |

| Table II-2 Parasitic elements of the FPGA                                                 | 75          |

| Table II-3 Ports definition for ELECIS-F modeling                                         | 82          |

| Table II-4 Comparison of the average current and power between the IA extracted           | with the    |

| inverse method and the estimation of Xilinx tool                                          | 94          |

| Table II-5 Calculated RMS errors between the different pulses                             | 102         |

| Table II-6 Dynamic power consumption and the data path delay given by Xilinx report       | rts for the |

| case studies                                                                              | 107         |

| Table III-1 Criticality level defined by DAL for aeronautic application in the standard D | O254 [2]    |

|                                                                                           | 125         |

| Table III-2 Failure rate values for an electronic component [10]                          | 127         |

| Table III-3 Procedural method and application for reliability modeling                    | 128         |

| Table III-4 MTOL matrix to solve models with measured TTF [28]                            | 140         |

| Table III-5 Matrix solution [28]                                                          | 140         |

| Table III-6 Equations for the acceleration factors matrix [28]                            | 140         |

| Table III-7 Proportionality factor of degradation mechanisms                              | 141         |

| Table III-8 Matrix solution using experimental results and extrapolation to untested of   | conditions  |

| (last 4 rows)                                                                             | 142         |

| Table III-9 Results of $E_a$ and $\gamma$ for the 45 nm FPGA [11]                         | 146         |

| Table IV-1 Absolute maximum ratings for the Spartan 6 DC characteristics [78]             | 154         |

| Table IV-2 DC characteristics for the different power domains at nominal, max rating      | and burn-   |

| out conditions                                                                            | 154         |

| Table IV-3 Voltage operating conditions defined for the step stress                       | 156         |

| Table IV-4 Life test time durations according to the TTF [26]                             | 158         |

| Table IV-5 Number of tested samples at the different stages of the step stress and the ac | celerated   |

| life test                                                                                 | 158         |

| Table IV-6 Summary of the tested configurations for the accelerated aging tests           | 159         |

| Table IV-7 Selected operating conditions for the preliminary test to M-HTOL               | 168         |

| Table IV-8 Selected stress conditions for M-HTOL test                                     | 170         |

| Table IV-9 Cumulative failure percentage for a given degradation criterion                | 178         |

| Table IV-10 Extrapolated drifts using the linear equations and the corresponding cumula      | ative |

|----------------------------------------------------------------------------------------------|-------|

| relative failures                                                                            | .182  |

| Table IV-11 Calculated MTTF and 90 % confidence level for the different stress conditions    | .183  |

| Table IV-12 Calculated drifts and median ranks for the stress conditions 1                   | .184  |

| Table IV-13 Calculated MTTF for the different stress conditions using Weibull's distribution | .186  |

| Table IV-14 Comparison of the reliability parameters between MSTORM model and the            | log-  |

| normal and Weibull's distributions                                                           | .186  |

| Table IV-15 Predicted reliability using MSTORM model for MSTORM data and FIDES               | and   |

| MIL-HDBK data                                                                                | .188  |

| Table IV-16 Dynamic power consumption and data path delay before and after aging for         | r the |

| delay line configuration                                                                     | .190  |

| Table 17 EMC standard of the transportation industry                                         | .207  |

| Table 18 List of automotive OEM specification                                                | .207  |

| Table 19 Gravity level of an IC of the IEC 62215-3 standard                                  | 209   |

## List of acronyms

**EMC** Electromagnetic Compatibility

DSM Deep Sub-Micron

Complementary Metal-Oxide-Semiconductor **CMOS**

**TSV** Through-Silicon Vias **Integrated Circuit** IC

**CISPR** Comité International Spécial des Perturbations Radioélectriques

**IEC** International Electrotechnical Commission

CE Conducted Emission  $\mathbf{RE}$ Radiated Emission CI **Conducted Immunity** RI Radiated Immunity **PCB** Printed Circuit Board

**EOT Equivalent Oxide Thickness**

**LSTP** Low Standby Technology for Portable applications

**EMI** Electromagnetic Interference

FIT Failure In Time

**MTTF** Mean Time To Failure

Advisory Group for Electronic Reliability of electronic Equipment **AGREE**

COTS Commercial Off-The-Shelf Field Programmable Gate Array **FPGA**

Constant Failure Rate **CFR**

Time Dependent Dielectric Breakdown **TDDB**

Electromigration  $\mathbf{EM}$

**NBTI** Negative Bias Temperature Instabilities

**HCI** Hot Carrier Injection **CHC** Channel Hot Carrier

**DAHC** Drain Avalanche Hot Carrier

**CHE** Channel Hot Electron LEM Lucky Electron Model

**SBD** Soft Breakdown **HBD** Hard Breakdown

**GIDL** Gate Induced Drain Leakage **SRAM** Static Random-Access Memory **EMR** Electromagnetic Robustness

**OEM** Original Equipment Manufacturer HTOL High Temperature Operating Life LTOL Low Temperature Operating Life **PTC** Power Temperature Cycling **EME Electromagnetic Emission**

EMS Electromagnetic Susceptibility SMPS Switch-Mode Power Supplies

**DPI** Direct Power Injection**PLL** Phase-Locked-Loop

ICEM Integrated Circuit Emission Model ICIM Integrated Circuit Immunity Model

**IBIS** Input/Output Buffer Information Specification

**PDN** Power Distribution Network

IA Internal ActivityIBC Inter-Block CouplingPI Power Integrity

FEM Finite Element Method

MoM Method of Moment

**FDTD** Finite Difference Time Domain

**PWL** Piece Wise Linear

VLSI Very Large Scale Integration

CLB Configurable Logic Blocs

**ELECIS** Electronic board for Long-term Electromagnetic Compatibility Issues Simulation

**SI** Signal Integrity

**VNA** Vector Network Analyzer

PEEC Partial Element Equivalent CircuitFE FD Finite Element Frequency Domain

RMS Root Mean Square XPA Xilinx Power Analyzer

**EIA** Electronic Industries Alliance

**JEDEC** Joint Electron Device Engineering Council

**PoF** Physics-of-Failure

HALT Highly Accelerated Life TestHASS Highly Accelerated Stress ScreenALM Accelerated Lifetime Model

AF Acceleration Factor

TST Transition State Theory

IPL Inverse Power Law

**BAZ** Boltzmann Arrhenius Zhurkov

MTOL Multiple Temperature Operational Life modelM-HTOL Multiple High Temperature Operational Life test

**MSTORM** Multi-phySics mulTi-stressOrs predictive Reliability Model

**SSALT** Step-Stress Accelerated Life Test

### General introduction

### Thesis context

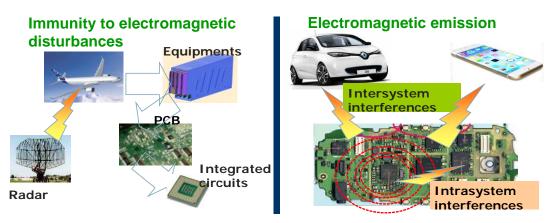

For many years, Electromagnetic Compatibility (EMC) has been a major constraint on electronic systems to ensure limited electromagnetic emission level and sufficient immunity to electromagnetic interference. This requirement is essential to guarantee safety levels in critical and long-term industrial applications. EMC does not only concern electronic systems and equipment, but also integrated circuits (ICs). Indeed, they are at the heart of EMC problems, since they are the source of electromagnetic emissions produced by an electronic system, but also the hardly disturbed element when this electronic system is subjected to electromagnetic interference. Thus, EMC has become a major challenge for integrated circuits [1].

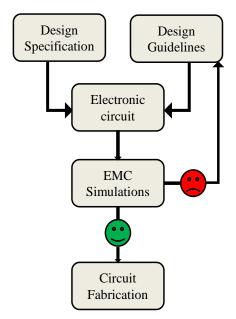

On the other hand, the technological evolution and the improved flexibility of integrated circuits have widely increased their integration in the aeronautical, space and automotive applications. However, this technological evolution is not without consequences on the emission and immunity levels of integrated circuits, mainly related to the increase in the number of transistors and the ever growing operating functions as well as the switching frequencies. Hence, in order to predict the EMC level of ICs using simulation tools, existing IEC standards (e.g. IEC 62433 [2]) have been proposed for the anticipation of EMC issues in order to propose and test solutions. These models allow avoiding the requalification phases in case of obsolescence and second sourcing and lead to saving time and money. In addition, besides the prediction of emission and immunity level at a PCB level, these models can help to assess and improve the effect of decoupling and filtering network, the PCB design and the IC configuration.

- o ICEM-CE: Integrated Circuit Emission Model for Conducted Emission

- o ICEM-RE: Integrated Circuit Emission Model for Conducted Emission

- o ICIM-CI: Integrated Circuit Emission Model for Conducted Emission

However, the presented EMC of IC models are not very much spread due to IC manufacturing confidentiality issues, and the low profit in developing such models comparing to their cost. Furthermore, the existing method for the construction of EMC of ICs models presents several limitations, such as their dependence on measurements and the need of multiple optimization phases. Thus, the present work research deals with a key question for EMC modeling: How to construct an EMC of a complex IC model using a new predictive methodology in a reduced time and set of data?

Besides the EMC aspect, the reliability of IC is also a binding subject. During their operating lifetime, integrated circuits are affected by different intrinsic degradation mechanisms, which are accelerated due the harsh environmental operating conditions (high temperature, thermal cycling, electrical stress, etc.). These degradation mechanisms do not only cause the breakdown of integrated circuits (hard failure), but also lead to the generation of drifts in the performances of

integrated circuits (soft failure). This effect is increasingly noteworthy in CMOS (Complementary Metal-Oxide-Semiconductor) circuits with deep submicron (DSM) technology (gate size less than 90 nm) [3][4]. There are existing standard models for the prediction of the reliability of ICs for the different industrial applications. The most traditional standards for reliability modeling are the MIL-HDBK-217F and FIDES, but they have been proposed considering only one dominant failure mechanism and do not take into account the possible combination of several degradation mechanisms after aging. Hence, the need of a modern reliability model for advanced ICs has been felt and recent researches dealing with their development.

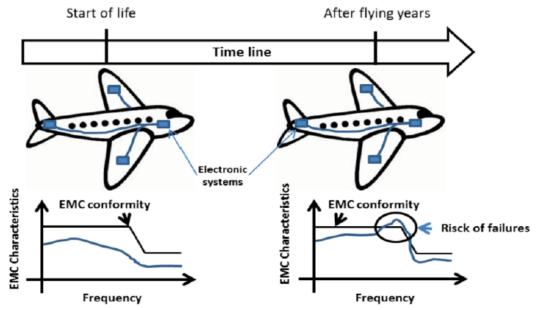

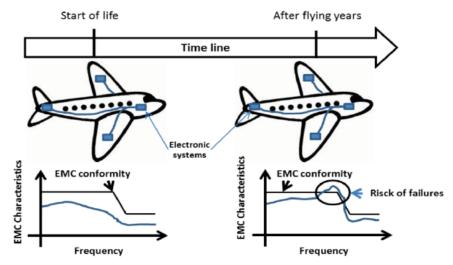

On the other hand, even if the aging of ICs does not compromise the functioning of the circuit, it can present a significant impact on EMC performance, as shown in recent research works [5][6][7][8]. The acceleration of the intrinsic degradation mechanisms in integrated circuits can lead to the variations of emission and immunity levels, affecting the EMC margins required by the final application. Therefore, there is no certainty that in a given environment and after certain lifetime duration, an electronic system is still compliant from an EMC the point of view. Figure 1 describes the problem of long-term electromagnetic robustness for aeronautic applications. Today, there is no existing tool that allows the prediction of EMC variations during the life cycle of a system. The recent researches that study the aging effect on EMC level relies on measurements under specific testing conditions and do not propose any method to predict the EMC level for untested operating conditions. The objective of this project is to demonstrate the feasibility of the construction of a new predictive electromagnetic robustness model.

Figure 1 Long-term electromagnetic robustness

This thesis is part of the work package 3 of the "Robustesse Electronique" (Electronic Robustness) project of IRT Saint-Exupéry deals with the development of predictive models to ensure the long-term electromagnetic compatibility robustness of embedded electronic systems. The purpose of this work is to develop EMC models for integrated circuits that take into account the environment and aging effect [9]. This project is supported by several industrials in Toulouse region (Continental, Airbus group innovation, Airbus, Nexio) and academic structures (LAAS CNRS, IMS Bordeaux).

The results of the work leaded in the work package 1 of the "Robustesse Electronique" project concern the construction of a predictive reliability model that combines the different activated degradation mechanisms with a multiple stress method. These results have been followed up for the long-term electromagnetic robustness prediction [10][11].

Compared to traditional reliability studies, the present long-term EM robustness study does not focus only on the components' lifetime, but also on the evolution over time of electromagnetic emission levels of ICs. The long-term electromagnetic robustness research work is applied to circuits that remain functional after a given period of stress.

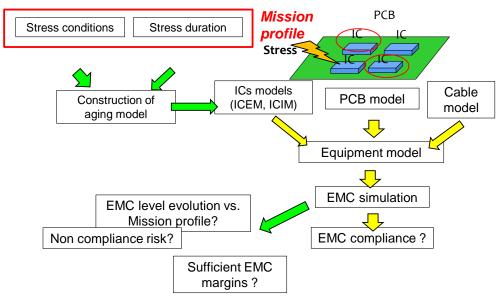

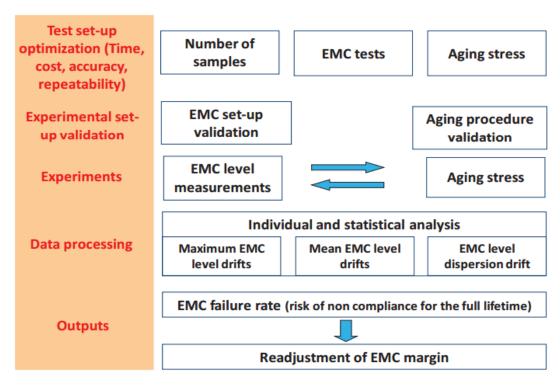

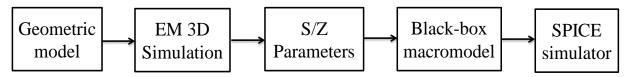

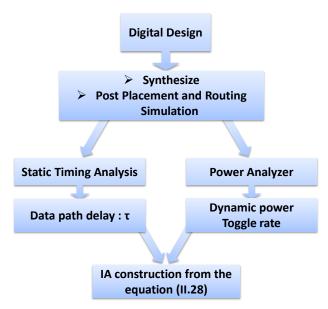

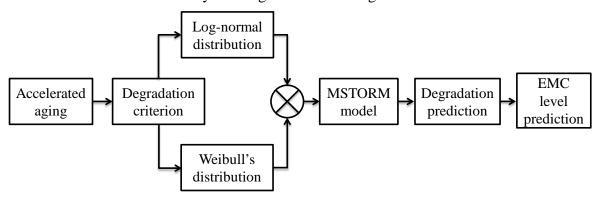

As presented in Figure 2, the aim of this project is the development of a generic methodology for the prediction of EMC level of an IC before and after aging under any operating conditions.

Figure 2 Workflow of long-term electromagnetic robustness prediction

## **Scope of this dissertation**

Based on the context presented above, this thesis deals with two main subjects:

- The improvement of IC models for EMC, especially the construction of ICEM-CE model for advanced integrated circuits dedicated to embedded applications with a proposal of new construction methodology to overcome the issues of the standard methods.

- o A new methodology proposal for the prediction of long-term conducted emission level based on a new reliability model. This model must be predictive, i.e. able to extrapolate the mean time required to a given EMC level drift in various stress conditions, even if there are multiple stress sources.

This manuscript is organized as follow:

The Chapter I presents a general overview on the effect of ICs reliability issues on the long-term electromagnetic robustness. This chapter introduces the technological evolution of CMOS circuits and the different aspects of EMC of ICs as it is presented in the state of the art. Furthermore, the reliability of ICs is explained with the presentation of the main activated degradation mechanisms during the operating lifetime of a CMOS IC. Finally, previous longterm electromagnetic robustness research works are briefly summarized.

The Chapter II deals with the methodology of construction of an ICEM-CE model of a complex digital circuit (in this study, a FPGA designed in 45 nm CMOS technology). The different blocks of the ICEM-CE model are constructed following the standard methods. In addition, a new methodology is proposed for the construction of the internal activity of the FPGA based on the manufacturer estimation tools and the component signal integrity models (IBIS). Compared to the standard approach, the proposed method simplifies the model extraction process and limits the influence of uncertainty. The results of this new approach will be compared to the standard method. Finally, a new developed tool for automatic extraction of the IA block is presented.

The Chapter III introduces the traditional and most recent models for reliability prediction used in the different industrial applications. To understand the reliability modeling approach, different acceleration models are presented for single and multiple stresses studies. Finally, the MSTORM model that allows the reliability prediction for combined degradation mechanisms is introduced. MSTORM will form the basis of the proposed methodology to predict the long-term electromagnetic robustness of ICs.

The Chapter IV presents the methodology of accelerated aging tests in order to construct the reliability model of the studied FPGA and compare the obtained data to the MSTORM model. Furthermore, the aging tests allow observing its effect on signal integrity and conducted emission (CE). Then the observed drift for a given time to failure is integrated into the ICEM-CE model for CE level simulation.

## References

- [1] S. Ben Dhia, M. Ramdani, E. Sicard, "Electromagnetic Compatibility of Integrated Circuits Techniques for Low Emission and Susceptibility", Springer, 2006

- [2] IEC62433-2 EMC IC modeling Part 2: Models of integrated circuits for EMI behavioural simulation - Conducted emissions modeling (ICEM-CE) - Edition 1.0, October 2008, IEC.

- [3] M. White, Y. Chen, "Scaled CMOS Technology Reliability Users Guide" JPL Publication 08-14 3/08, Pasadena, California.

- [4] McPherson JW. Reliability trends with advanced CMOS scaling and the implications for design. In: IEEE Custom Integrated Circuits Conference (CICC), 2007.

- [5] A. Boyer, S. Ben Dhia, B. Li, C. Lemoine, B. Vrignon, "Prediction of Long-term Immunity of a Phase-Locked Loop", Journal of Electronic Testing, December 2012, Volume 28, Issue 6, pp 791-802, DOI 10.1007/s10836-012-5335-y

- [6] S. Ben Dhia, A. Boyer, "Long-term Electro-Magnetic Robustness of Integrated Circuits: EMRIC research project", Microelectronic Reliability, vol. 53, pp. 1266-1272, 2013.

- [7] A. Boyer, S. Ben Dhia, B. Li, N. Berbel, R. Fernandez-Garcia, "Experimental Investigations on electrical Stress Impact on Integrated Circuit Electromagnetic Emission", IEEE Transaction on Electromagnetic Compatibility, vol. 56, no 1, February 2014, pp. 44-50, 10.1109/ 10.1109/TEMC.2013.2272195.

- [8] A. Boyer, S. Ben Dhia, « Effect of Aging on Power Integrity and Conducted Emission of Digital Integrated Circuits », Journal of Low Power Electronics (JOLPE), Vol. 10, No 1, March 2014.

- [9] A. Durier, "A methodologic project to characterize and model EMC behavior of COTS components after ageing", EMC Compo 2015, Edimburgh, Scotland, November 2015.

- [10] E. Suhir, A. Bensoussan, "Aerospace Optoelectronics Reliability: Application of Multi-Parametric BAZ Model" IEEE Aerospace Conference, March 1-8 2014.

- [11] J. B. Bernstein, A. Bensoussan, E. Bender, "Reliability prediction with MTOL", Microelectronics reliability journal, 2016.

## Chapter I. Effect of ICs reliability issues on long-term electromagnetic robustness

With the development of the nanoscales circuits and their strong integration in the different embedded application areas, the EMC constraints raise more problems related to the evolution of the electrical characteristics of the integrated circuits. In addition, the integration of the Deep Sub-Micron (DSM) circuits in critical environments implies the appearance of degradations, which impairs the functional safety of the electronic devices. Thus, it has become crucial to study the electromagnetic compatibility compliance and the reliability of integrated circuits to characterize their electromagnetic robustness.

In this chapter, the first section is dedicated to a presentation of the technology evolution from the past to the predicted future, and the different aspects of the electromagnetic compatibility (emissions, susceptibility) of integrated circuit are presented and the transistors scaling impact on the evolution of the electromagnetic compatibility is discussed. The second section concerns the reliability of integrated circuit, the different degradation mechanism will be presented and their evolution with the new technologies. Finally, the aging effect on the electromagnetic emissions and susceptibility is presented with case studies from the "state of the art".

## 1. Overview on EMC of integrated circuits

## 1.1. Evolution of CMOS technology

#### 1.1.1 CMOS technology scaling theory

The birth of CMOS (Complementary Metal-Oxide-Semiconductor) technology took place in 1963; it was invented by Franck Wanlass at Fairchild semiconductor. Since then, CMOS technology is widely used for the development of integrated circuits as microprocessors, microcontrollers, memories and other digital circuits. The evolution of the economic context of electronic industry since the 1990's implied strong requirements in terms of reducing the power density and increasing the performance of integrated circuits.

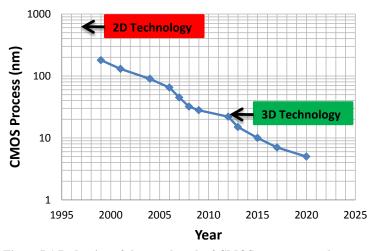

Over the last 15 years, the use of integrated circuits has evolved in the various application areas. The main purpose was to miniaturize electronic equipment to include increasingly complex electronic functions in a reduced space, which affected the transistors scaling [12]. As displayed below in the Figure I-1, the CMOS technology process has presented an important shrinkage from 180 nm in 2000 (2D technology) to reach 5 nm in 2020 involving the 3D technology from 2012. The 3D technology integration consists in manufacturing integrated circuits by stacking silicon wafer vertically using through-silicon vias (TSV) interconnections. The 3D technology allows the increase of system performance with decreasing the interconnect distance between the region of a chip and decreasing wiring parasitic [2].

Figure I-1 Reduction of the gate length of CMOS process over the years

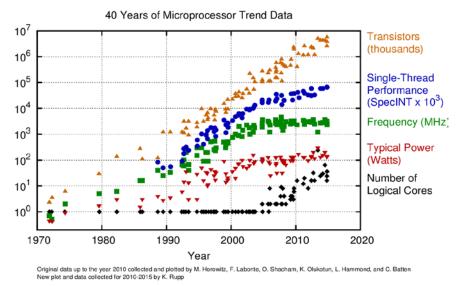

In 1965, Gordon Moore observed that the number of components inside a chip has doubled every 18 months [14]. He established an outstanding law called Moore's law that gave a quantitative estimation of the electronic progress. The evolution of the digital electronic industry predicted by Moore's law presented a good accuracy for the last decades and involved a major technological advance of various digital circuits as the increase of memories capacity and the development of sensors. The consequence of electronic industry progress for the last 40 years is presented in the Figure I-2 where the data was collected by [15] and completed for 2010-2015 by K. Rupp, it shows an important evolution of transistor count as predicted by Moore's law due to the reduction of the gate length which enhanced the number of logical cores. In the same Figure, as suggested by Dennard [16], the power density growth is proportional to the number of transistors; the reason of the power density increase is related to the die size and the fast frequency scaling [17].

Figure I-2 Evolution of ICs characteristics with the technology scaling [15]

## 1.1.2 Impact of technology scaling on ICs

The evolution of the CMOS technology scaling has a major impact on the performances of the ICs. A significant decrease in performance gain is predicted below the power supply voltage of 1,5 V. This is related to the threshold voltage which decreases more slowly than the historical trend and leads to an aggressive design of MOS devices with a very high electric field in the gate oxide. Thereby, in the last six decades, manufacturers of devices for critical applications such as aeronautic, automotive, space and military have contributed to the development of the semiconductor reliability field. The main challenges that can hinder the transistors scaling can be depicted by different categories: the **physical challenge** comes from the increase of the leakage current which induce a negative leverage on the CMOS device functionalities, the powerthermal challenge, as mentioned in the previous paragraph, the increase of the transistors count leads to the increase of the power consumption and the need of a higher thermal dissipation, the material challenge is mainly related to the ability of the dielectric and the wiring materials to insure a reliable insulation and conduction, the technological challenge results from the lack of competence of lithography-based techniques to afford a resolution below the wavelength of light to manufacture CMOS components, and finally the economical challenge related to the increase of the cost of manufacturing more scaled transistors [18].

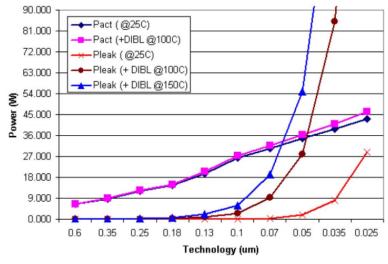

For the new scaled transistors technologies the power consumption at a single switching event has decreased, but the total on chip power consumption increased. The technology scaling impact on the power consumption concerns the dynamic power consumption and the leakage current, as presented in the Figure I-3 the dynamic power  $P_{act}$  increases linearly and the leakage power  $P_{leak}$  is increasing exponentially, due to the scaling down of the threshold voltage, and presents a higher sensitivity to the temperature [3]. In digital CMOS components, leakage power is a critical parameter that strongly affects the performance of the circuits; it induces the over-heat of the device and the decrease of the circuit lifetime. As a result the leakage power must be thoroughly controlled during the early design stages.

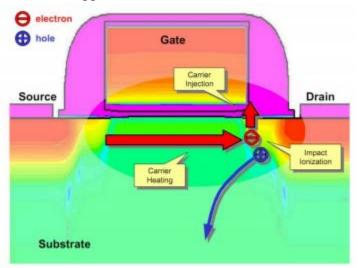

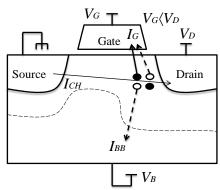

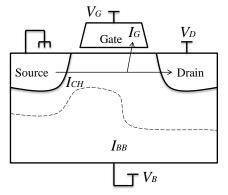

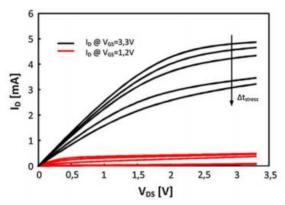

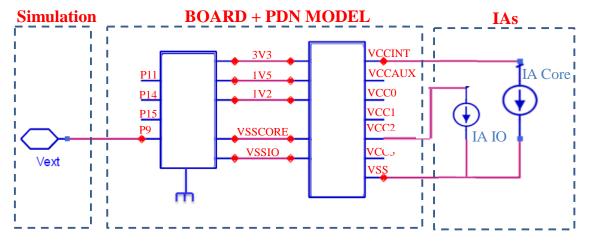

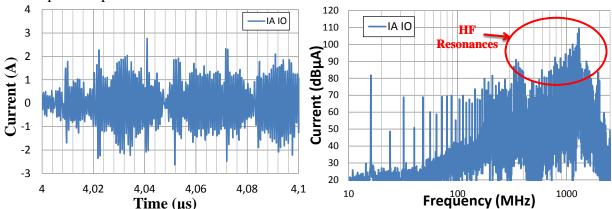

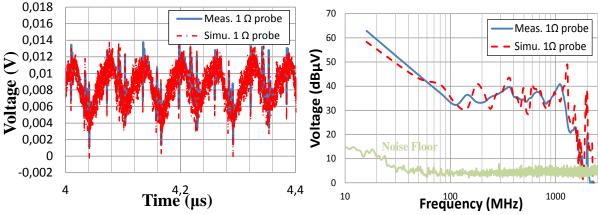

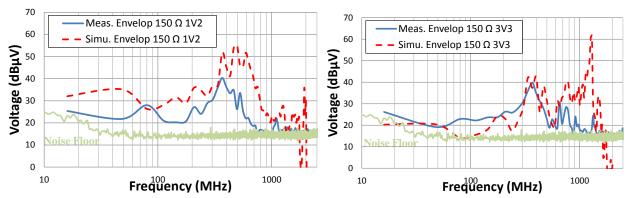

Figure I-3 Evolution of the leakage power and the dynamic power with technology scaling for different temperatures and constant die size [3]