# Programming methodologies for ADAS applications in parallel heterogeneous architectures

Djamila Dekkiche

#### ▶ To cite this version:

Djamila Dekkiche. Programming methodologies for ADAS applications in parallel heterogeneous architectures. Computer Vision and Pattern Recognition [cs.CV]. Université Paris Saclay (COmUE), 2017. English. NNT: 2017SACLS388. tel-02061977

### HAL Id: tel-02061977 https://theses.hal.science/tel-02061977

Submitted on 8 Mar 2019

HAL is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

NNT: 2017SACLS388

# Thèse de doctorat de l'Université Paris-Saclay Préparée à Université Paris-Sud

Laboratoire des Systems et Applications des Technologies de l'Information et de l'Energie

Ecole doctorale n°580

Sciences et Technologies de l'Information et de la Communication

Spécialité de doctorat

Traitement du signal et des images

par

## Mme. Djamila DEKKICHE

Programming methodologies of ADAS applications on parallel heterogeneous architectures

Thèse présentée et soutenue à "Digiteo Labs, Gif-sur-Yvette", le 10 Novembre 2017.

#### Composition du Jury:

| Μ. | François VERDIER | Professeur, Université de Nice              | (Président du jury)     |

|----|------------------|---------------------------------------------|-------------------------|

| Μ. | Vincent FREMONT  | Maître de conférences, UTC, Compiègne       | (Rapporteur)            |

| Μ. | Dominique HOUZET | Professeur, Grenoble-INP, Grenoble          | (Rapporteur)            |

| Μ. | Marc DURANTON    | Expert international, CEA LIST              | (Examinateur)           |

| Μ. | Alain MERIGOT    | Professeur, Université Paris-sud            | (Directeur de thèse)    |

| Μ. | Bastien VINCKE   | Maître de conférences, Université Paris-sud | (Co-Directeur de thèse) |

| Μ. | Witold KLAUDEL   | Chef de projet, Renault, IRT SystemX        | (Invité)                |

**Title:** Programming methodologies of ADAS applications on parallel heterogeneous architectures

**Keywords:** ADAS, parallel computing, computer vision, embedded systems

Abstract: Computer Vision (CV) is crucial for understanding and analyzing the driving scene to build more intelligent Advanced Driver Assistance Systems (ADAS). However, implementing CV-based ADAS in a real automotive environment is not straightforward. Indeed, CV algorithms combine the challenges of high computing performance and algorithm accuracy. To respond to these requirements, new heterogeneous circuits are developed. They consist of several processing units with different parallel computing technologies as GPU, dedicated accelerators, etc. To better exploit the performances of such architectures, different languages are required depending on the underlying parallel execution model.

In this work, we investigate various parallel programming methodologies based on a complex case study of stereo vision. We introduce the relevant features and limitations of each approach. We evaluate the employed programming tools mainly in terms of computation performances and programming productivity. The feedback of this research is crucial for the development of future CV algorithms in adequacy with parallel architectures with a best compromise between computing performance, algorithm accuracy and programming efforts.

**Titre:** Méthodologies de programmation d'algorithmes de traitement d'images sur des architectures parallèles et hétérogènes

Mots Clés: ADAS, traitement parallèle, computer vision, systèmes embarqués

**Résumé:** La vision par ordinateur est primordiale pour la compréhension et l'analyse d'une scène routière afin de construire des systèmes d'aide à la conduite (ADAS) plus intelligents. Cependant, l'implémentation de ces systèmes dans un réel environnement automobile et loin d'être simple. En effet, ces applications nécessitent une haute performance de calcul en plus d'une précision algorithmique. Pour répondre à ces exigences, de nouvelles architectures hétérogènes sont apparues. Elles sont composées de plusieurs unités de traitement avec différentes technologies de calcul parallèle: GPU, accélérateurs dédiés, etc. Pour mieux exploiter les performances de ces architectures, différents langages sont nécessaires en fonction du modèle d'exécution paral-

lèle.

Dans cette thèse, nous étudions diverses méthodologies de programmation parallèle. Nous utilisons une étude de cas complexe basée sur la stéréo-vision. présentons les caractéristiques et les limites de chaque approche. Nous évaluons ensuite les outils employés principalement en terme de performances de calcul et de difficulté de programmation. Le retour de ce travail de recherche est crucial pour le développement de futurs algorithmes de traitement d'images en adéquation avec les architectures parallèles avec un meilleur compromis entre les performances de calcul, la précision algorithmique et la difficulté de programmation.

To my loving parents Ahmed and Ferroudja

To my husband Amirouche

To my brother and sisters

To my family

To my friends

This work would not have been possible without your love and support.

#### Acknowledgements

This dissertation would not have been possible without the guidance and the support of several individuals, who contributed and extended their valuable assistance in the working out and completion of this study.

First, I give thanks to God for protection and ability to do work.

Foremost, I would like to express my sincere gratitude to both my advisor Alain Mérigot and co-supervisor Bastien Vincke for the continuous support of my Ph.D study and research, for their patience, confidence and immense knowledge. Their guidance helped me in all the time of research and writing of this thesis. I thank them for giving me the opportunity to work under their direction and for believing in my capacities.

I would like to thank the rest of my thesis committee for accepting to judge this work: Mr. Marc Duranton, Pr. Dominique Houzet, Mr. Vincent Frémont, Pr. François Verdier, Mr. Witold Klaudel and Mr. Joel Falcou.

This research work has been carried out in the framework of the Technological Research Institute SystemX, and therefore granted with public funds within the scope of the French Program "Investissements d'Avenir". My sincere thanks go to IRT SystemX Staff, ELA project members for providing the environment and required resources to complete this work. I would like to thank my referee Mr. Aymen Boudguiga for his support, help and for correcting my scientific papers.

Last but not the least, I would like to thank my family: my parents, Dad and Mom, you have always encouraged me, you did all your best to help and support me. I would never be able to thank you enough. I would like to thank also my husband who supported and always believed on me.

#### **Publications**

#### **International Journal**

- "Targeting System-Level and Kernel-Level Optimizations of Computer Vision Applications on Embedded Systems"

- D. Dekkiche, B. Vincke and A. Mérigot, Journal of Low Power Electronics (JOLPE), to appear on December 2017.

#### **International Conferences and Symposiums**

- "Targeting System-Level and Kernel-Level Optimizations of Computer Vision Applications on Embedded Systems"

- D. Dekkiche, B. Vincke and A. Mérigot, International Symposium on Embedded Computing and System Design (ISED), Patna, India, 2016.

- 2. "Investigation and Performance Analysis of OpenVX Framework Optimizations on Computer Vision Applications"

- D. Dekkiche, B. Vincke and A. Mérigot, International Conference on Control, Automation, Robotics and Vision (ICARCV), Phuket, Thailande, 2016.

- 3. "Vehicles Detection in Stereo Vision Based on Disparity Map Segmentation and Objects Classification"

- D. Dekkiche, B. Vincke and A. Mérigot, International Symposium on Visual Computing (ISVC), pp. 762-773, Las Vegas, USA, 2015.

## Contents

| Li | st of | Figure  | es                                                 | X   |

|----|-------|---------|----------------------------------------------------|-----|

| Li | st of | Tables  | 5                                                  | xiv |

| 1  | Int   | rodu    | ction                                              | 1   |

|    | 1.1   | Conte   | xt: Embedding Vision-Based ADAS                    | 2   |

|    |       | 1.1.1   | ADAS Challenges and Opportunities                  | 3   |

|    |       | 1.1.2   | Real-Time ADAS                                     | 3   |

|    | 1.2   | Proble  | em Statement                                       | 4   |

|    |       | 1.2.1   | Challenges of Embedded Image Processing Algorithms | 4   |

|    |       | 1.2.2   | Hardware Platforms                                 | 6   |

|    |       | 1.2.3   | Software Tools                                     | 7   |

|    | 1.3   | Motiva  | ations                                             | 9   |

|    | 1.4   | Resear  | rch Goals and Contributions                        | 11  |

|    | 1.5   | Thesis  | organization                                       | 13  |

| 2  | Sta   | ate of  | the Art                                            | 15  |

|    | 2.1   | Paralle | elism Fundamentals                                 | 16  |

|    | 2.2   | Embe    | dded Platforms for Vision-based ADAS               | 16  |

|    |       | 2.2.1   | Multi-cores                                        | 17  |

|    |       | 2.2.2   | GPUs                                               | 18  |

|    |       | 2.2.3   | FPGAs                                              | 19  |

|    |       | 2.2.4   | ASICs                                              | 20  |

|    |       | 2.2.5   | Heterogeneous Architectures                        | 20  |

|    | 2.3   | Paralle | el Software Tools for Embedded Platforms           | 21  |

|    |       | 2.3.1   | Directive-based Tools                              | 23  |

|   |     |         | 2.3.1.1 OpenMP                                                   | 23 |

|---|-----|---------|------------------------------------------------------------------|----|

|   |     |         | 2.3.1.2 OpenACC                                                  | 25 |

|   |     | 2.3.2   | Low-level APIs                                                   | 28 |

|   |     |         | 2.3.2.1 CUDA                                                     | 28 |

|   |     |         | 2.3.2.2 OpenCL                                                   | 30 |

|   |     | 2.3.3   | Data Flow-Based Graphs for Parallel Programming                  | 31 |

|   |     | 2.3.4   | DSL                                                              | 32 |

|   |     |         | 2.3.4.1 Halide                                                   | 32 |

|   |     |         | 2.3.4.2 NT2                                                      | 33 |

|   |     | 2.3.5   | Vectorization: SIMD                                              | 36 |

|   | 2.4 | Conclu  | usion                                                            | 37 |

| 3 | ΔГ  | ) AS T  | Use Case                                                         |    |

| J |     |         |                                                                  | 39 |

|   | 3.1 |         | G                                                                | 39 |

|   |     | 3.1.1   |                                                                  | 40 |

|   | 3.2 | Stereo  |                                                                  | 41 |

|   |     | 3.2.1   |                                                                  | 41 |

|   |     | 3.2.2   |                                                                  | 43 |

|   |     |         |                                                                  | 45 |

|   |     |         | 3.2.2.2 Cost Aggregation                                         | 45 |

|   |     |         | 3.2.2.3 Disparity Computation                                    | 46 |

|   |     |         | 3.2.2.4 Disparity Refinement                                     | 46 |

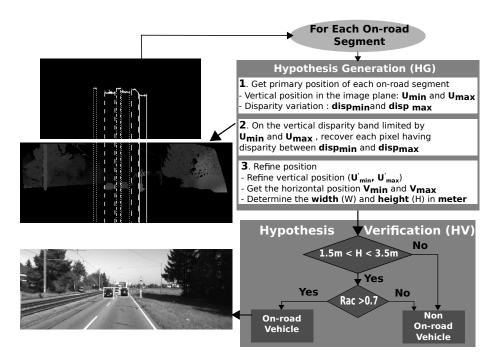

|   | 3.3 | Vehicle | es Detection Proposed Algorithm                                  | 47 |

|   |     | 3.3.1   | Level 1 : Disparity Map Generation                               | 48 |

|   |     |         | 3.3.1.1 Supports Points                                          | 49 |

|   |     |         | 3.3.1.2 Generative Probabilistic Model for Dense Stereo Matching | 50 |

|   |     |         | 3.3.1.3 Samples' Selection on the Right Image                    | 52 |

|   |     |         | 3.3.1.4 Disparity Estimation                                     | 52 |

|   |     | 3.3.2   | Level 2 : Scene Segmentation                                     | 53 |

|   |     |         | 3.3.2.1 Road Detection                                           | 53 |

|   |     |         | 3.3.2.2 Pixels' Classification                                   | 54 |

|   |     |         | 3.3.2.3 Free Space Propagation                                   | 54 |

|   |     |        | 3.3.2.4 Sky Subtraction                                       | 55         |

|---|-----|--------|---------------------------------------------------------------|------------|

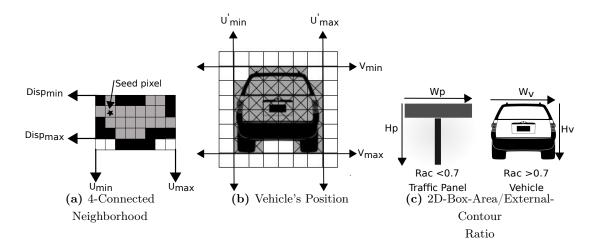

|   |     | 3.3.3  | Level 3 : Vehicles Detection                                  | 55         |

|   |     |        | 3.3.3.1 Phase 1 : Off-Road Features Subtraction $\dots \dots$ | 56         |

|   |     |        | 3.3.3.2 Phase 2 : On-Road Vehicles Detection                  | 58         |

|   | 3.4 | Exper  | imental Results                                               | 59         |

|   |     | 3.4.1  | Experimental Design                                           | 59         |

|   |     | 3.4.2  | Analysis of Obtained Results                                  | 60         |

|   | 3.5 | Discus | ssion                                                         | 62         |

| 4 | Ke  | rnel-l | Level Optimizations on CPU                                    |            |

| - |     |        | ation and Shared Memory Parallelization                       | 64         |

|   | 4.1 |        | Based Stereo Matching Algorithm                               | 65         |

|   |     | 4.1.1  | ELAS : Original CPU Based Algorithm                           | 65         |

|   |     | 4.1.2  | A-ELAS: Adapt to Parallelize                                  | 68         |

|   |     | 4.1.3  | A-ELAS : Profiling and Analysis                               | 70         |

|   | 4.2 | Exper  | imental Design                                                | 71         |

|   | 4.3 | SIMD   | Implementation                                                | 72         |

|   |     | 4.3.1  | Intel(SSE) vs ARM(NEON)                                       | 73         |

|   |     | 4.3.2  | ARMv7(Cortex-A15) vs ARMv8(Cortex-A57)                        | 75         |

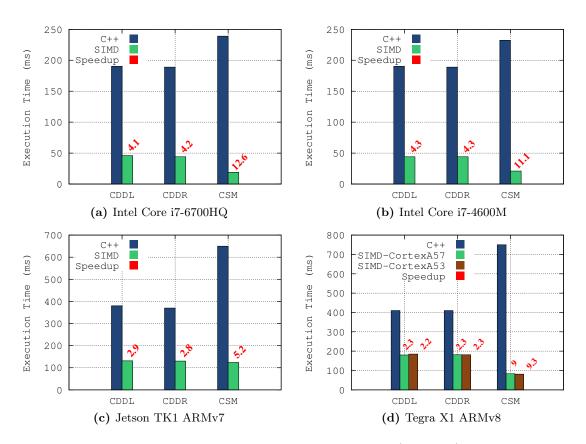

|   |     | 4.3.3  | Obtained Results                                              | 76         |

|   | 4.4 | Open   | MP Implementation                                             | <b>7</b> 9 |

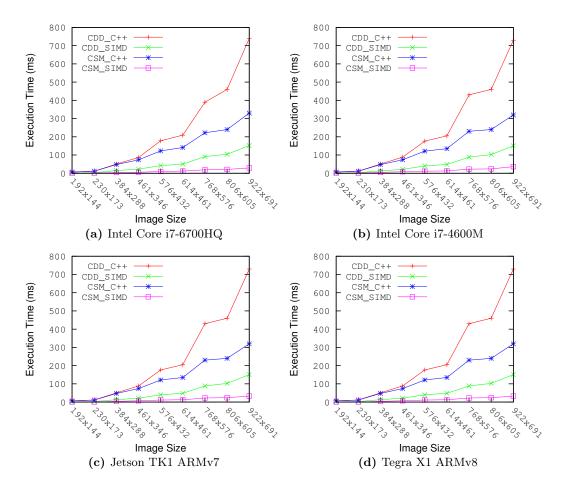

|   |     | 4.4.1  | Obtained Results                                              | 80         |

|   | 4.5 | SIMD   | $+ \ OpenMP  . \ . \ . \ . \ . \ . \ . \ . \ . \ .$           | 82         |

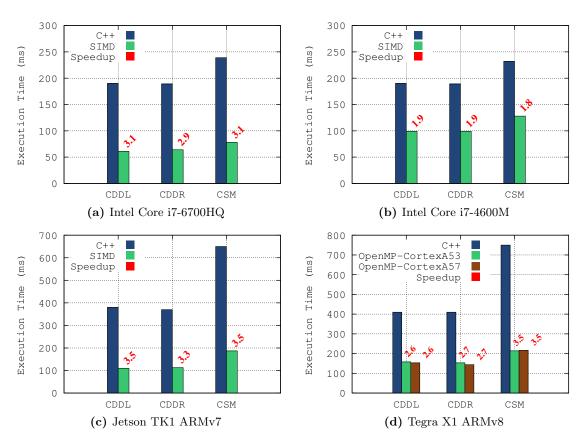

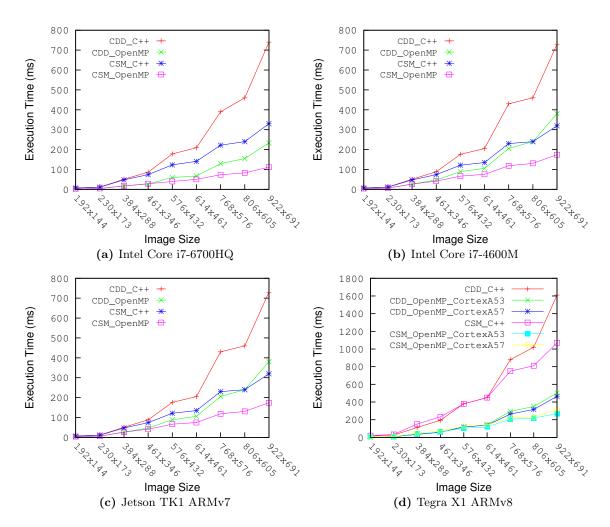

|   |     | 4.5.1  | Obtained Results                                              | 83         |

|   | 4.6 | OpenA  | ACC Parallelization on CPU                                    | 84         |

|   |     | 4.6.1  | Obtained Results                                              | 84         |

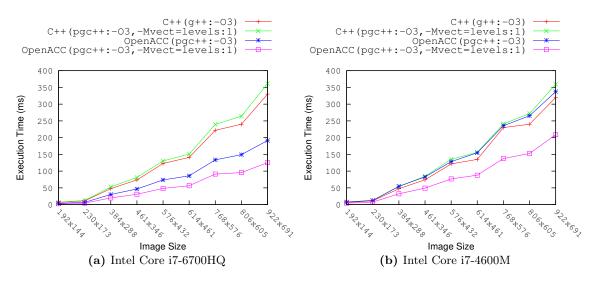

|   |     |        | 4.6.1.1 CDD Function                                          | 84         |

|   |     |        | 4.6.1.2 CSM Function                                          | 87         |

|   | 4.7 | NT2 I  | mplementation                                                 | 92         |

|   |     | 4.7.1  | Obtained Results                                              | 93         |

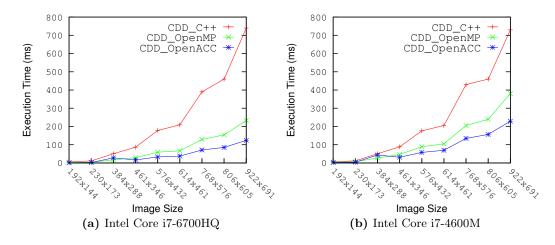

|   |     |        | 4.7.1.1 CDD Function                                          | 93         |

|   |     |        | 4.7.1.2 CSM Function                                          | 96         |

|   | 4.8 | Evalua | ation                                                         | 98         |

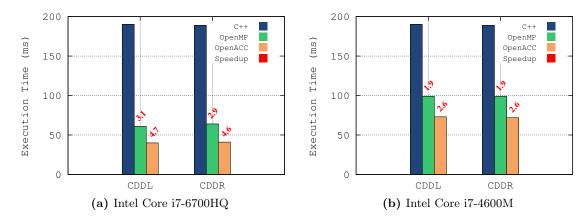

|   |     | 4.8.1  | OpenMP vs OpenACC                                      | <br>99  |

|---|-----|--------|--------------------------------------------------------|---------|

|   |     |        | 4.8.1.1 CDD Function                                   | <br>99  |

|   |     |        | 4.8.1.2 CSM Function                                   | <br>100 |

|   |     |        | 4.8.1.3 Limitations of OpenACC on Multi-core Systems   | <br>101 |

|   |     | 4.8.2  | NT2 vs SIMD                                            | <br>102 |

|   | 4.9 | Discus | ssion                                                  | <br>102 |

| 5 | Ke  | rnel-I | Level Optimizations                                    |         |

|   |     |        | plementation                                           | 104     |

|   | 5.1 | GPU    | Architecture Overview                                  | <br>105 |

|   | 5.2 | Perfor | rmance Bounds on GPUs                                  | <br>105 |

|   | 5.3 | Optim  | nizations Techniques on GPUs                           | <br>107 |

|   | 5.4 | Nvpro  | of Metrics                                             | <br>108 |

|   | 5.5 | Exper  | rimental Design                                        | <br>109 |

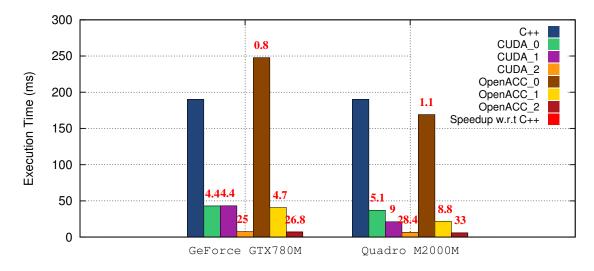

|   | 5.6 | Open   | ACC and CUDA Optimization of CDD Function              | <br>110 |

|   |     | 5.6.1  | First Naive Implementation                             | <br>111 |

|   |     |        | 5.6.1.1 CUDA Kernel                                    | <br>111 |

|   |     |        | 5.6.1.2 OpenACC kernel                                 | <br>114 |

|   |     | 5.6.2  | Optimization 1 : L1 Caching of Global Loads            | <br>117 |

|   |     |        | 5.6.2.1 CUDA Kernel                                    | <br>119 |

|   |     |        | 5.6.2.2 OpenACC Kernel                                 | <br>120 |

|   |     | 5.6.3  | Optimization 2 : Minimize Global Memory Use/Accesses . | <br>122 |

|   |     |        | 5.6.3.1 CUDA Kernel                                    | <br>123 |

|   |     |        | 5.6.3.2 OpenACC Kernel                                 | <br>124 |

|   |     | 5.6.4  | Optimization 3 : Use Shared Memory                     | <br>125 |

|   |     |        | 5.6.4.1 First Naive Implementation                     | <br>125 |

|   |     |        | 5.6.4.2 Optimize Regular Access Pattern                | <br>127 |

|   |     |        | 5.6.4.3 Maximize Number of Warps                       | <br>128 |

|   | 5.7 | Open   | ACC and CUDA Optimizations of CSM                      | <br>130 |

|   |     | 5.7.1  | First Naive Implementation                             | <br>131 |

|   |     |        | 5.7.1.1 CUDA Kernel                                    | <br>131 |

|   |     |        | 5.7.1.2 OpenACC Kernel                                 | <br>132 |

|   |     | 572    | First Optimization with OpenACC: avoid warp divergence | 132     |

|   |     | 5.7.3   | Second Optimization with OpenACC: Explicit Loop Unrolling $\blacksquare 3$ | }3         |

|---|-----|---------|----------------------------------------------------------------------------|------------|

|   | 5.8 | Evalua  | ation: CUDA vs OpenACC                                                     | <b>}</b> 4 |

|   |     | 5.8.1   | Productivity                                                               | 34         |

|   |     | 5.8.2   | Portability                                                                | <b>}</b> 5 |

|   |     | 5.8.3   | Performance                                                                | <u>}6</u>  |

|   |     |         | 5.8.3.1 OpenACC Benefits and Limitations                                   | <u>}6</u>  |

|   | 5.9 | Discus  | ssion                                                                      | <u>}6</u>  |

| 6 | Ke  | rnel-S  | System-Level Optimizations [13]                                            | 8          |

|   | 6.1 | OpenV   | /X                                                                         | <u>}9</u>  |

|   |     | 6.1.1   | Background                                                                 | <u>}9</u>  |

|   |     | 6.1.2   | Programming Model: Front-End                                               | 10         |

|   |     | 6.1.3   | System-Level Optimizations                                                 | 12         |

|   |     | 6.1.4   | OpenVX User Kernel Tiling Extension                                        | 13         |

|   | 6.2 | Boost.  | SIMD                                                                       | 4          |

|   |     | 6.2.1   | Why boost.SIMD                                                             | 4          |

|   |     | 6.2.2   | What is boost.SIMD                                                         | 6          |

|   | 6.3 | System  | n-level Optimizations                                                      | 6          |

|   |     | 6.3.1   | Obtained Results                                                           | 17         |

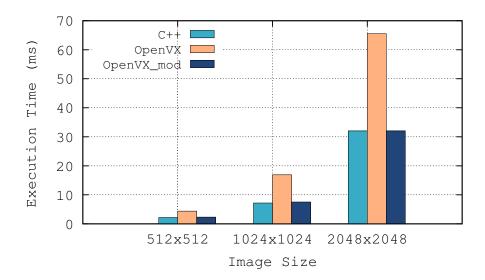

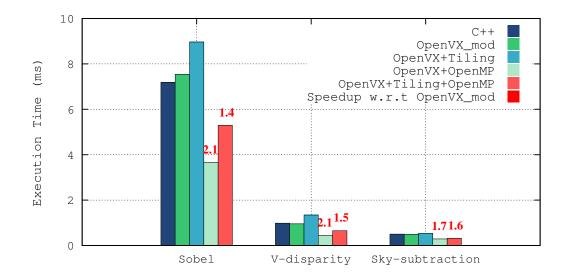

|   |     |         | 6.3.1.1 First Experience : OpenVX vs C++                                   | 17         |

|   |     |         | 6.3.1.2 Impact of Data Access Pattern                                      | 1          |

|   |     |         | 6.3.1.3 Kernels Merge                                                      | <u>5</u> 2 |

|   |     |         | 6.3.1.4 Data Tiling                                                        | 4          |

|   |     |         | 6.3.1.5 OpenVX with OpenMP                                                 | 6          |

|   |     |         | 6.3.1.6 OpenVX Data Tiling with OpenMP                                     | 7          |

|   |     | 6.3.2   | Discussion and Analysis of Obtained Results                                | 8          |

|   | 6.4 | kernel- | -System-level Optimizations                                                | 8          |

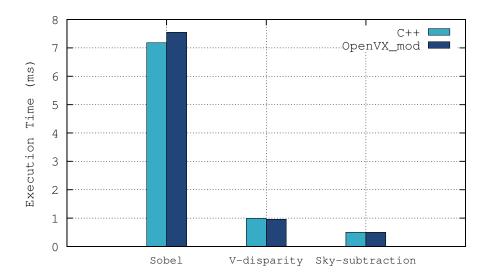

|   |     | 6.4.1   | Obtained Results                                                           | <u>i0</u>  |

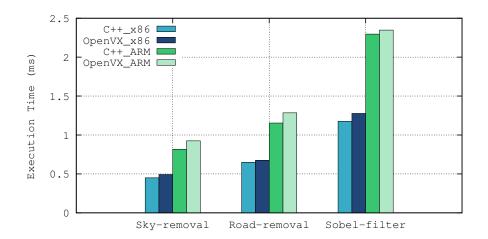

|   |     |         | 6.4.1.1 OpenVX on Embedded Platforms                                       | <u>i0</u>  |

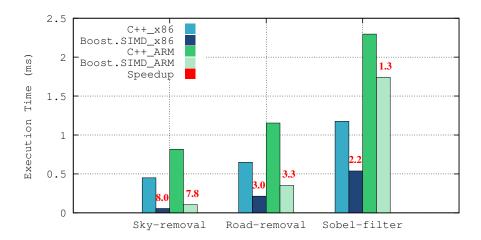

|   |     |         | 6.4.1.2 Vectorization Results with boost.SIMD                              | i1         |

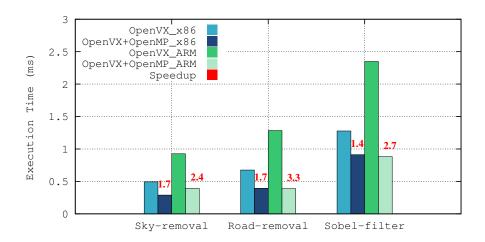

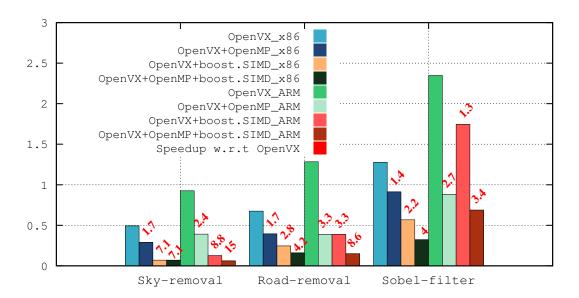

|   |     |         | 6.4.1.3 Shared Memory Parallelization Results with OpenVX . 16             | <u>i3</u>  |

|   |     |         | 6.4.1.4 Shared Memory Parallelization and Vectorization on OpenVX          | ζ          |

|   |     |         | with boost SIMD                                                            |            |

#### CONTENTS

|              | 6.5   | Discussion                                | 166        |

|--------------|-------|-------------------------------------------|------------|

| 7            | Con   | nclusion                                  | <b>169</b> |

|              | 7.1   | Conclusions                               | 169        |

|              | 7.2   | Future Works                              | 173        |

| $\mathbf{A}$ | Syn   | thèse en Français                         | 176        |

|              | A.1   | Contexte                                  | 176        |

|              |       | A.1.1 ADAS : Challenges et Opportunités   | 177        |

|              | A.2   | Problématique                             | 177        |

|              | A.3   | Motivations                               | 178        |

|              | A.4   | Approche et Objectives                    | 178        |

|              |       | A.4.1 Cas d'usage                         | 179        |

|              |       | A.4.2 Architectures                       | 180        |

|              |       | A.4.3 Langages de Programmation Parallèle | 180        |

|              | A.5   | Résultats                                 | 181        |

|              | A.6   | Contributions et Conclusions              | 183        |

| Re           | efere | nces                                      | 185        |

# List of Figures

| 1.1  | Architecture of an ADAS                                                    | 2  |

|------|----------------------------------------------------------------------------|----|

| 1.2  | Processing Levels Specifications                                           | 5  |

| 1.3  | Embedded ADAS Development Process and Challenges                           | 10 |

| 2.1  | Parallel Programming Models                                                | 22 |

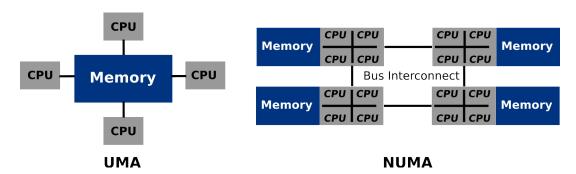

| 2.2  | UMA and NUMA Memory Models                                                 | 24 |

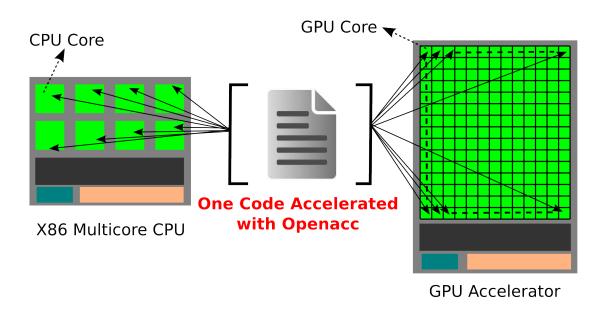

| 2.3  | CPU and GPU Model of OpenACC                                               | 26 |

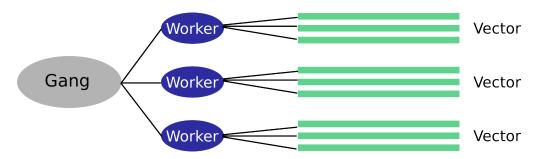

| 2.4  | OpenACC Programming Granularity                                            | 27 |

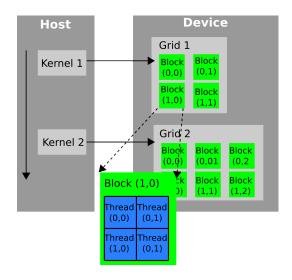

| 2.5  | CUDA Memory Grid Configuration                                             | 29 |

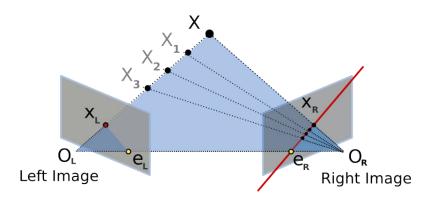

| 3.1  | Epipolar Geometry in Stereo Vision                                         | 42 |

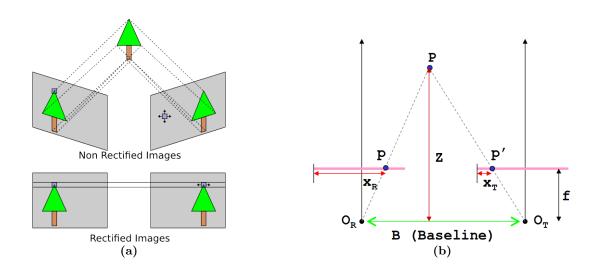

| 3.2  | Rectification (a) and Depth Measurement (b) from Stereo Matching           | 43 |

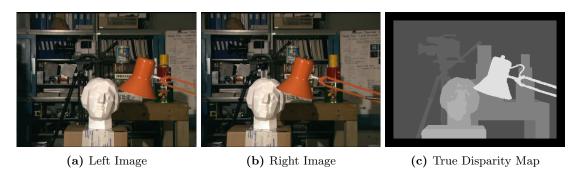

| 3.3  | Disparity Map Example from Middlebury Dataset $\blacksquare$ (Tsukuba2001) | 44 |

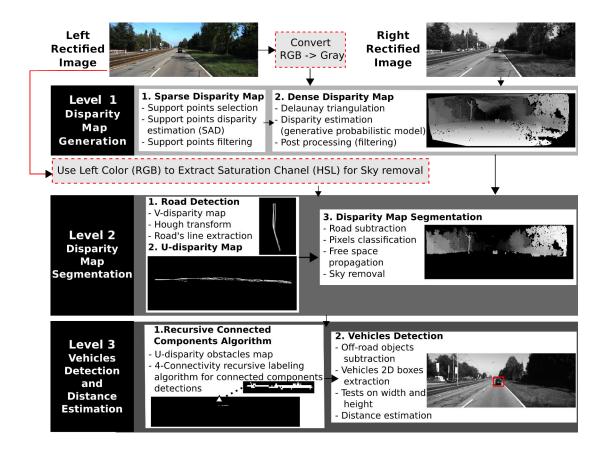

| 3.4  | Proposed Vehicles Detection Algorithm's Functional Diagram                 | 47 |

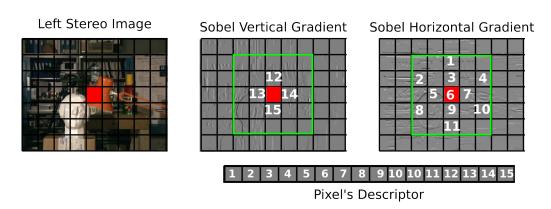

| 3.5  | Pixel's Descriptor in Elas Algorithm                                       | 49 |

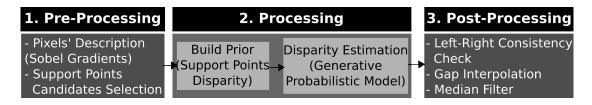

| 3.6  | ELAS Functional Diagram                                                    | 49 |

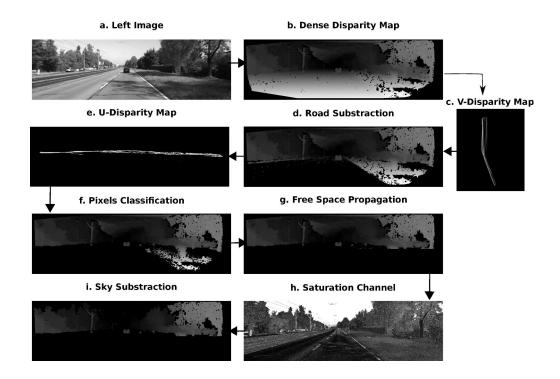

| 3.7  | Scene Segmentation Approach                                                | 53 |

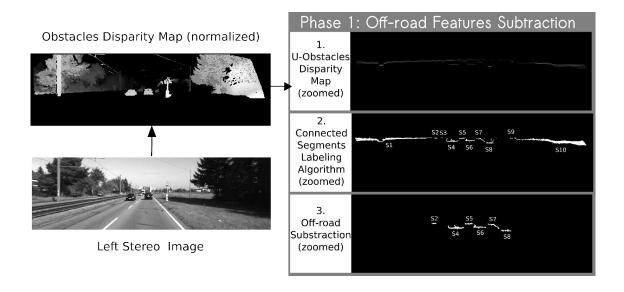

| 3.8  | Vehicles Detection Algorithm: Phase 1 Off-road Features Subtraction $$ .   | 56 |

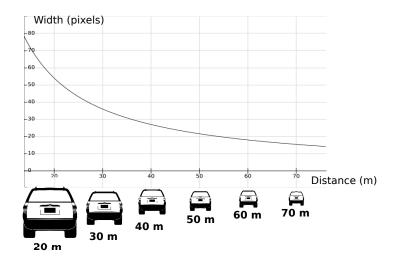

| 3.9  | Vehicle's Width Variation in Pixels with Distance for a 1.5 m Vehicle's    |    |

|      | Width                                                                      | 57 |

| 3.10 | Objects Classification and Vehicles Identification                         | 58 |

| 3.11 | Vehicles Detection Algorithm: Phase 2 On-Road Vehicles Detection $$        | 59 |

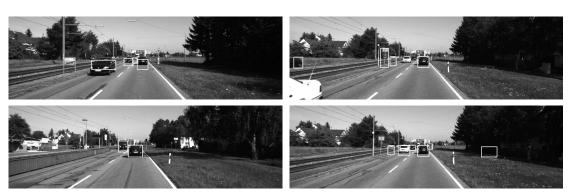

| 3.12 | Some Detections Results Obtained from KITTI Dataset                        | 61 |

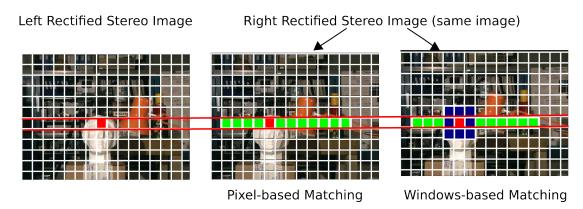

| 4.1  | Pixel-based vs Windows-based Stereo Matching                               | 66 |

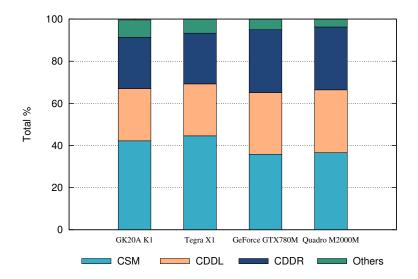

| 4.2  | A-ELAS Profiling Results on KITTI Dataset                                  | 71 |

#### LIST OF FIGURES

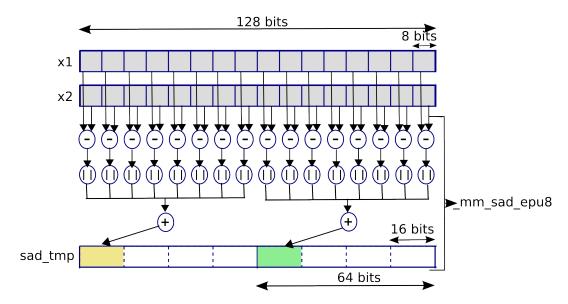

| 4.3  | Functional diagram of SSE SAD Intrinsic                                                   | 74  |

|------|-------------------------------------------------------------------------------------------|-----|

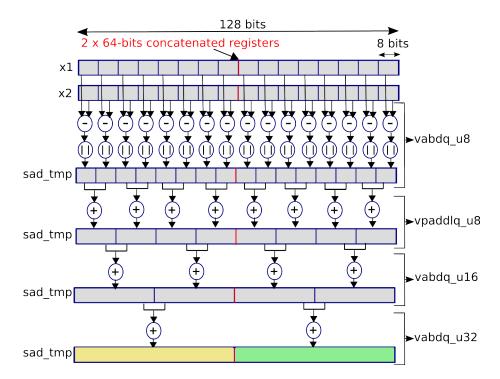

| 4.4  | Functional diagram of NEON Equivalent SAD Intrinsics                                      | 75  |

| 4.5  | C++ vs SIMD Execution Time on KITTI(1242x375) dataset                                     | 77  |

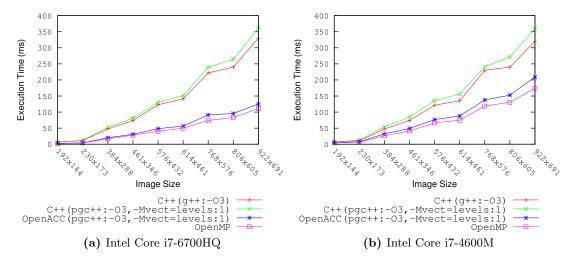

| 4.6  | C++ vs SSE Execution Time on Middlebury dataset                                           | 78  |

| 4.7  | C++ vs OpenMP Execution Time on KITTI(1242x375) Dataset                                   | 80  |

| 4.8  | $\mathrm{C}++$ vs OpenMP Execution Time on Middlebury Datasets                            | 81  |

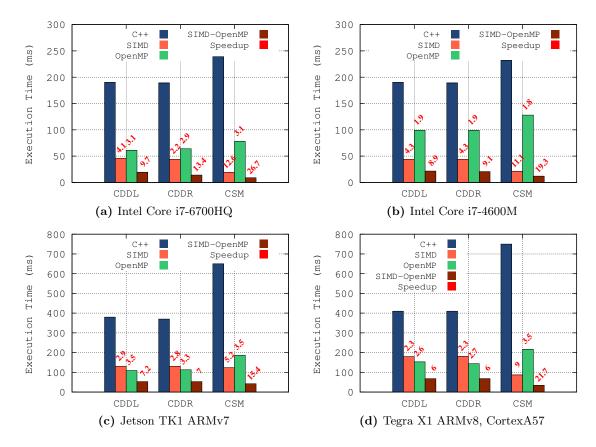

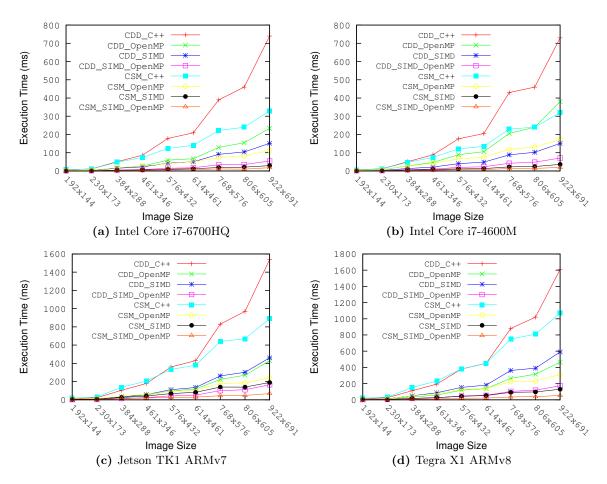

| 4.9  | $\mathrm{C}++$ vs SIMD vs OpenMP Performance on KITTI Dataset                             | 82  |

| 4.10 | $\mathrm{C}++$ vs SIMD vs OpenMP Performance on Middlebury Dataset                        | 83  |

| 4.11 | PGI Compiling Information Feedback of CDDL Function with OpenACC                          | 86  |

| 4.12 | C++ vs OpenACC Execution Time on KITTI Dataset of CDD Function.                           | 86  |

| 4.13 | C++ vs OpenACC Execution Time on Middlebury Dataset of CDD                                |     |

|      | Function                                                                                  | 87  |

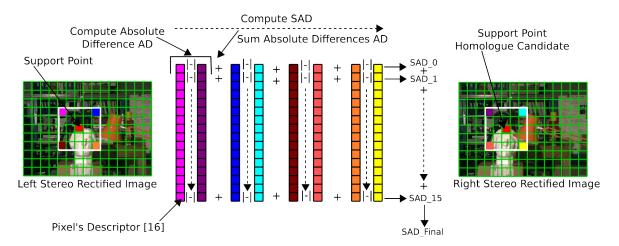

| 4.14 | CSM Cost Function Approach                                                                | 88  |

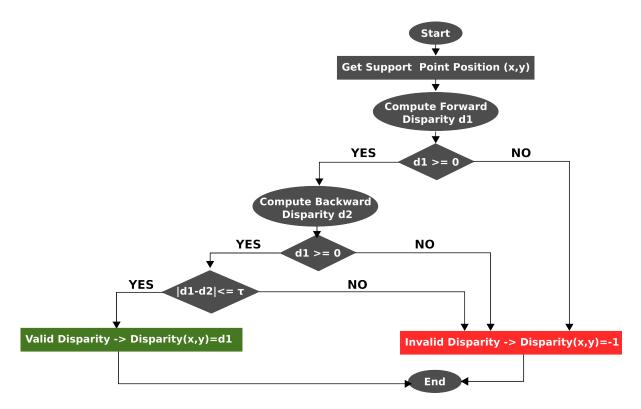

| 4.15 | CSM Algorithm Flowchart                                                                   | 89  |

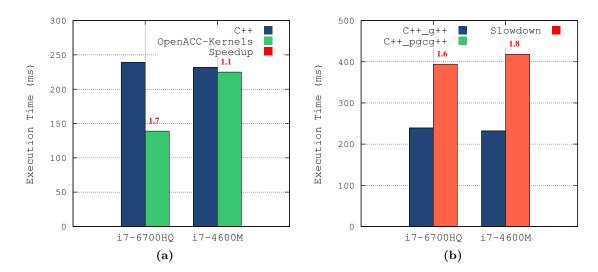

| 4.16 | $\mathrm{C}++$ vs OpenACC Execution Time on KITTI Dataset of CSM Function.                | 90  |

| 4.17 | C++ vs OpenACC Execution Time on KITTI Dataset of CSM Function.                           | 91  |

| 4.18 | C++ vs OpenACC Execution Time on Middlebury Dataset of CSM                                |     |

|      | Function                                                                                  | 92  |

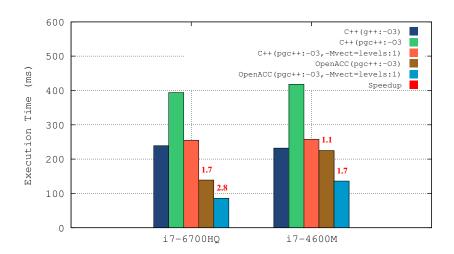

| 4.19 | Execution Time of CSM Function with NT2 on KITTI Dataset                                  | 98  |

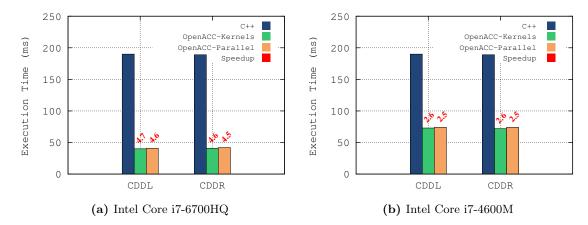

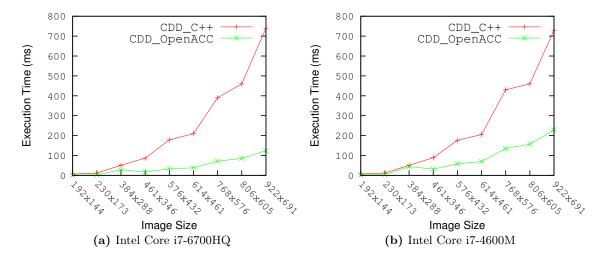

| 4.20 | $\mathrm{C}++$ vs $\mathrm{OpenMP}$ vs $\mathrm{OpenACC}$ Execution Time on KITTI Dataset | 99  |

| 4.21 | C++ vs OpenMP vs OpenACC Execution Time of CDD Function on                                |     |

|      | Middlebury Dataset                                                                        | 100 |

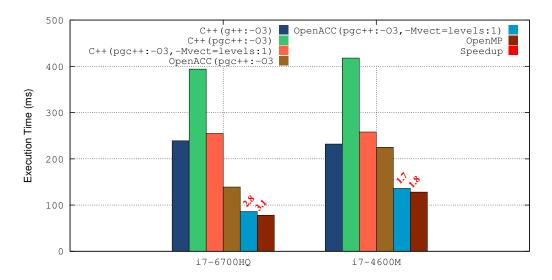

| 4.22 | Execution Time of CSM Function                                                            | 101 |

| 4.23 | C++ vs OpenMP vs OpenACC Execution Time of CSM Function on                                |     |

|      | Middlebury Dataset                                                                        | 101 |

|      |                                                                                           |     |

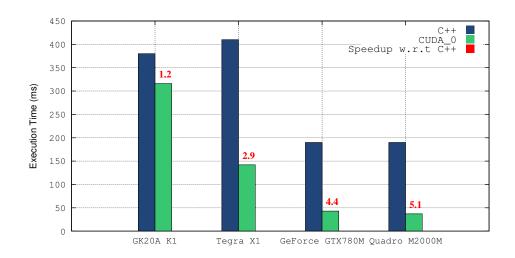

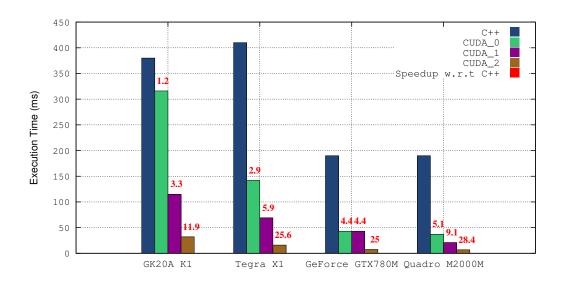

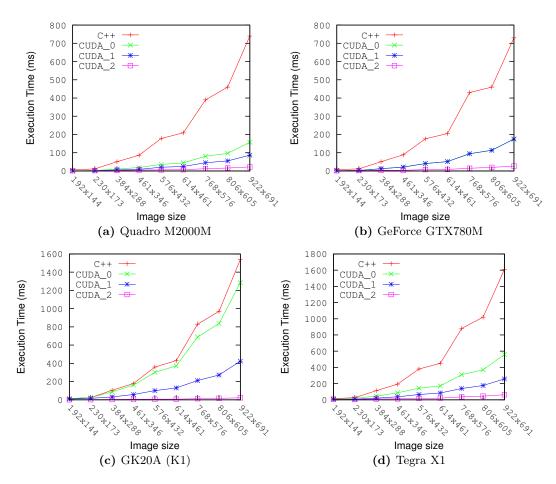

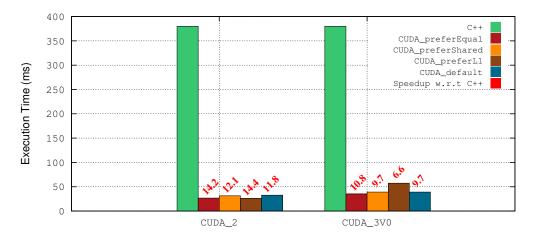

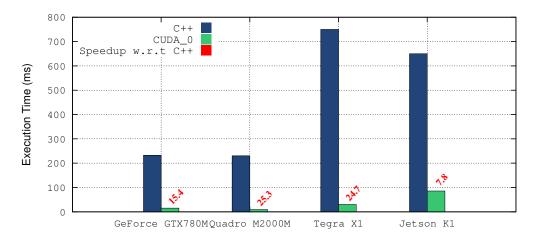

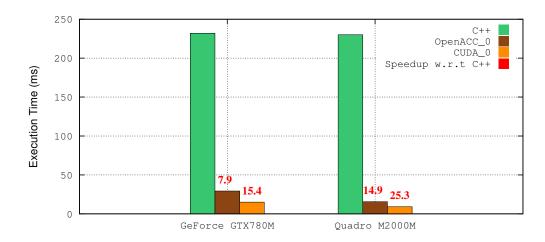

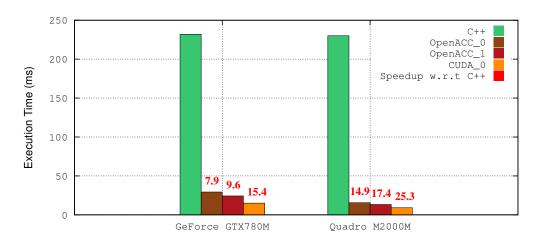

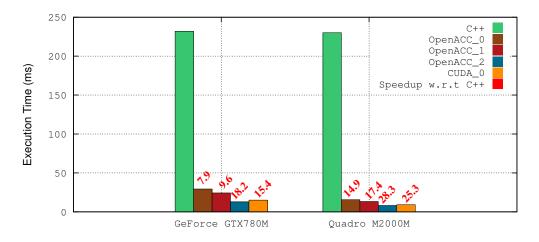

| 5.1  | Execution Time of First CDD CUDA Kernel on KITTI(1242x375)                                | 112 |

| 5.2  | Execution Time of First CDD OpenACC Kernel vs First CDD CUDA kernel                       |     |

|      | on KITTI( $1242x375$ )                                                                    | 115 |

| 5.3  | Execution Time of Optimized First CDD OpenACC Kernel vs First CDD                         |     |

|      | CUDA on KITTI(1242x375)                                                                   | 116 |

| 5.4  | Execution Time of CDD CUDA Kernel with L1 Caching on KITTI(1242x375)                      | 119 |

#### LIST OF FIGURES

| 5.5  | Execution Time of CDD CUDA Kernel with L1 Caching on Middlebury                  |     |

|------|----------------------------------------------------------------------------------|-----|

|      | Dataset                                                                          | 121 |

| 5.6  | Execution Time of OpenACC kernels on Middlebury Dataset                          | 122 |

| 5.7  | Execution Time of Third CDD CUDA Kernel on KITTI(1242x375)                       | 122 |

| 5.8  | Execution Time of Third ${\tt CDD}$ ${\tt CUDA}$ Kernel on Middlebury Dataset $$ | 123 |

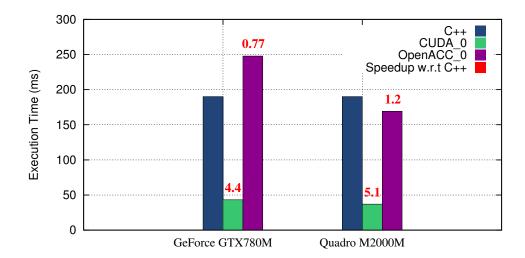

| 5.9  | Execution Time of CDD CUDA and OpenACC kernels on $KITTI(1242x375)$              | 124 |

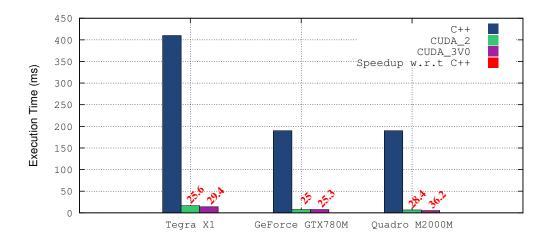

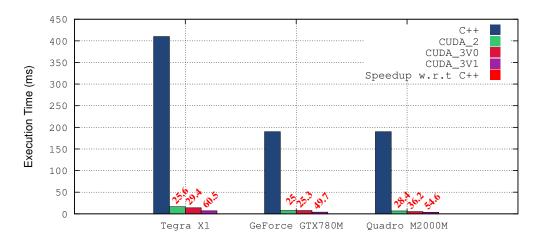

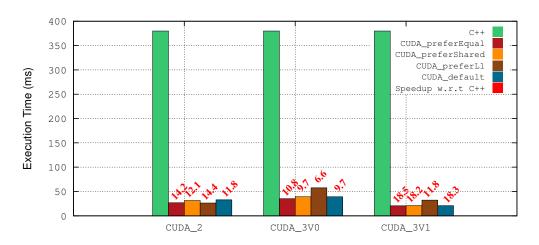

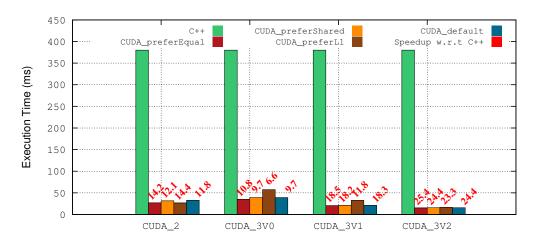

| 5.10 | Execution Time of First Version of Third CDD CUDA (CUDA3_V0) Kernel              |     |

|      | with Shared Memory on KITTI Dataset                                              | 126 |

| 5.11 | Execution Time of First Version of Third CDD CUDA (CUDA3_V0) Kernel              |     |

|      | with Shared Memory on KITTI Dataset, in Jetson K1 $\dots \dots$                  | 126 |

| 5.12 | Execution Time of Second Version of Third CDD $$ CUDA $$ (CUDA $$ 3V1) Ker-      |     |

|      | nel with Shared Memory on KITTI Dataset                                          | 127 |

| 5.13 | Execution Time of Second Version of Third CDD $$ CUDA $$ (CUDA $$ 3V1) Ker-      |     |

|      | nel with Shared Memory on KITTI Dataset in Jetson K1                             | 128 |

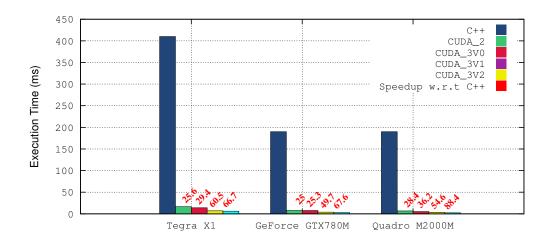

| 5.14 | Execution Time of Third Version of Third CDD CUDA (CUDA_3V2) Ker-                |     |

|      | nel with Shared Memory on KITTI Dataset                                          | 129 |

| 5.15 | Execution Time of Third Version of Third CDD CUDA (CUDA_3V2) Ker-                |     |

|      | nel with Shared Memory on KITTI Dataset in Jetson K1                             | 129 |

| 5.16 | Execution Time of CSM CUDA First Kernel on KITTI(1242x375) with CUDA             | 131 |

| 5.17 | Execution Time of CSM OpenACC First Kernel on $KITTI(1242x375)$                  | 132 |

| 5.18 | Execution Time of CSM OpenACC Second Kernel on $KITTI(1242x375)$                 | 133 |

| 5.19 | Execution Time of CSM <code>OpenACC</code> Third Kernel on KITTI(1242x375) $$    | 134 |

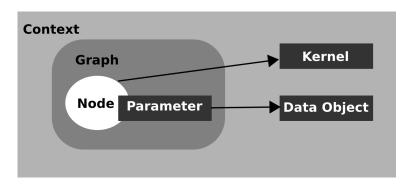

| 6.1  | OpenVX Framework Objects                                                         | 140 |

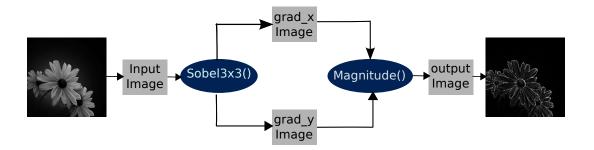

| 6.2  | OpenVX Sample Graph Diagram of Sobel Filter                                      | 141 |

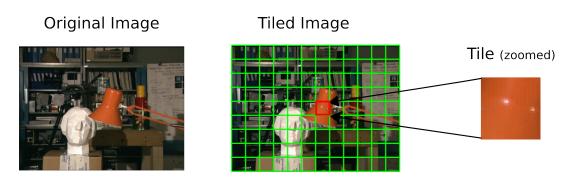

| 6.3  | Tiling Principle in Image Processing                                             | 143 |

| 6.4  | Some Classes of Data Access Pattern                                              | 147 |

| 6.5  | Employed Images for Sobel Filter                                                 | 148 |

| 6.6  | Performance Comparison Between C++ Language and OpenVX Frame-                    |     |

|      | work on Sobel Edge Detector                                                      | 150 |

| 6.7  | Data Access Pattern Impact on OpenVX Execution Time                              | 152 |

| 6.8  | Kernels Merge Execution Time with OpenVX on Sobel Filter                         | 153 |

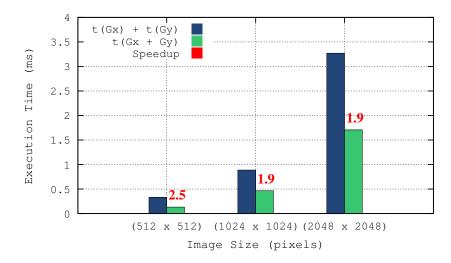

| 6.9  | Obtained Execution Times with OpenVX Tiling Extension                            | 154 |

#### LIST OF FIGURES

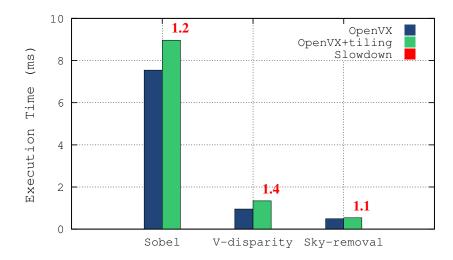

| 6.10 | Obtained Execution Times on OpenVX with OpenMP                                                  |

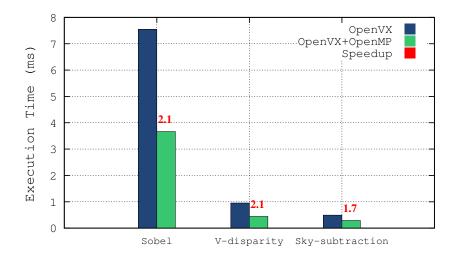

|------|-------------------------------------------------------------------------------------------------|

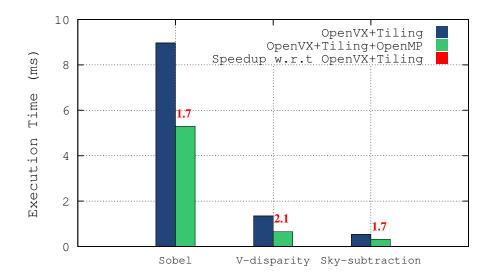

| 6.11 | Accelerating OpenVX Tiling Extension with OpenMP                                                |

| 6.12 | Summary of the Obtained Results with the Different Optimizations Tested                         |

|      | on OpenVX                                                                                       |

| 6.13 | $\mathrm{C}++$ vs OpenVX Obtained Performances on Fixed and Embedded Systems.                   |

| 6.14 | $\mathrm{C}++$ vs $\mathrm{OpenVX}$ vs $\mathrm{NT2}$ Obtained Performances on Fixed and Embed- |

|      | ded Systems                                                                                     |

| 6.15 | OpenMP Parallelization Performances on OpenVX                                                   |

| 6.16 | Execution time (ms) of boost.SIMD Vectorization and OpenMP paral-                               |

|      | lelization on OpenVX                                                                            |

# List of Tables

| 2.1 | CUDA Device Memory Specifications                                        | 30  |

|-----|--------------------------------------------------------------------------|-----|

| 3.1 | KITTI Datasets Specifications                                            | 60  |

| 3.2 | On-road Vehicles Detection Evaluation                                    | 61  |

| 3.3 | Comparison of our Algorithm with other On-Road Vehicles Detection        |     |

|     | Algorithms                                                               | 62  |

| 4.1 | Employed Platforms CPU Specification                                     | 72  |

| 4.2 | SIMD Compiling Options                                                   | 76  |

| 4.3 | SIMD Intrinsics Latency                                                  | 78  |

| 4.4 | $\mathrm{C}++$ Execution Time of CSM with pgc++ Compiling Options vs g++ |     |

|     | on KITTI Dataset                                                         | 90  |

| 4.5 | OpenACC Execution Time of CSM with pgc++ Compiling Options on            |     |

|     | KITTI Dataset                                                            | 91  |

| 4.6 | Execution Time (ms) of CDDL Function (Listing $\boxed{4.5}$ ) with NT2   | 95  |

| 5.1 | GPUs Specifications                                                      | 110 |

| 5.2 | CDD CUDA First kernel results on KITTI(1242x375): GPU execution          |     |

|     | time, Nvprof Metrics and Events                                          | 113 |

| 5.3 | OpenACC Configuration with Kernel Clause                                 | 115 |

| 5.4 | Some nvprof Metrics and Events of OpenACC_0 and OpenACC_1 Kernels        | 117 |

| 5.5 | L1 Cache/Shared Memory Configuration Options on Compute 3.x Devices      | 118 |

| 5.6 | GPUs Memory Specifications                                               | 118 |

| 5.7 | Nvprof Metrics of CDD CUDA Second Kernel with L1 Caching (1242x375)      | 120 |

| 5.8 | CSM and CDD Specifications                                               | 130 |

#### LIST OF TABLES

| 6.1 | Execution Time of Kernel Merge Optimization on Sobel Filter | 52 |

|-----|-------------------------------------------------------------|----|

| 6.2 | Kernels Specifications                                      | 60 |

| 6.3 | Kernels Specifications at arithmetic level                  | 63 |

| 7.1 | Evaluation of Employed Parallel Programming Tools           | 72 |

| A.1 | Evaluation d'Outils de Programmation Parallèle              | 82 |

\_

#### 1

#### Introduction

As reported by the World Health Organization (WHO) in 2015 [2], every year approximately 1.25 million people die as a result of road traffic crash. Between 20 and 50 million more people suffer from non-fatal injuries, with many incurring a disability as a result of their injury. Most of these accidents are attributed to human errors or drivers distractions. Although the big efforts spent since 1990s to develop safety technologies solutions such as airbags, anti-lock brakes, etc, human casualties in the road environment are still too high. To better manage the road traffic and reduce the risk of accidents, new technologies have been proposed, called Advanced Driver Assistance Systems (ADAS), such as the Adaptive Cruise Control (ACC) and the Lane Departure Warning (LDW) systems. ADAS are on-board intelligent systems developed to avoid the risk of accidents and improve road safety by assisting the drivers in their driving tasks. These systems help with monitoring, warning, braking, and steering tasks while driving. The demand of ADAS is expected to increase over the next decade. This is largely requested by regulatory and consumers interest for safety applications that protect drivers and reduce accidents. Indeed, both the European Union and the United States are planing to equip all vehicles with autonomous emergency-braking systems and forward-collision warning systems by 2020.

This research work has been carried out in the framework of the Technological Research Institute SystemX (IRT SystemX), and therefore granted with public funds within the scope of the French Program "Investissements d'Avenir". The IRT SystemX is specialized in digital sciences, it holds collaborative projects bringing together research laboratories and industrial companies. This work is carried out in a project called "Electronique et Logiciel pour l'Automobile" with academic laboratories and automobile

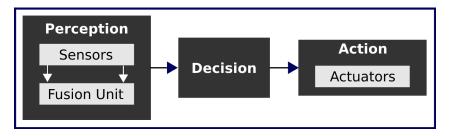

Figure 1.1: Architecture of an ADAS

industrial partners such as: Renault, PSA, Intempora, Continental, Valeo . . . . The project aims to study and investigate the different aspects related to autonomous cars such as security, vision-based ADAS and real time supervisors. My work is involved within the second task "image processing" where we investigate the different parallel programming tools as well the embedding methodologies of ADAS applications.

#### 1.1 Context: Embedding Vision-Based ADAS

An ADAS is considered as complex real time embedded system which consists of three important layers [3], [4] as illustrated in Figure [1.1].

- The *perception* layer includes a set of sensors such as radars and cameras. It may also include a sensor data fusion unit which allows the computation of appropriate sensors data to estimate a consistent state of a vehicle and its environment.

- The *decision* layer uses the data fusion unit outputs to analyze the current situation and to decide the appropriate actions to be transmitted to actuators.

- The *action* layer receives the actions from the decision layer, and either it delivers visual, acoustic and/or haptic warning information to the driver, or it provides automatic actions such as braking.

As depicted in Figure [1.1], the perception layer consists of a set of sensors and a fusion unit. Usually we find passive sensors as cameras, and active sensors such as radars and lidars. Computer vision, together with radar and lidar, is at the forefront of technologies that enable the evolution of ADAS. Radars and lidars offer some advantages, such as long detection range (about 1-200 m), and capability to operate under extreme weather conditions. However, it is vulnerable to false positives, especially around road curves,

since it is not able to recognize objects. Camera-based systems have also their own limitations. They are very affected by weather conditions, and they are not as reliable as radar when obtaining depth information. On the other hand, they have a wider field of view, and more importantly, they can recognize and categorize objects. From cost point of view, cameras are usually cheaper than radars. For all these reasons, modern ADAS applications use sensor fusion to combine the strengths of all these technologies. Normally, a radar or lidar sensor is used to detect potential candidates, and then, during a second stage, computer vision is applied to analyze the detected objects. However, not all applications need sensor fusion, and some applications such as Lane Departure Warning (LDW) or Driver Fatigue Warning (DFW) can rely entirely on a camera-based system.

#### 1.1.1 ADAS Challenges and Opportunities

There are several challenges to design, implement, deploy, and operate ADAS. The system is expected to be *fast* in processing data, *accurately predict* context, and react in *real time*. In addition, it is required to be *robust*, *reliable*, and have *low error* rates. There have been significant efforts and researches to solve all these challenges and to develop the technology that will make ADAS and autonomous driving a reality.

ADAS are considered as hard real-time control systems in the automotive domain. ADAS use a lot of data reported from several sensors. These data must be updated regularly to reflect the current environment state. Thus, these systems need to be managed by real-time database systems in order to store and manipulate real-time data efficiently. However, the design of ADAS is highly complex; it is difficult to model the time constraints related to both data and transactions.

#### 1.1.2 Real-Time ADAS

Computer vision algorithms are traditionally designed to give high accuracy with less focus on speed or execution time [5]. However, ADAS require images to be processed as they are captured so that the car can react quickly to changes. A fast computer vision algorithm has to complete its execution within a predictable time bound so that time spent on one frame does not delay the next frame.

An autonomous vehicle must be as good as or better than a human driver. The average reaction time of an human driver alert is 700 ms [6]. Hence, each ADAS task

must have a runtime that is bounded above by 700 ms. In safety-critical tasks that could prevent the loss of life such as pedestrian detection, the bound should be much lower. In an automotive real-time system, many programs will execute as periodic tasks, with different periods depending on the program's purpose. For example, the vehicles detector **must run as frequently as possible**. When the vehicles detector finishes processing an image it should **immediately** start again processing the newest image from the camera since what it has been processed is already out of date. In system with lower criticality, such as lane departure warning, the period between executions of the task may be much longer.

#### 1.2 Problem Statement

The role of computer vision in understanding and analyzing the driving scene is of great importance in order to build more intelligent driver assistance systems. However, the implementation of these Computer vision-based applications in a real automotive environment is not straightforward. The vast majority of works of the scientific literature test their driver assistance algorithms on standard PCs. When these algorithms are ported to an embedded device, they see their performance degraded and sometimes they cannot even be implemented. Since there are several requirements and constrains to be taken into account, there is a big gap between what is tested in a standard PC and what finally runs in the embedded platform. Furthermore, there is no standard hardware and software for a specific application. Hence, different architectures and programming tools have been proposed by the industry and the scientific community and it is on still non-mature markets.

#### 1.2.1 Challenges of Embedded Image Processing Algorithms

Image processing algorithms combine the challenges of high computing performance and algorithm accuracy to cope with the rapidly rising resolution and frame rate of sensors and the increasing complexity of image processing algorithms.

To understand the challenge of efficient image processing, consider a  $3 \times 3$  box filter implemented as separate horizontal and vertical passes. We might write this in C++ as a sequence of two loop nests. An efficient implementation on a modern CPU requires SIMD vectorization and multi-threading. However, once we start to exploit parallelism,

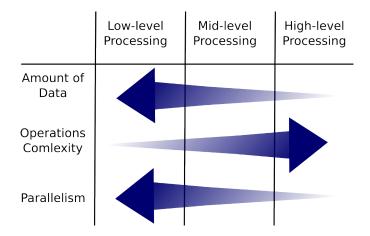

Figure 1.2: Processing Levels Specifications

the algorithm becomes bottlenecked on memory bandwidth. Computing the entire horizontal pass before the vertical pass destroys producer-consumer locality. In other words, horizontally intermediate values are computed before they are consumed by the vertical pass. This doubles the storage and memory bandwidth required. Exploiting locality requires interleaving the two stages by tiling and fusing the loops. Tiles must be carefully sized for alignment, and efficient fusion redundant computing values on the overlapping boundaries of intermediate tiles. At the end, these optimizations allow to accelerate the considered  $3 \times 3$  box filter.

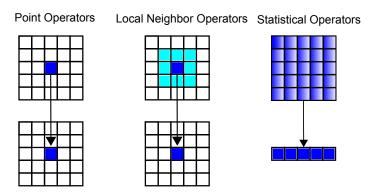

From this simple example, we notice that accelerating image processing algorithms is not a trivial task. In this work, we focus on the real aspect and requirements to embed vision-based ADAS. Obtaining a real time performance on embedded vision is a very challenging task, as there is no hardware architecture that meets perfectly the requirements of each processing level and kernel specifications. From the literature, we distinguish three different processing levels in computer vision applications: low-level, mid-level and high-level . Figure 1.2 illustrates the specifications of each level in terms of parallelism, data amount and complexity.

In low-level processing, we find repetitive operations at pixel level which is then characterized by high level of parallelism. As an example, we may cite simple filters such as edge detectors (Sobel) and noise reduction (Gaussian). These processing are usually optimized through SIMD instructions. In the second processing level—mid-level—, operations are performed on certain region of interest which respond to particular

criteria. This level includes operations such as features extraction, segmentation, object classification and optical flow. This level shows lower parallelism and higher complexity compared to filters. These operations can only be parallelized on high performance architectures such as many-core and GPUs. Finally, the last level includes decision-making operations where sequential processing is present the most of the time.

#### 1.2.2 Hardware Platforms

As discussed previously, computer vision applications deal with an important amount of data requiring high computing performance. Also, a hardware product that is installed inside a vehicle must be embedded and needs to fulfill the requirements of embedded vision systems. Actually, there is no hardware architecture that meets perfectly all the requirements. This section gives an overview of available hardware.

FPGA A Field Programmable Gate Array (FPGA) is an IC designed to be configured by a customer after manufacturing. They have lower power consumption and they are better suited for low-level processing than general purpose hardware, where they clearly outperform them. However, they are not so good for the serial processing necessary in mid and high levels. As FPGAs are dynamically programmable, they can be reconfigured to different applications. For instance, a driver-assistance system might use different applications at day and night, or when driving through tunnels. Rather than have all the algorithms implemented in custom hardware (ASICs) at the same time, an FPGA-based system can select the most suitable algorithm, reconfigure, and continue processing.

**GPU** Graphics Processing Unit (GPU) was initially designed to accelerate the creation of images intended for output to a display and for image rendering tasks. Nowadays, GPUs are also used for general-purpose computing. GPUs have traditionally been considered as power consuming devices and they are not very frequent yet in vehicle applications. However, recent solutions such as the NVIDIA DRIVE PX platform based on the NVIDIA Tegra X1 SoC are very promising.

**DSP** Digital Signal Processors (DSPs) have been the first choice in image processing applications. DSPs offer single cycle multiply and accumulation operations, in addition to parallel processing capabilities and integrated memory blocks. DSPs are very attractive for embedded automotive applications since they offer a good price to performance ratio. However, they require higher cost compared with other options such as FPGAs, and usually, they are not easy and fast to program.

Multi-core Systems Multi-core systems are usually appreciated by car manufactures and suppliers for many reasons. First, existing software of multiple conventional single-core processors can be executed in parallel without any software changes using an appropriate operating system. Second, multi-core systems are at the lower end of the price scale.

Heterogeneous Architectures Each of the previously discussed hardware solutions has some advantages and limitations. For instance, GPUs provide high performance computing but consume an important amount of energy. FPGAs consume less energy but need more time and knowledge to prototype, design and program an application. To cope with this issue and find a better compromise between computing performance, energy efficiency and cost, heterogeneous Systems on Chips (SoCs) have been introduced. Semiconductor manufacturers proposed to integrate two or more processing units with different technologies in the same chip. SoCs are usually cheaper and have higher reliability than multi-chip solutions. Recently there is a growing trend to use System on Chips in embedded vision. As examples, we can cite Texas Instruments (TI) TDAx SoCs (ARM, DSP, EVE) and NVIDIA Tegra X1 (ARM, GPU).

#### 1.2.3 Software Tools

To address vision-based ADAS challenges in embedded systems, several approaches have been presented that introduce an additional layer of abstraction between the developer and the actual target hardware. These approaches aim to cope with the high computation needs and energy efficiency demand of image processing algorithms particularly in terms of real time requirements.

As first approaches, we find extensions to C programming language and libraries or APIs. These approaches allow to keep the original C code. Parallelization is performed

by adding for instance directives to the for loops. OpenMP [11] and OpenACC [12] optimize image processing algorithms via the compiler at the loop level through directives. Both OpenMP and OpenACC can be used on CPUs and GPUs. OpenACC has been initially developed to target different hardwares. However, OpenMP was only supported on CPU-based systems such as multi-core architectures for shared memory parallelization. GPU support is available from OpenMP.4.0 release.

Relevant parallel languages have been proposed in graphics such as CUDA [13] and OpenCL [14]. These languages employ single program multiple data programming model. CUDA can only be used on NVIDIA GPUs. OpenCL is a well known programming environment for both many-core accelerators and GPUs. It is supported by some heterogeneous architectures like Altera FPGA architecture [15]. Like C, they allow the specification of very high performance implementations for many algorithms. But because parallel work distribution, synchronization, kernel fusion, and memory are all explicitly managed by the programmer, complex algorithms are often not adapted to these languages, and the optimizations required are often specific to an architecture, so code must be rewritten for different platforms.

The previous discussed programming languages and libraries are general purpose techniques. However, some domain-specific languages (DSL) for image processing applications exist such as Halide [I6]. Halide is a programming language for image processing algorithms targeting different architectures including x86/SSE, ARM v7/NEON, GPU(CUDA, OpenCL) and Native Client. Halide model is based on stencil pipelines for better locality and parallelism. We find also Numerical Template Toolbox NT2. It is a C++ library-based DSL. It uses generative programming idioms so that architecture features become mere parameters of the code generation process.

There are some compilers which allow automatic parallelization. These compilers examine the for loops to automatically decide sections that can be run in parallel, as well as how many threads to use. As an example, Intel C/C++ compiler icc does this when the option -parallel is enabled. At a glance, the automatic parallelization compiler seems to be the best solution since it does not require the user to do anything, but in reality, as the code becomes more complex, the compiler has difficulty finding what can be parallelized, making the performance suffer. To our best knowledge nowadays (July 2017), no existing compiler (at least no commercial) can auto-generate parallel code for heterogeneous systems such as the accelerator.

#### 1.3 Motivations

Embedding vision-based ADAS applications raised important scientific challenges which were behind the birth of this work. As discussed previously, vision-based ADAS require high performance computing in real time. This led to the design and development of new architectures and new programming languages. Both proposed hardwares and softwares have different features and no one is perfect of a specific application. For instance, GPUs respond to the performance computing requirement of image processing algorithms, but they are considered as power consuming devices. In the other hand, FPGAs consume less power but require more time to design and develop an application based on hardware description languages such as VHDL. From software point of view, high-level techniques such as compiler directives (OpenMP, OpenACC) are easy to use and no code rewriting is required anymore. However, there are some functionalities which are not managed such as shared and texture memory in GPUs. CUDA which is a low-level language support more features and allows the programmer to better optimize the code for instance at different memory levels. However, with CUDA, code rewriting is required.

As a general idea, it is not evident to find the best architecture and parallel language which will respect our constraints particularly in terms of real time requirements. Indeed, things get more complicated in heterogeneous architectures where different computing technologies are employed which may then need different programming techniques.

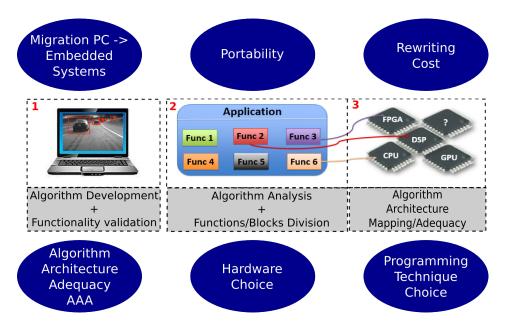

Figure 1.3 illustrates the development process of embedded ADAS as well as the corresponding challenges. Globally, embedding an ADAS application requires **three** major steps. First, after the algorithm specifications are set, the algorithm is developed on a standard fixed platform (PC). The algorithm is then validated at functionality level. Second, before moving to embedded platforms, some analysis of the code is required to determine the bottlenecks—most time consuming functions— and the algorithm is decoupled to small blocks referred as **functions** or **kernels**. Third, porting process can be started by focusing on the previously identified bottlenecks.

During the whole process, the developer meets a set of challenges as illustrated in Figure [1.3] (blue bubbles):

Efficient migration PC → embedded systems While this seems to be straightforward, it is not that evident. With small codes and less algorithm complexity,

Figure 1.3: Embedded ADAS Development Process and Challenges.

developers may port the whole algorithm at once. However, with more complicated algorithm, sometimes it is better to make *progressive* migration. In other words, we port one block (function, kernel) at once. This is a good approach for fast debugging.

- Portability If different architectures are targeted, then the portability becomes a crucial point. Since most of the high-level languages such as CUDA can only be applied to NVIDIA GPUs.

- Rewriting cost This is related to portability. If we use different architectures, we may need different programming languages. Hence, rewriting is required which is a time consuming process which has also a cost at economy level for companies.

- Parallel programming technique(s)' selection As we have seen previously, different parallel programming techniques exist. Each one has its advantages and limitations. The developer needs sometimes to write the algorithm with different techniques to select the best approach at the end.

- Hardware selection At hardware level, there are also a wide choice. Some architectures are designed for energy efficiency purpose as FPGA. Others provides high performance computing as FPGAs.

• Algorithm Architecture Adequacy (AAA) Embedding image processing algorithms may require some adaptations less or more important at algorithmic level to achieve the requirements. A compromise between algorithm quality and speedup is necessary on embedded vision-based applications.

#### 1.4 Research Goals and Contributions

In this thesis, the previously presented challenges are targeted. We focus mainly on the portability issue of vision-based ADAS applications. Portability is related to parallel programming techniques in one hand and to the choice of the hardware in another hand.

In this work, we first propose an algorithm for vehicles detection based on stereo vision [17]. The algorithm is based on disparity map segmentation and objects classifications. It is worth noting that this algorithm has not been developed to compete or to give better performance compared to the existing works in the literature. It has been rather developed to be used as a use-case for our experiments on embedding vision-based algorithms. This algorithm has two important features:

- 1. High performance computing To target the previously discussed challenges, we need to have a time consuming algorithm which needs to be processed in real-time in embedded systems. For this reason, we selected the stereo vision as perception system. Stereo matching is then performed to generate a disparity map. Stereo matching is one of the most studied problems in computer vision. For decades, many stereo matching algorithms have been proposed with new improvements in both matching accuracy and and algorithm efficiency. Most of the proposed works tend to be contradictory in reported results: accurate stereo matching methods are usually time consuming. For this reason, we selected to include stereo matching in our ADAS application.

- 2. Various kernels specifications When parallelizing image processing algorithms, optimizations may differ from one kernel to another. This difference comes from kernels' specifications. By specifications we mean for instance data access pattern, data flow, data dependency, etc. Each feature requires a specific optimization. As an example, let's take Sobel filter. From data access pattern point of view, it is a local neighboring operator. To compute each output pixel, we need the

neighboring pixels of the corresponding input pixel. This feature implies to focus on memory accesses and cache locality for better performance. We developed the algorithm in such a way to have a variety of kernels with different features. This allows us to perform different experiments and test various optimizations.

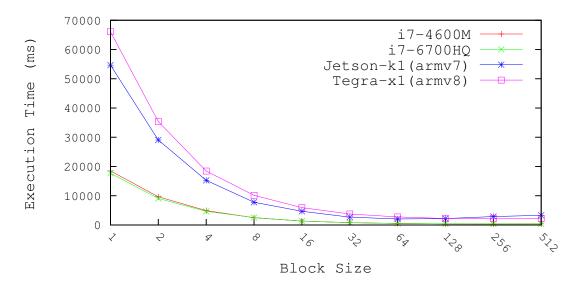

Once the algorithm is developed and validated, we move to the core of this thesis. We start the process of embedding the algorithm. We target different architectures available in the market an we use various parallel programming methodologies. We selected multi-core systems (CPU-based) and NVIDIA platforms; Jetson k1 and Tegra X1 (GPU-based). The choice is based on two important criteria. First, we selected the most available and employed platforms in automobile industry nowadays such NVIDIA platforms. Second, we focus on the stability and the performance of the hardware in one hand and the maturity of the corresponding software in the other hand. For each employed architecture, we introduce its relevant features and then describes their effects on the applied algorithm and the parallelization approaches.

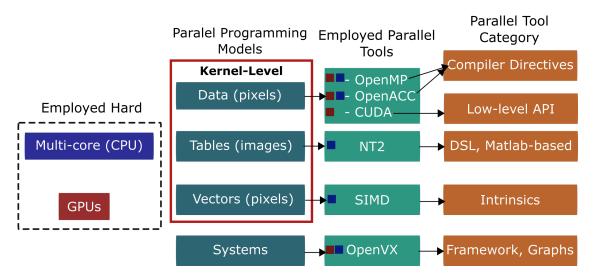

For image processing, the global organization of execution and storage is critical. Image processing pipelines are both wide and deep: they consist of many data-parallel stages that benefit hugely from parallel execution across pixels. However, stages are often memory bandwidth limited; they do little work per load and store. Gains in speed therefore come not just from optimizing the inner loops, but also from global program transformations such as tiling and fusion that exploit producer-consumer locality down the pipeline. In other words, optimizations of vision-based applications fall in two major axes: kernel-level and system-level. By kernel-level optimizations we mean all optimizations that we apply on kernels or small functions. In this case, we usually use traditional parallel languages such as OpenMP, OpenCL, CUDA, etc. With these tools, we only optimize parts of the algorithm. In the second axis-system-level—, we aim to optimize the algorithm as a whole system. This is performed by focusing for instance on data transfers and allocations, memory bandwidth and inter-processor communications. Usually these optimizations are managed through frameworks such as OpenVX.

In this work we target both axes. In the first part, we employ and investigate kernel-level optimizations. We use different parallel techniques such as vectorization and shared memory parallelization. We use also various programming approaches starting from high-level techniques such compiler directives (OpenMP, OpenACC) to low-level

approaches (CUDA). We test different optimizations to accelerate the algorithm on the selected architectures. The best choice of optimization is architecture-specific; implementations optimized for an x86 multicore and for a modern GPU often bear little resemblance to each other. Each optimization is tested with the different programming techniques for evaluating the obtained results at the end. We present the advantages and limitations of each technique. We evaluate the employed approaches in terms of obtained performances and programming productivity.

In the second part, we target the second axis; system-level optimizations. We use OpenVX framework which allows us to apply some system-level optimizations such as kernels fusion and data tiling. We investigate the different proposed optimizations [IS].

In the third part, we propose an approach to target both kernel-level and system-level optimizations [19]. To our best knowledge, this approach has not yet proposed in the literature. We propose to embed customized computer vision kernels on OpenVX framework. We use different techniques to accelerate kernels and then embed them in OpenVX to benefit from its system-level optimizations simultaneously.

The feedback of this research is crucial for the development of future image processing applications in adequacy with parallel architectures with a best compromise between computing performance and algorithm accuracy.

#### 1.5 Thesis Organization

Chapter 2 refers to related works regarding ADAS vision-based acceleration on embedded systems. We enumerate the different programming techniques proposed and employed in the literature.

In chapter 3, we present the use-case we developed and employed in this thesis to perform our experiments. It is an ADAS application which performs vehicles detection based on stereo vision. We present the algorithm in details. A comparison with the state of the art is also provided at the end.

The first part of chapter 4 concentrates on analyzing the algorithm from the execution time point view. We identify the bottlenecks; those functions or part of the code which are the most time consuming in the whole algorithm. After that, we propose to adapt the application at algorithmic level to respond to some features required in parallel computing such regular access pattern. In the second part, we give the first

results of accelerating the algorithm on CPU-based approaches at kernel-level. Different programming techniques are employed which perform either vectorization or shared memory parallelization. At the end of the chapter, we evaluate the obtained results and the contribution as well as the limitation of each programming technique.

In chapter 5, we propose to accelerate the algorithm on GPU-based systems at kernel-level. We propose different optimizations from high priority to low priority according to the complexity of GPUs architectures and memory hierarchy. We use two different approach, a low-level and a high-level technique. We discuss the obtained results, the issues encountered as well as the performance obtained. At the end, we compare the two approaches from different aspects: performance, productivity, limitations, etc.

In chapters 6, we start by investigating the OpenVX framework. We test some system-level techniques such as *kernels fusion* and *data tiling*. We show the relevant features and limitations of each technique. In the second part, we propose a novel approach to accelerate vision kernels at both kernel- and system-level. We propose to integrate accelerated kernels on OpenVX framework to benefit at the same time from the system-level optimizations of this framework. We test the approach on different architectures.

The thesis concludes with a summary of the different contributions and an outlook on potential perspectives.

#### 2

#### State of the Art

Recently Computer Vision (CV) applications have rapidly emerged in the field of autonomous driving. Both algorithm accuracy and execution time are important metrics in designing real-time CV algorithms. Existing CV algorithms usually perform well in one aspect but not good enough in the other. Indeed, researchers and developers focus either on improving accuracy or on code optimization of an existing algorithm. There are two main ways to accelerate the algorithm. The first approach consist in optimizing at algorithmic level by using specific algorithm. In the second approach, we rely on hardware capabilities of some dedicated high performance architectures such as FPGAs and GPUs. In this case, we exploit the performance of these architectures through software optimizations by using specific programming languages or parallel techniques to accelerate the algorithm.

Developing CV algorithms for embedded systems is often severely constrained by the computation requirements and hardware resources of the corresponding systems, as well as the real-time operating conditions. Developers must be able to optimize the performance of their applications within the constraints imposed to the systems. Performance metrics in terms of data processing throughput and accuracy have to be balanced with other optimization objectives, such as code/data size, memory bandwidth, latency, and power consumption. It is a challenging task for embedded developers to be able to map a CV algorithm derived from theoretical research to performance-optimized software that is running in real time on an embedded platform. The author in [20] gives an overview of the different challenges we are faced to when using high performances embedded systems.

#### 2.1 Parallelism Fundamentals

Parallel processing is applied to accelerate computation by sharing the workload among multiple processors. Scientific applications are typically subdivided into two major classes; regular and irregular applications. In regular applications, the data structures used are dense arrays and the accesses to these data structures can be characterized well at compile time. In irregular applications, some of the data structures used may be sparse arrays whose structure can only be determined at the time of program execution.

In terms of algorithm design, parallel computing strategies profits from the natural parallelism present in the algorithm which provides two main resources of parallelism:

- Data parallelism is the simultaneous execution on multiple cores of the same function across the elements of a dataset.

- Task parallelism is the simultaneous execution on multiple cores of many different functions across the same or different datasets.

In image processing and CV algorithms, task parallelism may exist, however, it is data parallelism that can be most efficiently exploited for the following reasons. Firstly, comparing to task parallelism, data parallelism is present more often in image processing algorithms. Secondly, even if task parallelism exists, it only offers limited opportunities for parallelization and speed improvement. Also, the significant increase of image resolution increases the computational requirements of most image processing algorithms rapidly. These high performance requirements can only be compensated by exploiting data parallelism. Consequently, in this thesis, we will focus on exploiting data parallelisms in CV algorithms.

#### 2.2 Embedded Platforms for Vision-based ADAS

Achieving optimal results in terms of speed and accuracy depends both on the algorithm and the hardware platform. Usually, real-time image processing algorithms with low errors compared to the ground truth are characterized by heavy computations. One promising direction to achieve real-time processing in high performance computing applications such as image processing would be to exploit the computing performance and parallelism in some dedicated architectures.

Nowadays, there are different types of parallel computers which have been built or proposed. These architectures can be classified differently based on several aspects. One important feature is whether or not the parallel machine has a *single shared memory*. In a shared memory machine, all of the processors read from and write to a single common memory. This memory is connected to the processors through an interconnection network. In a non-shared memory computer, we rather find processors which have private local memories, and an interconnection network is used for communication. Usually, the shared memory parallel machines are easier to program since the user does not care about or perform any communication operation. However, the non-shared memory parallel computers are generally more efficient because local data accesses do not go through an interconnection network. Also, the programmer performs communication operations in the most efficient manner possible.

Another important feature to classify parallel machines is whether it operates in a Single Instruction Multiple Data Stream (SIMD) or Multiple Instruction Multiple Data Stream (MIMD) mode. In MIMD mode, the machine has the ability to process different instructions on different data simultaneously. In other words, the cores can process multiple tasks at the same time, and the system is designed to exploit task parallelism. Each core is considered as a fully functional single core processor. Hence, they are completely compatible with sequential programs for single core processors. In the other hand, the SIMD architecture aims to exploit only the data parallelism by executing the same instruction on the multiple data streams simultaneously. Since all the cores or the Processing Elements (PEs) share the same instruction at the same time, SIMD processors have significantly lower hardware complexity than MIMD processors. Hence, it is easily possible to find more PEs in SIMD processors that in MIMD processors. This results in a significant speed improvement when exploiting data parallelism with SIMD. However, the greater data-parallelism the SIMD processors are designed to exploit, the more hardware limitations the processors will have. As a result, processors designed to utilize the data parallelism usually are incompatible with programs or algorithms designed for sequential processors.

#### 2.2.1 Multi-cores

One of the most important innovation in computer engineering has been the development of *multi-core* processors. They are composed of two or more cores in a single physical package. Today, many processors, including Digital Signal Processors (DSPs) and Graphical Processing Units (GPUs) (21) have a multi-core design, driven by the demand of higher performance. CPU vendors have changed strategy away from increasing the raw clock rate to adding on-chip support for multi-threading by increasing the number of cores; dual-, quad- and many-core are now commonplace. Signal and image processing developers can benefit dramatically from these advances in hardware, by modifying single-threaded code to exploit parallelism to run on multiple cores. Also, one important reason of using multi-core machines is the presence of a shared memory. This decreases significantly the cost of data transfers and inter-cores communication. However, a coherence protocol is required to ensure that the data read by a processor is consistent. It also provides a set of rules to keep the data in the cache of a processor consistent. Another reason to use multi-core processors is the programming facility at software-level based on some extensions to traditional programming languages such as C. This allows the programmer to benefit from the computing performances of multicore processors with less programming efforts. These extensions will be discussed in the next section.

Different works have been proposed in the literature to implement ADAS applications on CPU-based multi-core systems. In [22], the authors presented a vision-based vehicle detection and tracking pipeline. An approach based on smartphone cameras is employed which supposes a versatile solution and an alternative to other expensive and complex sensors on the vehicle, such as LiDAR and radars. The algorithm runs at 7.6 fps (frames per second) on iPhone 5, 13.2 fps on iPhone 6 and 62.5 fps on a simulator with Intel i7 processor. The authors in [23] presented an implementation of a traffic sign detection system on a multi-core processor. The whole system can run at 25 fps on the multi-core processor, where 10 worker threads are used. In [24], a pedestrian detection algorithm was implemented on multi-core work station with Intel processor. The experimental results showed a speedup ranging from 2 to 4.

## 2.2.2 GPUs

GPUs were initially developed to perform graphical calculations. In 2006, most GPUs were designed based on a graphic pipeline model. The inputs were geometric primitives which are processed through several stages such as vertex operations and composition to give a final image [25]. Each element of this pipeline is processed by a separate

hardware computing unit and multiple copies of the pipeline were printed on a GPU. This allows the execution of thousands of operations simultaneously to produce images as outputs in the screen.

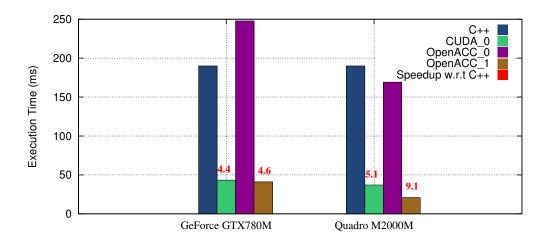

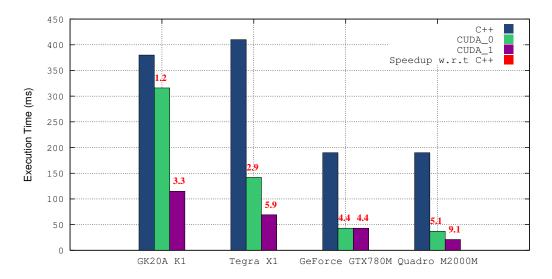

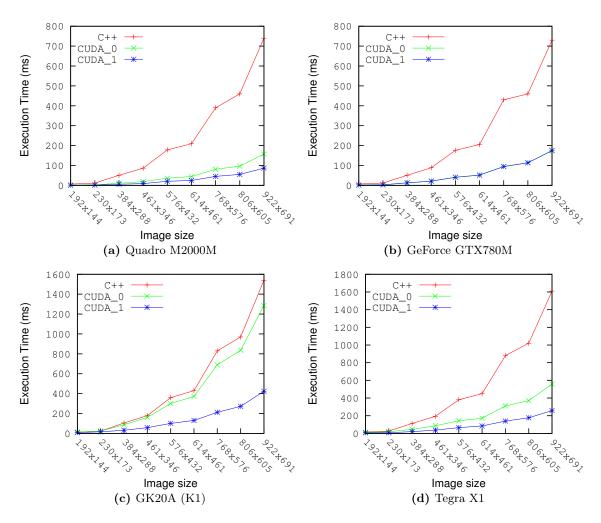

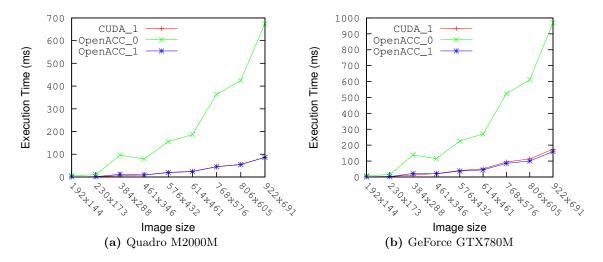

The success of GPUs in graphics led to extend their application to more general purpose applications. General Purpose GPUs (GPGPUs) are considered as a more generalized hardware which makes them suitable for a wide range of algorithms. They are increasingly used in scientific supercomputers and other high performance applications [26]. As applications in general require more and more computation capabilities, GPUs are increasingly implemented in mobile phones, tablets and other low cost devices.