# An AC-DC Topology Based on an Interleaved Modular Multilevel Converter Feasible to Solid-State Transformer Applications

Davi Rabelo Joca

## ▶ To cite this version:

Davi Rabelo Joca. An AC-DC Topology Based on an Interleaved Modular Multilevel Converter Feasible to Solid-State Transformer Applications. Other. Université Paris Saclay (COmUE); Universidade federal do Ceará, 2019. English. NNT: 2019SACLC010. tel-02043239

# HAL Id: tel-02043239 https://theses.hal.science/tel-02043239

Submitted on 20 Feb 2019

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# An AC-DC Topology Based on an Interleaved Modular Multilevel Converter Feasible to Solid-State Transformer Applications

Thèse de doctorat de l'Université Paris-Saclay et l'Universidade Federal do Ceará, préparée à la CentraleSupélec

École doctorale n°575 Electrical, Optical, Bio: Physics and Engineering (EOBE) Spécialité de doctorat: Génie Électrique

Thèse présentée et soutenue à Fortaleza, le 11 janvier 2019, par

# Davi Rabelo Joca

#### Composition du Jury:

Montiê Alves Vitorino

Professor Adjunto, Universidade Federal de Campina Grande Président/Rapporteur

Bruno Francois

Professeur, École Centrale de Lille Rapporteur

Gustavo Alves de Lima Henn

Professor Adjunto, Univ. da Integ. Intern. da Lusofonia Afro-Brasileira Examinateur

Tobias Rafael Fernandes Neto

Hardware Architect, Valeo Siemens automotive germany GmbH Examinateur

Luiz Henrique Silva Colado Barreto

Professor Associado, Universidade Federal do Ceará (GPEC) Directeur de thèse

Jean-Claude Vannier

Professeur, CentraleSupélec (GeePs)

Directeur de thèse

Demercil de Souza Oliveira Jr.

Professor Associado, Universidade Federal do Ceará (GPEC) Co-Directeur de thèse

Loïc Quéval

Professeur Assistant, CentraleSupélec (GeePs)

Co-Directeur de thèse

RÉSUMÉ DE LA THÈSE

Ce travail concerne l'étude et la réalisation d'une topologie de convertisseur d'électronique de

puissance inspirée du convertisseur multiniveau modulaire, et intégrant un entrelaçage et un

transformateur moyenne fréquence.

Le réseau électrique actuel a été initialement conçu pour assurer des transferts de puissance

unidirectionnels, avec des dispositifs de protection spécifiques. Les transformateurs y jouent un

rôle essentiel pour le réglage du niveau de tension et l'isolation galvanique.

Le futur système électrique devra lui se réinventer. En effet, la connexion de nouvelles unités

de production décentralisée (éolien, solaire), de nouveau dispositifs de stockage (batteries) et

de nouveaux types de charge (véhicules électriques) implique des transferts de puissance

bidirectionnels. De plus, le développement des réseaux à courant continu (CC) et leur

connexion avec le réseau à courant alternatif (CA) actuel à différent niveaux (transport,

distribution) est un défi majeur. Le transformateur devra lui aussi évoluer pour offrir de

nouvelles fonctionnalités : conversion CA-CC, réglage dynamique de la tension, protection, etc.

Le transformateur d'électronique de puissance (TEP) peut apporter cette flexibilité.

Parmi plusieurs topologies pour les applications TEP, le convertisseur multiniveau modulaire

(CMM) est déjà reconnu dans l'industrie comme étant une solution adaptée aux applications de

moyenne et haute tension. Plusieurs caractéristiques contribuent à son adoption, telles que sa

fiabilité et son faible taux de distorsion harmonique. D'autre part, des topologies utilisant des

transformateurs d'interphase ou un transformateur moyenne fréquence sont de plus en plus

plébiscitées car elles présentent des avantages en termes de réduction des pertes par conduction,

de poids et de volume et donc de coût par rapport aux topologies utilisant des transformateurs

50-60 Hz conventionnels.

Dans ce contexte, il est proposé ici d'associer un convertisseur multiniveau modulaire entrelacé

et un transformateur d'isolation moyenne fréquence. Cette topologie présente les avantages

combinés des CMMs, des convertisseurs à transformateurs d'interphase et des convertisseurs à

transformateur moyenne fréquence. Elle pourrait être utilisée comme étage CA-CC d'un

transformateur d'électronique de puissance, l'objectif étant la connexion directe entre un réseau

alternatif moyenne tension et un réseau continu basse tension.

La structure du convertisseur proposé est divisée en deux parties: haute tension et basse tension.

Du côté haute tension, le convertisseur est connecté à un réseau CA haute tension. Le courant

est partagé entre deux branches d'un CMM par un transformateur d'interphase. Cet entrelaçage

permettrait la réduction des pertes par conduction dans les interrupteurs. Chaque branche du

CMM est composée de deux bras composés chacun de N modules connectés en série et d'une

bobine de bras. Chaque module est composé d'un demi-pont d'IGBT et d'un condensateur. Les

bobines de bras ont pour tâche de limiter les courants de défaut ainsi que le courant de

circulation. Un transformateur moyenne fréquence (TMF) connecte les points milieux des

branches de CMM au côté basse tension. Le transformateur fournit l'isolation galvanique. Du

côté basse tension, un convertisseur de pont complet est connecté à un condensateur et au réseau

CC basse tension.

A partir du modèle mathématique du côté haute tension, un circuit électrique simplifié

équivalent a été obtenu. On montre qu'il est possible de contrôler à la fois la tension côté CA à

50-60 Hz et la tension primaire du TMF à 10 kHz grâce à une modulation vectorielle spatiale

adaptée des bras du CMM. Ce point constitue la première originalité du travail.

Comme dans tout convertisseur multiniveau modulaire, l'équilibrage de la tension des

condensateurs des modules est nécessaire à son bon fonctionnement. Il a été démontré que le

courant de circulation pouvait être minimisé en jouant sur le nombre de modules actifs. De cette

manière, l'équilibrage de la tension des condensateurs et la minimisation du courant de

circulation sont combinés dans un seul algorithme. Ce point constitue une autre originalité du

travail.

Du côté basse tension, une modulation de largeur d'impulsion (MLI) avec élimination sélective

d'harmonique a été choisie. Elle vise à supprimer la composante harmonique de troisième ordre

(et ses multiples), ce qui permet de réduire la tension efficace et le courant efficace du TMF.

Les fonctions de transfert du convertisseur ont été obtenues par modélisation. Du côté haute

tension, une structure de contrôle PI en cascade avec une boucle de courant interne et une

**Université Paris-Saclay**

Espace Technologique / Immeuble Discovery Route de l'Orme aux Merisiers RD 128 / 91190 Saint-Aubin, France boucle de tension externe a été adoptée. La synchronisation des tensions est obtenue à l'aide

d'une Phase-Locked Loop (PLL). La commande contrôle la phase du courant d'entrée et la

tension du bus CC (contrôle Vdc-Q). Du côté basse tension, la théorie du gyrateur a été utilisée.

La commande contrôle la tension côté CC en régulant l'angle de déphasage entre la tension

primaire et la tension secondaire du MFT. Cet angle peut être positif (mode redresseur) ou

négatif (mode inverseur). Les deux contrôleurs sont indépendants mais permettent de

commander à la fois le flux de puissance active (côté CC et côté CA), la puissance réactive du

côté CA et la tension du bus CC.

A partir de la modélisation mathématique du convertisseur et de l'analyse de la modulation, le

nombre optimal de modules et le rapport optimal de transformation du TMF ont été calculés.

Pour cette dernière analyse, le nouveau concept de rapport cyclique effectif a été présenté pour

obtenir les équations de tension du transformateur. De plus, le comportement de la tension

primaire du TMF, en termes de valeur efficace et de distorsion harmonique totale, a été évalué.

Ces informations sont importantes pour dimensionner les éléments du convertisseur.

Une première validation de la topologie proposée a été menée par simulation. Pour un

convertisseur triphasé de 100 kW, le schéma de conception a pu être vérifié et le cahier des

charges a été respecté. En particulier, on a montré que les règles pour la connexion d'un réseau

CC basse tension à un réseau CA moyenne tension, normalisées par la norme IEEE STD 519-

2014, sont respectées en régime permanent et en régime dynamique. Des simulations en régime

dynamique (inversion du flux de puissance) ont démontré la bidirectionnalité du convertisseur

et la stabilité du schéma de contrôle proposé.

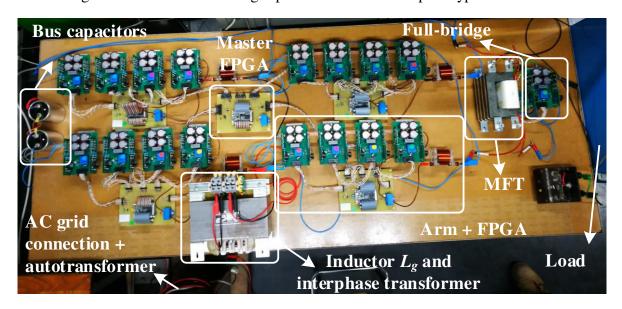

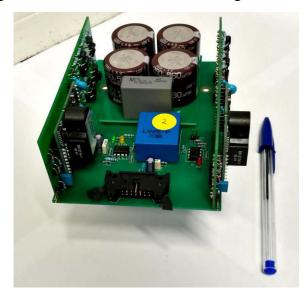

Une seconde validation de la topologie proposée a été faite en développant un prototype de

convertisseur monophasé de 720 W. Le prototype a été conçu et construit au laboratoire GeePs

(Group of Electrical Engineering - Paris) en France, lors du séjour de cet auteur dans le cadre

d'un partenariat entre le Brésil et la France (financement Erasmus Mundus Smart<sup>2</sup>). Plusieurs

contraintes comme la disponibilité des matériaux, le délai de fabrication, les compétences

techniques des techniciens et le budget ont été rencontrées pour élaborer les paramètres et les

spécifications du convertisseur.

Université Paris-Saclay

Espace Technologique / Immeuble Discovery Route de l'Orme aux Merisiers RD 128 / 91190 Saint-Aubin, France

Pour ce prototype, chaque bras est composé de quatre modules pont complet. Chaque module

est composé de deux drivers et de ses composants auxiliaires, d'un module IGBT en pont

complet, d'un capteur de tension, d'un circuit de protection contre les surtensions et d'un circuit

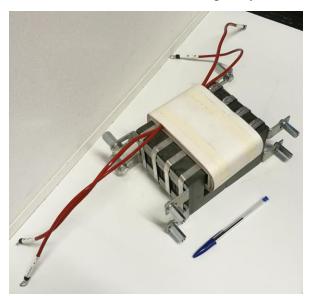

de protection contre la surchauffe. Le transformateur d'interphase et le transformateur moyenne

fréquence ont été dimensionnés en interne puis fabriqué par un prestataire externe.

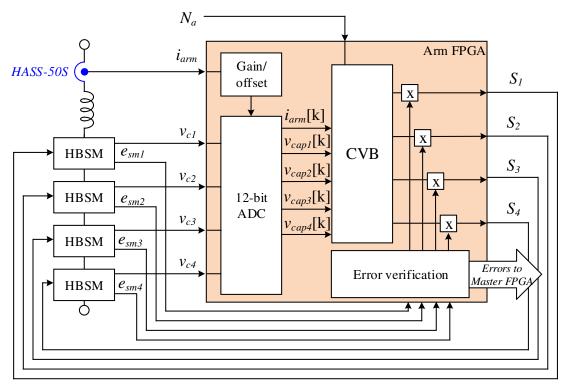

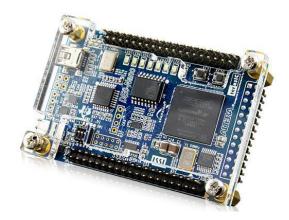

Chaque bras est contrôlé par un FPGA (Field Programmable Gate Array) dont les tâches sont

la vérification des erreurs, la mesure du courant du bras, et la mesure et l'équilibrage de la

tension des condensateurs des modules.

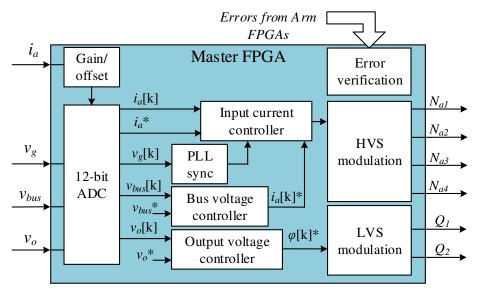

Un FPGA maître gère les quatre FPGAs de bras. Il a trois modes de fonctionnement : mode

d'initialisation, mode de charge des condensateurs des modules et mode stationnaire. En mode

stationnaire, le FPGA maître contrôle en boucle ouverte ou en boucle fermée le courant d'entrée,

la tension de bus et la tension de sortie. Il communique uniquement le nombre de modules à

activer à chaque FPGA de bras.

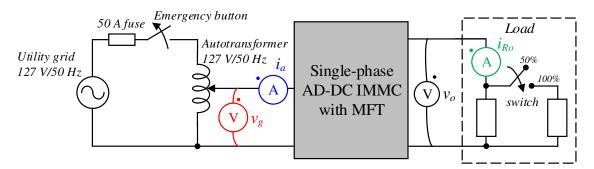

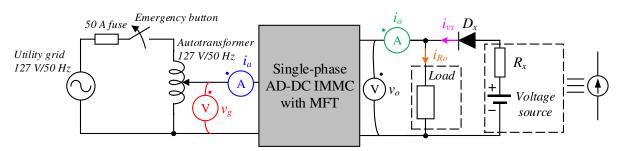

Pour vérifier le fonctionnement du convertisseur, quatre types de tests ont été effectués :

opération en régime permanent avec contrôle en boucle ouverte, opération en régime permanent

avec contrôle en boucle fermée, opération en régime dynamique avec contrôle en boucle fermée

pour une commutation de charge, et opération en régime dynamique avec contrôle en boucle

fermée pour une inversion du flux de puissance.

Malgrès certaines difficultés, les résultats expérimentaux montrent que le convertisseur

fonctionne comme prévu. Ces problèmes étaient du aux transformateur d'interphase et

transformateur à moyenne fréquence, qui s'est révélé difficile à concevoir et à construire et,

également, leurs inductances de fuite qui ne devait pas être aussi élevée. Le système de contrôle

a dû être recalculé pour ajuster le fonctionnement du convertisseur pendant les tests avec

contrôle en boucle fermée. En outre, quelques bruits ont été obtenus lors des mesures. Le

système de contrôle a dû être recalculé pour ajuster le fonctionnement du convertisseur pendant

les tests avec contrôle en boucle fermée et des filtres numériques ont été ajoutés dans le code

de programme du FPGA.

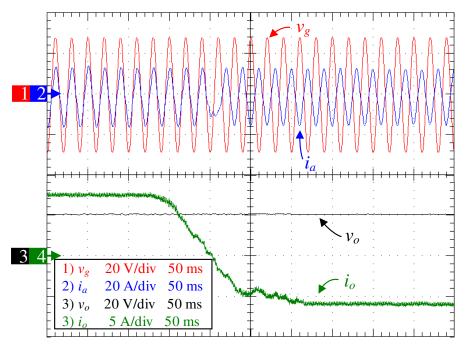

En particulier, les tensions (réseau CA, condensateurs, transformateur et réseau CC) et les

courants (réseau CA, transformateur, réseau CC) correspondent aux résultats de la simulation.

Les tests en régime dynamique (inversion du flux de puissance) ont démontré la

bidirectionnalité du convertisseur et la stabilité du schéma de contrôle proposé.

De cette façon, l'étude a démontré la possibilité d'utiliser des solutions nécessitant des

transformateurs d'électronique de puissance, tels qu'un étage CA-CC, pour la connexion entre

les réseaux de distribution et les microgrilles à courant continu. Le convertisseur proposé

présentait les caractéristiques nécessaires à cette type de application et respectait les

recommandations des normes brésiliennes et internationales.

Comme travaux futurs, il est suggéré d'étudier le convertisseur proposé en configuration «

back-to-back ». Une telle topologie pourrait être intéressante pour les transformateurs

d'électronique de puissance CA-CA. Pour tenter de réduire davantage l'encombrement du

convertisseur, on pourrait envisager d'utiliser une MFT triphasée au lieu d'une MFT par phase.

La conception et la réalisation de transformateurs à moyenne fréquence se sont révélées

difficiles et, par conséquent, une telle topologie nécessiterait probablement une étude détaillée

de le transformateur moyenne fréquence seule.

.• O

#### LIST OF ABBREVIATIONS AND ACRONYMS

AC Alternating Current

ANEEL Agência Nacional de Energia Elétrica

CCM Circulating Currents Minimization

CHB Cascaded H-Bridge

CVB Capacitors Voltage Balancing

DC Direct Current

DSP Digital Signal Processor FBC Full-Bridge Converter

FC Flying Capacitor

FPGA Field-Programmable Gate Array

HBSM Half-Bridge Submodule

HV High Voltage

HVAC High Voltage Alternating Current

HVDC High Voltage Direct Current

HVS High-Voltage Side

IEEE Institute of Electrical and Electronics Engineers

IMMC Interleaved Modular Multilevel Converter

LV Low Voltage

LVAC Low Voltage Alternating Current

LVDC Low Voltage Direct Current

LVS Low-Voltage Side

MFT Medium-Frequency Transformer

MIT Massachusetts Institute of Technology

MMC Modular Multilevel Converter

MV Medium Voltage

MVAC Medium Voltage Alternating Current

MVDC Medium Voltage Direct Current

M<sup>2</sup>LC Modular Multi Level Converter

NPC Neutral-Point Clamped

PI Proportional Integrator

PRODIST Procedimentos de Distribuição de Energia Elétrica no Sistema Elétrico

Nacional

RMS Root Mean Square

SHE-PWM Selective Harmonic Elimination Pulse-Width Modulation

SST Solid-State Transformer

STATCOM Static Synchronous Compensators

THD Total Harmonic Distortion

THDi Current Total Harmonic Distortion

THDv Voltage Total Harmonic Distortion

ZCS Zero Current Switching

ZVS Zero Voltage Switching

# LIST OF CONTENTS

| 1     | INTRODUCTION                                                       | 11 |

|-------|--------------------------------------------------------------------|----|

| 1.1   | Context                                                            | 11 |

| 1.2   | SST concepts                                                       | 13 |

| 1.3   | SST topologies for DC power distribution systems                   | 16 |

| 1.4   | Motivation and constraints                                         | 21 |

| 1.5   | Thesis objectives                                                  | 21 |

| 1.6   | Outline                                                            | 22 |

| 2     | PROPOSED TOPOLOGY                                                  | 23 |

| 2.1   | Structure                                                          | 23 |

| 2.2   | Principle of operation                                             | 26 |

| 2.3   | HVS Modeling                                                       | 28 |

| 2.3.1 | Leg mid-point voltages $v_{xn}$ and $v_{yn}$                       | 29 |

| 2.3.2 | Input voltage van and MFT primary voltage vp                       | 30 |

| 2.3.3 | Bus voltage v <sub>bus</sub>                                       | 33 |

| 2.4   | HVS modulation technique                                           | 34 |

| 2.5   | LVS modulation technique                                           | 36 |

| 62.6  | Capacitors voltage balancing and circulating currents minimization |    |

|       | algorithm                                                          | 37 |

| 2.7   | Control scheme                                                     | 39 |

| 2.7.1 | HVS plant                                                          | 39 |

| 2.7.2 | LVS plant                                                          | 41 |

| 2.7.3 | HVS and LVS control scheme                                         | 43 |

| 2.8   | Final comments                                                     | 45 |

| 3     | CONVERTER ANALYSIS, DESIGN AND SIMULATION                          | 46 |

| 3.1   | Converter analysis                                                 | 46 |

| 3.1.1 | Optimum number of submodules per arm $N_{opt}$                     | 46 |

| 3.1.2 | Optimum transformer turns ratio k <sub>opt</sub>                   | 49 |

| 3.1.3 | RMS value and THD of the voltage v <sub>t</sub>                    | 53 |

| 3.1.4 | Losses                                                             | 55 |

| 3.2   | Design                                             | 55  |

|-------|----------------------------------------------------|-----|

| 3.2.1 | Input inductor $L_g$                               | 56  |

| 3.2.2 | Arm inductor L                                     | 57  |

| 3.2.3 | Submodule capacitor C                              | 58  |

| 3.2.4 | Bus capacitors $C_{b1}$ and $C_{b2}$               | 60  |

| 3.2.5 | Medium-frequency transformer                       | 60  |

| 3.2.6 | Output capacitor C <sub>o</sub>                    | 61  |

| 3.3   | Simulation                                         | 61  |

| 3.3.1 | Steady-state operation                             | 62  |

| 3.3.2 | Power flow inversion operation                     | 66  |

| 3.4   | Final comments                                     | 67  |

| 4     | EXPERIMENTAL VALIDATION                            | 69  |

| 4.1   | Prototype specifications and overview              | 69  |

| 4.1.1 | Overview of the prototype                          | 71  |

| 4.1.2 | Overview of one submodule                          | 74  |

| 4.1.3 | Overview of the arm FPGA                           | 75  |

| 4.1.4 | Overview of the master FPGA                        | 77  |

| 4.2   | Experimental results                               | 78  |

| 4.2.1 | Steady-state operation                             | 78  |

| 4.2.2 | Dynamic operation                                  | 82  |

| 4.3   | Final comments                                     | 85  |

| 5     | CONCLUSIONS                                        | 86  |

| 5.1   | Scientific production                              | 87  |

| 5.1.1 | Proceedings papers                                 | 88  |

| 5.1.2 | Journal papers                                     | 88  |

|       | REFERENCES                                         | 9(  |

|       | APPENDIX A – HVS PLANT IN ROTATING REFERENCE FRAME | 99  |

|       | APPENDIX B – SIMULATION SCHEMATICS AND PARAMETERS  | 100 |

#### 1 INTRODUCTION

#### 1.1 Context

In the last decade, the smart grids topics are attracting a considerable interest from academia and industry. Researchers recognize this technology as an improvement of the three main stages that constitute the power system scheme (generation, transmission and distribution), contributing to the increase of its reliability and efficiency. The future electric system considers the new resources and load characteristics, such as energy storage systems (batteries, supercapacitors, etc.), renewable energy sources (photovoltaic panels, wind turbines, etc.), electric vehicles and electronic loads (TVs, LED lights, computers, etc.) (JHUNJHUNWALA; LOLLA; KAUR, 2016) (NORDMAN; CHRISTENSEN, 2016).

Within the current power system architecture, the power transformers play a key role with the galvanic isolation and the voltage level adjustment. This voltage may subsequently be reduced to distribution voltage levels for industrial, commercial and residential purposes (SHE *et al.*, 2013). In Brazil, the connection of AC (alternating current) distributed generation to the utility grid is regulated by the PRODIST norm, from the National Agency of Electric Energy - ANEEL (2016, p. 30). The PRODIST - Module 3 norm states that the distribution voltage levels are divided into:

- High-voltage (HV): 69 kV or 138 kV;

- Medium-voltage (MV): 13.8 kV or 34.5 kV;

- Low-voltage (LV): 127 V to 440 V.

Also, the PRODIST - Modules 3 and 8 norms regard to the connection proceedings and the energy quality, respectively, which state that for a generator with 75 kW or higher (ANEEL, 2016, p. 38):

- The connection must be made to the three-phase low-voltage AC grid (220 V or 380 V) or to the medium-voltage AC grid (13.8 kV);

- The connection point voltage must respect the nominal voltage limits ( $V_n$   $\pm 5\%$ )

- A coupling transformer must be used;

- When in islanded mode operation, both voltage and frequency at the connection point must be controlled;

- The power factor at the connection point must be higher than 0.92 (inductive or capacitive);

- The voltage total harmonic distortion (THD<sub>v</sub>) must be between the limits described in Table 1.1 (ANEEL, 2017, p. 15).

Table 1.1 – Limits for THD (% of the fundamental voltage).

| Parameters           | Nominal voltage (V <sub>n</sub> ) |                                               |                                            |  |  |

|----------------------|-----------------------------------|-----------------------------------------------|--------------------------------------------|--|--|

| 1 ar ameters         | $V_n \le 1 \text{ kV}$            | $1 \text{ kV} < V_{\text{n}} < 69 \text{ kV}$ | $69 \text{ kV} \le V_n \le 230 \text{ kV}$ |  |  |

| $THD_{v}$            | 10%                               | 8%                                            | 5%                                         |  |  |

| ${}^{*}THD_{v,even}$ | 2.5%                              | 2%                                            | 1%                                         |  |  |

| $^{**}THD_{v,odd}$   | 7.5%                              | 6%                                            | 4%                                         |  |  |

| $^{***}THD_{v,3}$    | 6.5%                              | 5%                                            | 3%                                         |  |  |

<sup>\*</sup>All even-order harmonics, non-multiple of 3.

Source: PRODIST – Module 8 norm – ANEEL (2017, p. 15).

Also, according to the recommended requirements for harmonic control in electrical systems, IEEE STD 519-2014 (2014, p. 7), the generators must meet the current total harmonic distortion (THD<sub>i</sub>) limits for the grid connection, as shown in Table 1.2. In this standard, each current harmonic component should be measured and limited (suppressed in Table 1.2).

Table 1.2 – Limits for THD<sub>i</sub> (% of the fundamental frequency component).

| Parameters          | Nominal voltage (V <sub>n</sub> )                     |                                          |                         |  |

|---------------------|-------------------------------------------------------|------------------------------------------|-------------------------|--|

| 1 ur unicters       | $120 \text{ V} < \text{V}_{\text{n}} < 69 \text{ kV}$ | $69 \text{ kV} < V_n \le 161 \text{ kV}$ | 161 kV < V <sub>n</sub> |  |

| *THD <sub>i,1</sub> | 5%                                                    | 2.5%                                     | 1.5%                    |  |

| $**THD_{i,2}$       | 20%                                                   | 10%                                      | 3.75%                   |  |

<sup>\*</sup>Scenario when short-circuit current is up to 20 times the nominal current.

Source: IEEE STD 519-2004 (2014, p. 7-9).

For the connection of DC (direct current) microgrids to the utility grid, there is no norm yet, but it is expected that a similar regulation will be applied.

<sup>\*\*</sup>All odd-order harmonics, non-multiple of 3.

<sup>\*\*\*\*</sup>All order harmonics multiple of 3.

<sup>\*\*</sup>Scenario when short-circuit current is higher than 50 times the nominal current.

13

The development trends of traditional low-frequency power transformers aim to

improve their aspects related to material engineering, insulation, and manufacturing processes,

while taking into account economic and environmental factors (SHE et al., 2013)

(RODRIGUEZ et al., 2017). Since the transformer frequency of operation is inversely

proportional to its volume, the trend is to increase the frequency. According to its frequency

operation, the transformers can be classified as follows (KOLAR; ORTIZ, 2014):

• Low-frequency: below 1 kHz

Medium-frequency: 1 kHz to 100 kHz

• High-frequency: higher than 100 kHz

The advance of the power devices and power electronics brought back once again

the attention for the use of DC power distribution in modern power systems, which could be

highly convenient along with the AC power distribution systems. Focusing on the microgrids,

one of good advantages of using DC power distribution is the elimination of unnecessary power

conversion stages, which increases the overall efficiency. Besides that, the absence of reactive

power and the lack of synchronization makes the system more efficient and simple to control

(RODRIGUEZ-DIAZ et al., 2016) (SHE et al., 2012).

The connection of distributed generations between AC and DC distribution lines

places a great challenge on the control and protection system (HUANG, 2016). Firstly, the

galvanic isolation and the voltage level adjustment are mandatory features. Therefore, there is

a strong need to provide technology which can manage the power and allow an easy connection.

In order to achieve this, it is necessary to have a reliable and fast voltage control in the network

(ZHAO et al., 2013). One of the options is the solid-state transformer (SST) technology.

1.2 SST concepts

The solid-state transformer (BOWERS et al, 1980), also called "intelligent

universal transformer" (LAI et al., 2005) or "electronic transformer" (BIFARETTI et al., 2011),

is considered to be the evolution of the traditional power transformer. Recognized as one of the

ten most emerging technologies by the Massachusetts Institute of Technology (MIT)

Technology Review in 2010 (SHE; HUANG; BURGOS, 2013), its oldest conception was

presented by McMurray (1970).

Currently, there isn't a standard conceptual definition concerning the SST

configurations, but they are mostly considered as an AC-AC conversion device. However,

Falcones, Ayyanar and Mao (2013), Qin and Kimball (2014), Rodriguez *et al.* (2017), Huber *et al.* (2017), Barreto *et al.* (2018), and other authors classify the SST as a multistage topology, *i.e.*, a structure with one or more conversion stages (AC-DC, DC-DC, DC-AC or AC-AC) followed by galvanic isolation and voltage level adjustment features. This is important to mention because some AC-DC SST topologies are applied in DC power distribution applications, as well as tractions auxiliary supplies and data-centers applications (HUBER *et al.*, 2017).

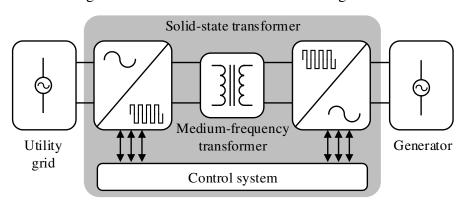

The SST includes a set of semiconductor components, a medium to high-frequency transformer and a control system, as an example shown in Figure 1.1. The SST has the same basic function than a traditional transformer: raise or reduce AC voltage levels and galvanic isolation. However, it has several advantages (TATCHO; JIANG; LI, 2011) (QIN; KIMBALL, 2013) (HUBER; KOLAR, 2014) (ZHAO *et al.*, 2017):

- Both input and output terminals can operate in direct current or alternating current;

- The voltage, current and frequency levels can be actively modified, so that it allows for bidirectional power flow control;

- Reactive energy compensation and active harmonic filtering can provide high quality voltage waveforms and improve the processed energy;

- Voltage drops and fault current limitation can be regulated by means of the control and protection system;

- The direction of the energy of any source (the concessionaires, the consumer and other transformers in the grid) to any destination can be managed by the most efficient possible route;

Figure 1.1 – Solid-state transformer configuration.

Source: author's right.

- The operating frequency is rated at the order of tens of kilohertz, thus, its intrinsic dimensions are greatly reduced if compared to their conventional counterparts;

- The control system allows dynamic and stable operations, managing the flow of energy between DC and AC energy systems, in medium-voltage and lowvoltage (LV) generation centers and loads.

Therefore, these SST features are clearly adequate to the context of power distribution systems and smart grids.

With these features, some studies suggest that when SSTs will be implemented, the manner how electricity is distributed will be radically modified, and the SSTs will become key components in the future smart grids (DRAGIČEVIĆ, 2016).

One example is shown in Figure 1.2, which presents a smart grid architecture with an AC-DC SST. The energy flow is managed between the MVAC (Medium-Voltage Alternating Current) and LVDC (Low-Voltage Direct Current) grids, allowing generation centers and load characteristics to work together. Also, through an inverter, the common LVAC (Low-Voltage Alternating Current) grids can still be connected to the smart grid (WANG *et al.*, 2013).

Utility grid Electric Windpower verhicles generation **MVAC** LVDC AC-DC Photovoltaic **SST** generation Inverter **Batteries** LVAC DC loads

Buildings

Figure 1.2 – Example of an AC-DC SST applied in a smart grid architecture.

Source: author's right.

Residences

**Firms**

16

However, the implementation of SSTs is highly complex. Firstly, due to their complex structures, which require a high number of switches, passive elements (diodes, capacitors and inductors), drivers and auxiliary circuits. These elements together with the voltage and current measurements must be controlled by one or more control devices, such as microcontrollers, DSPs (Digital Signal Processor), or FPGAs (Field-Programmable Gate Array) to manage the power flow.

The second challenge is due to the required large number of electronic components, which reliability can be affected if redundancy is not considered (HUANG *et al.*, 2017). The control system must protect the LV side against short circuits. When a fault situation occurs, only the closest upstream protection device should trigger in order to contain the effects (HUBER, KOLAR, 2017).

Last but not least, there aren't SST products that would allow a price comparison against the conventional transformer, but the cost could be probably a future issue. Estimations given by Huber and Kolar (2017) results in a range of 50-250 €/kVA, compared to the conventional transformers, which are around 10-25 €/kVA for a 100-1000 kVA power rating.

## 1.3 SST topologies for DC power distribution systems

There are several prominent topologies for SST applications, from two-level converters to the multilevel converters, which focus around different applications, topologies, power devices requirements, among others. Examples can be found in Zhao *et al.* (2013), She *et al.* (2013), Madhusoodhanan *et al.* (2015), and Barreto *et al.* (2018). However, since each SST application brings different characteristics to the table, this topic concentrates the attention in review studies focusing on DC power distribution systems, like the ones presented by She *et al.* (2012) and Rodriguez *et al.* (2017).

The multilevel converters have already been recognized as a good option for several medium- and high-voltage industrial applications, and they can be used into the SST conversion stages. Compared to two-level converters, they allow for an increase in the number of voltage levels at the output, which allows the reduction of the harmonic content and, consequently, the filter elements. The most well-known topologies are: NPC (Neutral-Point Clamped) (Figure 1.3a), FC (Flying Capacitor) (Figure 1.3b) and CHB (Cascaded H-Bridge) (Figure 1.3c). Also, other features are provided, as they allow a voltage rise without the need for step-up transformers, high efficiency, voltage and current efforts reduction on semiconductor

devices, common mode voltage elimination, among others (SADIGH; DARGAHI; CORZINE, 2015).

(a) (c)

Figure 1.3 – Conventional multilevel converters: (a) NPC, (b) FC and (c) CHB.

Source: author's right.

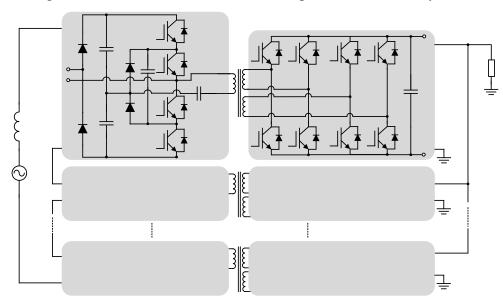

Based on the multilevel converters, Rodriguez *et al.* (2017) presented an AC-DC SST topology (Figure 1.4), using a NPC/FC converter connected to the primary of a medium-frequency transformer (MFT). At the two secondary windings, a four-leg full-bridge rectifier was connected to supply the load. Several advantages were addressed such as the single-stage AC-DC structure, ZVS and quasi-ZCS (soft-switching) for the whole operation power range, which increases its efficiency. Among its drawbacks, it doesn't provide a bidirectional power flow control, which is an important feature for the future power systems.

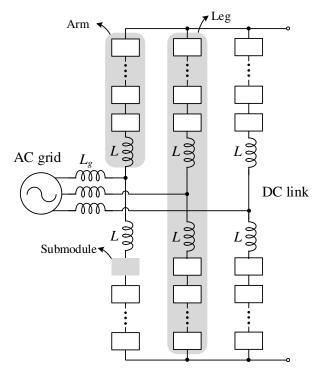

Also in the family of the multilevel converters, the modular multilevel converter (MMC) was patented by Marquardt (2001) and it is also consolidated in the industry as a suitable solution for HVDC (High Voltage Direct Current) applications (Figure 1.5). Compared to the conventional multilevel converters, it provides additional features such as the modular construction, allowing them to be designed for different voltage levels, current and power (modularity), scalability, bidirectional power flow, and waveforms with low harmonic distortion (GLINKA; MARQUARDT, 2005) (FALCONES; MAO; AYYANAR, 2010) (XIAOTIAN; GREEN, 2015) (HUBER; KOLAR, 2017). The MMCs are used in a wide Université Paris-Saclay

range of high-power applications, such as medium-voltage motor drives, offshore wind farms, static synchronous compensators (STATCOM) and solid-state transformers (DU *et al.*, 2018, p. 23) (SAHOO; MOHAN, 2017).

Figure 1.4 – AC-DC SST for electric DC power distribution systems.

Source: adapted from Rodriguez et al. (2017).

Figure 1.5 – Modular multilevel converter.

Source: adapted from Marquardt (2001).

Also, Glinka and Marquardt (2005) introduced the single-phase M<sup>2</sup>LC (Figure 1.6), which is an AC-AC MMC-based converter with two MMC legs connected to a medium-frequency transformer. At the MFT secondary side, there is a conventional AC traction converter (full-bridge rectifier plus an inverter). The topology can be extended to one-phase/three-phase by including an extra phase module. The structure has same advantages of the MMC including the galvanic isolation in medium-frequency, which reduces the transformer size and weight when compared to topologies using conventional 50-60 Hz transformers. Among its drawbacks, there is a large number of switches, increasing the switching losses, the complex structure enhances the controllability, and the cost of its implementation.

AC traction converter

Auxiliary power converter

Figure 1.6 – Single-phase AC-AC M<sup>2</sup>LC topology.

Source: adapted from Glinka and Marquardt (2005).

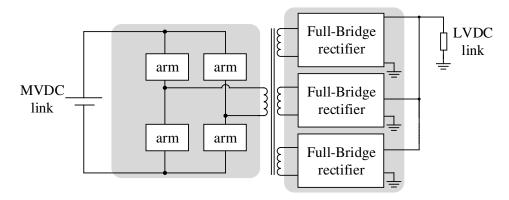

Similar to the M<sup>2</sup>LC, Wang *et al.* (2018) described a single-phase DC-DC structure with two MMC legs connected to the primary of a high-frequency transformer. There are three secondary windings connected to full-bridge converters to feed the load (Figure 1.7). The main idea is to interface a MVDC (Medium-Voltage Direct Current) and a LVDC link between DC distribution networks. Basically, it has the same advantages of the M<sup>2</sup>LC including the current sharing among the MMC legs that performs a conduction losses decrease. Among its drawbacks, it has the double number of switches per phase compared to the M<sup>2</sup>LC, which increases the structure complexity and the switching losses.

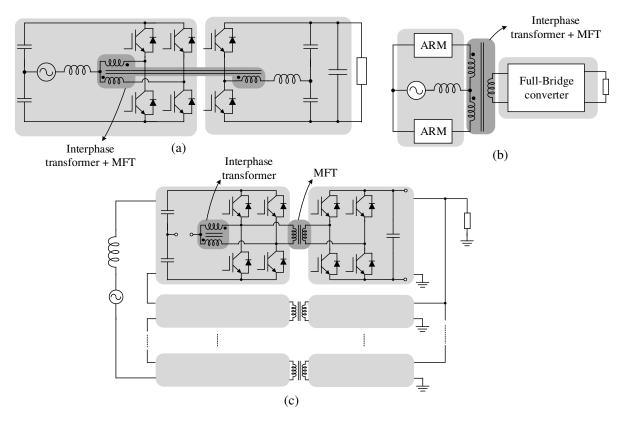

Although all these presented topologies are highly applicable to DC power distribution systems, another group of power converter uses not only the MMC-based structure, but also provides an interleaving feature combined together with the medium-frequency transformer. This interleaving element is called here as "interphase transformer". The interphase transformer brings some additional advantages to the converter such as the reduction of the total magnetic component size of the input inductor, the low current ripple and the

proper current sharing across the MMC legs (COUGO *et al.*, 2012) (BASCOPÉ; BARBI, 2000). Some examples are introduced by Oliveira Jr. *et al.* (2012), Pacheco *et al.* (2016) and Barreto *et al.* (2018) shown in Figure 1.8.

Figure 1.7 – Single-phase DC-DC MMC-based with high-frequency transformer SST topology for DC power distributions systems.

Source: adapted from Wang et al. (2018).

Figure 1.8 – Interleaved MMC-based topologies employed in SST applications: (a) Oliveira Jr. *et al.* (2012), (b) Pacheco *et al.* (2016) and (c) Barreto *et al.* (2018).

Source: adapted from Oliveira Jr. et al. (2012), Pacheco et al. (2016) and Barreto et al. (2018).

21

Therefore, the use of interleaved modular multilevel converters topologies together

with the solid-state transformers employed in DC power distribution systems applications is

justified.

1.4 Motivation and constraints

The future power systems challenges and the recent attention around the SST

applications in power distribution systems is the motivation behind this PhD research. Thus, an

AC-DC SST topology based on an interleaved modular multilevel converter structure is

proposed.

The main constraints of the topology are to provide not only the galvanic isolation

and voltage level adjustment features, but also including the features provided by the MMC-

based structure, the interleaving, and the medium-frequency transformer.

1.5 Thesis objectives

In this context, this thesis presents a novel interleaved modular multilevel converter

(IMMC) with a medium-frequency transformer. The proposed topology presents the combined

advantages as of conventional MMC, converters with MFT and interleaving. The interleaving

technique uses an interphase transformer, which reduces the conduction losses across the legs

and the IGBTs ratings reduction. The MFT allows its smaller and lighter footprint. Such

converter could be employed in high-power DC power distribution systems, as the AC-DC

stage of a SST for example.

One of the major contributions of this thesis is the mathematical modeling of the

IMMC, which allows the simultaneous generation of the low-frequency grid voltage and the

medium-frequency transformer primary voltage. Also, the capacitor voltage balancing and the

circulating currents minimization are combined together in a single algorithm.

In this work, features concerning the converter such as the design procedure, the

converter operation and modeling, the modulation technique, the capacitor voltage balancing

and circulating currents minimization algorithm, and the control scheme are detailed. In order

to validate the concept, the converter has first been simulated for the connection of the medium-

voltage utility grid connected to a low-voltage direct current link using a three-phase 100 kW

topology. Then a scaled-down single-phase 720 W prototype has been built and tested.

#### 1.6 Outline

The contents of this thesis are organized as follows:

- Chapter 1: a brief background of solid-state transformers for DC power distribution applications was presented: requirements and aspects. It was also presented an overview of the SST topologies for power distribution systems application, besides the thesis contextualization, motivation, and objectives.

- Chapter 2: the study of the proposed converter. The structure, the principle of

operation and the modeling provide fundamental concepts to understand and

develop the modulation technique, the voltage balancing and circulating

currents minimization algorithm, and the control scheme.

- Chapter 3: the analyses of the converter regarding the optimum number of submodules per arm, optimum transformer turns ratio, RMS and THD of the medium-frequency transformer primary voltage and losses. Also, this chapter presents the design methodology and the simulation results.

- Chapter 4: the experimental results of the proposed converter, considering the parameters and details of the small-scale single-phase prototype. It is presented the converter behavior under steady-state operation and dynamic operation.

- Chapter 5: the conclusion of the thesis. The future works from the PhD study is

presented as well, followed by the scientific production achieved during the

PhD period.

#### 2 PROPOSED TOPOLOGY

The proposed three-phase AC-DC IMMC is described in this section. The structure and the principle of operation describe the basis for the modeling, which is focused on obtaining the main equations that describe the influence of the submodules voltages across the input and transformer terminals, and the bus voltage. From that, the modulation techniques in both sides are developed in order to operate the aforementioned voltages following some restrictions. The capacitors voltage balancing and the circulating currents minimization are coordinated to be handled in a single algorithm. The control scheme is elaborated according to the converter plants, in each side, regulating the input current, the bus voltage and the output voltage while controlling the power flow between the AC and DC grids.

#### 2.1 Structure

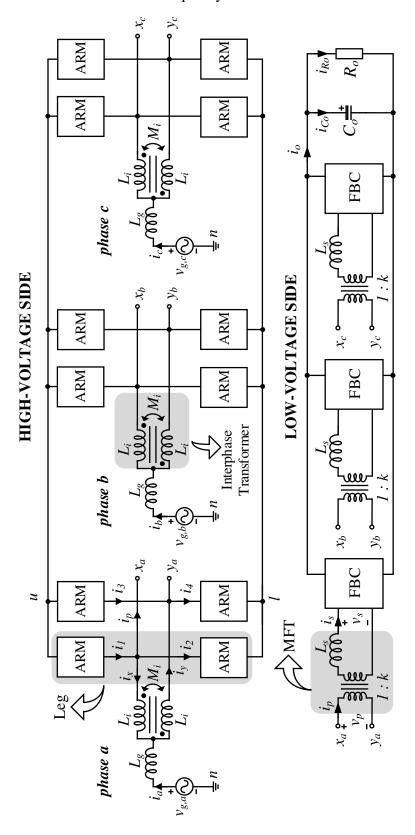

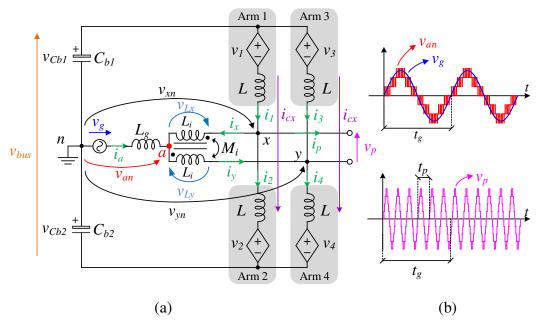

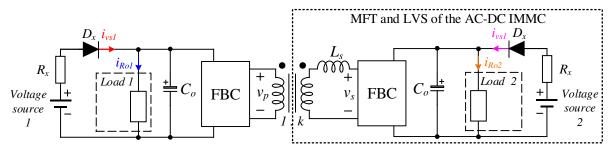

The structure of a three-phase AC-DC IMMC with medium frequency transformer is shown in Figure 2.1. The converter has three identical and independent phases (a, b, c), each one divided into high-voltage side (HVS) and low-voltage side (LVS).

At the HVS, one phase is made of one input inductor, one interphase transformer and two legs (X and Y). The three phases are connected to each other at the positive and negative DC bars referred as u and l, respectively. Each phase is connected to the medium-voltage AC grid through the input inductor  $L_g$ . The input current is shared between the two legs through an interphase transformer, with turn ratio 1:1, self-inductance  $L_i$  and mutual inductance  $M_i$ . The interleaving inductors help to decrease the semiconductors efforts, and thus, their conduction losses (BASCOPÉ; BARBI, 2000).

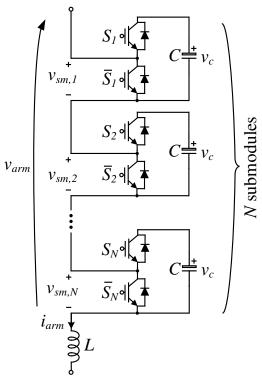

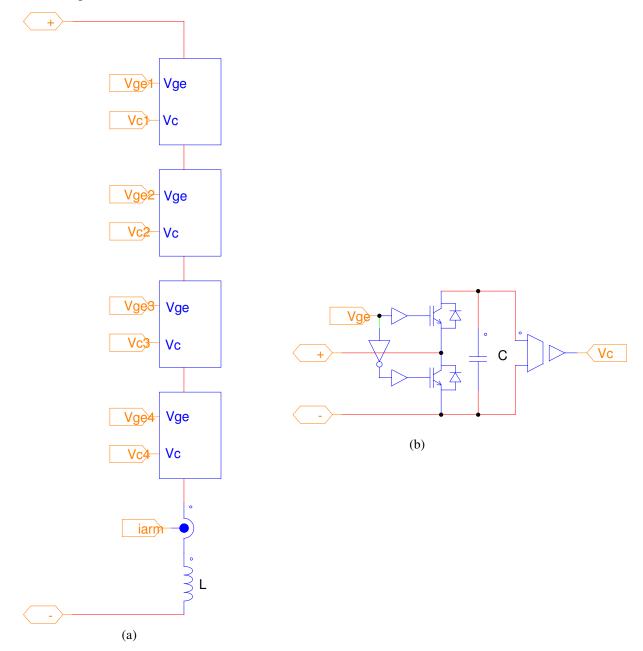

Each converter leg is made of two arms. One converter arm is composed of N half-bridge submodules (HBSM) connected in series with an arm inductor (L), as shown in Figure 2.2. The arm inductors have the task of limiting the currents through the submodules due to the instantaneous voltage difference between the arms. Each HBSM is composed of two switches (S and  $\overline{S}$ ) with antiparallel diodes operating in a complementary way, and one capacitor (C).

Thanks to the similarity with the MMC topology, this structure allows the same features, such as, modular construction, low total harmonic distortion (THD) of voltages and currents, large number of voltage levels and redundant submodules in each arm to achieve a fault-tolerant operation (DU *et al.*, 2018).

Figure 2.1 – Structure of a three-phase AC-DC interleaved modular multilevel converter with medium frequency transformer.

Source: author's right.

Figure 2.2 – Structure of a converter arm.

Source: author's right.

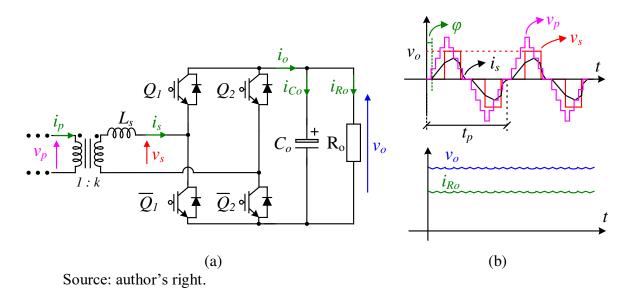

The connection of the HVS to the LVS is made by a medium-frequency transformer (MFT) in each phase, where k is the transformer turns ratio and  $L_s$  is the transformer leakage inductance reflected to secondary side.

The MFT primary side is connected to the mid-points of each converter leg ( $x_a$ ,  $y_a$ ,  $x_b$ ,  $y_b$ ,  $x_c$ ,  $y_c$ ), while its secondary side is connected to a full-bridge converter (FBC). The transformer offers the galvanic isolation. The medium-frequency operation allows a volume and weight reduction when compared to conventional low-frequency transformers.

$Q_1$   $Q_2$   $Q_3$   $Q_4$   $Q_5$   $Q_7$   $Q_7$

Figure 2.3 – Structure of a full-bridge converter.

Source: author's right.

At the LVS, each FBC is composed of four switches  $(Q_1, \overline{Q_1}, Q_2 \text{ and } \overline{Q_2})$  with antiparallel diodes, operating in a complementary way (Figure 2.3). The three FBCs are connected to a single output capacitor  $(C_o)$  and the load  $(R_o)$ .

#### 2.2 Principle of operation

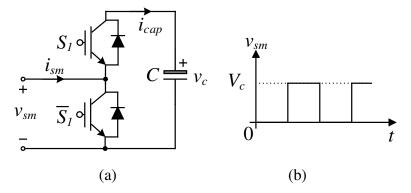

At the HVS, the HBSM produce the arm voltages. As illustrated in Figure 2.4, according to the top switch state S, the submodule output waveform  $v_{sm}$  is capable to achieve two voltage levels, "0" and " $v_c$ ". Depending on the submodule input current direction  $i_{sm}$ , the capacitor voltage  $v_c$  can either increase, decrease or not change. The possible switching states of the HBSM are described in Table 2.1.

Figure 2.4 – Half-bridge submodule and output voltage waveform.

Source: author's right.

Table 2.1 – Switching states of HBSM.

| State | $S_I$ | $v_{sm}$ | $i_{sm} > 0$   | $i_{sm} \leq 0$  |

|-------|-------|----------|----------------|------------------|

| I     | 0     | 0        | $v_c \approx$  | $v_c \approx$    |

| II    | 1     | $v_c$    | $v_c \uparrow$ | $v_c \downarrow$ |

$\approx$  = no change,  $\uparrow$  = increase,  $\downarrow$  = decrease

Source: author's right.

Therefore, each HBSM output voltage  $v_{sm}$  can be represented in terms of the capacitor voltage and the switching state of top switch  $S_I$  as the equation (2.1).

$$v_{sm}(t) = S_1(t) \cdot v_c(t) \tag{2.1}$$

The equation (2.1) can be expanded to obtain the voltage across the arm in terms of the capacitors average voltage  $V_c$  and the number of active submodules  $\delta$ , as represented in equation (2.2).

$$v_{arm}(t) = \delta(t) \cdot V_c \tag{2.2}$$

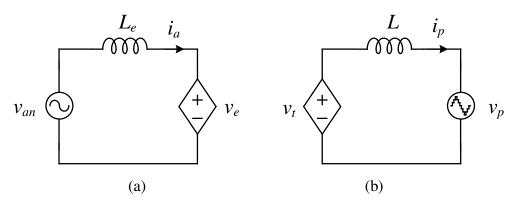

From equation (2.2), each arm can be represented by a controlled voltage source and, therefore, one phase is described as the equivalent circuit shown in Figure 2.5 (a).

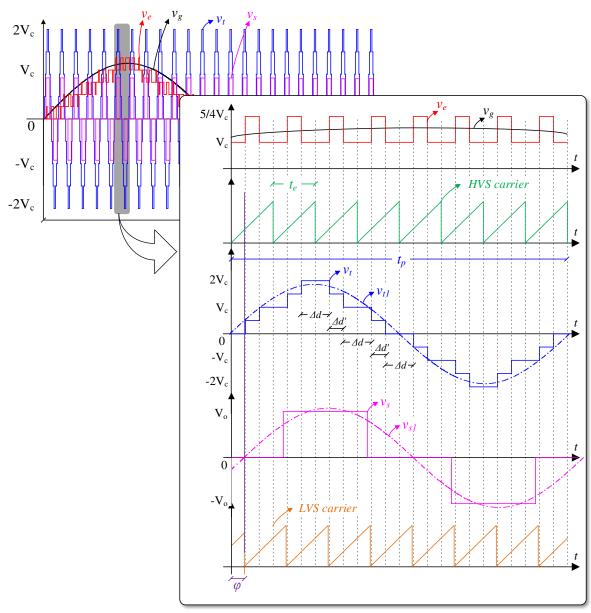

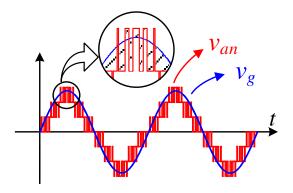

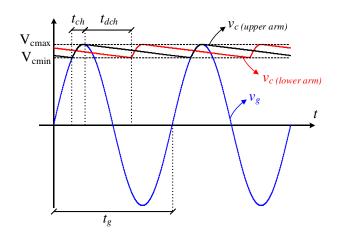

One important specificity of this converter is that the HVS modulation sets the number of active submodules per arm to generate simultaneously, the low frequency input voltage  $v_{an}$  and MFT medium frequency primary voltage  $v_p$ . The idealized waveforms of  $v_{an}$ ,  $v_g$  and  $v_p$  are presented in Figure 2.5 (b).  $t_g$  and  $t_p$  are the periods of the  $v_g$  and  $v_p$ , respectively.

Figure 2.5 – HVS principle of operation: (a) 1-phase equivalent circuit and (b) idealized waveforms of the grid voltage  $v_g$ , input voltage  $v_{an}$  and MFT primary voltage  $v_p$ .

Source: author's right.

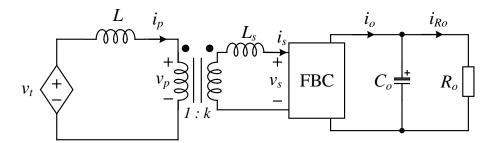

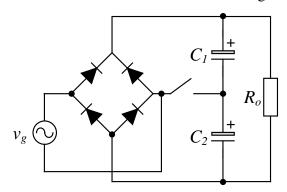

At the LVS, the operation of the FBC is shown in Figure 2.6 (a). Assuming that a large output capacitor  $C_o$  is used, the voltage of the MFT secondary  $v_s$  is related to the output average voltage  $V_o$  and to the switching states of the top switches  $Q_1$  and  $Q_2$  by

$$v_s(t) = V_o \cdot (Q_1(t) - Q_2(t)) \tag{2.3}$$

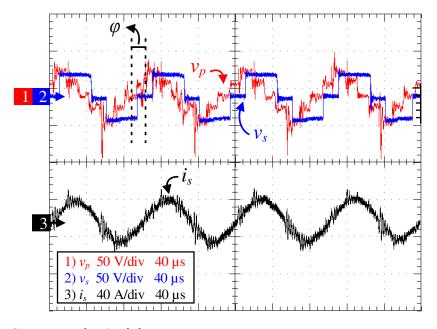

The power transferred to the load  $R_o$  depends on the phase-shift angle  $\varphi$  between the MFT primary and secondary voltages  $v_p$  and  $v_s$ . Therefore, the LVS controller regulates the output voltage  $v_o$  by setting the phase-shift angle  $\varphi$ , while the LVS modulation send the gate signals to switches  $Q_I$  and  $Q_2$ . The idealized waveforms of the MFT voltages  $v_p$  and  $v_s$ , the MFT secondary current  $i_s$ , the output voltage  $v_o$  and the output current  $i_o$  are presented in Figure 2.6 (b).

Figure 2.6 – LVS principle of operation: (a) 1-phase equivalent circuit and (b) idealized waveforms of MFT voltages  $v_p$  and  $v_s$ , the MFT secondary current  $i_s$ , output voltage  $v_o$  and output load current  $i_{Ro}$ .

#### 2.3 HVS Modeling

The main objective of the modeling is to obtain the equivalent circuits that represent the converter on its high-voltage side. Three variables are required: input voltage  $v_{an}$ ,

transformer primary voltage  $v_p$  and bus voltage  $v_{bus}$ . The following sections describe the modeling procedure in detail.

In summary, from the number of active submodules on each arm  $\delta_1$ ,  $\delta_2$ ,  $\delta_3$  and  $\delta_4$  in each phase, it is possible to obtain the switching states  $a_x$  and  $a_y$ . The combination of the average voltage on the submodules capacitors  $V_c$  and the switching states  $a_x$  and  $a_y$  provides the virtual voltages  $v_e$  and  $v_t$ , which are equivalent voltages produced by the submodules. The virtual voltages  $v_e$  and  $v_t$  do not exist physically, but they are respectively related to the input voltage  $v_{an}$ , the transformer primary voltage  $v_p$ , which can be measured.

In the same way, from the number of active submodules on each arm  $\delta_1$ ,  $\delta_2$ ,  $\delta_3$  and  $\delta_4$ , the number of active submodules on each leg  $n_x$  and  $n_y$  are calculated. Thus, together with the circulating currents on each leg  $i_{cx}$  and  $i_{cy}$ , the bus voltage  $v_{bus}$  is obtained.

#### 2.3.1 Leg mid-point voltages $v_{xn}$ and $v_{yn}$

At the HVS, considering phase a and assuming that the submodules capacitors are regulated at  $V_c$ , the converter arm voltages are described by

$$\begin{cases} v_1(t) = \delta_1(t) \cdot V_c \\ v_2(t) = \delta_2(t) \cdot V_c \\ v_3(t) = \delta_3(t) \cdot V_c \\ v_4(t) = \delta_4(t) \cdot V_c \end{cases}$$

$$(2.4)$$

where,  $\delta_1$ ,  $\delta_2$ ,  $\delta_3$  and  $\delta_4$  are the number of active submodules in the respective arms 1, 2, 3 and 4. Defining the switching states  $a_x$  and  $a_y$  as

$$\begin{cases} a_{x}(t) \triangleq \delta_{2}(t) - \delta_{1}(t) \\ a_{y}(t) \triangleq \delta_{4}(t) - \delta_{3}(t) \end{cases}$$

(2.5)

Assuming that the upper arms voltages are equal to the lower arms voltages (Figure 2.5), *i.e.*,

$$v_{Cb1}(t) = v_{Cb2}(t) (2.6)$$

Using the Kirchhoff's laws in circuit of the Figure 2.5 (a), considering (2.4), (2.5) and (2.6), the pole voltages are obtained

$$\begin{cases} v_{xn}(t) = \frac{1}{2} \left( V_c \, a_x(t) + L \left( \frac{di_2(t)}{dt} - \frac{di_1(t)}{dt} \right) \right) \\ v_{yn}(t) = \frac{1}{2} \left( V_c \, a_y(t) + L \left( \frac{di_4(t)}{dt} - \frac{di_3(t)}{dt} \right) \right) \end{cases}$$

(2.7)

# 2.3.2 Input voltage van and MFT primary voltage vp

Using Kirchhoff's laws, the input voltage  $v_{an}$  is

$$v_{an}(t) = \frac{1}{2} \left( v_{xn}(t) + v_{yn}(t) - v_{Lx}(t) + v_{Ly}(t) \right)$$

(2.8)

where  $v_{Lx}$  and  $v_{Ly}$  are the voltage across the interphase transformer windings, given as

$$\begin{cases} v_{Lx}(t) = L_i \frac{di_x(t)}{dt} + M_i \frac{di_y(t)}{dt} \\ v_{Ly}(t) = L_i \frac{di_y(t)}{dt} + M_i \frac{di_x(t)}{dt} \end{cases}$$

(2.9)

The transformer primary voltage  $v_p$  is

$$v_p(t) = v_{xn}(t) - v_{yn}(t)$$

(2.10)

Also, from Figure 2.5 (a), the input current  $i_a$  and the interphase transformer currents  $i_x$  and  $i_y$  are given as in (2.11).

$$\begin{cases} i_a(t) = i_y(t) - i_x(t) \\ i_x(t) = i_1(t) - i_2(t) - i_p(t) \\ i_y(t) = i_4(t) + i_3(t) - i_p(t) \end{cases}$$

(2.11)

From (2.11), the relationship between the HVS currents are given by (2.12).

$$\begin{cases} i_a(t) = i_y(t) - i_x(t) \\ i_a(t) = i_2(t) - i_1(t) + i_4(t) - i_3(t) \\ i_p(t) + i_m(t) = \frac{1}{2} (i_1(t) - i_2(t) - i_3(t) + i_4(t)) \end{cases}$$

(2.12)

where,  $i_m$  is the differential current of interphase transformer, calculated by

$$i_m(t) \triangleq \frac{1}{2} \left( i_x(t) + i_y(t) \right) \tag{2.13}$$

Observe that the interphase transformer has a 1:1 turn ratio. Thus, the fundamental of currents  $i_x$  and  $i_y$  have the same amplitudes  $I_{a\_p}/2$ , where  $I_{a\_p}$  is the input current amplitude, and are phase-shifted by 180° from each other. Assuming that the harmonics of currents  $i_x$  and  $i_y$  are small, the differential current  $i_m$  can be neglected. Then (2.12) can be rewritten as in (2.14).

$$\begin{cases}

i_a(t) = i_y(t) - i_x(t) \\

i_a(t) = i_2(t) - i_1(t) + i_4(t) - i_3(t) \\

i_p(t) = \frac{1}{2} (i_1(t) - i_2(t) - i_3(t) + i_4(t))

\end{cases}$$

(2.14)

Defining the equivalent inductance  $L_e$ ,

$$L_e \triangleq \frac{L_i - M_i}{2} + \frac{L}{4} \tag{2.15}$$

Defining the virtual voltages  $v_e$  and  $v_t$ , which are generated by the submodules switching states, given in (2.16) and (2.17), respectively,

$$v_e(t) \triangleq \frac{V_c}{4} \left( a_x(t) + a_y(t) \right) \tag{2.16}$$

$$v_t(t) \triangleq \frac{V_c}{2} \left( a_x(t) - a_y(t) \right) \tag{2.17}$$

Substituting (2.7), (2.9), (2.14), (2.15), (2.16) and (2.17) in (2.8) and (2.10), it's possible to obtain a decoupled equivalent model for the low-frequency side and the MFT primary voltage  $v_p$ , described by

$$v_{an}(t) = v_e(t) + L_e \frac{di_a(t)}{dt}$$

(2.18)

$$v_p(t) = v_t(t) - L\frac{di_p(t)}{dt}$$

(2.19)

From (2.18) and (2.19), it's possible to obtain the equivalent circuits of Figure 2.7. It is observed that the virtual voltages  $v_e$  and  $v_t$ , resulting from the submodule states  $(a_x, a_y)$  directly related to the voltages  $v_{an}$  and  $v_p$ . Thus, it is possible to control these voltages through the modulation technique.

Figure 2.7 – HVS decoupled equivalent circuits: (a) low-frequency grid side circuit and (b) MFT primary side circuit.

Source: author's right.

#### 2.3.3 Bus voltage v<sub>bus</sub>

Naming  $n_x$  and  $n_y$  the number of active submodules in each converter leg, then

$$\begin{cases} n_{\chi}(t) \triangleq \delta_{1}(t) + \delta_{2}(t) \\ n_{y}(t) \triangleq \delta_{3}(t) + \delta_{4}(t) \end{cases}$$

(2.20)

In the same way, using the Kirchhoff's laws in the circuit of Figure 2.5 (a), the bus voltage  $v_{bus}$  is described as

$$v_{bus}(t) = \frac{V_c}{2} \left( n_x(t) + n_y(t) \right) + \frac{L}{2} \left( \frac{di_1}{dt} + \frac{di_2}{dt} + \frac{di_3}{dt} + \frac{di_4}{dt} \right)$$

(2.21)

By default, the circulating currents are due to existing unbalanced voltages among the voltages across the DC link and submodules capacitors (LI *et al.*, 2015). Since there are two legs per phase in the proposed converter, each one has a circulating current component  $i_{cx}$  and  $i_{cy}$ , which can be calculated as

$$\begin{cases} i_{cx}(t) \triangleq \frac{1}{2}(i_1(t) + i_2(t)) \\ i_{cy}(t) \triangleq \frac{1}{2}(i_3(t) + i_4(t)) \end{cases}$$

(2.22)

Therefore, substituting (2.22) in (2.21)

$$v_{bus}(t) = \frac{V_c}{2} \left( n_x(t) + n_y(t) \right) + \frac{L}{2} \left( \frac{di_{cx}}{dt} + \frac{di_{cy}}{dt} \right)$$

$$(2.23)$$

This equation is used to develop the circulating current minimization algorithm.

## 2.4 HVS modulation technique

A HVS modulation must be developed to obtain the desired virtual voltages ( $v_e$  and  $v_t$ ), which are respectively related to the input voltage  $v_{an}$  and MFT primary voltage  $v_p$ , in each phase.

Among the possible techniques (DEBNATH *et al.*, 2015) (KONSTANTINOU; CIOBOTARU; AGELIDIS, 2013) (PICAS *et al.*, 2015) (DENG *et al.*, 2016), the adopted modulation technique is based on the space vector modulation. According to the number of submodules N present in each arm, the implementation begins by listing all the possible switching states in terms of the  $v_e$  and  $v_t$  voltages. This is possible since  $v_e$  and  $v_t$  are directly related to the submodules switching states by equations (2.16) and (2.17). Assuming 4 submodules per arm, the resulting space-state diagram is shown in Figure 2.8. The switching states are divided into sectors. One sector corresponds to a given level of  $v_e$ . Thus, the operation of the vector sequence follows the same pattern for all sectors.

$a_{x} = 4$   $a_{x} = 3$   $a_{x} = 2$   $a_{x} = 1$   $a_{x} = 0$   $a_{x} = -1$   $a_{x} = -2$   $a_{x} = -3$   $a_{x} = -4$   $a_{y} = 0$   $a_{y} = 1$   $a_{y} = 0$   $a_{y} = 1$   $a_{y} = 3$   $a_{y} = 4$   $a_{y} = 4$

Figure 2.8 – HVS modulation technique: space-state diagram.

Source: author's right.

The modulation indices  $M_e$  and  $M_t$  describe by how much the state-space diagram is modulated in each axis ( $v_e$  and  $v_t$ ). They can be respectively calculated as:

$$\begin{cases} M_e = \frac{2 V_{e\_p}}{N V_c} \\ M_t = \frac{V_{t\_p}}{N V_c} \end{cases}$$

(2.24)

where,  $V_{e\_p}$  and  $V_{t\_p}$  are the selected peak states of the voltages  $v_e$  and  $v_t$ , respectively.

For instance, the adopted operating region in Figure 2.8 results in

$\begin{cases} M_e = \frac{2 V_{e\_p}}{N V_c} = \frac{2 \left(\frac{5}{4} V_c\right)}{4 V_c} = 0.625 \\ M_t = \frac{V_{t\_p}}{N V_c} = \frac{2 V_c}{4 V_c} = 0.5 \end{cases}$ (2.25)

From (2.24), the relation between both modulation indices is calculated by

$$M_e = \frac{2N+1}{2N} - M_t \tag{2.26}$$

Among all the possible states, only a reduced number of states is chosen and constitutes an "operating region". The choice of this region follows some restrictions:

- The MFT primary voltage  $v_p$  must have the same operation frequency in entire region, *i.e.*, the same number of states for any sector of  $v_e$  (rectangular region);

- Modulation indices  $M_e$  and  $M_t$  are limited by the chosen region and they must be compatible with the grid voltage levels and the number of submodules in each arm;

- The number of levels in the  $v_e$  and  $v_t$  voltages must be compatible with the desired THD.

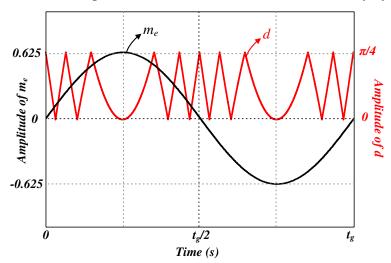

Taking as an example in red color region of Figure 2.8, the vector sequence of one sector and the waveforms of the voltages  $v_e$  and  $v_t$  is illustrated in Figure 2.9.

Figure 2.9 – HVS modulation technique: vector sequence of one sector and the waveforms of the voltages  $v_e$  and  $v_t$ .

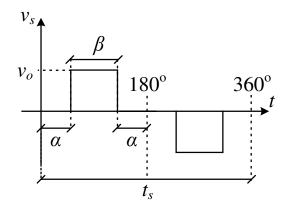

## 2.5 LVS modulation technique

At the LVS, the choice of the modulation technique took into account that the full-bridge converter provides the maximum of three voltage levels in the MFT secondary voltage. Thus, the SHE-PWM (Selective Harmonic Elimination Pulse-Width Modulation) was chosen to suppress the third order harmonic component (and its multiples), due to it being the one with the smaller order, which enables the reduction of MFT voltage and current stresses (SANCHEZ-RUIZ *et al.*, 2017).

According to the SHE-PWM equations and choosing the third harmonic ( $h_e = 3$ ) to be eliminated, the interval  $\beta$  is given by

$$\beta = \frac{2\pi}{h_e} = \frac{2\pi}{3} \, rad = 120^o \tag{2.27}$$

Therefore, the expected MFT secondary voltage  $v_s$  waveform is illustrated in Figure 2.10.

Figure 2.10 – LVS modulation technique: MFT secondary voltage waveform  $v_s$ .

Source: author's right.

# 2.6 Capacitors voltage balancing and circulating currents minimization algorithm

As for any modular multilevel converter, the submodules capacitor voltage balancing is mandatory for its functional operation (GHETTI *et al.*, 2017). From (2.23), it is observed that the circulating currents derivatives changes according to  $n_x$ ,  $n_y$  and  $v_{bus}$ . If  $v_{bus}$  is kept regulated by the control system, by setting the number of active submodules in each leg  $n_x$  and  $n_y$ , it is possible to change the direction of the circulating current in order to minimize it. For that, since the average bus voltage  $v_{bus}$  is nearly equal to  $NV_c$ , the following equations must be respected

$$\begin{cases}

\frac{di_{cx}(t)}{dt} = \frac{V_c}{2L} \left( N - n_x(t) \right) \\

\frac{di_{cy}(t)}{dt} = \frac{V_c}{2L} \left( N - n_y(t) \right)

\end{cases}$$

(2.28)

Therefore, according to the circulating currents flow ( $i_{cx}$  and  $i_{cy}$ ), there are two possible situations:

- If the circulating current is increasing, the number of active submodules in each leg  $(n_x$  and  $n_y)$  must be higher than N;

- If the circulating current is falling, the number of active submodules in each leg ( $n_x$  and  $n_y$ ) must be lower than N.

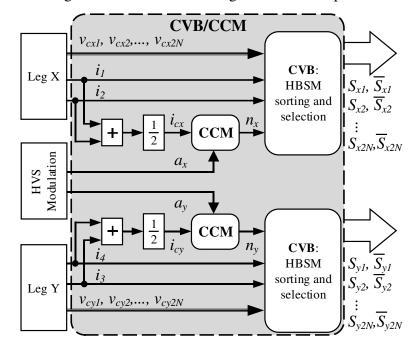

From that, the capacitors voltage balancing (CVB) and the circulating currents minimization (CCM) can be combined together in a single algorithm (CVB/CCM), as illustrated in Figure 2.11. This is one important specificity of this converter. The algorithm is used in each leg and the steps are described as follows:

Figure 2.11 – CVB/CCM algorithm in each phase.

- i. The voltages of 2N submodules capacitors in each leg are measured and compared with each other;

- ii. The arm currents  $(i_1, i_2, i_3 \text{ and } i_4)$  are measured and the circulating currents are calculated using (2.22);

- iii. The modulation technique block sends the switching states ( $a_x$  and  $a_y$ ) to the CCM block;

- iv. From the circulating currents flow and the modulation technique state variables, the number of active submodules in each leg  $(n_x$  and  $n_y)$  are calculated in CCM block and sent to the CVB block;

- v. In CVB block, according to the arm currents flows and the capacitors voltages, is verified:

- If the arm current is higher than zero, the arm is absorbing energy, therefore, the submodules with lower voltage across the capacitors are chosen and activated;

- If the arm current is lower than zero, the arm is supplying energy, therefore, the submodules with higher voltage across the capacitors are chosen and activated.

#### 2.7 Control scheme

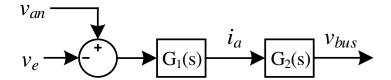

# 2.7.1 HVS plant

Concerning the HVS plant, two transfer functions are obtained using the one-phase equivalent circuit from Figure 2.5.

Applying Laplace's transform to (2.17), the single-phase plant transfer function  $G_I$  is obtained and represents the behavior of the input current by the equivalent inductor voltage given in (2.29).

$$G_1(s) = \frac{i_a(s)}{v_{an}(t) - v_e(t)} = \frac{1}{s L_e}$$

(2.29)

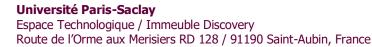

For the three-phase topology, (2.29) is expanded in dq-axis rotating reference frame (see Appendix A) (BAHRANI *et al.*, 2011), which results in

$$\begin{cases} v_{e,d} = v_d(t) - L_e \frac{di_d(t)}{dt} + \omega L_e i_q(t) \\ v_{e,q} = -L_e \frac{di_q(t)}{dt} - \omega L_e i_d(t) \end{cases}$$

(2.30)

Where  $v_{e,d}$  and  $v_{e,q}$  are, respectively, the direct axis and the quadrature axis of the virtual voltage  $v_e$ ,  $v_d$  is the grid voltage direct axis,  $\omega$  is the grid angular frequency,  $i_d$  and  $i_q$  are, respectively, the direct axis and the quadrature axis of the input current.

The bus voltage plant transfer function  $G_2$  consider that the input power  $p_{in}$  and output power  $p_{out}$  are nearly equal:  $p_{in} \cong p_{out}$ . In Figure 2.5 is observed that the AC grid supplies the arm submodules, which in its turn supplies the low-voltage side through the MFT. Thus,

$$p_{in} \cong p_{arm1} + p_{arm2} + p_{arm3} + p_{arm4} \cong 4 p_{arm} \cong p_{out}$$

$$\tag{2.31}$$

Therefore,

$$\begin{cases} p_{in}(t) = v_g(t) \, i_a(t) \\ p_{out}(t) = 4 \, v_{arm}(t) \, i_{arm}(t) \end{cases}$$

(2.32)

Since each arm is turned-on in every half-period of the grid voltage, i.e.,  $T = t_g/2$ , and assuming that capacitors voltages are balanced, the average voltage  $V_{arm}$  across the arms in steady-state is calculated by

$$V_{arm} = \frac{1}{T} \int_{0}^{T} N v_{c} dt = \frac{1}{t_{g}} \int_{0}^{\frac{t_{g}}{2}} N v_{c} dt = \frac{N V_{c}}{2}$$

(2.33)

Assuming that the capacitors voltages are balanced,  $n_x$  and  $n_y$  are "balanced" and kept around N. Thus, from (2.23), the bus voltage is equal to

$$v_{bus}(t) \cong \frac{v_c(t)}{2} (n_x + n_y) = \frac{v_c(t)}{2} (N + N) = N v_c(t)$$

(2.34)

From Figure 2.2, (2.1) and (2.34), the arms currents given by

$$i_{arm}(t) \cong i_{cap}(t) = C \frac{dv_c(t)}{dt} = \frac{C}{N} \frac{dv_{bus}(t)}{dt}$$

(2.35)

Substituting (2.33) and (2.35) in (2.32)

$$\begin{cases} p_{in}(t) = v_g(t) i_a(t) \\ p_{out}(t) = 2 C V_c \frac{dv_{bus}(t)}{dt} \end{cases}$$

(2.36)

Applying the Laplace's transform to (2.36), it returns the plant transfer function  $G_2$ , which represents the behavior of the bus voltage by the input current

$$G_2(s) = \frac{v_{bus}(s)}{i_a(s)} = \frac{V_g}{s \ 2 \ V_c \ C}$$

(2.37)

where,  $V_g$  is the grid RMS voltage.

From what precedes, the HVS can be modeled as cascaded plants ( $G_1$  and  $G_2$ ), as shown in Figure 2.12.

Figure 2.12 – HVS plant of the single-phase AC-DC IMMC.

Source: author's right.

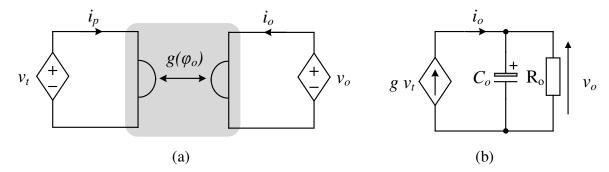

## 2.7.2 LVS plant

The LVS plant is obtained using the gyrator theory (TELLEGEN, 1948), which circuit model is described in Figure 2.13 (a), and then considering the FBC equivalent circuit, as illustrated in Figure 2.13 (b) (SANTOS *et al.*, 2011) (OLIVEIRA FILHO, 2015).

The gyrator conductance g is the gain, given in (2.38), representing the relationship between the output current ( $i_0$ ) and the phase-shift angle  $\varphi$  for a linearized boundary condition of the LVS in steady-state situation.

$$g(\varphi_o) = \frac{\partial I_o}{\partial \varphi_o} = \frac{V_o}{k \ 2\pi \ f_t \ L_t} cos\varphi_o \tag{2.38}$$

Figure 2.13 – LVS plant transfer function: (a) gyrator model, (b) FBC equivalent circuit.

Source: adapted from (SANTOS, 2011).

where  $f_t$  is the transformer frequency and  $L_t$  is equivalent inductance determined by

$$L_t = \frac{L}{k^2} + L_s \tag{2.39}$$

With this gyrator gain, the power flow between the primary and secondary sides is regulated by the phase-shift angle  $\varphi$  between the MFT primary voltage  $v_p$  and the secondary voltage  $v_s$ . Therefore, if the phase-shift angle  $\varphi$  increases, the transferred power increases, otherwise, it decreases. This angle can be either positive (rectifier mode) or negative (inverter mode).

From Figure 2.13 (b), the FBC transfer function  $G_{ivo}$  represents the behavior of the output voltage  $v_o$  and the output current  $i_o$ , given by

$$G_{vio}(s) = \frac{v_o(s)}{i_o(s)} = \frac{R_o}{s R_o C_o + 1}$$

(2.40)

Thus, the plant transfer function  $G_3$  is the combination of the gyrator gain g and the transfer function  $G_{ivo}$  and represents the behavior of the output voltage  $v_o$  by the phase-shift angle  $\varphi_o$ , given by

$$G_3(s) = \frac{v_o(s)}{\varphi_o(s)} = \frac{g R_o}{s R_o C_o + 1}$$

(2.41)

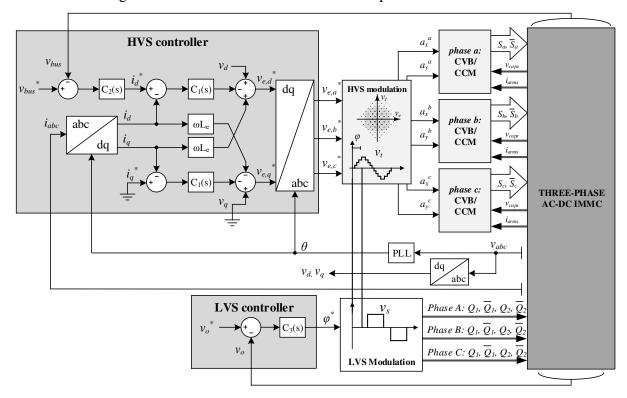

#### 2.7.3 HVS and LVS control scheme

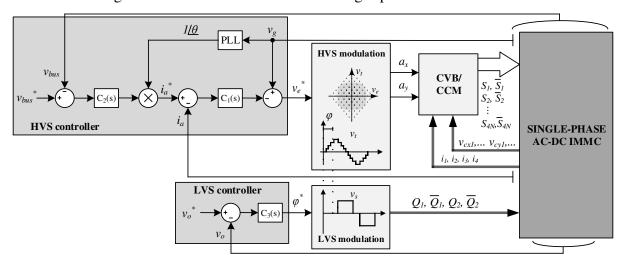

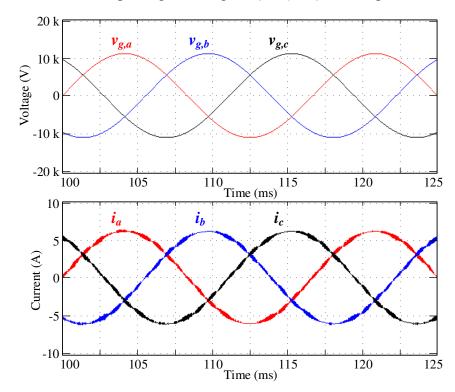

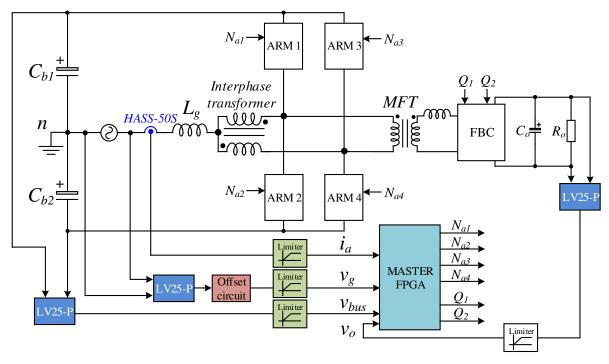

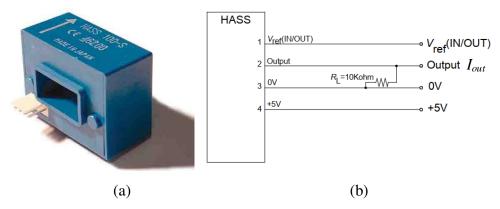

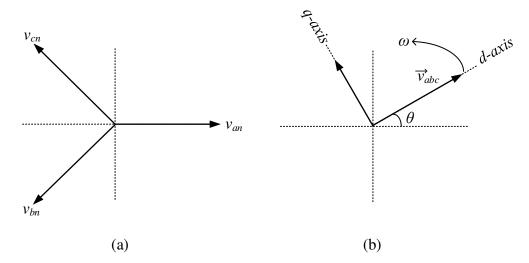

The control schemes for the AC-DC IMMC three-phase and the single-phase topologies are shown in Figure 2.14 and Figure 2.15, respectively. In both control schemes, at the HVS, the controller monitors the input current and bus voltage. At the LVS, the output DC voltage is regulated using the gyrator theory. Both HVS and LVS controllers are independent.

The three-phase controller is applied in a medium-voltage high-power application, which is analyzed through simulation in Chapter 3. The single-phase controller was experimentally validated in Chapter 4.

The K factor method (VENABLE, 1983) was used in all controllers' design, following the constraints in Table 2.2. Even with the second order double zero pole cascaded plant (section 2.7), the controllers tuning was possible to realize due to the high capacitance value on the  $G_2$ , which makes it slow. Therefore, PI controllers could fulfill the application.

Figure 2.14 – Control scheme of the three-phase AC-DC IMMC.

Figure 2.15 – Control scheme of the single-phase AC-DC IMMC.

Table 2.2 – Constraints of the controllers' design using K factor method.

| Controller         | Input current $C_I$ | Bus voltage $C_2$ | Output voltage $C_3$ |

|--------------------|---------------------|-------------------|----------------------|

| Constraint         |                     |                   |                      |

| Crossing frequency | 10 kHz              | 12 Hz             | 1.25 kHz             |

| Phase margin       | 60°                 | 90°               | 60°                  |

| Controller type    | 2                   | 2                 | 2                    |

Source: author's right.

Following the HVS side cascaded transfer functions, both the single-phase and three-phase topologies control structures are cascaded and composed of inner and the outer loops with their respective controllers ( $C_1$  and  $C_2$ ). The voltages  $v_{an}$  and  $v_g$  (single-phase control scheme) and the voltages  $v_d$ ,  $v_q$  (three-phase control scheme) are obtained from PLL (phase-locked loop) signals of from the AC grid.

The outer loop keeps the bus voltage  $(v_{bus})$  as constant as possible, following its reference  $(v_{bus})$ , and its output becomes the reference  $(i_a)$  for the single-phase control scheme, and  $(i_d)$ ,  $i_q$  for the three-phase control scheme) for the inner loop. The inner loop measures and regulates the input currents  $(i_a)$  for the single-phase control scheme, and  $(i_d)$ ,  $(i_q)$  for the three-phase control scheme) according to their references  $(i_a)$ ,  $(i_q)$ ,  $(i_q)$  in order to allow the submodule capacitors to be charged.

In single-phase control scheme, the modulating signal  $v_e^*$  are directly applied to the HVS modulation technique block. In the three-phase control scheme, it is necessary to

45

employ the inverse Park transform (dq – abc) to provide the modulating signals  $v_{e,a}^*$ ,  $v_{e,b}^*$ ,  $v_{e,c}^*$  and apply them to the HVS modulation block.

and apply them to the 11 v5 modulation block.

Therefore, the HVS modulation block sends the switching states  $(a_x \text{ and } a_y)$  to the CVP/CCM block in order to select and to drive the HPSMs.

CVB/CCM block in order to sort, to select and to drive the HBSMs.

At the LVS, the control structure is the same for both single-phase and three-phase topologies, which are composed of one loop with a controller  $(C_3)$ . The phase-shift angle  $\varphi$  is calculated by the output voltage controller  $C_3$ , in order to regulate the output voltage  $v_o$  to follow to its reference  $v_o^*$ , and sent to the LVS modulation block, which generates the FBC drive signals.

2.8 Final comments

This chapter presented the study of the proposed an AC-DC interleaved modular multilevel converter with medium-frequency transformer. The theoretical analysis consisted on the converter structure, principle of operation and modeling. From that, the high-voltage side equivalent circuits described the how the simultaneous generation of the low-frequency grid voltage and the medium-frequency transformer primary voltage can be achieved. Further, this feature was used in the proposed modulation technique.

The capacitors voltage balancing and the circulating currents minimization are combined together in a single algorithm. This is another important characteristic, which simplifies the hardware implementation.

The transfer functions of the converter plants allowed to regulate the AC current and the DC bus voltage, on the high-voltage side, and the DC voltage and power flow, on the low-voltage side. Thus, the control system can be employed by using proportional-integral controllers and requiring less hardware resources.

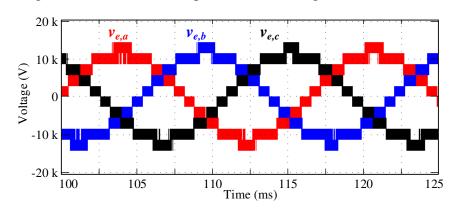

# 3 CONVERTER ANALYSIS, DESIGN AND SIMULATION

Based on the converter study and the modulation analysis, some analyses are developed here in order to obtain the optimum number of submodules per arm  $N_{opt}$ , the optimum transformer ratio  $k_{opt}$ , to evaluate the virtual voltage  $v_t$  behavior, concerning its RMS value and total harmonic distortion, and to understand the converter losses under full-load and no-load conditions. Also, the AC-DC IMMC design is described and tested through simulation for a 100 kVA three-phase converter applied as an AC-DC stage of a DC power distribution system. The steady-state and the power flow inversion conditions are simulated.

## 3.1 Converter analysis

# 3.1.1 Optimum number of submodules per arm Nopt

As described in chapter 2, section 2.4, the modulation technique was developed in order to obtain the desired submodules voltages ( $v_e$  and  $v_t$ ), which are respectively related to the input voltage and the MFT primary voltage ( $v_{an}$  and  $v_p$ ), in each phase. The operating region is highly appropriate, because the overall submodules frequency  $f_{sm}$  is constant and sub-harmonics can be neglected.

From the modulation technique point of view, the required number of active submodules per arm depends on of the grid voltage level and the voltage in each submodule capacitor. However, the total converter current effort must be considered to find a current balance across the input elements (input inductor, interphase transformer), the arm elements (arm inductors, submodule capacitors and switches) and the MFT.

Concerning the current efforts, the one-phase HVS equivalent circuit illustrated in Figure 2.5 was used. Assuming the steady-state condition without losses and the number of submodules per arm N is set to a large value. The following equations are used to describe the approximated RMS currents efforts on the input inductor  $I_a$ , interphase transformer windings  $I_x$  and  $I_y$ , the MFT primary  $I_p$  and the arms  $I_{arm}$  (KORN *et al.*, 2011).

$$I_a = \frac{\sqrt{2} P_{hvs}}{V_{e_p}} \tag{3.1}$$

$$I_x = I_y = \frac{I_a}{2} \tag{3.2}$$

$$I_p = \frac{\sqrt{2} P_{hvs}}{V_{tn}} \tag{3.3}$$

$$I_{arm} = \sqrt{\left(\frac{I_a}{4}\right)^2 + \left(\frac{I_p}{2}\right)^2} \tag{3.4}$$

where,  $P_{hvs}$  is the HVS output power.

Therefore, the converter total RMS current effort  $I_{total}$  is given by

$$I_{total} = 4 N I_{arm} (3.5)$$

From the modulation indexes  $M_e$  and  $M_t$  equations, given by (2.24), the peak states of the voltages  $v_e$  and  $v_t$ , respectively, are calculated as

$$V_{e_{-}p} = \frac{N M_e V_c}{2} \tag{3.6}$$

$$V_{t p} = M_t N V_c \tag{3.7}$$

Substituting (3.6) and (3.7) in (3.1) and (3.3), respectively, and assuming that the HVS output power  $P_{hvs}$  is nearly equal to the converter output power  $P_o$ , the input current and the MFT primary current are calculated by

$$I_a = \frac{2\sqrt{2}P_o}{M_e N V_c} \tag{3.8}$$

$$I_p = \frac{\sqrt{2}P_o}{M_t N V_c} \tag{3.9}$$

Substituting (3.8) and (3.9) in (3.4):

$$I_{arm} = \frac{\sqrt{2} P_o}{2 N V_c} \sqrt{\frac{0.5}{M_e^2} + \frac{1}{M_t^2}}$$

(3.10)

Then, substituting (3.10) in (3.5), it results in:

$$I_{total} = \frac{2\sqrt{2} P_o}{V_c} \sqrt{\frac{0.5}{M_e^2} + \frac{1}{M_t^2}}$$

(3.11)

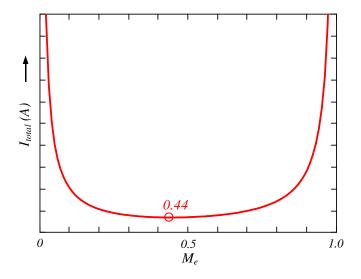

From (3.11), it is observed that the total current effort depends on the converter power, the submodule voltage and the modulation indices. Since the modulation indices are related to each other by (2.26), using (3.11), Figure 3.1 is obtained and describes the relation of the total current effort  $I_{total}$  versus modulation index  $M_e$  on the converter. It should be noted that these efforts are only related to the conduction losses.

Figure 3.1 – Converter total current effort  $I_{total}$  versus modulation index  $M_e$ .

Source: author's right.

It is observed that the smaller current effort occurs when the converter operates with  $M_e = 0.44$ . For instance, by modifying the input modulation index to  $M_e = 0.70$ , the current stresses increase by 45%, while the number of submodules per arm is reduced by 37.1%.

Thus, (3.6) can be rewritten as

$$N = \frac{2 \, V_{e\_p}}{M_e \, V_c} \tag{3.12}$$

In (3.12), it is assumed that the peak voltage  $V_{e_p}$  is nearly equal to the peak grid voltage  $V_{g_p}$ . Also, substituting the modulation index  $M_e = 0.44$ , which is the value that produces the smaller total current effort on the converter, the optimum number of submodules per arm  $N_{opt}$  can be derived and calculated by

$$N_{opt} = \frac{2 V_{g_p}}{M_e V_c} \cong \frac{2\sqrt{2} V_g}{0.44 V_c} \cong 6.43 \frac{V_g}{V_c}$$

(3.13)

## 3.1.2 Optimum transformer turns ratio $k_{opt}$

It is well-known that the transformer turns ratio k can be calculated by

$$k = \frac{V_p}{V_s} \tag{3.14}$$

where,  $V_p$  and  $V_s$  are the RMS primary and secondary voltages, respectively, of an ideal transformer.

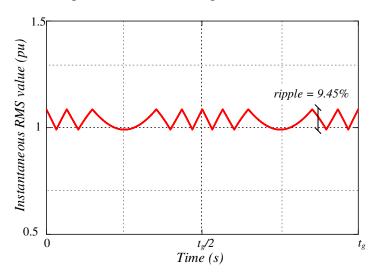

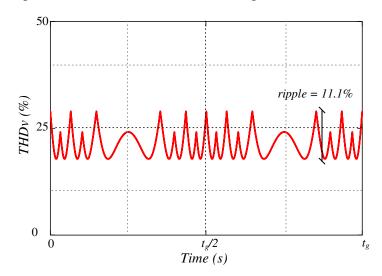

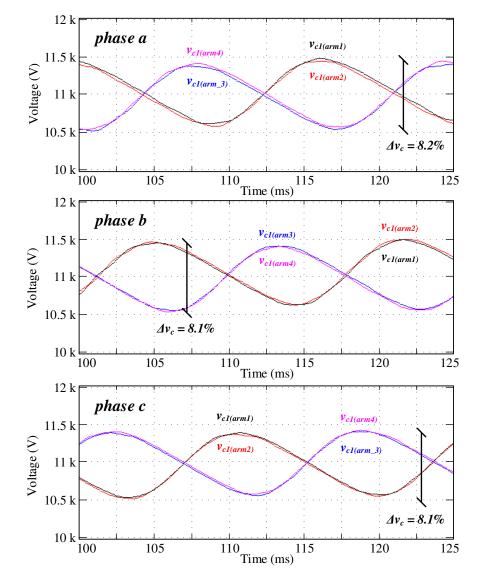

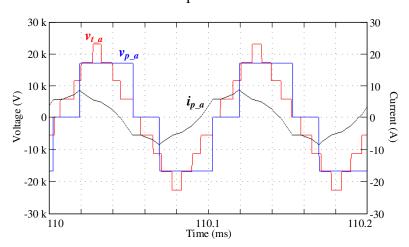

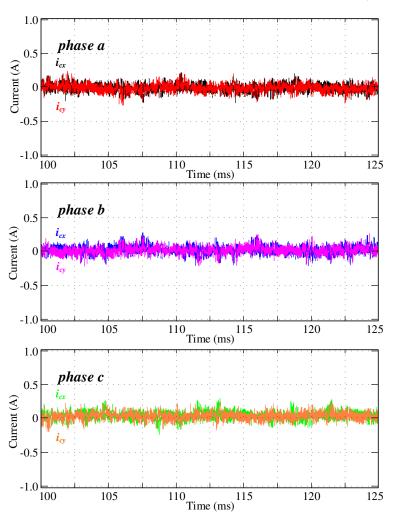

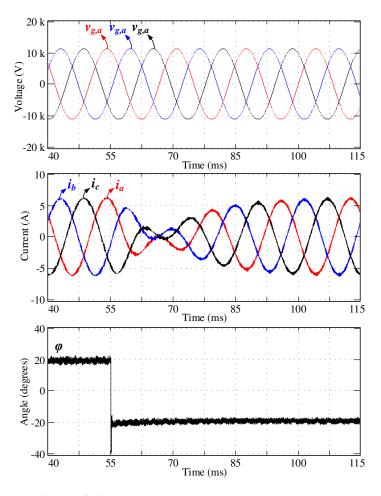

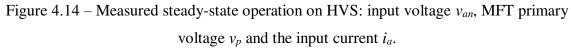

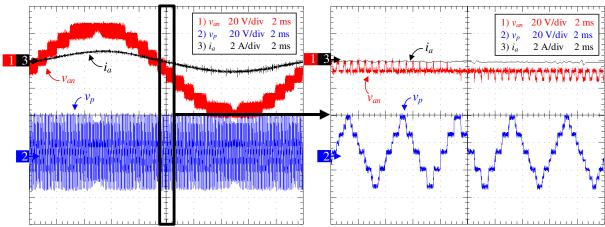

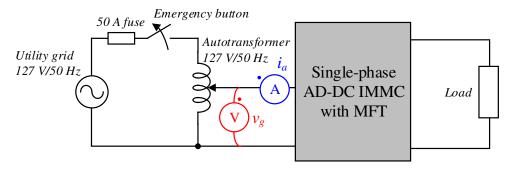

The application of a sinusoidal or a square wave on the primary side will be reflected on the secondary side, *i.e.*, the full power generated by the primary voltage and current harmonics are all carried together to the secondary side.