# Contribution à la conception d'un système d'acquisition de signaux biomédicaux pour la télésurveillance médicale Mariam Tlili

### ▶ To cite this version:

Mariam Tlili. Contribution à la conception d'un système d'acquisition de signaux biomédicaux pour la télésurveillance médicale. Electronique. Université de Bordeaux; Université de Carthage (Tunisie), 2018. Français. NNT: 2018BORD0159. tel-01985550

### HAL Id: tel-01985550 https://theses.hal.science/tel-01985550

Submitted on 18 Jan 2019

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

Président

Rapporteur

Rapporteur

Invité

Examinateur

### THÈSE EN COTUTELLE PRÉSENTÉE

POUR OBTENIR LE GRADE DE

### DOCTEUR DE L'UNIVERSITÉ DE BORDEAUX ET DE L'ECOLE SUPERIEURE DES COMMUNICATIONS DE TUNIS

ÉCOLE DOCTORALE DES SCIENCES PHYSIQUES ET DE L'INGENIEUR DE L'UBX

ET ÉCOLE DOCTORALE DES TECHNOLOGIES DE L'INFORMATION ET DE LA COMMUNICATION de SUP'COM

En Electronique et En Technologies de l'Information de la Communication

Par Mariam TLILI

### TITRE

# Contribution à la conception d'un système d'acquisition de signaux biomédicaux pour la télésurveillance médicale

Sous la direction de

Dominique DALLET, Professeur des Universités à Bordeaux INP, France, et de Chiheb REBAI, Professeur à SUP'COM, Tunisie Sous l'encadrement de

François Rivet, Maître de conférence à Bordeaux INP, France, de Manel BEN ROMDHANE, Maître Assistant à SUP'COM, Tunisie et de Asma MAALEJ Maître Assistant à l'ENIT, Tunisie

Soutenue le 23 Octobre 2018 à SUP'COM, Tunis, devant le jury composé de :

Mme BEN JEBARA, Sofia Professer

M. BENABES, Philippe Professer

M. MASMOUDI, Mohamed Professer

M. ROMAIN, Olivier Professer

M. CHEIKH, Mehdi Country M

Professeur à SUP'COM Professeur à CentraleSupelec Professeur à l'ENIS Professeur à l'Université de Cergy-Pontoise Country Manager à General Electric Healthcare

A mon père Nabil, ma source d'inspiration et mon idole,

A ma mère Samia, mon réservoir d'amour éternel,

A mon frère Chouaeb, mes sæurs Fayrouz et Aya, mes sources de bonheurs

A mon mari Souhail, en apprenant à te connaître mon horizon est devenu plus clair, plus joyeux.

I'avoue que si je suis là, c'est grâce à vous. J'espère pouvoir réaliser, aujourd'hui, l'un de vos rêves

A tous mes amis et à tous ceux qui ont cru en moi, je vous dédie ce travail.

« Prenez de chaque science ce qu'elle a de meilleur, comme les abeilles qui mangent de chaque fleur ce qu'elle a de plus beau, lequel engendre deux essences précieuses, l'une est porteuse de guérison pour les gens, l'autre fournit de la lumière. »

Hi Ibn Hbi Talib

« La vie n'est jamais un long couloir rectiligne que l'on traverserait d'une traite, libre comme le vent, mais un dédale de passages dans lequel il faut trouver son chemin, perdu et désorienté, condamné par moments à échouer au fond d'un cul-de-sac.

Mais il se trouve toujours, pour peu qu'on ait la foi, une porte entrouverte, même la plus inattendue, qui se révèlera être la voie qu'il fallait prendre. »

> Brchibald Joseph Cronin (1896–1982)

Les travaux de recherche détaillés dans ce manuscrit ont été conduits dans le cadre d'une thèse en co-tutelle préparée en vue de l'obtention du diplôme de Doctorat en Technologies de l'Information et des Communications de l'Ecole Supérieure des Communications de Tunis (SUP'COM), en Tunisie et en Electronique de l'Université de Bordeaux (UBx), en France.

Ces travaux de thèse de Doctorat sont le fruit d'une collaboration entre l'équipe Circuits Mixtes et Techniques Avancés pour les Systèmes de Communications (MSCAS) du laboratoire de recherche Systèmes de Communications Innovants et Verts (GRESCOM, Green and Smart Communications System), et les deux équipes Circuits et Systèmes Numériques (CSN) et Circuits et Systèmes (CAS), appartenant au groupe Conception du laboratoire de l'Intégration du Matériau au Système (IMS), relevant de l'Université de Bordeaux, de l'Institut Polytechnique de Bordeaux (Bordeaux INP) et du Centre National de la Recherche Scientifique (CNRS). Dans ce contexte, je souhaite exprimer ma sincère gratitude et ma profonde reconnaissance à Monsieur Yann DEVAL, Professeur à l'Université de Bordeaux, le directeur du laboratoire de recherche IMS, et à Monsieur Adel GHAZEL, Professeur à SUP'COM, et le directeur du laboratoire de recherche GRESCOM pour m'avoir accueillie au sein des deux laboratoires pour la réalisation de mes travaux de thèse.

### J'adresse tous mes remerciements à :

Madame Sofia BEN JEBARA, Professeur à SUP'COM, Tunisie, pour l'honneur qu'elle m'a fait en acceptant de présider le jury de cette thèse et pour m'avoir initiée au traitement avancé des signaux 1D et 2D lorsque j'étais son élève. Qu'elle en soit profondément remerciée.

Monsieur Philippe BENABES, Professeur à CentraleSupelec, France, pour son honorable participation à mon jury de thèse en qualité de rapporteur de mon travail et pour le temps consacré à la lecture et la correction de cette thèse.

Monsieur Mohamed MASMOUDI, Professeur à l'Ecole Nationale d'Ingénieur de Sfax (ENIS), Tunisie, pour avoir accepté de rapporter cette thèse et dont les remarques et commentaires me permettront d'améliorer la compréhension de ce mémoire.

Monsieur Olivier ROMAIN, Professeur à l'Université de Cergy-Pontoise, France, d'avoir accepté de faire partie du jury de cette thèse en contribuant, avec sa grande rigueur scientifique, à la discussion de ces travaux.

Monsieur Mehdi Cheikh, Senior Manager, Country Manager à General Electric Healthcare, Tunisie, pour son honorable participation au jury de cette thèse. Je tiens à l'assurer de ma profonde reconnaissance pour l'intérêt qu'il porte à ce travail.

Monsieur Dominique DALLET, Professeur des Universités à Bordeaux INP, France, et Chef du groupe Conception du laboratoire IMS, pour avoir dirigé mes travaux de thèse. Ses qualités pédagogiques et scientifiques ont été prépondérantes pour la réussite de cette thèse. Je tiens à lui exprimer mes plus vifs remerciements pour être disponible malgré les difficultés du travail à distance et ses nombreuses responsabilités, ainsi que pour ses encouragements, notamment lors de mes séjours au laboratoire IMS.

Monsieur Chiheb REBAI, Professeur à SUP'COM, Tunisie, et Chef de l'équipe MSCAS à GRESCOM, pour la confiance qu'il m'a accordée en me proposant ce sujet de recherche et pour l'honneur qu'il m'a fait en acceptant de diriger mes travaux de thèse. Je lui adresse mes remerciements pour ses multiples conseils et pour toutes les heures qu'il a consacrées à diriger ma thèse. Sa compétence, sa rigueur scientifique et sa clairvoyance m'ont beaucoup appris.

Madame Manel BEN ROMDHANE Ep. ABID, Maître Assistant à SUP'COM, Tunisie, et Chercheur Senior à GRESCOM, pour l'encadrement de mes travaux de thèse. Je tiens à lui exprimer ma gratitude pour les heures passées à la relecture méticuleuse de chaque travail réalisé. Ses propositions enrichissantes et son intérêt immense à l'avancée de mes travaux étaient des éléments moteurs. Cette thèse lui doit beaucoup.

Madame Asma MAALEJ Ep. BOUATTOUR, Maître Assistant à l'ENIT, Tunisie, et Chercheur Senior à GRESCOM, pour l'encadrement de mes travaux de thèse. Sa capacité d'analyse, ses propositions avisées et sa disponibilité jusqu'au bout sont pour beaucoup dans le résultat final de ce travail. Je tiens sincèrement à la remercier pour ses encouragements qui m'ont aidées à franchir plusieurs obstacles.

Monsieur François RIVET, Maître de Conférences à Bordeaux INP, France, et Chef de l'équipe Circuits et Systèmes du laboratoire IMS, pour sa contribution à l'encadrement de mes travaux de thèse. Nos discussions m'ont beaucoup appris en matière de conception de circuits intégrés.

J'associe à ces remerciements, également :

Docteur Sadika KHEMAKHEM Ep. BEN ROMDHANE, médecin cardiologue de libre pratique, ancienne médecin principale des hôpitaux de Tunis et spécialiste en écho doppler cardiaque, en holters tensionnel et rythmique, en épreuve d'effort et en cardiologie du sport, pour être une grande ressource pour la sélection et l'évaluation de certains signaux ECG. Je la remercie pour sa participation enrichissante et son extrême gentillesse.

Les ingénieurs de configuration des outils de CAO et tout le personnel du service informatique au laboratoire IMS, notamment Monsieur Olivier MAZZOUFFRE, Monsieur David BEDENES et Monsieur Patrick VILLESUZANNE, sans lesquels la conception électronique n'était pas possible.

Tout le personnel administratif à l'Université de Bordeaux, à l'IMS et à SUP'COM. Je tiens tout particulièrement à remercier Mdame Brigitte BORDES, Madame Mathilde DALBOS, Madame Stéphanie Danaux, Monsieur Fethi TLILI, Madame Leila NAJJAR, Madame Samia

BOUZOUITA, Madame Imen AZZOUNI et Madame Jihene OUERGUI. Leurs conseils et leur patience m'ont aidé à franchir beaucoup d'obstacles.

# Titre : Contribution à la conception d'un système d'acquisition de signaux biomédicaux pour la télésurveillance médicale

#### Résumé:

Cette thèse de Doctorat s'inscrit dans le cadre des travaux de recherches qui visent la réduction de la consommation de puissance des dispositifs portables dédiés à l'acquisition et la transmission des signaux biomédicaux. Les contributions de ce travail sont la modélisation, le dimensionnement et la conception d'un convertisseur analogique-numérique à traversée de niveaux (LC-ADC, Level-Crossing Analog-to-Digital Converter) pour la numérisation des signaux électrocardiogramme (ECG). L'apport de ce travail de thèse est la réduction de la fréquence d'échantillonnage moyenne et donc la diminution de la quantité des données à transmettre en origine de la consommation excessive de puissance dans ces dispositifs. Les travaux de modélisation ont permis de proposer un modèle détaillé de l'architecture LC-ADC dans MATLAB/SIMULINK pour la validation fonctionnelle du convertisseur, la vérification de la robustesse du dimensionnement au niveau système et l'anticipation des distorsions introduites par les erreurs du circuit ou par les variations des paramètres intrinsèques du signal ECG. Les résultats du dimensionnement ont permis de choisir une résolution de 8 bits pour le LC-ADC, une fréquence de 10 kHz pour l'horloge de quantification du temps, 12 bits pour la résolution des intervalles de temps quantifiés. Un dimensionnement supplémentaire, adapté au signal sinusoïdal de fréquence 220 Hz est également effectué aboutissant aux mêmes paramètres de dimensionnement avec une fréquence d'horloge égale à 500 kHz. Les résultats de validation du LC-ADC dimensionné, en utilisant des signaux ECG réels normaux et pathologiques, en présence de l'erreur de quantification du temps uniquement puis après ajout des erreurs des composants analogiques du LC-ADC, ont montré une bonne qualité des signaux ECG pour une lecture par le médecin. En termes de réduction des volumes de données numérisées, le LC-ADC a atténué la fréquence d'échantillonnage moyenne allant jusqu'à 25 % de la fréquence d'un ADC uniforme avec un taux de compression allant jusqu'à 80 % des données générées par un ADC uniforme. L'ajout d'un étage de compression numérique par interpolation polynomiale d'Hermite cubique a augmenté le taux de compression à 95 %. Le modèle ainsi dimensionné du LC-ADC a fait l'objet d'une conception en technologie CMOS 180 nm UMC en suivant une approche ascendante (bottom-up). Un circuit incluant un préamplificateur de tension de gain 40 dB, le LC-ADC à 8 bits et un générateur de signaux d'horloge de fréquences 10 et 500 kHz a été conçu avec une tension d'alimentation de 1.8 V et une plage du signal d'entrée de 1 V. La simulation du circuit électrique incluant le LC-ADC et le préamplificateur a montré une consommation de puissance de  $3.07 \mu W$ . Un rapport signal-sur-distorsion égal à 25.5 dB est mesuré. Avec un écart de 4.2 dB par rapport à la valeur limite de 21 dB, une bonne qualité du signal ECG est obtenue. Finalement, la réalisation du dessin des masques du circuit global a permis d'estimer une surface de 0.2 mm<sup>2</sup>. Les valeurs ainsi mesurées en termes de consommation de puissance et de surface sont parmi les plus faibles reportées dans la littératures par rapport aux circuits LC-ADC conçus pour la numérisation des signaux ECG.

**Mots clés :** convertisseur analogique-numérique à traversée de niveaux, électrocardiogramme, modélisation, dimensionnement, conception en technologie CMOS.

## Title: Contribution to the design of a biomedical signal acquisition system for medical telemonitoring

#### **Abstract:**

The presented Doctorate thesis research work falls within research activities aiming to reduce the power consumption of biomedical signals' acquisition and transmission portable devices. The contributions of this research work are the modeling, the system-level design and the circuit-level design of a level-crossing analog-to-digital converter (LC-ADC) in order to digitize electrocardiogram (ECG) signals. The presented research work results have led to the reduction of the average sampling frequency and thus the data volumes to be transmitted which are behind the excessive power consumption of these devices. A detailed LC-ADC model has been implemented in in MATLAB/SIMULINK which is useful for functional simulations of the converter, for validation of the system-level design and for anticipation of signal distortions that are caused by the LC-ADC analog components' errors and also by intrinsic parameters' variations of ECG signals. The system-level design results are the choice of an 8-bit resolution for the LC-ADC, a 10kHz frequency for the time-quantization clock and a 12-bit resolution for binary encoding of the quantized time intervals. Additionally, a 220-Hz sinusoidal signal is also considered for the design of the LC-ADC which has led to mainly the same design parameters with a clock frequency equal to 500 kHz. The validation results of the LC-ADC system-level design, using normal and pathological ECG signals in the presence of the time quantization error only and also after addition of the analog components' errors, have shown good signal quality for easy interpretation by the doctor. In terms of data volumes reduction, the average sampling rate reached by the LC-ADC has been attenuated to 25 % of the sampling frequency of a uniform ADC with a compression ratio as high as 80 %. Thanks to additional digital data-compression using cubic Hermitian polynomial interpolation, the compression ratio has been increased to 95 %. The LC-ADC model has been designed in CMOS 180 nm UMC technology using bottom-up approach. The designed circuit includes a 40-dB gain voltage preamplifier, the 8-bit LC-ADC and a clock signal generator of 10 Hz and 500 kHz frequencies. The circuits have been designed with a 1.8 V supply voltage and a 1 V input signal dynamic range. Electrical circuit simulations including the LC-ADC and the preamplifier circuits have shown a 3.07  $\mu W$  power consumption. Besides, a signal-to-distortion ratio equal to 25.5 dB is measured. With 4.2 dBs obove the lowest signal-to-distortion ratio limit, which is equal to 21 dB, good ECG signal quality is achieved. Finally, drawing the global circuit's layout has made it possible to estimate the occupied surface area which is equal to  $0.0.2 \ mm^2$ . The measured values in terms of power consumption and circuit area are among the lowest reported in the literature for the digitization of ECG signals.

**Keywords:** level-crossing analog-to-digital converter, electrocardiogram, modeling, system-level design, circuit-level design in CMOS technology.

#### Laboratoire de l'Intégration du Matériau au Système

[IMS, CNRS UMR5218, Bâtiment A31, 351 Cours de la Libération, 33400 Talence, France [Intitulé, n° de l'unité et adresse de l'unité de recherche]

Laboratoire Systèmes de communications innovants et verts

[GRESCOM, Cité Technologique des Communications, Rte de Raoued Km 3,5 - 2083, Ariana Tunisie]

### Liste des notations

$A_{vc}$  Gain du comparateur  $A_{av}$  Gain petit signaux

AccHAccumulateur pour le niveau de référence supérieurAccLAccumulateur pour le niveau de référence inférieur $a_{gi}$ Amplitude de la fonction gaussienne modélisant une onde i

aj Coefficient du polynôme modélisant le DACatan2 Fonction arc tangente à deux arguments

$b_i$  Un bit

$b_{gi}$  Ecart type de la fonction gaussienne modélisant une onde i

*c*<sub>0</sub> Signal de contrôle du multiplexeur

$egin{array}{ll} C_0 & {

m Capacit\'e \, unitaire} \ C_{ac} & {

m Capacit\'e \, de \, couplage} \end{array}$

$C_{as}$  Capacité pour annulation de l'effet de dégénération de la source

$egin{array}{ll} C_{eq} & {

m Capacit\'e\ \'equivalente} \ C_i & i^{\grave{e}me}\ {

m capacit\'e\ du\ DAC} \ C_L & {

m Capacit\'e\ de\ charge} \ \end{array}$

clk Signal d'horloge de référence

Cmpt Sortie du compteur

CompDComparateur pour la détection d'une traversée par rapport au niveau inférieurCompUComparateur pour la détection d'une traversée par rapport le niveau supérieur

*C*<sub>ox</sub> Capacité de l'isolant

$\begin{array}{ll} \textit{CR}_{\textit{LC-ADC}} & \text{Taux de compression intrinsèque du LC-ADC} \\ \textit{CR}_{\textit{interp}_{\textit{max}}} & \text{Taux de compression maximale par interpolation} \\ \textit{CR}_{\textit{interp}_{\textit{min}}} & \text{Taux de compression minimal par interpolation} \end{array}$

d(.)/dt Dérivée par rapport au temps

$D \times D$  Dimension de Φ et Ψ

d Degré du polynôme modélisant le DAC

DEC DécrémenterD<sub>i</sub> Entrée d'une bascule

DNL Erreur de non-linéarité différentielle

$DNL_{max}$  Erreur de non-linéarité différentielle maximale

DT Durée en seconde

$E_{0/1}$  Signal d'entrée d'un composant numérique

ECG<sub>en</sub> Signal d'entrée du LC-ADC

$\overline{ECG}_{en}$  Valeur moyenne du signal d'entrée

$\widehat{ECG}_{s}$  Signal ECG reconstruit

$ECG_s$  Données d'amplitude générées par le LC-ADC  $E_{DAC}$  Tension d'alimentation du modèle RC

$e_{gen_{0.1}}$  Bits de contrôle du multiplexeur

$E_H$  Tension finale de charge

$e_i$   $i^{\grave{e}me}$  bit de  $E_{0/1}$

$E_L$  Tension finale de décharge  $e_{n0/1}$  Signal d'entrée de la porte logique

ENOB Nombre de bits effectif

$F_c$  Fréquence de l'horloge de référence

$f_{en}$  Fréquence d'une sinusoïde

$F_m$  Fréquence moyenne d'échantillonnage du LC-ADC  $F_{max}$  Fréquence maximale dans la bande du signal ECG  $F_{inf}$  Fréquence inférieure à l'horloge la plus rapide de l'ADC

Fréquence d'échantillonnage de l'ADC uniforme

$F_{sup}$  Fréquence de l'horloge la plus rapide de l'ADC

$egin{array}{ll} g_{ds_{ai}} & ext{Conductance du transistor } M_{ai} \ g_{ds_i} & ext{Conductance du transistor } M_i \ g_{m_{ai}} & ext{Transductance du transistor } M_{ai} \ g_{m_i} & ext{Transductance du transistor } M_i \ \end{array}$

I Courant de polarisation de l'étage de sortie du comparateur

$I_0$  Courant de polarisation de la paire différentielle  $I_{bias}$  Courant de polarisation de l'amplificateur  $ICMR_-$  Tension d'entrée en mode commun minimale  $ICMR_+$  Tension d'entrée en mode commun maximale

$I_d$  Courant du drain  $I_{fuite}$  Courant de fuite INC Incrémenter

$INL_{max}$  Erreur de non-linéarité intégrale maximale

$I_p$  Courant de polarisation du pont diviseur de tension

K Nombre d'ondelettes retenues par l'OMP

*k* Facteur de translation

l Déviation standard d'une distribution gaussienne

L Longueur de grille d'un transistor

$l_0(x)$  Cardinal de x

$l_1(x)$  Somme des éléments de x en valeur absolue

l<sub>2</sub> Norme euclidienne

$\begin{array}{ll} L_{max} & \text{Longueur de grille maximale} \\ L_{min} & \text{Largeur de grille minimale} \\ log_{10}(.) & \text{Fonction logarithme à base 10} \\ log_2 & \text{Fonction logarithme à base 2} \end{array}$

$L_s$  Nombre d'échantillons dans le signal x

LSB Bit de poids le plus faible

m Résolution d'un ADC uniforme

M Résolution du LC-ADC et de son DAC

$m_{\alpha}$  Nombre de bits de  $\alpha$   $m_{\beta}$  Nombre de bits de  $\beta$  Nombre de bits de  $\gamma$

$M_{ai}$  Transistor du préamplificateur  $M_i$  Transistor du comparateur

mod Fonction modulo

MuxDMultiplexeur contrôlé par DECMSBBit de poids le plus fortMSBBit de poids le plus fort

MuxU Multiplexeur contrôlé par DEC

MuxTI Multiplexeur pour sélection des intervalles de temps

MuxUD Multiplexeur contrôlé par INC

n Indice

N Résolution du compteur du LC-ADC

$\begin{array}{ll} N_{ADC} & \text{Nombre d'échantillons générés par un ADC uniforme} \\ N_C & \text{Nombre de colonnes de la matrice d'ondelettes} \\ N_L & \text{Nombre de lignes de la matrice d'ondelettes} \\ N_{LC-ADC} & \text{Nombre d'échantillons générés par le LC-ADC} \\ N_{LSC} & \text{Nombre de lignes de la matrice d'acquisition} \end{array}$

PEPleine échelle du LC-ADCP(S)Polynôme d'interpolationP(x)Puissance d'un signal discretPDFFonction de densité de probabilité $P_i$ Morceau du polynôme d'interpolation

*PRD*<sub>c</sub> PRD après compression et décompression par ondelettes

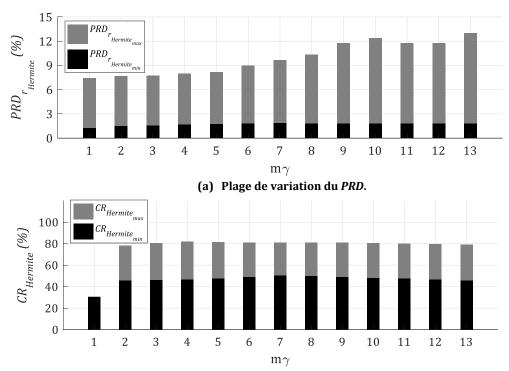

$PRD_{interp_{max}} \qquad \text{PRD maximal après compression et reconstruction par interpolation} \\ PRD_{interp_{min}} \qquad \text{PRD minimal après compression et reconstruction par interpolation} \\ PRD_{interp_{min}} \qquad \text{PRD minimal après compression et reconstruction par interpolation} \\ PRD_{interp_{min}} \qquad \text{PRD minimal après compression et reconstruction par interpolation} \\ PRD_{interp_{min}} \qquad \text{PRD}_{interp_{min}} \qquad \text{PRD}_{interp_{min}} \qquad \text{PRD}_{interp_{min}} \\ PRD_{interp_{min}} \qquad \text{PRD$

$PRD_{lcadc}$  PRD après numérisation par le LC-ADC et reconstruction par interpolation linéaire  $PRD_r$  PRD après compression, décompression et reconstruction par interpolation linéaire

$egin{array}{ll} q & ext{Pas de quantification} \ Q_i & ext{Sortie d'une bascule} \end{array}$

R Ensemble des nombres réels

Rapport de résolution/ Reste de soustraction entre deux signaux discrets

$R_{aeq}$  Résistance équivalente d'entrée

$egin{array}{ll} R_{eq} & ext{R\'esistance \'equivalente} \\ reset & ext{Remise \`a z\'ero du compteur} \\ \end{array}$

$R_{on_i}$  Résistance équivalente de l' $i^{\grave{e}me}$  branche du DAC  $R_{on_{H/L}}$  Résistance équivalente de la porte de transmission

$R_{on_n}$  Résistance équivalente d'un transistor NMOS en état passant  $R_{on_n}$  Résistance équivalente d'un transistor PMOS en état passant

$Rst_G$  Remise à zéro globale

SCR<sub>opt</sub> Taux de compression d'échantillons optimal S Signal de sortie d'un composant numérique

$S^-$  Valeur précédente de S  $S_{mux3}$  Sortie de MuxUD

S/D Rapport signal-sur-distorsion

S VECTEUR DES COEFFICIENTS D'ONDELETTES

Valeur numérique du niveau de référence supérieur

Valeur numérique du niveau de référence inférieur

Set Signal de mise à un

$s_i$  Signal de sortie d'une porte logique

SNR Rapport signal-à-bruit  $SR, SR_{min}$  Slew rate du comparateur  $Sw_i$  Commutateur CMOS

t Un instant

*T<sub>c</sub>* Période de l'horloge de référence

TG1/2 Porte de transmission

TI Intervalle de temps relatif au signal ECG  $\widehat{TI}_h$  Intervalle de temps relatif au signal ECG  $t^{imp}$  intervalle de temps relatif au signal ECG

$\widehat{Tl}_{hl}$  Intervalle de temps relatif à un segment du signal ECG

$t_p, t_{p_{inv}}$  Temps de propagation  $t_r$  Temps de réponse  $V^+$  Niveau de référence su

V+ Niveau de référence supérieurV- Niveau de référence inférieur

$V_{as}$  Tension de source  $V_{DC}$  Composante continue

$V_{DS}$  Différence de potentiel entre drain et source

$V_E$  Tension d'Early

$V_{G_{bias}}$  Tension de polarisation de la grille

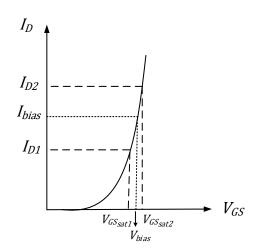

$V_{GS}$  Différence de potentiel entre grille et source

$V_{GSsat}$  Différence de potentiel entre grille et source à la saturation

$egin{array}{ll} V_{ctrl} & ext{Tension de contrôle de l'oscillateur en anneau} \ v_e & ext{Signal d'entrée de l'amplificateur de tension} \end{array}$

$V_{en}$  Signal d'entrée analogique  $V_{DAC}$  Tension de sortie du DAC

$V_{DAC_{NL}}$  Points de la courbe de transfert non-linéaire simulée

$V^+_{DAC_{NLmod}}$  Réponse non-linéaires décrivant le niveau de référence supérieur  $V^-_{DAC_{NLmod}}$  Réponse non-linéaires décrivant niveau de référence supérieur

$V_{dd}$  Tension d'alimentation

$V_o^+$  Niveau de référence supérieur effectif  $V_o^-$  Niveau de référence inférieur effectif

$V_{OH}$  Valeur maximale de la tension sortie du comparateur  $V_{OL}$  Valeur minimale de la tension de sortie du comparateur

$V_{pp}$  Amplitude crête à crête

$V_{refL}$  Tension de référence minimale du DAC

$V_{refH}$  Tension de référence maximale du DAC

$V_{sens}$  Sensibilité du comparateur

$V_{th_{n/n}}$  Tension de seuil du transistor NMOS ou PMOS

W Largeur de grille du transistor  $W_{max}$  Largeur de grille maximale  $W_{min}$  Largeur de grille minimale

$\begin{array}{ll} (W/L)_{ai} & \text{Rapport de dimensions d'un transistor dans l'amplificateur} \\ (W/L)_i & \text{Rapport de dimensions d'un transistor dans le comparateur} \\ (W/L)_{int_n} & \text{Rapport de dimensions d'un transistor NMOS dans un interrupteur} \\ (W/L)_{int_P} & \text{Rapport de dimensions d'un transistor PMOS dans un interrupteur} \end{array}$

*x* Valeur ou signal quelconque

$\hat{x}$  Signal x reconstruit par interpolation

$ar{x}$  Valeur moyenne de x  $\lfloor x \rfloor$  partie entière de x  $\vert x \vert$  Valeur absolue de x  $(x_0, y_0, z_0)$  Conditions initiales

(x, y, z) Système de coordonnées d'un plan tridimensionnel

Y Vecteurs des acquisitionsż Dérivée première de z

z Composante verticale du plan 3D  $Z_H$  Impédance équivalente du DAC

$Z_i$  Impédance équivalente de l' $i^{ème}$  branche du DAC

ET logique

⊕ Porte logique ou exclusif∈ Appartenance à un ensemble

$\begin{array}{ll} \Pi & & Produit \\ \Sigma & & Somme \end{array}$

$\Sigma\Delta$  Convertisseur sigma-delta

lpha Nombre de point éliminés par compression par interpolation  $lpha_i$  Nombre des points éliminés dans un vecteur d'Hermite

$\alpha_{max}$  Valeur maximale de  $\alpha$

β Paramètre temporel dans la compression par interpolation

$\beta_{max}$  Valeur maximale de eta

γ Paramètre temporel dans la compression par interpolation

$\gamma_{max}$  Valeur maximale de  $\gamma$   $\epsilon$  Erreur résiduelle

$\delta$  Temps de boucle du LC-ADC

$\delta_{max}$  Temps de boucle maximal du LC-ADC

$\delta t_n$  Erreur de quantification de l'instant de traversée de niveau

$\delta T_n$  Erreur de quantification de l'intervalle de temps entre deux traversées de

niveaux successives

$\delta V_n$  Erreur de quantification de l'amplitude  $\Theta$  Matrice d'acquisition compressée

$\theta$  Position angulaire

$heta_{gi}$  Déplacement angulaire de l'onde i

$\lambda$  Facteur de modulation de la longueur du canal dans un transistor MOS  $\lambda_n$  Facteur de modulation de la longueur du canal dans un transistor NMOS Facteur de modulation de la longueur du canal dans un transistor PMOS

$\mu_n$  Mobilité des électrons  $\mu_p$  Mobilité des trous

$\Delta \theta_{gi}$  Position relative d'une onde i par à l'onde R

$\Delta I$  Variation du courant

$\Delta L$  Distance entre le point de pincement et la fin du canal dans un transistor MOS

$\begin{array}{ll} \Delta V & \text{Tension diff\'erentielle infiniment faible} \\ \xi_0 & \text{Erreur d'approximation parcimonieuse} \end{array}$

$\xi_1$  Erreur d'approximation parcimonieuse par un algorithme de débruitage

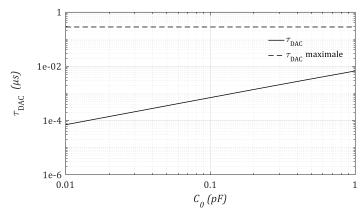

$au_{DAC}$  Constante de temps du DAC

Φ Matrice inverse de la matrice des ondelettes ou matrice de décomposition

$egin{array}{l} \phi_i \ \psi_1 \ \Psi \ \psi^j \end{array}$

$i^{\grave{e}me}$  ligne de  $\Phi$  Ondelette mère Matrice des ondelettes ou dictionnaire ou matrice de décompression

Sous-matrice de  $\boldsymbol{\Psi}$

### Acronymes et sigles

μC MICROCONTROLLEUR

ADC ANALOG TO DIGITAL CONVERTOR

AVC ACCIDENTS VASCULAIRES CEREBRAUX CRYPTOGENIQUES

AZTEC AMPLITUDE ZONE TIME EPOCH CODING

BP BASIS PURSUIT

BPM BATTEMENT PAR MINUTE

CAN CONVERTISSEUR ANALOGIQUE NUMERIQUE

CEI COMMISSION ÉLECTROTECHNIQUE INTERNATIONALE

CMOS COMPLEMENTARY METAL OXIDE SEMICONDUCTOR

CORTES COORDINATE REDUCTION TIME ENCODING SYSTEM

COTS COMMERCIAL-OFF-THE-SHELF

CR COMPRESSION RATIO

CS COMPRESSIVE SENSING

DCT DISCRETE COSINE TRANSFORM

DRC

DESIGN RULE CHECK

DSP

DATA SIGNAL PROCESSOR

DNL

DIFFERENTIAL NON-LINEARITY

DWT

DISCRETE WAVELET TRANSFORM

EMD

EMPIRICAL MODE DECOMPOSITION

E/B

ECHANTILLONNEUR BLOQUEUR

ECG ELECTROCARDIOGRAMME

ECG-graphe ELECTROCARDIOGRAPHE

ECG-scope ELECTROCARDIOSCOPE

EEG ELECTROENCEPHALOGRAMME

EMG ELECTROMYOGRAMME

ENOB EFFECTIVE BIT RESOLUTION

ERC ELECTRICAL RULE CHECK

EZW EMBEDDED ZEROTREE WAVELET

FFT FAST FOURIER TRANSFORM

FS FULL SCALE

FSG FLUORINATED SILICON GLASS

GMF GLOBAL MATCHED FILTER

GSM GLOBAL SYSTEM FOR MOBILE COMMUNICATION

INL INTEGRAL NON-LINEARITY

LC-ADC LEVEL CROSSING ANALOG TO DIGITAL CONVERTOR

LSB LEAST SIGNIFICANT BIT LOOK UP TABLE

LSV LAYOUT VERSUS SCHEMATIC

MedRadio Medical Device Radiocommunications Service Spectrum

MEZW MODIFIED EMBEDDED ZEROTREE WAVELET

MCG MAGNÉTOCARDIOGRAMME

MIMCAP METAL-INSULATOR-METAL CAPACITOR

MOSFET METAL OXIDE SEMICONDUCTOR FIELD EFFECT TRANSISTOR

MP MATCHING PURSUIT

MSB MOST SIGNIFICANT BIT

Na+ Sodium

NCAP N-CHANNEL CAPACITOR

NMOS N-CHANNEL METAL OXIDE SEMICONDUCTOR

NL Non-Linearite

NP-complexe Polynome Non-deterministe complexe

OMP ORTHOGONAL MATCHING PURSUIT

PE PLEINE ECHELLE

PCAP P-CHANNEL CAPACITOR

PMOS P-CHANNEL METAL OXIDE SEMICONDUCTOR

PRD PERCENTAGE ROOT MEAN SQUARE DIFFERENCE

RAM RANDOM ACCESS MEMORY

raz Remise A Zero RF Radio frequence RS Serial Port

SAR SUCCESSIVE APPROXIMATION REGISTER

SCR SAMPLE COMPRESSION RATIO

SNR SIGNAL TO NOISE RATIO

SPIHT SET PARTITIONING IN HIERARCHICAL TREES

SR SLEW RATE

S/D SIGNAL-TO-DISTORSION RATIO

TFT TRANSFOMÉE DE FOURIER DISCRÈTE

UMC UNITED MICROELECTRONICS CORPPORTATION

USB UNIVERSAL SERIAL PORT

WBAN WIRELESS BODY NETWORK

Wibio'ACT WIRELESS BIOMEDICAL ACQUISITION AND TRANSMISSION

WiFi Wireless Fidelity

| Ava   | nt-propo   | OS                                                                        | iii  |

|-------|------------|---------------------------------------------------------------------------|------|

| Rés   | umé et n   | nots clefs                                                                | vii  |

| Abs   | tract and  | d keywords                                                                | viii |

| List  | e des not  | tations                                                                   | ix   |

| Acro  | onymes e   | et sigles                                                                 | xv   |

| Tab   | le des m   | atières                                                                   | xvii |

| Tab   | le des fig | gures                                                                     | xxi  |

| Liste | e des tab  | oleaux                                                                    | xxv  |

|       |            | ı générale                                                                |      |

|       | pitre 1.   | Caractéristiques et systèmes de numérisation des signaux ECG              |      |

| 1.1.  | •          | duction                                                                   |      |

| 1.2.  |            | de l'art des systèmes d'acquisition des signaux électrocardiogrammes      |      |

|       | 1.2.1.     | Classification des signaux biomédicaux                                    |      |

|       | 1.2.2.     | Systèmes classiques de surveillance de l'activité électrique cardiaque    |      |

|       | 1.2.3.     | Limites des systèmes classiques pour la surveillance cardiaque à distance |      |

| 1.3.  | Anal       | yse du signal électrocardiogramme                                         | 16   |

|       | 1.3.1.     | Caractéristiques médicales de l'électrocardiogramme                       | 16   |

|       | 1.3.2.     | Caractère parcimonieux de l'électrocardiogramme                           | 19   |

| 1.4.  | Etat       | de l'art de la numérisation des signaux ECG                               | 23   |

|       | 1.4.1.     | Convertisseur à approximations successives                                | 23   |

|       | 1.4.2.     | Convertisseur sigma-delta                                                 | 26   |

|       | 1.4.3.     | Convertisseur à traversée de niveaux                                      | 28   |

|       | 1.4.4.     | Etude comparative                                                         | 31   |

| 1.5.  | Conc       | lusion                                                                    | 33   |

| Cha   | pitre 2.   | Modélisation et dimensionnement d'un LC-ADC                               | 35   |

| 2.1.  | Intro      | duction                                                                   | 35   |

| 2.2.  | Prése      | entation du fonctionnement du LC-ADC                                      | 36   |

|       | 2.2.1.     | Description des blocs constitutifs                                        | 36   |

| 4.1.        | Introd   | luction                                                                                         | .109  |

|-------------|----------|-------------------------------------------------------------------------------------------------|-------|

| Cha         | pitre 4. | Conception du LC-ADC en technologie CMOS 180 nm UMC                                             | .109  |

| 3.5.        | Concl    | usion                                                                                           | .107  |

|             | 3.4.4.   | Etude comparative des méthodes de compression                                                   | 104   |

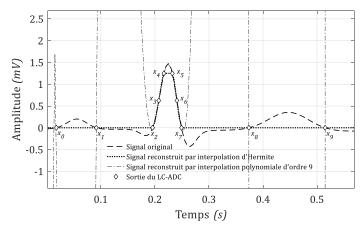

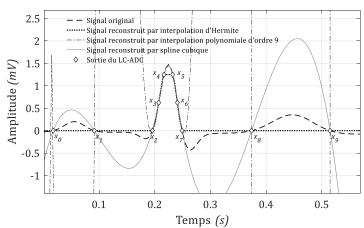

|             | 3.4.3.   | Résultats de la compression par interpolation polynomiale cubique                               | . 101 |

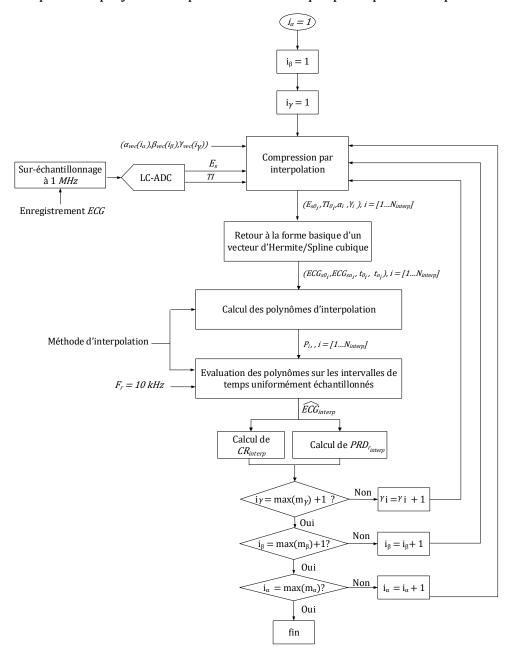

|             | 3.4.2.   | Méthodologie de l'étude de compression par interpolation d'Hermite                              | 95    |

|             | 3.4.1.   | Introduction à l'interpolation polynomiale                                                      | 90    |

| 3.4.        | Etude    | de la compression par interpolation                                                             | 90    |

|             | 3.3.4.   | Résultats de comparaison et choix de la famille d'ondelettes                                    | 84    |

|             | 3.3.3.   | Méthodologie de l'étude de compression par ondelettes                                           | 81    |

|             | 3.3.2.   | Familles d'ondelettes adéquates pour les signaux ECG                                            | 80    |

|             | 3.3.1.   | Transformée en ondelettes                                                                       | 78    |

| 3.3.        | Etude    | de la compression par ondelettes                                                                | 78    |

|             | 3.2.2.   | Etat de l'art des méthodes de compressions classiques                                           | 75    |

|             | 3.2.1.   | Etude de l'apport de compression du LC-ADC                                                      | 72    |

|             |          |                                                                                                 |       |

| 3.2.        |          | de l'opportunité de la compression après numérisation du signal ECG pa                          |       |

| 3.1.        |          | luction                                                                                         |       |

| •           | '        | Etuae ae l'opportunite ae la compression apres numerisation au signal.<br>C                     |       |

|             | pitre 3. |                                                                                                 |       |

| 2.5.        | •        | usion                                                                                           |       |

|             | 2.4.4.   | Analyse des performances du LC-ADC avec les signaux ECG en présence des erreurs des analogiques | 65    |

|             | 2.4.3.   | Analyse des performances du LC-ADC avec les signaux ECG                                         | 63    |

|             | 2.4.2.   | Dimensionnement du LC-ADC pour numériser les signaux ECG                                        |       |

|             | 2.4.1.   | Modèle mathématique d'un signal ECG                                                             | 54    |

| 2.4.        | Dimei    | nsionnement d'un LC-ADC pour la numérisation d'un signal ECG                                    | 54    |

|             | 2.3.2.   | Analyse des performances du LC-ADC en présence d'erreurs                                        | 51    |

|             | 2.3.1.   | Modèles d'erreurs dans l'architecture du LC-ADC                                                 | 47    |

| <i>2.3.</i> | Modé     | lisation des erreurs des composants analogiques du LC-ADC                                       | 46    |

|             | 2.2.4.   | Analyse du fonctionnement du LC-ADC avec un signal sinusoïdal                                   | 42    |

|             | temps    |                                                                                                 |       |

|             | 2.2.3.   | Modélisation du fonctionnement du LC-ADC en présence de l'erreur de quantification du           |       |

|             | 2.2.2.   | Analyse de l'erreur de quantification du temps                                                  | 38    |

| 4.3.1. Spécifications et dimensionnement de l'étage de pré-amplification                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 4.2. | Métho       | dologie de conception et spécifications globales du LC-ADC                      | 110 |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-------------|---------------------------------------------------------------------------------|-----|

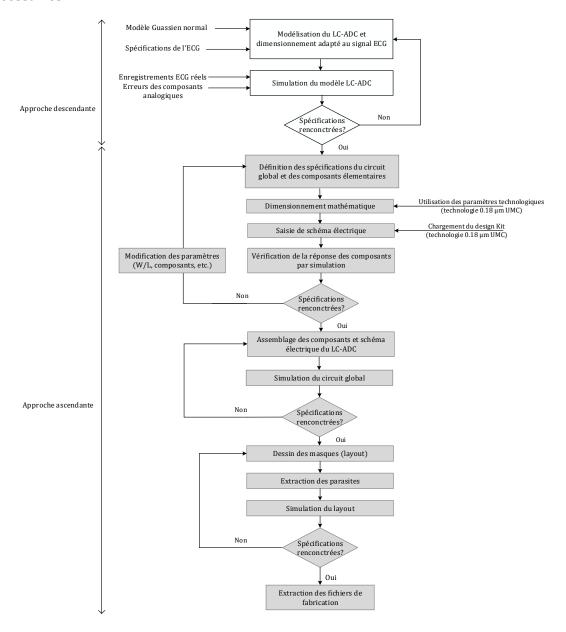

| 4.3. Spécifications et dimensionnement des étages du LC-ADC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |      | 4.2.1.      | Méthodologie de conception du LC-ADC                                            | 110 |

| 4.3.1. Spécifications et dimensionnement de l'étage de pré-amplification                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |      | 4.2.2.      | Spécifications globales du LC-ADC                                               | 112 |

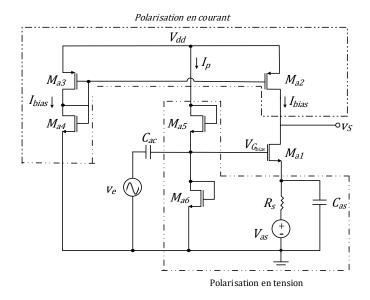

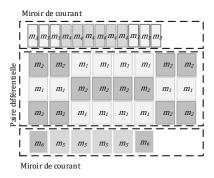

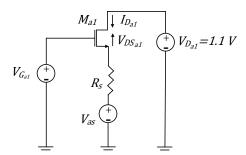

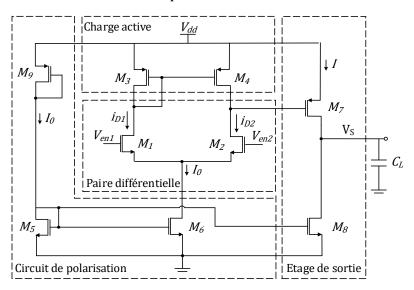

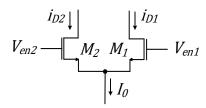

| 4.3.2. Spécifications et dimensionnement de l'étage de comparaison                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 4.3. | Spécifi     | ications et dimensionnement des étages du LC-ADC                                | 114 |

| 4.3.3. Spécifications et dimensionnement de l'étage de conversion numérique-analogique 122 4.3.4. Conception de l'étage de mise à jour des niveaux de références 125 4.3.5. Conception de l'étage de suivi du temps 128 4.3.6. Conception du générateur du signal d'horloge 131 4.3.7. Conception de l'étage de sortie 134 4.4. Validation de la conception 137 4.4.1. Simulation du schéma électronique global 137 4.4.2. Résultats préliminaires du layout 144 4.4.3. Discussion 146 4.5. Conclusion 148 Conclusion générale 151 Annexe A : Signaux ECG 155 Annexe B : Liste des ondelettes 157 Annexe B : Liste des ondelettes 157 Annexe C : Algorithme OMP 159 Annexe D : Résultats de l'étude de compression par spline cubique 161 Annexe E : Transistor MOSFET et technologie CMOS 180 nm UMC 163 Annexe F : Dimensionnement du préamplificateur 169 Annexe G : Principe de fonctionnement et dimensionnement du comparateur 175 Annexe G : Principe de fonctionnement et dimensionnement du DAC 185 |      | 4.3.1.      | Spécifications et dimensionnement de l'étage de pré-amplification               | 114 |

| 4.3.4. Conception de l'étage de mise à jour des niveaux de références                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |      | 4.3.2.      | Spécifications et dimensionnement de l'étage de comparaison                     | 117 |

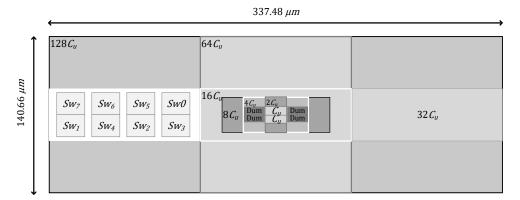

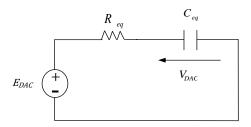

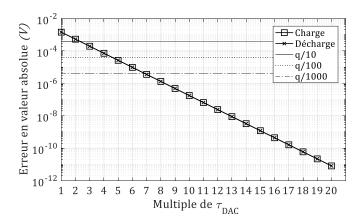

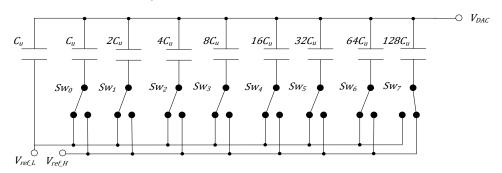

| 4.3.5. Conception de l'étage de suivi du temps                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |      | 4.3.3.      | Spécifications et dimensionnement de l'étage de conversion numérique-analogique | 122 |

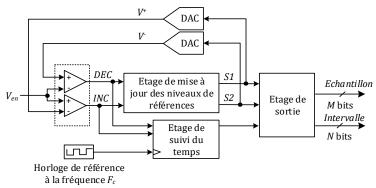

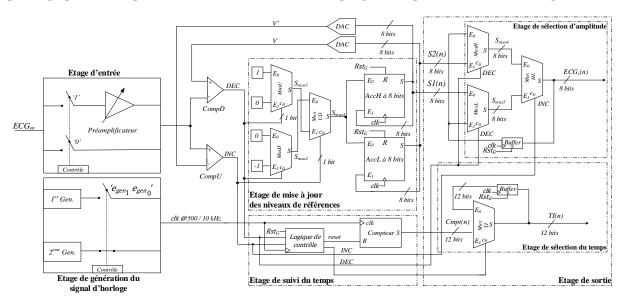

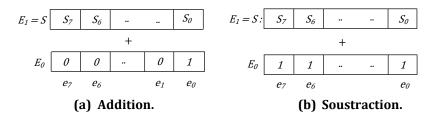

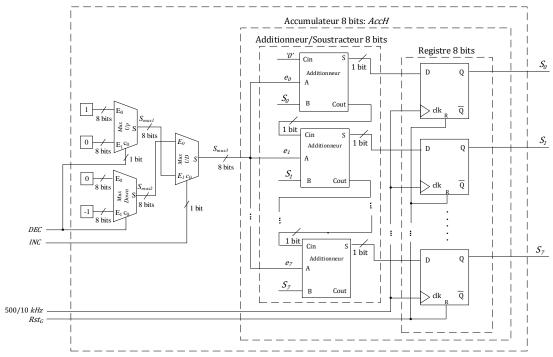

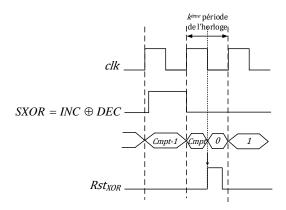

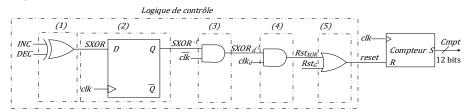

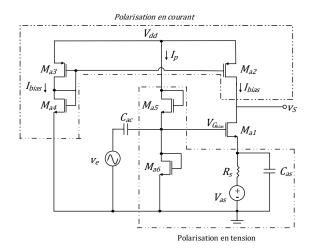

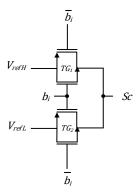

| 4.3.6. Conception du générateur du signal d'horloge                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |      | 4.3.4.      | Conception de l'étage de mise à jour des niveaux de références                  | 125 |

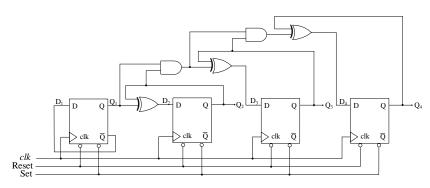

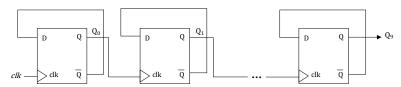

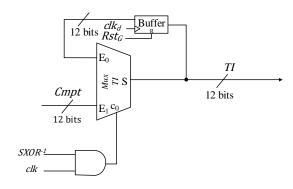

| 4.3.7. Conception de l'étage de sortie                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |      | 4.3.5.      | Conception de l'étage de suivi du temps                                         | 128 |

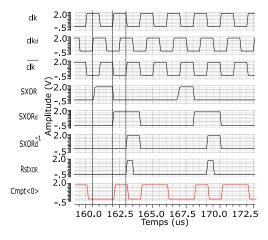

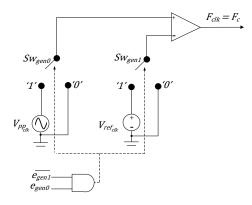

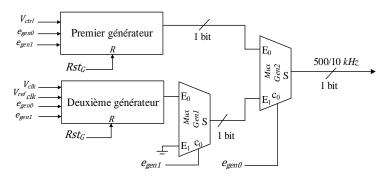

| 4.4. Validation de la conception                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |      | 4.3.6.      | Conception du générateur du signal d'horloge                                    | 131 |

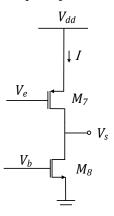

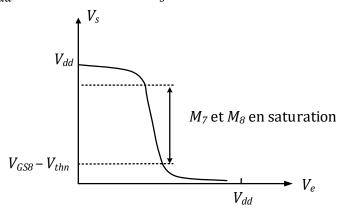

| 4.4.1. Simulation du schéma électronique global                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |      | 4.3.7.      | Conception de l'étage de sortie                                                 | 134 |

| 4.4.2. Résultats préliminaires du layout                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 4.4. | Valida      | tion de la conception                                                           | 137 |

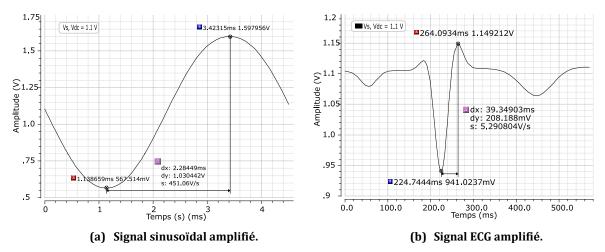

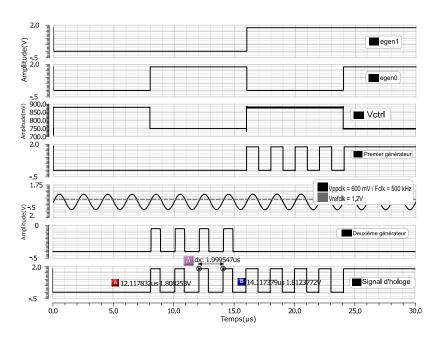

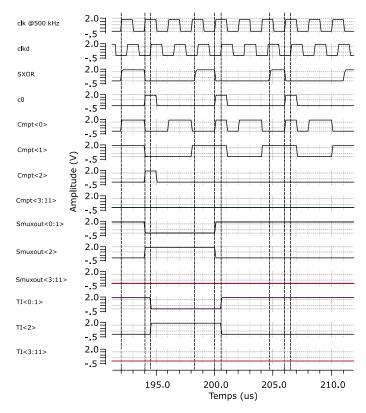

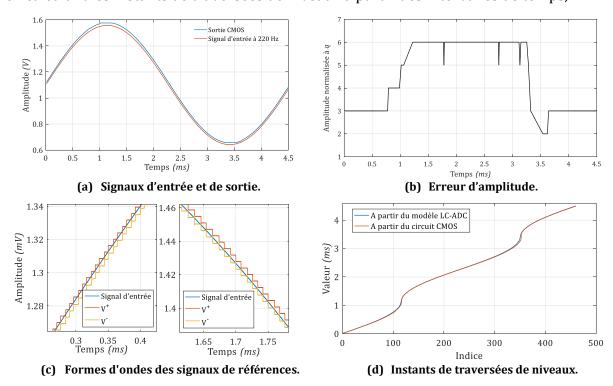

| 4.4.3. Discussion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |      | 4.4.1.      | Simulation du schéma électronique global                                        | 137 |

| 4.5. Conclusion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |      | 4.4.2.      | Résultats préliminaires du layout                                               | 144 |

| Conclusion générale                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |      | 4.4.3.      | Discussion                                                                      | 146 |

| Annexe A: Signaux ECG                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 4.5. | Conclu      | rsion                                                                           | 148 |

| Annexe B: Liste des ondelettes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Con  | clusion gé  | nérale                                                                          | 151 |

| Annexe B: Liste des ondelettes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Ann  | exe A : Sid | anaux ECG                                                                       | 155 |

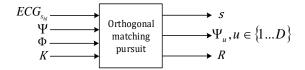

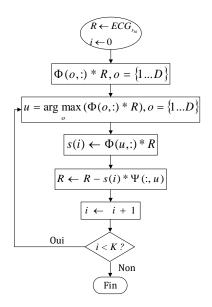

| Annexe C : Algorithme OMP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |      |             |                                                                                 |     |

| Annexe D : Résultats de l'étude de compression par spline cubique                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |      |             |                                                                                 |     |

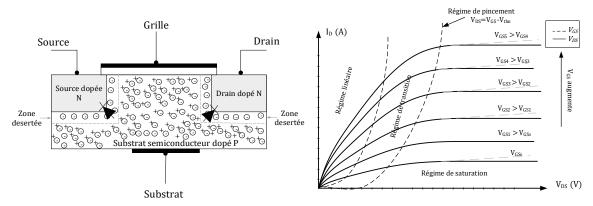

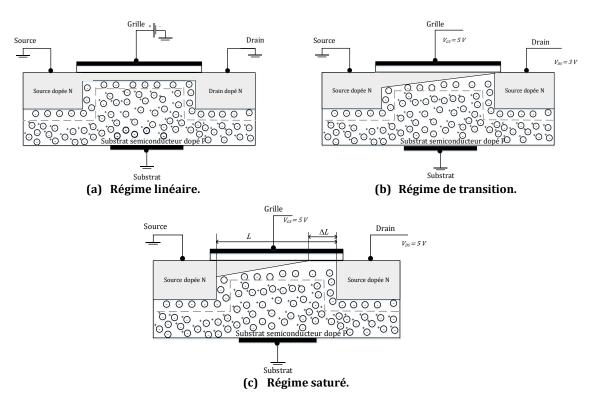

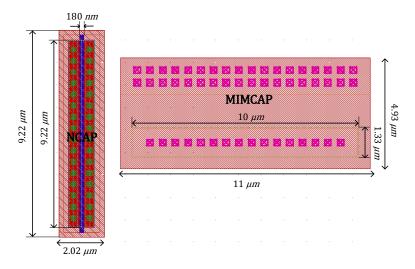

| Annexe E : Transistor MOSFET et technologie CMOS 180 nm UMC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |      |             |                                                                                 |     |

| Annexe F : Dimensionnement du préamplificateur169  Annexe G : Principe de fonctionnement et dimensionnement du comparateur175  Annexe H : Commutateur CMOS et dimensionnement du DAC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |      |             |                                                                                 |     |

| Annexe G: Principe de fonctionnement et dimensionnement du comparateur175  Annexe H: Commutateur CMOS et dimensionnement du DAC185                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Ann  | exe E : Tro | ansistor MOSFET et technologie CMOS 180 nm UMC                                  | 163 |

| Annexe H : Commutateur CMOS et dimensionnement du DAC185                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Ann  | exe F : Diı | nensionnement du préamplificateur                                               | 169 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Ann  | exe G : Pr  | incipe de fonctionnement et dimensionnement du comparateur                      | 175 |

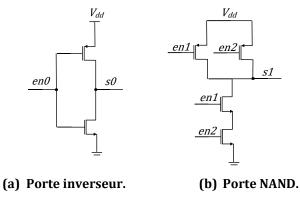

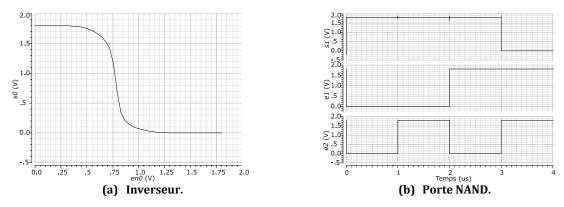

| Annexe I : Eléments de la bibliothèque numérique conçue191                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Ann  | exe H : Co  | mmutateur CMOS et dimensionnement du DAC                                        | 185 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Ann  | exe I : Elé | ments de la bibliothèque numérique concue                                       | 191 |

| Références193                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |      |             |                                                                                 |     |

## **Table des figures**

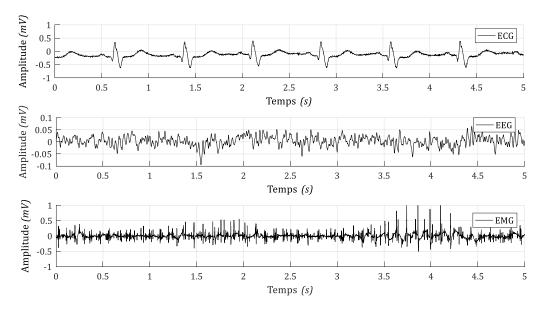

| Figure 1. 1 Signaux bioélectriques.                                                                                     | 7      |

|-------------------------------------------------------------------------------------------------------------------------|--------|

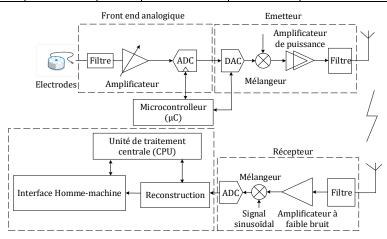

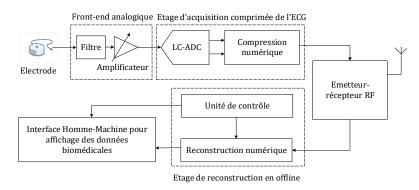

| Figure 1. 2 Chaîne d'acquisition, de transmission sans-fil et de traitement numérique d'un signal ECG.                  | 13     |

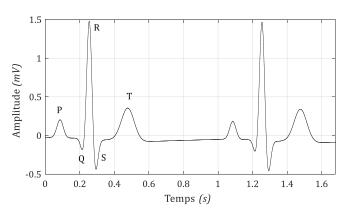

| Figure 1. 3 Ondes caractéristiques d'un signal ECG : enregistrement "rec_1m" de la base de données '                    | 'ECG-  |

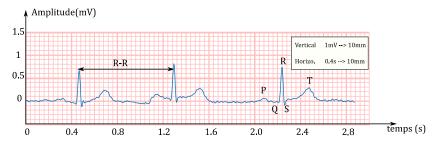

| ID" (ecgidb)                                                                                                            | 17     |

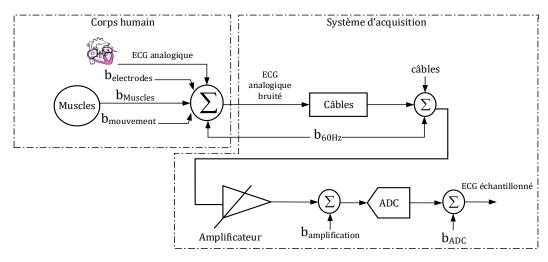

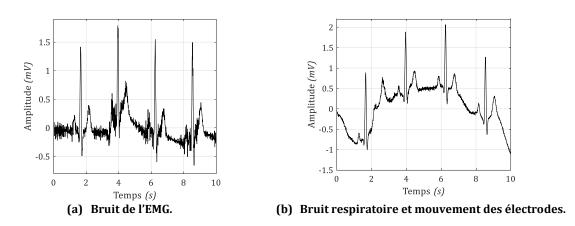

| Figure 1. 4 Bruits de la chaîne d'acquisition de l'ECG.                                                                 | 18     |

| Figure 1. 5 Mise en relief de deux exemples de bruits dans l'ECG.                                                       | 18     |

| Figure 1. 6 Convertisseur analogique numérique de type SAR                                                              | 24     |

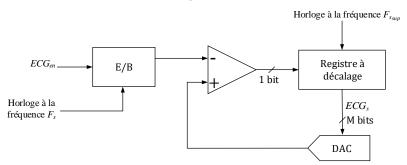

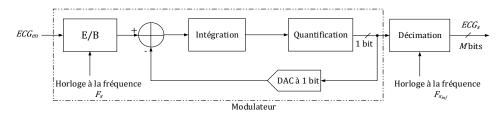

| Figure 1. 7 Convertisseur Sigma-Delta                                                                                   |        |

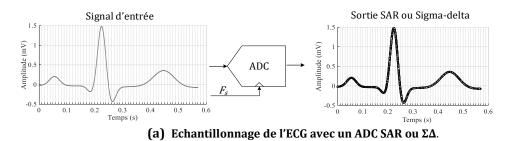

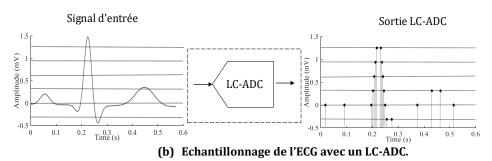

| Figure 1. 8 Principe de l'échantillonnage par traversée de niveaux.                                                     |        |

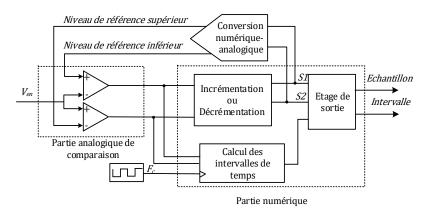

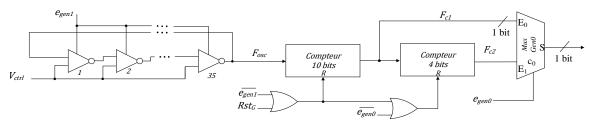

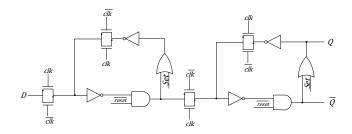

| Figure 1. 9 Schéma fonctionnel du LC-ADC                                                                                |        |

| Figure 1. 10 Comparaison de l'échantillonnage uniforme et de l'échantillonnage par traversée de niv                     | eaux.  |

|                                                                                                                         | 32     |

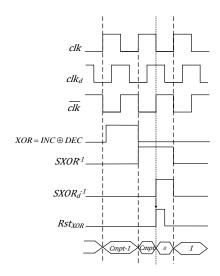

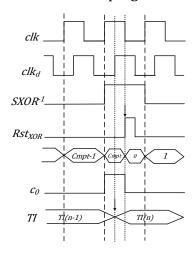

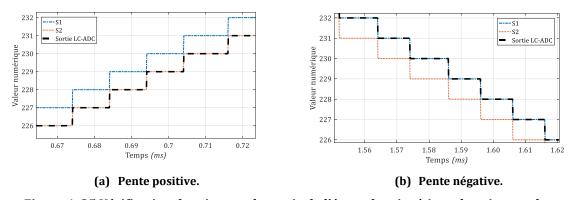

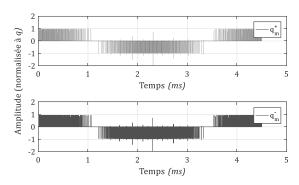

| Figure 2. 1 Schéma fonctionnel du LC-ADC                                                                                | 37     |

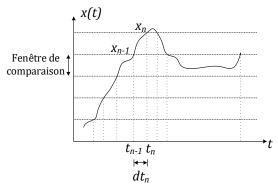

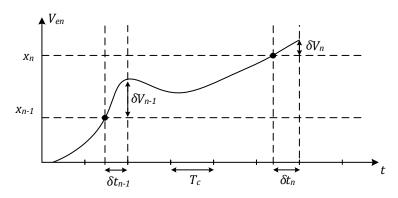

| Figure 2. 2 Erreur de quantification du temps dans un LC-ADC pour un signal quelconque                                  |        |

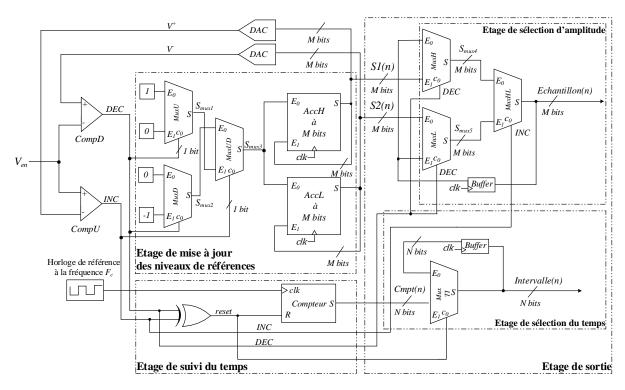

| Figure 2. 3 Modèle structurel du LC-ADC à <i>M</i> bits.                                                                |        |

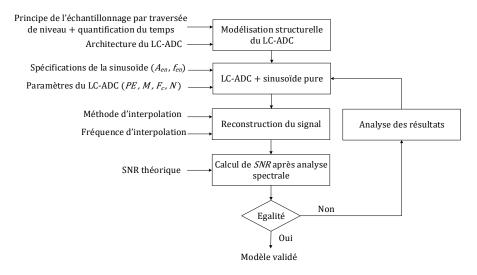

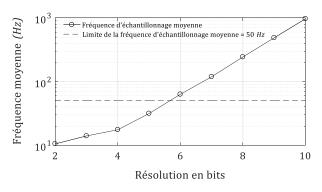

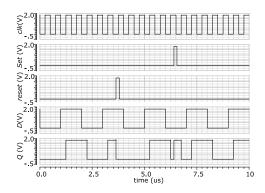

| Figure 2. 4 Méthodologie d'analyse du fonctionnement du LC-ADC avec un signal sinusoïdal                                |        |

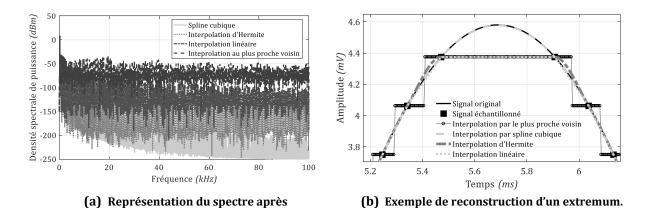

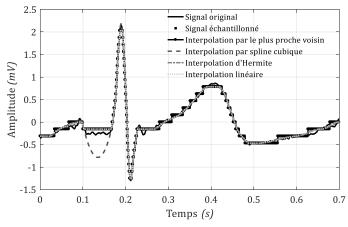

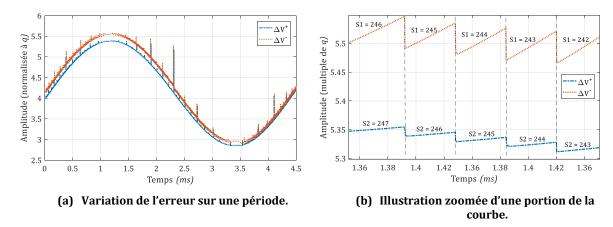

| Figure 2. 5 Comparaison de quatre algorithmes de reconstruction.                                                        |        |

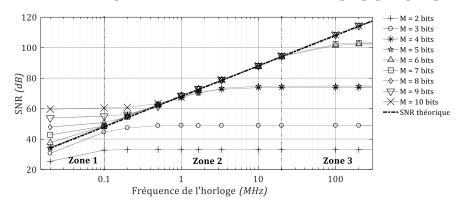

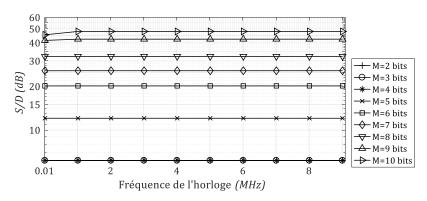

| Figure 2. 6 Variations du <i>SNR</i> en fonction de <i>M</i> et <i>F<sub>c</sub></i>                                    |        |

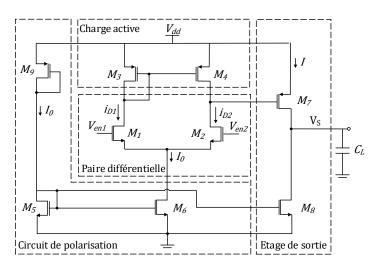

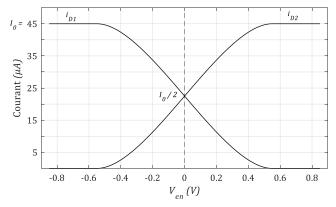

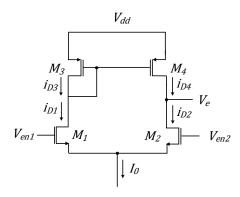

| Figure 2. 7 Circuit du comparateur                                                                                      |        |

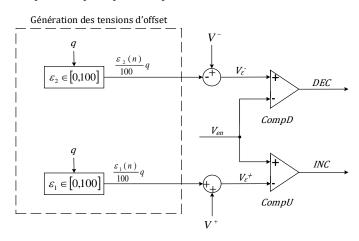

| Figure 2. 8 Modèle d'erreur de la tension d'offset.                                                                     |        |

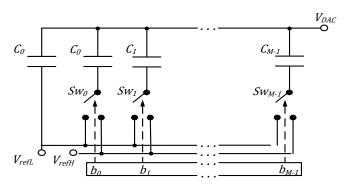

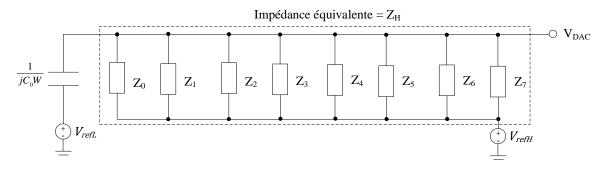

| Figure 2. 9 Architecture d'un DAC à division de charge de résolution <i>M</i> bits                                      |        |

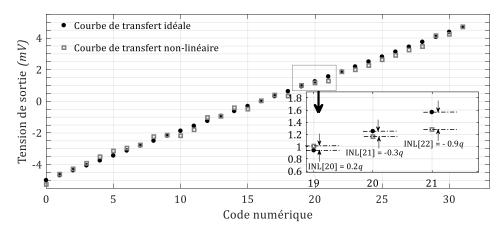

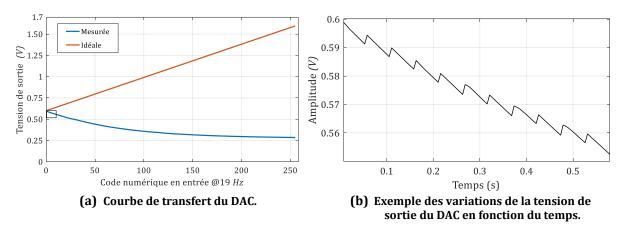

| Figure 2. 10 Exemple de courbes de transfert d'un DAC 5 à bits dans les cas linéaire et non-linéaire                    |        |

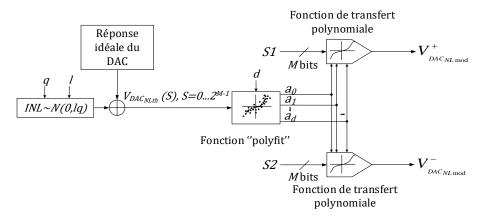

| Figure 2. 11 Modèle des erreurs de non-linéarité                                                                        |        |

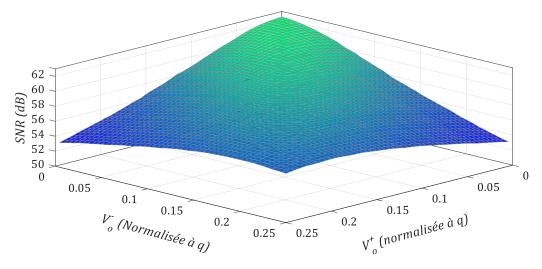

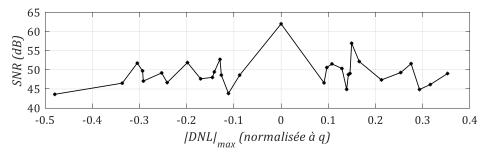

| Figure 2. 12 Variations du SNR en fonction des tensions d'offset des comparateurs                                       |        |

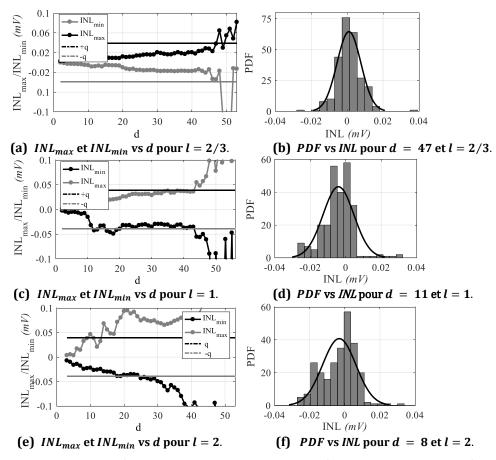

| Figure 2. 13 Estimation du degré de la fonction polynomiale modélisant les DACs non-linéaires pour                      | trois  |

| valeurs de l                                                                                                            | 53     |

| Figure 2. 14 Variations du SNR en fonction des erreurs de non-linéarité différentielle maximale pou                     | r une  |

| erreur d'INL entre ±q                                                                                                   |        |

| Figure 2. 15 Tracé du modèle d'un ECG normal                                                                            |        |

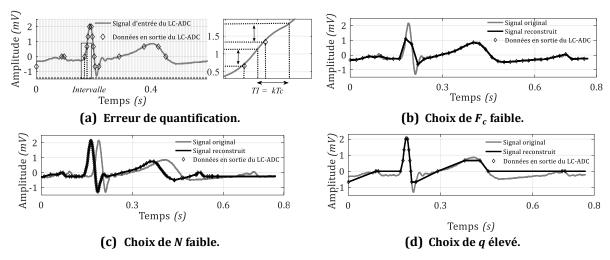

| Figure 2. 16 Erreurs systématiques liés aux mauvais choix des paramètres du LC-ADC                                      |        |

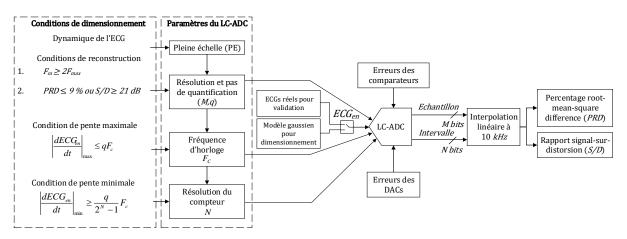

| Figure 2. 17 Méthodologie de dimensionnement et d'évaluation du LC-ADC                                                  | 58     |

| $Figure\ 2.\ 18\ Comparaison\ des\ performances\ de\ quatre\ algorithmes\ de\ reconstruction\ pour\ la\ reconstruction$ | iction |

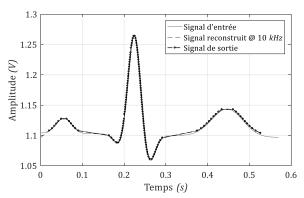

| du signal ECG.                                                                                                          |        |

| Figure 2. 19 Conditions de reconstruction pour le choix de M pour un modèle Gaussien d'un ECG no                        | rmal.  |

|                                                                                                                         |        |

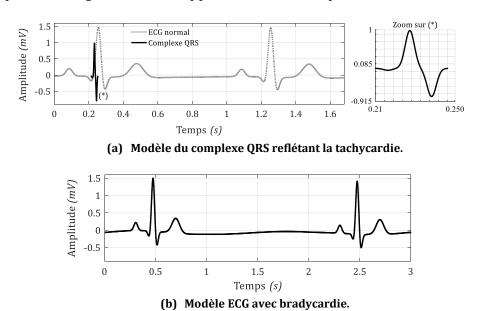

| Figure 2. 20 Modèles Gaussiens pour la représentation de la tachycardie et la bradycardie                               |        |

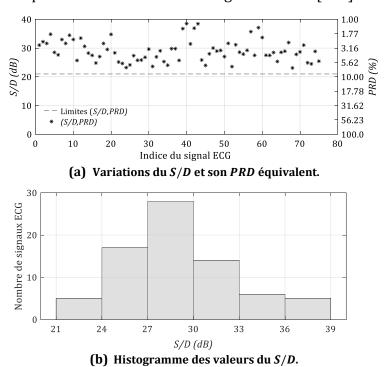

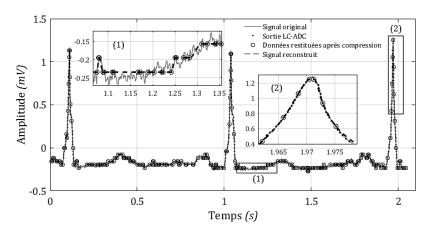

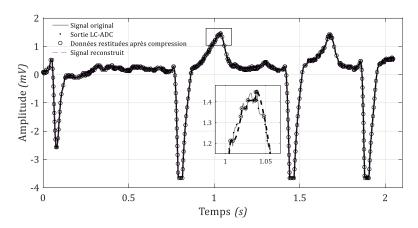

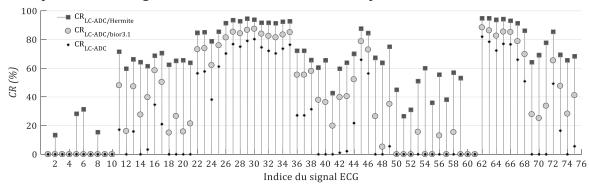

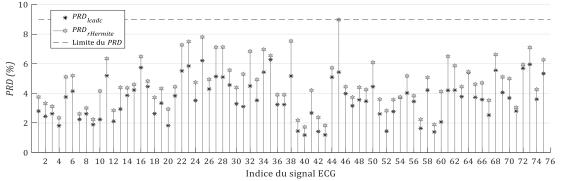

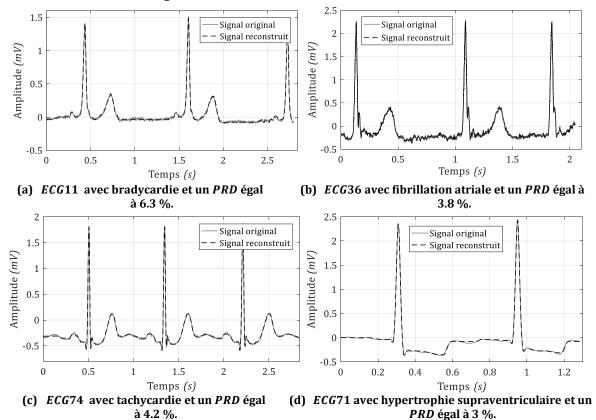

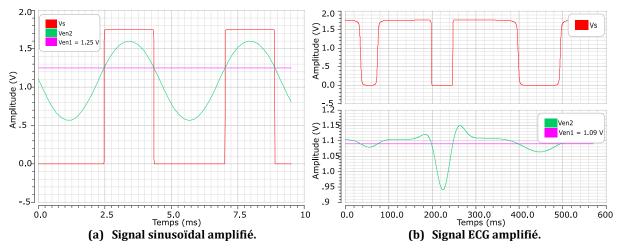

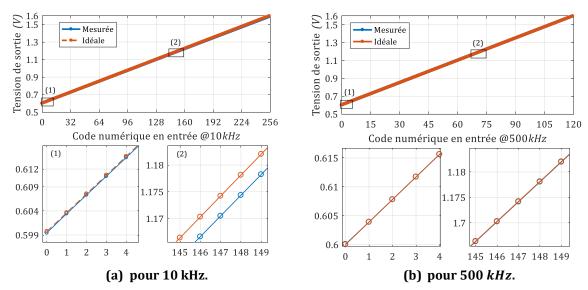

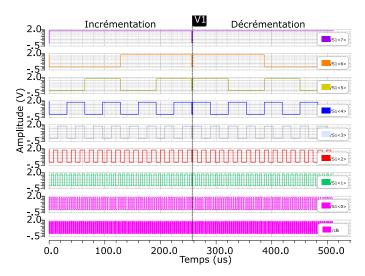

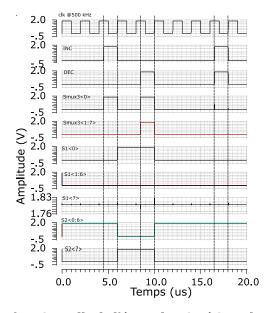

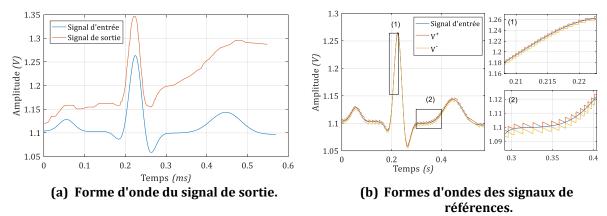

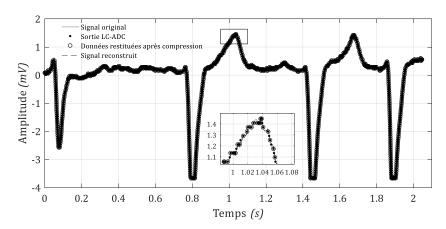

| Figure 2. 21 Résultats de simulation du modèle LC-ADC en utilisant 75 enregistrements d'ECGs réels.                     | 64     |

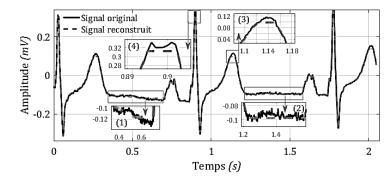

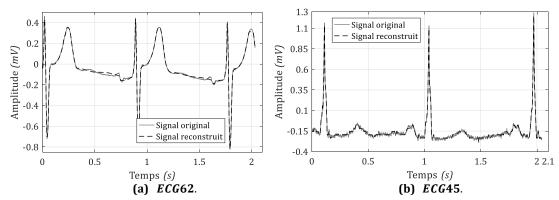

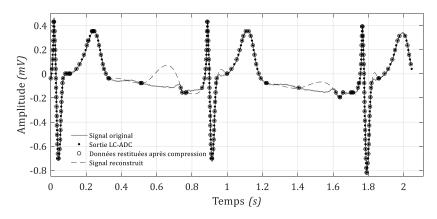

| Figure 2. 22 Deux exemples de signaux ECG avant et après échantillonnage et reconstruction                              |        |

| Figure 2. 23 Distorsions dans le signal <i>ECG68</i> dues à sa faible dynamique d'amplitude et au bruit                 |        |

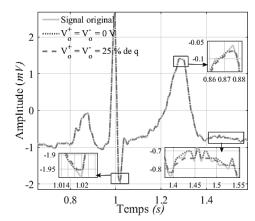

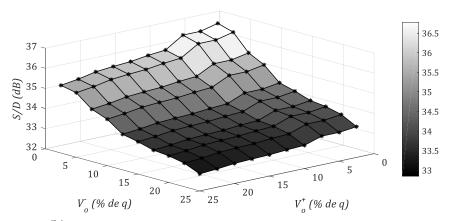

| Figure 2. 24 Résultats de simulation du LC-ADC avec une tension d'offset des comparateurs pour le c                     |        |

| signal ECG52                                                                                                            | 67     |

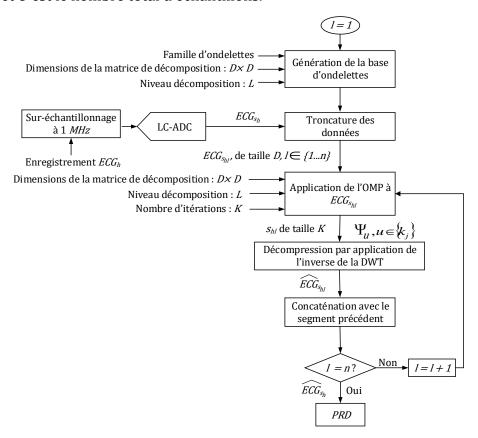

| Figure 3. 1 Schéma fonctionnel du système d'acquisition cardiaque                                                       | 72     |

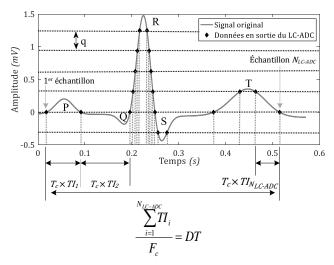

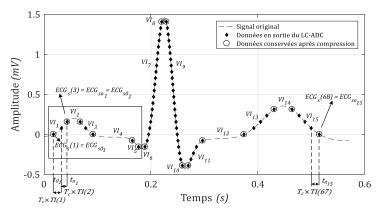

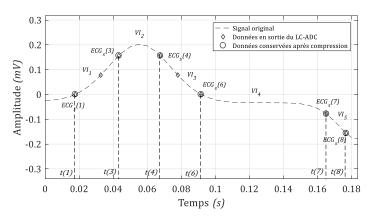

| Figure 3. 2 Signal ECG échantillonné par le LC-ADC.                                                                     |        |

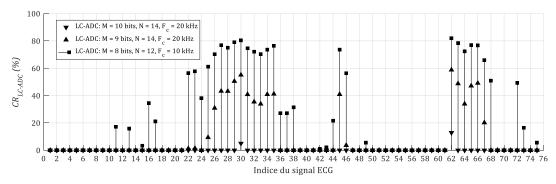

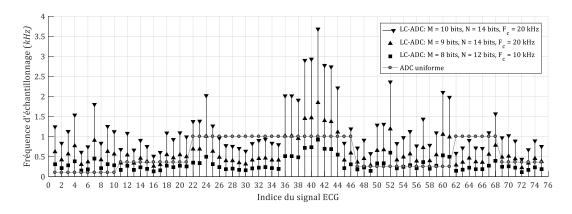

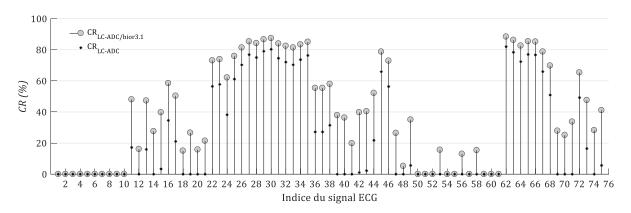

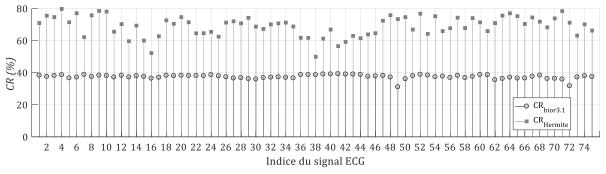

| Figure 3. 3 Variations du taux de compression pour différents signaux ECG, résolutions du com résolutions du LC-ADC.                                                                                                   |            |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

| Figure 3. 4 Variations de la fréquence moyenne d'échantillonnage pour différents signaux ECG, rés du compteur et résolutions du LC-ADC.                                                                                |            |

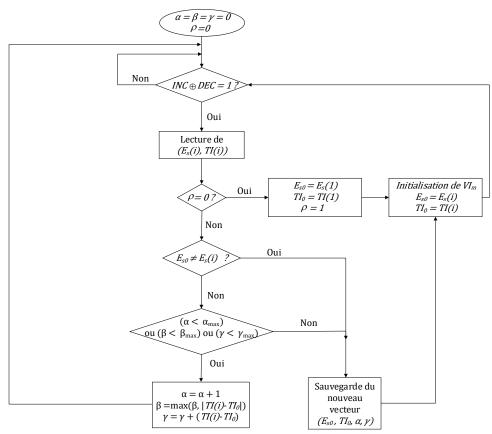

| Figure 3. 5 Organigramme de l'algorithme d'étude de compression.                                                                                                                                                       | 82         |

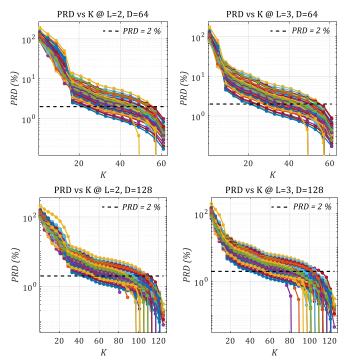

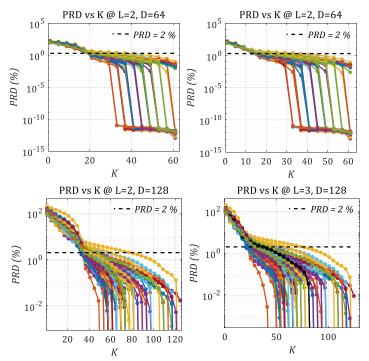

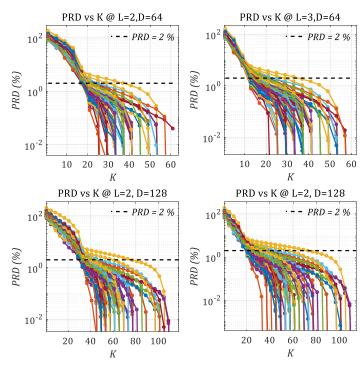

| Figure 3. 6 Variations du PRD en fonction du nombre d'ondelettes retenues pour le cas des ondelett                                                                                                                     |            |

| Figure 3. 7 Variations du <i>PRD</i> en fonction du nombre d'ondelettes retenues pour le cas des ondelet                                                                                                               | ttes db2.  |

| Figure 3. 8 Variations du PRD en fonction du nombre d'ondelettes retenues pour le cas des on bior2.2                                                                                                                   | delettes   |

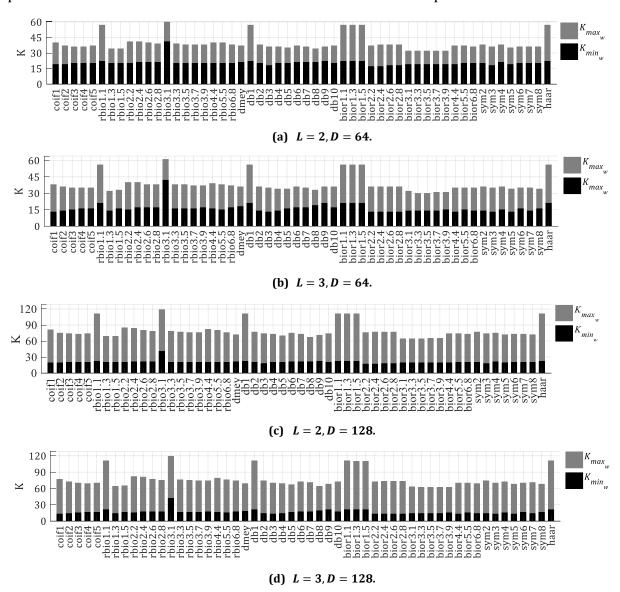

| Figure 3. 9 Variations du nombre d'ondelettes retenues pour un $PRD$ de 2 %, en fonction des d'ondelettes et des valeurs de $L$ et $D$                                                                                 |            |

| Figure 3. 10 Variations du taux de compression, CR, en fonction des signaux ECG                                                                                                                                        | 89         |