## Development of an Efficient Methodology for Modeling Parasitic Effects within a Broadband Test Circuit

Kassem Hamze

#### ▶ To cite this version:

Kassem Hamze. Development of an Efficient Methodology for Modeling Parasitic Effects within a Broadband Test Circuit. Electronics. Normandie Université, 2018. English. NNT: 2018NORMC232 . tel-01958150

### HAL Id: tel-01958150 https://theses.hal.science/tel-01958150

Submitted on 17 Dec 2018

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

### THÈSE

### Pour obtenir le diplôme de doctorat

### Spécialité ELECTRONIQUE, MICROELECTRONIQUE, OPTIQUE ET LASERS,

### **OPTOELECTRONIQUE MICROONDES**

Préparée au sein de l'Université de Caen Normandie

### Development of an Efficient Methodology for Modeling Parasitic Effects within a Broadband Test Circuit

### Présentée et soutenue par Kassem HAMZE

| Thèse soutenue publiquement le 06/11/2018<br>devant le jury composé de |                                                                      |                       |  |

|------------------------------------------------------------------------|----------------------------------------------------------------------|-----------------------|--|

| Mme NATHALIE DELTIMPLE                                                 | Maître de conférences HDR, IMS-Bordeaux                              | Rapporteur du jury    |  |

| M. JEAN-GUY TARTARIN                                                   | Professeur des universités, UNIVERSITE TOULOUSE 3 PAUL<br>SABATIER   | Rapporteur du jury    |  |

| M. EDOUARD DE LEDINGHEN                                                | Directeur, PRESTO-ENGINEERING CAEN                                   | Membre du jury        |  |

| M. CHRISTOPHE GAQUIERRE                                                | Professeur des universités, UNIVERSITE LILLE 1 SCIENCES ET TECHNOLOG | Président du jury     |  |

| M. VUONG TÂN-PHU                                                       | Professeur des universités, INP Grenoble                             | Membre du jury        |  |

| M. SIDINA WANE                                                         | Ingénieur HDR, E-V Technologies                                      | Membre du jury        |  |

| M. PHILIPPE DESCAMPS                                                   | Professeur des universités, 14 ENSI de Caen                          | Directeur de thèse    |  |

| M. DANIEL PASQUET                                                      | Professeur émérite, ENSEA                                            | Co-directeur de thèse |  |

Thèse dirigée par PHILIPPE DESCAMPS et DANIEL PASQUET, Laboratoire de cristallographie et sciences des materiaux (Caen)

# ACKNOWLEDGMENT

This work has been carried out under financial support of Presto Engineering Inc. This CIFRE thesis was realized through a collaboration among Ecole Nationale Supérieure d'Ingénieurs de Caen (ENSICAEN), Crismat laboratory, Presto Engineering Europe and NXP Caen.

In the following paragraphs, I would like to acknowledge all the people, who helped me, each of them in his/her own unique way, to accomplish my thesis.

First of all, I would like to thank all the members of the jury for their participation in the eight-party committee, including Mr. Jean Guy TARTARIN, Professor from University of Toulouse, LAAS, Mrs. Nathalie DELTIMPLE, Doctor and HDR from university of Bordeaux, IMS, Mr. Christophe GAQUIERE, Professor from University of Lille, IEMN and Mr. Tan Phu VUONG, Professor from University of Grenoble, IMEP-LAHC.

Also, I would like to acknowledge my supervisors. Prof. Philippe DESCAMPS, the director of my thesis from ENSICAEN (Caen, France), Prof. Daniel PASQUET, the co-director from ENSEA (CERGY, France) and Mr. Edouard DE LEDINGHEN, Test engineer leader from Presto Engineering Europe (Caen, France), for the assignment of this thesis, for their continuous support, guidance and for their ideas that in essence have been implemented in this project.

Furthermore, I would also like to acknowledge with much appreciation for Mr. Dominique LESENECHAL, who was always available to solve any technical problem and for Dr. Sidina WANE for his cooperation and support.

Above all, I want to thank my beloved parents and friends for their love, sacrifices, companion, patience and support during my academic years.

# **TABLE OF CONTENTS**

| TABLE OF CONTENTS                                     |

|-------------------------------------------------------|

| GLOSSARY11                                            |

| GENERAL INTRODUCTION14                                |

| I. CONTEXT AND STATE OF THE ART17                     |

| I.1 Introduction                                      |

| I.2 Context and motivation                            |

| I.3 Evolution of network Analyzer                     |

| I.3.1 Scalar network analyzer                         |

| I.4 Vector network analyzers                          |

| I.4.1 Measuring of S-parameters                       |

| I.4.2 SOLT calibration                                |

| I.5 Self calibration methods                          |

| I.5.1 TRL procedure                                   |

| I.6 Industrial context                                |

| I.6.1 Load board                                      |

| I.6.2 Device under test (DUT)                         |

| I.7 Conclusion                                        |

| II. TRL CALIBRATION TECHNIQUE AND DE-EMBEDDING METHOD |

| II.1 Introduction                                     |

| II.2 Methodology description for TRL calibration      |

| II.2.1 Standards definition                           |

| II.2    | 2.2 Calculation of the error terms                        |    |

|---------|-----------------------------------------------------------|----|

| II.3    | DUT embedded within a PCB                                 |    |

| II.4    | Two-port board setup                                      | 40 |

| II.4    | 1.1 Calibration steps                                     | 41 |

| II.4    | 1.2 DUT measurements                                      | 44 |

| II.5    | First validation of the method                            | 44 |

| II.6    | Conclusion and Perspectives                               | 48 |

| III. ME | ASUREMENT METHODOLOGY AND EXTRACTION RESULTS              | 50 |

| III.1   | Introduction                                              | 52 |

| III.2   | Characteristics of a device that undergoes test           | 53 |

| III.3   | Calibration standards: design model and fabrication       | 54 |

| III.    | 3.1 Design model                                          | 54 |

| III.    | 3.2 Calibration standards under fabrication               | 56 |

| III.4   | E.M simulation validation                                 | 57 |

| III.    | 4.1 PCB model                                             | 58 |

| III.    | 4.2 Use of E.M simulations for the calibration standards  | 58 |

| III.    | 4.3 Simulated measurements with an active two-port device | 59 |

| III.5   | Calibration standards behavior                            | 60 |

| III.    | 5.1 Measuring of standards by GS probes                   | 60 |

| III.    | 5.2 Verification of the calibration using standards       | 62 |

| III.6   | Measurement: evaluation and validation                    | 64 |

| III.    | 6.1 Board specification                                   | 65 |

| III.    | 6.2 Measurements validation                               | 65 |

| III.    | 6.3 Parasitic coupling effects                            | 68 |

| III.7 Applications to power measurements                         |               |

|------------------------------------------------------------------|---------------|

| III.7.1 Available power gain                                     |               |

| III.7.2 Insertion power gain                                     | 71            |

| III.7.3 Operating power gain                                     | 72            |

| III.7.4 Transducer gain                                          | 73            |

| III.8 Conclusion and Perspectives                                | 74            |

| IV. MULTI-PORT TRL CALIBRATION FOR DIFFERENTIAL                  | DEVICES76     |

| IV.1 Introduction                                                |               |

| IV.2 TRL mixed mode de-embedding method                          | 79            |

| IV.2.1 Natural modes                                             |               |

| IV.2.2 Mixed modes                                               |               |

| IV.2.3 In terms of power waves                                   |               |

| IV.2.4 Characteristic Impedance for non-coupled lines            |               |

| IV.2.5 S-matrix transformation between natural and mixed m       | odes83        |

| IV.3 Differential input and single output device                 |               |

| IV.3.1 S-matrix transformation                                   |               |

| IV.3.2 Z-matrix transformation for a single input and differen   | tial output85 |

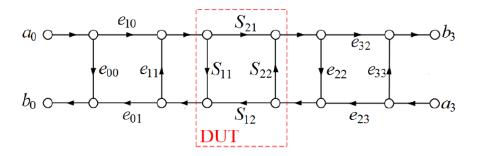

| IV.4 TRL calibration process                                     |               |

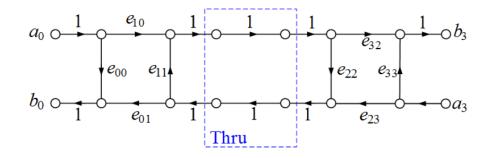

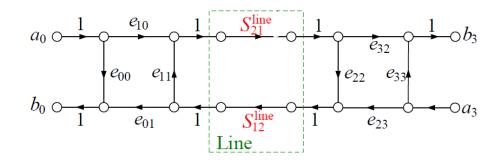

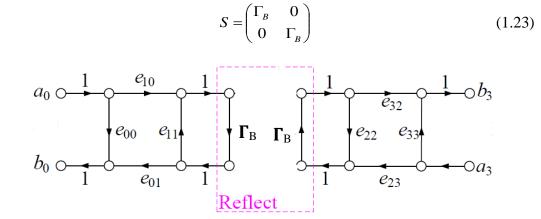

| IV.4.1 First TRL between P1 and P3 using Thru1, Line1 and I      | Reflect86     |

| IV.4.2 Second TRL between $P_2$ and $P_3$ using Thru2, Line2 and | d Reflect87   |

| IV.4.3 Determination of Z <sub>21</sub>                          |               |

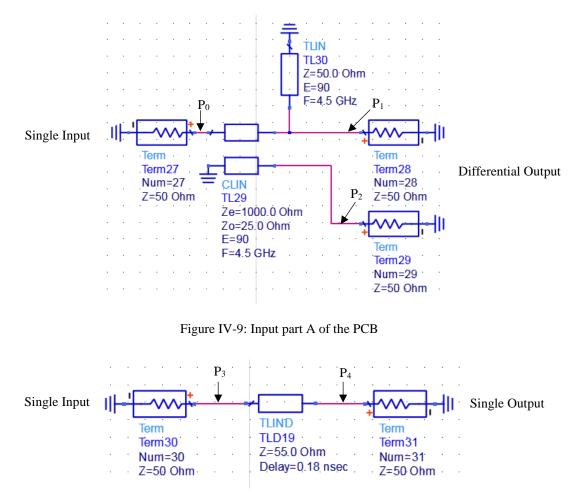

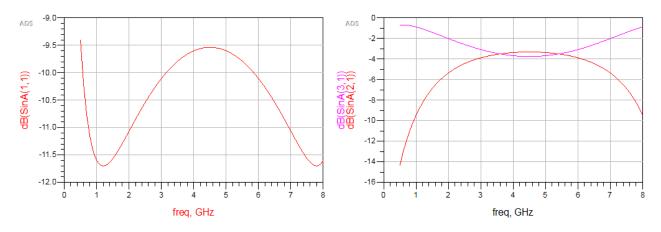

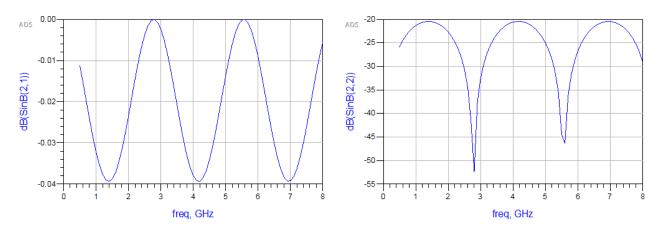

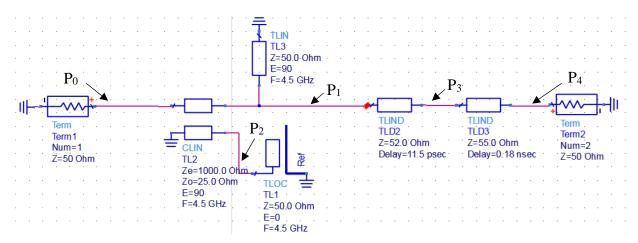

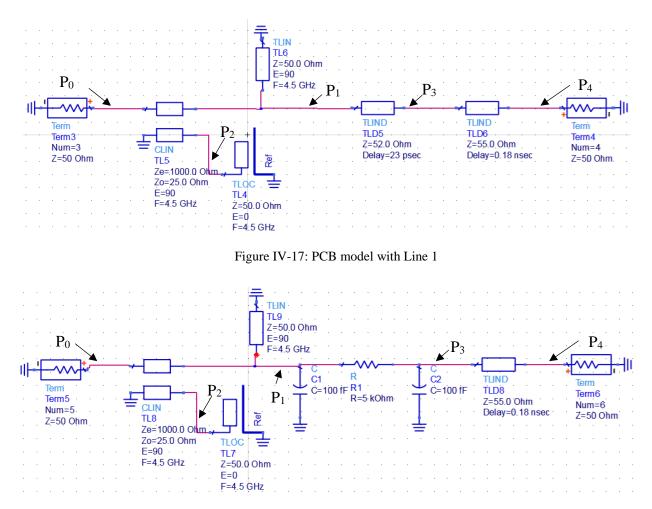

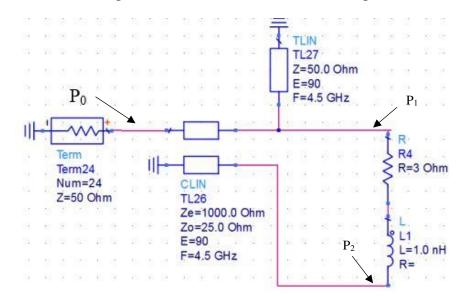

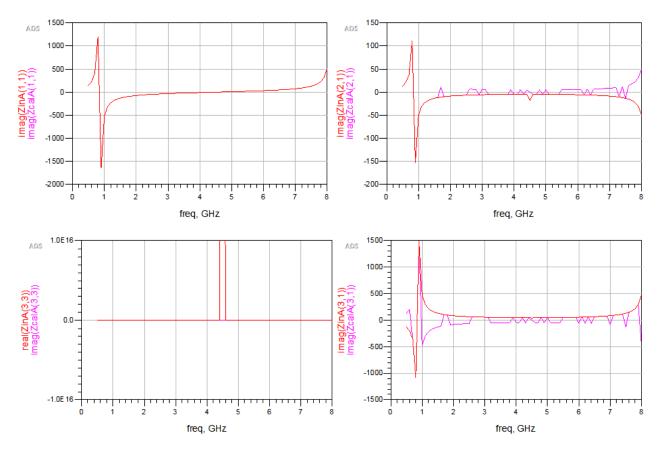

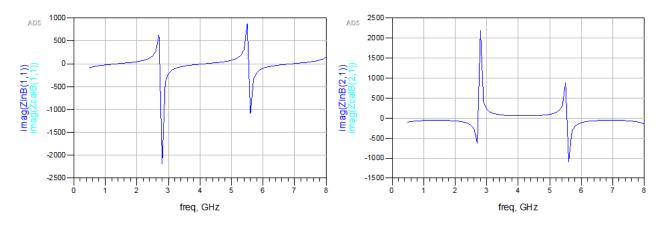

| IV.5 Circuit simulation using ADS                                | 90            |

| IV.5.1 Input/Output parts of PCB                                 | 90            |

| IV.5.2 Standards description with ADS elements                   | 91            |

| IV.                  | 5.3 Double TRL calibration and determination of $Z_{21}$ |  |

|----------------------|----------------------------------------------------------|--|

| IV.                  | 5.4 Initial vs. Calculated A and B parameters            |  |

| IV.6                 | Conclusion and Perspectives                              |  |

| V. GEN               | ERAL CONCLUSION AND PERSPECTIVES                         |  |

| <b>V</b> .1          | General Conclusion                                       |  |

| V.2                  | Perspectives                                             |  |

| REFER                | ENCES                                                    |  |

| LIST OF FIGURES      |                                                          |  |

| LIST OF PUBLICATIONS |                                                          |  |

| APPENDIX 1           |                                                          |  |

| APPENDIX 2           |                                                          |  |

| ABSTRACT130          |                                                          |  |

| RESUME               |                                                          |  |

# GLOSSARY

| ENSICAEN | Ecole Nationale Supérieure d'Ingénieurs de CAEN |

|----------|-------------------------------------------------|

| RF       | Radio Frequency                                 |

| mm       | Millimeter-Wave                                 |

| PCB      | Printed Circuit Board                           |

| VNA      | Vector Network Analyzer                         |

| DUT      | Device Under Test                               |

| SOLT     | Short-Open-Load-Thru                            |

| ADC      | Analogue Digital Converter                      |

| CW       | Continuous Wave                                 |

| CPW      | Coplanar Wave Guide                             |

| TRL      | Thru-Reflect-Line                               |

| SOLR     | Short-Open-Load-Reciprocal                      |

| LRM      | Line-Reflect-Match                              |

| TSD      | Thru-Short-Delay                                |

| HFSS     | High Frequency Structure Stimulator             |

| 3D       | 3 Dimensions                                    |

| 2.5D     | 2.5 Dimensions                                  |

| ADS      | Advanced Design System                          |

| GS       | Ground-Signal                                   |

| GSG      | Ground-Signal-Ground                            |

| e.m     | Electromagnetic-Simulation              |

|---------|-----------------------------------------|

| НВТ     | Heterojunction bipolar Transistor       |

| MMIC    | Monolithic Microwave Integrated Circuit |

| WLAN    | Wide Local Area Network                 |

| LNA     | Low Noise Amplifier                     |

| TX      | Transmitter Mode                        |

| RX      | Receiver Mode                           |

| PA      | Power Amplifier                         |

| ANT     | Antenna                                 |

| GND     | Ground                                  |

| TAR     | Thru-Antenna-Receiver                   |

| TAT     | Thru-Antenna-Transmitter                |

| LAR     | Line-Antenna-Receiver                   |

| LAT     | Line-Antenna-Transmitter                |

| RAR     | Reflect-Antenna-Receiver                |

| RAT     | Reflect-Antenna-Transmitter             |

| EVB     | Evaluation Board                        |

| Cal-Kit | Calibration Kit                         |

# **GENERAL INTRODUCTION**

#### 1. Thesis frame

The thesis subject is "Development of an Efficient Methodology for Modelling Parasitic effects within a Broadband Circuit". The thesis has been prepared in a common laboratory among Ecole Nationale Supérieure d'Ingénieurs de CAEN (ENSICAEN), Crismat laboratory, Presto Engineering Europe and NXP Caen.

The thesis subject was found, when engineers from the industrial environment start to complain form the difference in behavior between the test board and the final end product for the customers. The study begun by measuring an active device within a load board and to compare it with the same device soldered on the final application board. Many difficulties found during the characterization and modeling in order to locate the critical sources of errors which have lead to the next studies. Some works in this thesis are not only to resolve the error issues within the test board, but also to support our partners in industrial society to de-embed the errors from the final end product device and then be able to optimize the production yield.

#### 2. Organization of thesis manuscript

The manuscript is organized in 5 chapters.

- ✓ Chapter 1 presents the context and state of the art for the evolution of network analyzer and calibration methods. The purpose of chapter 1 is to give a global background of the different calibration methods that have been used during measurements and our new approach for a TRL technique. The state of art of the method developed in this thesis will be presented in details in the next chapters.

- ✓ Chapter 2 presents the new approach for the TRL technique and de-embedding method with analytical equations. The different calibration steps and de-embedding have been described and an overview scheme for a full two-port board setup has been shown with the placement of standards and reference planes. At the end of this chapter an example has been studied for the first validation.

- ✓ Chapter 3 concentrates on the measurement methodology and extraction of results. The device to be tested has been described and the design model and fabrication for the TRL standards have been shown. Then an evaluation and verification of the measurements have been done using an evaluation board by a comparison the measurement results with calculated ones.

- ✓ Chapter 4 presents a multi-port TRL calibration method for a differential device. It shows a mixed-mode TRL de-embedding method and a four-port measurement method using a two-port Vector Analyzer Network (VNA). This chapter introduces also a double TRL calibration methodology for a DUT with differential input and single output.

- ✓ Chapter 5 concludes the thesis with a summary of the obtained results. The perspectives and technical challenges are presented.

# CHAPTER I

# **CONTEXT AND STATE OF THE ART**

#### I.1 Introduction

Chapter I presents the objectives and motivation of the thesis in the background of the RF, mmwaves and the history of vector analyzers and calibration methods. This chapter is organized as follows. Paragraph I.2 shows the history of RF/microwave network analyzers. Then, paragraph I.3 presents an evolution of network analyzers. Paragraph I.4 shows a description of vector network analyzer with its measurement S-parameters and SOLT calibration errors. Furthermore, paragraph I.5 presents the self-calibration procedures and a de-embedding technique. Paragraph I.6 shows an overview scheme of a device embedded within a test socket in a load board, the place of reference planes where the measurements takes place and our new approach for TRL calibration. Finally, paragraph I.7 concludes chapter I.

#### I.2 Context and motivation

The RF/microwave network analyzer has enabled the evolution of high frequency components and how they are designed. The basic ability to measure transmission, reflection, and impedance properties of circuits and devices enables engineers to optimize the performance of amplifiers, frequency converters, signal separation and altering devices, and other components. The performance of communications and defense systems depends heavily on the capabilities of these components and their test systems [1-3].

Network analyzers — being vector measuring instruments — have the unique ability to apply error correction techniques to improve their accuracy. Initially, short circuits were used to establish the maximum level of reflection magnitude. Precision transmission lines, sliding loads, and sliding shorts were used as impedance standards. Precision attenuators, such as piston and rotary vane variable attenuators, were used to establish transmission loss reference levels. Such calibration methods were able to remove some of the measurement scalar errors [4-6]. The 8407 and 8410 swept frequency vector network analyzers made it possible to correct some of the vector errors. The 8542 made full vector error correction possible for the first time [7]. It also allowed imperfect standards, such as the open-standard, to be denied by a device model. The short-open-load through calibration method was fully enabled.

A surge in research on VNA calibration methods brought us the through-reflect-line family of calibrations, which was implemented in the 8510 [8]. Measurement accuracy became limited by

the accuracy of the calibration standards. Thus, ultra-precision reference transmission lines and slotless female contacts were introduced. Electronic calibration was invented to simplify calibration; a single connection and a software controlled sequence completed the process. Multi-port, differential, and non-linear calibration methods and standards are the current challenges [9].

#### I.3 Evolution of network Analyzer

Network Analyzer Architectures Historically, scalar network analyzers were a common tool used to characterize a network using only the magnitude of the signal. However, as network analysis technology matured, the development of digital components, such as analog-to-digital converters (ADCs), greatly simplified the design of vector network analyzers [10-12]. As a result, most modern VNAs are capable of measuring both scalar (magnitude) and vector (magnitude and phase) information about a signal.

#### I.3.1 Scalar network analyzer

Scalar network analyzers typically capture a broadband signal and convert it to DC or low frequency AC in order to measure the power of the signal. Examples of the hardware used to accomplish this include diodes and thermoelectric devices. The main advantage of scalar network analyzers is that the hardware required for down conversion and power detection is relatively simple and inexpensive. In addition, because the detectors are broadband devices, it is unnecessary to re-tune the receiver to measure power at a different frequency.

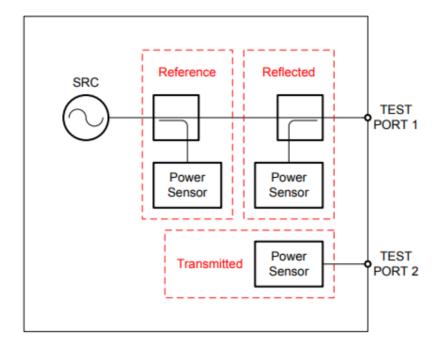

Thus, performing a frequency sweep is as simple as re-tuning the frequency of the microwave source and measuring the power at each frequency step [13]. Due to their relatively simple architecture, scalar network analyzers are capable of relatively fast frequency sweeps. Note that some scalar network analyzers simplify the hardware even further by removing the reference sensor. In these designs, however, a slightly more complicated measurement sequence is required. A simplified block diagram of a scalar network analyzer is shown in Fig. I-1.

Figure I-1: Simplified Scalar network analyzer block diagram

Scalar analyzers make transmission or insertion loss measurements by using a signal source that sweeps repetitively over the frequency range of interest. If the reference detector is not available, you can calculate the transmission coefficient as the power ratio of the transmitted signal with and without the device under test (DUT) in the signal path.

While scalar network analyzers have the benefit of simplicity of design, they are also prone to inherent challenges. For example, broadband detectors are susceptible to spurious tones and broadband noise. In addition, because the calibration is scalar in nature, it is not as accurate as full vector calibration. Due to their lack of selectivity, scalar network analyzers tend to have limited dynamic range compared to vector network analyzers.

#### I.4 Vector network analyzers

Vector network analyzers generally use full heterodyne receivers to measure both the phase and magnitude of signals and are often significantly more complex than scalar network analyzers. Measurements made with vector network analyzers are often more accurate, and the narrowband nature of the receivers provides better rejection of broadband noise and spurious tones, allowing for improved dynamic range. Furthermore, calibration can use more complex error models, which provide greater accuracy [15]. Due to the complexity of the heterodyne receiver architectures of

vector network analyzers, these instruments generally perform frequency sweeps more slowly than broadband scalar network analyzers. In addition, the added complexity often makes them more expensive.

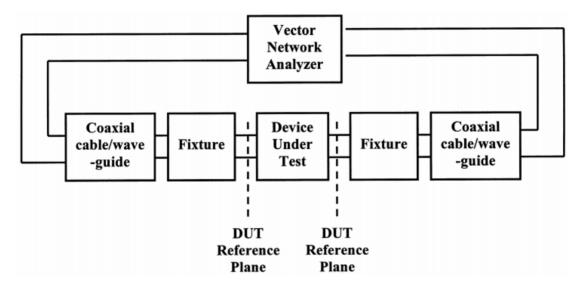

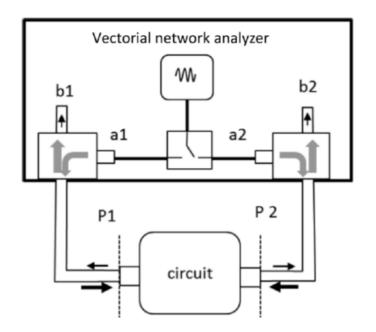

The fundamental principle of a vector network analyzer is to measure the amplitude and phase of both incident and reflected waves at the various ports of the DUT. The general design of a VNA is to stimulate an RF network at a given port with a stepped or swept continuous wave (CW) signal and to measure the travelling waves, not only at the stimulus port but at all the ports of the network terminated with specific load impedances, typically 50 Ohms or 75 Ohms. Often, the device under test (DUT) is fabricated in a noncoaxial or waveguide medium and thus requires fixtures and additional cabling to enable an electrical connection to the VNA [16]. A typical but simplified VNA architecture is illustrated in Fig. I-5.

Figure I-2: Overall scheme for vector network analyzer

#### I.4.1 Measuring of S-parameters

The measurement of S parameters assumes a generator making it possible to send a signal on the device and to measure the signal reflected. This assumes that we are working with a reference impedance  $Z_0$  to determine the reflection coefficient. In most applications, this reference impedance, also called access impedance, is equal to 50  $\Omega$ .

Figure I-3: Simplified operating principle of a vector network analyzer

The device is connected to the analyzer by high-quality radiofrequency cables over which the incident signal and the reflected signal propagate at the same time as shown in Fig. I-6. The measurement of S<sub>1</sub> parameters is based on the alternating application of signals  $a_1$  and  $a_2$  and the separation of the reflected signal from the incident signal at the coupler from the active access side, and the measurement of the signal transmitted from the other side [17]. The impedances of the different access points being equal to the reference impedance  $Z_0$ , we measure the S parameters.

These measurements allow us to take losses and dispersal in the cables into account, as well as directivity defects in the couplers [18-19]. These corrections are made via stages of calibration prior to any measurement. Calibration of a vector network analyzer enables us to correct the various systematic errors due to the test system: losses and directivity defects in couplers and conversion losses in detectors.

#### I.4.2 SOLT calibration

The Short-Open-Load-Thru is the oldest, most used and widely adopted calibration technique. It has been developed for simple reflectometer VNAs assuming that forward and reverse measurements are made by independent setups [20-21]. The simplest form of calibration uses three loads: short circuit, open circuit, and 50  $\Omega$  load (SOLT: short, open, load, thru).

Standard calibrations are used to correct the effects of cables and vector network analyzer components in order to place reference planes in  $P_1$  and  $P_2$ .

In a vector analysis bench, we must correct the following various types of errors:

- Systematic errors: losses and directivity defects in couplers, detector conversion losses, signal frequency variations, etc.

- **4** Random errors: component noise, switcher and connection repetitiveness.

- Characteristic derivatives: thermal derivatives, contact aging, physical modification of cables, etc.

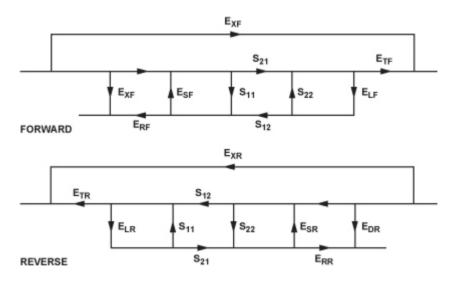

Figure I-4: Systematic errors in vector network analyzer

Although the location of the reference plane on VNA measurements is one factor that affects measurement results, VNAs are also subject to a range of inherent instrument impairments that can also be accounted for through calibration. In general, there are four main contributions to this imperfection.

The various errors in Fig. I-7 correspond to:

- $\downarrow$  E<sub>DF</sub>, E<sub>DR</sub>: directivity;

- $\downarrow$  E<sub>RF</sub>, E<sub>RR</sub>: reflection tracking;

- $\downarrow$  E<sub>XF</sub>, E<sub>XR</sub>: isolation;

$\downarrow$  E<sub>LF</sub>, E<sub>LR</sub>: Load match;

F & R: forward and reverse respectively.

The sources of error listed above are often referred to as systematic sources of error because they systematically affect the measurement at all times [22]. The effects of systematic errors on a measurement result, shown in Fig. I-4, can largely be removed through calibration.

#### I.5 Self calibration methods

Network analyzer self-calibration procedures for the eight-term error model have been available for over 20 years [23-24]. The self calibration methods have been developed for double reflectometer VNAs as shown in Fig. I-3. As far as only one setup is considered, the model can be described by a unique flow chart where some terms in Fig. I-4 are equal (e.g  $E_{SF} = E_{LR}$ ). A correction procedure is sometimes used to eliminate the switching errors due to a non-ideal source and load match. This, together with the isolation measurement, extends the eight-term model essentially to the 12-term error model.

The accuracy of network analyzers is enhanced by calibrating the setup at its measurement ports. Usually this is performed by applying the well-known 12-term procedure, employing the standards thru, match, short and open [25-26]. While the 12-term procedure depends only on fully known standards, there are some other methods in use allowing for partly unknown standards.

There are many self calibration techniques which differ by the kind of standards and the math adopted. They were introduced in as TSD (thru, short, delay), in as LRM (line, reflect, match) [27-28] and in as TRL (thru, reflect, line) [29]. They can be implemented in a double reflectometer as shown in as well as in other configurations.

Here the more common ones are presented and in particular those called:

- Thru-Reflect-Line

- Line-Reflect-Match

- Thru-Short-Delay

LRM is a particular case of TRL which has many characteristics as broad band performances and where the VNA reference impedance is set by the load.

#### I.5.1 TRL procedure

This technique uses a Thru which is typically either a direct connection between the ports, a longer Line and an unknown reflection standard [30-32].

The main characteristics of the TRL calibration are:

1. The propagation constant of the line is obtained as a by-product of the calibration.

2. The characteristic impedance of the line sets the reference impedance of the VNA.

3. The length difference between the line and the thru does not have to be a multiple of the wavelength.

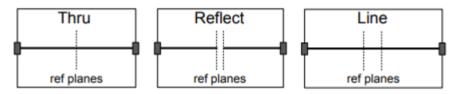

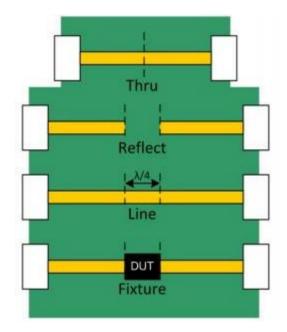

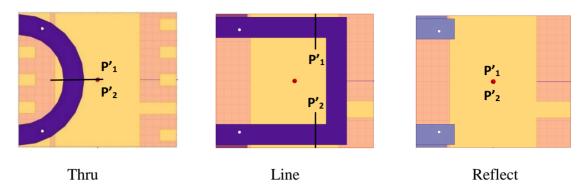

This calibration makes it possible to place reference planes on a printed circuit using calibration components created by the user, compatible with the device being tested [33-36]. Calibration devices are shown in Fig. I-5.

Figure I-5: TRL calibration standards

The creation of the calibration components in Fig. I-5 must comply with the following rules:

- **4** Thru: the two access points are connected to one another by a line of length  $La_1 + La_2$ .

- Reflect: a printed circuit is created in which the lines are open at the level of the reference planes.

- Line: we need a line with an excess length  $\Delta L$  on a frequency band. We can show that it must introduce a phase difference, different from  $k\pi$ , between the low frequency and the high frequency of the band. The minimum measurable phase difference is estimated at 15°, and the phase introduced by the line between access points between 15° and 165°, for a band ratio  $F_{\text{max}}/F_{\text{min}} = 11$ .

For all devices, the access points must be as reproducible as possible in order to minimize errors.

#### I.6 Industrial context

The development of interconnected devices and communication technologies has put on the market billions of RF semiconductor units. The modulation scheme complexity, always increasing to improve the data rate pushes the RF technology towards its limits in term of noise level or signal quality. Testing such parameters with the right accuracy is then becoming really challenging. Previous methods, only based on simple rules to design a clean RF load boards are not enough to keep the expected yield level. It is now required to have an accurate picture of all losses and distortions brought by the test fixture to the measurement. The challenge is here to be able to set the test limits with more accuracy, in order to clearly isolate the device performance from the test fixture influence.

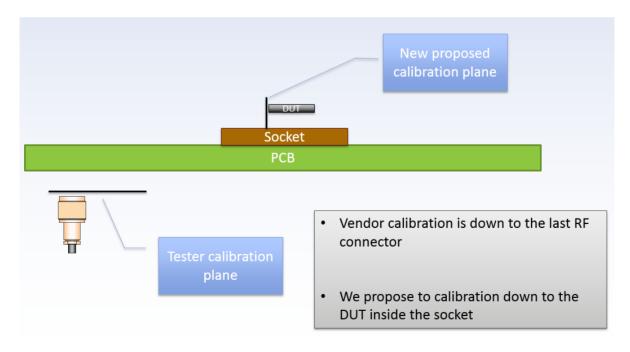

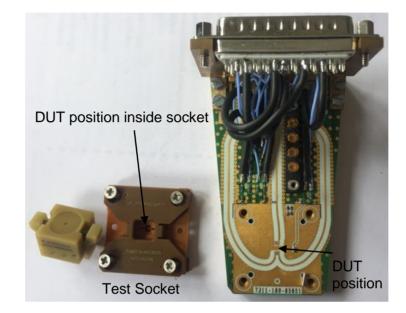

#### I.6.1 Load board

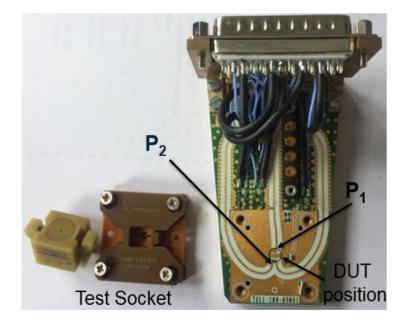

For its measurement, a device under test (DUT) is embedded into a socket which is embedded in a measurement board. The measurement is performed using a vector network analyzer (VNA) at the outer accesses of the board after an appropriate calibration [37-38]. The de-embedding is a method which consists of removing the unwanted elements (the board and the socket) in order to reach the characteristics of the circuit itself as shown in Fig. I-6 below.

To make the de-embedding possible, a calibration is necessary. It consists of finding the right method to extract the parameters of the input and output accesses. We propose to define convenient elements that will be placed instead of the circuit. Many methods exist, but they use calibration circuits that are not compatible with the geometry of our equipment.

One of the most accurate and efficient method is TRL (Thru-Reflect-Line). The detailed analytical calculation is shown in **Appendix 1**. But the characteristic impedance of the line must be known. That means that we need to design the line on a well-known substrate with well-known geometry [39].

De-Embedding is a process that removes the effects of unwanted portions of the structure that are embedded in the measured data by subtracting their contribution. However, just as in an RF measurement, understanding of the inner workings of the process can sometimes allow you to design our circuits in such a way as to produce more accurate results or analyze our circuit more efficiently.

#### I.6.2 Device under test (DUT)

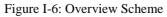

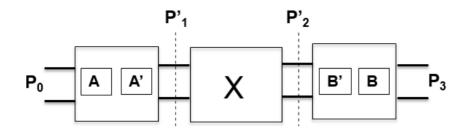

For control, DUTs are placed inside a test board. Measurement setups can collect the information between the input and output ports of the board. We must remove by calculation the parts of the board situated between the board ports and the DUT ports. This operation is called "de-embedding". It uses vector network analyzer measurements.

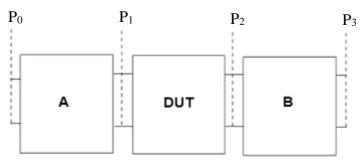

The measurement test board is described in Fig. I-7. It appears three two-ports: the input accesss (between  $P_0$  and  $P_1$ ), the output accesses (between  $P_2$  and  $P_3$ ) and the device under test itself (between  $P_1$  and  $P_2$ ). They can be described by their S-parameters (or other parameters).

Figure I-7: Overview two-port board

In order to get the total response of the system we will have to handle the S- parameters matrices. In order to simplify the task somewhat, it is convenient to use the T-parameters representation of the block. Therefore:

$$\mathbf{T}_{\text{measured}} = \mathbf{T}_{\text{IN}} * \mathbf{T}_{\text{DUT}} * \mathbf{T}_{\text{OUT}}$$

[I-1]

#### I.7 Conclusion

The calibration of two-port VNAs has greatly enhanced the measurement accuracy of microwave devices. In the following chapter we will show the analytical calculation of TRL calibration methodology and de-embedding technique, based on the eight-term error model of a two port vector network analyzer measurement system. Then eight error terms of fixtures are derived directly from the S parameters of the fabricated calibration standards measured from the coaxial reference plane.

To test our algorithm, first we use a load board with a socket be measured which is used normally in production to test thousands of devices between reference PCB board plane (RF coaxial connectors) within short period of time and an evaluation board with a soldered device and without socket to measure the device's behavior.

# CHAPTER II

# TRL CALIBRATION TECHNIQUE AND DE-EMBEDDING METHOD

# **II.1** Introduction

In measuring circuits at microwave frequencies, it is essential to access the DUT (Device Under Test) at a known reference plane, particularly when measuring devices whose characteristics are affected simultaneously by input and output impedances. A major problem encountered when using vector network analyzer to obtain the S-parameters of a DUT is the need to separate the errors of the fixtures, transmission lines etc... The S- parameters of those errors are consequently introduced into the measurement results as errors. To get the S parameters of DUTs, the effect of the errors should be removed [40-41].

Various calibration techniques are used to measure devices at microwave frequencies. One of those techniques using standards of a "thru" line, "reflect". TRL is one type in a family of two-port self-calibrations that better support on-wafer measurements and test fixtures.

The chapter is built around four main sections:

- The first section describes the methodology used to perform our new approach for TRL calibration.

- The second section presents in details the analytical calculations for achieving calibration and de-embedding for a single input/output device.

- ✤ The third section shows an extraction of device's behavior by our study.

- The final section discusses the final results of an applied example which by comparison with simulations confirm the studied done.

# **II.2** Methodology description for TRL calibration

We plan to use the TRL calculations in an original manner. As the TRL standards are not available in our technology, we design and fabricate specific standards that are inspired from TRL [42]. Each standard is previously characterized, either with an electromagnetic simulation or an on-wafer measurement.

The Thru-Reflect-Line (TRL) calibration algorithm and several of its' variants are frequently described as providing the best opportunity for the most accurate VNA measurements [43]. Foundations for this perspective are partially driven from the fact that, unlike with some calibration

algorithms (Short-Open-Load-Thru for example) the response of the calibration standards need not be known a priori. This allows the standards to be patterned in the same substrate and with the same launch transition behavior as the device under test (DUT).

# II.2.1 Standards definition

Figure II-1: TRL calibration model

The creation of the calibration standards in Fig. II-1 must comply with the following rules:

**4** Thru: Ideally, a zero length through line where the measurement ports are directly connected.

The S-matrix of thru is:

$$S = \begin{pmatrix} 0 & 1 \\ 1 & 0 \end{pmatrix}$$

[II-1]

Reflect: A highly reflective device (most often a short or open). The absolute reflection coefficient is derived from the additional standard measurement information, but knowledge of the electrical length must be within one-fourth wavelength to ensure proper identification of the standard.

It is important to use the identical reflection standards to calibrate both ports. If the phases of the reflection coefficients are equal, the reference planes are situated in the middle of the thru. A printed circuit can be created in which the lines are open at the level of the reference planes. For on-wafer measurement, the reflect may be obtained by lifted probes.

The S-matrix of reflect is:

$$\mathbf{S} = \begin{pmatrix} \Gamma & T \\ T & \Gamma \end{pmatrix}$$

[II-2]

Where  $|T| \ll |\Gamma|$

Line: A nonzero length through line with the same intrinsic impedance as the through standard. The difference between the phase shifts of the line and thru standards require a minimum of 15 degrees to 165 degrees. It is not necessary to know the propagation constant because it is calculated from the extra measurement information. But the reference impedance is equal to the characteristic impedance of the line. It must be known before measurement (when it exists for TEM and quasi-TEM modes) if necessary by the use of an electromagnetic simulator.

The required phase relationship between the thru and line standards creates restrictions on the frequency span that can be measured with a given though and line combination. If a larger frequency span is needed, use multiple lines must be used.

The S-matrix of line is:

$$S = \begin{pmatrix} 0 & X \\ X & 0 \end{pmatrix}$$

[II-3]

For an actual line  $X = e^{-\varkappa}$

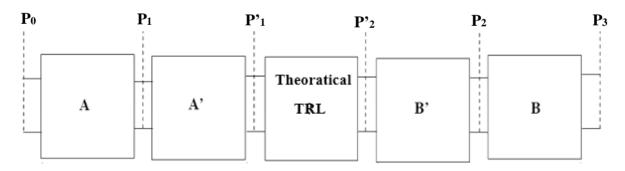

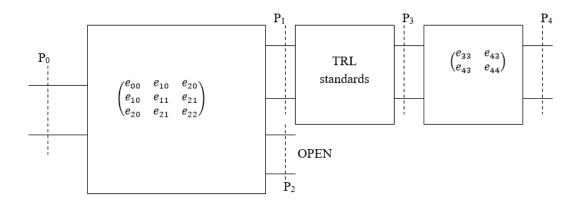

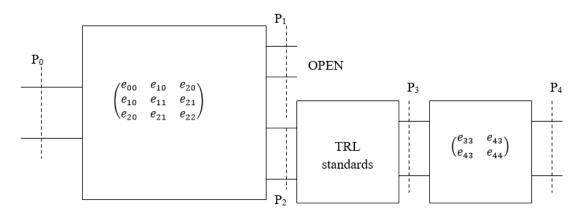

Figure II-2: Two-port measurement setup

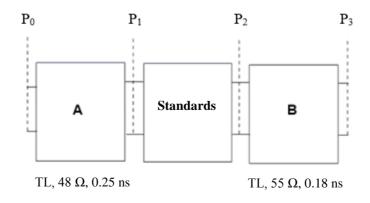

Fig. II-2, describes the measurement setup. Planes  $P_0$  and  $P_3$  are the input and output ports of the board. A first full-two-port calibration is made between these planes (e.g. SOLT between SMA connectors). The two-port A and B represent respectively the input and output accesses of the board.  $P_1$  and  $P_2$  are the reference planes of the DUT. The DUT and the calibration elements are placed between  $P_1$  and  $P_2$ .

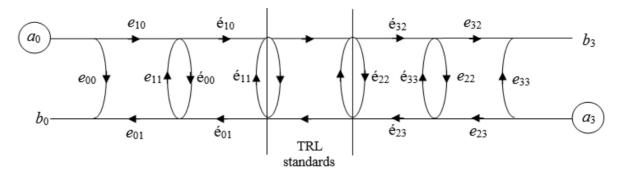

#### **II.2.2** Calculation of the error terms

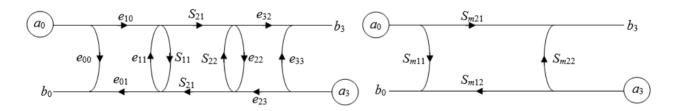

For a full analytical calculation about the TRL calibration and de-embedding method please refers to **appendix 1** at the end of manuscript. Generally, the calculation is presented with matrices handling [44]. The proposed calculation is completely analytical and can be easily introduced into a measurement software for fast quick operations.

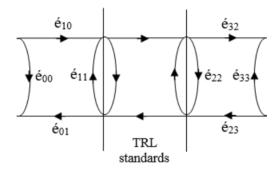

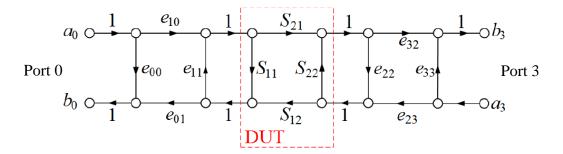

The flow chart on the left handed side shows the system of errors terms distributed within the setup of two-port measurement. It is the 8-term error model which should have been described in chapter 1. While the right handed one corresponds to the S-parameters measured by the VNA between planes  $P_0$  and  $P_3$ .

Figure II-3: Distribution of system of errors within two-port network

## **II.3 DUT embedded within a PCB**

For a TRL calibration between VNA reference ports, the input impedance of a planes  $P_1$  and  $P_2$  of the VNA are not matched. In our case we deal with corrected measurements after the SOLT calculation between the RF coaxial input/output connectors. The "corrected VNA" ports are matched.

In our case, we cannot have exact TRL standards. We must find a new method compatible with our facilities [45-47]. The De-embedding technique that we propose in our project, must extract the input and output error terms at the level of DUT i.e RF feed transmission lines effects, fixture

effects etc... and to shift the reference test planes from RF coaxial connectors till the position of pins where the device under test lies.

Fig. II-4& II-5 show the load board setup. The DUT is put in the middle of the test socket which is embedded into a board.  $P_1$  and  $P_2$  are defined in the middle of the socket,  $P_0$  and  $P_3$  are defined in the SMA connector reference planes.

Figure II-4: RF coaxial input/output ports

Figure II-5: Load board setup

We will design and fabricate standards that are not exactly TRL standards as shown in Fig. II-6.

Figure II-6: Examples of fabricated standards

The calibration standards have been chosen not too far from the TRL (thru-reflect-line) standards. But for our method, their S-parameters must be known. In a first approach, they have measured by on-wafer GS probes or simulated with an E.M simulator (e.g HFSS, CST). So, we know exactly what we put between planes  $P_1$  and  $P_2$  during the calibration.

# II.4 Two-port board setup

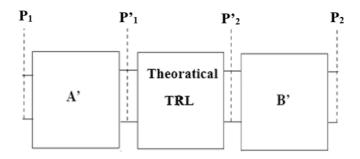

The calibration standards placed between  $P_1$  and  $P_2$  are virtually split into three two-ports. In the middle, between the fictitious planes  $P'_1$  and  $P'_2$ , the theoretical TRL standards are placed as shown in Fig. II-7. That means that the two-ports A' and B' transform the actual calibration elements into TRL virtual standards.

Figure II-7: Reference plane's distribution for two-port board

We assume that each standard consists of an ideal TRL standard (between  $P'_1$  and  $P'_2$  in Fig. II.2) embedded into fictitious two-ports A' (between  $P_1$  and  $P'_1$ ) and B' (between  $P'_2$  and  $P_2$ ). That means that the two-ports A' and B' transform the actual calibration elements into TRL virtual standards.

Figure II-8: Identification of errors for a two-port board

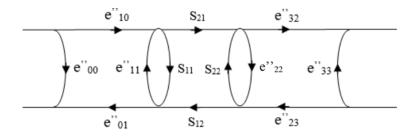

Once the three calibration standards have been measured between  $P_1$  and  $P_2$ , the board including the elements is measured using the SOLT calibration between  $P_0$  and  $P_3$ . A TRL calculation gives the characteristics of A' and B'. The board including the elements is measured between  $P_3$  and  $P_4$ . Another TRL calculation gives the characteristic of AA' and B'B.

The characteristics of two-port A and B will be useful for the de-embedding. During the measurement itself, the DUT is placed between planes  $P_1$  and  $P_2$ . The measurement is made between  $P_0$  and  $P_3$ . Using transfer matrices, we have to remove A and B to reach the DUT parameters [48].

In the following, the "TRL" calibrations are simplified by:

- > They use calibrated measurement. After correction, the situation is like if  $a_3=0$  for the forward measurements and  $a_0=0$  for the reverse measurement.

- > All the two-ports are physically reciprocal passive. So, in the calculation of the error terms  $e_{10}=e_{01}$  and  $e_{32}=e_{23}$ .

## **II.4.1** Calibration steps

## 📥 Step 1:

On-wafer GS calibration between P<sub>1</sub> and P<sub>2</sub> when necessary.

## **4** Step 2

On-wafer measurement between  $P_1$  and  $P_2$  with the three circuits between  $P_1$  and  $P_2$ .

Figure II-9: Planes configuration for a standard

TRL calculation giving  $e'_{ij}$  or electromagnetic simulation.

Figure II-10: Error terms in a standard

$$\mathbf{S}_{\mathbf{A}'} = \begin{pmatrix} e'_{00} & e'_{10} \\ e'_{10} & e'_{11} \end{pmatrix} \qquad \mathbf{S}_{\mathbf{B}'} = \begin{pmatrix} e'_{22} & e'_{32} \\ e'_{32} & e'_{33} \end{pmatrix}$$

[II-4]

$$\mathbf{T}_{\mathbf{A}'} = \begin{pmatrix} -\frac{e_{00}'e_{11}' - e_{10}'^2}{e_{10}'} & \frac{e_{00}'}{e_{10}'} \\ -\frac{e_{11}'}{e_{10}'} & \frac{1}{e_{10}'} \end{pmatrix} \qquad \mathbf{T}_{\mathbf{B}'} = \begin{pmatrix} -\frac{e_{22}'e_{33}' - e_{32}'^2}{e_{32}'} & \frac{e_{22}'}{e_{32}'} \\ -\frac{e_{32}'}{e_{32}'} & \frac{1}{e_{32}'} \end{pmatrix}$$

[II-5]

# 4 Step 3

Coaxial SOLT calibration between P<sub>0</sub> and P<sub>3</sub>

# \rm **Step 4**

Measurement between  $P_0$  and  $P_3$  with the three circuits between  $P_1$  and  $P_2$ .

Figure II-11: Planes configuration for a measurement setup

TRL calculation giving *e*''<sub>*ij*</sub>.

Figure II-12: Distribution of error terms between RF coaxial connectors

$$\mathbf{S}_{\mathbf{A}\mathbf{A}'} = \begin{pmatrix} e_{00}'' & e_{10}'' \\ e_{10}'' & e_{11}'' \end{pmatrix} \qquad \qquad \mathbf{S}_{\mathbf{B}'\mathbf{B}} = \begin{pmatrix} e_{22}'' & e_{32}'' \\ e_{32}'' & e_{33}'' \\ e_{32}'' & e_{33}'' \end{pmatrix}$$

[II-6]

$$\mathbf{T}_{\mathbf{A}\mathbf{A}'} = \begin{pmatrix} -\frac{e_{00}'' e_{11}'' - e_{10}''^2}{e_{10}''} & \frac{e_{00}''}{e_{10}''} \\ -\frac{e_{11}''}{e_{10}''} & \frac{1}{e_{10}''} \end{pmatrix} \qquad \mathbf{T}_{\mathbf{B}'\mathbf{B}} = \begin{pmatrix} -\frac{e_{22}'' e_{33}'' - e_{32}''^2}{e_{32}''} & \frac{e_{22}''}{e_{32}''} \\ -\frac{e_{33}''}{e_{32}''} & \frac{1}{e_{32}''} \end{pmatrix}$$

[II-7]

4 Step 5

Extraction of the error model

$$T_A = T_{AA'} T_{A'}^{-1}$$

;  $T_B = T_{B'}^{-1} T_{B'B}$  [II-8]

#### **II.4.2 DUT** measurements

Measurement between  $P_0$  and  $P_3$  with the DUT between  $P_1$  and  $P_2$ .

Measured S-parameters:

$$\mathbf{S}_{\mathbf{m}} = \begin{pmatrix} S_{m11} & S_{m12} \\ S_{m21} & S_{m22} \end{pmatrix}$$

[II-9]

$$\mathbf{T}_{\mathbf{m}} = \begin{pmatrix} -\frac{S_{m11}S_{m22} - S_{m12}S_{m21}}{S_{m21}} & \frac{S_{m11}}{S_{m21}} \\ -\frac{S_{m22}}{S_{m21}} & \frac{1}{S_{m21}} \end{pmatrix}$$

[II-10]

Extraction of device's parameters by de-embedding:

$$\mathbf{T} = \mathbf{T}_{\mathbf{A}}^{-1} \mathbf{T}_{\mathbf{m}} \mathbf{T}_{\mathbf{B}}^{-1}$$

[II-11]

$$\mathbf{S} = \begin{pmatrix} \frac{T_{12}}{T_{22}} & \frac{T_{11}T_{22} - T_{12}T_{21}}{T_{22}} \\ \frac{1}{T_{22}} & -\frac{T_{21}}{T_{22}} \end{pmatrix}$$

[II-12]

## **II.5** First validation of the method

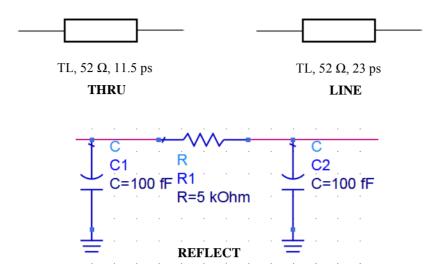

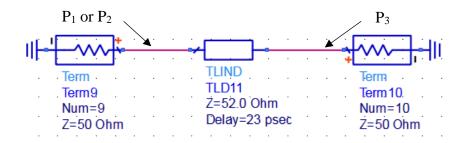

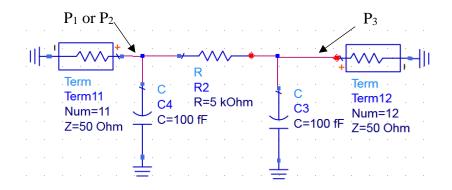

The measurements have been simulated using Keysight's ADS as shown in the configuration setup of Fig. II-13. The calibration standards are described in Fig. II-14.

Figure II-13: Simulated calibration setup

Figure II-14: Simulated standards

The steps of de-embedding that were described in previous section will be used to extract the system of errors again and compare it to the introduced or calculated ones.

- Step 1: calculate the virtual errors A' & B' from three calibrated elements.

- Step 2: calculate AA' & B'B from the measurements of three elements.

- Step 3: extract the error model A & B from previous system of errors (AA', B'B, A' & B').

$$T_{A} = T_{AA'} T_{A'}^{-1}$$

;  $T_{B} = T_{B'}^{-1} T_{B'B}$  [II-13]

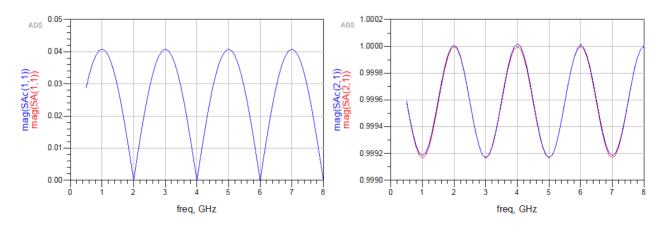

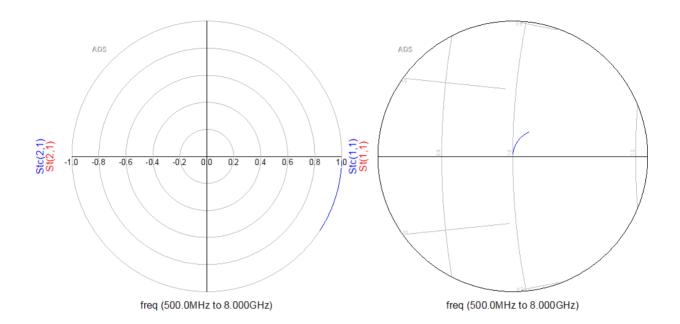

Fig. II-15, compares the introduced S-parameters A (in red) to the simulated ones (in blue).

Figure II-15: Simulated vs. Introduced S parameters of input board

Fig. II-16 till II-18 show the simulated vs. introduced for the three calibration standards (Thru, line and Reflect) respectively.

Figure II-16: Simulated vs. Introduced S parameters for Thru standard

Figure II-17: Simulated vs. Introduced S parameters for Line standard

Figure II-18: Simulated vs. Introduced S parameters for Reflect standard

By comparison we find that there is no differences during all over the band of frequency. The other parameters are in a very good agreement as far as the parasitic resonance does not appear for higher frequencies. Their differences are null and this confirms the validity of our analytical calculations for calibration technique and de-embedding method and also it shows that the method is applicable. This study will be applied on different devices as we will see in the following chapter.

# **II.6** Conclusion and Perspectives

In this Chapter, we have used a new approach for a TRL calibration technique and de-embedding method. The way that we use the technique show the validity of our approach. All the analytical calculations needed to apply to new approach have been shown.

An overview scheme for a full two-port board setup with the different steps needed to perform the calibration has been described. At the end of this chapter, an example has been studied to show the validation of the proposed study. Simulated vs. Introduced S-parameters for different calibration standards were compared and the results confirm the validity of this technique.

In the next chapters, this study will be applied on different types of devices. First on the following chapter where we are going to test an active MMIC device used for WLAN with different modes. Then on chapter 4 where we will give a further applications to this study where the device that we will investigate is a differential device.

# CHAPTER III

# **MEASUREMENT METHODOLOGY AND**

# **EXTRACTION RESULTS**

# **III.1** Introduction

The design of passive circuits that are used in calibration step is a complex and very precise procedure in which many steps have to be carefully taken into account for a successful and efficient implementation in order to be fit within the test socket of a load board. In past years, a great number of substrate integrated circuits have been developed [49]. Our aim is to present a TRL calibration kit for device measurements, and to verify its validity for de-embedding the effect of the SMA connectors, transmission feeding lines, mismatch etc... An additional advantage of this calibration kit is that any designer or researcher can fabricate their own calibration kit with standard machinery for manufacturing planar circuits, so it is much cheaper than any other standard commercial calibration kits, which besides they can correct better the deviations due to the measurement circuit between the network analyzer itself and the SMA connectors [50].

To perform a TRL calibration, three standards have to be manufactured (so called TRL). These standards must help de-embed the errors from the measurements and shift the reference planes down to the pins of DUT. Once the standards have been manufactured, the procedure that has to be followed is that usual in TRL calibration. First, we define the calibration kit on a chip mechanically and electrically compatible with the device to measure. Then we measure the three standards of the calibration kit in their reference planes with a vector network analyzer.

Alternatively, when the on-wafer measurement facilities are not available, the standards may be simulated with a 2.5D or 3D electromagnetic simulator. The device is measured between the outer ports of the board after a coaxial calibration (e.g. an SOLT calibration between SMA ports). The calibration process itself consists of replacing the device by the three standards and calculating the figures useful for our de-embedding method calculation [51].

Chapter III is organized as follows. Paragraph III.2 presents a description about the device that undergoes test. Then, paragraph III.3 shows the design model of the calibration standards using a 3D e.m simulator HFSS and later on the fabricated ones. A fully e-m simulated experiment is proposed in paragraph III.4 and an example of HBT that had been measured. Then in paragraph 5, a measurements for the different calibration standards. Paragraph III.6 shows the measurements validation of a device with LNA and bypass mode. Paragraph III-7 shows the application for power measurements and finally, paragraph III.8 concludes chapter III.

# **III.2** Characteristics of a device that undergoes test

The device under test (DUT), is a manufactured product undergoing testing, either at first manufacture or later during its life cycle as part of ongoing functional testing and calibration checks. But during its life time, the DUT is soldered and cannot be included into the board. This can include a test after repair to establish that the product is performing in accordance with the original product specification.

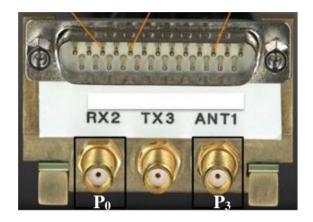

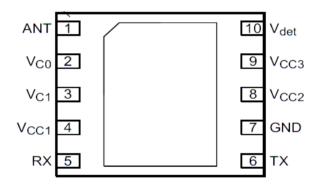

Our device that undergoes test is a fully integrated RF front-end MMIC for WLAN. It includes a Low-Noise Amplifier, a TX Power Amplifier and an integrated power detector covering the entire ISM band. It has RX by-pass mode for high signal handling and low-power TX mode to optimize power efficiency of the PA for low-power levels.

Fig. III-1 below shows a pin configuration of the device to be tested.

Figure III-1: Pin's configuration of the tested device

| Symbol           | Pin             | Description                |

|------------------|-----------------|----------------------------|

| ANT              | 1               | Antenna in/out pin         |

| V <sub>co</sub>  | 2               | C <sub>0</sub> control pin |

| V <sub>C1</sub>  | 3               | C <sub>1</sub> control pin |

| V <sub>CC1</sub> | 4               | Supply voltage (LNA)       |

| RX               | 5               | RX output                  |

| TX               | 6               | TX input                   |

| GND              | 7               | Ground                     |

| V <sub>CC2</sub> | 8               | Supply voltage (PA)        |

| V <sub>CC3</sub> | 9               | Supply voltage (PA)        |

| V <sub>det</sub> | 10              | Detection voltage          |

| GND              | Exposed die pad | Ground                     |

Table III-1: Pin's description of DUT

Table III-1 shows a pin description of the device under test. It contains 10 pins numbered from one to ten and an exposed die pad for ground centered at the middle of the device. This device of body 2.0 mm x 1.7 mm x 0.35 mm must be introduced inside test socket of a test board as shown in Fig. III-2.

Figure III-2: Schema of the test board

# **III.3** Calibration standards: design model and fabrication

# III.3.1 Design model

We have design the layouts of the calibration standards under the same restrictions as the device above and respecting all the tolerances given by the manufacturer. These designs are studied under two situations.

- First situation: three models of calibration standards which correspond to thru, line and reflect are situated between A (antenna) and R (receiver).

- Second situation: Another three models of calibration standards which correspond to thru, line and reflect are situated between T (transmitter) and A (antenna).

The name of each element has been chosen as follows:

- **4** First letter **T** for thru, **L** for line, **R** for reflect.

- **4** Second letter **A** for antenna.

$\blacksquare$  Third letter **R** for receiver and **T** for transmitter.

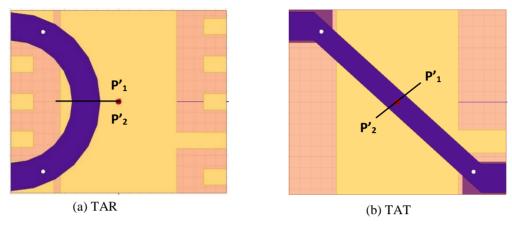

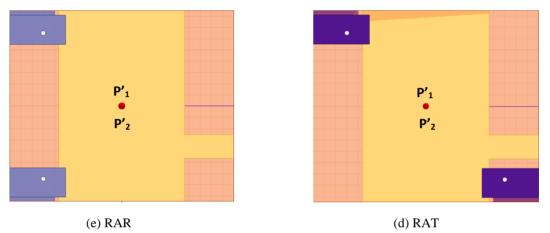

Fig. III-3 till III-5, show the layout of different calibration elements.

When we put the TAR or TAT between  $P_1$  and  $P_2$ , we consider that a thru is placed between  $P'_1$  and  $P'_2$ .

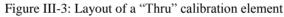

Figure III-4: Layout of a "Line" calibration element

When we put LAT or LAR between  $P_1$  and  $P_2$ , we consider that a line is placed between  $P'_1$  and  $P'_2$ .

$$\mathbf{S} = \begin{pmatrix} 0 & X \\ X & 0 \end{pmatrix}$$

[III-2]

The zeros for the reflection coefficients mean that the reference impedance between planes  $P_1$  and  $P_2$  is the characteristic impedance of the line standard.

In our case, the reference impedance is the reference impedance of the GS measurement (i.e. the load for SOLT or the characteristic impedance of the line for TRL). Here, the VNA was calibrated in TRL with an alumina calibration substrate [52]. That means that the reference impedance is 50  $\Omega$ .

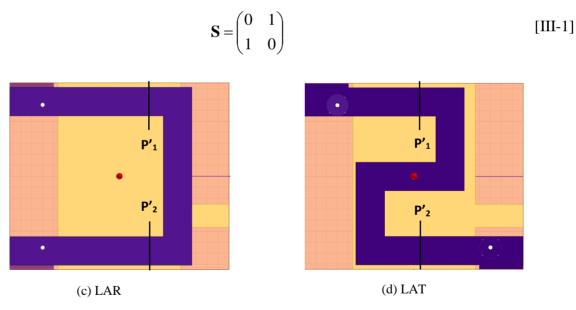

Figure III-5: Layout of a "Reflect" calibration element

When we put RAT or RAR between  $P_1$  and  $P_2$ , we consider that reflects are placed in  $P'_1$  and  $P'_2$ .

$$\mathbf{S} = \begin{pmatrix} \Gamma & 0\\ 0 & \Gamma \end{pmatrix}$$

[III-3]

The common value for  $\Gamma$  means that the reference planes between P'<sub>1</sub> and P'<sub>2</sub> is placed in the middle of thru.

These circuits have been optimized using Keysight's HFSS 3D electromagnetic simulator. The shape and place of the ground has been carefully designed in order to allow GS probe measurements.

## **III.3.2** Calibration standards under fabrication

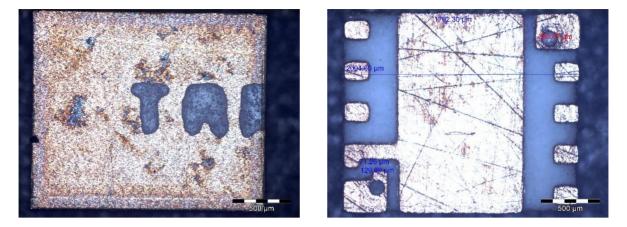

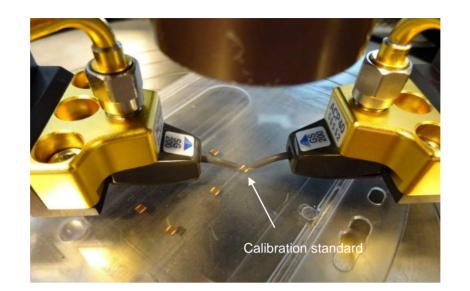

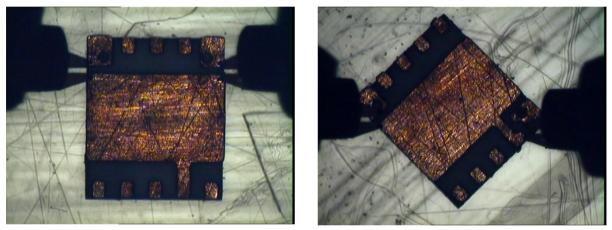

Fig. III-6 and III-7, show some photos under microscopic level for the fabricated calibration standards that will be used to perform TRL calibration.

Figure III-6: Top and Bottom view of "TAT" fabricated standard

Figure III-7: Top and Bottom view of "LAR" fabricated standard

The design of these standards has been done under some restrictions. One of these is the capability of testing those standards by GS probes and by replacing these standards by DUT under VNA tester. This double function enables us to extract the measurements of circuits alone in order to introduce their results in calibration process. The transmission of signal will be at the upper part of circuits which is shown by different transmission lines and the measurements using GS probes are done at the lower part which contains the signal and ground needed for such test [53].

# **III.4 E.M simulation validation**

In this part we will use an on-wafer measured HBT transistor as a DUT and we cascade the two half parts of PCB that we have modeled using HFSS as input/output parts. The three design standards Thru, Line and reflect shown before from Fig. III-3 to III-5, will be used to perform the calibration process.

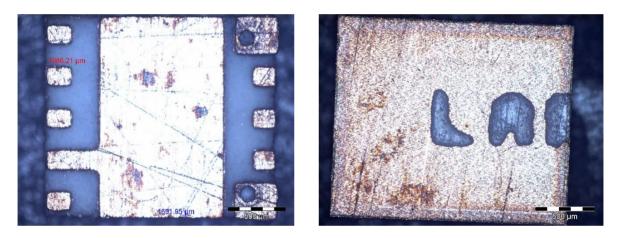

## III.4.1 PCB model

The following figures show a PCB and three standards (Thru, Line and Reflect) which have been modeled and simulated by HFSS 3D electromagnetic software. Using ADS (Advanced Design System) we cascade the two halves of PCB by each standard and later HBT.

Figure III-8: HFSS PCB model

# **III.4.2** Use of E.M simulations for the calibration standards

It is not always possible to have a VNA equipment with a probe station and GS probes. In that case, it is necessary to be confident in electromagnetic simulation to know exactly what is put between planes  $P_1$  and  $P_2$  during the calibration process. Fig. III-9, compares the results for some standards using E.M simulation and GS probe measurements [54].

Figure III-9: S parameters of a "Thru" and "Ref" calibration standards

Red curves referred to the electromagnetic simulation results and the blue ones are for the GS probes measurement. The comparison of transmission coefficient  $S_{21 dB}$  for a reference standard doesn't show any difference between the e.m simulated standard using HFSS and under GS probes.

While the slight difference shown in the phase study, is referred mainly to the position of the probes on the circuit, where our GS probes are lied on the tested circuit within two positions: 45 and 180 degrees according to the type of standard under test e.g (TAT, TAR etc...) which explains clearly the difference in phase.

#### **III.4.3** Simulated measurements with an active two-port device

The simulation measurements are done between the RF coaxial connectors planes which they represent the input and output of the board  $P_3$  and  $P_4$  respectively.

The DUT (device under test) in our case here is HBT (heterojunction bipolar transistor) where it's placed at the level of pins of the socket  $P_1$  and  $P_2$ .

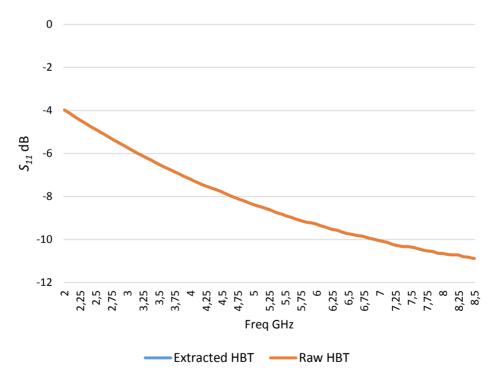

Figure III-10: Measured and calculated  $S_{11 dB}$  of HBT

Figure III-11: Measured and calculated phase  $S_{21 \text{ degree}}$  of HBT

Fig. III-10 and Fig. III-11, show the results of extracted and raw HBT for  $S_{11}$  in dB and  $S_{21}$  in phase respectively.

The results don't show any difference at the level of transmission and reflection coefficients. The measurements evaluate clearly the validity of our technique and its efficiency.

This technique will be applied on the device that had been described in paragraph III-2.

## **III.5** Calibration standards behavior

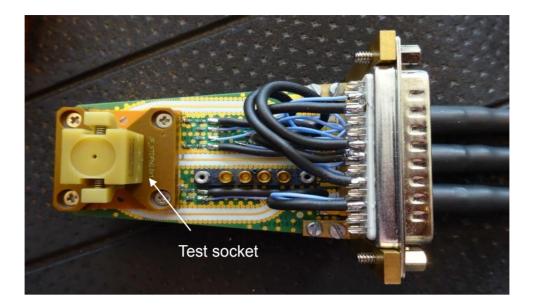

Different standards were modeled and tested as shown in section III.1. These standards will be measured first by GS probes and later they will be placed respectively inside socket of a test board (Fig. III-2) to be tested by a vector network analyzer between the outer coaxial planes.

## **III.5.1** Measuring of standards by GS probes

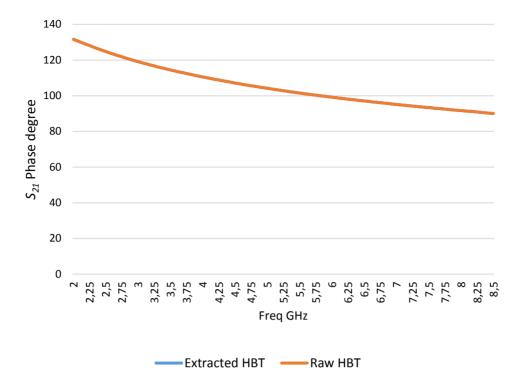

Fig. III-12, shows some photos for the standards under GS probes measurement. These photos were taken under macro and microscopic levels in order to show clearly the placement of probes at the right locations.

Figure III-12: Standards calibration under GS probes

The standards above are showing the probes in 180° & 45° face to face. These constraints are essential in order to meet the requirements of calibration of such DUT.

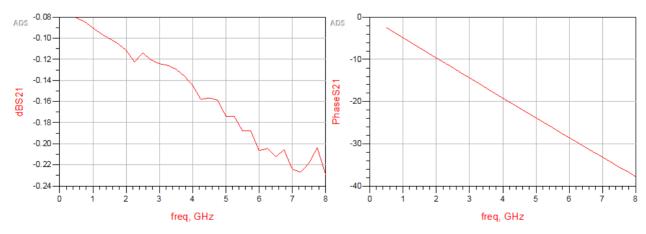

Figure III-13: S parameters of a "Thru" standard

Figure III-14: S parameters of a "Line" standard

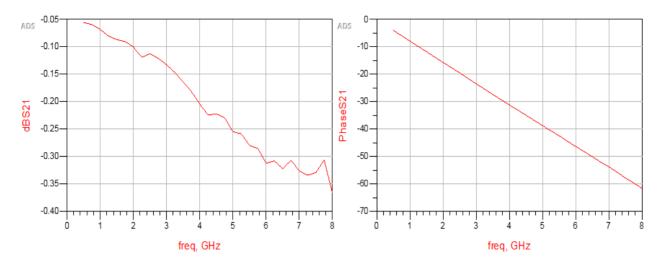

Figure III-15: S parameters of a "Reflect" standard

Fig. III-13 to III-15, show the measurement results of the three fabricated calibration standards: Thru, Line and reflect respectively.

## **III.5.2** Verification of the calibration using standards

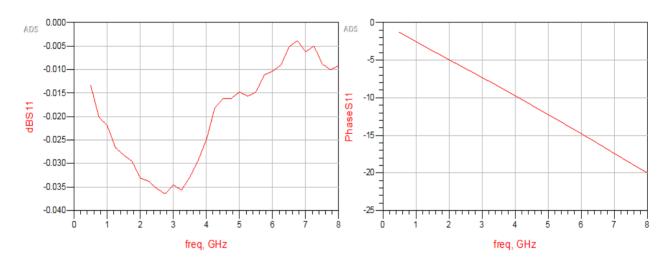

The calibration standards will be placed respectively inside the socket of the test board which shown in Fig. III-16.

Figure III-16: Test board with a socket

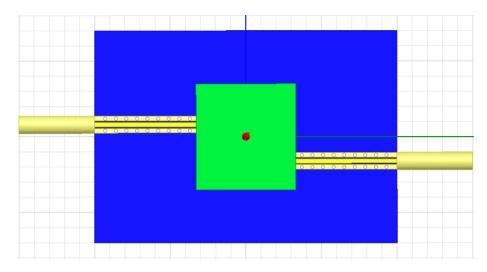

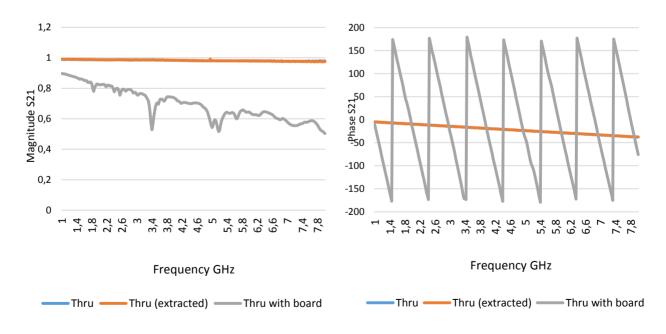

Fig. III-17 and III-18 show the comparison results between under three cases of study:

- **4** Calibration standards under GS probes (blue curves).

- **4** Calibration standards within test board (gray curves).

- **4** Extraction results of the standards after de-embedding (orange curves).

Figure III-17: "Thru" standard behavior in three cases

Figure III-18: "line" standard behavior in three cases

By comparing the standards with and without board (Gray and blue respectively), we could see clearly the difference at the level of magnitude and phase. The difference between the magnitudes correspond mainly to the losses which exist in the board. These losses have several origins (mismatch, coupling, resistance etc.). The phase due to the length of the PCB lines is compensated by the calibration. The remaining difference are due to the position of the pins on the chip.

De-embedding described in previous sections aim to reduce these errors or losses at the input and output of DUT after set of measurements which are used for calibration. Standard extracted (thru & Line) which are shown in Fig. III-10 & Fig. III-11, were deducted from the measurement of standards with board after controlled by de-embedding. By comparing those results to the ones with samples under GS probes, we can clarify easily that the importance of this technique is essential for extracting the behavior of samples within complex board. The confirmation of this technique has been proved clearly by comparing samples extracted with samples only (under probes). The difference is null and this confirms the importance of using this technique in extracting error terms in calibration.

# **III.6** Measurement: evaluation and validation

The de-embedding method developed in chapter 2 gives the S-parameters of a DUT between  $P_1$  and  $P_2$  when the actual measurements were made between  $P_0$  and  $P_3$ .

## **III.6.1** Board specification

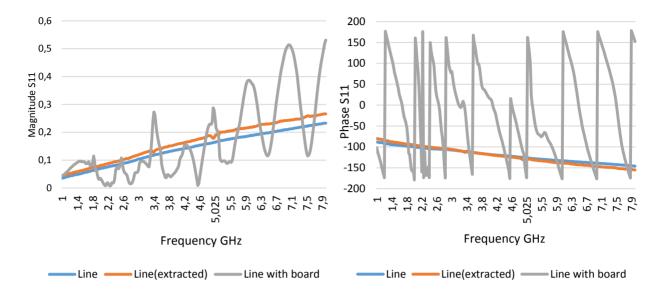

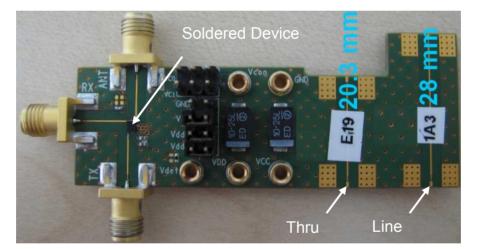

To validate the measurement results and de-embedding technique, we must compare the result with direct measurement between  $P_1$  and  $P_2$ . For this purpose, we have used an evaluation board (EVB) as shown in Fig. III-20, this board contains a TRL calibration kit consisting of two microstrip lines 1A3 and E19 which corresponds to thru and line. The chip has been soldered on the board. That means that it cannot be used for a production test with tens of components every minute (see chapter 1).

The device that we will use in our measurements is the device described in paragraph III-2. This device will be tested and measured within two boards:

Load Board: where the device is laying inside the socket of the test board shown in Fig. III-13.

Evaluation Board: where the device is soldered in an evaluation board (EVB) shown in Fig. III-19.

Figure III-19: Evaluation board (EVB)

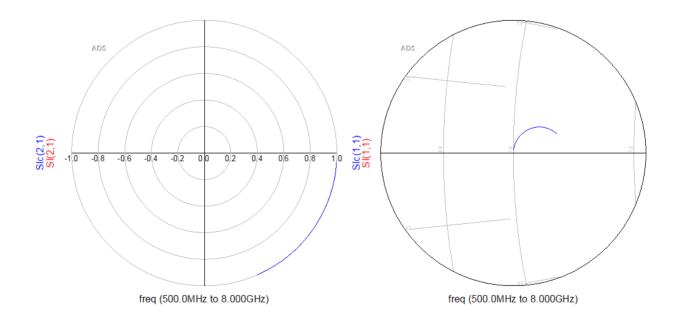

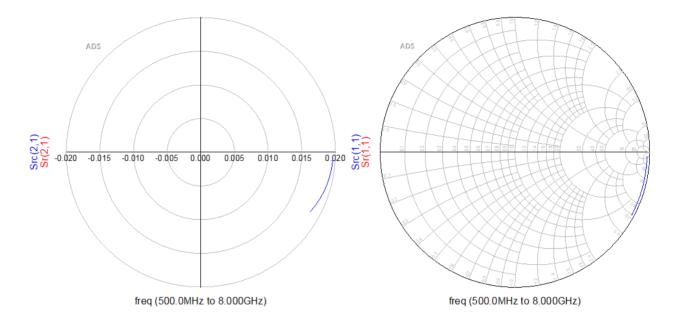

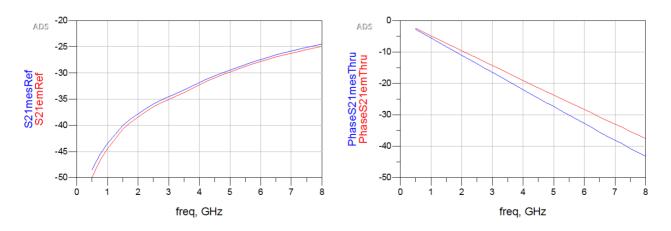

# **III.6.2** Measurements validation

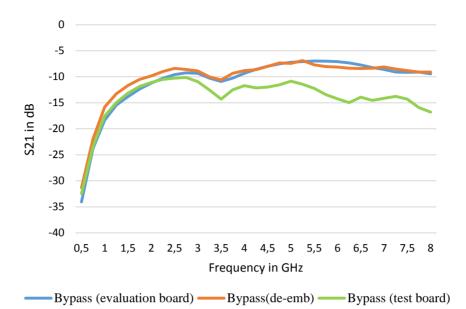

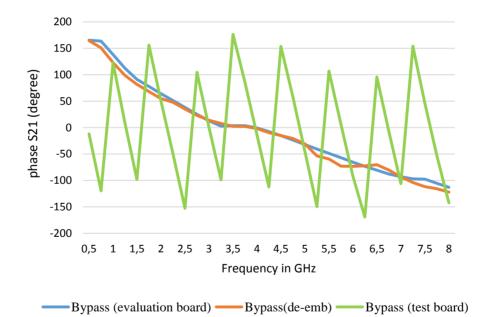

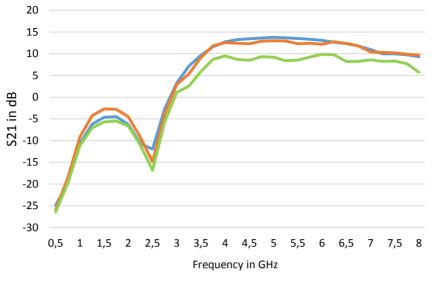

Figures III-20 till III-22 below illustrate the behavior of a device under test in two modes: LNA (Low noise amplifier) and Bypass modes. The measurement study has been done under three cases:

- **4** Blue curves correspond to the DUT in evaluation board.

- ✤ Orange curves correspond to the extracted DUT by de-embedding

- **4** Green curves correspond to the DUT in test board

Figure III-20: S<sub>21</sub> dB for DUT in ByPass mode

Figure III-21: S<sub>21</sub> phase for DUT in ByPass mode

The calibration and de-embedding technique described in chapter II is applied on the measurements of the device with a test board in order to remove the errors within the board. The result of this extraction is presented in the figures above under the name de-emb in orange curves.

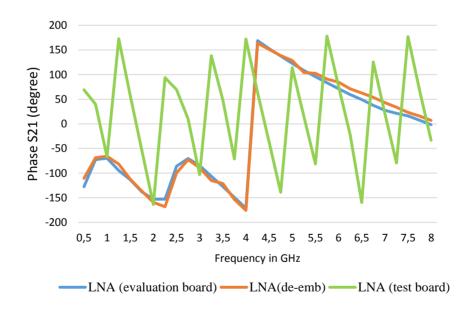

LNA (evaluation board) LNA(de-emb) LNA (test board)

Figure III-22: S<sub>21</sub> dB for DUT in LNA mode

Figure III-23: S<sub>21</sub> phase for DUT in LNA mode

The comparison between the de-embedded DUT (orange curves) and the measured one in a test board (green curves) shows a clear difference in the transmission level (dB and phase) for the two studied modes. The difference in the two curves corresponds mainly to the losses which are embedded within the test board. These losses have several origins (mismatch, coupling, resistance etc.) and they have been compensated well by calibration and de-embedding. To confirm the validity of the technique used, a result of measurements of an evaluation board (blue curves) for the same device will be compared with the de-embedded ones (orange curves). By comparison these two curves, we could see clearly that the results are quite the same. This validates that the study that had been done is sufficient for compensating the losses.

We can see on the  $S_{21}$  transmission in dB and phase that the correction of the access point, transmission lines and mismatch losses is corrected for all frequencies. Note that this technique is fairly general and makes it possible to correct the losses embedded within a PCB.

#### **III.6.3** Parasitic coupling effects

Parasitic effects are becoming more critical with increasing requirements on performance, density, complexity, and levels of integration in RFIC designs. For radio frequency (RF) designs, parasitic effects such as IC package pin leakage and substrate coupling are now widely seen [55]. This leads to the need to model the parasitic networks in the areas of chip-package and substrate. The parasitic couplings are the effect of the pins and the leakage in the substrate. The coupling between the pins has been measured by removing the DUT from the board [56].

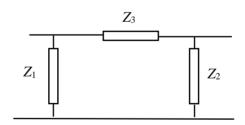

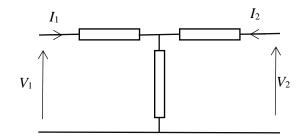

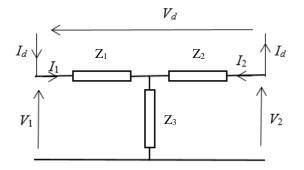

The measured parameters allow to calculate the admittance matrix  $\mathbf{Y}_{\mathbf{P}}$  which represents a picircuit describing the parasitic coupling between the pins (Fig. III-24).

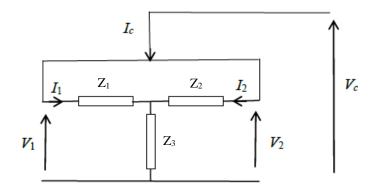

Figure III-24: Pi-circuit model

An RLCG equivalent circuit is derived from Z or Y-parameters. Y-parameters are convenient if we want to model our circuit under test with elements in a pi topology (one component across, and two in shunt). Z-parameters are convenient when we want to model the circuit with a T type of topology (two components in series with a shunt element between them) [57].

Each branch of the  $\pi$  or T equivalent topology is represented by an admittance or by an impedance, noted in *Yparameters* or *Zparameters* respectively. Each impedance in the picircuit can be considered as a resistance in parallel with a capacitance [58].

The value of each is described below:

$$R_1 = \frac{1}{\operatorname{Re}(Y_{11} + Y_{21})}$$

;  $R_2 = \frac{1}{\operatorname{Re}(Y_{22} + Y_{21})}$ ;  $R_3 = \frac{-1}{\operatorname{Re}(Y_{21})}$  [III-4]

$$C_1 = \frac{\operatorname{Im}(Y_{11} + Y_{21})}{\omega}$$

;  $C_2 = \frac{\operatorname{Im}(Y_{22} + Y_{21})}{\omega}$ ;  $C_3 = \frac{-\operatorname{Im}(Y_{21})}{\omega}$  [III-5]

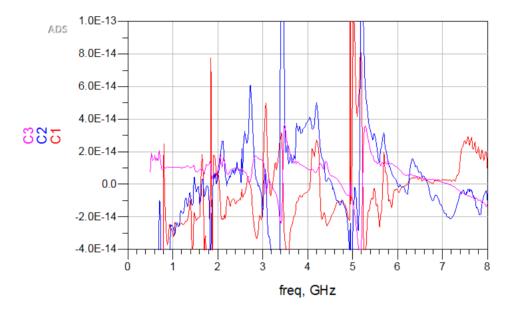

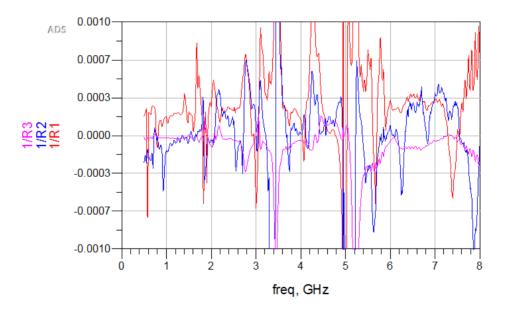

Figure III-25: Capacitance

Figure III-26: Conductance

As we could see in Fig. III-25 and III-26, the capacitance and conductance is very small which show that reflect is almost unilateral and also that the coupling between the input and output parts of the board is negligible.

## **III.7** Applications to power measurements

The power gain of an electrical network is the ratio of an output power to an input power. Unlike other signal gains, such as voltage and current gain, "power gain" may be ambiguous as the meaning of terms "input power" and "output power" is not always clear. Three important power gains are operating power gain, transducer power gain and available power gain [59].

Note that all these definitions of power gains employ the use of average (as opposed to instantaneous) power quantities and therefore the term "average" is often suppressed, which can be confusing at occasions.

## **III.7.1** Available power gain

The available power that the two-port could transfer to the conjugate of its output impedance  $(\Gamma_{OUT})$  divided by the available power that the source could transfer to the conjugate of its Thevenin impedance.

It's useful for noise measurement study [60].

$$G_{a} = \frac{|S_{21}|^{2} (1 - |\Gamma_{s}|^{2})}{(1 - |\Gamma_{OUT}|^{2}) (1 - S_{11} \Gamma_{s})^{2}}$$

[III-6]

With:

$$\Gamma_{OUT} = S_{22} + \frac{S_{12}S_{21}\Gamma_S}{1 - S_{11}\Gamma_S}$$

and  $\Gamma_S = 0$  [III-7]

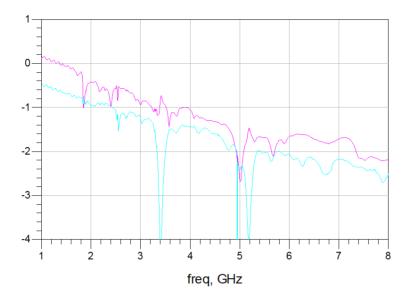

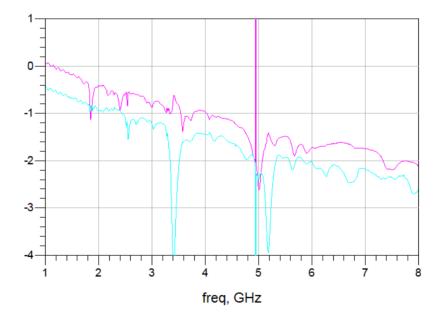

In Fig. III-27, the available power gain at input and output parts correspond to pink and light blue color respectively.

Figure III-27: Available power gain

#### **III.7.2** Insertion power gain

It's defined as the signal power loss introduced by the RF switch between the input port and the output port in its on-state. It's measured by inserting the DUT between a generator and a load. The numerator of the ratio is the power delivered to the load while the DUT is inserted. The denominator, or reference power, is the power delivered to the load while the source is directly connected.

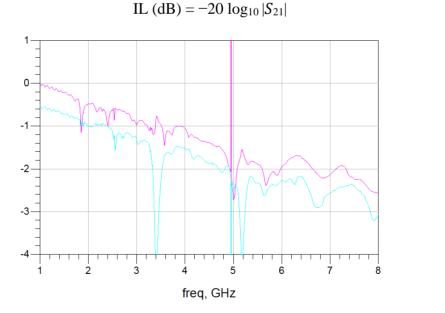

Figure III-28: Insertion power gain

[III-8]

In Fig. III-28, the insertion power gain at input and output parts correspond to pink and light blue color respectively.

#### **III.7.3** Operating power gain

The power that is transferred from the two-port output to the load  $\Gamma_L$  divided by the power that is transferred from the source to the two-port input. It can be written in terms of the two-port s-parameters and the load reflection coefficient.

$$G = \frac{|S_{21}|^2 (1 - |\Gamma_L|^2)}{(1 - |\Gamma_{IN}|^2) |1 - S_{22} \Gamma_L|^2}$$

[III-9]

With:

$$\Gamma_{IN} = S_{11} + \frac{S_{12}S_{21}\Gamma_L}{1 - S_{22}\Gamma_L}$$

and  $\Gamma_L = 0$  [III-10]

Figure III-29: Operating power gain

In Fig. III-29, the operating power gain at input and output parts correspond to pink and light blue color respectively.

#### **III.7.4** Transducer gain

The power that is transferred from the two-port output to the load  $\Gamma_L$  divided by the available power that the source could transfer to the conjugate of its Thevenin impedance (reflection coefficient  $\Gamma_{IN}$ ).

$$G_{T} = \frac{|S_{21}|^{2} (1 - |\Gamma_{L}|^{2}) (1 - |\Gamma_{S}|^{2})}{|1 - \Gamma_{IN} \Gamma_{S}|^{2} |1 - S_{22} \Gamma_{L}|^{2}}$$

[III-11]

With

$$\Gamma_{IN} = S_{11} + \frac{S_{12}S_{21}\Gamma_L}{1 - S_{22}\Gamma_L}$$

[III-12]

And  $\Gamma_S = 0$  and  $\Gamma_L = 0$ , the result is the same like the insertion gain because we take into consideration that the input and output of DUT are matched.

#### **III.8** Conclusion and Perspectives

The measurement of S parameters enable characterization in terms of the reflection and transmission of a signal in a printed circuits board (PCB), however, requires calibration and deembedding techniques that must be put in place in order to correct defects related to the device and measurement cabling.

Our method is fully compatible with on-wafer and a device within a board. It provides directly the S-parameters in the device reference planes. In some cases, where a calibration is not directly possible in the DUT reference planes, the device accesses need to be characterized and modeled. In many applications, components are mounted on a PCB that holds power supply circuits, control circuits and lines for RF or high-speed signals. To measure these components, specific techniques make it possible to correct the effects of connection lines (losses, mismatching, etc.).

The purpose of de-embedding is to calculate the S parameters of a component based on measurements of an overall measurement of the component mounted on PCB with access lines of and on knowledge of the equivalent access line propagation parameters. This requires either a prior measurement of the S parameters of the access lines, or a measurement of the overall access line (without the component).

## CHAPTER IV

# **MULTI-PORT TRL CALIBRATION FOR**

## **DIFFERENTIAL DEVICES**

## **IV.1** Introduction

More and more circuits in telecommunication technologies are differential structures. This simplifies the design of RF functions and helps to the parasitic frequencies rejection. Measurement methods developed particularly for these differential circuits will reduce characterization time and increase accuracy. A differential circuit with at least three ports (two inputs and one output) demands multi-port tests. In addition, multi-port measurement is also required to determine mutual coupling between differential interconnections which influences significantly package performance due to the trend of increasing operation frequency, and signal density. Before an RF measurement, a calibration must be done. The algorithm developed in the recent publications such as [61] allows rigorous mixed modes measurement. However their main drawback is so complex and often with many assumptions.

TRL (Thru-Reflect-Line) is one of the most popular methods because it places the reference planes at the input and output of the DUT directly on the wafer. It assumes that the characteristic impedance is clearly defined for each line standard. When the accesses are constituted by coupled lines, the propagation constants and the characteristic impedances of the quasi-TEM *c* and  $\pi$  modes are defined [62]. For symmetric access lines, that means that the propagation constants and the characteristic impedances, so called mixed modes. When the waveguides are not homogeneous (e.g. micro-strip or coplanar waveguide) these propagation constants and characteristic impedances are different each from the other. Actually, the TRL calibration allow S-parameters measurement [63]. We must keep in mind that S-parameters are defined for propagation modes and not for voltages and currents. This means that the classical 4 port TRL de-embedding is not valid. The mixed mode de-embedding process is more rigorous. When there is no coupling between the access lines or when the mixed modes are quasi-TEM, the propagation constants and the characteristic impedances are equal. In that case, it is possible to consider the natural "modes" for the description of the DUT.

This is organized as follows. Paragraph IV.2 presents the TRL mixed-mode de-embedding method. Paragraph IV.3 describes the transformation matrix calculations for differential input and single output device. In paragraph IV.4, a full study for double TRL calibration process for a differential device and later in paragraph IV.5, the circuit simulation schemes and the extraction results. Finally in paragraph IV.6, a general conclusion and perspectives.

#### IV.2 TRL mixed mode de-embedding method

In this paragraph, we describe a mixed mode TRL de-embedding method. The first part reminds the essential notions on natural and mixed modes, and the transformation between them. Then in the second part, the error model is proposed and the calculation of the error terms is detailed [64]. The third part will present the experiment to verify the method with some line structures realized based on glass substrate. The final part will conclude the method.

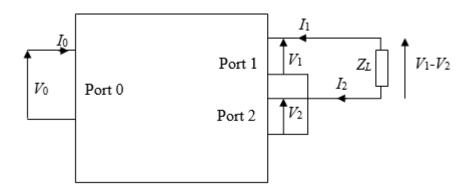

#### IV.2.1 Natural modes

The natural "modes" are defined from voltages and currents. There are not real modes because they do not correspond to eigen solution of the propagation equation [65].

For Port *i*, the power waves  $a_i$  and  $b_i$  are defined by:

$$a_i = \frac{1}{2} \left( \frac{V_i}{\sqrt{Z_i}} + I_i \sqrt{Z_i} \right)$$

[IV-1]

$$b_i = \frac{1}{2} \left( \frac{V_i}{\sqrt{Z_i}} - I_i \sqrt{Z_i} \right)$$

[IV-2]

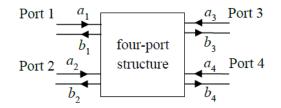

The corresponding natural *S* and *T* parameters of a four-port structure shown in Figure IV-1 are defined by Eq. (IV-1) and (IV-2).

Figure IV-1: four-port structure