# Design of tunable radiofrequency blocks in FD-SOI technology for IoT applications

Jennifer Desèvedavy

### ▶ To cite this version:

Jennifer Desèvedavy. Design of tunable radiofrequency blocks in FD-SOI technology for IoT applications. Electronics. Université de Bordeaux, 2018. English. NNT: 2018BORD0177. tel-01952786

### HAL Id: tel-01952786 https://theses.hal.science/tel-01952786

Submitted on 12 Dec 2018

HAL is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

### THÈSE PRÉSENTÉE POUR OBTENIR LE GRADE DE

### **DOCTEUR DE**

### L'UNIVERSITÉ DE BORDEAUX

ÉCOLE DOCTORALE DES SCIENCES PHYSIQUES ET DE L'INGENIEUR SPÉCIALITÉ ÉLECTRONIQUE

Par Jennifer DESEVEDAVY

# CONCEPTION DE CIRCUITS INTEGRES RADIOFREQUENCES RECONFIGURABLES EN TECHNOLOGIE FD-SOI POUR APPLICATIONS IOT

Sous la direction de : Thierry TARIS

(Co-directeur : Dominique MORCHE)

Soutenue le 8 octobre 2018,

### Membres du jury:

| M. David Bol        | Professeur | Université de Louvain     | Rapporteur            |

|---------------------|------------|---------------------------|-----------------------|

| M. Sylvain Bourdel  | Professeur | Université Grenoble Alpes | Président- Rapporteur |

| M. Olivier Tesson   | HDR        | NXP Caen                  | Examinateur           |

| M. Thierry Taris    | Professeur | IMS Bordeaux              | Directeur de thèse    |

| M. Dominique Morche | HDR        | CEA Leti Grenoble         | Co-directeur de thèse |

| M. Frédéric Hameau  | Ingénieur  | CEA Leti Grenoble         | Encadrant             |

| M. Patrick Audebert | Ingénieur  | CEA Leti Grenoble         | Co-encadrant          |

## **ABSTRACT**

# DESIGN OF TUNABLE RADIOFREQUENCY BLOCKS IN FD-SOI TECHNOLOGY FOR IOT APPLICATIONS

Communicating objects are inviting themselves into daily life leading to digitization of the physical world. This explosion of multimedia wireless applications for consumer electronics makes the power consumption a key metric in the design of multi-mode wireless portable devices. Conventional transceivers have fixed performances and are designed to meet high performances in all wireless link conditions. However, most of the time, the channel of communication is not at worst case and these transceivers are therefore over specified. Being aware of the channel link conditions would allow such devices to adapt themselves and to reduce significantly their power consumption. Therefore, the challenge is to propose a QoS (Quality of Service) in terms of communication range, response time as instance, equivalent to industrial modules with a reduced overall power consumption.

To address this purpose, this thesis proposes a design strategy for the implementation of adaptive radio-frequency receiver (Rx) modules. Hence the Rx front end achieves the correct QoS for various scenarii of communications with a minimum of power consumption.

As a proof of concept, the adaptive approach is demonstrated with the design of a tunable LNA (Low Noise Amplifier). As the first element of the receiver chain, the LNA limits the receiver in terms of sensitivity and is therefore a good candidate to perform reconfiguration. The body biasing of the FD-SOI (Fully Depleted Silicon-On-Insulator) technology is first exploited to reduce the power consumption of a circuit and then as an opportunity to perform circuit tunability.

**KEYWORDS:** Low Noise Amplifier – Integrated Circuit - FD-SOI – Radiofrequency - Reconfigurable

# RÉSUMÉ

# CONCEPTION DE CIRCUITS INTEGRES RADIOFREQUENCES RECONFIGURABLES EN TECHNOLOGIE FD-SOI POUR APPLICATIONS IOT

La pénétration importante d'objets communicants dans notre vie quotidienne révèle des défis important quant à leur développement. Notamment l'explosion d'applications multimédia sans fil pour l'électronique grand public fait de la consommation électrique une métrique clef dans la conception des dispositifs portables multimodes sans fil. Les émetteurs-récepteurs conventionnels proposent des performances fixes et sont conçus pour respecter ces hautes performances dans toutes les conditions de communication sans fil. Cependant, la plupart du temps, le canal n'est pas dans le pire cas de communication et ces émetteurs-récepteurs sont donc surdimensionnés. En connaissant l'état du canal en temps réel, de tels dispositifs pourraient s'adapter aux besoins et réduire significativement leur consommation électrique. Le défi consiste à respecter la Qualité de Service , ou Quality of Service (QoS) en anglais, imposée par les différents standards de communication. Afin de rester compétitifs, les émetteurs-récepteurs adaptatifs doivent donc proposer une même QoS que ceux déjà disponibles sur le marché. Ainsi, ni la portée de communication ni le temps de réponse ne peuvent être dégradés.

Basé sur ces exigences, cette thèse propose une technique d'adaptation pour la conception d'un récepteur reconfigurable qui fonctionne à la limite des performances nécessaires pour recevoir le signal utile. Ainsi, le récepteur proposé est toujours au minimum de consommation électrique tout en garantissant la bonne QoS. Ceci permet alors de multiplier la durée de vie de sa batterie par un facteur 5.

Cette adaptabilité est démontrée ensuite côté circuit par la conception d'un LNA (Amplificateur Faible Bruit) dont les performances sont reconfigurables. En effet, en tant que premier élément de la chaîne de réception, le LNA limite le récepteur en termes de sensibilité. Ces travaux exploitent la technologie FD-SOI (Fully Depleted Silicon-On-Insulator) pour d'une part, réduire la consommation du LNA et d'autre part, ajouter de la reconfigurabilité à ce même circuit.

**MOTS-CLES :** Amplificateur Faible Bruit - Circuits intégrés - FD-SOI - Radiofréquence - Reconfigurable

## **ACKNOWLEDGMENT**

This work would not have been possible without the outstanding assistance and support of many other individuals.

First, I would like to thank my research advisor, Pr. Thierry Taris for his support and guidance throughout these three years, always available despite the distance. His vision of the research field has been both inspiring and challenging.

I would like to express my heartfelt gratitude to my thesis supervisor, Mr. Frédéric Hameau. He was always there every step of the way, guiding me in the right direction as I grew as a researcher and also as a human being. I sincerely thank him for that.

I take this opportunity to also thank my co-advisor, Dr. Dominique Morche for his ability to think out of the box which inspires me a lot.

I would also like to thank my co-supervisor, Mr. Patrick Audebert for his guidance and encouragement.

On a larger scale, the LAIR team has provided an interdisciplinary environment which encourages all sorts of productive research, so thank you all for the precious shared moments. I am thankful for the professional and personal support I received from many of my colleagues – Anthony, Baudouin, Clément, Ayssar, Alex G., Alex S., David, J-B, Gilles, Pierre, Carolynn, Didier, Emeric, Jérôme, Guillaume and many others – over these three years. I was lucky to cross paths with many interesting people who have enriched my life through these years at the LAIR lab.

My special thanks to Mr. Pierre Vincent and Mr. Eric Mercier for giving me the opportunity to study this interesting research topic within the DACLE/LAIR.

I sincerely appreciate what I learnt from my PhD student colleagues – Marguerite, Tu, Florian and Saad – to whom I wish much strength to complete their PhD degree.

I also thank the thesis committee members – Pr. David Bol from UC Louvain, Pr. Sylvain Bourdel from Université Grenoble Alpes and Mr. Olivier Tesson from NXP Caen – for evaluating my research and accepting to participate as the Jury.

I would like to thank Magali De Matos and Gabrielle Guitton from IMS Bordeaux for their availability and their help during the measurements of the ULP LNA.

I am extremely grateful to my mother Mrs. Marie-Jo Zaini and my father Mr. Serge Zaini for their unconditional love and their unshakable trust which I have felt not only during my thesis but all through my life. I have always found strength and encouragement in their love and support.

Many thanks to my sisters, especially Miss. Emmanuelle Zaini and Miss. Nadège Helly for their support (especially for the wedding organization!) and the continuous WhatsApp conversations that helped a lot during hard working days. Dadou, who provided real time pictures of my nephews Lucas and Ethan making me smile every day. Manu, our never-ending 4 in 1 conversations inspired me a lot. I also want to thank my entire extended family and my closest friends for their support and love.

I would especially like to present my deepest gratitude to my parents-in-law, Mrs. Pascale Desèvedavy and Mr. Hervé Desèvedavy for their continuous encouragement and precious advice during the past three years. Thank you for making me feel like your daughter, I am so lucky to be part of your family.

| Last but definitely not least, I want to thank my husband Yann for his endless support, patience and care. He has always been there for me and I am very lucky to have him by my side. I am so thankful for his presence in my life and I dedicate this work to him. Merci mon amour. |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                                                                                                                                                                                       |

|                                                                                                                                                                                                                                                                                       |

| Jennifer Desèvedavy<br>Grenoble, France                                                                                                                                                                                                                                               |

| Grenobie, France                                                                                                                                                                                                                                                                      |

|                                                                                                                                                                                                                                                                                       |

|                                                                                                                                                                                                                                                                                       |

|                                                                                                                                                                                                                                                                                       |

|                                                                                                                                                                                                                                                                                       |

|                                                                                                                                                                                                                                                                                       |

|                                                                                                                                                                                                                                                                                       |

|                                                                                                                                                                                                                                                                                       |

|                                                                                                                                                                                                                                                                                       |

|                                                                                                                                                                                                                                                                                       |

|                                                                                                                                                                                                                                                                                       |

# TABLE OF CONTENTS

| ABSTRA  | ACT                                                            | 3  |

|---------|----------------------------------------------------------------|----|

|         | ıÉ                                                             |    |

| ACKNO   | WLEDGMENT                                                      | 5  |

|         | OF CONTENTS                                                    |    |

| LIST O  | F FIGURES                                                      | 11 |

| LIST O  | F TABLES                                                       | 14 |

| ABBREV  | VIATIONS                                                       |    |

|         |                                                                |    |

| CHAPTER | 1: Introduction                                                | 17 |

| 1.1 In  | ternet Of Things and Wireless Sensor Networks                  | 18 |

| 1.2 C   | hallenges in Transceiver Designs                               | 19 |

| 1.3 FI  | D-SOI Technology: Good Candidate for IoT Applications          | 21 |

| 1.4 T   | hesis Purpose and Organization                                 | 22 |

| CHAPTER | 2: TUNABLE RECEIVER: SYSTEM-LEVEL ANALYSIS                     | 23 |

| 2.1 St  | ate Of the Art of Adaptive Receiver techniques                 | 24 |

| 2.1.1   | Wake-Up Receivers                                              | 25 |

| 2.1.2   | MAC or Network Level Adaptability                              | 25 |

| 2.1.3   | Analog-RF Adaptability                                         | 26 |

| 2.1.4   | Proposed Approach                                              | 27 |

| 2.2 Pr  | roposed Channel Aware Receiver                                 | 29 |

| 2.2.1   | Context of Application                                         | 29 |

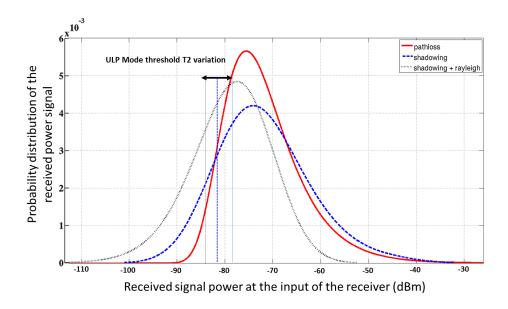

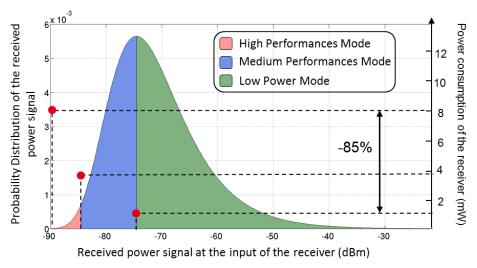

| 2.2.2   | Probability Distribution Function of the Received Power Signal | 30 |

| 2.2.3   | Model of the Receiver Sensitivity and Power Consumption        | 32 |

| 2.2.4   | Optimal Reconfigurable Thresholds                              | 33 |

| 2.2.5   | Comparison of the Proposed Receiver with an Existing Solution  | 37 |

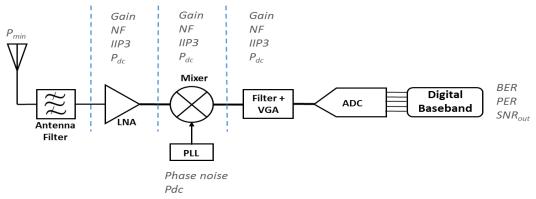

| 2.3 Li  | nk Budget on the Proposed Receiver                             | 39 |

| 2.3.1    | Key Performances of the Blocks Composing a Receiver           | 39              |

|----------|---------------------------------------------------------------|-----------------|

| 2.3.2    | Performances of the Receiver in Each Operating Mode           | 40              |

| 2.3.3    | Performances of the LNA in Each Operating Mode                | 41              |

| 2.4 Sy   | rstem-Level Analysis: Summary                                 | 42              |

| CHAPTER  | 3: DESIGN OF AN ULP LNA USING FD-SOI BODY BIASING             | : CIRCUIT-LEVEL |

| ANALYSIS |                                                               | 43              |

| 3.1 St   | ate of the Art of Inductorless ULP LNAs                       | 44              |

| 3.1.1    | Common Source (CS) Topologies                                 | 44              |

| 3.1.2    | Common Gate (CG) Topologies                                   | 48              |

| 3.1.3    | Other Design Techniques                                       | 51              |

| 3.1.4    | State of the Art inductorless ULP LNA: Conclusion             | 53              |

| 3.2 Pr   | roposed ULP LNA                                               | 54              |

| 3.2.1    | Input Impedance                                               | 54              |

| 3.2.2    | Voltage Gain                                                  | 55              |

| 3.2.3    | Noise Figure                                                  | 55              |

| 3.2.4    | Linearity                                                     | 56              |

| 3.3 D    | esign Methodology                                             | 58              |

| 3.3.1    | Behavior of the circuit                                       | 58              |

| 3.3.2    | Limitations                                                   | 61              |

| 3.4 In   | vestigations on Back Bias                                     | 63              |

| 3.5 In   | tegrated Circuit (IC) Implementation and Measurement Results  | 66              |

| 3.6 D    | esign of an ULP LNA using FD-SOI Body Biasing: Summary        | 71              |

|          | 4: Design of a Tunable LNA with FD-SOI Back<br>Level Analysis |                 |

| 4.1 St   | ate of the Art of Techniques to Add Tunability in LNAs        | 73              |

| 4.1.1    | Biasing Scaling Tuning                                        | 73              |

| 4.1.2    | Load Tuning                                                   |                 |

| 4.1.3    | Transistors Switches Tuning                                   | 79              |

| 4.1.4    | State of the Art of Tunable LNAs: Conclusion                  | 81              |

| 4.2   | Prop        | posed Tunable LNA Design                                   | 82  |

|-------|-------------|------------------------------------------------------------|-----|

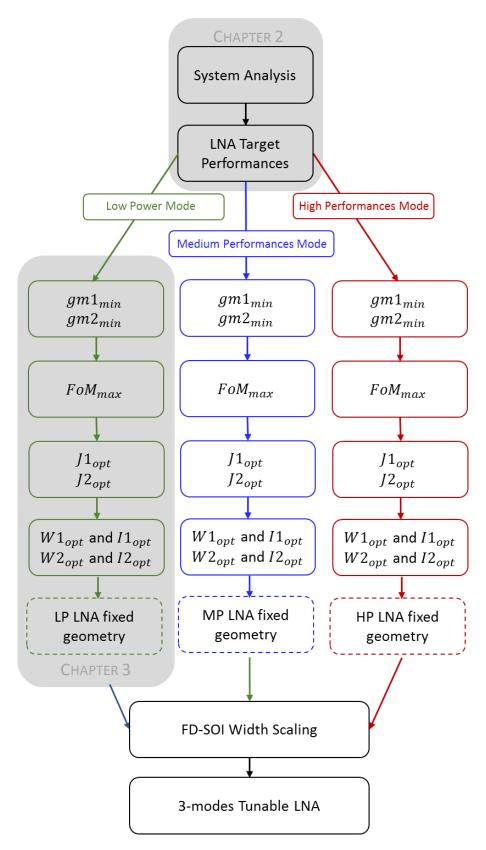

| 4.2   | 2.1         | Design Flow                                                | 82  |

| 4.2   | 2.2         | Investigation on Back Bias of FD-SOI Transistors           | 86  |

| 4.2   | 2.3         | Proposed Technique for Reconfigurable LNA Design           | 88  |

| 4.3   | Effi        | ciency Evaluation of the Proposed Technique                | 91  |

| 4.3   | 3.1         | Advantages & Limitations of the Proposed Technique         | 91  |

| 4.3   | 3.2         | Comparison of the Proposed Method with Other Methods       | 97  |

| 4.4   | Inte        | grated Circuit (IC) Implementation and Measurement Results | 101 |

| 4.4   | <b>l.</b> 1 | The Chip                                                   | 101 |

| 4.4   | 1.2         | Measurement Results                                        | 102 |

| 4.4   | 1.3         | Comparison with Existing LNAs                              | 107 |

| 4.5   | Des         | ign of a Tunable LNA with FD-SOI Back Gate Tuning: Summary | 110 |

| Снарт | ER 5        | : CONCLUSION AND PERSPECTIVES                              |     |

| 5.1   | Key         | Contributions of This Work                                 | 112 |

| 5.2   | Futi        | are Work                                                   | 113 |

| 5.3   | List        | of Contributions                                           | 114 |

| APP   | PENDI       | X                                                          | 116 |

| LN    | A No        | ISE CALCULATION                                            |     |

| Rin   | LIOGI       | RAPHY                                                      | 122 |

# LIST OF FIGURES

| FIGURE 1.1 50 BILLION OF CONNECTIONS IN 2020 [1]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 18   |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| FIGURE 1.2 APPLICATION DOMAINS OF THE INTERNET OF THINGS (IOT).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 19   |

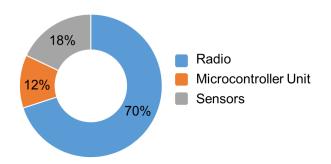

| FIGURE 1.3 REPARTITION OF THE POWER CONSUMPTION IN A WIRELESS SENSOR NODE [3]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 20   |

| FIGURE 2.1 WIRELESS LINK COMMUNICATION.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |      |

| FIGURE 2.2 BASIC CONCEPT OF WAKE-UP RADIO.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |      |

| FIGURE 2.3 ADAPTIVE TRANSCEIVER ILLUSTRATION.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |      |

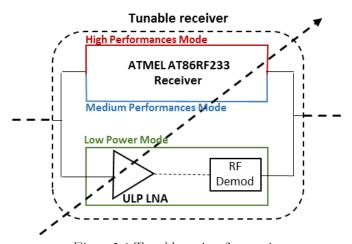

| FIGURE 2.4 ILLUSTRATION OF THE PROPOSED TUNABLE RECEIVER.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 27   |

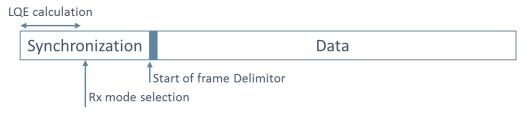

| FIGURE 2.5 SELECTION OF THE RECEIVER OPERATING MODE DURING THE SYNCHRONIZATION PREAMBLE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |      |

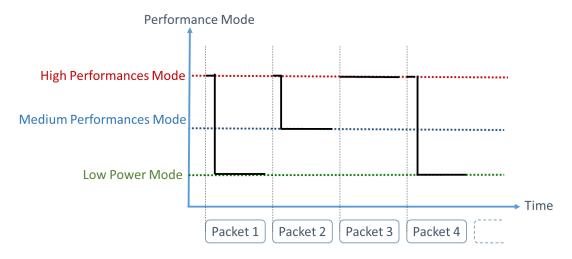

| FIGURE 2.6 INTRA-FRAME 3-LEVELS TUNABLE RECEIVER.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 28   |

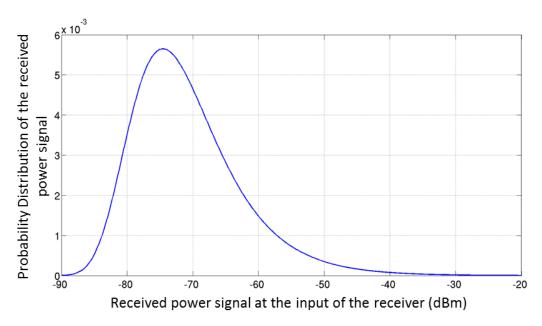

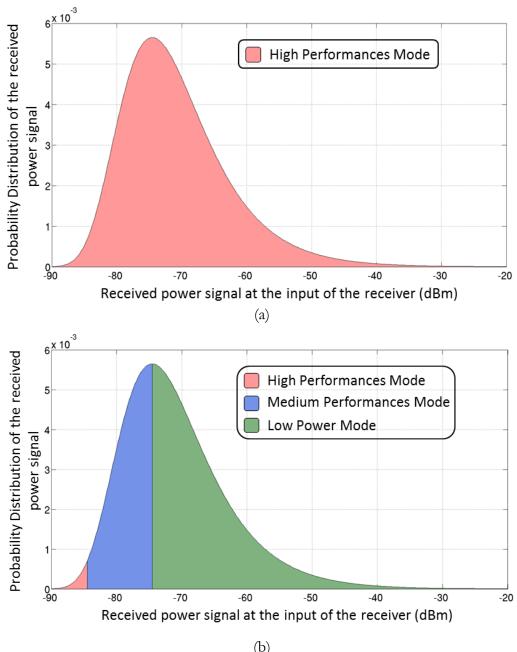

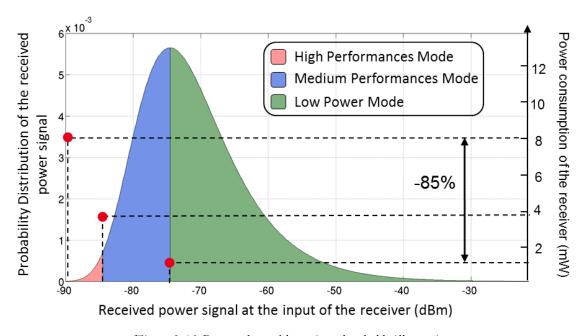

| FIGURE 2.7 PROBABILITY DISTRIBUTION FUNCTION OF THE RECEIVED POWER SIGNAL AT THE INPUT OF THE RECEIVER.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 32   |

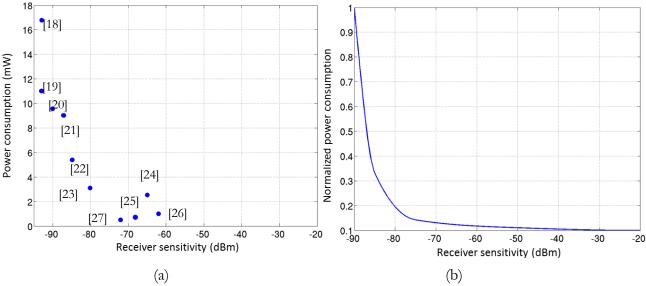

| FIGURE 2.8 POWER CONSUMPTION VERSUS THE RECEIVER SENSITIVITY: (A) STATE OF THE ART (B) NORMALIZED POWER CONSUMPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | ۱ 33 |

| FIGURE 2.9 (A) TRADITIONAL 1-MODE RECEIVER; (B) TUNABLE RECEIVER FOR POWER SAVINGS.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 34   |

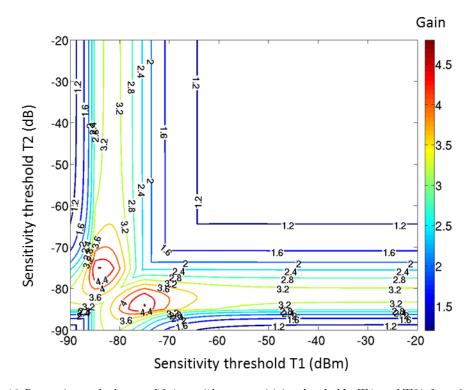

| FIGURE 2.10 BEST GAIN ON THE BATTERY LIFETIME WITH TWO SENSITIVITY THRESHOLDS (T1 AND T2) FOR A 3-MODES RECEIVER                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 35   |

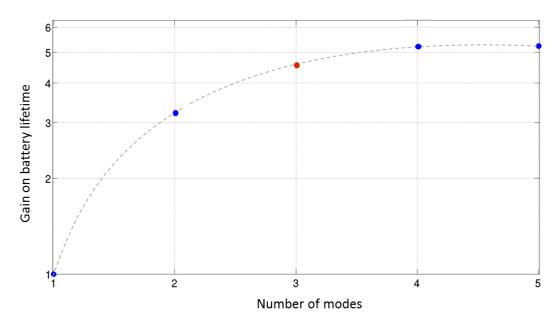

| FIGURE 2.11 MAXIMUM GAIN ON THE BATTERY LIFETIME FOR EACH NUMBER OF MODES CONFIGURATIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 36   |

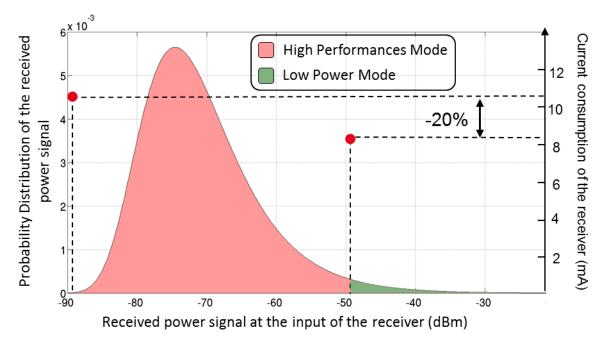

| FIGURE 2.12 TUNABLE RECEIVER THRESHOLDS ILLUSTRATION: EXTREME MODES OF THE ATMEL AT86RF233.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 38   |

| FIGURE 2.13 PROPOSED TUNABLE RECEIVER THRESHOLDS ILLUSTRATION.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 38   |

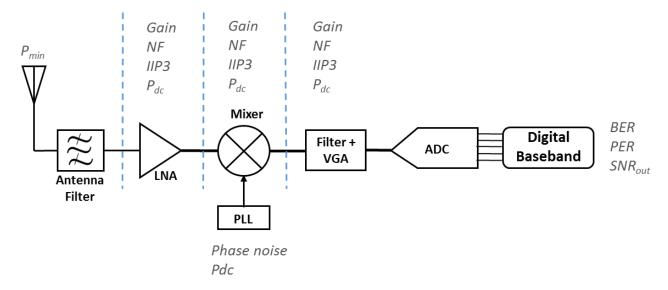

| FIGURE 2.14 TRADITIONAL RECEIVER ARCHITECTURE AND KEY PERFORMANCES OF THE BLOCKS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 40   |

| FIGURE 3.1 TUNABLE RECEIVER FIRST VERSION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 43   |

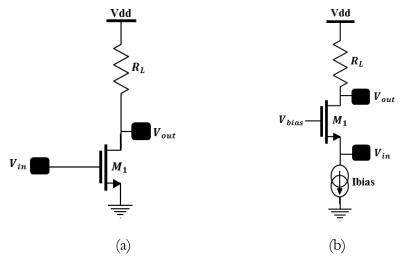

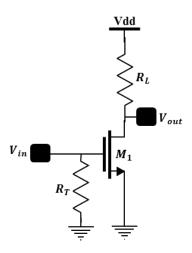

| FIGURE 3.2 BASIC TOPOLOGIES FOR AMPLIFIERS: (A) COMMON SOURCE; (B) COMMON GATE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 44   |

| FIGURE 3.3 COMMON SOURCE RESISTIVELY TERMINATED LNA.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |      |

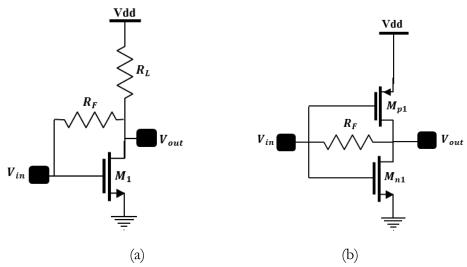

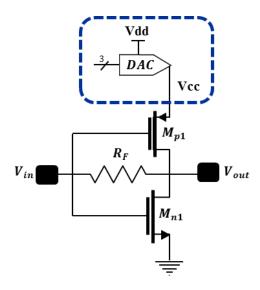

| FIGURE 3.4 COMMON SOURCE RESISTIVE SHUNT FEEDBACK LNA: (A) RESISTIVE SHUNT FEEDBACK; (B) CURRENT REUSED INVERTER                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 46   |

| FIGURE 3.5 COMMON SOURCE ACTIVE SHUNT FEEDBACK LNA.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 47   |

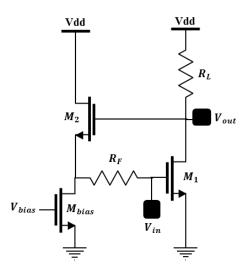

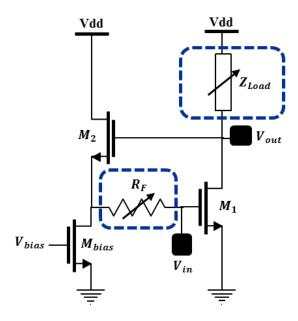

| FIGURE 3.6 COMMON GATE PASSIVE FEEDBACK TOPOLOGIES: (A) SERIES FEEDBACK; (B) CURRENT REUSED INVERTER                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 48   |

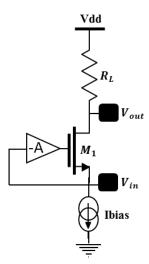

| FIGURE 3.7 COMMON GATE ACTIVE SHUNT FEEDBACK TOPOLOGY                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 49   |

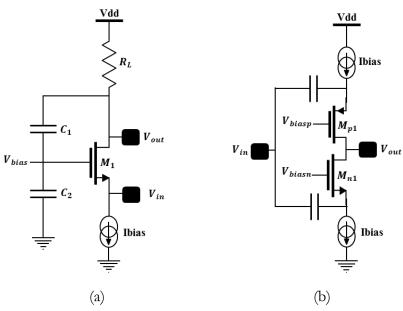

| FIGURE 3.8 COMMON GATE FEEDFORWARD TOPOLOGY                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 50   |

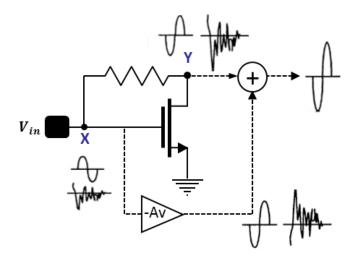

| FIGURE 3.9 NOISE CANCELLING TECHNIQUE [44].                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 51   |

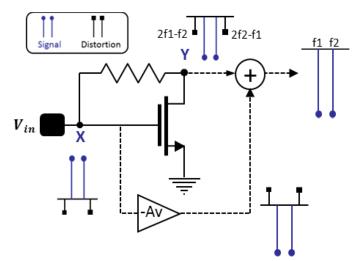

| FIGURE 3.10 DISTORTION CANCELLING TECHNIQUE [46]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 52   |

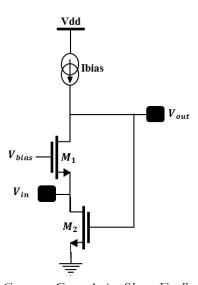

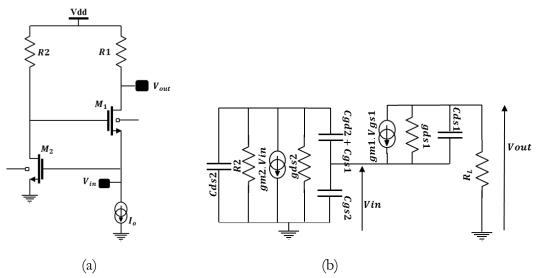

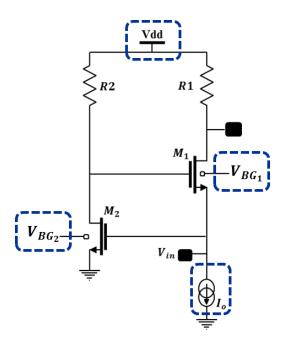

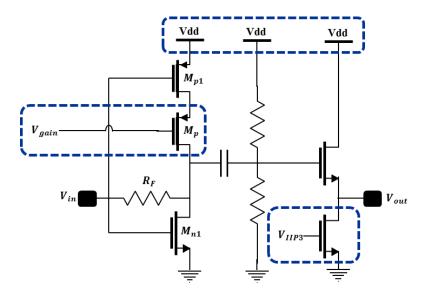

| FIGURE 3.11 CG GM-BOOST LNA: (a) SCHEMATIC; (B) SMALL SIGNAL MODEL.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 54   |

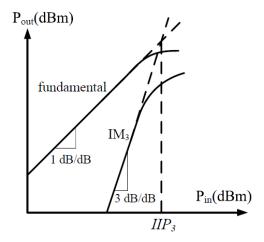

| FIGURE 3.12 DEFINITION OF IIP3: OUTPUT POWER VERSUS INPUT POWER AT TWO FREQUENCIES.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 57   |

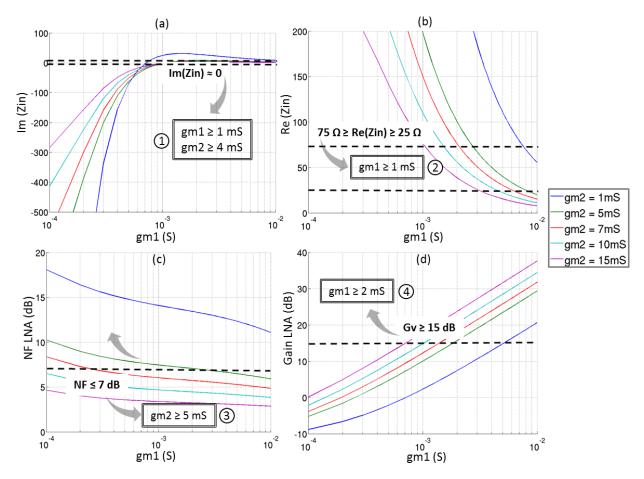

| FIGURE 3.13 BEHAVIOR OF THE CIRCUIT FOR SEVERAL (GM1, GM2): (A) IMAGINARY PART OF ZIN; (B) REAL PART OF ZIN; (C) NOISE FIGURE 3.13 BEHAVIOR OF THE CIRCUIT FOR SEVERAL (GM1, GM2): (A) IMAGINARY PART OF ZIN; (B) REAL PART OF ZIN; (C) NOISE FIGURE 3.13 BEHAVIOR OF THE CIRCUIT FOR SEVERAL (GM1, GM2): (A) IMAGINARY PART OF ZIN; (B) REAL PART OF ZIN; (C) NOISE FIGURE 3.13 BEHAVIOR OF THE CIRCUIT FOR SEVERAL (GM1, GM2): (A) IMAGINARY PART OF ZIN; (B) REAL PART OF ZIN; (C) NOISE FIGURE 3.13 BEHAVIOR OF ZIN; (C) NOISE FIGURE 3.14 BEHAVIOR OF ZIN; (C) NOISE FIGURE 3.14 BEHAVIOR (D) VOLTAGE GAIN IN dB. |      |

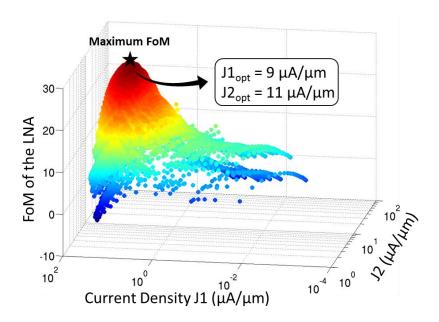

| FIGURE 3.14 FACTOR OF MERIT OF THE LNA VERSUS THE CURRENT DENSITY OF TRANSISTORS M1 AND M2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |      |

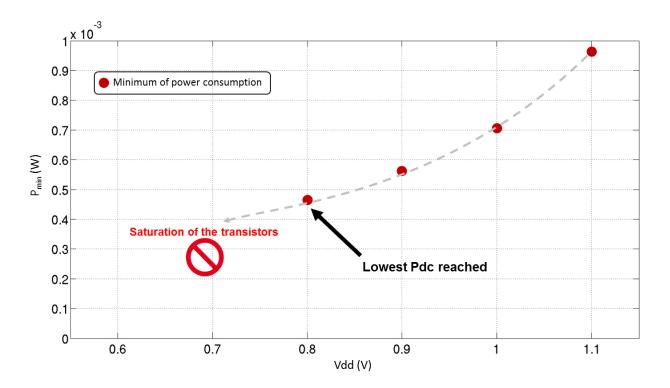

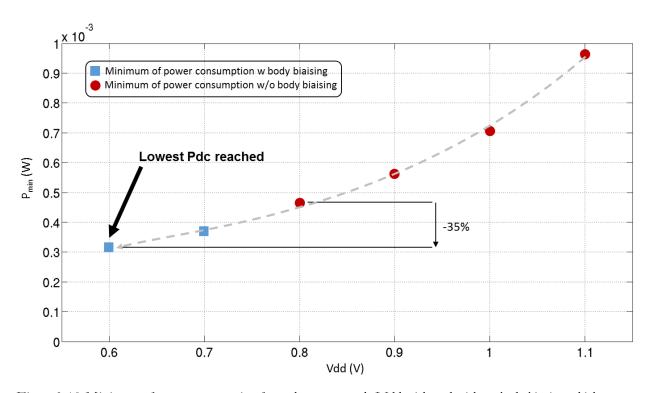

| FIGURE 3.15 MINIMUM OF POWER CONSUMPTION FOR EACH POWER SUPPLY VDD WHICH RESPECTS THE CONDITIONS NOISE FIGURE <                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |      |

| AND GAIN > 15 dB.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |      |

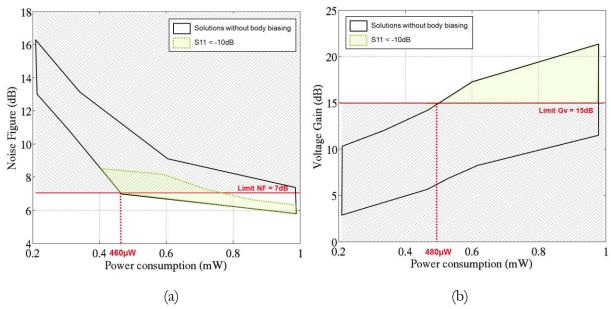

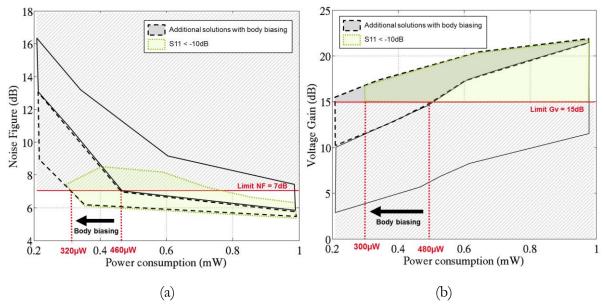

| FIGURE 3.16 MINIMUM OF POWER CONSUMPTION WITHOUT BODY BIASING TO GUARANTEE: (A) NOISE FIGURE < 7 dB and (B) Gain :                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |      |

| dB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |      |

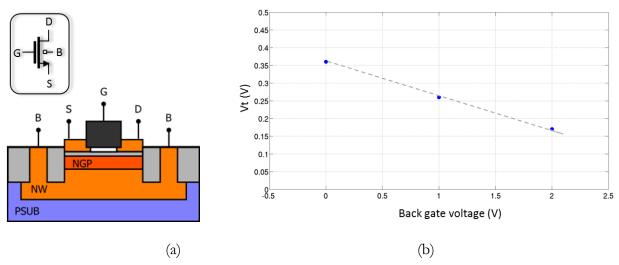

| FIGURE 3.17 FD-SOI TECHNOLOGY: (A) CROSS-SECTION OF A NMOS LVT FD-SOI TRANSISTOR; (B) VTH VERSUS BACK GATE VC               |           |

|-----------------------------------------------------------------------------------------------------------------------------|-----------|

| NMOS LVT.                                                                                                                   |           |

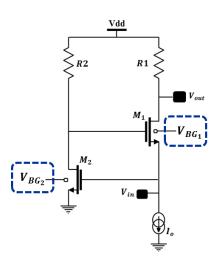

| FIGURE 3.18 COMMON GATE GM-BOOST LNA WITH BODY BIASING TUNING KNOBS.                                                        |           |

| FIGURE 3.19 MINIMUM OF POWER CONSUMPTION FOR EACH POWER SUPPLY VDD WITH BODY BIASING WHICH RESPECTS THE CO                  |           |

| Noise Figure < 7dB and Gain > 15 dB.                                                                                        |           |

| Figure 3.20 Minimum of power consumption with body biasing to guarantee: (a) Noise Figure $<$ 7 $dB$ and (b) Gai            |           |

|                                                                                                                             |           |

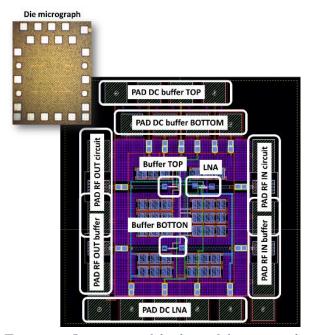

| FIGURE 3.21 LAYOUT VIEW OF THE CHIP AND DIE MICROGRAPH.                                                                     |           |

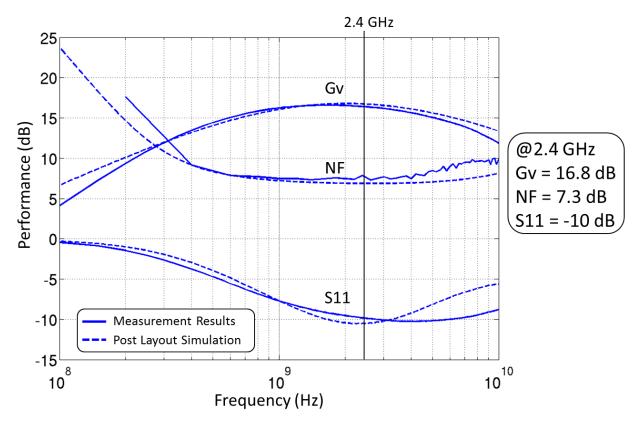

| FIGURE 3.22 GAIN, NOISE FIGURE AND INPUT MATCHING MEASUREMENTS RESULTS OF THE PROPOSED ULP LNA                              |           |

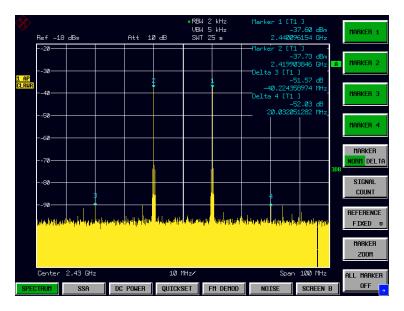

| FIGURE 3.23 IIP3 MEASUREMENT RESULT OF THE ULP LNA.                                                                         |           |

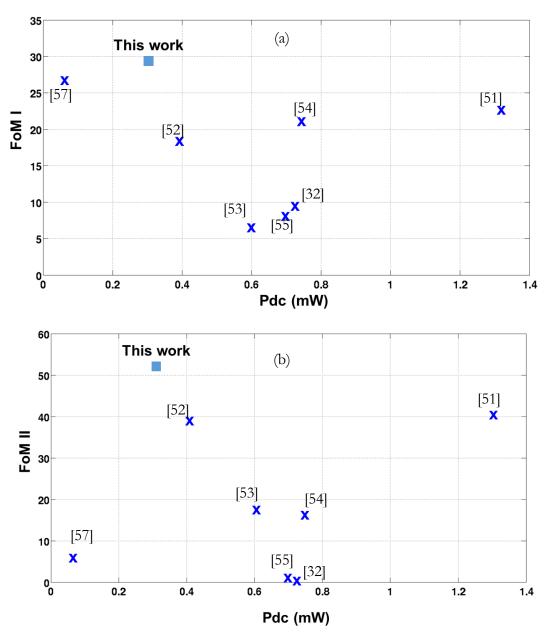

| FIGURE 3.24 COMPARISON OF THE PROPOSED LNA WITH THE STATE OF THE ART LNAS: (A) FIGURE OF MERIT I (FOM I) VERSU              |           |

| POWER CONSUMPTION AND (B) FOM II VERSUS THE POWER CONSUMPTION.                                                              | 69        |

| Figure 4.1 Reconfigurable LNA based on bias tuning technique [56]                                                           | 74        |

| FIGURE 4.2 RECONFIGURABLE LNA BASED ON POWER SUPPLY TUNING TECHNIQUE [57].                                                  | 76        |

| Figure 4.3 Reconfigurable LNA based on bias technique [60].                                                                 | 77        |

| Figure 4.4 Reconfigurable LNA based on load tuning technique [36].                                                          | 78        |

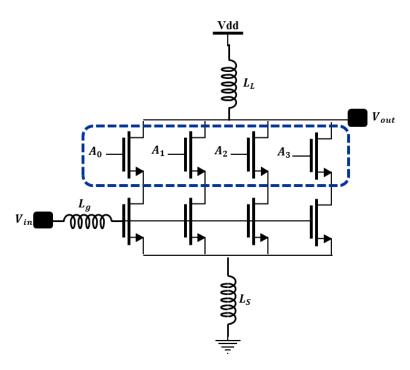

| FIGURE 4.5 RECONFIGURABLE LNA BASED ON WIDTH SCALING TECHNIQUE [63]                                                         | 80        |

| FIGURE 4.6 DESIGN FLOW OF THE PROPOSED TUNABLE LNA.                                                                         | 83        |

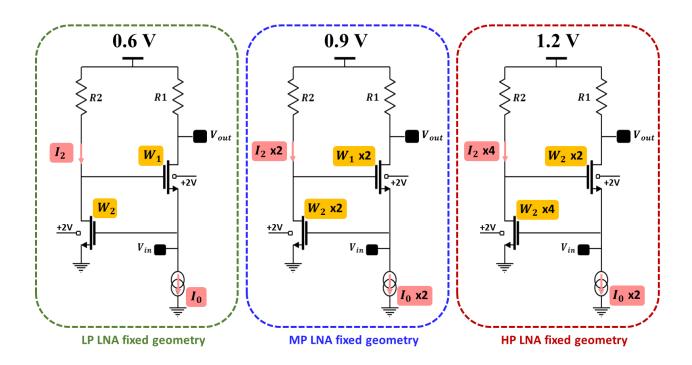

| FIGURE 4.7 DESIGN OF THREE FIXED GEOMETRY LNAS                                                                              | 84        |

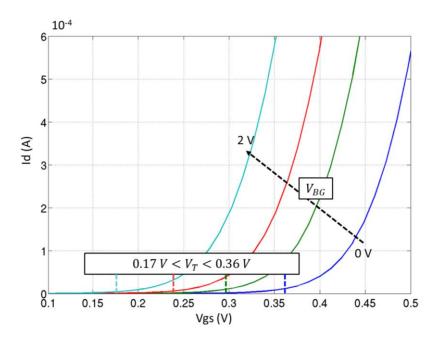

| FIGURE 4.8 DRAIN CURRENT ID VERSUS GATE-TO-SOURCE VOLTAGE VGS FOR SEVERAL BACK GATE VOLTAGE. SIMULATIONS PERFO              | RMED FOR  |

| A NLVT, W=20μm, LMIN TRANSISTOR                                                                                             | 86        |

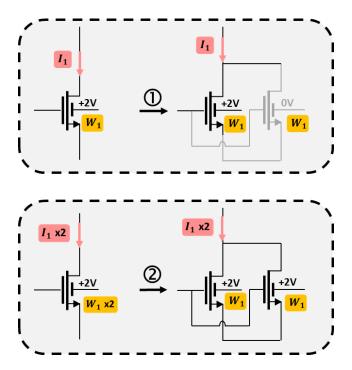

| Figure 4.9 Effects of the back gate voltage                                                                                 | 87        |

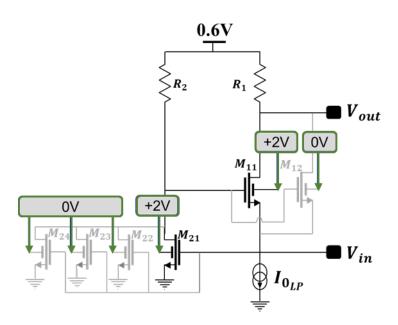

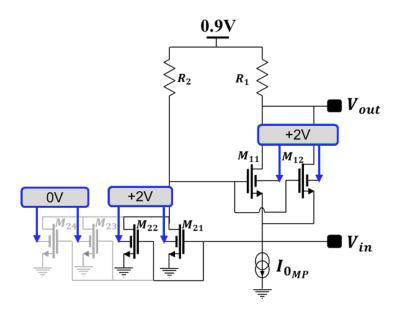

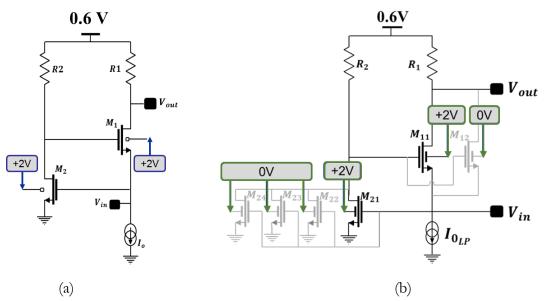

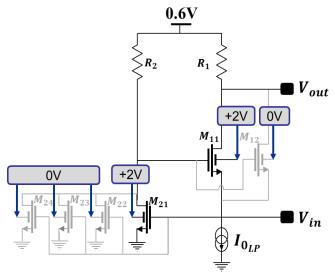

| FIGURE 4.10 PROPOSED RECONFIGURABLE FD-SOI LNA IN ITS LOW POWER MODE                                                        | 89        |

| FIGURE 4.11 PROPOSED RECONFIGURABLE FD-SOI LNA IN ITS MEDIUM PERFORMANCES MODE                                              | 89        |

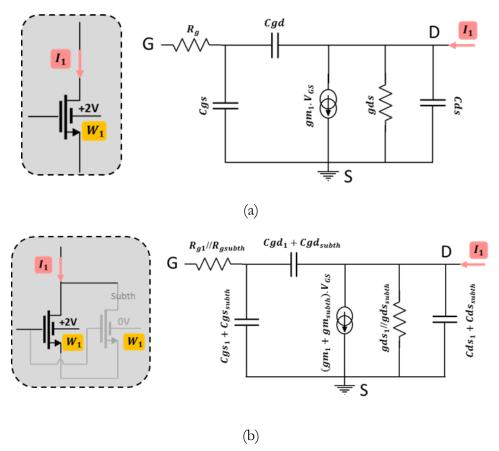

| FIGURE 4.12 PROPOSED RECONFIGURABLE FD-SOI LNA IN ITS HIGH PERFORMANCES MODE                                                |           |

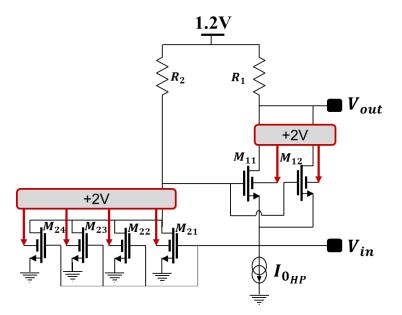

| FIGURE 4.13 THREE POSSIBILITIES TO COMPENSATE THE EFFECT OF THE SUBTHRESHOLD TRANSISTOR                                     |           |

| Figure 4.14 Small signal model of (a): the transistor in strong inversion alone and (b): the transistor in strong           | INVERSION |

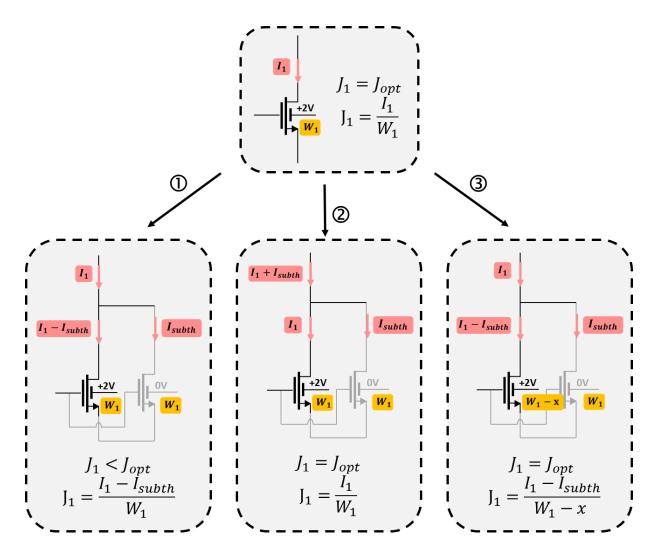

| WITH THE SUBTHRESHOLD TRANSISTOR IN PARALLEL                                                                                | 95        |

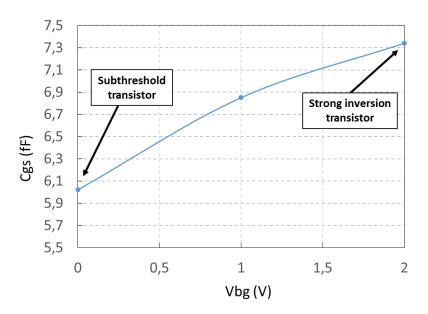

| Figure $4.15$ Simulation of the effect of the back gate on the gate-to-source capacitance at fixed biasing (VDs=5 $\%$      | )0mV;     |

| VGS=300mV) ON A SINGLE TRANSISTOR (W=20um; LMIN).                                                                           | 96        |

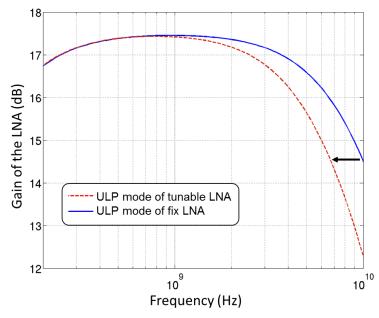

| Figure 4.16 Effect of subthreshold parallel transistors on the simulated gain of the tunable LNA in low power               |           |

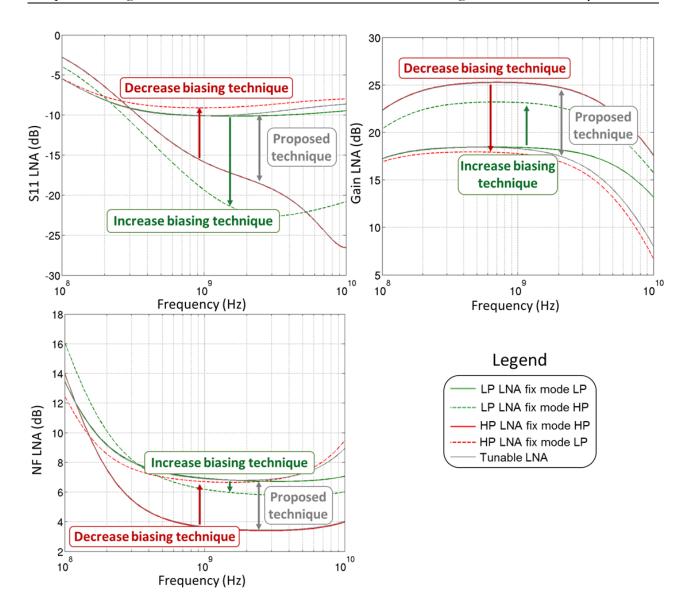

| Figure 4.17 Comparison of the Noise Figure, Gain and Input Matching of the tunability methods on the CG gm-e                |           |

| LNA.                                                                                                                        |           |

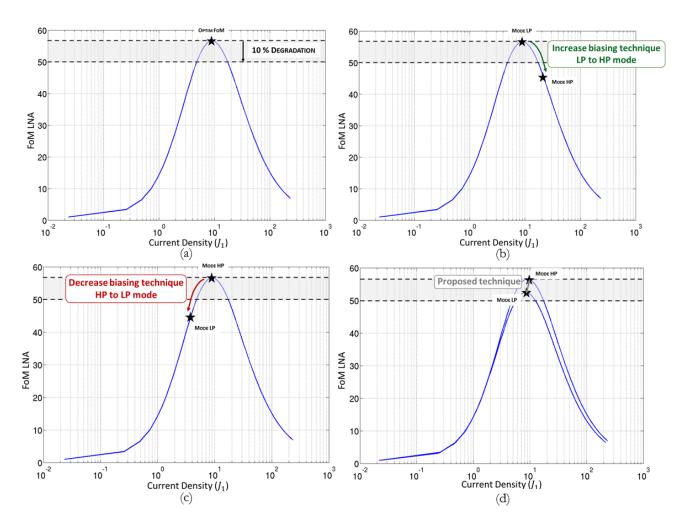

| Figure 4.18 Comparison of FoM of the tunability methods on the CG gm-boost LNA: (a) FoM versus current den                  |           |

| TRANSISTOR M1 FOR THIS STRUCTURE AND MAXIMUM DEGRADATION; (B) RESULTS FOR INCREASE BIASING TECHNIQUE; (C                    |           |

| FOR DECREASE BIASING TECHNIQUE; (D) RESULTS FOR PROPOSED TECHNIQUE                                                          | •         |

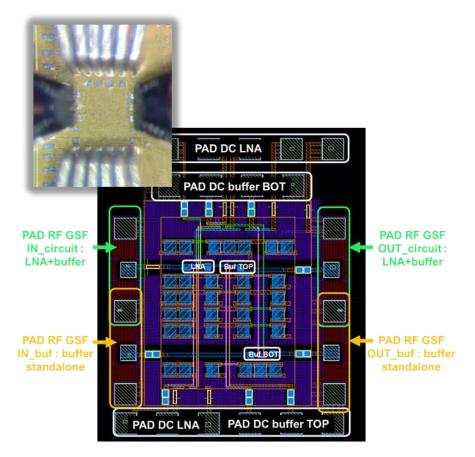

| Figure 4.19 Layout and die micrograph of the chip.                                                                          |           |

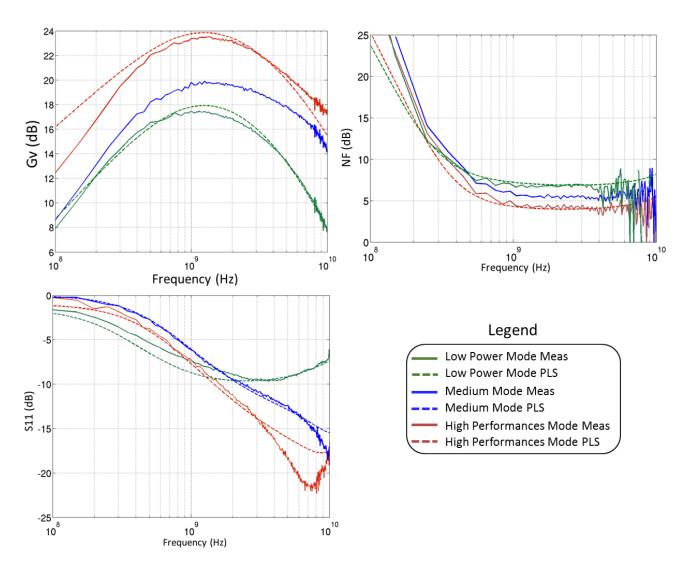

| Figure 4.20 Voltage gain (dB), noise figure (dB) and input matching (dB) measurements and Post Layout Simula                |           |

| RESULTS OF THE TUNABLE LNA IN ITS THREE OPERATING MODES.                                                                    |           |

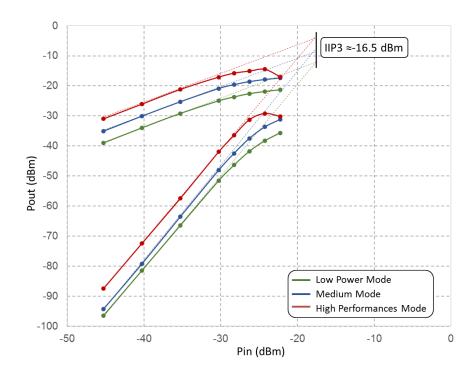

| Figure 4.21 3 <sup>RD</sup> order Input Intermodulation Point (IIP3) measurements results of the tunable LNA in its three c |           |

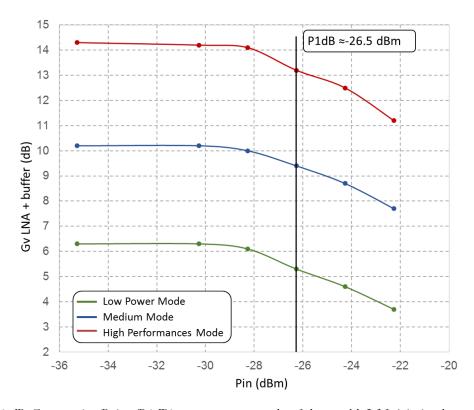

| MODES.                                                                                                                      |           |

| Figure 4.22 1-dB Compression Point (P1dB) measurements results of the tunable LNA in its three operating moi                |           |

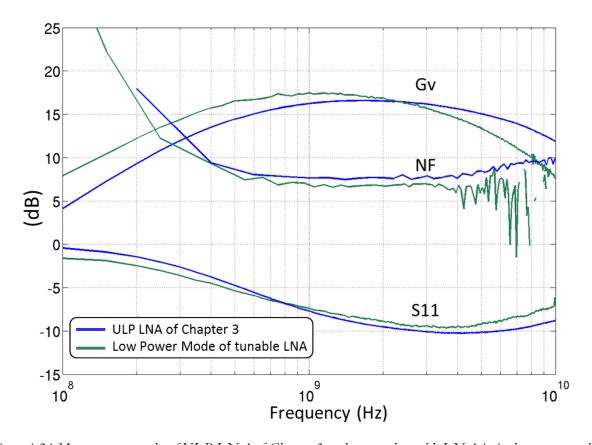

| Figure 4.23 Comparison of: (a) the ULP LNA of Chapter 3 and (b) the low power mode of the proposed tunable LNA | ا 10 4 |

|----------------------------------------------------------------------------------------------------------------|--------|

| FIGURE 4.24 MEASUREMENT RESULTS OF ULP LNA OF CHAPTER 3 AND PROPOSED TUNABLE LNA IN ITS LOW POWER MODE         | 106    |

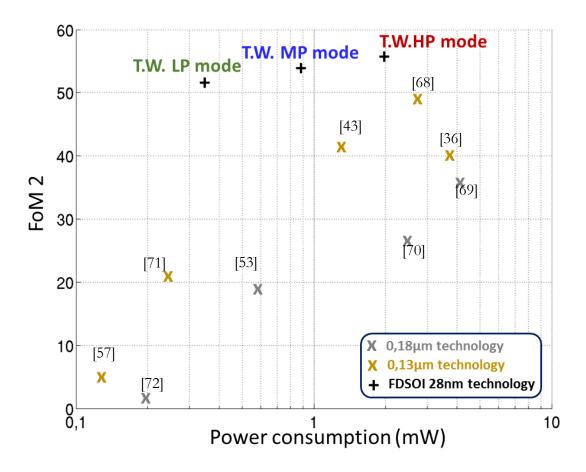

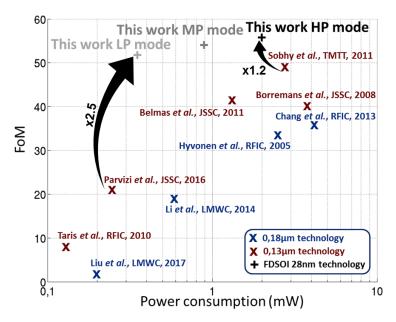

| Figure 4.25 Figure of Merit (FoM) of the State of the Art LNAs versus the power consumption                    | 107    |

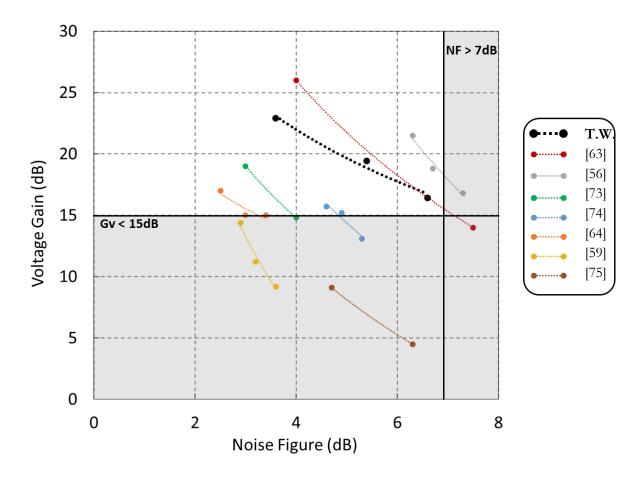

| Figure 4.26 State of the Art of tunable LNAs: variation range of performances in noise figure and voltage gain | 109    |

|                                                                                                                |        |

| FIGURE 5.1 PROBABILITY DISTRIBUTION OF THE RECEIVED POWER SIGNAL FOR SEVERAL CHANNEL CONDITIONS.               | 113    |

|                                                                                                                |        |

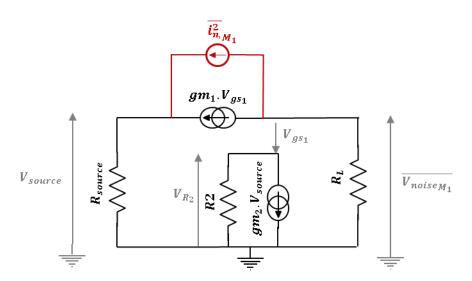

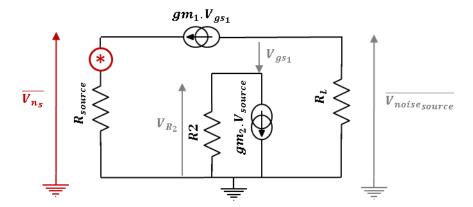

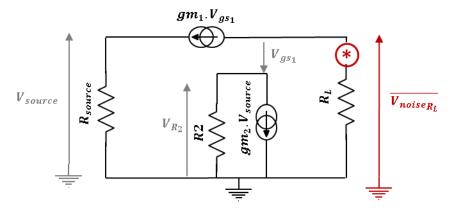

| FIGURE A.1 OUTPUT NOISE GENERATED BY TRANSISTOR M1.                                                            | 116    |

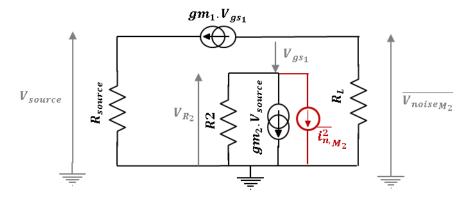

| FIGURE A.2 OUTPUT NOISE GENERATED BY TRANSISTOR M2.                                                            | 117    |

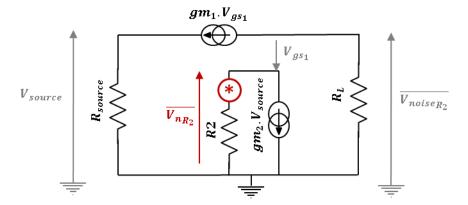

| FIGURE A.3 OUTPUT NOISE GENERATED BY RESISTANCE R2.                                                            | 118    |

| Figure A.4 Output noise generated by the source resistance Rsource.                                            | 119    |

| FIGURE A 5 OUTDUT NOISE CENEDATED BY THE LOAD DESISTANCE PI                                                    | 120    |

# LIST OF TABLES

| TABLE 2.2 SENSITIVITY THRESHOLDS FOR 3-MODES TUNABLE RECEIVER.  TABLE 2.3 COMPARISON OF THE PROPOSED RECEIVER WITH AN INDUSTRIAL MODULE.  TABLE 2.4 RECEIVER TARGETED DESIGN PERFORMANCES FOR EACH CONFIGURATION.  TABLE 2.5 LNA TARGETED DESIGN PERFORMANCES FOR EACH CONFIGURATION.  TABLE 3.1 ULP LNA SPECIFICATIONS.  TABLE 3.2 COMPARISON OF THE PROPOSED LNA WITH THE STATE OF THE ART LNAS.  TABLE 4.1 PERFORMANCES OF THE TUNABLE LNA IN [56].  TABLE 4.2 PERFORMANCES OF THE TUNABLE LNA IN [57].  TABLE 4.3 PERFORMANCES OF THE TUNABLE LNA IN [60]. | 39<br>41<br>42 |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

| TABLE 2.4 RECEIVER TARGETED DESIGN PERFORMANCES FOR EACH CONFIGURATION.  TABLE 2.5 LNA TARGETED DESIGN PERFORMANCES FOR EACH CONFIGURATION.  TABLE 3.1 ULP LNA SPECIFICATIONS.  TABLE 3.2 COMPARISON OF THE PROPOSED LNA WITH THE STATE OF THE ART LNAS.  TABLE 4.1 PERFORMANCES OF THE TUNABLE LNA IN [56].  TABLE 4.2 PERFORMANCES OF THE TUNABLE LNA IN [57].  TABLE 4.3 PERFORMANCES OF THE TUNABLE LNA IN [60].                                                                                                                                           | 41<br>42       |

| TABLE 2.5 LNA TARGETED DESIGN PERFORMANCES FOR EACH CONFIGURATION.  TABLE 3.1 ULP LNA SPECIFICATIONS.  TABLE 3.2 COMPARISON OF THE PROPOSED LNA WITH THE STATE OF THE ART LNAS.  TABLE 4.1 PERFORMANCES OF THE TUNABLE LNA IN [56].  TABLE 4.2 PERFORMANCES OF THE TUNABLE LNA IN [57].  TABLE 4.3 PERFORMANCES OF THE TUNABLE LNA IN [60].                                                                                                                                                                                                                    | 42             |

| TABLE 3.1 ULP LNA SPECIFICATIONS.  TABLE 3.2 COMPARISON OF THE PROPOSED LNA WITH THE STATE OF THE ART LNAS.  TABLE 4.1 PERFORMANCES OF THE TUNABLE LNA IN [56].  TABLE 4.2 PERFORMANCES OF THE TUNABLE LNA IN [57].  TABLE 4.3 PERFORMANCES OF THE TUNABLE LNA IN [60].                                                                                                                                                                                                                                                                                        |                |

| TABLE 3.2 COMPARISON OF THE PROPOSED LNA WITH THE STATE OF THE ART LNAS.  TABLE 4.1 PERFORMANCES OF THE TUNABLE LNA IN [56].  TABLE 4.2 PERFORMANCES OF THE TUNABLE LNA IN [57].  TABLE 4.3 PERFORMANCES OF THE TUNABLE LNA IN [60].                                                                                                                                                                                                                                                                                                                           |                |

| Table 4.1 Performances of the tunable LNA in [56]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                |

| Table 4.2 Performances of the tunable LNA in [57]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 70             |

| Table 4.3 Performances of the tunable LNA in [60].                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 75             |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 76             |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                |

| Table 4.4 Performances of the tunable LNA in [36].                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                |

| Table 4.5 Performances of the tunable LNA in [63].                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 80             |

| Table 4.6 LNA targeted design performances for each configuration.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                |

| Table 4.7 Details of the three LNAs.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                |

| Table 4.8 Evolution of the performances between options ① and ②                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 94             |

| TABLE 4.9 COMPARISON OF THE PERFORMANCES FOR THREE METHODS OF RECONFIGURATION AT A SIMULATION LEVEL                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 99             |

| Table 4.10 Measurement results of the tunable LNA at 2.4GHz.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | . 105          |

| Table 4.11 Comparison of the proposed LNA with the State of The Art LNAs.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | . 108          |

| Table 4.12 Comparison of the ranges of performances of the State of the Art tunable LNAs.                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | . 108          |

# **ABBREVIATIONS**

ADC Analog-to-Digital Convertor

BBGEN Back Bias Generator

BER Bit Error Rate

BG Back Gate

CG Common Gate

CGA Voltage Gain Amplifier

CS Common Source

DPLC Dynamic Packet Length Control FD-SOI Fully Depleted Silicon-On-Insulator

FoM Figure of Merit

Gv Voltage Gain

IC Integrated Circuit

IIP3 Input Referred Third Order Intercept Point

IM IntermodulationIoT Internet of ThingsLNA Low Noise AmplifierLQE Link Quality Estimator

NF Noise Figure

P1dB 1-dB Compression Point PDF Probability Density Function

PLL Phase Locked Loop

PVT Process, Voltages and Temperature

QoS Quality of Service

RSSI Received Strength Signal Indicator SNDR Signal to Noise Distortion Ratio

SNR Signal to Noise Ratio

SoA State of the Art

SPI Serial Peripheral Interface

ULP Ultra-Low Power

ULV Ultra-Low Voltage

UTBB Ultra-Thin Body and Buried oxide

WSN Wireless Sensor Network

| 16 |  |  |  |

|----|--|--|--|

|    |  |  |  |

# CHAPTER 1

### **INTRODUCTION**

ommunicating objects are inviting themselves into daily life and the physical world becomes more and more digitized. This emerging technological age, called the Internet of Things (IoT), unveils new requirements in terms of cost, surface area and battery lifetime. The challenge is to find innovative solutions to add intelligence to communicating systems.

In this Chapter, the context of Wireless Sensor Network (WSN) for IoT applications is first presented. Then, the challenges in the design of wireless transceivers for WSN due to this IoT paradigm are commented. The interest of the Ultra-Thin Body and Buried-oxide Fully Depleted Silicon-On-Insulator (UTBB FD-SOI) technology to improve performances and flexibility of communicating nodes is discussed. Finally, the thesis organization and purpose are highlighted.

### 1.1 INTERNET OF THINGS AND WIRELESS SENSOR NETWORKS

Based on the Ericsson annual report of 2010 [1], the world went through a turning point for mobile communications which gave rise to a massive development of connections (more than 50 billion of connections are expected this year) as depicted in Figure 1.1. Objects are now connected to the Internet services, able to recognize their environment, to organize themselves into networks or interact with humans. IoT is totally shifting the way people interact with their surroundings.

# Turning point for mobile communication PEOPLE PLACES 1980 1990 2000 2010 2020

### 50 BILLION CONNECTIONS IN 2020

Figure 1.1 50 billion of connections in 2020 [1].

What makes IoT devices and components "smart" are the numerous sensors and microprocessors featuring the devices which enable advanced functionalities. WSNs are several types of sensors able to monitor information, to sense the environment, to collect important data and send them to a management entity. They are part of today's IoT paradigm.

As illustrated in Figure 1.2, there are various domains of applications of WSNs. Traditional homes or workplaces can be transformed to smart homes or smart workplaces. Intelligence can be broadened to a whole city becoming a smart city. In the health domain the IoT is also providing solutions.

Figure 1.2 Application domains of the Internet of Things (IoT).

This massive development of sensors for IoT applications means wireless communicating nodes with small form factor for an easy distribution in the environment, reduced power consumption for an extended lifetime and limited impact on the environment as detailed in [2].

This vision of the IoT induces major challenges in the design of autonomous WSNs. The limited battery storage is the blocking point of fully energy autonomy. In fact, the evolution of battery technologies is not able to follow the trend of the drastic increase of energy efficiency.

These emergent technologies unveil new constraints for Integrated Circuit (IC) design.

### 1.2 CHALLENGES IN TRANSCEIVER DESIGNS

The power consumption of a node is shared between the radio communication part, the MicroController Unit (MCU) and sensors. For IoT applications, the radio part is one of the most power hungry part as illustrated in Figure 1.3 [3]. Therefore, it is of importance to further reduce the power consumption of RadioFrequency (RF) transceivers.

Figure 1.3 Repartition of the power consumption in a wireless sensor node [3].

Wireless communicating objects call for a high level of specifications to guarantee the Quality of Service (QoS) of specific standards along with a small power consumption.

Hence, challenges in Radio Frequency Integrated Circuit (RFIC) dedicated to IoT applications are as follows:

- SMALL FORM FACTOR: reducing the size of communicating nodes by decreasing the footprint of the circuits for total transparency in the environment and unobtrusive network to propose a "green connected planet";

- LOW POWER: in a large network with many communicating nodes, battery replacement can be difficult, expensive or even impossible. Nodes have to be able to operate over a long period of time;

- LOW COST: the deployment of billions of connected objects is only possible if the cost of a node is very low;

- QUALITY: fulfilling the performance requirements in order to respect the targeted QoS set by the standards is essential.

Therefore, further deployment of communicating objects demands a smart use of the available power budget. Consequently, these challenges become important targets in IoT RFIC designs to yield long lifetime autonomous WSNs which cope with these new constraints. The next Subsection demonstrates how advanced technologies can contribute to address the aforementioned challenges.

### 1.3 FD-SOI TECHNOLOGY: GOOD CANDIDATE FOR IOT APPLICATIONS

The technology scaling following the Moore's law is getting harder to keep on. The evolution towards the down-scaling of the sizes of transistors gates has reached its limits with the conventional bulk Complementary Metal Oxide Semi-conductor (CMOS) technology. In deeply scaled CMOS transistors, due to their narrow channels, small-geometry effects start to affect their behavior. The Short Channel Effects (SCE), as the Drain-Induced Barrier Lowering (DIBL) and the velocity saturation tend to increase the standby leakage currents and reduce the current efficiency of a transistor. As a consequence, the gate cannot completely shut down the transistor and the subthreshold leakage currents appear between the drain and the source [4].

A promising technology for overcoming this limitation is the FD-SOI technology. In fact, the critical and massive deployment of the IoT requires efficient energy flexibility. Therefore, adaptive solutions able to operate at different voltage supplies, even at very low voltages around threshold levels, are needed. The FD-SOI technology provides this flexibility and offers good performances from normal voltage operation mode to low voltage levels. Moreover, this technology is promising for designing very low leakage systems when the node will remain in idle state. The application of a back biasing voltage in FD-SOI enables a compromise between very low leakage and high speed and can change the operating conditions depending on the state of the device as demonstrated in [5].

The FD-SOI technology is therefore a good candidate to perform flexibility and to fulfil the needs of the wide deployment of the IoT applications:

- SMALL FORM FACTOR: the use of advanced node FD-SOI 28 nm technology is part of the surface reduction. The design of inductorless structures is also a good solution to decrease the surface area of the chip;

- LOW POWER: this technology offers possibility to decrease the power supply and to reduce the power consumption while maintaining good performances;

- LOW COST: the FD-SOI technology is a solution for integration of digital, analog mixed and Radio Frquency (RF) signals in a single System on Chip (SoC)

- QUALITY: the FD-SOI technology is able to provide a wide range of tunability between high speed and low leakage [5].

This work proposes to take advantage of this advanced node in order to, first, improve the performances of the analog part which becomes predominant as long as the technology scales and then, add tunability in circuits to work at minimum power levels.

### 1.4 THESIS PURPOSE AND ORGANIZATION

The purpose of this research is to reduce the energy dedicated to communication in wireless sensor nodes by bringing flexibility throughout technological and architectural solutions. First, a system level approach is proposed to increase the battery lifetime of WSNs is proposed. The FD-SOI technology is then investigfated to address the concept of tunability in Radio modules introduced in the system-level approach. The final target is the design of a low area and Ultra Low Power (ULP) Low Noise Amplifier (LNA) which can optimally adapt its performances and power consumption with the real-time needs of the receiver.

To address this goal, the thesis is organized as follow:

- Chapter 2 proposes a new approach to increase the battery lifetime of a radio receiver based on a discrete reconfiguration of the set of performances. More specifically, it defines with analytic demonstrations the thresholds of reconfiguration enabling a significant power saving.

- Chapter 3 concentrates on an optimization of the power consumption of the first block of a receiver: the LNA. It details the optimization of the design of an inductorless LNA able to address the low power mode of the tunable receiver. An investigation on the use of the body biasing of the FD-SOI technology to decrease the power supply and thus, the power consumption of the LNA without loss of performance is also proposed.

- Chapter 4 presents the design of a reconfigurable LNA which suits the three levels of performance defined in Chapter 2. It describes a new method to change the effective width of amplifying transistors in order to achieve at a maximum Figure of Merit (FoM) for each mode of operation.

- Chapter 5 outlines the conclusion of this thesis and discusses the future investigations.

### CHAPTER 2

### TUNABLE RECEIVER: SYSTEM-LEVEL ANALYSIS

he explosion of multimedia wireless applications for consumer electronics makes the power consumption a key metric in the design of multi-mode wireless portable devices. Conventional transceivers have fixed performances and are designed to meet high performance in all wireless link conditions. However, most of the time, the channel is not at worst case and these transceivers are therefore over specified. Being aware of the channel link conditions would allow such devices to adapt themselves and to significantly reduce their power consumption. However, the challenge is that the Quality of Service (QoS) of adaptive transceivers should be equivalent to that offered by conventional ones, to stay competitive. As an example, neither the communication range nor the data rate can be degraded. Therefore, the sensitivity of the proposed receiver has to be equal to the sensitivity of today's products.

This Chapter explores the benefits of an adaptive receiver featuring different modes of operation to save power. From a general perspective the proposed investigations address one of the tough challenges posed by the massive deployment of Internet of Things (IoT) communicating nodes:

### How can battery lifetime of communicating nodes be significantly extended?

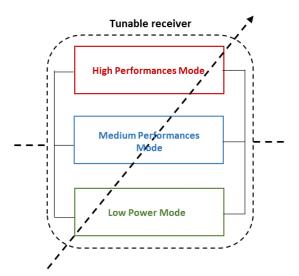

To answer this question, this Chapter proposes an adaptation technique for the design of a tunable receiver which can always operate at the edge of needed performances and thus, at minimum power consumption while keeping the needed QoS.

A State of the Art (SoA) of adaptive systems is first presented in order to evaluate the existing solutions dedicated to reduce the power consumption. Then, the general approach of the proposed channel aware receiver is described. A methodology to define the thresholds of reconfiguration for maximum energy efficiency in a receiver is detailed. Finally, a link budget analysis of the entire receiver down to the Low Noise Amplifier (LNA) is proposed in order to validate the feasibility of the proposed system analysis.

### 2.1 STATE OF THE ART OF ADAPTIVE RECEIVER TECHNIQUES

The energy cost of a transmission can be, at first order, assimilated to the integration of the instantaneous power consumption over the transmission duration. The possibilities to reduce this energy cost are twofold: reducing the instantaneous power consumption of the transceiver, or decreasing the transmission duration.

The performance degradation of energy reduction techniques is evaluated through the wireless link budget of Equation (2.1) [7].

$$SNR_{min} = P_{TX} - CL - (10.\log(BW) - 174 + NF)$$

(2.1)

With  $SNR_{min}$  in dB the minimum Signal to Noise Ratio required for correct quality of transmission,  $P_{TX}$  the transmission power in dBm, CL the Channel Loss in dB, BW the receiver bandwidth, -174 dBm the noise floor and NF the Noise Figure of the receiver.

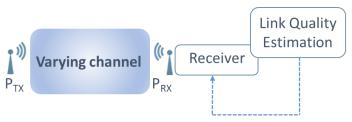

Figure 2.1 illustrates a transmission between the transmitter and the receiver with the basic metrics of the wireless link equation.

Figure 2.1 Wireless link communication.

Therefore, reducing the energy cost of a transmission can be achieved by decreasing  $P_{TX}$  in the transmission module, and/or reducing the NF or BW of the receiver part, or varying the required  $SNR_{min}$ . Many works have been proposed to decrease the transmitted power such as adaptive Power Amplifier (PA) on the transmitter part.

This work concentrates on the receiver part. Different power reduction and adaptation strategies have already been proposed in the State of the Art as detailed in next Subsections.

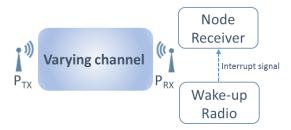

### 2.1.1 WAKE-UP RECEIVERS

A first well-known solution is to resort to wake-up radio. This technique consists of adding a supplemental receiver in parallel to the main receiver. Its goal is to listen to the channel and to switch ON the main receiver only when a communication is requested. The basic concept of wake up radio is depicted in Figure 2.2.

In [8], a wake up radio design is proposed consuming only 52  $\mu$ W. It shows that a wake up receiver is a good solution to drastically reduce the power consumption of the receiver.

Figure 2.2 Basic concept of Wake-Up radio.

However, to decrease this consumption, the sensitivity is degraded to -72 dBm with 100 kbps of data rate. It is therefore impossible to detect a distant communicating node. This approach is very interesting to decrease the power consumption of short range communication but does not fulfill the high QoS required by the standards.

### 2.1.2 MAC OR NETWORK LEVEL ADAPTABILITY

New solutions to save power on the RadioFrequency (RF) communication have also been developed at MAC or network level such as energy efficient protocols where the transmission data rate can vary when the sensitivity of the node is reduced [9].

Adjusting the data rate to the receiver sensitivity technique has also been used in the industry. For instance, the Atmel AT86RF231 module proposes a variation of its data rate from 250 kb/s to 2 Mb/s. Consequently, the sensitivity is decreased from -101 dBm to -88 dBm respectively.

The work proposed in [10] adapts the spreading code lengths and enables an improvement of the battery lifetime of 36 %. A low power adaptive digital baseband for standard IEEE 802.15.4 through a variation of word length and sampling frequency is presented in [11]. Another technique to increase the battery lifetime is to modulate the transmitted packet length. In [12], a Dynamic Packet Length Control (DPLC) has been proposed for Wireless Sensor Network (WSN) applications. The authors show that the ratio between received useful bytes and the overall transmitted bytes can be used as a Link Quality Estimator (LQE). The results show a maximum power reduction of 41.8%

compared to a fixed frame length implementation. Nevertheless, the modulation on frame technique is more efficient on applications where large volumes of data have to be transmitted.

These approaches address mainly digital baseband. This is indeed particularly interesting but to be fully energy efficient, tunability has to be added to the analog-RF part of the receiver which consumes a significant portion of the power.

### 2.1.3 ANALOG-RF ADAPTABILITY