# Déploiement d'applications parallèles sur une architecture distribuée matériellement reconfigurable

Roland Christian Gamom Ngounou Ewo

#### ▶ To cite this version:

Roland Christian Gamom Ngounou Ewo. Déploiement d'applications parallèles sur une architecture distribuée matériellement reconfigurable. Automatique. Université de Cergy Pontoise, 2015. Français. NNT: 2015 CERG0773. tel-01344747

## HAL Id: tel-01344747 https://theses.hal.science/tel-01344747

Submitted on 12 Jul 2016

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

### THÈSE DE DOCTORAT DE L'UNIVERSITÉ DE CERGY-PONTOISE

Spécialité

### Science Technique Informatique Communication

Cergy

Présentée par

### Roland Christian GAMOM NGOUNOU EWO

Pour obtenir le grade de

### DOCTEUR de l'UNIVERSITÉ CERGY-PONTOISE

Sujet de la thèse:

# Déploiement d'applications parallèles sur une architecture distribuée matériellement reconfigurable

Soutenue le 22 Juin 2015

devant le jury composé de :

| M. Bertrand GRANADO        | LIP6 (Paris)  | Directeur de thèse |

|----------------------------|---------------|--------------------|

| M. Fabrice MULLER          | LEAT (Nice)   | Rapporteur         |

| M. Samy Meftali            | LIFL (Lille)  | Rapporteur         |

| M. Bertrand Hilaire FOTSIN | ETS (Dschang) | Co-directeur       |

| M. Emmanuel CHAILLOUX      | LIP6 (Paris)  | Examinateur        |

| M. Andréa PINNA            | LIP6 (Paris)  | Examinateur        |

| M. Benoît Miramond         | ETIS (Cergy)  | Examinateur        |

| M. Sébastien PILLEMENT     | IETR (Nantes) | Examinateur        |

|                            |               |                    |

Roland Christian GAMOM NGOUNOU EWO

30 juin 2015

#### Résumé

Parmi les cibles architecturales susceptibles d'être utilisées pour réaliser un système de traitement sur puce (SoC), les architectures reconfigurables dynamiquement (ARD) offrent un potentiel de flexibilité et de dynamicité intéressant. Cependant ce potentiel est encore difficile à exploiter pour réaliser des applications massivement parallèles sur puce. Dans nos travaux nous avons recensé et analysé les solutions actuellement proposées pour utiliser les ARDs et nous avons constaté leurs limites parmi lesquelles : l'utilisation d'une technologie particulière ou d'architecture propriétaire, l'absence de prise en compte des applications parallèles, le passage à l'échelle difficile, l'absence de langage adopté par la communauté pour l'utilisation de la flexibilité des ARDs, ....

Pour déployer une application sur une ARD il est nécessaire de considérer l'hétérogénéité et la dynamicité de l'architecture matérielle d'une part et la parallélisation des traitements d'autre part. L'hétérogénéité permet d'avoir une architecture de traitement adaptée aux besoins fonctionnels de l'application. La dynamicité permet de prendre en compte la dépendance des applications au contexte et de la nature des données. Finalement, une application est naturellement parallèle.

Dans nos travaux nous proposons une solution pour le déploiement sur une ARD d'une application parallèle en utilisant les flots de conception standard des SoC. Cette solution est appelée MATIP (MPI Application Task Integreation Platform) et utilise des primitives du standard MPI version 2 pour effectuer les communications et reconfigurer l'architecture de traitement. MATIP est une solution de déploiement au niveau de la conception basée plate-forme (PBD).

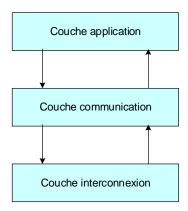

La plateforme MATIP est modélisée en trois couches : interconnexion, communication et application. Nous avons conçu chaque couche pour que l'ensemble satisfasse les besoins en hétérogénéité et dynamicité des applications parallèles . Pour cela MATIP utilise une architecture à mémoire distribuée et exploite le paradigme de programmation parallèle par passage de message qui favorise le passage à l'échelle de la plateforme.

MATIP facilite le déploiement d'une application parallèle sur puce à travers un *template* en langage Vhdl d'intégration de tâches. L'utilisation des primitives de communication se fait en invoquant des procédures Vhdl.

MATIP libère le concepteur de tous les détails liés à l'interconnexion, à la communication entre les tâches et à la gestion de la reconfiguration dynamique de la cible matérielle. Un démonstrateur de MATIP a été réalisée sur des FPGA Xilinx à travers la mise en œuvre d'une application constituée de deux tâches statiques et deux tâches dynamiques. MATIP offre une bande passante de 2,4 Gb/s et une la latence pour le transfert d'un octet de 3,43 µs ce qui comparée à d'autres plateformes MPI (TMD-MPI, SOC-MPI, MPI HAL) met MATIP à l'état de l'art.

#### Remerciements

Cette thèse à bénéficié de nombreuses contributions que je souhaite mentionner ici.

#### Je remercie:

- MM MULLER Fabrice et MEFTALI Samy pour avoir accepté d'être les rapporteurs de cette thèse. Leurs précieuses observations, questions et remarques ont permis d'enrichir ce travail.

- Tous les membres du jury pour la peine qu'ils se donnée à examiner ce travail.

#### Ma reconnaissance va à :

- M. MBOUENDA Martin qui m'a formé comme étudiant, m'a coché en tant qu'enseignant puis m'a encouragé dans mes travaux de recherches.

- M. FOTSIN Hilaire Bertrand, mon co-directeur, pour ses encourageants, ses recommandations et son travail de relecture et corrections.

- M. PINNA Andréa pour ses conseils scientifiques, son travail de relecture et corrections.

- M. BOBDA Christophe de l'Université de l'Arkansas (U.S.A) qui a répondu favorablement à ma demande d'informations.

#### Ma profonde gratitude:

- À M. GRANADO Bertrand, mon Directeur de thèse, pour sa confiance, sa disponibilité, ses conseils scientifiques ainsi que son soutien logistique, matériel et financier sans lesquels cette thèse n'aurait pas été réalisée.

- Aux membres des équipes ASTRE du laboratoire ETIS de Cergy-Pontoise et SYEL du laboratoire LIP6 de Paris pour leur accueil et les moments conviviaux que nous avons passés ensemble.

- Au Ministère de la Coopération française (Campus France) et l'Université de Douala qui ont participé au financement de cette thèse.

- A Mme BEBOA EWO, ma mère, pour son soutien à toute épreuve, ses conseils et orientations littéraires.

- À Coretta GAMOM, mon épouse, pour ses encourageants et l'encadrement solitaire de nos enfants pendant mon absence.

## Table des matières

| Li    | iste d               | les tab | bleaux                                                  | 11 |

|-------|----------------------|---------|---------------------------------------------------------|----|

| $T_i$ | able (               | des fig | ures                                                    | 13 |

| Li    | ${ m iste} \ { m d}$ | les abr | réviations                                              | 17 |

| In    | trod                 | uction  | générale                                                | 21 |

| 1     | $\operatorname{Pro}$ | bléma   | tique                                                   | 23 |

|       | 1.1                  | Introd  | luction                                                 | 24 |

|       | 1.2                  | Les pi  | rincipales contraintes des systèmes sur puce            | 25 |

|       |                      | 1.2.1   | Augmenter la puissance de traitement                    | 25 |

|       |                      | 1.2.2   | La flexibilité du développement                         | 26 |

|       |                      | 1.2.3   | Économiser les ressources matérielles et l'énergie      | 26 |

|       |                      | 1.2.4   | Accomplir simultanément plusieurs tâches sur puce       | 26 |

|       |                      | 1.2.5   | Un processeur sur mesure pour chaque tâche              | 27 |

|       |                      | 1.2.6   | La convergence                                          | 27 |

|       |                      | 1.2.7   | Le passage à l'échelle                                  | 27 |

|       | 1.3                  | Pourq   | uoi un MP-RSoC                                          | 27 |

|       |                      | 1.3.1   | Le Coût de fabrication des puces                        | 28 |

|       |                      | 1.3.2   | La dynamicité                                           | 28 |

|       |                      | 1.3.3   | La disponibilité                                        | 28 |

|       | 1.4                  | Les ty  | vpes d'ARD et les outils des MP-RSoC                    | 29 |

|       |                      | 1.4.1   | ARD pour MP-RSoC                                        | 29 |

|       |                      | 1.4.2   | Outils de programmation et de configuration du MP-RSoC  | 30 |

|       | 1.5                  | Les or  | ptions et les possibilités de mise en œuvre des MP-RSoC | 32 |

|       |                      | 1.5.1   | Le partitionnement du MP-RSoC                           | 32 |

|       |                      | 1.5.2   | Les modules du MP-RSoC                                  | 32 |

|       |                      | 1.5.3   | Partition statique et partition dynamique du MP-RSoC    | 33 |

|       | 1.6                  | Le MI   | P-RSoC : un système parallèle                           | 34 |

|       |                      | 1.6.1   | Tâches matérielles et tâches logicielles                | 34 |

|       |                      | 1.6.2   | Les architectures de traitements parallèles             | 34 |

|   |     | 1.6.3    | Modèles mémoire de l'application parallèle                        |

|---|-----|----------|-------------------------------------------------------------------|

|   |     |          | 1.6.3.1 Systèmes parallèles à mémoire partagée                    |

|   |     |          | 1.6.3.2 Systèmes parallèles à mémoire distribuée                  |

|   |     | 1.6.4    | L'interconnexion des systèmes parallèles                          |

|   |     | 1.6.5    | Application parallèle et MP-RSoC                                  |

|   | 1.7 | Conce    | voir et utiliser les MP-RSoC                                      |

|   | 1.8 | Concl    | asion                                                             |

| 2 | Éta | t de l'a | art 39                                                            |

|   | 2.1 | Introd   | uction                                                            |

|   | 2.2 | VHDI     | et MP-RSoC : le langage et ses limites                            |

|   |     | 2.2.1    | Les objectifs du VHDL                                             |

|   |     | 2.2.2    | La dynamicité en VHDL                                             |

|   | 2.3 | Outils   | de modélisation et niveau d'abstraction du MP-RSoC                |

|   | 2.4 | Outils   | niveau RTL                                                        |

|   |     | 2.4.1    | Dreams, RapidSmith                                                |

|   |     | 2.4.2    | cPCAP 44                                                          |

|   |     | 2.4.3    | RecoBus builder                                                   |

|   |     | 2.4.4    | GoAhead                                                           |

|   |     | 2.4.5    | Plateforme FPX et l'outil PARBIT                                  |

|   | 2.5 | Outils   | de niveau Algorithmique (HLS)                                     |

|   |     | 2.5.1    | LegUP                                                             |

|   |     | 2.5.2    | Synphony HLS                                                      |

|   |     | 2.5.3    | CatapultC                                                         |

|   |     | 2.5.4    | L'outil VIVADO HLS                                                |

|   |     | 2.5.5    | Limites à l'intégration des conceptions HLS dans les MP-RSoC 52   |

|   | 2.6 | Les ou   | tils de niveau PBD                                                |

|   |     | 2.6.1    | Projet FOSFOR (Flexible Operating System For Reconfigurable Plat- |

|   |     |          | form)                                                             |

|   |     | 2.6.2    | Le projet TMD-MPI                                                 |

|   |     | 2.6.3    | La plateforme SoC-MPI                                             |

|   |     | 2.6.4    | le projet BORPH                                                   |

|   |     | 2.6.5    | le projet SPoRE                                                   |

|   | 2.7 | Les ou   | tils de niveau MDE/MDA                                            |

|   |     | 2.7.1    | Koski                                                             |

|   |     | 2.7.2    | Gaspard                                                           |

|   |     | 2.7.3    | FAMOUS                                                            |

|   |     | 2.7.4    | MopCom                                                            |

|   |     | 275      | Les limites des outils MDE/MDA 61                                 |

|   | 2.8 | Concl | usion      |                                                                | 62 |

|---|-----|-------|------------|----------------------------------------------------------------|----|

| 3 | MA  |       |            | me MP-RSoC utilisant MPI-2                                     | 65 |

|   | 3.1 |       |            |                                                                | 66 |

|   | 3.2 |       |            | ion parallèle et le MPI                                        | 67 |

|   |     | 3.2.1 |            | lard MPI et ses différentes mises en œuvre                     | 67 |

|   |     | 3.2.2 |            | t RMA                                                          | 68 |

|   |     | 3.2.3 |            | de MPI2-RMA pour les MP-RSoC                                   | 69 |

|   | 3.3 | Couch | e d'interc | connexion                                                      | 70 |

|   |     | 3.3.1 | Types d    | 'interconnexions                                               | 70 |

|   |     |       | 3.3.1.1    | L'interconnexion à l'aide d'un bus                             | 71 |

|   |     |       | 3.3.1.2    | L'interconnexion à l'aide d'un réseau sur puce                 | 71 |

|   |     |       | 3.3.1.3    | Choix de l'interconnexion pour un MP-RSoC                      | 72 |

|   |     | 3.3.2 | Crossbar   | r pour MP-RSoC                                                 | 73 |

|   |     |       | 3.3.2.1    | La matrice interconnectée élémentaire (Crossbar)               | 73 |

|   |     |       | 3.3.2.2    | Gestionnaire de port d'entrée                                  | 74 |

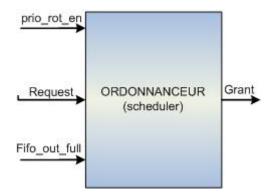

|   |     | 3.3.3 | Ordonna    | anceur                                                         | 76 |

|   |     |       | 3.3.3.1    | Gestionnaire du port de sortie                                 | 80 |

|   |     | 3.3.4 | Résultat   | s de mise en œuvre de la couche d'interconnexion               | 80 |

|   |     | 3.3.5 | Conclusi   | ion                                                            | 81 |

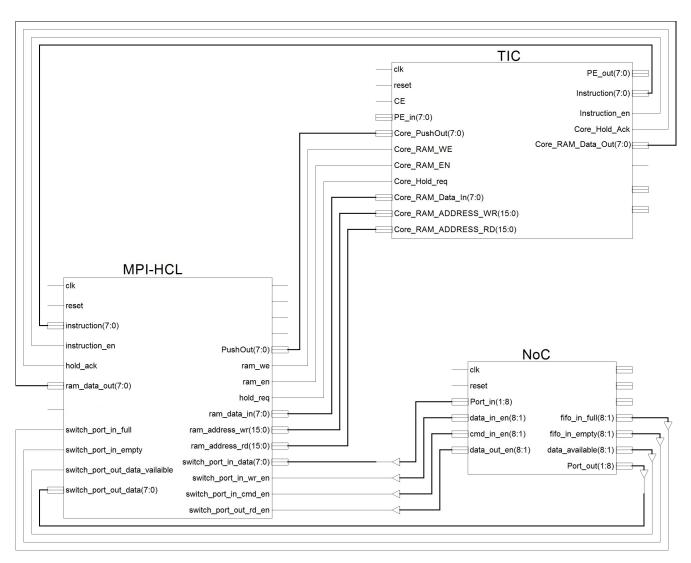

|   | 3.4 | Couch | e de comi  | munication: Le composant MPI-HCL                               | 82 |

|   |     | 3.4.1 | Principe   | e de la couche de communication                                | 83 |

|   |     | 3.4.2 | Rôle des   | s primitives MPI codées en Vhdl                                | 83 |

|   |     | 3.4.3 | Descript   | ion des modules de MPI-HCL                                     | 84 |

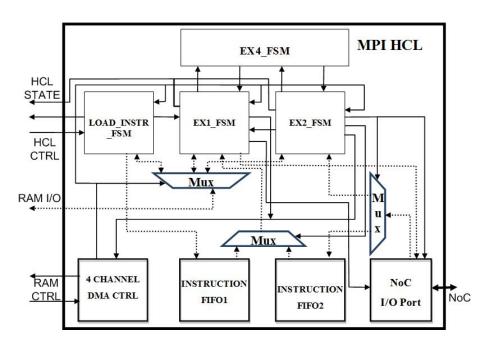

|   |     |       | 3.4.3.1    | Modèle logique du composant de communication MPI-HCL           | 84 |

|   |     |       | 3.4.3.2    | Modèle physique du composant MPI-HCL                           | 86 |

|   |     | 3.4.4 | La mém     | oire de communication                                          | 87 |

|   |     |       | 3.4.4.1    | Zone registre R $\dots$                                        | 88 |

|   |     |       | 3.4.4.2    | La zone de codage et de transfert T                            | 90 |

|   |     | 3.4.5 | Fonction   | nnement du composant MPI-HCL                                   | 90 |

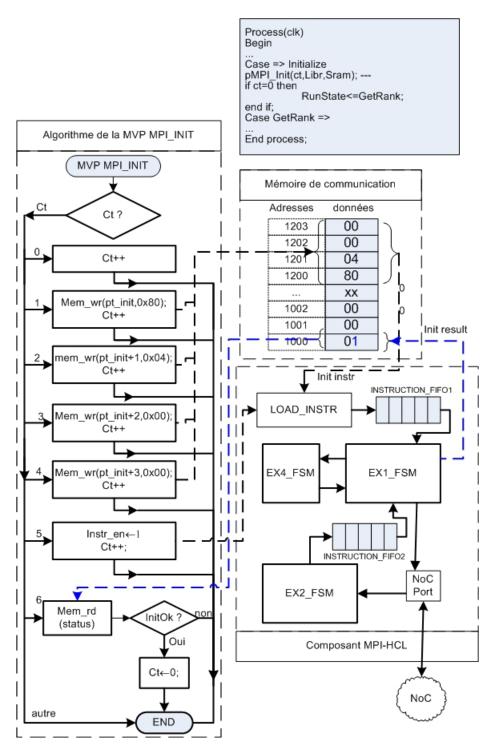

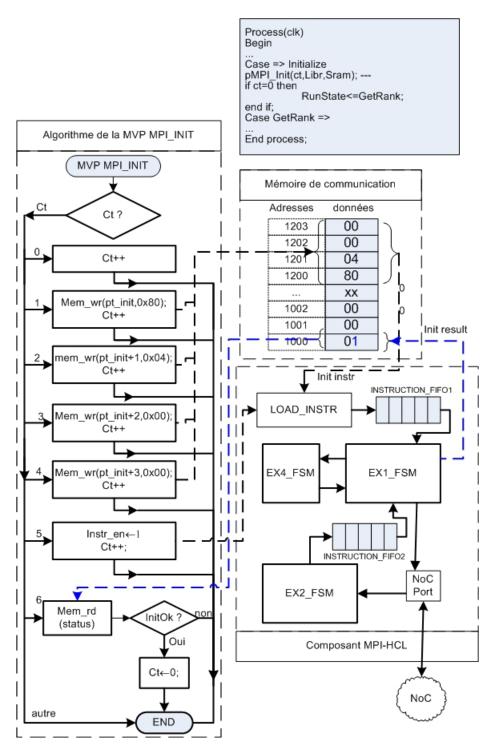

|   |     |       | 3.4.5.1    | L'initialisation des communications avec MPI-HCL               | 90 |

|   |     |       | 3.4.5.2    | Utilisation des modules MVP                                    | 93 |

|   |     |       | 3.4.5.3    | Initialisation des fenêtres mémoire de stockage des données .  | 93 |

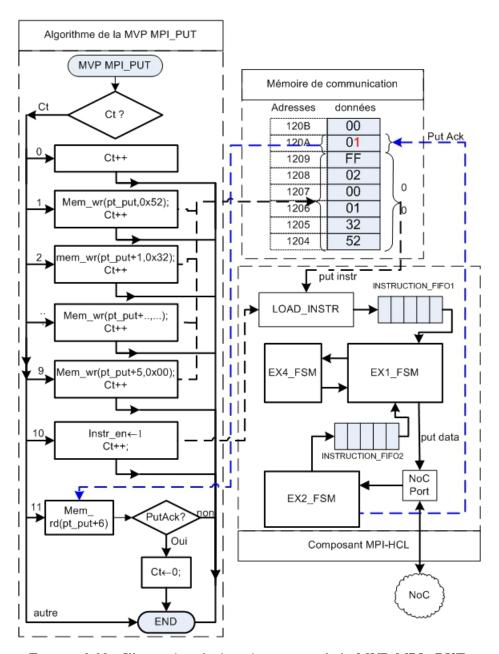

|   |     |       | 3.4.5.4    | Émission-réception des données                                 | 95 |

|   |     | 3.4.6 | La syncl   | hronisation des transferts avec MPI-HCL                        | 96 |

|   |     |       | 3.4.6.1    | Mise en œuvre adoptée pour les primitives de synchronisation   | 96 |

|   |     |       | 3.4.6.2    | Les différents types de messages entre une source et une cible | 97 |

|   |     |       | 3.4.6.3    | Les registres de gestion de la synchronisation                 | 97 |

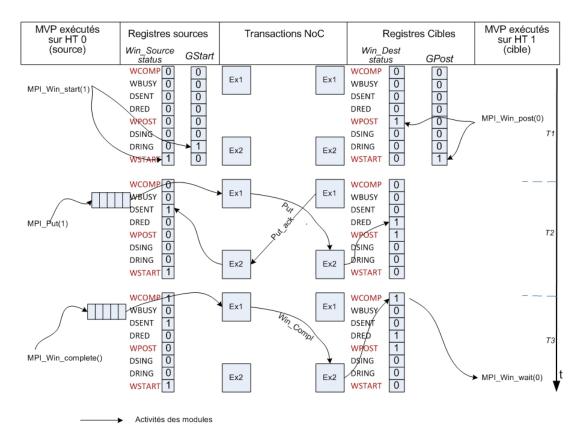

|   |     |       | 3.4.6.4    | Processus de synchronisation de la primitive MPI_Put           | 97 |

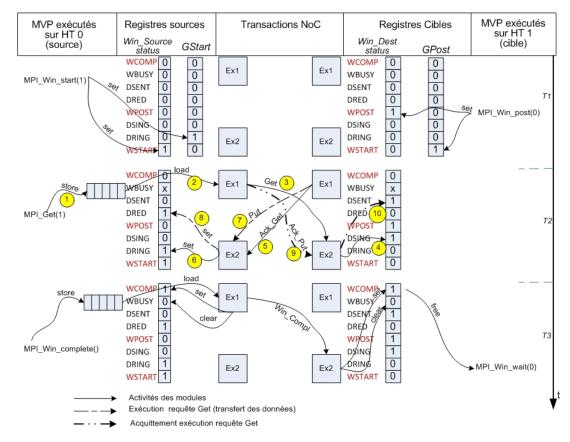

|   |                |        | 3.4.6.5     | Processus de synchronisation de la primitive MPI_Get         | 98  |

|---|----------------|--------|-------------|--------------------------------------------------------------|-----|

|   |                | 3.4.7  | Finalisati  | on des transferts                                            | 101 |

|   |                | 3.4.8  | Mise en o   | œuvre sur un FPGA                                            | 101 |

|   | 3.5            | Couch  | e applicati | on                                                           | 104 |

|   |                | 3.5.1  | Introduct   | ion                                                          | 104 |

|   |                | 3.5.2  | Tâche ma    | atérielle                                                    | 104 |

|   |                | 3.5.3  | Composa     | nt d'intégration de la tâche matérielle : TIC                | 107 |

|   |                | 3.5.4  | L'interfac  | ce entre la tâche matérielle et le TIC                       | 109 |

|   |                | 3.5.5  | L'interfac  | ce de la couche application                                  | 110 |

|   |                | 3.5.6  | L'interfac  | ce logique entre la tâche matérielle et le composant MPI-HCL | 110 |

|   |                | 3.5.7  | Descripti   | on d'une tâche matérielle utilisant des modules MVP          | 112 |

|   | 3.6            | Discus | sion        |                                                              | 113 |

|   | 3.7            | conclu | sion        |                                                              | 115 |

| 4 | $\mathbf{Rec}$ | onfigu | ration dy   | namique avec MATIP                                           | 117 |

|   | 4.1            | Introd | uction      |                                                              | 118 |

|   | 4.2            | Exécu  | tion dynar  | nique des tâches matérielles                                 | 118 |

|   |                | 4.2.1  | La foncti   | on Spawn de MPI                                              | 119 |

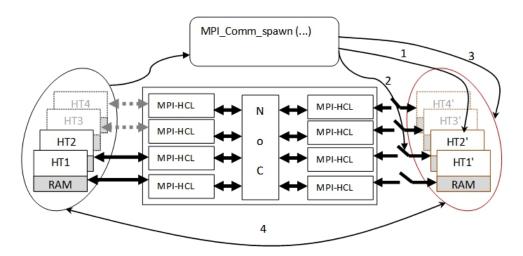

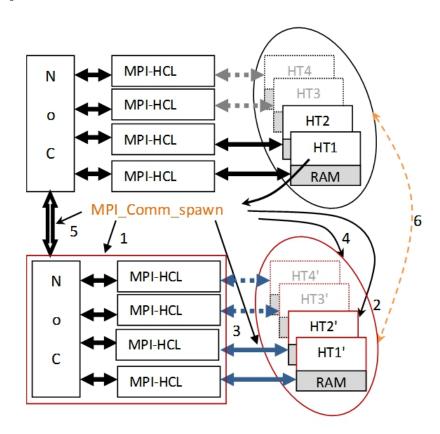

|   |                |        | 4.2.1.1     | Fonctionnement de MPI_Comm_spawn()                           | 120 |

|   |                |        | 4.2.1.2     | Variante de MPI_Comm_Spawn: MPI_Comm_Modify()                | 120 |

|   |                |        | 4.2.1.3     | Achèvement d'une tâche dynamique                             | 120 |

|   |                | 4.2.2  | Options of  | de mise en œuvre matérielle de MPI_Comm_modify()             | 121 |

|   |                |        | 4.2.2.1     | Architecture fixe                                            | 121 |

|   |                |        | 4.2.2.2     | Architecture modifiable                                      | 121 |

|   |                |        | 4.2.2.3     | Architecture incrémentale                                    | 122 |

|   |                | 4.2.3  | Différents  | s scénarii pour l'implémentation de la primitive spawn       | 123 |

|   |                | 4.2.4  | Choix d'u   | un scénario pour la mise en œuvre de MPI_Comm_modify() .     | 125 |

|   |                | 4.2.5  | Étapes d    | 'exécution de la primitive MPI_Comm_modify() sur MATIP       | 126 |

|   |                |        | 4.2.5.1     | étape 1 : appel collectif du spawn                           | 126 |

|   |                |        | 4.2.5.2     | étape 2 : Chargement et activation des nouvelles tâches      | 128 |

|   |                |        | 4.2.5.3     | étape 3 : Initialisation des nouvelles tâches                | 128 |

|   |                |        | 4.2.5.4     | étape 4 : Fin du $Spawn$                                     | 128 |

|   | 4.3            | Mise e | n œuvre d   | le MATIP dans un FPGA Xilinx Artix 7                         | 128 |

|   |                | 4.3.1  | Préparati   | ion du déploiement avec MATIP                                | 129 |

|   |                |        | 4.3.1.1     | Synthèse des partions de l'application                       | 129 |

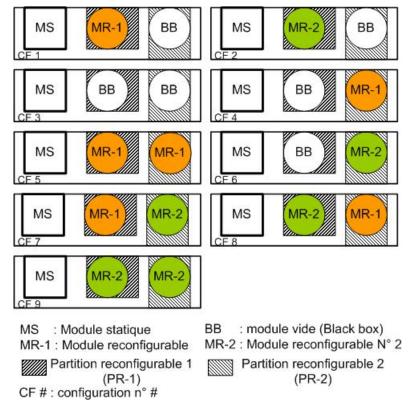

|   |                |        | 4.3.1.2     | Définition des configurations                                | 130 |

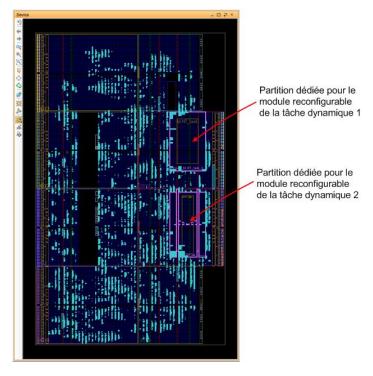

|   |                |        | 4.3.1.3     | Définition des limites de la partition reconfigurable        | 130 |

|   |                |        | 4.3.1.4     | Stockage des données de configuration                        | 133 |

|   |                | 4.3.2  | Exécution   | n du déploiement avec MATIP                                  | 133 |

|              |       |         | 4.3.2.1   | Découplage des modules pendant la reconfiguration partielle | 133 |

|--------------|-------|---------|-----------|-------------------------------------------------------------|-----|

|              |       |         | 4.3.2.2   | Utilisation du port ICAP pour le chargement d'un bitstream  |     |

|              |       |         |           | partiel                                                     | 134 |

|              |       | 4.3.3   | Méthodo   | ologie de déploiement du démonstrateur MATIP                | 134 |

|              | 4.4   | Perfor  | mances d  | e la plateforme MATIP                                       | 135 |

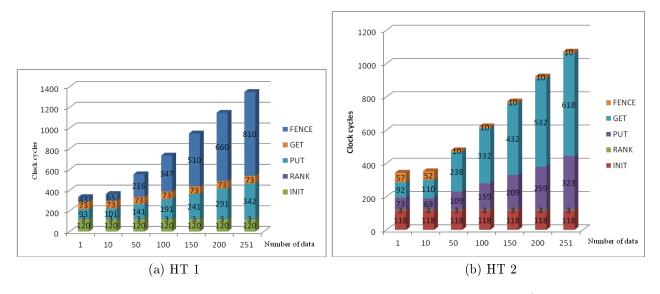

|              |       | 4.4.1   | Perform   | ances et utilisation des MVP                                | 137 |

|              |       | 4.4.2   | La laten  | ce des primitives de communication                          | 139 |

|              |       | 4.4.3   | Utilisati | on de MATIP pour synchroniser des HT                        | 142 |

|              |       | 4.4.4   | Exemple   | e de description des tâches matérielles en Vhdl             | 143 |

|              | 4.5   | Concl   | ısion     |                                                             | 152 |

| Co           | onclu | ısion e | t perspe  | ctives                                                      | 154 |

| $\mathbf{A}$ | Cod   | les sou | rces      |                                                             | 161 |

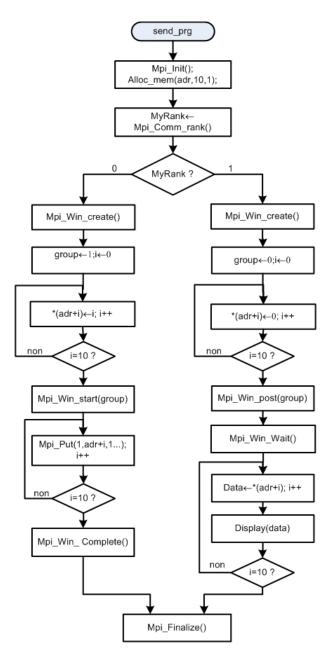

|              | A.1   | Code    | source en | langage C du programme send_prg                             | 161 |

|              | A.2   | Const   | antes pou | r la zone de transfert des instructions                     | 163 |

|              | A.3   | Code    | source du | programme send_prg Vhdl                                     | 164 |

|              | A.4   | Descri  | ption d'u | ne tâche matérielle dynamique                               | 168 |

## Liste des tableaux

| 1.1  | Evolution des besoins des SoC dans les terminaux mobiles                                   | 25  |

|------|--------------------------------------------------------------------------------------------|-----|

| 1.2  | Plateformes pour architectures reconfigurables trouvées dans la littérature                | 31  |

| 3.1  | Ressources utilisées par les versions 4 à 16 ports du composant d'intercon-                |     |

|      | nexion sur un FPGA Artix-7 xc7a100t                                                        | 81  |

| 3.2  | Format des instructions de MPI-HCL                                                         | 84  |

| 3.3  | registres du composant MPI-HCL                                                             | 89  |

| 3.4  | liste des instructions traitées par MPI-HCL et leur code d'instruction $\ \ldots \ \ldots$ | 91  |

| 3.5  | Ressources consommées par une HT dans le FPGA xc6lx45                                      | 102 |

| 3.6  | Ressources consommées par MATIP 1.0 avec deux HT dans le FPGA xc6lx45                      | 102 |

| 3.7  | Latence (en cycle d'horloge) des primitives MPI-HCL                                        | 102 |

| 3.8  | Comparaison des latences de plateformes MPI                                                | 104 |

| 3.9  | Liste des fichiers du template de la plateforme MATIP (MPI Application Task                |     |

|      | Integration Platform)                                                                      | 108 |

| 3.10 | Signaux de gestion de l'arbitre RAM                                                        | 109 |

| 4.1  | Synthèse des options de mise en œuvre des tâches dynamiques dans le MP-RSoC                | 122 |

| 4.2  | Synthèse des actions pour chaque scénario                                                  | 126 |

| 4.3  | Consommation des ressources après synthèse de la plateforme sur un Xilinx                  |     |

|      | Spartan 6 xc6lx45                                                                          | 136 |

| 4.4  | Utilisation des ressources par module du démonstrateur                                     | 137 |

| 4.5  | Ressources utilisées par les démonstrateurs FOSFOR et MATIP                                | 138 |

| 4.6  | Comparaison entre FOSFOR et MATIP                                                          | 142 |

## Table des figures

| 1.1  | Compromis entre performance et flexibilité des architectures reconfigurables | 29 |

|------|------------------------------------------------------------------------------|----|

| 1.2  | Système hétérogème et système homogène [24]                                  | 33 |

| 1.3  | Architecture de base d'un système reconfigurable dynamiquement               | 33 |

| 1.4  | Taxonomie de Flynn                                                           | 35 |

| 1.5  | Système à mémoire partagée et système à mémoire distribuée [24]              | 36 |

| 1.6  | interconnexion des systèmes parallèles                                       | 37 |

| 1.7  | Méthodes de raffinement de la conception                                     | 38 |

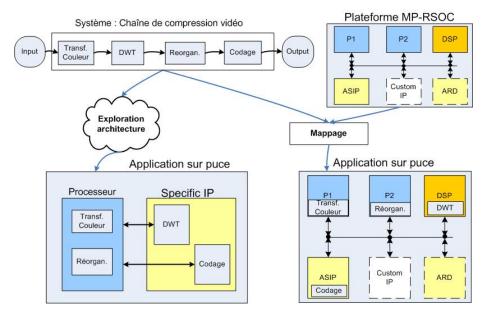

| 1.8  | Exemple de déploiement d'une application de décompression vidéo sur un       |    |

|      | MP-RSoC                                                                      | 38 |

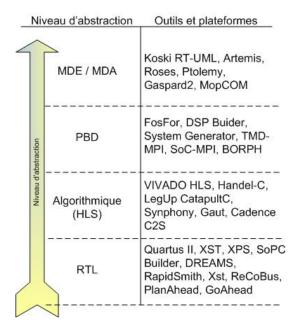

| 2.1  | Outils de conception des MP-RSoC selon leur niveau d'abstraction             | 44 |

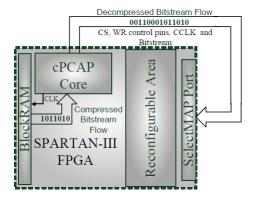

| 2.2  | Architecture de la plateforme cPCAP[43]                                      | 45 |

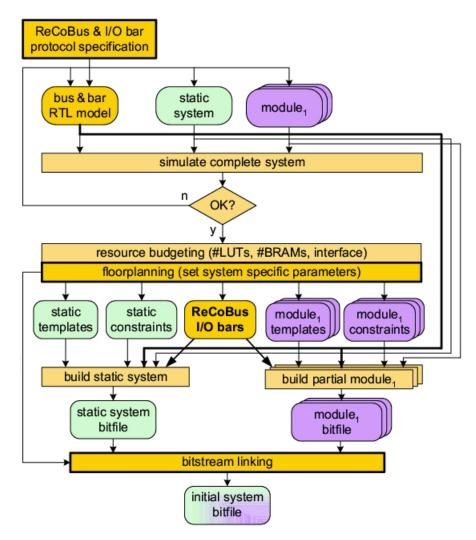

| 2.3  | Flot de conception à l'aide de l'outil RecoBus Builder [45]                  | 47 |

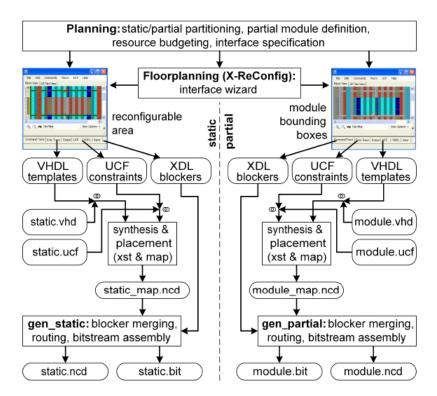

| 2.4  | Flot de déploiement d'une application ayant un module reconfigurable avec    |    |

|      | GoAhead sur FPGA Xilinx Spartan 6 [46]                                       | 48 |

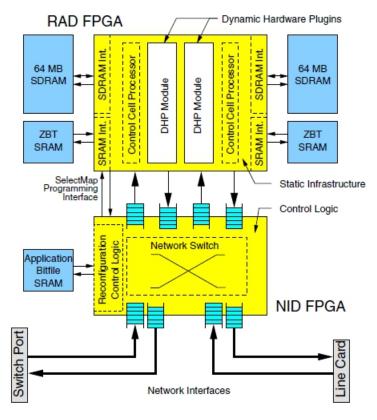

| 2.5  | La plateforme FPX [47]                                                       | 49 |

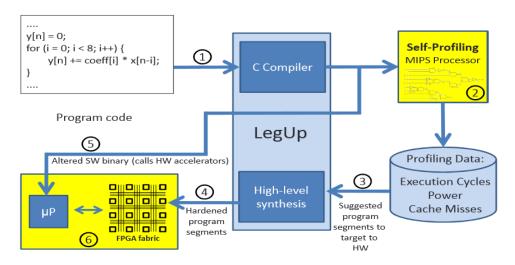

| 2.6  | Flot standard de conception LegUp [49]                                       | 50 |

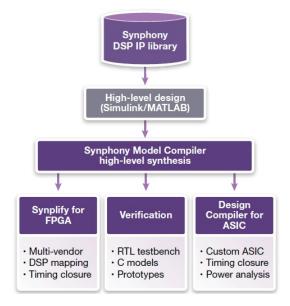

| 2.7  | Flot de conception avec Synphony Model Compiler [51]                         | 51 |

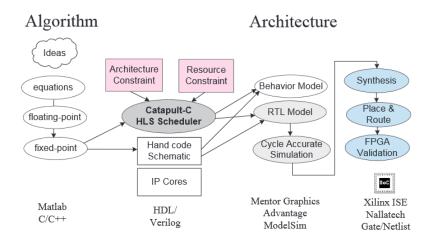

| 2.8  | Flot de conception HLS avec CatapultC [52]                                   | 51 |

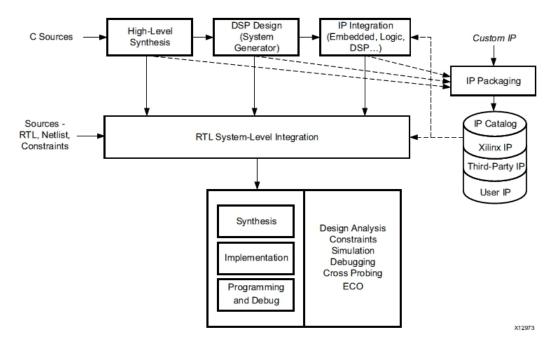

| 2.9  | Flot standard de conception avec VIVADO HLS [53]                             | 53 |

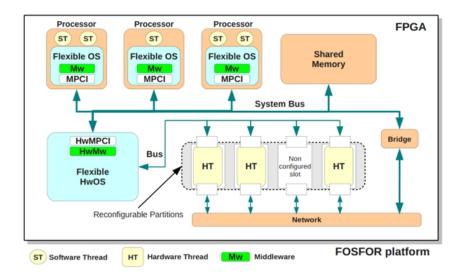

| 2.10 | plateforme MP-RSoC du projet FOSFOR [58]                                     | 54 |

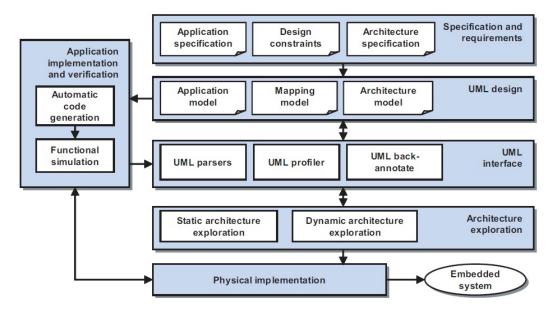

| 2.11 | Méthodologie de conception avec les outils Koski [70]                        | 58 |

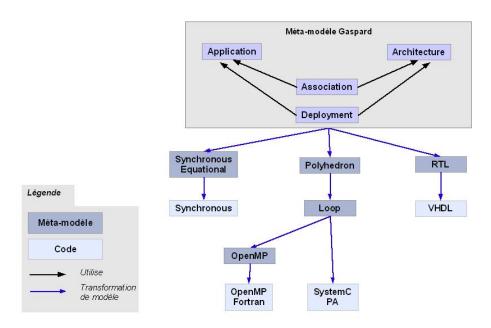

| 2.12 | Méthodologie de conception avec Gaspard [71]                                 | 59 |

| 2.13 | Modèle d'exécution d'une application construite à l'aide de FAMOUS $[73]$    | 59 |

| 2.14 | Flot de conception FAMOUS [74]                                               | 60 |

| 2.15 | Méthodologie de conception avec MopCom [75]                                  | 61 |

| 3.1  | Modèle en couches de MATIP                                                   | 67 |

| 3.2  | Rapport entre connexions et contention dans un réseau (d'après [83])         | 70 |

| 3.3  | Principe d'un réseau sur puce                                                | 72 |

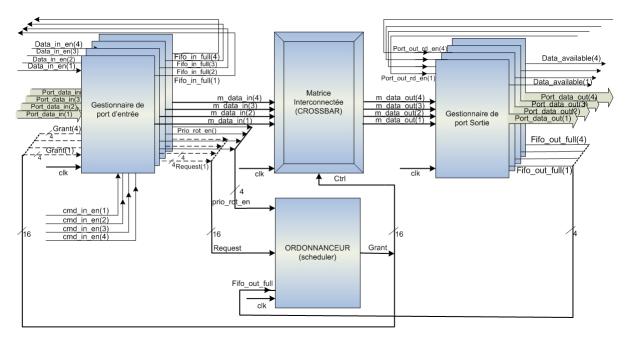

| 3.4  | Schéma de principe du réseau d'interconnexion                                | 73 |

| 3.5  | Matrice interconnectée $(Crossbar)$                                                           |

|------|-----------------------------------------------------------------------------------------------|

| 3.6  | Architecture du réseau d'interconnexion à base du crossbar 4x4                                |

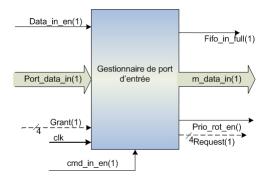

| 3.7  | Gestionnaire de port d'entrée n° 1 pour le réseau                                             |

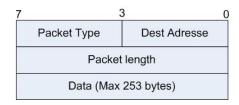

| 3.8  | Trame des paquets circulant sur le réseau                                                     |

| 3.9  | Arbitre composé de cellules à propagation de retenue pour crossbar 4x4                        |

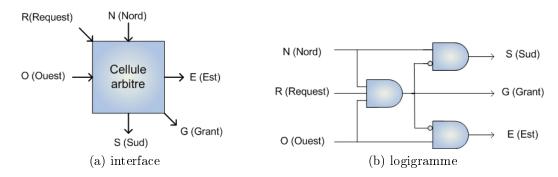

| 3.10 | Cellule arbitre : (a) interface et en (b) un exemple de mise en œvre en logique               |

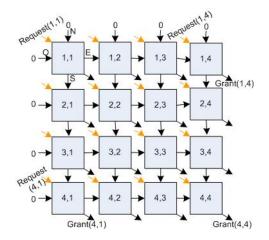

|      | combinatoire [88]                                                                             |

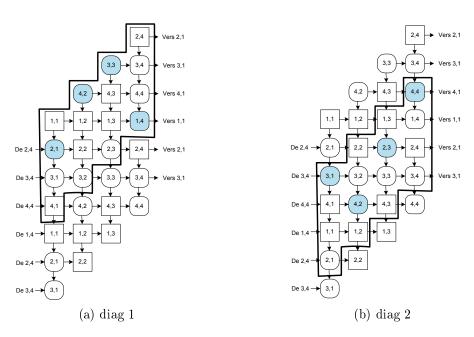

| 3.11 | Architecture DPA de l'ordonnanceur                                                            |

| 3.12 | Cellule arbitre DPA pour le réseau d'interconnexion                                           |

| 3.13 | L'ordonnanceur                                                                                |

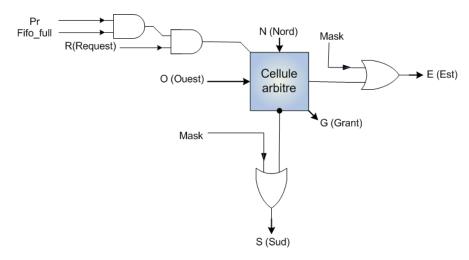

| 3.14 | Gestionnaire du port de sortie n°1                                                            |

| 3.15 | Performance de la couche d'interconnexion en fonction du nombre de ports 82                   |

| 3.16 | Couche de communication                                                                       |

| 3.17 | Modèle logique du processeur MPI-HCL                                                          |

| 3.18 | Architecture interne du composant MPI-HCL                                                     |

| 3.19 | Organisation de la mémoire de communication du composant MPI-HCL 88                           |

| 3.20 | Illustration du fonctionnement de la MVP MPI_INIT                                             |

| 3.21 | Illustration du fonctionnement de la MVP MPI_INIT                                             |

| 3.22 | Illustration du fonctionnement de la MVP MPI_PUT                                              |

| 3.23 | Synchronisation lors du processus d'envoi d'un message (put_prg) 99                           |

| 3.24 | Synchronisation lors du processus de réception d'un message ( $\operatorname{Get\_prg}$ ) 103 |

| 3.25 | résultats des performances en cycles d'horloge de MATIP                                       |

| 3.26 | Modèle en couches de la plateforme MPI-HCL                                                    |

| 3.27 | Tâche matérielle intégrée dans le TIC                                                         |

| 3.28 | Principe d'utilisation des tâches matérielles                                                 |

| 3.29 | Architecture de la plateforme MATIP                                                           |

| 3.30 | Structure du TIC qui encapsule la tâche utilisateur                                           |

| 3.31 | Interface TIC encapsulant la tâche matérielle (HT) 110                                        |

| 3.32 | Interface entre les trois composants constituant les trois couches de MATIP . $117$           |

| 3.33 | Algorithme permettant l'envoi de données entre deux tâches parallèles d'un                    |

|      | même programme                                                                                |

| 4.1  | Création dynamique de processus à l'aide de la fonction MPI_Comm_spawn() . 119                |

| 4.2  | Spawn par activation de tâches existantes                                                     |

| 4.3  | Spawn par replication dynamique de toute l'architecture                                       |

| 4.4  | Spawn par ajout dynamique de nouvelles tâches à une architecture existante $125$              |

| 4.5  | Exécution du $spawn$ : requête, chargement et activation de nouvelles tâches. $127$           |

| 4.6  | Exécution du spawn: Initialisation, acquittement et fin de la primitive 127                   |

| 4.7  | Préparation du déploiement de l'application parallèle avec MATIP sur FPGA    |      |

|------|------------------------------------------------------------------------------|------|

|      | Xilinx Artix-7                                                               | 129  |

| 4.8  | Différentes configurations à partir d'un module statique et deux modules re- |      |

|      | configurables                                                                | 131  |

| 4.9  | Exemple de fichier Bitstream partiel généré par PlanAhead pour le FPGA       |      |

|      | ARTIX-7. le mot de synchronisation indique le début des données de reconfi-  |      |

|      | guration                                                                     | 131  |

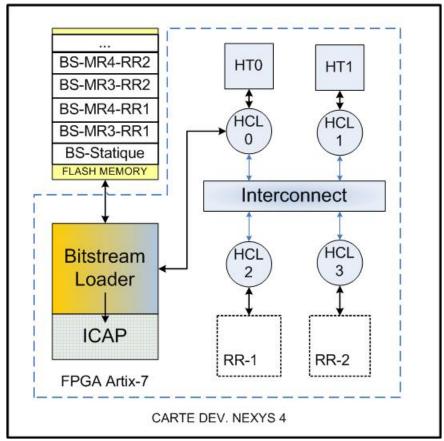

| 4.10 | Mise en œuvre du démonstrateur MATIP sur carte Digilent Nexys 4              | 132  |

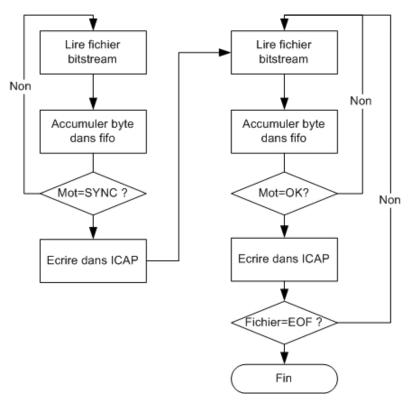

| 4.11 | Algorithme de la primitive de reconfiguration du FPGA à travers ICAP         | 133  |

| 4.12 | Implantation de la partition statique de MATIP dans un FPGA Artix-7. $$ . $$ | 135  |

| 4.13 | Démonstrateur MATIP avec 4 tâches dont deux sont chargées dynamiquement.     | .139 |

| 4.14 | Performance des MVP des tâches matérielles statiques                         | 140  |

| 4.15 | Performance des MVP des tâches matérielles dynamiques                        | 141  |

| 4.16 | Chronogramme des communications dans l'application de démonstration $\ \ .$  | 144  |

| 4.17 | NoC hierarchique                                                             | 157  |

| 1 18 | Architecture Cloud SoC                                                       | 158  |

## Liste des abréviations

AES . . . . . Advanced Encryption Standard

ALU . . . . . Arithmetic Logic Unit

AMS . . . . . Analog/Mixed-Signal

**API** . . . . . Application Programming Interface

ASIC . . . . . Application-Specific Integrated Circuit

ASIP . . . . . Application-Specific Instruction-set Processor

CPU . . . . . Central Processing Unit

CRC . . . . . Cyclic Redundancy Check

**DMA** . . . . . Direct Memory Access

**DRAM** . . . . Dynamic Random Access Memory

**DSP** . . . . . Digital Signal Processor

**EFSM** . . . . Extended Finite-State Machine

FAMOUS . . Flot de modélisation et de conception rapide pour les systèmes dynami-

quement reconfigurable

**FIFO** . . . . . First-In-First-Out

FPGA . . . . Field Programmable Gate Array

FSM . . . . . Finite-State Machine

GUI . . . . . Graphical User Interface

**HAL** . . . . . Hardware Abstraction Layer

**HDL** . . . . . Hardware Description Language

**HIBI** . . . . . Heterogeneous IP Block Interconnection

**HW** . . . . . . Hardware

IC . . . . . . Integrated Circuit

**IP** . . . . . . Intellectual Property

**IPC** . . . . . Inter-Processor Communication

ITRS . . . . . International Technology Roadmap for Semiconductors

**KPN** . . . . . Kahn Process Network

LAN . . . . . Local Area Network

MAC . . . . . Medium Access Control

MARTE . . . Modeling and Analysis of Real-Time and Embedded Systems

MDA . . . . . Model Driven Architecture

MDE . . . . . Model Driven Engineering

MoC . . . . . Model of Computation

MOPS . . . . Mega operations per second

MPSoC . . . MultiProcessor System-on-Chip

MP-RSoC . . Multi Processing Reconfigurable System-on-Chip

**NoC** . . . . Network-on-Chip

**OCP** . . . . . Open Core Protocol

**OMG** . . . . Object Management Group

**OS** . . . . . Operating System

**PC** . . . . . . Personal Computer

**PBD** . . . . . Platform Based Design

PE . . . . . . Processing Element

PN . . . . . . Process Network

QoS . . . . . . Quality of Service

RAM . . . . . Random Access Memory

RISC . . . . . Reduced Instruction-Set Computer

**ROM** . . . . . Read-Only Memory

RTL . . . . . Register Transfer Level

RTOS . . . . Real-Time Operating System

**RSM** . . . . . Repetitive Structure Modeling

SA . . . . . . Simulated Annealing

**SDF** . . . . . Synchronous Data Flow

SDL . . . . . Specification and Description Language

SoC . . . . . System-on-Chip

SRAM . . . . Static Random Access Memory

$\mathbf{SW}$  . . . . . Software

TDMA . . . . Time Division Multiple Access

TLM . . . . . Transaction Level Modeling

TUT . . . . . Tampere University of Technology

UAL . . . . Unité Arithmétique et Logique

UML . . . . . Unified Modeling Language

VCC . . . . . Virtual Component Codesign

TABLE DES FIGURES 19

$\mathbf{VHDL}$  . . . . VHSIC Hardware Description Language

$\mathbf{VHSIC}$  . . . . Very High Speed Integrated Circuit

$\mathbf{VLSI}$  . . . . . Very Large Scale Integration

**WLAN** . . . . Wireless Local Area Network

## Introduction générale

Les avancées de la technologie des semi-conducteurs favorisent la réalisation des systèmes sur puces (SoC) de plus en plus performants. Ces SoC (System on Chip), sont sans cesse améliorés pour augmenter la puissance de traitement, réduire la consommation d'énergie et intégrer plus de fonctionnalités dans des applications. L'augmentation des fonctionnalités est une conséquence de la loi de Moore qui prévoit d'intégrer 24 milliards de transistors à l'horizon 2024 sur une puce d'un cm² [1]. Pour réaliser le microprocesseur Pentium 4 Willamete, Intel a utilisé 42 millions de transistors, par conséquent il sera possible d'intégrer 500 Pentium IV sur une seule puce en 2024. Certaines unités de calcul telle que l'ARM7 occupent moins de 500 mille transistors ainsi, il serait possible d'intégrer plus de 40 mille ARM7 dans une puce en 2024. Les avancées technologiques et la grande densité d'intégration des transistors impactent la conception des systèmes sur puce en autorisant de nouvelles architectures, l'hétérogénéité et la dynamicité des unités de traitement. L'hétérogénéité peut être réalisée en mêlant des unités de traitement numériques et des unités de traitement analogiques sur une même puce; mais elle peut aussi être le fruit du mélange de différentes unités de traitements numériques, chacune adaptée à un traitement spécifique de l'application.

Les progrès des technologies de reconfiguration dynamique des circuits logiques permettent au concepteur de systèmes sur puce de disposer de matériels flexibles ayant d'importantes zones reconfigurables. A titre d'exemple, le FPGA Xilinx Virtex 7 XV-2000T possède 6,8 milliards de transistors dont plus de la moitié appartient aux régions reconfigurables du circuit[2]. Une zone reconfigurable dans un FPGA regroupe un ensemble de ressources logiques qui peuvent être configurées à tout moment pour exécuter une tâche; ainsi, les zones reconfigurables peuvent être assimilées à des unités de traitement au même titre que les processeurs. La fabrication des puces mixtes mélangeant des processeurs et des unités d'exécution matérielles dynamiquement reconfigurables permet la réalisation des systèmes de multi-traitement sur puce dynamiquement reconfigurables que nous désignons sous l'accronyme MP-RSoC(Multi Processing Reconfigurable System On Chip). Le développement d'applications parallèles pour ces MP-RSoC ne peut être efficace que si leur sont associés des outils facilitant le déploiement et la gestion de ces applications à l'instar des outils utilisés dans les HPC (High Performance Computer) pour créer et exploiter des applications parallèles.

22 TABLE DES FIGURES

Tandis que les outils pour HPC automatisent toutes les phases allant de la compilation d'une application parallèle à son exécution, les outils disponibles pour MP-RSoC n'offrent qu'un support limité du déploiement automatique de l'application parallèle. La conséquence est que le temps passé à mettre au point une application parallèle pour MP-RSoC est très long et les opérations à effectuer pour la déployer sont fastidieuses. Nous nous intéressons dans cette thèse à la réalisation et au déploiement d'application parallèles pour MP-RSoC.

Dans le prochain chapitre, nous revenons sur l'intérêt des MP-RSoC et sur les difficultés rencontrées lors de leur utilisation. Le deuxième chapitre est un état de l'art des outils et plateformes permettant d'utiliser les MP-RSoC. Au troisième chapitre, nous présentons MA-TIP, la plateforme de déploiement d'applications parallèles pour MP-RSoC que nous avons conçue et nous détaillons la conception de chacune de ses couches. Au chapitre quatre nous étendons la plateforme MATIP en introduisant le support de la reconfiguration dynamique et validons sa mise en œuvre sur un FPGA Xilinx Artix-7. Enfin nous concluons ce travail et annonçons les perspectives.

## Chapitre 1

## Problématique

## Sommaire

| 1.1 | Intr           | oduction                                                  | 24        |

|-----|----------------|-----------------------------------------------------------|-----------|

| 1.2 | $\mathbf{Les}$ | principales contraintes des systèmes sur puce             | <b>25</b> |

|     | 1.2.1          | Augmenter la puissance de traitement                      | 25        |

|     | 1.2.2          | La flexibilité du développement                           | 26        |

|     | 1.2.3          | Économiser les ressources matérielles et l'énergie        | 26        |

|     | 1.2.4          | Accomplir simultanément plusieurs tâches sur puce         | 26        |

|     | 1.2.5          | Un processeur sur mesure pour chaque tâche                | 27        |

|     | 1.2.6          | La convergence                                            | 27        |

|     | 1.2.7          | Le passage à l'échelle                                    | 27        |

| 1.3 | Pou            | rquoi un MP-RSoC                                          | <b>27</b> |

|     | 1.3.1          | Le Coût de fabrication des puces                          | 28        |

|     | 1.3.2          | La dynamicité                                             | 28        |

|     | 1.3.3          | La disponibilité                                          | 28        |

| 1.4 | $\mathbf{Les}$ | types d'ARD et les outils des MP-RSoC                     | 29        |

|     | 1.4.1          | ARD pour MP-RSoC                                          | 29        |

|     | 1.4.2          | Outils de programmation et de configuration du MP-RSoC $$ | 30        |

| 1.5 | $\mathbf{Les}$ | options et les possibilités de mise en œuvre des MP-RSoC  | 32        |

|     | 1.5.1          | Le partitionnement du MP-RSoC                             | 32        |

|     | 1.5.2          | Les modules du MP-RSoC                                    | 32        |

|     | 1.5.3          | Partition statique et partition dynamique du MP-RSoC      | 33        |

| 1.6 | Le N           | MP-RSoC : un système parallèle                            | 34        |

|     | 1.6.1          | Tâches matérielles et tâches logicielles                  | 34        |

|     | 1.6.2          | Les architectures de traitements parallèles               | 34        |

|     | 1.6.3          | Modèles mémoire de l'application parallèle                | 35        |

|     |                | 1.6.3.1 Systèmes parallèles à mémoire partagée            | 35        |

|     |       | 1.6.3.2 Systèmes parallèles à mémoire distribuée | 35 |

|-----|-------|--------------------------------------------------|----|

|     | 1.6.4 | L'interconnexion des systèmes parallèles         | 36 |

|     | 1.6.5 | Application parallèle et MP-RSoC                 | 37 |

| 1.7 | Con   | cevoir et utiliser les MP-RSoC                   | 7  |

| 1.8 | Con   | clusion                                          | 8  |

#### 1.1 Introduction

Les besoins en puissance de traitement ne cessent d'augmenter dans un contexte fortement contraint entre autre par la limitation de l'énergie consommable, la majorité des applications pour SoC étant destinée à des équipements autonomes embarqués. Le tableau 1.1 montre par exemple que les besoins des terminaux mobiles en terme de puissance de calcul mesurée en MOPS <sup>1</sup>, croissent de façon exponentielle [3], alors que l'énergie disponible progresse linéairement.

Ce besoin en performances a conduit à la parallélisation des traitements, multipliant ainsi le budget en énergie et en surface des puces. Une piste pour arriver à obtenir les performances induites par l'application tout en satisfaisant les autres contraintes des systèmes embarqués est de tirer partie du caractère dynamique des applications. Plus précisément, il s'agit pour nous d'utiliser la possibilité offerte par la reconfiguration dynamique des circuits électroniques afin d'adapter le système sur puce aux besoins calculatoires tout en limitant le budget en énergie [4] ou le budget en surface [5].

Les circuits électroniques dynamiquement reconfigurables sont les lieux de mise en œuvre de systèmes parallèles sur puce reconfigurables que nous avons nommés MP-RSoC pour Multi Processing - Reconfigurable System on Chip. Ces systèmes sur puce sont la plateforme d'exécution des applications parallèles. En analysant les besoins et les contraintes liés à la conception des SoC, nous avons identifié un ensemble de caractéristiques que le concepteur doit prendre en compte pour réaliser un MP-RSoC.

La prochaine section, rappelle les principales contraintes des systèmes embarqués; la section 3 montre la réponse du modèle MP-RSoC à la problématique des systèmes embarqués; la section 4 présente les outils et les types d'architectures reconfigurables dynamiquement pour MP-RSoC; la section 5 rappelle les partitionnements du MP-RSoC; la section 6 décrit les modèles parallèles pour MP-RSoC; la section 7 interroge sur l'utilisation des MP-RSoC et la section 8 est une conclusion.

<sup>1.</sup> million d'opérations par seconde

| Année                  | 1995 | 2000              | 2005 | 2010     | 2015      |  |

|------------------------|------|-------------------|------|----------|-----------|--|

| Génération             | 2G   | 2,5-3G 3,5G pre-4 |      | pre-4G   | 4G        |  |

| Standard               | GSM  | GPRS-UMTS         | HSPA | HSPA-LTE | LTE/LTE-A |  |

| Débit Mb/s             | 0,01 | 0,1               | 1    | 10       | 100       |  |

| Capa batteries (Wh)    | 1    | 2                 | 3    | 4        | 5         |  |

| Charge de calcul (GOPS | 0,1  | 1                 | 10   | 100      | 1000      |  |

| #Coeurs programmables  | 1    | 2                 | 4    | 8        | 16        |  |

Tableau 1.1: Evolution des besoins des SoC dans les terminaux mobiles [3]

### 1.2 Les principales contraintes des systèmes sur puce

Le système sur puce (SoC) désigne une plateforme de traitement qui est confinée dans une puce et intégrée dans un équipement pour gérer une partie ou la totalité des traitements automatisés. Il peut contenir des composants numériques, analogiques, mixtes, et souvent les composants de radio-fréquence. Une utilisation typique des SoC relève du domaine des systèmes embarqués. Les systèmes sur puce doivent être capables de satisfaire un certain nombre de contraintes qui sont définies par les besoins de l'application et par leur environnement d'utilisation.

#### 1.2.1 Augmenter la puissance de traitement

Les nouvelles applications telles que la réalité augmentée, la biométrie dans les systèmes de sécurité, demandent de disposer d'équipements capables de traitements complexes comme l'incrustation en temps réel d'un objet dans une séquence vidéo ou l'identification automatique par la reconnaissance faciale. Ces applications sont généralement embarquées sur des équipements miniatures comme les *Google glass* [6] et exigent de disposer d'une puissance de calcul de plusieurs centaines de GOPS pour exécuter convenablement les applications.

Dans plusieurs domaines les traitements gagnent en complexité; le temps est loin où il suffisait d'avoir un capteur de température et des valeurs de consigne dont le franchissement déclenchait une action. Aujourd'hui, les systèmes qui contrôlent la température d'un procédé peuvent en plus, calculer le gradient pour déclencher encore plus d'actions.

Pour améliorer le trafic des informations et la qualité de service sur un réseau, certains routeurs sont capables de compresser plusieurs paquets d'informations ou de donner la priorité à quelques paquets après un sondage du trafic. Dans le domaine médical, les professionnels ont besoin d'appareils d'imagerie avec une meilleure résolution, capable de compresser, de stocker et de transmettre des images sans perte de qualité. Ces besoins impliquent de doter ces appareils de plus de puissance de traitement pour la mise en œuvre d'algorithmes complexes [7] réalisant ces objectifs.

Le tableau 1.1 montre que la dernière génération (4G) de protocole de communication

sans fil requiert 1000 GOPS tandis que la 1G n'en demandait que 0,1 GOPS. Ces applications illustrent le besoin d'une plus grande puissance de calcul dans les systèmes sur puce.

#### 1.2.2 La flexibilité du développement

Le temps de mise sur le marché d'une nouvelle application des systèmes sur puce doit être le plus court possible, afin de profiter pleinement des nouvelles idées et de nouveaux concepts. Ceci exige la disponibilité d'outils permettant d'assister les concepteurs dans toutes les phases de développement des nouveaux produits.

#### 1.2.3 Économiser les ressources matérielles et l'énergie

Plusieurs facteurs militent en faveur d'une réduction de l'énergie consommée par les SoC. Les industriels souhaitent rallonger la durée de fonctionnement des systèmes alimentés par batterie pour accroître l'autonomie et donner plus de confort aux utilisateurs. Une puce qui contient un grand nombre de transistors en activité consomme de l'énergie et dissipe de la chaleur proportionnellement au nombre de transistors. Il existe alors un risque de surchauffe et de destruction. Contrôler intelligemment le nombre de transistors actifs dans le SoC est un moyen pour réduire ce problème.

La possibilité de reconfigurer dynamiquement une unité de traitement permet de réutiliser les mêmes ressources logiques pour exécuter différentes fonctionnalités, entraînant du même coup une économie d'énergie et une économie des ressources logiques. A plus grande échelle, toute économie d'énergie et de ressources contribue à la réduction de la pollution de l'environnement sur notre planète.

### 1.2.4 Accomplir simultanément plusieurs tâches sur puce

Pour obtenir une grande puissance de calcul, la parallélisation des traitements est une option naturelle, elle permet en plus de réduire la fréquence du circuit en augmentant la capacité de traitement. La parallélisation des traitements peut permettre d'exécuter plusieurs applications sur le même équipement avec de bonnes performances pour chacune d'elles. Les utilisateurs de smartphones, par exemple, peuvent simultanément : recevoir leurs communications, naviguer sur Internet, écouter la musique, suivre leur itinéraire à l'aide du GPS. Pour arriver à intégrer autant de fonctionnalités sur un SoC, les concepteurs ont besoin de nouveaux modèles pour concevoir leurs applications et de nouveaux outils pour les réaliser. En pratique ceci implique de repenser totalement leurs applications pour tirer profit du parallélisme des unités d'exécution.

#### 1.2.5 Un processeur sur mesure pour chaque tâche

Les différentes fonctionnalités d'une ou de plusieurs applications sollicitent des traitements très différents les uns des autres. Il est souhaitable que les unités d'exécution intégrées dans le SoC s'adaptent le plus efficacement à chaque type de traitement. Les SoC ainsi créés sont hétérogènes, favorisant la faible consommation d'énergie par l'utilisation d'unités d'exécution adaptées telles que des DSP, des VLIW, des ASIP <sup>2</sup> [8] ou des circuits reconfigurables. Cette contrainte demande que le SoC soit flexible, pour accepter des processeurs et des IP provenant de différentes sources, et puisse les mettre en œuvre à la demande.

#### 1.2.6 La convergence

La convergence dénote le fait d'intégrer tout un ensemble d'applications dans un seul et même équipement comme le smartphone, nécessitant la prise en compte de modèles de calculs différents. En effet, ces applications ont des contraintes différentes et requièrent de très fortes capacités de calculs. Ces constats amènent à la définition d'architectures parallèles hétérogènes intégrant différents opérateurs plus ou moins flexibles, mais performants pour un domaine d'application.

#### 1.2.7 Le passage à l'échelle

Les nouveaux systèmes doivent supporter le passage à l'échelle. Ceci afin de rentabiliser à long terme les développements en supportant des applications non définies lors de la conception du système. Une solution, est alors de concevoir des systèmes sur puce reconfigurables permettant l'adaptation de l'architecture.

## 1.3 Pourquoi un MP-RSoC

Nous définissons le terme MP-RSoC par rapport au terme MPSoC qui désigne dans la littérature un système sur puce ayant plusieurs unités d'exécution (multicoeurs).

MP-RSoC: variante de MPSoC comprenant une application parallèle déployée sur une puce contenant une architecture dynamiquement reconfigurable (ARD). Contrairement au MPSoC, les modules fonctionnels et les chemins de données du MP-RSoC peuvent être modifiés, ajoutés ou supprimés pendant leur fonctionnement. Le MP-RSoC facilite la mise à jour et l'évolution des systèmes sur puce.

Comme exemple de MP-RSoC, on peut citer le Zynq de Xilinx [9] qui est une puce contenant un processeur Cortex A9 dual core et une zone ARD, où il est possible d'exécuter des modules fonctionnels réalisés par programmation à l'aide du processeur tout en utilisant les ressources logiques reconfigurables pour définir des unités d'exécution sur mesure adaptées

<sup>2.</sup> Application-Specific Instruction set Processors

aux besoins de l'application. Un MP-RSoC permet la convergence et le passage à l'échelle du fait de la flexibilité de l'architecture.

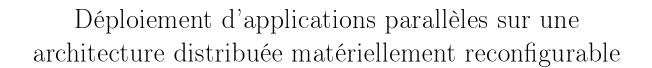

#### 1.3.1 Le Coût de fabrication des puces

La diminution de la taille des transistors va de paire avec l'augmentation des coûts de fabrication des puces. Ainsi, alors que les équipements pour la fabrication des masques en technologie 65 nm reviennent à 1,5 million de dollars US, il en coûte le double pour une fabrication en technologie 45 nm et il faudra compter 60 millions de dollars pour ceux permettant la technologie 14 nm [10]. Cette contrainte économique forte, pose le problème de la réutilisation des architectures et des codes. Les MP-RSoC peuvent donner lieu au développement de systèmes personnalisables et flexibles, fournissant des puissances de calculs proches de celles obtenues par un SoC dédié, réalisé à l'aide d'un ASIC (voir figure 1.1). La flexibilité du MP-RSoC peut favoriser la réduction des coûts lorsque le même système sur puce s'adapte à plusieurs domaines applicatifs : téléphonie mobile, automobile, imagerie, avionique, réseaux de communication, cloud, monétique, etc. La flexibilité répond de plus à des demandes spécifiques du marché des SoC comme la dynamicité [11].

#### 1.3.2 La dynamicité

La dynamicité est une caractéristique de plusieurs applications, comme la radio logicielle ou la vidéo embarquée, qui nécessitent de supporter des variabilités dans leur exécution en fonction des conditions extérieures telles que les performances du canal de transmission. Ces applications sont intégrées dans des dispositifs connectés en réseau, créant l'*Everyware* <sup>3</sup> [12] qui, par définition, est dynamique. La dynamicité est aussi requise du fait de la vitesse d'évolution des applications et/ou des normes. l'ARD du MP-RSoC permet naturellement au matériel de s'adapter à la dynamicité de l'application embarquée.

## 1.3.3 La disponibilité

Ces dernières années les circuits logiques programmables ont connu un très grand développement et leur prix de revient baisse tandis que leurs performances augmentent, les rendant plus accessibles [13]. Les MP-RSoC sont construits autour des architectures telles que le FPGA <sup>4</sup> qui supporte d'ores et déjà la reconfiguration dynamique. Aujourd'hui il est possible de concevoir un MP-RSoC à la fois flexible au niveau logiciel et au niveau matériel.

<sup>3.</sup> terme inventée et utilisée par A. Greenfield pour parler des dispositifs de traitement, petits et peu coûteux, connectés en réseau (intégrés et distribués dans les objets de la vie quotidienne), visant à créer un espace quotidien intelligent.

<sup>4.</sup> Field Programmable Gate Array

Figure 1.1 : Compromis entre performance et flexibilité des architectures reconfigurables

## 1.4 Les types d'ARD et les outils des MP-RSoC

Les architectures matérielles des MP-RSoC rencontrées dans la littérature sont de type grain fin (configurable au niveau du bit), ou grain épais (configurable au niveau fonctionnel) et les outils qui permettent d'y déployer des applications sont spécifiques à chacune d'elle.

Une plateforme est une base de travail à partir de laquelle on peut utiliser un ensemble de logiciels afin de développer une application.

## 1.4.1 ARD pour MP-RSoC

Les MP-RSoC intègrent des ARD qui peuvent être à grain fin comme le FPGA qui permet une configuration au niveau d'opérateurs booléens. Elles peuvent aussi être à grain épais comme l'architecture MATRIX [14] et proposer une configuration à base des bancs de registres, d'UAL programmables, de processeurs à jeu d'instructions variables, d'unités d'interconnexion qui opèrent sur des mots de taille fixe ou variable. Autour des années 2000 un grand engouement est observé pour le développement des MP-RSoC. Le tableau 1.2 présente un certain nombre de projets présentant des architectures de traitements originales. Malheureusement, la révolution dans l'utilisation des MP-RSoC n'a pas eu lieu et les solutions

proposées sont en majorité restées dans les cartons ou ont été abandonnées à cause de la relative difficulté pour leur mise en œuvre et de la résistance au changement.

Le tableau 1.2 précise pour chaque projet : l'architecture d'interconnexion des unités d'exécution, leur granularité, le mode de déploiement de l'application embarquée sur le matériel et le domaine d'utilisation de la plateforme ou de l'environnement proposé. Le type de ressources de base et l'organisation matérielle de l'ARD ont un grand impact sur le développement des outils de déploiement de l'application. Des architectures complexes ou sophistiquées ont difficilement de bons outils qui leurs sont associés. Une solution consiste à avoir une architecture matérielle simple et un outil de déploiement qui peut lui-même configurer l'ARD suivant les besoins de l'application [15].

#### 1.4.2 Outils de programmation et de configuration du MP-RSoC

Les structures de programmation pour architectures reconfigurables sont très dépendantes de l'organisation matérielle et de la granularité qui favorise l'utilisation de différents langages. Pour les plateformes MorphoSys, MATRIX, et REMARC le langage utilisé est l'assembleur [15]. La plateforme DART offre un atelier logiciel comprenant un compilateur C, un synthétiseur et un simulateur dédié [16]. D'autres plateformes disposent de flux de conception automatique à partir du langage HDL ou d'un langage de programmation de haut niveau comme le *Native Mapping Language* (NML) [17] pour la plateforme XPP <sup>5</sup>.

Les environnements diffèrent par l'approche utilisée pour le mappage technologique, le placement et le routage. Le mappage technologique est relativement simple pour les architectures à grain épais dans lesquelles les opérateurs sont déjà prédéfinis; il est plus complexe pour les architectures à grain fin telles que les FPGA.

Pour améliorer la performance de l'application, plusieurs projets MP-RSoC ont proposé un nouveau langage de programmation et un nouveau compilateur/synthétiseur pour mieux cibler leur architecture. Ce dernier est chargé d'utiliser la reconfiguration du matériel pour optimiser les unités de traitement comme dans [18] et [19].

Définir un paradigme de programmation pour un MP-RSoC est une tâche difficile. Il n'y a pas une méthode générale qui couvre la programmation de toutes les unités d'exécution. Les unités de type processeurs généralistes peuvent être programmées dans un langage comme le C/C++ mais d'autres unités d'exécution ayant un jeu d'instructions plus spécifiques nécessitent un langage particulier ou une extension spécifique du langage de programmation usuel. La reconfiguration dynamique peut être intégrée dans l'application à l'aide d'un compilateur ou d'un outil de déploiement ou être entièrement laissée sous le contrôle du concepteur de l'application en fonction des tâches à exécuter. Il n'existe pas aujourd'hui un modèle bien établi de déploiement d'application sur un MP-RSoC, chaque projet propose plutôt son propre modèle.

<sup>5.</sup> eXtreme Processing Platform

Tableau 1.2: Plateformes pour architectures reconfigurables trouvées dans la littérature

| Project     | first<br>publ. | Source | Archi-<br>tecture  | Granula-<br>rity                 | Fabrics                                 | Mapping                        | Intended target application        | Language      |

|-------------|----------------|--------|--------------------|----------------------------------|-----------------------------------------|--------------------------------|------------------------------------|---------------|

| DART        | 2003           | [16]   | 2-D array          | 8 & 16 bit                       | hierarchical<br>buses                   | run-time re-<br>configuration  | 3G<br>telecommuni-<br>cation       | С             |

| PADDI-2     | 1993           | [14]   | crossbar           | 16 bit                           | multiple<br>crossbar                    | routing                        | DSP and others                     |               |

| DP-FPGA     | 1994           | [14]   | 2-D array          | 1 & 4 bit,<br>multi-<br>granular | inhomogenous<br>routing chan-<br>nels   | switchbox<br>routing           | regular data-<br>paths             |               |

| KressArray  | 1995           | [14]   | 2-D mesh           | family : select<br>pathwidth     | multiple NN <sup>6</sup> & bus segments | (co-<br>)compilation           | (adaptable)                        |               |

| Colt        | 1996           | [14]   | 2-D array          | 1 & 16 bit inhomogenous          | (sophisticated)                         | run time re-<br>configuration  | highly dyna-<br>mic reconfig.      |               |

| RaPID       | 1996           | [14]   | 1-D array          | 16 bit                           | segmented<br>buses                      | channel rou-<br>ting           | pipelining                         | Rapid-C       |

| Matrix      | 1996           | [5]    | 2-D mesh           | 8 bit, multi-<br>granular        | 8NN, length 4<br>& global lines         | multi-length                   | general pur-<br>pose               | Assembler     |

| RAW         | 1997           | [14]   | 2-D mesh           | 8 bit, multi-<br>granular        | 8NN switched connections                | switchbox<br>rout              | experimental                       |               |

| Garp        | 1997           | [14]   | 2-D mesh           | 2 bit                            | global & semi-global lines              | heuristic rou-<br>ting         | loop accelera-<br>tion             |               |

| Pleiades    | 1997           | [14]   | mesh /<br>crossbar | multi-<br>granular               | multiple seg-<br>mented cross-<br>bar   | switchbox<br>routing           | multimedia                         |               |

| PipeRench   | 1998           | [14]   | 1-D array          | 128 bits                         | (sophisticated)                         | scheduling                     | pipelining                         |               |

| REMARC      | 1998           | [20]   | 2-D mesh           | 16 bit                           | NN & full<br>length buses               | (information<br>not available) | multimedia                         | Assembler     |

| MorphoSys   | 1999           | [18]   | 2-D mesh           | 16 bit                           | NN, length<br>2 & 3 global<br>lines     | manual P&R                     | (not disclosed)                    | Assembler     |

| CHESS       | 1999           | [14]   | hexagon<br>mesh    | 4 bit, multi-<br>granular        | 8NN and buses                           | JHDL compilation               | multimedia                         |               |

| DReAM       | 2000           | [19]   | 2-D array          | 8 &16 bit                        | NN, segmented buses                     | co-<br>compilation             | next genera-<br>tion wireless      |               |

| Chameleon   | 2000           | [14]   | 2-D array          | 32 bit                           | (not disclosed)                         | co-<br>compilation             | tele- & data<br>communica-<br>tion |               |

| MorphICs    | 2000           | [14]   | 2-D array          | (not disclosed)                  | (not disclosed)                         | (not disclosed)                | next genera-<br>tion wireless      |               |

| PACT<br>XPP | 2003           | [17]   | 2-D mesh           | 32 bits                          | NN, switched connections & global lines | compiler run-<br>time reconf   | general pur-<br>pose               | Native<br>NML |

# 1.5 Les options et les possibilités de mise en œuvre des MP-RSoC

Les contraintes de la conception des MP-RSoC placent le concepteur devant un ensemble de possibilités qu'il faut comprendre et analyser pour faire les bons choix.

Le concepteur d'un MP-RSoC doit faire un compromis entre le temps de développement et les performances de l'application, puis entre la souplesse de programmation des différentes tâches de l'application et leur performance. Le concepteur doit également considérer la surface occupée sur la puce par l'application et le coût du développement. Si tous les modules fonctionnels de l'application sont exclusivement réalisés à l'aide des ressources logiques de base, les performances de l'application pourraient être optimales mais le temps de développement qui est lié au coût, et la surface occupée deviennent très vite prohibitifs.

#### 1.5.1 Le partitionnement du MP-RSoC

Deux aspects à prendre en compte lors de la mise en œuvre d'une application sur un MP-RSoC : le partitionnement spatio temporel identifie les segments de l'application qui peuvent s'exécuter indépendamment les uns des autres sur une tranche de temps; le partitionnement architectural définit les tâches réalisables logiciellement et celles réalisables matériellement. Plus précisément Il s'agit d'une part, lors de la conception, de décider si des tâches doivent être réalisées à l'aide de processeurs ou si des tâches doivent être directement implantées matériellement. Il s'agit d'autre part, lors de l'exécution, de décider quand une tâche doit être chargée en mémoire ou configurée. Ce partitionnement dans le cadre d'un MP-RSoC ne peut être intégralement décidé avant l'exécution. Pour exploiter au mieux les caractéristiques dynamiques d'une application, le partitionnement doit avoir lieu durant l'exécution. Il est, dans ce cadre, intéressant de disposer d'un intergiciel qui fournit ces services à l'instar d'un OS comme dans [21] ou bien de disposer d'une bibliothèque de primitives qui donne à chaque tâche de l'application les primitives permettant de gérer ses communications et le chargement dynamique des configurations applicatives pendant le fonctionnement du MP-RSoC.

#### 1.5.2 Les modules du MP-RSoC

Le MP-RSoC peut être physiquement modélisé comme un ensemble de modules qui échangent des données pour réaliser une application. Le module est à minima l'unité d'exécution qui accomplit au moins une fonction constitutive d'une tâche de l'application ou à maxima une unité de traitement complexe responsable de plusieurs tâches tel qu'un processeur. Sur la puce, le concepteur de MP-RSoC dispose des modules physiques et des modules virtuels encore appelés blocs IP. Pour faire fonctionner les modules ensemble, il leur associe des interfaces d'interconnexion pour assurer les communications. Différents standards ont

été fournis pour l'interfaçage. Nous pouvons citer : VCI (Virtual component interface) développé par VSIA [22], OCP (Open Core Protocol) développé par OCP-IP (Open Core Protocol-International Partnership) et IP-XACT développé par le consortium SPIRIT [23]. L'utilisation de ces standards spécifiques augmente la complexité de la conception des MP-RSoC et rend difficile la réutilisation des IP. Dans ce cas de figure, il est nécessaire, lors de la conception, de prendre en compte cet interfaçage et de disposer d'outils qui soient capables de gérer la diversité des standards, ou bien qui imposent une norme commune, pour réaliser un MP-RSoC hétérogène (voir figure 1.2)

FIGURE 1.2 : Système hétérogème et système homogène [24]

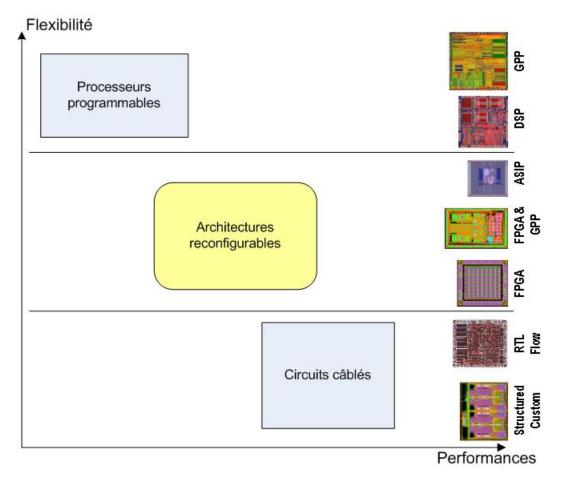

#### 1.5.3Partition statique et partition dynamique du MP-RSoC

Certains modules du MP-RSoC seront déployés en permanence sur la puce, ils constitueront la partition statique du MP-RSoC tandis que d'autres modules seront déployés dynamiquement. Les modules dynamiques sont configurés sur les ressources logiques de l'ARD suivant l'évolution de l'application. La figure 1.3 présente le principe d'organisation d'un MP-RSoC utilisant des régions reconfigurables réservées pour accueillir des modules dynamiques. Ces régions échangent des informations avec la partition statique du MP-RSoC à l'aide des connecteurs internes, les Bus macro de Xilinx [25] par exemple.

FIGURE 1.3: Architecture de base d'un système reconfigurable dynamiquement

#### 1.6 Le MP-RSoC : un système parallèle

Les opérations logiques sont naturellement concurrentes dans les puces ayant des ARD, ce qui permet de facto de réaliser des systèmes de traitements parallèles. Le MP-RSoC doit être structuré suivant un modèle de système parallèle afin de faciliter le travail du concepteur de l'application. Sans un modèle de structuration de l'application parallèle, le concepteur serait obligé de synchroniser les modules de traitement par un système adhoc alors que l'utilisation d'un modèle donne la possibilité de réaliser des mécanismes de synchronisation standardisés ou mieux, d'utiliser un mécanisme de synchronisation déjà disponible afin de réaliser plus rapidement son application. Nous définissons dans cette section la notion de tâche matérielle et rappelons les architectures des systèmes parallèles.

#### 1.6.1 Tâches matérielles et tâches logicielles

Tâche logicielle: désigne une instance exécutable sur un processeur d'un algorithme, d'un processus, d'un traitement, ou d'une fonctionnalité quelconque. Une tâche logicielle peut utiliser d'autres primitives ou fonctions (sous-tâches) pour son exécution, elle peut ainsi requérir plusieurs unités d'exécution.

Tâche matérielle : désigne la réalisation directe sur les ressources logiques d'une puce, d'un algorithme, d'un processus, d'un traitement ou d'une fonctionnalité quelconque à partir d'un code écrit en langage de description matérielle. Une tâche matérielle peut être décrite en assemblant des IP ou en utilisant des modules IP dans la description.

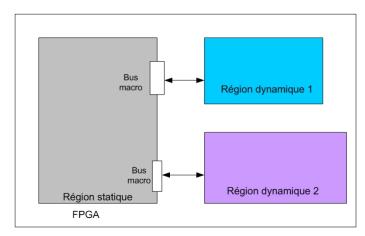

#### 1.6.2 Les architectures de traitements parallèles

Suivant la classification de Flynn [26], une architecture parallèle peut être de type SIMD, MISD ou MIMD (voir figure 1.4). Chaque type décrit l'interaction entre le flux de données, le flux d'instructions et l'unité d'exécution. Dans le type SIMD, il s'agit d'une architecture où les unités d'exécution traitent la même instruction sur des données différentes. Les processeurs vectoriels, les processeurs de traitement graphique sont des exemples d'architectures SIMD.

Dans le type MISD, les différentes unités d'exécution traitent en parallèle le même jeu de données par des instructions potentiellement différentes, les architectures pipeline appartiennent à ce type. Dans le type MIMD, les unités d'exécution traitent différents ensembles de données à l'aide de différents ensembles d'instructions; c'est le cas des systèmes multiprocesseurs. Le type SISD de la figure 1.4 désigne une architecture mono traitement : l'unité d'exécution réalise un traitement sur une donnée à l'aide d'une instruction.

La structure MIMD est celle qui permet la mise en œuvre du parallélisme des tâches dans un MP-RSoC, chaque tâche matérielle peut indépendamment traiter un ensemble particulier de données.

Figure 1.4 : Taxonomie de Flynn

#### 1.6.3 Modèles mémoire de l'application parallèle

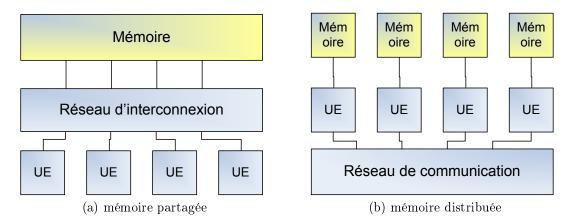

Dans la littérature, on distingue suivant la répartition du stockage des données deux modèles de systèmes parallèles : les systèmes parallèles à mémoire partagée (voir figure 1.5a), et les systèmes parallèles à mémoire distribuée (voir figure 1.5b). Chaque modèle influence directement la conception matérielle ainsi que le modèle de déploiement d'application du MP-RSoC. La figure 1.5 montre une architecture à mémoire partagée et une architecture à mémoire distribuée.

#### 1.6.3.1 Systèmes parallèles à mémoire partagée

Dans les systèmes à mémoire partagée, toutes les unités d'exécution (UE) partagent les ressources de la même mémoire; par conséquent, tous les changements faits par une UE à un emplacement mémoire deviennent visibles à toutes les autres UE. D'un point de vue conceptuel, les systèmes à mémoire partagée sont peu évolutifs. Ceci est dû au fait que la bande passante d'accès à la mémoire du système s'amenuise avec la croissance du nombre d'UE. Dans un système à mémoire partagée, les différents processus échangent des informations à travers les variables partagées. Les systèmes à mémoire partagée exigent des mécanismes de synchronisation et de protection des variables partagées en mémoire tels que les sémaphores, les barrières et les serrures. POSIX threads [27] et OpenMP [28] permettent de mettre en œuvre une application parallèle dans un système multiprocesseurs à mémoire partagée.

#### 1.6.3.2 Systèmes parallèles à mémoire distribuée

Dans les systèmes à mémoire distribuée, chaque unité d'exécution a sa mémoire privée (voir figure 1.5b). Les UE communiquent de manière explicite et utilisent un protocole de communication particulier. Les systèmes à mémoires distribuées sont potentiellement plus évolutifs, car les supports de communication sont partagés entre les unités d'exécution [24]. Les systèmes à mémoire distribuée exigent des mécanismes pour supporter les communications explicites entre les instances des tâches. Habituellement une bibliothèque de primitives est utilisée pour permettre d'écrire sur les canaux de communications. La bibliothèque MPI

Figure 1.5 : Système à mémoire partagée et système à mémoire distribuée [24]

(Message Passing Interface) est le standard le plus utilisé [29]. Le principal inconvénient de l'architecture à mémoire distribuée est qu'elle nécessite un protocole de communication et mobilise plus de ressources pour sa réalisation que le partage de la mémoire entre les UE. Une application parallèle dans un système multiprocesseurs à mémoire distribuée est plus complexe à mettre en œuvre que dans un système multiprocesseurs à mémoire partagée du fait de la spécification explicite du parallélisme.

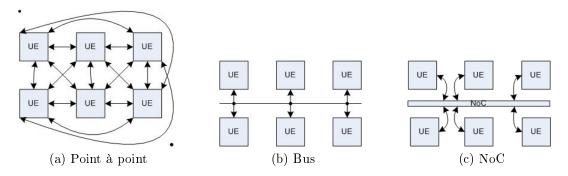

#### 1.6.4 L'interconnexion des systèmes parallèles

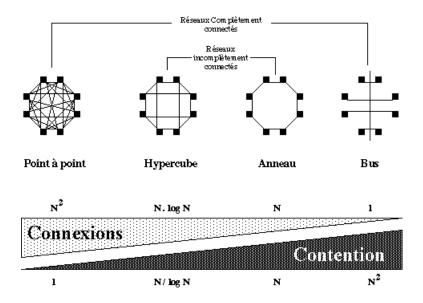

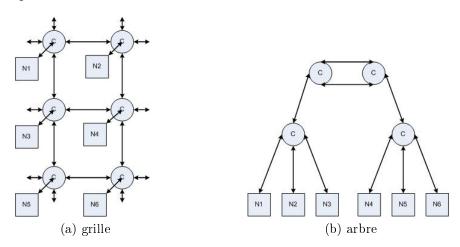

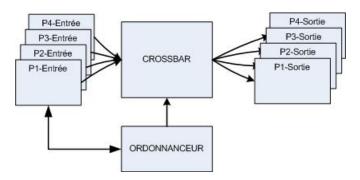

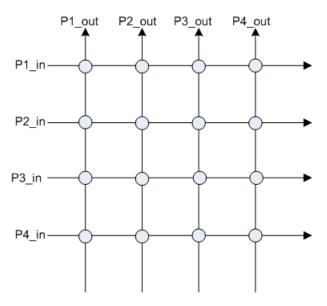

Pour la mise en œuvre d'un MP-RSoC, il est nécessaire de choisir une topologie physique des connexions qui permette aux UE de communiquer dans la puce. A ce niveau on distingue trois grandes orientations.

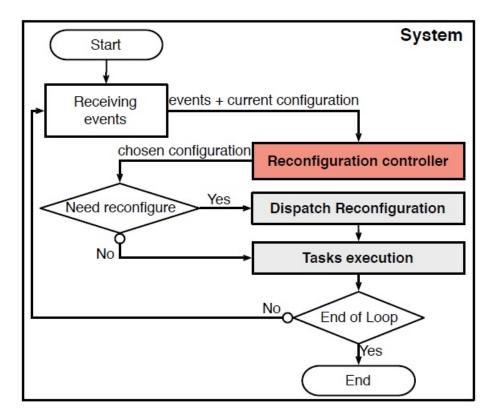

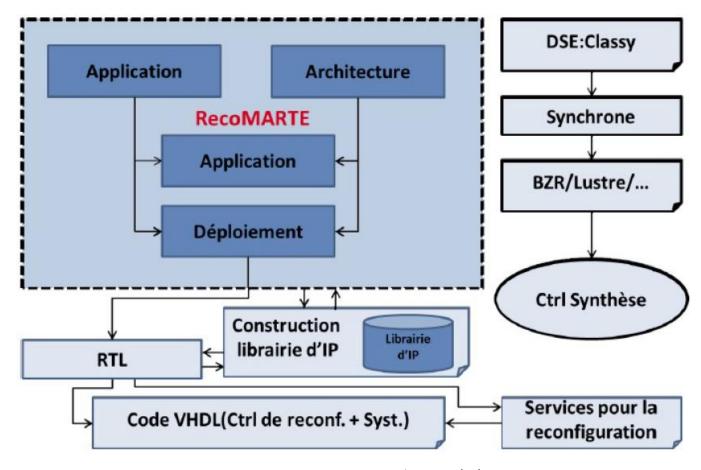

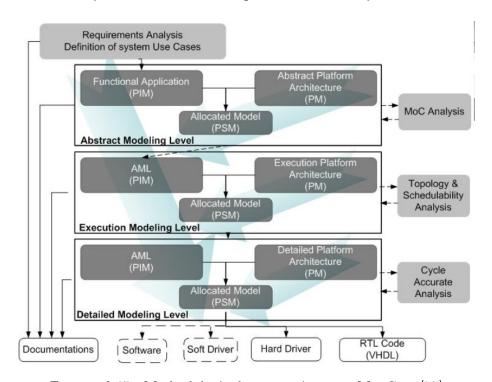

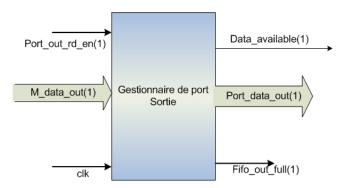

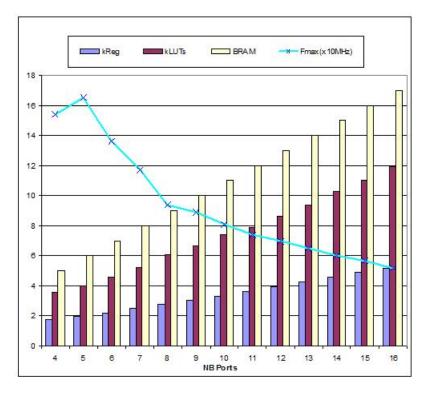

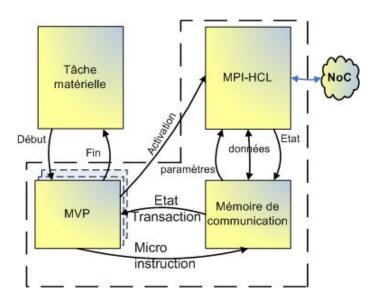

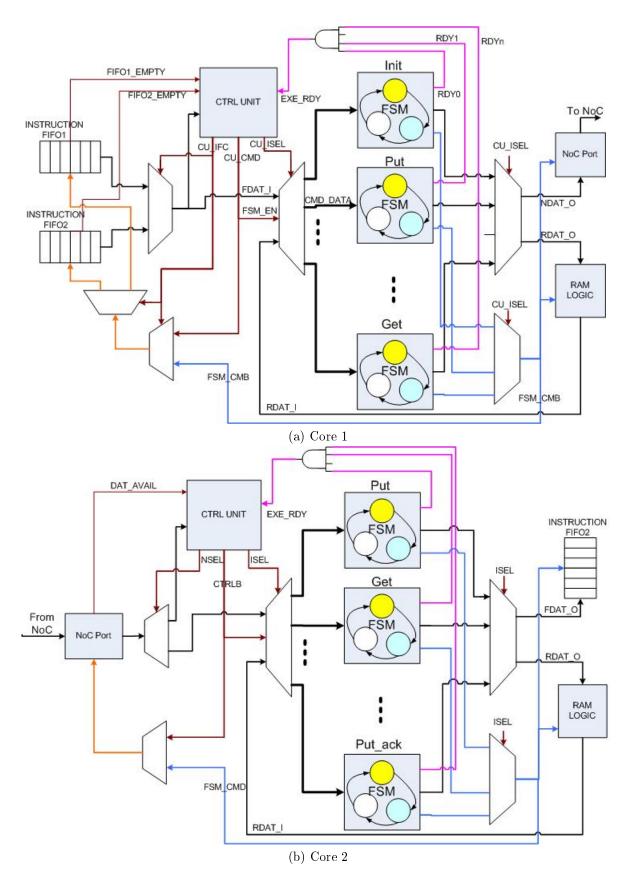

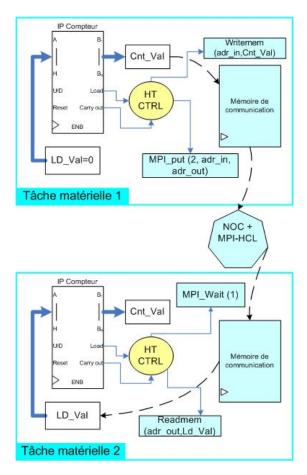

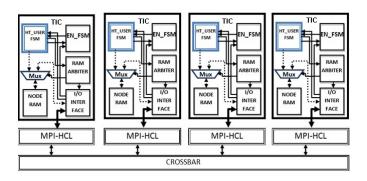

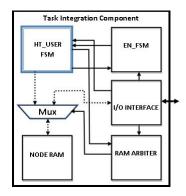

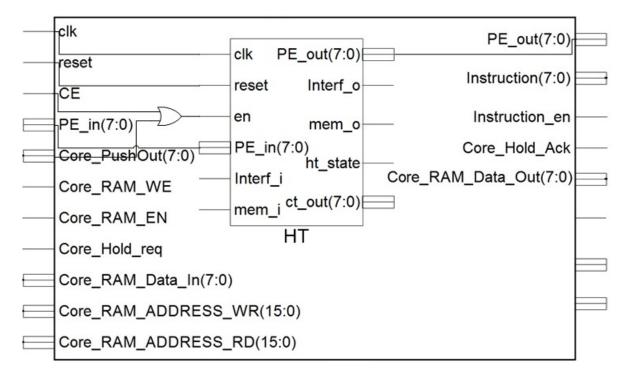

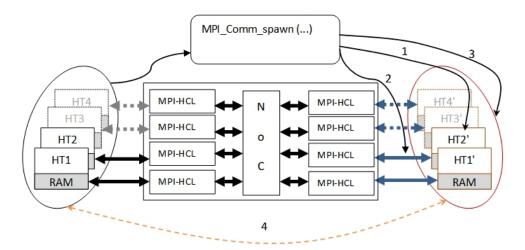

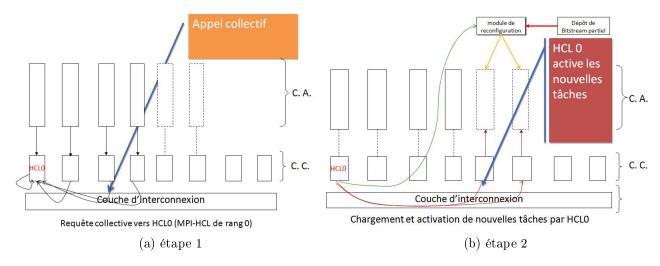

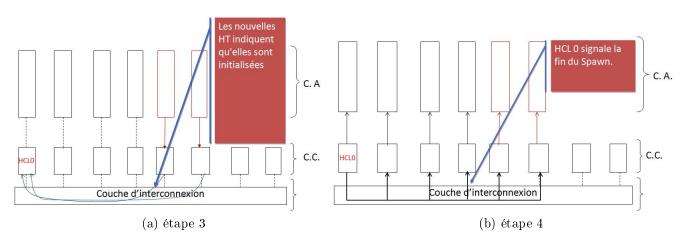

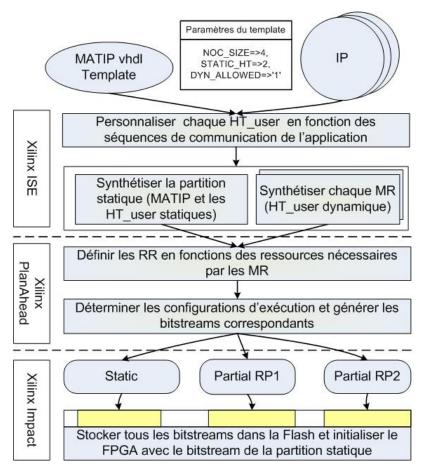

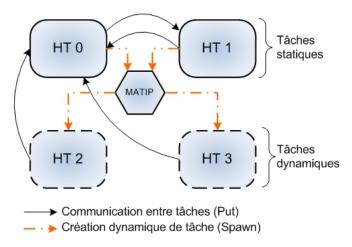

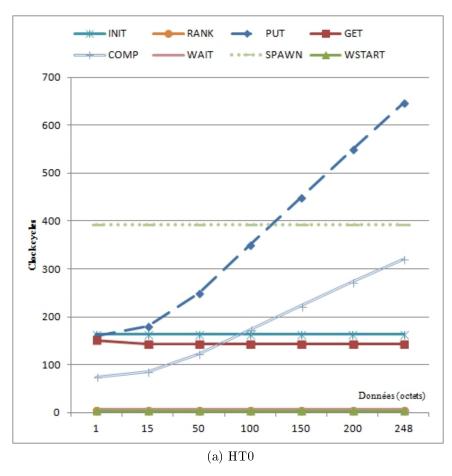

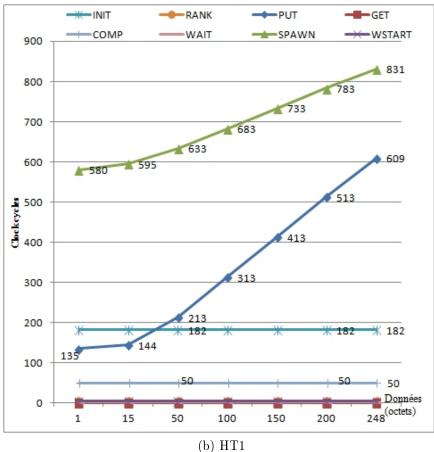

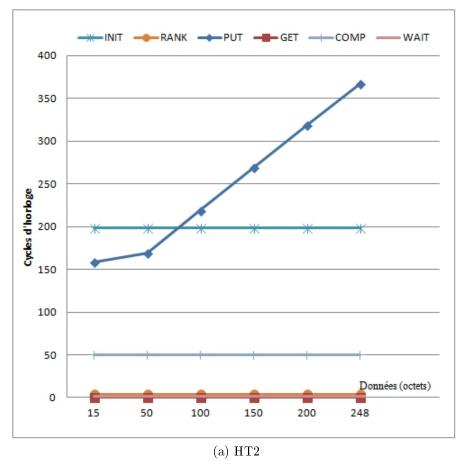

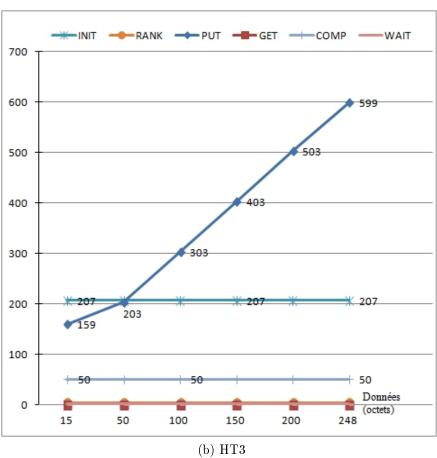

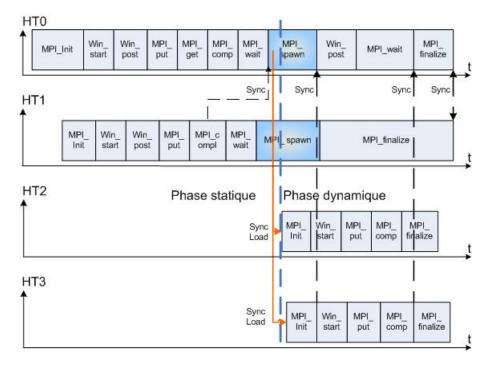

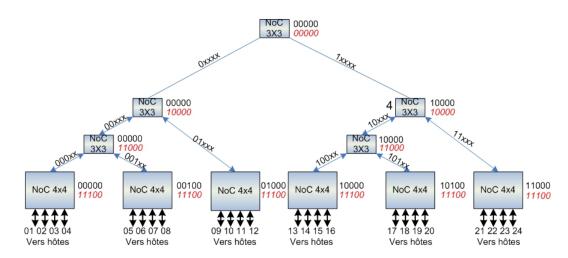

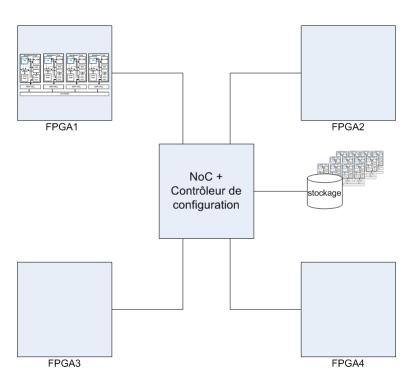

- i Point à point (représenté en figure 1.6a) : les noeuds possèdent entre eux des liaisons directes ce qui permet d'avoir une grande bande passante car le support de communication n'est pas partagé. Néanmoins il n'est pas facile de faire évoluer le système à cause du coût silicium induit.