## De l'ingénierie de contacts métalliques aux transistors 3D à grille entourante: Architectures alternatives pour MOS nanométriques

Guilhem Larrieu

### ▶ To cite this version:

Guilhem Larrieu. De l'ingénierie de contacts métalliques aux transistors 3D à grille entourante : Architectures alternatives pour MOS nanométriques. Micro et nanotechnologies/Microélectronique. Universite Toulouse III Paul Sabatier, 2016. tel-01292061

### HAL Id: tel-01292061 https://theses.hal.science/tel-01292061

Submitted on 22 Mar 2016

HAL is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

## UNIVERSITE DE TOULOUSE III

## Habilitation à Diriger des Recherches

De l'ingénierie de contacts métalliques aux transistors 3D à grille entourante : Architectures alternatives pour MOS nanométriques.

Soutenu le 11 février 2016 par

### **Guilhem LARRIEU**

LAAS-CNRS

### Jury:

| Dr. Thomas ERNST, CEA LETI, Grenoble       | Rapporteur  |

|--------------------------------------------|-------------|

| Pr. Cristell MANEUX, IMS, Bordeaux         | Rapporteur  |

| Pr. Dimitris TSOUKALAS, NTUA, Athènes      | Rapporteur  |

| Pr. Frédéric MORANCHO, LAAS-CNRS, Toulouse | Président   |

| Pr. Adrian IONESCU, EPFL, Lausanne         | Examinateur |

| Dr. Stéphane MONFRAY, STMicro, Crolles     | Examinateur |

| Dr. Fuccio CRISTIANO, LAAS-CNRS, Toulouse  | Examinateur |

| Dr. Liviu Nicu, LAAS-CNRS, Toulouse        | Invité      |

|                                            |             |

### SOMMAIRE

| Р              | réamb      | ule    |                                                                                    | 5  |

|----------------|------------|--------|------------------------------------------------------------------------------------|----|

| 1              | Ap         | proc   | he alternative du module S/D : Ségrégation de dopants dans des contacts alliés     | 7  |

|                | 1.1        | Pos    | sition du probleme                                                                 | 7  |

|                | 1.2        | Ing    | énierie matériau : modulation de hauteurs de barrière par ségrégation de dopants   | 11 |

|                | 1.2        | 2.1    | Siliciures à faible hauteur de barrière.                                           | 11 |

| 1.2.2<br>1.2.3 |            | 2.2    | Concept de modulation de barrière par ségrégation de dopants                       | 14 |

|                |            | 2.3    | Ségrégation de dopants sur des contacts de type p.                                 | 17 |

|                | 1.2        | 2.4    | Ségrégation de dopants sur des contacts de type n.                                 | 18 |

|                | 1.3        | Inte   | égration de contacts métalliques à l'échelle de dispositifs :                      | 22 |

|                | 1.3<br>sul |        | Développement d'un procédé de transistor à grille métallique nanométrique sur SOI. | 22 |

|                | 1.3        | 3.2    | Développement de transistor p-MOSFET à source/drain métalliques                    | 24 |

|                | 1.3        | 3.3    | Développement de transistor n-MOSFET à source/drain métalliques                    | 27 |

|                | 1.4        | Car    | ractérisations hyperfréquences et de dispositifs logiques élémentaires:            | 31 |

|                | 1.4        | l.1    | Caractérisation d'inverseur CMOS à source/drain métallique unique                  | 31 |

|                | 1.4        | 1.2    | Caractérisation hyperfréquence de MOSFETs à source/drain métalliques               | 35 |

|                | 1.5        | Co     | nclusion                                                                           | 36 |

|                | 1.6        | Sele   | ection d'articles                                                                  | 36 |

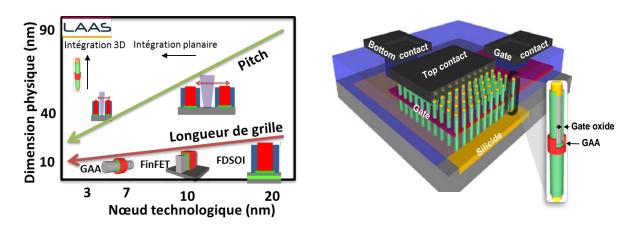

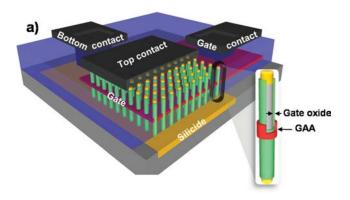

| 2              | Tr         | ansist | tors 3D à nanofils                                                                 | 48 |

| 2.1 Posi       |            |        | sition du problème et concept:                                                     | 48 |

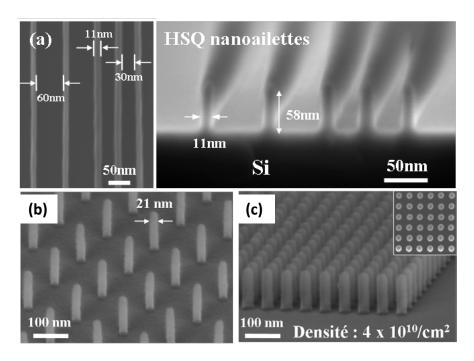

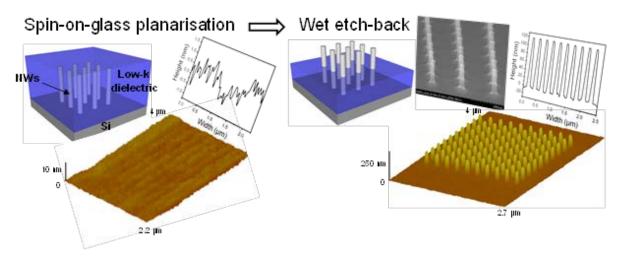

| 2.2 Réalisati  |            | Réa    | alisation de réseau localisé de nanofils                                           | 50 |

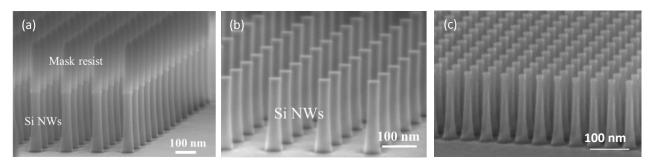

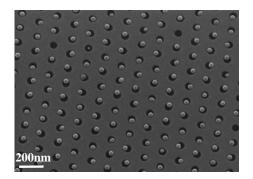

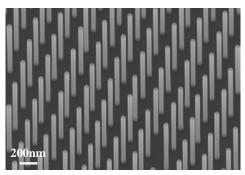

|                | 2.2        | 2.1    | Approche descendante (top-down)                                                    | 50 |

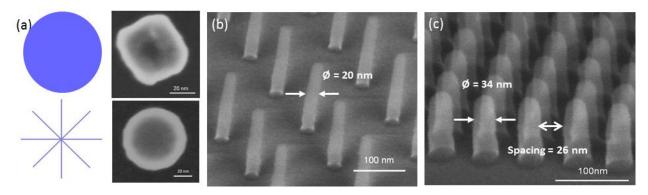

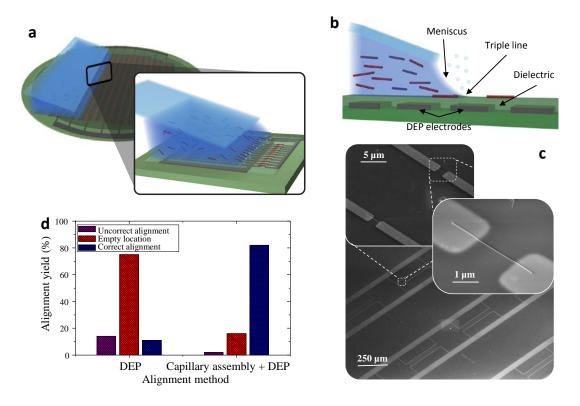

|                | 2.2        | 2.2    | Approche combinatoire (top-down / bottom-up)                                       | 53 |

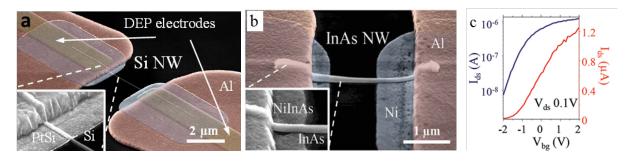

|                | 2.3        | Ing    | rénierie de matériaux sur des nanostructures 1D.                                   | 60 |

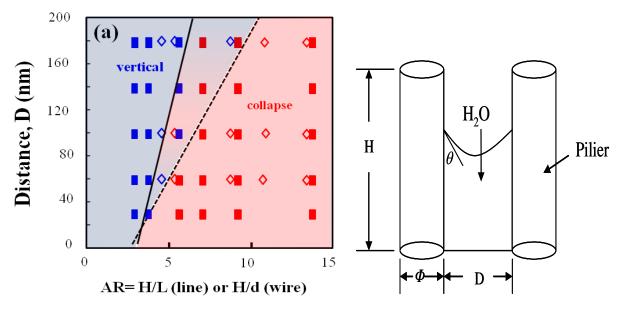

|                | 2.3        | 3.1    | Effondrement de nanostructures par capillarité.                                    | 61 |

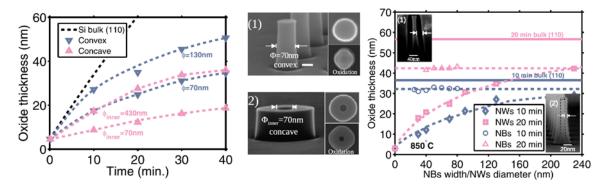

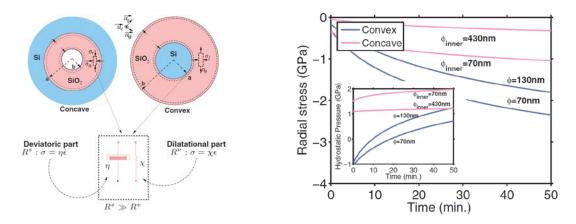

|                | 2.3        | 3.2    | Oxydation de nano-objets                                                           | 63 |

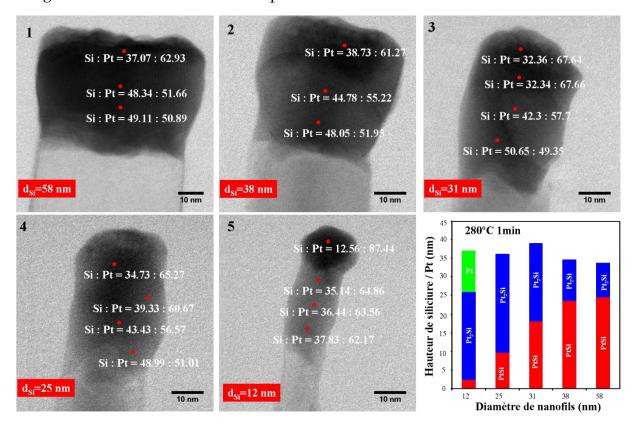

|                | 2.3        | 3.3    | Formation d'alliage métallique dans des nanofils                                   | 65 |

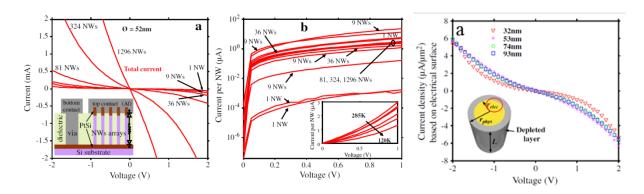

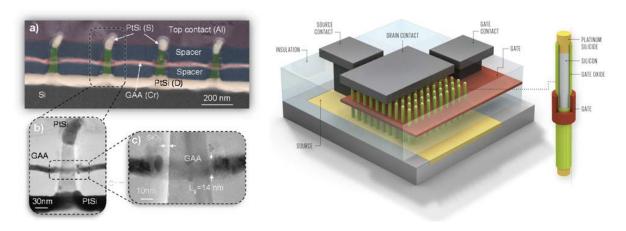

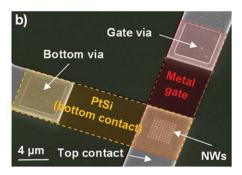

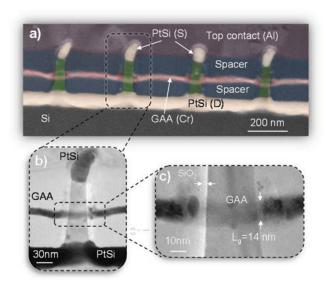

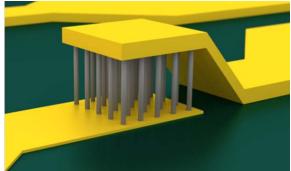

|                | 2.4        | Tra    | unsistors 3D nanométriques : développement et caractérisations                     | 67 |

| 2.4          | .1                                                                                                             | Contacts S/D                                                                                                                     | 67                                                            |

|--------------|----------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------|

| 2.4          | .2                                                                                                             | Ingenierie des couches à l'échelle nano – transistor 3D                                                                          | 70                                                            |

| 2.4          | .3                                                                                                             | Comportement électrique des dispositifs                                                                                          | 72                                                            |

| 2.5          | Cor                                                                                                            | nclusion                                                                                                                         | 76                                                            |

| 2.6          | Sele                                                                                                           | ction d'articles                                                                                                                 | 76                                                            |

| Per          | spec                                                                                                           | tives                                                                                                                            | 98                                                            |

| 3.1          | Tra                                                                                                            | nsistors 3D à nanofils : approches faiblement énergivores pour le 3nm                                                            | 98                                                            |

| 3.2<br>bio/c |                                                                                                                |                                                                                                                                  | .102                                                          |

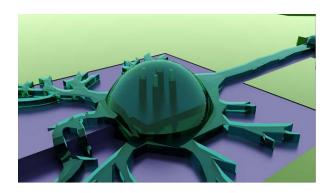

|              |                                                                                                                | Interface nanofil/neurone pour la mesure intracellulaire de l'activité de neurones elles                                         | .103                                                          |

| 3.2          | .2                                                                                                             | Capteurs de gaz 3D à nanofils                                                                                                    | .106                                                          |

| 4 Annexes    |                                                                                                                | 5                                                                                                                                | .108                                                          |

| 4.1          | Cur                                                                                                            | riculum vitae                                                                                                                    | .108                                                          |

| 4.2          | List                                                                                                           | e bibliographique                                                                                                                | .109                                                          |

| 4.3          | Act                                                                                                            | ivites d'encadrement                                                                                                             | .119                                                          |

| 4.4          | Tra                                                                                                            | vaux d'expertises                                                                                                                | .121                                                          |

| 4.5          | Val                                                                                                            | orisation                                                                                                                        | .121                                                          |

| Bio          | bliog                                                                                                          | graphie                                                                                                                          | .124                                                          |

|              | 2.4<br>2.4<br>2.5<br>2.6<br>Per<br>3.1<br>3.2<br>bio/c<br>3.2<br>ind<br>3.2<br>4.1<br>4.2<br>4.3<br>4.4<br>4.5 | 2.6 Selection Perspects 3.1 Trans 3.2 Dévision/chimics 3.2.1 individus 3.2.2 Annexes 4.1 Cur 4.2 List 4.3 Act 4.4 Trans 4.5 Vale | 2.4.2 Ingenierie des couches à l'échelle nano – transistor 3D |

Condenser quinze années de recherche en moins de quatre-vingt pages est un exercice délicat qui demande des choix. J'ai décidé de présenter dans ce mémoire un condensé de mon activité en tant que chargé de recherche entre octobre 2005 et octobre 2015.

J'ai obtenu mon diplôme d'ingénieur à Polytech'Lille en 2000, avec une spécialisation en science des matériaux ainsi qu'un diplôme d'études approfondies (DEA) en microtechnologie et microélectronique cette même année à l'université des sciences de Lille1. J'ai passé ma thèse de doctorat en avril 2004 sur la fabrication des transistors à contacts source/drain Schottky à l'IEMN (Villeneuve d'Ascq). Puis, jusqu'en octobre 2005, j'étais chercheur postdoctoral à l'Université du Texas d'Arlington (UTA) dans le groupe du Pr. Meng Tao, travaillant sur le traitement de l'interface oxyde de grille à haute constante diélectrique/silicium par des approches de reconstruction de surface. J'ai intégré le 1er octobre 2005 l'Institut d'Electronique de Microélectronique et de Nanotechnologie IEMN (UMR-CNRS 8520) en tant que chargé de recherche CNRS.

Le manuscrit se compose en trois parties : les deux premières concernent les deux grandes périodes autour de la modulation de barrière Schottky par ségrégation de dopant et autour de l'intégration verticale de transistors à nanofils. Enfin la troisième partie détaille mes perspectives de recherche.

La première période a été mise à profit pour réaliser le programme de recherche proposé lors de mon recrutement au CNRS consacré à l'étude de technologie source/drain métallique, avec en particulier le développement de l'approche de ségrégation de dopant pour moduler la hauteur de barrière Schottky. Cette activité, centrale jusqu'en 2009, a ensuite baissé en régime pour s'arrêter en 2011 avec la complète démonstration de la technologie dans des circuits logiques élémentaires.

Un deuxième thème, que j'ai initié en 2008, est consacré à l'intégration générique de dispositifs à effet de champ à base de nanofils verticaux. Basé sur des premiers résultats obtenus à l'IEMN, j'ai effectué une mobilité géographique ainsi que thématique au LAAS-CNRS (UPR-8001) de Toulouse pour y développer un thème de recherche sur la nanoélectronique à base de nanofils.

### 1 APPROCHE ALTERNATIVE DU MODULE S/D : SEGREGATION DE DOPANTS DANS DES CONTACTS ALLIES

Lors des 40 dernières années, la technologie CMOS a permis une véritable révolution dans le traitement de l'information, sans cesse améliorée grâce à la diminution continue des dimensions des composants. Lors des 10 dernières années, un effort significatif a été porté sur l'étude du transport électronique dans des structures de taille nanométrique afin de poursuivre la diminution des dimensions pour des longueurs de grille avoisinant 10 nm. L'architecture source/drain, au même titre que celle liée à la grille, est un challenge énorme pour la réalisation des générations de longueur de grille inférieure à 40 nm. Les difficultés sont multiples, on peut citer par exemple la réalisation de jonctions ultra courtes avec un contrôle serré de la profondeur d'extension et du gradient des concentrations de dopant ou encore de contacter ces régions avec des matériaux de faibles résistances et de faibles résistances spécifiques de contact.

#### 1.1 POSITION DU PROBLEME

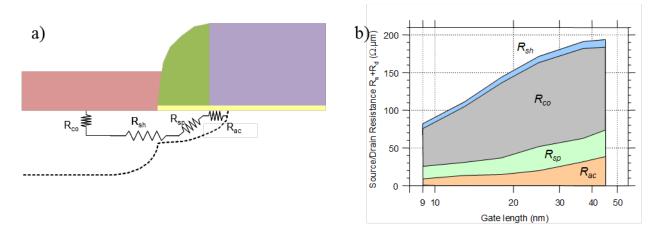

Quand le courant traverse un des deux terminaux source/drain vers le canal du transistor, la résistance associée (Fig. 1 a) peut être décomposée en quatre contributions résistives ¹: (i) Rc la résistance de contact, (ii) Rsh la résistance de diffusion de la zone de silicium fortement dopée, (iii) Rsp la résistance de défocalisation et (iv) Rac la résistance de la couche d'accumulation, ces deux derniers termes étant liés à la répartition des lignes de courants quand les porteurs entrent dans la jonction et dépendent du gradient de dopant et de la polarisation de grille.

Lorsque le transistor est soumis aux règles de miniaturisation, la résistance du canal (qui varie en L<sub>g</sub>) diminue alors que la résistance série source/drain augmente. A partir de modèles provenant à la fois de Kim et al. <sup>2</sup> et de *MASTAR* <sup>3</sup>, il a été mis en évidence que la résistance de contact (R<sub>co</sub>) était une contribution dominante de la résistance série totale, comme indiqué dans la Fig. 1 b. Il apparaît clairement que la résistance de contact associée à l'interface entre le siliciure et le silicium dopé du contact devient en fin de compte la composante principale de résistance parasite des contacts source / drain.

Fig. 1: a) Représentation schématique des contributions de résistance associées à l'architecture S / D d'un MOSFET: résistance de contact  $(R_{co})$ , résistance de diffusion  $(R_{sh})$ , résistance défocalisation  $(R_{sp})$  et résistance d'accumulation  $(R_{ac})$ . (b) Différentes composantes de la résistance série S/D d'un n MOSFET calculées en utilisant le modèle MASTAR³ en fonction de la longueur de grille du transistor.

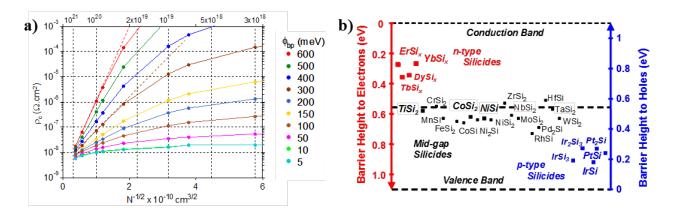

Afin de comprendre le transport du courant à travers l'interface siliciure / semiconducteur, il est important de noter que l'injection du courant dépend à la fois de la capacité des porteurs à surmonter la hauteur de barrière Schottky (émission thermoionique - TE) et de traverser cette barrière (tunnel ou émission de champ - FE). Des contacts sur silicium fortement dopé sont essentiellement régis par le second mécanisme. Dans ce cas, la résistivité spécifique de contact  $\rho_c$  ( $\Omega$ .cm²) peut être correctement évaluée par l'expression suivante  $^4$ :

$$\rho_c \approx \exp\left(\frac{4\pi\sqrt{\varepsilon \cdot m^*}}{h} \cdot \frac{\Phi_b}{\sqrt{N_d}}\right)$$

EQ. 1

où  $\varepsilon$  est la permittivité du semi-conducteur,  $m^*$  la masse effective des porteurs,  $\Phi_b$  la hauteur de barrière, h la constante de Planck, et  $N_d$  le dopage à l'interface entre le siliciure et le silicium. Cette équation décrit clairement la dépendance exponentielle de  $\rho_c$  avec la hauteur de la barrière et le niveau de dopage. L'émission thermoionique tend à dominer dans les semiconducteurs faiblement dopés. Lorsque la barrière devient suffisamment étroite pour que l'injection par tunnel se produise, l'émission de champ prend la relève de l'émission thermoionique dans la gamme de dopage élevé. Dans la gamme de dopage intermédiaire, le transport peut être également dominé par une émission thermoionique assistée par effet de champ (TFE), où les porteurs excités thermiquement atteignent un niveau d'énergie où la barrière est suffisamment étroite afin que l'émission de champ à travers une barrière d'énergie triangulaire se produise<sup>5</sup>.

Fig. 2: a): Résistivité spécifique de contact calculée ( $\rho_c$ ) d'une jonction Schottky en fonction du niveau de dopage de silicium de type p pour différentes valeur de hauteur de barrière Schottky. b) Hauteurs de barrière d'électrons (axe de gauche) et de trous (axe de droite) pour différents types d'alliage de silicium.

Jusqu'à présent, les siliciures utilisés pour l'intégration de contact source / drain dans les technologies CMOS disposent d'une fonction de travail verrouillée au milieu du gap du silicium (Eg). Pour ces siliciures, comme CoSi2, TiSi2, NiSi, la hauteur de barrière à l'injection d'électrons (type n) est de l'ordre de  $\phi_{bn} \sim 0.5$  - 0.6eV. En supposant que les barrières Schottky qui contrôlent l'injection d'électrons et de trous sont complémentaires sur le gap, ie  $(\phi_{bn} + \phi_{bp}) = E_g \sim 1.12 \text{eV}$  à 300K, il est facile de vérifier que φ<sub>bp</sub> est du même ordre de grandeur. Le principal avantage de cette approche conventionnelle réside dans l'utilisation d'un siliciure unique pour, à la fois, un MOSFET de type n et de type p, conduisant alors à un schéma d'intégration simple du module de source / drain. Bien que la plupart des siliciures à base métaux de transition et de terre rare présentent des caractéristiques Schottky dites de « milieu de gap » comme représenté sur la Fig. 2b, il est intéressant d'observer que certains siliciures disposent d'une hauteur de barrière relativement faible, de type p comme PtSi, IrSi, ou de type n comme ErSix, YbSix. Ces siliciures de bord de bande offrent des hauteurs de barrière Schottky d'environ 0.2 eV par rapport à la bande de valence pour les siliciures de type p et d'environ 0.3 eV par rapport à la bande de conduction pour des siliciures de type n. Etant donné que la résistivité de contact spécifique varie de manière exponentielle avec φ<sub>b</sub> comme explicité dans l'éq.1 et Fig. 2a, la réduction de la hauteur de la barrière fournit un effet de levier supplémentaire pour réduire encore  $\rho_c$ .

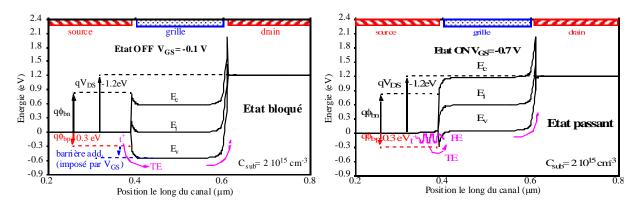

Mon projet de recherche d'entrée au CNRS proposait la conception, la fabrication et l'évaluation d'une structure MOS à source/ drain Schottky. Afin de s'affranchir des challenges inhérents à la formation de contacts ohmiques sur des jonctions fortement dopées, le projet propose leurs remplacements par des jonctions siliciurées à très faibles hauteurs de barrières Schottky et de les implémenter dans des dispositifs MOSFETs à grille métallique sur substrat silicium sur isolant (SOI). Cette architecture utilise un film

actif de silicium d'une dizaine de nanomètres complètement déplété. Le mode de fonctionnement est schématiquement représenté en *Fig. 3*. Lorsque le transistor est bloqué, un porteur doit franchir par effet thermo-électronique une barrière égale à la barrière Schottky du contact plus la contribution due à l'effet de champ développé par la grille. Lorsque le transistor est passant, c'est à dire quand un potentiel de grille permet de décaler les bandes d'énergie vers le haut, un porteur ne doit franchir, par effet thermo-électronique ou tunnel, que la barrière Schottky pour être injecté dans le canal. On comprend aisément que plus cette barrière est faible, plus facile sera l'injection.

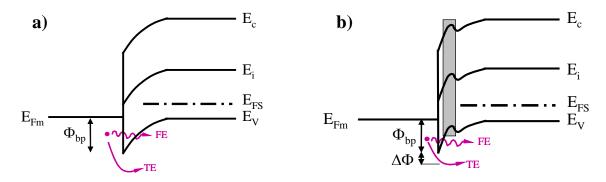

Fig. 3: Courbure de bande de valence entre source et drain d'un transistor SB-MOS de type p. (a) état bloqué: une large et profonde barrière est développée par l'effet de champ à travers la grille (b) état passant: la courbure de bande au voisinage de la source permet la circulation d'un courant par effet thermoélectronique et par effet tunnel.

Sur la base d'un niveau de performance requis pour un nœud de la technologie défini, il est possible de faire une comparaison entre une architecture S/D conventionnelle à jonction fortement dopée et une architecture à contacts Schottky. Par exemple, Connelly et al.<sup>6</sup> ont simulé le temps de commutation de portes logiques intégrant des CMOS double-grille de 25nm, à la fois avec des contacts Schottky et des contacts S/D fortement dopés. Les simulations montrent que les dispositifs avec des contacts S / D métalliques ayant une barrière de 0.1 eV possèdent des performances comparables à des technologies S /D fortement dopées avec une résistivité de contact de 3x10-8 Ω cm-2. Un CMOS « Zero »-barrière Schottky serait alors 50% plus rapide que son équivalent en S / D dopée. Dans ce contexte, il peut être facile de comprendre que la quête de contacts à très faible barrière Schottky (inférieure à 0.1 eV) est la clé pour surperformer les dispositifs conventionnels.

Cette thématique de recherche s'articule autour de 3 axes:

*Ingénierie matériau* : le développement et la complète caractérisation de contacts Schottky de type n et de type p présentant des barrières sub-0.1 eV.

Intégration de dispositif : l'intégration des contacts Schottky les plus prometteurs, c'est à dire de très faible hauteur de barrière pour les électrons et pour les trous, dans un dispositif à grille métallique nanométrique sur substrat SOI totalement déplété.

Caractérisation : la caractérisation de la technologie Schottky avec la réalisation de circuits logiques élémentaires et de dispositifs MOS optimisés pour la caractérisation hyperfréquence.

## 1.2 INGENIERIE MATERIAU : MODULATION DE HAUTEURS DE BARRIERE PAR SEGREGATION DE DOPANTS

La maîtrise technologique et l'obtention de contacts Schottky présentant une barrière sub-0.1 eV sont une des clés qui permettront aux technologies source/drain Schottky de surpasser les technologies classiques. Pour ce faire, deux phases d'étude se sont succédées : tout d'abord, l'étude de siliciures à faibles hauteurs de barrière (cinétique de réaction, hauteur de barrière) puis le développement de l'approche de ségrégation de dopants à l'interface siliciure/silicium pour moduler la hauteur de barrière.

#### 1.2.1 SILICIURES A FAIBLE HAUTEUR DE BARRIERE.

Comme ce fut le cas pour le siliciure de platine<sup>7</sup>, une première direction fut de mettre en œuvre un siliciure qui possède une hauteur de barrière intrinsèque (pour les électrons et les trous) la plus faible possible. Les siliciures à base de terre rare sont les candidats les plus prometteurs pour le type n alors que le siliciure d'iridium propose une faible hauteur de barrière pour les trous, potentiellement encore plus faible que le siliciure de platine.

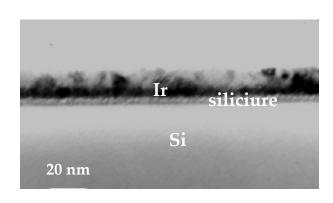

Une étude détaillée<sup>8,9</sup> a été menée sur la complète caractérisation du siliciure d'iridium en termes de stœchiométrie, de cinétique de réaction, de morphologie de couche et de performance électrique. Des analyses de spectrométrie photoélectronique X (XPS) ont permis d'identifier la chimie de réaction de siliciuration. Ces analyses ont pu être complétées par des observations en microscopie électronique en transmission (TEM) pour évaluer la rugosité de l'interface ainsi que l'épaisseur des couches présentes.

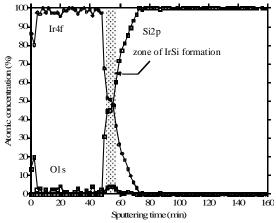

Pour illustrer ce point, la coupe TEM d'un siliciure d'iridium obtenu après recuit rapide à  $300^{\circ}$ C (*Fig. 4*) fait apparaître une couche de 3 nm environ entre le silicium et le métal. L'analyse XPS de cet échantillon (*Fig. 5*) permet d'identifier la phase en question (IrSi). A plus haute température, un deuxième siliciure d'iridium a été mis en évidence et sa stœchiométrie clairement identifiée (IrSi<sub>1.6</sub>). Un modèle basé sur la variation de l'intensité mesurée des spectres d'Ir4f a été utilisé pour obtenir les coefficients cinétiques de réaction de IrSi (E<sub>A</sub>= 2.48 eV, D<sub>0</sub> = 9 cm²/s). Les sections TEM indiquent que la rugosité d'interface de siliciure/silicium augmente avec l'augmentation de la température du recuit de siliciuration. La caractérisation électrique de contacts de siliciure d'iridium a permis de pointer la température de formation offrant la valeur de résistance de contact la plus faible (~ 0.1eV). Néanmoins, le siliciure est extrêmement sensible à l'oxygène rendant son intégration complexe et il n'existe pas de solution chimique capable d'attaquer sélectivement le métal par rapport au siliciure lors d'une intégration de dispositif. Une méthode alternative par attaque plasma a été développée mais n'est pas satisfaisante d'un point de vue d'intégration.

**Fig. 4 :** Section de coupe TEM d'un siliciure d'iridium formé à 300°C par recuit rapide. Un siliciure d'iridium de 3 nm est visible à l'interface Si/Ir.

Fig. 5: Profil d'analyse XPS d'un siliciure d'iridium formé à 300°C par recuit rapide. La phase formée est IrSi.

Pour une implémentation de contacts Schottky de type n, des siliciures à très faible hauteur de barrière pour les électrons sont nécessaires. Les candidats les plus prometteurs sont les siliciures à base de terre rare. Ces matériaux très sensibles à l'oxygène seront utilisés sous condition maîtrisée (recuit sous ultra vide dans une chambre d'évaporation et/ou couche de barrière à la diffusion de l'oxygène). Une chambre de recuit sous ultra vide a été couplée à l'enceinte de dépôt métallique afin de réaliser la siliciuration sous vide secondaire et ainsi préserver l'interface de réaction de

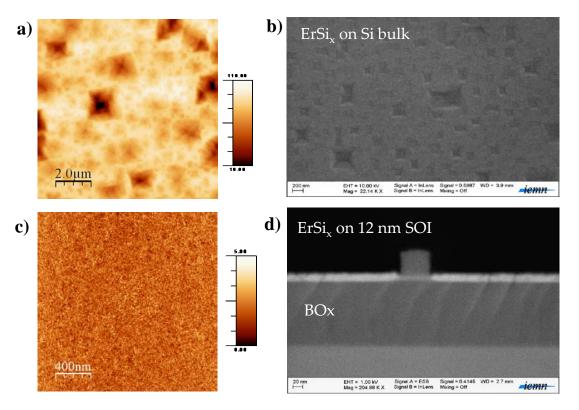

toute contamination d'oxygène. Une étude détaillée sur la formation de siliciure d'erbium et d'ytterbium sous ultra vide<sup>10</sup> a été réalisée couplant des analyses chimiques par diffraction des rayons X (XRD) et XPS à des caractérisations électriques des hauteurs de barrières associées. Les analyses structurales du film de Yb-Si ont montré que le siliciure cristallise à une température supérieure à 400°C pour former une phase YbSi<sub>2-x</sub>. Une hauteur de barrière moyenne pour les électrons de 0.32 eV a été extraite entre 420 et 620 °C avec une valeur minimale de 0.29 eV à 520 °C. Une analyse similaire a été effectuée pour le siliciure d'erbium qui cristallise au-dessus de 380°C pour former une phase ErSi<sub>2-x</sub>. Ce même siliciure, réalisé à 520°C, possède une hauteur de barrière de 0.28 eV. Une caractéristique de la croissance de siliciure de terre rare sur silicium massif est la formation de larges défauts structuraux donnant lieu à des films rugueux et peu homogènes. Une analyse par microscopie à force atomique (AFM) et microscopie électronique à balayage (MEB) d'une couche de siliciure d'erbium sur substrat massif est donnée à titre d'exemple, Fig. 6 a et Fig. 6 b, respectivement. Le mécanisme de formation de trous de forme rectangulaire dont les bords sont orientés suivant les directions [110]/[1-10] est basé sur une nucléation non homogène du siliciure avec une sur-diffusion latérale du silicium<sup>11</sup>. Pour la première fois, il a été démontré que ce phénomène n'existe pas lors de la formation de siliciure sur un substrat SOI ultra fin du fait d'une réserve de silicium limitée<sup>11</sup>. Le film obtenu est homogène et de rugosité très faible (**Fig. 6** c et **Fig. 6** d). Il a été aussi observé que l'intégrité du canal sous la grille était préservée (Fig. 6 d) indiquant que le silicium n'est pas latéralement pompé lors de la réaction de siliciuration. Enfin, un procédé de retrait sélectif original basé sur une solution sans peroxyde a été mis au point<sup>11</sup> en vue de l'intégration de tels contacts dans un dispositif MOSFET.

Fig. 6: a) Image de la topographie de surface par AFM et b) image de la surface par MEB d'une couche de siliciure d'erbium sur substrat massif. c) Image de la topographie de surface par AFM et d) image en coupe d'un même couche de siliciure d'erbium sur substrat SOI.

# 1.2.2 CONCEPT DE MODULATION DE BARRIERE PAR SEGREGATION DE DOPANTS.

#### 1.2.2.1 Vers des hauteurs de barrière sub-0.1eV.

Comme reporté dans la partie introductive, des approches de modélisation ont établi que la hauteur de la barrière ne doit pas dépasser 0.1 eV afin de positionner l'architecture SB-MOSFET avantageusement par rapport à une technologie conventionnelle<sup>6</sup>. Pour atteindre cet objectif, plusieurs techniques ont été proposées pour défaire le verrouillage du niveau de Fermi qui régit la hauteur de la barrière. Une première approche est basée sur la reconstruction de la surface (100) de semiconducteurs grâce à des passivations à base de monocouche de sélénium<sup>12</sup>. Une autre approche propose de bloquer la formation d'états induits par le métal dans le gap (Metal-Induced Gap States MIGS), qui sont invoqués comme à l'origine du verrouillage du niveau de Fermi, en intercalant un isolant ultra-mince entre le métal et le silicium<sup>6</sup>. Bien que l'efficacité de ces méthodes ait été partiellement démontrée sur des structures de test, leur implémentation dans un procédé MOSFET auto-alignée reste un exercice

difficile. Plus récemment, en utilisant le concept de ségrégation de dopant, il a été démontré qu'une accumulation de dopant à l'interface métal / semi-conducteur pouvait induire une réduction de hauteur de barrière Schottky via un budget thermique réduit 13,14.

### 1.2.2.2 Mécanismes d'injection et implémentation.

Le mécanisme en question, appelé ségrégation de dopants, consiste à implanter des dopants puis les faire diffuser jusqu'à l'interface par une activation thermique à faible budget thermique. Parce que ce dernier est relativement limité, la diffusion en profondeur des dopants est circoncise atténuant les problèmes associés à la formation de jonctions ultra-minces. Une barrière Schottky fait référence à un contact métal/semiconducteur où la barrière de potentiel à leur interface peut être représentée par un diagramme de bande d'énergie schématisé **Fig.** 7a. Pour être injecté du métal vers le semi-conducteur, un porteur peut traverser à travers la barrière par effet de champ ou sauter au-dessus de cette barrière par émission thermoélectronique. Le rôle de la ségrégation de dopants à l'interface siliciure/silicium est d'améliorer l'injection de porteurs.

Fig. 7: Représentation schématique de la courbure de bande au voisinage de l'interface métal/silicium sans (gauche) et avec (droite) ségrégation de dopant.

Il est généralement admis que la couche de dopants dans le silicium forme un dipôle avec une charge d'image de signe opposé du côté métallique. Le mécanisme physique exact régissant cette approche de dipôle est encore sujet à débat. Bien que la ségrégation de dopant soit généralement conduite à une température relativement basse, on peut supposer qu'une fraction de dopants soit néanmoins incorporée dans des sites substitutionnel de silicium et deviennent actifs. Basé sur des principes premiers de calculs (ab initio) <sup>15</sup>, d'autres approches théoriques suggèrent que des dopants sur des sites de substitutionnel de silicium induisent des dipôles locaux qui modifient l'amplitude de la hauteur de barrière Schottky. Dans tous les cas, l'électrostatique résultant du dipôle induit de cette ségrégation de dopant est censée dominer le verrouillage du niveau de Fermi <sup>16</sup> et modifier localement la courbure de bande (**Fig. 7**)

b). En conséquence, il constitue un levier efficace pour moduler à la fois la hauteur et la largeur de barrière Schottky. La barrière alors amincie favorise l'injection tunnel alors que l'abaissement de barrière améliore l'injection thermoélectronique.

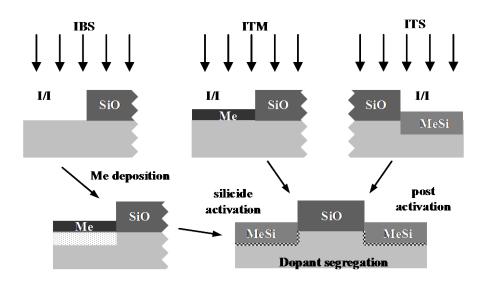

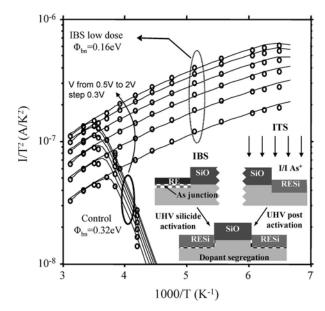

Une jonction à ségrégation de dopants peut être fabriquée suivant trois modes de réalisation, décrits **Fig. 8**: i) implantation dans le silicium suivie par le dépôt de métal et le recuit de siliciuration, appelée implantation avant le siliciure (*implantation-before-silicide: IBS*), ii) implantation dans le métal (*implantation-through-metal: ITM*) suivie de la siliciuration et finalement iii) implantation dans le siliciure (*implantation-through-silicide: ITS*) suivie d'une étape d'activation à basse température. Suivant les deux premières techniques, les impuretés implantées diffusent et ségrégent simultanément avec la formation du siliciure alors que dans le troisième mode de réalisation, les éléments ségrégent lors d'une seconde étape de recuit, après la formation du siliciure. L'avantage potentiel de ces deux dernières techniques est l'absence de génération de défauts dans le silicium lors de l'implantation car les dopants sont confinés dans le siliciure ou le métal. La région proche de la jonction est donc sans défauts cristallins laissant présager de faible courant de fuite.

Fig. 8: Illustration schématique des trois modes de réalisation de jonctions à ségrégation de dopants: i) implantation dans le silicium suivie par le dépôt de métal et le recuit de siliciuration, appelé implantation avant le siliciure (implantation-before-silicide: IBS), ii) implantation dans le métal (implantation-through-metal: ITM) suivie de la siliciuration et finalement iii) implantation dans le siliciure (implantation-through-silicide: ITS) suivie d'une étape d'activation à basse température.

#### 1.2.2.3 Première approche de ségrégation de dopant.

Tout d'abord, R. Thornton en 1981 introduit le concept de ségrégation de dopant<sup>17</sup>, avec une approche d'implantation avant siliciuration (IBS). En utilisant une

couche mince interfaciale de type p, il a démontré une élévation de la hauteur de la barrière sur contacts Schottky en PtSi sur silicium de type n. La couche de type p est formée par implantation ionique de faible profondeur, suivie d'une accumulation à l'interface métal-silicium lorsque le siliciure est formé. Ensuite, Horiuchi et Yamaguchi ont proposé d'implanter directement dans un métal réfractaire (Ti, W ou Pd) et d'induire la ségrégation au cours de l'étape de siliciuration<sup>18</sup>. Nagasawa a essayé la même approche en utilisant du molybdène <sup>19</sup>. Le concept de diffusion de dopant dans le siliciure a été introduit par Shone et al. en 1985 <sup>20</sup>, où les dopants ont été implantés dans du siliciure de tungstène (WSi<sub>2</sub>) et puis ségrégés par une étape de recuit. La diffusion après implantation dans le métal et le siliciure a également été étudiée en utilisant CoSi<sub>2</sub> <sup>21</sup> ou PtSi<sup>13</sup>.

### 1.2.3 SEGREGATION DE DOPANTS SUR DES CONTACTS DE TYPE P.

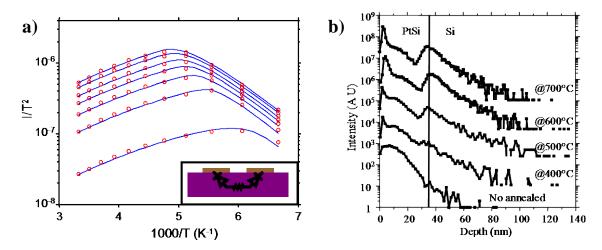

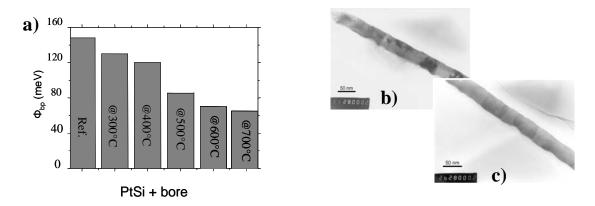

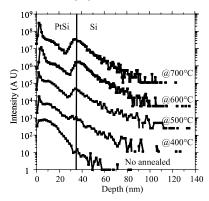

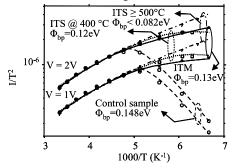

L'association de dopants de type p (accepteurs) à des siliciures à faible hauteur de barrière pour les trous (PtSi par exemple) apparaît comme une approche naturelle et physiquement crédible. Les conditions d'implantation ont été optimisées par simulation Monte Carlo (TRIM<sup>22</sup>) puis validées par analyses Spectrométrie de Masse d'Ions Secondaires (Secondary Ion Mass Spectrometry, SIMS). Par exemple, une implantation de BF<sub>2</sub><sup>+</sup> à 20kV avec une dose de 10<sup>15</sup> cm<sup>-3</sup> permet le confinement de la majorité des dopants dans un film de 40 nm de PtSi. Les échantillons ont été caractérisés par SIMS afin d'identifier la ségrégation des dopants à l'interface siliciure/silicium. L'impact du procédé sur la hauteur de barrière a ensuite été analysé en utilisant une structure de test électrique inédite (encart Fig. 9a) composée de deux contacts Schottky identiques séparés par gap de silicium micrométrique. Les caractéristiques I(V) en fonction de la température (Fig. 9a) peuvent être corrélées à un modèle électrique prenant en compte l'injection thermoélectronique et par effet de champ<sup>23</sup>. Il est ainsi possible d'extraire la valeur de la hauteur de barrière (ie.  $\Phi_{bp}$ =0.15 eV pour un contact PtSi classique). Les **Fig.** 9b et Fig. 10a présentent le profil SIMS et la hauteur de barrière associée d'un contact PtSi obtenu après implantation dans le siliciure et activé par différents budgets thermiques. Il apparaît clairement que dès 400°C, une ségrégation de dopant est visible avec un impact plus significatif sur la hauteur de barrière ( $\Phi_{bp}$ =0.12 eV). La diffusion du bore dans le siliciure est nettement plus grande que dans le silicium ce qui permet une diffusion rapide des dopants dans le siliciure jusqu'à l'interface siliciure/silicium où intervient une accumulation de dopants, même à température modérée. Un recuit postimplantation à 500°C pendant 5 min entraîne une ségrégation de dopants à l'interface encore plus nette<sup>24</sup> avec une hauteur de barrière associée inférieure à la valeur cible de 0.1 eV. Des coupes TEM, réalisées sur ces échantillons (Fig. 10 b-c), n'ont pas révélé d'évolutions notables de la morphologie de la couche de siliciure après implantation et traitement thermique. L'épaisseur de la couche (38 nm), la rugosité de l'interface et la

taille des grains restent inchangées. La deuxième approche investiguée, implantation dans le métal (ITM), est moins prometteuse car ce schéma semble provoquer une exo diffusion très importante des dopants en dehors du contact entraînant une perte de dose conséquente (75%). La ségrégation de dopant est alors très minime et l'impact sur la hauteur de barrière reste modéré ( $\Phi_{bp}$ =0.13 eV).

Fig. 9: a) Caractéristiques I(V) en fonction de la température (tracé d'Arrhénius) sur des contacts de PtSi. Les mesures expérimentales (rouge) peuvent être corrélées à un modèle électrique (bleu) prenant en compte l'injection thermo-electronique et par effet de champ (avec Φ<sub>bp</sub>= 0.15 eV). En encart, la structure de test électrique composée de deux contacts Schottky identiques séparés par un gap de silicium. b) Profil SIMS d'un contact de PtSi obtenu par ITS - implantation de BF<sub>2+</sub> dans 35 nm PtSi puis activation thermique pendant 5 min à différentes températures.

Fig. 10: a) Variation de la hauteur de barrière Schottky fonction de la température d'activation ITS. Sections de coupe TEM d'un siliciure de platine (b) et d'un même siliciure après ITS (c) avec une activation thermique à 500°C, 5 min. Aucun changement de morphologie n'est à noter.

#### 1.2.4 SEGREGATION DE DOPANTS SUR DES CONTACTS DE TYPE N.

De la même manière que pour le type p, l'association de dopants de type n (donneurs) à des siliciures à faibles hauteurs de barrière pour les électrons (ErSi<sub>1.7</sub>, YbSi<sub>1.8</sub>

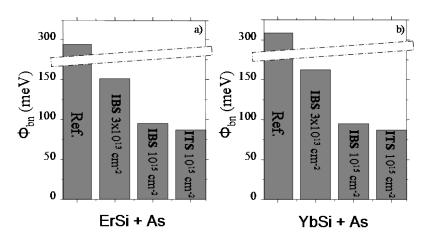

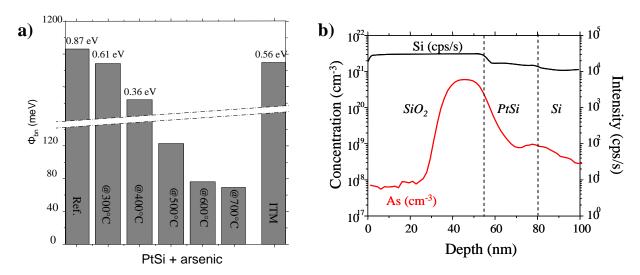

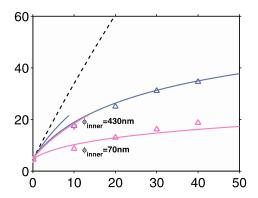

par ex.) apparaît comme une approche naturelle. La ségrégation de dopants sur des siliciures à base de terre rare n'avait, jusqu'alors, jamais été évaluée. Afin de tenir compte des spécificités de la formation de ces siliciures (sensibilité à l'oxygène), l'implantation a été réalisée avant la formation du siliciure (IBS) ou dans le siliciure (ITS) puis activée dans une chambre sous ultra vide. La Fig. 11, présente un résumé des hauteurs de barrière pour les électrons extraites sur des contacts en ErSi<sub>x</sub> (Fig. 11a) et YbSix (Fig. 11b) avec une ségrégation d'arsenic. A titre de comparaison, la hauteur de barrière extraite sur un contact non ségrégé est de 0.28 eV et 0.32 eV pour ErSix et YbSix, respectivement. Les effets de la ségrégation de dopants sur la hauteur de barrière semblent être indépendants du matériau considéré puisque la même tendance est observée avec un contact à base d'erbium ou ytterbium. Même avec une faible dose (3x10<sup>13</sup> cm<sup>-2</sup>), une ségrégation d'arsenic obtenue par IBS entraîne une réduction de barrière de plus de 50% et l'utilisation d'une dose plus élevée (1015 cm-2) permet d'abaisser la barrière sous la barre des 0.1eV. Enfin, l'approche ITS avec une dose d'As de 10<sup>15</sup> cm<sup>-2</sup> et un recuit d'activation de 500°C sous UHV permet d'abaisser la barrière sous 80 meV.

Fig. 11 : Résumé des hauteurs de barrière pour les électrons extraites sur des contacts en a) ErSix et b)

YbSix avec une ségrégation d'arsenic

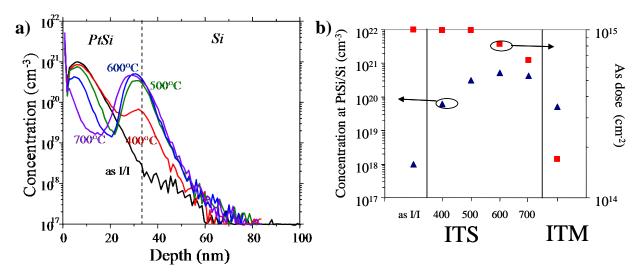

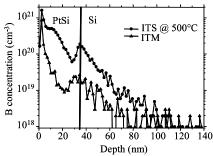

Comme nous venons de le voir, l'association de dopants de type donneurs avec un siliciure bord de bande de conduction (e.g. ErSi<sub>1.7</sub>, YbSi<sub>1.8</sub>) est combinaison évidente. Néanmoins, la formation de siliciure à base de terre rare est très délicate avec une très grande sensibilité avec l'oxygène, une grande réactivité avec les diélectriques et une mauvaise stabilité en température. Par opposition, le siliciure de platine, PtSi, est un alliage beaucoup plus stable et qui possède naturellement une faible barrière Schottky pour les trous (proche de la bande de valence). Alors, PtSi semble, en principe, être un médiocre candidat pour produire une très faible barrière Schottky aux électrons. Néanmoins, l'association de PtSi avec des dopants de type donneurs s'est révélée être particulièrement pertinente. La **Fig.12**a présente les profils d'arsenic obtenus sur des

échantillons ITS. Après implantation, le pic d'arsenic est situé dans la partie haute du film de siliciure et la quasi-totalité de la dose est confinée dans le siliciure. La ségrégation est activée par des recuits rapides pour des températures variant de 400°C à 700°C. A 400°C, l'As diffuse dans la couche et commence à s'accumuler à l'interface PtSi/Si. A 500°C, la ségrégation de dopant est visible et c'est d'autant plus vrai pour des températures supérieures mais sans un effet exponentiel. La Fig.12b propose l'évolution de la concentration As à l'interface PtSi/Si et de la dose totale dans les différents échantillons. Un recuit d'activation, même à température modérée (400°C) entraîne une augmentation drastique du pic d'arsenic à l'interface siliciure/silicium, passant de 1x10<sup>18</sup> cm<sup>-3</sup> sans activation à 6x10<sup>19</sup> cm<sup>-3</sup> à 400°C pour enfin saturer autour de 4x10<sup>20</sup> cm<sup>-3</sup> à partir de 500°C. La dose totale implantée reste totalement dans l'échantillon pour des recuits jusqu'à 500°C puis pour des températures plus élevées, une faible perte de dose est observée due à une exo diffusion des dopants vers la surface du siliciure accentuée par la température. Comme prévu, une large hauteur de barrière aux électrons de 0.87 eV est mesurée sur un contact de PtSi sans ségrégation (Fig. 13 a). L'impact de l'accumulation de dopants à l'interface PtSi/Si sur la hauteur de barrière du contact est très significatif. Alors qu'une température d'activation de 300°C offre une hauteur de barrière de 0.61 eV, une augmentation de la température de recuit de 100°C permet une réduction de la hauteur de barrière de 50% de plus. Enfin, cette barrière chute en dessous de 80 meV pour une activation à 600°C et 70 meV pour une activation à 700°C.

Fig.12: a) Profil SIMS d'un contact de PtSi obtenu par ITS - implantation de As+ dans 35 nm PtSi puis activation thermique pendant 5 min à différentes températures. b) Evolution de la concentration As à l'interface PtSi/Si et de la dose totale dans l'échantillon pour un procédé ITS (fonction de la température d'activation) et un procédé ITM.

Concernant l'approche ITM, il a été relevé une perte de dose extrêmement élevée (86%) correspondant à une dose restante dans l'échantillon de 1.4x10<sup>14</sup> cm<sup>-2</sup>.

L'accumulation de dopants à l'interface siliciure / silicium est alors bien moins prononcée que dans l'approche ITS, ce qui induit une réduction modérée de la hauteur de barrière (0.67 eV). Ce phénomène a déjà été observé pour la ségrégation de bore avec une perte de dose similaire (75%).

Fig. 13: a) Variation de la hauteur de barrière Schottky fonction de la température d'activation ITS. b)

Profil SIMS d'un contact de PtSi obtenu par ITM - implantation de As+ dans le Pt avec une

encapsulation d'oxyde.

Dans l'approche ITM, les mécanismes de diffusion sont bien plus complexes que dans le cas de l'ITS. Lors de la réaction de siliciuration, le platine, le silicium et l'arsenic peuvent diffuser en même temps. Comme les dopants sont la plus petite espèce mise en jeu, le front de siliciuration semble diriger le mécanisme d'accumulation. Lors de la siliciuration du platine, la première réaction est une diffusion du Pt dans le Si pour former le composé intermédiaire Pt2Si, alors que dans la seconde réaction, Si diffuse dans le Pt2Si pour former le composé stable PtSi. Ces deux réactions sont connues pour se produire successivement<sup>7</sup>: la réaction (1) nécessite la complète consommation de la couche de platine initiale avant que la réaction (2) ne débute. Lors de la seconde réaction, le front de siliciuration commence de l'interface siliciure/silicium pour finir à la surface supérieure du contact. Il est suggéré que le front de réaction entraîne les impuretés à la surface supérieure puis les repousse en dehors du contact. Ce type de mécanisme n'est pas lié à une diffusion conventionnelle gouvernée par la température puisque dans l'approche ITS, même à haute température, la quasi-totalité de la dose est toujours présente dans le contact. Pour valider ces hypothèses, un empilement inédit faisant intervenir l'approche ITM a été analysé par SIMS (Fig. 13 b). Après dépôt de Pt et implantation As, 50 nm de SiO2 a été déposé afin d'encapsuler le métal. La siliciuration est alors effectuée comme dans les précédents exemples. Comme spéculé, une grande

majorité de dopants sont poussés hors de la couche de PtSi et se retrouvent prisonniers dans la couche de protection en oxyde.

Ainsi, ces expérimentations démontrent la possibilité de la modulation de hauteur de barrière Schottky sous la barre des 0.1eV pour les trous et les électrons grâce à une ségrégation de dopant à faible budget thermique.

# 1.3 INTEGRATION DE CONTACTS METALLIQUES A L'ECHELLE DE DISPOSITIFS :

# 1.3.1 DEVELOPPEMENT D'UN PROCEDE DE TRANSISTOR A GRILLE METALLIQUE NANOMETRIQUE SUR SUBSTRAT SOI.

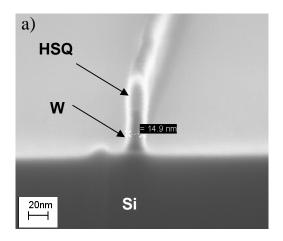

Une attention particulière a été portée sur le développement du module de grille pour améliorer la reproductibilité de cette étape tout en diminuant encore les dimensions afin de réaliser une grille métallique de longueur inférieure à 20 nm sur substrat SOI. Un travail certain a été entrepris sur les différentes étapes du module de grille (gravure, dépôt, lithographie permettant la définition de la grille). Le choix du métal de grille (tungstène) permet de travailler avec une tension de seuil particulièrement bien adaptée pour des dispositifs n-MOS et p-MOS avancés et de ne pas être limité par les températures des traitements thermiques. Un oxyde de grille (SiO<sub>2</sub>) inférieur à 2 nm offre des courants de fuites qui ne détériorent pas le fonctionnement du transistor. Une résine électronique négative (HSQ) permet de réaliser des lignes de haute définition afin d'être utilisée comme masque de gravure. L'optimisation de cette étape, avec notamment une correction des effets de proximité qui intègrent les effets des électrons directs et retro-diffusés, a permis l'obtention d'une dose optimale pour un large panel de dimension de grille (de 15 nm à 5 µm). Un exemple de résultat obtenu après gravure du tungstène est présenté Fig. 14a avec la réalisation d'une grille de tungstène de 14 nm de large pour une hauteur de 70 nm. Les choix judicieux des gaz de gravure (SF<sub>6</sub>/N<sub>2</sub>)<sup>25</sup> et des paramètres de l'attaque plasma RIE (faible pression, puissance modérée) assurent l'obtention de profils de grille verticaux et d'une fin d'attaque parfaitement maîtrisée. L'utilisation d'un nitrure PECVD forme, après gravure anisotrope, des espaceurs ultra minces (10 nm) sans dégrader le métal de grille (**Fig. 14**b). Le procédé d'encapsulation du tungstène assure une parfaite protection contre les gravures chimiques.

Fig. 14 : Coupe MEB a) d'une grille de transistor en tungstène de 14 nm de large et b) d'une grille de transistor en tungstène de 14 nm de large, encapsulée par deux espaceurs de nitrure de largeur inférieure à 10 nm.

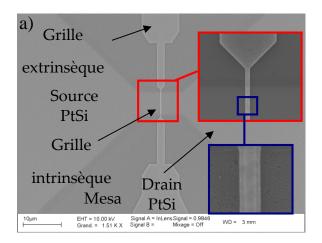

Pour obtenir une complète évaluation de l'architecture source/drain Schottky, des dispositifs optimisés pour des caractérisations statiques et radio fréquences ont été développés. Des transistors de longueurs de grille (Lg) variant de 15 nm à 5 μm avec des largeurs de grille (W) de 10 μm à 100 nm sont réalisés (**Fig. 15**a) afin d'évaluer les différents contacts développés dans l'étude matériau puis de positionner les performances statiques des dispositifs par rapport à l'état de l'art (Ion, Ioff, pente sous le seuil, effet canaux court DIBL, transconductance ...).

D'autre part, une des caractéristiques d'intérêt de ce type de dispositif est liée au nonsource/drain par la grille et de des zones métal/semiconducteur abrupte. Cette configuration lui offre un avantage substantiel<sup>26</sup> sur la minimisation des capacités de recouvrement, en particulier sur la capacité grilledrain (capacité Miller) qui impacte fortement les performances en fréquence maximum d'oscillation. De plus, l'interface siliciure/Si atomiquement abrupte permet d'optimiser les résistances d'accès. Des structures optimisées du point de vue hyperfréquence ont été développées afin de démontrer l'avantage de l'architecture source/drain Schottky. Il existe un large choix de structures RF à largeur et longueur de grille variable, à source ou grille commune. Dans un premier temps, une technologie à deux niveaux de métal est développée (métal 1 : grille tungstène et S/D siliciure, métal 2 : plot d'épaississement Ti/Al pour contact avec des pointes coplanaires RF). Dans cette configuration, un maximum de deux doigts de grille peut être mis en parallèle (Fig. 15b). Enfin, des structures isolées sont disponibles afin de faciliter l'extraction des paramètres hyperfréquence des dispositifs.

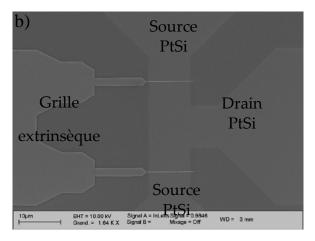

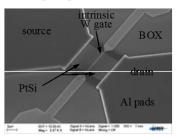

Fig. 15: Image MEB a) d'un transistor MOSFET à barrière Schottky de longueur de grille intrinsèque de 50 nm sur substrat SOI fin (10nm). b) d'un transistor MOSFET à barrière Schottky à deux doigts de grille en parallèle optimisé pour la caractérisation hyperfréquence (Lg = 40 nm, W = 10 μm).

# 1.3.2 DEVELOPPEMENT DE TRANSISTOR P-MOSFET A SOURCE/DRAIN METALLIQUES.

### 1.3.2.1 Intégration de siliciure bord de bande de valence

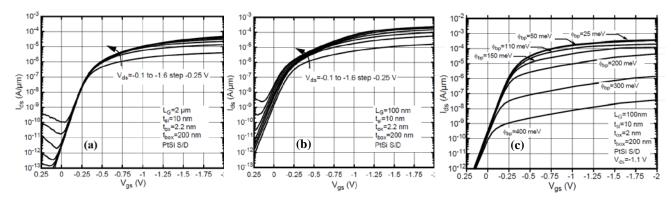

Premièrement, des transistors sur SOI faiblement dopés ont été réalisés avec des contacts source/drain en siliciure de platine. La Fig. 16 propose deux exemples de caractéristiques de transfert mesurés sur un canal long (1000nm) et sur un canal court (100 nm). Les performances obtenues en termes de courant de commande ainsi que de contrôle des effets canaux courts se sont positionnées favorablement par rapport à l'état de l'art de composants source/drain métalliques de type p<sup>27</sup>. Néanmoins, il apparaît clairement que le courant est affecté par la hauteur de barrière Schottky avec un aplatissement visible sur la caractéristique de transfert en régime de faible accumulation  $(V_g \sim -0.5V)$  ce qui dégrade le courant de commande. Cet effet est perceptible pour un canal long et devient prépondérant lorsque la longueur de grille devient faible (diminution de la résistance du canal). Une explication possible est le passage d'une conduction contrôlée par le canal à une conduction tunnel contrôlée par le contact, expliquant le changement de pente quand une condition de bande plate se produit à la jonction de source / canal. Ce point de vue est correct dans la limite où la hauteur de barrière n'est pas suffisamment faible (Fig. 16c). Alors, l'amélioration des performances de ces dispositifs passe par un travail sur la réduction de la hauteur de barrière Schottky.

Fig. 16: Caractéristiques de transfert I<sub>ds</sub>-V<sub>gs</sub> mesurées sur deux transistors SB-MOSFET de type p avec S/D en PtSi de longueur de grille de a) 1000 nm et de b) 100 nm. c) Caractéristiques de transfert I<sub>ds</sub>-V<sub>gs</sub> simulées de SB-MOSFET à Vd=-1.1V pour un dispositif de 100nm de longueur de grille. Les simulations incluent différentes hauteurs de barrières (25, 50, 110, 150, 200, 300, and 400 meV).

### 1.3.2.2 Influence du dopage du canal.

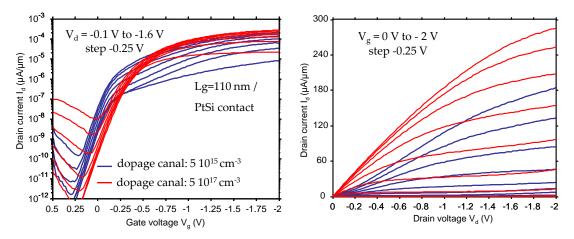

Il a été démontré qu'une augmentation modérée du dopage d'un substrat de silicium de type p permettait de réduire la hauteur de barrière d'un contact de PtSi en dessous de  $0.1 \, \text{eV}^{28}$  grâce à une courbure de bande (force image) induite par les dopants de type p au voisinage de l'interface siliciure/silicium. L'intégration de PtSi p-MOSFETs sur un substrat SOI modérément dopé ( $5 \times 10^{17} \, \text{cm}^{-3}$ ) a résulté d'une augmentation de courant de commande de 60% pour un canal de 110 nm (**Fig. 17**). L'aplatissement de la caractéristique  $I_d$ - $V_g$  n'est alors plus perceptible et la résistance de contact S/D ne limite plus le courant. Le niveau de dopage est suffisamment faible pour ne pas affecter la mobilité des porteurs dans le canal ni pour dégrader l'immunité contre les effets canaux courts<sup>28</sup>. Le champ électrostatique développé par la grille permet de dépléter le canal lorsque le transistor est à l'état bloqué.

Fig. 17: Comparaison de caractéristiques Ids-Vos et Ids-Vos mesurées sur des SB-MOSFETs type p de longueur de grille de 110 nm avec des contacts S/D en PtSi sur un canal SOI faiblement et modérément dopé.

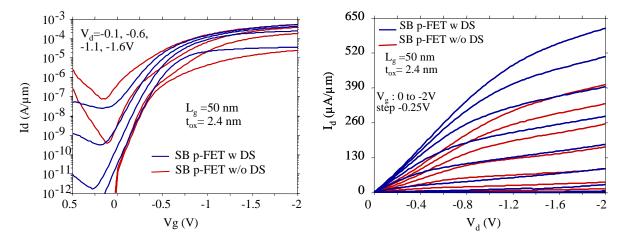

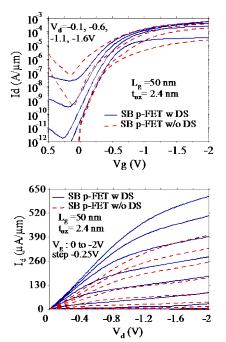

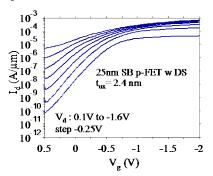

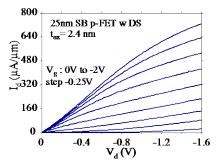

L'intégration du siliciure de platine associée à une ségrégation de bore par implantation dans le siliciure (ITS) s'est révélée être la plus efficace pour réduire la hauteur de barrière Schottky. Des transistors avec des longueurs de grille jusqu'à 25 nm ont été ainsi fabriqués et caractérisés. Des caractéristiques Id-Vg et Id-Vd d'un transistor de 50 nm de long avec ou sans ségrégation de dopant sont présentées en Fig. 19. L'amélioration drastique en terme de courant de commande est attribuée à la réduction de barrière Schottky induite par l'accumulation de bore à l'interface du contact. Sur le dispositif sans ségrégation, on retrouve l'aplatissement des courbes Id-Vg proche de la tension de seuil, signature d'une limitation du courant par la barrière Schottky. Cet effet est supprimé avec les jonctions ségrégées. Un nouvel état de l'art en terme de performance de courant de commande a été établi avec une longueur de grille de 25  $nm^{24}$ : 814  $\mu A/\mu m$  à  $V_g$ =-2V/ $V_d$ =-2V et 682  $\mu A/\mu m$  à  $V_g$ =-2V/  $V_d$ =-1.6V. En considérant une tension d'alimentation de 1.1 V, un Ion de 530 μA/μm à Vg=-2V/Vd=-1.1V avec un oxyde de grille de 2.5 nm peut être raisonnablement considéré comme une figure représentative d'un courant de commande à V<sub>g</sub>= V<sub>d</sub>=-1.1V avec un oxyde d'épaisseur équivalente de ~1.2 nm. Bien qu'il soit encore trop tôt pour conclure définitivement sur la miniaturisation de la technique de ségrégation de dopant, ces derniers résultats donnent une première série de preuves qui supportent son utilisation potentielle dans des dispositifs ultimes (< 25 nm).

Fig. 18: Comparaison de caractéristiques Ids-Vds et Ids-Vds mesurées sur des SB-MOSFETs type p de longueur de grille de 50 nm avec des contacts S/D en PtSi avec ou sans ségrégation de bore par ITS.

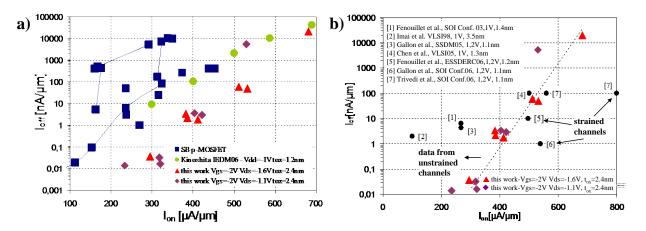

Enfin, une comparaison de l'état de l'art (**Fig. 19**a) des transistors p-MOSFET à source/drain métalliques, incluant les dispositifs à ségrégation de dopants, place les performances présentées très favorablement. **Fig. 19**b démontre aussi que ces jonctions métalliques se positionnent parmi les meilleures performances obtenues sur des p-FETs en technologie SOI, comparaison faite sur des publications de mêmes générations. En

considérant que la ligne tirée est représentative des meilleures performances réalisables sans introduction d'ingénierie de contraintes, il peut être raisonnablement conclu que le courant est limité par la résistance du canal et non par celle des zones source/drain.

Fig. 19: a) Compilation des meilleures performances Ion/Ioff de transistors MOS à source/drain Schottky de type p avec les résultats obtenus au cours de ces travaux. b) Compilation des meilleures performances Ion/Ioff de transistors MOS conventionnels de type p sur substrat SOI publié jusqu'alors avec les résultats obtenus au cours de ces travaux.

# 1.3.3 DEVELOPPEMENT DE TRANSISTOR N-MOSFET A SOURCE/DRAIN METALLIQUES.

### 1.3.3.1 Intégration de siliciures bord de bande de conduction.

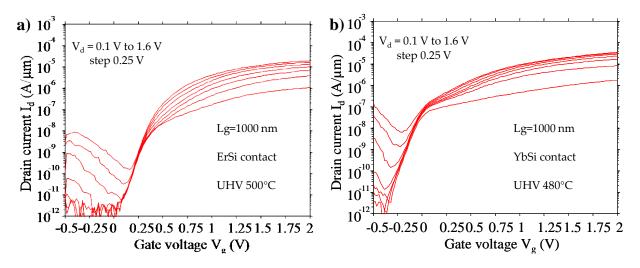

Suivant la même approche que pour les dispositifs de type p, les contacts à base de terre rare, étudiés et optimisés d'un point de vue matériau, ont été implémentés à l'échelle du dispositif. L'intégration de siliciure de terre rare à base d'erbium (**Fig. 20**a) et d'ytterbium (**Fig. 20**b) sur des dispositifs nFET sur substrat SOI ultra fin a été démontrée. Dans les deux cas, pour un dispositif à canal long, la signature d'une hauteur de barrière Schottky excessive (~ 0.3 eV) est perceptible sur les caractéristiques  $I_d$ - $V_g$  limitant sévèrement les courants de commande (de l'ordre de la dizaine de  $\mu$ A/ $\mu$ m). Ce phénomène sera d'autant plus marqué que la longueur de grille du dispositif sera réduite, rendant l'implémentation de tels contacts pour des futures générations de dispositifs très compromise.

Fig. 20: Caractéristique de transfert  $I_{ds}$ - $V_{gs}$  mesurée sur un transistor SB-MOSFET de type n de longueur de grille de 1000 nm avec S/D(a) en ErSi et (b) YbSi.

#### 1.3.3.2 Intégration de contact à base de terre rare avec ségrégation de dopants.

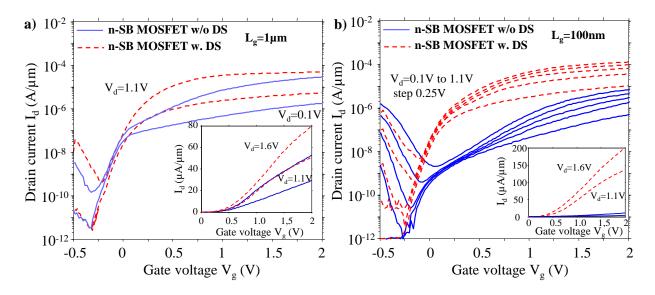

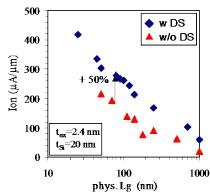

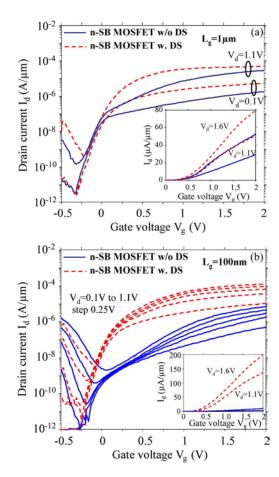

Présentée dans l'étude matériau, une solution pour intégrer un siliciure de terre rare avec une hauteur de barrière inférieure à  $0.2 \, \text{eV}$  est d'introduire à l'interface siliciure/silicium une ségrégation de dopant d'arsenic. Les **Fig. 21** comparent les caractéristiques statiques ( $I_d$ – $V_g$ ) de transistors avec des contacts S/D en YbSi<sub>1.8</sub> avec ségrégation d'arsenic et des transistors similaires sans ségrégation de dopant (échantillon de contrôle) pour des longueurs de grille de 1  $\mu$ m (**Fig. 21**a) et de 100 nm (**Fig. 21**b).

D'un point de vue qualitatif, alors que le transistor de contrôle en YbSi présente un aplatissement sensible des caractéristiques  $I_{ds}$ - $V_{gs}$  à la transition entre les régimes sous le seuil et faible-accumulation (0 < $V_g$  <0.5), une telle limitation n'est pas observée pour des jonctions S / D Schottky ségrégées en raison de la réduction drastique SBH. L'avantage en termes de courant de commande est dévoilé par la caractéristique  $I_{ds}$ - $V_{gs}$  en échelle linéaire (encart **Fig. 21**a) qui révèle une amélioration de 50% pour le dispositif de 1 µm de long. L'avantage est encore mieux illustré dans le cas du dispositif 100-nm de longueur de grille (encart **Fig. 21**b), où une plus faible résistance de canal exacerbe les limitations de performance provenant des extensions S / D. Le transistor à S/D métallique avec ségrégation d'As possède un courant de commande  $I_{on}$  = 252 µA / µm à  $V_{gs}$  =  $V_{ds}$  = 2 V qui représente une amélioration de plus de 10 × par rapport au dispositif de contrôle.

Ainsi, l'association de dopants de type donneurs avec un siliciure bord de bande de conduction (e.g. ErSi<sub>1.7</sub>, YbSi<sub>1.8</sub>) apparaît comme une solution naturelle. Néanmoins, la formation de siliciure à base de terre rare est très délicate avec une très grande

sensibilité avec l'oxygène, une grande réactivité avec les diélectriques et une mauvaise stabilité en température ce qui pourrait être un frein à leur développement à grande échelle.

Fig. 21: Caractéristiques de transfert  $I_{ds}$ - $V_{gs}$  mesurées sur deux transistors SB-MOSFET de type n avec S/D en YbSi avec ségrégation d'arsenic par IBS réalisé sous UHV 520°C de longueur de grille de a) 1000 nm et b) 100nm.

### 1.3.3.3 Intégration de contact à base de PtSi avec ségrégation d'arsenic.

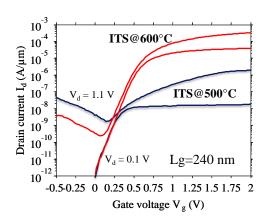

Par opposition, PtSi est un siliciure beaucoup plus stable mais possède naturellement une faible barrière Schottky pour les trous (proche de la bande de valence). Alors, PtSi semble, en théorie, être un médiocre candidat pour produire une très faible barrière Schottky aux électrons, l'implémentation d'une ségrégation d'arsenic peut drastiquement améliorer la situation (cf. **Fig. 13**a). De tels contacts ont été implémentés sur des transistors nFETs sur un substrat SOI ultrafin (~12nm). **Fig. 22** montre qu'une étape d'activation faite à 500°C n'est pas suffisante pour permettre un abaissement de barrière significatif induisant une caractéristique statique ambipolaire. Le courant de commande, fortement limité par la hauteur de barrière excessive, est relativement faible (~4  $\mu$ A/ $\mu$ m @ V<sub>DD</sub>=2V). Par contre, lorsque cette étape d'activation est réalisée à 600°C, la hauteur de barrière est maintenant abaissée sous la valeur cible de 0.1 eV offrant une caractéristique statique quasi-parfaite. Le courant n'est plus limité par la résistance de contact et propose un Ion de 286  $\mu$ A/ $\mu$ m at V<sub>g</sub>=V<sub>d</sub>=2V, mesuré directement sur le siliciure avant l'étape de plot de contact.

Fig. 22: Caractéristiques de transfert  $I_{ds}$ - $V_{gs}$  mesurées sur deux transistors SB-MOSFET de type n avec S/D en PtSi de longueur de grille de 240 nm avec ségrégation d'arsenic par ITS activé à 500°C et 600°C.

En se basant sur ces résultats, un procédé complet a été réalisé avec des dispositifs dont la longueur de grille est miniaturisée jusqu'à 70 nm. L'étape d'activation est choisie à 600°C et la réalisation des plots d'épaississement permet une diminution significative des résistances d'accès. A titre d'exemple, un transistor de 240 nm de long possède un courant à l'état passant de 461  $\mu$ A/ $\mu$ m à V<sub>g</sub>=2V / V<sub>d</sub>=1.6V et 410  $\mu$ A/ $\mu$ m à V<sub>g</sub>=2V / V<sub>d</sub>=1.1V avec un courant de fuite de 110 nA/ $\mu$ m à V<sub>d</sub>=1.6V et 35 nA/ $\mu$ m à V<sub>d</sub>=1.1V. La pente sous le seuil et le DIBL sont de 83 mV/dec et 49 mV/V, respectivement.

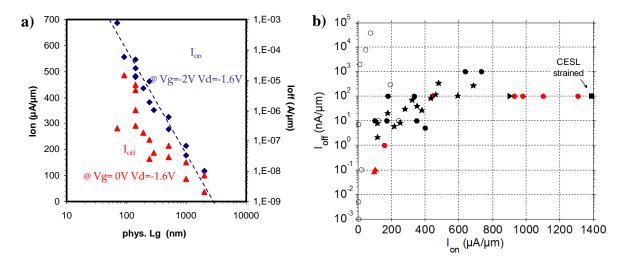

La Fig. 23a propose l'évolution du maximum de courant de commande et du courant de fuite en fonction de la longueur de grille. Ion suit la règle conventionnelle en 1/Lc, indiquant que les résistances S/D n'exercent pas de limitation excessive sur le courant. Une valeur moyenne de Ion à Lg=100 nm est de 580 μA/μm pour Vd=1.6V et Vg=2V, ce qui correspond à 16% de mieux en comparaison avec un pMOSFET utilisant une ségrégation de dopant de bore (Ion=490 μA/μm). Dans les deux cas, la résistance du canal domine la résistance totale et le courant n'est pas limité par la résistance de contact. Alors, la différence de courant de commande provient, en grande part, d'une mobilité supérieure des électrons par rapport aux trous entraînant une résistance de canal pour le nMOS légèrement plus faible que pour le pMOS. Le courant de fuite augmente avec la diminution de la longueur de grille, tout en restant dans une gamme acceptable. Enfin, la Fig. 23b présente l'état de l'art pour les transistors à source/drain métalliques de type n avec ou sans implémentation de ségrégation de dopants. Les résultats obtenus au cours de ces recherches sont en position très favorables lorsqu'ils sont comparés à des technologies planaires. En effet, les points rouges et la référence 31

correspondent à des architectures particulières (canaux contraints ou activation à haute température).

Fig. 23: a) Ion et Ioff en fonction de la longueur de grille de SB-nMOSFETs avec As ségrégé sur des contacts PtSi. b) Etat de l'art des performances de SB-nMOSFET: figure de mérite Ioff-Ion. Symboles ouvert/plein correspondent à des technologies sans ou avec implémentation de ségrégation de dopant, respectivement. Les symboles rouges correspondent à des procédés à haute température. ★ [ce travail], ▲ [29], ▶ [30] ■ [31]

# 1.4 CARACTERISATIONS HYPERFREQUENCES ET DE DISPOSITIFS LOGIQUES ELEMENTAIRES:

# 1.4.1 CARACTERISATION D'INVERSEUR CMOS A SOURCE/DRAIN METALLIQUE UNIQUE.

Cette partie présente la première démonstration et caractérisation d'inverseurs CMOS obtenus par ségrégation de dopant à basse température. Cette approche a abouti au dépôt d'un brevet français <sup>32</sup> par le CNRS avec des extensions internationales (Europe, Etats-Unis, Japon). Elle permet de lever les deux points de blocage majeurs à l'implémentation de source/drain Schottky: l'utilisation d'un siliciure unique et des hauteurs de barrière inférieures à 0.1eV pour les deux types. L'invention permet ainsi de proposer une solution performante, viable et faible coût pour la fabrication des zones

source/drain des futures générations technologiques de MOSFETs complémentaires. Le procédé proposé est dit froid (pas d'étape d'activation des dopants à haute température), levant de nombreuses contraintes en termes d'intégration notamment pour l'empilement de grille comprenant par exemple un diélectrique high-k et une grille métallique.

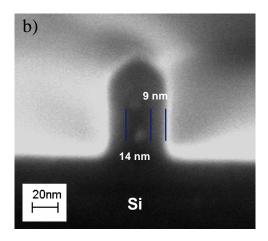

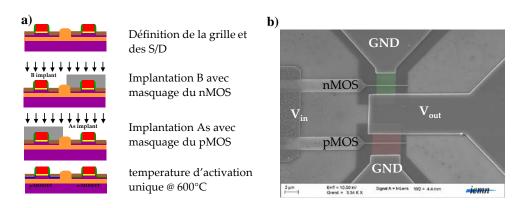

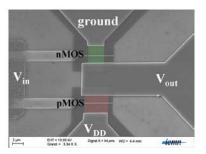

La Fig. 1Fig. 24a présente le procédé de fabrication d'un tel dispositif CMOS. Il débute par la formation des zones d'isolation et des grilles de transistors pouvant intégrer un oxyde thermique avec une grille en poly-silicium mais aussi un diélectrique à haute constante diélectrique (Hk) avec une grille métallique. Aucune formation de jonction ni d'implantation n'est nécessaire. Un espaceur en diélectrique de chaque côté de la grille est ensuite réalisé. Le siliciure de platine est formé sur les zones source/drain des transistors de type p et n. Puis des éléments du groupe III (BF<sub>2</sub>+ 15 keV, 5×10<sup>14</sup> cm<sup>-2</sup>) sont confinés dans le siliciure par implantation ionique pour la réalisation des contacts de type p, le transistor complémentaire (type n) étant protégé par masquage. La densité du siliciure est 4 fois plus grande que celle du silicium, la couche métallique est un écran lors de l'implantation, les éléments sont rapidement freinés et sont donc majoritairement localisés dans cette couche. La même approche est suivie pour le transistor complémentaire : Des éléments du groupe V (As+ 17 keV, 5×1014 cm-2) sont confinés dans le siliciure par implantation ionique pour la réalisation des contacts de type n, le transistor complémentaire (type p) étant protégé par masquage. Enfin, une étape unique de recuit à basse température (< 700°C) est utilisée pour faire ségréger les dopants à l'interface entre le siliciure et le semi-conducteur.

Fig. 24: a) Description des étapes du procédé de fabrication d'un dispositif MOSFET complémentaire intégrant des zones source/drain en PtSi dont la hauteur de barrière est modulée par ségrégation de dopants. b) Image MEB d'un dispositif CMOS réalisé avec en rouge, le pFET et en vert le nFET.

La **Fig. 24**b présente une vue aérienne MEB d'un SB-CMOSFETs, composé d'un n- MOS dans la partie supérieure et d'un p- MOS dans la partie inférieure. Les régions

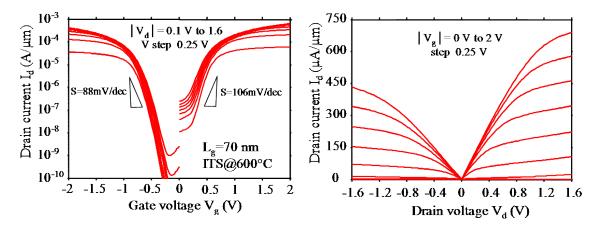

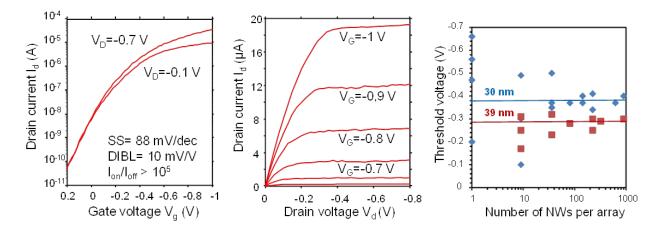

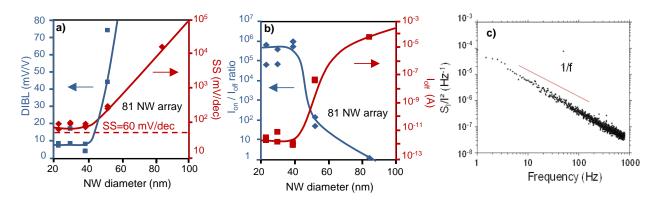

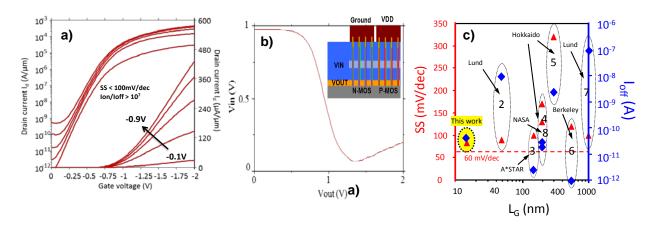

verte et rouge sont les fenêtres d'implantation pour respectivement l'arsenic et le bore. Une isolation par gravure (mesa) sépare les deux transistors afin d'empêcher la diffusion des dopants vers le dispositif complémentaire. La **Fig. 25** propose les caractéristiques statiques  $I_d\text{-}V_g$  et  $I_d\text{-}V_d$  d'un transistor de 70 nm de long. D'un point de vue qualitatif, aucune inflexion sous-linéaire n'est observée sur les courbes  $I_d\text{-}V_d\text{s}$  indiquant que les hauteurs de barrière pour les deux types de transistors sont suffisamment basses pour ne pas limiter l'injection de support à la jonction de la source. Le courant de commande pour les dispositifs de type n et p est de  $I_{on}$  = 596/378  $\mu\text{A}/\mu\text{m}$  à  $V_{dd}$  = 1.1 V avec  $|V_{gs}|$  = 2 V pour tenir compte de l'épaisseur d'oxyde de grille de 2.4 nm. La valeur de la pente sous le seuil à faible  $V_{ds}$  est proche pour les deux polarités de transistors, à savoir, 106 et 88 mV / dec pour les transistors de type n et p, respectivement. En circuiterie CMOS conventionnelle, la largeur W du transistor p-MOS est typiquement 2-2.5X plus large que celle du n-MOSFETs. Dans le cas présent, les largeurs du n- MOS et du p- MOS sont de 3 $\mu\text{m}$  et 4.5 $\mu\text{m}$  respectivement afin de préserver une symétrie dans le fonctionnement basique du circuit.

Fig. 25: Caractéristiques statiques Id-Vg et Id-Vd d'un transistor de 70 nm de long

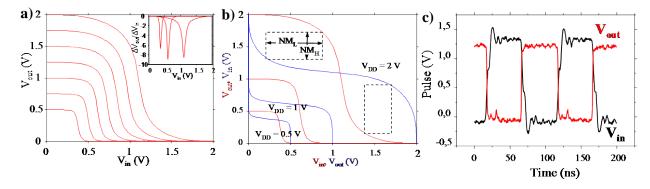

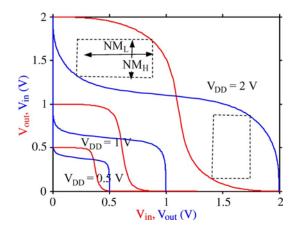

La **Fig. 26**a présente les caractéristiques statiques de transfert (VTC) d'un inverseur de 70 nm de long. Plusieurs  $V_{dd}$  sont considérées, allant de 0.5 à 2 V par pas de 0.25 V. Pour chaque condition de tension d'alimentation, d'excellents VTC sont obtenus avec un état haut égal à  $V_{DD}$  et un état bas égal à 0. Ceci indique que des courants de fuite, quand les transistors sont bloqués, sont suffisamment faibles pour ne pas dégrader les états logiques haut et bas. L'encart de la **Fig. 26**a montre les variations de gain de tension de VTC ( $\Delta V_{out}/\Delta V_{in}$ ) pour plusieurs  $V_{dd}$ . La distribution fortement pointue révèle une zone étroite de transition qui équivaut à 210 mV pour  $V_{dd}$  = 1 V. La position du pic à ~ 0.6 V, est légèrement décalée de  $V_{dd}$  / 2 en raison d'une asymétrie non compensée entre les courants de saturation n et p-MOS. Cette asymétrie provient partiellement de l'abaissement de barrière induit par le drain (DIBL), pour les deux

polarités de transistors (177 et 126 mV / V pour n et p MOSFET, respectivement). Bien que le rapport de la largeur des dispositifs (W<sub>p</sub> / W<sub>n</sub>) ait été ajusté afin d'obtenir des courants de saturation équivalents à  $|V_{gs}| = 2 \text{ V}$  (pour compenser l'oxyde de grille épais), la mesure directe de VTC rend cette correction impraticable. Pour affiner l'analyse, les marges de bruits statiques ont été évaluées en utilisant le critère de produit maximal (maximum product criterion (MPC)<sup>33</sup>) qui maximise la zone des rectangles qui peuvent être intégrés dans les boucles VTC d'inverseurs croisés, en interchangeant Vin et Vout sur les axes x- et y- (Fig. 26b). La marge de bruit haute (NM<sub>H</sub>= V<sub>OH</sub>-V<sub>IH</sub>) et la marge de bruit basse (NML= VoL-VIL) sont schématisées sur la figure. D'excellentes performances ont été démontrées avec par exemple pour VDD=1V, NMH= 0,21 V / NM<sub>L</sub>=0.47V. Enfin, la réponse dynamique à 10 MHz de l'inverseur CMOS (**Fig. 26**c) présente d'excellentes propriétés régénératrices. L'intérêt de cette démonstration était de montrer qu'un siliciure unique couplé à une stratégie à faible température de ségrégation offre une approche efficace, viable et de la fabrication à faible coût pour les futurs nœuds technologiques de MOSFET complémentaires. Gardant à l'esprit la réduction du budget thermique rigoureux requis par l'introduction de nouveaux matériaux dans le procédé CMOS, cette approche est également particulièrement bien adaptée à l'intégration de matériaux sensibles à la température et pour l'empilement monolithique de dispositifs en trois dimensions qui doivent se conformer à la réduction thermique sévère du budget pour garantir la stabilité siliciure.

Fig. 26: a) Caractéristiques de transfert en tension d'un inverseur SB-MOSFET à différents V<sub>DD</sub> (de 0.5V à 2 V avec un pas de 0.25 V) avec une longueur de grille de 70 nm W<sub>n-MOS</sub> = 3 μm, W<sub>p-MOS</sub> = 4.5 μm. Le gain en tension (ΔV<sub>out</sub>/ΔV<sub>in</sub>) est donné en insert pour 3 différents V<sub>DD</sub> (0.5, 1 and 2 V). b) Caractéristiques statiques de transfert V<sub>DD</sub> (0.5V, 1V et 2V) en interchangeant V<sub>in</sub> et V<sub>out</sub> sur les axes x-et y-pour identifier les marges de bruit N<sub>ML</sub> and N<sub>MH</sub> suivant le critère du produit maximal. c) Réponse dynamique (impulsion) de l'inverseur SB-MOSFET à V<sub>DD</sub> = 1.2V.

# 1.4.2 CARACTERISATION HYPERFREQUENCE DE MOSFETS A SOURCE/DRAIN METALLIQUES.

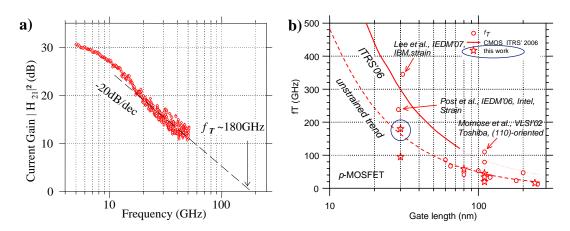

Des dispositifs optimisés pour la caractérisation hyperfréquence (présentés dans la section 1.3.1) ont permis de compléter la caractérisation de la technologie à source/drain métalliques. Ces mesures ont été réalisées avec l'expertise du groupe anode de l'IEMN, spécialisé en mesures RF. Les paramètres S ont été mesurés jusqu'à 50 Ghz en utilisant un analyseur de réseau micro-onde. La calibration des pointes a été réalisée en suivant une procédure conventionnelle (SOLT) et les accès coplanaires des dispositifs ont été retranchés en utilisant des structures ouvertes. ("Open Test Structure"). Les fréquences de coupure sont obtenues par extrapolation du gain en courant  $|H_{21}|^2$  en utilisant la pente théorique à -20dB/dec. Une performance RF record pour un dispositif de type p non contraint sur substrat SOI (Fig. 27a) a été démontrée sur un pFET de 30 nm avec ségrégation de bore avec une fréquence de coupure fr de 180 GHz <sup>24</sup>. Comparé à l'état de l'art (Fig. 27b), ce résultat constitue l'un des meilleurs jamais reportés dans la littérature à la date de publication pour des dispositifs pMOS non contraints.

Des travaux complémentaires de modélisation  $^{34}$  ont montré que l'optimisation de la couche de dopant par un contrôle minutieux de la concentration de dopant et l'extension latérale permet, via la réduction des résistances de contact source / drain, d'obtenir une valeur  $F_t$  à très faible consommation d'énergie en courant continu (45  $\mu$ W /  $\mu$ m), qui est très prometteur pour traiter les applications analogiques basse tension.

Fig. 27: a) Paramètres S d'un p-MOSFET de 30 nm avec une ségrégation de dopant de bore mesurés jusqu'à 50GHz avec  $V_g$ = $V_d$ =-2V, b) Etat de l'art de fréquence de coupure  $f_T$  pour des p-MOSFETs massif ou SOI – les architectures de canaux particulières sont mentionnées.

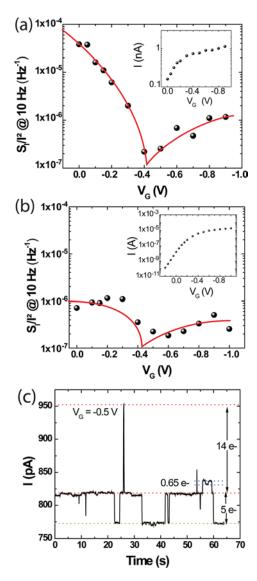

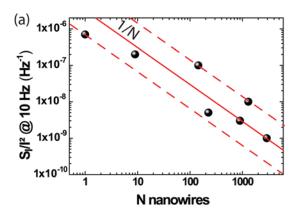

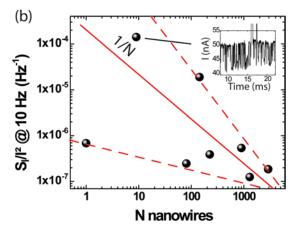

Finalement, nous avons étudié le bruit à basse fréquence dans les jonctions Schottky ainsi que dans des transistors SB-FET<sup>35</sup>. Il a été démontré que, même pour les très petites valeurs de hauteurs de barrière Schottky (φ <0,1 eV), la contribution de la barrière sur le bruit n'est pas négligeable même si le courant est dominé par la résistance de canal. En outre, il y a une décroissance exponentielle du bruit normalisé avec la tension de drain V<sub>d</sub>, qui est un point important à considérer pour les applications d'amplificateur ou de capteurs. La modulation de la barrière par des moyens technologiques, tel que la ségrégation de dopant, tend à réduire l'amplitude du bruit, même si des contributions additionnelles de bruit par génération-recombinaison et par piégeage ont été remarquées pour de faibles valeurs de V<sub>d</sub> pour les dispositifs de type p. Un modèle a été établi permettant une formulation générique du bruit BF, applicable dans n'importe quel type de dispositifs SB-FET.

#### 1.5 CONCLUSION

Le programme de recherche sur les transistors à source/drain métalliques a abouti à de nombreux faits saillants. L'étude matériau a permis une compréhension fine de siliciures bord de bande de valence (platine, iridium) et de conduction (erbium et ytterbium). Ces siliciures associés à une ségrégation de dopants offrent des hauteurs de barrière Schottky pour les trous mais aussi pour les électrons sous la valeur cible de 0.1 eV. Un procédé de transistor a été développé avec des grilles métalliques jusqu'à 20 nm de long sur substrat SOI ultrafin. L'implémentation de tels siliciures a démontré des performances statiques de transistors de type p et n au meilleur international. Le développement d'un inverseur CMOS intégrant un siliciure unique et des ségrégations de dopants activées à basse température (600°C) a été proposé pour la première fois et a débouché sur un dépôt de brevet. Enfin, des caractérisations hyperfréquences ont révélées que cette architecture était très compétitive par rapport à une architecture source/drain conventionnelle.

#### 1.6 SELECTION D'ARTICLES

## Low Temperature Implementation of Dopant-Segregated Band-edge Metallic S/D junctions in Thin-Body SOI p-MOSFETs.

$\begin{array}{c} G. \ Larrieu^{(1)}, E. \ Dubois^{(1)}, R. \ Valentin^{(1)}, N. \ Breil^{(1,2)}, F. \ Danneville^{(1)}, \\ G. \ Dambrine^{(1)}, J.P. \ Raskin^{(3)}, J.C. \ Pesant^{(1)}. \end{array}$

IEMN – UMR CNRS 8520, Avenue Poincaré, BP 60069, 59652 Villeneuve d'Ascq, France.

STMicroelectronics, 850 rue Jean Monnet, 38926 Crolles Cedex France

UCL, Place du Levant, 3, Maxwell Building, B-1348 Louvain-la-Neuve, Belgium. guilhem.larrieu@isen.iemn.univ-lille1.fr, tel:+33 320 197 917, fax:+33 320 197 884.

#### Abstract

This paper proposes the implementation of a dopant segregated band-edge silicide using implantation-to-silicide and low temperature activation (500°C). The integration of platinum silicide coupled to boron segregation demonstrates a 50% enhancement of the current drive over the dopant-free approach. RF characterization unveils a cut-off frequency  $f_{\rm T}$  of 180 GHz at  $\rm L_g=30$  nm without application of channel stressors.

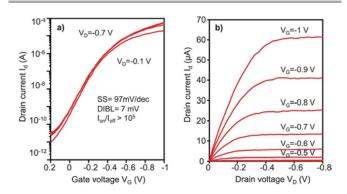

#### 1-Introduction