# Techniques for the evaluation and the improvement of emergent technologies' behavior facing random errors

Enrico Costenaro

### ► To cite this version:

Enrico Costenaro. Techniques for the evaluation and the improvement of emergent technologies' behavior facing random errors. Micro and nanotechnologies/Microelectronics. Université Grenoble Alpes, 2015. English. NNT: 2015GREAT137. tel-01279142

## HAL Id: tel-01279142 https://theses.hal.science/tel-01279142

Submitted on 25 Feb 2016  $\,$

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# UNIVERSITÉ GRENOBLE ALPES

## THÈSE

Pour obtenir le grade de

## DOCTEUR DE L'UNIVERSITÉ DE GRENOBLE ALPES

Spécialité : Nano Électronique et Nano Technologies

Arrêté ministériel : 7 aoôt 2006

## Présentée par Enrico COSTENARO

Thèse dirigée par **Mihail NICOLAIDIS** et co-encadrée par **Marian-Dan ALEXANDRESCU**

préparée au sein du laboratoire TIMA dans l'École Doctorale Électronique, Électrotechnique, Automatique et Traitement du signal

# Techniques pour l'évaluation et l'amélioration du comportement des technologies émergentes face aux fautes aléatoires

Thèse soutenue publiquement le **9 décembre 2015**, devant le jury composé de :

## Dr. Mir SALVADOR

CNRS (Laboratoire TIMA, Grenoble), Président **Professor Massimo VIOLANTE** Politecnico di Torino, Rapporteur **Professor Abbas DANDACHE** Université de Lorraine, Rapporteur **Dr. Mihail NICOLAIDIS** CNRS (Laboratoire TIMA, Grenoble), Directeur de thèse

#### Acknowledgments

Firstly, I would like to express my sincere gratitude to my thesis supervisor Michael Nicolaidis, head of ARIS group of TIMA, for the continuous support of my PhD study and related research, for his guidance, his criticism and encouragement, as well as good humor and optimism.

My sincere thanks also goes to my thesis co-supervisor Dan Alexandrescu, CEO of IROC Technologies, I am grateful for his encouragement, for granting me time to write my thesis, for his help in proofreading my manuscript and especially for his friendship.

I wish to express my thanks to Prof. Massimo Violante and Prof. Abbas Dandache for serving on my thesis committee and providing their feedback.

I would like to thank Dr. Salvador Mir, head of TIMA Laboratory, for agreeing to be the president of my thesis jury.

I thank my colleagues at IROC Technologies for all the good time we have had since I joined the company. In particular, I am grateful to Dr. Adrian Evans with whom I collaborated on several works and Jocelyne Baudoin who helped proofreading all the french texts I wrote .

Last, but certainly not least, I would like to thank my family: my wife, Sara, my parents, Giovanni and Mariella, and my brothers, Daniele and Alberto, for encouraging and supporting me for my choices, my work and throughout writing this thesis.

# Contents

| 1                | Intr | roduction 1                                                 |  |  |  |  |  |  |

|------------------|------|-------------------------------------------------------------|--|--|--|--|--|--|

|                  | 1.1  | 1 Introduction                                              |  |  |  |  |  |  |

|                  | 1.2  | Radiation Environments and Anomalies                        |  |  |  |  |  |  |

|                  |      | 1.2.1 Space Radiation Environment                           |  |  |  |  |  |  |

|                  |      | 1.2.2 Terrestrial Radiation Environment                     |  |  |  |  |  |  |

|                  | 1.3  | Single Event Effects - Mechanism and Classification         |  |  |  |  |  |  |

|                  |      | 1.3.1 Particles and Interactions                            |  |  |  |  |  |  |

|                  |      | 1.3.2 Single Event Effects Classification                   |  |  |  |  |  |  |

| <b>2</b>         | Sing | gle Event Effect Analysis 35                                |  |  |  |  |  |  |

|                  | 2.1  | Introduction                                                |  |  |  |  |  |  |

|                  | 2.2  | Technology SER Characterization                             |  |  |  |  |  |  |

|                  |      | 2.2.1 Memory Intrinsic SER Characterization                 |  |  |  |  |  |  |

|                  |      | 2.2.2 Standard Cell Intrinsic SER Characterization          |  |  |  |  |  |  |

|                  | 2.3  | Masking Effects                                             |  |  |  |  |  |  |

|                  |      | 2.3.1 Electrical De-Rating                                  |  |  |  |  |  |  |

|                  |      | 2.3.2 Logic De-Rating 37                                    |  |  |  |  |  |  |

|                  |      | 2.3.3 Temporal De-Rating 39                                 |  |  |  |  |  |  |

|                  |      | 2.3.4 Functional De-Rating 41                               |  |  |  |  |  |  |

|                  |      | 2.3.5 Memory De-Rating                                      |  |  |  |  |  |  |

|                  | 2.4  | Overall SER Computation    43                               |  |  |  |  |  |  |

| 3                | Sing | Single Event Transient Analysis 47                          |  |  |  |  |  |  |

|                  | 3.1  | Introduction                                                |  |  |  |  |  |  |

|                  | 3.2  | SET Characterization of the Standard Cell Library 49        |  |  |  |  |  |  |

|                  |      | 3.2.1 TFIT Overview                                         |  |  |  |  |  |  |

|                  |      | 3.2.2 Per-cells state SER figures                           |  |  |  |  |  |  |

|                  |      | 3.2.3 Overall per-cell SER figures                          |  |  |  |  |  |  |

|                  |      | 3.2.4 Transistor Contribution to the Overall Cell SER 55    |  |  |  |  |  |  |

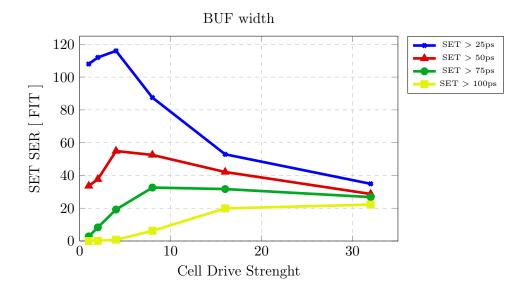

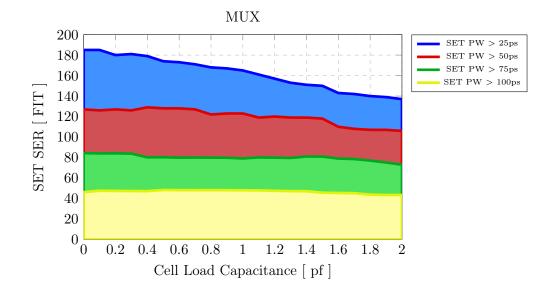

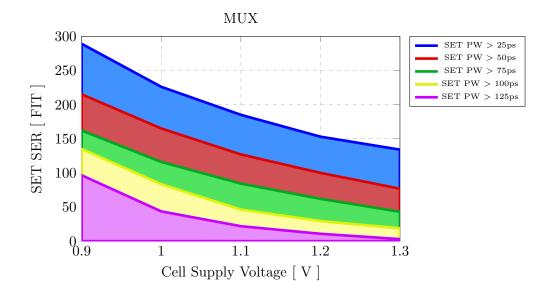

|                  |      | 3.2.5 Single Event Transient SER: Influencing Factors       |  |  |  |  |  |  |

|                  | 3.3  | SET Propagation Analysis                                    |  |  |  |  |  |  |

|                  |      | 3.3.1 Classic serial fault simulation approach              |  |  |  |  |  |  |

|                  |      | 3.3.2 Accelerated SET simulation                            |  |  |  |  |  |  |

|                  |      | 3.3.3 Static, probabilistic fault propagation approaches 67 |  |  |  |  |  |  |

|                  | 3.4  | Conclusions                                                 |  |  |  |  |  |  |

| 4                | Sing | gle Event Analysis for Sequential Logic 71                  |  |  |  |  |  |  |

| 4.1 Introduction |      |                                                             |  |  |  |  |  |  |

|                  | 4.2  | Single Event Effects in Sequential Cells                    |  |  |  |  |  |  |

|                  | 4.3  | SER Analysis of Sequential Cell States                      |  |  |  |  |  |  |

|                 |       | 4.3.1 SEU results for standard flip-flops               | 76  |  |  |  |  |

|-----------------|-------|---------------------------------------------------------|-----|--|--|--|--|

|                 |       | 4.3.2 SET results for standard flip-flops               | 79  |  |  |  |  |

|                 | 4.4   | Master and Slave Temporal De-Rating                     | 80  |  |  |  |  |

|                 |       | 4.4.1 Long Paths                                        | 80  |  |  |  |  |

|                 |       | 4.4.2 Short Paths                                       | 81  |  |  |  |  |

|                 |       | 4.4.3 Further Comments                                  | 81  |  |  |  |  |

|                 | 4.5   | Cell State Analysis in Complex Designs                  | 82  |  |  |  |  |

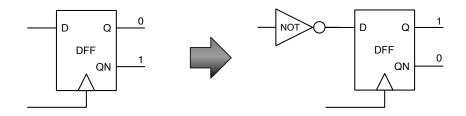

|                 | 4.6   | State-Aware SER Improvement                             | 83  |  |  |  |  |

|                 |       | 4.6.1 Preference Towards Lower SER Data State           | 83  |  |  |  |  |

|                 | 4.7   | Conclusions                                             | 84  |  |  |  |  |

| 5               | Der   | rating Analysis of a Complex CPU                        |     |  |  |  |  |

|                 | 5.1   | Introduction                                            | 85  |  |  |  |  |

|                 |       | 5.1.1 Statistical Confidence                            | 86  |  |  |  |  |

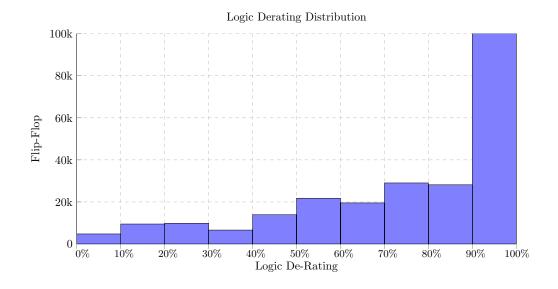

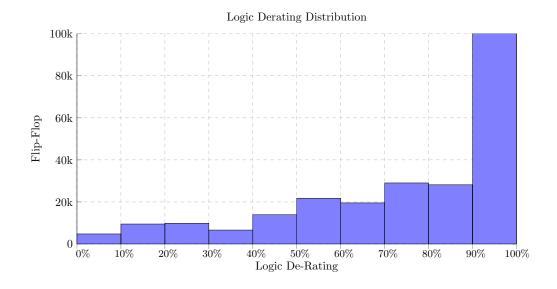

|                 | 5.2   | Logic De-Rating Analysis                                | 87  |  |  |  |  |

|                 | 5.3   | Memory De-Rating Analysis                               | 87  |  |  |  |  |

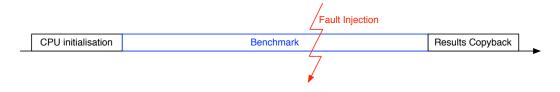

|                 | 5.4   | Functional De-Rating Analysis                           |     |  |  |  |  |

|                 |       | 5.4.1 Fault Classification                              | 90  |  |  |  |  |

|                 | 5.5   | Conclusion                                              | 102 |  |  |  |  |

| 6               | Con   | onclusion 10                                            |     |  |  |  |  |

|                 | 6.1   | Single Event Transient Analysis                         | 105 |  |  |  |  |

|                 | 6.2   | Single Event Analysis for Sequential Logic              |     |  |  |  |  |

|                 | 6.3   | Derating Analysis of a Complex CPU                      | 106 |  |  |  |  |

|                 | 6.4   | Summary                                                 | 107 |  |  |  |  |

| Δ               | Flin  | -Flop SEU Reduction through Minimization of the Tempora | al  |  |  |  |  |

|                 | _     | nerability Factor (TVF)                                 | 109 |  |  |  |  |

|                 | A.1   | Introduction                                            |     |  |  |  |  |

|                 | A.2   | Overview of SEU Masking Factors                         |     |  |  |  |  |

|                 | A.3   | TVF Optimization                                        |     |  |  |  |  |

|                 | A.4   | Area and Power Constraints                              |     |  |  |  |  |

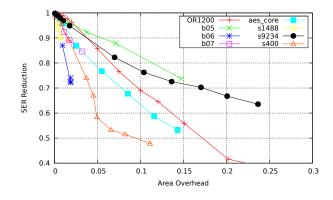

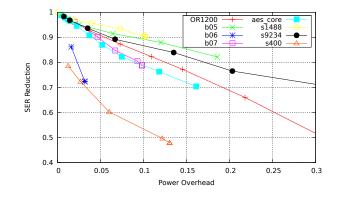

|                 | A.5   | Experimental Results                                    |     |  |  |  |  |

|                 | A.6   | Conclusions                                             |     |  |  |  |  |

| Bibliography 12 |       |                                                         |     |  |  |  |  |

| - Ri            | hling | rranhv                                                  | 121 |  |  |  |  |

# Glossary

- ASIC Application Specific Integrated Circuit. 85

- BEOL Back End Of Line. 16

- BGA Ball Grid Array. 16

- BPSG Boron Doped Phosphosilicate Glass. 14, 15

- CMOS Complementary Metal Oxide Semiconductor. 24, 28, 30

- **CPU** Central Processing Unit. 2, 43, 49, 82, 86, 87, 89–92, 106

- **DoE** Design of Experiment. 51

- DRAM Dynamic Random Access Memory. 26, 28

- **DUE** Detectable Uncorrectable Error. 2, 86, 90, 93, 95–97, 103, 107

- **DUT** Device Under Test. 59

- ECC Error Correcting Code. 71, 89

- EDA Electronic Design Automation. 52, 75

- **EDR** Electrical De-Rating. 35, 37, 59, 106

- FDR Functional De-Rating. 36, 41, 43, 86, 87, 90, 107

- **FET** Field Effect Transistor. 28

- **FIT** Failure In Time. 50, 51, 53, 73, 76, 79, 80, 82, 83, 86

- FPGA Field Programmable Gate Array. 28

- GCR Galactic Cosmic Rays. 3, 8

- IC Integrated Circuit. 2

- LA Low Alpha. 18

- LDR Logical De-Rating. 35, 37, 59, 60, 86, 87, 106, 107

- **LET** Linear Energy Transfer. 11, 19, 21, 51, 55

- MBU Multiple Bit Upset. 28, 36

- MCU Multiple Cell Upset. 28, 36

- **MDR** Memory De-Rating. 35, 86, 87, 107

- MOS Metal Oxide Semiconductor. 30, 33

- **MOSFET** Metal Oxide Semiconductor Field Effect Transistor. 28, 30

- PC Program Counter. 93

- **PIPB** Propagation Induced Pulse Broadening. 41, 42, 60, 106

- **PPSFP** Parallel Pattern Single Fault Propagation. 87, 107

- **PW** Pulse Width. 37, 40, 51, 68, 76

- **RTL** Register Transfer Language. 82

- **SAA** South Atlantic anomaly. 5, 6

- **SBU** Single Bit Upset. 26, 28, 36

- **SDC** Silent Data Corruption. 2, 86, 90, 93, 95–97, 103, 107

- **SDF** Standard Delay Format. 49, 59, 61

- **SE** Soft Error. 35, 43

- SEB Single Event Burnout. 28

- **SECDED** Single Error Correct, Double Error Detect. 28

- **SEE** Single Event Effect. 1, 15, 18, 22, 24, 26, 28, 35–37, 47–50, 55, 65, 71–74, 78, 84, 85

- SEFI Single Event Functional Interrupt. 28

- SEGR Single Event Gate Rupture. 28, 30

- SEL Single Event Latchup. 28

- **SEMT** Single Event Multiple Transient. 26

- **SEMU** Single Event Multiple Upset. 26

- SER Soft Error Rate. 36, 37, 40, 48–51, 53–56, 58–60, 65, 66, 68, 69, 72–76, 78–87, 89, 92, 93, 97, 103, 106, 107

- **SESB** Single Event induced Snap Back. 30

- **SET** Single Event Transient. 2, 26, 36, 37, 39–41, 44, 48–51, 53, 55, 56, 58–61, 63, 65–69, 72, 74–76, 78–80, 105, 106

- SEU Single Event Upset. 2, 26, 36, 37, 39, 40, 44, 48, 71–76, 79, 80, 87, 92, 97, 105, 106

- **SoCFIT** System on Chip FIT. A tool developed by IROC Technologies to estimate the SER sensitivity of complex circuits. 85–87, 89, 92, 97

- SRAM Static Random Access Memory. 26, 28, 36, 86, 89, 106

- TCAD Technology CAD. 49–51

- **TDR** Temporal De-Rating. 2, 35, 39, 40, 59, 66, 79, 86, 87, 106

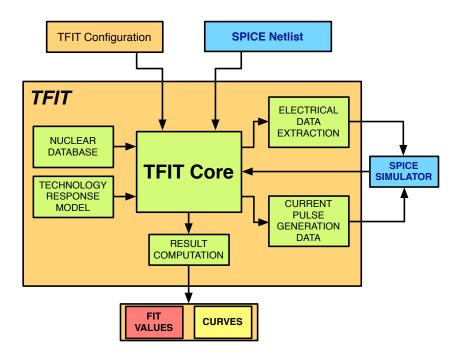

- TFIT Transistor FIT. A tool developed by IROC Technologies to estimate the SER sensitivity of individual cells. These can be memory cells, sequential cells or combinatorial cells. 49, 51, 52, 54, 75, 76, 85, 105, 106

- **TID** Total Ionizing Dose. 24

- **UBM** Under Bump Metallurgy. 17

- ULA Ultra Low Alpha. 18

- VCD Value Change Dump. 82

- VPI Verilog Procedural Interface. 66, 88, 92

# Chapter 1 Introduction

#### Contents

| 1.1 Intr                                                | oduction                        | 1                                                         | 1  |  |  |  |

|---------------------------------------------------------|---------------------------------|-----------------------------------------------------------|----|--|--|--|

| 1.2 Radiation Environments and Anomalies                |                                 |                                                           |    |  |  |  |

| 1.2.1                                                   | 2.1 Space Radiation Environment |                                                           |    |  |  |  |

|                                                         | 1.2.1.1                         | Particles trapped by the earth's magnetic field $\ . \ .$ | 3  |  |  |  |

|                                                         | 1.2.1.2                         | Galactic Cosmic Rays                                      | 8  |  |  |  |

|                                                         | 1.2.1.3                         | Solar Particle Events                                     | 9  |  |  |  |

| 1.2.2 Terrestrial Radiation Environment                 |                                 |                                                           |    |  |  |  |

|                                                         | 1.2.2.1                         | Thermal Neutrons                                          | 14 |  |  |  |

|                                                         | 1.2.2.2                         | Muons                                                     | 15 |  |  |  |

|                                                         | 1.2.2.3                         | Alpha Particles                                           | 15 |  |  |  |

| 1.3 Single Event Effects - Mechanism and Classification |                                 |                                                           |    |  |  |  |

| 1.3.1 Particles and Interactions                        |                                 |                                                           |    |  |  |  |

|                                                         | 1.3.1.1                         | Gamma and X-Ray Ionization                                | 18 |  |  |  |

|                                                         | 1.3.1.2                         | Energetic Particle Ionization                             | 19 |  |  |  |

|                                                         | 1.3.1.3                         | Cumulative Radiation Effects                              | 24 |  |  |  |

| 1.3.2 Single Event Effects Classification               |                                 |                                                           |    |  |  |  |

|                                                         | 1.3.2.1                         | Soft Errors                                               | 26 |  |  |  |

|                                                         | 1.3.2.2                         | Hard Errors                                               | 28 |  |  |  |

#### 1.1 Introduction

The continuing evolution of the technology allows building increasingly complex electronic devices integrating more and more functions. This evolution is not free of problems, or more appropriate, challenges to overcome. An increasing source of problems concerning the reliability of new technological processes is the perturbation induced by energetic particles (the Single Event Effects(SEEs)). First applications to incite some interest with respect to SEEs were obviously limited to specific applications: aero-space, high-reliability, nuclear facilities equipment and implantable medical devices. However, technological advances make possible the continuous diminution of the transistor size, rendering the components more sensitive to perturbations induced by radiation. Thus, is no longer possible to ignore Single Events for future and present technologies working in a natural environment. The focus of this thesis is on soft error analysis and mitigation techniques for very large circuits. The main contributions consist of advancement in the analysis of Single Event Transient and Single Event Upset.

The manuscript is organized as follows. The first chapter is divided in two parts, the first section provide an overview of the radiation environments where microelectronic devices and integrated circuits may be used. The second section presents the main single event effects with their triggering mechanism including some basic notion of nuclear physics. Chapter 2 introduces the soft error analysis methodology presenting the basic de-rating effects. In chapter 3 presents a detailed Single Event Transient analysis flow, from the technology characterization to the propagation analysis. Chapter 4 describes an advanced Single Event analysis for sequential logic, including some considerations about the Single Event Transient (SET) sensitivity of sequential cells. A low cost Single Event Upset (SEU) mitigation solution was proposed and validated on a large (190kFF) design.

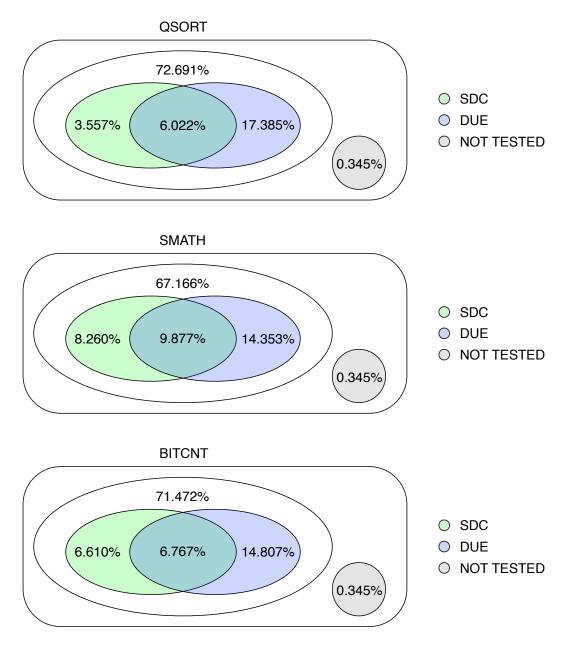

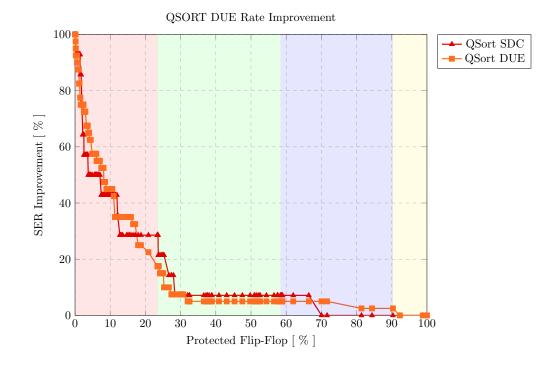

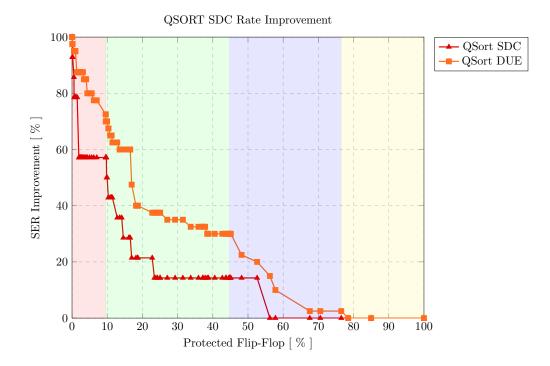

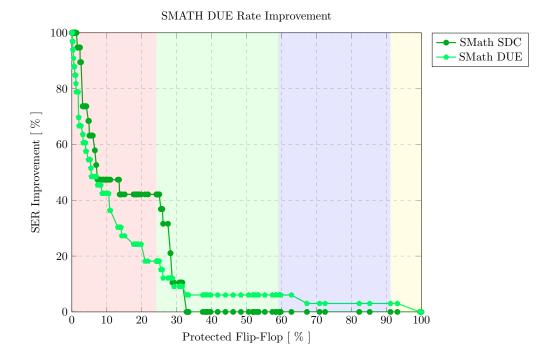

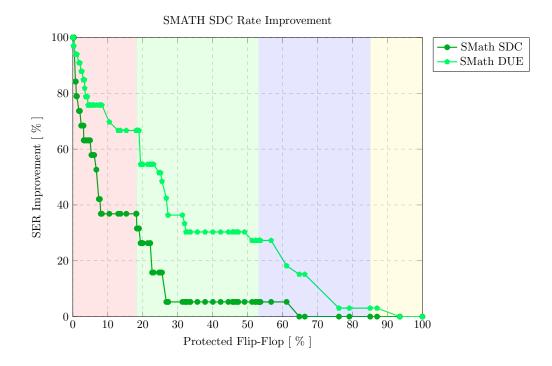

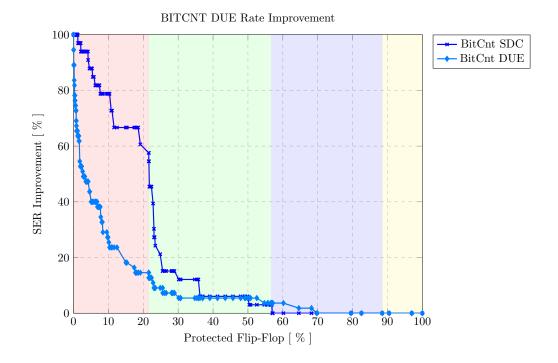

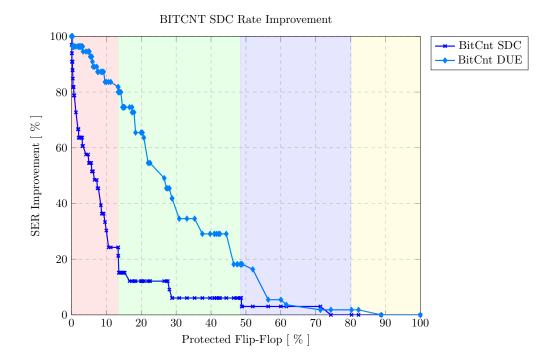

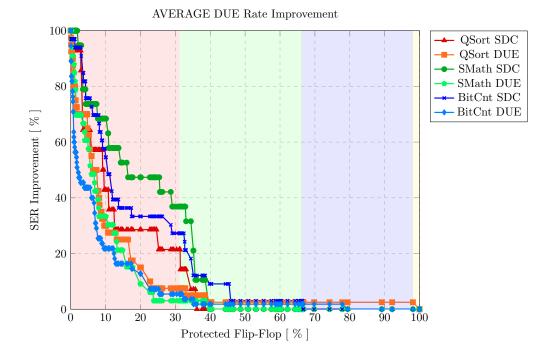

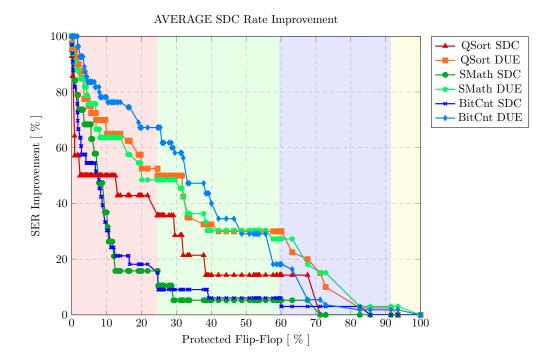

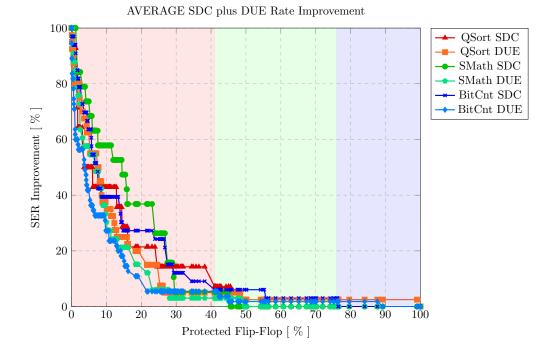

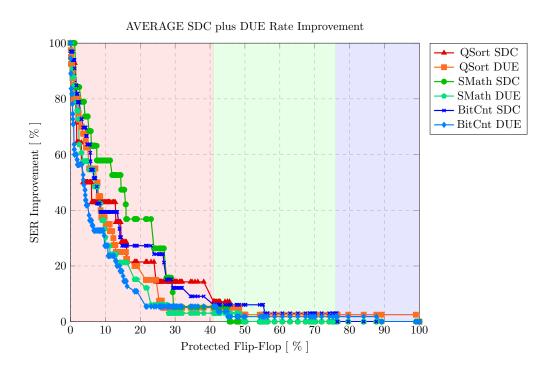

Chapter 5 presents the results of functional analysis of a single-core-implementation of a complex commercial Central Processing Unit (CPU) counting about 250k Flip-Flops. Three representative benchmarks were considered for this analysis. For each benchmark scenario, three fault injection campaigns were performed. From the fault injection results a mitigation scenario is proposed. The results obtained show that the failure rates, both Silent Data Corruption (SDC) and Detectable Uncorrectable Error (DUE), can be reduced considerably by hardening a limited percentage of flip-flops instances.

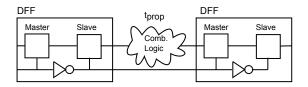

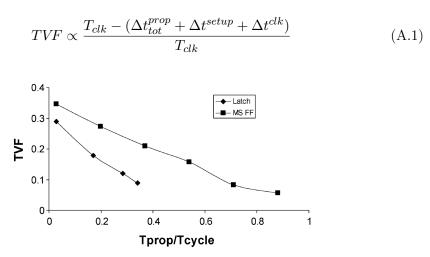

This is followed, in chapter 6, by the conclusions and a discussion of plans for future work. In addition to the main topics of the thesis, additional work performed in the context of a collaborative project is presented in the appendix A: a technique for the mitigation of flip-flop soft-errors through an optimization of the Temporal De-Rating (TDR) is proposed.

Overall, the work presented in this manuscript seeks to propose new techniques and methodologies in order to enable finer grained analysis of the effect of faults while having industry-level performances.

#### **1.2** Radiation Environments and Anomalies

Microelectronic devices and Integrated Circuits(ICs) can be exposed to a wide range of radiation environments. The types of particles, their energies, fluxes, and fluences (or total dose) can vary considerably among the different radiation environments that electronics devices can be exposed to. These differences can lead to large variations in radiation-induced degradation. In this section, we present an overview of the different radiation environments.

#### **1.2.1** Space Radiation Environment

The concentrations and types of particles in the space environment vary significantly with altitude, angle of inclination and solar activity. As such, it is nearly impossible to define a *typical* space environment [Schwank 2008]. Particles present in the space radiation environment include.

- 1. Particles trapped by the earth's magnetic field high energy particles (Galactic Cosmic Rays (GCR) and Solar Particles) that are not deflected by the magnetic field and become trapped in the planet's magnetic field (Figure 1.1).

- 2. Galactic Cosmic Rays (GCR) high-energy atomic nuclei coming outside the solar system, from which all of the surrounding electrons have been stripped away during their passage through the galaxy.

- 3. Solar Particle Events high-energy nuclei that are associated with solar activity, they are ejected from the Sun due to plasma heating, acceleration, and numerous other forces.

#### 1.2.1.1 Particles trapped by the earth's magnetic field

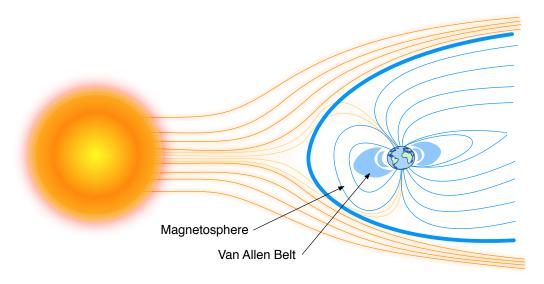

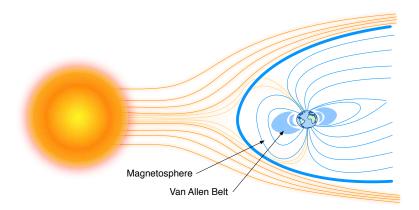

The Earth's magnetic field creates a geomagnetic cavity known as the magnetosphere [Faruk 2012] (Figure 1.1). The magnetic field lines trap low-energy charged particles. These trapped particles consist primarily of electrons and protons, although some heavy ions are also trapped.

Figure 1.1: Solar wind and Earth's magnetosphere.

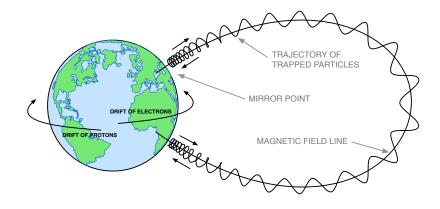

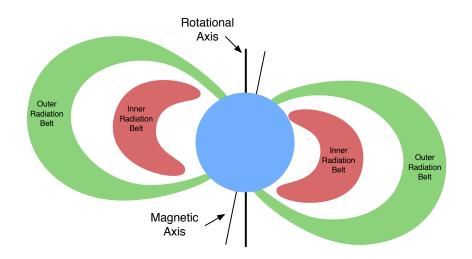

The trapped particles gyrate spirally around the magnetic field lines and are reflected back and forth between the poles where the fields are confined. The motion of the trapped particles is illustrated in Figure 1.2 [Faruk 2012]. This motion of charged particles forms bands of electrons and protons around the earth, which constitute the two primary radiation belts (Figures 1.1, 1.3) or Van-Allen Belts.

Figure 1.2: Motion of trapped particles in the earth's magnetosphere [Faruk 2012].

Figure 1.3: Van Allen radiation belts.

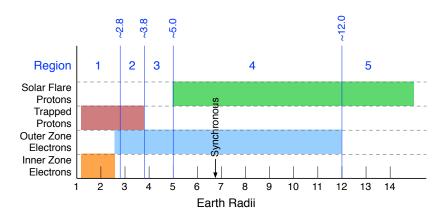

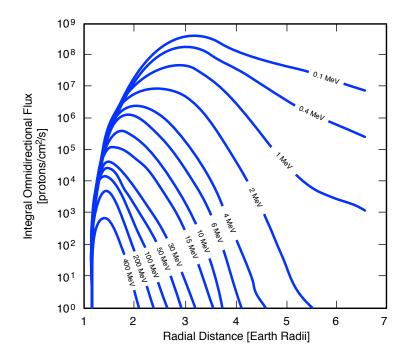

The boundaries of these domains at the equator are illustrated in Figure 1.4 [Faruk 2012] <sup>1</sup>. Because of variations in the magnetic field lines with latitude, the boundaries of the radiation belts vary with latitude (angle of inclination). The domains can be divided into five regions. Trapped protons exist primarily in regions *one* and *two* that extend from slightly above 1 earth radius to 3.8 earth radii (purple bar in Figure 1.4 [Stassinopoulos 1988]). The distribution of proton flux as a function of energy and radial distance is given in Figure 1.5 [Stassinopoulos 1988].

Figure 1.4: Boundaries of the domains for solar flare and trapped protons and outer and inner zone electrons [Faruk 2012].

Trapped protons in the earth's magnetosphere can have energies as high as 500 MeV [Faruk 2012]. Note that the altitude corresponding to the peak in flux decreases with proton energy. Protons with energies greater than 10 MeV primarily occupy regions *one* and *two* [Faruk 2012]. Protons originating from solar flares are present predominantly in regions *four* and *five* (Figure 1.4 [Stassinopoulos 1988]).

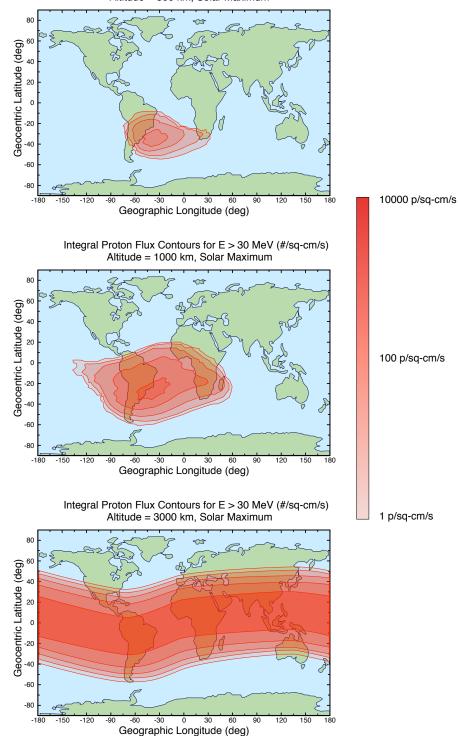

South Atlantic Anomaly Above the Atlantic Ocean centered off the coast of South America, earth's inner Van Allen radiation belt comes closest to the Earth's surface, causing a region of increased proton flux at relatively low altitudes. This region is called the South Atlantic anomaly (SAA), and exists because Van Allen radiation belts are aligned with the magnetic axis of the Earth, which is tilted by 11 degrees from the rotation axis of the Earth, and are not symmetrically placed with respect to the Earth's surface [Barth 1997].

In this region, the flux of protons with energies greater than 30MeV can be as much as  $10^4$  times higher than in comparable altitudes over other regions of the earth. At higher altitudes, the magnetic sphere is more uniform and the South Atlantic Anomaly disappears [Barth 1997], [Petersen 1981]. Figure 1.6 shows maps of the proton belt structure at altitudes of 500 km, 1000 km, and 3000 km, indicating

<sup>&</sup>lt;sup>1</sup>Distances are specified in earth radii (one earth radius is equal to 6380 km) referenced to the center of the earth, i.e., one earth radius is at the earth's surface.

Figure 1.5: Distribution of proton flux as a function of energy and radial distance [Stassinopoulos 1988].

the location of the SAA at low altitudes and the emergence of the background Van Allen belt structure at 3000 km [Barth 1997].

Electrons are present predominantly from region one to region four [Faruk 2012]. The electron domain is divided into two zones, an inner outer zone (Figure 1.4). The outer zone electrons have higher fluxes (10 times higher) and energies than the inner zone electrons. The maximum energy of trapped electrons is approximately 7MeV in the outer zone; whereas, the maximum energy is less than 5MeV for electrons in the inner zone [Faruk 2012]. At these energies, electron interactions are not a threat for single-event effects, but they must be considered for the total-dose effects.

Fluxes of electrons and protons in particular orbits can be estimated from existing models. The primary models of Earth's radiation belts that are in widespread use are AP-8 [Sawyer 1976] and AE-8 [Vette 1991]. The AP-8 models are of trapped protons and include AP-8 MAX and AP-8 MIN, valid for periods of solar maximum and solar minimum, respectively. The AE-8 models for trapped electrons similarly include AE-8 MAX and AE-8 MIN. Experimental data indicate that trapped particle populations are highly dynamic. Large solar events are known to have created temporary proton belts and have enhanced the electron belts [Gussenhoven 1991, Gussenhoven 1993, Dyer 1993]. These results indicate that the static AP-8 and AE-8 models may significantly underestimate the concentration of protons and electrons [Vette 1977, Abel 1994, Heynderickx 1996]. New, dynamic models of the trapped particle radiation environment are being developed to describe

Integral Proton Flux Contours for E > 30 MeV (#/sq-cm/s) Altitude = 500 km, Solar Maximum

Figure 1.6: Integral proton flux contours as a function of latitude and longitude at 500 km, 1000 km, and 3000 km.

the solar-modulated environment more accurately [Piet 2006, Brautigam 2004].

#### 1.2.1.2 Galactic Cosmic Rays

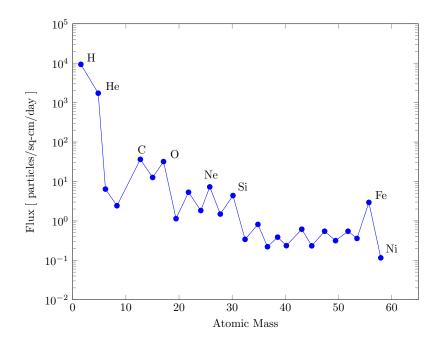

Galactic cosmic rays (GCR) originate from sources outside our solar system and are always present. In the absence of solar activity, cosmic radiation is composed entirely of galactic radiation. GCRs are atomic nuclei from which all of the surrounding electrons have been stripped away during their high-speed passage through the galaxy. Outside of our solar system, the spectrum of galactic cosmic rays is believed to be uniform. Its composition as a function of atomic mass is given in Figure 1.7 [Sexton 1992, Meyer 1974]. It consists mostly of protons (Hydrogen nuclei) (85%) and alpha particles (helium nuclei) (14%). Less than 1% of the galactic cosmic ray spectrum is composed of high-energy heavy-ions.

Figure 1.7: Flux of galactic cosmic ray particles for atomic masses up to 59 [Sexton 1992, Meyer 1974].

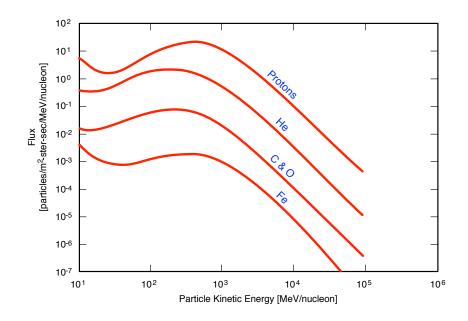

Figure 1.7 shows that the flux of protons is more than two orders of magnitude higher than the flux of either carbon or oxygen. The energy spectrum of galactic cosmic rays is given in Figure 1.8 [Adams 1981]. Note that the x-axis unit of Figure 1.8 is MeV/nucleon, thus, for carbon with 12 nucleons, the point at 100MeV/nucleon on the x-axis corresponds to an energy of 1.2GeV. For most ions, the flux peaks between 100 and 1000MeV/nucleon. For carbon, the peak flux is at an energy of approximately 2.4GeV. For protons and alpha particles, the energy of the ion can be more than 100GeV/nucleon. At these high energies, it is nearly impossible to shield electronic devices from cosmic rays.

Figure 1.8: Energy spectrum of galactic cosmic rays [Adams 1981].

#### 1.2.1.3 Solar Particle Events

The frequency and severity of solar particle events is naturally dependent on the solar activity. Solar particle events (most commonly referred to as solar flares, but also including larger events such as coronal mass ejections) are random in nature, but follow the 11 - year cycle of solar activity.

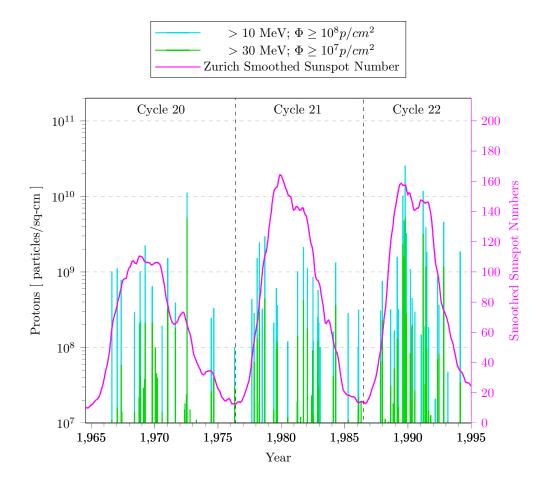

Figure 1.9 shows solar event proton fluences for solar cycles 20-22, superimposed over a plot of the sunspot number [Barth 1997].

High-fluence proton events occur during solar active years, Interestingly, the galactic cosmic ray flux is anti-correlated to the solar cycle, with maximum galactic cosmic ray flux occurring during solar minimum conditions [Nuntiyakul 2014].

After a solar flare occurs, particles begin to arrive near the earth within tens of minutes, peak in intensity within two hours to one day, and are gone within a few days to one week (except for some solar flare particles which are trapped in the earth's radiation belts).

In a solar flare, energetic protons, alpha particles and heavy ions are emitted. In most solar flares, the majority of emitted particles are protons (90-95%) and alpha particles. Heavy ions constitute only a small fraction of the emitted particles, and the number of heavy ions is normally insignificant compared to the background concentration of heavy ions from galactic cosmic rays. In a large solar flare, the number of protons and alpha particles can be greatly enhanced ( $10^4$  times) over the background galactic cosmic ray spectrum; whereas, the number of heavy ions for a large solar flare approaches up to 50% of the background galactic cosmic concentration of heavy ions [Adams 1981]. Associated with a solar flare is the solar

Figure 1.9: Correlation of proton solar event fluence to sunspot number for solar cycles 20-22. Sunspot number shown by the solid line plot [Barth 1997].

wind or solar plasma. The solar wind usually arrives near the earth within one to two days after a solar flare [Shea 1988]. As the solar wind strikes the magnetosphere, it can cause disturbances in the geomagnetic fields (geomagnetic storm), compressing them towards the earth. As a result, the solar wind can enhance the total dose received by devices in low-earth orbits.

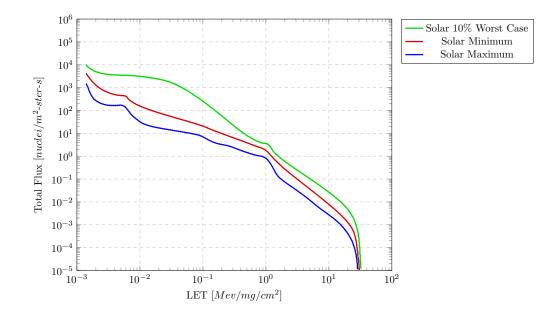

Figure 1.10: Flux of cosmic ray particles at solar maximum, at solar minimum, and for Adams's [Adams 1982] 10% worst-case environment.

Figure 1.10 is a plot of the angular flux of cosmic ray particles (both solar and galactic) during solar minimum and maximum inside a spacecraft in geosynchronous orbit with 25 mils of aluminum shielding as a function of the Linear Energy Transfer  $(\text{LET})^2$  [Adams 1982].

#### **1.2.2** Terrestrial Radiation Environment

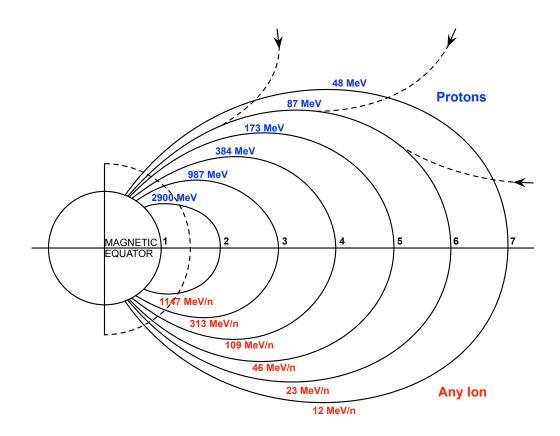

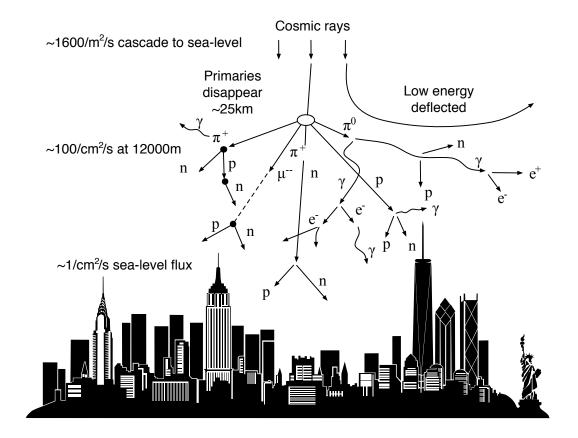

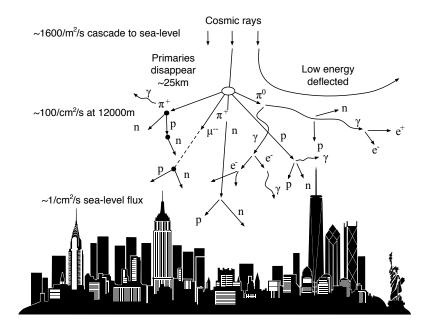

When cosmic rays reach the earth's atmosphere, they collide with atomic nuclei in air and create cascades of interactions and reaction products (Leptons, Photons, Hadrons), including neutrons, called air shower (Figure 1.12). Figure 1.11 shows the energy required for protons (blue) and other ions (red) to penetrate the magnetosphere [Stassinopoulos 1988].

<sup>&</sup>lt;sup>2</sup>The term linear energy transfer (LET) is frequently used to describe the energy loss per unit path length of a particle as it passes through a material. LET has units of  $MeV \cdot cm^2/mg$ . Because the energy loss per unit path length (in MeV/cm) is normalized by the density of the target material (in  $mg/cm^3$ ), LET may be quoted roughly independent of the target. It can easily relate the LET of a particle to its charge deposition per unit path length. In silicon, an LET of 97  $MeV \cdot cm^2/mg$  corresponds to a charge deposition of 1  $pC/\mu m$ .

Figure 1.11: Total energy required to penetrate the magnetosphere

Figure 1.12: Schematic view of cosmic rays causing cascades of particles

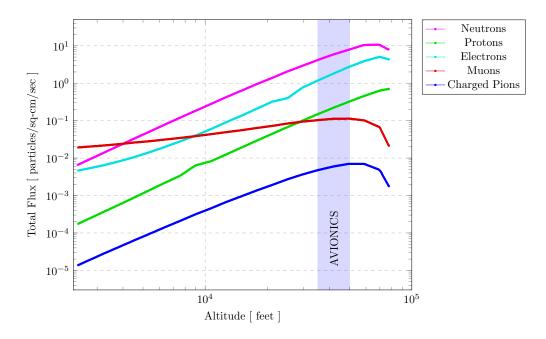

The intensity of cosmic-ray-induced neutrons (and other secondary cosmic radiation, including protons) in the atmosphere varies with altitude (Figure 1.13) [O'Brien 1971, O'Brien 1978], location in the geomagnetic field and solar magnetic activity. Atmospheric shielding at a given altitude is determined by the mass thickness per unit area of the air above, called areal density or atmospheric depth.

Figure 1.13: Particle Flux vs. Altitude at 54° Latitude [O'Brien 1971, O'Brien 1978]

The location and conditions for the *reference cosmic-ray-induced terrestrial neu*tron differential flux have been chosen to be New York City (Figure 1.12) outdoors at sea level at a time of average solar activity. Per the JEDEC specification [JESD89A 2006], the reference neutron flux in New York City is 13 neutrons/cm<sup>2</sup>/hour [Gordon 2004].

#### 1.2.2.1 Thermal Neutrons

Thermal Neutrons are neutrons that have lost kinetic energy until they reach a state where they are in thermal equilibrium with their environment. Certain nuclear fission reactions become much more probable with these low-energy neutrons and result in reactions yielding charged particles.

The most common such reaction is with the 10 - B isotope of boron. Boron is used as a p-type dopant and is also used as an implant in insulating layers formed of Boron Doped Phosphosilicate Glass (BPSG). Thermal neutrons can interact with these materials, and the charged particles generated from this reaction can induce soft errors [Baumann 2005].

Recent work on thermal neutrons [Fang 2014, Wen 2010a, Wen 2010b] has shown

that even when BPSG is not used in the fabrication process, devices can have a sensitivity to thermal neutrons.

#### 1.2.2.2 Muons

Atmospheric muons represent an important part of the natural radiation constraint at ground level. Muons belong to the Meson component in the atmospheric cosmic ray cascades and are the products of the decay of charged pions via the weak interaction. They constitute the most preponderant charged particles at sea level [O'Brien 1971, O'Brien 1978]. Muons are charged particles; both negative and positive muons can loss their kinetic energy by ionization process when they travel through matter [Serre 2012]. But this interaction with matter is tenuous and muons can travel large distances in matter, thus deeply penetrating into material circuits. Ziegler and Lanford have been the first authors to point out precisely how muons can interact with matter at relatively low incident primary energies [Ziegler 1979]. They decompose the interaction into three primary processes:

- 1. *Muon direct ionization wake*. A charged muon loses its kinetic energy passing through semiconductor material by excitation of bound electrons and frees electron-hole pairs along its path as a result.

- 2. *Electromagnetic scattering* which induces energetic coulomb silicon nucleus recoil.

- 3. Capture of the negative muons by atomic nuclei when they are quasi stopped in matter. This complex capture mechanism releases recoiling heavy nuclei with a simultaneous emission of light particles (neutrons, protons, deuterons,  $\alpha$  particles, etc.).

Muons-induced SEEs were predicted in a number of early works on microelectronic reliability: Wallmark and Marcus provided a brief investigation of the role of these particles as one of the fundamental physical limits to continued microelectronic scaling [Wallmark 1962]. Ziegler and Lanford provided a much expanded investigation of cosmic ray induced error rates and predicted the coming of a dramatic increase in errors with decreased critical charge [Ziegler 1979]. Recent Experimental results [Sierawski 2010, Sierawski 2011] indicate technology scaling increases the sensitivity of microelectronics to soft errors from low-energy muons.

#### 1.2.2.3 Alpha Particles

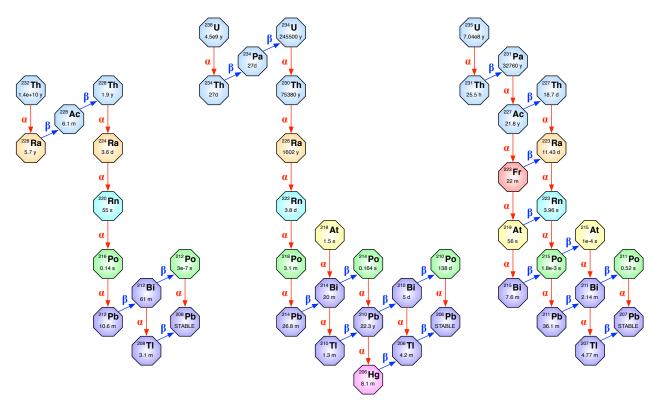

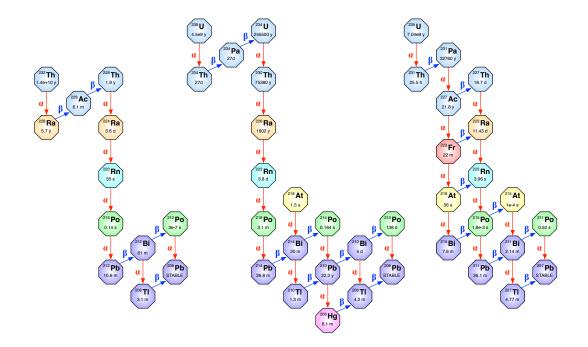

Alpha particles are a type of ionizing radiation emitted through the decay of unstable isotopes. They consist of two protons and two neutrons bound together into a particle identical to a helium nucleus. In semiconductor devices, the main source of alpha particles is from packaging materials. There are three radioactive decay chains (Figure 1.14) that are primarily responsible for the  $\alpha$  particles:

- 1. The Thorium chain, which starts with Thorium-232 and finishes with Lead-208.

- 2. The Uranium-238 chain, which starts with Uranium-238 and finishes with Lead-206.

- 3. The Uranium-235 chain, which starts with Uranium-235 and finishes with Lead-206.

Certain reactions along these decay chains result in the emission of an alpha particle as shown by the red arrows in Figure 1.14.

Figure 1.14: Thorium and Uranium Decay Chains.

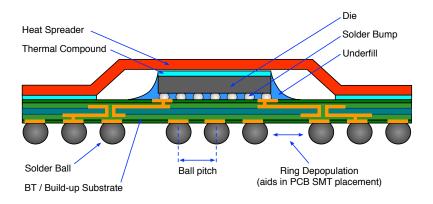

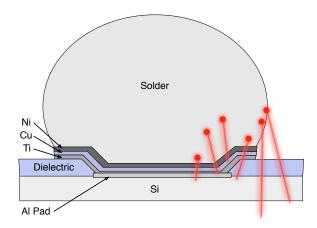

Alpha-particles-induced soft errors are primarily of concern for Ball Grid Array (BGA) packages, especially flip-chips. Figure 1.15 shows the cross section of a typical flip-flip package. Any materials that are within  $100\mu m$  of the die could potentially emit alpha particles that affect the die. The energy of alpha particles is attenuated as they traverse the Back End Of Line (BEOL) materials before they reach the substrate (Figure 1.16).

**Specifications of Materials Alpha Particle Emissivity** There are no formal definitions or standards (JEDEC, ISO, IEC, IEEE, etc.) for acceptable levels ma-

Figure 1.15: Cross Section of Typical Flip-Chip Package.

Figure 1.16: Cross-section schematic of a UBM and solder bump for a flip-chip interconnect.

terials alpha particle emissivity. The following two terms are commonly used in industry [Wilkinson 2011]:

- Low Alpha (LA) Low Alpha:  $emissivity \leq 0.05 \ \alpha/cm^2/hour$  (sometime expressed as  $50 \ \alpha \cdot khr^{-1} \cdot cm^{-2}$ )

- Ultra Low Alpha (ULA) Ultra Low Alpha:  $emissivity \leq 0.002 \alpha/cm^2/hour$  (sometime expressed as  $2 \alpha \cdot khr^{-1} \cdot cm^{-2}$ )

#### **1.3** Single Event Effects - Mechanism and Classification

Single Event Effects (SEEs) are induced by the interaction of an ionizing particle with electronic components. Ionizing particles can be primary (such as heavy ions in space environment or alpha particles produced by radioactive isotopes contained in the die or its packaging), or secondary (recoils) created by the nuclear interaction of a particle, like a neutron or a proton with silicon, oxygen or any other atom of the die.

Energetic Particles can ionize (directly or indirectly) atoms, generating electronhole pairs. As long as the energies of the generated electrons and holes are higher than the minimum energy required to create an electron-hole pair, these new electrons and holes can generate additional electron-hole pairs (A single, high-energy incident photon, electron, or proton can create thousands of electron-hole pairs).

This section describes the physical mechanisms that induce SEEs and to defines and classify the different ways they alter circuit operation. First, a brief introduction of nuclear physics, interaction mechanisms, and energy deposition, is given. Then, the effects observed in electronic devices will be defined and classified.

#### **1.3.1** Particles and Interactions

#### 1.3.1.1 Gamma and X-Ray Ionization

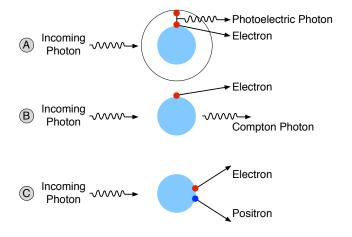

Photons interact with material through three different processes, namely the photoelectric (or fluorescent) effect, the compton effect, and pair production effect [McLean 1987]. These processes are illustrated in Figure 1.17. For each of these processes, the primary result of the interaction is the creation of energetic secondary electrons.

Low-energy photons interact with material predominantly through the photoelectric effect. The photoelectric effect is illustrated in Figure 1.17.a. The incident photon excites an electron from an inner shell of the target atom to a high enough state to be emitted free of the target atom. The incident photon is completely absorbed. Thus, the photoelectric effect creates a free electron (photoelectric electron) and an ionized atom. In addition, as the photoelectric electron is emitted, an electron in an outer orbit of the atom will fall into the spot vacated by the photoelectron causing a low-energy photon to be emitted. For higher-energy photons, Compton scattering is the most probable type of interaction. Compton scattering is illustrated in Figure 1.17.b. The photon collides with an atom and it transfers a fraction of its energy to an electron of the target atom, giving the electron sufficient energy to be emitted free of the target atom. For Compton scattering, a photon of lower energy is created which is free to interact with other target atoms. It can also create a free electron and an ionized atom.

Pair production occurs only for very-high energy photons (E > 3MeV). This process is illustrated in Figure 1.17.c. The incident photon collides with a target atom creating an electron-positron pair. A positron has the same properties as an electron (charge and mass), except that the charge is positive. The incident photon is completely annihilated in pair production.

Figure 1.17: Schematic drawing of three processes through which photons interact with material: a) photoelectric effect, b) Compton scattering, and c) pair production [McLean 1987].

#### 1.3.1.2 Energetic Particle Ionization

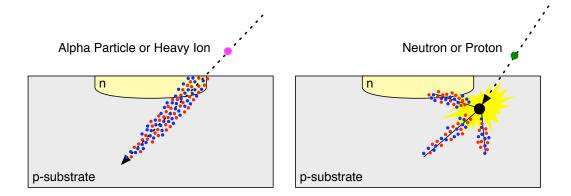

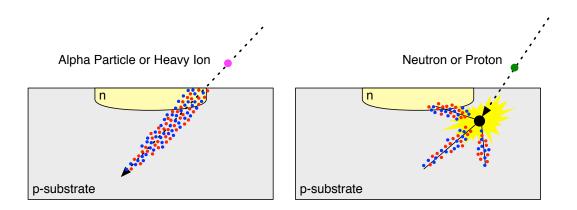

There are two primary methods by which energetic particle radiation releases charge in a semiconductor device: direct ionization by the incident particle itself, and ionization by secondary particles created by nuclear reactions between the incident particle and the struck device. Both mechanisms can lead to integrated circuit malfunction.

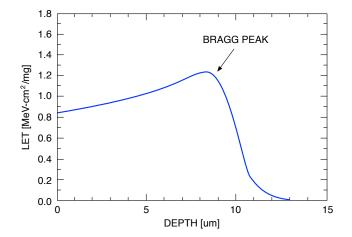

**Direct Ionization** As an energetic particle passes through a material, it loses energy by excitation and ionization of atoms, creating a very high density electronhole plasma along the path of the particle. The amount of energy that a particle deposits per unit depth in a material is given by its stopping power. The massstopping power is defined as the linear energy transfer, LET.

Figure 1.18: Particle Interactions Methods: Direct and Indirect Ionization

Figure 1.19: Stopping power (LET) versus depth for an alpha particle in silicon [Sexton 1992].

The integral of LET over path length gives the total deposited energy. Figure 1.19 [Sexton 1992] is a plot of stopping power (LET) for 2.5MeV alpha particle as a function of depth in silicon. The point of maximum stopping power is called the Bragg peak. The LET for a given particle depends on the target material and the particle's energy.

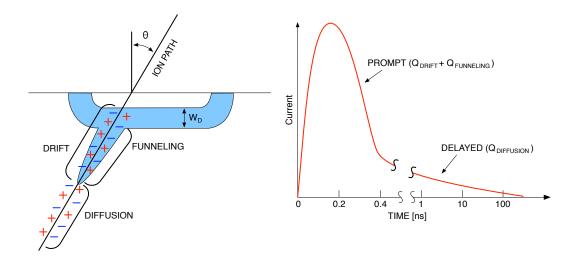

Figure 1.20: Schematic diagram and time dependence for charge collection by drift, funneling, and diffusion [Schwank 2008].

If an energetic particle passes through a p - n junction, charge can be collected at the electrodes by drift of carriers from the depletion region. The drift of carriers to the electrodes occurs within hundreds of picoseconds after a particle strike. This is represented as  $Q_D$  in Figure 1.20 [Schwank 2008].

The amount of charge that is collected by drift of carriers within the depletion region can be greatly enhanced by *field funneling* [Hsieh 1981] ( $Q_F$  in Figure 1.20). The density of the electron-hole created by the ion strike is considerably greater than the doping concentration of typical p-n junctions [McLean 1982]. The high concentrations of electron and holes in the plasma will distort the original depletion region of the junction along the path of the ion. As a consequence, the junction field region creates a *funnel region* that extends down into the substrate as depicted in Figure 1.20.

The funnel will exist as long as the concentration of electron-hole pairs in the plasma created by the ion strike is large compared to the doping concentration of the substrate. Diffusion of carriers to the edge of the junction depletion or funnel region contributes a another component to the collected charge. The diffusion of carriers takes much longer (nanoseconds to microseconds) than the drift component. The diffusion of carriers is noted as  $Q_{DF}$  in Figure 1.20.

**Indirect Ionization** Light particles (neutron and protons) usually [Weulersse 2011] do not produce enough charge to cause SEEs by direct ionization. However, protons and neutrons can both produce significant SEE rates due to indirect mechanisms. As a high-energy proton or neutron enters the semiconductor lattice it may undergo a nuclear interaction with a target nucleus. Any one of several nuclear reactions may occur, including:

- 1. Elastic Interaction

- 2. Inelastic Interaction

- 3. Inelastic Collision

- 4. Nuclear Fission

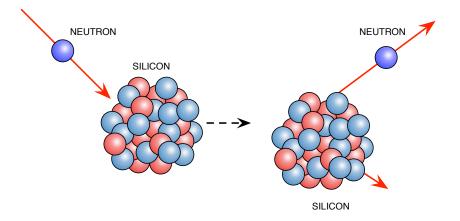

**Elastic Interaction** In the elastic process (Figure 1.21), the recoil nucleus is identical to the target nucleus. In the collision, the total kinetic energy and the momentum of the neutron-target nucleus system are conserved. A fraction of the energy of the neutron is given to the nucleus [Nicolaidis 2011, Chapter 2].

Figure 1.21: Elastic Interaction

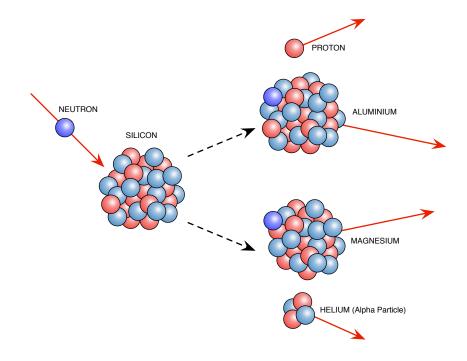

**Inelastic Interaction** Nonelastic interactions (spallation) group all the interactions that result in a fragmentation of the nucleus in two or more recoil fragments. Generally, the lighter recoil is indicated to describe the reaction: (n, p),  $(n, \alpha)$ , (n, d). The heavier element is obtained by the equilibrium of the number of neutrons and protons before and after the reaction. With <sup>28</sup>Si as the target nucleus, (n, p) reaction results in a proton and Al recoil while  $(n, \alpha)$  reaction results in He and Mgrecoils (Figure 1.22) [Nicolaidis 2011, Chapter 2].

Figure 1.22: Inelastic Interaction

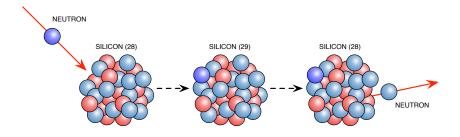

**Inelastic Collision -** (n, n') In this reaction, the incident neutron is absorbed in the target nucleus and a short time later a neutron is ejected with a lower energy, sharing a part of the total kinetic energy with the recoil target nucleus (Figure 1.23) [Nicolaidis 2011, Chapter 2].

Figure 1.23: Inelastic Collision

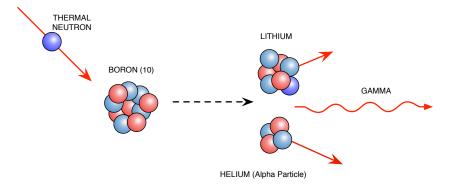

**Fission** Two isotopes of boron exist,  ${}^{10}B$  (19.1% abundance) and  ${}^{11}B$  (80.1% abundance). Different from other isotopes  ${}^{10}B$  is highly unstable when exposed to neutrons. Furthermore, while other isotopes emit only gamma photons after absorbing a neutron, the  ${}^{10}B$  nucleus fissions, producing an excited <sup>7</sup>Li recoil nucleus and an alpha particle (Figure 1.24). Although neutrons with any energy can induce

fission, the probability decreases rapidly with increasing neutron energy. Therefore, only thermal neutrons need to be considered [Nicolaidis 2011, Chapter 1].

Figure 1.24: Nuclear Fission

#### 1.3.1.3 Cumulative Radiation Effects

Electronics used in space or highly radioactive environments may be degraded due to the cumulative effect of exposure to radiation.

**Total Ionizing Dose** Total Ionizing Dose (TID) effect results from charge being trapped in the oxide layer and causing a change in the characteristics of the transistor. Cumulative long term ionizing damage due to protons and electrons can cause devices to suffer threshold voltage shifts, increased device leakage (power consumption), timing changes, decreased functionality, etc.

**Displacement Effects** Highly energized particles may displace atoms in the silicon lattice (Figure 1.25) of active devices and thereby affect their function. Bipolar devices and especially optical devices may be very sensitive to this effect. Complementary Metal Oxide Semiconductor (CMOS) integrated circuits are normally not considered to suffer degradation by displacement damage.

#### 1.3.2 Single Event Effects Classification

SEE is general term that groups all the possible effects induced by the interaction of an ionizing particle with electronic components. These effects are classified in hard errors and soft errors: Hard errors are non-recoverable errors. Soft errors may be recovered by a reset, a power cycle or simply a rewrite of the information. The following sections presents

Figure 1.25: Displacement Effect

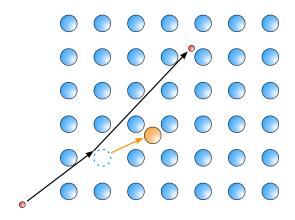

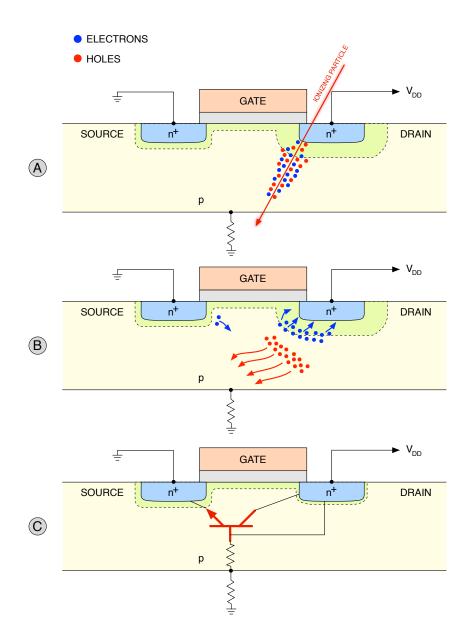

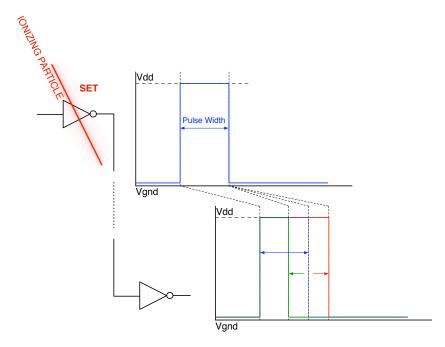

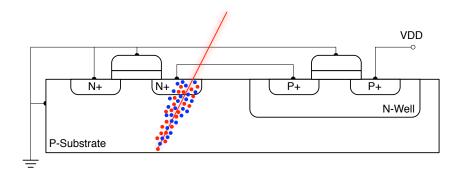

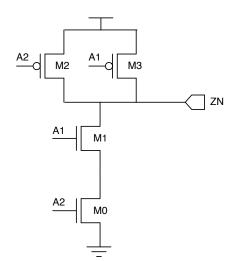

Figure 1.26: Single Event Transient production: interaction of an ionizing particle with an inverter.

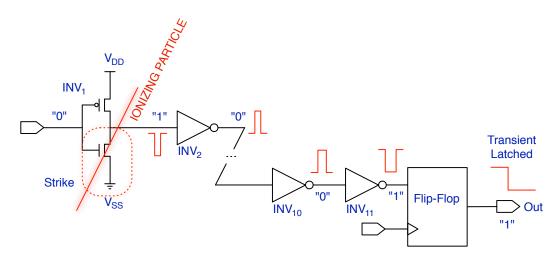

## 1.3.2.1 Soft Errors

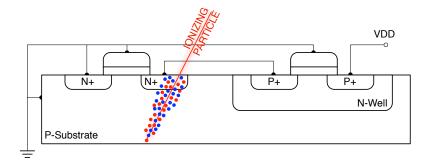

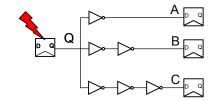

Single Event Transient Single Event Transients (SET) are momentary voltage or current disturbances affecting combinational gates. In the case where a single particle strike (the particle itself or its recoils) would affect two or more combinational gates, the SEE is called Single Event Multiple Transient (SEMT) [Harada 2011, Rossi 2005]. Although an SET does cause a transient in the gate output struck by the recoil ion, it may propagate through subsequent gates and eventually cause an Soft Error when it reaches a memory element (Figure 1.27 [Gadlage 2009]).

Figure 1.27: Single Event Transient: generation and propagation [Gadlage 2009].

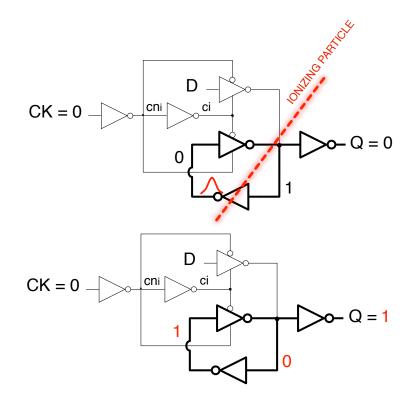

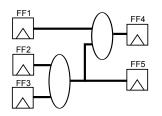

**Single Event Upset** A Single Event Upset SEU occurs when an ionizing particle strike modifies the electrical state of a storage cell, such that an error is produced when the cell is read. In an Static Random Access Memory (SRAM) or a flip-flop, the state of the memory is reversed. In a Dynamic Random Access Memory (DRAM), the charge stored can be slightly modified and interpreted as a wrong value by the read circuitry. In the case where a single particle strike (the particle itself or its recoils) would affect two or more combinational gates, the SEE is Single Event Multiple Upset (SEMU) [Dodd 2003].

Single Bit Upset, Multi Cell Upset, Multi Bit Upset - SBU, MCU, MBU Single Bit Upsets(SBUs) are events, equivalent to SEUs, induced in a memory by SEEs. The interaction of an ionizing particle with the memory is obviously dependent on the type of the memory. As an example, the production mechanism of the SBU in an SRAM device is similar to the SEU mechanism described earlier for sequential cells (Figure 1.28).

Figure 1.28: Single Event Upset mechanism.

In the case where a single particle strike (the particle itself or its recoils) would affect two or more memory cells, the SEE is called Multiple Cell Upset (MCU). If the physically neighborhood cells affected by particle interaction belong to the same logical word, then an Multiple Bit Upset (MBU) is produced.

The MCU/MBU analysis is particularly interesting when considering the eventual error protection mechanisms. SBUs are corrected by the most common errormitigation techniques - the Single Error Correct, Double Error Detect (SECDED) codes, such as the Hamming code. Thus, the SBUs in SECDED protected memories will not need particular care. However, the MBUs will not be corrected by this code, causing further errors in the circuit. The MBU probability can be considerably reduced by implementing column multiplexing.

**Single Event Functional Interrupt - SEFI** Single Event Functional Interrupt (SEFI) is a broad term that refers to an anomalous behavior observed in complex devices (flash memories, DRAM, SRAM, Field Programmable Gate Array (FPGA), microprocessors, micro-controllers, etc.). It can be the result of the upset of some registers or latches that are used in the configuration of the working modes of these complex devices. he effect of a SEFI is detectable and it does not result in permanent damage. A SEFI can be recovered by resetting or power-cycling the device.

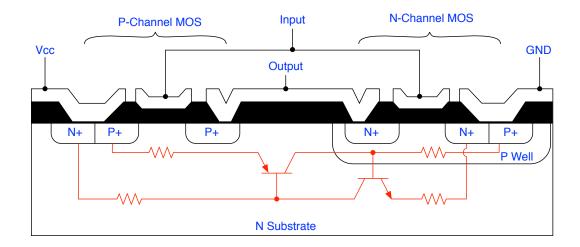

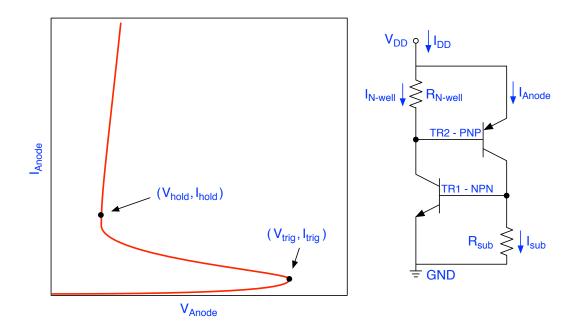

Single Event Latchup - SEL A Single Event Latchup (SEL) is a potentially catastrophic condition where a low resistance path develops between power supply and ground [Sexton 2003] on a device that remains after the triggering event is removed. When currents are sufficiently high metal traces can vaporize, bond wires can fuse open, and silicon regions can be melted due to thermal runaway. Once latched, this high current condition will continue until power is removed from the device or it fails catastrophically. Figure 1.29 shows the parasitic structure leading to latchup on the cross-section of a Bulk CMOS technology. Figure 1.30 shows the I - V characteristic of a latchup.

#### 1.3.2.2 Hard Errors

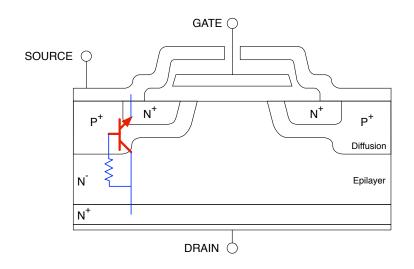

**Single Event Burnout - SEB** A Single Event Burnout (SEB) occurs when the passage of an energetic particle heavy ion causes a power Field Effect Transistor (FET) to enter second breakdown [Sexton 2003]. If not rapidly quenched, the resultant high current causes the device to go into thermal runaway resulting in destructive failure. Single Event Gate Rupture (SEGR) is often observed simultaneously with SEB in power Metal Oxide Semiconductor Field Effect Transistors(MOSFETs). Figure 1.31 shows the parasitic structure responsible of SEB on the cross-section of a vertical power MOSFET.

**Single Event Gate Rupture - SEGR** Single-Event Gate-Rupture (SEGR) is a condition where the gate dielectric isolating the gate and channel regions fails [Sexton 2003]. The SEGR process [Sexton 2003] is initiated when a heavy ion strikes

Figure 1.29: Structure Leading to Latchup Highlighted on the Cross-Section of a Bulk CMOS Technology (n-substrate material).

Figure 1.30: I-V Characteristic of a Latchup and Thyristor Formed by PNPN Junction.

Figure 1.31: Structure responsible of SEB Highlighted on the Cross-Section of a Vertical Power MOSFET

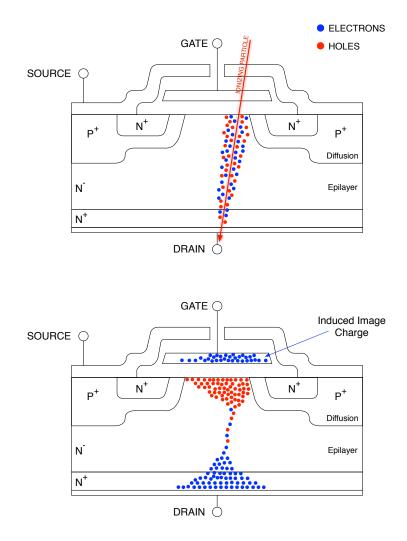

the device in the neck region (the neck region is the area between the p-body diffusions at the surface). The ion strike creates a filament of electron-hole pairs. For an n-channel power MOSFET, the generated holes drift toward the interface and the electrons toward the drain contact due to the electric field resulting from the positive drain bias. Upon reaching the interface, the holes start to pile up at the interface and leak off, only slowly, toward the source contact. This pool of positive charge increases the electric field in the oxide, and when the field exceeds a critical value, oxide breakdown occurs. The collected holes then discharge through the oxide, heating the structure locally. If the breakdown current lasts long enough, it creates a permanent short-circuit through the oxide. Figure 1.32 shows the SEGR mechanism.

Single Event induced Snap Back - SESB A Single Event induced Snap Back (SESB), is a stable regenerative condition similar to latchup, caused by drain-to-source breakdown in normal n-Metal Oxide Semiconductor (MOS) transistors [Sexton 2003]. Like latchup, a high current condition results that can cause permanent damage to a device. Unlike latchup, a p-n-p-n four layer structure is not necessary for snap back. For this reason, it is often referred to as transistor latchup.

All device types have the epitaxial n-layer on the highly doped n+ material. Since the off-state N-MOS transistors are responsible for the snapback in a CMOS circuit, we expect a well developed depletion region around the drain as shown in 1.33.a. Soon after the passage of an ion through the depletion region, the electronhole pairs commence movement along the field lines. Most electrons travel toward the drain, whereas the holes move mainly toward the source (Figure 1.33.b). Some holes, however, travel through the p-regions toward the ground plane. At this

Figure 1.32: SEGR Mechanism [Sexton 2003]

Figure 1.33: SESB Mechanism [Ochoa 1983]

stage the parasitic bipolar transistor can be turned on as shown in 1.33.c. Once the parasitic transistor is turned on and the regenerative breakdown condition has occurred, the transistor can be shut off only when the current between the drain and the source is reduced below the cut-off (sustaining) current level. The effect of funneling may accelerate the onset of the snapback. The introduction of the p-well feature slightly complicates the picture since additional parasitic (vertical) bipolar transistors become active. Nevertheless, the basic model describes the main snapback mechanism, i.e., a low resistance path is formed between the source and the drain of the off-state-N-MOSMOS transistor [Ochoa 1983].

## CHAPTER 2 Single Event Effect Analysis

### Contents

| 2.1 Intr | oduction                                     | <b>35</b> |

|----------|----------------------------------------------|-----------|

| 2.2 Tec  | hnology SER Characterization                 | 36        |

| 2.2.1    | Memory Intrinsic SER Characterization        | 36        |

| 2.2.2    | Standard Cell Intrinsic SER Characterization | 36        |

| 2.3 Mas  | sking Effects                                | 37        |

| 2.3.1    | Electrical De-Rating                         | 37        |

| 2.3.2    | Logic De-Rating                              | 37        |

| 2.3.3    | Temporal De-Rating                           | 39        |

| 2.3.4    | Functional De-Rating                         | 41        |

| 2.3.5    | Memory De-Rating                             | 43        |

| 2.4 Ove  | rall SER Computation                         | <b>43</b> |

## 2.1 Introduction

Hardware is intrinsically unreliable. External and internal perturbations can cause data corruption, faulty states and unpredictable circuit behavior. Single Events Effects (SEEs) represent a particularly representative example of such issues. SEEs are caused by energetic particles from the environment (neutrons, protons, heavy ions, muons, ...) or from the device's own materials (alpha particles emitted by radioactive contaminants).

Hardware (Low-level) faults represents the direct outcome of a Single Event on the output of the affected cell: Single Event Transients in combinational cells and Single Event Upsets in sequential cells. These faults must propagate in the logic network up to the input of a memorization element: a memory block or a sequential cell. Then, If the event is latched in the memorization element, the fault becomes a Soft Error. If the Soft Error causes an observable modification of the expected systems' behavior, then the Functional Failure is a usable concept for this occurrence. Analyzing the effect of faults induced by Soft Error (SE) in complex integrated circuits remains challenging. The vast majority of faults do not propagate due to the various de-rating (or masking effects): Electrical De-Rating (EDR), Logical De-Rating (LDR), TDR, Memory De-Rating (MDR) and Functional De-Rating (FDR). In the following sections, these de-rating (or masking) mechanisms are described.

In the following section will present the three main step of an Soft Error Rate (SER) analysis methodology: the technology SER characterization of standard cells and memory blocks, the various de-rating factors and finally the overall SER calculation. The SER methodology presented focuses on non-destructive SEEs: Bit Upsets in memory blocks and sequential cells, Transients in combinational cells.

## 2.2 Technology SER Characterization

The technology SER characterization is the first step of the presented SER methodology. Raw SER data should be provided in terms of raw (intrinsic) rate/probability of occurrence of logic SEU or SET for combinational, sequential and memory cells for a specific environment.

The final operating environment should be also carefully analyzed, of a particular interest to most commercial and aeronautical applications is the natural background, terrestrial environment characterized by a natural contribution of atmospheric neutrons and internal alpha particles from contaminants. The neutron SER is specific to the technology and the environment (altitude and localization). The alpha contribution depends strongly on the sensitivity of the cell to alpha particles and the alpha emissivity rate of the packaging materials.

## 2.2.1 Memory Intrinsic SER Characterization

SRAM memory blocks are prime targets for any reliability-related initiatives. Their high integration levels, reduced features size and small critical charge make them sensitive to Single Event Effects. Thus, the first task consists in characterizing the SEE performances of the memory instances with regard to Single Event Upsets affecting data stored in the memorization cells but also Single Event Effects on addressing/decoding/control logic. This analysis should concern both qualitative (type, manifestation and outcome of the events) and quantitative aspects (event rate/type for a given working environment).

The set of memory characterization data is comprised of: Single Bit Upset (SBU) rates and Multiple Cell Upset (MCU) rates for each possible pattern and Multiple Bit Upsets (MBU) rates for different column multiplexing configurations.

## 2.2.2 Standard Cell Intrinsic SER Characterization

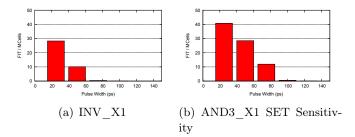

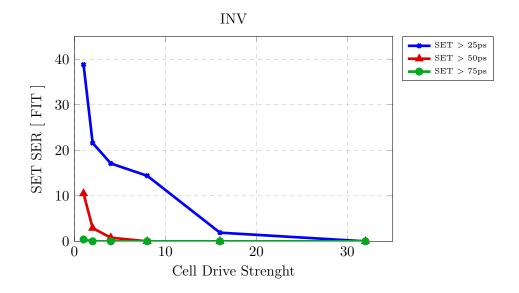

SEUs - Single Event Upsets affecting the sequential cells of the design have an obvious impact on the circuit reliability. Single Event Transients - SETs affecting combinational cells are much more difficult to characterize: the transient pulses at the output of the cell have various shapes, amplitudes and durations. Moreover, the SET parameters strongly depend on the state and the neighborhood of the cell. Lastly, the standard cell library may contain an order of magnitude more

combinational cells with various functions and drive strengths than sequential cells, requiring an adequate characterization effort through radiation testing or simulation. Moreover, the actual cell behavior also depends on the circuit implementation and the usage of the cells for a given workload. The fan-out of a combinational cell will have a strong impact on SET characteristics. The signal values on the inputs of the cells will determine the sensitive transistors and implicitly the occurrence probability of the SEE

Standard cell SER characterization data should be provided in terms of raw (intrinsic) rate/probability of occurrence of logic SEU or SET for combinational and sequential cells for a given environment. Pulse width distributions of logic, rectangular SETs should be also provided.

## 2.3 Masking Effects

Not all radiation induced faults propagate and produce errors because of the numerous masking effects. The raw rate of faults can be de-rated to obtain an effective error rate using a de-rating factor. In this work, a de-rating factor of 1 indicates that all faults propagate and a value of 0 indicates that all faults are blocked. The definitions are important as some authors use the term masking factor to indicate the fraction of faults that are masked, which is the opposite of a de-rating factor.

## 2.3.1 Electrical De-Rating

The Electrical De-Rating (EDR) quantifies the electrical attenuation of an SET and thus its capability to propagate through the logic network.

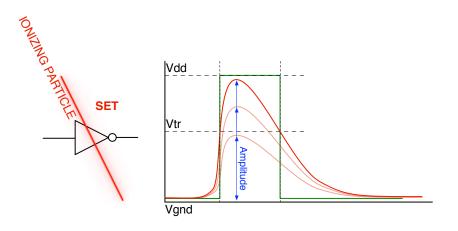

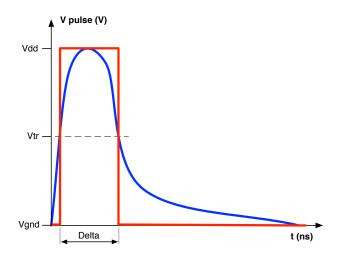

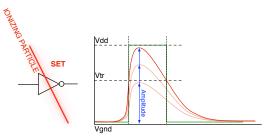

One aspect of electrical de-rating is accounted for by considering how the induced analog pulse is mapped to a digital pulse. The shape of a radiation induced pulse is shown in Figure 2.1 and based on the logic threshold voltage, it can be modeled as a digital pulse of width Pulse Width (PW). Pulses whose amplitude never reaches  $V_{th}$  are masked [Hane 2008, Tanaka 2009]. A further aspect of EDR relates to the fact that when the pulse duration is short (comparable to the gate rise/fall times), it may be attenuated as it passes through downstream gates.

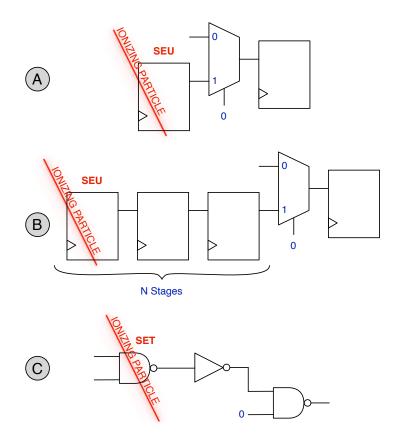

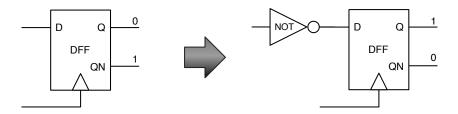

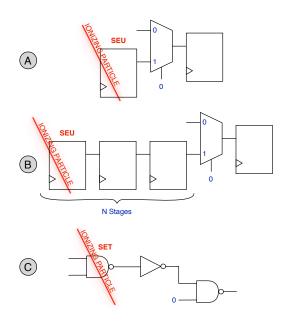

## 2.3.2 Logic De-Rating

Logic De-Rating (LDR) consists in evaluating the propagation of the logic fault from the output of the affected cell to the inputs of a sequential/memory cell. According to the state of the circuit (the values of the signals and cell outputs), the propagation of the fault is subject to logic blocking [Vilchis 2012], [Nicolaidis 2011, Chapter 5]. Figure 2.2 presents the concept of Logic De-Rating for SEUs: within the clock cycle when it occurs (figure 2.2.a) and over several clock cycles (figure 2.2.b). And for SET (figure 2.2.c).

Figure 2.1: Electrical De-Rating

Figure 2.2: Logic De-Rating of SEUs and SETs

## 2.3.3 Temporal De-Rating

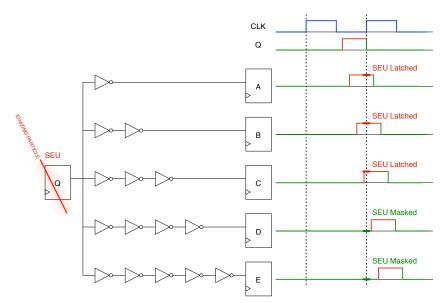

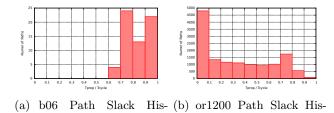

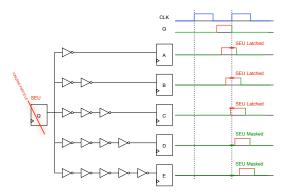

Temporal de-rating (TDR<sup>1</sup>) relates to the *opportunity window* of a fault (SET or SEU) to be latched in a down-stream memorizing element (Flip-Flop, Latch, Memory). If the fault is not stored in a register or a memory cell, there is no impact in the functioning of the circuit (the fault is dropped). The memorization of the fault depends on its type:

**SEU Temporal De-Rating** SEUs must arrive in the affected register early in the clock period in order to propagate through the logic network and reach the next sequential stage. Figure 2.3 shows the cases of masked and unmasked SEUs.

An SEU affecting a sequential cell, unless logically-masked, will propagate through the downstream logic combinational network and reach the next sequential logic stage. The SEU will remain on the flip-flop outputs until the next latching (clock) cycle.

Figure 2.3: SEU Temporal derating

Since the SEU arrival is a random phenomenon (likewise to the SET) the SEU Temporal De-Rating is defined as the ratio between the *opportunity window* and the clock period; the opportunity window depends on the paths' delay and on the setup/hold times of the downstream flip-flop. The TDR is given by equation 2.1 [Nicolaidis 2011, Chapter 5].

$$SEU Temporal De-Rating = \frac{t_{slack} + \frac{t_{setup}}{2} - \frac{t_{hold}}{2}}{T_{clock}}$$

(2.1)

<sup>&</sup>lt;sup>1</sup>In some works [Seifert 2004, Ghahroodi 2011, Bramnik 2013, Nguyen 2005] the term Temporal Vulnerability Factor (TVF) is used instead of TDR

If the downstream paths are relaxed (high slack), the opportunity window for a SEU is quite large. If the flip-flop belongs to the critical path or similarly-timed paths, the slack is very low and thus the opportunity window is reduced, with a sharp decrease in the TDR values. Intuitively, it is clear that the same circuit will exhibit worse sequential SER values at lower clock frequencies.

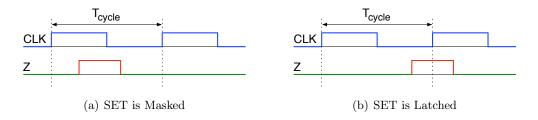

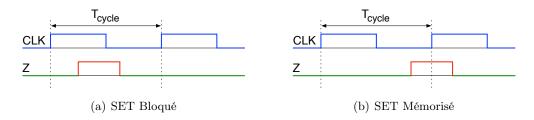

**SET Temporal De-Rating** SETs must cause an incorrect value on the input of a memorizing element during the latching window. Figure 2.4 shows the cases of masked (figure 2.4(a)) and unmasked (figure 2.4(a)) SET. Single Event Transients manifest as short pulses on the output of the affected cell. SETs are possible in the case of combinational cells but also in the case of sequential elements such as flip-flop and latches when the Single Event only affects the output stages but not the inner memorization loop [Alexandrescu 2013].

Figure 2.4: SET Temporal De-Rating

An SET, unless logically-masked, will propagate through the downstream logic combinational network and reach the next sequential logic stage. The TDR represents probability of the SET to be memorized. Since the SET is a random phenomenon, the TDR depends on to the pulse width (PW) and the clock period. To a first approximation, the TDR is proportional to the ratio of the induced pulse width to the clock period as shown in equation 2.2, where  $p_i$  is the probability of having a transient with PW = i.

$$TDR_{SET} = \frac{\sum_{i=minPW}^{maxPW} p_i \cdot i}{T_{clk}}$$

(2.2)

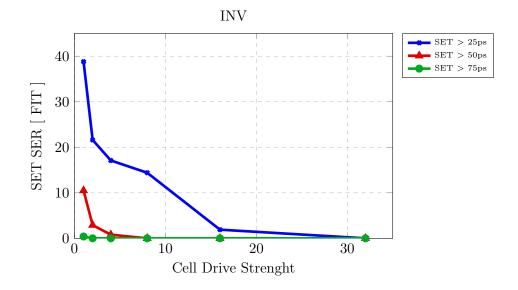

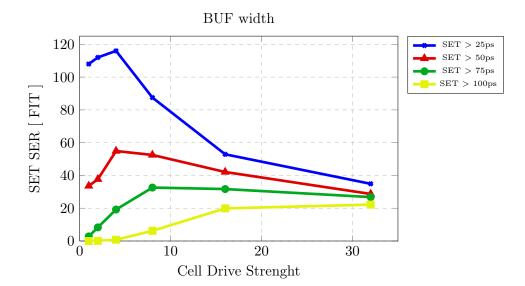

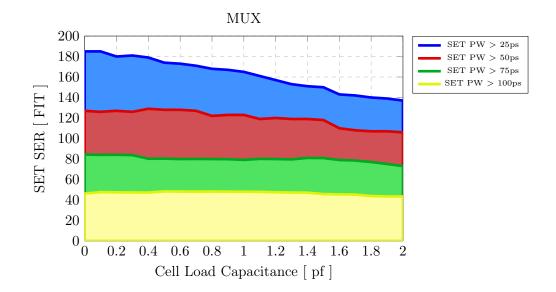

For recent technology nodes, most of the combinational cells exhibit pulse duration of tens/hundreds picoseconds [Evans 2013b, Costenaro 2013a], which is still low with regard to nanosecond-clock period. Thus the temporal de-rating is strong for the SETs and will reduce their relative criticality. However, extensive test results have shown that at higher frequencies, the TDR factor increases and the effect of SETs is more severe [Mahatme 2011, Nguyen 2005, Gill 2009].

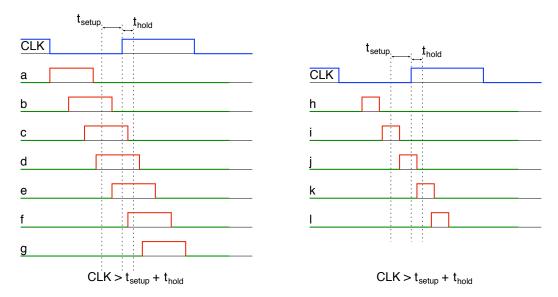

In figure 2.5 the possible alignments of a pulse compared to the sampling clock edge are shown, both for the case when the pulse is longer and shorter than the setup-hold window. For the cases of  $PW > t_{setup} + t_{hold}$ , the *Overlapping Width*, OW, is defined to be the extent of the pulse that lies within the setup-hold window.

The error capture probability is taken to be proportional to the ratio of OW to the full setup-hold window:  $\frac{OW}{t_{hold}+t_{setup}}$ . For the cases of  $PW < t_{setup} + t_{hold}$ , the two violation cases are considered

For the cases of  $PW < t_{setup} + t_{hold}$ , the two violation cases are considered together, and the error latching probability is taken to be linear with the overlapping width ratio as before. A SET can occur at any time in the clock period with a uniform probability. In both cases above, averaged over the full clock period, the overall error latching probability is  $\frac{PW}{T_{clk}}$ . The calulated error probability for each case is shown in table 4.5

Figure 2.5: SET Pulse Alignment Cases Evans 2013a, Costenaro 2013b

It is important to note that in this analysis, the pulse width of interest is that at the input to the sampling flip-flop. The shape of a radiation induced pulse may be distorted as it propagates through a combinatorial network. This effect is referred to as Propagation Induced Pulse Broadening (PIPB) (Figure 2.6) and has been extensively studied in [Cavrois 2008, Sterpone 2011, Ferlet-Cavrois 2010].

## 2.3.4 Functional De-Rating

Functional De-rating (FDR) [Silburt 2009], [Nicolaidis 2011, Chapter 5] evaluates whether the Soft Error has any observable impact (failure classes) on the functioning of the circuit, board or system. It takes in account the actual usage of the circuit and the function of the system.

The *observability* criteria could involve both objective and subjective aspects to discriminate between the fault-free and faulty states of the system. An objective example of the discrimination criteria could be the comparison of the primary outputs of the circuit under test to the reference, fault-free ones. Any difference could be legitimately classified as a failure. However, a subjective observer may add his

| Table  | 2.1:    | SET   | Pulse | Alignment | and | Capture | Probabilities | [Evans 2013a, |

|--------|---------|-------|-------|-----------|-----|---------|---------------|---------------|

| Coster | naro 20 | )13b] |       |           |     |         |               |               |

| Pulse Width                 | Case | Case Error Prob.                                                                                           | Comments              |

|-----------------------------|------|------------------------------------------------------------------------------------------------------------|-----------------------|

|                             | а    | 0.0                                                                                                        | Correct value latched |

|                             | b    | $\frac{1}{T_{clk}} \cdot \int_0^{t_{setup}} \frac{OW}{t_{hold} + t_{setup}} \mathrm{d}OW$                  | Set-up time violation |

|                             | с    | $\frac{1}{T_{clk}} \cdot \int_{t_{setup}}^{t_{setup}+t_{hold}} \frac{OW}{t_{hold}+t_{setup}} \mathrm{d}OW$ | Hold time violation   |

| $PW > t_{setup} + t_{hold}$ | d    | $\frac{\overline{T_{clk}} \cdot J_{t_{setup}}}{\frac{PW - t_{setup} - t_{hold}}{T_{clk}}} dOW$             | Wrong value latched   |

|                             | е    | $\frac{1}{T_{clk}} \cdot \int_{t_{hold}}^{t_{setup}+t_{hold}} \frac{OW}{t_{hold}+t_{setup}} \mathrm{d}OW$  | Set-up time violation |

|                             | f    | $\frac{1}{T_{clk}} \cdot \int_0^{t_h old} \frac{OW}{t_{hold} + t_{setup}} \mathrm{d}OW$                    | Hold time violation   |

|                             | g    | 0.0                                                                                                        | Correct value latched |

|                             | h    | 0.0                                                                                                        | Correct value latched |

|                             | i    | $\frac{1}{T_{clk}} \cdot \int_0^{t_{setup}} \frac{OW}{t_{hold} + t_{setup}} \mathrm{d}OW$                  | Set-up time violation |

| $PW < t_{setup} + t_{hold}$ | j    | $\frac{PW \cdot (t_{hold} + t_{setup} - PW)}{T_{clk} \cdot (t_{hold} + t_{setup})}$                        | Metastability         |

|                             | k    | $\frac{1}{T_{clk}} \cdot \int_0^{t_{hold}} \frac{OW}{t_{hold} + t_{setup}} \mathrm{d}OW$                   | Hold time violation   |

|                             | 1    | 0.0                                                                                                        | Correct value latched |

| Overall                     | -    | $\frac{PW}{T_{clk}}$                                                                                       | -                     |

Figure 2.6: Propagation Induced Pulse Broadening - PIPB

own weight/criticality to the observed difference. The recorded primary output difference may not be relevant for specific cases or applications, removing the observed failure.

The failure classification implies some degree of subjectivity, since a criticality parameter can be also added to the fault classes. Furthermore, the usage of the circuit will have a strong impact on the failure analysis, since different function modes/applications will exhibit different SE-related failures. If the circuit under test has a clearly-stated function, then the functional de-rating will have to consider this specific functions and the effect of relevant parameters. However, for generalpurpose circuits such as CPUs, the possible application field is quite large, thus rendering the FDR analysis much more complex.

As stated, the FDR computation takes in account the propagation of the Soft Error during several clock cycles. The implied goal is to evaluate whether the SE

- has been silently discarded (dropped), without any further impact on the functioning of the circuit

- remains in the circuit in a latent state without any observable degradation of the function or structure of the circuit

- produces a functional failure.

Differently from the other derating factors, the FDR is not a *single* number but, for a given application, there will be as many FDRs as the number of failure classes considered.

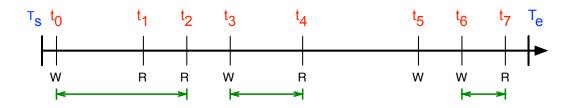

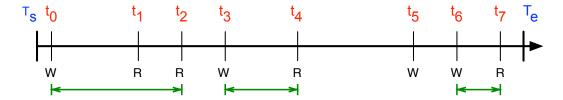

## 2.3.5 Memory De-Rating

The Memory De-Rating [Alexandrescu 2011] represents the portion of time during which the data stored in a memory will eventually be read and thus used by the application. This metric is called *vulnerability window* and it corresponds to the time between a write access to an address and the last read access to that address before the end of the simulation or before another write access to that address (Figure 2.7). Oppositely, during the time between the last read access and a write access, the data is still in the memory but will not be used by the circuit. If an upset occurs during this time, it will have no effect because the corrupted data will never be read and will be overwritten by the write access. Figure 2.7 shows a series of read and write accesses to a memory address; the corresponding memory derating is given by equation 2.3.

Memory De-Rating =

$$\frac{(t_2 - t_0) + (t_4 - t_3) + (t_7 - t_6)}{T_e - T_s}$$

(2.3)

## 2.4 Overall SER Computation

The overall SER analysis combines the data obtained from the technology SER characterization with the de-rating information to provide an application and environment-

Figure 2.7: Sequence of memory accesses

dependent SER figures for the considered design.

For a given application and considering a specific failure class j, the failure rate for a *chip* can be calculated with the following equations:

$$SER_{chip,j} = SER_{sequential,j} + SER_{comb,j} + SER_{memory,j} + SER_{clock,j}$$

(2.4)

The contribution, to the overall failure rate, of the sequential portion of the circuit can be calculated with the following equations:

$$SER_{sequential,j} = \sum_{i \in FlipFlop} SEU - FIT_i \cdot LDR_i \cdot TDR_i \cdot FDR_{i,j}$$

(2.5)

$$SER_{comb,j} = \sum_{i \in Gate} FDR_{i,j} \cdot LDR_{i,j} \cdot \int_{w=min}^{w=max} SET - FIT_i(w) \cdot TDR_i(w) \cdot EDR_i(w) dw$$

(2.6)

$$SER_{memory,j} = \sum_{i \in Memory} FIT(i) \cdot MDR_{i,j}$$

(2.7)

where:

- *j* represents a class of failure (all equations)

- SEU- $FIT_i$  represents the intrinsic rate of occurrence of SEUs for the sequential instance instance *i* (equation 2.5)

- w represents the pulse width(equation 2.6)

- SET- $FIT_i(w)$  represents the intrinsic rate of occurrence of SETs for the combinational instance instance *i* (equation 2.6)

- FIT(i) represents the uncorrectable error rate for the memory instance *i* (equation 2.7)

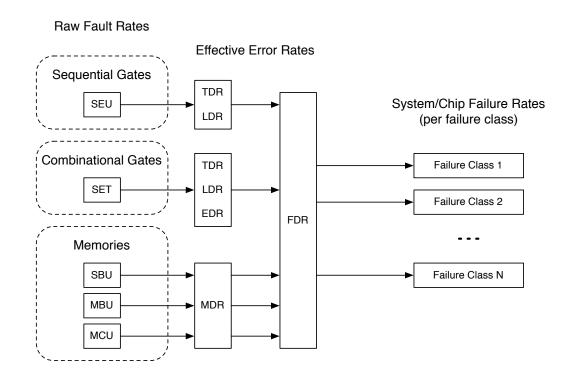

A high-level view of the SER analysis from faults to system level failures is shown in figure 2.8 [Evans 2014]. On the left are the faults that can be induced in flip-flops, logic gates and memories. In the middle the de-rating effects and on the right the failure rate per each failure class.

Figure 2.8: Soft Error Effect Analysis [Evans 2014]

# CHAPTER 3 Single Event Transient Analysis

## Contents

| 3.1        | Intro | oduction  |                                                                | <b>47</b> |

|------------|-------|-----------|----------------------------------------------------------------|-----------|

| <b>3.2</b> | SET   | Charact   | terization of the Standard Cell Library                        | <b>49</b> |

|            | 3.2.1 | TFIT O    | verview                                                        | 51        |

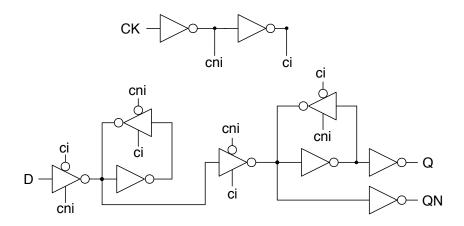

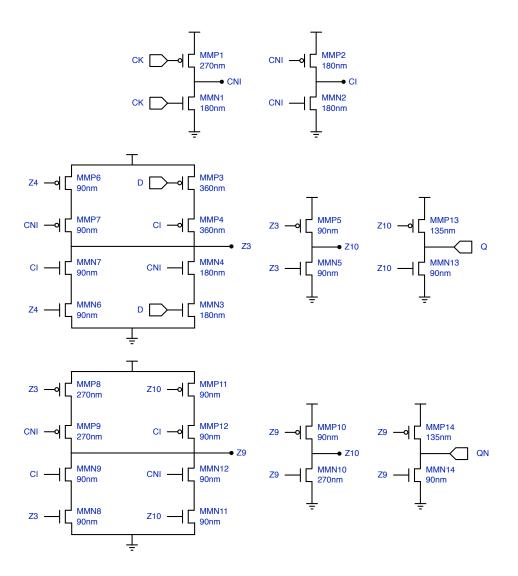

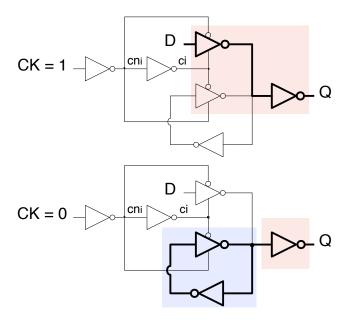

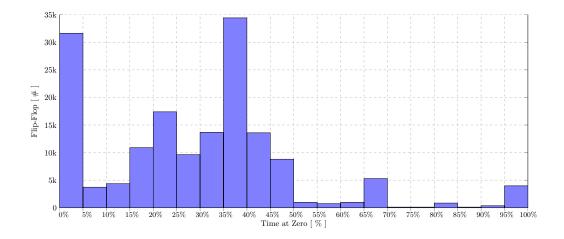

|            |       | 3.2.1.1   | Technology Response Model                                      | 51        |