# Characterization and design of architectures for phase-change memories based on alternative-to-GST materials

Athanasios Kiouseloglou

#### ▶ To cite this version:

Athanasios Kiouseloglou. Characterization and design of architectures for phase-change memories based on alternative-to-GST materials. Micro and nanotechnologies/Microelectronics. Université Grenoble Alpes; Università degli studi (Pavie, Italie), 2015. English. NNT: 2015GREAT128. tel-01278433

#### HAL Id: tel-01278433 https://theses.hal.science/tel-01278433

Submitted on 24 Feb 2016

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

#### **THÈSE**

Pour obtenir le grade de

# DOCTEUR DE L'UNIVERSITÉ GRENOBLE ALPES préparée dans le cadre d'une cotutelle entre l'Université Grenoble Alpes et l'Université de Pavia

Spécialité : Nano Électronique et Nano Technologies et Microélectronique

Arrêté ministériel : le 6 janvier 2005 - 7 août 2006

Présentée par

#### Athanasios KIOUSELOGLOU

Thèse dirigée par Fabien CLERMIDY et codirigée par Guido TORELLI

préparée au sein du CEA-LETI dans l'École Doctorale Électronique, Electrotechnique, Automatique et Traitement du Signal (UGA) et au sein du Laboratoire des Microsystèmes Intégreés du Dipartimento di Ingegneria Industriale e dell'Informazione

dans l'École Doctorale de Sciences de l'Ingenierie (UniPV)

# Caractérisation et conception d'architectures basées sur des mémoires à changement de phase

Thèse soutenue publiquement le **17 décembre 2015** devant le jury composé de :

Monsieur Jean-Michel PORTAL

Prof., Université d'Aix-Marseille (France)

Monsieur Alessandro SPINELLI

Prof., Politecnico di Milano (Italie)

Monsieur Alessandro CABRINI

Ing., Université de Pavia (Italie)

Monsieur Fabien CLERMIDY

HDR, CEA-LETI, Grenoble (France)

Monsieur Luca PERNIOLA

Ing., CEA-LETI, Grenoble (France)

Monsieur Guido TORELLI

Prof., Université de Pavia (Italie)

Monsieur Jean-Michel MIRABEL

Ing., STMicroelectronics, Rousset (France)

Encadrant

Rapporteur

Encadrant

Co-Directeur de thèse

Directeur de thèse

Président rapporteur

Invité

# Contents

| C  | Contents                                           |         |                                              |    |  |  |

|----|----------------------------------------------------|---------|----------------------------------------------|----|--|--|

| A  | Abstract - Résumé                                  |         |                                              |    |  |  |

| A  | ckno                                               | wledge  | ments                                        | v  |  |  |

| In | trod                                               | uction  |                                              | 1  |  |  |

| 1  | Soli                                               | d-Stat  | e Memory Technologies                        | 5  |  |  |

|    | 1.1                                                | Solid-S | State Memories - An Overview                 | 7  |  |  |

|    |                                                    | 1.1.1   | Static Random Access Memory - SRAM           | 11 |  |  |

|    |                                                    | 1.1.2   | Dynamic Random Access Memory - DRAM          | 12 |  |  |

|    |                                                    | 1.1.3   | Flash Memory                                 | 14 |  |  |

|    |                                                    | 1.1.4   | Magnetoresistive Random Access Memory - MRAM | 19 |  |  |

|    |                                                    | 1.1.5   | Ferroelectric Random Access Memory - FeRAM   | 21 |  |  |

|    |                                                    | 1.1.6   | Resistive Random Access Memory - ReRAM       | 23 |  |  |

|    | 1.2                                                | Phase   | Change Memory                                | 27 |  |  |

|    |                                                    | 1.2.1   | Historical Background                        | 27 |  |  |

|    |                                                    | 1.2.2   | Phase Change Materials                       | 28 |  |  |

|    |                                                    | 1.2.3   | Operation Principle                          | 31 |  |  |

|    |                                                    | 1.2.4   | The Crystalline Phase                        | 33 |  |  |

|    |                                                    | 1.2.5   | The Amorphous Phase                          | 35 |  |  |

|    |                                                    | 1.2.6   | Phase Change Memory Cell Architectures       | 40 |  |  |

|    |                                                    | 1.2.7   | PCM Applications and Challenges              | 44 |  |  |

|    | 1.3                                                | Summ    | ary of the Chapter                           | 52 |  |  |

| 2  | Performance Optimization of Phase Change Memory 58 |         |                                              |    |  |  |

|    | 2.1                                                | Electr  | ical Characterization of the PCM Cell        | 56 |  |  |

|    |                                                    | 2.1.1   | Main Electrical Parameters                   | 56 |  |  |

|    |                                                    | 2.1.2   | Thermal Parameters                           | 58 |  |  |

|    |                                                    | 2.1.3   | The Device                                   | 59 |  |  |

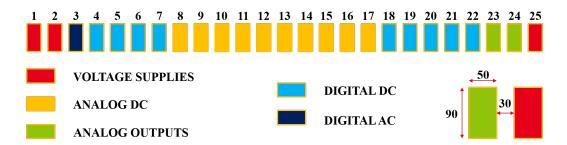

|    |                                                    | 2.1.4   | The Equipment                                | 62 |  |  |

|    | 2.2                                                | Phase   | Change Memory Reliability                    | 63 |  |  |

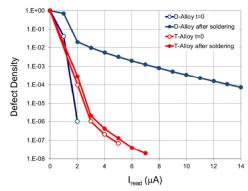

|    |                                                    | 2.2.1   | Cycling Endurance                            | 65 |  |  |

|    |                                                    | 2.2.2   | Data Disturbs                                | 66 |  |  |

|    |                                                    | 2.2.3   | Data Retention                               | 67 |  |  |

|    |                                                    | 224     | Resistance Drift                             | 68 |  |  |

ii Contents

|              | 2.3                | Phase Change Material Engineering                 | 69  |  |  |  |

|--------------|--------------------|---------------------------------------------------|-----|--|--|--|

|              |                    | 2.3.1 N-doped GST                                 | 70  |  |  |  |

|              |                    | 2.3.2 C-doped GST                                 | 72  |  |  |  |

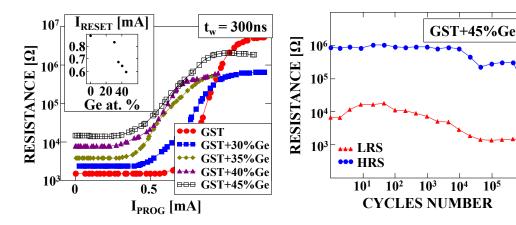

|              |                    | 2.3.3 Ge-rich GST                                 | 75  |  |  |  |

|              | 2.4                | Experimental results                              | 77  |  |  |  |

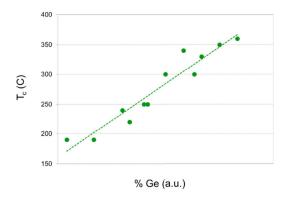

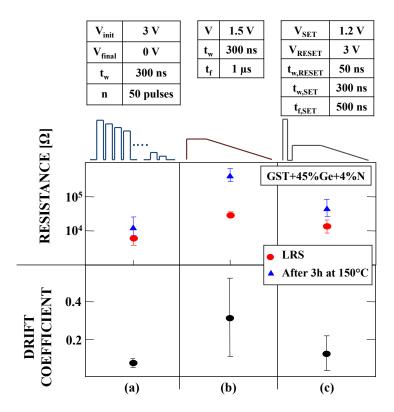

|              |                    | 2.4.1 Thermal Stability                           | 78  |  |  |  |

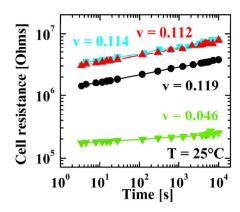

|              |                    | 2.4.2 Drift of the Low Resistance State           | 82  |  |  |  |

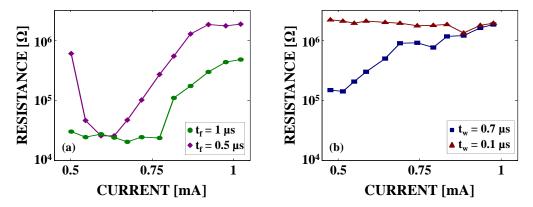

|              |                    | 2.4.3 Crystallization Speed                       | 85  |  |  |  |

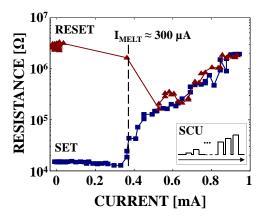

|              | 2.5                | The R–SET Pulse                                   | 87  |  |  |  |

|              | 2.6                | Summary of the Chapter                            | 91  |  |  |  |

| 3            | Inn                | ovative PCM Circuit Design                        | 93  |  |  |  |

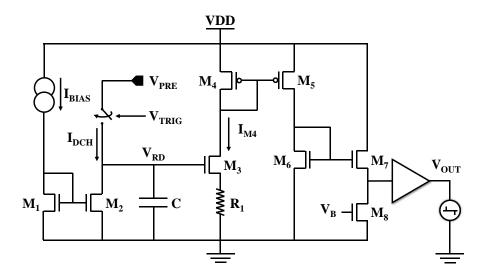

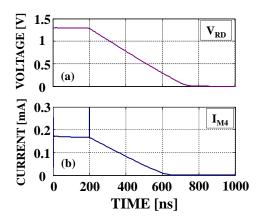

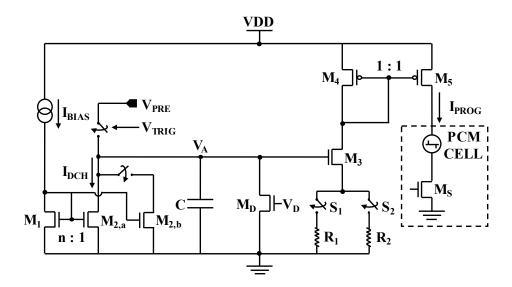

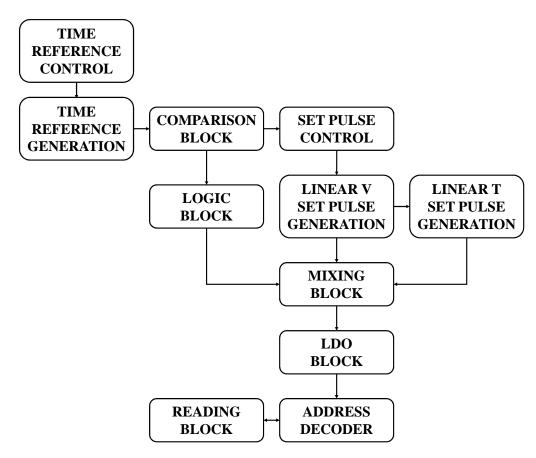

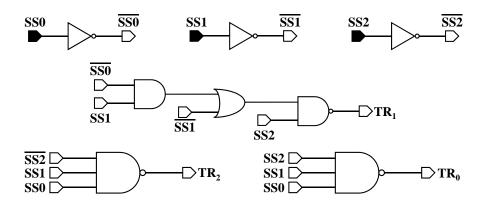

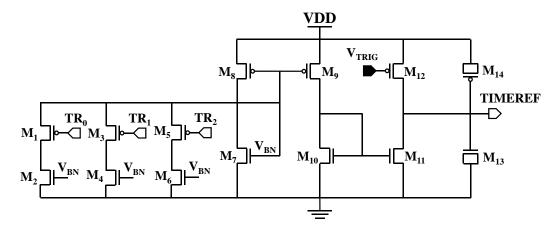

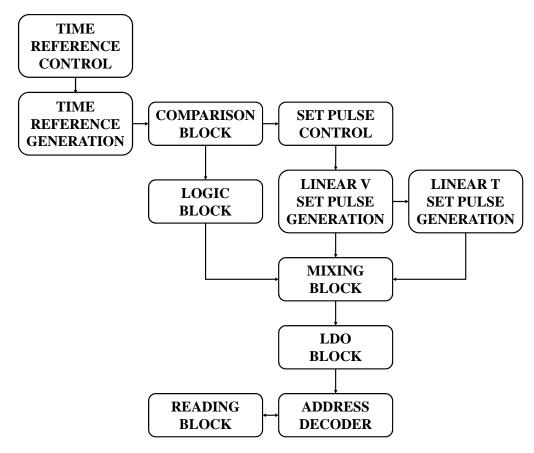

|              | 3.1                | The R-SET Pulse Generator                         | 94  |  |  |  |

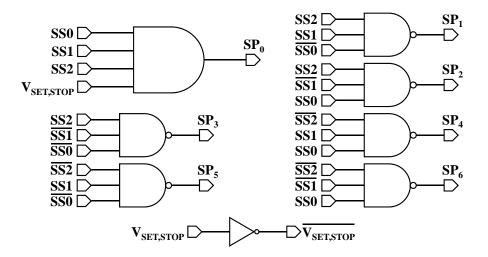

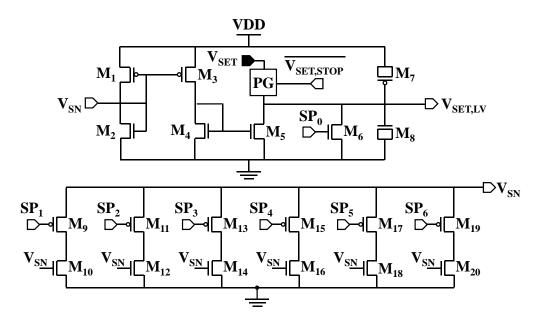

|              |                    | 3.1.1 Circuit Operation                           | 95  |  |  |  |

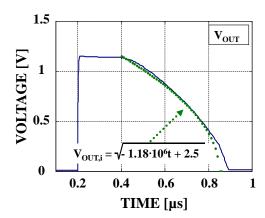

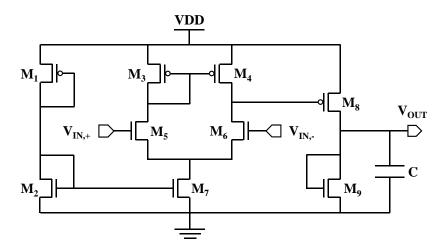

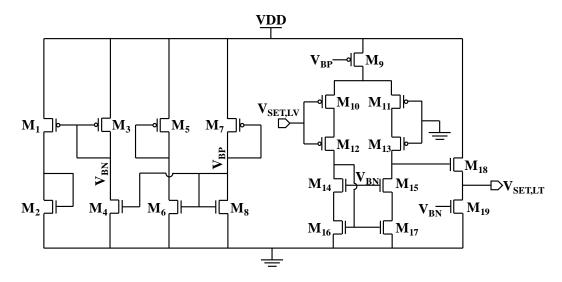

|              | 3.2                | Pulse Generator for Optimized Temperature Profile | 103 |  |  |  |

|              |                    | 3.2.1 Voltage Controlled Temperature              | 103 |  |  |  |

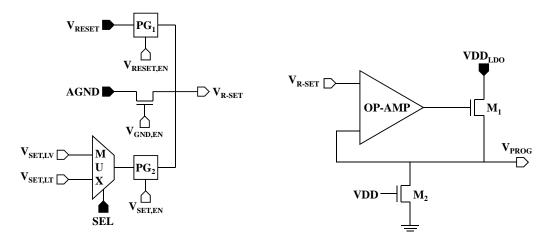

|              |                    | 3.2.2 On-Chip Implementation Design               | 104 |  |  |  |

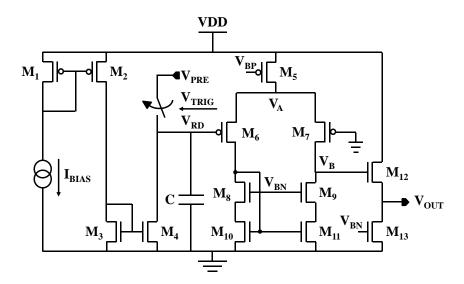

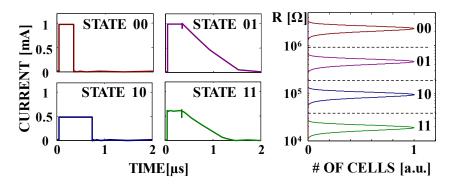

|              | 3.3                | Multilevel Cell Programming Circuit               | 111 |  |  |  |

|              |                    | 3.3.1 MLC Programming Algorithm                   | 111 |  |  |  |

|              |                    | 3.3.2 Proposed Pulse Generator                    | 115 |  |  |  |

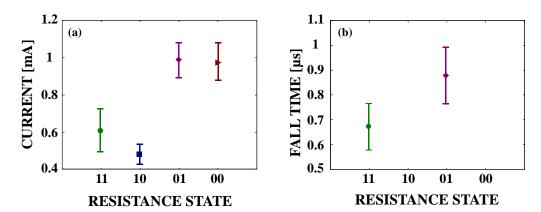

|              |                    | 3.3.3 Programmed Resistance Variation             | 117 |  |  |  |

|              | 3.4                | Summary of the Chapter                            | 118 |  |  |  |

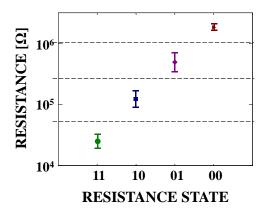

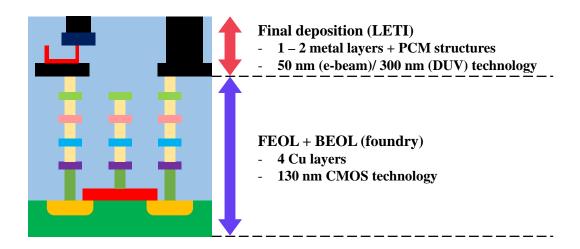

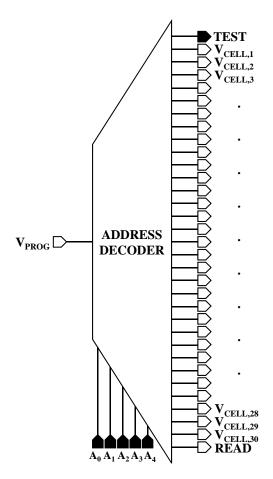

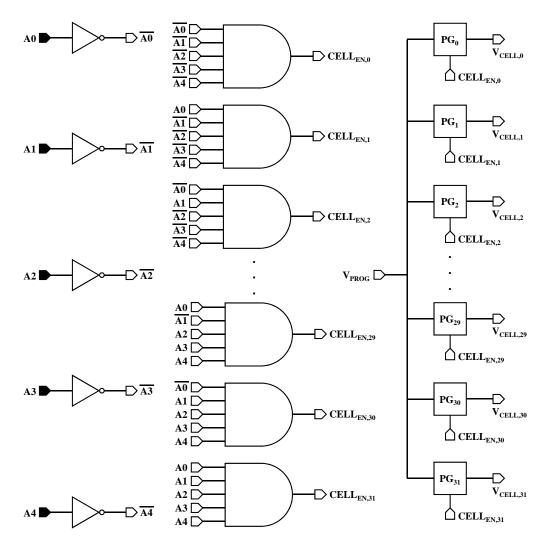

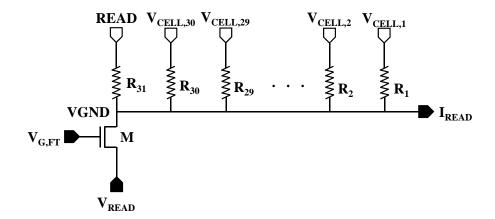

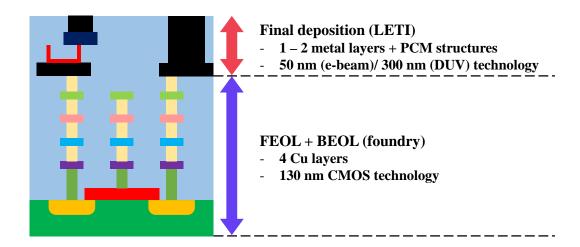

| 4            | On-                | Wafer Pulse Generator                             | 121 |  |  |  |

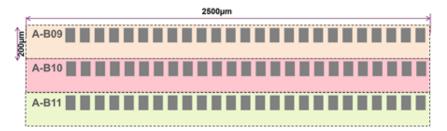

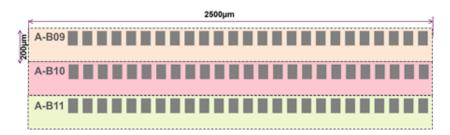

|              | 4.1                | Design Implementation                             | 122 |  |  |  |

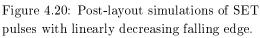

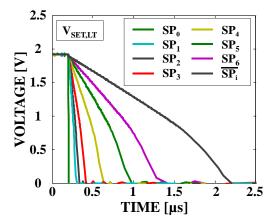

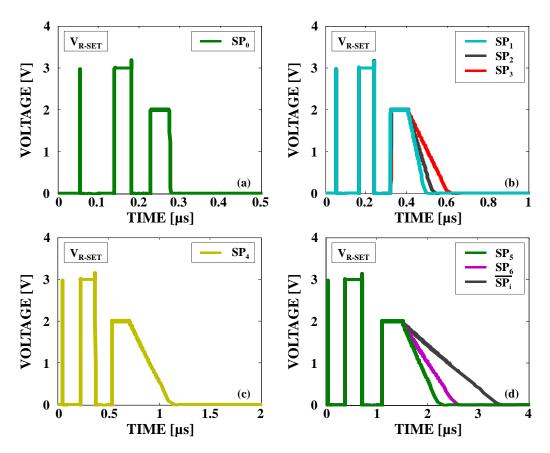

|              | 4.2                | Post-Layout Simulations                           | 134 |  |  |  |

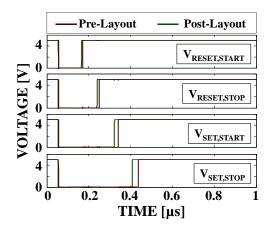

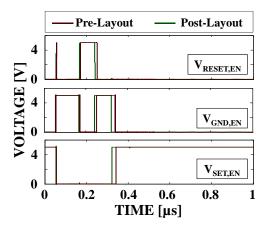

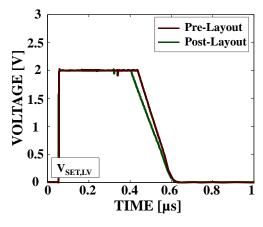

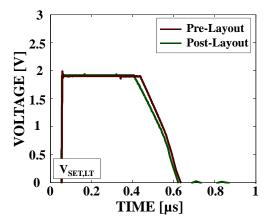

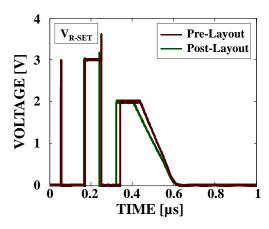

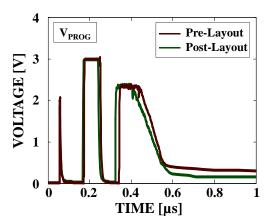

|              |                    | 4.2.1 Schematic vs. Post-Layout Simulations       | 137 |  |  |  |

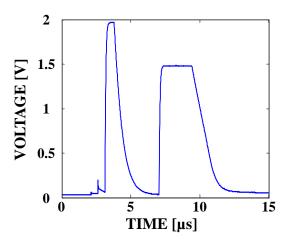

|              | 4.3                | Experimental Results                              | 139 |  |  |  |

|              | 4.4                | Summary of the Chapter                            | 145 |  |  |  |

| C            | onclu              | usions and Perspectives                           | 147 |  |  |  |

| A            | utho               | r's Publications List                             | 151 |  |  |  |

| Bibliography |                    |                                                   |     |  |  |  |

| $\mathbf{R}$ | Résumé en français |                                                   |     |  |  |  |

Abstract

#### Abstract - Résumé

<u>Title:</u> Characterization and Design of Architectures for Phase-Change Memories based on alternative-to-GST materials

Abstract: Semiconductor memory has always been an indispensable component of modern electronic systems. The increasing demand for highly scaled memory devices has led to the development of reliable non-volatile memories that are used in computing systems for permanent data storage and are capable of achieving high data rates, with the same or lower power dissipation levels as those of current advanced memory solutions.

Among the emerging non-volatile memory technologies, Phase Change Memory (PCM) is the most promising candidate to replace conventional Flash memory technology. PCM offers a wide variety of features, such as fast read and write access, excellent scalability potential, baseline CMOS compatibility and exceptional high-temperature data retention and endurance performances, and can therefore pave the way for applications not only in memory devices, but also in energy demanding, high-performance computer systems. However, some reliability issues still need to be addressed in order for PCM to establish itself as a competitive Flash memory replacement.

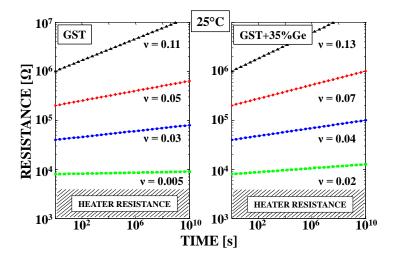

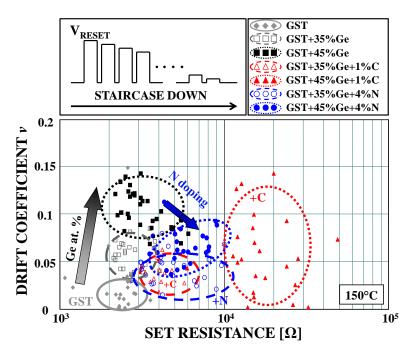

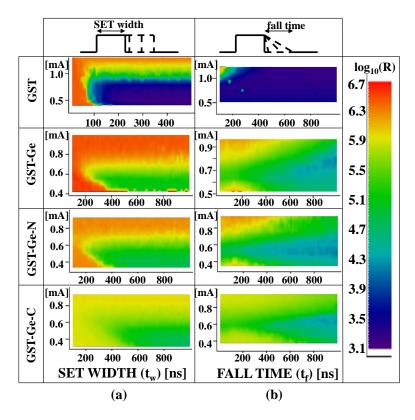

This work focuses on the study of embedded Phase Change Memory in order to optimize device performance and propose solutions to overcome the key bottlenecks of the technology, targeting high-temperature applications. In order to enhance the reliability of the technology, the stoichiometry of the phase change material was appropriately engineered and dopants were added, resulting in an optimized thermal stability of the device. A decrease in the programming speed of the memory technology was also reported, along with a residual resistivity drift of the low resistance state towards higher resistance values over time.

A novel programming technique was introduced, thanks to which the programming speed of the devices was improved and, at the same time, the resistance drift phenomenon could be successfully addressed. Moreover, an algorithm for programming PCM devices to multiple bits per cell using a single-pulse procedure was also presented. A pulse generator dedicated to provide the desired voltage pulses at its output was designed and experimentally tested, fitting the programming demands of a wide variety of materials under study and enabling accurate programming targeting the performance optimization of the technology.

iv Résumé

# <u>Titre</u>: Caractérisation et conception d'architectures basées sur des mémoires à changement de phase

<u>Résumé:</u> Les mémoires à base de semi-conducteur sont indispensables pour les dispositifs électroniques actuels. La demande croissante pour des dispositifs mémoires fortement miniaturisés a entraîné le développement de mémoires non volatiles fiables qui sont utilisées dans des systèmes informatiques pour le stockage de données et qui sont capables d'atteindre des débits de données élevés, avec des niveaux de dissipation d'énergie équivalents voire moindres que ceux des technologies mémoires actuelles.

Parmi les technologies de mémoires non-volatiles émergentes, les mémoires à changement de phase (PCM) sont le candidat le plus prometteur pour remplacer la technologie de mémoire Flash conventionnelle. Les PCM offrent une grande variété de fonctions, comme une lecture et une écriture rapide, un excellent potentiel de miniaturisation, une compatibilité CMOS et des performances élevées de rétention de données à haute température et d'endurance, et peuvent donc ouvrir la voie à des applications non seulement pour les dispositifs mémoires, mais également pour les systèmes informatiques à hautes performances. Cependant, certains problèmes de fiabilité doivent encore être résolus pour que les PCM se positionnent comme un remplacement concurrentiel de la mémoire Flash.

Ce travail se concentre sur l'étude de mémoires à changement de phase intégrées afin d'optimiser leurs performances et de proposer des solutions pour surmonter les principaux points critiques de la technologie, ciblant des applications à hautes températures. Afin d'améliorer la fiabilité de la technologie, la stœchiométrie du matériau à changement de phase a été conçue de façon appropriée et des dopants ont été ajoutés, optimisant ainsi la stabilité thermique. Une diminution de la vitesse de programmation est également rapportée, ainsi qu'un drift résiduel de la résistance de l'état faiblement résistif vers des valeurs de résistance plus élevées au cours du temps.

Une nouvelle technique de programmation est introduite, permettant d'améliorer la vitesse de programmation des dispositifs et, dans le même temps, de réduire avec succès le phénomène de drift en résistance. Par ailleurs, un algorithme de programmation des PCM multi-bits est présenté. Un générateur d'impulsions fournissant des impulsions avec la tension souhaitée en sortie a été conçu et testé expérimentalement, répondant aux demandes de programmation d'une grande variété de matériaux innovants et en permettant la programmation précise et l'optimisation des performances des PCM.

## Acknowledgements

First of all, I would like to thank my supervisor Luca Perniola for giving me the opportunity to work in CEA-LETI for the past three years. Having his trust and confidence pushed me and motivated me to work hard and thanks to him, I got the opportunity to work in a great scientific environment, on a topic that I ended up loving. This period was one of the best of my life, making me better on a personal and a professional level, and this would have not been possible without him putting his trust in me.

I would also like to thank my thesis directors, Fabien Clermidy and Guido Torelli for their collaboration and their scientific input. Alessandro Cabrini, my tutor during my stay in Pavia, is another person I am feeling grateful towards, as well as Olivier Thomas, who guided me during my short collaboration with the memory design team of DACLE.

Besides my official supervisors, the biggest "thank you" should be given to my behind-the-scenes supervisor, dear friend and colleague, Gabriele Navarro. I'd like to thank him for always standing next to me, not only professionally, but also personally. Always eager to help me and encourage me for the best, he transmitted his warmth and passion for what he was doing, and I am truly grateful I got to work by his side, learn so many things from him and get to know him on a personal level.

Of course I also need to thank my friends for their support and the great times we had together. The old ones, Thilo and Natalija, who I was super lucky to end up working together with and are practically family to me, but also a bunch of new ones, I met in Grenoble and in Pavia, such as Cécile, Daniele, Davide, Erika, Giorgio, Hadi, (best office mate I could ever imagine) Julia, Lorenzo, Marinela, Sara and of course my beloved friend Yiota! Thank you all for stoically listening to my complaints and for always putting a smile on my face!

There are also so many colleagues I would like to thank for their collaboration, so hoping that I am not forgetting anyone, I would like to thank Martin, my fellow PCM traveler since day one, Onofrio, Quentin, Thérèse, Thomas, Sarra, Boubacar, Adam D., Issam, Vincent, Loic, Alexia, Bastien, Adam M., Alex, Giuseppe, Jérémy, Mouhamad and Mourad for our great talks and fun times.

I would also like to thank my colleagues from the electrical characterization lab, the people from the memory design team in DACLE, and the permanent stuff from the memory components laboratory for their collaboration and their immediate availability every time I had questions. Last but not least, I would like to thank my colleagues and the professors in the University in Pavia, who also gave me valuable input when I needed help during my stay there.

Finally, I would like to thank my family for their unconditional love and support.

Η Ιθάκη σ' έδωσε τ' ωραίο ταξίδι, χωρίς αυτην δεν θα βγαινες στον δρόμο. Αλλα δεν έχει να σε δώσει πια. Κι αν πτωχική την βρεις, η Ιθάκη δε σε γέλασε. Έτσι σοφός που έγινες, με τόση πείρα, ήδη θα το κατάλαβες οι Ιθάκες τι σημαίνουν.

Ithaca, C. P. Cavafy (1910)

### Introduction

#### Context

Social scientists have reached the conclusion that we are living through an era in which "the generation of wealth, the exercise of power, and the creation of cultural codes came to depend on the technological capacity of societies and individuals, with information technologies as the core of this capacity" [1]. The way modern society handles information, strongly depends on the technological breakthroughs, which allowed us to process and store more information much faster than a few years ago.

The information revolution was made possible thanks to several technological improvements in fabrication techniques from one side and to the increased understanding of solid-state electronics mechanisms from the other side. The invention of the integrated circuit by J. Kilby in 1958 totally changed the world and the way we live on it, while the ability to place a large number of electronic devices on the same chip further allowed for the invention of the first personal computer in 1977. It was only a matter of time before the Internet became a free platform, gradually connecting all personal computers in the World Wide Web.

The exponential technological development of integrated circuits followed the well-known Moore's law, which was fairly simple in its concept: according to Moore, the number of devices that can be integrated on a chip of fixed area would double every 12 months. This simple prediction (later amended to doubling the number of devices every 18 - 24 months) unleashed a powerful economic cycle of investment followed by enhanced products and innovative applications motivating even more investment. Moore's Law has become a driving force behind dramatic reductions in unit cost over the past few decades for memory, enabling products of higher density and ultimately putting enormous amounts of memory in the hands of the consumer at reduced cost [2].

Semiconductor memory has always been an indispensable component of modern electronic systems. All familiar computing platforms, ranging from hand-held devices to large supercomputers, use storage systems for storing data temporarily or permanently, having reached TB of capacities in considerably less space and power consumption, yet maintaining a high speed [3].

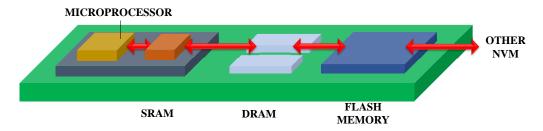

The roots of memory technologies used in modern computing systems date back to early 1970's, when the semiconductor industry was still in its nascent stage. These technologies include solid-state memories such as Static RAM (SRAM), Dynamic RAM (DRAM), and EPROM, as well as mechanical memories like tape and Hard Disk Drive (HDD).

2 Introduction

From floppy disks and magnetic Hard Disk Drives to Flash memory cards and Solid-State Drives conventionally used nowadays, there has been a remarkable increase in the available memory capacity during the past years, enabling higher storage density at a lower price.

The scalability of these memory technologies has been a key factor in the emergence of increasingly complex computing devices, however, the exponentially increasing demand for an enriched end-user experience and increased performance in mainstream computing applications is rendering these memory technologies obsolete. Driven by multi-core computing, virtualization, and processor integration trends, the global electronics and semiconductor industry has been feeling the need for next-generation main memory solutions that are capable of achieving high data rates, with the same or lower power dissipation levels as that of current advanced conventional memory solutions.

For non-volatile data storage, magnetic hard disk drives have been in use for over five decades. Nonetheless, since the arrival of portable electronic devices such as music players and mobile phones, Flash memory has been introduced into the information storage hierarchy between DRAM and HDD. Flash has become the dominant data storage device for mobile electronics. Even enterprise-scale computing systems and cloud data storage systems use Flash to complement the storage capabilities of HDD. Nevertheless, the integration limit of Flash memories is slowly approaching, and many new types of memory have been proposed to replace conventional Flash technology.

Emerging non-volatile memory technologies such as magnetic random access memory (MRAM), ferroelectric random access memory (FeRAM), resistive random access memory (ReRAM) and phase change memory (PCM) combine the speed of SRAM, the density of DRAM, and the non-volatility of Flash and therefore, are continuously being investigated since they demonstrate characteristics which are very attractive for future memory hierarchies [4].

PCM is considered the leading solution for the next NVM generation, demonstrating numerous advantages that make it competitive against established memory technologies, not only for stand-alone, but for embedded applications as well, and showing unique capabilities with respect to competing memory technologies. Thanks to its proven good scalability as well as easy integration in advanced CMOS nodes, high-density memory demonstrators and even commercial products have made their

appearance, while the combination of small cell size and good performance, offers Phase Change Memories the opportunity to be strongly considered for Storage Class Memory [5] operations, in addition to embedded non-volatile memory applications. Furthermore, as 3-D is becoming the new technological scaling paradigm, interesting pathways to realize 3-D PCM are explored [6].

Nevertheless, some performances should be further optimized. More specifically, for stand-alone applications, a reduction of the power consumption is necessary, while for embedded applications, the reliability of the technology has to be improved, as well as the high-temperature data retention. Reducing the programming current requires scaling of the active material volume, demanding new cell configurations or concepts, while the thermal stability of the technology can be improved by proper material engineering.

#### Thesis Presentation

This work focuses on the electrical characterization and the design of architectures for Phase Change Memory based on innovative materials, targeting device performance optimization. To this purpose, extensive electrical studies on state-of-the-art devices have been conducted in order to understand the benefits that are introduced by the use of novel materials. Additionally, novel programming techniques are investigated to deal with the problems emerging by the technology.

Chapter 1 is intended to give an overview of memory concepts that are widely used in present memory hierarchy or are under study and are going to replace existing memory technologies. Modern memory systems have requirements that cannot be met by a single memory technology, thus motivating the development of emerging device concepts that could potentially replace well-established players in the memory market. A standard memory hierarchy is presented and existing volatile and non-volatile memory technologies are introduced. At the end of the Chapter, Phase Change Memory is introduced and presented in depth. The main operation principle of the technology is discussed and the mechanisms leading to phase transition are explained. Some of the main issues of the technology, such as the resistivity drift are examined and potential applications for PCM are introduced.

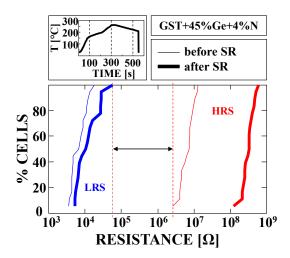

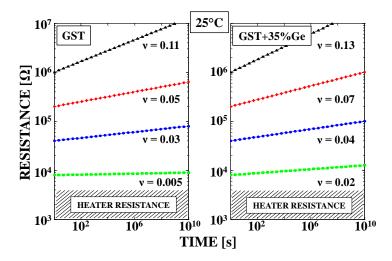

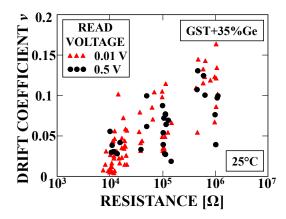

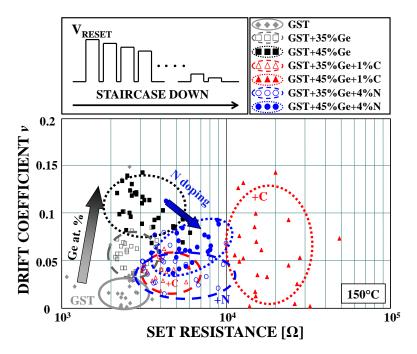

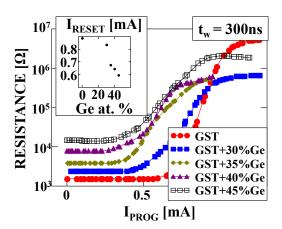

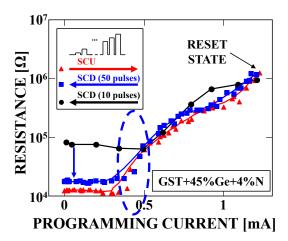

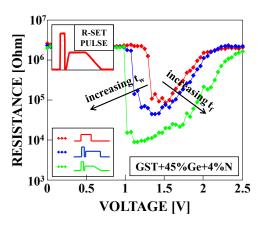

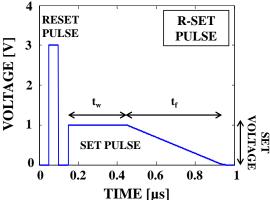

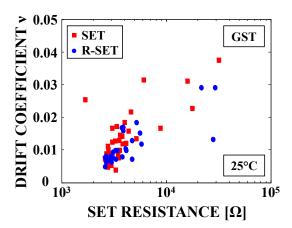

Chapter 2 presents the electrical parameters of a PCM device, as well as the characterization setup used in order to perform the reliability analysis, along with the main reliability issues of PCM leading to the need for appropriate engineering of phase change material stoichiometry in order to improve the thermal stability of our devices. Some of the best data retention results reported in literature, in Ge-rich based devices fabricated in the framework of the collaboration with STMicroelectronics are presented. Thanks to a new programming technique, we demonstrate the possibility to improve the programming speed of these devices and reduce the drift

4 Introduction

phenomenon that affects the resistance stability of PCM technology, in particular at high temperature, thus proving the suitability of this particular phase change material for embedded applications.

Chapter 3 focuses on the circuit design of architectures intended for optimized PCM operation. Starting from the innovative programming technique introduced in the previous Chapter, we present a pulse generator able to provide this kind of pulse sequence. A circuit capable of generating a linearly decreasing temperature profile, thus leading to an optimum device programming is also introduced. At the end of the Chapter a current pulse generator capable of providing pulses for programming the cell into multiple bits per cell is introduced and the programming algorithm enabling Multilevel Cell programming in PCM is also examined.

Chapter 4 is dedicated to the design approach that was followed to fabricate an on-wafer pulse generator. The analytical schematics of the circuit are presented as well as the physical layout of the designed circuit. Schematic simulations are compared to the simulations extracted from the finally laid-out circuit and the results are in very good agreement, thus confirming the validity of the followed approach. Finally, experimental results on silicon are provided, showing the functionality of the fabricated circuit and its potential to be used for testing purposes.

In the end, the general conclusions of this work are provided, summarizing the main results obtained and proposing perspectives for future research activity on this technology, taking into consideration the performance optimization of PCM technology introduced within the context of this study.

## Solid-State Memory Technologies

An ideal memory system should be fast, cheap, persistent and big (highly dense). Until now, all memory technologies address only some of these characteristics. For instance, Static Random Access Memory (SRAM) is very fast but also expensive, has low density and is not persistent. Dynamic RAM (DRAM) is cheaper; however, it is slower and not persistent as well. Disks on the other hand, are cheap, highly dense and persistent, but are considerably slow. Flash memory lies somewhere between DRAM and disks: it is a non-volatile memory (NVM) with higher density than DRAM, but suffers from much higher latency.

Nowadays, research is moving along three main axes for embedded memory devices:

- a) scaling down the cell size of the memory cell;

- b) scaling down the operating voltage;

- c) increasing the density of stored bits (and consequently reducing the cost per bit) by using a Multilevel Cell (MLC) approach, which consists in storing more than one bits in a single cell.

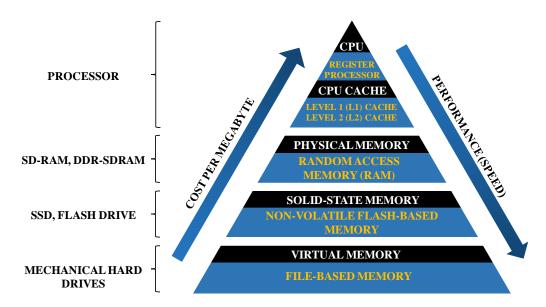

Luckily, it is possible to design a memory system that satisfies all the above development trends in a single memory hierarchy. Such a hierarchy enables the creation of a system that features fast performance, high power efficiency and low cost. More specifically, this system can be implemented by a memory hierarchy consisting of many different memory levels, as shown in Fig. 1.1. Memories in the top levels of this hierarchy are faster and smaller, but have a higher cost, whereas memories in the bottom layers are progressively larger and cheaper, but feature considerably lower access speed.

In modern computing systems, a hierarchy of volatile and non-volatile data storage devices is used in order to achieve an optimal trade-off between cost and performance. On top of the hierarchy pyramid, we find the portion of the memory that is the closest to the processor core and requires frequent access (CPU registers and cache memory). For this reason, this portion requires the fastest operation speed possible, while it is also the most expensive due to the large chip area required.

Figure 1.1: Simplified Computer Memory Hierarchy.

Other levels in the memory hierarchy are optimized for storage capacity and speed. For example, physical memory, which is usually indicated simply as "Memory", is used by the central progressing unit (CPU) to store the results of computation, which are ready to be (partly) transferred to the logic memory when further computation steps are needed. The program/erase time of this memory, which is usually implemented as a DRAM is around 10 ns, while its cost per bit is reduced with respect to logic memory, allowing for larger memory capability. DRAM and cache memory can be classified as volatile memories, since data stored in them is lost once the power supply is switched off.

Finally, the bottom of the pyramid consists of non-volatile memory, which allows permanently storing the large volume of bits defining the PC software, together with the results of computation and personal data. This kind of memory shows longer write/erase time, ranging from few tens of  $\mu$ s to few ms and a rather low cost per bit, with memory capacity that can reach hundreds of GB.

Currently, DRAM and hard disk drives (HDD's) are responsible for 40% of the total server power consumption, while this percentage rises up to 70% in portable devices. This means that a high-performance, high-density, low-power consumption and low-cost NVM technology whose access time falls between that of an HDD and the dynamic memory located near the processor would significantly improve overall system performance. Future green IT applications will then need both better performance and lower power consumption in order to allow for a sustainable technological development.

One important aspect that also needs to be taken into account when discussing the future perspectives of memory market, is the rapid growth of data centers for cloud computing. Generally, cloud storage can provide users with immediate access to a broad range of resources, also serving as a natural disaster-proof backup solution. The cloud computing market is predicted to see an explosive growth from a 41 billion \$ market in 2011 to a 241 billion \$ market in 2020. One of the key technical bottlenecks of this novel system architecture is expected to be its storage capacity. It is for this reason that a fast, cheap and reliable non-volatile memory technology will be one of the most important success factors for semiconductors companies in the near future. The main factor that will enable such changes will also be the ability to optimize energy consumption of both giant, concentrated databases and small, distributed portable devices.

To sustain the continuous scaling and thus be able to appear competitive in the future, conventionally used memory devices may be obliged to undergo revolutionary changes, since some of the limitations within each type of memory are becoming more and more evident. Several emerging memory concepts are introduced, aiming to go beyond those limitations and potentially replace all or most of the existing semiconductor memory technologies and become a "Universal Memory" [7]. The benefit of implementing such a device would be the control of an enormous market, which has expanded from computer applications to all kinds of consumer electronic products [8].

In this Chapter, we introduce the reasons why memory plays a key role in modern computing systems. Thanks to the memory hierarchy used in present-day computer architectures, we highlight the main requirements and specifications for different memory technologies and present well-known memory technologies such as SRAM, DRAM and Flash Memory, before moving on to emerging memory concepts. Among the wide range of next generation memory devices covered in this Chapter, we study the basic operation principles of Magnetoresistive Random-Access Memory (MRAM), Ferroelectric RAM (FeRAM), Resistive Random-Access Memory (ReRAM) and Phase Change Memory (PCM). PCM is the focus of this work; therefore, its behavior and performance are thoroughly examined.

#### 1.1 Solid-State Memories - An Overview

Solid-state memories are a category of devices that have been developed in parallel with logic computing. SRAM (Static Random Access Memory) and DRAM (Dynamic Random Access Memory) are the oldest semiconductor memories introduced at the end of the 60's. Their main advantage is their fast access time, however, they are volatile memories. This means that the information can be maintained only through continuous refresh and is lost when the power supply is switched off.

Figure 1.2: Memory Hierarchy of the future aiming at power reduction. Lower latency and lower power consumption will be obtained by a flattened system architecture including granular non-volatile memory already at the back end of line (BEOL) stage.

The non-volatile memory concept has been pursued in order to electrically write/erase the information and to maintain it without power consumption typically for a period of (at least) ten years.

Flash memory can be seen as a conjunction of the three main "memory families", i.e. DRAM, Read Only Memory (ROM) and Electrically Erasable Programmable Read Only Memory (EEPROM) [9]. What should be noted is that all of these memory types are still in use today, but none of them completely fulfills the properties of the others. The two most successful families in terms of revenue are DRAM and Flash memory, hereinafter often referred to as Flash.

Different categories of memories are used complementarily in computing applications and several kinds of memories are used together. Emerging memory concepts stem from this desire of merging several categories, thus creating a "Universal memory" that could replace all other memories and simplify system integration.

However, history shows that new successful memory concepts have rather been used in complement with existing others, moving the frontier between the categories rather than completely replacing one kind. The present memory hierarchy is obliged to undergo major changes, flattening its architecture in order to achieve lower latency and higher power efficiency, making use of existing memory technologies (Fig. 1.2). However, this evolution might take some time. DRAM did not replace SRAM, Hard Disk did not replace Tape and Flash did not replace Hard Disk. Nevertheless, the need for fast access prevents the use of any mechanical component and requires the use of solid-state memory. In this quest, few memory concepts exist that could be introduced in the next decade.

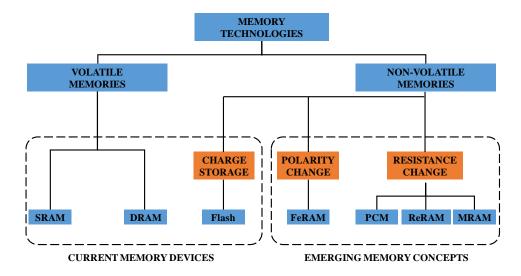

In terms of functional criteria, existing silicon-based semiconductor memories can be categorized into two main groups: volatile and non-volatile (Fig. 1.3). On the one hand, in volatile memories, the information eventually fades when power supply is turned off, unless the devices used to store data are periodically refreshed. On the other hand, non-volatile memories retain stored information even when power supply is turned off. Volatile memories, such as SRAM and DRAM, need voltage supply to

Figure 1.3: Overview of the semiconductor memory classification according to their functional criteria.

maintain their information, whereas non-volatile memories, namely Flash memories, are able to hold their information without any power supply. DRAM, SRAM and Flash are today's dominant solid-state memory technologies and have been around for a long time. Among them, Flash is the most recently introduced [10].

SRAM is built in CMOS technology with six transistors per cell, while DRAM is built using one transistor and one capacitor per cell, which allows much higher density and lower cost per bit. Flash memory works with a Floating Gate (FG) component.

DRAM has an advantage over SRAM of only needing one MOSFET with a capacitor. Moreover, it is also cheap to produce, as well as less power consuming when compared to SRAM, but demonstrates lower speed. SRAM is faster and easy to control. Nevertheless, SRAM needs many transistors (is thus expensive) and is more power consuming than DRAM.

Volatile memories consist mostly of DRAM, which can be further classified into SDRAM. The market for DRAM devices exceeds the market for SRAM devices by far, although a small amount of SRAM devices is used in almost all logic and memory chips. Forthcoming volatile memory technologies that hope to replace or compete with SRAM and DRAM include Zero-capacitor Random Access Memory (Z-RAM), Twin-Transistor Random Access Memory (TTRAM), Advanced Random Access Memory (A-RAM) and ETA RAM [11]. In the industry, new universal and stable memory technologies will make their appearance as real contenders to displace either or both Flash and DRAM.

Flash memory does not require power to store information but is slower than SRAM and DRAM. This memory technology can be further divided into two cate-

gories: NOR Flash, characterized by word programming granularity and large cell size and NAND Flash, characterized by page programming and small cell size.

Today, non-volatile memories are highly reliable and can be programmed by using a simple microcomputer. Among them, emerging non-volatile memories and especially Flash, have been the fastest growing segment of the semiconductor market during the last 10 years. There are mainly five types of non-volatile memory technology: Flash memory, magnetic random access memory (MRAM), ferroelectric random access memory (FeRAM), oxide based resistive random access memory (ReRAM) and phase change memory (PCM).

MRAM is an NVM technology, where data is not stored in an electric charge flow, but by magnetic storage elements. FeRAM is a random access memory similar in construction to DRAM but uses a ferroelectric layer instead of a dielectric layer to achieve non-volatility. ReRAM is a non-volatile memory that bases its operation on a dielectric, normally insulating, which is made to conduct through a filament or conduction path formed after the application of a sufficiently high voltage. Arguably, this is a memristor technology and should be considered as a potentially strong candidate to challenge NAND Flash.

Finally, PCM is a non-volatile random-access memory, based on a reversible phase transition between the amorphous and the crystalline state of a chalcogenide (a material that has been used to manufacture read/writable compact disks, CD-RW's and digital versatile disks, DVD's), which is accomplished by heating and cooling of this material.

An ideal memory device, or a so-called "Universal memory", should be able to simultaneously satisfy at least three requirements: high speed, high density and non-volatility (retention). Up until now, such a memory device has not been developed. The floating gate non-volatile semiconductor memory has high density and retention, but its program/erase speed is low. DRAM has high speed (access time of approximately 10 ns) and high density, but it is volatile. In contrast, SRAM has very high speed (access time of hundreds of ps), but its application range is limited due to its very low density and volatility.

Researchers are in inspiring search of novel non-volatile memories, which will successfully lead to the realization and commercialization of the "Universal memory". Among these emerging concepts, it is expected that PCM will have better scalability than other emerging technologies. Additionally, MRAM, FeRAM and PCM are in commercial production but still remain limited to niche applications and are many years away from competing for industry adoption [12].

#### 1.1.1 Static Random Access Memory - SRAM

Cache memory is employed to store frequently used information and can be placed at several layers of the computer architecture, but probably the most important layer is processor cache. The speed of the cache is typically inversely proportional to its size. This means that processor cache memory needs to be very fast and small in order to save search time.

The technology that best matches this basic set of requirements is Static Random Access Memory. SRAM is a high-performance semiconductor memory, which is designed using standard CMOS transistors arranged as an addressable latch. As a memory technology, SRAM is the fastest memory in the modern hierarchy, but it requires significant area to implement.

An SRAM cell is generally used for instruction registers and as cache memory in modern processors, because these elements store data that is needed and handled immediately by the CPU. Delay in this data constitutes a direct delay in instruction processing, so SRAM must be used for this function to ensure reasonable processor performance.

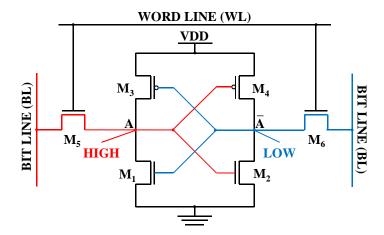

The schematic of a typical SRAM cell is shown in Fig. 1.4. The cell consists of six transistors, configured as a gated latch. Transistor pairs  $M_3$ - $M_1$  and  $M_4$ - $M_2$  form two cross-coupled CMOS inverters (i.e. the input of the first inverter is connected to the output of the second inverter and vice-versa), thus giving rise to a simple latch. This latch is then gated by transistors  $M_5$  and  $M_6$ .

SRAM is a true random access memory where both the Word Line (WL) and Bit Line (BL) are accessed to address a single element. The WL is connected to the gates of the two access transistors, while the BL's are connected to the drains/sources of  $M_5$  and  $M_6$ . This SRAM cell requires two complementary BL signals to write

Figure 1.4: Circuit schematic of a 6T SRAM cell.

the cell. When the WL is high, the cell simply receives the high-low or low-high configuration provided by the BL, which is then latched when the WL goes low.

In modern memory systems, the contribution of the inverter gate delay to the write access time is generally less than 1 ns. In an actual SRAM, read and write speed also depends on the distance of the memory from the arithmetic logic unit and the time involved in the array control electronics. An SRAM array is generally integrated on the same CPU chip, which performs logic operations and thus maintains a fast access time even at system level (in contrast to DRAM).

For instance, when used as a register, which is as close as possible to logic computation, SRAM latency is less than 1 ns. When used as a cache, SRAM latency at system level ranges from 1 to 20 ns. Furthermore, high speed in SRAM is enabled by direct integration with CMOS processor logic but this is also a reason why the maximum capacity of SRAM is limited. Considering that a state-of-the-art microprocessor might have up to one billion transistors on a single chip and each SRAM cell requires six transistors, as described above, we can assume that if all transistors on the chip were used as SRAM cells, the chip itself could only constitute a memory of a few hundred Mbit, or less than 30 MB of SRAM. This is the reason why typical modern CPU's only have several MB of SRAM and, hence, application memory heavily relies on DRAM.

#### 1.1.2 Dynamic Random Access Memory - DRAM

While some of the most frequently used data are kept in cache in order to lower access time, most of the memory addressing space used by a program is usually stored in the main memory. Main memories have to be big enough to hold most of the data needed by a program and can be slower than cache, since the most frequently used data are already being cached. Since more capacity is needed, the cost-per-bit of the main memory also needs to be lower than in the case of cache. These requirements can be satisfied by Dynamic Random Access Memory.

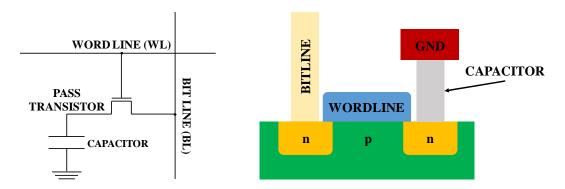

DRAM is a type of memory that stores each bit of data in a capacitor within an integrated circuit (Fig. 1.5). The capacitor can be either charged or discharged. These two capacitor states are used to represent two logic values, referred to as "1" and "0". Since p-n junctions and even transistors in their OFF state are affected by a small leakage current, the capacitors may slowly discharge and the information stored in the memory cell will eventually fade, unless the capacitor charge is periodically refreshed. Because of this refresh requirement, DRAM is a dynamic memory.

DRAM is usually arranged in a rectangular array of charge storage cells that consist of one capacitor and one transistor per data bit. A simple example of a four-by-four cell matrix can be seen in Fig. 1.6. As in the case of SRAM, the horizontal

Figure 1.5: Schematic representations of a DRAM cell. Data is stored in a capacitor that can be either charged or discharged, representing two logic values, namely "1" and "0".

lines connecting each row of cells are known as Word Lines, whereas the vertical lines, which are connected to the cells belonging to the same column, are referred to as Bit Lines.

Each cell is addressed by selecting the corresponding WL and BL. In order to read a cell, its respective WL is driven high, thus connecting the storage capacitor to the selected BL: the ensuing voltage variation on the BL allows the contents of the cell to be sensed. However, this operation destroys the data of the cell, due to the huge difference between the small storage capacitance and the heavy BL capacitance. It should be also pointed out that, when reading a cell in a given row,

Figure 1.6: Array of DRAM cells consisting of one capacitor and one transistor per cell.

all the cells in the same row are also connected to their respective BL's and, hence, their data are destroyed. For this reason, all the cells of the addressed WL are read and are then written back to the level corresponding to the sensed data. This approach is also followed to refresh a DRAM: all WL's are sequentially accessed in order to read all the associated cells and then re-write them.

In order to store data in a cell, its respective WL is driven high and its respective BL is driven to the desired value (high or low). The BL is held at the desired value even when the WL voltage is removed. While performing a write operation on a particular cell, all the columns in the selected row are sensed simultaneously and are then re-written to the level corresponding to the sensed data.

Unlike SRAM, DRAM exhibits structural simplicity [13]. Only one transistor and one capacitor are required to store information for one bit. This allows DRAM to reach very high densities when compared to SRAM, where six transistors are needed for the same amount of information. The transistors and capacitors used are extremely small; billions can fit on a single memory chip. However, despite its numerous advantages, DRAM is a volatile memory, i.e. it is incapable of retaining its data once power supply is removed, and its operation speed is lower than that of SRAM.

Despite the fact that DRAM has been able to double its capacity every two years, its latency does not follow an equally impressive improvement. Moreover, DRAM technology is bound to hit a density wall, which will eventually result in its replacement by emerging memory technologies, such as Spin Transfer Torque RAM or Phase Change Memory.

#### 1.1.3 Flash Memory

Flash memory has been conceived by Professor Fujio Masuoka in 1980 and was first presented in 1984. The word Flash comes from the fact that the data from a whole memory block (referred to as sector) can be erased in one single shot. With an electrical erase, it is possible to reprogram the read only memory in situ without removing the memory from the system. The design of the memory was based on a NOR array configuration (see below) and was dedicated to code storage. This memory is commonly called NOR Flash memory. In order to decrease the cost of Flash memory, NAND Flash memory was also invented by Professor Fujio Masuoka in 1987. NAND Flash memory has been dedicated to data storage and is based on a NAND array configuration.

#### 1.1.3.1 Operation Principle

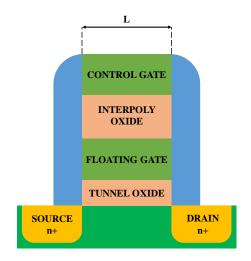

Flash Memory is based on a MOS transistor structure with a modified gate stack (Fig. 1.7). The gate stack is composed by a poly-silicon floating gate embedded

memory cell along the Bit Line.

Figure 1.7: Schematic cross section of a Flash Figure 1.8: Current-voltage characteristic of a Flash memory cell ( $V_{CG}$  = control gate voltage).

in silicon oxide (SiO<sub>2</sub>) that is used as electron storage element and an accessible polysilicon gate (referred to as control gate), which are insulated by means of a dielectric (to improve capacitive coupling between the control and the floating gate, the interpoly dielectric commonly consists of a sandwich of silicon dioxide, silicon nitride and silicon dioxide, which is referred to as oxide-nitride-oxide, ONO). The oxide between the channel of the MOS device and the floating gate is named tunnel oxide, since the cell is written by making electrical charge (i.e. electrons) pass through this oxide layer.

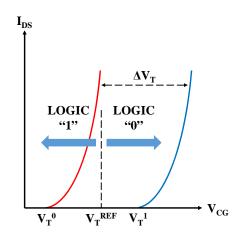

Fig. 1.8 shows a typical I-V curve of a Flash memory cell. The charge in the floating gate induces a shift of the transistor threshold voltage  $\Delta V_T$  that is called the programming window and constitutes a key parameter of the cell. When the floating gate is uncharged, the cell is erased. The threshold voltage of the cell is equal to V<sub>T,erase</sub> and represents the "1" state. When the floating gate is charged with electrons, the threshold voltage  $V_{T,prog}$  becomes higher  $(V_{T,prog} > V_{T,erase})$ and the cell is considered written or "0" state [14], [9].

During cell read-out, the control gate is biased to V<sub>G,read</sub>, which is a voltage that lies between the programmed and the erased threshold voltage:  $V_{T,erase} < V_{G,read} < 0$  $V_{T,prog}$ . As a result, when the cell is erased,  $V_{T} = V_{T,erase} < V_{G,read}$ , the transistor is on and current can flow through the cell. The cell is in the "1" state. On the contrary, when the cell has been written,  $V_T = V_{T,prog} > V_{G,read}$ , the transistor is off and, hence, no current flows through the cell, thus indicating that the cell is in the "0" state.

In order to ensure fast read-out, the threshold voltage shift between the programmed and the erased state must be as high as possible (on the order of several

Figure 1.9: Schematic representation of a Flash memory cell organized in a NOR array configuration. The memory cells are connected in parallel. Each cell has its source terminal connected directly to ground, while the drain terminal is connected to a BL. The control gate is shared along the WL.

Volts) with a steep sub-threshold slope to ensure clear separation between the ON and the OFF state. Moreover, the ON current  $I_{\rm ON}$  must be as high as possible. Parasitic currents should be as small as possible in order to have a small OFF current  $I_{\rm OFF}$ . In current Flash technology, the difference between  $I_{\rm ON}$  and  $I_{\rm OFF}$  has been reported to be up to six orders of magnitude.

#### 1.1.3.2 NOR vs. NAND Flash

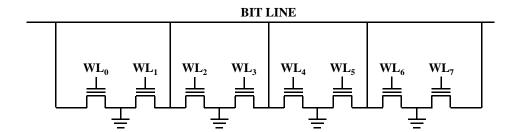

The organization of NOR Flash, shown in Fig. 1.9, is the following: several memory cells are connected in parallel. Each cell has its source terminal connected to a line referred to as the Source Line (which is common to all the cells in a memory sector) and its drain terminal connected to the same BL. The control gate is shared among all cells belonging to the same WL, which run orthogonally to the BL's. The drain contacts of the transistors connected to the BL are shared between two adjacent cells. This architecture allows random access of any cells in the array as the drain of each cell can be addressed through BL selection.

This configuration of elementary devices is called "NOR Flash" architecture because it operates as a NOR gate (one BL can be seen as the output of a NOR gate whose input terminals are the WL's of all the cells belonging to the considered BL).

The NOR Flash organization allows fast random access (approximately 100 ns). Programming (i.e. setting the memory cell to "0") is carried out at word level (or, better, at the level of a group of words) and is typically a slower operation (approximately 5 µs). Erasing (i.e. resetting the memory cell to "1") is also carried out at block level and is even slower (typically around 200 ms). Taking these characteristics into account, the NOR Flash is used principally as a read only memory mainly in applications such as code storage, for which the random access time is important but programming/erasing operations are rarely carried out.

Figure 1.10: Schematic representation of a Flash memory cell organized in a NAND array configuration. The memory cells are connected in series, allowing a great level of parallelism.

Moreover, in a NOR Flash architecture, the manufacturer guarantees that all individual bits are functional and meet retention and endurance specifications. No implementation of Error Correction Code (ECC) is needed from the user side. In some cases (such as in MLC architectures), an internal ECC, which is totally transparent to the user, may be present. As far as the size of the cell is concerned, the presence of one shared contact for each pair of cells brings its size to 6F<sup>2</sup>.

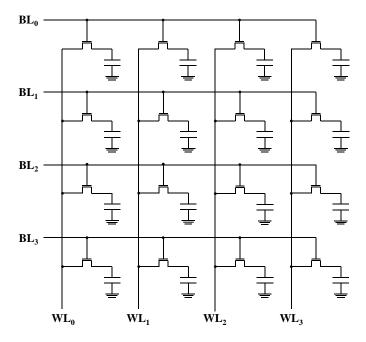

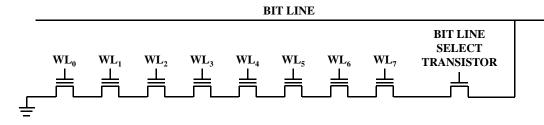

The organization of a NAND Flash is shown in Fig. 1.10. In this configuration, several groups of floating gate transistors are connected in series. These FG transistor groups are then connected, via some additional transistors, to a NOR-style Bit Line array in the same way in which single transistors are organized in a NOR Flash array. Due to this arrangement, the BL is pulled low if and only if all WL's in the selected string are driven above the threshold voltage of the transistors.

This organization of elementary transistors is called NAND Flash because the FG transistors are connected in a way similar to the transistors in a NAND gate. When compared to NOR Flash architecture, replacing single transistors with strings of transistors requires an additional level of addressing. The series arrangement of the FG transistors gives rise to poor random access time, which is generally counteracted at system level by reading a large number of cells (generally, all the cells of an entire WL, referred to as a page) and then sequentially feeding the read data to the output by means of high-speed circuits. Poor latency and high throughput are therefore typical of this kind of Flash memory.

NAND Flash programming is performed at page level and is carried out in approximately 0.2 ms. Erasing is performed at block level and takes about 2 ms. Thanks to these characteristics, Flash NAND is better suited to data storage, where problems of latency are minor and random access time is not very important. In this configuration, the use of external ECC is mandatory (at the expense of higher latency), because the manufacturer does not guarantee each single cell and commercial devices may contain a few defective cells.

An additional advantage of NAND Flash architecture when compared to NOR Flash architecture is that a single drain contact per device group is required, which

allows reaching an optimal cell size of  $4F^2$  and, hence, a 30% area gain with respect to a NOR Flash array, resulting in higher density.

Many of the advantages and disadvantages of NOR and NAND Flash devices arise directly from the differences in the architecture used for their implementation. Not surprisingly, the names for these two technologies carry a significant clue as to the implementation differences [15]. The extra connections used in the NOR architecture provide some additional flexibility when compared to NAND configuration, whereas NAND devices have a simpler and more silicon-efficient layout than NOR devices due to their series structure as well as the smaller number of ground wires and BL's with respect to NOR devices.

Both NOR and NAND Flash memory devices push density even further by storing more than one data bit per cell. Multilevel cell devices store two bits per cell by trapping four different levels of charge in the storage cell, thus establishing four different threshold voltages. Nevertheless, more complex read and write circuits as well as more complex error management algorithms are required when storing multiple bits per cell. On the other hand, the overall benefit in cost per bit typically outweighs the added complexity and reduced performance that comes with more advanced management techniques.

#### 1.1.3.3 Main Issues and Perspectives

While Flash memory has enabled the emergence of a wide range of consumer products, it does not fulfill all requirements to establish itself as a "Universal Memory". The main limitations are read bandwidth for NAND Flash and write bandwidth for NOR Flash. The speed gap of Flash with respect to DRAM is still large, while its endurance is limited to  $10^6$  cycles. The high voltage needed for the operation of the cell is also a strong limitation for future interfacing with leading edge CMOS technology. As a result, other candidates are expected to replace Flash memory. Some of them (MRAM, FeRAM, PCM) are already used in niche market, whereas others (ReRAM) have promising characteristics and are slowly starting their introduction in the memory market (ReRAM).

Even though these new technologies usually require the introduction of new materials and device architectures that prevent direct competition with the low-price and reliable materials of standard Flash technology, the inability of Flash to scale below the 20 nm node renders the development of these new memory concepts necessary in order to efficiently replace Flash and establish themselves as potential Storage Class Memory candidates [5].

In the following paragraphs, several replacement solutions of Flash memory are investigated. Herewith are presented MRAM, FeRAM, ReRAM and PCM. These technologies are investigated for code storage operations in order to replace the NOR

Figure 1.11: An MRAM cell consisting of a Magnetic Tunnel Junction (MTJ) in series with a transistor for bit read selection. Perpendicular write lines above and below the MTJ select a single tunnel junction during programming.

Flash memory that starts to face strong scaling challenges. Nevertheless, for data storage applications, they still do not have the possibility to compete with NAND Flash in terms of scalability and cost.

#### 1.1.4 Magnetoresistive Random Access Memory - MRAM

Magnetoresistive Random Access Memory (MRAM) is a non-volatile memory technology that has been under development since the 1990's. The increased density modern memory technologies demonstrate, kept it in a niche role in the market, but its supporters believe that its advantages are so overwhelming that MRAM will eventually become dominant for all types of memory [16].

MRAM combines non-volatility with high read and write speed and unlimited endurance. The MRAM storage element resides in the metal interconnect layers above the silicon, allowing its process to be optimized independently from the underlying semiconductor process, thus making itself cost-effective to integrate.

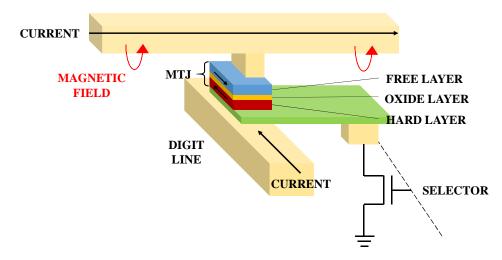

Unlike conventional memory technologies, data in MRAM is not stored as electric charge or current flow but as the magnetization polarity of a magnetic storage element. State-of-the-art MRAM combines a magnetoresistive magnetic tunnel junction with a single pass transistor for bit selection during reading (Fig. 1.11). The tunnel junction has a free magnetic layer, a tunneling dielectric layer and a fixed magnetic layer. The magnetization of the fixed layer is prevented from rotating (permanent magnet set to a particular polarity), whereas the magnetization of the free layer can be switched in order to match the magnetization of an external field and is used for information storage. The resistance of the tunnel junction depends

on the relative magnetization orientation of the free layer with respect to that of a fixed layer, being much lower when the two layers have the same magnetization polarity. This configuration is known as a spin valve and is the simplest structure for an MRAM cell.

Reading is accomplished by measuring the electrical resistance of the cell. Because of the magnetic tunnel effect, the electrical resistance of the cell changes due to the orientation of the fields in the two magnetic plates. The magnetization polarity of the writable plane and, consequently, the resistance of the cell can be determined by measuring the resulting current through the cell, when a bias of approximately 0.3 V is applied. Typically, if the two plates have the same polarity (larger electric current through the cell), we have a logic "1", while in the case of the opposite polarity, the measured current is higher and we have a logic "0".

MRAM has similar performance to SRAM, similar density to DRAM (with a much lower power consumption), is faster and suffers no degradation in time when compared to Flash memory. This combination of characteristics makes it a good candidate for a "Universal Memory", able to replace SRAM, DRAM, EEPROM and Flash. A huge amount of research is carried out into developing it, however, MRAM still has to face several challenges before it can be introduced to the market on a large scale.

One of these challenges relates to the switching current distribution. The write selection scheme that is conventionally used in MRAM requires tight and uniform switching current distributions, which cannot be always achieved. Another current-related concern for MRAM is its relatively small read-out signal, which effectively limits its read speed.

As with any new memory technology, the most obvious concerns relate to the long-term stability of memory device elements and characteristics, such as the ultra thin tunneling barrier, the stability of the magnetic layers in the free layer and data retention. Accelerated tests show that these mechanisms have negligible impact on memory performance at operating conditions. In particular, the tunneling barrier is likely to be highly stable, because aluminum oxide has a high breakdown voltage even at very small thicknesses, MRAM uses a low operating voltage and only the magnetic tunnel junctions that are being read are subject to voltage stress.

Future generations of MRAM will use smaller tunnel junctions and will thus have to re-address the above challenges. Nevertheless, going towards smaller dimensions should not introduce more bit-to-bit variations or jeopardize data retention. The switching current will not increase with reduced bit size, however, the current density will scale inversely with the conductor area and electromigration may therefore become an issue. At that point, spin momentum transfer (magnetization polarity switching by a spin-polarized current) might become a viable alternative to 2-D write selection.

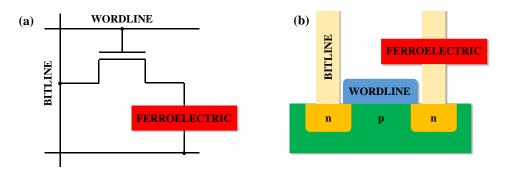

Figure 1.12: Schematic representation (a) and cross section (b) of a FeRAM cell. FeRAM is similar in structure to DRAM and uses ferroelectric films instead of a conventional capacitor to store information.

#### 1.1.5 Ferroelectric Random Access Memory - FeRAM

FeRAM (Ferroelectric Random Access Memory) is a high-performance and low-power non-volatile memory that combines the benefits of conventional non-volatile memories (Flash and EEPROM) and high-speed RAM (SRAM and DRAM). This memory technology outperforms existing memories like EEPROM and Flash, is less power-consuming and much faster and has greater endurance to multiple read and write operations [17].

FeRAM is similar in structure to DRAM but uses a ferroelectric layer instead of a dielectric one to achieve non-volatility, as can be seen in Fig. 1.12. The FeRAM cell structure, which is similar to the transistor and capacitor structure of a DRAM cell, does not require the same high programming voltages as Flash. By using the polarization of a ferroelectric film material placed between two electrodes, it is possible to store information, offering non-volatile data storage, while still being significantly more energy-efficient when compared with conventional memory technologies. Moreover, it offers the same functionality as Flash memory and some of its advantages include lower power consumption, fast read/write performance and an essentially unlimited endurance (reaching up to  $10^{12}$  cycles).

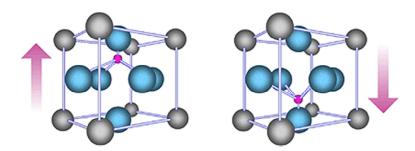

FeRAM uses ferroelectric films as a capacitor for storing data. Ferroelectric materials exhibit a non-linear relationship between the applied electric field and the stored charge. More specifically, the characteristic of ferroelectric materials has the form of a hysteresis loop, which is similar to the hysteresis loop of ferromagnetic materials. The dielectric constant of a ferroelectric material is typically much higher than that of a linear dielectric because of the effects of semi-permanent electric dipoles formed in the crystal structure of the material. When an external electric field is applied to a dielectric, the dipoles tend to align themselves with the field direction, producing small shifts in the positions of atoms and, hence, in the distributions of electronic charge in the crystal structure. After the applied voltage is

Figure 1.13: PZT (Pb $\{Zr,Ti\}O_3$ ), which has a perovskite-type structure (ABO<sub>3</sub>), is commonly used in ferroelectric memory. When an electric field is applied, Zr/Ti atoms shift up or down (depending on the field polarity) and this polarization remains when the electric field is removed.

removed, the dipoles retain their polarization state. Bits are stored as one of two possible electric polarizations in each data storage cell.

In FeRAM applications, PZT (Pb{Zr,Ti}O<sub>3</sub>), which has a perovskite-type structure (ABO<sub>3</sub>), is commonly used [18]. When an electric field is applied, the Zr/Ti atom shifts up or down and this polarization remains once the electric field is removed (Fig. 1.13). This material property provides non-volatility and keeps the power required for data storage low.

In terms of programming, FeRAM is similar to DRAM. Writing is accomplished by applying a voltage across the ferroelectric layer and, hence, forcing the atoms inside into the "up" or "down" orientation (depending on the polarity of the applied voltage), thereby storing a "1" or a "0". Reading, however, is different than in DRAM. The cell is forced into a particular state: if the cell was already programmed to a state similar to the one it is forced to, nothing will happen in the output lines. If the cell was programmed in the opposite state, the re-orientation of the atoms in the ferroelectric film will cause a brief pulse of current in the output lines, as electrons are pushed out of the metal towards the electrode contacts. Since this process overwrites the cell, reading FeRAM is a destructive process and requires the cell to be re-written to the original state if the information stored in it is altered.

Texas Instruments proved that it is possible to embed FeRAM cells in a CMOS fabrication process using two additional masking steps. Flash typically requires nine masks. This enables for example, the integration of FeRAM on micro-controllers, where a simplified process would reduce cost. However, the materials used to make FeRAM are not commonly used in CMOS integrated circuit manufacturing. Both the PZT ferroelectric layer and the noble metals used for electrodes raise CMOS process compatibility and contamination issues.

However, the storage density FeRAM demonstrates is much lower than that of Flash memory and, therefore, its fabrication cost is much higher. Flash memory cells can store multiple bits per cell (up to three in the highest density NAND Flash devices) and for this reason the areal bit density of Flash memory is much

higher with respect to FeRAM, bringing the cost per bit of Flash memory orders of magnitude below that of FeRAM. The density of FeRAM arrays might be increased by improvements in FeRAM fabrication process flow and cell structures, such as the development of vertical capacitor structures (the same way as for DRAM) to reduce the area of the cell footprint.

#### 1.1.6 Resistive Random Access Memory - ReRAM

The last technology alternative presented here is Resistive RAM (ReRAM). Non-volatility is based on the reversible breakdown of an oxide. This technology is still at a research stage. The memory device consists of a resistance-changeable material sandwiched by two terminal electrodes. Resistance change can be achieved by applying controlled current or voltage pulses to the electrodes. The resistance state remains stable with no need for refresh.

Up to date, a number of different switching characteristics have been observed in a variety of material systems, which include NiO<sub>2</sub>, TiO<sub>2</sub>, HfO<sub>2</sub>, WOx, CuOx and TaOx. In fact, it has become understood that a number of combinations of an oxide with metal electrodes can exhibit some kind of resistance switching behavior [19].

Two main classes of ReRAM, based on different mechanisms, exist: OxRAM based on metallic filament formation and CBRAM based on ionic conduction. Oxide-based RAM is the object of research by companies such as Fujitsu, Samsung, Macronix, Panasonic, Sharp, STMicroelectronics, SMIC and TSMC. CB-RAM is (or has been) the object of research by companies such as Qimonda, Micron, Samsung and Sony.

#### 1.1.6.1 Oxide-based Resistive Random Access Memories - OxRAM

Resistive switching refers to the physical phenomenon where a dielectric suddenly changes its resistance under the application of an electric field or current. This resistance change is non-volatile and reversible. Typical resistive switching systems are capacitor-like devices, where the electrode is an ordinary metal and the dielectric a transition metal oxide. An interesting application of resistive switching is the fabrication of novel non-volatile oxide-based resistive random access memories (OxRAM). This effect also represents the base of the operation of the so-called memristor devices [20] and neuromorphic memory applications [21].

OxRAM is expected to be a memory technology that can bring a revolution in memory hierarchy and system architecture, since it can be integrated with conventional CMOS in a simple way and presents a lot of advantages, such as low cost, BEOL compatibility, non-volatility with high-speed, bit-alterable read/write, good endurance and potentially low power/energy consumption.

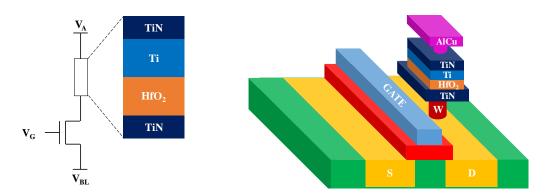

Figure 1.14: A typical 1T1R structure of OxRAM based on HfO<sub>2</sub>.

A basic OxRAM structure consists of an oxide material sandwiched between two metal electrodes (metal-insulator-metal - MIM) (Fig. 1.14). The structure exhibits resistive switching between a High Resistance State (HRS) and a Low Resistance State (LRS). The devices, which initially feature a very high resistance due to the HfO<sub>2</sub> insulating layer, are formed by applying a positive voltage. This induces a soft breakdown of the insulating layer and the formation of a conductive filament (CF) rich in oxygen vacancies and thus the device reaches the LRS.

Upon the application of a voltage of opposite polarity across the device, a RESET operation occurs: the CF is partially disrupted, thus bringing the device to the HRS. Applying a positive voltage across the device (with a lower amplitude with respect to the forming operation) leads to the reformation of the CF and the device is switched back to the LRS. To read the data from the cell, a small read voltage is applied that does not affect the state of the memory cell but is able to detect whether the cell is in the HRS or in the LRS.

A filamentary OxRAM device exhibits a characteristic of abrupt current increase during forming/SET operations. Therefore, a current limiter, which can optimally clamp the forming/SET current, is necessary to prevent the degradation of the HRS (protecting the cell from a permanent dielectric breakdown during the SET operation) and eventually the failure of the memory device. Due to the benefits of fast response time and very large incremental output resistance in the saturation region, a transistor may serve as an excellent current limiter.

One of the key motivations that pushed the development of metal-oxide ReRAM technology is its potential scalability to the nanometer regime. In principle, OxRAM can potentially scale to sub-10 nm dimensions. The resistance of the HRS increases as the inverse of the cell area. The conduction current in the LRS is mainly filamentary conduction current. This means that the resistance of the LRS has only a slight dependence on the cell area. This trend of increasing the HRS/LRS resistance ratio as cell area decreases is a benefit of device scaling. In recent years, more and more

Figure 1.15: Schematic illustration of the CBRAM switching mechanism. In order to achieve the ON state, a redox reaction drives Ag ions into the electrolyte, which results in a conductive bridge. When programming the cell to the OFF state, the size and the number of the Ag-rich clusters is reduced, thus breaking the conductive bridge [24].

metal-oxide memory devices with sub-100 nm feature size have been fabricated by either optical or e-beam lithography.

Nevertheless, one of the major barriers to large-scale manufacturing of OxRAM is the poor uniformity of device characteristics. Significant parameter fluctuations exist in terms of variation of the switching voltages as well as of the HRS and LRS resistance values. The variations of the resistance switching include temporal (cycle to cycle) and spatial fluctuations (device to device). The origin of these variations may be attributed to the stochastic nature of oxygen vacancies generation [22]. The LRS resistance variation comes from the variation of the number or the size of CF's, thus the reduction of possible filament paths effectively confines the active switching region and leads to a reduction of the LRS variation. The HRS resistance variation results from the variation of the ruptured CF's length. The observed variation is an intrinsic property of OxRAM technology, which needs to be addressed in order for the technology to become a viable non-volatile memory solution.

#### 1.1.6.2 Conductive Bridge Random Access Memory - CBRAM

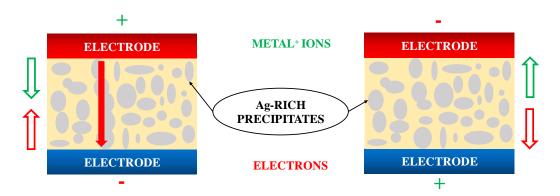

Conductive Bridge Random Access Memory (CBRAM) is a highly promising future non-volatile memory technology, since it exhibits high-speed switching, low SET/RESET currents and ease of BEOL integration. Its operation is based on a steady-state electrolyte, in which ions such as Ag<sup>+</sup> or Cu<sup>+</sup> move along the applied field and form a conductive bridge in the electrolyte [23]. A typical CBRAM memory cell consists of a layer of a Metal-Oxide resistive layer, deposited on a metal plug, combined with a Cu-based ion supply layer, deposited as a top electrode.

Fig. 1.15 illustrates the CBRAM switching mechanism, which is based on the polarity dependent electrochemical deposition and removal of metal in a thin solid-

state electrolyte film. The ON state (low resistance) is achieved by applying a positive bias larger than a threshold voltage  $V_{TH}$ , at the oxidizable anode, which results in redox reactions driving  $Ag^+$  ions into the electrolyte. This leads to the formation of metal-rich clusters, which form a conductive bridge between the two electrodes. The device can be switched back to the OFF state by applying a reverse bias voltage. In this case, metal ions are removed from the glass and, due to that, the size and number of metal-rich clusters are reduced, thus resulting in an erased conductive bridge (resistance increase) [24].

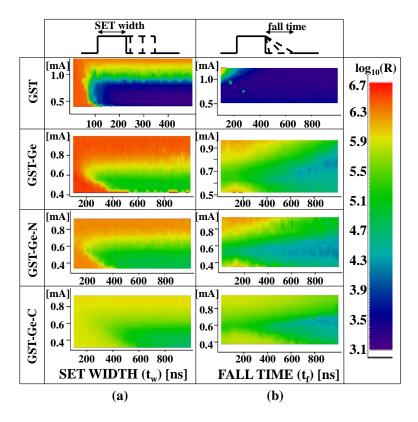

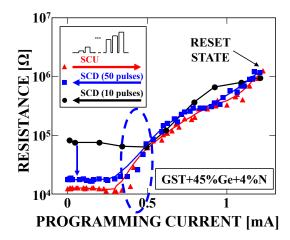

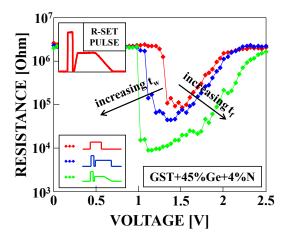

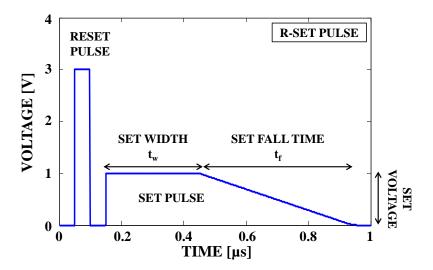

Despite its promise, CBRAM still needs to address many issues in order to establish itself as a key protagonist in the non-volatile memory market. New CBRAM generations use oxides as electrolytes and a Cu-based active electrode in order to improve the thermal stability, tolerating a slight increase of the operating voltages. Nevertheless, an issue of oxide-based CBRAM remains the variability of the High Resistance State, which results in a dispersion and instability of retention characteristics at high temperature. It has been recently reported that the filament morphology as well as the programming conditions can drastically increase high temperature data retention, leading to thermally stable cells at high temperatures [25], [26].

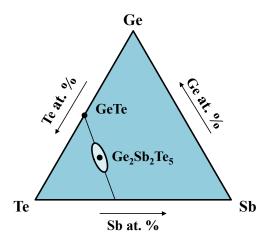

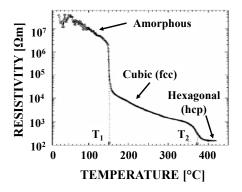

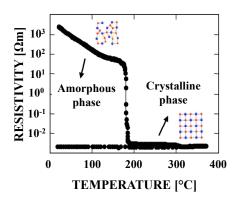

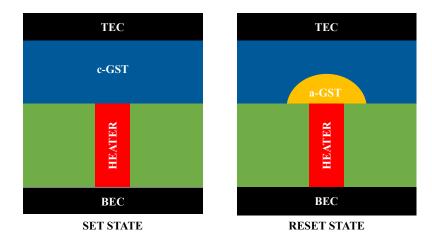

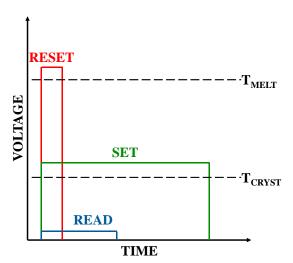

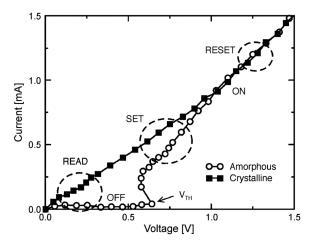

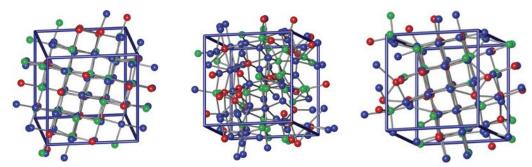

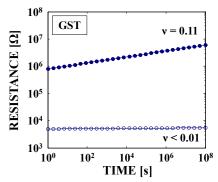

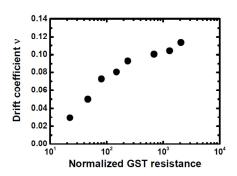

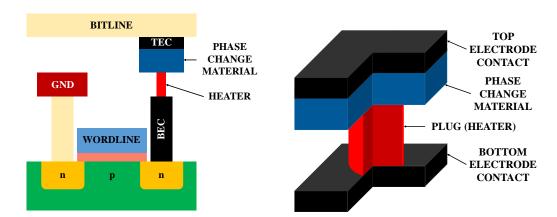

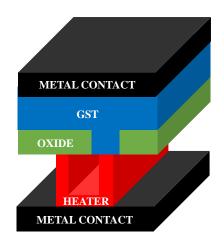

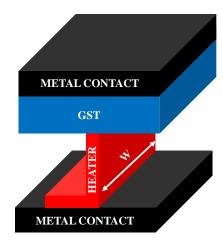

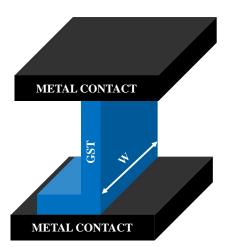

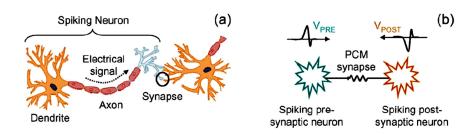

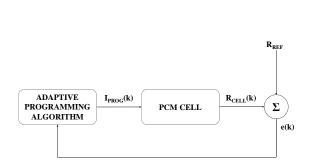

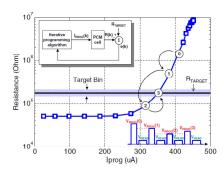

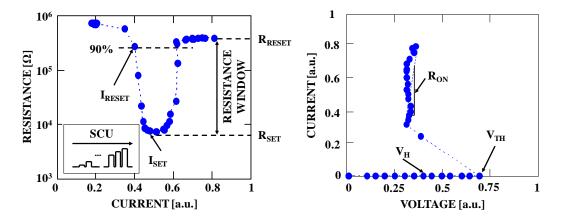

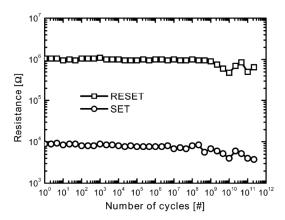

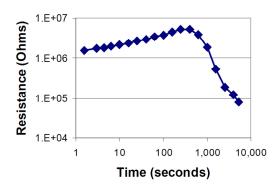

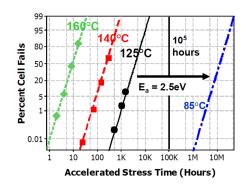

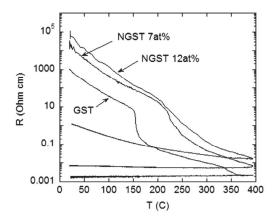

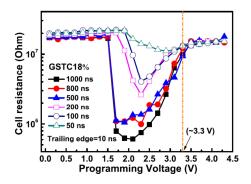

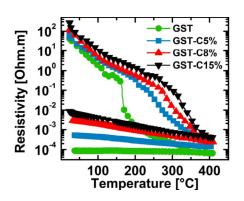

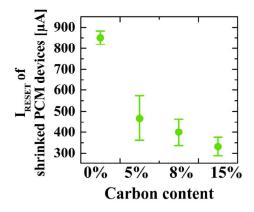

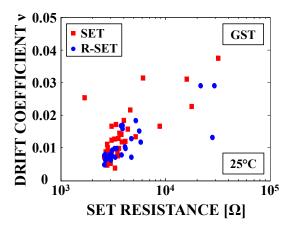

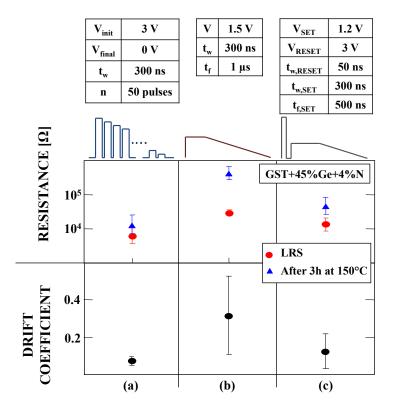

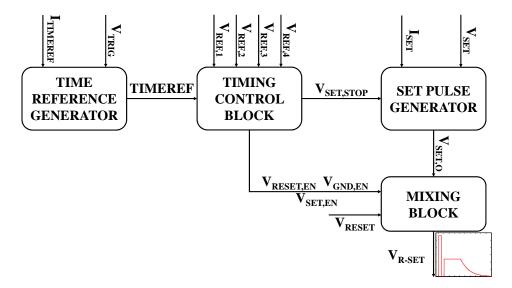

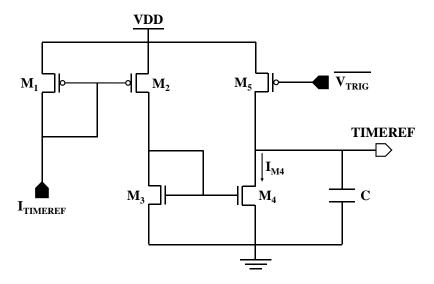

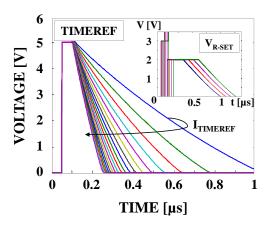

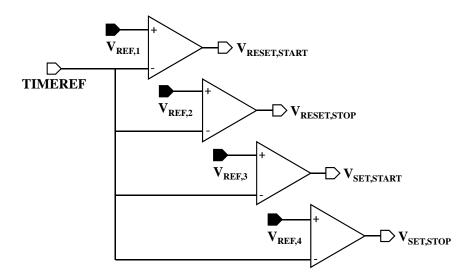

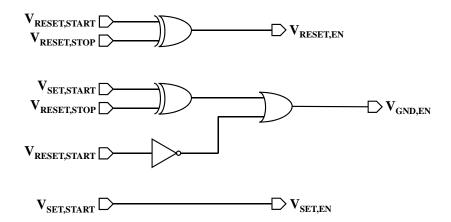

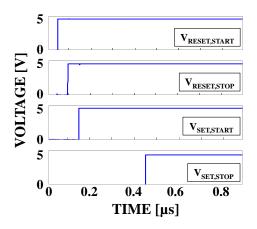

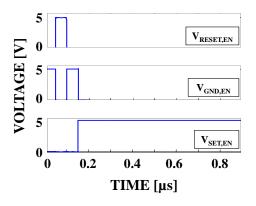

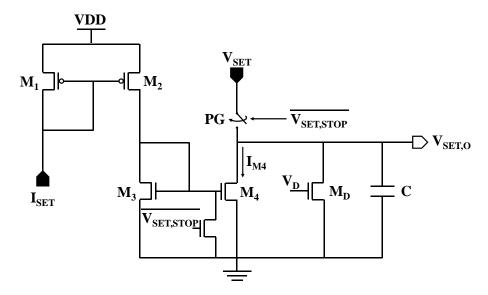

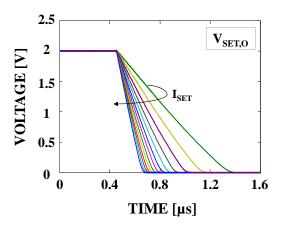

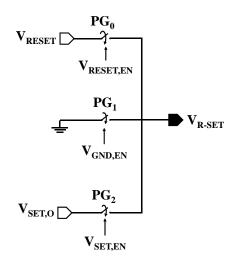

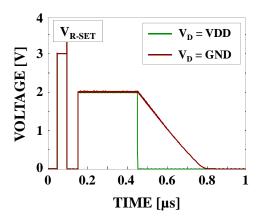

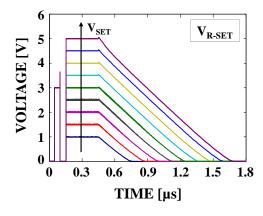

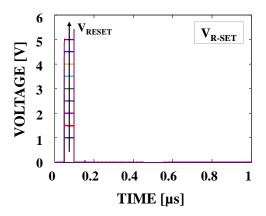

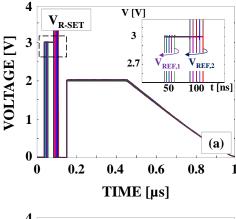

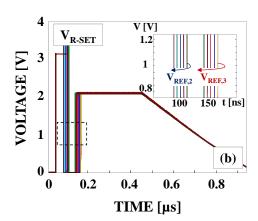

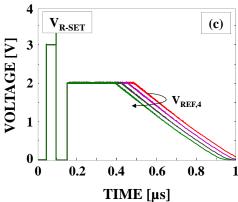

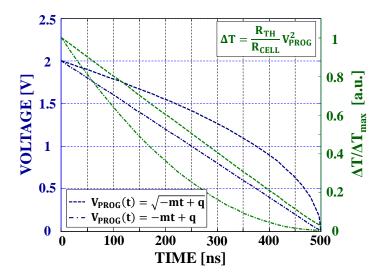

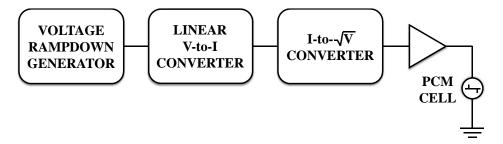

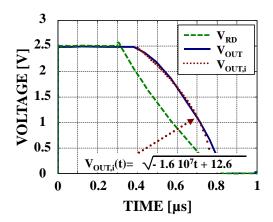

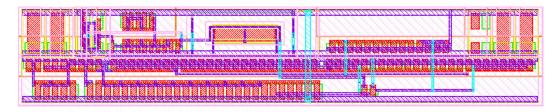

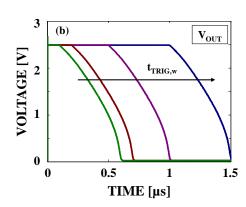

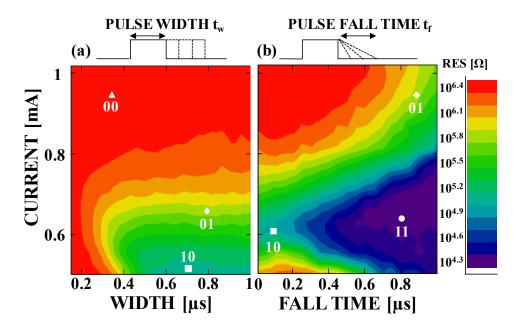

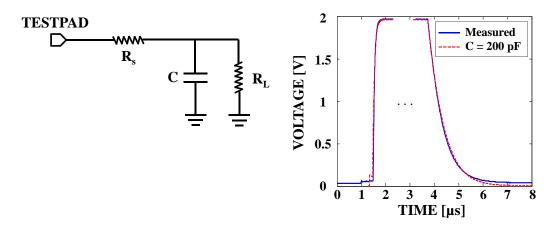

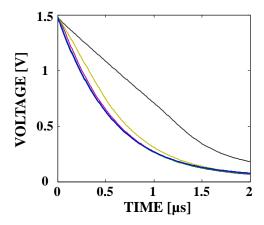

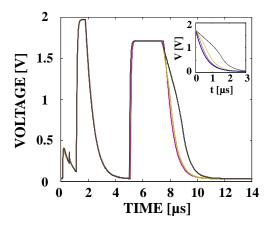

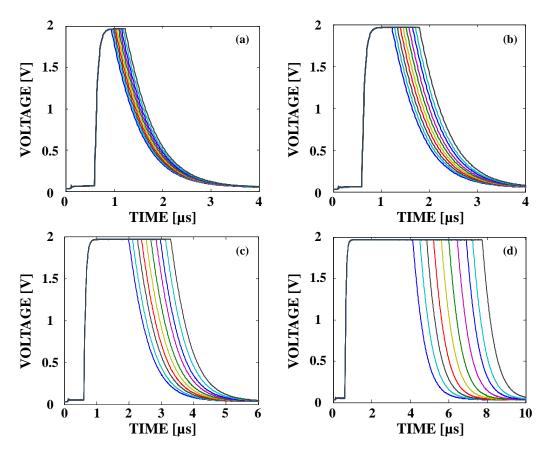

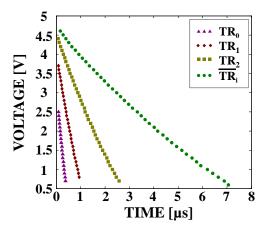

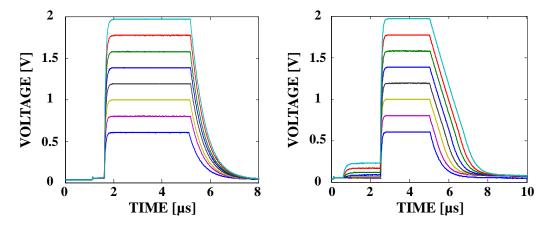

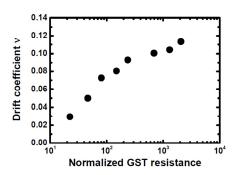

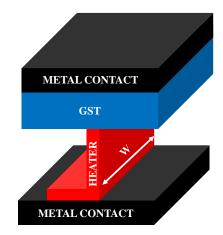

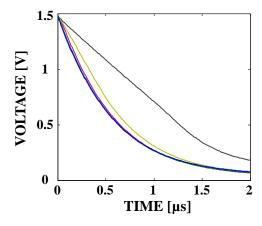

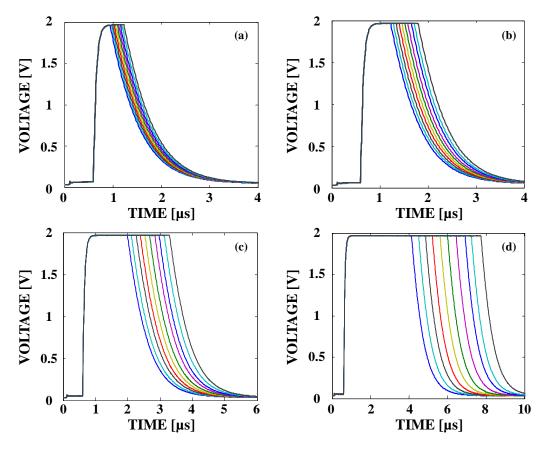

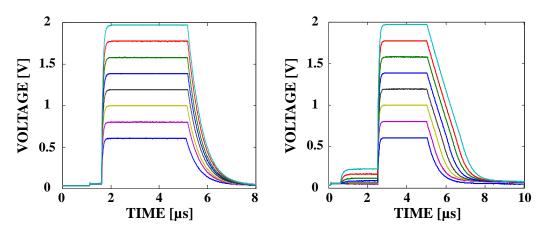

#### 1.2 Phase Change Memory