# Development of predictive models for the electromagnetic robustness of electronic components $_{\rm He\ Huang}$

#### ▶ To cite this version:

He Huang. Development of predictive models for the electromagnetic robustness of electronic components. Micro and nanotechnologies/Microelectronics. INSA de Toulouse, 2015. English. NNT: 2015ISAT0036. tel-01261471

### HAL Id: tel-01261471 https://theses.hal.science/tel-01261471

Submitted on 25 Jan 2016

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# **THÈSE**

#### En vue de l'obtention du

### DOCTORAT DE L'UNIVERSITÉ DE TOULOUSE

Délivré par :

Institut National des Sciences Appliquées de Toulouse (INSA de Toulouse)

#### Présentée et soutenue par : He HUANG

le lundi 7 décembre 2015

Titre:

Développement de modèles prédictifs pour la robustesse électromagnétique des composants électroniques

#### École doctorale et discipline ou spécialité :

ED GEET: Micro et Nanosystèmes

Unité de recherche:

LAAS-CNRS

#### Directeur/trice(s) de Thèse:

Sonia BEN DHIA (Maitre de conférences/HDR - INSA Toulouse, LAAS-CNRS) Alexandre BOYER(Maitre de conférences - INSA Toulouse, LAAS-CNRS)

#### Jury:

Jean-Marie DILHAC (Professeur, INSA Toulouse) Président du Jury Geneviève DUCHAMP (Professeur, Université Bordeaux) Rapporteur Miguel Jesus ROCA ADROVER (Professeur, Universitat de les Illes Balears) Rapporteur Flavio CANAVERO (Professeur, Politecnico di Torino) Examinateur Bertrand VRIGNON (Ingénieur, Freescale France) Invité

### **Abstract**

One important objective of the electromagnetic compatibility (EMC) studies is to make the products compliant with the EMC requirement of the customers or the standards. However, all the EMC compliance verifications are applied before the delivery of final products. So we might have some new questions about the EMC performance during their lifetime. Will the product still be EMC compliant in several years? Can a product keep the same EMC performance during its whole lifetime? If not, how long the EMC compliance can be maintained?

The study of the long-term EMC level, which is called "electromagnetic robustness", appeared in the recent years. Past works showed that the degradation caused by aging could induce failures of electronic system, including a harmful evolution of electromagnetic compatibility. In this study, the long-term evolution of the EMC levels of two electronic component groups has been studied. The first electronic component type is the integrated circuit. The high-frequency currents and voltages during the switching activities of ICs are responsible for unintentional emissions or coupling. Besides, ICs are also very often the victim of electromagnetic interference. Another group of components is the passive component. In an electronic system, the IC components usually work together with the passive components at PCB level. The functions of passive components in an electronic system, such as filtering and decoupling, also have an important influence on the EMC levels.

In order to analyze the long-term evolution of the EMC level of the electronic components, the study in this thesis tends to propose general predictive methods for the electromagnetic compatibility levels of electronic components which evolve with time.

#### Key words:

Electromagnetic robustness, Electromagnetic compatibility, Aging, Degradation mechanisms, EMC modeling, Degradation modeling, Integrated circuits, Passive components, Electromagnetic Reliability

### Résumé

Un objectif important des études de la compatibilité électromagnétique (CEM) est de rendre les produits conformes aux exigences CEM des clients ou les normes. Cependant, toutes les vérifications de la conformité CEM sont appliquées avant la livraison des produits finis. Donc nous pourrions avoir de nouvelles questions sur les performances CEM des systèmes électroniques au cours de leur vie. Les comportements CEM de ces produits seront-ils toujours conformes dans plusieurs années ? Un produit peut-il garder les mêmes performances CEM pendant toute sa durée de vie ? Si non, combien de temps la conformité CEM peut-elle être maintenue ?

L'étude à long terme de l'évolution des niveaux CEM, appelée "robustesse électromagnétique», est apparue ces dernières années. Les travaux précédents ont montré que la dégradation causée par le vieillissement pourrait induire des défaillances de système électronique, y compris une évolution de la compatibilité électromagnétique. Dans cette étude, l'évolution à long terme des niveaux CEM de deux groupes de composants électroniques a été étudiée. Le premier type de composant électronique est le circuit intégré. Les courants de hautes fréquences et les tensions induites au cours des activités de commutation de circuits intégrés sont responsables des émissions électromagnétiques non intentionnelles. En outre, les circuits intégrés sont aussi très souvent les victimes d'interférences électromagnétiques. Un autre groupe de composants est formé par les composants passifs. Dans un système électronique, les circuits intégrés fonctionnent souvent avec les composants passifs sur un même circuit imprimé. Les fonctions des composants passifs dans un système électronique, telles que le filtrage et le découplage, ont également une influence importante sur les niveaux de CEM.

Afin d'analyser l'évolution à long terme des niveaux CEM des composants électroniques, les travaux présentés dans cette thèse ont pour objectif de proposer des méthodes générales pour prédire l'évolution dans les temps des niveaux de compatibilité électromagnétique des composants électroniques.

#### Mots clés:

Robustesse électromagnétique, Compatibilité électromagnétique, Vieillissement, Mécanismes de dégradation, Modélisation CEM, Modélisation de la dégradation, Circuits intégrés, Composants passifs, Fiabilité électromagnétique

### Remerciements

Ce travail a été effectué au sein du Laboratoire d'analyse et d'architecture des systèmes. Je voudrais commencer par remercier Jean Arlat, directeur du LAAS, pour m'avoir accueilli durant ces trois années de thèse.

J'adresse mes sincères remerciements à Jean-Marie Dilhac qui me fait l'honneur de présider mon jury, ainsi qu'à Geneviève Duchamp et à Miguel Jesús Roca Adrover qui ont accepté d'être rapporteurs de ce manuscrit de thèse. Je leur en suis très reconnaissant, en particulier pour la qualité des conseils et des remarques concernant la correction du manuscrit. Je tiens aussi à remercier Flavio Canavero et Bertrand Vrignon pour leur participation au jury et l'intérêt qu'ils ont porté à mes travaux de recherche.

Je souhaiterais témoigner toute ma sympatie et ma vive reconnaissance à mes encadrants de thèse, Sonia Ben Dhia et Alexandre Boyer, pour toute leur aide. Ils ont toujours été là pour me soutenir et me conseiller durant mes trois ans de thèse. Je voudrais les remercier pour leur disponibilité et leur confiance. Ils m'ont également beaucoup aidé pour la rédaction de ce mémoire.

Un grand merci à tout le personnel technique et administratif du laboratoire pour leur aide et leur bonne humeur. Au cours de ces années j'ai fait parti de l'équipe «Énergie et systèmes embarqués» sous la direction de Jean-Marie Dilhac au sein du LAAS. Les discussions que j'ai pu avoir durant les réunions d'équipe ou en dehors avec Marise Bafleur, Fabrice Caignet, Patrick Tounsi, Veljko Tomasevic, Chaimae Ghfiri m'ont beaucoup apporté. Je tiens tout particulièrement à exprimer ma gratitude à Ascension De Sousa Berdat pour ses aides de l'organisation.

Je tiens aussi remercier tous les collegus de mon grand bureau, Camille, Hiba, Anaïs, Christophe, Veljko, Tanguy, Sylvain, Hakim et Yannick pour leur gentillesse et leur humeur. Ils m'ont beaucoup aidé et sont devenus des amis à qui je souhaite tout le courage qu'ils m'ont apporté.

Je remercie toutes les amis avec qui j'ai partagé ces années de thèse, en particulier à Cheng et Marco pour leur soutien.

Enfin, je ne peux terminer ces remerciments sans exprimer toute ma gratitude à mes parents et ma famille, en particulier à Rémi, Yali, Alain, Chloé, Nina et Sophie qui m'ont soutenu tout au long de cette thèse.

# **Table of contents**

| ABSTRACT.   |                                                          | I    |

|-------------|----------------------------------------------------------|------|

| RESUME      |                                                          | ا    |

| REMERCIEN   | MENTS                                                    |      |

| TABLE OF C  | CONTENTS                                                 | IV   |

| LIST OF FIG | GURES                                                    | IX   |

| LIST OF TAE | BLES                                                     | XVII |

| CHAPTER I.  | . GENERAL INTRODUCTION                                   | 1    |

| I.1. T      | THESIS CONTEXT                                           | 1    |

| 1.2. S      | Scope of this dissertation                               | 2    |

| I.3. R      | References                                               | 3    |

| CHAPTER II  | II. LONG TERM ELECTROMAGNETIC COMPATIBILITY              | 5    |

| II.1. II    | Introduction                                             | 5    |

| II.2. E     | ELECTROMAGNETIC COMPATIBILITY ISSUES                     | 5    |

| II.2.1.     | A small discussion about EMC                             | 5    |

| 11.2.2.     | What is EMC?                                             | 7    |

| II.2.3.     | History scope                                            | 8    |

| II.3. E     | EMC of integrated circuits                               | 11   |

| II.3.1.     | Brief historical review                                  | 12   |

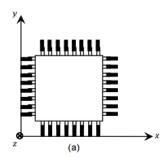

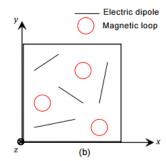

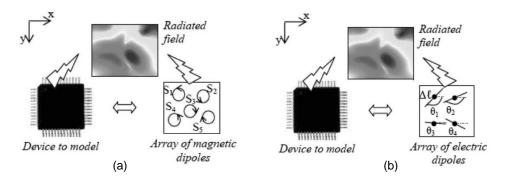

| II.3.2.     | Mechanisms of EMC at circuit level                       | 13   |

| 11.3.2      | .2.1. Interference coupling modes of integrated circuits | 13   |

| 11.3.2      | .2.2. Mechanisms of electromagnetic emission             | 15   |

| II.3.2      | .2.3. Mechanisms of electromagnetic susceptibility       | 16   |

| II.3.3.     | Influence of IC technological evolution on EMC           | 19   |

| 11.3.4.     | EMC measurement of ICs                                   | 21   |

| II.3.4      | .4.1. EME measurement methods                            | 22   |

| II.3.4      | .4.2. EMI measurement methods                            | 23   |

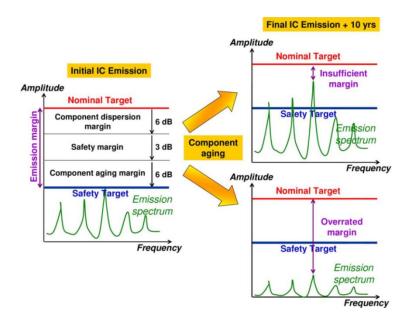

| 11.3.4      | .4.3. Margins of EMC level                               | 25   |

| II.3.5.     | EMC modeling for IC design                               | 27   |

| II.4. EN             | 1 Robustness                                                            | 30        |

|----------------------|-------------------------------------------------------------------------|-----------|

| II.4.1.              | Context                                                                 | 30        |

| 11.4.2.              | EMC problem in long term                                                | 31        |

| 11.4.3.              | Prediction of EMC evolution induced by aging                            | 33        |

| 11.4.4.              | EMC drift dispersion induced by aging                                   | 35        |

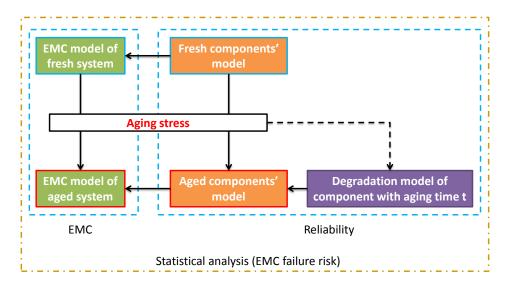

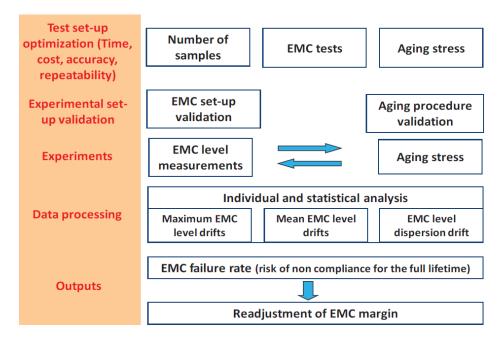

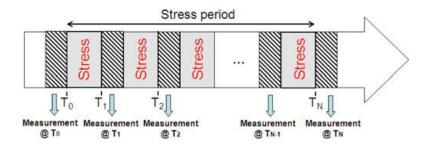

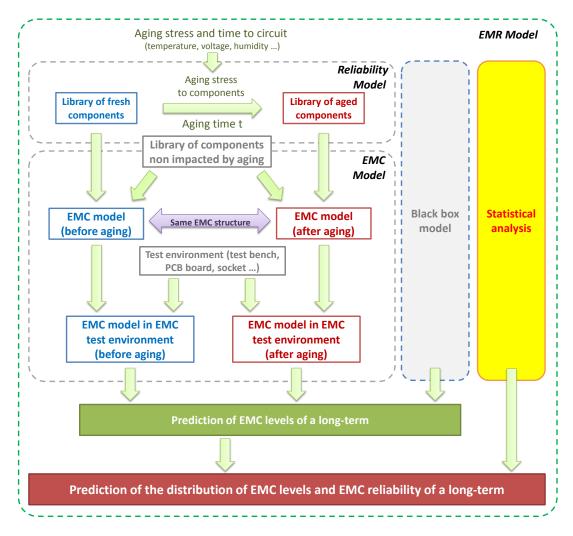

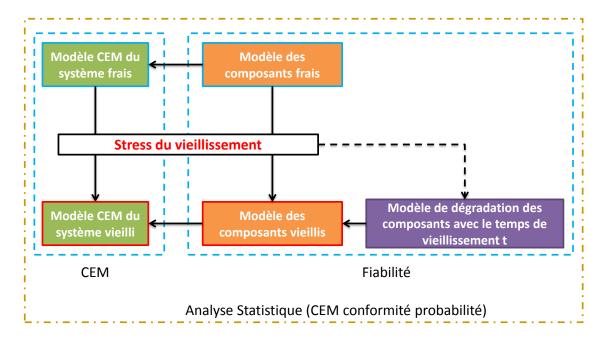

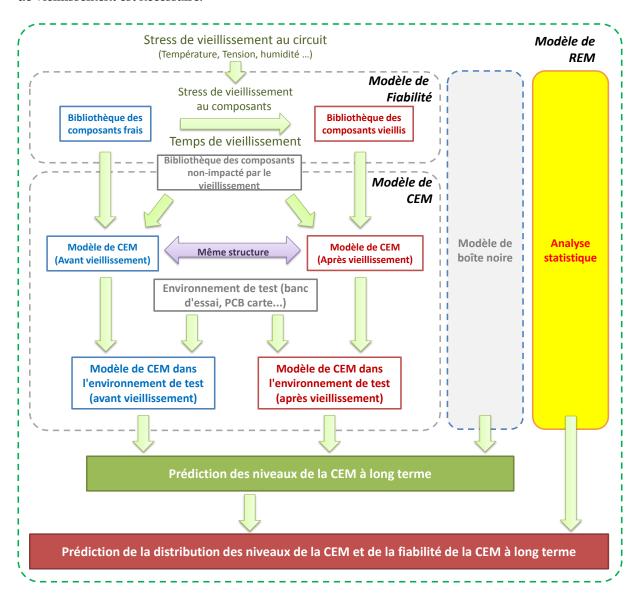

| 11.4.5.              | General EMR prediction flow                                             | 36        |

| II.5. Co             | NCLUSION                                                                | 37        |

| II.6. RE             | FERENCES                                                                | 38        |

| CHAPTER III.         | ORIGIN OF EMC DRIFT WITH TIME: RELIABILITY ISSUES OF ELECTRONIC DEVICES | S 41      |

| III.1. INT           | RODUCTION                                                               |           |

|                      | LIABILITY OF ELECTRONIC DEVICES                                         |           |

| III.2.1.             | Definition of reliability                                               |           |

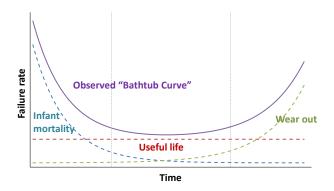

| III.2.1.<br>III.2.2. | Failure rate and Bathtub curve                                          |           |

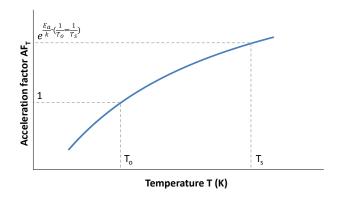

|                      | Accelerated aging test                                                  |           |

| III.2.3.             | 5 5                                                                     |           |

| III.2.3.             |                                                                         |           |

| III.2.3.<br>III.2.3. |                                                                         |           |

|                      | ING IMPACT ON SEMICONDUCTORS AND MODELING                               |           |

| III.3.1.             | Degradation mechanisms of semiconductors                                |           |

| III.3.1.             |                                                                         |           |

| III.3.1.             |                                                                         |           |

| III.3.1.             | ·                                                                       |           |

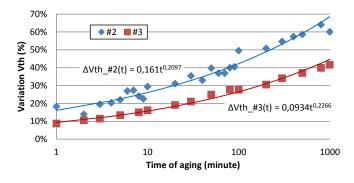

| III.3.2.             | Degradation characterization of transistors                             |           |

| III.3.2.             |                                                                         |           |

|                      | Characterization of NBTI on PMOS                                        |           |

| III.3.2.             | Parameter extraction: Threshold voltage                                 | 58        |

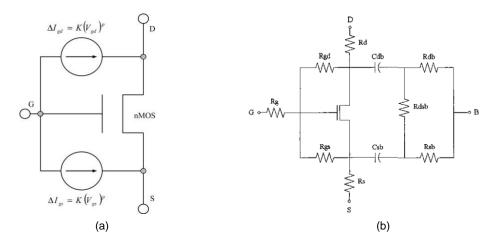

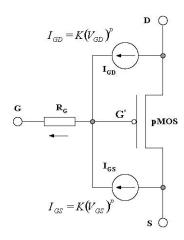

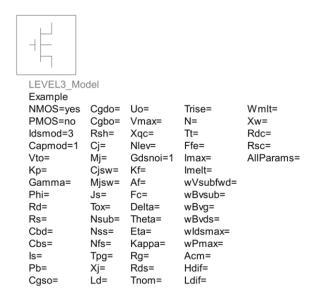

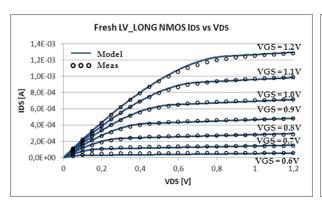

| III.3.3.             | Modeling of transistor aging                                            | 59        |

| III.3.3.             | Transistor equivalent circuit models                                    | 60        |

| III.3.3.             | Degradation modeling based on transistor models                         | 62        |

| III.4. AG            | ING IMPACT ON PASSIVE DEVICES AND MODELING                              | 67        |

| III.4.1.             | Aging impact on passive components                                      | 67        |

| III.4.1.             | 1. Resistor                                                             | 67        |

| III.4.1.             | 2. Capacitors                                                           | 68        |

| III.4.1.             | 3. Inductor                                                             | 73        |

| III.4.2.             | Aging characterization of passive devices                               | 74        |

| III.4.2.             | Network analysis method                                                 | 75        |

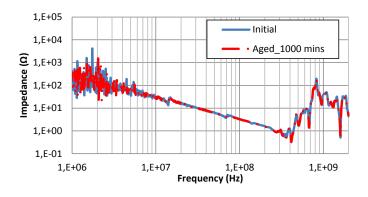

| III.4.2.             | Impedance characterization during aging                                 | 76        |

| III.4.3.             | Degradation modeling of passive devices                                 | <i>77</i> |

| III.4.3.             | Equivalent circuit model of Resistor                                    | 78        |

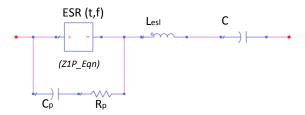

| III.4.3.2.      | Equivalent circuit model of Capacitor                                            | 79  |

|-----------------|----------------------------------------------------------------------------------|-----|

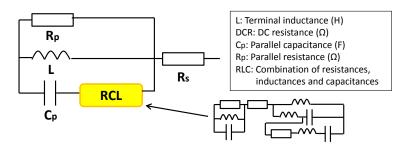

| III.4.3.3.      | Equivalent circuit model of Inductor                                             | 83  |

| III.4.3.4.      | Aging impact modeling for passive devices                                        | 85  |

| III.5. CASES    | STUDY: MODELING OF AGING IMPACT ON PASSIVE DEVICES                               | 87  |

| III.5.1.        | Experimental set-up                                                              | 87  |

| III.5.2.        | Characterization of aging impact                                                 | 89  |

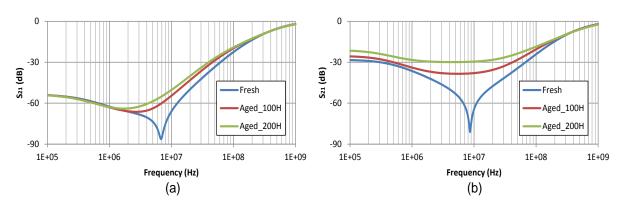

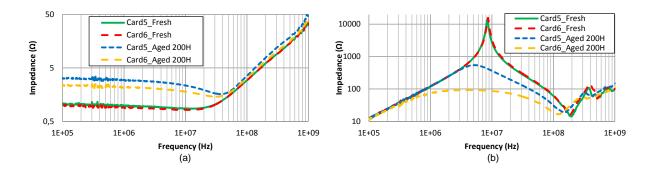

| III.5.2.1.      | Evolution caused by aging stress: effect on capacitors                           | 89  |

| III.5.2.2.      | Evolution caused by aging stress: effect on inductors                            | 91  |

| III.5.2.3.      | Comparison of evolution in two aging conditions                                  | 92  |

| III.5.3.        | Modeling of aging impact on passive devices                                      | 92  |

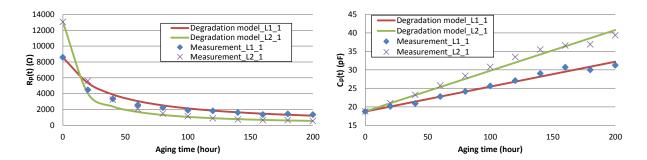

| III.5.3.1.      | Modeling of aluminum capacitor degradation                                       | 93  |

| III.5.3.2.      | Modeling of powder iron inductor degradation                                     | 96  |

| <i>III.5.4.</i> | Conclusion of the case study                                                     | 98  |

| III.6. Conc     | _USION                                                                           | 98  |

| III.7. REFER    | ENCE                                                                             | 99  |

| CHAPTER IV.     | CHARACTERIZATION AND MODELING OF LONG-TERM EMC EVOLUTION                         | 106 |

| IV.1. INTRO     | DUCTION                                                                          | 106 |

| IV.2. EMR       | CHARACTERIZATION                                                                 | 106 |

| IV.2.1.         | Characterization flow                                                            | 106 |

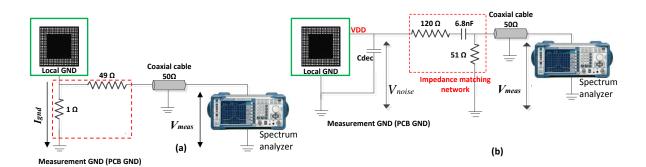

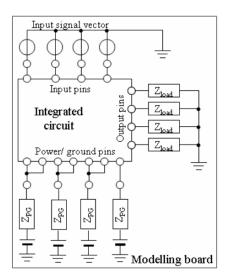

| IV.2.2.         | EMC measurements for ICs adapted to EMR                                          | 108 |

| IV.2.2.1.       | Measurement of conducted emissions: 1 $\Omega/150~\Omega$ direct coupling method | 109 |

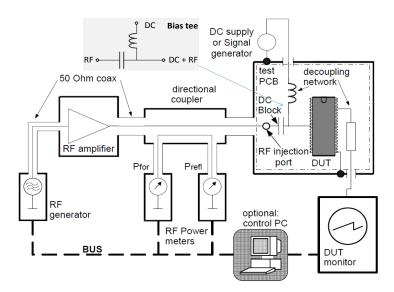

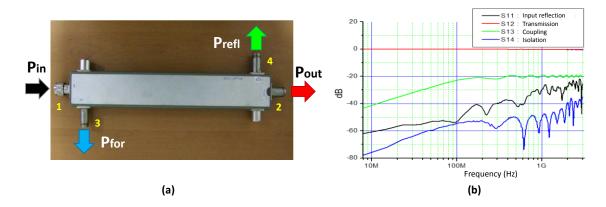

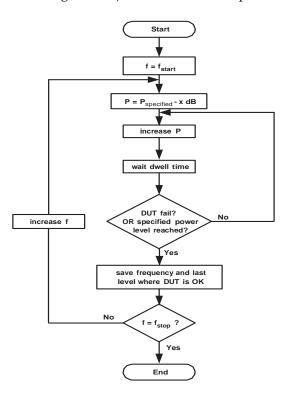

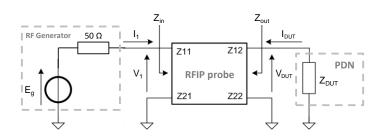

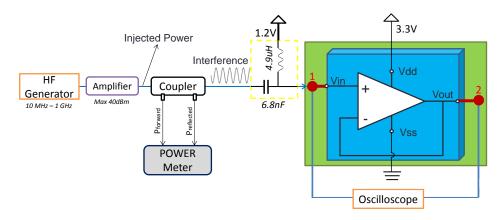

| IV.2.2.2.       | Measurement of conducted immunity: Direct RF power injection method              | 110 |

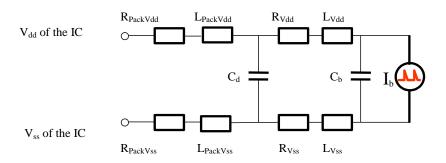

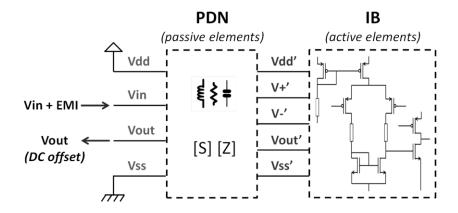

| IV.3. EMC       | MODELING OF ICS                                                                  | 113 |

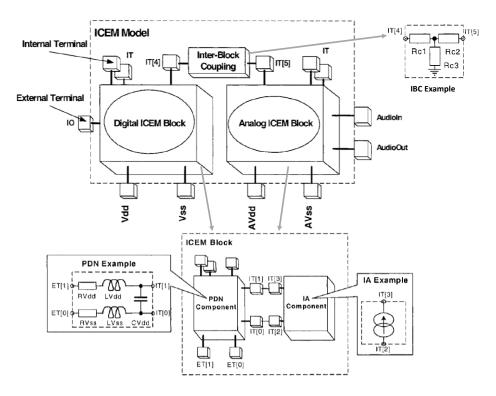

| IV.3.1.         | ICEM model                                                                       | 113 |

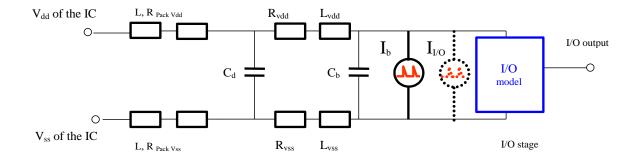

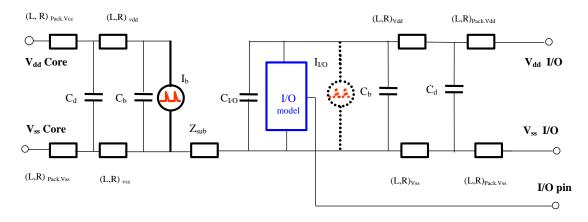

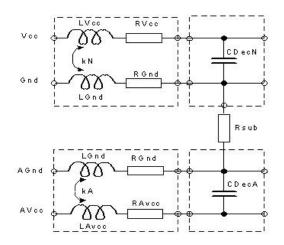

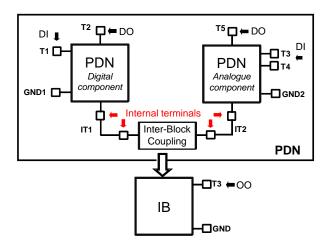

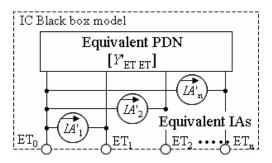

| IV.3.1.1.       | Structure of ICEM                                                                | 113 |

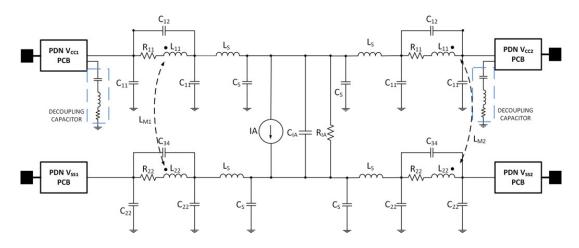

| IV.3.1.2.       | ICEM-CE modeling structures                                                      | 115 |

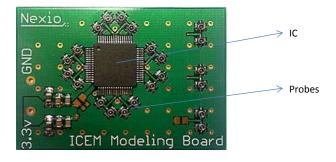

| IV.3.1.3.       | Modeling process of ICEM-CE                                                      | 117 |

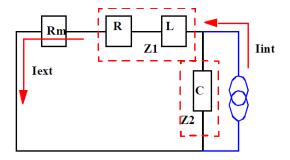

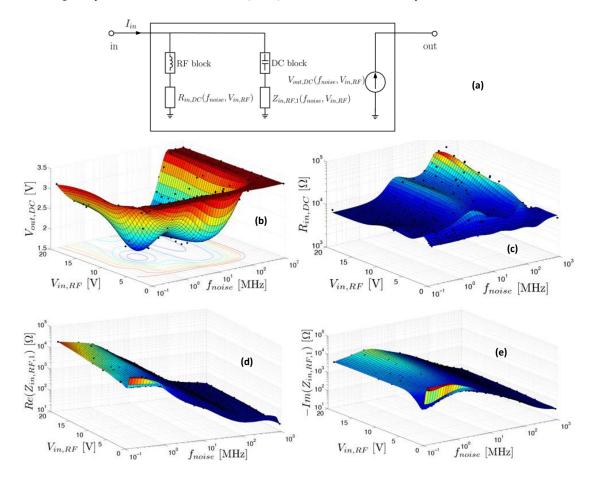

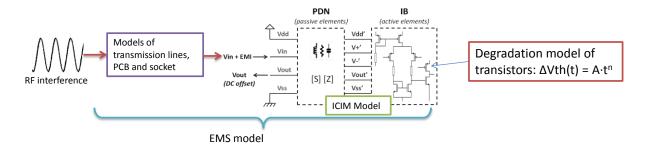

| IV.3.2.         | ICIM model                                                                       | 122 |

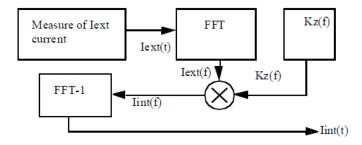

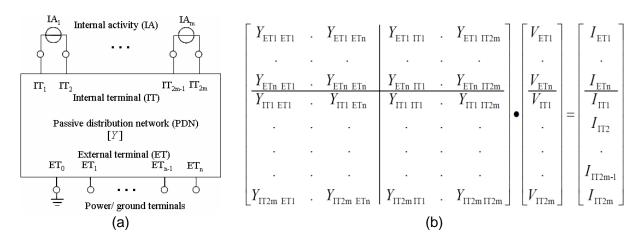

| IV.3.2.1.       | Structure of ICIM-CI                                                             | 122 |

| IV.3.2.2.       | Modeling process of ICIM-CI                                                      | 124 |

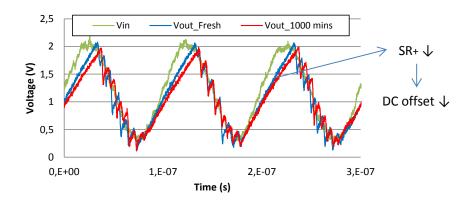

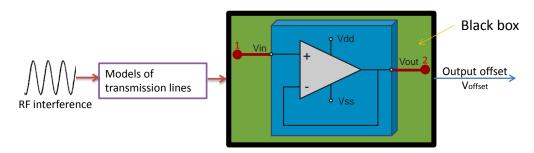

| IV.3.3.         | EMC black-box model                                                              | 126 |

| IV.3.3.1.       | Black box modeling in EME model                                                  | 127 |

| IV.3.3.1.       | Black box modeling in EMI model                                                  | 129 |

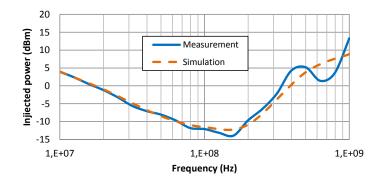

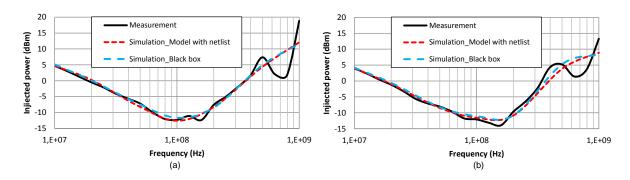

| IV.3.4.         | Validation of model                                                              | 132 |

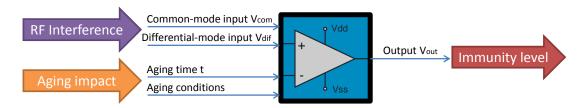

| IV.4. EMR       | MODELING PROCESS                                                                 | 134 |

| IV.5. CASES     | STUDY 1: PREDICTION OF AGING IMPACT ON EMI OF AN OPERATIONAL AMPLIFIER           | 137 |

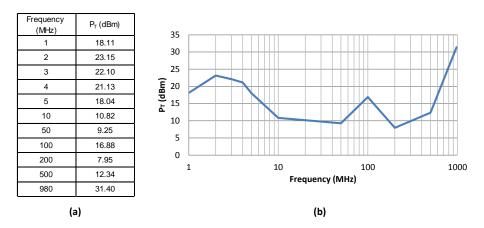

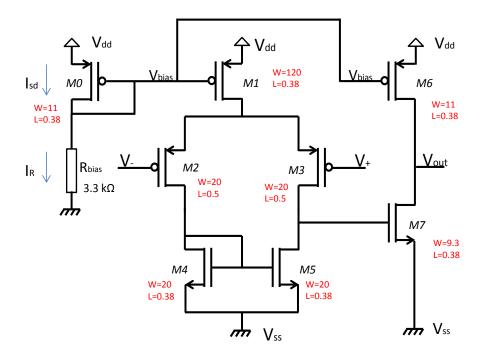

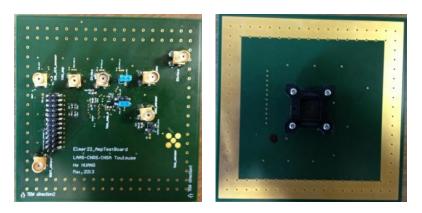

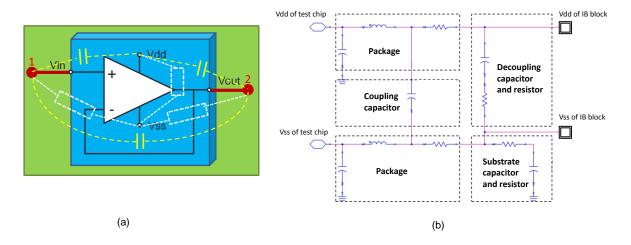

| IV.5.1.         | DUT and experimental set-up                                                      | 137 |

| IV.5.1.1.       | Device under test                                                                | 137 |

| J\/ 5 1 2       | Immunity test configuration                                                      | 138 |

|       | IV.5.1.3.     | Accelerated aging test                                                                  | 139   |

|-------|---------------|-----------------------------------------------------------------------------------------|-------|

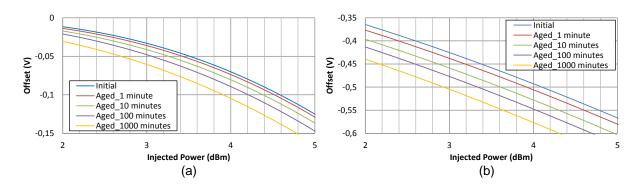

| N     | /.5.2.        | Measurement results                                                                     | . 141 |

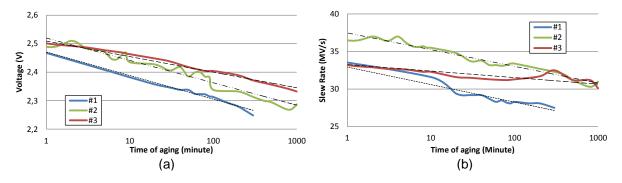

|       | IV.5.2.1.     | Evolution of the electrical parameters of the opamp during aging                        | 141   |

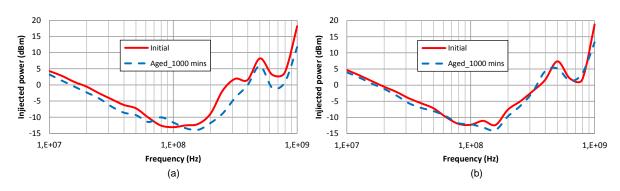

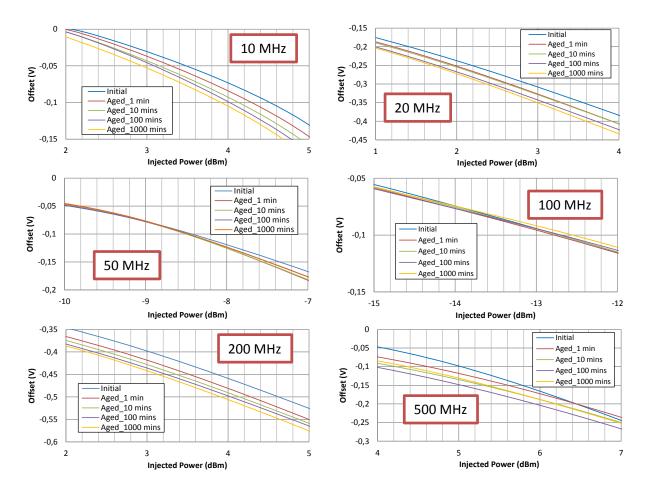

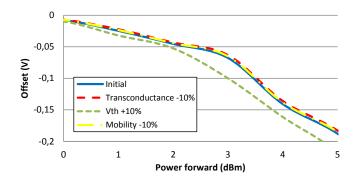

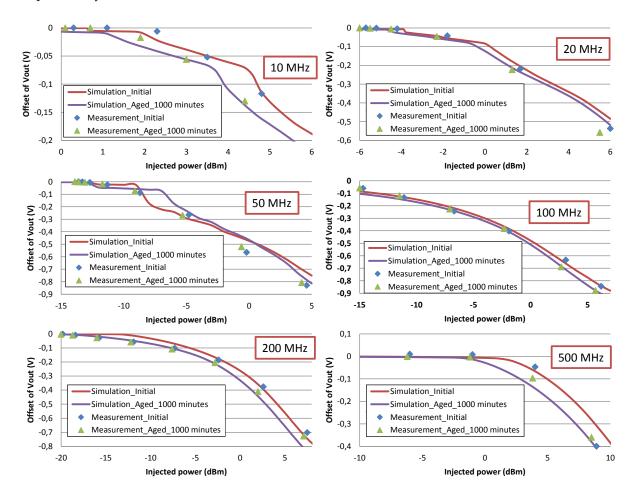

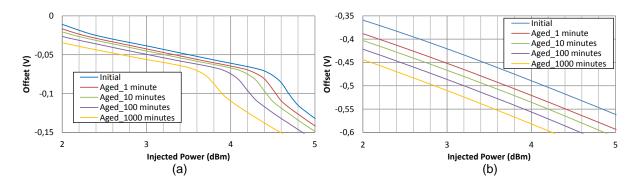

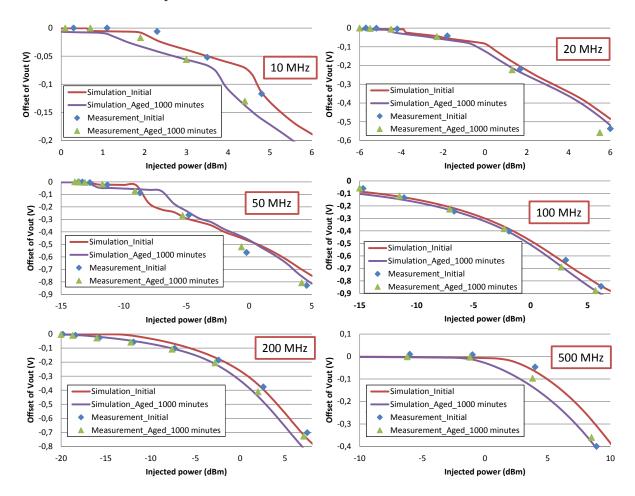

|       | IV.5.2.2.     | Evolution of electromagnetic susceptibility                                             | 144   |

| /\    | /.5.3.        | Long-term immunity prediction                                                           | . 146 |

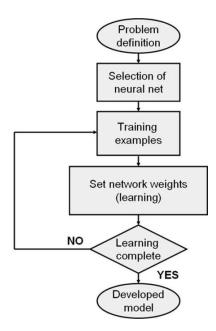

|       | IV.5.3.1.     | Susceptibility model                                                                    | 146   |

|       | IV.5.3.2.     | Aging effect model                                                                      | 150   |

|       | IV.5.3.3.     | Long-term Susceptibility Simulation                                                     | 152   |

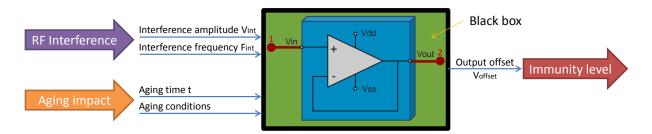

| /\    | /.5.4.        | Black box modeling                                                                      | . 154 |

|       | IV.5.4.1.     | Description of the method                                                               | 154   |

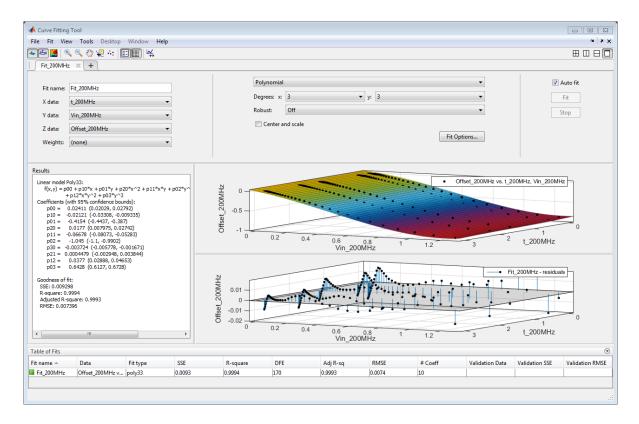

|       | IV.5.4.2.     |                                                                                         |       |

|       | IV.5.4.3.     |                                                                                         |       |

| N     | /.5.5.        | Conclusion of case study                                                                | . 159 |

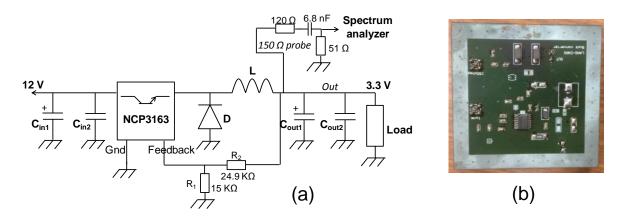

| IV.6  | . CASE        | STUDY 2: PREDICTION OF THE ELECTROMAGNETIC EMISSION EVOLUTION OF A BUCK DC-DC CONVERTER | . 160 |

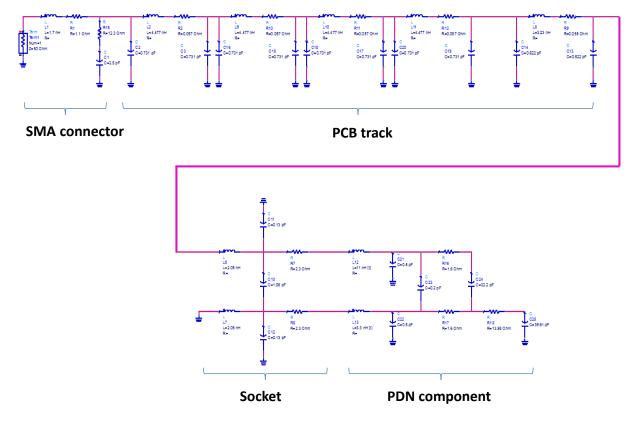

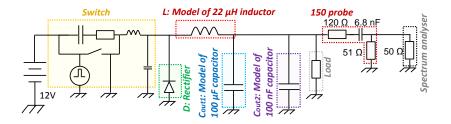

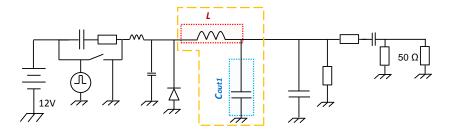

| N     | /.6.1.        | DUT and experimental set-up                                                             | . 161 |

| /\    | /.6.2.        | Measurement results                                                                     | . 163 |

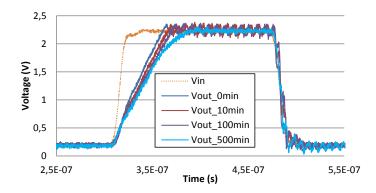

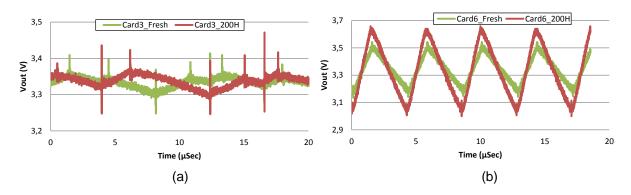

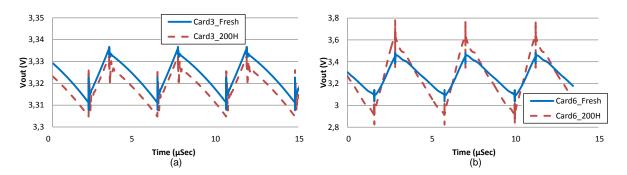

|       | IV.6.2.1.     | Evolution of the output voltage ripple                                                  | 163   |

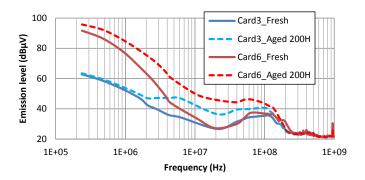

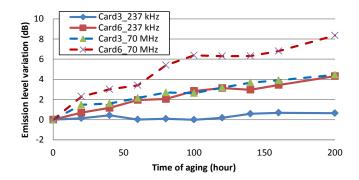

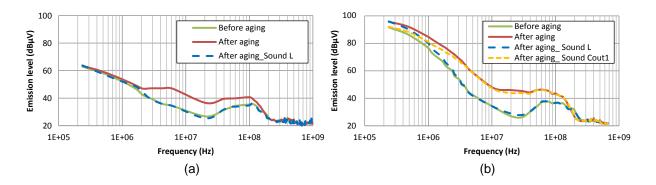

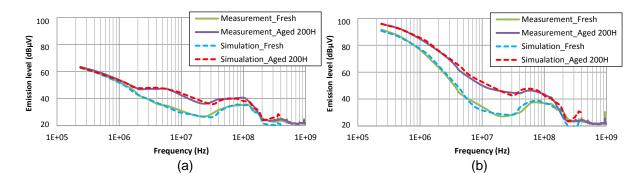

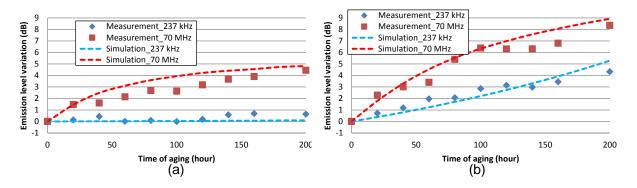

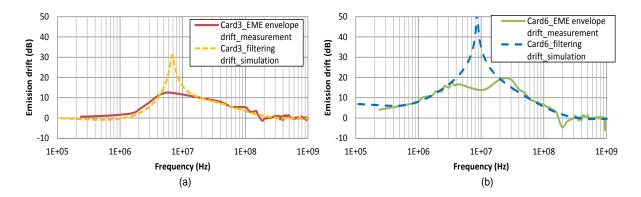

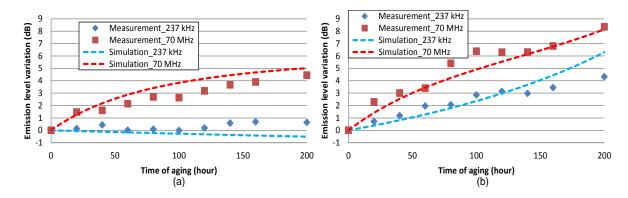

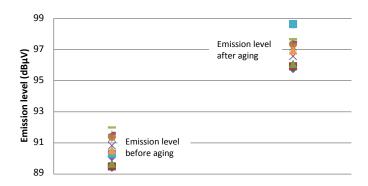

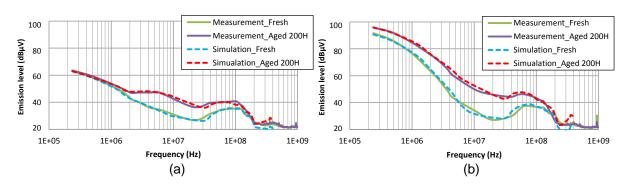

|       | IV.6.2.2.     | Evolution of the conducted emission                                                     | 164   |

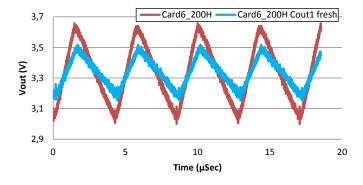

|       | IV.6.2.3.     | Identification of degraded devices                                                      | 165   |

|       | IV.6.2.4.     | Aging impact on passive devices                                                         | 166   |

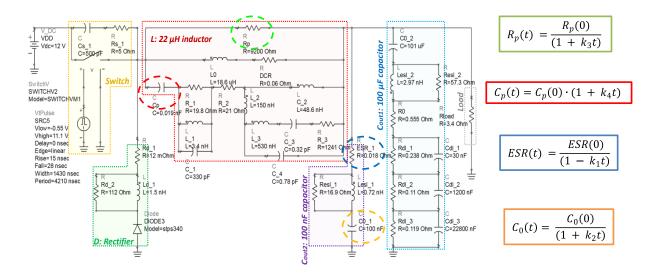

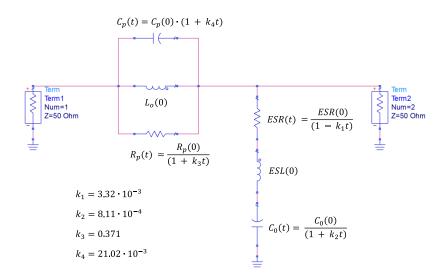

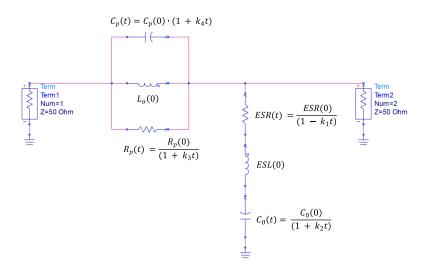

| /\    | /.6.3.        | Modeling of the evolution of conducted emission                                         | . 167 |

| N     | /.6.4.        | Prediction of EME drift by the impedance drift of the passive devices                   | . 169 |

| /\    | /.6.5.        | Conclusion of case study                                                                | . 172 |

| IV.7  | . Cond        | CLUSION                                                                                 | . 173 |

| IV.8  | . Refe        | RENCES                                                                                  | . 174 |

| СНАРТ | ΓER V.        | STATISTICAL ANALYSIS FOR THE EMR PREDICTION                                             | . 180 |

| V.1.  | INTRO         | DDUCTION                                                                                | . 180 |

| V.2.  | STAT          | ISTICAL ANALYSIS IN EMC STUDY                                                           | . 180 |

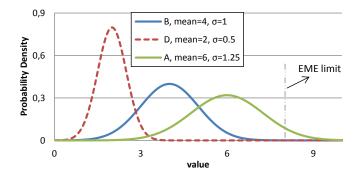

| V     | .2.1.         | Statistics and EMC                                                                      | . 181 |

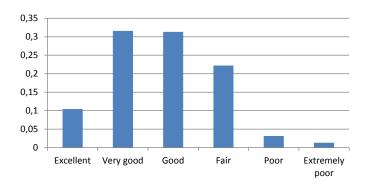

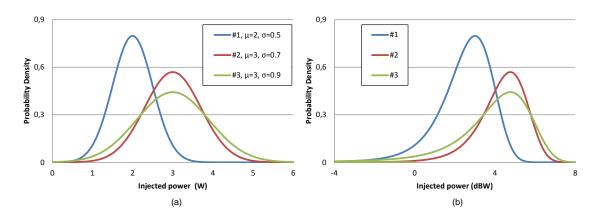

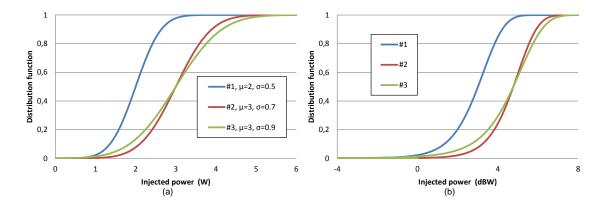

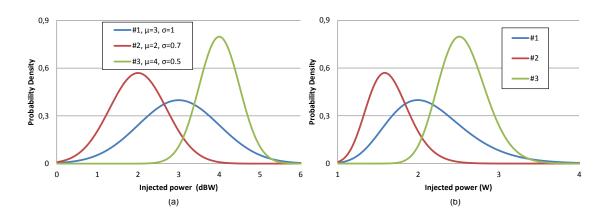

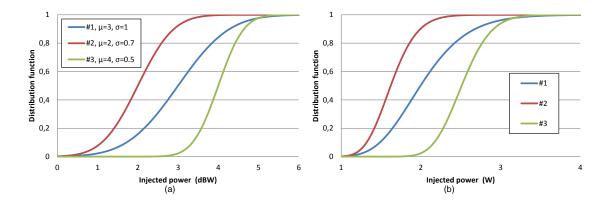

| V     | .2.2.         | Statistical distributions for EMC levels                                                | . 182 |

|       | V.2.2.1.      | Normal distribution                                                                     | 182   |

|       | V.2.2.2.      | Lognormal distribution                                                                  | 183   |

|       | V.2.2.3.      | EMC distribution based on distribution of sub-components                                | 185   |

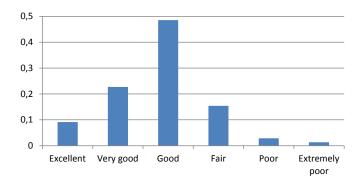

|       | V.2.2.4.      | Determination of statistical distributions for EMC levels                               | 186   |

| V.3.  | STAT          | ISTICAL ANALYSIS OF EMC DRIFT                                                           | . 187 |

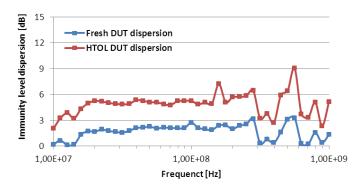

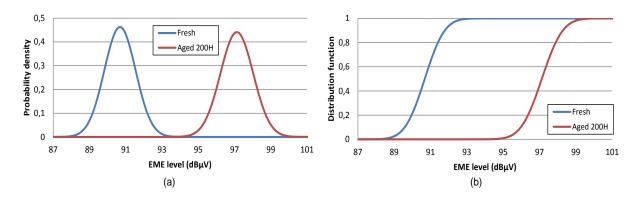

| V     | .3.1.         | Statistical characterization for EMC drift                                              | . 187 |

| V     | <i>'.3.2.</i> | EMC distribution after aging                                                            | . 189 |

| V.4.  | EMC           | RELIABILITY                                                                             | . 191 |

| V     | .4.1.         | Main statistical distributions for reliability study                                    | . 191 |

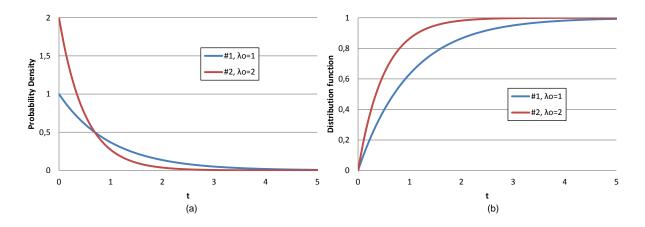

|                                                                                                                  | Exponential distribution                                                                                                                                                                                                                                                                                                                                                                  | . 192                                                                                                     |

|------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|

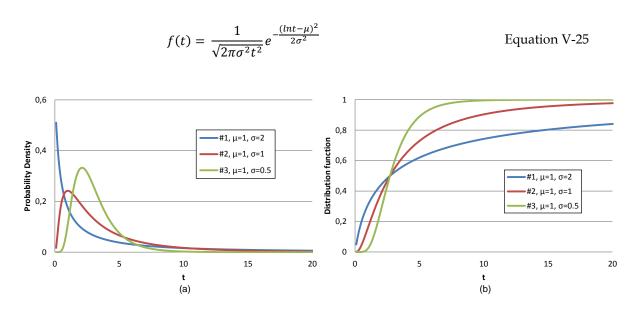

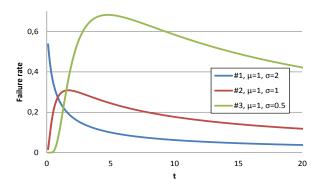

| V.4.1.2.                                                                                                         | Lognormal distribution                                                                                                                                                                                                                                                                                                                                                                    | . 193                                                                                                     |

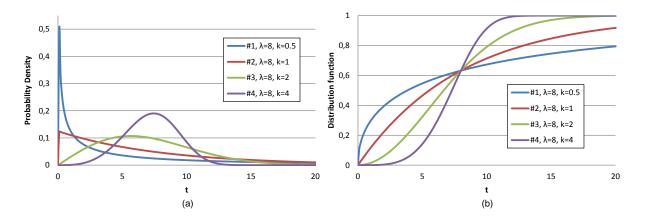

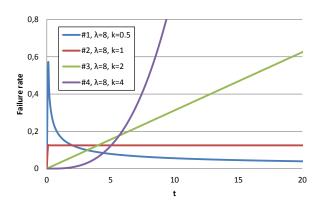

| V.4.1.3.                                                                                                         | Weibull distribution                                                                                                                                                                                                                                                                                                                                                                      | . 194                                                                                                     |

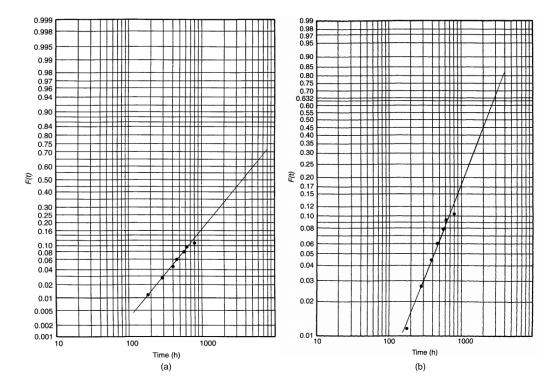

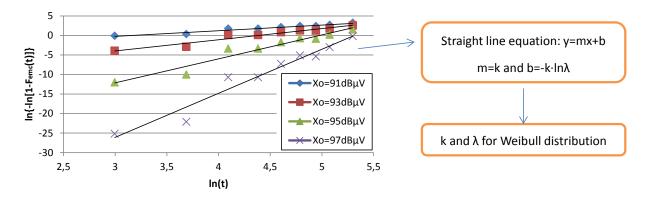

| V.4.1.4.                                                                                                         | Extraction of distribution                                                                                                                                                                                                                                                                                                                                                                | . 195                                                                                                     |

| V.4.1.5.                                                                                                         | Determination of distribution                                                                                                                                                                                                                                                                                                                                                             | . 196                                                                                                     |

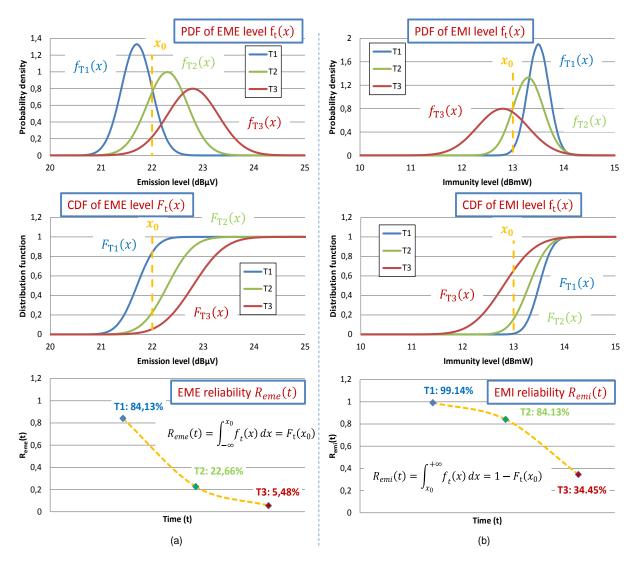

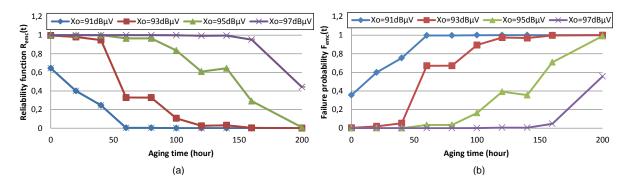

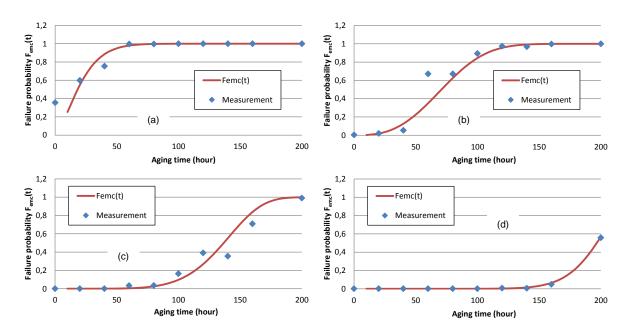

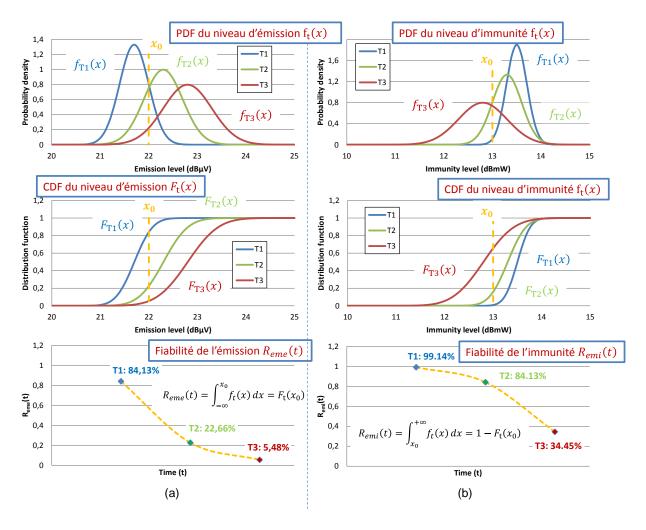

| V.4.2.                                                                                                           | EMC reliability distribution                                                                                                                                                                                                                                                                                                                                                              | 197                                                                                                       |

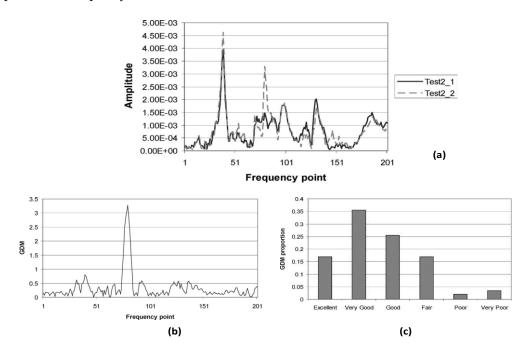

| V.5. CASI                                                                                                        | STUDY: STATISTICAL ANALYSIS OF THE EME RELIABILITY OF A BUCK DC-DC CONVERTER                                                                                                                                                                                                                                                                                                              | 201                                                                                                       |

| V.5.1.                                                                                                           | Problematic analysis                                                                                                                                                                                                                                                                                                                                                                      | 201                                                                                                       |

| V.5.2.                                                                                                           | Extraction of EME reliability based on measurement results                                                                                                                                                                                                                                                                                                                                | 202                                                                                                       |

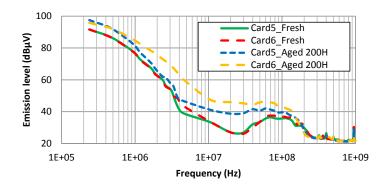

| V.5.2.1.                                                                                                         | Characterization of EME evolution                                                                                                                                                                                                                                                                                                                                                         | . 202                                                                                                     |

| V.5.2.2.                                                                                                         | Extraction of EME reliability                                                                                                                                                                                                                                                                                                                                                             | . 204                                                                                                     |

| V.5.3.                                                                                                           | Prediction of EME reliability                                                                                                                                                                                                                                                                                                                                                             | 205                                                                                                       |

| V.5.3.1.                                                                                                         | Description of method                                                                                                                                                                                                                                                                                                                                                                     | . 206                                                                                                     |

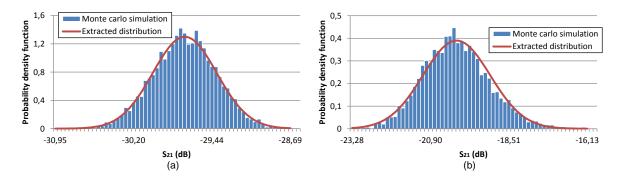

| V.5.3.2.                                                                                                         | Simulation of EME reliability                                                                                                                                                                                                                                                                                                                                                             | . 207                                                                                                     |

| V.5.4.                                                                                                           | Conclusion of case study                                                                                                                                                                                                                                                                                                                                                                  | 210                                                                                                       |

| V.6. Con                                                                                                         | CLUSION                                                                                                                                                                                                                                                                                                                                                                                   | 210                                                                                                       |

| V.7. Refe                                                                                                        | RENCE                                                                                                                                                                                                                                                                                                                                                                                     | 211                                                                                                       |

| CHAPTER VI.                                                                                                      | GENERAL CONCLUSION                                                                                                                                                                                                                                                                                                                                                                        | 214                                                                                                       |

| CHAPTER VII.                                                                                                     | RESUME EN FRANÇAIS                                                                                                                                                                                                                                                                                                                                                                        | 217                                                                                                       |

|                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                           |

| VII.1. INTR                                                                                                      | ODUCTION                                                                                                                                                                                                                                                                                                                                                                                  | 217                                                                                                       |

|                                                                                                                  | PATIBILITE ELECTROMAGNETIQUE A LONG TERME                                                                                                                                                                                                                                                                                                                                                 |                                                                                                           |

|                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                           | 219                                                                                                       |

| VII.2. COM                                                                                                       | PATIBILITE ELECTROMAGNETIQUE A LONG TERME                                                                                                                                                                                                                                                                                                                                                 | 219<br>219                                                                                                |

| VII.2. CON<br>VII.2.1.<br>VII.2.2.                                                                               | PATIBILITE ELECTROMAGNETIQUE A LONG TERME                                                                                                                                                                                                                                                                                                                                                 | 219<br>219<br>220                                                                                         |

| VII.2. COM<br><i>VII.2.1.</i><br><i>VII.2.2.</i><br>VII.3. Mon                                                   | PATIBILITE ELECTROMAGNETIQUE A LONG TERME                                                                                                                                                                                                                                                                                                                                                 | 219<br>219<br>220                                                                                         |

| VII.2. COM<br><i>VII.2.1.</i><br><i>VII.2.2.</i><br>VII.3. Mod                                                   | PATIBILITE ELECTROMAGNETIQUE A LONG TERME  Contexte de la robustesse électromagnétique  Prédiction de CEM évolution induite par le vieillissement  DELISATION DE LA DEGRADATION DES COMPOSANTS.                                                                                                                                                                                           | 219<br>219<br>220<br>223<br>224                                                                           |

| VII.2. CON<br><i>VII.2.1.</i><br><i>VII.2.2.</i><br>VII.3. MOI<br>VII.4. CAR                                     | PATIBILITE ELECTROMAGNETIQUE A LONG TERME                                                                                                                                                                                                                                                                                                                                                 | <ul><li>219</li><li>219</li><li>220</li><li>223</li><li>224</li><li>224</li></ul>                         |

| VII.2. COM<br>VII.2.1.<br>VII.2.2.<br>VII.3. MOI<br>VII.4. CAR.<br>VII.4.1.<br>VII.4.2.                          | PATIBILITE ELECTROMAGNETIQUE A LONG TERME  Contexte de la robustesse électromagnétique  Prédiction de CEM évolution induite par le vieillissement  DELISATION DE LA DEGRADATION DES COMPOSANTS.  ACTERISATION ET MODELISATION DE LA CEM A LONG TERME  Caractérisation de la CEM à long terme                                                                                              | <ul><li>219</li><li>219</li><li>220</li><li>223</li><li>224</li><li>224</li><li>225</li></ul>             |

| VII.2. CON  VII.2.1.  VII.2.2.  VII.3. MOI  VII.4. CAR.  VII.4.1.  VII.4.2.  VII.5. ANA                          | PATIBILITE ELECTROMAGNETIQUE A LONG TERME                                                                                                                                                                                                                                                                                                                                                 | <ul><li>219</li><li>219</li><li>220</li><li>223</li><li>224</li><li>224</li><li>225</li><li>228</li></ul> |

| VII.2. CON  VII.2.1.  VII.2.2.  VII.3. MOI  VII.4. CAR.  VII.4.1.  VII.4.2.  VII.5. ANA  VII.6. CON              | PATIBILITE ELECTROMAGNETIQUE A LONG TERME                                                                                                                                                                                                                                                                                                                                                 | 219<br>220<br>223<br>224<br>224<br>225<br>228<br>231                                                      |

| VII.2. CON  VII.2.1.  VII.2.2.  VII.3. MOI  VII.4. CAR.  VII.4.1.  VII.4.2.  VII.5. ANA  VII.6. CON  VII.7. REFE | PATIBILITE ELECTROMAGNETIQUE A LONG TERME  Contexte de la robustesse électromagnétique  Prédiction de CEM évolution induite par le vieillissement  DELISATION DE LA DEGRADATION DES COMPOSANTS.  ACTERISATION ET MODELISATION DE LA CEM A LONG TERME  Caractérisation de la CEM à long terme  Modélisation de la CEM à long terme  LYSE STATISTIQUE POUR LA PREDICTION DE LA REM  CLUSION | 219<br>220<br>223<br>224<br>224<br>225<br>228<br>231<br>232                                               |

# List of figures

| Figure I-1   | A view inside the double-deck A380's cockpit [AIRBUS]                                             | 2    |

|--------------|---------------------------------------------------------------------------------------------------|------|

| Figure II-1  | Notification about the use of electronic devices in United Airlines Boeing 747-400 Passenger Safe | ety  |

| Instruc      | tion Card [AERO04]                                                                                | 6    |

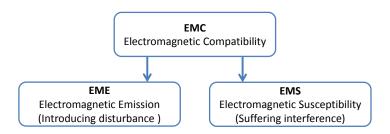

| Figure II-2  | Two parts of EMC definition [REDO10]                                                              | 7    |

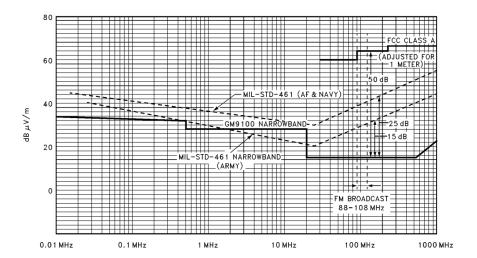

| Figure II-3  | Comparison of radiated emission specifications of commercial application (FCC), Military (MIL-    | -    |

| STD-46       | 51) and Automotive (GM9100) [BAYN96]                                                              | . 10 |

| Figure II-4  | CE mark (a) for European Economic Area and FCC Declaration of Conformity label (b) for US         | . 10 |

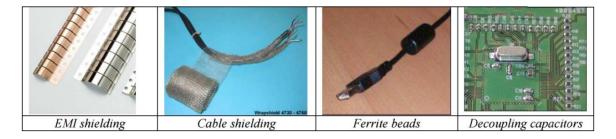

| Figure II-5  | Different techniques used at system, cable and PCB level to overcome EMC problems [SICA11].       | . 11 |

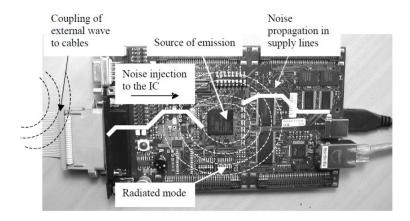

| Figure II-6  | Conducted, radiated emission and susceptibility of an integrated circuit at PCB level [SICA11]    | . 12 |

| Figure II-7  | Teardown analysis of an IPhone 6 Plus [DEMP14]                                                    | . 13 |

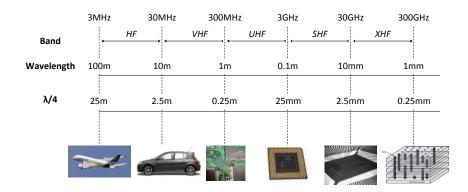

| Figure II-8  | Frequency bands of RF disturbance and the corresponding wavelength                                | . 14 |

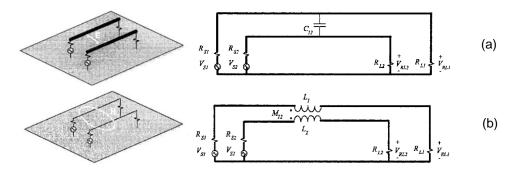

| Figure II-9  | Electric field coupling (a) and Magnetic field coupling (b) between two signal rails [BEND06]     | . 14 |

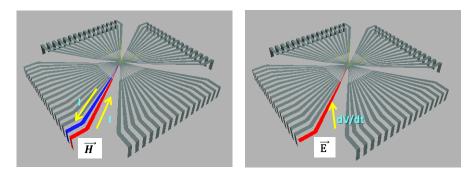

| Figure II-10 | Mechanisms of the magnetic (right) and electric (left) near field coupling [BOYE05]               | . 14 |

| Figure II-11 | Two circuits sharing a common current return path [BEND06]                                        | . 15 |

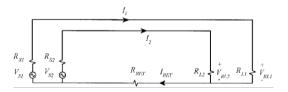

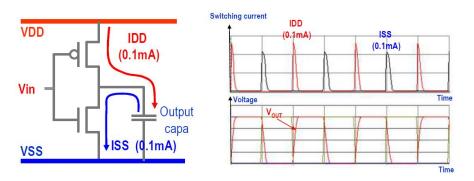

| Figure II-12 | Basic mechanisms of CMOS circuit current - inverter example [SICA11]                              | . 15 |

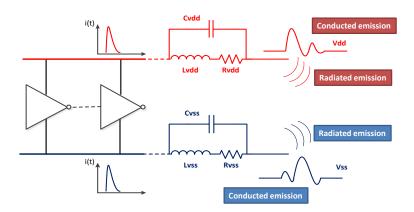

| Figure II-13 | IC parasitic emission due to switching activity and parasitic power supply interconnections       |      |

| [SICA1       | 1] 16                                                                                             |      |

| Figure II-14 | Parasitic radio-frequency sources which may disturb integrated circuits                           | . 17 |

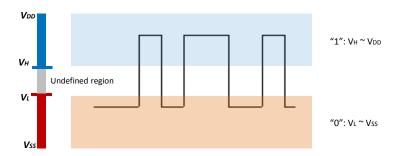

| Figure II-15 | Definition of logic state of digital circuits                                                     | . 17 |

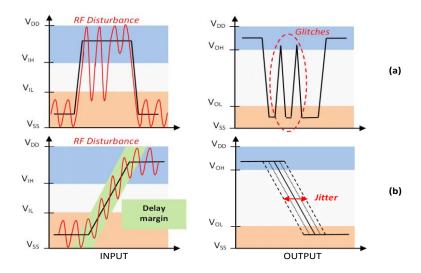

| Figure II-16 | Failures of an inverter induced by RF disturbance [LI11]                                          | . 18 |

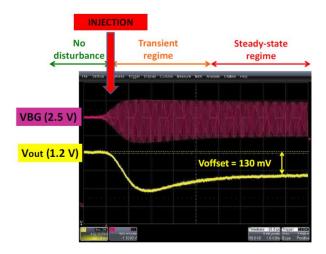

| Figure II-17 | DC offset induced by the EMI injected in the power supply of a bandgap voltage reference          | . 19 |

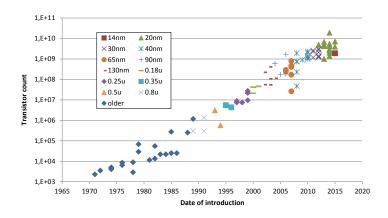

| Figure II-18 | Microprocessor transistor counts & Moore's law                                                    | . 20 |

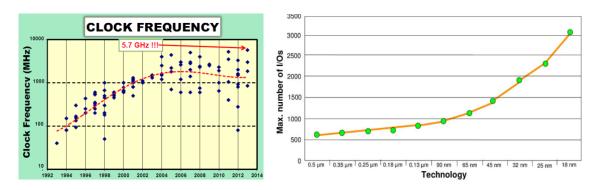

| Figure II-19 | (left) Trends towards a saturation of the CPU clock frequencies [ISSCC]; (right) Evolution of     |      |

| maxim        | um number of I/Os [ITRS]                                                                          | . 21 |

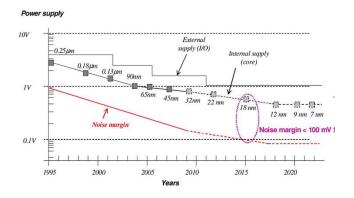

| Figure II-20 | Reduction of internal supply voltage leads to a reduced noise margin [RAMD09]                     |      |

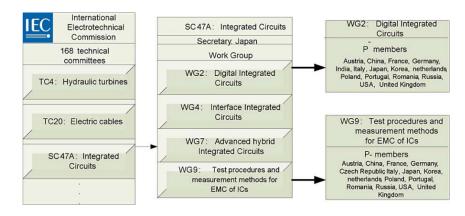

| Figure II-21 | Structure of IEC working groups for EMC of ICs [RAMD09]                                           | . 22 |

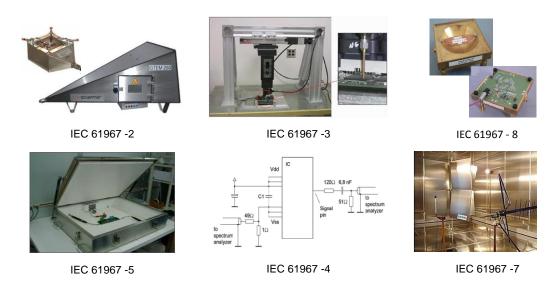

| Figure II-22 | IC electromagnetic emission measurement methods                                                   | . 23 |

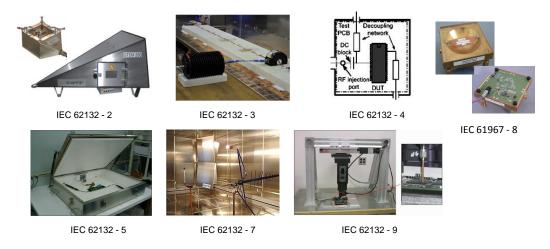

| Figure II-23 | IC electromagnetic immunity measurement methods                                                   | . 24 |

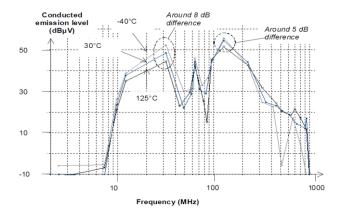

| Figure II-24 | Conducted emission measured on Port S (port inactive) of a 16-bits microcontroller for varying    |      |

| temper       | rature (-40°C, 30°C, 125°C) [BEND07]                                                              | . 26 |

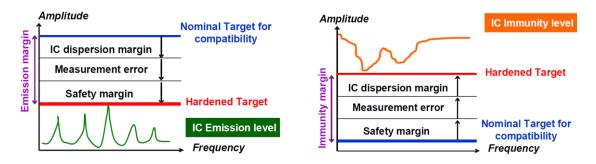

| Figure II-25 | Verification of EMC compliance with additional margins [BEND09]                                   | . 27 |

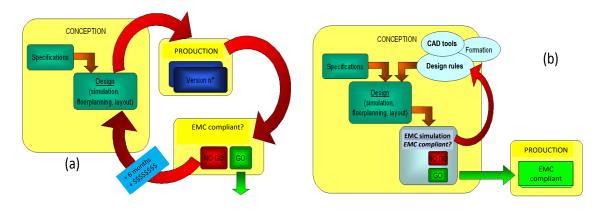

| Figure II-26 | IC design flow evolution [VRIG05]                                                                 | . 27 |

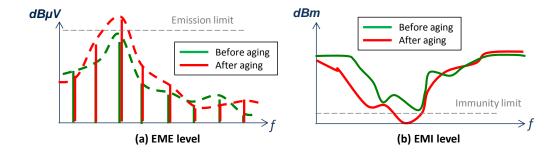

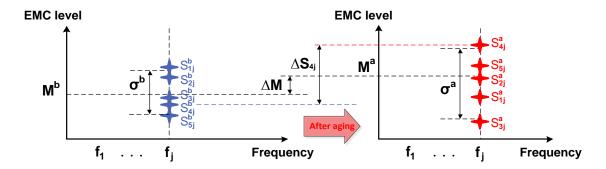

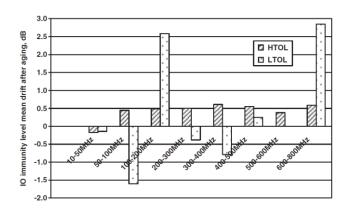

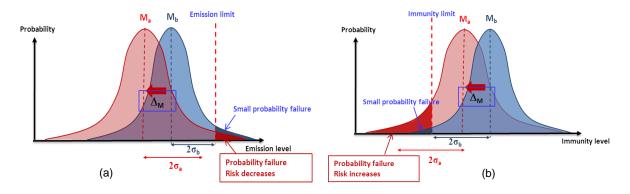

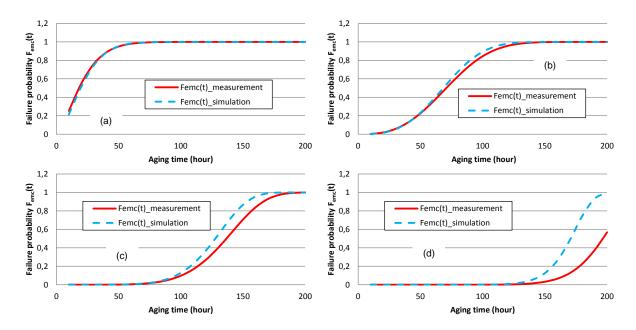

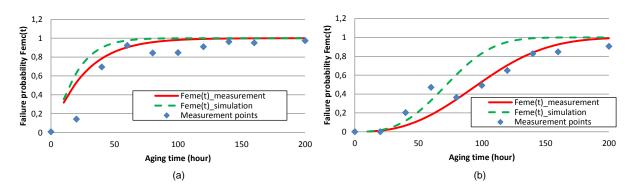

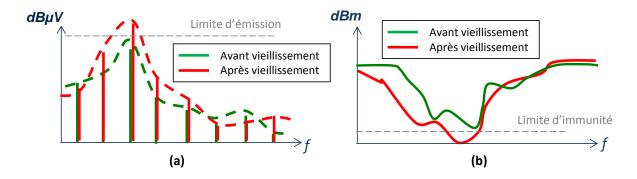

| Figure II-27 | Possible evolution of FMC levels after aging: (a) FME level. (b) FMI level                        | 32   |

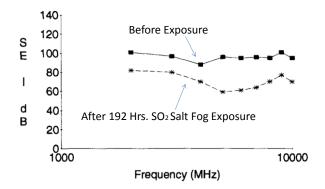

| Figure II-28  | Shielding effectiveness versus frequency for NiGr Gasket-6061-T6 aluminum flange [LESS93]                             | 32    |

|---------------|-----------------------------------------------------------------------------------------------------------------------|-------|

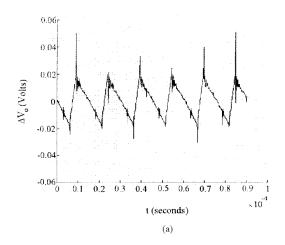

| Figure II-29  | Influence on output voltage of a SMPS with different output filtering capacitor: (a) Sound                            |       |

| capacito      | r, (b) aged capacitor [LAHY98]                                                                                        | 33    |

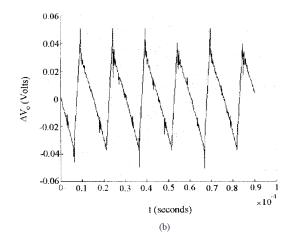

| Figure II-30  | Change in conducted emission of the output buffer after 7-V electrical stress over 120 min (left)                     |       |

| and a dig     | gital core before and after 3- and 4-V electrical stress (right) [BOYE14]                                             | 34    |

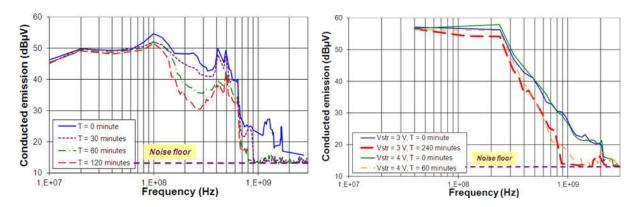

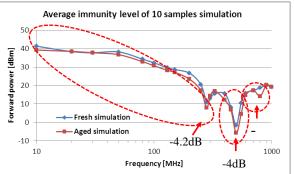

| Figure II-31  | PLL EM immunity measurement (left) and simulation (right) before and after ageing [LI11]                              | 35    |

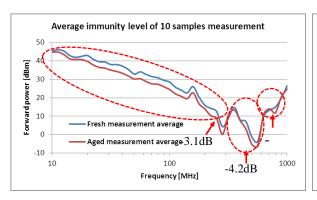

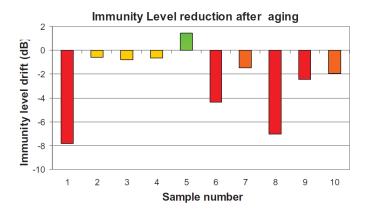

| Figure II-32  | Immunity Evolution to conducted injection of PLL after aging of 10 samples [BOYE11]                                   | 35    |

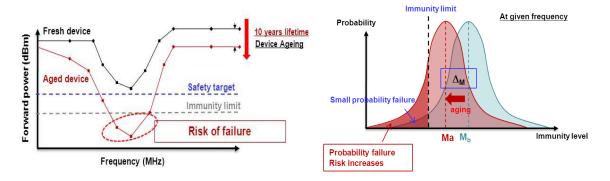

| Figure II-33  | Immunity level decrease with device aging (left) worst case, (right) statistical view [LI10]                          | 36    |

| Figure II-34  | General EMR modeling flow                                                                                             | 36    |

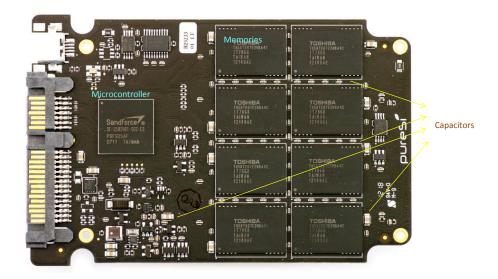

| Figure III-1  | Example of the PCB card of a SSD disk (pureSilicon Kage K1 Enterprise SSD) [LIND12]                                   | 42    |

| Figure III-2  | Bathtub curve                                                                                                         | 45    |

| Figure III-3  | Acceleration factor AF <sub>T</sub> vs. operating temperature                                                         | 47    |

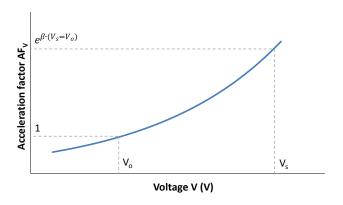

| Figure III-4  | Acceleration factor AFV vs. operating voltage                                                                         | 48    |

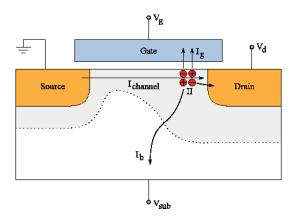

| Figure III-5  | DAHC injection mechanism for an N-channel MOSFET [ENTN07]                                                             | 52    |

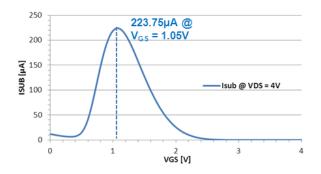

| Figure III-6  | Choice of $V_{GS}$ to obtain maximum $I_{SUB}$ of a NMOS in technology 90 nm of thin oxide [LI11]                     | 52    |

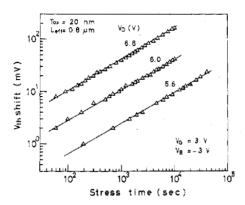

| Figure III-7  | Device degradations in $V_{TH}$ as a function of stress time and drain voltage [TAKE83b]                              | 53    |

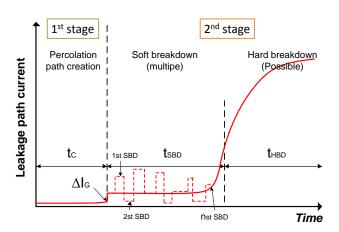

| Figure III-8  | Two stages of breakdown in thin oxide transistor [KAZC04]                                                             | 54    |

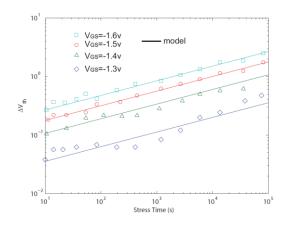

| Figure III-9  | V <sub>TH</sub> shift vs. NBTI stress time [WANG11]                                                                   | 55    |

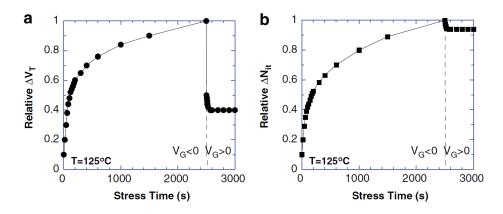

| Figure III-10 | Saturation and recovery phenomenon of NBTI for two parameters: threshold voltage (a) and                              |       |

| interface     | e traps charge (b)                                                                                                    | 56    |

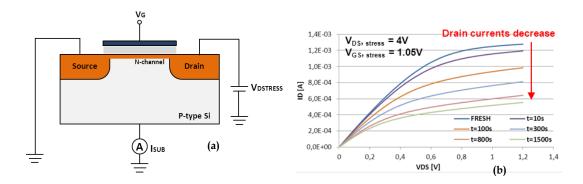

| Figure III-11 | NMOS HCI test method: (a) Experimental stress condition for NMOS HCI test, (b) IDS vs. VI                             | )S    |

| curve ev      | rolution due to HCI degradation [LI11]                                                                                | 57    |

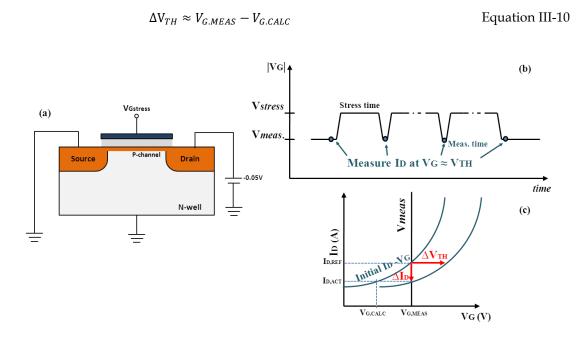

| Figure III-12 | PMOS NBTI fast $\Delta$ ID method: (a) Experimental stress condition for PMOS NBTI test, (b) Stre                     | ss    |

| and mea       | is urement gate voltage during the fast $\Delta ID$ method, (c) IDS vs. VG curve for $\Delta V_{TH}$ calculation [LI1 | 1]    |

|               | 58                                                                                                                    |       |

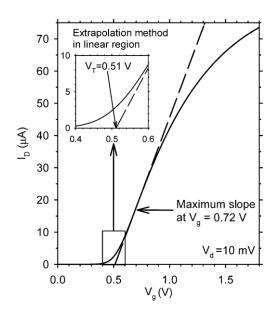

| Figure III-13 | ELR method implemented on the ID-Vg characteristics of the test bulk device [ORTI02]                                  | 59    |

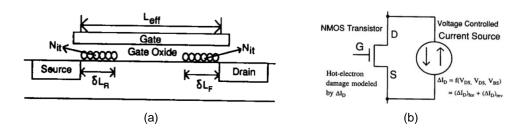

| Figure III-14 | Bidirectional mode interface trap generation near both drain and source (a) and BERT n-                               |       |

| MOSFET        | Γ HCI drain current ΔId circuit model (b) [QUAD91]                                                                    | 60    |

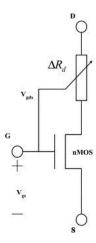

| Figure III-15 | HISREM HCI circuit model [BERN06]                                                                                     | 61    |

| Figure III-16 | Power law leakage current model (a) and RF failure circuit model (b) [BERN06] [YANG03]                                | 61    |

| Figure III-17 | NBTI circuit model [BERN06]                                                                                           | 62    |

| Figure III-18 | SPICE level 3 transistor model                                                                                        | 63    |

| Figure III-19 | Comparison of measurement and simulation with SPICE level 3: Fresh device (left) and device                           | :e    |

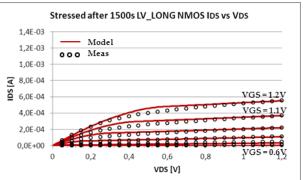

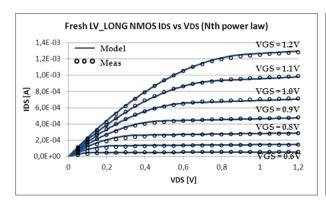

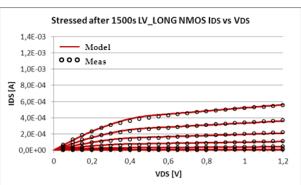

| stressed      | after 1500s (right) [LI11]                                                                                            | 64    |

| Figure III-20 | Comparison of measurement and simulation with Nth power law: Fresh device (left) and dev                              | vice. |

| stressed      | after 1500s (right) [LI11]                                                                                            | 65    |

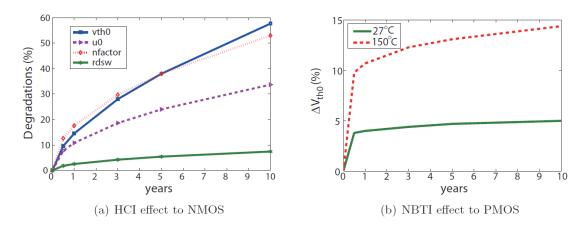

| Figure III-21 | HCI and NBTI induced physical parameters degradation in NMOS and PMOS transistor                                      |       |

| [CAI13]       | 66                                                                                                                    |       |

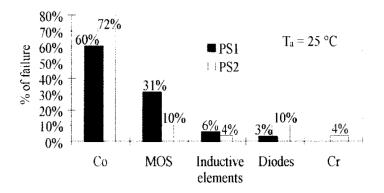

| Figure III-22 | Distribution of failure according to component type in a power application [LAHY98]                                   | 67    |

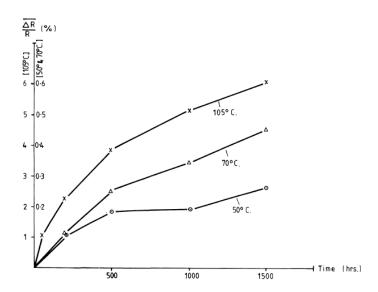

| Figure III-23 | Variation of resistance value of thick film resistors at different storage temperature [PRAN84]                       | ] 68  |

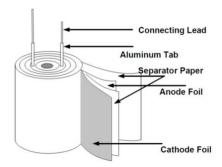

| Figure III-24 | Physical model of aluminum electrolytic capacitor [KULK12]                                                            | 69    |

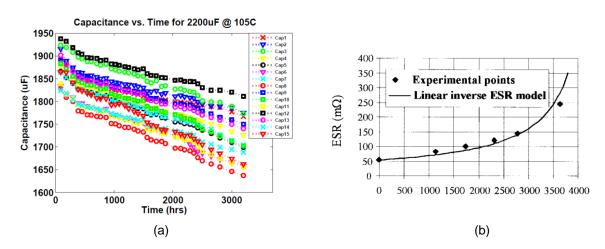

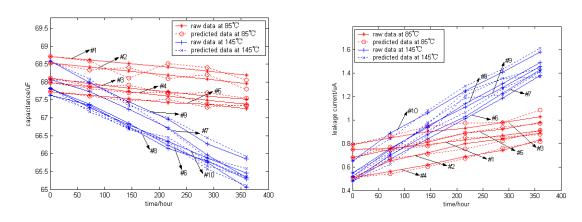

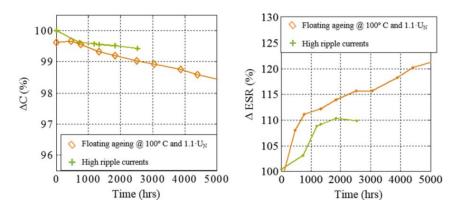

| Figure III-25    | Parameters' evolution of aluminum electronic capacitors with time: (a) Capacitance evolution       | n     |

|------------------|----------------------------------------------------------------------------------------------------|-------|

| [KULK12]         | ; (b) ESR evolution [LAHY98]                                                                       | 69    |

| Figure III-26    | Parameters evolution of tantalum capacitors with time: Capacitance (left) and Leakage curre        | nt    |

| (right) [HI      | UAN11]                                                                                             | 71    |

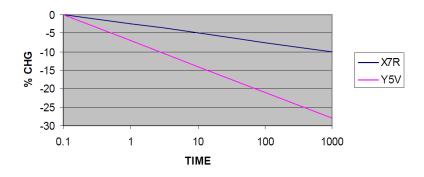

| Figure III-27    | Capacitance evolution of Class 2 ceramic capacitors [JOHA12]                                       | 71    |

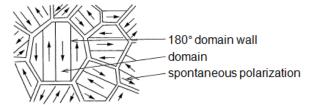

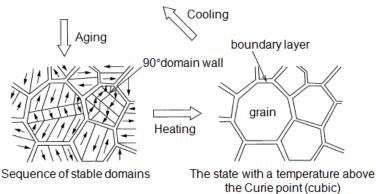

| Figure III-28    | Aging mechanism and reversing aging mechanism for the ceramic capacitor [MURA]                     | 72    |

| Figure III-29    | Comparison of ESR and C evolution for a metallized film capacitor under two different agin         | g     |

| conditions       | s [MAKD15]                                                                                         | 73    |

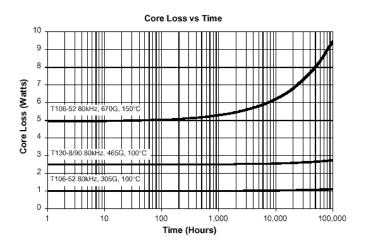

| Figure III-30    | Core loss evolution under different operating conditions (temperature, peak AC flux density        | 7)    |

| vs. aging t      | time [MATE]                                                                                        | 74    |

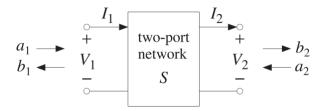

| Figure III-31    | Two-port network [ORFA08]                                                                          | 75    |

| Figure III-32    | Incertitude level of three impedance measurement configurations [LAFO10]                           | 76    |

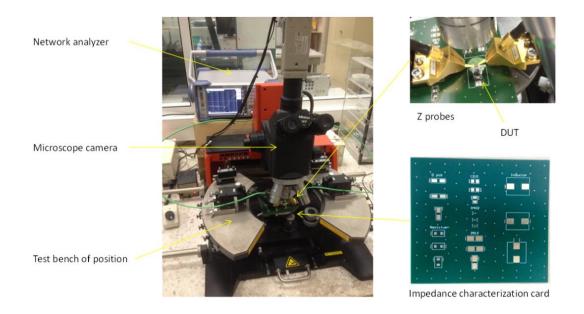

| Figure III-33 Im | npedance measurement test bench by VNA                                                             | 77    |

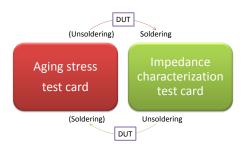

| Figure III-34    | Impedance characterization during aging process for passive devices                                | 77    |

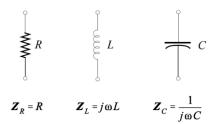

| Figure III-35    | Basic impedance model of passive devices                                                           | 78    |

| Figure III-36    | Equivalent circuit model for resistor                                                              | 78    |

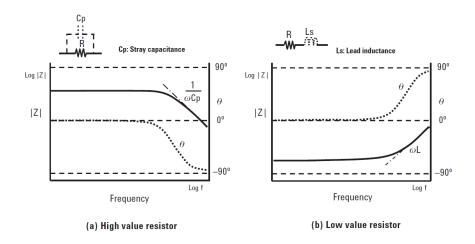

| Figure III-37    | Resistor frequency response and corresponding models [AGIL13]                                      | 79    |

| Figure III-38    | Impedance measurement (dotted line) and modeling (solid line) of thin film chip resistors of       | :     |

| different v      | value [VISH06]                                                                                     | 79    |

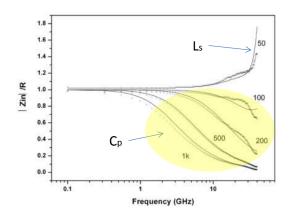

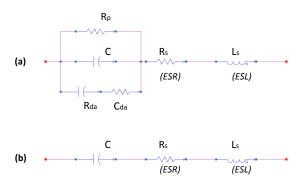

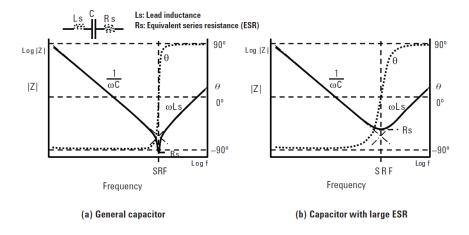

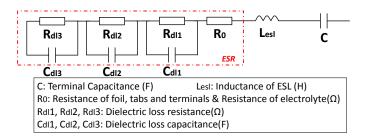

| Figure III-39    | Equivalent circuit models for capacitor: (a) complete model, (b) simplified model                  | 80    |

| Figure III-40    | Capacitor frequency response and corresponding models [AGIL13]                                     | 80    |

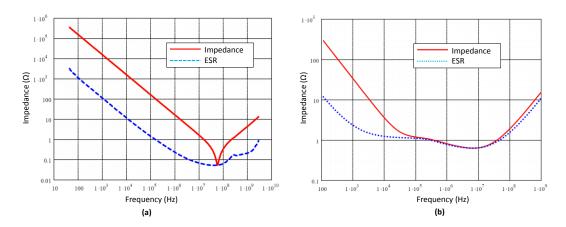

| Figure III-41    | Impedance and ESR of capacitors: (a) TDK 0603 X7R 10 nF, (b) KEMET tantalum capacitor 4.           | .7    |

| μF [LAFO         | 010]                                                                                               | 81    |

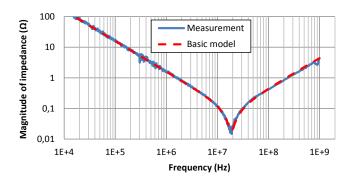

| Figure III-42    | Basic equivalent circuit model for a X7R ceramic capacitor 100 nF                                  | 81    |

| Figure III-43    | Impedance measurement (solid line) and modeling (dotted line) of a X7R ceramic capacitor in        | 100   |

| nF               | 82                                                                                                 |       |

| Figure III-44    | Equivalent circuit models for capacitor with a resistor-capacitor pair [GASP97]                    | 82    |

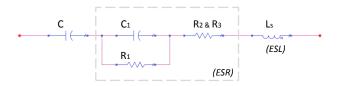

| Figure III-45    | Three equivalent circuit models for an aluminum electrolytic capacitor 100 $\mu F$ : (a) Basic mod | el,   |

| (b) Model        | with one resistor-capacitor pair, (c) Model with three resistor-capacitor pairs                    | 83    |

| Figure III-46    | Impedance measurement and three modeling results of an aluminum electrolytic capacitor 1           | 00    |

| μF               | 83                                                                                                 |       |

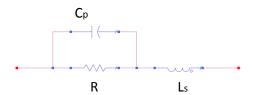

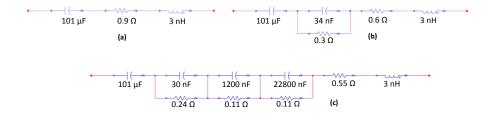

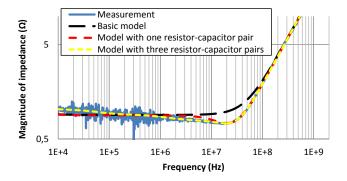

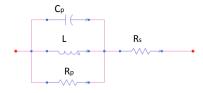

| Figure III-47    | Basic equivalent circuit models for inductor                                                       | 83    |

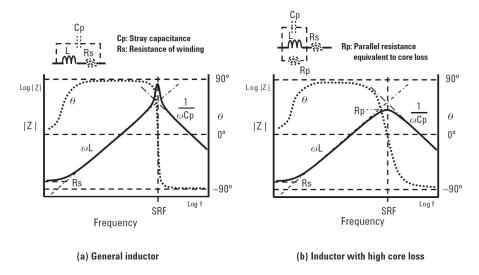

| Figure III-48    | Inductor frequency response and corresponding models [AGIL13]                                      | 84    |

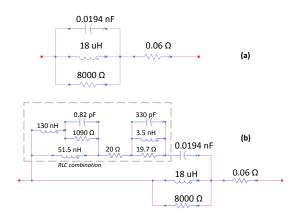

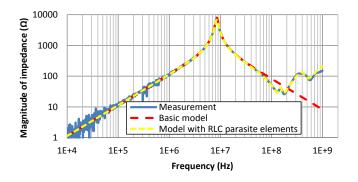

| Figure III-49    | Two equivalent circuit models for an powder iron inductor 22 $\mu F$ : (a) Basic model, (b) Model  | 1     |

| with RLC         | parasitic elements                                                                                 | 85    |

| Figure III-50    | Impedance measurement and two modeling results of an powder iron inductor 22 $\mu\text{F}$         | 85    |

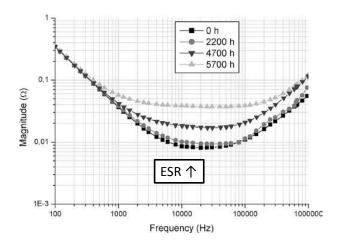

| Figure III-51    | Variation of impedance vs. aging time of an aluminum electrolytic capacitor [PERI04]               | 86    |

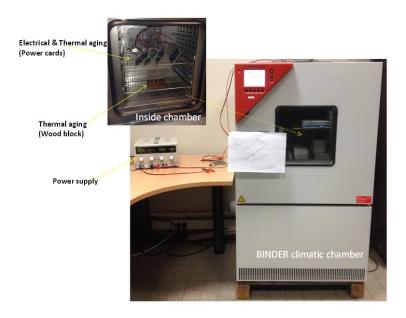

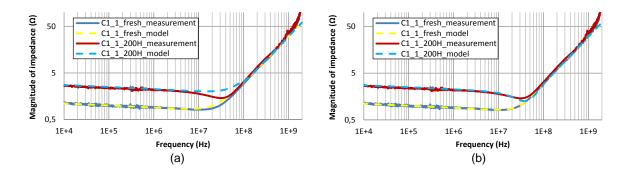

| Figure III-52    | Aging stress configuration of passive devices                                                      | 88    |

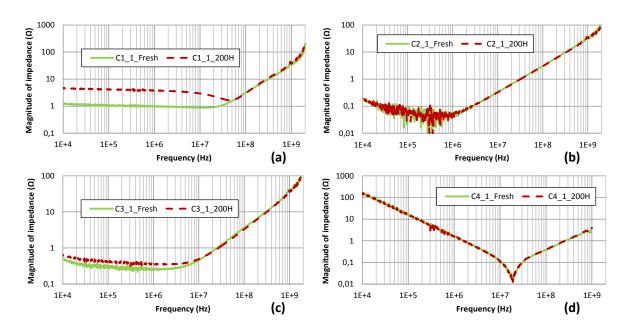

| Figure III-53    | Impedance evolution of capacitors before and after thermal aging: (a) C1: Aluminum electro         | lytic |

| capacitor        | 100 μF; (b) C2: Tantalum capacitor 100 μF; (c) C3: Aluminum electrolytic capacitor 47 μF; (d) C4   | 4:    |

| X7R ceran        | nic canacitor 100 nF                                                                               | 89    |

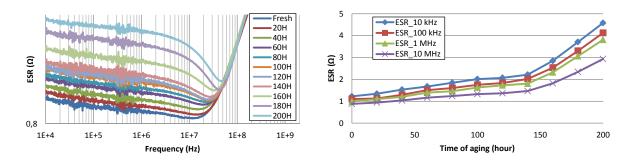

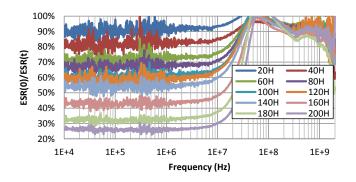

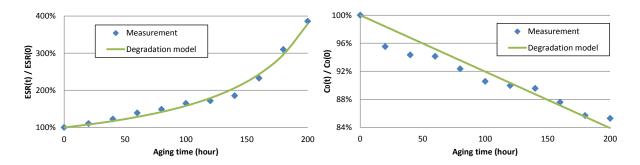

| Figure III-54   | ESR evolution of C1_1 aluminum electrolytic capacitor 100 $\mu F$ with time: ESR of each phase                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |       |

|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| during a        | ging (left); Evolution at different frequencies (right)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 90    |

| Figure III-55   | ESR(0)/ESR(t) with aging time t of C1_1 aluminum electrolytic capacitor 100 $\mu F$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 90    |

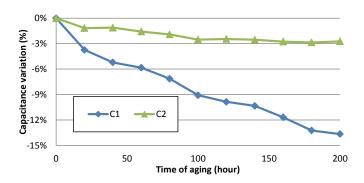

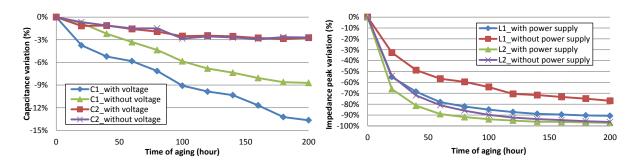

| Figure III-56   | Mean variation of capacitance with aging time of aluminum electrolytic capacitor C1 and                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |       |

| tantalum        | n capacitor C2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 91    |

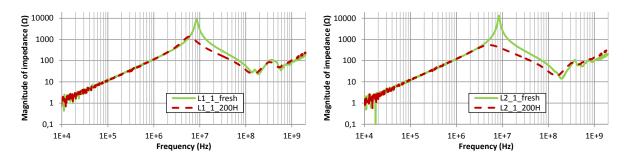

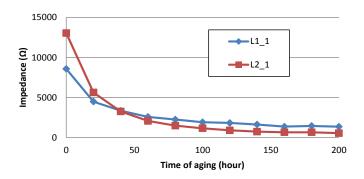

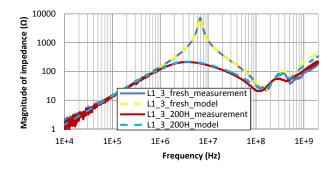

| Figure III-57   | Impedance evolution of inductors before and after thermal aging: L1, manufacturer Vishay                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |       |

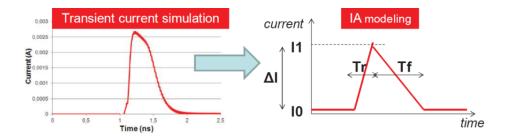

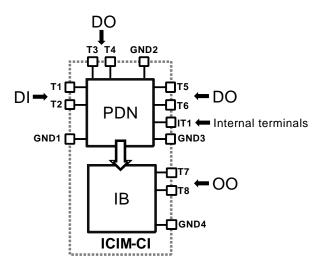

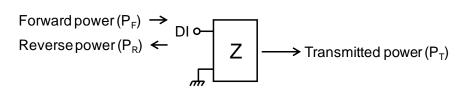

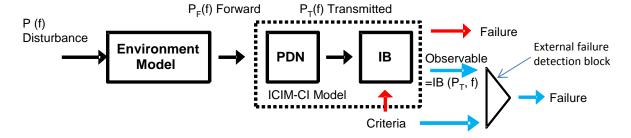

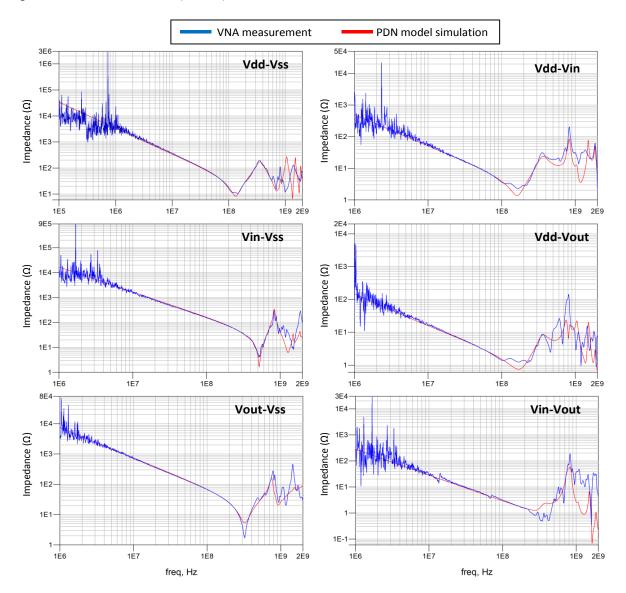

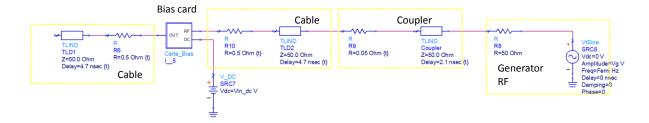

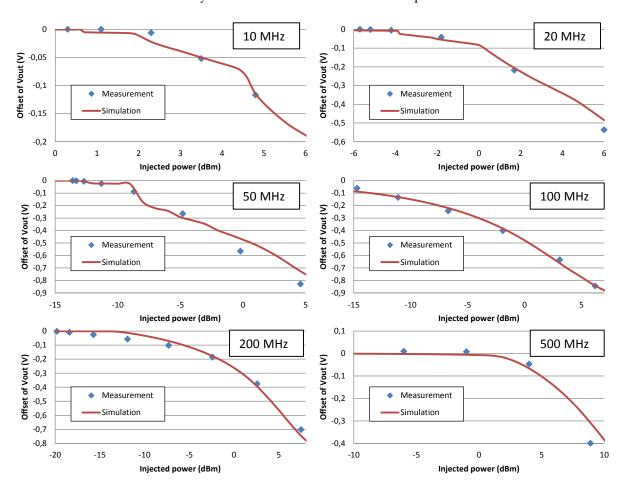

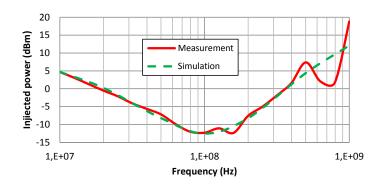

| (left); L2,     | , manufacturer Coiltronics (right)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 91    |