# Conception d'un micro-réseau intégré NOC tolérant les fautes multiples statiques et dynamiques

Yi Gang

#### ▶ To cite this version:

Yi Gang. Conception d'un micro-réseau intégré NOC tolérant les fautes multiples statiques et dynamiques. Micro et nanotechnologies/Microélectronique. Université Grenoble Alpes, 2015. Français. NNT: 2015GREAT103. tel-01259475

# HAL Id: tel-01259475 https://theses.hal.science/tel-01259475

Submitted on 20 Jan 2016

HAL is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

## UNIVERSITÉ GRENOBLE ALPES

## **THÈSE**

Pour obtenir le grade de

## DOCTEUR DE L'UNIVERSITÉ GRENOBLE ALPES

Spécialité : « Micro et Nano Électronique»

Arrêté ministériel : 7 août 2006

Présentée par

#### Yi GANG

Thèse dirigée par **Mme. Lorena ANGHEL** et codirigée par **M. Mounir BENABDENBI**

préparée au sein du Laboratoire TIMA dans l'École Doctorale d'Électronique, Électrotechnique, Automatique, et Traitement du Signal (EEATS)

# Conception d'un micro-réseau intégré NOC tolérant les fautes multiples statiques et dynamiques

Thèse soutenue publiquement le **05 novembre 2015**, devant le jury composé de :

#### M. Habib MEHREZ

Professeur, Université Paris 6 (Président & Rapporteur)

#### M. Ian O'CONNOR

Professeur, Ecole Central de Lyon (Rapporteur)

#### Mme. Lorena ANGHEL

Professeur, Institut polytechnique de Grenoble (Directrice de thèse)

#### M. Mounir BENABDENBI

Maître de Conférences, Institut polytechnique de Grenoble (Co-encadrant de thèse)

#### TITRE

Conception d'un micro-réseau intégré NOC tolérant les fautes multiples statiques et dynamiques

#### RESUME

Les progrès dans les technologies à base de semi-conducteurs et la demande croissante de puissance de calcul poussent vers une intégration dans une même puce de plus en plus de processeurs intégrés. Par conséquent les réseaux sur puce remplacent progressivement les bus de communication, ceux-ci offrant plus de débit et permettant une mise à l'échelle simplifiée.

Parallèlement, la réduction de la finesse de gravure entraine une augmentation de la sensibilité des circuits au processus de fabrication et à son environnement d'utilisation. Les défauts de fabrication et le taux de défaillances pendant la durée de vie du circuit augmentent lorsque l'on passe d'une technologie à une autre. Intégrer des techniques de tolérance aux fautes dans un circuit devient indispensable, en particulier pour les circuits évoluant dans un environnement très sensible (aérospatial, automobile, santé, ...).

Nous présentons dans ce travail de thèse, des techniques permettant d'améliorer la tolérance aux fautes des micro-réseaux intégrés dans des circuits évoluant dans un environnement difficile. Le NoC doit ainsi être capable de s'affranchir de la présence de nombreuses fautes. Les travaux publiés jusqu'ici proposaient des solutions pour un seul type de faute.

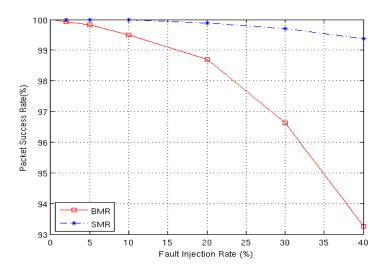

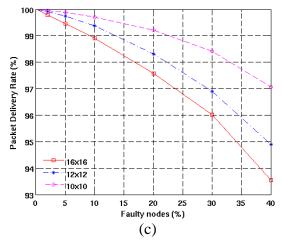

En considérant les contraintes de surface et de consommation du domaine de l'embarqué, nous avons proposé un algorithme de routage adaptatif tolérant à la fois les fautes intermittentes, transitoires et permanentes. En combinant et adaptant des techniques existantes de retransmission de flits, de fragmentation et de regroupement de paquet, notre approche permet de s'affranchir de nombreuses fautes statiques et dynamiques. Les très nombreuses simulations réalisées ont permis de montrer entre autre que, l'algorithme proposé permet d'atteindre un taux de livraison de paquets de 97,68% pour un NoC 16x16 en maille 2D en présence de 384 liens défectueux simultanés, et 93,40% lorsque 103 routeurs sont défaillants. Nous avons étendu l'algorithme aux topologies de type tore avec des résultats bien meilleurs.

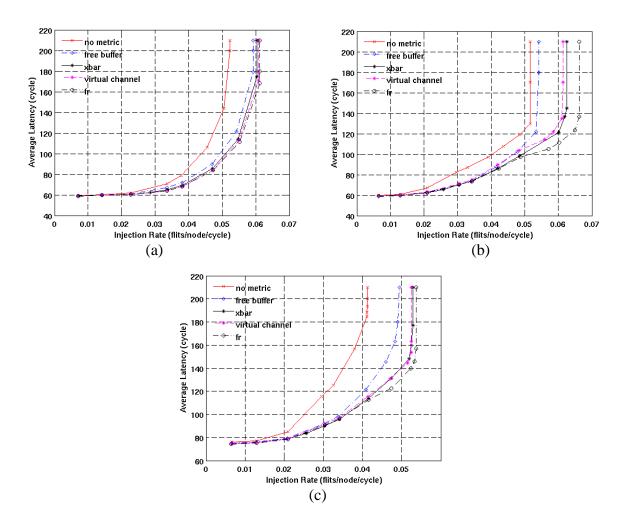

Une autre originalité de cette thèse est que nous avons inclus dans cet algorithme une fonction de gestion de la congestion. Pour cela nous avons défini une nouvelle métrique de mesure de la congestion (Flit Remain) plus pertinente que les métriques utilisées et publiées jusqu'ici. Les expériences ont montré que l'utilisation de cette métrique permet de réduire la latence (au niveau du pic de saturation) de 2,5 % à 16,1 %, selon le type de trafic généré, par rapport à la plus efficace des métriques existante.

La combinaison du routage adaptatif tolérant les fautes statiques et dynamiques et la gestion de la congestion offrent une solution qui permet d'avoir un NoC et par extension un circuit beaucoup plus résilient.

#### **MOTS CLEFS**

MPSoCs, NoC, routage adaptif, tolérance aux fautes, injection des fautes

#### TITRE

Design of a Network on chip (NoC) that tolerates multiple static and dynamic faults

#### **ABSTRACT**

The quest for higher-performance and low-power consumption has driven the microelectronics' industry race towards aggressive technology scaling and multicore chip designs. In this many-core era, the Network-on-chip (NoCs) becomes the most promising solution for on-chip communication because of its performance scaling with the number of IPs integrated in the chip.

Fault tolerance becomes mandatory as the CMOS technology continues shrinking down. The yield and the reliability are more and more affected by factors such as manufacturing defects, process variations, environment variations, cosmic radiations, and so on. As a result, the designs should be able to provide full functionality (e.g. critical systems), or at least allow degraded mode in a context of high failure rates. To accomplish this, the systems should be able to adapt to manufacturing and runtime failures.

In this thesis, some techniques are proposed to improve the fault tolerance ability of NoC based circuits working in harsh environments. As previous works allow the handling of one type of fault at a time, we propose here a solution where different kinds of faults can be tolerated concurrently.

Considering constraints such as area and power consumption, a fault tolerant adaptive routing algorithm was proposed, which can cope with transient, intermittent and permanent faults. Combined with some existing techniques, like flit retransmission and packet fragmentation, this approach allows tolerating numerous static and dynamic faults. Simulations results show that the proposed solution allows a high packet delivery success rate: for a 16x16 2D Mesh NoC, 97.68% in the presence of 384 simultaneous link faults, and 93.40% with the presence of 103 simultaneous router faults. This success rate is even higher when this algorithm is extended to NoCs with Tore topology.

Another contribution of this thesis is the inclusion of a congestion management function in the proposed routing algorithm. For this purpose, we introduce a novel metric of congestion measurement named Flit Remain. The experimental results show that using this new congestion metric allows a reduction of the average latency of the Network on Chip from 2.5% to 16.1% when compared to the existing metrics.

The combination of static and dynamic fault tolerant and adaptive routing and the congestion management offers a solution, which allows designing a NoC highly resilient.

#### **KEYWORDS**

Network on Chip (NoC), MPSoCs, adaptive routing, fault tolerance, congestion

## Remerciements

Je tiens tout d'abord à remercier Mme Lorena Anghel, Professeur de Grenoble INP, pour avoir accepté d'être le directeur de cette thèse. Je tiens à lui exprimer ma reconnaissance pour sa disponibilité, ses conseils et sa gentillesse.

Je remercie Mr. Mounir Benabdenbi, Maître de Conférence de Grenoble INP durant ma thèse, pour m'avoir proposé cette thèse, dirigé et soutenu durant ces dernières années. Son encadrement, ses encouragements, sa confiance, ses conseils et ses critiques m'ont permis de progresser et mener à bien ce travail. Qu'il trouve ici l'expression de ma sincère reconnaissance.

Mes gratitudes s'adressent également à Mr Habib Mehrez, Professeur à l'Université Paris 6, pour l'honneur qu'il accepté d'être président et rapporteur de ma thèse. Merci à Mr. Ian O'Connor, Professeur de l'Ecole Central de Lyon qui a rapporté également cette thèse. Je les remercie profondément pour leurs remarques, leurs conseils et leurs critiques constructives.

Je tiens à remercier M. Michael Dimopolos pour ses suggestions et supports au cours de l'avancement de cette thèse. J'aimerais remercier Mr. Alexandre Chagoya pour son assistance au CIME.

Je remercie les Directeurs successifs du laboratoire TIMA pour m'avoir accueilli, Mme. Dominique Borrione, Professeur de l'Université Grenoble Alpes et Mr. Salvador Mir, directeur actuel de TIMA. Je voudrais remercier les chercheurs et personnel administratif et du Laboratoire TIMA pour m'avoir accueilli. Je pense à Anne-Laure, Laurence, Marie-Christine, Youness, Sophie, et le personnel du service informatique, Nicolas, Frederic et Ahmed pour leur disponibilité permanente et leur aide à l'égard de mon travail.

Merci à tous mes collègues des Laboratoires TIMA et avec qui j'ai eu le plaisir de travailler, très particulièrement Claudia Rusu, Hai Yu, Gilles Bizot, Diarga Fall, Hamayun Muhammad, Fabien Chaix, Vladimir Paska, Adrian Evans, Wassim Mansour, Saif Ur Rehman, Michael Dimopolous, Mihai Iordache et Amir Charif.

Enfin, je remercie ma famille et mes amis pour leur soutien et leurs encouragements. Finalement je réserve mon dernier merci, spécial et sincère à ma famille et mes parents pour leur soutien et leurs encouragements.

# Table des matières

| Résumé                                                                                      | i   |

|---------------------------------------------------------------------------------------------|-----|

| Table des matières                                                                          | iii |

| Liste des figures                                                                           | v   |

| Liste des abréviations                                                                      | vii |

| Introduction                                                                                | 1   |

| Chapitre 1 Contexte et Problématique                                                        | 5   |

| 1.1 Terminologie des réseaux sur puce                                                       | 6   |

| 1.2 Gestion de la congestion                                                                | 13  |

| 1.3 Gestion des fautes                                                                      | 14  |

| 1.3.1 Types de fautes                                                                       | 14  |

| 1.3.2 Modèles de fautes dans un NoC                                                         | 16  |

| 1.3.3 Tolérance aux fautes multi-niveaux                                                    | 17  |

| 1.4 Les contributions                                                                       | 17  |

| Chapitre 2 Etat de l'art                                                                    | 19  |

| 2.1 Congestion de réseau sur puce                                                           | 22  |

| 2.2 Gestion de fautes                                                                       | 29  |

| 2.2.1 Notion de tolérance aux fautes                                                        | 29  |

| 2.2.2 Techniques de tolérance aux fautes dans un NoC                                        | 32  |

| 2.3 Plateforme virtuelle d'expérimentation                                                  | 42  |

| 2.4 Conclusions                                                                             | 43  |

| Chapitre 3 Algorithmes de routage tolérant aux fautes avec prise en compte de la congestion | 45  |

| 3.1 Tolérance aux fautes                                                                    | 40  |

| 3.1.1 Hypothèse                                                                             | 46  |

| 3.1.2 Le recouvrement de paquet                                                             |     |

| 3.1.2 Routage pour la Maille 2D                                                             |     |

| 3.1.3 Routage pour le Tore 2D                                                               |     |

| 3.2 Cangestian de réseau sur nuce                                                           | 64  |

| 3.2.1 Nouvelle métrique de congestion – Flit Remain (FR)      | 64  |

|---------------------------------------------------------------|-----|

| 3.2.2 Etude de cas : comparaison de deux métriques FB et FR   | 65  |

| 3.2.3 Amélioration de la nouvelle métrique FR                 | 70  |

| 3.3 Microarchitecture du routeur proposé                      | 71  |

| 3.4 Conclusions                                               | 75  |

| Chapitre 4 Expérimentations et Résultats                      | 77  |

| 4.1 Plateforme d'expérimentation                              | 78  |

| 4.1.1 Simulateur utilisé :                                    | 78  |

| 4.1.2 Génération de trafics synthétisés                       | 81  |

| 4.1.3 Génération de fautes                                    | 82  |

| 4.2 Résultats expérimentaux                                   | 84  |

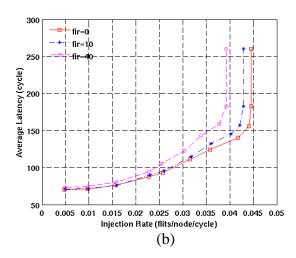

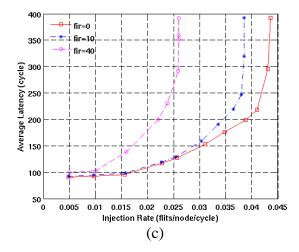

| 4.2.1 Comparaison des métriques de congestion                 | 85  |

| 4.2.2 Tolérance aux fautes : performance BPR et SPR           | 87  |

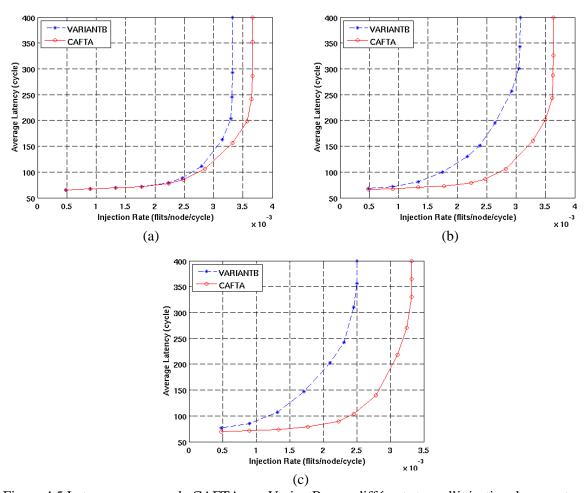

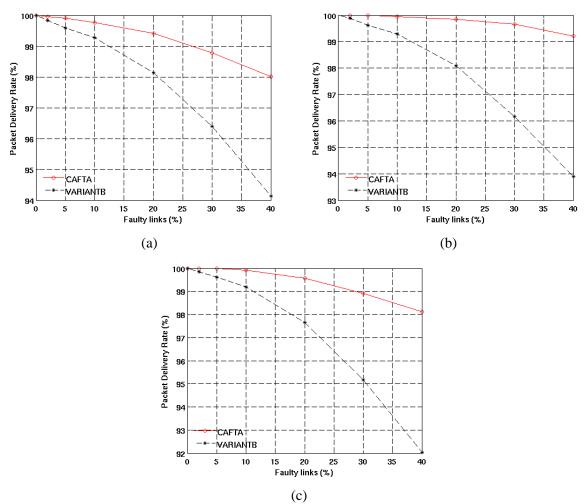

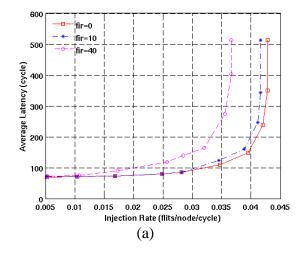

| 4.2.3 Comparaison CAFTA - Variant B                           | 88  |

| 4.2.4 Etude de l'algorithme CAFTA pour un réseau en maille 2D | 91  |

| 4.2.5 Performance de l'algorithme de routage CAFTA en tore 2D | 95  |

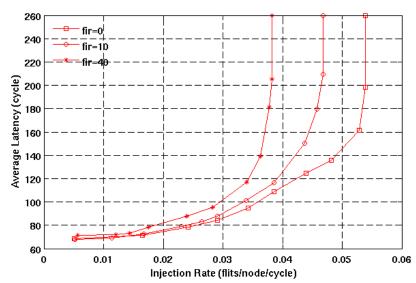

| 4.3 Amélioration de la métrique de congestion                 | 96  |

| 4.4 Conclusions                                               | 98  |

| Chapitre 5 Conclusions et perspectives                        | 101 |

| 5.1 Conclusions générales                                     | 102 |

| 5.2 Perspectives                                              | 103 |

| Bibliographie                                                 | 105 |

| Annexe A Résultats des simulations pour le Tore 2D            | 111 |

| Annexe B Publications issues de ce travail de thèse           | 117 |

# Liste des figures

| Figure 0.1 Tendance des besoins en capacité de calcul pour les SoCs (ITRS 2011)                                                                                           | 2  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Figure 0.2 Taux de défaillance induit par les problèmes de variabilité pour trois types de circuit 2011)                                                                  |    |

| Figure 1.1 Routeurs avec et sans canaux virtuels                                                                                                                          |    |

| Figure 1.2 Routage South-Last (à gauche) / North-Last (à droite)                                                                                                          | 11 |

| Figure 1.3 Un exemple de réseau virtuel                                                                                                                                   | 11 |

| Figure 1.4 Les couches de protocole d'un NoC                                                                                                                              | 12 |

| Figure 1.5 Modèles de faute : (a) un routeur avec 5 ports, deux liens unidirectionnels pour chaq (b) modèle de faute de lien unidirectionnel. (c) modèle de faute de nœud | 16 |

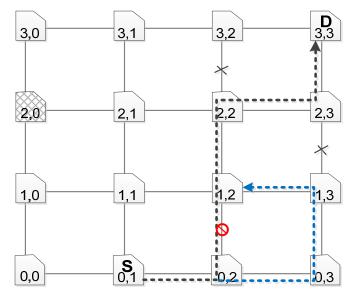

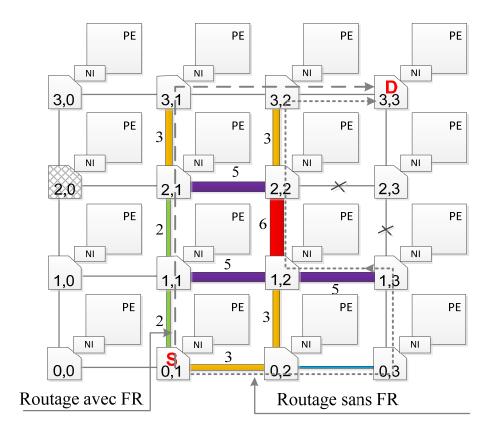

| Figure 2.2 Technique NoP: src: nœud source (0,0), dest: nœud destinataire (3,2) [Ma 2011]                                                                                 |    |

| Figure 2.3 Exemple de RCA: src: nœud source (0,0), dest: nœud destinataire (3,2)                                                                                          |    |

| Figure 2.4 Exemple de RCA dans un NoC avec plusieurs applications [Ma 2011]                                                                                               |    |

| Figure 2.5 Exemple de DBAR : src : nœud source (0,0), dest : nœud destinataire (3,2)                                                                                      |    |

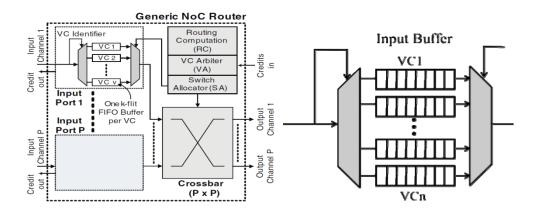

| Figure 2.6 Structure d'un routeur de référence et le tampon d'entrée                                                                                                      | 27 |

| Figure 2.7 Relation entre la faute, l'erreur et la défaillance                                                                                                            | 29 |

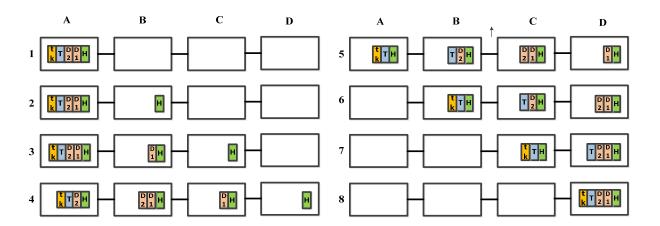

| Figure 2.8 Un exemple d'un avancement d'un paquet par UTP                                                                                                                 | 34 |

| Figure 2.9 Tolérance à une faute par UTP                                                                                                                                  | 35 |

| Figure 2.10 L'interblocage créé par deux paquets multicast                                                                                                                | 37 |

| Figure 2.11 Fragmentation de paquet multicast                                                                                                                             | 37 |

| Figure 2.12 Un exemple d'application de source virtuelle                                                                                                                  | 40 |

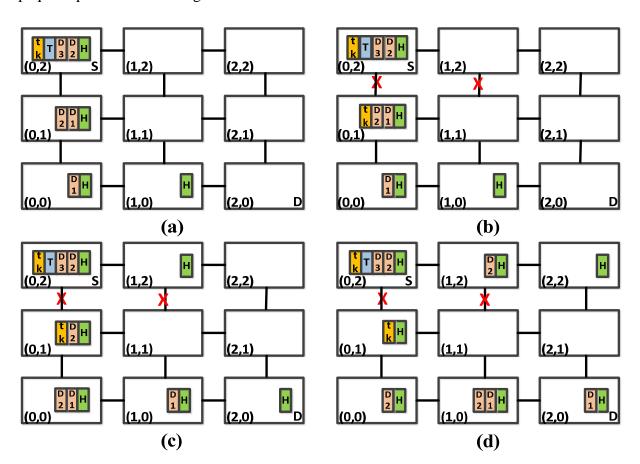

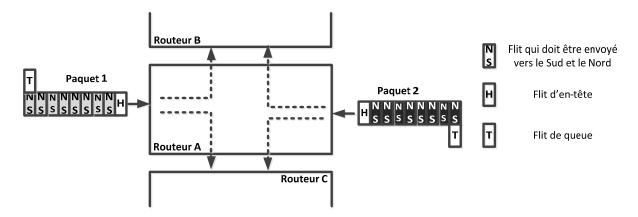

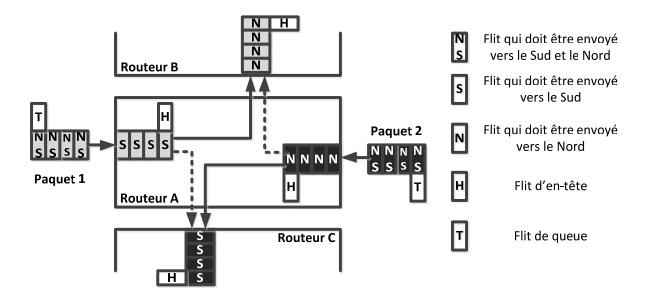

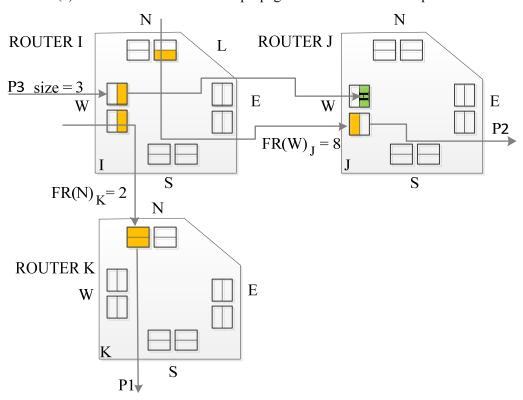

| Figure 3.1 BPR: recouvrement lors d'une rupture de paquet                                                                                                                 | 49 |

| Figure 3.2 Recouvrement de paquet utilisant la technique SPR                                                                                                              | 51 |

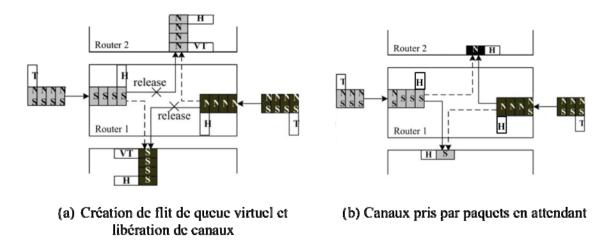

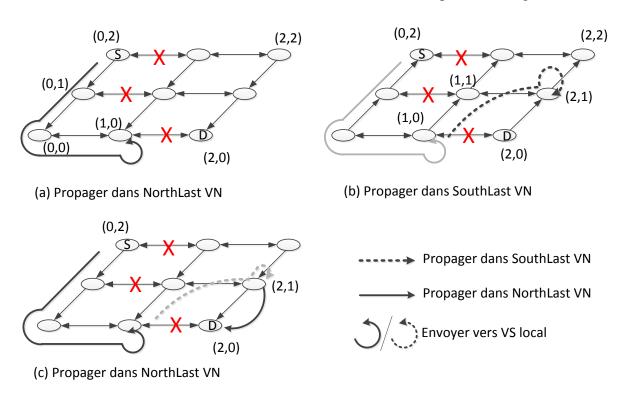

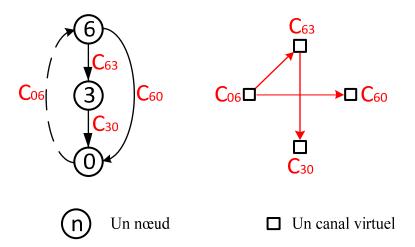

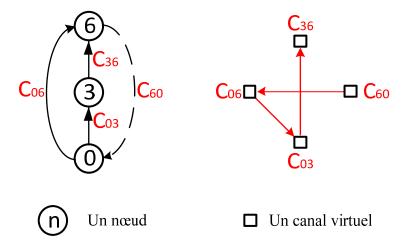

| Figure 3.3 Partitionnement de réseaux virtuels pour la Maille 2D                                                                                                          | 53 |

| Figure 3.4 Pseudocode de l'algorithme de routage CAFTA                                                                                                                    | 54 |

| Figure 3.5 Partitionnement de réseaux virtuels pour le tore 2D                                                                                                            | 55 |

| Figure 3.6 Un exemple de 3x3 Tore 2D                                                                                                                                      | 56 |

| Figure 3.7 Un exemple de 3x3 Tore 2D                                                                                                                                      | 56 |

| Figure 3.8 Restriction appliquée au réseau virtuel NorthLast                                                                                                              | 57 |

| Figure 3.9 Restriction appliquée au réseau virtuel SouthLast                                                                                                              | 58 |

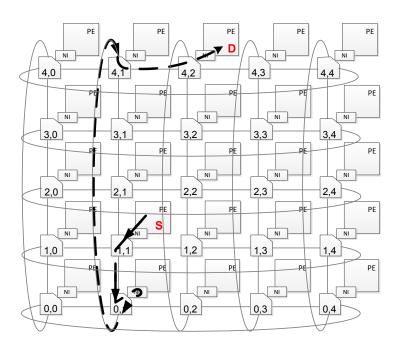

| Figure 3.10 Cas 1 un paquet injecté par une source à la frontière sud                                                                                                     | 59 |

| Figure 3.11 Cas 2 un paquet est injecté par une source virtuelle                                                                                                          | 59 |

| Figure 3.12 Dépendance de canal acyclique entre les liens enveloppants horizontaux                                                                                                                                                                 | 50 |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Figure 3.13 Dépendance de canal acyclique pour les 4 liens enveloppants                                                                                                                                                                            | 51 |

| Figure 3.14 Pseudo-code de l'algorithme de routage CAFTA                                                                                                                                                                                           | 52 |

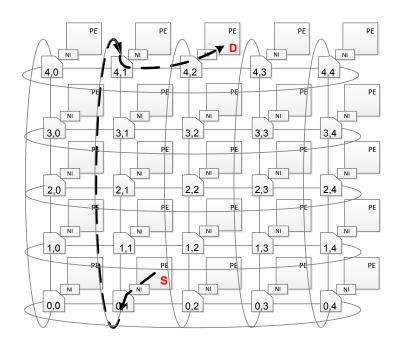

| Figure 3.15 Exemple de routage CAFTA dans un tore 2D 8x8                                                                                                                                                                                           | 53 |

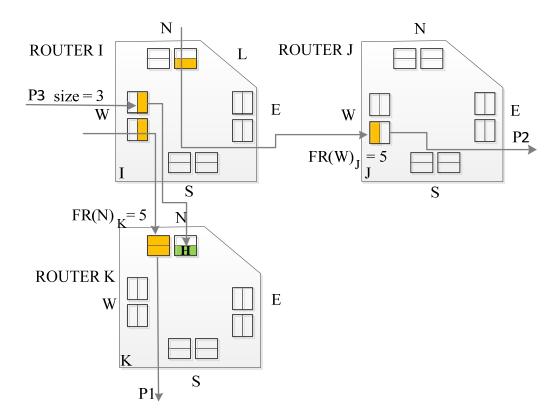

| Figure 3.16 Exemple du calcul de la mise à jour de la métrique FR métrique                                                                                                                                                                         | 58 |

| Figure 3.17 Exemple d'un paquet contournant la zone congestionnée grâce à la métrique FR                                                                                                                                                           | 59 |

| Figure 3.18 Cas d'inadéquation de la métrique FR                                                                                                                                                                                                   | 70 |

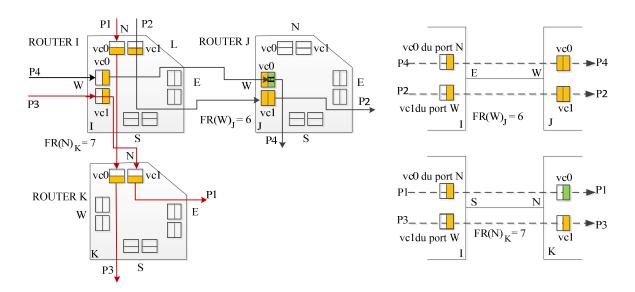

| Figure 3.19 Architecure du routeur Ri,j                                                                                                                                                                                                            | 12 |

| Figure 3.20 Le mécanisme de la conscience de fautes pour le routeur Ri,j                                                                                                                                                                           | 73 |

| Figure 3.21 Schéma d'un port d'entrée avec la logique dédiée au recouvrement de paquet                                                                                                                                                             |    |

| Figure 4.1 Flot de simulation                                                                                                                                                                                                                      |    |

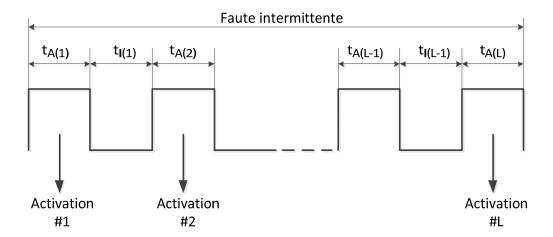

| Figure 4.2 Mise en œuvre de l'injection d'une faute intermittente                                                                                                                                                                                  |    |

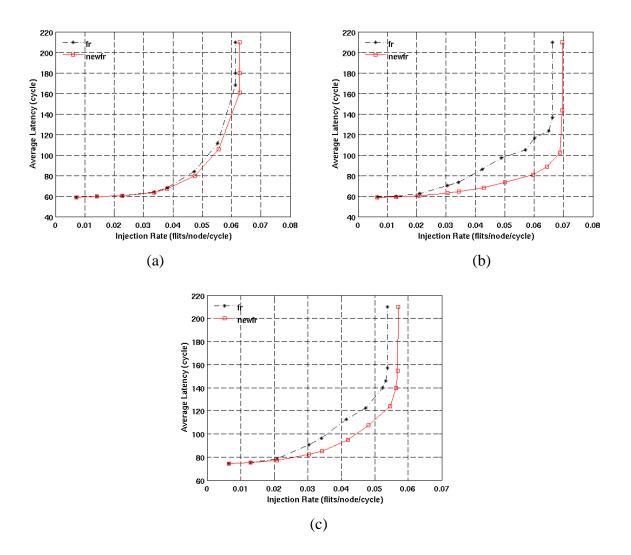

| Figure 4.3 Latence moyenne avec différentes métriques de mesure de congestion pour les trafics : (a)  Uniform Random », (b) « Transpose », (c) « Bit complement », pour un NoC 12x12 sans injection de fautes                                      | *  |

| Figure 4.4 Taux de paquets délivrés avec succès avec différents ratios d'injection de faute (faute de liens) sous le trafic «Uniform Random» pour un NoC en maille16x16                                                                            |    |

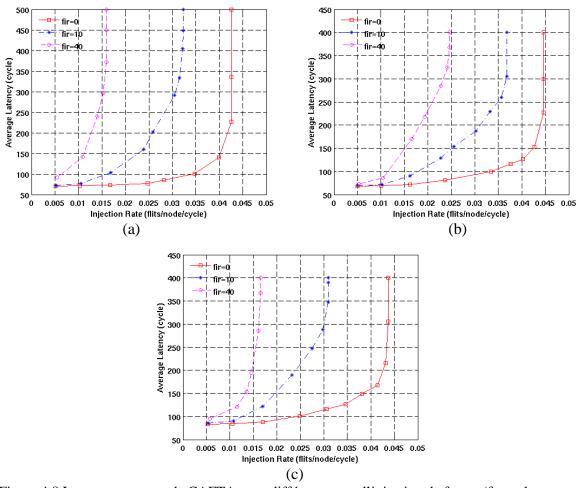

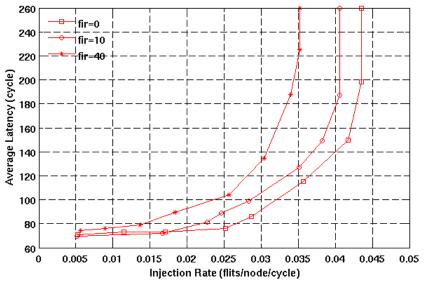

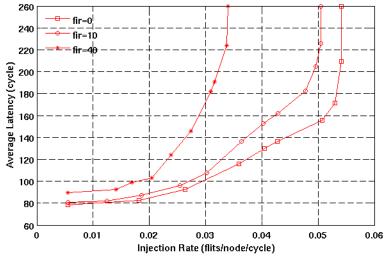

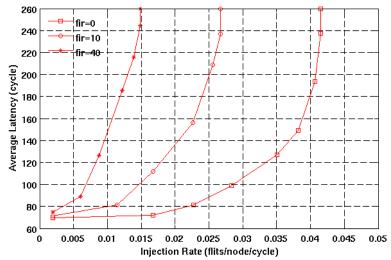

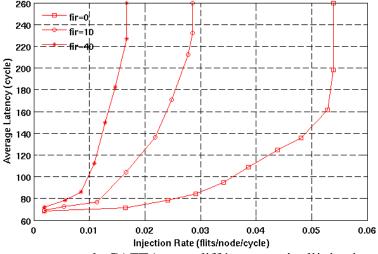

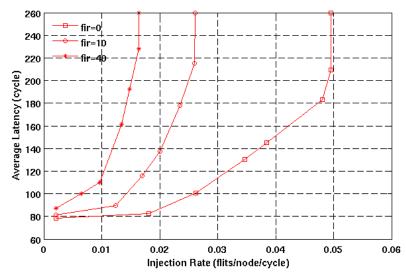

| Figure 4.5 Latence moyenne de CAFTA v.s. VariantB avec différents taux d'injection de paquet sous le trafic « Uniform Random» pour un NoC 16x16 en maille 2D (a) 0% fautes de lien (b) 10% (c) 40%                                                 |    |

| Figure 4.6 Taux de réussite avec différents ratios d'injection de faute (faute de liens) sous le trafic : (  « Uniform Random », (b) « Transpose », (c) « Bit complement », pour un NoC en  maille16x16                                            | a) |

| Figure 4.7 Latence moyenne de CAFTA avec différents taux d'injection de fautes (fautes de liens) sous le trafic: (a) « Uniform Random », (b) « Transpose », (c) « Bit complement », pour u NoC 16x16 en maille 2D                                  | n  |

| Figure 4.8 Latence moyenne de CAFTA avec différents taux d'injection de fautes (faute de routeurs) sous le trafic (a) « Uniform Random », (b) « Transpose », (c) « Bit complement », pour un NoC 16x16 2D Mesh                                     | 1  |

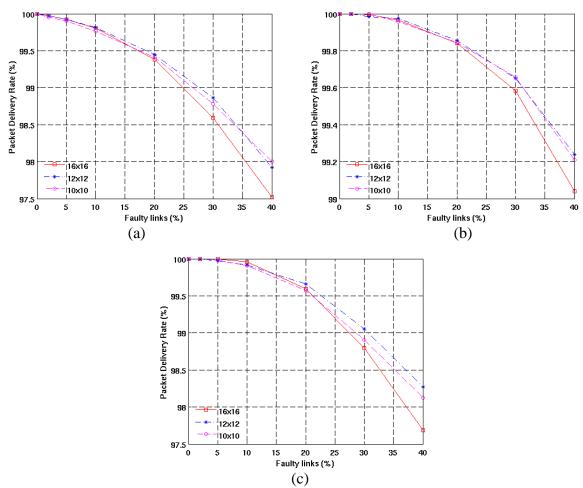

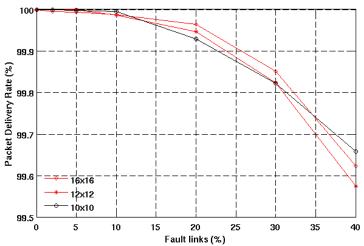

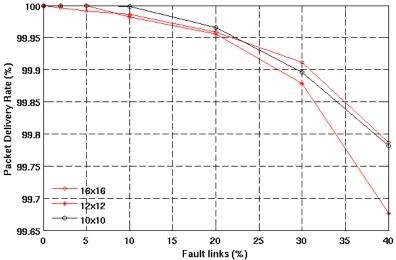

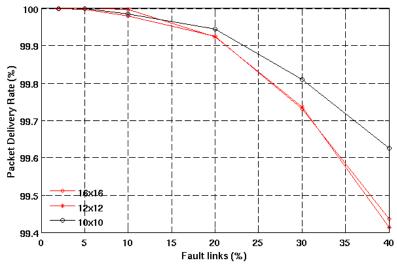

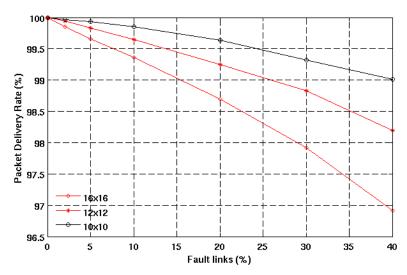

| Figure 4.9 Taux de paquets délivrés avec succès pour différentes tailles de réseau et différents taux d'injection de faute (faute de liens) sous le trafic (a) « Uniform Random », (b) « Transpos », (c) « Bit complement », pour un NoC 2D Mesh   |    |

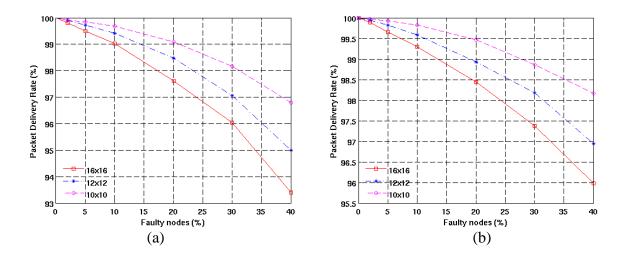

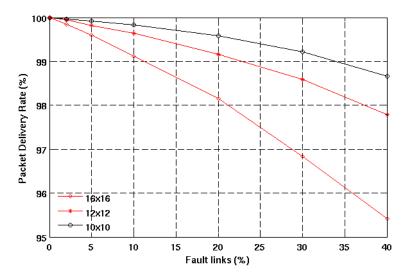

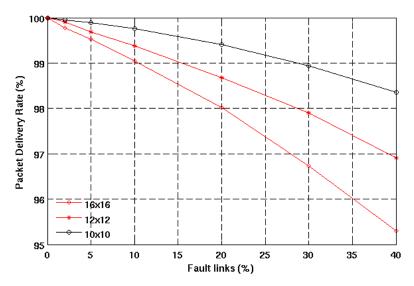

| Figure 4.10 Taux de paquets délivrés avec succès pour différentes tailles de réseau et différents taux d'injection de fautes (faute de nœud) sous le trafic (a) « Uniform Random », (b) « Transpose », (c) « Bit complement », pour un NoC 2D Mesh |    |

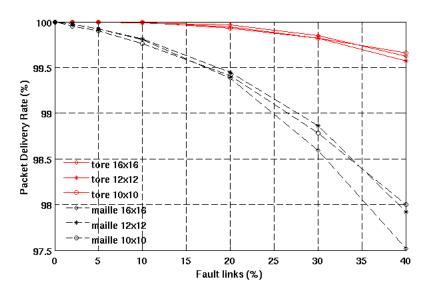

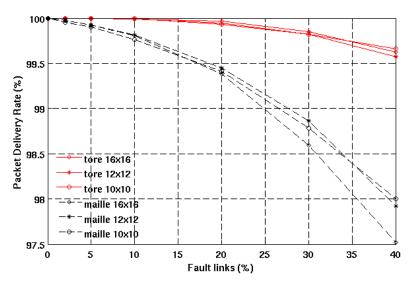

| Figure 4.11 Comparaison de la fiabilité entre le tore et la maille sous le trafic « Uniform Random»                                                                                                                                                |    |

| Figure 4.12 Latence moyenne avec différentes métriques de congestion sous le trafic (a) « Uniform Random », (b) « Transpose» et (c) pour un NoC 16x16 sans injection de fautes                                                                     | 97 |

## Liste des abréviations

BPR Bypass Packet Recovery

BW Buffer Write

ECC Error-correcting code

FB Free Buffer

FIFO First In First Out

Flit Flow control digit

FR Flit Remain

MPSOC Multiprocessors System on Chip

NACK Negative Acknowledgment

NI Network InterfaceNOC Network on ChipPE Processing Element

Phit Physic Digit

QoS Quality of Service (Qualité de service)

RC Route Calculation

SA Switch allocation

SAF Save and Forward

SBST Software-Based Self-Test

SOC System on Chip

SPR Splitting Packet Recovery

ST Switch Transfer

UTP Unique Token Protocol

VCA Virtual Channel Allocation

VC Virtual Channel (Canal virtuel)

VCT Virtual Cut Through

VN Virtual Network

VS Virtual Source

WH Wormhole

# Introduction

L gouverne l'industrie des semi-conducteurs ces dernières décennies. Grâce ou à cause de la loi de Moore, on intègre de plus en plus de blocs dans une seule puce. Les systèmes sur puce (System on Chip, SoC) peuvent contenir ainsi un microprocesseur, de la mémoire, des périphériques, des capteurs et encore d'autres composants permettant ainsi de répondre à la demande du marché de l'électronique grand public.

Cependant augmenter les performances tout en baissant ou en maitrisant la consommation est devenu un problème majeur. De ce fait, la course à la fréquence n'étant plus possible, la solution privilégiée pour garantir de meilleures performances consiste à intégrer plusieurs processeurs dans une seule puce. Un SoC avec plusieurs processeurs intégrés est appelé système multiprocesseurs sur puce (MPSoC).

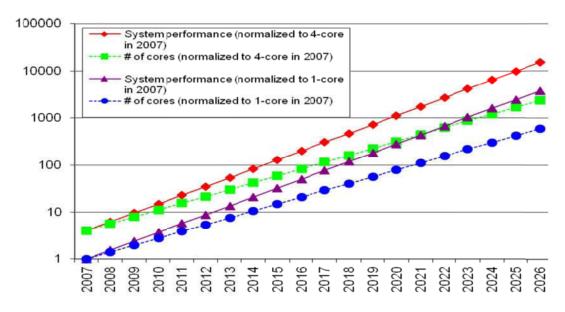

Selon l'étude d'ITRS [ITR11a], le développement des « Smartphones » en particulier, et des technologies multimédia en général a créé de nouveaux besoins: appareil photo, streaming de médias (décodage vidéo), les jeux en trois dimensions interactives, GPS, capteurs biologiques, etc. Ces applications nécessitent de plus en plus de puissance de calcul comme représenté sur la figure 0.1. L'intégration d'un certain nombre de processeurs dans une seule puce est donc une solution potentielle pour faire face à la puissance de calcul exigée en permanence par des applications embarquées avec une contrainte de temps de mise sur le marché (Time to Market) toujours aussi forte. Dans ces MPSoCs, le nombre d'unité de traitement (Process Element, PE) devrait augmenter de manière significative dans les prochaines années [ITR11a] (figure 0-1) et atteindre « mille cœurs» en 2023.

Cependant, la conception basée sur l'agrégation de plusieurs blocs (IPs) dans un MPSoC génère un certain nombre de défis. L'un des plus importants est le problème de communication inter IPs. Des interconnexions implémentées avec un ou des bus classiques ne sont plus suffisantes. Ces architectures ne peuvent plus fournir la bande passante nécessaire et posent aussi des problèmes de mise à l'échelle.

Pour pallier ces limitations, la solution étudiée et préférée dans le monde des architectures MPSoC depuis plus d'une décennie est celle basée sur le paradigme des réseaux

sur puce (Network on Chip, NoC) [Benini 2002]. Un NoC offre en effet une solution de communication « scalable » et modulaire et répond au problème du haut débit tout en ayant une consommation maîtrisée.

Figure 0.1 Tendance des besoins en capacité de calcul pour les SoCs (ITRS 2011)

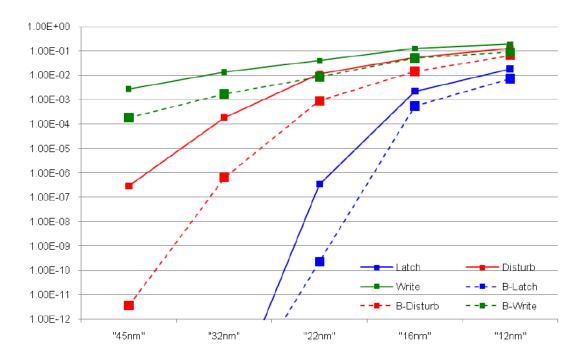

Avec la capacité d'intégration croissante de la technologie CMOS, les systèmes sur puce sont de plus en plus sensibles à différents facteurs qui influent considérablement sur leur rendement de fabrication et leur fiabilité lors de la mise en service. A côté des défauts dits catastrophiques (pannes permanentes), les défauts paramétriques notamment dus aux problèmes de variabilité, sont de plus aigus [ITR11]. Ces défauts paramétriques liés à la variabilité des paramètres des transistors amènent à un comportement similaire à celui induit par des défauts catastrophiques. Ainsi la fiabilité des circuits intégrés est menacée par les variations de tension et de fréquence [Weiser 1994], par le vieillissement, les effets des phénomènes de radiation [Ziegler 1979][Ziegler 1981][Ziegler 1996], les variations thermiques et électriques, le bruit intrinsèque, la diaphonie, etc.

Pour illustrer cela, la figure 0.2 nous montre l'évolution du taux de défaillance de trois circuits CMOS couramment utilisés (cellule SRAM, verrou et inverseur) pour différents nœuds technologiques [ITR11].

Figure 0.2 Taux de défaillance induit par les problèmes de variabilité pour trois types de circuits ITRS 2011)

Il est donc indispensable de prendre en compte dès la phase de spécification l'aspect gestion des défaillances pour assurer un fonctionnement correct et continu du circuit dans son environnement, et cela même lorsque le taux de défaillance est élevé.

Pour des applications critiques (aérospatial, automobile, biomédical, ...) différentes techniques de tolérance aux fautes sont utilisées et cela à plusieurs niveaux (circuit/système et matériel/logiciel).

Le travail décrit dans ce document s'inscrit dans ce contexte et cible principalement la tolérance aux fautes des réseaux sur puces. Ce travail fait suite, et vient en complément, à la thèse de Vladimir Pasca [Pasca 2011] qui a proposé pour les NoCs des solutions de tolérance aux fautes au niveau circuit et au niveau lien.

Pour compléter cela, de manière orthogonale, nous proposerons dans ce manuscrit des solutions au niveau algorithme de routage et système, qui permettent de tolérer des défauts nombreux, de différents types et origines, et qui tiennent compte de la congestion (due à la variation du trafic ou induite par les défauts).

Dans cette thèse, un algorithme de routage adaptatif tolérant aux fautes est présenté. Sa spécificité est qu'il permet de tolérer à la fois des fautes permanentes, transitoires et intermittentes. Une nouvelle technique de recouvrement de paquet est utilisée permettant de garantir un haut niveau de fiabilité dans un contexte de taux de défaillances élevée. Pour

réduire la latence et router les paquets de manière plus efficace vers des zones moins congestionnées, une nouvelle métrique de congestion est introduite. Un algorithme exploitant cette métrique et les états de congestion des liens et des routeurs est proposé et implémenté.

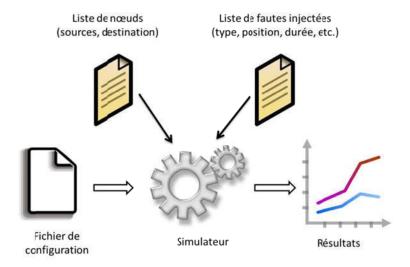

Des simulations intensives sur des plateformes virtuelles ont été effectuées avec des injections de fautes permanentes, transitoires, et intermittentes, pour représenter de manière réaliste les défauts pouvant survenir dans un NoC. Les résultats en terme de tolérance aux fautes, taux de défaillance et latence démontrent l'efficacité des solutions proposées.

Ce mémoire est organisé comme suit :

Dans le premier chapitre, les problématiques liées à la tolérance aux fautes et à la congestion des NoC seront exposées.

Une étude des différentes techniques existantes traitant ces deux points sera décrite dans le chapitre 2 « Etat de l'art ».

Dans le chapitre 3, les algorithmes tolérants aux fautes et de gestion de la congestion seront présentés ainsi que la microarchitecture du routeur réalisant ces fonctionnalités.

La plateforme d'expérimentation, le simulateur de réseau et les mécanismes d'injection de fautes seront décrits dans le chapitre 4. Dans ce même chapitre les résultats de simulation seront analysés et discutés.

Enfin le dernier chapitre permettra de tirer les conclusions sur ce travail et ouvrira sur les améliorations à apporter et les perspectives.

# **Chapitre 1 Contexte et Problématique**

| 1.1 Terminologie des réseaux sur puce    | 6  |

|------------------------------------------|----|

| 1.2 Gestion de la congestion             | 13 |

| 1.3 Gestion des fautes                   |    |

|                                          |    |

| 1.3.1 Types de fautes                    |    |

| 1.3.2 Modèles de fautes dans un NoC      | 16 |

| 1.3.3 Tolérance aux fautes multi-niveaux | 17 |

| 1.4 Les contributions                    | 17 |

Ce chapitre introduit brièvement la thématique des réseaux sur puce en présentant d'abord quelques notions de bases comme la topologie, le routage, le protocole de communication, le contrôle de flux, etc. Nous pourrons ensuite mieux définir les deux problèmes liés à la congestion dans le réseau et la tolérance aux fautes qui sont les deux points majeurs traités dans cette thèse.

### 1.1 Terminologie des réseaux sur puce

Un réseau sur puce, en anglais Network on Chip (NoC), est proposé comme une infrastructure d'interconnexion pour les communications dans un système sur puce (SoC). Appelé aussi micro réseau, par rapport au macro réseau qui relie un certain nombre d'ordinateurs par des câbles et des routeurs, il emprunte les modèles des macros réseaux au niveau de sa conception.

#### **Topologie**

La topologie définit l'arrangement des nœuds et des liens du réseau, en termes de placement et de connectivité des nœuds les uns par rapport aux autres.

En termes de connectivité, les topologies sont usuellement réparties en trois classes : directes, indirectes et hybrides. Dans le réseau direct, appelé aussi réseau point-à-point, chaque nœud est connecté à un certain nombre de nœuds voisins. Chaque nœud se compose d'un routeur, qui est connecté d'une part directement aux routeurs des nœuds voisins, et d'autre part à l'unité de traitement locale via une interface réseau (en anglais, Network Interface, NI). Dans un réseau indirect, la connexion entre les nœuds est établie par l'intermédiaire d'un certain nombre de commutateurs (switches). Le réseau hybride est une combinaison des deux types précédents.

#### Commutation

La commutation définie la façon dont est établie la connexion entre une paire de nœuds source-destination ainsi que la manière dont est acheminée un message. Il existe principalement deux modes de commutation :

<u>Commutation de circuit</u>: le chemin entre la paire source-destination doit être établi avant l'envoi d'un message. Les ressources allouées aux préalables ne peuvent être libérées

qu'une fois la transmission terminée. La commutation de circuit garantit une latence minimale une fois le chemin établi, mais la phase d'initialisation introduit un délai important. De plus, au niveau global, le débit est limité parce que le canal est réservé pendant la durée d'acheminement du message, bloquant ainsi l'envoi d'autres messages.

Commutation de paquet : dans ce mode de commutation, le message est divisé en plusieurs paquets (eux même divisés en flit, en anglais flow control digit). Le paquet est injecté dans le réseau sans allouer un chemin entre la paire source-destination contrairement à la commutation de circuit. Chaque paquet contient les informations nécessaires pour le routage, par exemple, l'adresse de destination, la taille du paquet en unité de flit, etc. Un paquet arrive dans un tampon d'entrée du routeur, et après calcul de routage, le paquet est envoyé vers un port de sortie correspondant sa destination. Il y a trois types de commutation de paquet en termes de stratégie de gestion de la propagation : Store and Forward (SAF), Virtual Cut-Through (VCT) et Wormhole (WH).

SAF : le paquet est le quantum de base pour une transmission. Ainsi un paquet ne peut être envoyé vers le routeur aval que s'il y a un tampon libre de taille suffisante pour stocker l'ensemble du paquet.

VCT améliore la latence par rapport à SAF en permettant d'envoyer le paquet vers le routeur aval, sans attendre, dès que celui-ci possède suffisamment de place pour accueillir le paquet. Le routeur courant n'est pas obligé de stocker tout le paquet avant de le transmettre. Cependant VC, comme SAF nécessite de prévoir un tampon dans chaque routeur au moins égal à la taille du paquet.

WH: la commutation de paquet de type Wormhole considère le flit comme unité de transmission. Cela a pour conséquence de réduire les besoins en espace mémoire pour les stockages intermédiaires. Le paquet peut avancer vers le routeur aval dès que celui-ci a dans ses tampons d'entrées/sorties un espace mémoire au moins équivalent à la taille d'un flit. Un paquet est composé de trois parties: un flit d'en-tête, des flits de corps (charge utile, en anglais payload) et un flit de queue. Le flit d'en-tête découvre le chemin vers la destination et réserve en même temps les ressources nécessaires pour le reste du paquet. Au passage du flit de queue, les ressources sont libérées et deviennent disponibles pour d'autres paquets.

La commutation de paquet de type Wormhole offre de meilleures performances que celles de SAF et VCT, mais WH introduit des risques d'inter-blocages des messages circulant

dans le réseau. Ces problèmes d'inter-blocages peuvent être résolu en utilisant un routage adéquat. Pour les systèmes sur puce la commutation de paquet de type Wormhole est préférée aux autres non seulement à cause des performances supérieures qu'elle permet mais aussi à cause d'une implémentation moins couteuse en surface. Nous nous focaliserons donc dans la suite de ce document sur les NoCs utilisant ce type de stratégie de communication.

#### Routage

Le routage définit quel chemin va être utilisé par un message/paquet du nœud source au nœud destination. Dans le cas Wormhole, l'en-tête d'un paquet (flit d'en-tête) contient les informations nécessaires à son routage. Lorsque le flit d'en-tête arrive à un nœud, le chemin vers le prochain nœud est défini par la fonction de routage. On distingue les routages déterministes et les routages adaptatifs [Duato 2003].

Le routage déterministe définit toujours le même chemin à suivre pour une paire (source, destination) donnée. Un exemple est le routage par ordre de dimensions, tel que le routage XY souvent employé dans un réseau sur puce en maille 2D (2D Mesh). Le paquet avance vers sa destination en traversant toujours en priorité la dimension X puis la dimension Y. La distance entre la source et la destination est minimale. Parmi les routages déterministes on trouve aussi les routages South Last, North Last, Negative First [Kariniemi 2004], ..., dans lesquels un sens de propagation des paquets est supprimé pour éviter les problèmes de « deadlock » (inter-blocages). L'avantage des routages déterministes réside dans la simplicité d'implémentation, cependant ils manquent de flexibilité pour les nœuds / zones congestionnées ou défaillantes. Ce problème peut être résolu par un routage adaptif qui peut se référer à des critères comme la santé des liens de sortie, l'état d'un nœud ou de ses voisins, le trafic du réseau, etc. lors de la décision de routage. Avec ces critères, les paquets peuvent éviter les zones du réseau congestionnées ou défaillantes et par conséquent diminuer la latence. Cependant, l'implémentation est plus complexe que celle du routage déterministe. En plus le routage adaptif peut induire d'autres phénomènes dynamiques comme les « Live-Lock, » qui correspondent à une situation où un paquet continue à parcourir le réseau mais sans jamais arriver à destination, situation à laquelle le routage déterministe est naturellement immun.

#### Protocole de contrôle de flux

Le contrôle de flux détermine comment les ressources du réseau (canaux physiques/ virtuels, tampons, ...) sont allouées aux paquets qui circulent dans ce réseau. Pour la commutation Wormhole, le contrôle de flux est généralement basé sur le mécanisme de crédit d'émission. Le routeur en amont possède des compteurs qui mesurent dans le routeur aval le nombre de tampons d'entrée libres pour chaque canal. Lorsque le routeur amont transmet un flit dans un canal, le compteur correspondant est décrémenté. Si un compteur est nul, cela signifie que le tampon en aval correspondant est plein et aucun autre flit ne peut être transmis jusqu'à ce que de la place se libère. Lorsque le routeur aval envoie à son tour un flit, il libère une partie du tampon associé, il renvoie un crédit vers le routeur en amont et le compteur correspondant est incrémenté.

#### **Canal virtuel**

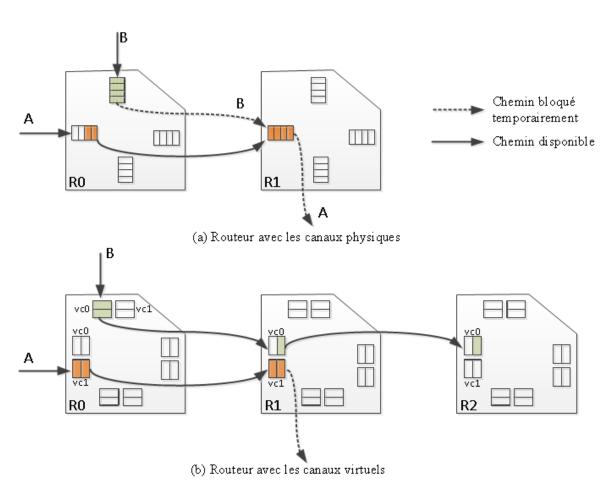

Figure 1.1 Routeurs avec et sans canaux virtuels

Dans la commutation WH le flit d'en-tête réserve un chemin physique et le reste des flits suivent. A un instant donné, on peut voir apparaître des problèmes de concurrence d'accès à un tampon d'entrée de routeur, de paquets provenant de plusieurs routeurs. Les tampons fonctionnent généralement comme des FIFOs. Ainsi, dès qu'un paquet occupe un tampon d'un canal physique, aucun autre paquet ne peut accéder à ce canal physique.

Sur l'exemple de la figure 1.1.a, un paquet A prend le canal physique (port d'entrée Est du routeur R1), et A est bloqué temporairement dans R0 et R1. En même temps, le paquet B doit aussi être envoyé vers le port d'entrée Est de R1. Bien que le lien physique soit libre, le paquet B ne peut pas traverser car le canal physique est pris par le paquet A.

Pour éviter cela, la notion de canal virtuel a été introduite. Ainsi un canal physique peut supporter plusieurs canaux virtuels (en anglais Virtual Channel, VC) multiplexés sur ce canal physique. En effet, l'intérêt des canaux virtuels est de découpler les canaux physiques des tampons mémoire. Cela permet à de multiples paquets de partager un même canal physique. Dans la figure 1.1.b, nous reprenons l'exemple précédent mais cette fois avec un routeur ayant 2 VCs pour chaque port d'entrée. Le paquet A entre dans le port Est du routeur R0 en occupant VC1 puis est envoyé vers le port est du routeur R1 toujours sur le canal VC1. Le paquet B entre en même temps sur le port Est de R0 en occupant le canal VC0. Comme le tampon d'entrée du canal VC0 du routeur R1 est libre, ainsi que le lien physique entre R0 et R1, le paquet B peut transiter vers R1 puis R2. Grâce aux canaux virtuels, les paquets peuvent traverser le même lien en multiplexant le temps d'accès, le débit est augmenté en cas de congestion et par conséquent la latence moyenne est diminuée.

Comme dit précédemment la notion de canal virtuel a aussi été introduite pour éviter l'inter blocage qui correspond à une situation où tous les paquets sont bloqués parce qu'ils s'attendent les uns les autres, attendant que les ressources qu'ils demandent se libèrent [Dally 1992]. L'utilisation des canaux virtuels permet d'avoir une plus grande diversité de routages possibles et permet de choisir la stratégie de qualité de service (QoS) adéquate en mettant les priorités sur les bons canaux et en allouant la bande passante pour les trafics prioritaires [Felicijan 2004][Rostislav 2005][Beigne 2005]-

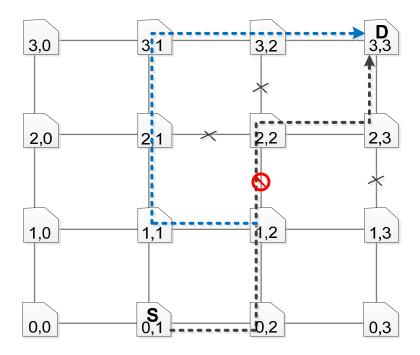

#### Réseau virtuel

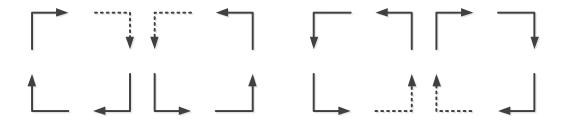

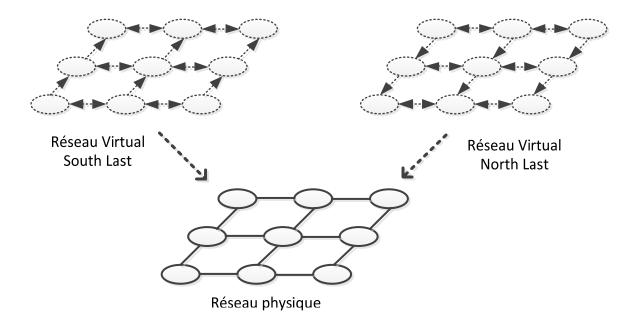

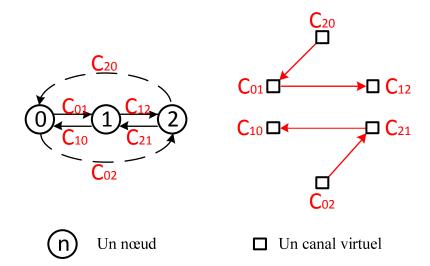

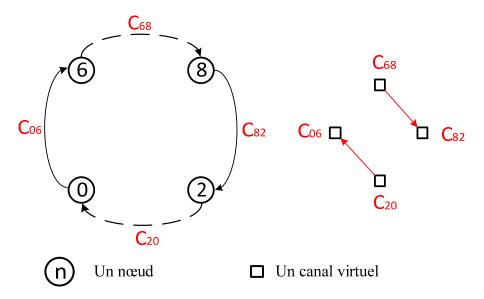

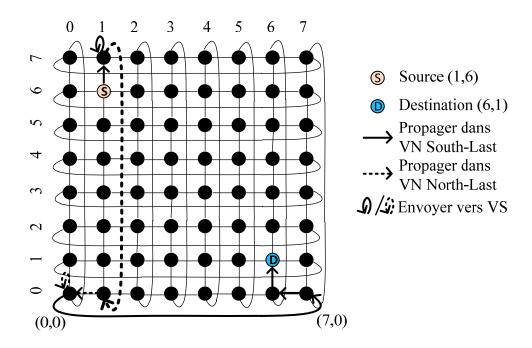

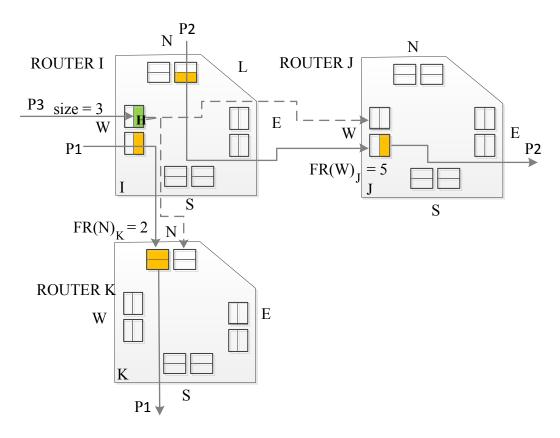

Figure 1.2 Routage South-Last (à gauche) / North-Last (à droite)

Figure 1.3 Un exemple de réseau virtuel

En 1995 [Cunningham 1995] la notion de « Réseau virtuel » (en anglais Virtual Network, abrégé VN) a été introduite. Un VN est un réseau logique projeté sur le réseau physique qui utilise les canaux virtuels. La figure 1.3 représente deux VNs (SouthLast VN et NorthLast VN) projetés sur le réseau physique qui a 4 canaux virtuels. A chaque VN est attribué 2 canaux virtuels. Chaque VN dans cet exemple possède son propre algorithme de routage. Les messages dont la destination est au sud de la source sont injectés dans le VN NorthLast, et les messages dont la destination est au nord de la source sont injectés dans le VN SouthLast. L'utilisation de plusieurs VNs augmente ainsi la diversité des routages effectifs.

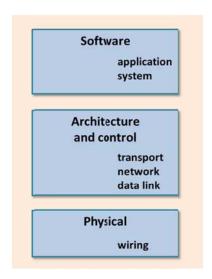

#### Les couches d'un réseau sur puce

En 2002 Benini a proposé des piles protocolaires adaptées au réseau sur puce, comme schématisé sur la figure 1.4 [Benini 2002]. Le réseau sur puce peut être vu comme une couche physique, une couche architecture et contrôle et une couche logicielle.

Figure 1.4 Les couches de protocole d'un NoC

La couche physique correspond aux fils physiques interconnectant les routeurs. La couche architecture et contrôle se décompose en trois niveaux : le niveau lien qui lie les nœuds et permet la transmission de messages; le niveau réseau qui détermine le parcours des données et l'adressage logique ; et le niveau transport qui permet d'établir la connexion entre les nœuds du réseau.

#### Critères guidant les choix de conception

Pour mesurer et quantifier les performances d'un réseau sur puce, nous avons besoin de métriques. L'un des critères les plus importants est la latence. Celle-ci correspond au délai entre le moment où un paquet est injecté dans le réseau sur puce par le nœud source et le moment où il est consommé par le nœud destination.

Un autre critère souvent considéré est le débit effectif ou bande passante utile, qui quantifie le volume de données transitant dans le réseau par unité de temps. Deux autres métriques non moins importantes sont la surface de silicium et le profil énergétique qui vont rendre compte de l'efficacité d'une conception de réseau sur puce par rapport à une autre. Enfin, pour ce qui concerne la fiabilité, et plus particulièrement la tolérance aux fautes, le taux de réussite de paquets donne une bonne indication sur la stratégie choisie. Ce taux correspond

au nombre de paquets arrivant à destination par rapport au nombre total de paquets injectés, cela pour un type de trafic donné, un débit donné et pour un certain taux de défaillance.

Ces différentes métriques aident le concepteur à choisir une stratégie par rapport à une autre selon ses contraintes, ses priorités (surface, rapidité, basse consommation ou robustesse)

#### 1.2 Gestion de la congestion

La performance d'un NoC est liée à la gestion de la congestion en cas de trafic élevé. Le problème peut être décrit comme suit : avec une charge du réseau basse ou moyenne, le taux de trafic accepté est égal au taux d'injection. Cependant, si le trafic augmente et atteint ou dépasse un certain niveau (le point de saturation), le taux de trafic accepté diminue et la latence augmente fortement et par conséquent, le débit effectif maximal ne répond plus aux attentes. La raison en est que lorsque le trafic est élevé, plusieurs paquets entrent en concurrence pour accéder aux mêmes ressources (canaux physiques ou virtuels, ports de sortie, etc.). Cependant seul un paquet peut réserver une ressource, les autres restent dans une file d'attente et bloquent à leur tour d'autres paquets amonts. Une telle situation peut conduire à la saturation du réseau et fortement dégrader les performances.

Plusieurs travaux sur les comportements des réseaux, avec des trafics correspondant à des applications réelles, montrent que ces trafics sont irréguliers, en rafales, et le trafic-pic va jusqu'à saturer le réseau [Flich 1999] [Martinez 1999] [Silla 1998].

La gestion de la congestion est donc incontournable et sa mise en œuvre est multi contraintes: large bande passante demandée avec en même temps une implémentation faible en surface et basse consommation.

Pour traiter le problème de la congestion, trois étapes doivent être observées:

- Mesure de la congestion : il est nécessaire dans un premier temps de définir des métriques et des moyens de mesurer la congestion dans le réseau en surveillant par exemple la latence ou les états du réseau.

- 2. Notification/propagation de l'information de la congestion : une fois que la congestion est détectée, il faut signaler/transmettre cette information au bloc décisionnaire local ou global.

- 3. Action pour la congestion : il s'agit ici de traiter l'information de congestion et d'appliquer la stratégie de désengorgement choisie. Plusieurs travaux proposent

une régulation du trafic. Lors de la détection de la congestion, les nœuds sources réduisent le taux d'injection de messages dans le réseau [Gerla 1980] [Jacobson 1988] [Jain 1992], voire stoppe l'injection complètement. D'autres travaux ont proposé l'utilisation d'un routage non-minimal (au contraire du routage minimal en termes de nombre de sauts/hops) pour équilibrer la charge sur le réseau [Dally 1993]. Des solutions introduisant l'ajout de tampons supplémentaires ont été proposées, cela afin de ralentir les messages et réduire le trafic du réseau [Smai 1998].

Cependant toutes les techniques proposées précédemment sont adaptées à des NoC sans défauts. Hors, pour les futurs MPSoCs, les taux de défaillance vont aller crescendo. Le nombre de défauts, dus entre autre au vieillissement, va s'accroitre de manière significative entrainant de manière inéluctable des problèmes de congestion, avant même que le NoC soit saturé par un trafic élevé.

#### Les questions qui peuvent se poser sont les suivantes :

- a) Les métriques de mesure de la congestion existantes sont elles optimales et adaptées ?

- b) Peut on mettre en place une solution de traitement de la congestion qui tienne compte non seulement du trafic mais aussi des ressources du NoC qui sont ou deviennent défectueuses ?

Une première contribution de cette thèse va consister à répondre à ces questions.

#### 1.3 Gestion des fautes

#### 1.3.1 Types de fautes

Les défauts dans un circuit intégrés peuvent être modélisés par ce que l'on appelle des fautes et ces dernières peuvent être rangées dans trois catégories selon leur comportement : permanentes, transitoire et intermittentes.

Les fautes permanentes correspondent à des changements physiques irréversibles dans le circuit dus par exemple à des perturbations dans le processus de fabrication ou aux phénomènes de vieillissement du circuit chez l'utilisateur. Sans traitement adéquat, une faute permanente ne peut donc être éliminée par une simple réinitialisation du circuit.

Les fautes transitoires sont pour leur part induites par des événements environnementaux externes temporaires. Par exemple les radiations solaires créent un flux de particules qui peuvent modifier l'état d'un nœud du circuit. Ces fautes ne sont pas destructrices. Ainsi, une erreur due à une faute transitoire peut être éliminée par la réinitialisation du matériel. Les fautes transitoires apparaissent généralement pendant un temps très court.

Les fautes intermittentes sont dues quant à elles au fonctionnement du circuit dans un environnement instable : variations de température, de tension d'alimentation, etc. Similaire aux fautes transitoires, une faute intermittente a aussi une durée de vie courte, mais elle apparaît et disparaît aléatoirement dans le temps sans période fixe. Pour leur modélisation, elles sont souvent regroupées sous la forme d'une rafale de fautes d'une durée de plusieurs cycles [Yu 2012]. Comme les fautes transitoires, les erreurs dues à une faute intermittente peuvent être réglées par la réinitialisation du circuit.

En bref, sauf pour les fautes permanentes qui endommagent physiquement la puce, les fautes transitoires et intermittentes peuvent être éliminées par la réinitialisation. Cependant, cette procédure est longue et pendant cette période le système n'est pas disponible. L'application doit être stoppée complètement, et tous les résultats obtenus précédemment sont perdus si des mécanismes de sauvegarde et de restauration du système n'ont pas été prévus, sans compter que ces mécanismes augmentent eux aussi le temps de non-disponibilité du système ainsi que sa complexité.

Dans la littérature scientifique, les solutions permettant de tolérer la présence de fautes dans un NoC sont nombreuses. Cependant, chaque solution proposée ne cible qu'un type de faute : permanente, transitoire ou intermittente, ce qui ne reflète que partiellement la réalité des circuits actuels et futurs où l'on retrouve un mix de ces trois types de fautes.

Ainsi une autre question à laquelle va essayer de répondre ce travail est :

c) Peut on proposer une architecture de NoC permettant de tolérer simultanément des fautes multiples et de type différents à savoir permanentes, transitoires et intermittentes ?

#### 1.3.2 Modèles de fautes dans un NoC

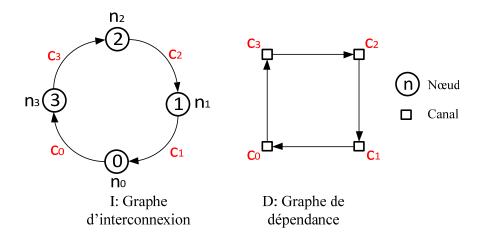

Outre les types de fautes cités précédemment, on peut se poser la question de la granularité du défaut considéré. En effet la solution choisie pour tolérer un défaut sera plus ou moins couteuse et complexe selon la granularité de l'erreur à « réparer ».

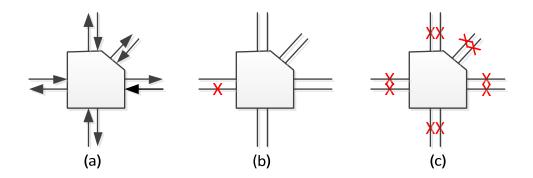

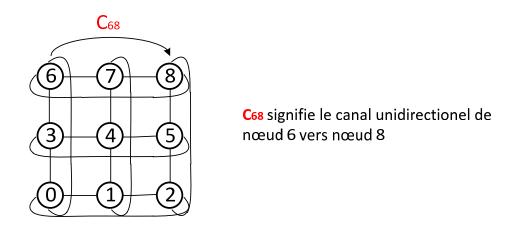

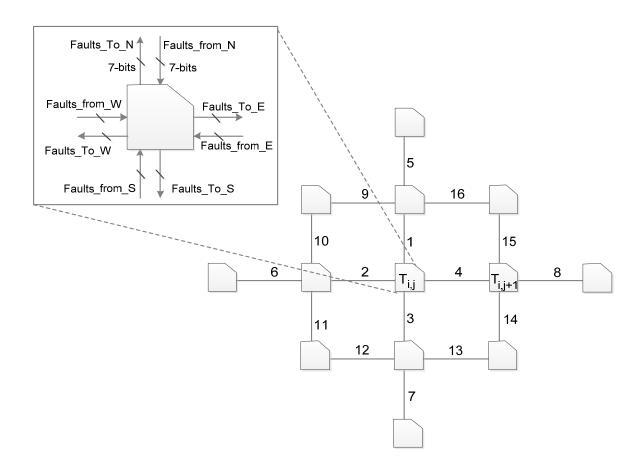

Les routeurs dans un NoC sont interconnectés par des paires de liens unidirectionnels (connexion bidirectionnelle). Chaque lien unidirectionnel regroupe des fils parallèles dont le nombre est égal à la taille d'un phit (digit physique). Les NoCs ciblés par ce travail sont des micro-réseaux qui seront utilisés dans des systèmes massivement multi-processeurs et dont les taux de défaillance seront élevés. Il semble donc judicieux dans un premier temps, pour des raisons de simplicité, de privilégier deux modèles de faute à gros grain :

- un lien unidirectionnel est défectueux. Cela peut être du à un défaut des fils reliant les routeurs ou à un défaut sur les ports d'entrée/sortie de ces mêmes routeurs. Les liens partiellement défectueux, dans lesquels seulement une partie des fils du lien est fonctionnelle ne seront pas considérés dans ce travail. Ainsi un lien complet est considéré comme défectueux lorsque ses deux liens unidirectionnels sont considérés comme fautifs.

- Un nœud est défectueux. Avec le modèle de faute de lien décrit précédemment, un nœud est considéré comme un nœud défaillant lorsque tous ses liens sont défectueux.

Figure 1.5 Modèles de faute : (a) un routeur avec 5 ports, deux liens unidirectionnels pour chaque port. (b) modèle de faute de lien unidirectionnel. (c) modèle de faute de nœud.

La figure 1.5 montre les différents modèles de faute considérés dans cette thèse, avec un routeur avec 5 ports (sud, nord, est, ouest et local). Nous considérons que tous les liens sont défaillants simultanément pour un nœud défectueux.

#### 1.3.3 Tolérance aux fautes multi-niveaux

Différentes techniques de tolérance aux fautes existent selon le niveau/la couche d'abstraction où elles interviennent. Elles sont le plus souvent basées sur l'introduction de redondance de données, de redondance temporelle ou spatiale.

Au niveau circuit, on peut trouver des techniques comme GRAAL [Nicolaidis 2007], qui permettent de tolérer des fautes transitoires de types « soft error » en effectuant un double échantillonnage.

Au niveau lien, pour détecter et corriger des fautes, il est possible d'introduire des techniques à base de codes de détection et correction d'erreurs (ECC) [Pasca 2011], de retransmettre et/ou de sérialiser les données [Nicolaidis 2011].

Au niveau du système ou de l'application, des techniques logicielles peuvent permettre de détecter, stopper et relancer une application en cas de défaillance du système : techniques de Checkpoint & Rollback [Rusu 2010], migration des tâches vers des ressources saines, ...

Au niveau routage, les solutions proposées sont basées soit sur un routage déterministe, soit sur un routage adaptatif. Comme indiqué précédemment le routage adaptatif est préférable pour des systèmes où la disponibilité de service est un critère primordial, le système n'ayant pas besoin d'être réinitialisé en cas de défaillance.

Cependant il n'y a pas de solution idéale qui permette à elle seule de détecter et tolérer tous les types de faute possibles. En fait ces techniques sont complémentaires. Selon la criticité de l'application finale et de la technologie utilisée, une combinaison de solutions multi-niveaux devra être mise en place : par exemple ECC (lien) + retransmission (système) + routage adaptatif.

#### 1.4 Les contributions

L'objectif de ce travail de thèse est d'améliorer les performances d'un NoC en termes de latence et débit pour un trafic élevé et en présence de fautes nombreuses et de différents types. Pour cela, on se propose à la fois d'améliorer le traitement de la congestion et de tolérer des fautes qui peuvent être permanentes, transitoires ou intermittentes. Les solutions proposées jusqu'ici permettent de traiter chaque type de faute indépendamment des autres et

pour des taux de défaillance qui ne correspondent pas à ce que l'on va rencontrer avec des densités d'intégration toujours plus grande. Le contexte dans lequel nous nous plaçons dans ce travail de thèse cible les applications s'exécutant sur du matériel soumis à un taux de défaillances élevées et où le critère de disponibilité est un paramètre clé. Ainsi les techniques de gestion de trafic et de tolérance aux fautes que nous proposons par la suite s'exécuterons en ligne, c'est-à-dire en cours d'exécution de l'application.

Les contributions originales qui vont être décrites et étudiées dans la suite de ce manuscrit sont :

- 1) Proposition et étude d'une nouvelle métrique de mesure de la congestion.

- 2) Amélioration, adaptation et implémentation de techniques de tolérance aux fautes permanentes, transitoires et intermittentes.

- 3) Intégration des propositions 1) et 2) pour proposer une microarchitecture du routeur correspondant.

- 4) Extension de la proposition aux topologies de type Tore.

- 5) Des simulations extensives faisant varier différents paramètres nous permettront d'évaluer l'efficacité et la viabilité de ces nouvelles approches.

# Chapitre 2 Etat de l'art

| 2.1 Congestion de réseau sur puce                    | 22 |

|------------------------------------------------------|----|

| 2.2 Gestion de fautes                                | 29 |

| 2.2.1 Notion de tolérance aux fautes                 | 29 |

| 2.2.2 Techniques de tolérance aux fautes dans un NoC | 32 |

| 2.3 Plateforme virtuelle d'expérimentation           | 42 |

| 2.4 Conclusions                                      | 43 |

Dans ce chapitre nous allons dans un premier temps restreindre les champs de recherche en fonction des objectifs initiaux. Suite à cela les travaux existant les plus pertinents concernant la gestion de la congestion puis la tolérance aux fautes dans les NOCs seront présentés. Nous étudierons leurs limites en termes d'efficacité, de coût et de complexité. Nous décrirons ensuite comment nous avons sélectionné une plateforme de simulation parmi les différentes existantes.

#### Caractéristiques du NoC étudié

Pour répondre aux questions soulevées précédemment tout en ciblant des NoCs pour systèmes massivement multiprocesseurs et dans un contexte de défaillances élevées, il faut au préalable définir les caractéristiques des NoCs qui feront l'objet de cette étude. Les deux contraintes primordiales qui vont guider les différents choix de conception sont la surface de silicium et la consommation additionnelles.

**Topologie** : 2D Mesh. Pour tenir compte de la mise à l'échelle nous choisissons de travailler sur des réseaux en maille 2D puis en tore 2D. Les solutions trouvées pourront alors plus facilement être étendues aux réseaux 3D.

Commutation: Wormhole. Le type de commutation choisie est la commutation de paquet WormHole car elle nécessite moins de mémoires tampons que SAF et VCT. De plus WH permet d'avoir une latence peu élevée, ce qui correspond à un de nos objectifs. Par conséquent, le contrôle de flux le plus approprié est celui basé sur le crédit [Dally 2004]. Néanmoins, la commutation de type WormHole introduit le risque de création d'interblocages. Il faut donc prévoir des techniques de prévention ou bien de recouvrement de l'interblocage.

Routage: Nous souhaitons tolérer des fautes en ligne, sans avoir à réinitialiser le système, le routage adaptif est donc le plus adapté, le routage déterministe ne pouvant pas modifier en cours d'exécution le routage en présence de liens/routeurs défectueux ou congestionnés. Les contraintes dues à l'embarqué, notamment la surface de silicium, font qu'on préfèrera un routage mis en œuvre grâce à des machines à états finis (FSM) plutôt qu'à l'utilisation de tables de routages. Enfin, pour éviter l'interblocage, nous utiliserons des canaux virtuels.

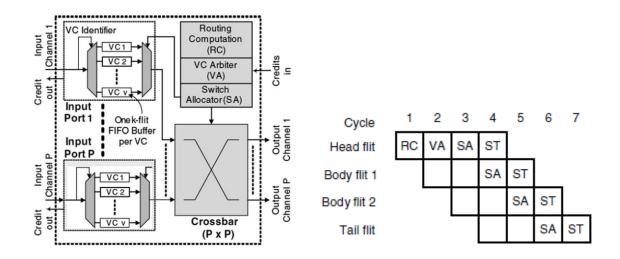

#### Architecture type du routeur

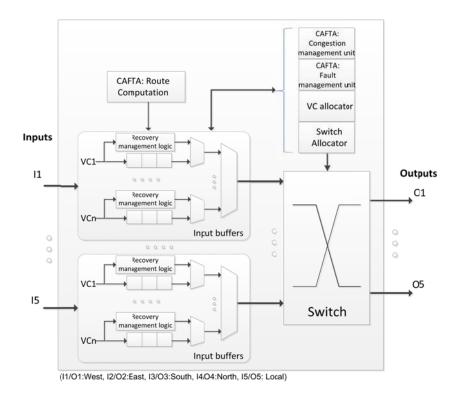

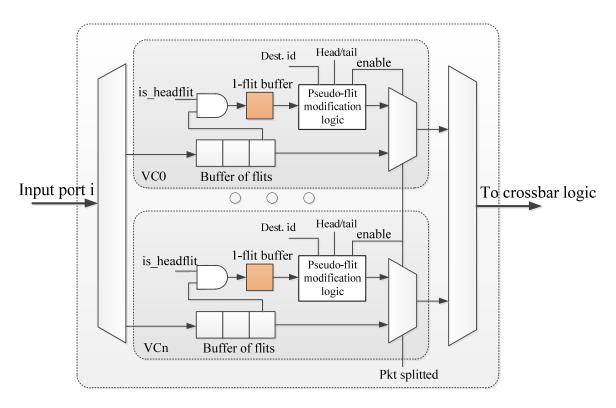

Il découle de ces choix et contraintes pour les NoCs embarqués, une architecture de routeur présentée sur la figure 2.1. Ce routeur est constitué de tampons en entrée, le contrôle de flux est à base de crédits et la commutation est de type WormHole. L'architecture du routeur est un pipeline à 4 étages [Dally 2004]. Ces étages correspondent à l'écriture dans les tampons (Buffer Write, abrégé BW), au calcul du routage (Route Computation, abrégé RC), à l'allocation du canal virtuel (Virtual Channel Allocation, abrégé VA), à l'allocation de commutation (Switch Allocation abrégé SA) et au transfert de commutation (Switch Transfer abrégé ST).

Figure 2.1 Structure d'un routeur à canaux virtuels pour réseau sur puce

Quand un flit d'en-tête arrive à un port d'entrée P, il est stocké dans le canal virtuel VC correspondant. L'adresse de destination stockée dans le flit d'en-tête est lue par le bloc RC qui calcule par quel port va sortir ce paquet (Nord, Sud, Est, Ouest). Dans le cycle suivant, le bloc VA attribue un canal virtuel correspondant, dans le routeur aval. Si en même temps plusieurs paquets demandent le même canal, le canal est attribué à un paquet selon une politique de type Round Robin ou FCFS (First-come, first-served). Lorsque le canal virtuel est alloué, dans le cycle suivant (ST), le paquet demande son transfert vers le tampon du routeur aval. Le paquet à qui est attribué le lien peut avancer d'un flit vers sa destination.

La littérature sur les réseaux d'interconnexion d'une manière générale est très vaste et fournie et son intégration dans les circuits a accéléré le nombre de travaux de recherche sur le sujet depuis la fin des années 1990. Une conférence leur est même dédiée : le symposium NoCs depuis 2007.

Nous ne ferons donc pas dans la suite un état de l'arte exhaustif des techniques de gestion de la congestion et de tolérance aux fautes. Seules les techniques correspondant aux NoCs dont les caractéristiques ont été citées plus haut seront décrites.

#### 2.1 Congestion de réseau sur puce

La congestion dans un réseau sur puce de type commutation de paquet correspond à un état où la performance est dégradée due à la saturation des ressources du réseau, tels que les liens, les tampons, les canaux virtuels, etc. Les effets résultant des problèmes de congestion incluent : retard de livraison de messages (latence), réduction du débit (bande passante), voire paralysie, toutes les communications s'arrêtent.

Les approches existantes pour la gestion de la congestion peuvent être classées en deux catégories : la prévention de la congestion et le recouvrement [Yang 1995].

#### Prévention

La prévention nécessite pour chaque nœud du circuit d'avoir l'autorisation d'injecter un paquet dans le réseau. Basé sur les connexions établies, le taux d'injection de messages est régulé en fonction des ressources réservées. L'inconvénient de ce type de gestion est que le débit du réseau est limité et cela d'autant plus que la qualité de service est élevée.

#### • Recouvrement

Les techniques de recouvrement sont basées sur la surveillance du réseau et déclenchent des actions si la congestion est détectée. Cette approche consiste en trois étapes.

Premièrement, la congestion doit être détectée localement. Certaines stratégies [Hyatt 1997][Smai 1998] mesurent le temps d'attentes des messages bloqués, alors que d'autres [Ascia 2008] [Gratz 2008] [Ma 2011] regardent l'état d'utilisation des ressources de réseau.

Deuxièmement, la congestion doit être notifiée aux nœuds du réseau. Nous pouvons classer ces techniques en deux catégories en termes de champ de notification : local/régional ou global.

Troisièmement, des actions doivent être appliquées pour résoudre le problème de congestion. Localement [Dally 1993] [Baydal 2005], en arrivant vers un nœud ou une région, un paquet peut être amené à contourner la zone, selon le degré de congestion et cela avec l'aide d'un algorithme de routage adaptif. Globalement, au niveau du réseau, le taux

d'injection de nouveaux messages dans les différents nœuds peut être ajusté à la baisse [Baydal 2005] [Thottethodi 2001] [Towles 2003]. Ces deux techniques, contournement et régulation du trafic, sont complémentaires et orthogonales et peuvent être utilisées ensembles

Nous présentons dans la suite trois approches différentes de gestion de la congestion par recouvrement qui utilisent des techniques de contournement

#### 1. NoP

Dans un réseau utilisant un contrôle de flux basé sur le crédit, le routeur de chaque nœud a la possibilité de connaître les états de congestion de ses voisins (nombres de canaux virtuels, nombres de cases disponibles des tampons dans le routeur aval). Cette connaîssance est appelée conscience de la congestion locale (en anglais Local Congestion Awareness, abrégé LCA).

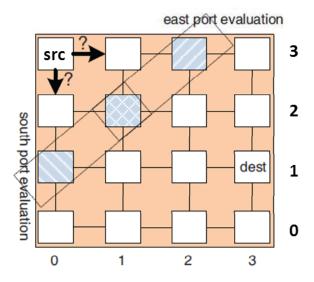

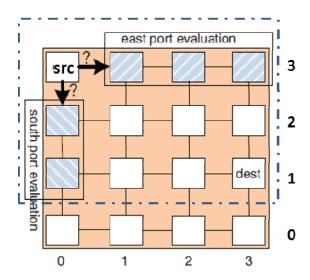

Figure 2.2 Technique NoP: src: nœud source (0,0), dest: nœud destinataire (3,2) [Ma 2011]

Afin d'éviter la congestion, NoP (en anglais Neighbors on Path, abrégé NoP) évalue la congestion de nœuds distants de deux rangs (hops) par rapport au nœud courant en utilisant la LCA de ses voisins au lieu de ne prendre en compte que sa propre LCA [Ascia 2008].

La figure 2.2 présente un exemple de NoC utilisant l'approche NoP. Lorsqu'un paquet est injecté dans le nœud de source (0,3), le routage adaptatif donne 2 directions possibles vers sa destination, l'un est l'est vers le nœud (1,3) et l'autre est le sud vers le nœud (0,2). Le choix doit être fait en comparant les états de congestion sur ces deux directions. NoP calcule,

anticipe les directions de sortie pour le paquet qui arrive dans le nœud (1,3) ou dans le nœud (0,2):

- 1, Mesure de congestion : la métrique de congestion « nombre de tampons libres dans les canaux» (« Free Buffer ») est mesurée pour chaque possibilité de routage (0,2) et (1,3). Chaque mesure prend en compte la mesure des tampons libres des nœuds directement voisins pour chaque cas, ici (0,1) et (1,2) pour le premier cas et (1,2) et (2,3) pour le second.

- 2, Propagation de la métrique de congestion : les mesures de congestion pour les deux voisins (0,2) et (1,3) sont envoyées au nœud (0,3).

- 3, Agrégation des métriques de congestion : la métrique pour la direction vers le nœud (0,2) est la somme des « Free Buffer » pour les canaux allant vers les nœuds (0,1) et (1,2) ; de même, la métrique pour la direction vers le nœud (1,3) est la somme des « Free Buffer » pour les canaux allant vers les nœuds (1,2) et (2,3). Le paquet sera envoyé alors vers le nœud dont la mesure est la plus faible.

Les résultats observés pour cette technique montrent des performances (latence) bien meilleures que le cas où seulement LCA (1 hop) est considérée. Cependant seule la congestion sur une petite région (une distance de 2 hops) peut être prise en compte, ce qui est limitant lorsqu'on vise des réseaux de grandes tailles. Un autre inconvénient est que le surcoût au niveau du silicium pour implanter cette technique est non négligeable.

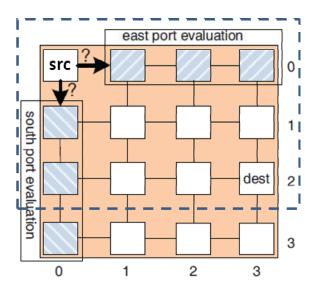

Figure 2.3 Exemple de RCA : src : nœud source (0,0), dest : nœud destinataire (3,2)

#### 2. RCA

NoP prend donc en compte seulement les informations de congestion à une distance de 2 hops. RCA (en anglais Regional Congestion Awareness, abrégé RCA) [Gratz 2008] résout ce problème par la propagation de l'état de congestion le long des axes (figure 2.3).

- 1, Mesure de congestion : dans chaque nœud, la métrique de congestion LCA est mesurée pour tous les canaux liés.

- 2, Propagation de la métrique de congestion : les mesures de congestion sont propagées le long de toutes les dimensions (par exemple, pour une topologie maille 2D, la propagation est horizontale et verticale.)

- 3, Agrégation de la métrique de congestion : la métrique pour le nœud (0,2) est la somme des métriques de tous les nœuds verticaux du nœud (0,3) jusqu'au nœud (0,0); et la métrique pour le nœud (1,3) est la somme des métriques de tous les nœuds horizontaux du nœud (3,0) jusqu'au nœud (0,0).

Figure 2.4 Exemple de RCA dans un NoC avec plusieurs applications [Ma 2011]

RCA peut donc évaluer la congestion globale sur les axes de propagation, et cela à chaque cycle au fur et à mesure que le paquet avance. Cependant, cette méthode inclut dans son calcul de routage des nœuds / régions non pertinents. Ainsi dans la figure 2.3, RCA évalue la congestion dans tout le réseau au lieu de s'arrêter à la zone de taille 3x4 qui est

définie par les positions de la paire source et destination. Cela peut entrainer de mauvais choix de routage. Par exemple, dans le cas où le MPSoC est prévu pour exécuter plusieurs applications et que le NoC est partitionné en conséquence mais sans prévoir de technique d'isolation ou de filtrage, on peut se retrouver dans la situation illustrée sur la figure 2.4. Dans ce cas la mesure de congestion va entrainer un routage du paquet vers la mauvaise direction.

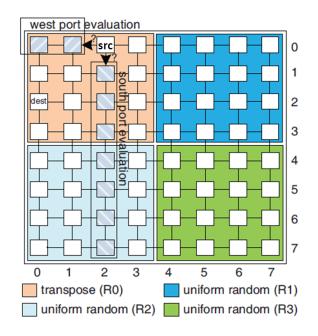

#### 3. DBAR

Une solution remédiant à ce problème a été mise au point. DBAR ([Ma 2011] prend en compte la position du nœud destination (zone de parcours minimale). Il résout le problème « d'interférence » dans RCA en filtrant les mesures de congestion au-delà de la zone du parcours minimal défini par la paire source-destination.

Figure 2.5 Exemple de DBAR : src : nœud source (0,0), dest : nœud destinataire (3,2)

DBAR évalue l'état de la congestion en suivant les principes suivants:

- 1, Mesure de congestion : dans chaque nœud, la métrique de congestion LCA est mesurée, comme précédemment.

- 2, Propagation de la métrique de congestion : Comme pour l'approche RCA, les mesures de congestion sont propagées suivant les axes X et Y.

- 3, Agrégation de la métrique de congestion : ici la différence de DBAR par rapport à RCA est que DBAR sur un axe donné ne fait la somme des mesures de congestions que jusqu'au niveau de la destination et pas sur tout l'axe. Cette technique définit bien la zone

connexe ou l'information de congestion est pertinente. De plus, elle permet de résoudre le problème soulevé par RCA lorsqu'un système est multi-applicatif et que le NoC doit être partitionné.

# Inconvénients majeurs de ces techniques (NoP, RCA, DBAR)

Ces techniques pour la propagation/notification des mesures de congestion nécessitent un nombre important de fils supplémentaires entre les routeurs. Les fonctions d'agrégation (sommation) et de calcul du routage ne sont pas négligeables en terme de surcoût en silicium. Enfin, la propagation de notification dure un cycle pour chaque hop. Les informations sur les états de congestion deviennent assez rapidement obsolètes lorsqu'un paquet doit voyager sur une longue distance. Ces dernières deviennent inutiles et donnent une vision erronée de la congestion d'une zone, entrainant une possible augmentation de la congestion.

# Métriques de mesure de la congestion

Les différentes approches décrites précédemment n'utilisent pas les mêmes métriques de mesure de la congestion. NoP utilise le nombre de cases de tampons libres en unité de flit. RCA exploite des métriques combinées parmi lesquelles le nombre de tampons libres, le nombre de canaux virtuels libres et le nombre de requêtes de transfert dans le crossbar vers un port de sortie donné. Quant à DBAR, l'approche mesure le nombre de canaux virtuels libres.

Figure 2.6 Structure d'un routeur de référence et le tampon d'entrée

Une première raison au fait que les métriques utilisées ne sont pas les mêmes est qu'elles ne se basent pas sur la même architecture de routeur.

Pour un routeur à canaux virtuels, le nombre de canaux libres pour un port d'entrée signifie que ce port peut recevoir plusieurs nouveaux paquets. Pour un routeur à canaux

physiques, ce nombre est soit 0 soit 1. Le nombre de cases libres est un meilleur indicateur sur l'état de congestion.

Mais de manière générale, aucune des métriques utilisées jusqu'ici ne peut donner une information précise sur l'état de congestion. Si nous prenons le routeur à canaux virtuels comme routeur de référence, il est clair que si moins on a de canaux virtuels libres ou si plus on a des tampons bien remplis, plus les canaux sont congestionnés. Cependant le nombre de canaux virtuels libres n'informe pas sur le fait qu'un tampon est bien rempli, à moitié ou peu rempli. De même le nombre de tampons libres, ne donne pas d'information sur l'utilisation des canaux virtuels. Mais ceci dit, un paquet ne pourra pas avancer s'il n'y pas de canal virtuel libre en aval même si tous les tampons des canaux virtuels sont peu remplis.

Ces observations nous amènent à penser que les métriques utilisées bien qu'utiles ne sont pas suffisantes pour donner une évaluation précise de la congestion sur un nœud, même lorsqu'elles sont combinées entre elles comme dans l'approche RCA.

Nous avons montré dans cette section les principales méthodes de gestion de la congestion dans un NoC. De manière générale, pour une architecture donnée on doit se poser les questions suivantes :

- Métrique de congestion : quelle est la plus pertinente ?

- Propagation de la congestion et champ de notification : que propager et jusqu'où ?

- Agrégation et choix du routage : quel algorithme de routage doit être mis en œuvre pour guider les paquets de manière efficace du point de vue de la congestion ?

Dans le chapitre suivant, nous allons répondre à ces questions en analysant le trafic dans le réseau. Nous proposerons une nouvelle métrique de mesure de la congestion plus représentative que les métriques existantes. Cette métrique pourra être appliquée aux techniques discutées dans ce chapitre.

## 2.2 Gestion de fautes

Cette section a pour but de présenter quelques notions de base sur la tolérance aux fautes, puis de décrire quelques approches spécifiques au type de NoC visé dans cette thèse.

#### 2.2.1 Notion de tolérance aux fautes

D'après la définition dans [Avizienis 2004], la sûreté d'un système est représentée principalement par ses trois attributs :

La disponibilité : il s'agit de savoir si le système est toujours disponible et fournit la fonction correcte.

La fiabilité : le système a t'il un taux de défaillance élevé ? Ce dernier peut rendre le système hors service partiellement ou complètement.

La maintenabilité : quelle est la difficulté pour mettre à jour le système ou le réparer après une défaillance ?

En terme de mesure, nous pouvons qualifier la fiabilité d'un système par son taux de défaillances, le temps moyen entre deux défaillances consécutives et le temps moyen de remise en service après une défaillance.

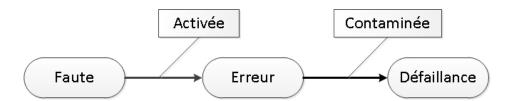

La fiabilité d'un système est mise en péril par des fautes, des erreurs et des défaillances. Le lien entre ces trois notions est illustré dans la figure 2.7.

Figure 2.7 Relation entre la faute, l'erreur et la défaillance

Une faute est un modèle mathématique représentant le comportement d'un ensemble de défauts physiques pour un système donné. Par exemple, pour les circuits VLSI, le modèle le plus utilisé est le modèle de collage (stuck-at-1/0) correspondant à une affectation permanente à 0 ou 1 d'une entrée ou sortie de porte logique. Il existe d'autres modèles faisant intervenir entre autre une notion de temporalité/durée de la faute.

Une erreur correspond à l'activation de la faute lors de l'exécution. Elle correspond à un décalage entre le comportement souhaité et le comportement réel. Elle a lieu à l'intérieur du système, et correspond par exemple à une donnée erronée ou un état invalide.

Une défaillance correspond à la propagation de l'erreur vers les sorties du système (contamination). Elle peut être d'importance plus ou moins grande selon la criticité de l'application, selon qu'elle modifie les données seulement ou stoppe l'exécution du système.

Ainsi une faute non masquée et activée conduit à une erreur, qui peut entrainer une défaillance.

En ce qui concerne les méthodes permettant d'améliorer la fiabilité d'un système, elles peuvent être classées en quatre catégories : prévention de fautes, prévision de fautes, suppression de fautes, et tolérance aux fautes. Ces quatre approches peuvent cohabiter et coopérer afin de rendre un système plus fiable. Cependant, les trois premières (prévention, prévision, et suppression) n'interviennent que dans la phase de conception et de fabrication. Par exemple, les structures de durcissement contre les effets des radiations sont définies et ajoutées dans la phase de conception et les circuits pour lesquels des fautes ont été détectées sont enlevés pendant la phase de test de fabrication.

Pendant l'utilisation du système, des fautes peuvent apparaître et cela de manière aléatoire. Ces fautes peuvent être dues aux effets du vieillissement, des variations de fréquence, de température et de tension (DVFS), aux effets de diaphonie, du bruit, etc.