# Conception et réalisation d'amplificateur de puissance MMIC large-bande haut rendement en technologie GaN

Victor Dupuy

### ▶ To cite this version:

Victor Dupuy. Conception et réalisation d'amplificateur de puissance MMIC large-bande haut rendement en technologie GaN. Electronique. Université de Bordeaux, 2014. Français. NNT: 2014BORD0211. tel-01238858

# HAL Id: tel-01238858 https://theses.hal.science/tel-01238858

Submitted on 7 Dec 2015

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

## THÈSE PRÉSENTÉE

### POUR OBTENIR LE GRADE DE

### DOCTEUR DE

# L'UNIVERSITÉ DE BORDEAUX

ÉCOLE DOCTORALE DE SCIENCES PHYSIQUES ET DE L'INGÉNIEUR SPÉCIALITÉ ÉLECTRONIQUE

Par Victor, DUPUY

# Conception et réalisation d'amplificateur de puissance MMIC large-bande haut rendement en technologie GaN

Sous la direction de : Pr. Eric KERHERVÉ, INP BORDEAUX co-directeur: DR. Nathalie DELTIMPLE (HDR), INP BORDEAUX

Soutenue le 22 Octobre 2014

### Membres du jury:

| M. KERHERVE, Eric, INP BORDEAUX                | Professeur | directeur de thèse     |

|------------------------------------------------|------------|------------------------|

| Mme. DELTIMPE, Nathalie, INP BORDEAUX          | HDR        | co-directrice de thèse |

| M. GAQUIERE, Chritstophe, Université de LILLE  | Profes     | seur rapporteur        |

| M. QUÉRÉ, Raymond, Université de LIMOGES       | Profes     | seur rapporteur        |

| Mme. MANEUX, Cristell, Université de BORDEA    | UX Profes  | seur examinateur       |

| M. MANCUSO, Yves, Thales Systèmes Aéroportés   |            | examinateur            |

| M. GARREC, Patrick, Thales Systèmes Aéroportés | S          | examinateur            |

| M. MALLET-GUY, Benoit, Thales Systèmes Aérop   | portés     | invité                 |

| M. PIOTROWICZ, Stéphane, Thales III-V LAB      |            | invité                 |

### Abstract

**Titre :** Conception et ralisation d'amplificateur de puissance MMIC largebande haut rendement en technologie GaN

Résumé: Ces travaux de thése se concentrent sur la conception d'amplificateur de puissance MMIC large-bande haut rendement en technologie GaN pour des applications militaires de type radar et guerre électronique. Les objectifs principaux sont de proposer des structures innovantes de combinaison de puissance notamment pour réduire la taille des amplificateurs actuels tout en essayant d'améliorer leur rendement dans le même temps. Pour cela, une partie importante de ces travaux consiste au développement de combineurs de puissance ultra compactes et faibles pertes. Une fois ces combineurs réalisés et mesurés, ils sont intégrés dans des amplificateurs de puissance afin de prouver leur fonctionalité et les avantages qu'ils apportent.

Différents types d'amplificateur tant au niveau de l'architecture que des performances sont réalisés au cours de ces travaux.

Mots clés: GaN, MMIC, amplificateur de haute puissance, combinaison de puissance, haut-rendement

**Title :** Design and realizations of wideband and high efficiency GaN MMIC high power amplifiers

**Abstract:** This work focus on the design of wideband and high efficiency GaN MMIC high power amplifiers for military applications such as radar and electronic warfare. The main objectives consist in finding innovative power combining structures in order to decrease the overall size of amplifiers and increasing their efficiency at the same time. For these matters, an important part of this work consisted in the design and realization of

ultra compact and low loss power combiners. Once the combiners realized and measured, they are integrated into power amplifiers to prove their functionality and the advantages they bring.

Several kind of amplifiers have been realized whether regrind their architecture or their performances.

**Keywords** GaN, MMIC, high power amplifier, power combining, high efficiency

# Contents

| Li            | st of          | Figure  | es         |                                                          | $\mathbf{v}$ |

|---------------|----------------|---------|------------|----------------------------------------------------------|--------------|

| $\mathbf{Li}$ | ${ m st}$ of   | Tables  | 5          |                                                          | xi           |

| 1             | Intr           | oducti  | ion        |                                                          | 1            |

| 2             | $\mathbf{Bib}$ | liograp | ohy and    | Context                                                  | 3            |

|               | 2.1            | Milita  | ry applica | ations                                                   | 3            |

|               | 2.2            | GaN d   | levices an | nd technologies                                          | 7            |

|               |                | 2.2.1   | Silicon a  | and wide bandgap devices                                 | 7            |

|               | 2.3            | The H   | EMT Ga     | ${\bf N}$ : a transistor dedicated to power applications | 8            |

|               |                | 2.3.1   | Transist   | or Basics                                                | 8            |

|               |                | 2.3.2   | The Gal    | N HEMT                                                   | 10           |

|               |                |         | 2.3.2.1    | History and principle                                    | 10           |

|               |                |         | 2.3.2.2    | Physical structure                                       | 11           |

|               |                |         | 2.3.2.3    | Electrical characteristics                               | 12           |

|               |                |         | 2.3.2.4    | Figures of merit                                         | 16           |

|               | 2.4            | Power   | r Amplifie | er Design                                                | 17           |

|               |                | 2.4.1   | Definition | ons                                                      | 17           |

|               |                |         | 2.4.1.1    | Power                                                    | 17           |

|               |                |         | 2.4.1.2    | Gain                                                     | 19           |

|               |                |         | 2.4.1.3    | Efficiency                                               | 20           |

|               |                |         | 2.4.1.4    | Linearity                                                | 21           |

|               |                | 2.4.2   | Power A    | Amplifier Basics                                         | 22           |

|               |                |         | 2.4.2.1    | Power Amplifier Classes                                  | 27           |

|               |                | 2.4.3   | Amplifie   | ers Topologies                                           | 31           |

# CONTENTS

|   |     |         | 2.4.3.1 Single-ended topologies            |

|---|-----|---------|--------------------------------------------|

|   |     |         | 2.4.3.2 Balanced / Differential topologies |

|   |     | 2.4.4   | Wideband amplifiers                        |

|   |     |         | 2.4.4.1 Reactively matched amplifiers      |

|   |     |         | 2.4.4.2 Feedback amplifiers                |

|   |     |         | 2.4.4.3 Traveling wave amplifiers          |

|   | 2.5 | State   | of art                                     |

|   |     | 2.5.1   | X-band                                     |

|   |     | 2.5.2   | Wideband: C-band to Ku-band amplifiers 46  |

|   | 2.6 | Thesis  | contribution                               |

| 3 | Pow | ver Co  | mbining 53                                 |

|   | 3.1 | Theor   | y on combiners for power amplifiers        |

|   |     | 3.1.1   | Current combiners                          |

|   |     | 3.1.2   | Transformers                               |

|   |     | 3.1.3   | Couplers                                   |

|   | 3.2 | Vertica | al coupling and elements stacking          |

|   |     | 3.2.1   | Mechanical aspects                         |

|   |     | 3.2.2   | Electrical aspects                         |

|   | 3.3 | Realiz  | ations                                     |

|   |     | 3.3.1   | Stacked Balun                              |

|   |     |         | 3.3.1.1 C to X-band balun                  |

|   |     |         | 3.3.1.2 X to Ku band balun                 |

| 4 | Wic | leband  | High Power Amplifiers 99                   |

|   | 4.1 | C to Y  | K-band high power amplifier                |

|   |     | 4.1.1   | Specifications                             |

|   |     | 4.1.2   | Output power stage                         |

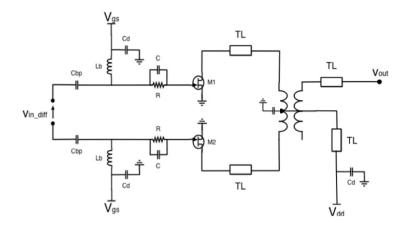

|   |     | 4.1.3   | Input stage: active balun                  |

|   |     | 4.1.4   | Overall HPA Architecture                   |

|   | 4.2 | X to I  | Ku-band traveling wave amplifier           |

|   |     | 4.2.1   | Specifications                             |

|   |     | 4.2.2   | Design methodology                         |

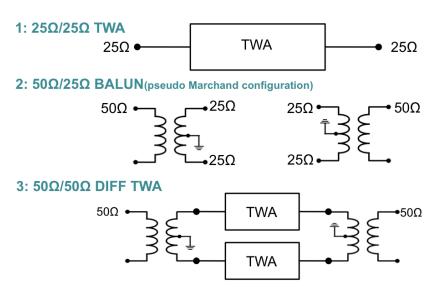

|   |     | 4 2 3   | 25 Ohms / 25 Ohms single TWA               |

|              |       |                                          | CONTENTS |

|--------------|-------|------------------------------------------|----------|

|              | 4.3   | 4.2.4 50 Ohms / 50 Ohms differential TWA |          |

| 5            | Cor   | nclusion and Perspectives                | 145      |

| 6            | List  | t of Publications                        | 147      |

| $\mathbf{R}$ | efere | ences                                    | 149      |

# CONTENTS

# List of Figures

| 2.1  | Example of a 300W hybrid S-band power amplifier module                          | 4  |

|------|---------------------------------------------------------------------------------|----|

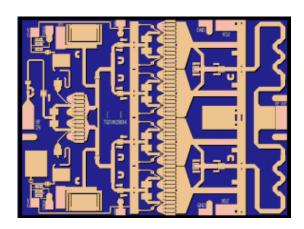

| 2.2  | Example of a X-band full MMIC HPA                                               | 5  |

| 2.3  | Example of C-band to Ku-band three stages MMIC HPA $\ \ldots \ \ldots \ \ldots$ | Ę  |

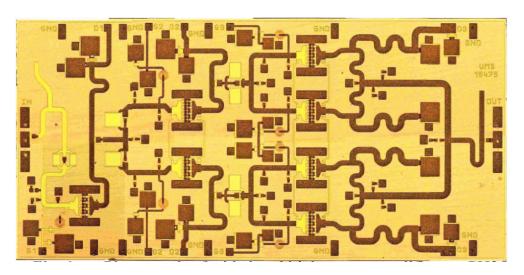

| 2.4  | Example of a full module based on MMIC's $\ldots$                               | 6  |

| 2.5  | Heterojunction bipolar transistor                                               | ć  |

| 2.6  | Field effect transistor                                                         | 10 |

| 2.7  | AlGaN/GaN HEMT cut view                                                         | 11 |

| 2.8  | HEMT small signal electrical model                                              | 13 |

| 2.9  | Output static characteristic of an HEMT transistor                              | 15 |

| 2.10 | Power coming in and out an Amplifier                                            | 18 |

| 2.11 | 1dB input and output compression point                                          | 22 |

| 2.12 | Scattering Parameters principle                                                 | 23 |

| 2.13 | Example of S-parameters plots (linear and Smith chart)                          | 25 |

| 2.14 | Stable amplifier vs. unstable amplifier                                         | 26 |

| 2.15 | Sinusoidal amplifier classes                                                    | 28 |

| 2.16 | Amplifier classes vs. bias point                                                | 29 |

| 2.17 | Non Sinusoidal amplifier classes                                                | 31 |

| 2.18 | Common-source power amplifier                                                   | 32 |

| 2.19 | Cascode power amplifier                                                         | 34 |

| 2.20 | Current combined power amplifier                                                | 35 |

| 2.21 | Balanced (pseudo-differential) power amplifier                                  | 36 |

| 2.22 | Differential power amplifier                                                    | 37 |

| 2.23 | Reactively matched amplifier                                                    | 39 |

| 2.24 | Feedback amplifier                                                              | 40 |

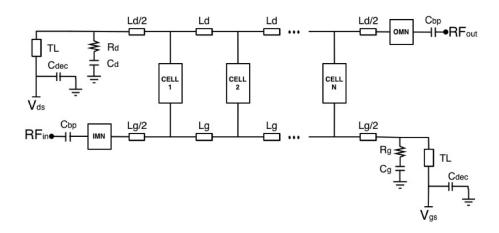

| 2.25 | Traveling wave amplifier                                                                | 41 |

|------|-----------------------------------------------------------------------------------------|----|

| 2.26 | Compact two stages current combined GaN HPA                                             | 43 |

| 2.27 | Compact two stages current combined GaN HPA                                             | 44 |

| 2.28 | A 14W GaN HPA realized with<br>UMS GH25 process                                         | 45 |

| 2.29 | C-Ku band 20W reactively matched GaN amplifier                                          | 47 |

| 2.30 | $14\mathrm{W}$ 2-18 GHz GaN Non-uniform Distributed Power Amplifier $\ \ldots \ \ldots$ | 48 |

| 2.31 | Decade bandwidth 2 to 20GHz GaN differential distributed power amplifier $$             | 49 |

| 3.1  | A 2-way Wilkinson combiner                                                              | 56 |

| 3.2  | A 2-way lumped Wilkinson combiner                                                       | 56 |

| 3.3  | A 19GHz, 3 stages 16 way Wilkinson combiner from the German Space $$                    |    |

|      | Agency                                                                                  | 57 |

| 3.4  | HPA output stage using a transformed Wilkinson combiner $\ \ldots \ \ldots$             | 58 |

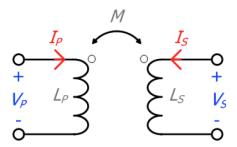

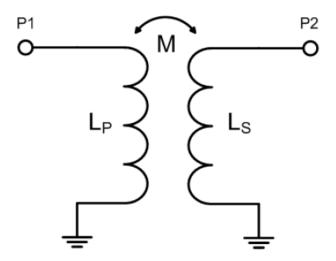

| 3.5  | Transformer representation                                                              | 58 |

| 3.6  | Transformer in 2-ports configuration                                                    | 60 |

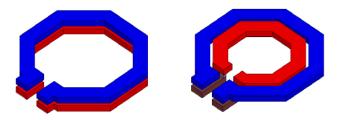

| 3.7  | Stacked transformer (left) and planar transformer (right) $\ \ldots \ \ldots \ \ldots$  | 63 |

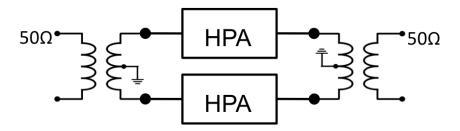

| 3.8  | Power amplifiers combined with baluns                                                   | 64 |

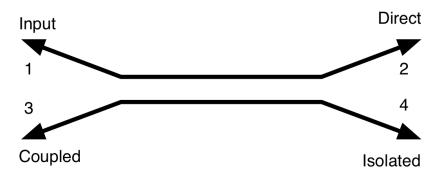

| 3.9  | Typical coupler representation and ports name                                           | 65 |

| 3.10 | Example of an HPA using couplers for power splitting/combining $$                       | 68 |

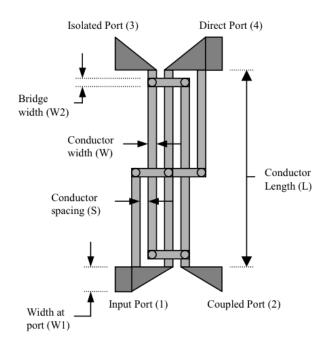

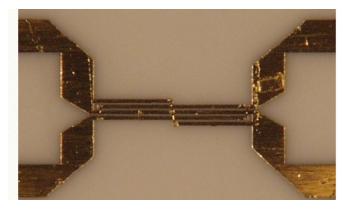

| 3.11 | Representation of a Lange coupler and port denomination                                 | 69 |

| 3.12 | Lange coupler on alumina substrate                                                      | 69 |

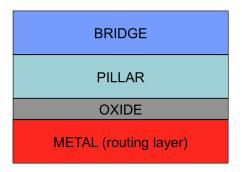

| 3.13 | Simplified MMIC layers stack                                                            | 71 |

| 3.14 | Two lines crossing thanks to an air-bridge                                              | 71 |

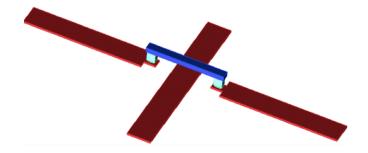

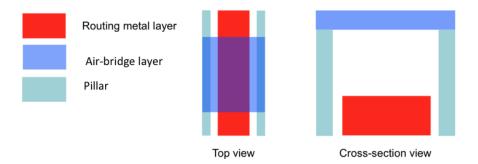

| 3.15 | Airbridge used as a stacked layer                                                       | 72 |

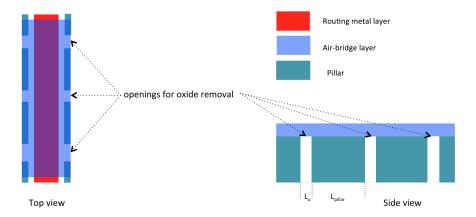

| 3.16 | Openings in pillars for oxide removal                                                   | 73 |

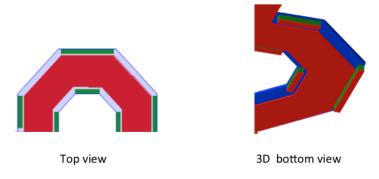

| 3.17 | Example of a possible shape realizable, top view                                        | 74 |

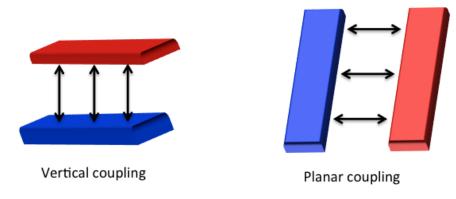

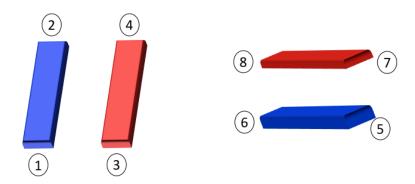

| 3.18 | Illustration of vertical (left) and planar (right) coupling $\dots \dots \dots$         | 75 |

| 3.19 | Simulated testbench to compare planar and vertical coupling $\dots \dots$               | 76 |

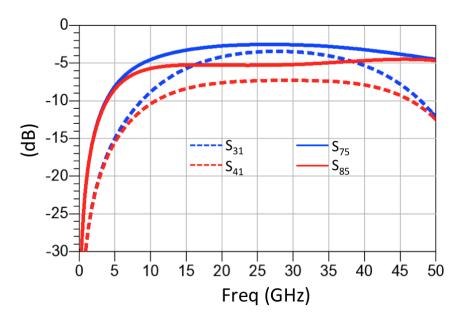

| 3.20 | Comparaison of energy transfer between planar and vertical coupling                     | 77 |

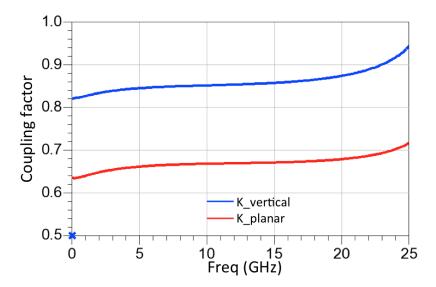

| 3.21 | Comparaison of coupling factor between planar and vertical coupling $ . $ .             | 78 |

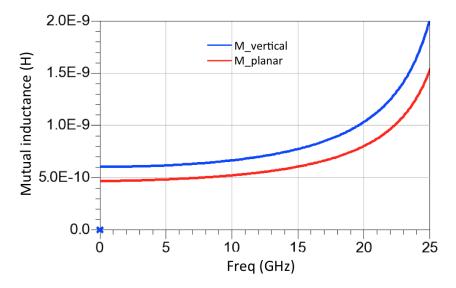

| 3.22 | Comparaison of mutual inductance between planar and vertical coupling                   | 79 |

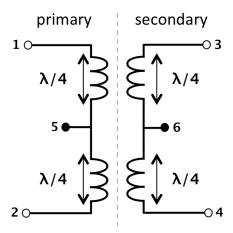

| 3.23 | Detailed representation of a balun                                                      | 80 |

| 3 24 | Ontimal impedances for a balun with a transformation ratio of one                       | 81 |

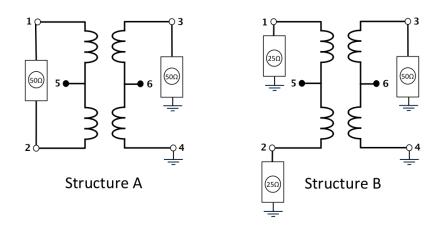

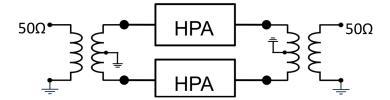

| 3.25 | Elementary HPA combined with baluns                                                   | 82  |

|------|---------------------------------------------------------------------------------------|-----|

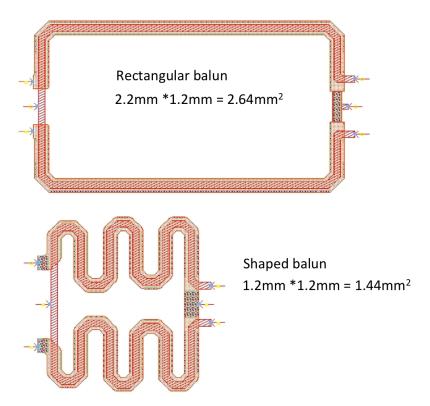

| 3.26 | Elementary balun shapes : rectangular (left) and circular (right) $\ \ldots \ \ldots$ | 83  |

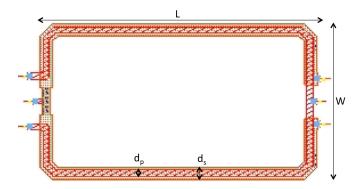

| 3.27 | Rectangle balun and principal dimensions                                              | 83  |

| 3.28 | Balun configuration for geometry tuning                                               | 84  |

| 3.29 | Balun response vs. geometry                                                           | 85  |

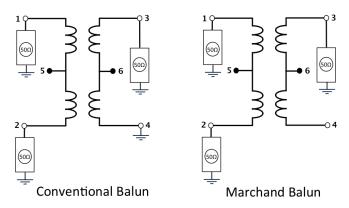

| 3.30 | Conventional and Marchand balun arheitecture                                          | 86  |

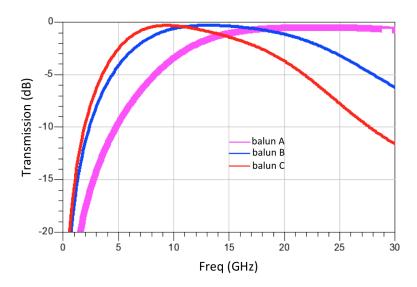

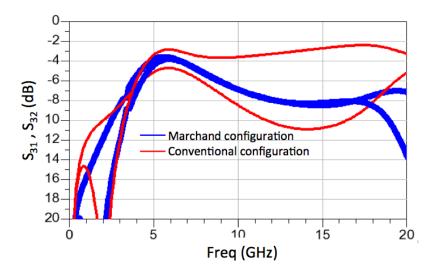

| 3.31 | Transmission parameters for a conventional and a Marchand balun $\ . \ . \ .$         | 87  |

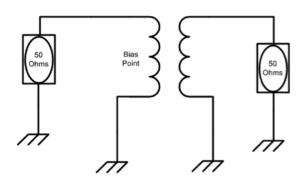

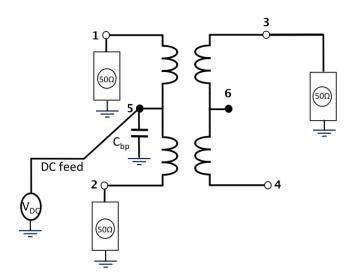

| 3.32 | Using winding midpoint as DC feed                                                     | 87  |

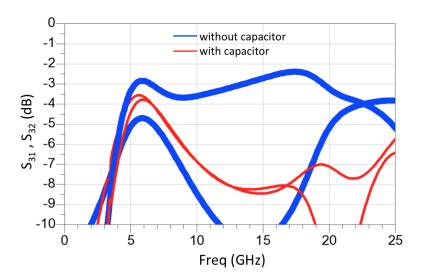

| 3.33 | Transmission parameters for a balun with DC block capacitor and without               | 88  |

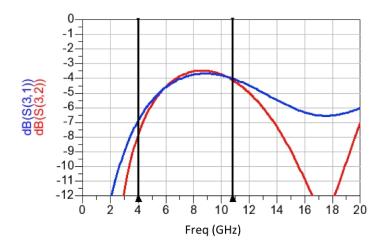

| 3.34 | Transmission parameters for the rectangle balun                                       | 89  |

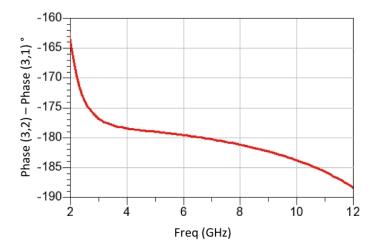

| 3.35 | Phase difference for the rectangle balun                                              | 90  |

| 3.36 | Shaping a balun to reduce its size                                                    | 91  |

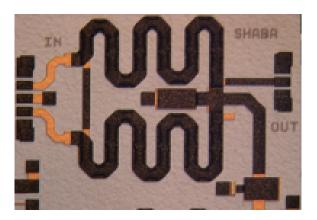

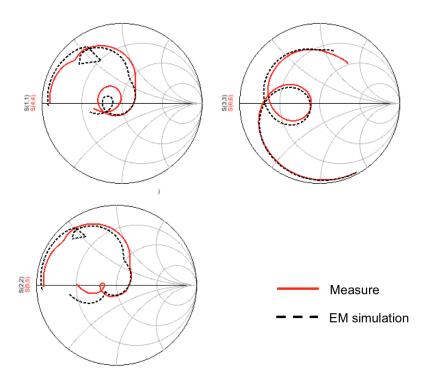

| 3.37 | Realized C to X band balun                                                            | 92  |

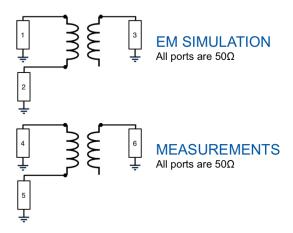

| 3.38 | Ports configuration for EM simulation and measurement                                 | 92  |

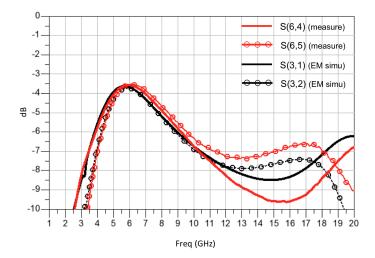

| 3.39 | Transmission comparison for EM simulation and measurement                             | 93  |

| 3.40 | Phase difference comparison for EM simulation and measurement                         | 94  |

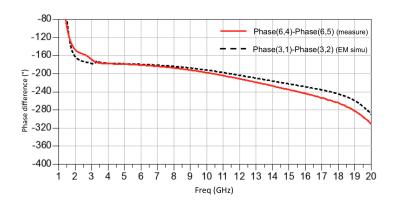

| 3.41 | Impedances comparison for EM simulation and measurement (2Ghz to                      |     |

|      | 12GHz)                                                                                | 95  |

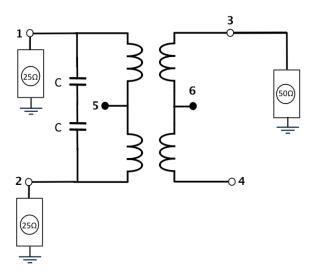

| 3.42 | Capacitor added in parallel to the differential winding to reduce size and            |     |

|      | increase bandwidth                                                                    | 96  |

| 3.43 | X to Ku-band balun with inside capacitors                                             | 97  |

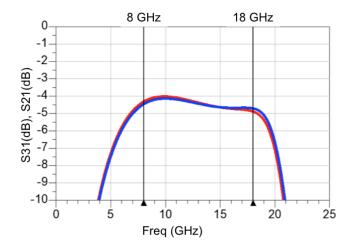

| 3.44 | X to Ku-band balun transmission parameters                                            | 97  |

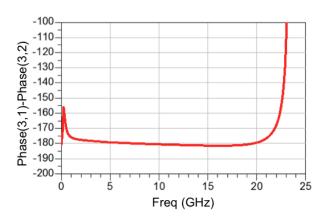

| 3.45 | ${\bf X}$ to Ku-band balun phase difference between differential paths                | 98  |

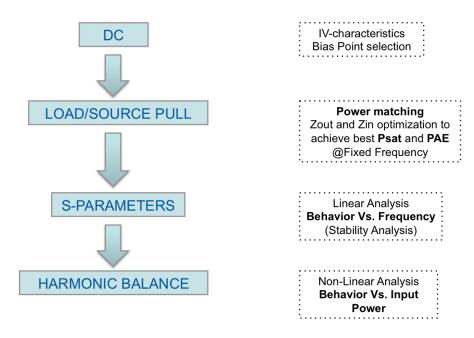

| 4.1  | Proposed designed flow for HPA design                                                 | 101 |

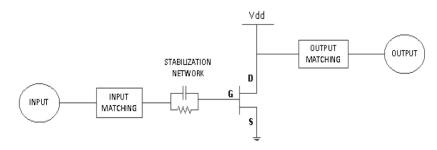

| 4.2  | Common source topology used to characterize transistors                               | 102 |

| 4.3  | $I_{ds}$ vs. $V_{ds}$ for various $V_{gs}$ for an $8*125\mu m$ device                 | 103 |

| 4.4  | $I_{ds}$ vs. $V_{gs}$ for $V_{ds}$ =25V for an 8*125 $\mu$ m device                   | 104 |

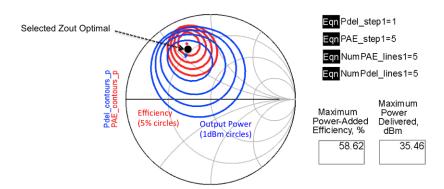

| 4.5  | Load pull simulation results for an $8*125\mu\mathrm{m}$ device at 8GHz               | 105 |

| 4.6  | Comparison between different gate widths for an 8 fingers transistor at               |     |

|      | 10GHz                                                                                 | 106 |

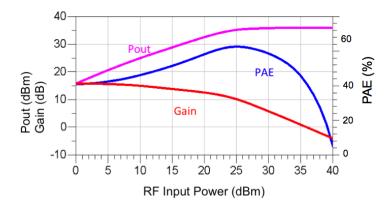

| 4.7  | Non linear simulation results for an $8*125\mu\mathrm{m}$ device at $10\mathrm{GHz}$  | 107 |

| 4.8  | $8*125\mu$ m device characteristics vs. frequency                                     | 108 |

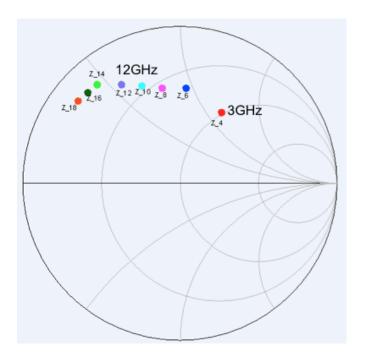

| 4.9  | $8*125\mu\mathrm{m}$ device selected optimal impedances in Smith chart                    | 109 |

|------|-------------------------------------------------------------------------------------------|-----|

| 4.10 | Selected architecture for the output stage                                                | 110 |

| 4.11 | Simulated small signal gain of the output stage standal<br>one chip                       | 111 |

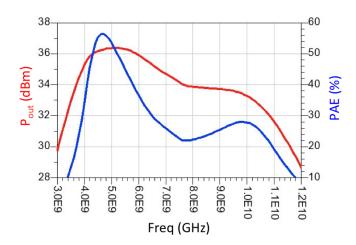

| 4.12 | Simulated output power and PAE vs. frequency for $P_i$ n=29dBm for                        |     |

|      | output stage standalone chip $\ldots \ldots \ldots \ldots \ldots \ldots$                  | 111 |

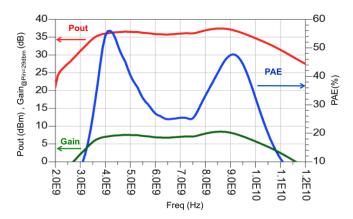

| 4.13 | Simulated output power, PAE and gain vs. frequency for $P_{in}$ =29dBm                    |     |

|      | for output stage with a matched input                                                     | 112 |

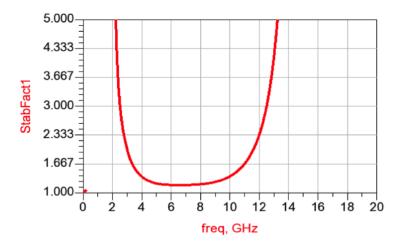

| 4.14 | Rollet factor from DC to 20GHz                                                            | 113 |

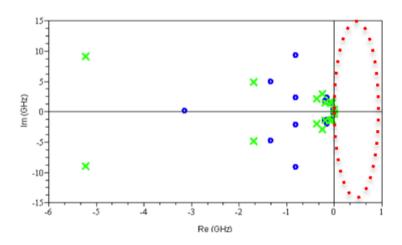

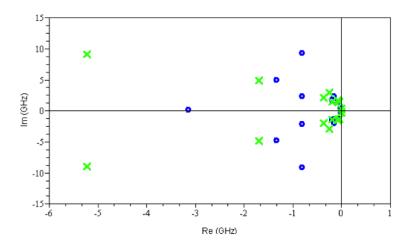

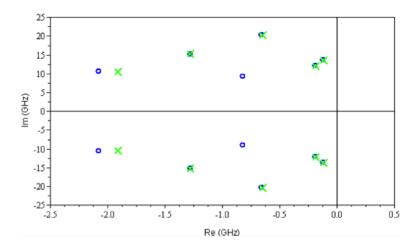

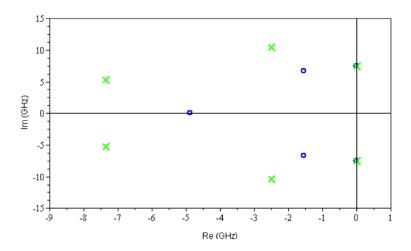

| 4.15 | Example of a Bilbao stability analysis                                                    | 114 |

| 4.16 | Bilbao stability analysis : DC to 10 GHz, pertubator at gate $\ \ldots \ \ldots$          | 114 |

| 4.17 | Bilbao stability analysis : 10 to 20 GHz, pertubator at drain $\ \ldots \ \ldots$         | 115 |

| 4.18 | Bilbao stability analysis : 5 to 10 GHz, pertubator at output $\ \ldots \ \ldots$         | 115 |

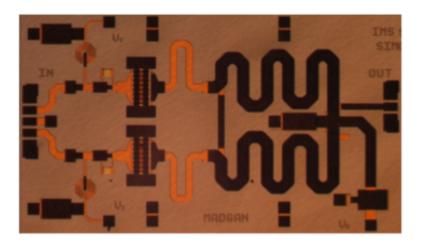

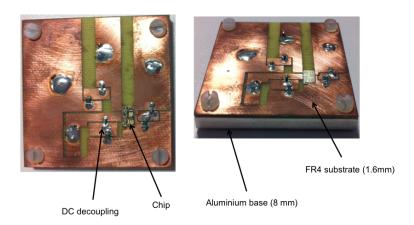

| 4.19 | Picture of the output stage standalone chip $\dots$                                       | 116 |

| 4.20 | Die reported on an aluminum substrate                                                     | 116 |

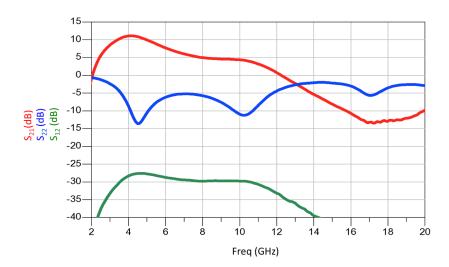

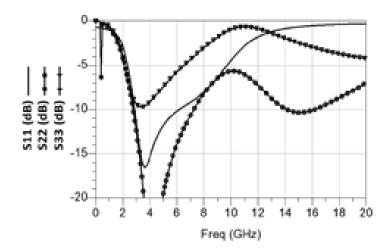

| 4.21 | Small signal measurements for the output stage                                            | 117 |

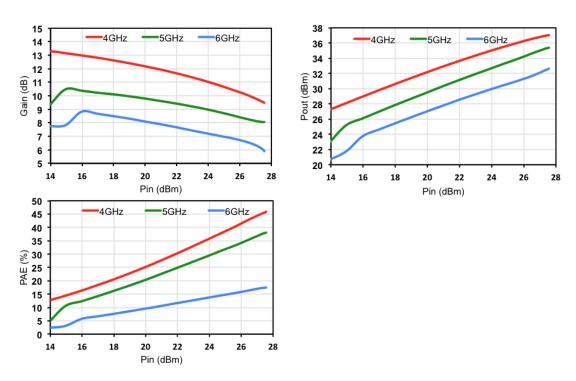

| 4.22 | Non linear measurements for the output stage at 4GHz, 5GHz and 6GHz: $$                   |     |

|      | Gain (top left), output power (top right) and PAE (bottom left) $\ \ldots \ \ldots$       | 118 |

| 4.23 | Non linear measurement and simulation results comparison $\ \ \ldots \ \ldots \ \ \ldots$ | 118 |

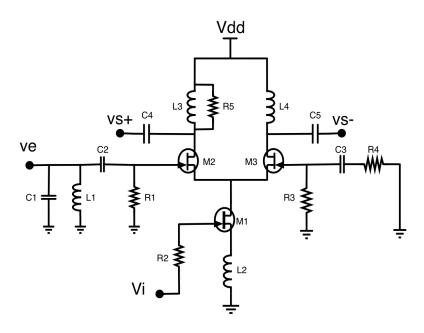

| 4.24 | Differential pair used as an active balun                                                 | 120 |

| 4.25 | Input and outputs matching                                                                | 121 |

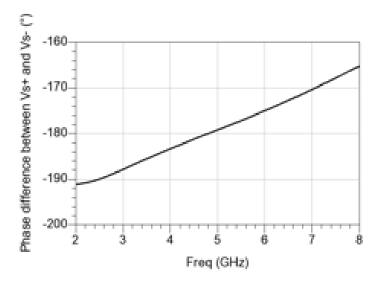

| 4.26 | Phase difference between the differential outputs $\dots \dots \dots$ .                   | 122 |

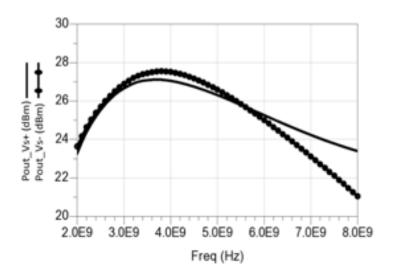

| 4.27 | Output power vs. frequency for each output path at $\mathrm{P}_{in}{=}20\mathrm{dBm}$     | 123 |

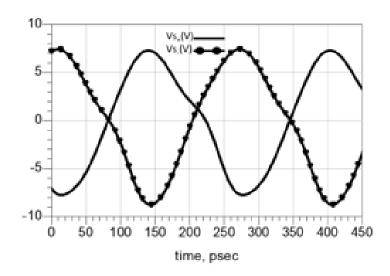

| 4.28 | Output voltage waveforms at $3.8 {\rm GHz}$                                               | 123 |

| 4.29 | Output power vs. input power at 3.8GHz                                                    | 124 |

| 4.30 | Active balun layout view                                                                  | 125 |

| 4.31 | Architecture proposed for the overall HPA                                                 | 126 |

| 4.32 | Full HPA small signal gain                                                                | 127 |

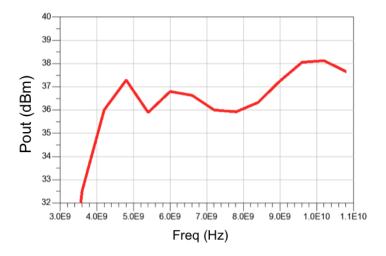

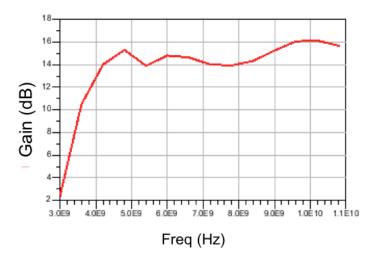

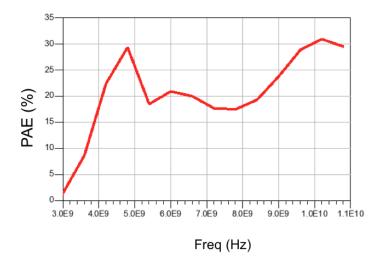

| 4.33 | Full HPA output power vs. frequency for $P_{in}$ =22dBm                                   | 128 |

| 4.34 | Full HPA gain vs. frequency for $P_{in}$ =22dBm                                           | 128 |

| 4.35 | Full HPA PAE vs. frequency for $P_{in}$ =22dBm                                            | 129 |

| 4.36 | Full HPA performances                                                                     | 130 |

| 4.37 | Differential TWA design methodology                                                       | 132 |

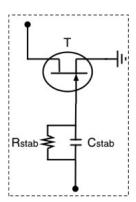

| 4.38 | Schematical representation of a TWA                                                       | 134 |

| 4.39 | Common source cell                                                                        | 135 |

|------|-------------------------------------------------------------------------------------------|-----|

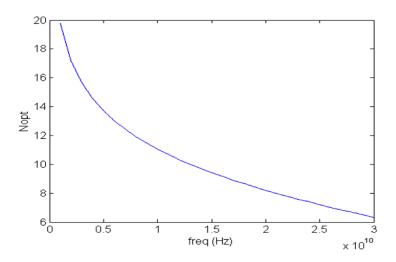

| 4.40 | Optimal number of cells vs. maximal frequency of operation                                | 135 |

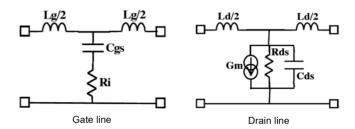

| 4.41 | Low pass filters introduced by cells connection                                           | 136 |

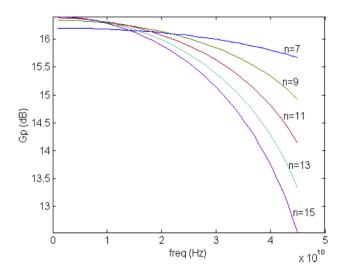

| 4.42 | Power gain vs. frequency for various number of cells                                      | 136 |

| 4.43 | Number of cells optimization in function of gain, output power and band-                  |     |

|      | width                                                                                     | 137 |

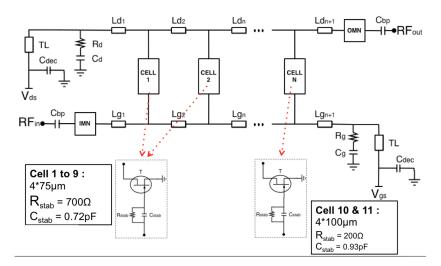

| 4.44 | Selected architecture for the single TWA                                                  | 138 |

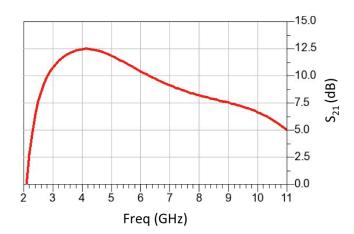

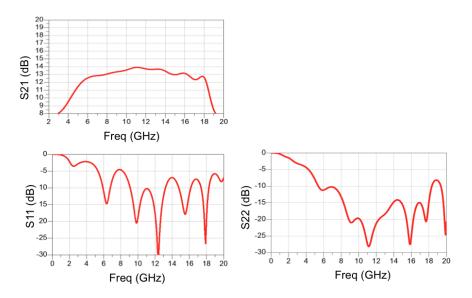

| 4.45 | Small signal simulation for the single TWA                                                | 139 |

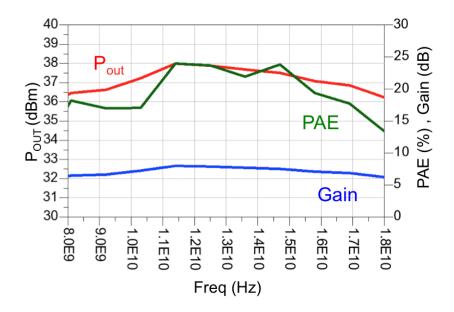

| 4.46 | Large signal simulation results for the single TWA at $\mathrm{P}_{in}{=}30\mathrm{dBm}~$ | 139 |

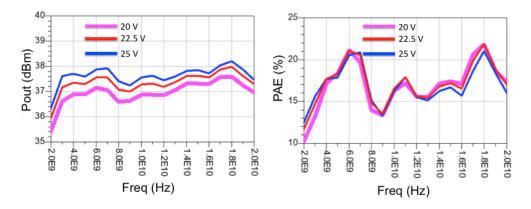

| 4.47 | Output power and PAE for various drain voltage                                            | 140 |

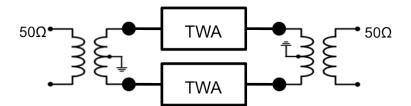

| 4.48 | Differential TWA representation                                                           | 140 |

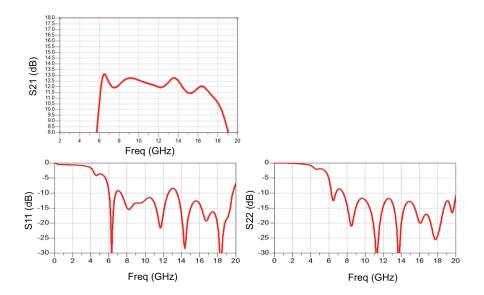

| 4.49 | Small signal simulation results the differential TWA                                      | 141 |

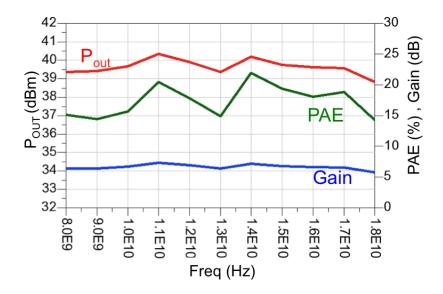

| 4.50 | Large signal simulation results for the single TWA at $\mathrm{P}_{in}{=}33\mathrm{dBm}$  | 142 |

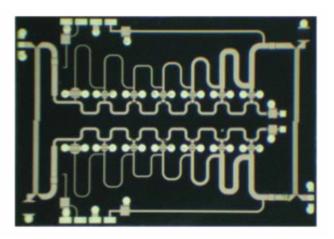

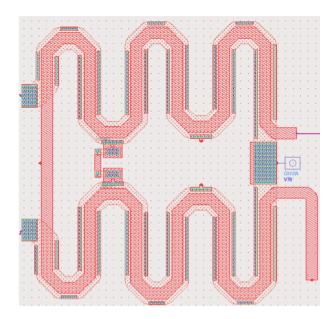

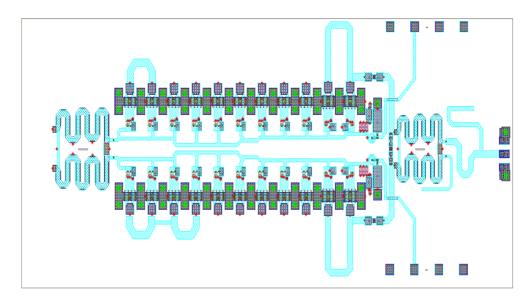

| 4.51 | TWA partial layout                                                                        | 143 |

| 4.52 | GaN TWA state of art                                                                      | 144 |

# List of Tables

| 2.1 | Frequency bands and military applications                      | 4   |

|-----|----------------------------------------------------------------|-----|

| 2.2 | Material Properties                                            | 8   |

| 2.3 | Amplifiers classes summary                                     | 32  |

| 2.4 | Wideband amplifiers comparison                                 | 38  |

| 2.5 | Wideband amplifiers comparison                                 | 42  |

| 2.6 | X-band high power amplifiers state of art                      | 46  |

| 2.7 | Wideband high power amplifiers state of art                    | 49  |

| 3.1 | Coupling factor vs. insertion loss                             | 67  |

| 3.2 | Ports configuration for insertion loss simulation              | 76  |

| 3.3 | Ports configuration for coupling factor extraction             | 77  |

| 3.4 | Quarter wave length upon frequency in GaN material             | 81  |

| 3.5 | Balun sizes for geometry optimizaton                           | 84  |

| 3.6 | Comparison between theoretical and simulated electrical length |     |

|     | (rectangular balun)                                            | 85  |

| 3.7 | X to Ku-band balun performances                                | 98  |

| 4.1 | C to X band HPA specifications                                 | 100 |

| 4.2 | X to $K_u$ band HPA specifications                             | 131 |

| 4.3 | Differential TWA performances                                  | 142 |

# LIST OF TABLES

# 1

# Introduction

In every day life, we are surrounded by wireless communicating devices everywhere. In the past decades, we have witnessed a tremendous growth in the overall wireless communications market. Together with this growth, major improvements and research progresses have made it possible for wireless devices to achieve impressive performances. For example, thanks to the 4G/LTE standard a customer can surf the web walking on the street on his mobile phone as fast as he would at home on his computer with a DSL internet connection. Achievements of this kind are now made possible by the improvements made in terms of radio-frequencies transmitters? and emitters? architectures and integrated circuits technologies too.

Historically, it all starts in in 1864 when James Clerk Maxwell proposed a theory that predicates the behavior of electromagnetic waves and their interactions with the matter, even though Hans Christian Orsted was the first person making a link between electricity and magnetism back in 1820. Then from the second half of the 19th century till the 1930's various kind of wireless communications appear such as telegraph, hertzian links or transatlantic links. However, next major improvements happened during World War II where techniques and devices such as radio jamming, encrypted communications, walkie-talkies and of course radars took birth. Since then, military applications and needs kept increasing and thus offering means and goals to research in terms of wireless communications.

The aim of this thesis is to develop innovative High Power Amplifiers (HPA) for military wireless communication systems. The Power Amplifier (PA) is the key component of any wireless (and even wired) transmitter. Indeed the main performances such

### 1. INTRODUCTION

as the range of action, the lifetime, the link speed and the quality of transmission are directly related to the PA performances. Basically, when designing an HPA dedicated to be implement in a transmitter of any kind, the following criteria are fundamentals:

• Output power: range of action

• Bandwidth: data rate

• Efficiency: life time and power management

• Size: ease of integration

• Linearity: quality of the link

The radars and electronic warfare applications targeted in this work do not demand strong requirements in terms of amplifiers linearity. Indeed while amplifier linearity is critical for most communication applications, they are strongly relaxed in these particular electronic warfare and radars applications. On the contrary highly non linear behavior is preferred most of time. On the contrary output power, bandwidth, efficiency and size are critical. Apparition of wide band gap devices about ten years ago has permitted to achieve output powers and efficiencies not even imaginable with any Silicon based technology. For example output power over 100Watts at 1GHz and over 20W at 10GHz have been reported with efficiencies around 50%.

In this work we focus on the design of wideband HPAs with high efficiency and small size.

In chapter 3, a presentation of the main military applications is made, then the basics and principles of power amplifier design are depicted. This chapter ends with a state of art of High power amplifiers.

Chapter 42 focuses on power combiners, it starts with theory on combiners before detailing the innovative power combiners realized and measured.

Finally, chapter 5 presents two different power amplifiers realized in this work, one working from C to X band and the other one from X to  $K_u$  band, they are both using the combiners introduced in the previous chapter.

# Bibliography and Context

# 2.1 Military applications

Even though it is not considered as a mass market as mobile phones or civilian wireless communications for example, the amount of funds and manpower involved to develop new solutions for military communications have reached a very high level. Indeed, it is a strategic matter for many countries to be at the state of art in terms of military applications and systems. It is a well known fact that a lot of innovations and new technologies have come from the military side. Constraints in terms of performances, reliability and robustness dictated by the harsh environment the systems have to deal with, result most of the time in systems and circuits that define a new state of the art.

Most of the applications are located in the DC to 40GHz frequency range. Table 2.1 summarizes these applications as a function of the frequency bands. From HF band to L band, the circuits are discrete most of the time. Due to the wavelengths corresponding to these frequencies, it would not be neither realistic nor viable to implement systems in any kind of integrated circuits. In fact, size of chips would be so large that among other things the cost of fabrication would not be affordable. Circuits working in S-band can be either integrated or discrete. Power levels of more than 1000W are often targeted for S-band radars for example and these levels can not be achieved in a chip so lots of discrete components are still out there to meet this kind of specifications.

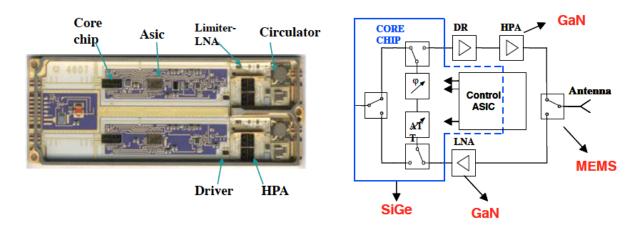

However, a solution into combining multiple MMICs on a printed board or module is more and more used, this is know as the hybrid approach. Fig 2.1 is an example of 300W

| Name    | Frequency (GHz) | Application                    |

|---------|-----------------|--------------------------------|

| HF      | 0.003 - 0.03    | OTH surveillance               |

| VHF     | 0.03 - 0.3      | Long-range surveillance        |

| UHF     | 0.3 - 1         | Long-range surveillance        |

| L-band  | 1 - 2           | Long-range surveillance        |

| S-band  | 2 - 4           | Moderate-range surveillance    |

| C-band  | 4 - 8           | Long-range tracking            |

| X-band  | 8 - 12          | Short-range tracking           |

| Ku-band | 12 -18          | High-resolution mapping        |

| K-band  | 18 - 27         | Police/traffic radar           |

| Ka-band | 27 - 40         | Police/high-resolution mapping |

Table 2.1: Frequency bands and military applications

Figure 2.1: Example of a 300W hybrid S-band power amplifier module -

power amplifier module operating from 2.7GHz to 2.9GHz developed by MACOM. It illustrates the principle: two MMICs (white blocks on the picture) are combined through a printed board to increase output power. To make thermal management better a metal base is attached to the bottom of the board, then the power dissipation area is larger than it would be in a single chip so heat is evacuated faster. This results in the module operating at lower ambient temperature which leads into improved performances and increased lifetime.

For C-band and beyond, full-MMICs solutions are very often the solution of choice for two main reasons. Firstly, required output powers are not as high as for S-band applications, they are in the 5W to 50W and this kind of power levels can be achieved in a single MMIC chip. Secondly, printed boards have significant loss at 4GHz and

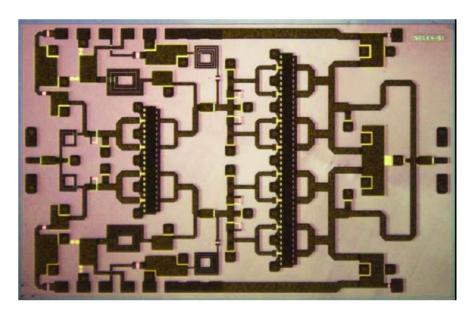

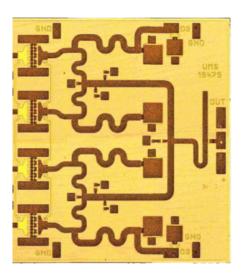

Figure 2.2: Example of a X-band full MMIC HPA -

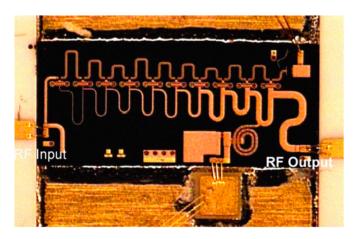

over, so in terms of performances and efficiency it is best for the RF signal to stay inside the chip as much as possible, that is why fully integrated circuits are preferred for C-band and over. Fig 2.2 is an example of an X-band HPA GaAs full MMIC from Triquint, it delivers 38dBm from 9GHz to 10GHz and occupies an area of 9.2mm<sup>2</sup>. It is a two stages high power amplifier using current combiners as splitter and combiner.

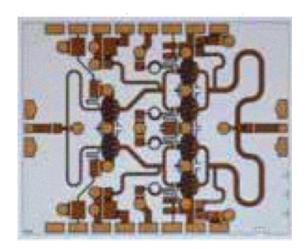

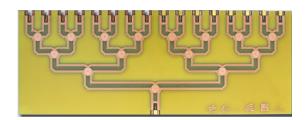

Figure 2.3: Example of C-band to Ku-band three stages MMIC HPA -

Another example of a full MMIC is presented in Fig 2.3. It is a GaN HPA operating from 6GHz to 18GHz delivering more than 6 W of output power with an efficiency going from 13% to 25% upon frequency. The die size is of 19.8mm<sup>2</sup> for this three stages amplifier. It has been implemented in the soon to be released UMS GH25 GaN process.

### 2. BIBLIOGRAPHY AND CONTEXT

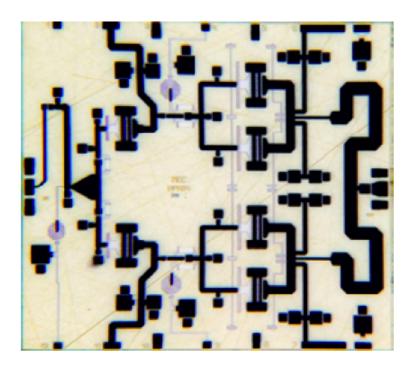

For most applications, MMICs are not meant to be used as standalone components but are dedicated to be integrated into systems to achieve complex functions. The idea is to integrate several MMICs together with low cost silicon ICs and even dies from other technologies sometimes to realize very specific functions. An example of a T/R module from THALES SA dedicated to X-band radar applications is shown in Fig 2.4. The core chip composed of variable gain amplifiers, delay blocks and phase shifters is fully integrated in a Silicon chip, so is the logic control for the overall module. The HPA for the TX path and the LNA for the RX path are both GaN MMICs while the antenna switch can either be a MEMS switch, a circulator or probably a GaN switch in the next future. All of these components are implemented in a single board and encapsulated to make a full T/R module dedicated to X-band radar applications.

Due to the power levels required, the bandwidth requirements and the robustness needed to comply with military applications, it is obvious that a low cost silicon technology like CMOS bulk for example is not going to be a good candidate. SiGe (Silicon Germanium based technologies) have shown drastic progress in terms of delivered power over the past few years but they have not quite reach high enough numbers in terms of power and efficiency yet. Moreover SiGe technologies suffer from their difficulties to evacuate heat. Wide bandgap based technologies have been the material of choice for many years in the military domain. Indeed, most of the chips dedicated to military applications are made in GaAs such as radar core chip and T/R module. However, recently a great interest has be shown for GaN devices who have the same advantages

Figure 2.4: Example of a full module based on MMIC's -

as GaAs ones compared to Silicon based devices but with a much higher power density and thermal conductivity.

## 2.2 GaN devices and technologies

### 2.2.1 Silicon and wide bandgap devices

The following parameters are a relevant background to compare each material advantages and disadvantages :

- Bandgap: defined as the energy level difference between the lower and the upper side of the valence band of a material. It corresponds to the amount of energy needed by an electron to climb from the valence band to the conduction band. It determines the maximal temperature of operation of the device. Moreover, the higher the bandgap is, the less sensible to radiations the component is going to be.

- Breakdown field: defined as the maximum voltage a device can handle (with regards to its size) a device can handle before deterioration. High breakdown voltage is directly to high output power because the component can be biased at an high DC value and important voltage swings can be applied to it.

- Electron mobility: an high electron mobility will result in less resistive losses and thus better performances in terms of gain.

- Thermal conductivity: defines the ability of a component to dissipate heat. High thermal conductivity results in a device operating at a lower temperature and thus having better performances. This number strongly affects the device efficiency.

In Table 2.2, these key parameters are compared for Si, GaAs and GaN material. Looking at the numbers, it appears that GaN as a bandgap three times bigger than Si and a breakdown voltage ten times bigger. Consequently, a GaN based device would be able to handle voltage swings ten times higher than Si and then obviously generate much more power. More power means more DC power consumption and thus more heat too, but thanks to its high bandgap value GaN material will operate at a lower

### 2. BIBLIOGRAPHY AND CONTEXT

temperature than a Si device so self heating is not going to be an issue. Silicon-Carbide (SiC) looks like a good candidate in terms of bandgap and breakdown field but it suffers from a low electron mobility. However, we will see in the following that its very high thermal conductivity makes it suitable for high temperatures operations.

| Property                     | Si   | GaAs | GaN         | 4H-SiC   |

|------------------------------|------|------|-------------|----------|

| Bandgap (eV)                 | 1.1  | 1.43 | 3.4         | 3.26     |

| Breakdown field $(V/\mu m)$  | 30   | 40   | 300         | 200< 300 |

| Electron mobility $(cm^2/s)$ | 1500 | 8500 | 1500 (2DEG) | 700      |

| Thermal conductivity (W/cmK) | 1.3  | 0.55 | > 1.5       | < 3.8    |

| Dielectric constant (Er)     | 11.7 | 12.9 | 9           | 9.7      |

Table 2.2: Material Properties

# 2.3 The HEMT GaN: a transistor dedicated to power applications

### 2.3.1 Transistor Basics

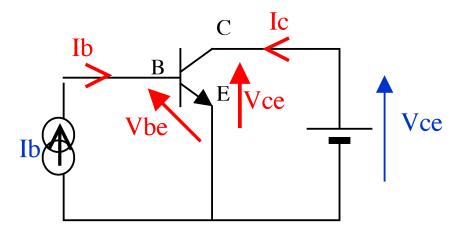

Historically the transistor was first invented at the Bell Laboratories in December 1947 by John Bardeen, Walter Houser Brattain and William Bradford Shockley, they received a nobel prize in 1956 for this discovery. Initially they tried to realize a field effect transistor (FET) as the one described by Julius Edgar Lilienfeld back in 1925 but they ended up discovering the phenomenon of current amplification which latter resulted in the heterojunction bipolar transistor (HBT). A transistor is a semi-conductor device with three terminals. It can either perform an amplifying function or a switch one (OFF or ON state). There are two different kinds of transistors, each having several variants. The first one is the HBT (Fig 2.5) which terminals are named, base, emitter and collector. Its behavior is mainly dictated by the current on its base, indeed current can flow between the collector and the emitter when the current applied on the base is high enough. The main parameter for this kind of transistor is its current gain  $\beta$  defined by :  $I_c = \beta I_b$ . HBT transistors behave very well in terms of noise at low frequencies and can achieve very high oscillating frequencies too. Moreover they can achieve very interesting power densities which make them suitable for many different applications.

On the down side, HBTs suffer from self heating effects as their current increase with temperature so techniques such has emitter degeneration have to be used.

Figure 2.5: Heterojunction bipolar transistor -

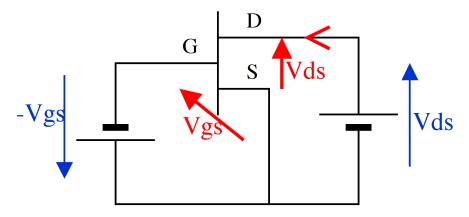

The other kind of transistor is the FET (Fig 2.6), its terminals are called gate, drain and source. The amount of current flowing from the drain to the source is dependent on the source voltage. The most relevant parameter for this type of transistor is its transconductance gm defined by:  $gm = I_d/V_{gs}$ . Due to its intrinsic characteristics, this kind of transistor is well suited to perform as a switch, in fact a low value on its gate would result in the transistor to behave as an open circuit (OFF state) while a high value on its gate would make it behave as a short circuit (ON state). If the switching speed is high enough, then this transistor can perform various digital functions such as logic gates or processors for example, that is the case of CMOS transistors which are the devices of choice when talking about very large scale integration at low cost.

FET based transistors can also be of great interest for high power applications such as the MESFET (Metal semi-conductor FET) for example or more recently the high electron mobility transistor (HEMT). HEMT transistors have been the transistors used to make all of the designs presented in this thesis, so a special and detailed focus on them is made in the following part.

Figure 2.6: Field effect transistor -

### 2.3.2 The GaN HEMT

### 2.3.2.1 History and principle

HEMT (High Electron Mobility Transistor) appeared in the 80's and have been introduced as unique microwave devices with the smallest noise characteristic existing worldwide. The HEMT is seen as major evolution of the MESFET transistor and has replaced it in many cases since the 90's. Since then, it never stopped developing and can now be found in lots of electronic devices among which cellular phones or cars for example.

Even though it appears to behave as any FET transistor because the current flowing from drain to source is depending on the voltage applied to the gate, the mechanisms involved are quite different. Indeed it is made of an heterojunction and a junction between two material with different forbidden energy gaps. From this heterojunction, the creation of a very thin undoped canal with a low resistivity appears which results in very high electron mobility. This layer called the two-dimensional electron gas is the consequence of both spontaneous and piezoelectric polarization. So the fundamental transistor effect is here obtained with the modulation of this two-dimension gas by the gate voltage while in a MESFET transistor the gate voltage dictates the width of the conduction canal between drain and source.

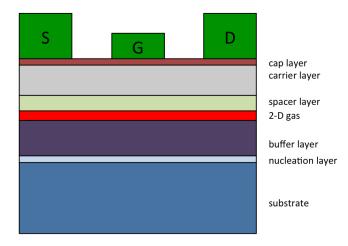

### 2.3.2.2 Physical structure

Fig 2.7 represents the section view of an AlGaN/GaN HEMT transistor similar to the ones used in this work. It represents the layers involved in the realization of such a transistor. This picture is not technology specific but intends to describe the general architecture of any AlGaN/GaN HEMT.

Figure 2.7: AlGaN/GaN HEMT cut view -

An HEMT transistor is composed of a substrate, a material with a large forbidden energy gap and another material with a smaller energy gap. As said earlier, it is the junction between these two materials that lead to the 2-D electron gas creation. An other important phenomenon is the presence of a Schottky junction between the gate metal layer and the substrate.

### 2. BIBLIOGRAPHY AND CONTEXT

Here is a description of the layers presented in Fig 2.7:

- Substrate: Due to their difficulty to manufacture and their high cost, GaN substrates are almost never used. 4H-SiC is a popular choice due to its good ability to dissipate heat and because it has the same crystalline network as GaN so they match easily. Diamond and Sapphire are best in terms of power dissipation but their cost prevent them to be used for mass market.

- Nucleation layer: Made of AlN, this layer prevents interfacial charges to happen for GaN on the SiC substrate.

- Buffer layer: This layer is made in a low forbidden energy gap material, GaN in our case. The 2-D gas appears in the upper side of this layer.

- Spacer layer: This layer is made of a larger forbidden energy gap material, AlGaN in this case. This non intentionally doped layer is only a few nanometers thick and permits to reduce the electrons-carriers interactions between the 2-D gas and the doped layer. The thicker this layer is, the fastest the electrons mobility is and the smallest the charger density is, and vice versa of course.

- Carrier layer: Made of large gap material such as doped AlGaN, this layer is a few nanometers thick and its aluminum concentration is around 20 to 30%.

- Cap layer: This is the upper layer and its goal is to produce good ohmic contacts for both drain and source.

### 2.3.2.3 Electrical characteristics

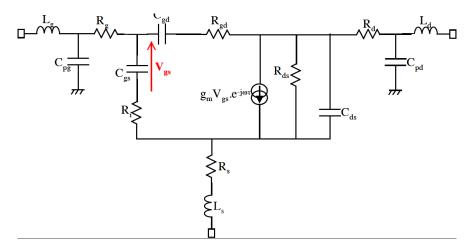

To design circuits with HEMT transistor, an electrical model is needed to perform simulations with CAD(Computer Aided Design) tools. Most of the time the small signal model is implemented with lumped elements such as the one presented in Fig 2.8. Basically, the transistor behavior is modeled by a voltage controlled current source.

These elements can be classified whether as intrinsic elements or extrinsic ones. Intrinsic elements are those inside the transistor which actually perform the transistor functions while extrinsic elements are the outside parasites such as the accesses. Both categories elements are listed and detailed in the following:

Let start with the intrinsic elements:

Figure 2.8: HEMT small signal electrical model -

• Current source: This is the main element describing the transistor effect. This current source is voltage controlled that models the phenomenon of gain inside the transistor. It is defined by:

$$I_{ds} = g_m v_{gs} e^- j^{\omega \tau}$$

(2.1)

$\tau$  models the delay due to the electrons transit time in the channel. The transconductance  $g_m$  is the fundamental transistor characteristic and represents the current variation modulated by the gate voltage, it is defined as:

$$g_m = \left. \frac{\partial I_{ds}}{\partial V_{gs}} \right|_{v_{ds} = v_{ds0}}$$

(2.2)

• Output conductances: It represents the current variation modulated by the drain voltage. It is a representation of the channel resistance ( $g_d=R_{ds}$ ) and is defined as:

$$g_d = \left. \frac{\partial I_{ds}}{\partial V_{ds}} \right|_{v_{gs} = v_{gs0}}$$

(2.3)

### 2. BIBLIOGRAPHY AND CONTEXT

• gate capacitances: The gate-source and gate-drain capacitances respectively  $C_{gs}$  and  $C_{ds}$  and illustrate the charge accumulation in the depopulated area located under the gate.  $C_{gs}$  models the variation of this charge accumulation modulated by the gate-source tension for a constant gate-drain tension and  $C_{ds}$  models this same variation modulated by the gate-drain tension for constant gate-source tension:

$$C_{gs} = \left. \frac{\partial Q_g}{\partial V_{gs}} \right|_{v_{qd} = v_{qd0}}$$

$$C_{gd} = \left. \frac{\partial Q_g}{\partial V_{gd}} \right|_{v_{gs}d = v_{gs0}}$$

(2.5)

- Drain-source capacitance:  $C_{ds}$  decries the capacitive coupling between the drain and source accesses.

- Resistances:  $R_i$  and  $R_{gd}$  model the fact that the channel is distributed.  $R_i$  is defined as the input resistance and permits to model the transistor input impedance while  $R_{gd}$  models the component feedback between input and output but is often neglected.

And now the extrinsic elements:

- Source resistance:  $R_s$  models the resistive apsect of the ohmic contact between the source electrode and the active area of the channel.

- **Drain resistance**:  $R_d$  models the resistive apsect of the ohmic contact between the drain electrode and the active area of the channel.

- Gate resistance:  $R_g$  represents the losses due to distributed effect along the gate electrode

- Gate access capacitances:  $C_{pg}$  and  $C_{pd}$  are the capacitances induced by the gate and drain accesses related to the substrate.

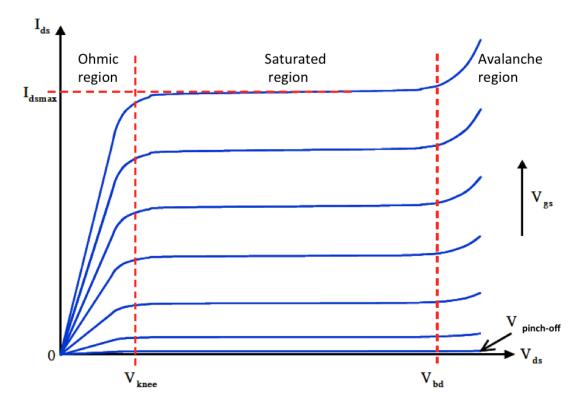

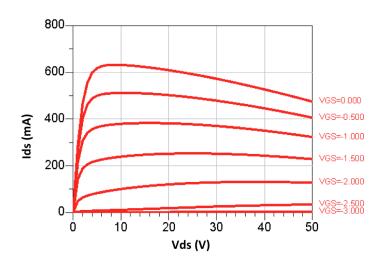

The most common and the easiest way to quantify an HEMT transistor behavior is through its  $I_{ds}$  versus both  $V_{ds}$  and  $V_{gs}$  charactherisitic. This plot is called the output static characteristic of the transistor. An example is presented in Fig 2.9. The drain source-current  $(I_{ds})$  is plotted versus the drain-source voltage  $(V_{ds})$  for various gate-source tensions  $(V_{gs})$ .

Figure 2.9: Output static characteristic of an HEMT transistor -

Four different regions or working modes can be discerned:

- Blocked region: Either or both  $V_{gs}$  and  $V_{ds}$  have values to low to activate the device so no current is flowing from drain to source. In this mode, the transistor ideally behave as an open circuit but in practical due to the parasitic elements it is approximated by a capacitance that grows with the transistor size. The transistor remains blocked while  $V_{gs}$  is lower than the transistor threshold voltage known as  $V_{th}$ .

- Ohmic region:  $I_{ds}$  increases linearly with  $V_{gs}$  and  $V_{ds}$ . In fact, with a  $V_{ds}$  increase the electrons mobility increases in the channel and the  $I_{ds}$  get

### 2. BIBLIOGRAPHY AND CONTEXT

larger. This region is called the ohmic one because the transistor behaves as resistor, indeed the current is proportional to a voltage. This region is limited by the point  $(V_{knee}, I_{dsmax})$ .

To ensure being in this mode of operation the following conditions have to be fulfilled:

$$v_{qs} = >v_{th}$$

and  $v_{ds} < (v_{qs} - v_{th})$

(2.6)

- saturated region: In this region reached at  $v_{ds}=v_{knee}$ , the electron mobility limit has been attained so the drain-source current for a specific  $v_{gs}$  value can not increase any more even if  $v_{ds}$  keeps being increased.  $I_{ds}$  is at its saturated value  $(I_{dSmax})$  hence the name of the region. The transistor ideally behaves as a current source because its current value is not affected by the voltage between drain and source. To ensure being in the saturated region, these conditions have to be respected:

$$v_{gs} = >v_{th}$$

and  $v_{ds}>(v_{gs}-v_{th})$

(2.7)

- avalanche region: When the field in the channel reaches its critical value, an avalanche phenomenon occurs. Electrons and holes are liberated more and more till a strong and fast increase of the drain-source current. This phenomenon is irreversible and results in the device destruction. This phenomenon happens when  $\mathbf{v}_{ds}$  reaches the transistor breakdown value known as  $\mathbf{V}_{bd}$ .

### 2.3.2.4 Figures of merit

To judge of a transistor performances and capacities three figures of merit have been defined, two of them are frequency related and the third one is noise related: - **cut off frequency**:  $f_t$  is the frequency at which the transistor current gain in short circuit is equal to the unity:

$$f_t = \frac{g_m}{2.\pi(c_{qs} + c_{qd})}$$

(2.8)

– maximal oscillating frequency:  $f_{max}$  is the frequency at which the matched transistor transductic gain is equal to the unity. If the assumption that  $(R_i C_{gd} \omega)^2 << 1$  is made then:

$$f_{max} = \frac{g_m}{4.\pi C_{gs}} \left(\frac{1}{R_i \cdot C_{gd}}\right)^{\frac{1}{2}} = \frac{f_t}{\left(4.R_i \cdot C_{gd}\right)^{\frac{1}{2}}}$$

(2.9)

noise factor: NF determines the noise generated by a device and is defined as:

$$NF = 2.\pi . C_{gs} (\frac{R_g + R_i}{C_{gm}})^{\frac{1}{2}}$$

# 2.4 Power Amplifier Design

### 2.4.1 Definitions

Let's start with a few definitions related to power amplifiers, they will be classified under the following categories: power, gain, efficiency and linearity.

### 2.4.1.1 Power

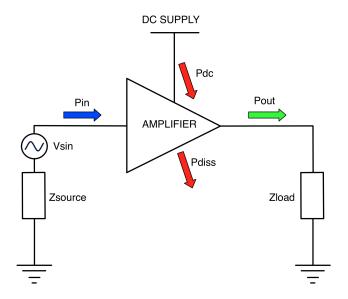

Fig 2.10 is an illustration of the input and output power paths in a generic amplifier.  $V_{sin}$  is assumed to be an RF source delivering a signal at a frequency  $f_0$ .

Figure 2.10: Power coming in and out an Amplifier -

According to physical law of conservation of energy, the total amount of energy getting in a physical device has to be strictly equal to the total amount of energy getting out this same device, then:

$$P_{in} + P_{dc} = P_{out} + P_{diss}$$

(2.11)

For a periodic signal of period  $T=1/f_0$ , the RF input power  $(P_{in})$  and the RF output power  $(P_{out})$  can be obtained with the following formula:

$$P = \frac{1}{T} \int_0^T v(t).i(t) dt$$

(2.12)

In the case of sinusoidal waves, the medium output power is defined by:

$$P_{out} = \mathbb{R}[\frac{1}{2}V_{out}.\overline{I_{out}}]$$

(2.13)

It is a common thing to model the output impedance by a purely resistive load  $R_L$ , in this case the output power can be expressed as:

$$P_{out} = \frac{V_{out}^2}{2.Z_{load}}$$

(2.14)

From Eq 2.14, we can notice that the output power is proportional to the square of the output voltage and that it decreases when the output load increases. We will comeback to this latter when talking about the advantages of wide bandgap devices for high output power applications. The amount of power delivered by the power supply is defined by:

$$P_{dc} = \frac{V_{dd}}{I_{dd}}$$

(2.15)

The amount of power which is not going out through the output load is dissipated through heat  $(P_{diss})$ . Low efficiencies amplifiers dissipate a lot of power through heat instead of delivering power the load. The official unit to express a power quantity is the Watt, however it is common to express it in dBm too. The conversion from one to an other is done with:

$$P[dBm] = 10log(1000.P[W])$$

(2.16)

### 2.4.1.2 Gain

When considering radio-frequencies circuits, the power gain is most of the time the one considered rather than the voltage gain. The traditional definition for the power gain is the transductic gain  $G_T$  that can be expressed by:

$$G_T = \frac{P_{out}}{P_{avail}}$$

(2.17)

#### 2. BIBLIOGRAPHY AND CONTEXT

where  $P_{out}$  stands for the output power delivered to the load and  $P_{avail}$  stands for the power available at the amplifier input.  $P_{avail}$  is equal to  $P_{in}$  defined earlier if and only if the source and the amplifier input are perfectly matched to each other, otherwise there are losses and  $P_{avail}$  is lower than  $P_{in}$ .

$$G_T[dB] = P_{out}[dBm] - P_{in}[dBm]$$

(2.18)

The power gain is maximal for low level input power, that is to say when all the devices making the amplifier are working in linear mode and not in saturation. The gain at saturation or the gain under compression are critical values too when considering an RF power amplifier. This gain is lower than the linear transductic gain  $(G_T)$  but is the one that matters when the amplifier is under conditions to deliver maximal power to the load (input power high enough).

#### 2.4.1.3 Efficiency

Efficiency is a critical criteria to judge the quality of a power amplifier. Indeed, it quantifies the ability to deliver power to a load while dissipating as less as possible through it. It specially matters in systems that are battery powered in order to increase lifetime or in embedded systems where heat dissipation can be an issue. There are, two main definitions to characterize an amplifier efficiency. The first one is called energetic efficiency and is defined as:

$$\eta = \frac{P_{out}}{P_{dc}}$$

(2.19)

This definition assumes that a power amplifier is actually a device that converts a DC energy into a RF energy. Thus,  $\eta$  is a number which quantifies the quality of the energy conversion. A value of 1 for  $\eta$  would mean that all the DC energy is converted into RF one, however due to the actives

devices parasitics and to the passive devices losses, this value can never be reached. A much more useful definition for power amplifiers is the Power Added Efficiency (PAE) which is expressed by:

$$PAE = \frac{P_{out} - P_{in}}{P_{dc}} = \eta (1 - \frac{1}{G_T})$$

(2.20)

The advantage of this definition is to combine both the energetic efficiency and the amplifier gain. In fact, high PAE are achieved with high gain  $(P_{out}-P_{in})$  and low DC consumption.

#### 2.4.1.4 Linearity

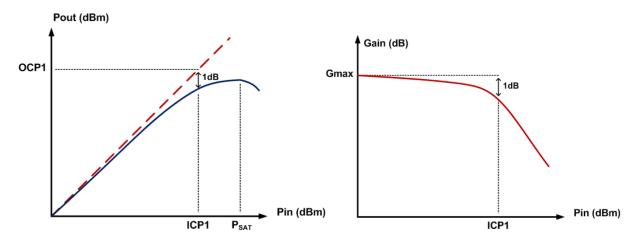

An amplifier is considered to be linear as long as the output signal follow a linear evolution compared to the input signal. This can be traduced by the fact that the amplifier keeps the same gain even if the input power is increasing. If it were the case, amplifiers could achieve an infinite output power, of course it does not work like that. Every amplifier has an output power limit and whatever is the input power the output power will never go beyond this limit. This limit is called the saturated output power. What actually happens is that when increasing the input power, the gain will start to slowly decrease and thus the amplifier will not have a linear behavior anymore. The amplifier is said to work in compression when its gain starts decreasing from its small signal value. The input and output power values for with the gain has decreased by 1dB are values used to characterize an amplifier. From this, we can define the three following parameters:

- \*  $\mathbf{P}_{sat}$ : Saturated output power. The maximal output power that can be reached by an amplifier regardless its input power.

- \* ICP1: Input compression point at 1dB. It is defined as the input power value for which the small-signal gain as decreased by 1dB.

- \* **OCP1**: Output compression point at 1dB. It is defined as the output power value for which the small-signal gain as decreased by 1dB.

If ICP1 and OCP1 are expressed in dBm and if  $G_T$  is expressed in dB then:

$$OCP1 = ICP1 + G_T - 1$$

(2.21)

Fig 2.11 is a graphical representation of the compression phenomenon. The left plots represents the output power versus the input power and we can notice that the evolution stops being linear at some point and the output power ultimately stops increasing at all to reach its saturated value. On the right plot, we can see that the gain decreases slowly while the input power increases till it reaches the 1dB compression point and then it drastically drops all the way down.

Figure 2.11: 1dB input and output compression point -

#### 2.4.2 Power Amplifier Basics

The study of a PA can either be done in linear mode of operation or large signal (non-linear) one. There are several parameters for each case which determine the performances of a PA. Most of the time, PA design is a combination of both linear and large signal behavior because most applications require specifications for each. A PA is considered to work in linear mode of operation whenever its input signal is small enough that it will not put

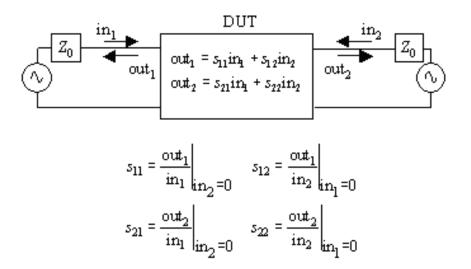

any active devices in saturation. One way to describe the linear behavior of a system is the use of scattering parameters (S-parameters). This approach is very popular especially for PA working at RF frequencies and beyond. It has the advantages to give many informations over a single analysis (whether it is simulation or measurement). Indeed, information such as input and output matching, gain and stability can be extracted directly from an S-parameter analysis. The principle of such an analysis is illustrated in Fig 2.12 for a 2 ports device. The amplifier is considered as a black box with a main input (in<sub>1</sub>) on the left side and a main output (out<sub>2</sub>) on the right side, an alternate output (out<sub>1</sub>) and an alternate input (in<sub>2</sub>) are also present to model reflection phenomenons.

Figure 2.12: Scattering Parameters principle -

The analysis technique consists in exciting alternatively each input and quantifying the amount of signal that is transmitted through the device and the amount reflected back to the excited input. Performing this analysis at each input results in the obtention of a scattering matrix composed of the following four parameters:

\*  $\mathbf{S}_{11}$ : Input reflection coefficient. Amount of the signal when excited through in<sub>1</sub> that does not go through the device but that is reflected back to the source through out<sub>1</sub>. This parameter gives information on

#### 2. BIBLIOGRAPHY AND CONTEXT

the input matching, an ideal PA would have  $S_{11}$  equal to 0, meaning that the signal applied through in 1 fully carries through the amplifier and none is sent back to the source.

- \* S<sub>22</sub>: Input reflection coefficient. Amount of the signal when excited through in<sub>2</sub> that does not go through the device but that is reflected back to the source through out<sub>2</sub>. This parameter gives information on the output matching, an ideal PA would have S<sub>22</sub> equal to 0.

- \*  $S_{21}$ : Transmission coefficient. Amount of the signal when excited through in<sub>1</sub> that goes through the device and that is outputted through out<sub>2</sub>. Also known as the device gain, it gives information on how much the device amplifies the input signal, the greater  $S_{21}$  is, the more gain an amplifier has.

- \* S<sub>12</sub>: Isolation coefficient. Amount of the signal when excited through in<sub>2</sub> that goes through the device and that is outputted through out<sub>1</sub>. This parameter gives information on the device stability, an ideally stable amplifier would have S<sub>12</sub> equal to 0, meaning that any signal sent through out<sub>2</sub> can not go all the way back to in<sub>1</sub>.

Most of the time,  $S_{21}$  and  $S_{12}$  parameters are expressed in dB and plotted versus frequency over a linear scale. A value of 0dB corresponds of a magnitude of 1, for example a device  $S_{21}$  equal to 0dB will output an exact copy of the input signal in terms of shape and amplitude. If  $S_{21}$  is negative in dB then the output signal will have a lower amplitude than the input one and if  $S_{21}$  is positive, then the amplitude of the output signal is going to be greater than the the input one and in this case we can talk about signal amplification. The reflection coefficients  $S_{11}$  and  $S_{22}$  can be expressed in dB versus frequency too but then it only gives information about the magnitude. It is commonly admitted for a power amplifier that  $S_{11}$  and  $S_{22}$  have to be lower than -10dB to ensure proper matching, it corresponds to no more than 10% of the signal being reflected to the source (or the load). To obtain informations about both magnitude and phase, reflections parameters can be plotted on a Smith Chart too. This visualization method is oftener used for impedance matching and to design matching networks.

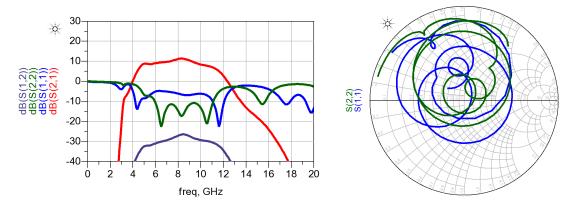

An example of S-parameters plot is presented in Fig 2.13 for both a linear representation and a Smith Chart representation.

Figure 2.13: Example of S-parameters plots (linear and Smith chart) -

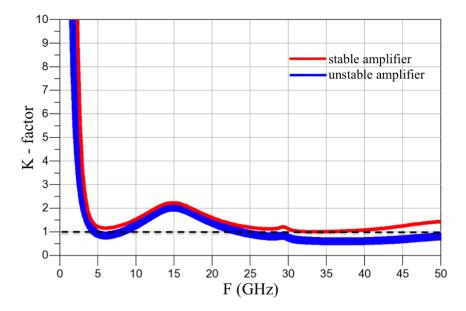

From an S-parameters analysis, information on linear stability can be extracted too. For any amplifier, stability is critical criterion to ensure. Indeed, an unstable amplifier is very likely to oscillate and thus not to behave as expected. To avoid this behavior, the amplifier must be unconditionally stable for every frequencies, unconditionally meaning for every impedances within the smith chart. A criteria to ensure unconditional stability has been proposed by John Rollet, it is called the Rollet's stability factor, but it is commonly called K-factor.

$$k = \frac{1 - |S_{11}|^2 - |S_{22}|^2 - |\Delta|^2}{2|S_{21}S_{12}|}$$

$$\Delta = S_{11}S_{22} - S_{12}S_{21}$$

(2.22)

This factor is calculated from S-parameters and is defined by Eq 2.22. Unconditional stability is theoretically ensured while K-factor remains over the unity. However, the K-factor is only relevant for a one stage amplifier. Indeed for a two (or more) stages amplifier, a value of k over one is not enough to ensure stability. It is preferable to consider the Rollet's stability factor as an informative parameter better than anything else. Let say that an amplifier with K-factor under one is unstable for sure and that an amplifier with K-factor greater than one as a chance to be stable. In Fig 2.14,

Figure 2.14: Stable amplifier vs. unstable amplifier -

the example of a stable amplifier and an unstable one is illustrated. The red plot corresponds to stable one where K remains over one from DC to 50GHz while the blue plot goes under one multiple times which correspond to an unstable and potentially oscillating amplifier.

Besides the Rollet factor, an other criteria know as the  $\mu$ -factor can be used as a proof of unconditional stability. The  $\mu$ -factor is defined in Eq 2.23, unconditional stability is ensured if  $\mu$  is greater than one. This formula applies for any two port devices wether it is single or multi stage, so a more valuable information can be extracted from the  $\mu$ -factor than from the k-factor. In practical, it is mandatory to check both factors and ensure they are greater than one.

$$\mu = \frac{1 - |S_{11}|^2}{|S_{22} - \overline{S_{11}}\Delta| + |S_{12}S_{21}|}$$

$$\Delta = S_{11}S_{22} - S_{12}S_{21}$$

(2.23)

#### 2.4.2.1 Power Amplifier Classes

Power Amplifiers are commonly designated by their classes. The class of operation an amplifier refers to both its bias point and to output voltage and current waveform shapes. Depending on the class, the amplifier will exhibits better performances either in terms of linearity or in terms of efficiency, the choice being mainly commanded by the application targeted. Amplifier classes can be separated into two main categories: sinusoidal classes and non-sinusoidal ones. It is important to notice than GaN based technologies do not offer complimentary transistors (as p-mos in cmos technologies for example), thus topologies and classes are limited.

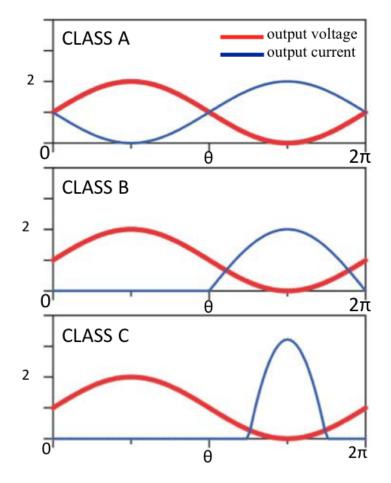

Class A, B and C are known as the sinusoidal ones because the output voltage wave as a sinus shape, here is a description for each of these classes:

- \* Class A: The amplifier is biased at a DC value equal to half the saturation current, meaning that it conducts at all time for both the positive and the negative half of the input wave. It is the best class in terms of linearity but the worst in terms of efficiency as transistors never switch of and thus always draw current even when there is no input signal.

- \* Class B: The amplifier is biased at a DC value precisely equals to the transistor threshold voltage, thus there is conduction only half of the time when the input signal is positive and the transistor remains off when the input is signal is negative. The efficiency is better than for class A amplifiers but the linearity is degraded. A push-pull configuration can be used to improve linearity, where a n-type transistor will take care of the positive half of the signal and an p-type one handles the negative side.

- \* Class C: The amplifier is biased at DC value lower than the threshold voltage so conduction happens only when the input signal is high enough, current is drawn less than half of the time. The efficiency is increased compared to a class B amplifier but the linearity is even more decreased.

Fig 2.15 is the representation of the output waveforms (both current and voltage) for the A, B and C classes. Voltage and current are both normalized, a value of one corresponding to quiescent voltage and current. We can notice that current is drawn at all time for class A, half of the time for class B and less than half of the time for class C.

Figure 2.15: Sinusoidal amplifier classes -

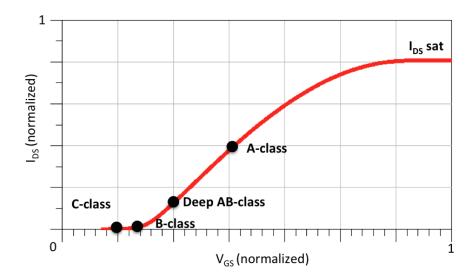

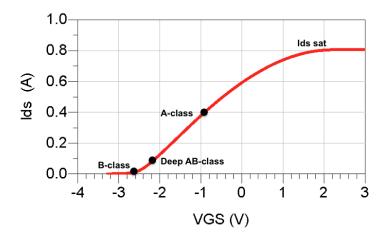

It is possible bias the amplifier at a point located somewhere between class A and class B, this is a called deep AB class. It consists in biasing transistors at 10 to 20 % of their saturated drain current, it has the advantage of drastically improving the efficiency when compared to class A operation and have an interesting behavior in terms of output power. Of course, linearity is strongly degraded but this is not a problem for applications

Figure 2.16: Amplifier classes vs. bias point -

such as military one where linearity is not required. Most of the amplifiers realized in this thesis have been biased in deep AB class at 10% of their saturated drain current.

In Fig 2.16, classes of representation are placed on a  $I_{DS}(V_{gs})$  plot. As expected, class A corresponds to a quiescent current equal to half of  $I_{Dsat}$ , class B is set exactly at the threshold voltage and deep AB class is somewhere in the 10 to 20% of  $I_{Dsat}$  region.

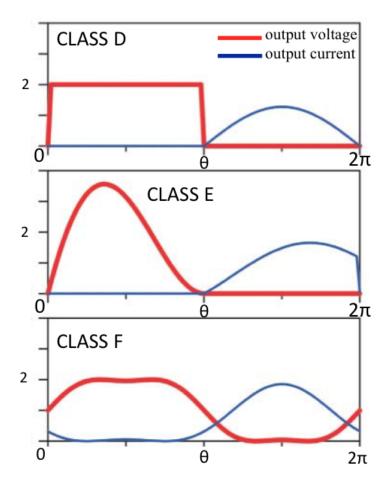

The non sinusoidal classes are based on making the active device work as a switch, that is to say being either in off-state or in saturated mode of operation. Ideally, in this kind of behavior either the current or the voltage is equal to zero, so the efficiency is maximal. However, transistors are not perfect, in fact they have parasitic impedances and capacitances so there is a non negligible amount of time where current and voltages are both non equal to zero. Moreover, these non sinusoidal classes often use impedance harmonic tuning for wave forming matters, which make them non suitable for wideband applications. The more common classes, D, E and F are depicted in the following:

\* Class D: Class-D amplifiers use two or more transistors (in pushpull like configuration) as switches to generate a square drain-voltage

#### 2. BIBLIOGRAPHY AND CONTEXT

waveform. A series-tuned output filter passes only the fundamental-frequency component to the load. Current is drawn only through the transistor that is on, resulting in a 100% theoretical efficiency for an ideal amplifier. However parasitics detailed before and non-zero switching time of transistors quite decrease this theoretical value.

- \* Class E: Class E employs a single transistor operated as a switch. The drain voltage waveform is the result of the sum of the DC and RF currents charging the drain-shunt capacitance. In optimum class E, the drain voltage drops to zero and has zero slope just as the transistor turns on.

- \* Class F: Class F boosts both efficiency and output by using harmonic resonators in the output network to shape the drain waveforms. The voltage waveform includes one or more odd harmonics and approximates a square wave, while the current includes even harmonics and approximates a half sine wave.

As for the sinusoidal classes, a normalized representation of the output waveforms is represented in Fig 2.17 for each of the D, E and F classes. It can be noticed that there is no overlapping between voltage and current waves.

Over the past years, new classes have been introduced but they more an improvement of already existing classes than whole new classes. For example, a class S amplifier is actually a class D amplifier which converts analog signals into digital pulses thanks to a delta-sigma modulator. An other one is class J, which actually consists in biasing the amplifier in deep AB class and presenting specific impedances to the harmonics in order to improve efficiency. Table 2.3 summarizes for all the classes depicted earlier the conduction angle (equivalent to time the transistor conducts over a period) and the theoretical efficiency for and ideal amplifier. To conclude, when linearity is critical class A should be privileged at the cost of efficiency. Non sinusoidal classes are of great interest to achieve very high efficiencies but their linearity is very poor and the harmonic impedance tuning techniques deployed prevent them to be implemented on wideband amplifiers. Thus,

Figure 2.17: Non Sinusoidal amplifier classes -

the AB class appears to be a good compromise between efficiency, power and wideband capabilities.

# 2.4.3 Amplifiers Topologies

Even though, there is an important amount of topologies from the most basic one to very exotic and unusual approaches, power amplifiers architectures can be classified in two main categories: single ended or balanced/differential. To increase performances such as gain or output power, it is common to cascade or parallelize several elementary cells. In the following a description of each approach is given together with some examples to illustrate them.

| Class      | Conduction Angle | Maximal Theoritical Efficiency |

|------------|------------------|--------------------------------|

| A          | 360°             | 50%                            |

| AB         | 180°to 360°      | 50% to 78.5%                   |

| В          | 180°             | 78.5%                          |

| С          | <180°            | 100%                           |

| D and over | ON/OFF switching | 100%                           |

Table 2.3: Amplifiers classes summary

# 2.4.3.1 Single-ended topologies

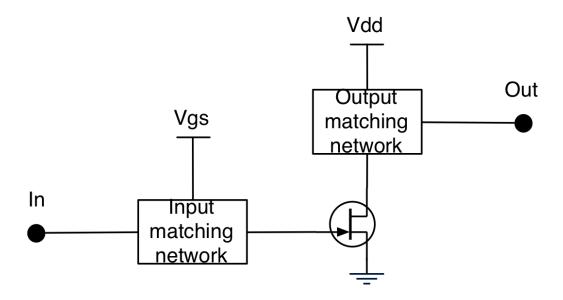

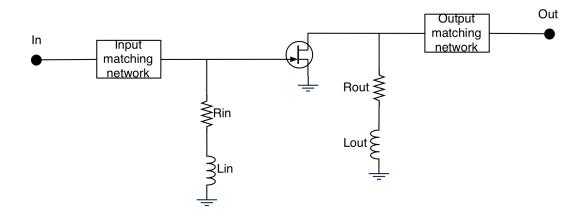

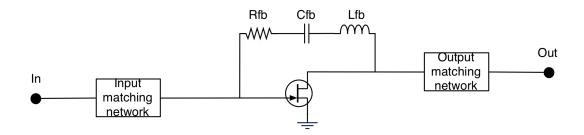

The single-ended approach basically consists in having one input and one output without any combining devices. The most simple structure is based on a single transistor and is called common-source architecture (Fig 2.18). The transistor gate acts as the RF input, the drain is the RF output and the source is grounded hence the common-source determination. Matching networks are placed at the gate and the drain for the amplifier to work at the desired frequency.

Figure 2.18: Common-source power amplifier -

This topology is pretty simple to implement and offers good performances in

terms of gain and frequency, however it suffers from a poor isolation making it though to optimize and easily unstable specially at low frequencies where the transistor has an important intrinsic gain. However, this low frequency stability issue can be fixed by placing an high pass filter on the transistor gate in order to decrease gain at low frequencies while not modifying at higher frequencies. Other variants based on a single transistor exist like the common-gate (gate grounded) or the common-drain (drain grounded) but they do not perform as well as the common source method so they are not used very much as power amplifier elementary cells.

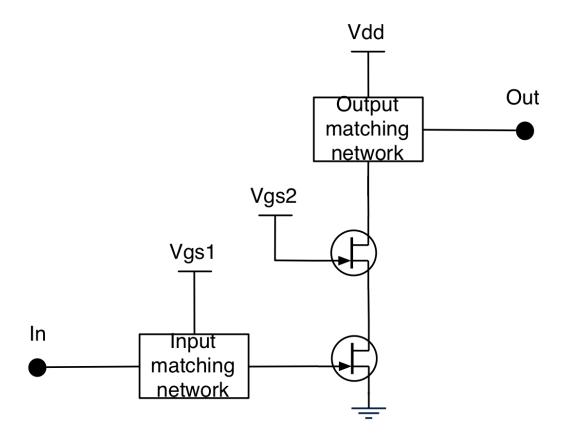

To improve the isolation and the power ability of a common source amplifier, an interesting approach is the cascode one (Fig 2.18). It consists in inserting a common-gate transistor on top of a common-source one. Indeed, the input and the output are now separated by two transistors instead of one which makes the isolation much higher. Moreover, by having two transistors in cascade, the supply voltage can be increased by a factor of two which results in a drastic increase regarding the output power.

However, cascode amplifiers can be though to stabilize, even impossible under certain conditions. An other issue is the connection between common-source drain and the common-gate source. Indeed, physically this connection is a transmission line which acts as low pass filter together with both transistors parasitic capacitances and this results in a decreased maximal frequency of operation.

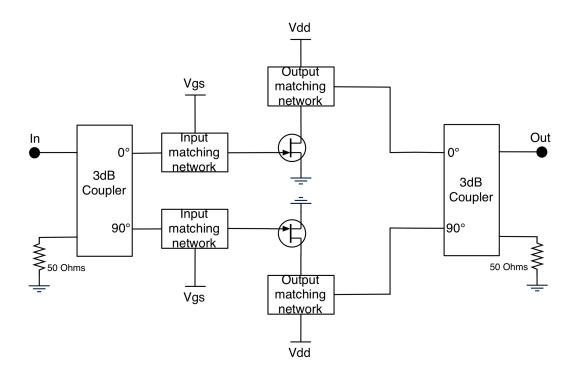

# 2.4.3.2 Balanced / Differential topologies

Balanced and differential topologies consist in combining or parallelizing several single-ended elementary cells such as common-source or cascades ones. The main advantage is the increase in terms of output power( two cells parallelized would deliver the amount of power as a single cell) with no costs on the gain but the main drawback is the need for splitters and combiners to make the cells work together. Combiners have losses that would affect the overall performances and they can fulfill a large die area which affects the cost of the overall amplifier.

Figure 2.19: Cascode power amplifier -

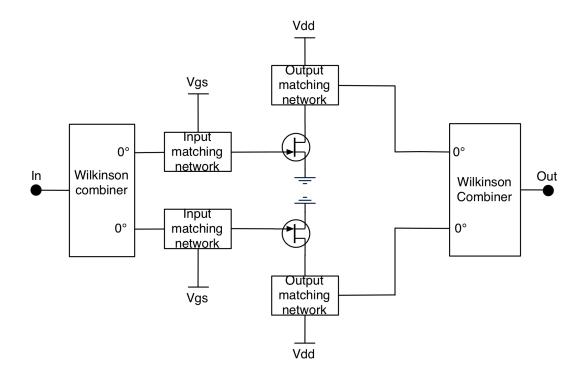

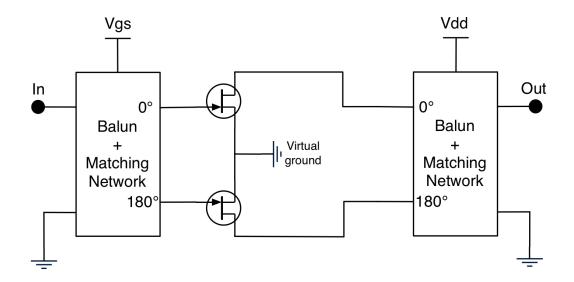

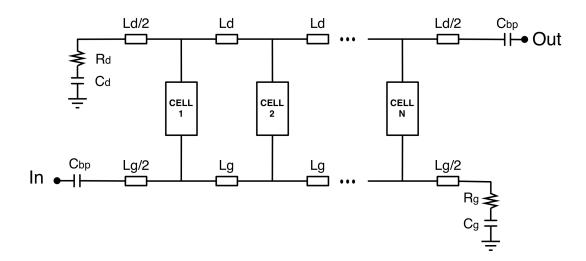

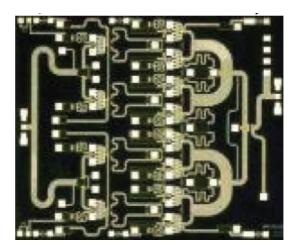

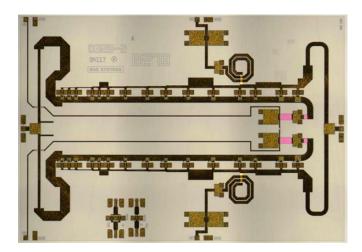

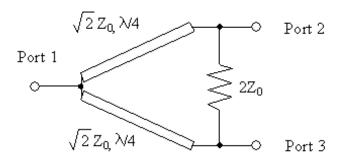

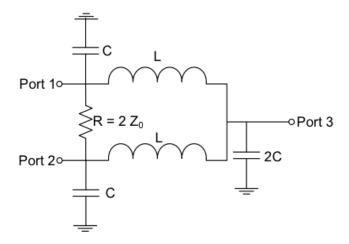

The easiest way to implement such an amplifier is the current combining approach Fig 2.20). Two elementary identical cells are parallelized and combined in phase. This combination can be easily done with a current splitter/combiner such has a wilkinson one, which is only composed of transmission lines and a resistor to ensure isolation between the two paths.

This approach benefits from the wilkinson combiner advantages which are the ease of design and the low loss abilities, so very good results in terms of output power and efficiency are usually obtained. However, these kind of combiners are based on transmission lines whom length need to be equal to  $\lambda/4$  of the working frequency . This results in very large size combiners and limited bandwidths. Even though, the combiner can be improved in terms of bandwidth by adding parallel elements to it at specific places,

Figure 2.20: Current combined power amplifier -

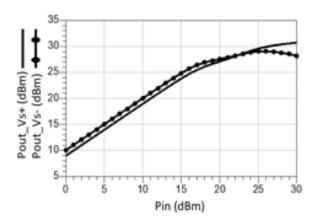

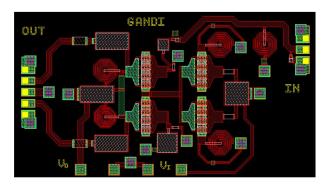

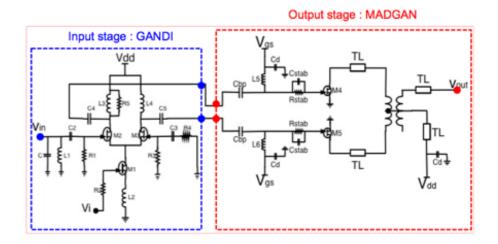

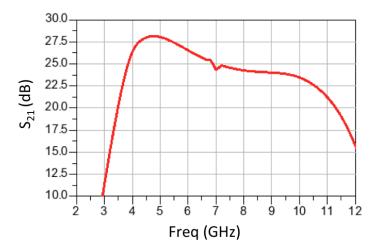

its size remains a critical issue. Moreover, an exact symmetry has to be respected in between the different paths or the cells are going to be imbalanced which would result in poor performances in the best case and the amplifier destruction in the worst case.