# Runtime enforcement of timed properties

Srinivas Pinisetty

#### ▶ To cite this version:

Srinivas Pinisetty. Runtime enforcement of timed properties. Automatic Control Engineering. Université de Rennes, 2015. English. NNT: 2015REN1S004. tel-01185842

### HAL Id: tel-01185842 https://theses.hal.science/tel-01185842

Submitted on 21 Aug 2015

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

Nº d'ordre : ANNÉE 2015

#### **THÈSE / UNIVERSITÉ DE RENNES 1**

sous le sceau de l'Université Européenne de Bretagne

pour le grade de

#### **DOCTEUR DE L'UNIVERSITÉ DE RENNES 1**

Mention : Informatique

École doctorale MATISSE

présentée par

# Srinivas PINISETTY

préparée à l'unité de recherche IRISA-INRIA: UMR 6074 Institut de recherche en informatique et système aléatoires ISTIC

Enforcement à

l'exécution de

propriétés temporisées

Thèse soutenue à Rennes le 23 janvier 2015

devant le jury composé de :

**Martin LEUCKER**

Professor, Université de Lübeck / Rapporteur

**Didier LIME**

HDR, Maître de Conférences, École Centrale de Nantes / Rapporteur

Sophie PINCHINAT

Professeure à Université de Rennes 1 / Examinatrice

Frédéric HERBRETEAU

Maître de conférence, ENSEIRB Bordeaux / Examinateur

Yliès FALCONE

Maître de conférence à Université de Grenoble 1 / Invité

Thierry JÉRON

Directeur de recherche à l'INRIA Rennes-Bretagne Atlantique / Directeur de thèse

Hervé Marchand

Chargé de recherche à l'INRIA Rennes-Bretagne Atlantique / Co-directeur de thèse

# Runtime Enforcement of Timed Properties

# Acknowledgements

This thesis has been influenced by many people, and I would like to thank all of them. Firstly, I must thank my supervisors Thierry Jéron, Hervé Marchand, and Yliès Falcone for offering me a PhD position, providing a very encouraging research environment, and accompanying me in every step of this long journey. In spite of their busy schedules, they always gave me time to discuss, to answer my questions, and attended to my concerns from day one. Discussions with them was always a pleasure given their passion for research, immense knowledge, experience, enthusiasm, and patience. I had learnt a lot from them during these years, and could not have imagined having better advisors for my PhD study.

I should also thank Yliès Falcone for visiting us several times, and also for inviting me a couple of times to his lab to conduct this research work. During my PhD, I also had a chance to work with Antoine Rollet and Omer Nguena Timo. I thank them for collaborating and their contributions in this work.

Further, I thank other members of the thesis examining committee: Didier Lime, Martin Leucker, Sophie Pinchinat, and Frédéric Herbreteau. It is a honour for me that you dedicated your time to read my thesis, and to attend my thesis defense. Reporters Didier Lime, and Martin Leucker provided detailed feedback on my thesis, and improved the quality of my thesis.

I also thank all the VERTECS and SUMO team members for supporting me and providing necessary information and help, for any issue I had (related to work or others) during my stay in Rennes. I thank my friends Yogesh, Raghu ram, Sharat, Akshay, Ajay, Mani, Hrishikesh, Aswin, Deepak, all my other friends, and team members at INRIA in Rennes for making these years of PhD study a memorable one.

I should also thank all my friends, and teachers who always encouraged me and provided valuable advices when I needed. I thank my wife for being with me during last months of my PhD study, and for understanding, supporting and encouraging me. Finally, very special thanks to my parents, sister and family for always believing in me and for standing by me throughout the course of my study.

| 1 | $\mathbf{R\acute{e}s}$ | sumé en Français                                               | 5  |  |  |

|---|------------------------|----------------------------------------------------------------|----|--|--|

|   | 1.1                    | Contexte                                                       | 6  |  |  |

|   | 1.2                    | Résumé de l'approche                                           | 9  |  |  |

|   | 1.3                    | Résultats                                                      | 10 |  |  |

| 2 | Inti                   | roduction                                                      | 13 |  |  |

|   | 2.1                    | Motivations for Runtime Enforcement                            | 13 |  |  |

|   | 2.2                    | Problem Statement                                              | 14 |  |  |

|   | 2.3                    | Contributions                                                  | 15 |  |  |

|   | 2.4                    | Outline                                                        | 18 |  |  |

| 3 | Sta                    | te of the Art                                                  | 21 |  |  |

|   | 3.1                    | Checking Correctness of a System                               | 21 |  |  |

|   | 3.2                    | Formal Verification Techniques                                 | 22 |  |  |

|   |                        | 3.2.1 Static verification techniques                           | 22 |  |  |

|   |                        | 3.2.1.1 Model checking                                         | 22 |  |  |

|   |                        | 3.2.1.2 Static analysis                                        | 23 |  |  |

|   |                        | 3.2.1.3 Theorem proving                                        | 24 |  |  |

|   |                        | 3.2.2 Dynamic verification techniques                          | 24 |  |  |

|   |                        | 3.2.2.1 Testing using formal methods                           | 24 |  |  |

|   |                        | 3.2.2.2 Runtime verification                                   | 25 |  |  |

|   | 3.3                    | Correcting Execution of a System at Runtime                    | 27 |  |  |

|   |                        | 3.3.1 Runtime enforcement of untimed properties                | 28 |  |  |

|   |                        | 3.3.2 Runtime enforcement of timed properties                  | 29 |  |  |

|   |                        | 3.3.3 Handling parametric specifications in runtime monitoring | 30 |  |  |

|   | 3.4                    | Summary                                                        | 30 |  |  |

| 4 | Not                    | tations and Background                                         | 31 |  |  |

|   | 4.1                    | Timed Systems, and Requirements with Time Constraints          | 31 |  |  |

|   | 4.2                    | Preliminaries and Notations                                    |    |  |  |

|   |                        | 4.2.1 Untimed languages                                        | 33 |  |  |

|   |                        | 4.2.2 Timed words and languages                                | 33 |  |  |

|   | 4.3                    | Timed Automata                                                 | 34 |  |  |

|   |                        | 4.3.1 Syntax and semantics                                     | 35 |  |  |

|   |     | 4.3.2   | Partition of states of timed automata                           | 38         |

|---|-----|---------|-----------------------------------------------------------------|------------|

|   |     | 4.3.3   | Classification of timed properties                              | 38         |

|   |     | 4.3.4   | Defining timed properties as timed automata                     | 39         |

|   |     | 4.3.5   | Combining properties using boolean operations                   | 40         |

|   |     | 4.3.6   | Verification of timed automata                                  | 42         |

|   | 4.4 | Summa   | ary                                                             | <b>4</b> 4 |

| 5 | Rui |         | Inforcement of Timed Properties                                 | 45         |

|   | 5.1 | Genera  | al Principles and Motivating Examples                           | 45         |

|   |     | 5.1.1   | General principles of enforcement monitoring in a timed context | 45         |

|   |     | 5.1.2   | Some motivating examples                                        | 47         |

|   | 5.2 | Prelim  | inaries to Runtime Enforcement                                  | 50         |

|   | 5.3 | Enforc  | ement Monitoring in a Timed Context                             | 51         |

|   |     | 5.3.1   | General principles                                              | 52         |

|   |     | 5.3.2   | Constraints on an enforcement mechanism                         | 52         |

|   | 5.4 | Enforc  | ement Functions: Input/Output Description of Enforcement Mech-  |            |

|   |     | anisms  |                                                                 | <b>5</b> 4 |

|   |     | 5.4.1   | Preliminaries to the definition of the enforcement function     | <b>5</b> 4 |

|   |     | 5.4.2   | Definition of the enforcement function                          | 55         |

|   |     | 5.4.3   | Behavior of the enforcement function over time                  | 59         |

|   | 5.5 | Enforc  | ement Monitors: Operational Description of Enforcement Mech-    |            |

|   |     | anisms  |                                                                 | 61         |

|   |     | 5.5.1   | Preliminaries to the definition of enforcement monitors         | 62         |

|   |     | 5.5.2   | Update function                                                 | 62         |

|   |     | 5.5.3   | Definition of enforcement monitors                              | 64         |

|   |     | 5.5.4   | Relating enforcement functions and enforcement monitors         | 67         |

|   | 5.6 | Summa   | ary                                                             | 69         |

| 6 | Imp | olement | cation and Evaluation                                           | 71         |

|   | 6.1 |         | ement Algorithms                                                | 71         |

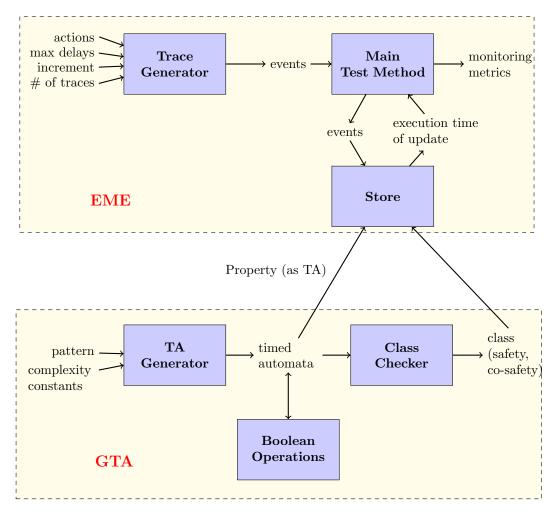

|   | 6.2 | Overvi  | ew and Architecture of TIPEX                                    | <b>7</b> 4 |

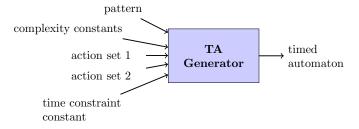

|   |     | 6.2.1   | GTA module                                                      | <b>7</b> 4 |

|   |     |         | 6.2.1.1 Generating basic timed automata                         | 76         |

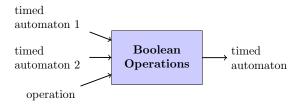

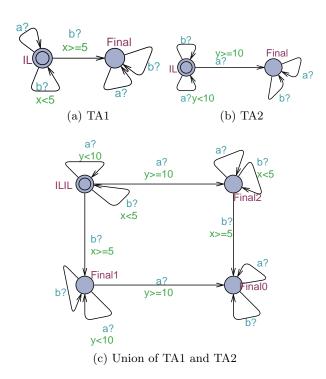

|   |     |         | 6.2.1.2 Combining timed automata                                | 78         |

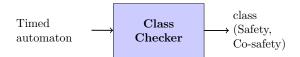

|   |     | 6.2.2   | Identifying the class of a timed automaton                      | 79         |

|   |     | 6.2.3   | EME module                                                      | 80         |

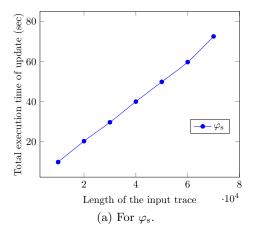

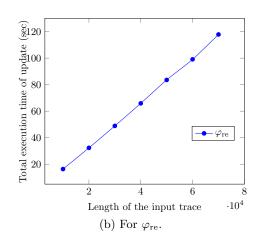

|   | 6.3 | Perfori | mance Evaluation of Function update                             | 81         |

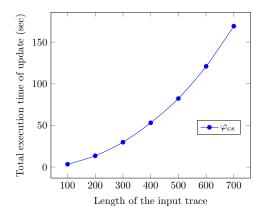

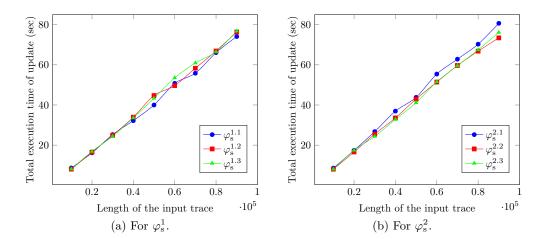

|   | 6.4 | Implen  | nentation of Simplified Algorithms for Safety Properties        | 83         |

|   | 6.5 | Discus  | sion and Summary                                                | 85         |

| 7 | Rui | ntime E | Enforcement of Parametric Timed Properties                      | 87         |

|   | 7.1 | Overvi  |                                                                 | 87         |

|   | 7.2 |         | inaries to Runtime Enforcement of Parametric Timed Properties   | 89         |

|   | 7.3 | Param   | etric Timed Automata with Variables                             | 90         |

|    |                          | 7.3.1                                                   | Syntax and semantics of a PTAV                                                                                                                                                                                                                                                                                             | 90                                           |

|----|--------------------------|---------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|

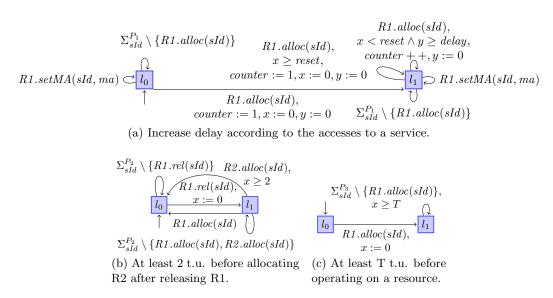

|    |                          |                                                         | Defining properties using PTAVs: A motivating example                                                                                                                                                                                                                                                                      | 92                                           |

|    | 7.4                      |                                                         | ement of Parametric Timed Properties                                                                                                                                                                                                                                                                                       | 93                                           |

|    | 7.4                      |                                                         | ation Domains                                                                                                                                                                                                                                                                                                              | 96                                           |

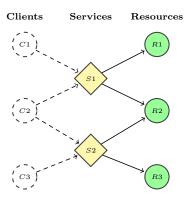

|    | 1.0                      | 7.5.1                                                   | Resource allocation                                                                                                                                                                                                                                                                                                        | 90                                           |

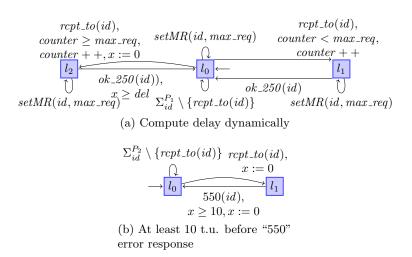

|    |                          |                                                         | Robust mail servers                                                                                                                                                                                                                                                                                                        | 98                                           |

|    | 7.6                      |                                                         |                                                                                                                                                                                                                                                                                                                            |                                              |

|    | 7.6                      |                                                         |                                                                                                                                                                                                                                                                                                                            | 101                                          |

|    |                          | 7.6.1                                                   | F                                                                                                                                                                                                                                                                                                                          | 101                                          |

|    |                          |                                                         | v                                                                                                                                                                                                                                                                                                                          | 102                                          |

|    | 7.7                      | Discuss                                                 | sion and Summary                                                                                                                                                                                                                                                                                                           | 103                                          |

| 8  | Con                      | clusion                                                 | and Future Work                                                                                                                                                                                                                                                                                                            | 05                                           |

| G  | 8.1                      |                                                         |                                                                                                                                                                                                                                                                                                                            | 105<br>105                                   |

|    | 8.2                      |                                                         | Work                                                                                                                                                                                                                                                                                                                       |                                              |

|    | 0.2                      | ruture                                                  | Work                                                                                                                                                                                                                                                                                                                       | LUO                                          |

| Bi | bliog                    | raphy                                                   | 1                                                                                                                                                                                                                                                                                                                          | 16                                           |

|    |                          | ,                                                       |                                                                                                                                                                                                                                                                                                                            |                                              |

|    |                          |                                                         |                                                                                                                                                                                                                                                                                                                            |                                              |

| Li | st of                    | Figure                                                  | ${f s}$                                                                                                                                                                                                                                                                                                                    | 18                                           |

|    |                          |                                                         |                                                                                                                                                                                                                                                                                                                            |                                              |

|    | Pro                      | ofs                                                     | 1                                                                                                                                                                                                                                                                                                                          | <b>25</b>                                    |

|    | Pro                      | ofs<br>Proof o                                          | of Proposition 5.1 (p. 57)                                                                                                                                                                                                                                                                                                 | . <b>25</b><br>125                           |

|    | Pro<br>A.1<br>A.2        | ofs<br>Proof o                                          | of Proposition 5.1 (p. 57)                                                                                                                                                                                                                                                                                                 | <b>25</b>                                    |

|    | Pro                      | ofs Proof of Proof of Prelimi                           | of Proposition 5.1 (p. 57)                                                                                                                                                                                                                                                                                                 | . <b>25</b><br>125<br>126                    |

|    | Pro<br>A.1<br>A.2        | ofs Proof of Proof of Prelimite Configu                 | of Proposition 5.1 (p. 57)  of Proposition 5.2 (p. 57)  inaries to the Proof of Proposition 5.3 (p. 69): Characterizing the arations of Enforcement Monitors                                                                                                                                                               | . <b>25</b><br>125<br>126                    |

|    | Pro<br>A.1<br>A.2        | ofs Proof of Proof of Prelimit Configu A.3.1            | of Proposition 5.1 (p. 57)                                                                                                                                                                                                                                                                                                 | .25<br>125<br>126<br>129                     |

|    | Pro<br>A.1<br>A.2        | ofs Proof of Proof of Prelimit Configur A.3.1 A.3.2     | of Proposition 5.1 (p. 57) of Proposition 5.2 (p. 57) inaries to the Proof of Proposition 5.3 (p. 69): Characterizing the arations of Enforcement Monitors Some remarks Some notations                                                                                                                                     | 25<br>125<br>126<br>129<br>129               |

|    | Pro<br>A.1<br>A.2        | ofs Proof of Prelimit Configu A.3.1 A.3.2 A.3.3         | of Proposition 5.1 (p. 57) of Proposition 5.2 (p. 57) inaries to the Proof of Proposition 5.3 (p. 69): Characterizing the rations of Enforcement Monitors Some remarks Some notations Some intermediate lemmas                                                                                                             | .25<br>125<br>126<br>129                     |

|    | Pro<br>A.1<br>A.2        | ofs Proof of Prelimit Configu A.3.1 A.3.2 A.3.3         | of Proposition 5.1 (p. 57)  of Proposition 5.2 (p. 57)  inaries to the Proof of Proposition 5.3 (p. 69): Characterizing the arations of Enforcement Monitors  Some remarks  Some notations  Some intermediate lemmas  Proof of Proposition 5.3: Relation between Enforcement Function                                      | 25<br>125<br>126<br>129<br>129<br>129        |

|    | Pro<br>A.1<br>A.2        | ofs Proof of Prelimit Configu A.3.1 A.3.2 A.3.3         | of Proposition 5.1 (p. 57)  of Proposition 5.2 (p. 57)  of Proposition 5.2 (p. 57)  of Proposition 5.3 (p. 69): Characterizing the arations of Enforcement Monitors  Some remarks  Some notations  Some intermediate lemmas  Proof of Proposition 5.3: Relation between Enforcement Function                               | 25<br>125<br>126<br>129<br>129               |

|    | Pro<br>A.1<br>A.2<br>A.3 | ofs Proof of Prelimit Configur A.3.1 A.3.2 A.3.3 A.3.4  | of Proposition 5.1 (p. 57)  of Proposition 5.2 (p. 57)  inaries to the Proof of Proposition 5.3 (p. 69): Characterizing the arations of Enforcement Monitors  Some remarks  Some notations  Some intermediate lemmas  Proof of Proposition 5.3: Relation between Enforcement Function and Enforcement Monitor              | 25<br>125<br>126<br>129<br>129<br>130        |

| A  | Pro<br>A.1<br>A.2<br>A.3 | ofs Proof of Prelimit Configur A.3.1 A.3.2 A.3.3 A.3.4  | of Proposition 5.1 (p. 57)  of Proposition 5.2 (p. 57)  inaries to the Proof of Proposition 5.3 (p. 69): Characterizing the rrations of Enforcement Monitors  Some remarks  Some notations  Some intermediate lemmas  Proof of Proposition 5.3: Relation between Enforcement Function and Enforcement Monitor  Dilications | 25<br>125<br>126<br>129<br>129<br>130<br>133 |

| A  | Pro A.1 A.2 A.3          | ofs Proof of Prelimit Configure A.3.1 A.3.2 A.3.3 A.3.4 | of Proposition 5.1 (p. 57)  of Proposition 5.2 (p. 57)  inaries to the Proof of Proposition 5.3 (p. 69): Characterizing the arations of Enforcement Monitors  Some remarks  Some notations  Some intermediate lemmas  Proof of Proposition 5.3: Relation between Enforcement Function and Enforcement Monitor              | 25<br>125<br>126<br>129<br>129<br>130<br>133 |

# Chapter 1

# Résumé en Français

Les techniques de vérification formelle comme le model-checking [CE82, QS82, BK08] sont bien adaptées pour la vérification de systèmes complexes critiques. Toutefois, même si plusieurs modèles formels, techniques d'analyse et outils ont été développés

ces dernières années, le passage à l'échelle de ces techniques constitue un goulet d'étranglement qui empêche leur utilisation à grande échelle dans l'industrie. Ce dernier point

motive l'utilisation de techniques et d'outils qui permettent à un logiciel ou à un système

de continuer à fonctionner même en présence de fautes ou de pannes. On peut dans ce

contexte citer l'enforcement de propriétés à l'exécution [Sch00, Fal10] (runtime enforcement), qui suit l'exécution d'un système et qui contrôle le respect d'exigences définies

formellement sur le système.

L'enforcement à l'exécution étend la vérification à l'exécution [BLS11] et peut se définir comme l'ensemble des théories, techniques et outils dont le but est d'assurer la conformité des exécutions d'un système vis à vis d'un ensemble de propriétés. L'utilisation d'un moniteur d'enforcement permet de transformer l'exécution du système (vue comme un séquence d'événements) pour satisfaire une propriété (p. ex. une propriété de sûreté). Ce moniteur d'enforcement est habituellement construit de manière à respecter deux contraintes :

- la séquence fournie en sortie par le moniteur d'enforcement doit satisfaire la propriété (correction), et

- si la séquence lue par le moniteur satisfait déjà la propriété, la sortie doit rester inchangée (transparence).

L'enforcement à l'exécution a été largement étudié ces dernières années pour des propriétés non-temporisées [Sch00, LBW09, FMFR11]. La notion de temps a déjà été prise en compte dans des approches d'enforcement à l'exécution dans [Mat07] pour des propriétés à temps discret, et dans [BJKZ13] où l'écoulement du temps est modélisé par une séquence d'événements incontrôlables ("ticks").

Dans cette thèse, nous nous intéressons aux mécanismes d'enforcement pour des propriétés temporisées à temps dense. Pour de telles propriétés (sur des séquences finies), non seulement l'ordre des événements est important (comme dans le cas non temporisé), mais le temps écoulé entre l'occurrence de deux événements influence également

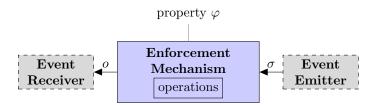

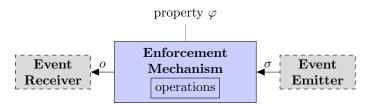

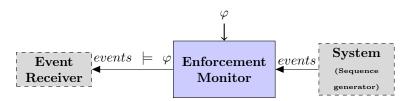

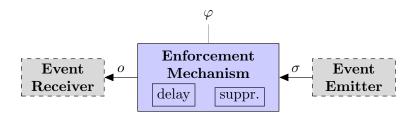

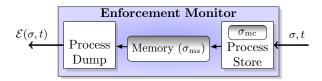

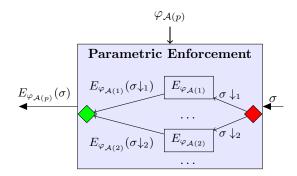

Figure 1.1: Mécanisme d'enforcement (enforcement mechanism).

l'évaluation de la propriété. Les propriétés temporisées permettent donc de décrire plus précisément les comportements désirés des systèmes dans la mesure où elles spécifient l'écoulement du temps attendu entre les événements. Ceci les rend particulièrement utiles pour certains domaines d'application [PFJM14a]. Par exemple, dans un contexte de sécurité, les moniteurs d'enforcement peuvent être utilisés comme des "firewalls" permettant d'éviter des attaques par déni de service en assurant un délai minimal entre des événements. Sur un réseau, les moniteurs d'enforcement peuvent être utilisés pour synchroniser des flux d'événements, ou pour assurer que les événements respectent les pré-conditions de services.

#### 1.1 Contexte

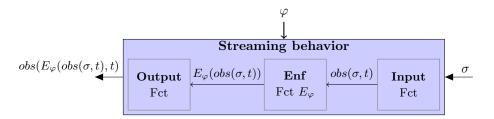

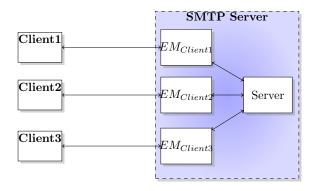

Dans cette thèse, nous nous focalisons sur l'enforcement à la volée de propriétés temporisées. Le contexte général est décrit par la Figure 2.1. Plus spécifiquement, étant donnée une propriété temporisée  $\varphi$ , nous cherchons à synthétiser un mécanisme d'enforcement fonctionnant à l'exécution. Afin d'être le plus général possible, ce mécanisme d'enforcement est supposé être placé entre un émetteur et un récepteur d'événments qui s'exécutent de manière asynchrone. Cette architecture abstraite est suffisamment générique pour être instanciée à un grand nombre de cas concrets où l'émetteur et le récepteur peuvent être vus soit comme un programme soit comme l'environnement.

Le but d'un moniteur d'enforcement est de lire une séquence d'événements  $\sigma$  (potentiellement incorrecte) produite par l'émetteur et de la transformer en une séquence de sortie o correcte vis à vis d'une propriété  $\varphi$ , o étant alors l'entrée du récepteur. Nous supposons que le médium de communication entre l'émetteur et le récepteur, via le mécanisme d'enforcement, est sûr et que ce dernier n'induit pas de délai de communication. Dans notre cadre temporisé, les événements sont modélisés par des actions auxquelles sont associées leurs dates d'occurrence. Les séquences d'événements en entrée et sortie du mécanisme d'enforcement sont donc modélisées comme des mots temporisés et le mécanisme d'enforcement est modélisé par une fonction de transformation de mots temporisés.

- Expressivité du formalisme des spécifications/propriétés. Un concept central en vérification et enforcement à l'exécution est la génération de moniteurs à partir d'un langage de spécification de haut niveau permettant de décrire les propriétés. Nous avons choisi de nous baser sur le modèle des automates temContexte 7

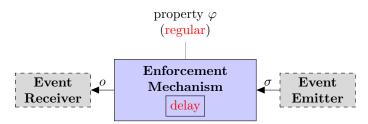

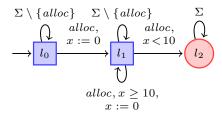

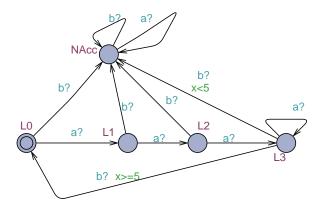

porisés qui est traditionnellement utilisé pour la modélisation et la vérification de systèmes temps-réels. Un automate temporisé (TA) [AD94] est un automate d'états finis étendu avec un ensemble fini de variables réelles appelées horloges servant à modéliser le temps (continu). Dans cette thèse, nous considérons 3 grandes classes de propriétés: Les propriétés de sûreté (safety) qui modélisent le fait que aucun comportement mauvais ne se produit; les co-safety qui modélisent le fait qu'un comportement désiré va inévitablement se produire après un temps fini et les propriétés régulières qui contiennent ces deux classes et regroupent toutes les propriétés modélisables par des TA. De plus, afin de considérer des spécifications encore plus expressives, nous avons également étendu les TA avec des variables entières et des paramètres.

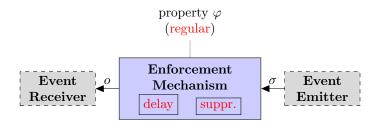

Capacité du mécanisme d'enforcement. Le mécanisme d'enforcement que nous considérons retarde le temps, c'est à dire que sa principale primitive d'enforcement permet d'augmenter la date d'occurrence des actions. Outre cet aspect, le moniteur peut également supprimer des actions quand il n'est plus possible de satisfaire une propriété en retardant les actions.

En résumé, étant donnés un propriété régulière  $\varphi$  et un mot temporisé  $\sigma$  en entrée, le mécanisme d'enforcement reçoit un mot temporisé  $\sigma$  et produit en sortie un mot temporisé  $\sigma$  qui satisfait  $\varphi$ . Le mot temporisé  $\sigma$  est obtenu en retardant les dates d'occurrence des actions d'une sous-séquence de  $\sigma$ .

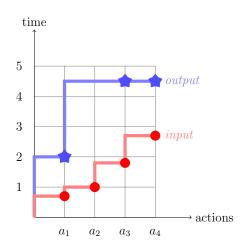

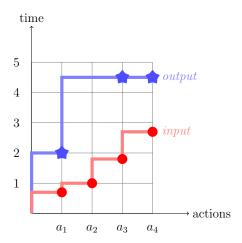

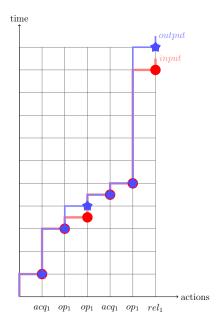

Figure 1.2: Comportement possible d'un mécanisme d'enforcement

La Figure 1.2 illustre le paradigme d'enforcement à l'exécution que nous considérons, c'est à dire comment un mécanisme d'enforcement se comporte afin de corriger une séquence d'entrée. La courbe rouge (resp. bleue) représente la séquence d'entrée (resp. de sortie) avec les actions en abscisse et les dates d'occurrence de celles-ci en ordonnée. En plus de la satisfaction de la propriété (non représentée sur la figure), le mécanisme d'enforcement ne doit pas changer l'ordre des actions, mais peut soit augmenter les dates d'occurrences de celles-ci,

soit supprimer les actions (p. ex. l'action  $a_2$ ). À noter qu'il peut réduire le délai entre 2 actions (p. ex.  $a_3$  et  $a_4$ ). De plus, de manière à avoir un impact minimal sur la séquence d'entrée, le mécanisme d'enforcement doit fournir les actions en sortie le plus tôt possible.

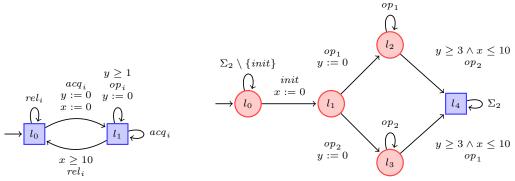

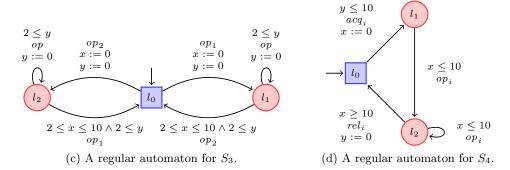

Pour continuer notre illustration du paradigme d'enforcement, considérons le cas de 2 processus accédant à une ressource partagée et réalisant une action sur celle-ci. Chaque processus i (avec  $i \in \{1,2\}$ ) interagit avec cette ressource via 3 actions: acquisition  $(acq_i)$ , release  $(rel_i)$ , et une opération spécifique  $(op_i)$ . De plus les 2 processus peuvent réaliser une action commune op. Le système démarre sur l'occurrence de l'action init. Dans la suite, la variable t permet de coder le passage du temps.

Considérons la spécification suivante: "Les opérations op<sub>1</sub> et op<sub>2</sub> doivent s'exécuter de manière transactionnelle. Les 2 opérations doivent être exécutées sans ordre a priori et toute transaction doit contenir à la fois l'opération op<sub>1</sub> et op<sub>2</sub>. Toute transaction doit se finir en moins de 10 unités de temps. Plusieurs occurrences de l'opération op peuvent se produire entre op<sub>1</sub> et op<sub>2</sub>. Enfin chaque opération doit être espacée de la précédente d'au moins 2 unités de temps.

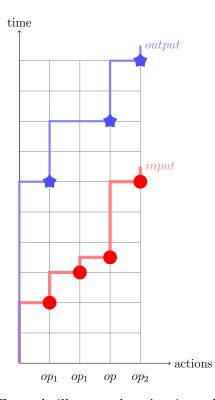

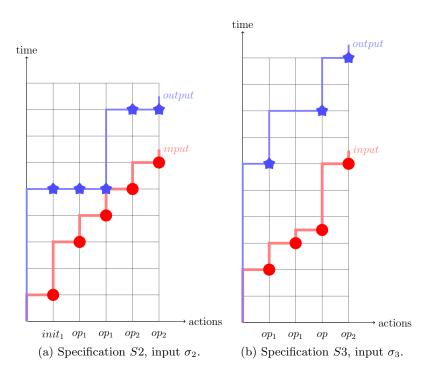

Figure 1.3: Exemple illustrant le mécanisme d'enforcement

Considérons la séquence d'entrée  $\sigma = (2, op_1) \cdot (3, op_1) \cdot (3.5, op) \cdot (6, op_2)$ . À t = 2, le moniteur d'enforcement ne peut produite  $op_1$  en sortie car cette action ne satisfait pas la propriété (et le moniteur ne connaît pas encore les dates et occurrences des événements suivants). À t = 3, Le moniteur reçoit une nouvelle fois l'action  $op_1$ .

Clairement, il n'y a aucune manière de calculer de nouvelles dates pour ces 2 actions  $op_1$  de manière à satisfaire la spécification. Le moniteur choisit donc de supprimer la deuxième occurrence de l'action  $op_1$ . À t=3.5, quand le moniteur reçoit l'action op, la séquence d'entrée ne satisfait toujours pas la spécification, mais il existe encore des continuations possibles permettant la satisfiabilité de celle-ci. À t=6, sur réception de l'action  $op_2$ , le moniteur peut calculer des délais appropriés entre les actions  $op_1$  suivi de op et  $op_2$  de manière à satisfaire la spécification. Ainsi, la date associée à  $op_1$  est fixée à 6 (c'est à dire la plus petite date possible au moment de la décision), 8 pour l'action op (le délai minimal entre deux actions est fixé à 2), et 10 pour l'action  $op_2$ . Finalement, comme décrit par la Figure 1.3, la sortie du moniteur d'enforcement pour  $op_2$  est  $op_1$ 0 est  $op_2$ 1.

#### 1.2 Résumé de l'approche

Ce paragraphe présente un résumé de l'approche utilisée pour la synthèse d'un moniteur d'enforcement pour une propriété temporisée.

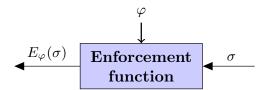

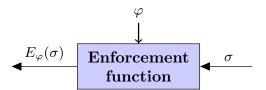

À un niveau abstrait, un mécanisme d'enforcement d'une propriété  $\varphi$  peut être vu comme une fonction prenant en entrée un mot temporisé et fournissant en sortie un mot temporisé satisfiant  $\varphi$  (c.f. Figure 5.5).

Figure 1.4: Fonction d'enforcement

Les contraintes que doivent satisfaire un mécanisme d'enforcement sont les suivantes:

- Contraintes physiques: toute événement produit en sortie par le moniteur d'enforcement ne peut être remis en cause par celui-ci.

- Correction: le moniteur doit produire uniquement des séquences qui satisfont la propriété  $\varphi$

- Transparence: le moniteur peut seulement i) retarder les actions sans en changer l'ordre d'occurrence ou ii) supprimer des événements.

Afin de simplifier la conception et l'implémentation d'un mécanisme d'enforcement dans un contexte temporisé, nous avons choisi de le décrire à trois niveaux d'abstraction: la fonction d'enforcement, le moniteur d'enforcement, et les algorithmes d'enforcement.

**Définition fonctionnelle.** Une fonction d'enforcement décrit une transformation fonctionnelle d'un mot temporisé (en entrée) en un autre mot temporisé (en sortie). Son but est de décrire, à un niveau abstrait, pour chaque mot temporisé  $\sigma$ , le mot de sortie  $E_{\varphi}(\sigma)$  attendu de manière à ce que cette fonction satisfasse les contraintes précédemment décrites.

Moniteur d'enforcement. Cette description fonctionnelle est par la suite raffinée en une vue plus concrète qui définit le comportement opérationnel d'un mécanisme d'enforcement en fonction du temps. Il est défini via un système de transitions étiquetées infini.

Implémentation et évaluation. Les algorithmes décrivent comment implémenter de manière concrète ces mécanismes d'enforcement pour toute propriété temporisée régulière spécifiée par un automate temporisé. L'implémentation est réalisée en Python et utilise des librairies UPPAAL [BY03]. Nos résultats expérimentaux nous ont permis d'avoir un premier retour sur expérience concernant la validité de notre approche et de montrer le caractère effectif des mécanismes d'enforcement dans un cadre temps-réel.

#### 1.3 Résultats

Nous avons développé des mécanismes d'enforcement à l'exécution pour des spécifications avec contraintes temporelles fortes. Dans cette thèse, nous avons décrit comment synthétiser des moniteurs d'enforcements à partir d'une description formelle des propriétés en termes d'automates temporisés. Toutes les propriétés temporisées modélisables par des automates temporisés finis sont supportées dans ce cadre. Les mécanismes d'enforcement permettent de retarder les actions (tout en permettant de réduire l'intervalle de temps entre celles-ci) et de supprimer des actions dès lors qu'il n'est plus possible de satisfaire la propriété en retardant les actions, et ceci quelque soit le futur possible. Des algorithmes basés sur ce mécanisme ont également été implémentés et leur correction est prouvée formellement.

Ce travail a donné lieu à plusieurs publications dans des conférences internationales et journaux. Nous rappelons ici les résultats pour chacune d'entre elles. Ceci montre l'évolution de notre démarche et la manière dont nous avons généralisé (et simplifié) l'approche au fil du temps.

- Runtime Enforcement of Timed Properties [PFJ<sup>+</sup>12].

- Dans [PFJ<sup>+</sup>12], nous avons introduit le concept d'enforcement à l'exécution pour des propriétés temporisées de safety et co-safety modélisées par des automates temporisées. Pour ce premier résultat la puissance des mécanismes d'enforcement se résumait à augmenter les délais entre chaque action. Nous avons proposé une notion d'optimalité du mécanisme d'enforcement qui devait, en fonction de la situation, calculer les plus petits délais entre chaque action afin de satisfaire la propriété (sous la contrainte que ceux-ci devaient être supérieurs aux délais initiaux). Ce travail a donné lieu à une première implémentation et à des expérimentations démontrant la validité de notre approche.

- Runtime Enforcement of Regular Timed Properties [PFJM14b].

L'approche présentée dans [PFJ<sup>+</sup>12] se focalise sur l'enforcement de propriétés de safety et co-safety. Nous avons par la suite étendu cette approche en considérant la classe des propriétés régulières, ces dernières permettant d'exprimer

<sup>1.</sup> Les titres correspondent à ceux des articles.

Résultats 11

notamment une certaine forme de comportement transactionnel. Une des difficultés à considérer est que ce type de propriétés n'est close ni par préfixe ni par suffixe. Pour un mot temporisé en entrée, le mot en sortie calculé par le moniteur d'enforcement alterne donc entre des préfixes qui satisfont la propriété et d'autres qui ne la satisfont pas, mais dont on est sur que son extension la satisfera. Le moniteur d'enforcement doit donc prendre en compte cet aspect lors du calcul des dates d'occurrence des actions et des éventuelles suppressions. Ce travail a également donné lieu à une nouvelle implémentation.

- Runtime Enforcement of Regular Timed Properties [PFJ<sup>+</sup>14].

Dans [PFJ<sup>+</sup>14], nous avons généralisé et simplifié les résultats de [PFJ<sup>+</sup>12, PFJM14b] et démontré formellement tous les résultats.

- Runtime Enforcement of Regular Timed Properties by Suppressing and Delaying Events.

Dans [PFJ<sup>+</sup>12, PFJM14b, PFJ<sup>+</sup>14] le moniteur ne pouvait qu'augmenter les délais entre les actions. Nous avons généralisé ce résultat dans un article soumis au journal Science of Computer Programming (SCP) en permettant au moniteur de supprimer des événements (seulement quand cela était nécessaire) et en lui permettant d'augmenter les dates d'occurrence d'événements (quitte à éventuellement réduire les délais entre événements).

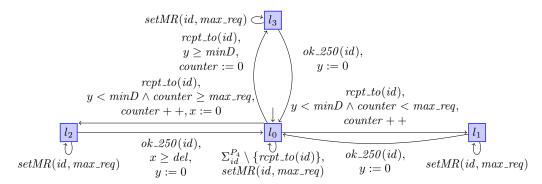

#### Runtime Enforcement of Parametric Timed Properties with Practical Applications [PFJM14a].

Pour divers domaines d'applications (sécurité des réseaux, protocoles de communications, etc), beaucoup de propriétés attendues du système comportent à la fois des contraintes sur le temps et sur les données. Dans [PFJM14a], nous avons donc étendu les résultats de [PFJ<sup>+</sup>12] en considérant un modèle de propriétés temporisées paramétrées avec variables (ces dernières pouvant être internes ou externes, c'est à dire portées par les événements). Un des paramètre permet d'instancier la propriété en fonction par exemple d'un numéro de session. Les événements reçus sont alors dispatchés sur des moniteurs en fonction de ce paramètre et ré-assemblés en sortie. Pour [PFJM14a], nous nous sommes focalisés sur des propriétés de safety et des moniteurs qui ne pouvaient qu'augmenter les délais entre les actions. Cette limitation a été levée dans le manuscrit de thèse: nous considérons maintenant tout type de propriétés et les possibilités du moniteur correspondent à celles décrites dans le papier soumis au journal SCP.

# Chapter 2

# Introduction

#### 2.1 Motivations for Runtime Enforcement

Embedded and cyber-physical systems (CPS) are usually composed of multiple subsystems that are distributed and possibly developed using several programming languages. The behavior of such systems is affected by several external factors since they generally interact with many systems and users, and are integrated in networked environments. As the complexity of a system and its environment increase, ensuring that the system is error-free becomes a challenge. Failure of a system may result in severe financial losses, and in case of a safety-critical system, it may be even worse since it may also result in loss of human lives [LT93].

Using formal methods and model driven development approaches for designing and developing systems is a major area of research. Expressing requirements using a formal specification will make requirements clearer and remove ambiguities and inconsistencies. Formal languages are more easily amenable to automatic processing, by means of tools [Jan02]. Various formal verification techniques such as model checking [BK08] involve the formal modeling of computing systems and the verification of properties on the models, including safety and timing properties. These model-based techniques are well suited for verifying complex safety-critical systems, because they guarantee absence of errors.

Although several formal modeling and analysis techniques and tools based on them have been developed over the years, scalability of the techniques is a central issue that has prevented their widespread adoption. This motivates the necessity for techniques and tools that enable the system to tolerate failures and to continue operating in case of failures. An example is runtime enforcement techniques [Sch00, Fal10] that monitor the execution of system (at runtime) and control its compliance against the requirements of the system that are formally defined. Runtime enforcement extends runtime verification [BLS11] and refers to the theories, techniques, and tools aiming at ensuring the conformance of the executions of systems under scrutiny with respect to some desired property. Using an enforcement monitor, an (untrustworthy) input execution (in the form of a sequence of events) is modified into an output sequence

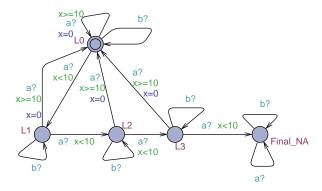

Figure 2.1: Enforcement mechanism.

that complies with a property (e.g., formalizing a safety requirement). It is based on two properties: the output sequence complies with the property (soundness) and if the input already complies with the property, it should be left unchanged (transparency).

Runtime enforcement has been extensively studied over the last decade in the context of untimed properties. According to how a monitor is allowed to correct the input sequence, several models of enforcement monitors have been proposed. Security automata [Sch00] focused on safety properties, and blocked the execution as soon as an illegal sequence of actions (not compliant with the property) is recognized. Later, several refinements have been proposed such as suppression automata [LBW09] that allowed to suppress events from the input sequence, insertion automata [LBW09] that allowed to insert events to the input sequence, and edit-automata [LBW09] or so-called generalized enforcement monitors [FMFR11] allowed to perform any of these primitives. The notion of time has been considered in previous runtime enforcement approaches such as in [Mat07] for discrete-time properties, and in [BJKZ13] which considers elapsing of time as a series of uncontrollable events ("ticks").

#### 2.2 Problem Statement

Motivations for extending runtime enforcement to timed properties abound. First, timed properties are more precise to specify desired behaviors of systems since they allow to explicitly state how time should elapse between events. Thus, timed properties/specifications can be particularly useful in some application domains [PFJM14a]. For instance, in the context of security monitoring, enforcement monitors can be used as firewalls to prevent denial of service attacks by ensuring a minimal delay between input events (carrying some request for a protected server). On a network, enforcement monitors can be used to synchronize streams of events together, or ensuring that a stream of events conforms to the pre-conditions of some service.

Context and objectives. The general context is depicted in Fig. 2.1. We focus on online enforcement of timed properties. More specifically, given a timed property  $\varphi$ , we want to synthesize an enforcement mechanism that operates at runtime. To be as general as possible, an enforcement mechanism is supposed to be placed between an event emitter and an event receiver. The emitter and receiver execute asynchronously. This abstract architecture is generic and can be instantiated to many concrete ones where the emitter and receiver are considered to be e.g., a program or the environment.

Contributions 15

An enforcement mechanism receives a sequence of timed events  $\sigma$  as input and transforms it into a sequence of timed events o. No constraint is required on  $\sigma$ , whereas the enforcement mechanism must ensure that o is correct with respect to property  $\varphi$ . Satisfaction of property  $\varphi$  by the output sequence is considered at the output of the enforcement mechanism and not at the input of the event receiver: we assume a reliable, without delay, and safe communication between the emitter and receiver. We do not consider any security, communication, nor reliability issue with events. The considered enforcement mechanisms are *time retardants*, i.e., their main enforcement primitive consists in delaying the received events.

To sum up, given some timed property  $\varphi$  and an input timed word  $\sigma$ , we aim to study mechanisms that input  $\sigma$  and output a sequence o that satisfies  $\varphi$  (soundness of the mechanism).

Various directions that we want to explore are:

- Expressiveness of the supported specification formalism A central concept in runtime verification and enforcement, is to generate monitors from some high-level specification of the property (which the monitor should verify or enforce). In our enforcement framework, we wanted to handle (formalize and synthesize enforcement monitors) all the specifications that we commonly encounter in real-life in various domains.

- Power of the enforcement mechanism Another interesting aspect is regarding the power of the enforcement mechanism. What can the enforcement mechanism do to the input sequence in order to correct it with respect to the property? How the notion of transparency can be adapted in our framework also depends on the power of the enforcement mechanism. Enforcement operations that require expensive computations may not be desirable in a timed context.

- Implementability We also wanted to investigate the feasibility of realizing the enforcement monitoring mechanism that we propose. We want to see whether it is feasible to synthesize enforcement monitors based on the proposed formal framework, and also to have a first assessment of performance.

#### 2.3 Contributions

This work resulted in publications in international conferences and journals (See Appendix B for the list of publications). We now summarize key contributions and how our work evolved.

#### - Runtime Enforcement of Timed Properties.

We initially started with limited properties, and considered runtime enforcement of timed safety and co-safety properties. Safety properties express that "something bad should never happen" and co-safety properties express that "something good should happen within a finite amount of time". The results related to enforcement of safety and co-safety properties were published in RV 2012 [PFJ $^+$ 12], introducing runtime enforcement framework for timed properties. We showed how runtime enforcers can be synthesized for any safety or co-safety timed property

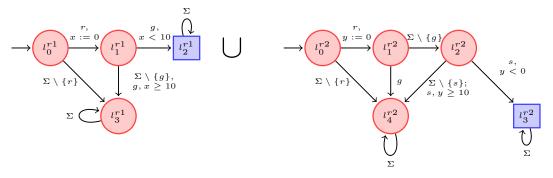

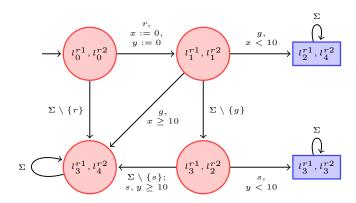

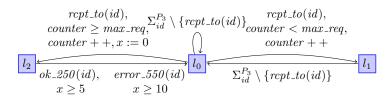

Figure 2.2: Supported properties and operations in [PFJ<sup>+</sup>12].

defined as timed automaton. Proposed runtime enforcers are time retardant: to correct an input sequence the enforcement mechanism has the power to introduce additional delays between the events of the input sequence. Output of the enforcement mechanism o satisfies  $\varphi$  (soundness of the mechanism), and has the same order of events as  $\sigma$  with possibly increased delays (transparency of the mechanism). Experiments have been performed on prototype monitors to show their effectiveness and the feasibility of our approach.

- Runtime Enforcement of Regular Timed Properties.

Figure 2.3: Supported properties and operations in [PFJM14b].

We later focused on supporting more properties in our enforcement framework introduced in [PFJ<sup>+</sup>12]. In the space of regular properties, some interesting properties of systems are neither safety nor co-safety properties. Indeed, some regular properties may express interesting properties of systems belonging to a larger class that allows to specify some form of transactional behavior. For example, the two following properties could specify the behavior of a server, and are neither safety nor co-safety properties.

- "Resource grants and releases alternate, starting with a grant, and every grant should be released within 15 to 20 time units (t.u.)".

- "Every 10 t.u., there should be a request for a resource followed by a grant. The request should occur within 5 t.u.".

The difficulty that arises when considering such properties is that the enforcement mechanisms should then consider the alternation between currently satisfying and not satisfying the property. The results in [PFJ<sup>+</sup>12] have further been extended to the enforcement of any regular timed property [PFJM14b]. We proposed enforcement monitor synthesis mechanisms for all regular timed properties. Also, for the enforcement of co-safety properties, the approach in [PFJ<sup>+</sup>12] assumes

Contributions 17

that time elapses differently for input and output sequences (the sequences are desynchronized). More precisely, the delay of the first event of the output sequence is computed from the moment an enforcement mechanism detects that its input sequence can be corrected (that is, the mechanism has read a sequence that can be delayed into a correct sequence). Compared to [PFJ<sup>+</sup>12], the approach in [PFJM14b] is more realistic as it does not suffer from this "shift" problem.

#### - Runtime Enforcement of Timed Properties revisited.

We later revisited, combined the results in [PFJ<sup>+</sup>12] and [PFJM14b], simplified the formalizations, provided more explanations, examples and detailed formal proofs of these results which has been published in the Formal Methods in System Design (FMSD) journal [PFJ<sup>+</sup>14].

More specifically, this paper provides the following additional contributions:

- proposes a more complete and revised theoretical framework for runtime enforcement of timed properties: we have re-visited the notations, unified and simplified the main definitions;

- proposes a completely new implementation of our EMs that offers better performance (compared to the ones in [PFJ+12]);

- synthesizes and evaluates EMs for more properties on longer executions;

- includes correctness proofs of the proposed mechanisms.

- Runtime Enforcement of Regular Timed Properties by Suppressing and Delaying Events.

Figure 2.4: Supported properties and operations in [FJMP14].

In [PFJ<sup>+</sup>12, PFJM14b] the enforcement mechanism can only increase the delay between events. When it is no more possible to correct the input sequence anymore by introducing additional delay, the enforcement mechanism halts and cannot correct any more input events. So, later the focus was on increasing the power of the enforcement mechanism which can both delay events to match timing constraints, and suppress events when no delaying is appropriate, thus allowing the enforcement mechanisms and systems to continue executing. Also, in all our earlier works [PFJ<sup>+</sup>12, PFJM14b, PFJ<sup>+</sup>14], enforcement mechanisms receive sequences of events composed of actions and delays between them, and can only increase those delays to satisfy the desired timed property. Here, we consider events composed of actions with absolute occurrence dates, and we allow to increase the dates (while allowing to reduce delays between events) and to suppress events. This work has been submitted to the Science of Computer

Programming (SCP) journal [FJMP14].

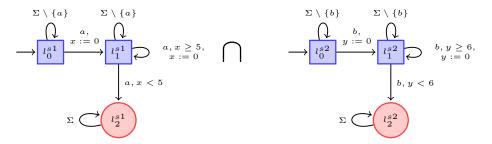

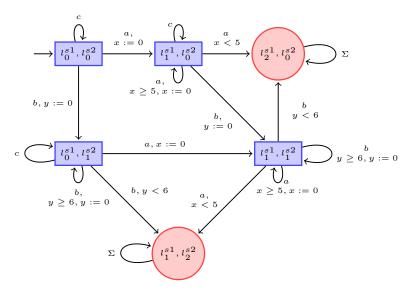

#### Runtime Enforcement of Parametric Timed Properties with Practical Applications.

When we considered requirements from some application domains such as network security, we noticed that some requirements have constraints both on time and data. Events also carry some data. To be able to formalize these requirements, that have constraints both on data and time, we felt the necessity to enrich Timed Automata (TA), the model we use to formally define requirements, with some additional features. We make one step towards practical runtime enforcement by considering event-based specifications where i) time between events matters and ii) events carry data values from the monitored system. We refer to this problem as enforcement monitoring for parametric timed specifications. To handle expressive specifications in our framework, we introduce the model of Parameterized Timed Automata with Variables (PTAVs). To guide us in the choice of expressiveness features we considered requirements in several application domains. With more expressive specifications (with parameterized events, internal variables, and session parameters), we improve the practicality and illustrate the usefulness of runtime enforcement on application scenarios. These results were published in WODES 2014 [PFJM14a].

#### - Prototype Implementations.

To show the practical feasibility of our theoretical results, the proposed algorithms were also implemented in Python using some UPPAAL [BY03] libraries. The tool set developed is described in Chapter 6. In addition to enforcement monitor synthesis, the tool also provides other functionalities such as combining timed automata using Boolean operations, and determining the class of a given timed automaton.

#### 2.4 Outline

This thesis is organized as follows:

Chapter 3 provides overview of various formal techniques related to checking the correctness of a system. It also describes and surveys related work on runtime enforcement techniques.

Chapter 4 provides the required background information. We describe all the preliminaries for formalizing timed properties and executions of a system. Timed automata are the formal model used to define properties. An enforcement monitor for a timed property is synthesized from a timed automaton defining the property. We describe the syntax and semantics of timed automata model, how timed automata can be combined using Boolean operations, and reachability analysis techniques for timed automata.

Chapter 5 presents runtime enforcement mechanisms for timed properties. We describe enforcement monitoring for systems where the physical time elapsing between actions matters. Executions are modeled as sequences of events composed of actions with dates (or timed words) and we consider runtime enforcement for timed specifi-

Outline 19

cations modeled as timed automata, in the general case of regular timed properties. The enforcement mechanisms have the power of both delaying events to match timing constraints, and suppressing events when no delaying is appropriate, thus allowing the enforcement mechanisms and systems to continue executing. To ease their design and their correctness-proof, enforcement mechanisms are described at several levels: enforcement functions that specify the input-output behavior in terms of transformations of timed words, constraints that should be satisfied by such functions, and enforcement monitors that describe the operational behavior of enforcement functions.

Chapter 6 presents enforcement algorithms describing the implementation of enforcement monitors described in Chapter 5. We validated the feasibility of enforcement monitoring for timed properties by prototyping the synthesis of enforcement monitors from timed automata. We describe the developed tool-chain, and discuss the experimental results in detail.

Chapter 7 presents runtime enforcement of parametric timed properties. We describe an extended model of timed automata, that can be used to formalize richer requirements (which have constraints both on time and data). We also extend our enforcement monitoring framework described in Chapter 5 to take in to account properties defined using the proposed extended model. Chapter 8 provides conclusions and outlines the future work.

20 Introduction

# Chapter 3

# State of the Art

In this chapter, we first provide a short overview of various techniques, related to checking the correctness of a system (that is checking whether the system satisfies the requirements). Later, we describe runtime enforcement techniques, which is related to correcting the execution of a system (at runtime) according to the requirements.

#### 3.1 Checking Correctness of a System

Generally, requirements are informal description of what we want a system to do. Requirements are the basis for the design, development and testing of a system.

The process of checking the correctness of a system (that is, whether the system conforms to the specification) is called as verification. The specification of the system, which is a set of requirements, is a description of the system (about what it should do/how it should behave). Generally, verification is done using techniques such as testing.

The process of executing a program or a system with the objective of finding errors in the system is called as testing. Testing a system involves experimentally and systematically checking the correctness of the system. Generally, testing is performed by executing the system in a controlled environment, by providing some specific test data as input to the system, and making observations during the execution of the tests. From the observations made during the execution, verdicts about the correctness of the system (whether it satisfies the specification) is assigned.

For the testing activities, the specification of the system acts as the correctness criterion against which the system is to be tested. A common practice is to write the specification informally, in natural language. Such informal specification is the basis for any testing activity.

Drawbacks of the traditional testing process and using informal specification. Although informal specifications (written in some natural language such as English and French) are easy to read, they may be ambiguous. Informal description of requirements are often incomplete and liable to different and possibly inconsistent interpretations. Relying on unclear, imprecise, incomplete and ambiguous specifications State of the Art

cause several problems in the testing process. Basing testing and verification activities on such informal specifications (which may have some inconsistencies) is not appropriate. Also, most of the testing activities are often incomplete, and they are used as a process to find errors, but cannot assure that the system is correct.

Formal specification and formal methods. A specification is said to be formal if it is expressed in a formal specification language which is a language having a precise syntax and semantics, and for which every statement in the language has a unique meaning mathematically. Such formal specification languages are often based on mathematical concepts such as mathematical logic. Advantage of such formal specifications and models is that they have a precise, unambiguous semantics, which enables the analysis of systems and the reasoning about them with mathematical precision.

Thus, using formal languages for specifying requirements will remove ambiguities and inconsistencies. Specifications described using formal languages, just as informal specifications, can be used in various development phases, and as contracts between developers and customers. Moreover, formal languages are more easily amenable to automatic processing, by means of tools. In contrast to informal specifications, formal specifications can be mathematically analysed since they are mathematically based. For example, methods (and tools) exist to automatically verify the absence of deadlock in the formal description of the design of the system. Formal specifications can also be used for generating test cases automatically.

#### 3.2 Formal Verification Techniques

Verification is the act of checking whether a system/product satisfies (conforms to) its specification. When formal languages and techniques (based on mathematics) are used in the verification process it is called as formal verification. Formal verification techniques can be divided into two sub-categories called as static and dynamic verification techniques.

#### 3.2.1 Static verification techniques

The static verification techniques are performed without actually executing the system being verified. Some of the static formal verification techniques are the following:

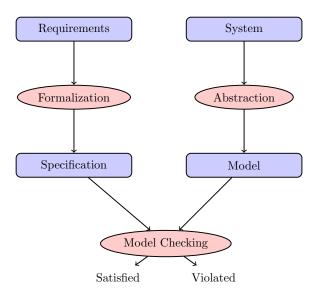

#### 3.2.1.1 Model checking

Model checking [CE82, QS82, BK08] is an automated approach to verify that a formal model of the system (usually described as a state transition system), satisfies the formal specification, defining the requirements of the system. Model of the system is an abstraction of the system (omitting details irrelevant for checking the desired properties) that describes how the state of the system may evolve over time. Models are typically described as automata (or its extensions with time, probability, cost, data etc), describing the possible states, initial states, and the possible transitions

between states. Properties are usually expressed in some form of temporal logic [HR04] such as Linear Temporal Logic (LTL) [Pnu77, HR04], and Computational Tree Logic (CTL) [CE82, HR04], having constructs to express constraints on how the state of a system may evolve. Model checkers such as Spin [Hol97] and UPPAAL [LPY97], are some of the available tools that perform model checking.

Figure 3.1: Model checking.

Figure 3.1 shows the process of applying model checking. To perform model checking on a system, a model of the system should be created, and the requirements (describing the desired properties of the system informally) should be formalized. The formalized requirements are called as properties (or property specification). The model checking algorithms (and tools), take the model and properties as input, and answer whether the model satisfies the properties (or not). The model checker explores all the possible states to decide whether the properties hold in all the (reachable) states. Incase if a property does not hold, then the model checker returns a counter example (which is a run of the model of the system, leading to a state in which the property does not hold).

#### 3.2.1.2 Static analysis

Static analysis is a powerful technique that enables automatic verification of programs. Using static analysis approach, various properties such as type safety and resource consumption can be checked [HBB+11]. Abstract static analysis [DKW08] techniques which are mostly used for compiler optimization, are also used for program verification. These techniques focus on computing approximate *sound* guarantees efficiently. However, the information provided is not always precise since it is usually based on an approximation.

Generally, static analysis tools such as [EL02, HBB<sup>+</sup>11] parse the source code and build an abstraction (model) of the system such as a directed graph. By traversing the

model, it is checked whether certain properties hold in the model. In case a violation is found in the model, it can also be expected in the source code.

#### 3.2.1.3 Theorem proving

In theorem proving approaches, for a mathematical statement to be true, a convening mathematical proof is constructed. If a proof cannot be found for a mathematical statement, then it cannot be concluded that the statement is true. In case a correct proof is found, the the statement is called a theorem. Several tools exist to help in the process of constructing formal proofs. For example interactive theorem provers such as COQ [BC04] are tools that can be use to construct a proof interactively. Proof checkers such as MetaMath [Met] can be used to check whether a proof is correct or not.

#### 3.2.2 Dynamic verification techniques

Dynamic verification techniques are performed by executing the system in a particular environment, providing specific input data to the system and observing its behavior (or output).

#### 3.2.2.1 Testing using formal methods

Several problems occur in the testing process since the specifications (which are written informally) are often incomplete or ambiguous. Basing testing activities on a formal specification is an advantage since formal specification is precise, complete, consistent and unambiguous. This is a first big advantage in contrast with traditional testing processes where such a basis for testing is often lacking.

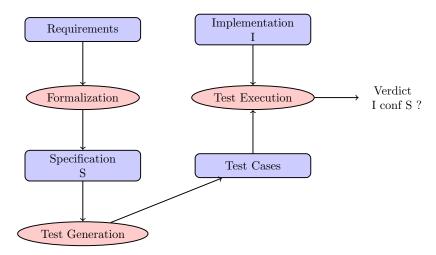

Figure 3.2: Conformance testing with formal methods.

Checking functional correctness of a black-box system under test by means of testing is known as conformance testing [Jan02, JJ05]. Formal specifications are also amenable

to automatic processing by tools, which is another advantage of formal specifications for testing. For conformance testing with formal methods, a formal specification is the starting point for the generation of test cases [Jan02]. Figure 3.2 gives an overview of the process. Algorithms (which have sound formal basis) have been developed for automatically generating test cases from a formal specification. This opens the way towards completely automating testing, where the system under test and its formal specification are the only required prerequisites. Moreover, they have been implemented in tools such as TGV [JJ05], STG [CJRZ02], and TorX [BB05], leading to automatic, faster and less error-prone generation of test cases. STG avoids enumerating the specification's state space, and uses symbolic generation techniques. Regarding conformance testing of real-time systems, there are tools such as TTG [KT09] based on the model of partially-observable, non-deterministic timed automata.

#### 3.2.2.2 Runtime verification

Runtime verification [BLS11, FZ12] refers to the theories, techniques, and tools that allow checking whether a run of a system under scrutiny satisfies (or violates) a given correctness property. It is a formal verification technique, complementing the other formal verification techniques discussed so far such as model checking.

Runtime verification techniques do not influence the program execution, and deals only with detection of violation (or satisfaction) of properties. In runtime verification, checking whether a run of a system satisfies a property is performed using a monitor.

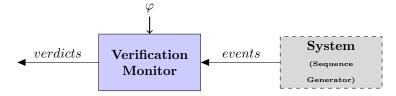

Figure 3.3: Verification monitor.

The first step of monitoring approaches consists in instrumenting the underlying system so as to partially observe the events or the parts of its global state that may influence the property under scrutiny. A verification monitor as shown in Figure 3.3 is a decision procedure emitting verdicts stating the correctness of the (partial) observed trace generated from the system execution. The system being monitored is regarded as a sequence generator. The set of verdicts may contain more than two different truth values such as  $\{true, false, inconclusive\}$ . The verdict provided by the monitor is true if the current input fulfills the property (irrespective of how the current input is extended), false if a misbehavior is detected, and inconclusive otherwise. Formally, if  $\varphi$  denotes the property (the set of valid runs), then runtime verification is about checking whether a run of a system belongs to the property  $\varphi$ . The monitor can operate either online by receiving events in a lock-step manner with the execution of the system or offline by reading a log/sequence of system events/actions. A central concept in runtime verification, is to generate monitors from some high-level specification of

State of the Art

the property which the monitor should check/verify. Monitors are generated from specifications such as Linear Temporal Logic (LTL) [BLS11].

Relation with other formal verification techniques In model checking, all executions of a given model of a system are examined, to answer whether the model satisfies the property, and in runtime verification, we check whether a particular execution of a system satisfies the property. Runtime verification deals only with observed executions of systems (generated by the real system), and does not require a model of the system. Runtime verification can be applied to black box system (that is, with knowledge only about the interfaces of the system, without the details of its internals). But, to perform model checking, we need to know all the internal details of a system in order to build an abstract model of the system. The model checking approach also suffers from the state explosion problem [BK08], since the whole state space of the model of the system (all possible executions) is generated. Runtime verification techniques are lightweight, avoiding problems such as state explosion, since only a single execution of the system is considered. Runtime verification can be considered as a form of passive testing, since it does not require to create any special test data, and require only to observe the results/behavior of a running system. Thus, runtime verification can be used in complement to other verification techniques when the system model is too big to handle with model checking, or when the system model is not available, or if the internal details of the system are unknown (that is, when the system is a black-box where only the outputs are observable).

In runtime verification, the complexity of generating the monitor from the specification is generally negligible (since the monitor is generated once, and offline). The complexity of the monitor (the memory it requires and the time it takes), for checking an execution is of interest, since runtime monitors are typically a part of an executing system, and should influence the system minimally.

A brief overview of some runtime verification frameworks Three categories of runtime verification frameworks can be distinguished according to the formalism used to express the input property. In propositional approaches, properties refer to events taken from a finite set of propositional names. For instance, a propositional property may rule the ordering of function calls in a program. Monitoring such kind of properties has received a lot of attention [BLS11].

Parametric approaches have received a growing interest in the last five years. In this case, events in the property are augmented with formal parameters, instantiated at runtime [CR09, BFH<sup>+</sup>12].

In timed approaches, the observed time between events may influence the truthvalue of the property. It turns out that monitoring of timed properties (where time is continuous) is a much harder problem because of (at least) two reasons. First, modeling timed requirements requires a more complex formalism involving time as a continuous parameter. Second, when monitoring a timed property, the problem that arises is that the overhead induced by the monitor (i.e., the time spent executing the monitoring code) influences the truth-value of the monitored property. Consequently, without assumptions and limitations on the computation performed by monitors, not much information can be gained from the verdicts produced by the monitor.

Few attempts have been made on monitoring systems with respect to timed properties. Bauer et al. propose an approach to runtime verify timed-bounded properties expressed in a variant of Timed Linear Temporal Logic (TLTL) [BLS11]. Contrarily to TLTL, the considered logic, TLTL<sub>3</sub>, processes finite timed words and the truth-values of this logic are suitable for monitoring. After reading some timed word u, the monitor synthesized for a TLTL<sub>3</sub> formula  $\varphi$  states verdict  $\top$  (resp.  $\perp$ ) when there is no infinite timed continuation w such that  $u \cdot w$  satisfies (resp. does not satisfy)  $\varphi$ . Another variant of LTL in a timed context is Metric Temporal Logic (MTL), a dense extension of LTL. Nickovic et al. [MNP06, NP10] propose a translation of MTL to timed automata. The translation is defined under the bounded variability assumption stating that, in a finite interval, a bounded number of events can arrive to the monitor. Still for MTL, Thati et al. propose an online monitoring algorithm which works by rewriting of the monitored formula and study its complexity [TR05]. Basin et al. propose an improvement of the aforementioned approach with a better complexity but considering only the past fragment of MTL [BKZ11]. Most of the other works related to runtime verification of timed properties are tools such as AMT [NM07] and LARVA [CPS09a].

One of the important features of runtime verification, compared to the other verification techniques is that it is performed at runtime (analysing a system during its execution). Thus, in addition to detecting errors, runtime verification techniques can be used/extended to act whenever an error/incorrect behavior of a system is detected. The techniques developed for runtime verification are the basis for other techniques dealing with correcting the execution of system at runtime (discussed in the later section).

#### 3.3 Correcting Execution of a System at Runtime