## From dataflow-based video coding tools to dedicated embedded multi-core platforms

Hervé Yviquel

### ► To cite this version:

Hervé Yviquel. From dataflow-based video coding tools to dedicated embedded multi-core platforms. Other [cs.OH]. Université de Rennes, 2013. English. NNT: 2013REN1S095. tel-00939346

## HAL Id: tel-00939346 https://theses.hal.science/tel-00939346

Submitted on 30 Jan 2014

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

THÈSE / UNIVERSITÉ DE RENNES 1 sous le sceau de l'Université Européenne de Bretagne

pour le grade de

## **DOCTEUR DE L'UNIVERSITÉ DE RENNES 1**

Mention : Informatique

École doctorale Matisse

présentée par

# Hervé Yviquel

préparée à l'unité de recherche IRISA (UMR 6074) Institut de Recherche en Informatique et Systèmes Aléatoires École Nationale Supérieure des Sciences Appliquées et de Technologie

## From

**Dataflow-Based**

**Video Coding Tools**

to Dedicated

**Embedded Multi-Core**

## Platforms

### Thèse soutenue à Lannion le 25 octobre 2013

devant le jury composé de :

Alain GIRAULT,

Directeur de recherche, Inria Rhône-Alpes / Rapporteur

## Marco MATTAVELLI,

Maitre d'enseignement et de recherche, École Polytechnique Fédérale de Lausanne / Rapporteur

## Tanguy RISSET,

Professeur des universités, Institut National des Sciences Appliquées de Lyon / Examinateur

Jarmo TAKALA,

Professeur, Tampere University of Technology / Examinateur

**Emmanuel CASSEAU**

Professeur des universités, Université de Rennes 1 / Directeur de thèse

### Mickaël RAULET

Ingénieur de Recherche, Institut National des Sciences Appliquées de Rennes / Co-directeur de thèse

Hervé Yviquel: From Dataflow-based Video Coding Tools to Dedicated Embedded Multi-core Platforms, © 2010-2013

Don't loaf and invite inspiration; light out after it with a club,

and if you don't get it you will nonetheless get something that looks remarkably like it.

— Jack London

#### ABSTRACT

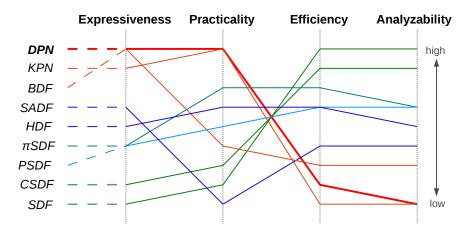

The development of multimedia technology, along with the emergence of parallel architectures, has revived the interest on dataflow programming for designing embedded systems. Indeed, dataflow programming offers a flexible development approach in order to build complex applications while expressing concurrency and parallelism explicitly. Paradoxically, most of the studies focus on static dataflow models of computation, even if a pragmatic development process requires the expressiveness and the practicality of a programming language based on dynamic dataflow models, such as the language included in the Reconfigurable Video Coding framework.

In this thesis, we describe a development environment for dataflow programming that eases multimedia development for embedded multi-core platforms. This development environment is built upon a modular software architecture that benefits from modern software engineering techniques such as meta modeling and aspect-oriented programming. Then, we develop an optimized software implementation of dataflow programs targeting desktop and embedded multi-core platforms. Our implementation aims to bridge the gap between the practicality of the programming language and the efficiency of the execution. Finally, we present a set of runtime actors mapping/scheduling algorithms that enable the execution of dynamic dataflow programs over multi-core platforms with scalable performance.

#### RÉSUMÉ

Le développement du multimédia, avec l'émergence des architectures parallèles, a ravivé l'intérêt de la programmation flux de données pour la conception de systèmes embarqués. En effet, la programmation flux de données offre une approche de développement suffisament flexible pour créer des applications complexes tout en exprimant la concurrence et le parallélisme explicitement. Paradoxalement, la plupart des études portent sur des modèles flux de données statiques, même si un processus de développement pragmatique nécessite l'expressivité et la practicité d'un langage de programmation basé sur un modèle flux de données dynamiques, comme le langage de programmation utilisé dans le cadre de Reconfigurable Video Coding.

Dans cette thèse, nous décrivons un environnement de développement pour la programmation flux de données qui facilite le développement multimédia pour des plates-formes multi-cœr embarquées. Cet environnement de développement repose sur une architecture logicielle modulaire qui bénéficie de techniques modernes de génie logiciel telles que la méta modélisation et la programmation orientée aspect. Ensuite, nous développons une implémentation logicielle optimisée des programmes flux de données ciblant aussi bien les ordinateurs de bureau que les plates-formes embarquées. Notre implémentation vise à combler le fossé entre la practicité du langage de programmation et l'efficacité de son exécution. Enfin, nous présentons un ensemble d'algorithmes de projection et d'ordonnancement d'acteurs qui permettent l'exécution de programmes flux de données dynamiques sur des plates-formes multi-cœur avec des performances extensibles.

Feeling gratitude and not expressing it is like wrapping a present and not giving it.

- William Arthur Ward

First, I would like to thank my advisors Pr Emmanuel Casseau and Dr Mickaël Raulet for their help and support during these three years. Working with both of you has been a very pleasant experience from a scientific point of view, as much as from a human relation point of view. Thank you for your trust in my work, the freedom you let me has been a great source of motivation. Emmanuel, thank you for all your consideration: Your wise advices as well as your ability to take a step back on my work are one of the reasons of the success of my PhD. Mickaël, Thank you for the close and unlimited support: Your expertise in video decoding has always been very helpful to make things working, and our long discussions have helped me to take the right decisions. In fact, working with both of you has been very enriching and I hope that our collaboration will be able to continue.

I would also like to give my thanks to Pr Alain Girault and Pr Marco Mattavelli for reviewing this thesis, and to Pr Tanguy Risset and Pr Jarmo Takala for participating to the jury. All your comments on my work were detailed and very encouraging. Marco, thank you for allowing the multiple collaborations with your team. Tanguy, thank you for you interest on my work. Alain, thank your again for your reviewing: Reading your comments on my thesis was a true pleasure. Jarmo, thank you for your involvement in my PhD: The few months I spent in visit at Tampere have been truly profitable for me.

I would like to extend my thanks to the people that I have had the pleasure to work with. Thanks to the former PhD students for introducing me to the world of Orcc: Matthieu Wipliez, Jérôme Gorin and Nicolas Siret. Matthieu, our never-ending debates have always been a pleasure for me. Thanks to all my collegues with who I have enjoyed working with: Antoine Lorence, Khaled Jerbi, Alexandre Sanchez, Maxime Pelcat, Jean-François Nezan. I would also like to thank Pekka Jääskeläinen for making me feel very welcome during my visit in Tampere. In fact, I would like to thank the Orcc and TCE communities as a whole for actively participating in the development of the tools which offers solid basements to this work. I would also give a special thanks to Angélique Le Pennec and Jocelyne Tremier for managing administrative tasks seamlessly.

Additionally, I would like to thank my family and friends for their support during all these years. Big thanks to my parents and sisters for their love. Thank you for accepting my craziness has it is. Many thanks to all my friends: Thank you for all the good time spent together, for all the incredible parties we have made.

Finally, I would like to give a special thanks to my hidden proofreader that has spent so many nights to fix and improve the English of this thesis.

#### CONTENTS

| 1                               | INTRODUCTION |                |                                              |          |

|---------------------------------|--------------|----------------|----------------------------------------------|----------|

|                                 | 1.1          | Lands          | scape of Embedded Computing                  | 1        |

|                                 |              | 1.1.1          | Embedded Hardware                            | 2        |

|                                 |              | 1.1.2          | Embedded Software                            | 2        |

|                                 |              | 1.1.3          | Embedded System Design                       | 3        |

|                                 | 1.2          |                | approach and Contributions                   | 4        |

|                                 | 1.3          | Outlir         | ne                                           | 5        |

| i                               | BAC          | KGROU          | ND                                           | 7        |

| 2 EMBEDDED PARALLEL PROGRAMMING |              |                |                                              | 9        |

|                                 | 2.1          | Parall         | elism is Everywhere                          | 9        |

|                                 | 2.2          | Embe           | dded Parallel Platforms                      | 10       |

|                                 |              | 2.2.1          | Homogeneous versus Heterogeneous             | 11       |

|                                 |              | 2.2.2          | Memory Architecture                          | 12       |

|                                 |              | 2.2.3          | Memory Hierarchy                             | 13       |

|                                 |              | 2.2.4          | On-Chip Interconnection Network              | 14       |

|                                 | 2.3          |                | el Programming Models                        | 15       |

|                                 |              | 2.3.1          | General-Purpose Parallel Programming         | 16       |

|                                 |              | 2.3.2          | Assisted Parallel Programing                 | 17       |

|                                 |              | 2.3.3          | High-level Parallel Programming              | 18       |

|                                 | 2.4          |                | ing and Scheduling                           | 20       |

|                                 | 2.5          |                | usion                                        | 21       |

| 3                               |              |                | V PROGRAMMING                                | 23       |

|                                 | 3.1          |                | ition of a Dataflow Program                  | 24       |

|                                 | 3.2          |                | ow Paradigm to Enhance Programming           | 24       |

|                                 |              | 3.2.1          | Modular Programming                          | 25       |

|                                 |              | 3.2.2          | Parallel Programming                         | 25       |

|                                 | 3.3          |                | l of Computation                             | 27       |

|                                 |              | 3.3.1          | Kahn Process NetworkDataflow Process Network | 27       |

|                                 |              | 3.3.2          |                                              | 28       |

|                                 |              | 3.3.3          | Static Dataflow Models                       | 29       |

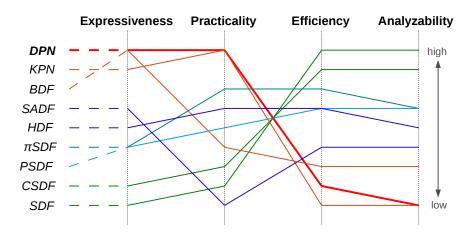

|                                 | 2.4          | 3.3.4<br>Comp  | paring Dataflow MoCs                         | 29<br>20 |

|                                 | 3.4          | 1              | Characterization of Dataflow MoCs            | 30<br>20 |

|                                 |              | 3.4.1          | Taxonomy of Dataflow MoCs                    | 30<br>21 |

|                                 | 3.5          | 3.4.2<br>Dynai | mic Modeling Requires Dynamic Analysis       | 31<br>22 |

|                                 | 3.3          | 3.5.1          | Classification                               | 32<br>22 |

|                                 |              | 3.5.2          | Critical Path Analysis                       | 32<br>22 |

|                                 | 3.6          |                | tion Models                                  | 33<br>34 |

|                                 | 3.0          | 3.6.1          | Multi-Threading                              | 34<br>34 |

|                                 |              | 3.6.2          | Dynamic Scheduling                           | 35       |

|                                 |              | 3.6.3          | Static Scheduling                            | 36       |

|                                 |              | 3.6.4          | Multi-core scheduling                        | 37       |

|                                 | 3.7          | • •            | ng Dataflow-based Languages and Tools        | 38       |

|                                 | 3.8          |                | usion                                        | 39       |

| 4                               | -            |                | URABLE VIDEO CODING                          | 41       |

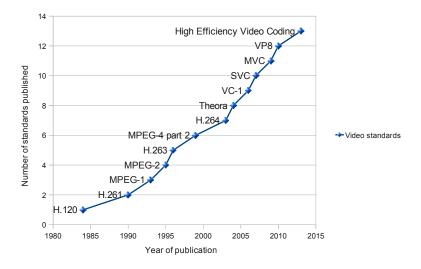

| r                               | 4.1          |                | s of the Standardization Process             | 41       |

|                                 |              | 4.1.1          | Multiplication of the Standards              | 41       |

|                                 |              | 4.1.2          | Monolithic Specifications of the Standards   | 43       |

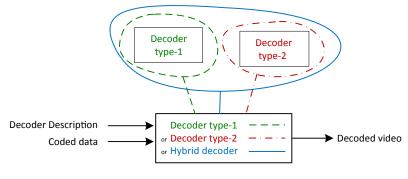

|    | 4.2 | An In<br>4.2.1 | novative Development Framework                       | 43<br>44 |

|----|-----|----------------|------------------------------------------------------|----------|

|    |     | 4.2.2          | Towards the RVC Vision                               | 45       |

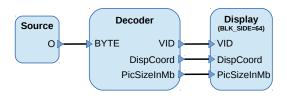

|    | 4.3 | Multir         | nedia-Specific Languages                             | 46       |

|    |     | 4.3.1          | From Text to Visual Network Programming              | 46       |

|    |     | 4.3.2          | Actor Programming Made Easy                          | 48       |

|    | 4.4 | Applie         | cations                                              | 51       |

|    |     | 4.4.1          | Video Codecs                                         | 51       |

|    |     | 4.4.2          | Other Applications                                   | 53       |

|    | 4.5 | Existir        | ng Tools Supporting RVC                              | 53       |

|    |     | 4.5.1          | OpenDF                                               | 54       |

|    |     | 4.5.2          | Orcc                                                 | 54       |

|    | 4.6 | Advar          | nces and Challenges of the RVC Framework             | 55       |

|    |     | 4.6.1          | Tools Development                                    | 55       |

|    |     | 4.6.2          | Applications Development                             | 56       |

|    |     | 4.6.3          | Platform Implementation                              | 57       |

|    | 4.7 | Conclu         | usion                                                | 58       |

|    |     |                |                                                      |          |

| ii | CON | ITRIBU         | TIONS                                                | 59       |

| 5  |     |                | D DEVELOPMENT ENVIRONMENT FOR DATAFLOW PRO-          |          |

|    |     | MMIN           |                                                      | 61       |

|    | 5.1 |                | ced Dataflow-specific Compilation Infrastructure     | 61       |

|    |     | 5.1.1          | Multi-Target Compilation Infrastructure              | 62       |

|    |     | 5.1.2          | Model-driven Compilation Infrastructure              | 63       |

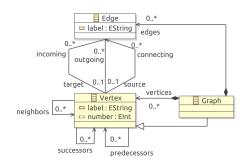

|    |     | 5.1.3          | Unified Graph Library                                | 64       |

|    |     | 5.1.4          | Separation of Concerns                               | 65       |

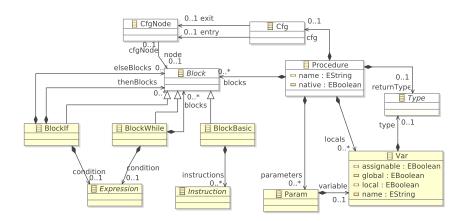

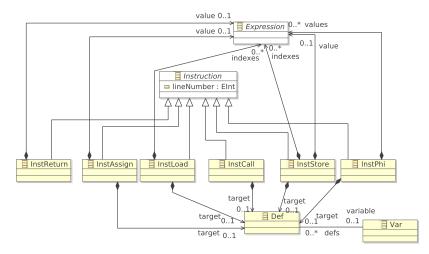

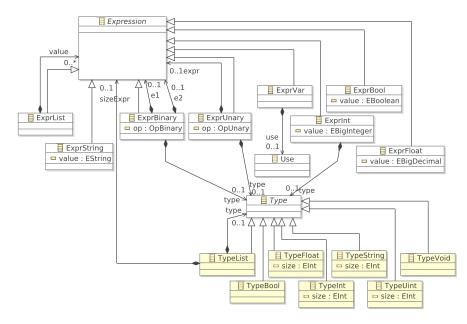

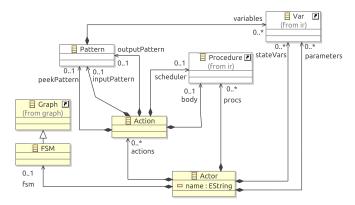

|    |     | 5.1.5          | Procedural Aspect of the Intermediate Representation | 65       |

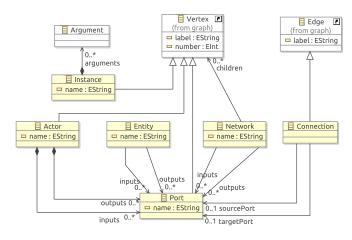

|    |     | 5.1.6          | Dataflow Aspect of the Intermediate Representation   | 68       |

|    | 5.2 |                | ecture Model for Dedicated Embedded Multi-Core Plat- |          |

|    |     |                | D A 12 /                                             | 70       |

|    |     | 5.2.1          | Processor Architecture                               | 71       |

|    |     | 5.2.2          | Predefined Configurations of Processors              | 72       |

|    |     | 5.2.3          | Dataflow-specific Memory Architecture                | 72       |

|    | 5.3 |                | ow Compiler for Embedded Multi-core Platforms        | 74       |

|    |     | 5.3.1          | Multi-stage Co-design Flow                           | 74       |

|    |     | 5.3.2          | Hardware Synthesis                                   | 76       |

|    |     | 5.3.3          | Software Synthesis                                   | 77       |

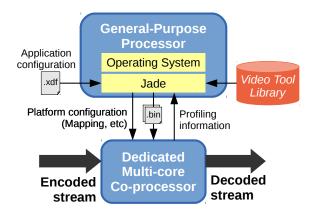

|    |     | 5.3.4          | Simulation Infrastructure                            | 78       |

| (  | 5.4 |                |                                                      | 80       |

| 6  |     |                | O SOFTWARE IMPLEMENTATION OF DYNAMIC DATAFLOW        |          |

|    |     | GRAMS          |                                                      | 81       |

|    | 6.1 |                | mentation of Dataflow Process Networks               | 81       |

|    | 6.2 | 6.2.1          | ized Communications                                  | 82       |

|    |     | 6.2.1<br>6.2.2 | Software Circular Buffer                             | 82       |

|    |     |                |                                                      | 83       |

|    |     | 6.2.3          | Control-Free Communications                          | 84       |

|    |     | 6.2.4          |                                                      | 85       |

|    |     | 6.2.5<br>6.2.6 | Copy-Free Communications                             | 86<br>87 |

|    | 6 - | 6.2.6<br>Optim | Efficient Broadcasting of Communications             | 87<br>88 |

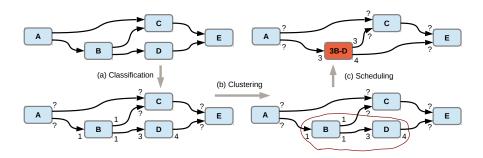

|    | 6.3 | 6.3.1          | ized Scheduling                                      | 88<br>89 |

|    |     | -              | Action Scheduling                                    | -        |

|    |     | 6.3.2<br>6.3.3 | Actor Machine                                        | 89       |

|    |     | 0.3.3          |                                                      | 90       |

|     |     | 6.3.4  | Quasi-Static Scheduling                            | 91  |

|-----|-----|--------|----------------------------------------------------|-----|

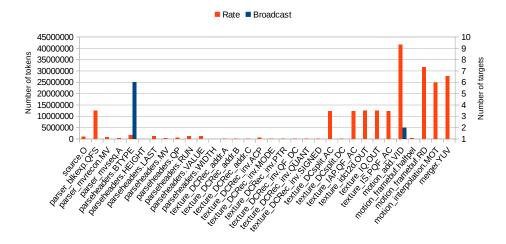

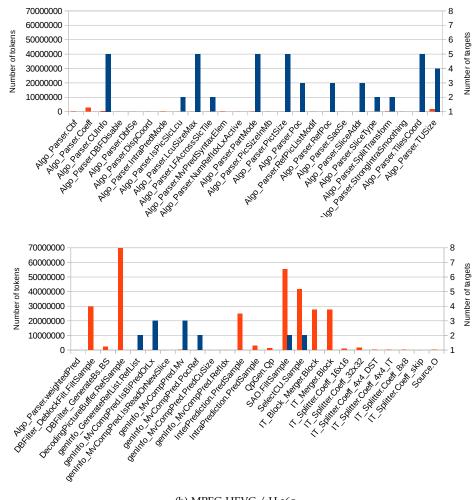

|     | 6.4 | Study  | of RVC-based Video Decoders                        | 92  |

|     |     | 6.4.1  | Experimental setup                                 | 92  |

|     |     | 6.4.2  | Analysis of Global Performance                     | 93  |

|     |     | 6.4.3  | Analysis of Internal Communications                | 94  |

|     |     | 6.4.4  | Analysis of the Application Decomposition          | 95  |

|     |     | 6.4.5  | Comparison of the Scheduling Strategies            | 99  |

|     | 6.5 | Conclu | usion                                              | 101 |

| 7   | SCA | LABLE  | MULTI-CORE SCHEDULING OF DYNAMIC DATAFLOW          |     |

|     | PRO | GRAMS  | 3                                                  | 103 |

|     | 7.1 | Actors | Mapping                                            | 104 |

|     |     | 7.1.1  | Definition of the metrics                          | 104 |

|     |     | 7.1.2  | Evolutionary-based Actor Mapping                   | 105 |

|     |     | 7.1.3  | Graph Partitioning problem                         | 106 |

|     |     | 7.1.4  | Graph partition methodology                        | 107 |

|     |     | 7.1.5  | Mapping Flow                                       | 108 |

|     | 7.2 |        | Scheduling                                         | 109 |

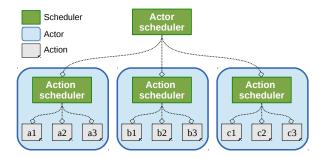

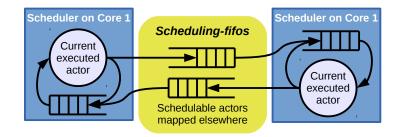

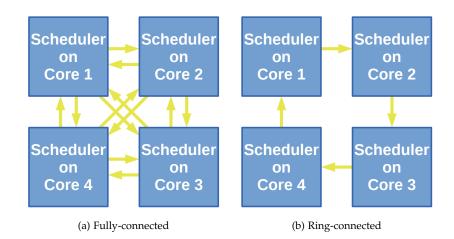

|     |     | 7.2.1  | Distributed Scheduler                              | 109 |

|     |     | 7.2.2  | Multi-core Scheduling Strategies                   | 109 |

|     |     | 7.2.3  | Lock-Free Scheduling Communications                | 110 |

|     | 7.3 | Scalab | ility Analysis of RVC-based Video Decoders         | 111 |

|     |     | 7.3.1  | Experimental setup                                 | 112 |

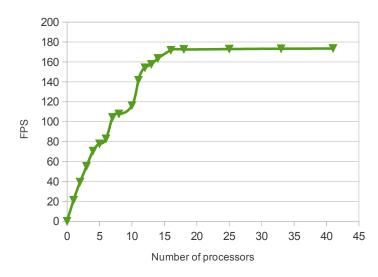

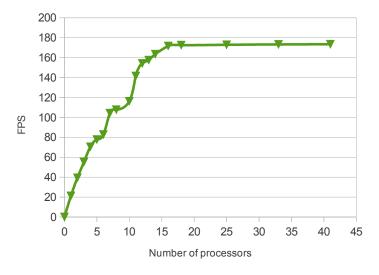

|     |     | 7.3.2  | Desktop Multi-core Implementation                  | 113 |

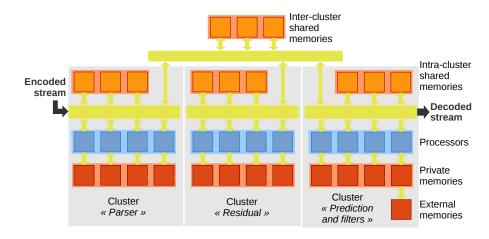

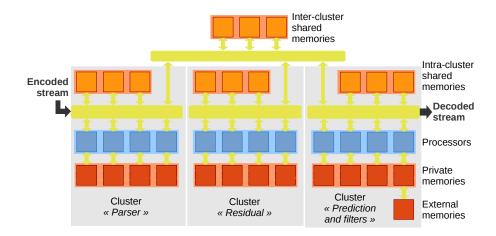

|     |     | 7.3.3  | Embedded Multi-core Implementation                 | 116 |

|     | 7.4 | Conclu | usion                                              | 117 |

| 8   |     |        | ONS AND OUTLOOK                                    | 119 |

|     | 8.1 |        | nary                                               | 119 |

|     | 8.2 | -      | ectives                                            | 120 |

|     |     | 8.2.1  | An Even More Advanced Development Environment .    | 120 |

|     |     | 8.2.2  | An Even More Optimized Software Implementation .   | 121 |

|     |     | 8.2.3  | Towards a Platform Dedicated to RVC-based Video    |     |

|     |     |        | Decoders                                           | 122 |

| iii | API | PENDIX | (                                                  | 125 |

| Α   |     |        | N FRANÇAIS                                         | 127 |

|     |     |        | nes embarqués                                      | 127 |

|     |     | A.1.1  | Matériels embarqués                                | 128 |

|     |     | A.1.2  | Logiciels embarqués                                | 128 |

|     |     | A.1.3  | Conception de systèmes embarqués                   | 129 |

|     | A.2 | 9      | oche et contributions                              | 129 |

|     | A.3 | État d |                                                    | 131 |

|     | 5   | A.3.1  | Programmation flux de données                      | 131 |

|     |     | A.3.2  | Reconfigurable Video Coding                        | 132 |

|     | A.4 | Enviro | onnement de développement dédié                    | 133 |

|     | •   | A.4.1  | Infrastructure de programmation flux de données    | 134 |

|     |     | A.4.2  | Modèle d'architecture dédié                        | 134 |

|     |     | А.4.3  | Co-conception de systèmes embarqués                | 136 |

|     | A.5 |        | mentation logicielle des programmes flux de donnée | 136 |

|     | -   | A.5.1  | Implémentation optimisée                           | 137 |

|     |     | A.5.2  | Implémentation extensible                          | 138 |

|     | А.6 | Conclu | usion et perspectives                              | 138 |

|     |     | A.6.1  | Environnement de développement avancé              | 139 |

|     |     | A.6.2  | Implémentation logicielle optimisée                | 140 |

|     |     |        |                                                    |     |

| A.6.3 Plate-forme dédiée aux codecs vidéo RVC | 141 |

|-----------------------------------------------|-----|

| PUBLICATIONS                                  | 152 |

| BIBLIOGRAPHY                                  | 153 |

To invent an airplane is nothing. To build one is something. But to fly is everything.

— Otto Lilienthal, Aviation pioneer

This thesis investigates pragmatic programming approaches of real-world applications for current and upcoming embedded systems. Actually, the programming experience is becoming a central problem for embedded computing. On the one hand, embedded devices are now complex hardware systems, known as *Multi-Processor System-on-Chip* (MPSoC), that include more and more heterogeneous components on a single chip in order to increase product functionalities and to meet expectations of the embedded market. On the other hand, the complexity of the software deployed on these devices keeps growing exponentially, because these are being used to solve more difficult technical problems. As a result, programmers have to implement increasingly complex applications for increasingly complex devices while respecting time-to-market and cost demand requirements.

This thesis aims at providing a toolkit to ease the development of realworld applications for MPSoC-based platforms from a pragmatic point of view. Thus, we propose to implement and evaluate a set of methodologies for designing embedded systems from the application specification to the platform implementation. In order to benefit from all parallelism present in the algorithms, applications are already specified in a decomposed form, called *Dataflow Process Network* (DPN), by way of a practical dataflow language inheriting from CAL Actor Language. They are latter mapped onto Very Long Instruction Word -like processors which are able to execute multiple operations at the same time. We evaluate the toolkit using state-ofthe-art video decoders, including the emerging High Efficiency Video Coding (HEVC) standard.

Now, let us take a look of the landscape of embedded computing in order to understand the complexity of the problematic that this thesis faces.

#### 1.1 LANDSCAPE OF EMBEDDED COMPUTING

Embedded systems are now widely used, much more than other computing systems with billions sold every year [182], flooding the market of general-purpose computers. Recent analyses have shown a drop in sales of desktop computers in favor of smartphones, tablets and other embedded devices. As opposed to general-purpose computers, embedded systems must meet quantifiable goals: real-time performance, restricted power/energy consumption and market cost. Thus, the design of embedded systems is entirely guided by these quantifiable goals which make it much more challenging than general-purpose computers design.

#### 1.1.1 Embedded Hardware

Up till recent years, embedded devices were designed around a single processor associated with a set of peripherals and hardware accelerators. However, the increasing demand for flexibility from the embedded market has resulted in a migration from hardware to software. In other words, previously hardwired functionalities are now performed by programmable processors.

To handle increasingly demanding applications, the design of higher performance processors was achieved, until recent years, by increasing processor frequency. But, similarly to general-purpose computers, embedded systems have hit the *power wall* of the semiconductor technology, forcing chip manufacturers to look towards multi-core architectures to improve the overall system performance. As a result, embedded systems integrate more and more programmable processors, but contrary to general-purpose computers, most of these processors are tailored to specific tasks in order to bridge the gap between hardware efficiency and software flexibility.

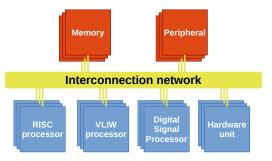

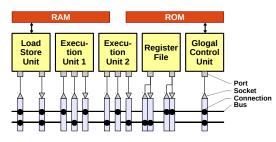

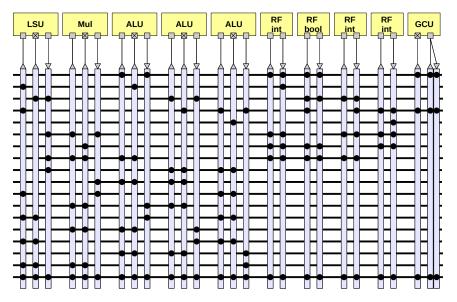

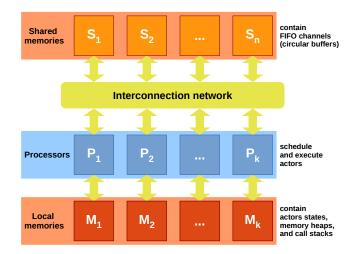

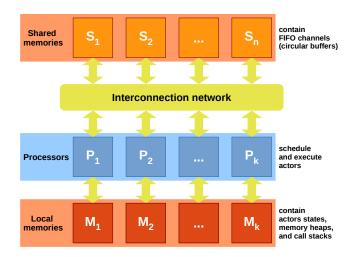

Figure 1: Generic MPSoC-based platform

Embedded devices are now complex heterogeneous multi-core platforms with an increasing number of processor cores so as to meet the performance requirement (Figure 1). For example, commercial many-core platforms like Intel SCC, Tilera TILE or STMicroelectronics SThorm [22] contain already hundred of programmable cores. The increasing number of processor cores has however raised new questions about hardware designs, such as the memory organization and the interconnection network, and about the way to program such a complex architecture.

#### 1.1.2 Embedded Software

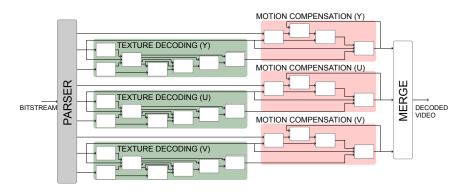

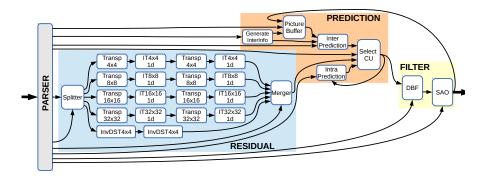

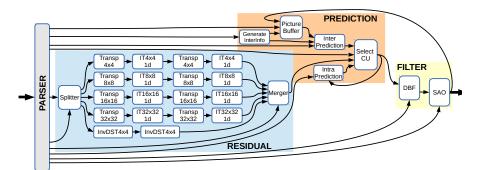

Early forms of embedded software were small programs usually written in assembly to get maximal performance. They can be now complex applications containing multiple algorithms [183]. Moreover, the nature of the computations performed in different parts of the application can vary widely (types of operations, memory requirement, parallelism, etc). As a matter of fact, this variability matches well with heterogeneous architectures. As an example, considering the structure of modern video decoders [150], the motion compensation has clearly the largest requirement in memory space and bandwidth, while the residual decoding and the intra prediction are mostly computational.

The embedded market is currently driven by user application demands increasing the complexity of embedded software. For instance, on the one hand, the new video compression standard namely HEVC reduces bit-rate requirement by 50% with same picture quality as its predecessor, and thus allows higher-definition video. On the other hand, HEVC standard increases the computational complexity by 1.6x compared to its predecessor [171]. Complex applications are often limited to certain application domains like multimedia and communication. For example in a 3G phone, above 60% of the power and over 90% of the available performance are consumed by radio and multimedia applications [170].

Beyond the heterogeneity and the complexity of the applications, targeting multi-core platforms raises new questions concerning embedded software, such as the application decomposition in parallel tasks as well as the mapping and scheduling of these tasks on the multi-core platform.

#### 1.1.3 Embedded System Design

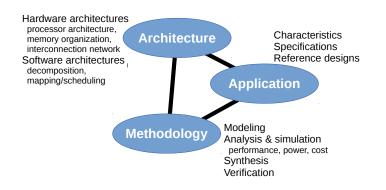

Today, embedded computing is confronted to a fast technology evolution and a great variety of computing systems. Therefore, highly flexible design processes are required. As a matter of fact, the design of embedded systems can be decomposed in three aspects (architecture, application and methodology) as illustrated in Figure 2.

Since software and hardware are tightly coupled in embedded system design, embedded designers have to consider all architectural aspects including the organization of the hardware components (processors, memories, interconnections), the decomposition of the software in tasks in order to benefit as much as possible from the parallelism, and the mapping between the hardware and the software to get the best performance. Additionally, designers have to deeply understand their applications to take advantage of all possible optimizations. Finally, methodologies are central for successful embedded system design. Modeling provides higher-level of abstractions that are necessary to handle the growing complexity of embedded systems. As regards to the difficulty of analyzing and debugging hardware platforms, simulation and analysis are necessary to determine the efficiency and the cost of the design. Model-based design requires synthesis tools translating high-level specifications into optimized implementations. Moreover, automatic verification processes are also essential to achieve the required reliability level with minimal cost.

Figure 2: Aspects of embedded system design (adapted from Wolf's analysis [182])

In conclusion, tools are particularly important in embedded system design. Tools allow rapid design of embedded systems to deal with time-tomarket pressure while achieving their high constraints of efficiency and reliability. 3

#### 1.2 OUR APPROACH AND CONTRIBUTIONS

The emergence of massively parallel architectures, along with the need for modularity in software design, has revived the interest in dataflow programming. Indeed, dataflow programming offers a flexible development approach which is able to build complex applications while expressing concurrency and parallelism explicitly. Paradoxically, most of the studies stay focused on static dataflow programming, even if a pragmatic development process requires the expressiveness and the practicality offered by dynamic dataflow programming.

MPEG has however introduced an innovative framework, called *Reconfigurable Video Coding* (RVC), that can be considered as the first large-scale experimentation on dynamic dataflow programming to our knowledge. RVC has been initially introduced to overcome the lack of interoperability between the various video codecs deployed in the market. The framework allows the development of video coding tools, among other applications, in a modular and reusable fashion thanks to the inclusion of a subset of CAL programming language.

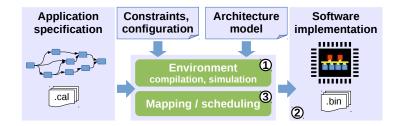

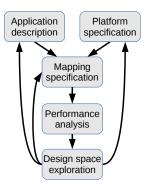

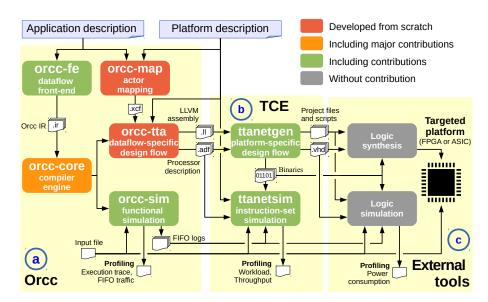

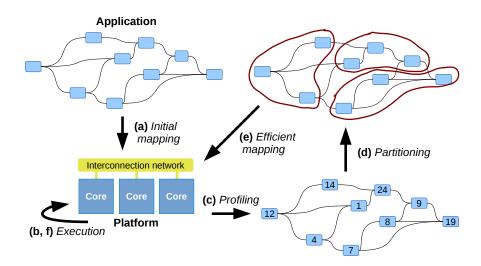

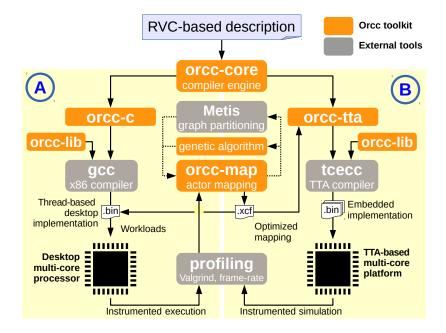

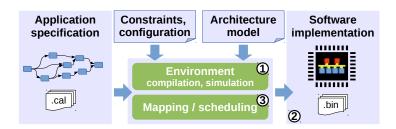

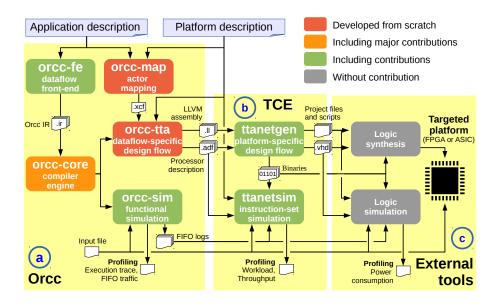

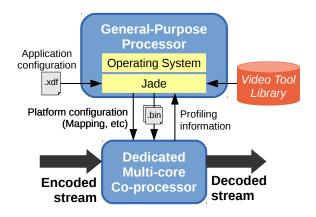

Figure 3: Contributions of this thesis on dataflow-based embedded system design

All along this thesis, we study all steps of the development of RVC-based video decoders (Figure 3), from their specification based on the dataflow paradigm to their implementation on embedded multi-core platforms. This thesis makes the following contributions:

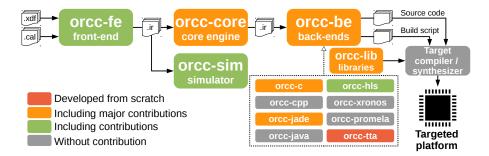

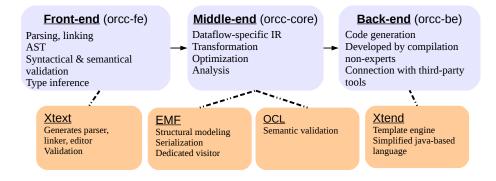

- **Contribution 1** [5, 7, 2, 3]: An entire co-design flow to develop RVCbased applications for embedded multi-core platforms. The co-design flow relies on a advanced simulation process and a dedicated architecture model. Additionally, the multi-target compilation infrastructure underlying our co-design flow has been enhanced by the way of modern software engineering techniques such as *Model-Driven Engineering* (MDE).

- **Contribution 2** [8, 1]: An optimized software implementation of dynamic dataflow programs based on efficient communication techniques that limit the accesses to the memory, and based on advanced scheduling strategies that reduce the overhead of the scheduling.

- Contribution 3 [4, 6]: A set of actor mapping/scheduling algorithms executable at runtime in order to handle the unpredictable behavior of dynamic dataflow programs, and to achieve scalable performance over multi-core platforms, either desktop multi-core processors or embedded multi-core platforms.

In addition to the specification of our dataflow-based development process, we evaluate the efficiency of this contribution using a set of video decoders, including a decoder based on the HEVC standard, that were implemented within the RVC framework.

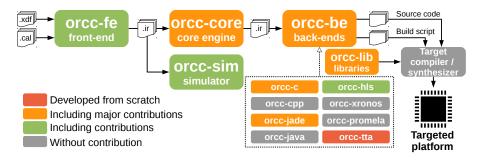

All this work has been implemented within two open-source software: a dataflow-based development environment known under the name of Open RVC-CAL Compiler (Orcc) [134], and a co-design toolkit using Transport-Trigger Architecture (TTA) as the architecture template called TTA-based Co-design Environment (TCE) [166].

#### 1.3 OUTLINE

This thesis is decomposed in two distinct parts as follows. Part I contains an introduction to the global notions and research problems discussed in this thesis, and details also the previous works that lead to our work. Chapter 2 explores the existing programming models of embedded multi-core platforms including the influence of the hardware architecture. Then, Chapter 3 focuses on dataflow programming and shows the pragmatism underlying the dynamic dataflow model for software development. Finally, Chapter 4 introduces the Reconfigurable Video Coding framework, and deeply inspects its current state for highlighting the open challenges of the approach.

Part II contains the contributions and proposed techniques of this thesis. Chapter 5 starts by introducing the tool flow. Chapter 6 details our optimized software implementation of dynamic dataflow programs. Chapter 7 closes this part by proposing a set of actor mapping/scheduling algorithms in order to obtain scalable performance on multi-core platforms.

Part I

### BACKGROUND

#### EMBEDDED PARALLEL PROGRAMMING

We have seen that computer programming is an art,

because it applies accumulated knowledge to the world, because it requires skill and ingenuity, and especially because it produces objects of beauty.

— Donald E. Knuth [114]

Embedded computing has emerged in early in the history of computer sciences. Already in 1951, a group of researchers from the MIT have built the Whirlwind computer, the first real-time computer, which was adopted by the U.S. Air Force to integrate its air defense system. Latter in 1966, the Apollo Guidance Computer was designed at the MIT to integrate the navigation system that controls the spacecraft of the Apollo program. While the Whirlwind can hardly be considered as an embedded system because of its impressive dimensions, the Apollo Guidance Computer was embedded in the aircraft modules of several lunar missions requiring more compact dimensions. Since this time, embedded systems have massively gained in popularity, and are now everywhere.

Similarly, processor programming has moved well beyond the early days of assembly programming of 8-bit micro-controllers. The advances in compilation have allowed the translation of high-level language programs into efficient machine code. As a consequence, the developer simply writes his application keeping its attention on software aspects, and lets the compiler in charge of code optimization to reach the expected performance.

The physical limitations of current semiconductor technology have made it increasingly difficult to achieve frequency improvements in processors. Thus, hardware designers have organized computers, including embedded systems, into multi-core architecture to achieve the performance required for current applications. This raise of parallel computing has however introduced new challenges to both programmers and compiler developers. On the one hand, the programmers have to describe their application in such a way that the compiler is able to decompose it in parallel computations. On the other hand, the compiler has to translate the application to machine code that can exploit all the parallel ability of the executing platform.

#### 2.1 PARALLELISM IS EVERYWHERE

The execution of an algorithm onto multiple processing units involves parallelism which can be defined as the *decomposition* of the computation into multiple pieces that can be executed in parallel [169].

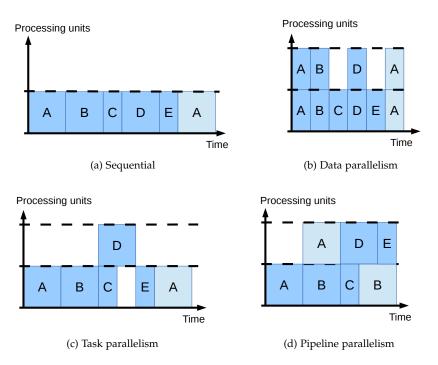

Let us differentiate the *granularity* of the decomposition (fine-grain and coarse-grain) from the *form* of the decomposition (task, data and pipeline parallelisms). On the one hand, the granularity of the parallelism describes the amount of computation in relation to communication [156]. During this thesis, we distinguish only fine and coarse granularities:

- **Fine-grain parallelism** refers to *instruction-level parallelism* that has been typically exploited by Very Long Instruction Word (VLIW) and super-scalar processors.

- **Coarse-grain parallelism** refers to *task-level parallelism*, also called *thread-level parallelism*, that has been typically exploited by multi-processor platforms.

On the other hand, the form of the parallelism describes the decomposition of the computation into multiple chunks of smaller entities:

- **Data parallelism**, requiring *data decomposition*, is the simultaneous execution of the same computation across different datasets.

- **Task parallelism**, requiring *functional decomposition*, is the simultaneous execution of different computations across the same or different datasets.

- **Pipeline parallelism**, requiring *temporal decomposition*, is the simultaneous execution of multiple stages of a given computation. To achieve pipelining, the computation must be applied repeatedly and must be subdivided into a sequence of subtasks. The subtasks can then be performed in an overlapped fashion.

Combining all forms and granularities in *multi-level parallelism* (Table 1), let us fully exploit the potential parallelism of the application. The challenge is then to leverage the multi-level parallelism according to the processing capabilities of the platform.

|          | Fine-grain          | Coarse-grain          |  |

|----------|---------------------|-----------------------|--|

|          | Instruction, Loop   | Procedure, Subprogram |  |

| Task     | VLIW instruction    | Concurrent thread     |  |

| Data     | Vectorization       | Kernel function       |  |

| Pipeline | Software pipelining | Thread pipelining     |  |

Table 1: Parallelism is multi-form and multi-level

#### 2.2 EMBEDDED PARALLEL PLATFORMS

Computer systems have traditionally been characterized by their Instruction Set Architecture (ISA). The ISA provides the visible interface to program the processor: the operations available, the number of operands necessary for a given operation, as well as the type and the size of the operands, and the storage locations that are available. Computer systems are then categorized depending on the complexity of their instruction sets, known as Reduced Instruction Set Computer (RISC) and Complex Instruction Set Computer (CISC). The development of specialized processors such as Application-Specific Instruction-Set Processor (ASIP) and Digital Signal Processor (DSP), and the emergence of heterogeneous and hybrid systems make this classification outdated.

The most popular taxonomy of parallel systems has been introduced by Flynn in 1972 [77]. Flynn classifies computer organization according to the multiplicity of the hardware resources provided to the instruction and data streams :

- **Single Instruction Single Data streams (SISD)** computer organization represents traditional serial processors. Instructions are executed sequentially but may be overlapped in their execution stages.

- **Single Instruction Multiple Data streams (SIMD)** computer organization represents most Graphics Processing Units (GPUs) available today. Multiple processing elements execute simultaneously the same instruction but operate on different data sets from distinct data streams.

- **Multiple Instruction Single Data streams (MISD)** computer organization represents systolic arrays. Multiple processing units execute distinct instructions over the same data stream and its derivatives. The results of one processing unit become the input of the next processing unit in the array.

- Multiple Instruction Multiple Data streams (MIMD) computer organization represents multi-core platforms. Multiple processing elements execute distinct instructions which are operating over distinct data streams.

Obviously, the last three classes of computer organization are the classes of parallel computers.

#### 2.2.1 Homogeneous versus Heterogeneous

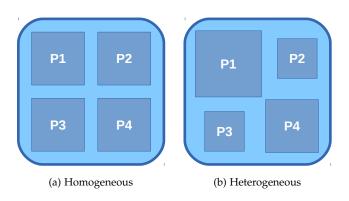

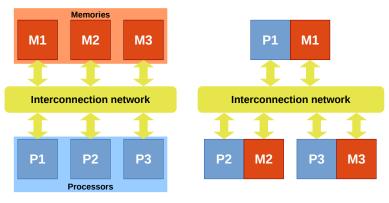

Knowing that multi-core platforms are by definition composed of multiple cores, they can be classified as *homogeneous* or *heterogeneous* (Figure 4):

- Homogeneous platforms are composed of identical cores (Figure 4a). For instance, Texas Instruments commercializes a set of homogeneous multi-core platforms (excluding hardware accelerators), known as Key-Stone TMS320C667x family, that targets a large range of application domains including machine vision and software defined radio.

- Heterogeneous platforms are composed of different types of cores (Figure 4b) that make their programming more challenging. The heterogeneity can however refer to several aspects of the processor cores (frequency, ISA, etc). For instance, the big.LITTLE MP is an heterogeneous architecture developed by ARM coupling a low power Cortex-A7 processor with a more powerful Cortex-A15 processor, both sharing the same ISA [92]. Nvidia commercializes another type of heterogeneous Multi-Processor System-on-Chips (MPSoCs), known as the Tegra's family, that are composed of an ARM processor and a Geforce GPU.

In fact, most of modern MPSoCs are heterogeneous and embed in the same chip General-Purpose Processors (GPPs), DSPs and hardware accelerators, but homogeneous organizations can still be present locally. As an example, the STHORM multi-core platform developed by STMicroelectronics is composed of homogeneous clusters of processors [22].

Heterogeneity is obviously the solution to handle all forms and levels of parallelism that are present inside the algorithms. Heterogeneity makes however the implementation process of applications exponentially harder by adding new constraints to the application mapping and scheduling, and by requiring multiple compilation flows.

Multi-core platforms are not only characterized by the architecture of their processor cores but also by their memory architecture.

Figure 4: Processor architectures characterizing multi-core platforms

#### 2.2.2 Memory Architecture

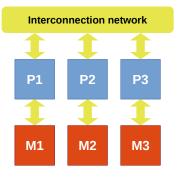

Multi-core systems are traditionally based on shared-memory architectures, i.e. multiple processors fully connected to one or multiple memory modules through an interconnection network with no access restriction. As the number of processors grows (many-core processors already comprise hundreds of cores), it quickly becomes impossible for a centralized memory system to meet the bandwidth needs of the processors. Then, distributed memory system becomes a necessity [147].

Memory architectures are usually classified as follow [185]:

- Uniform Memory Access (UMA): The memory is shared and can be accessed uniformly by all processors (Figure 5a), in other words the processors have an equal access and access times to any memory location. In UMA, all the processors are tightly-coupled with the memory components. Such a centralized memory architecture is commonly used in GPP such as the ARM Cortex A-15.

- Non-Uniform Memory Access (NUMA): The memory is shared and can be similarly accessed by all processors but not with an equal access time (Figure 5b). In NUMA, processors and memory components are clustered making the memory accesses across the clusters slower but still possible. For instance, in Figure 5b the processor P1 can access both memories M1 and M2, but accessing M1 will be much faster than accessing M2 because P1 and M1 are tightly-coupled.

- NO Remote Memory Access (NORMA): The memory is not shared by the processors, i.e. distributed memory, but the processors can communicate directly through the interconnection network by the way of a dedicated communication protocol (Figure 5c). IBM's Cell processors are popular NORMA-based commercial platforms [109].

The memory architecture of multi-core platforms impacts directly the programming of processors. Therefore, the programming of shared-memory platforms and distributed-memory platforms is usually very different.

On the one hand, the programming of shared-memory systems stays closely similar to the programming of uniprocessor systems, which makes it easier to be handle by the developers. In fact, communication among processors is simply achieved by writing to and reading memory locations since all processors are allowed to see data written by any processor. But, multiple

(a) Uniform Memory Access

(b) Non-Uniform Memory Access

(c) NO Remote Memory Access

Figure 5: Memory architectures characterizing multi-core platforms

processors may access the same memory location concurrently and cause unexpected behaviors, usually called *race conditions*. Thus, the synchronization among processors is required and usually achieved using locks and barriers.

On the other hand, the programming of distributed-memory systems requires additional interfaces to handle communication among processors. Since each processor has its own memory system, a processor must communicate explicitly with the other processors to exchange data using dedicated methods such as message passing. Thus, programming distributed-memory systems is not as natural as shared-memory systems. For instance, IBM's Cell processors suffer from the complexity of their programming.

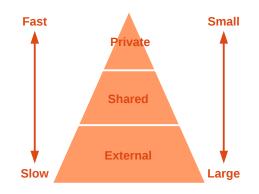

#### 2.2.3 Memory Hierarchy

Similarly to uniprocessor, designing multi-core platform on top of hierarchical memory organization (Figure 6), brings several advantages:

- Reduction of the latency of memory accesses by replicating data in small and fast memory components.

- Reduction of the demands of external memory bandwidth by exploiting *spatial locality* and *temporal locality* of data accesses within algorithms.

As we have seen, shared-memory systems do not scale well when the number of processors increases: the interconnection network connecting the

#### 14 EMBEDDED PARALLEL PROGRAMMING

processors to the shared memory becomes a bottleneck when too many processors are trying to access it simultaneously. Therefore, the introduction of a private level to the memory hierarchy limits the contention on the interconnection network. But, the memory being shared, the replication of data at private-level introduces a problem of consistency between the memory components, when a data is replicated and goes out of synchronization with the original values where the modifications have taken place. Consequently, the systems have to ensure the coherency between the memory components.

Figure 6: Hierarchical memory organization for multi-core platforms

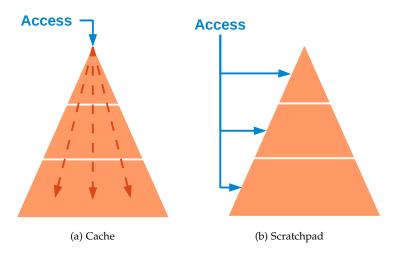

In embedded systems, two types of hierarchical memory, known as cache and scrachpad memories, are dominating the market (Figure 7):

- CACHE Data replication is controlled by the hardware that automatically loads the data when needed, providing transparent memory accesses to the developers but implying unpredictable access time [161] (Figure 7a). In fact, cache mechanism has been extensively used and studied in general-purpose computing.

- SCRATCHPAD Data replication is controlled by the software, done explicitly by the developer or added automatically by the compiler [19, 18] (Figure 7b). In fact, predictability is the key attribute of scratchpad memories [182]. All data movement being solved at compile-time, scratchpad memories have a smaller power consumption than caches.

Even if cache and scratchpad memories have different approaches to solve the *memory wall*, they may be mixed in the same system to benefit from all aspects.

#### 2.2.4 On-Chip Interconnection Network

The interconnection network is responsible for the exchange of information between the components of the multi-core platform. Consequently, the global performance of the multi-core platform is directly affected by the efficiency of its interconnection network. Two types of exchange are possible:

- Simple accesses from processors to memories.

- Direct communication from a processor to another, to provide message passing facility.

Figure 7: Hardware versus software implementation of hierarchical memories

Two types of interconnection network are dominating for intra-chip communication, bus and Network-on-Chip (NoC). We sum up their properties in Table 2.

BUSES Bus interconnect has been the dominant architecture for intra-chip communications, but its lack of scalability makes it clearly not suitable for massively parallel systems. One the one hand, bus-based systems provide high-speed communication and large communication bandwitch while keeping low-cost implementation and easy testability. On the other hand, it suffers from a number of drawbacks such as a poor scalability, no fault tolerance, and a limited parallelism exploitation. Actually, even a well-designed bus-based system may suffer from data congestions that limit the global performance of the system. It is also not inherently scalable. As more and more modules are added to a bus, not only data congestion increases, but power consumption also rises due to the increased load presented to the bus driver circuits.

NETWORK-ON-CHIP NoC is another interconnection scheme that has the potential to overcome the limitations of bus-based interconnections. In a NoC-based system, the components are connected via a multistage switching system composed of point-to-point links. Such a multistage interconnection avoids the scaling issues of long wires. Since several paths may be available in the network, the switches dynamically route the data according to the communication traffic, similarly to networking theory. Consequently, the scalability of the interconnection network comes at the expense of the variability in memory access latencies (i.e.NUMA) as well as increased design complexity to guarantee correctness and fairness and to avoid deadlocks and starvations.

#### 2.3 PARALLEL PROGRAMMING MODELS

Programming languages are historically sequential, making the programming of modern embedded platform a challenge. In their survey about MPSoC design methods and tools [138, 137], Park et al. classify the exist-

|     | Pros             | Cons              |

|-----|------------------|-------------------|

| Bus | High-speed       | Scalability       |

|     | Low-cost         |                   |

|     | Large bandwidth  |                   |

| NoC | High-speed       | Design complexity |

|     | Scalability      | Variable latency  |

|     | Power efficiency |                   |

Table 2: Comparison of interconnection networks

ing programming approaches of MPSoC based on the initial specification of the applications as follows:

- Compiler-based approaches that use compilation techniques to automatically extract the parallelism from the sequential description of an application,

- Language-extension approaches that ask the programmer to provide additional parallelism information into the description of the application using directives or Application Programming Interface (API) in order to help the compiler during the parallelizing stage,

- Model-based approaches that rely on Model of Computations (MoCs) to describe an application to abstract the parallel description of the application, and

- Platform-based approaches, an additional category introduced by Park as a model-based approach that embeds parallel information and architectural constraints.

Park's taxonomy clearly shows the challenge of programming multi-core platforms by exposing the variety of studies about MPSoCs programming but it suffers from few aspects. First, his classification does not highlight the tight link between the platform architecture and its programming. Then, the last category only is a bit artificial since it only includes his own work. As a consequence, we organized our overview of parallel programming approaches for embedded systems as follows: General-purpose programming, assisted programming, and high-level programming.

#### 2.3.1 General-Purpose Parallel Programming

Programming languages are designed to create programs that control computers on which they are running. Knowing that, most general-purpose programming models directly inherit from an underlying processor architecture. Like imperative programming inherits from the Von Newman architecture, both ensure a sequential execution of the instructions according to the control flow. Similarly, parallel programming models inherit from the architecture of parallel platforms. For instance, multi-threading abstracts sharedmemory architecture, message-passing abstracts distributed-memory, and stream processing abstracts GPU-like architecture.

MULTI-THREADING Definitely the most widely used parallel programming model, that is to say multi-threading, is based on the parallel execution of tasks, called threads, that share a single address-space. The shared memory makes multi-threading ideal to program platforms based on shared memory architecture. But, in the thread model, the programmer has to handle every low-level details, from the creation of the threads to their synchronizations. In fact, multi-threading requires synchronization primitives, such as semaphores, to handle concurrent memory accesses.

A well-know implementation of the thread model is the POSIX threading library *pthread*.

MESSAGE PASSING Another well-known parallel programming model is message passing in which the developer describes a set of concurrent processes that exchange data by sending and receiving messages. In contrast with multi-threading, message-passing systems have been introduced to program platforms based on distributed memory architecture. In messagepassing systems, communications may be point-to-point, collective, synchronous, or asynchronous. Synchronous communications, also called *rendezvous*, require sender and receiver to wait for each other in order to transfer a message, synchronizing the processes and removing the need for buffering mechanism. Asynchronous communication simply delivers a message from the sender to the receiver without any assumption on the availability of the receiver.

Message Passing Interface (MPI) is a standardized message-passing system resulting of a joint effort of academician and industrial researchers [79]. While MPI has been heavily used in High Performance Computing (HPC), the emergence of NoC-based interconnection network has revived the interest of MPI for programming embedded multi-core platforms [75, 108].

STREAM PROCESSING More recently, the development of General-Purpose Processing on GPUs (GPGPU) has revived this interest for an SIMD-related programming model usually called stream processing. Instead of describing task parallelism, this model focuses on computations, usually called *kernels*, that can be applied simultaneously on a large panel of data. Data-parallel programming is usually built on top of an abstract architectural model composed of one *host* that controls the execution and a set of *devices* in which the kernels are executed. Because the kernels usually operate on huge amount of data, the developer has to manage precisely the data transfers between host and devices.

OpenCL and CUDA are well-know GPGPU-based implementations of stream processing principle. OpenCL is developed by Khronos as a standard for heterogeneous computing while CUDA is provided by Nvidia in order to give GPGPU facilities to their products. Brook [40] is another programming language, developed at Standford university, that inherits directly from stream processing.

#### 2.3.2 Assisted Parallel Programing

General-purpose parallel programming is clearly error-prone and usually requires from the developer a real expertise about parallel computing to take care of low-level details. A large portion of applications is already written in a sequential way, and knowing that modifying an existing application is a well-known source of bugs, many efforts have been made to provide assisted parallelization methodologies. AUTOMATIC PARALLELIZATION The ultimate goal, the *Holy Graal* of parallel computing, is the automated extraction of parallelism from the sequential description of the application. Early parallelization studies have focused on the extraction of instruction-level parallelism for VLIW processors. More recently, the extraction of fine-grain data parallelism, so-called *vectorization*, has been studied to take advantage of SIMD instructions such as Intel's MMX and ARM's NEON for general-purpose processors. However, embedded platforms require also a coarser decomposition to really benefit from multi-core architecture.

Most of coarse-grain parallelization techniques start by analyzing the program statically, to identify time-consuming portions and dependences, then try to decompose it in parallel tasks using heuristics. In order to overcome static analysis limitations, some studies propose to identify hidden parallelism, then expose it with the help of the developer [48]. Others studies used optimization techniques such as machine learning [47], integer linear programming [53, 54] or genetic algorithms [52] but they require execution profiling and may be time-consuming.

In fact, the efficiency of automatic parallelization remains limited on irregular applications. Generally speaking, automatic parallelization approaches suffer from a lack of knowledge about the application domain. Consequently, restricting general-purpose languages, or else extending the program with additional information, may improve the parallelization by making easier the analysis.

DIRECTIVE-BASED PROGRAMMING Directive-based programming aims at providing a rapid and easy-going parallelization methodology to the developer. Traditional programming languages are extended with a set of directives (such as *pragma* in C) that informs the compiler about the parallelism potential of certain portions of the program, usually loops but also parallel sections and even pipeline sections [122, 145].

1 #pragma omp parallel for

2 for (i = 0; i < N; i++) {

3 a[i] = 2 \* i;

4 }</pre>

Listing 1: One simple directive to parallelize a loop

OpenMP [57] is a standardized language extension (Listing 1) which relies on multi-threading. OpenMP is probably the most popular directive-based programming interface. OpenACC [133] is an emerging standard that aims to make easier GPGPU, similarly to HMPP [62].

#### 2.3.3 High-level Parallel Programming

Embedded computing usually relies on programming techniques that have been developed for general-purpose processors, but the specificities of embedded systems make their programming more challenging. Embedded systems have to meet memory footprint constraints, real-time performance constraints, as well as power consumption constraints. General-purpose parallel programming is error-prone and assisted parallelization of sequential programs is limited by nature. Thus, higher-level programming approaches aim to providing useful abstractions and optimization tools to efficiently program embedded systems. ALGORITHMIC SKELETONS Algorithmic skeletons are a high-level programming model that takes advantage of common programming patterns to hide the complexity of parallel programming [51]. Similarly to software design patterns, algorithmic skeletons define general programming solutions to solve common occurring problems. But, while software design patterns focus on software design, algorithmic skeletons provide parallel resolution of computational problems.

Algorithmic skeletons aim to be an effective, generic and high-level approach for parallel programming. To do so, a skeleton is both composed of a generic interface that abstracts parallel computations, communications, or interactions, and of an implementation that handles all low-level details related to the parallelization. The synchronization between the parallel computations is hidden by the implementation of the skeleton, reducing the risk of errors and making the code more portable.

Dozens of patterns have been proposed since the introduction of algorithmic skeletons as a solution for parallel programming. These patterns can be classified in three families [85]:

- Data-based patterns: Map, Fork, Reduce.

- Task-based patterns: Pipe, For, While, If.

- Resolution-based patterns: Divide & Conquer, Branch & Bound.

Obviously, algorithmic skeletons are not the ultimate solution of parallel programming but provide a set of best practices that have been proven useful.

DATAFLOW PROGRAMMING Dataflow programming is another high-level programming method that describes parallel applications inherently [58]. A dataflow program is described as a directed graph composed of a set of computational units interconnected by communication channels. Dataflow programming being also graphical, it is a very natural way for describing parallel algorithms. And, contrary to general-purpose parallel programming, dataflow programming is not built upon an underlying computer architecture.

In fact, dataflow programming is related to message passing in the sense that it describes a set of concurrent processes interacting by explicit communications. But, contrary to message passing, dataflow programming is build upon a strict formalism that provides useful abstractions and enables advanced analysis. For instance, the developer has to describe explicitly the communication network, so two processes cannot communicate directly if they are not linked by a communication channel. Dataflow programming being the main subject of Chapter 3, no more details are given here.

DOMAIN-SPECIFIC LANGUAGE As defined by Van Deursen et al. [61], a Domain-Specific Language (DSL) is a programming language or executable specification language that offers, through appropriate notations and abstractions, expressive power focused on, and usually restricted to, a particular problem domain. Thus, DSLs can provide knowledge about the application domain that is lacking in general-purpose languages, in order to allow automatic parallelization for example. Additionally, DSLs intend to be written by domain experts and not by experts in parallel programming.

For example, Streamit [168] and Halide [148] are DSL that inherit directly from stream processing. In contrast with general-purpose languages such as

OpenCL and CUDA, Streamit and Halide target especially signal processing applications and intend to simplify their development by providing a higher abstraction of the underlying architecture.

#### 2.4 MAPPING AND SCHEDULING

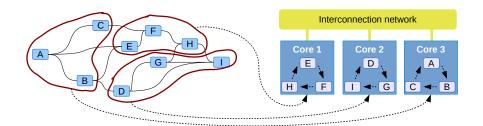

In contrast with traditional compilers that stay focused on instruction scheduling, MPSoC-based compilation flows have to take advantage of the parallel processing capabilities of multi-core platforms to satisfy the performance constraints of the applications. Let us assume that the application has been previously decomposed into small tasks using automatic, assisted or manual techniques. Then, the tasks composing the application are mapped and scheduled onto the executing platform, two distinct processes that are intimately related:

- The **mapping** is the process of assigning a processor to a task, in other words *where* the task is executed, that involves the *partitioning* of the pool of tasks.

- The **scheduling** is the process of deciding the moment of the execution of a task, in other words *when* the task is executed, that involves the *ordering* of the tasks and the *timing* of their execution.

The mapping and scheduling problem is a NP-hard problem, equivalent to *Quadratic Assignment Problem* [81]. Thus, many heuristics aim to find a nearly optimal solution satisfying all the given constraints. The heuristics depend on both the application description, usually represented as a *task graph*, and the platform specification, based on an *architecture model* such as S-LAM [140] or AADL [74], as well as the architecture model used in Syndex [91]. Due to the inherent constraints of embedded systems, mapping and scheduling heuristics may target power consumption and reliability, additionally to execution performance.

As presented in Table 3, Lee and Ha have classified the different approaches according to the moment, **run-time** or **compile-time**, when the mapping, ordering and timing stages are performed [118]. On the one hand, fully dynamic approaches can efficiently balance the workload of any application over the processors by making all decisions at run-time, but they come at the cost of a larger execution overhead. On the other hand, fully static approaches determine all decisions at compile-time to minimize the execution overhead, but they are only suitable for a subset of applications that do not have dynamic behavior. Static-assignment approaches partition the tasks over the processors at compile time to reduce the execution overhead at the cost of the load-balancing, and self-timed approaches additionally determine the ordering of the task execution at compile-time without notion of the time. Additionally, compile-time approaches bring guarantees on the obtained schedule which is a central benefit for safety critical systems. Indeed, proving real-time constraints on dynamic scheduling is difficult.

Similarly, Singh et al. introduce additional criteria to characterized scheduling and mapping methodologies [155]:

• Mapping methodologies can target either **homogeneous** platforms, composed of identical cores, or **heterogeneous** platforms, composed of different types of cores, as introduced previously by Section 2.2.1. The heterogeneity of multi-core platforms imposes additional parameters to mapping heuristics.

|                   | Mapping | Ordering | Timing  |

|-------------------|---------|----------|---------|

| Fully dynamic     | run     | run      | run     |

| Static-assignment | compile | run      | run     |

| Self-timed        | compile | compile  | run     |

| Fully static      | compile | compile  | compile |

Table 3: Dynamism-based taxonomy of mapping and scheduling approaches, runtime or compile-time, from Lee and Ha's work [118]

Mapping and scheduling methodologies performed at run-time require a management system responsible for taking the decisions. This system may be **centralized** and executed by in a single processor, dedicated or not, as well as **distributed** all over the platform.

Task mapping and scheduling have been extensively studied in both communities of general-purpose computing and embedded computing. A good overview of these techniques for embedded systems has been made by Singh et al. [155], and, as they say, the application mapping problem is still one of the most urgent problem to be solved for implementing embedded systems.

#### 2.5 CONCLUSION

All along this chapter, we have presented the variety of solutions for programming parallel platforms that clearly demonstrates its complexity. While expressing parallelism within an algorithm is already challenging, the architectural variability of parallel platforms in terms of component organization and interconnection makes the task infinitely harder.

While general-purpose computing stays often attached to conventional programming schemes, embedded computing must move towards higher-level programming approaches, like dataflow models and DSL, that provide the abstraction necessary to reach the efficiency and reliability that are required by embedded systems. While MoCs underlying dataflow programming provide formalism, DSLs provides domain knowledge by restricting the application description.

The next chapter deeply inspects dataflow programming, and we focus especially on practical aspects that enable the development of real-world applications. Then, Chapter 4 introduces the Reconfigurable Video Coding (RVC) framework, an innovating framework dedicated to the development of video coding tools that is built upon a dataflow-based DSL known as CAL Actor Language (CAL). After that, the last chapters describe the contributions of this thesis, that is to say the programming of embedded multi-core platforms thanks to the RVC framework.

3

Πάντα ῥεῖ (Panta rhei), "everything flows". — Heraclitus

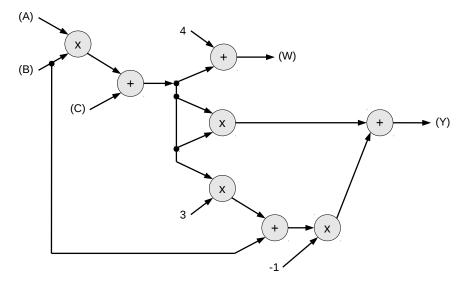

The concept of dataflow representation was introduced by Sutherland in 1966 as a visual way to describe an arithmetic computation [165]. Sutherland represents a sequence of arithmetic statements as a dataflow graph (Figure 8b), in contrast with its mathematical form (Figure 8a), to demonstrate the advantages of the graphical form. In fact, the graphical form replaces each temporary variable by a simple edge that symbolizes the dependences between the computations. Inversely, the graphical form emphasizes the input and output variables.

$$Z = A \times B + C$$

$W = Z + 4$

$Y = Z^2 - (3Z + B)$

(a) Written statement

(b) Graphical statement

Later in 1974, Dennis has described formally the first dataflow programming language [58]. In this language, a program is modeled as a directed graph where the edges represent the flow of data and the nodes describe control and computation.

Following his work on a dataflow language, Dennis has introduced a novel hardware architecture on top of the dataflow model, known under

### 24 DATAFLOW PROGRAMMING

the name of *static dataflow architecture* [59]. This architecture differs from the traditional *Von Neumann* architecture by making an instruction executable when all its inputs are available. As a consequence, the instruction-level parallelism can be directly exploited by the processor. Similarly, Watson et al. have introduced in 1979 the tagged-token dataflow architecture [174] to overcome the limitation of static dataflow architecture. But, the too fine granularity of dataflow architectures prevents them from obtaining scaled performance on large programs.

# 3.1 DEFINITION OF A DATAFLOW PROGRAM

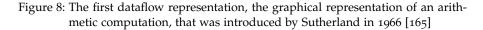

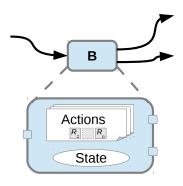

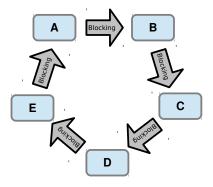

Thus, a dataflow program is defined as a directed graph (Figure 9) composed of a set of computational units interconnected by communication channels through ports:

- The communication corresponds to a stream of atomic data objects, called *tokens*, that follows the First-In-First-Out (FIFO) strategy.

- The computational units, usually called *processes* or *actors*, may first read some tokens from their input channels, may then process some internal computations, and may finally write some tokens to their output channels.

Conceptually, dataflow programming can be considered as the association of the component-oriented programming with message-passing communication.

Figure 9: A dataflow network of five processes, the vertices named from A to E, that communicate through a set of communication channels, represented by the directed edges

### 3.2 DATAFLOW PARADIGM TO ENHANCE PROGRAMMING

Since the early studies on dataflow paradigm, dataflow programming has been mainly considered as an interesting approach for two domains of application, signal processing and parallel processing [107, 159].

During the last twenty years, dataflow programming has been heavily used for the development of signal processing applications due to its consistency with the natural representation of the digital signals processing. More particularly, dataflow programming gives the opportunity to use visual programming so as to describe the interconnection between its components. Such a graphical approach is very natural and makes it more easily understandable by programmers who can focus on *how things connect*.

The emergence of massively parallel architectures, along with the difficulties to program these architecture, make dataflow paradigm an alternative to the imperative paradigm thanks to its ability to express concurrency without complex synchronization mechanism. The internal representation of the application is a network of processing blocks that only communicate through the communication channels. Consequently, the blocks are independent and do not produce any side-effect: This removes the potential concurrency issues that arise when the programmer is asked to manually manage the synchronization between the parallel computations.

# 3.2.1 Modular Programming

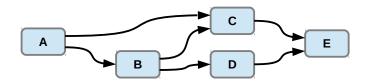

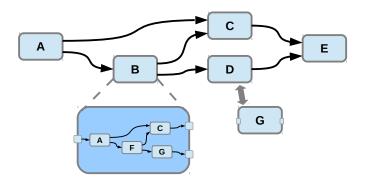

The decomposition of the program into *black boxes* enables the separation of concerns, improves **maintainability** by enforcing the encapsulation of the components, and makes the application description modular:

- **Hierarchical:** A component of the network may represent another network, such as the component B in Figure 10. The ability of an application to be specified in a hierarchical way is allowed by the strict separation between the modeling of the interconnection network and the behavior of the components.

- **Reusable:** A single component can be used to specify several applications, or can be used several time in the network which specifies the application, such as the components A and C in Figure 10 that are both reused by the subnetwork. This ability for a coded algorithm to be reused, is simplified by the strong encapsulation of the components in dataflow programming that makes them side-effect free. A feature also found in functional programming that highlights the strong links between functional and dataflow programming.

- **Reconfigurable:** A component can easily be replaced by another one while its interfaces (input and output ports) are strictly identical, such as the components D and G in Figure 10. Thus, the reconfigurability, i.e. the ability to switch the system into a new configuration in a timely and cost effective manner, is simplified by dataflow modeling.

Figure 10: The dataflow representation is modular by offering hierarchical ability, re-usability and reconfigurability.

# 3.2.2 Parallel Programming

A dataflow program states an abundance of parallelisms thanks to the explicit exposition of the concurrency. In its structural view, the dataflow model presents three potential degrees of parallelism (task, data and pipeline) that can be applied to different granularities of description (Figure 11).

- 1. **Task parallelism** refers to the potential parallelism between the independent parts of an application. In a dataflow context, it appears when two or more components do not have any dependency constraints (Figure 11c).

- 2. Data parallelism refers to a unique computation performed on different sets of data. It can be applied by duplicating a given component when it processes successively several sets of data with no dependencies between them (Figure 11b).

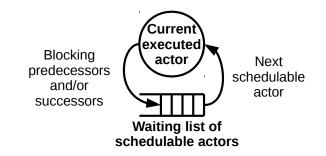

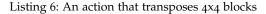

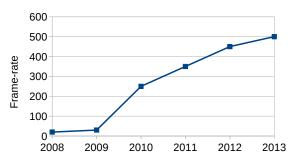

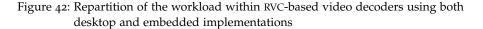

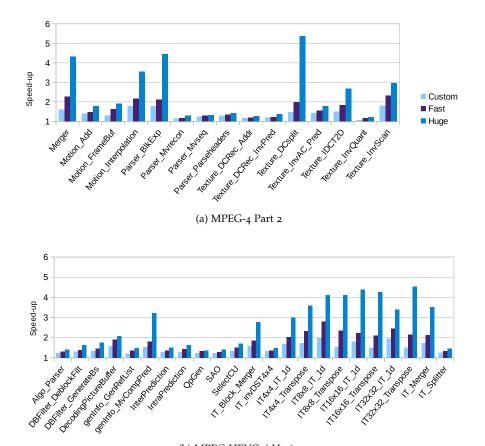

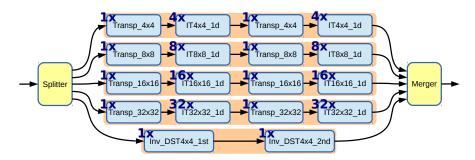

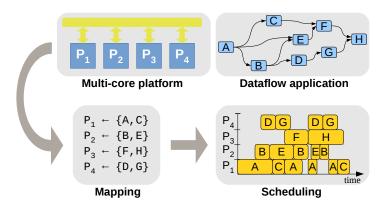

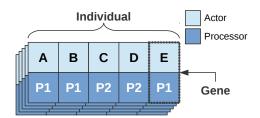

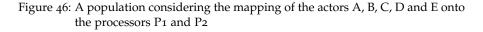

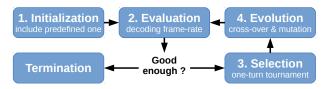

- 3. **Pipeline parallelism** can be considered as a mixture of task and data parallelisms. Pipelining represents the separation of a computation in several stages that can be executed in parallel. This parallelism is inherent to streaming execution model in case of a chain of components (Figure 11d). Pipelining does not enhance the throughput on one calculation, but the processing of a sequence of calculation.