# Evaluation of power management strategies on actual multiprocessor platforms

Jabran Khan Jadoon

#### ▶ To cite this version:

Jabran Khan Jadoon. Evaluation of power management strategies on actual multiprocessor platforms. Other. Université Nice Sophia Antipolis, 2013. English. NNT: 2013NICE4012. tel-00838799

## HAL Id: tel-00838799 https://theses.hal.science/tel-00838799

Submitted on 26 Jun 2013

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

#### UNIVERSITÉ DE NICE – SOPHIA ANTIPOLIS

# ÉCOLE DOCTORALE STIC

# SCIENCES ET TECHNOLOGIES DE L'INFORMATION ET DE LA COMMUNICATION

## **THÈSE**

pour obtenir le titre de

#### Docteur en Sciences

de l'Université de Nice – Sophia Antipolis

Mention: Électronique

Présentée et soutenue par

Jabran KHAN JADOON

# Evaluation of Power Management Strategies on Actual Multiprocessor Platforms

Thèse dirigée par Cécile BELLEUDY Laboratoire LEAT, Université de Nice - Sophia Antipolis - CNRS

Soutenue en 25 Mars 2013

#### Jury:

Nathalie JULIEN Professeur, Université de Bretagne-Sud Rapporteurs

François PECHEUX Maître de Conférence, Université Pierre et Marie Curie

Smail NIAR Professeur, Université de Valenciennes et Hainaut-Cambrésis Examinateurs

Michel Auguin Directeur de Recherche CNRS

Cécile BELLEUDY Maître de Conférence, Université de Nice-Sophia Antipolis Sébastien BILAVARN Maître de Conférence, Université de Nice-Sophia Antipolis

@khan

ALL RIGHTS RESERVED

#### UNIVERSITÉ DE NICE – SOPHIA ANTIPOLIS

# ÉCOLE DOCTORALE STIC

# SCIENCES ET TECHNOLOGIES DE L'INFORMATION ET DE LA COMMUNICATION

## **THÈSE**

pour obtenir le titre de

#### Docteur en Sciences

de l'Université de Nice – Sophia Antipolis

Mention: Électronique

Présentée et soutenue par

Jabran KHAN JADOON

# Evaluation of Power Management Strategies on Actual Multiprocessor Platforms

Thèse dirigée par Cécile BELLEUDY Laboratoire LEAT, Université de Nice - Sophia Antipolis - CNRS

Soutenue en 25 Mars 2013

#### Jury:

Nathalie JULIEN Professeur, Université de Bretagne-Sud Rapporteurs

François PECHEUX Maître de Conférence, Université Pierre et Marie Curie

Smail NIAR Professeur, Université de Valenciennes et Hainaut-Cambrésis Examinateurs

Michel Auguin Directeur de Recherche CNRS

Cécile BELLEUDY Maître de Conférence, Université de Nice-Sophia Antipolis Sébastien BILAVARN Maître de Conférence, Université de Nice-Sophia Antipolis

#### **ABSTRACT**

The purpose of this study is to investigate how power management strategies can be efficiently exploited in actual platforms. Primarily, the challenges in multicore based embedded systems lies in managing the energy expenditure, determining the scheduling behavior and establishing methods to monitor power and energy, so as to meet the demands of the battery life and load requirements. The work presented in this dissertation is a study of low power-aware strategies in the practical world for single and multiprocessor platforms. The approach used for this study is based on representative multiprocessor platforms (real or virtual) to identify the most influential parameters, at hardware as well as application level, unlike many existing works in which these parameters are often underestimated or sometimes even ignored. The work analyzes and compares in detail various experimentations with different power policies based on Dynamic Voltage and Frequency Scaling (DVFS) and Dynamic Power Switching (DPS) techniques, and investigates the conditions at which these policies are effective in terms of energy savings.

The results of these investigations reveal many interesting and notable conclusions that can serve as prerequisites for the efficient use of power management strategies. This work also shows the potential of advanced domain specific power strategies compared to real world available strategies that are general purpose based in their majority. Finally, some high level consumption models are derived from the different energy measurement results to let the estimation of power management benefits at early stages of a system development.

Dedicated to my beloved mother, father, brothers and sisters

and

to my beloved wife Mahrukh.

#### **ACKNOWLEDGEMENTS**

One of the joys of completion is to look over the journey past and remember all the friends and family who have helped and supported me along this long but fulfilling road. Completion of my PhD required countless selfless acts of support, generosity, and time by people in my personal and academic life. I can only attempt to humbly acknowledge and thank the people and institutions that have given me so much help throughout my PhD career and made this dissertation possible. I am thankful to the Higher Education Commission (HEC) of Pakistan for providing funding throughout my Masters and PhD career.

I am sincerely thankful to Miss. Cécile Belleudy, my advisor, for being a constant source of invaluable encouragement, aid, and expertise during my years at LEAT. I would also like to express my heartfelt gratitude to my co-supervisor Sébastien Bilavarn. He has provided insightful discussions about the research. I am very grateful for his scientific advice and knowledge and many insightful discussions and suggestions. The mentoring, friendship, and collegiality of both Cécile Belleudy and Sébastien Bilavarn enriched my academic life and have left a profound impression on how academic research and collaboration should ideally be conducted.

I would also like to thank Professor Nathalie Julien and François Pecheux for being my reviewers and thoroughly reading and acknowledging my thesis. In addition, I would like to thank Professor Michel Auguin and Professor Smail Niar to be part of my jury. It is no easy task, reviewing a thesis, and I am grateful for their detailed reviewing. To the many anonymous reviewers at the various international conferences, thank you for helping to shape and guide the direction of the work with your careful and instructive comments.

LEAT has provided a rich and fertile environment to study and explore new ideas. At LEAT, I would first like to thank Micheal Auguin who has been extremely supportive in allowing me to participate in lab activities whilst pursuing my PhD studies. I am grateful for the chance to be a part of the lab and thank for welcoming me as a friend and helping to develop the ideas in this thesis. Other colleagues who I owe gratitude for their support of my research or major PhD milestones include: Alain Pegatoquet, Bassem Ouni, Ons Mbarek, Khurram Bhatti, and Zeeshan Khan.

My family and friends have been an unending source of love and inspiration throughout my PhD career. I would not have contemplated this road if not for my parents, Hameedullah Khan and Yasmeen Akhtar, who instilled within me a love of creative pursuits, science and language, and believe in me, all of which finds a place in this thesis. To my parents, thank you. My wife, Mahrukh, has offered unconditional understanding and encouragement. My sisters, Madiha and Rawish, have kept me sane with their humor and understanding even from distance. My brothers, Ajram and Ahmer, have been great and selfless support to me throughout these years of my absence from home. My friends in French Riviera, Sharique, Usman, Imran, Sabir, Umer, Taimour, Ahmed, Wajahat, Waqas, and Asad have provided hours of enjoyable distraction from my work. I will always remember the time I have shared with them.

# **TABLE OF CONTENTS**

| ABSTRACT                                  | IV   |

|-------------------------------------------|------|

| TABLE OF CONTENTS                         | IV   |

| LIST OF FIGURES                           | VIII |

| LIST OF TABLES                            | x    |

| CHAPTER 1 : INTRODUCTION                  | 1    |

| 1.1 Contributions Outline                 | 1    |

| 1.2 List of Publications                  | 3    |

| CHAPTER 2 : POWER MANAGEMENT CHALLENGES   | 4    |

| 2.1 State of the Art                      | 6    |

| 2.1.1 Overview and Classification of Work | 7    |

| 2.1.2 Dynamic Power Switching (DPS)       | 7    |

| 2.1.3 DVFS Techniques                     | 12   |

| 2.1.4 Available Market Standards          | 13   |

| 2.1.4.1 Intel                             | 14   |

| 2.1.4.2 AMD                               | 16   |

| 2.1.4.3 ARM                               | 17   |

| 2.1.4.4 Linux                             | 19   |

| 2.1.4.5 Conclusion                        | 23   |

| 2.1.5 Academic Research                   | 23   |

| 2.1.5.1 Overview of Academic Research     | 23   |

| 2.1.5.2 Low Power Scheduling              | 25   |

| 2.1.6 Conclusion                          | 28   |

| 2.1.7 Focus and Objectives                            | 29             |

|-------------------------------------------------------|----------------|

| 2.2 Work Context                                      | 31             |

| 2.2.1 Problem Statement                               | 32             |

| 2.2.2 Platforms                                       | 33             |

| 2.2.2.1 ARM11 MPCore                                  | 34             |

| 2.2.2.2 ARM 1176JZF-S                                 | 35             |

| 2.2.2.3 QEMU_ARM1176                                  | 37             |

| 2.2.2.4 QEMU_CortexA9                                 | 38             |

| 2.2.3 Power Strategies                                | 39             |

| 2.2.3.1 DVFS Video Power Strategy                     | 39             |

| 2.2.3.2 Low Power DSF Scheduler                       | 39             |

| 2.2.3.3 Low Power AsDPM Scheduler                     | 40             |

| CHAPTER 3 : DVFS VIDEO POWER STRATEGY                 | 42             |

| 3.1 Introduction                                      | 42             |

| 3.1.1 Case study: H.264 Decoder                       | 44             |

| 3.1.2 DVFS Video Strategy Description                 | 44             |

| 3.2 DVFS Strategy Implementation and Experimentation  | 46             |

| 3.2.1 DVFS Strategy Implementation                    | 46             |

| 3.2.2 Power and Frame rate profiles                   | 47             |

|                                                       |                |

| 3.2.3 Energy Consumption Analysis                     | 50             |

| 3.2.3 Energy Consumption Analysis                     |                |

|                                                       | 51             |

| 3.3 Further Investigation of Energy Saving Conditions | 51             |

| 3.3 Further Investigation of Energy Saving Conditions | 51<br>52<br>53 |

| CHAPTER 4 : DSF POWER STRATEGY                    | 60 |

|---------------------------------------------------|----|

| 4.1 Introduction                                  | 60 |

| 4.1.1 DSF Strategy                                | 61 |

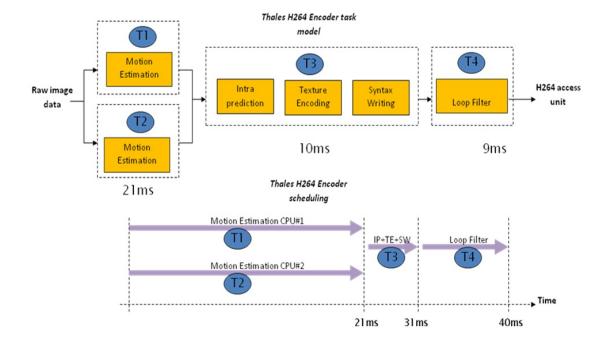

| 4.1.2 Application Examples                        | 61 |

| 4.2 DSF Implementation and Experimentation        | 64 |

| 4.2.1 DSF Implementation                          | 64 |

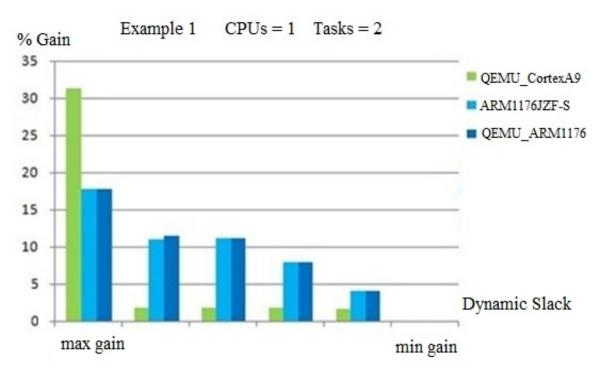

| 4.2.2 Experimentation on a Single Processor       | 65 |

| 4.2.3 Experimentation with Application Parameters | 67 |

| 4.3 Results and Analysis                          | 69 |

| 4.3.1 Multiprocessor Energy Savings               | 69 |

| 4.3.2 Analysis of Results                         | 70 |

| 4.4 Conclusion                                    | 71 |

| CHAPTER 5 : ASDPM POWER STRATEGY                  | 74 |

| 5.1 Introduction                                  | 74 |

| 5.1.1 AsDPM Strategy                              | 75 |

| 5.1.2 Application Examples                        | 76 |

| 5.2 AsDPM Implementation and Experimentation      | 78 |

| 5.2.1 AsDPM Implementation                        | 78 |

| 5.2.2 Energy Savings                              | 79 |

| 5.2.3 Further Analysis of Results                 | 82 |

| 5.3 Energy Gain Comparison of DSF and AsDPM       | 83 |

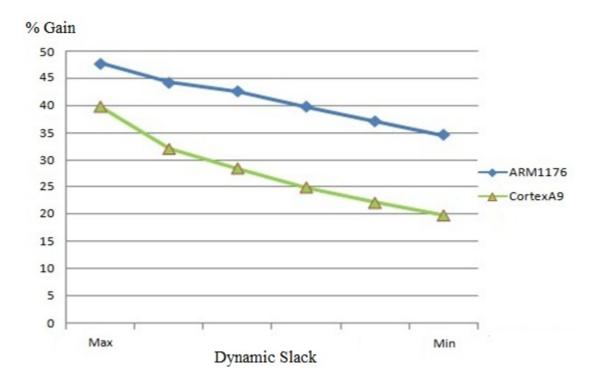

| 5.3.1 Energy Gains for DSF                        | 83 |

| 5.3.2 Comparison and Analysis of Results          | 85 |

| 5.4 Conclusion                                    | 87 |

| CHAPTER 6 : GLOBAL ANALYSIS AND CONCLUSION        | 90  |

|---------------------------------------------------|-----|

| 6.1 Power Management Effectiveness                | 90  |

| 6.1.1 Characteristics of Operating Points         | 91  |

| 6.1.1.1 Operating Points Inefficiency             | 91  |

| 6.1.1.2 Operating Points Impact on Energy Savings | 92  |

| 6.1.2 Latencies of Changing States                | 93  |

| 6.1.3 Application Level Conditions                | 94  |

| 6.1.4 Domain Specific Strategies                  | 95  |

| 6.1.5 Efficiency of DVFS vs. DPS                  | 96  |

| 6.1.5.1 DSF vs. AsDPM                             | 96  |

| 6.1.5.2 DVFS vs. DPS                              | 97  |

| 6.2 Power Models                                  | 97  |

| 6.2.1 DVFS Video Strategy                         | 98  |

| 6.2.2 DSF                                         | 99  |

| 6.2.3 AsDPM                                       | 100 |

| 6.3 Conclusion and Perspectives                   | 101 |

| 6.3.1 Perspectives                                | 103 |

| VITA                                              | 104 |

| BIBLIOGRAPHY                                      | 105 |

| APPENDIX A – ACRONYM INDEX                        | 112 |

# LIST OF FIGURES

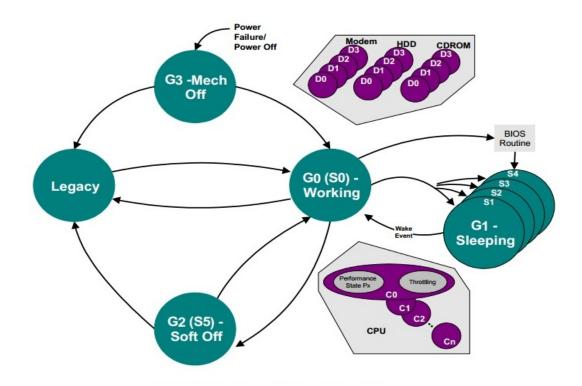

| Figure 2.1: Global System Power States and Transitions. [9]                                                                                 | 9          |

|---------------------------------------------------------------------------------------------------------------------------------------------|------------|

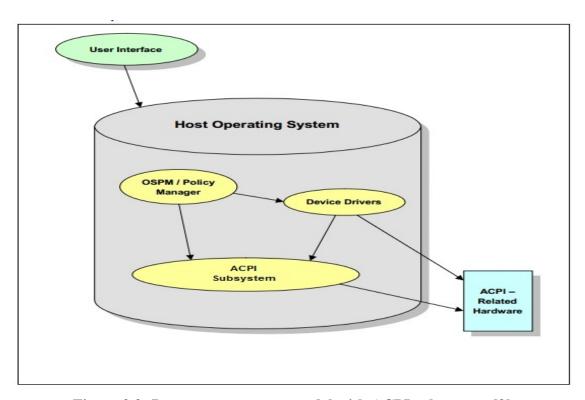

| Figure 2.2: Power management model with ACPI subsystem. [9]                                                                                 | .11        |

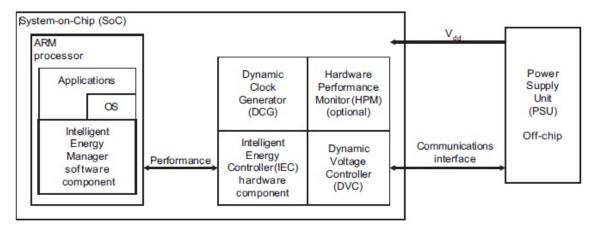

| Figure 2.3: Intelligent Energy Management Solution by ARM. [22]                                                                             | .19        |

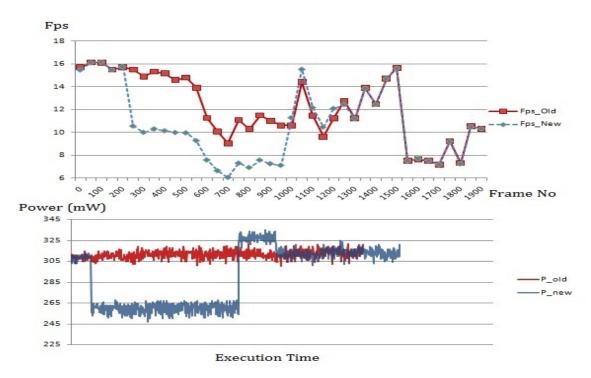

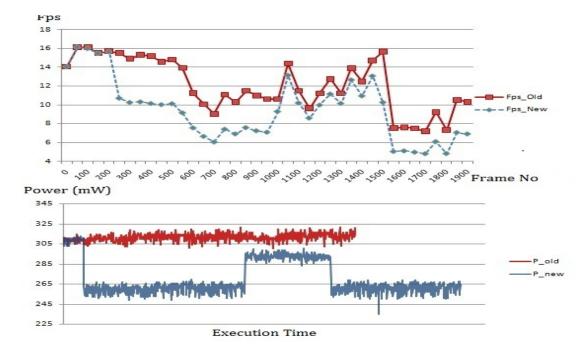

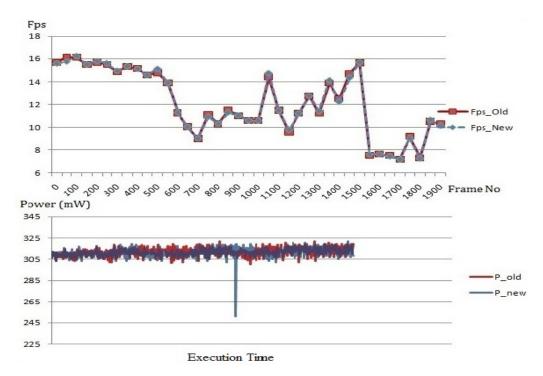

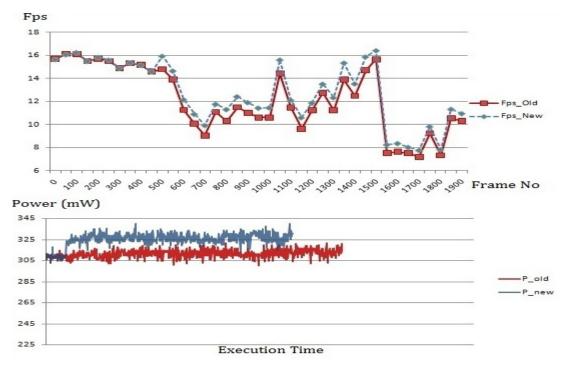

| Figure 3.1: Power and frame rate profiles for <i>adaptation_constraint</i> of 8 fps                                                         | .48        |

| Figure 3.2: Power and frame rate profiles for <i>adaptation_constraint</i> of 9 fps                                                         | .48        |

| Figure 3.3: Power and frame rate profiles for <i>adaptation_constraint</i> of 11 fps                                                        | .49        |

| Figure 3.4: Power and frame rate profiles for <i>adaptation_constraint</i> of 16 fps                                                        | .49        |

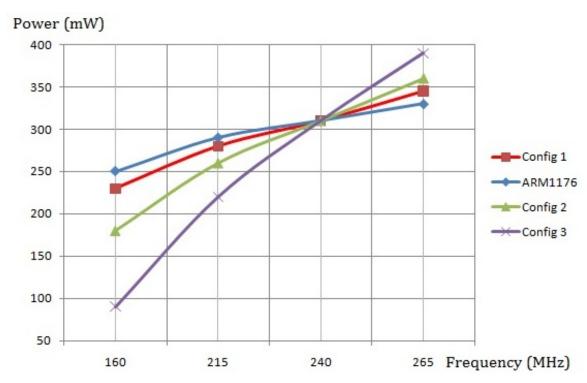

| Figure 3.5: Frequency and load power consumption of QEMU platform.                                                                          | .52        |

| Figure 3.6: Energy consumption vs. Adaptation constraint.                                                                                   | .55        |

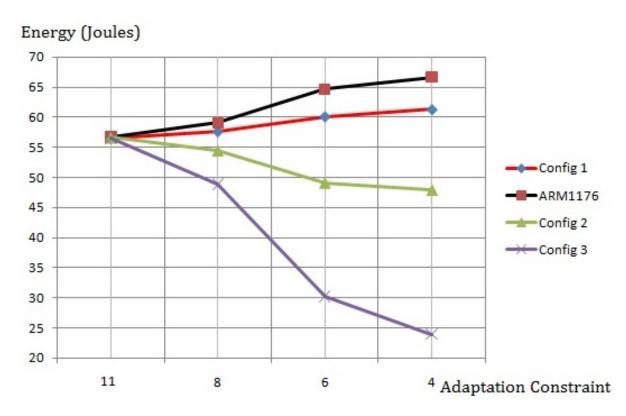

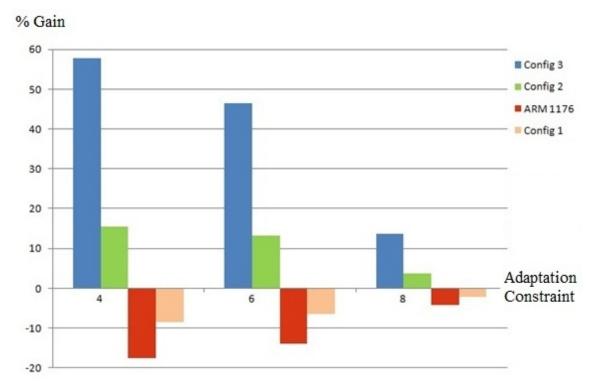

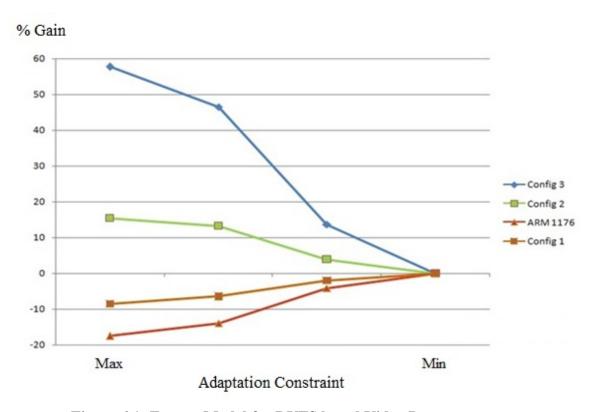

| Figure 3.7: Energy vs. adaptation_constraint for different platform configurations                                                          | .57        |

| Figure 4.1: Thales Task model of H.264 Encoder.                                                                                             | .63        |

| Figure 4.2: Percentage Energy gains for Example 1 on different platforms                                                                    | .66        |

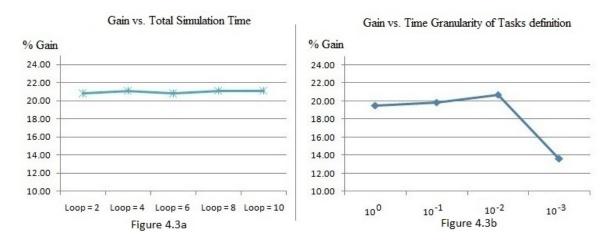

| Figure 4.3: Percentage of Energy Gain vs. Application parameters.                                                                           | .68        |

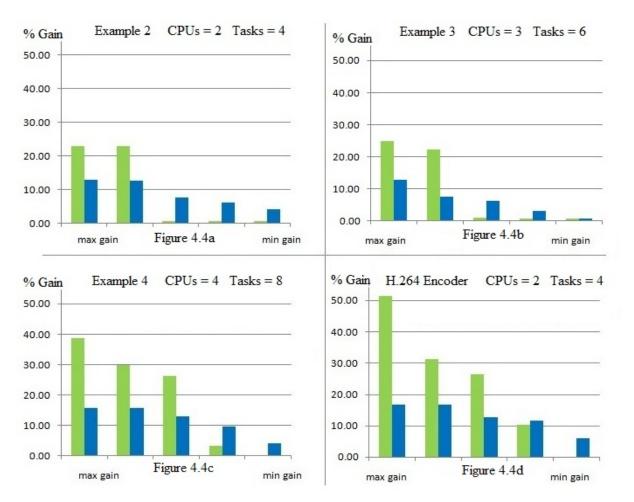

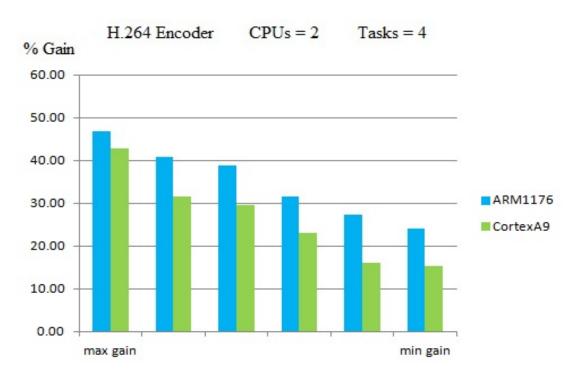

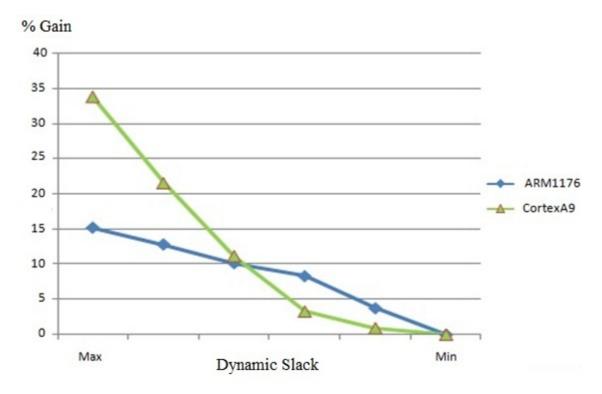

| Figure 4.4: Energy gains on QEMU_ARM1176 (blue) and QEMU_CortexA9 (green) platforms for different applications and platform configurations. |            |

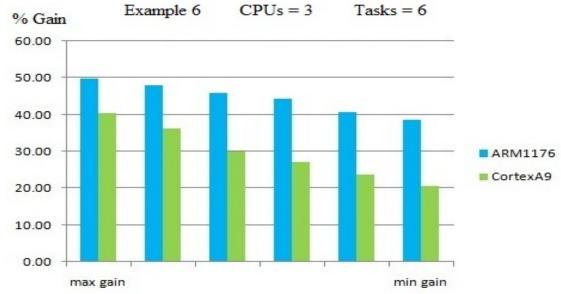

| Figure 5.1: Energy gains of Example 6 on QEMU platforms                                                                                     | .80        |

| Figure 5.2: Energy gains of Example 7 on QEMU platforms                                                                                     | .80        |

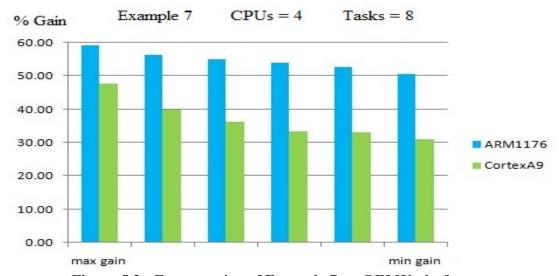

| Figure 5.3: Energy gains of <i>H.264Encoder</i> on QEMU platforms.                                                                          | .81        |

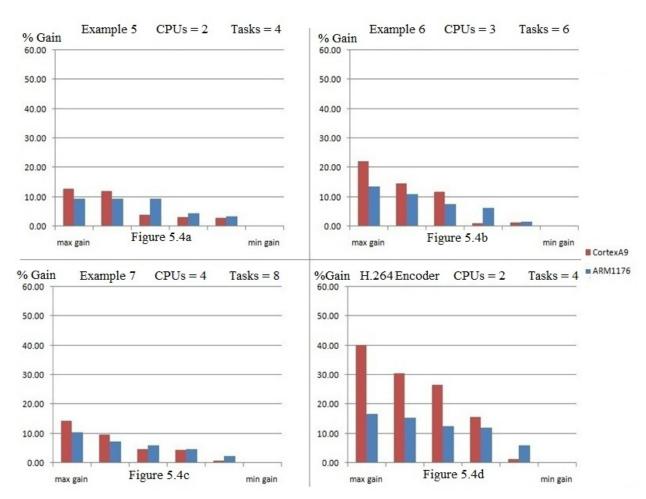

| Figure 5.4: Energy Gains for DSF Strategy on QEMU platforms.                                                                                | .84        |

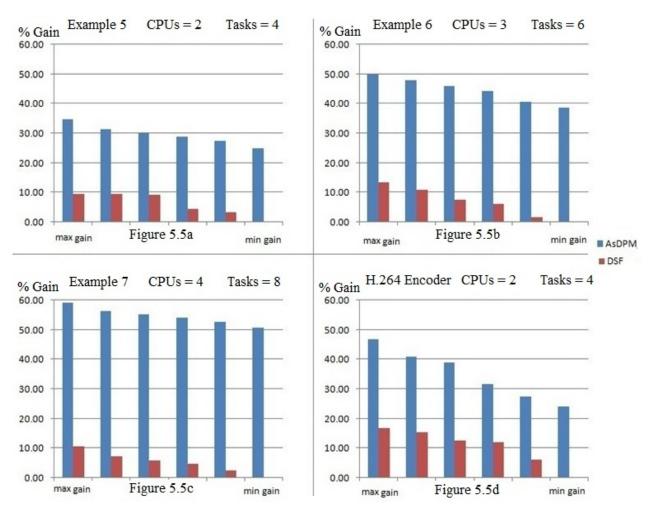

| Figure 5.5: AsDPM vs. DSF energy gains for different examples on QEMU_ARM117                                                                | 76.<br>.85 |

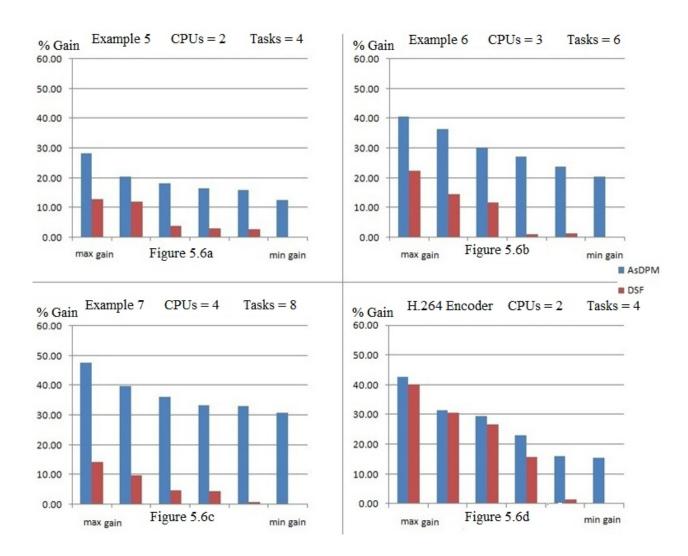

| Figure 5.6: AsDPM vs. DSF energy gains for different examples on QEMU_CortexAs                                                              |            |

|                                                                                                                                             | .86        |

| Figure 6.1: Energy Model for DVFS based Video Power strategy | 98  |

|--------------------------------------------------------------|-----|

| Figure 6.2: Energy Model for DSF power strategy              | 99  |

| Figure 6.3: Energy Model for AsDPM strategy                  | 100 |

# LIST OF TABLES

| Table 2.1: Supported Performance States for the Intel M-Processor [14]                               | .13 |

|------------------------------------------------------------------------------------------------------|-----|

| Table 2.2: Supported Voltages and Frequencies for Low Power AMD-  K6 <sup>TM</sup> 2E+Processors[20] | .17 |

| Table 3.1: Performance Analysis table for ARM1176JZF-S                                               | .51 |

| Table 3.2: Frequency vs. Energy for video Foreman (300 frames).                                      | .54 |

| Table 3.3: Frequency and load power consumption for different configuration of QEM platform.         |     |

| Table 4.1: Examples used for experimentation of DSF strategy                                         | .62 |

| Table 4.2: Energy consumption of <i>Example 1</i> on ARM1176JZF-S and QEMU_ARM1176 platform.         | .65 |

| Table 4.3: Power profile of QEMU_ARM1176 and QEMU_CortexA9 platform                                  | .71 |

| Table 5.1: Examples used for the experimentation of AsDPM strategy                                   | .76 |

| Table 5.2: Energy consumption of <i>Example 5</i> on QEMU platforms.                                 | .79 |

| Table 5.3: Energy Consumption and Gain for <i>H.264Encoder</i> .                                     | .82 |

| Table 5.4: Idle vs. load power levels for OEMU platforms at maximum frequency                        | .83 |

This thesis is partially funded by COMCAS project (CA501), a project labeled within the framework of CATRENE, the EUREKA cluster for Application and Technology Research in Europe on NanoElectronics; and partially by HEC PAKISTAN under program Overseas Scholarships for MS MS/MPHIL Leading to PhD in selected Fields ( Phase-II, Batch-II).

# Chapter 1: Introduction

This introduction aims at presenting the reader with a global outline of this study. The introduction part provides a general discussion on trends of energy consumption in modern systems, presents general objectives of this work and provides an outline of this thesis. A detailed literature review, work context, as well as problem statement are presented later in the respective chapter.

In recent years, there has been a rapid and wide spread growth of nontraditional computing platforms, especially mobile and portable computing devices. It is a common experience that current mobile devices (laptops, PDAs, etc.) can operate just for few hours before the battery gets exhausted. As applications are becoming more and more complex and processing power is continuously increasing, there is a significant impact on battery life. Embedded systems due to the advancement made in fabrication of powerful tiny processors, with the ability of having multiple cores and variable frequencies can be integrated in small handheld devices. The small physical size and limited battery life of these devices impose several constraints on power and energy consumption of these devices. In this context, most systems should be designed in a way to adapt themselves according to environment needs, precisely they need to adapt at the lowest energy consumption for a given performance level.

These constraints require rethinking the design process with power and energy issues as major concerns. It is really a waste if the equipments are not designed to be energy efficient with the abilities to power down during non-operating hours. Energy consumption is becoming more of a concern and is getting an increasingly larger percentage of the overall development costs as well. Reducing the energy consumption in embedded systems has become a prime criterion, motivated by the limited lifetime of battery operated systems.

This thesis provides a characterization of real challenges encountered while providing advance power management solutions in actual embedded systems. This thesis also provides a detailed analysis of power management challenges and review power saving techniques available with today's system-on-chip (SoC). We analyze different power management strategies on single and multiprocessor platforms and explore how different power management policies, each with their own methodologies, can really provide energy savings. The real implementation of different power management strategies

coincide with different issues therefore this work present a realistic approach by experimenting with different power management strategies in real world. This thesis demonstrates experimentation and analysis of three different domain specific power management strategies with the objective of pointing out different factors effecting the energy consumption. In addition, we provide different experimentation results to evaluate the effectiveness of these strategies and provide conditions under which the addressed strategies are feasible in modern systems.

In next section, we present a global outline of our contribution to address the above issues.

#### 1.1 Contributions Outline

Chapter 2: This chapter provides a detailed literature overview of our work. At the beginning of this chapter, we provide a detailed study of main power management solutions, industrial power management standards and academic research going in the field of power management. Afterwards, we introduce the focus and targets of our work to meet the power management challenges and consequently define our problem statement. The chapter then provides information about the target platforms and ends with the brief introduction to the different power strategies used to address the problem statement.

Chapter 3: This chapter provides a detailed experimentation about the first DVFS based video power strategy. The DVFS based strategies are shown to provide significant energy gains, where scaling down the frequency mostly provides decrease in power consumption. The experimentation and results provided in this chapter shows that various conditions should be met to achieve this energy savings. The chapter also highlights the importance of using domain or application specific strategies. At the end, the effect of operating points on the efficiency of a DVFS strategy and their influence on the energy savings is also investigated.

**Chapter 4:** This chapter provides experimentation of a second DVFS based *Dynamic Stretch to Fit* (DSF) strategy on single and multiprocessor platforms. DSF strategy is shown to provide significant energy gains in different platform configurations. The experimentations highlight the effects of load vs. idle power levels of the platforms. This chapter also provide certain application and platform limitations for using DSF strategy

as well as draw attention to the efficiency criteria of application or domain specific strategy.

Chapter 5: This chapter provides an analysis and experimentation of a Dynamic Power Switching (DPS) based power strategy for multiprocessor platforms called Assertive Dynamic Power Management (AsDPM). The application specific strategy is analyzed for its energy consumption and is further investigated for the conditions under which it is more efficient on certain platform than other. The chapter also provides the effects introduced by different application parameters, platform characteristics and state switching latencies on the efficiency of the AsDPM strategy. In addition, this chapter provides a comparative analysis of energy gains obtained by AsDPM with previous DSF strategy.

Chapter 6: This chapter provides major categorization of conditions obtained from the results of the above experimentations. First, it addresses power management effectiveness by classifying different application conditions, platform conditions, latencies of DVFS / DPS states and domain vs. general purpose strategies. Secondly, this chapter provides some high level power models derived from the results of energy gains obtained by our experimentations. At the end, this chapter provides a brief conclusion along with perspectives of furure work.

### 1.2 List of Publications

Personal publications in International Conferences:

- 1) **Khan, J**., Bilavarn, S., and Belleudy, C.: "Impact of operating points on DVFS power management," *In proceedings of 7th International Conference on Design & Technology of Integrated Systems in Nanoscale Era, DTIS'12*, Tunisia, May 2012.

- 2) **Khan, J.**, Bilavarn, S., and Belleudy, C.: "Energy analysis of a DVFS based power strategy on ARM platforms, " *In proceedings of FTFC 2012 : IEEE Faible Tension Faible Consommation, FTFC'12*, France, Jun 2012

- 3) **Khan, J.,** Bilavarn, S., Belleudy, C., and Bhatti, K.: "Energy analysis of a real-time multiprocessor control of idle states on ARM platforms," *In proceedings of Pervasive and Embedded Computing and CommunicationS PECCS'13*, Barcelona, Feb 2013.

## **Chapter 2: POWER MANAGEMENT CHALLENGES**

Moore's law states that the number of transistors in integrated circuits doubles approximately every two years [1]. As the technological advancement has proven this law to be correct, this decrease in size and increase in computational power impacts the power utilization of these highly complex components. Lower power consumption also means lesser heat dissipation, which increases system stability. However, this imposes major enhancements to the management of power for these new devices containing millions of transistors. The need for more complex and portable devices imposes new efforts on designing and implementing low power solutions. To increase the battery life of systems and give more reliability to the system, new techniques should be implemented to cope with power management issues. Power management challenges include considerations of overheating, energy cost as well as environmental concerns.

In the past, boot delay of a device was very long when it was switched on and people used to leave their devices turned on to avoid this delay hence wasting a lot of energy. This led to introduce new power features allowing devices not to fully turn off when unused. To reduce power utilization when a device is not active, consumer electronic devices introduced the concept of sleep or standby states. Old versions included manual handling of going from one state to another based on user inputs. However, as the processor execution speed is much higher to that of a user, relying only on the user does not provide enough power reduction. As the technological era changed, new power management schemes were introduced to tackle automatically the power management problem without the need of the user.

The power management in PCs and embedded systems has been handled historically with two different power managers i.e. Advanced Power Manager (APM) and Advance Configuration Power Interface (ACPI). Advanced Power Management (APM) represents the first stage, developed by Intel and Microsoft in 1992 [2]. Power management was performed through BIOS by turning off the display, disabling the hard disk after a preset period of idle time, or by idling CPU by entering in suspend state. APM lacked a lot of capabilities. For instance, power management was done as a background process by the BIOS instead of the Operating System (OS). For each different platform, this BIOS based APM was specific to the platform and had to be supplied by the manufacturer. The

second version named Advanced Configuration and Power Interface (ACPI) is still widely used in today's operating systems. ACPI is an open industry specification establishing a standard interface for OS direct configuration and power management of laptops, desktops, and servers. First released in December 1996, ACPI defines platform independent interfaces for hardware discovery, configuration, power management and monitoring. ACPI is superior to APM as it addresses the drawbacks of APM. Although ACPI is fully adopted in windows based platforms, however Linux support for ACPI is still evolving.

Besides these two major advancements of power managers, modern microprocessors also come with their own power management policies implemented in their BIOS. However, the evolution of these complex microprocessors does not fully compensate the energy demand and power optimization. Hence, operating systems may be limited by their general purpose software-based power management policies and could save further energy consumption for more demanding workloads like video and/or real-time processing for instance. In this work, we present a study of various power strategies on real-life applications and platforms. To do that, we investigate the conditions of energy gains of three distinct multiprocessor strategies: a Dynamic Voltage and Frequency Switching (DVFS) based strategy for video applications, a DVFS based deadline scheduling strategy and a Dynamic Power Switching (DPS) based deadline scheduling strategy. We also aim to investigate the conditions of efficiency and power reduction of these different strategies, so we promote a realistic investigation approach based on power measurements using actual multiprocessor platforms as much as possible.

We address all these issues in detail in the following sections. Section 2.1 provides an overview and discussion of existing works related to the general field of power management. An overview and classification of work are presented in section 2.1.1. In section 2.1.2 and section 2.1.3, we detail the two broadly used power management techniques, i.e. DVFS and DPS. We then move to section 2.1.4, to review market standards and their available power management solutions. We start with Intel platforms and their power management infrastructure in section 2.1.4.1. Then we cover AMD processors and their respective technologies in section 2.1.4.2. The ARM processors are famous for their low-power consumption; we thoroughly study their PM infrastructure in section 2.1.4.3. Afterwards in section 2.1.4.4, we move to the power management provided by the Linux operating system. At the end in section 2.1.4.5, a conclusion is

established on the discussion of these standards. An overview of academic research work is then shown in section 2.1.5 with a focus on low power scheduling techniques. In section 2.1.6, we provide a global conclusion about the advantages, shortcomings, as well as other possibilities of exploring the said techniques. In the end, section 2.1.7 puts light on our focus and objectives related to power management for multiprocessor platforms.

The second part of this chapter is to present our work context, why this work is carried out and how we can address the encountered shortcomings related to the power management on the representative platforms. Therefore, in section 2.2.1 we start by providing the problem statement. Afterwards, in section 2.2.2 we give information related to different platforms used in this work. We present the real platforms ARM11 MPCore and ARM1176JZF-S along with two QEMU based virtual platforms. At the end, we provide a brief introduction of various power management strategies in section 2.2.3, where the first dynamic video power strategy is described in subsection 2.2.3.1. In section 2.2.3.2, we introduce the DVFS based deadline scheduling technique and in section 2.2.3.3, we introduce the DPS based deadline scheduling technique.

#### 2.1 State of the Art

This state-of-the-art section provides an overview of historical approaches used by systems. There are a lot of power management techniques that are proposed or implemented in embedded systems. However, power management is a large domain and cannot be summarized entirely. We start by differentiating and discussing the proposed classification of work in the field of power management. In the following sections, we focus on the two broadly used power management techniques, i.e. DVFS and DPS. The presence of a large number of processor manufacturers result in a variety of techniques, in spite of this we discuss the main approaches used by largely developed standards (ARM, Intel, AMD, etc.) and their respective platforms. We give a clear view of how these industrial and commercial available products manage power consumption. A detailed discussion on power management policies and infrastructure used by the Linux OS is also presented. The state-of-the-art section also provides an overview of ongoing research in the field of power management in academic domain. As this is a very

large domain of research, we only focus on techniques used for processor level power management. We also discuss low power scheduling policies as they provide interesting solutions for power management in modern multiprocessor devices. At the end, we provide a general analysis and conclusion of this state-of-the-art regarding the targets and goals of our work.

#### 2.1.1 Overview and Classification of Work

In this section, we emphasize different power management techniques used in embedded systems. Power management can be done at different levels, i.e. operating system level, component level or application level. CPU power consumption is significant and is the main target of power management analysis in various studies. For example, numerous power aware models studied in [3-7] are shown and integrated into present performance simulators to investigate power consumption of the CPU, on a unit basis or for the processor as whole. Our focus is also on techniques which are related to processor level power management. Two popular techniques are mainly employed: Dynamic Power Switching (DPS) to switch off the power of a part of the circuit to idle states, and Dynamic Voltage and Frequency Scaling (DVFS) to tune a processor clock speed and voltage. In some works as in [8], DPS techniques are also referred to as Dynamic Power Management (DPM). DPM refers to an IBM and MontaVista initiative of developing a general and flexible dynamic power management architecture which is now outdated. We therefore use the term DPS instead of DPM in order to avoid confusion. In general, DVFS and DPS techniques are controlled by a power policy or power strategy. The next section provides a detailed discussion on these broadly used techniques.

#### 2.1.2 Dynamic Power Switching (DPS)

Dynamic Power Switching (DPS) is a well-known technique that selectively shutdowns or puts to sleep some active components in embedded systems, to manage energy consumption and heat dissipation problems. In early stages, power switching was under the control of Advanced Power Management (APM). APM provided different power modes like *full-on*, *enable*, *standby*, *suspend*, and *off*. A brief description of these modes is given below:

In *full-on* mode all components are fully powered and there is no power management occurring. In *enable* mode CPU is slowed or stopped (depending on BIOS), all other devices still draw full power and recover time is instantaneous. In APM *standby* mode,

CPU may be stopped depending on operation or activity, most devices are in low power mode as well as monitor enters its first power management mode. An activity can trigger a return to *enable* or *full-on* mode depending on the system and activity. In APM *suspend* mode CPU is stopped, most power-managed devices are not powered (network card may stay on) and APM provides maximum power savings. Activity can trigger a return to *standby*, *enable* or *full-on* depending on the BIOS though recovery time is very large. In APM *Off* mode operational parameters are saved, system turn off and draw no power.

A decision to enter low-power modes was controlled by timers and the return to full power (or higher-power modes) is directly triggered by activity from the keyboard, mouse, modem, or network. Such activities generate interrupt requests, or IROs, which signal the processor that it needs to respond to them. Even when a PC has powered down (but is not off), the BIOS still monitors IRQ activity. APM had a major drawback of its dependence on the BIOS. Another shortcoming was lack of intermediate power states and usually systems either uses full performance level or are always idle (inactive). ACPI addressed these issues and was later adopted and enhanced by all market sharers, and is still in use. ACPI allows direct power management by the Operating System. ACPI is a hierarchical power management technique having different system and device power states as shown in figure 2.1. ACPI naming convention divides the overall system components in set of manageable components like Global G-states, System S-states, Processor P-states, Busses B-states, Links L-states and Devices D-states. A numbering convention is also used where '0' is the main active state like G0, S0, D0, etc. The numbers from 1 to n represent the corresponding power levels. The higher number indicates the lower power consumption state in comparison to its previous ones. For example, P1 state consumes more power than P2, P3 or P4 state. ACPI subsystem uses these states to handle power management of individual devices, components or the overall system.

A summary of different states is discussed to give an idea of this dynamic power switching mechanism. Here, G-states are the top-level states for the overall system and reflect the user level perception. G-States are global operating states and are not configurable by the user. These are just used in documentation to specify certain system states such as on, off, sleeping. G0 is the working state, where the system is fully operational. G1 is a sleeping state where power consumption is small, and the system can be resumed without the need of booting. G2 is a soft off state in which the system

consumes a minimum amount of power, and the system must be restarted to be functional. G3 is a mechanical off state, where all hardware information is lost, and power consumption is zero. A hierarchical view of G-states with other system states is shown in figure 2.1.

Figure 2.1: Global System Power States and Transitions. [9]

The S-states are types of sleeping states within the G1 sleeping state. These are set in the BIOS and then configured in the power option's control panel (timeout in minutes). The S-states allow the system to save a significant amount of power when not being used. S0 is the working or fully powered state. S1 and S2 are similar low wake-up latency states except that in S2, the CPU and cache context are lost. S3 is a suspend to RAM state where the memory image is maintained and powered, while the CPU chipset and I/O devices lose their content. S4 is a suspend to disk or hibernate state where all devices are powered off. This state has the longest wake-up latency. The RAM content is lost and the platform content is maintained on the hard drive. The soft-off state S5 is similar to

S4 but here, the system requires complete re-boot when waking up. A system in S-state can be triggered by a motion sensor, LAN or GPIO activity.

The CPU power state or C-states are the processor power consumption and thermal management states within the global state G0. It reduces power consumption by putting the processor to sleep when it does not have code to execute. The entry and exit from Cstates are much faster in comparison to S-states. C-states require low processor power during idle light workloads. The C-states limits can be configured and set by the BIOS, and a processor can go to C-states several thousand times per second. These states can also be referred as operating, halt, sleep and deep sleep mode. The processor is in C0 state when it executes instructions. The C1 to Cn power states are processor sleeping states, where the processor consumes less power and dissipates less heat than in the C0 state. C1 is the lowest latency power state where the processor is in a non-executing state. C2 state offers improved power saving in comparison to C1. The contents of L1 cache are saved to L2 cache. C3 state also offers improved power scaling over C1 and C2, but the time latency of entrance and exit increases. In the C3 state, the core flushes the content of its L2 instruction cache and the shared L3 cache, while maintaining its architectural state. All core clocks stop at this point. The C-states are processor model specific, therefore some processors may contain further C4, C5, C6 states, etc.

While in the C0 state, ACPI allows the performance of the processor to be altered through a defined *throttling* process and through transitions into multiple performance states (P-states) as shown in figure 2.1. P0 provides maximum performance while consuming maximum power (at a higher frequency). Similarly, P1 is a state where the processor consumes less power than P0. The lesser power consumption also results in reducing the performance below the maximum. The P-states also depend upon the underlying hardware. The numbers of P-states are processor specific, where each state corresponds to a different frequency and power consumption level. Pn is the state where processor has lowest frequency and minimum power consumption. P-states are very useful to control non-critical workloads that do not require maximum frequency and power consumption throughout their execution.

ACPI also contains the device D-states (Figure 2.1) for managing power of peripheral devices. D0 is the active state and consumes maximum power. Devices often come with only on and off states. Therefore, D1 and D2 are rarely used. However, in devices like modems, D1 state provides functionality like modem controller to go into low power

mode, phone interface powered by the phone line, and speaker off. D3 is the state when a device is off. Like in case of a modem, the controller is switched off, phone interface turned off, speaker off. Additionally, it can be D3 hot or D3 cold depending on if primary power is removed or not.

The operating system uses these ACPI states with the help of a policy manager for power and energy management. An example of such a policy manager is OSPM as shown in figure 2.2. The policy manager defines a policy based on the different user, application or environmental parameters. The policy manager directs the rules for using efficiently the ACPI sleep states for the policy (or scheme). The ACPI sleep states are mostly selected by the policy manager when there is no workload on the processor. However, the processor is usually the most active element in embedded systems. Handling smartly the processor states has the potential for significant energy and power gains. Therefore, when a processor is active, the policy manager uses DVFS techniques to select the P-states for managing power, as detailed in the next section.

Figure 2.2: Power management model with ACPI subsystem. [9]

### 2.1.3 DVFS Techniques

Dynamic Voltage and Frequency Scaling (DVFS) is widely used for power management in modern processors, as it is an effective method for achieving low power consumption of CPU while meeting the performance requirements. The purpose of DVFS techniques is to scale dynamically the circuit speed and the supply voltage level of the processor, to process the system workload. The frequency and supply voltage are directly related to power consumption in CMOS technology as shown in [10]. Therefore, decreasing frequency and voltage will impact overall power consumption and will increase/decrease the total energy consumption. Modern microprocessors come with the built-in support for DVFS along with the support for DPS. A number of new microprocessors such as ARM1176JZF-S [11], ARM CortexA9 [12], AMD-K6<sup>TM</sup>-2E+Processors[13], Intel M series [14], Transmeta Crusoe [15] are equipped with the DVFS functionality.

Microprocessors are also provided with power management software (policies) to make use of DVFS techniques. A detailed description of some of the industry standards, as well as their power management policies and DVFS techniques are detailed in section 2.1.4. DVFS in popular operating systems, like Windows and Linux, is supported by the help of ACPI. The ACPI C0-states can be further divided into performance P-states as described in section 2.1.2. Different policies are defined based on performance and power needs, to use these P-states efficiently. For example, the OnDemand policy (governor) in Linux allows adapting the frequency to the workload using P-states. This governor allows the CPU to achieve maximum clock frequency when the system load is high and minimum frequency when the system is idle. The detailed description of Linux governors is given in section 2.1.4.4. Similarly, Windows OS comes with policies like Balanced, Max Power Saving, Max Performance. These policies use the ACPI infrastructure that allows the processor to change its frequency and voltage according to the workload. For example, in case of a *Balanced* scheme, ACPI chooses the best P-state level based on total average workload. An example of P-states of an Intel M-processor using Enhanced Intel SpeedStep (EIST) technology is shown in table 2.1. The corresponding frequency and voltage levels are also shown for each P-state. According to ACPI, P0 is the state where frequency is maximum (1.6 GHz), and voltage is also maximum (1.484 V). Similarly, the lowest P-state is P5 where the frequency and voltages are at their lowest values as shown in table 2.1.

P-States Frequency Voltage P0 (HFM) 1.6 GHz 1.484 V P1 1.420 V 1.4 GHz P2 1.2 GHz 1.276 V P3 1.0 GHz 1.164 V P4 800 MHz 1.036 V 0.956 V P5 (LFM) 600 MHz

**Table 2.1: Supported Performance States for the Intel M-Processor [14]**

Another important aspect of implementing a DVFS based strategy (policy) is its dependency on the operating points. Operating points in the context of DVFS are the frequency/voltage levels that a processor support (equivalent to P-states shown in table 2.1). DVFS based policies should be defined in a way to use these operating points efficiently. For instance, if the desired frequency for an application or workload is between two discrete levels, the one with higher value should be used. In this way, we can guarantee the temporal requirements. Researchers in [16], have proposed algorithms to map such required continuous frequency/voltage levels to discrete values, to utilize DVFS technology. Thanks to the advancements in micro architectures, modern processors are able to operate in a wide range of the frequency/voltage spectrum. This allows DVFS based policies to exploit a wide range of available P-states. For example, Intel SpeedStep technology evolved from changing frequency by taking steps of 200 MHz in its first version ( SpeedStep II).

#### 2.1.4 Available Market Standards

Traditionally, first technologies in power management were based on dynamically switching on and off the circuitry or components to achieve an overall lower power utilization [17]. Power management for computer systems has focused on regulating the power consumption in static modes (such as sleep, suspend). These de-activating states often require a user action to re-activate the system. Latencies and overheads are usually significant for entering and exiting of these states. In desktop and server systems, a firmware layer is typically added to support these modes. However, many architectures

provide the equivalent of a halt instruction that reduces CPU power during idle periods, with only a few clock cycles of latency.

With the advancement in technology and constraints such as size, cost and environmental effects, no design is complete without a thorough analysis of the power-supply architecture. Modern systems are therefore equipped with facilities such as dynamically changing the frequency and voltage, flexible power management modes, separate power domains, intelligent voltage regulators, etc. New micro architectures are designed with CMOS technology to consume less power. Power consumption at the processor level is generally divided into static and dynamic power. Accordingly, we have to decrease both the static and dynamic power to decrease the total power consumption. In the past, static power consumption has been small in comparison to dynamic power. However, factors contributing to leakage power, including quantum effects (such as gate-oxide layer tunneling) are becoming increasingly important with shrinking silicon feature sizes as discussed in [18].

Voltage has a quadratic relationship with power for dynamic power consumption, therefore decreasing voltage can significantly affect dynamic power utilization. With the availability of techniques like DVFS, new policies and power management methods are possible at different levels (i.e. OS, Hardware, etc.). ACPI is widely used to handle power management as detailed in the above section 2.1.2. Besides ACPI, modern microprocessors come with their own power management hardware and software to handle power consumption. Examples of such processors include Intel *SpeedStep*[14], AMD *Cool'n'Quiet* [19] and *PowerNow* [20], IBM *EnergyScale* [21] and ARM *IEM* [22]. A brief overview of power management policies used by Intel, AMD and ARM processors, as well as power management in Linux is detailed in the following sections.

#### **2.1.4.1 Intel**

There are several Intel® power management technologies that can be used by embedded developers to manage the balance between power consumption and performance. First, there are power states that define distinct "sleep" modes as well as different fully functional operating modes. Second, Enhanced Intel *SpeedStep*® Technology enables optimal performance at the lowest power by allowing the operating system to change the processor frequency and supply voltage. Third, Intel® Turbo Boost Technology provides additional processor frequency bins, above the base operating frequency (i.e. faster). An

embedded system only runs at the full throttle when workload demand is high, therefore, energy is mostly saved during non-peak times. Intel power management technologies give software developers granular control over the system operation.

Intel *SpeedStep*, that is a trademark for a series of dynamic frequency scaling technologies (including *SpeedStep* I, *SpeedStep* II, and *SpeedStep* III) allow the clock speed of the processor to be changed dynamically. This allows the processor to meet the performance needs for the operation being performed, while minimizing power drawn and heat dissipation. Power management in new Intel series processors, is provided by the built in *Enhanced Intel SpeedStep (EIST) technology. EIST* allows the processor performance and power consumption levels to be modified while a system is functioning. This is accomplished via application software, which changes the bus-to-core frequency ratio and the processor core voltage (Vcc). A variety of inputs such as the system power source, processor thermal state, or OS power policy is used to determine the proper operating state.

There are various versions of EIST present for Intel processors. The EIST V1.1 is used by second generation Pentium III processors. It enables the CPU to switch between predefined modes: the top and bottom modes are commonly known as high-frequency mode (HFM) and low-frequency mode (LFM). The frequencies and voltages (operating points) are stored within a read-only processor model specific register (MSR). This MSR ensures BIOS will not allow transitions to invalid states above the HFM or below the LFM. The other four operating points are stored within the BIOS code in a drop voltage table provided by vendors. An example of P-states for Intel M processor at 1.6 GHz is shown in table 2.1 in section 2.1.3, where the processor frequency is modeled to have steps of 200 MHz. Using EIST, Pentium III processors consume about 20 Watts at 1 GHz and it can be reduced to 6 Watts at 600 MHz. EIST V2.1 (Enhanced SpeedStep) is used in Pentium III-Mobile processors and is similar to the previous version. EIST V2.2 is adapted for Pentium 4-Mobile processors. With EIST V2.2, a 1.8 GHz Pentium 4-M consuming about 30 Watts can lower its frequency to 1.2 GHz, thus reducing power consumption to about 20 Watts. EIST V3.1 is used in the first and second generation of Pentium M processors (Banias and Dothan cores, used in Centrino platforms). With this technology, the CPU varies its frequency (and voltage) between about 40% and 100% of its base frequency in increments of 100 MHz (for Banias core) or 133 MHz (for Dothan core).

#### 2.1.4.2 AMD

AMD provides several power management technologies that can be used by software developers to deal with power and thermal issues. To manage power at the CPU level, the two most efficient technological standards provided by AMD are *Cool'n'Quiet* and *PowerNow. Cool'n'Quiet* is a CPU speed throttling and power saving technology introduced in the *Athlon64* processor line. The technology reduces the overall power consumption and lower heat generation, allowing for slower cooling fan operation. The objectives of cooler and quieter system execution result in the name *Cool'n'Quiet*. The technology is similar to Intel *SpeedStep* and AMD *PowerNow*. Due to its different usage, *Cool'n'Quiet* refers to the desktop and server chips, while *PowerNow* is used for laptops and mobile chips. The technology is also introduced on *e-stepping* Opterons; however, it is called Optimized Power Management (*OPM*), which is a re-tooled *Cool'n'Quiet* scheme designed to work with registered memory.

Cool'n'Quiet technology controls the processor performance automatically by dynamically adjusting the operating frequency and voltage up to 30 times per second to the task at hand. It reduces the power in two ways. First, it reduces the leakage power at idle. The Athlon64 puts itself to sleep when the HLT/STPGNT instruction is sent. At this stage, only the leakage power is drawn. The power is further cut down significantly by reducing the frequency and voltage. Secondly, it reduces the power needed during light and medium load. When the processor can cope with the work at a low frequency/voltage level, it stays at this level. The performance penalty of this solution is negligible. All Athlon64 and all A64 based Semprons greater than 1.8 GHz support this feature. Power can be saved significantly when an application does not require full performance. The processor can also respond to increased workloads, allowing the system to deliver a responsive computing experience.

Like *Cool'n'Quiet*, AMD *PowerNow* is also a speed throttling and power saving technology of AMD processors used in laptops. All *AMD-K6-2E+* and *AMD-K6-IIIE+* low power embedded processors support *PowerNow*. The processor clock speed and core voltages are automatically decreased (based on power policy) when the computer is under low load or idle, to save battery power and to reduce heat (noise). The AMD *PowerNow* technology supports a wide range of operating voltages ranging from 0.0925 V to 2 V (allowing 32 different core voltages with a step as small as 25 mV or 50 mV). The technology also supports frequency starting from as low as 133 MHz or

200 MHz (allowing steps of 33 MHz or 50 MHz) depending on the processor model. Table 2.2 shows an example voltage and frequency levels using *PowerNow* technology. The allowed voltage step is 0.1 volts with the respective frequency switching of 50 MHz.

Table 2.2: Supported Voltages and Frequencies for Low Power AMD-K6<sup>TM</sup>2E+Processors[20]

| Processor         | Core Voltage | Range of Supported Operating Frequencies | Active Power |  |

|-------------------|--------------|------------------------------------------|--------------|--|

| AMD-K6-2E+/450APZ | 1.7 V        | 450-200 MHz                              | 8.70-4.90 W  |  |

|                   | 1.6 V        | 400-200 MHz                              | 6.90-4.20 W  |  |

|                   | 1.5 V        | 350-200 MHz                              | 5.60-3.70 W  |  |

|                   | 1.4 V        | 300-200 MHz                              | 4.30-2.95 W  |  |

| AMD-K6-2E+/400xTZ | 1.6 V        | 400-200 MHz                              | 6.90-4.20 W  |  |

|                   | 1.5 V        | 350-200 MHz                              | 5.60-3.70 W  |  |

|                   | 1.4 V        | 300-200 MHz                              | 4.30-2.95 W  |  |

| AMD-K6-2E+/350xUZ | 1.5 V        | 350-200 MHz                              | 5.60-3.70 W  |  |

|                   | 1.4 V        | 300-200 MHz                              | 4.30-2.95 W  |  |

Beside DVFS support, *PowerNow* technology provides different operating modes like *High performance, Power saver* and *Automatic* mode defined for specific performance and power requirements. The AMD *PowerNow* technology contains *Enhanced Power Management (EPM)* Block that can be accessed by the OS to change operating frequency and voltages. The OS based power management policies are responsible for carrying the burden of invoking EPM block. However, locking of processor from external interrupts, snoops, etc. during transition is handled automatically.

AMD has also provided other power management technologies like *AMD PowerCap Manager* that allows IT data center managers to fix power consumption on server processors. Similarly, *Advanced Platform Management Link* (APML) technology provides new controls to monitor power and cooling. Detailed description of these technologies can be seen in [13].

## 2.1.4.3 ARM

ARM is very well known for developing low-power processor IP technology. The ARM power management kit contains a collection of standard cells specifically designed to allow the implementation of various low power techniques. Almost all ARM processors

contain support for low power states (idle states); additionally, cores like ARM1176JZF-S, CortexA9, CortexA15, etc. also contain support for DVFS. To allow DPS, the typical ARM processor allows support for four sleep states which are Active or Run, Standby, Dormant and Shutdown. The processor is in Run mode when everything is clocked and powered up. In a Standby state, the CPU clock is stopped by executing a Wait For Interrupt (WFI) instruction. WFI Standby mode disables most of the clocks in a processor, while keeping its logic powered up. This reduces the power drawn to the static leakage current, leaving a tiny clock power overhead requirement to enable the device to wake up. The *Dormant* state enables the processor to be powered down while leaving the caches powered up and maintaining their state. The *Shutdown* state powers down the entire device and all states, including the cache content which must be saved by an external software. The Power Management Controller (PMC) determines whether the processor should be put into Active, Standby, Dormant, or Shutdown state. However, the choice to use these states is controlled by a policy manager. For an example, Linux OS with the help of ACPI infrastructure contains a CPUIdle driver, to direct PMC to use one of the predefined low power states. The PMC informs the processor about the nature of reset that has occurred. Whether the reset occurred due to exiting *Dormant* mode or *Shutdow* mode, the processor is branched to the correct state restore routine.

To allow DVFS when in active state, ARM offers a system-level power management scheme called *Intelligent Energy Management (IEM)* for energy and power management. This is a combination of hardware and software technology that allows DVFS to reduce energy consumption. The *IEM* solution is designed primarily for battery-powered equipment, where the requirement is to have a long battery life. The *IEM* solution is also ideal for portable devices, for example, smart phones, feature phones, Personal Digital Assistants (PDA), handheld game consoles and media players, etc. A typical *IEM* System on Chip (SoC) solution is shown in figure 2.3. A complete *IEM* solution is made up of a number of hardware and software components. The *IEM* software component uses information (based on workload) from the operating system to build up a historical view of the application execution on the system. A number of different software algorithms are applied to classify the types of activity and to analyze their processor utilization patterns. The results of each analysis are combined to make a global prediction about the future performance requirement for the system. This prediction is used by the *Intelligent Energy Controller* IEC.

Figure 2.3: Intelligent Energy Management Solution by ARM. [22]

The IEC uses prediction performance level requests from the *IEM* software. The performance setting is communicated to the IEC, so that the platform scaling hardware can be controlled to bring the system to the required performance level. Battery life is extended by lowering the operating frequency and voltage of SoC components (such as the processor) which consequently reduces energy consumption. The IEC also measures the work done in the system to ensure that the software deadlines are not going to be missed. Additionally, the IEC also supports a maximum performance request feature. Further information regarding *IEM* and IEC can be seen in [22] and [23].

In the following section, we discuss the power management provided by Linux, to further understand how efficiently power can be saved. In addition, we also provide a discussion of academic works on power strategies, to highlight other opportunities for power management than workload based approaches.

#### 2.1.4.4 Linux

Besides available market standards and their power management solutions, popular operating systems like Linux, Windows, Mac OS also provide support for better power solutions to deal with rapid technological advancements. Linux is an open-source operating system that is widely used in modern devices. Linux supports two implementations of power management: Advanced Power Management (APM) and Advanced Configuration and Power Interface (ACPI). Detailed description of processor sleep states available in APM and ACPI is presented in section 2.1.2. In the following, we focus on the mechanisms and strategies used for proper exploitation of these states in Linux. At system level, ACPI defines mechanisms for putting the computer as a whole

in and out of system sleeping states. It also provides a general mechanism for any device to wake the computer. ACPI tables also describe motherboard devices, their power states, the power plans the devices are connected to, and controls for putting devices into different power states. This enables the OS to put devices into low-power states based on application overall power usage. According to the description of the ACPI states provided in section 2.1.2, each state introduces greater power savings but requires commensurately more time to awaken and begin performing work. Linux device drivers are generally responsible for saving device states before putting and restoring the device in low power modes. Generally, applications are not involved in power management state transitions.

Linux contains an infrastructure  $pm_dev$  to maintain information about every power management event. Device drivers must have to register themselves with Linux power management subsystem. They do this by calling  $pm_register$  that contains necessary device information like its type, identity (ID) and functionality. The Linux pm.h file contains various types and IDs used by these drivers. When a power management event occurs, arguments like device name, device state, device data, etc. are passed to device drivers to perform specific tasks. For example, in case the device is a liquid crystal display (LCD), an event could be  $pm_suspend$  to save the device state and turn off the display. Similarly, if a  $pm_resume$  event occurs, the LCD driver should restore the saved state back. When the device is not used anymore, its driver should unregister itself from the power management infrastructure. When a device is unregistered, the power management does not involve that device in future power management events.

At CPU level, power is controlled by using processor's idle power states (C-states) or by changing the CPU frequency (P-states). The number of C-states and P-states depend upon processor and can vary independently. These are typically implemented with the help of ACPI as described in section 2.1.2. However, special infrastructures are present to make use of these idle and performance states. The *CPUIdle* subsystem provides the functionality of separating the layers to make use of C-states. The *CPUIdle* drivers are found in architecture-specific ACPI code. On the other hand, the decision of choosing which idle state is decided by the policy (power strategy). Linux contains *CPUIdle governors* that allow the implementation of different policies for distinct needs. It should be noted that deeper sleep (C-states) saves more power, but the downside is that they have higher latency (the time the CPU needs to go back to C0).

Processor in operating state (C0 state) can be in one of different P-states. The *CPUFreq* is used to set a static or dynamic power policy for the system. It uses the *CPUFreq* driver to dynamically scale the processor frequencies at runtime. The *CPUFreq* provides a common interface to the various low-level technologies and high-level policies. The Linux in-kernel *governors* (policy governors that can change the CPU frequency based on different criteria), and CPU specific drivers (*CPUFreq*) are used to implement the technology for the specific processor. The processor consumes less power while still doing work, and the tradeoff comes between power and performance, rather than power and latency. Each governor has its own unique behavior, purpose, and suitability in terms of workload. Generally, there are five different types of *CPUFreq* governors, i.e. *Performance*, *Powersave*, *OnDemand*, *Conservative* and *Userspace*. A brief description of these governors is given below:

#### Performance

The *Performance* governor forces the CPU to use the highest possible clock frequency. This frequency is statically set and will not change. As such, this particular governor offers no power saving benefit. It is usually suitable for hours of heavy workload, and only during times wherein the CPU is rarely (or never) idle.

#### **Powersave**

The *Powersave* governor forces the CPU to use the lowest possible clock frequency. This frequency is statically set and will not change. By itself, this specific governor offers maximum power savings, but at the cost of the lowest CPU performance. The *Powersave* governor is more a "speed limiter" for CPU than a "power saver". It is most useful in systems and environments where overheating can be a problem.

#### **OnDemand**

The *OnDemand* governor is a dynamic governor that allows the CPU to achieve maximum clock frequency when the system load is high, and also minimum clock frequency when the system is idle. The *OnDemand* governor uses parameters such as the *sampling-rate*, *up-threshold*, *sampling-down-frequency*, *ignore-nice-load*, etc. to make the frequency switch decision. As an illustration, the *sampling-rate* is used to let the kernel decide how often (in microseconds) a transition is needed. *Up-threshold* is the average CPU usage (CPU %) during sampling time. Similarly, other parameters have

their own special functionality. While the *OnDemand* governor allows the system to adjust power consumption with respect to system load, it does so at the expense of latency related to frequency switching. For most systems, the *OnDemand* governor can provide the best compromise among heat emission, power consumption, performance, and manageability. When the system is only busy at specific times of the day, the *OnDemand* governor will automatically switch between maximum and minimum frequency depending on the load without any further intervention.

#### Conservative

Like the *OnDemand* governor, the *Conservative* governor also adjusts the clock frequency according to usage. However, while the *OnDemand* governor does so in a more aggressive manner (that is from maximum to minimum and back), the *Conservative* governor switches between frequencies more gracefully. This means that the *Conservative* governor will adjust to a clock frequency that it deems fitting for the load, rather than jumping to max speed the moment there is any load. A parameter called *freq\_step* is used to define frequency steps to smoothly increase or decrease frequency. Conservative governor can possibly provide significant savings in power consumption however; it does so at an ever greater latency than the *OnDemand* governor.

### Userspace

The *Userspace* governor allows user programs (or any process running as root) to set the frequency. This governor is normally used in conjunction with the cpuspeed daemon. A parameter called *Scaling\_setspeed* is used to write desired frequency. Consequently, *Userspace* is the most customizable of all the governors and depending on how it is used, it can actually provide a dynamic balance between performance and power consumption for the system.

The above discussion summarizes our discussion on available technologies, market standards and power management done in Linux OS. It also puts light on specific power management techniques provided by different manufacturers. A conclusion highlighting the benefits, drawbacks and limitations of these standards is given in the next section.

#### 2.1.4.5 Conclusion

Based on the above discussion, power management can be broadly divided into two categories. Firstly, OS based power management policies such as in Linux and secondly vendor specific power management policies like Intel's *EIST* or ARM's *IEM*. In both cases, such existing power management policies rely on the total workload of a system (which is more related to the hardware state), during a certain period to deal with power issues. These policies present the advantage of being applicable in all cases (general purpose), but the drawback is probably a certain level of inefficiency (since they do not really consider application knowledge).

Therefore, new power management solutions should be provided to overcome these shortcomings. The idea is to make a tradeoff between power and performance through power-aware algorithms. Currently, a lot of academic research is being done on accurately predicting the workload during a certain time period or to exploit other paradigms (e.g. Low power scheduling). Researchers are continuously exploring new techniques (based on application properties) to use the underlying hardware efficiently. Similarly, as some OS based policies give the user freedom to create its own custom defined policy, novel parameters (other than workload) should be used to define such custom policies, in order to further optimize energy and power consumption. The next section presents academic research on power strategies that have room for higher power savings.

## 2.1.5 Academic Research

#### 2.1.5.1 Overview of Academic Research

Researchers have focused on how to estimate and minimize power in modern systems at various levels of design. At the system level, dynamic power switching (DPS) can be efficiently used to put active components in shutdown or low power states to conserve energy. The fundamental principle for the applicability of DPS is that systems (and their components) experience non-uniform workloads during operation time. Due to this distinct behavior of workload, DPS techniques exhibit different behavior. A survey of various DPS based strategies is shown in [17], where a system-level approach is used to manage power. A dynamic power strategy (or policy) is used to control when and which

of the low-power states to apply. Existing policies are usually based on workload predictions and a detailed comparison of the different algorithms has been provided in the survey. From this survey and others like in [24], dynamic power policies are categorized into two broad categories i.e. *predictive* and *stochastic* schemes. *Predictive* schemes typically exploit temporal correlation between the past history of the workload and it's near future, to predict the upcoming workloads. *Stochastic* techniques model the workload behavior as a controlled Markov process and find the optimal power management based on the model. *Predictive* techniques may cause extra penalties like power loss in transition, wake-up state energy consumption, etc. when the workload is varying widely. However, *stochastic* approaches have inaccuracies in modeling workload variations and complexity involved in solving the optimization problem.

These issues primarily limit the use of both schemes for systems where the workload is either very ir-regular or the workload model is not known a priori. Some advanced history based heuristics and *stochastic* schemes have been shown in [25], to predict varying workloads with high accuracy. However, their computational complexity severely limits their use and may not be suitable for applications having huge workload revisions. Besides system level dynamic power switching approach, another way to reduce power consumption is the use of application knowledge because the application knows the most about its future workload. An example of such work is shown in [26], where a limited application knowledge such as the size and type of the frames is used for applying DPS. These above methods have their advantages and are simple to design. However, relying purely on policies that use only low power states can be efficient but not always optimal or applicable. Therefore, researchers started to explore new methods by utilizing the support of dynamic voltage and frequency scaling (DVFS).

A lot of work has been carried out for implementing DVFS based policies at the processor level [16, 27-34]. Generally, these algorithms can be classified as static or dynamic algorithms. Static algorithms have a complete knowledge of the task set and its constraints, such as deadlines, computation times, precedence constraints, and future release times. Frequency is statically decided before the execution of a task set. We can obtain a single processor frequency that never changes, or obtain variable frequencies that are statically decided before execution of a task set. An example of such an algorithm is shown in [16], where Sys-Clock and PM-Clock algorithms determine the frequency needed to complete the task set. The algorithm determines single clock frequency at admission control and keep it constant until the taskset changes. Static

algorithms are based on the assumption that processor speed can vary continuously in a given range. In practical world, processors only have discrete frequency levels so choosing a higher-frequency level than calculated may result in granting performance, but it may result in extra power consumption. Some static algorithms use task parameters as selection criteria to obtain the needed frequency. Given a set of periodic tasks, the sequence of frequency changes to be performed on the processor during execution can be calculated offline. The task schedule is periodic and the voltage schedule computed by this way is also periodic and can be stored in a table. An example of such an assignment is shown in [35], where distinct speed is assigned to different tasks, based on the voltage schedule table obtained by offline scheduling. However, there is a major drawback of static assignment of frequency. If an activation of a task is missed, the whole frequency assignment is affected and may become inefficient.