# Exploration architecturale pour la conception d'un système sur puce de vision robotique, adéquation algorithme-architecture d'un système embarqué temps-réel

Thomas Lefebvre

#### ▶ To cite this version:

Thomas Lefebvre. Exploration architecturale pour la conception d'un système sur puce de vision robotique, adéquation algorithme-architecture d'un système embarqué temps-réel. Autre. Université de Cergy Pontoise, 2012. Français. NNT: 2012CERG0582. tel-00783790

### HAL Id: tel-00783790 https://theses.hal.science/tel-00783790

Submitted on 27 Nov 2014

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# Exploration architecturale pour la conception d'un système sur puce de vision robotique, adéquation algorithme-architecture d'un système embarqué temps-réel

Thomas Lefebvre

Laboratoire ETIS

Université de Cergy-Pontoise

Thèse présentée pour le titre de Docteur de l'université de Cergy-Pontoise

Soutenue le Lundi 2 juillet 2012 devant la commission d'examen :

Michel Paindavoine : Rapporteur Jocelyn Sérot : Rapporteur Serge Weber : Examinateur Lionel Lacassagne : Examinateur Nicolas Cuperlier : Examinateur

Benoît Miramond : Encadrant de thèse Lounis Kessal : Co-Directeur de thèse François Verdier : Directeur de thèse

#### Résumé

La problématique de cette thèse se tient à l'interface des domaines scientifiques de l'adéquation algorithme architecture, des systèmes de vision bio-inspirée en robotique mobile et du traitement d'images. Le but est de rendre un robot autonome dans son processus de perception visuelle, en intégrant au sein du robot cette tâche cognitive habituellement déportée sur un serveur de calcul distant. Pour atteindre cet objectif, l'approche de conception employée suit un processus d'adéquation algorithme architecture, où les différentes étapes de traitement d'images sont analysées minutieusement. Les traitements d'image sont modifiés et déployés sur une architecture embarquée de façon à respecter des contraintes d'exécution temps-réel imposées par le contexte robotique.

La robotique mobile est un sujet de recherche académique qui s'appuie notamment sur des approches bio-mimétiques. La vision artificielle étudiée dans notre contexte emploie une approche bio-inspirée multirésolution, basée sur l'extraction et la mise en forme de zones caractéristiques de l'image.

Du fait de la complexité de ces traitements et des nombreuses contraintes liées à l'autonomie du robot, le déploiement de ce système de vision nécessite une démarche rigoureuse et complète d'exploration architecturale logicielle et matérielle. Ce processus d'exploration de l'espace de conception est présenté dans cette thèse. Les résultats de cette exploration ont mené à la conception d'une architecture principalement composée d'accélérateurs matériels de traitements (IP) paramétrables et modulaires, qui sera déployée sur un circuit reconfigurable de type FPGA. Ces IP et le fonctionnement interne de chacun d'entre eux sont décrits dans le document. L'impact des paramètres architecturaux sur l'utilisation des ressources matérielles est étudié pour les traitements principaux. Le déploiement de la partie logicielle restante est présenté pour plusieurs plate-formes FPGA potentielles.

Les performances obtenues pour cette solution architecturale sont enfin présentées. Ces résultats nous permettent aujourd'hui de conclure que la solution proposée permet d'embarquer le système de vision dans des robots mobiles en respectant les contraintes temps-réel qui sont imposées.

This Ph.D Thesis stands at the crossroads of three scientific domains: algorithm-architecture adequacy, bio-inspired vision systems in mobile robotics, and image processing. The goal is to make a robot autonomous in its visual perception, by the integration to the robot of this cognitive task, usually executed on remote processing servers. To achieve this goal, the design approach follows a path of algorithm architecture adequacy, where the different image processing steps of the vision system are minutely analysed. The image processing tasks are adapted and implemented on an embedded architecture in order to respect the real-time constraints imposed by the robotic context.

Mobile robotics as an academic research topic based on bio-mimetism. The artificial vision system studied in our context uses a bio-inspired multiresolution approach, based on the extraction and formatting of interest zones of the image.

Because of the complexity of these tasks and the many constraints due to the autonomy of the robot, the implementation of this vision system requires a rigorous and complete procedure for the software and hardware architectural exploration. This processus of exploration of the design space is presented in this document.

The results of this exploration have led to the design of an architecture primarly based on parametrable and scalable dedicated hardware processing units (IPs), which will be implemented on an FPGA reconfigurable circuit. These IPs and the inner workings of each of them are described in the document. The impact of their architectural parameters on the FPGA resources is studied for the main processing units. The implementation of the software part is presented for several potential FPGA platforms.

The achieved performance for this architectural solution are finally presented. These results allow us to conclude that the proposed solution allows the vision system to be embedded in mobile robots within the imposed real-time constraints.

#### Remerciements

Le document que vous avez entre vos mains est le résultat de plus de quatre ans de travail, et il n'aurait pas pu exister sans l'aide de nombreuses personnes.

Tout d'abord, je souhaite remercier les membres du jury qui ont jugé ce travail digne du grade de docteur : MM. Michel Paindavoine et Jocelyn Sérot, pour leur rôle de rapporteur et le travail qui y est associé; ainsi que MM. Serge Weber, Lionel Lacassagne, et Nicolas Cuperlier, pour avoir accepté le rôle d'examinateur.

Je remercie le laboratoire ETIS représenté par sa directrice, Inbar Fijalkow, pour l'accueil et les moyens mis à disposition pour l'hébergement de ce projet.

Je remercie aussi le service informatique d'ETIS, notamment Michel Leclerc, Michel Jordan, et bien sûr Laurent Protois, ainsi que les secrétaires Annick Bertinotti et Astrid Cébron pour leur aide précieuse.

Les travaux présentés dans ce document ont été dirigés par trois personnes que je souhaite remercier : François Verdier, pour la confiance et la liberté qu'il m'a accordé sur mes travaux, Lounis Kessal, pour son aide précieuse quant à la conception d'IP, et Benoît Miramond, qui est peu à peu devenu indispensable et qui a beaucoup aidé à orienter cette thèse, notamment en encadrant de nombreux stages et projets à l'université autour de mon sujet de thèse. Je les remercie également tous les trois pour leur travail de relecture sans lequel ce document serait beaucoup moins clair et lisible.

D'autres personnes ont pu m'aider lors de ces travaux, je souhaite donc remercier Laurent Fiack, Fred Demelo, David Bailly, ainsi que les stagiaires avec lesquels j'ai pu travailler.

Un grand merci à Mohamed El Amine Benkhelifa, qui m'a énormément aidé pour mes cours à l'IUT lors de mon monitorat et de mon contrat d'ATER, merci aussi à toute l'équipe de l'IUT GEII de Neuville, c'était sympa de passer de l'autre côté de la barrière.

Au cours des années passées à ETIS, j'ai pu voir de nombreuses personnes arriver au labo et/ou en partir, je souhaite remercier tout d'abord mes collègues de bureau : Emmanuel Huck, Abdel-Nasser Assimi, Heyckel Houas, et finalement Lotfi Bendaouia et Liang Zhou. Un grand merci aussi pour leur amitié et/ou leur sympathie à Samuel Garcia, Guy Wassi, Jean-Emmanuel Haugeard, David Gorisse, Auguste Venkiah, Julien Gony, Ayman Alsawah, Shuju Zhao, Laurent Rodriguez, Laurent Gantel, Amel Khiar, Jean-Christophe Sibel, Ludovic Danjean, Alexis Lechervy, Leila Meizou, Gaël Rigaud, Ismail Ktata, Erbao Li, Fatine Lahmani et enfin Roland-Christian Gamom Ngounou Ewo. J'en ai surement oublié, je les remercie aussi.

Merci aussi à Bertrand Granado, Emmanuelle Bourdel, Myriam Ariaudo, Philippe-Henri Gosselin, David Picard, et Fakhreddine Ghaffari, des permanents particulièrement sympas.

Enfin, si je suis content d'avoir fait cette thèse, c'est aussi et surtout car j'ai pu rencontrer Sonja Khatchadourian. Merci Sonja pour ton soutien et tes conseils lors de la fin de ma thèse. Merci aussi à Monique Khatchadourian et Sonja pour la préparation du délicieux pot de thèse.

Merci à mon père et à ma sœur, Bruno et Karine Lefebvre, qui ont pu assister à ma soutenance et même en comprendre les grandes lignes!

Merci à ma mère, qui voulait assister à ma soutenance, et dont la mémoire a été ma motivation principale pour tenir jusqu'au bout.

# Table des matières

| Т  | able                              | des fig  | ires                                              | V  |

|----|-----------------------------------|----------|---------------------------------------------------|----|

| Li | Liste des tableaux V Introduction |          |                                                   |    |

| In |                                   |          |                                                   |    |

|    | Cad                               | re du p  | $\mathrm{rojet}$                                  | 1  |

|    | Prol                              | blémati  | que                                               | 2  |

|    | Stru                              | icture d | u document                                        | 3  |

| 1  | Pré                               | sentat   | on du projet                                      | 5  |

|    | 1.1                               | Conte    | rte                                               | 5  |

|    |                                   | 1.1.1    | Équipes Neurocybernétique et ASTRE                | 5  |

|    |                                   | 1.1.2    | Présentation du système de vision                 | 6  |

|    |                                   | 1.1.3    | Place du système de vision au sein du robot       | 7  |

|    |                                   | 1.1.4    | Contraintes temps-réel non-strictes               | 8  |

|    |                                   | 1.1.5    | Consommation électrique et dimensions du système  | 9  |

|    | 1.2                               | Décou    | page fonctionnel                                  | 11 |

|    |                                   | 1.2.1    | Gradient                                          | 11 |

|    |                                   | 1.2.2    | Pyramide Gaussienne                               | 14 |

|    |                                   | 1.2.3    | Recherche de points d'intérêt                     | 17 |

|    |                                   | 1.2.4    | Tri des points d'intérêt                          | 18 |

|    |                                   | 1.2.5    | Mise en forme des caractéristiques locales        | 20 |

|    | 1.3                               | Flot d   | e conception du système de vision                 | 23 |

|    |                                   | 1.3.1    | Flot de conception logiciel embarqué              | 24 |

|    |                                   |          | 1.3.1.1 Caractérisation de l'application complète | 26 |

|    |                                   |          | 1.3.1.2 Découpage logiciel/matériel               | 27 |

#### TABLE DES MATIÈRES

|   |     |          | 1.3.1.3 Optimisation de la partie logicielle du SoC 28                                                                    |

|---|-----|----------|---------------------------------------------------------------------------------------------------------------------------|

|   |     |          | 1.3.1.4 Validation                                                                                                        |

|   |     | 1.3.2    | Déploiement matériel                                                                                                      |

|   |     |          | 1.3.2.1 Parallélisation                                                                                                   |

|   |     |          | 1.3.2.2 Mise en cascade                                                                                                   |

|   |     |          | 1.3.2.3 Validation - modèle logiciel d'IP                                                                                 |

|   |     | 1.3.3    | Architecture globale du système de vision                                                                                 |

|   |     | 1.3.4    | Tests et validation                                                                                                       |

| 2 | Éta | t de l'a | art 33                                                                                                                    |

|   | 2.1 | Vision   | artificielle                                                                                                              |

|   |     | 2.1.1    | Vision robotique                                                                                                          |

|   |     | 2.1.2    | Vision artificielle bio-inspirée                                                                                          |

|   | 2.2 | Camér    | ras intelligentes                                                                                                         |

|   | 2.3 | Traite   | ment d'image                                                                                                              |

|   |     | 2.3.1    | Caractérisation d'images                                                                                                  |

|   |     | 2.3.2    | Cartographie log-polaire                                                                                                  |

|   | 2.4 | Aspect   | ts technologiques                                                                                                         |

|   |     | 2.4.1    | Systèmes sur puces (SoC)                                                                                                  |

|   |     | 2.4.2    | Parallélisation des traitements                                                                                           |

| 3 | Exp | oloratio | on logicielle 51                                                                                                          |

|   | 3.1 | Algori   | thmes $\dots \dots \dots$ |

|   |     | 3.1.1    | Norme de gradient 2D                                                                                                      |

|   |     | 3.1.2    | Pyramide Gaussienne                                                                                                       |

|   |     |          | 3.1.2.1 Filtrages Gaussiens                                                                                               |

|   |     |          | 3.1.2.2 Sous-échantillonnages                                                                                             |

|   |     |          | 3.1.2.3 Différences de Gaussiennes                                                                                        |

|   |     | 3.1.3    | Recherche de points d'intérêt                                                                                             |

|   |     | 3.1.4    | Tri des points d'intérêt                                                                                                  |

|   |     | 3.1.5    | Mise en forme des voisinages de points d'intérêt                                                                          |

|   | 3.2 | Caract   | érisation de l'application                                                                                                |

|   |     | 3.2.1    | Durées d'exécution sur PC                                                                                                 |

|   |     | 3 2 2    | Durées d'exécution sur processeur embarqué 66                                                                             |

#### TABLE DES MATIÈRES

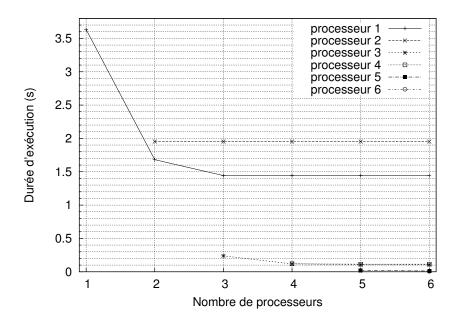

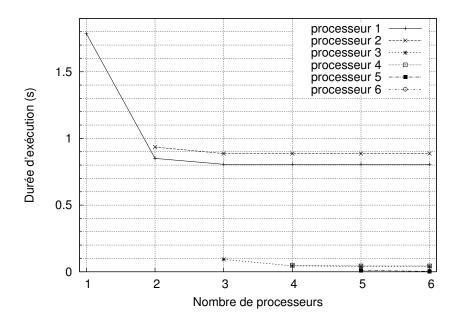

|   |      | 3.2.3                                       | Parallélisation logicielle embarquée                   | 69  |  |  |

|---|------|---------------------------------------------|--------------------------------------------------------|-----|--|--|

|   |      | 3.2.4                                       | Charge des canaux de communication                     | 72  |  |  |

|   | 3.3  | Conclu                                      | ısion                                                  | 75  |  |  |

| 4 | Arcl | Architecture des traitements matériels (IP) |                                                        |     |  |  |

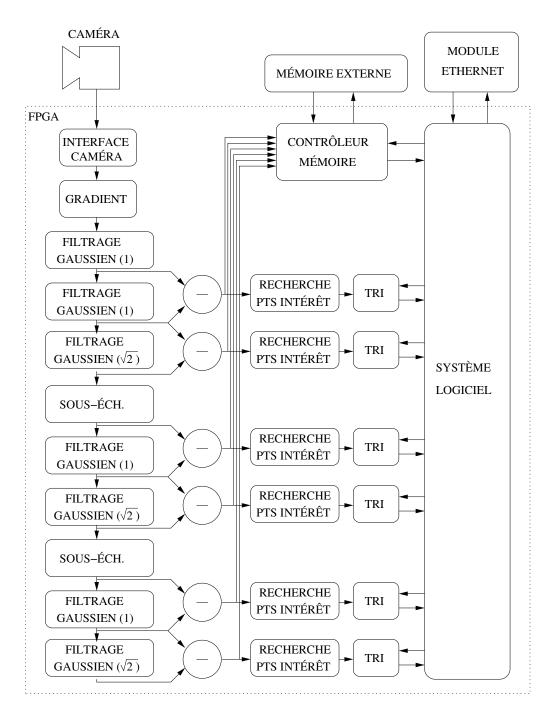

|   | 4.1  | Vue d'                                      | ensemble                                               | 77  |  |  |

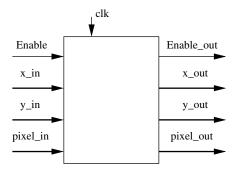

|   | 4.2  | Squele                                      | tte des IP                                             | 79  |  |  |

|   | 4.3  | Intens                                      | ité de gradient                                        | 81  |  |  |

|   | 4.4  | Filtrag                                     | ge Gaussien                                            | 82  |  |  |

|   |      | 4.4.1                                       | État de l'art : convolution Gaussienne 2D              | 83  |  |  |

|   |      | 4.4.2                                       | Noyau de convolution et division                       | 85  |  |  |

|   |      | 4.4.3                                       | Convolution 2D                                         | 87  |  |  |

|   |      | 4.4.4                                       | Coefficients redondants dans les noyaux de convolution | 91  |  |  |

|   |      | 4.4.5                                       | Séparation en deux convolutions 1D                     | 92  |  |  |

|   |      | 4.4.6                                       | Gestion des effets de bords                            | 93  |  |  |

|   | 4.5  | Différe                                     | ence de Gaussiennes                                    | 97  |  |  |

|   | 4.6  | Sous-é                                      | chantillonnage                                         | 98  |  |  |

|   | 4.7  | Reche                                       | rche de points d'intérêt                               | 99  |  |  |

|   | 4.8  | Tri de                                      | points d'intérêt                                       | 103 |  |  |

|   | 4.9  | Mise e                                      | en forme des caractéristiques log-polaires             | 105 |  |  |

|   | 4.10 | Conclu                                      | asion                                                  | 107 |  |  |

| 5 | Dép  | Déploiement 1                               |                                                        |     |  |  |

|   | 5.1  | Plate-                                      | forme de traitements                                   | 109 |  |  |

|   |      | 5.1.1                                       | Partitionnement logiciel/matériel                      | 109 |  |  |

|   |      | 5.1.2                                       | Interface réseau                                       | 111 |  |  |

|   | 5.2  | Valida                                      | tion de l'architecture                                 | 112 |  |  |

|   |      | 5.2.1                                       | Modèle logiciel des IP                                 | 112 |  |  |

|   |      | 5.2.2                                       | Simulation                                             | 117 |  |  |

|   | 5.3  | Réglag                                      | ge des paramètres                                      | 118 |  |  |

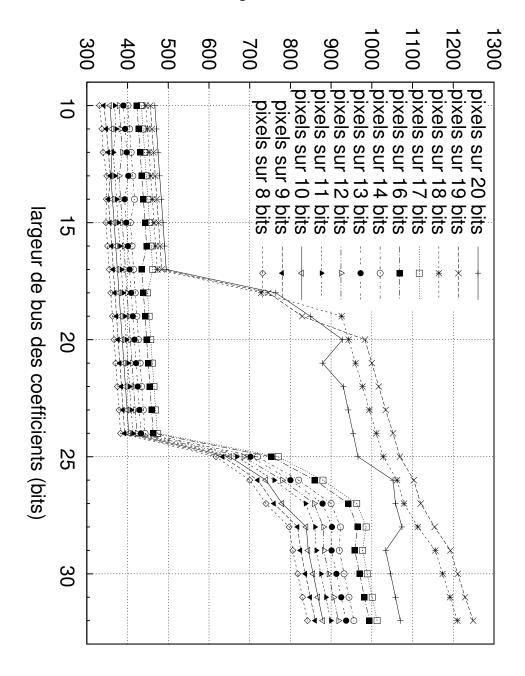

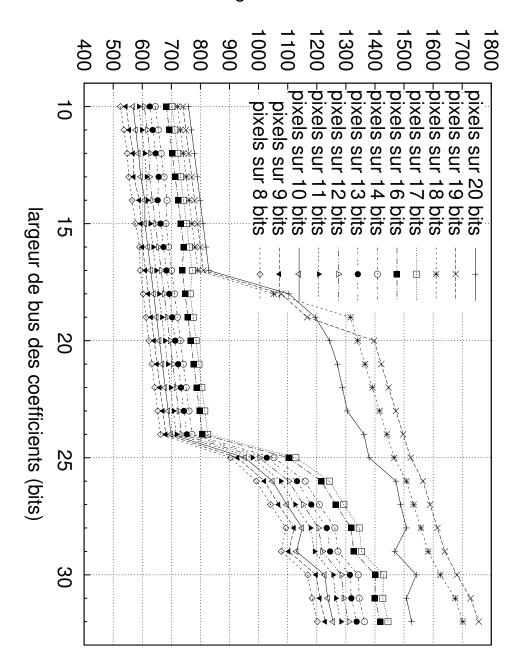

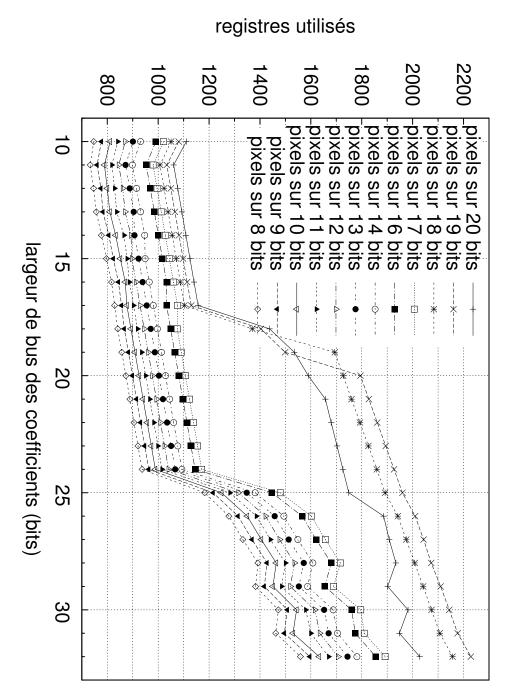

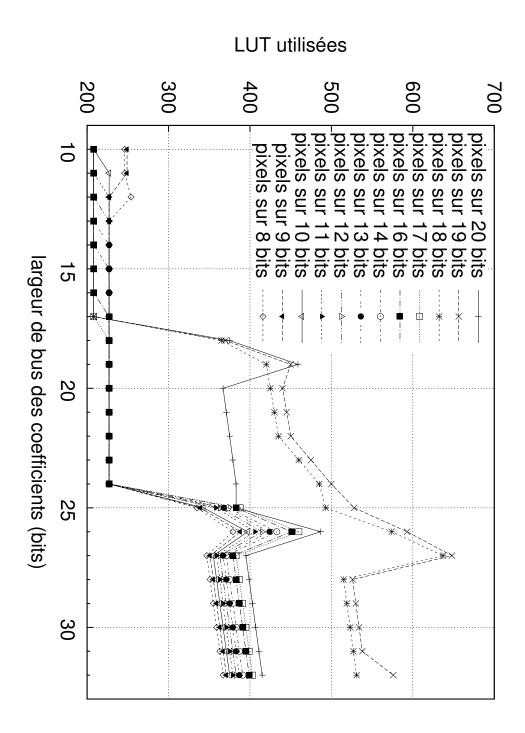

|   |      | 5.3.1                                       | Ressources utilisées par IP                            | 118 |  |  |

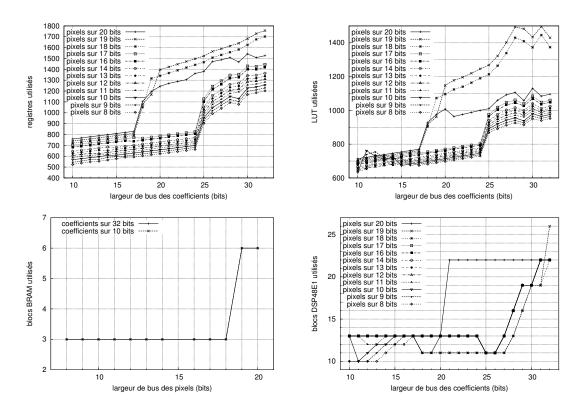

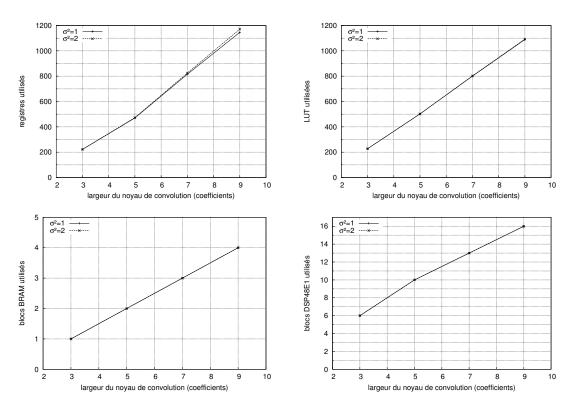

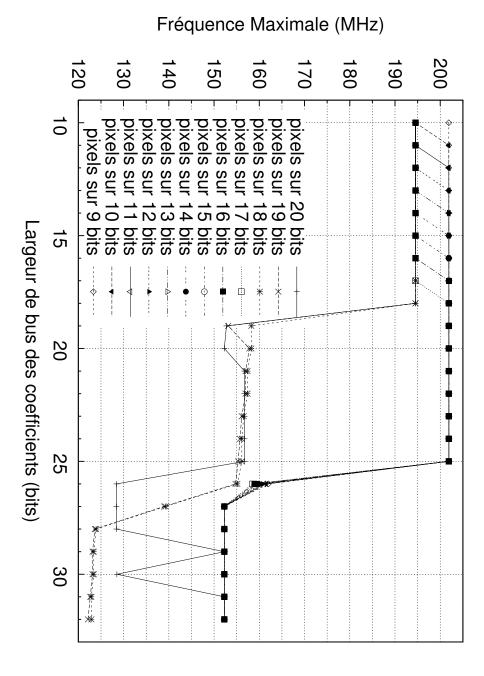

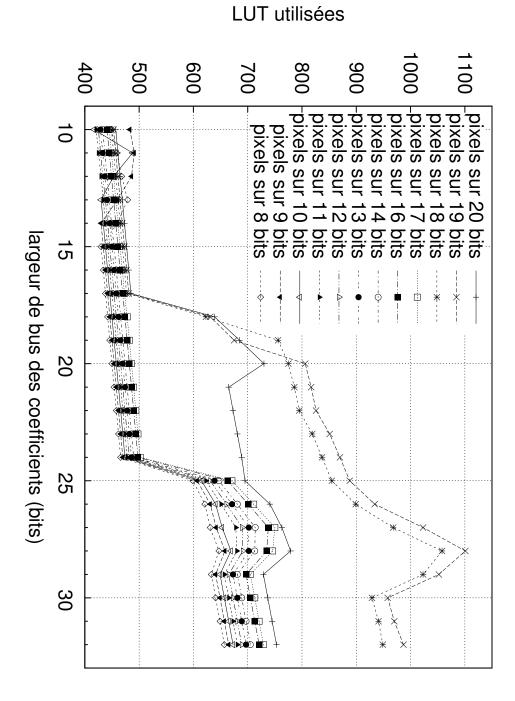

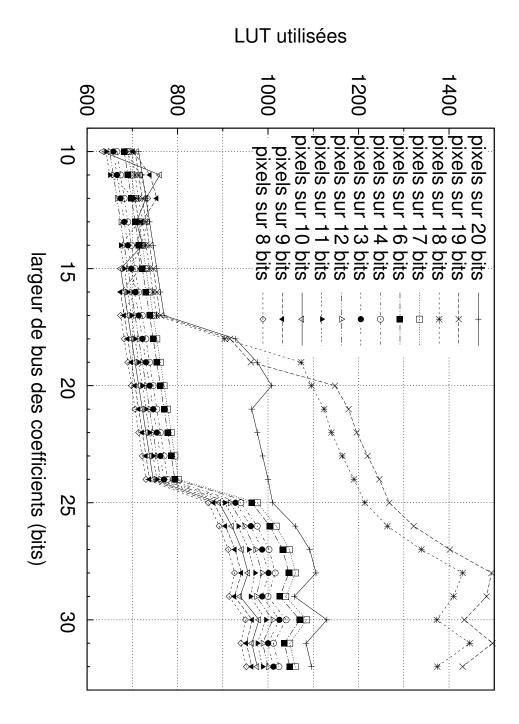

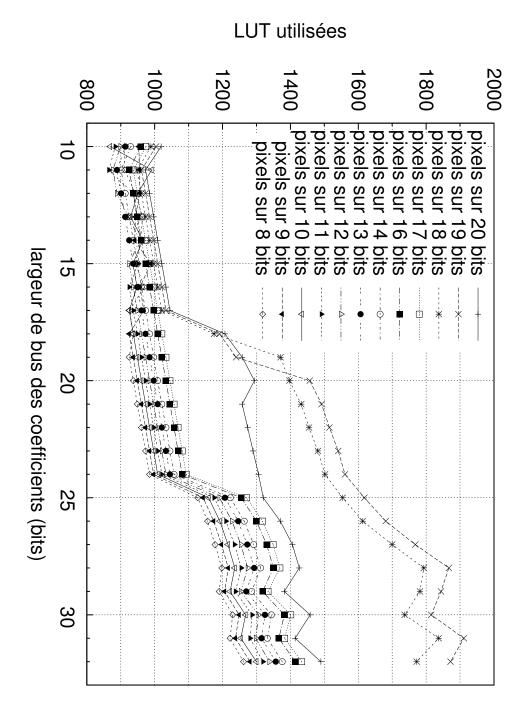

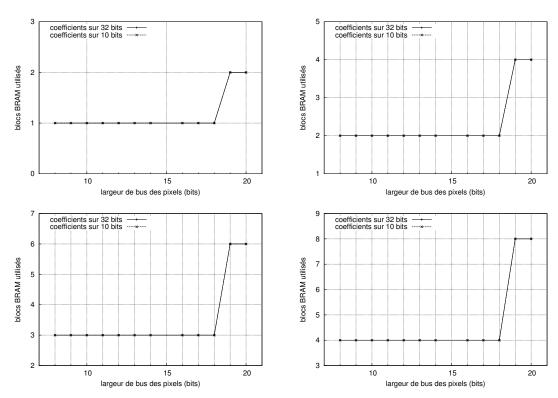

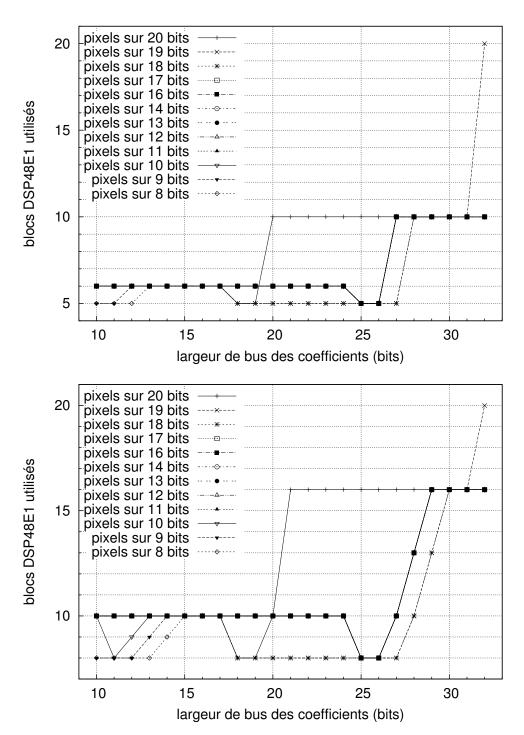

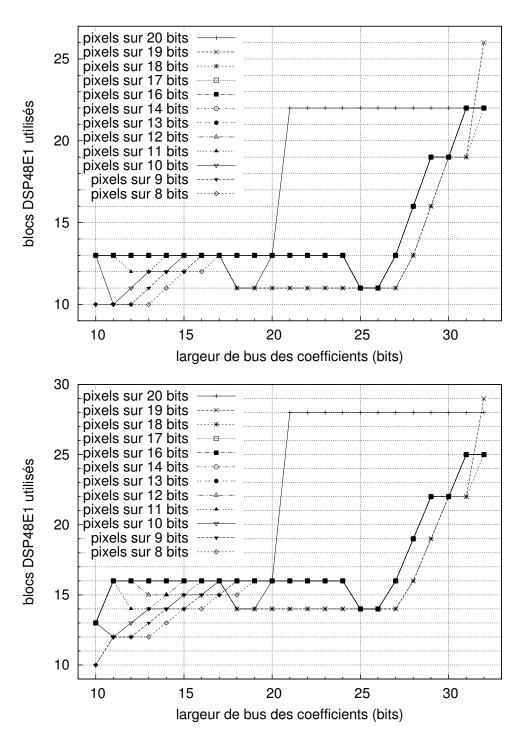

|   |      | 5.3.2                                       | Filtrage Gaussien                                      | 120 |  |  |

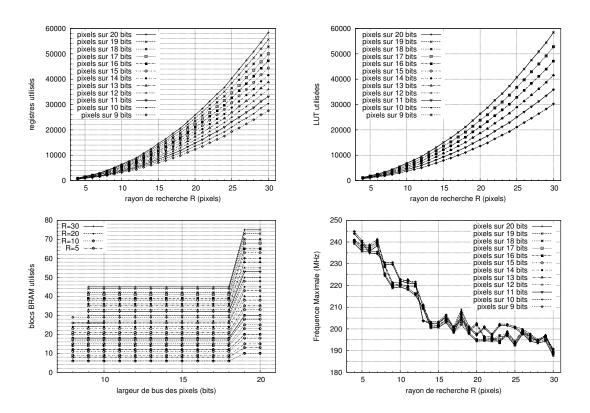

|   |      | 5.3.3                                       | Recherche de points d'intérêt                          | 123 |  |  |

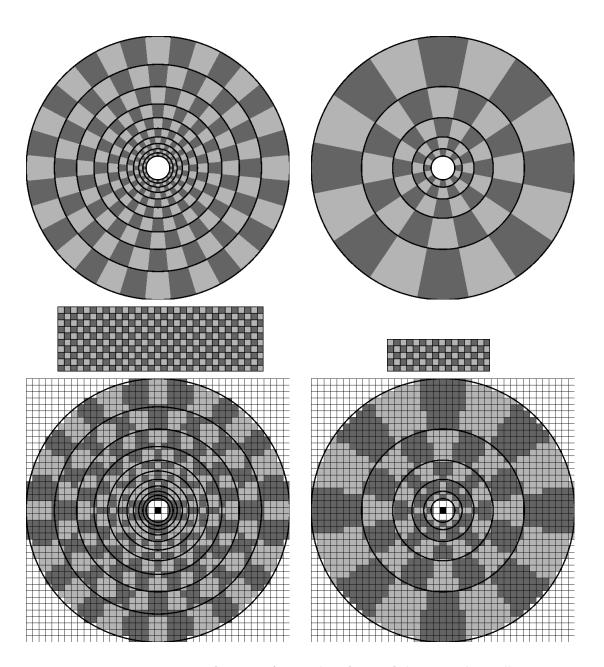

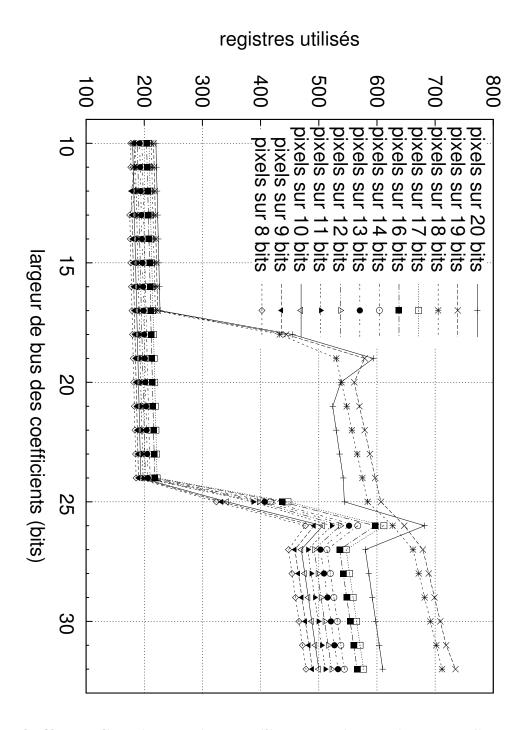

|   |      | 5 3 4                                       | Extraction de voisinages de points d'intérêt           | 126 |  |  |

#### TABLE DES MATIÈRES

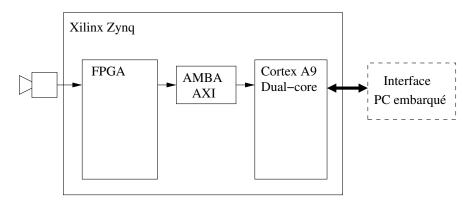

| 5.4 Choix de la plate-forme FPGA      | 127 |  |

|---------------------------------------|-----|--|

| Conclusion                            | 131 |  |

| Références                            |     |  |

| Annexes                               | 145 |  |

| Résultats de synthèse supplémentaires | 145 |  |

# Table des figures

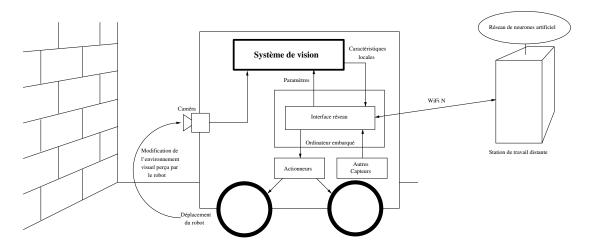

| 1.1 | Place du système de vision dans le robot                                  | 7  |

|-----|---------------------------------------------------------------------------|----|

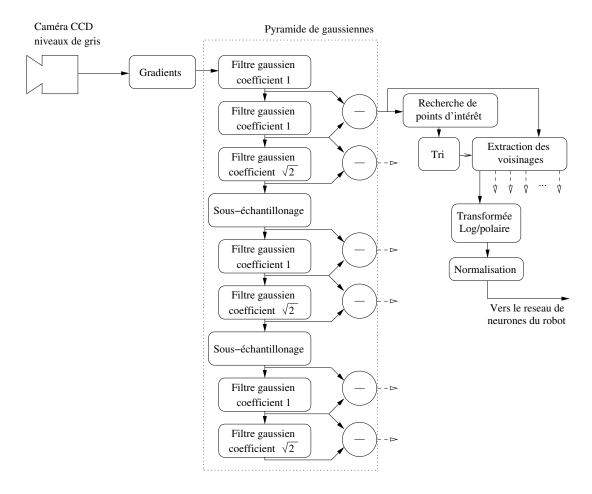

| 1.2 | Description fonctionnelle du système de vision                            | 12 |

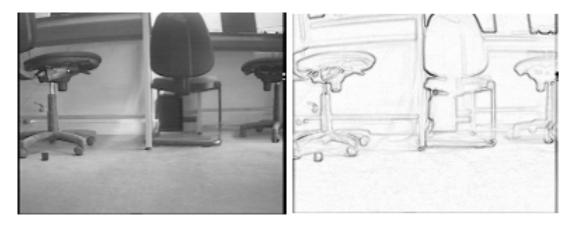

| 1.3 | Gradient                                                                  | 13 |

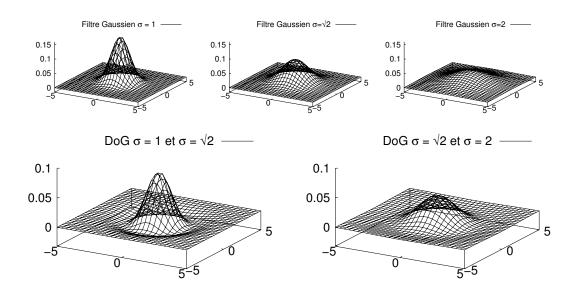

| 1.4 | Filtres de la pyramide Gaussienne                                         | 15 |

| 1.5 | Pyramide Gaussienne                                                       | 16 |

| 1.6 | Recherche et tri de points d'intérêt                                      | 19 |

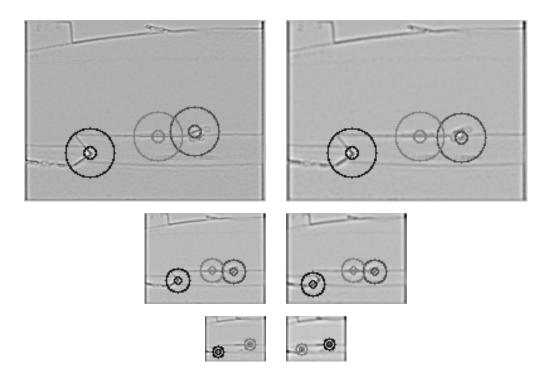

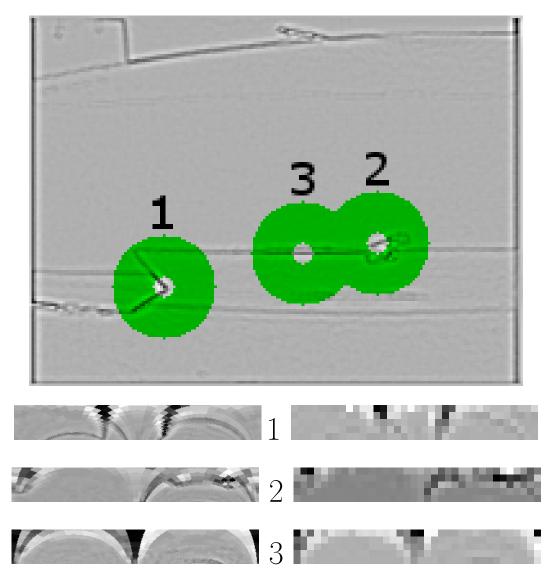

| 1.7 | Transformée log-polaire                                                   | 21 |

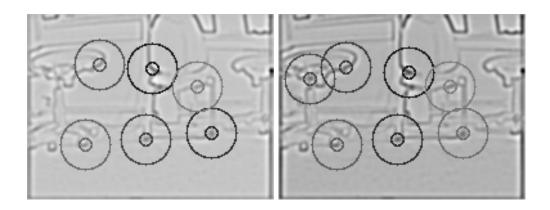

| 1.8 | Extraction de points d'intérêt                                            | 22 |

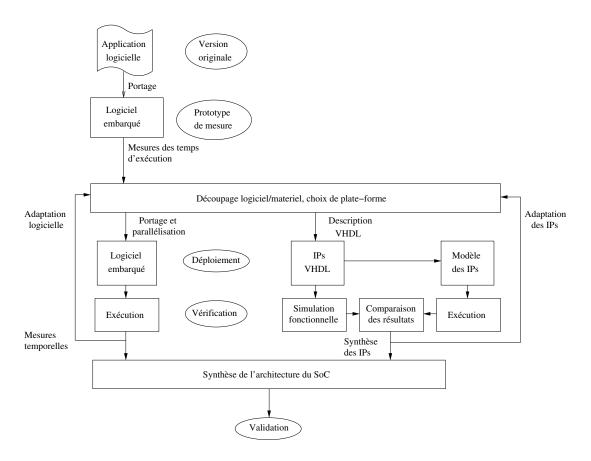

| 1.9 | Flot de conception                                                        | 25 |

| 3.1 | Opérateur de Sobel                                                        | 51 |

| 3.2 | Parallélisation sur processeurs embarqués : recherches et extractions des |    |

|     | points d'intérêt                                                          | 71 |

| 3.3 | Parallélisation sur processeurs embarqués : extractions de voisinages des |    |

|     | points d'intérêt                                                          | 72 |

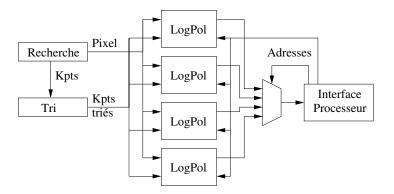

| 4.1 | Vue d'ensemble des IP                                                     | 78 |

| 4.2 | Interface des IP en flot de pixels                                        | 80 |

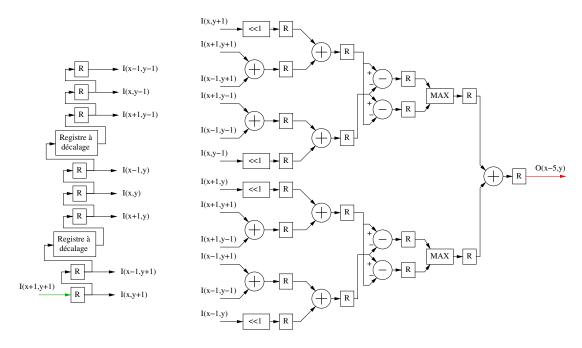

| 4.3 | IP d'intensité de gradient                                                | 81 |

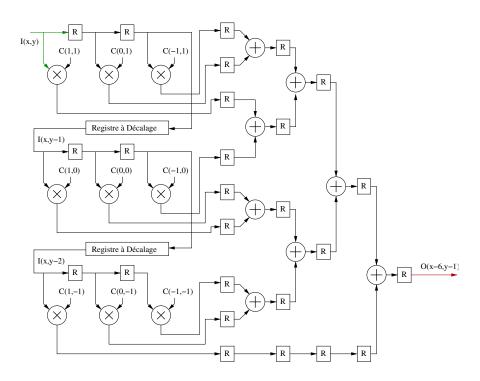

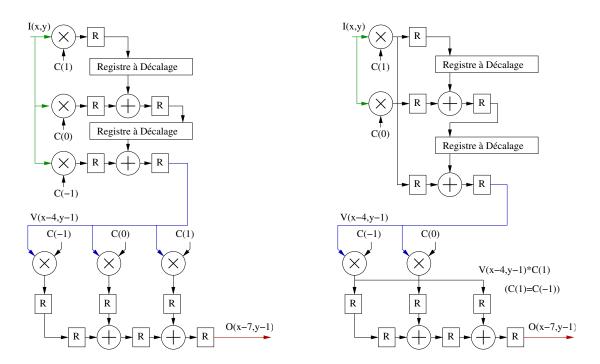

| 4.4 | Convolution 2D matérielle : Architecture traditionnelle                   | 88 |

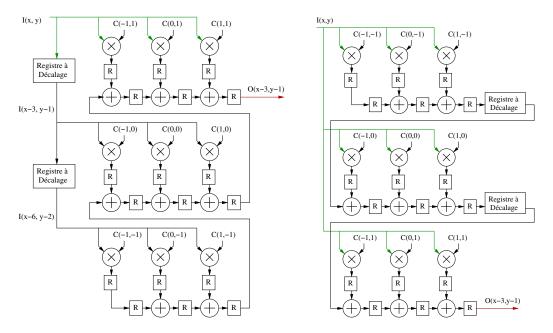

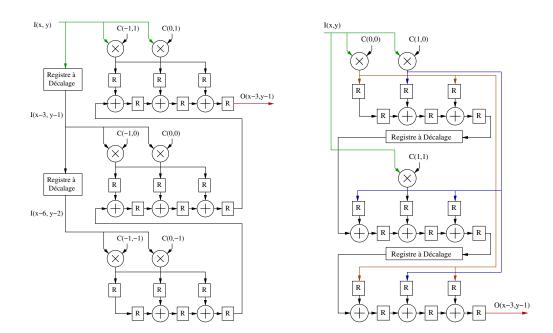

| 4.5 | Convolution 2D matérielle : Architectures type MACC                       | 89 |

| 4.6 | Convolution 2D matérielle : Coefficients redondants - architecture tradi- |    |

|     | tionnelle                                                                 | 92 |

| 4.7 | Convolution 2D matérielle : Coefficients redondants                       | 93 |

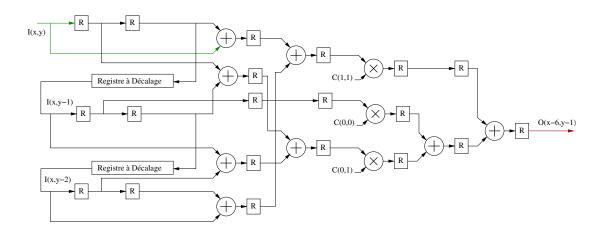

| 4.8 | Convolution 2D matérielle : deux passes 1D                                | 94 |

#### TABLE DES FIGURES

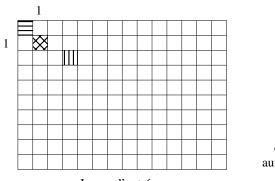

| 4.9  | Effets de bord de l'algorithme de convolution 2D                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 95  |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

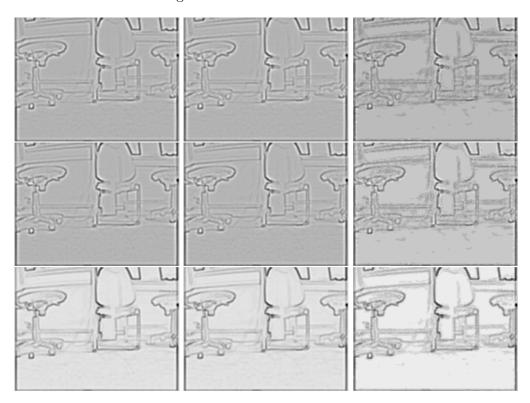

| 4.10 | Effets de bord cumulatifs théoriques des convolutions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 97  |

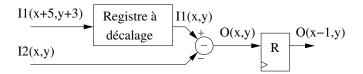

| 4.11 | IP de Différence de Gaussiennes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 98  |

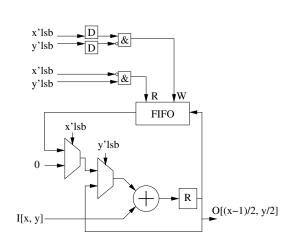

| 4.12 | IP de sous-échantillonnage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 99  |

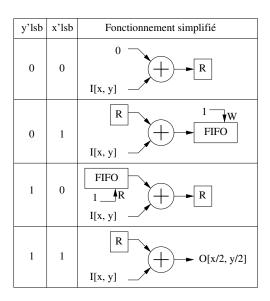

| 4.13 | IP de détection de points d'intérêt : élément décisionnel $\dots \dots \dots$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 100 |

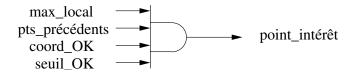

| 4.14 | IP de détection de points d'intérêt : détection de maximum local $\ \ . \ \ . \ \ .$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 101 |

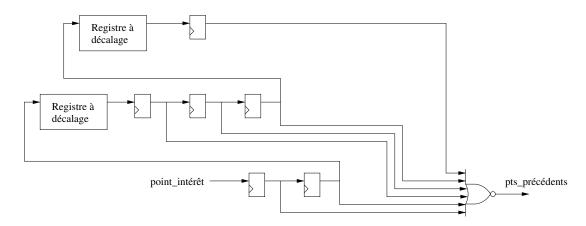

| 4.15 | IP de détection de points d'intérêt : inhibition en cas de point d'intérêt                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |     |

|      | précédent trop proche                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 101 |

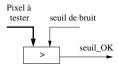

| 4.16 | IP de détection de points d'intérêt : seuil de bruit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 102 |

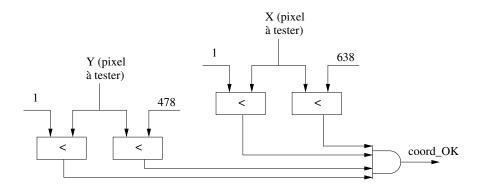

| 4.17 | IP de détection de points d'intérêt : inhibition sur les bords de l'image $% \left( 1\right) =\left( 1\right) \left( 1\right) $ | 102 |

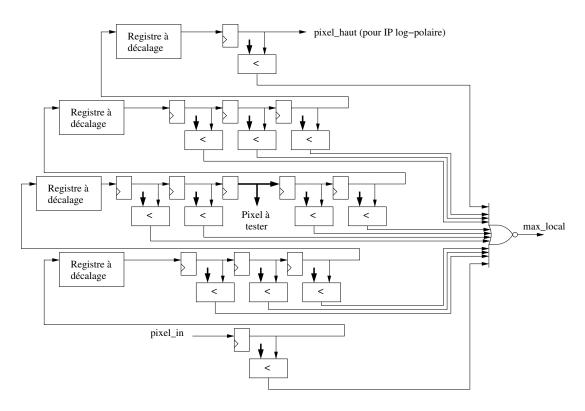

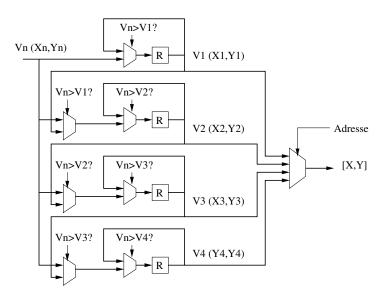

| 4.18 | Tri de points d'intérêt                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 104 |

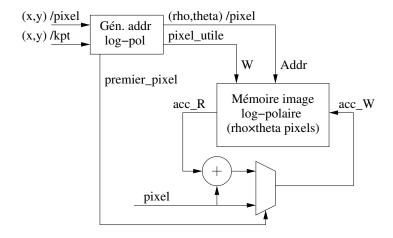

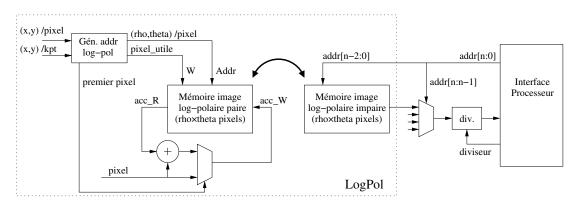

| 4.19 | Génération des caractéristiques log-polaires : schéma global $\ \ldots \ \ldots$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 105 |