## Decoupled (SSA-based) register allocators: from theory to practice, coping with just-in-time compilation and embedded processors constraints

Quentin Colombet

#### ▶ To cite this version:

Quentin Colombet. Decoupled (SSA-based) register allocators: from theory to practice, coping with just-in-time compilation and embedded processors constraints. Other [cs.OH]. Ecole normale supérieure de lyon - ENS LYON, 2012. English. NNT: 2012ENSL0777 . tel-00764405v2

### HAL Id: tel-00764405 https://theses.hal.science/tel-00764405v2

Submitted on 21 Feb 2013

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

#### **THÈSE**

en vue d'obtenir le grade de

Docteur de l'École Normale Supérieure de Lyon – Université de Lyon spécialité : Informatique

Laboratoire de l'Informatique du Parallèlisme École doctorale Informatique et Mathématiques de Lyon

présentée et soutenue publiquement le 07/12/12

par Monsieur Quentin COLOMBET

Decoupled (SSA-based) Register Allocators:

from Theory to Practice, Coping with Just-In-Time Compilation

and Embedded Processors Constraints.

Directeur de thèse : Monsieur Alain DARTE Co-directeur de thèse : Monsieur Fabrice RASTELLO

> Après avis de : Monsieur Vivek SARKAR, Membre/Rapporteur Monsieur Erven ROHOU, Membre/Rapporteur

Devant la Commission d'examen formée de :

Monsieur Erik ALTMAN, Membre Monsieur Albert COHEN, Membre Monsieur Alain DARTE, Membre

$Monsieur\ Vivek\ SARKAR,\ Membre/Rapporteur$

$Monsieur\ Fabrice\ RASTELLO,\ Membre$

Monsieur Erven ROHOU, Membre/Rapporteur

#### Abstract

In compilation, register allocation is the optimization that chooses which variables of the source program, in unlimited number, are mapped to the actual registers, in limited number. Parts of the live-ranges of the variables that cannot be mapped to registers are placed in memory. This eviction is called *spilling*.

Until recently, compilers mainly addressed register allocation via graph coloring using an idea developed by Chaitin et al. [33] in 1981. This approach addresses the spilling and the mapping of the variables to registers in one phase. In 2001, Appel and George [3] proposed to split the register allocation in two separate phases. This idea yields better and independent solutions for both problems, but requires a very aggressive form of live-range splitting, split everywhere, which renames all variables between all instructions of the program. However, in 2005, several groups [27, 84, 56, 16] observed that the static single assignment (SSA) form provides sufficient split points to decouple the register allocation as Appel and George suggested, unless register aliasing or precoloring constraints are involved.

Prior to this thesis, no alternative to this aggressive live-range splitting was available for decoupled register allocation with register aliasing. Other forms of architectural constraints, e.g., encoding and application binary interface (ABI) constraints, can be handled via a form of live-range splitting, more intensive than SSA but less aggressive than split everywhere [55].

This thesis covers all the aspects of decoupled register allocation under SSA with architectural constraints. In a first part, we focused on the spilling problem. Using an exact formulation of the spilling problem, we investigated the impact of SSA during this phase and compared several spilling approaches, exact or not, in our model. This comparison pointed out that SSA complicates the problem and that the state-of-the-art objective function, the static spill cost, used to optimize spill code placement may not be relevant for runtime performances. Following these observations, we evaluated several, existing or not, simplifications of the spilling problem that should help design a good spilling heuristic in terms of runtime performance, though not necessarily static spill cost.

The second part of the manuscript is dedicated to the assignment phase. We showed how to handle regular architectural constraints without intensive live-range splitting. Our approach is compatible with graph-coloring-based approaches, but also with scan-based approaches (traversal of the control-flow graph), as we demonstrated with our fast register allocator, *tree-scan*. Regarding register aliasing, we showed how to limit the effect of split everywhere and still having the decoupling property.

Finally, in a third part, we demonstrated how to improve the final assembly code via local recoloring techniques. These techniques help to deconstruct colored SSA, i.e., register-allocated SSA, and eliminates many copies instructions inserted for live-range splitting purposes.

We wanted all this work to be applicable to just-in-time (JIT) compilation for embedded targets, thus speed and memory footprint were a concern.

**Keywords:** Decoupled register allocation, register aliasing, precoloring, JIT, SSA, spilling.

#### Résumé

En compilation, l'allocation de registres est l'optimisation qui choisit quelles variables du programme source, en nombre illimité, sont stockées dans les registres physiques, en nombre limité. Les variables qui ne peuvent tenir en registre sont placées en mémoire. Cette éviction est appelée *spilling*.

Jusqu'à récemment, les compilateurs traitaient l'allocation de registres globalement via la coloration de graphes en utilisant une idée développée par Chaitin et al. [33] en 1981. En 2001, Appel et George [3] ont proposé de découper l'allocation de registres en deux phases distinctes. Cette idée permet de définir de meilleures solutions pour les deux problèmes, mais nécessite une forme très agressive de renommage des variables, le split everywhere, qui renomme toutes les variables entre toutes les instructions du programme. Cependant, en 2005, plusieurs groupes [27, 84, 56, 16] ont observé qu'en l'absence de contraintes d'aliasing de registres et de précoloriage, le passage en static single assignment (SSA) définit des points de renommage suffisants pour découpler l'allocation de registres tel que suggéré par Appel et George.

Avant cette thèse, pour les approches découplées, seule la technique agressive du *split everywhere* était disponible en présence d'aliasing de registres. Les autres formes de contraintes d'allocation, contraintes d'encodage d'instructions et celles dites d'application binary interface (ABI) peuvent être traitées par du renommage plus intensif qu'avec SSA mais moins qu'avec le *split everywhere* [55].

Cette thèse couvre tous les aspects de l'allocation de registres découplée sous SSA avec des contraintes architecturales. Dans une première partie, nous nous sommes concentrés sur le problème du *spill*. En utilisant une formulation exacte, nous avons mis en évidence le fait que SSA complique le problème et que la fonction objective de l'état de l'art, le coût statique de spill, utilisée pour optimiser le placement du code de spill n'est pas pertinente en ce qui concerne les performances d'exécution. Suivant ces observations, nous avons évalué plusieurs simplifications du problème, proposées antérieurement ou non, qui devraient permettre de concevoir un bonne heuristique en termes de performances d'exécution mais pas nécessairement de coût statique de spill.

La deuxième partie du manuscrit est dédiée à la phase d'assignation aux registres. Nous avons montré comment éviter un renommage intensif pour gérer les contraintes architecturales habituelles. Notre méthode est compatible avec les approches basées sur la coloration de graphe, mais aussi sur les scans (parcours du graphe de flot de contrôle), comme nous l'avons démontré avec notre allocateur de registre rapide, le tree-scan. En présence d'aliasing de registres, nous avons montré comment limiter les effets de split everywhere tout en ayant les bonnes propriétés des approches découplées.

Finalement, dans une troisième partie, nous avons montré comment améliorer le code assembleur final avec des techniques de recoloriage. Celles-ci aident à la déconstruction de SSA et à l'élimination des copies insérées par le renommage.

Enfin, nous voulions que nos travaux soient applicables à la compilation dite just-in-time (JIT) pour processeurs embarqués, ainsi la vitesse et l'empreinte mémoire ont été une préoccupation de tous les instants.

Mots clés: Allocation de registres découplée, JIT, SSA, aliasing de registres, contraintes de registres (precoloring), vidage en mémoire (spilling).

## Contents

| Ac | crony                     | ym                                         | 5  |

|----|---------------------------|--------------------------------------------|----|

| Ι  | Int                       | troduction                                 | 6  |

| 1  | Intr                      | roduction                                  | 7  |

|    | 1.1                       | Register Allocation                        | 7  |

|    | 1.2                       | Motivations                                | 9  |

|    | 1.3                       | Outline and Contributions                  | 10 |

| 2  | Pre                       | requisites and Hypotheses                  | 12 |

|    | 2.1                       | Program Representation                     | 12 |

|    |                           | 2.1.1 Code Operations                      | 12 |

|    |                           | 2.1.2 Control Flow Graph (CFG)             | 14 |

|    | 2.2                       | Static Single Assignment (SSA)             | 15 |

|    |                           | $2.2.1$ $\phi$ -Functions                  | 15 |

|    |                           | 2.2.2 Strictness and Dominance Property    | 16 |

|    |                           | 2.2.3 Conventional SSA                     | 16 |

|    |                           | 2.2.4 Deconstructing SSA                   | 16 |

|    |                           | 2.2.5 Liveness and SSA                     | 17 |

|    | 2.3                       | Register Allocation                        | 18 |

|    |                           | 2.3.1 Hypotheses                           | 18 |

|    |                           | 2.3.2 Global Register Allocation           | 21 |

|    |                           | 2.3.3 Decoupled Register Allocation        | 25 |

| II | $\mathbf{S}_{\mathbf{I}}$ | pill                                       | 31 |

| 3  | Stu                       | dying Optimal Spilling in the Light of SSA | 33 |

| •  | 3.1                       | Formulating "Optimal" Spilling             | 34 |

|    | J                         | 3.1.1 Existing "Exact" Formulations        | 34 |

|    |                           | 3.1.2 Limitations of Existing Approaches   | 35 |

|    | 3.2                       | A More "Optimal" Formulation               | 38 |

|    | J                         | 3.2.1 Basic Formulation                    | 39 |

|    |                           | 3.2.2 Emulating Other Formulations         | 41 |

|    |                           | 3.2.3 Handling SSA and $\phi$ -Functions   | 42 |

|    |                           | 3.2.4 Extended Formulation                 | 45 |

|    | 3 3                       | Experiments                                | 50 |

|         |                                                                      | 3.3.2<br>3.3.3                                                                                                                                           | Solving Time                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | $51 \\ 52 \\ 56$                                                                                                           |

|---------|----------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|

|         | 3.4                                                                  | 3.3.4<br>Conclus                                                                                                                                         | Execution Time Measurements                                                                                                                                                                                                                                                                                                                                                                                                                                                              | $\frac{57}{62}$                                                                                                            |

|         | 9.1                                                                  | Concra                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 02                                                                                                                         |

| 4       |                                                                      |                                                                                                                                                          | Better Spilling Heuristic                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 63                                                                                                                         |

|         | 4.1                                                                  |                                                                                                                                                          | g Spilling Criteria                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 63                                                                                                                         |

|         |                                                                      |                                                                                                                                                          | Static Spill Cost                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 63                                                                                                                         |

|         | 4.0                                                                  |                                                                                                                                                          | Furthest First                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 65                                                                                                                         |

|         | 4.2                                                                  |                                                                                                                                                          | ying Assumptions                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 67                                                                                                                         |

|         |                                                                      |                                                                                                                                                          | The Instruction store                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 67                                                                                                                         |

|         | 4.9                                                                  |                                                                                                                                                          | The Instruction load                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 70                                                                                                                         |

|         | 4.3                                                                  |                                                                                                                                                          | g Heuristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 72<br>72                                                                                                                   |

|         |                                                                      |                                                                                                                                                          | Graph Coloring                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                            |

|         |                                                                      |                                                                                                                                                          | Scan-Based Approaches                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 74                                                                                                                         |

|         | 4.4                                                                  |                                                                                                                                                          | Decoupled Approaches                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 75<br>76                                                                                                                   |

|         | 4.4                                                                  | _                                                                                                                                                        | ing Runtime                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 76                                                                                                                         |

|         |                                                                      |                                                                                                                                                          | Latency                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 76                                                                                                                         |

|         | 4.5                                                                  |                                                                                                                                                          | Helping the Scheduler                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 78<br>79                                                                                                                   |

|         | 4.0                                                                  | Conclus                                                                                                                                                  | sion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 19                                                                                                                         |

|         |                                                                      |                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                            |

|         |                                                                      |                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                            |

| Π       | Ι (                                                                  | Colorin                                                                                                                                                  | ng with Affinities and Antipathies                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 81                                                                                                                         |

|         |                                                                      |                                                                                                                                                          | <u>-</u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                            |

|         | Cole                                                                 | oring w                                                                                                                                                  | ith Encoding Constraints                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 83                                                                                                                         |

|         |                                                                      | oring w<br>Graph                                                                                                                                         | ith Encoding Constraints Coloring with Repairing                                                                                                                                                                                                                                                                                                                                                                                                                                         | <b>83</b><br>85                                                                                                            |

|         | Cole                                                                 | oring w<br>Graph<br>5.1.1                                                                                                                                | ith Encoding Constraints Coloring with Repairing                                                                                                                                                                                                                                                                                                                                                                                                                                         | 83<br>85<br>85                                                                                                             |

| II<br>5 | Cole                                                                 | oring w<br>Graph<br>5.1.1<br>5.1.2                                                                                                                       | ith Encoding Constraints Coloring with Repairing                                                                                                                                                                                                                                                                                                                                                                                                                                         | 83<br>85<br>85<br>86                                                                                                       |

|         | <b>Col</b> 6 5.1                                                     | oring w<br>Graph<br>5.1.1<br>5.1.2<br>5.1.3                                                                                                              | ith Encoding Constraints Coloring with Repairing                                                                                                                                                                                                                                                                                                                                                                                                                                         | 83<br>85<br>85<br>86<br>90                                                                                                 |

|         | Cole                                                                 | Graph 5.1.1 5.1.2 5.1.3 Tree-Sc                                                                                                                          | ith Encoding Constraints Coloring with Repairing                                                                                                                                                                                                                                                                                                                                                                                                                                         | 83<br>85<br>85<br>86<br>90                                                                                                 |

|         | <b>Col</b> 6 5.1                                                     | Graph 5.1.1 5.1.2 5.1.3 Tree-Sc 5.2.1                                                                                                                    | ith Encoding Constraints Coloring with Repairing                                                                                                                                                                                                                                                                                                                                                                                                                                         | 83<br>85<br>85<br>86<br>90<br>91                                                                                           |

|         | Cole 5.1                                                             | Graph 5.1.1 5.1.2 5.1.3 Tree-Sc 5.2.1 5.2.2                                                                                                              | ith Encoding Constraints Coloring with Repairing Model and restrictions Strategies Repairing Code can The Basic Algorithm Repairing                                                                                                                                                                                                                                                                                                                                                      | 83<br>85<br>85<br>86<br>90<br>91<br>91                                                                                     |

|         | 5.1<br>5.2<br>5.3                                                    | Graph 5.1.1 5.1.2 5.1.3 Tree-Sc 5.2.1 5.2.2 Biased                                                                                                       | ith Encoding Constraints  Coloring with Repairing  Model and restrictions  Strategies  Repairing Code  an  The Basic Algorithm  Repairing  Coloring                                                                                                                                                                                                                                                                                                                                      | 83<br>85<br>85<br>86<br>90<br>91<br>91<br>94                                                                               |

|         | 5.1<br>5.2<br>5.3<br>5.4                                             | Graph 5.1.1 5.1.2 5.1.3 Tree-Sc 5.2.1 5.2.2 Biased Related                                                                                               | ith Encoding Constraints  Coloring with Repairing  Model and restrictions  Strategies  Repairing Code  an  The Basic Algorithm  Repairing  Coloring  Work                                                                                                                                                                                                                                                                                                                                | 83<br>85<br>86<br>90<br>91<br>91<br>94<br>99                                                                               |

|         | 5.1<br>5.2<br>5.3                                                    | Graph 5.1.1 5.1.2 5.1.3 Tree-Sc 5.2.1 5.2.2 Biased Related Experir                                                                                       | ith Encoding Constraints  Coloring with Repairing  Model and restrictions  Strategies  Repairing Code  an  The Basic Algorithm  Repairing  Coloring  Work  ments                                                                                                                                                                                                                                                                                                                         | 83<br>85<br>86<br>90<br>91<br>91<br>94<br>99<br>102                                                                        |

|         | 5.1<br>5.2<br>5.3<br>5.4                                             | oring w<br>Graph<br>5.1.1<br>5.1.2<br>5.1.3<br>Tree-Sc<br>5.2.1<br>5.2.2<br>Biased<br>Related<br>Experir<br>5.5.1                                        | ith Encoding Constraints  Coloring with Repairing  Model and restrictions  Strategies  Repairing Code  can  The Basic Algorithm  Repairing  Coloring  Work  ments  Graph Coloring and Repairing                                                                                                                                                                                                                                                                                          | 83<br>85<br>86<br>90<br>91<br>91<br>94<br>99<br>102<br>105                                                                 |

|         | 5.1<br>5.2<br>5.3<br>5.4<br>5.5                                      | Graph 5.1.1 5.1.2 5.1.3 Tree-Sc 5.2.1 5.2.2 Biased Related Experin 5.5.1 5.5.2                                                                           | ith Encoding Constraints  Coloring with Repairing  Model and restrictions  Strategies  Repairing Code  can  The Basic Algorithm  Repairing  Coloring  Work  ments  Graph Coloring and Repairing  Tree-Scan                                                                                                                                                                                                                                                                               | 83<br>85<br>86<br>90<br>91<br>94<br>99<br>102<br>105<br>105                                                                |

|         | 5.1<br>5.2<br>5.3<br>5.4                                             | oring w<br>Graph<br>5.1.1<br>5.1.2<br>5.1.3<br>Tree-Sc<br>5.2.1<br>5.2.2<br>Biased<br>Related<br>Experir<br>5.5.1                                        | ith Encoding Constraints  Coloring with Repairing  Model and restrictions  Strategies  Repairing Code  can  The Basic Algorithm  Repairing  Coloring  Work  ments  Graph Coloring and Repairing  Tree-Scan                                                                                                                                                                                                                                                                               | 83<br>85<br>86<br>90<br>91<br>94<br>99<br>102<br>105<br>105                                                                |

|         | 5.1<br>5.2<br>5.3<br>5.4<br>5.5<br>5.6<br>Dec                        | Graph 5.1.1 5.1.2 5.1.3 Tree-Sc 5.2.1 5.2.2 Biased Related Experin 5.5.1 5.5.2 Conclust oupled                                                           | ith Encoding Constraints Coloring with Repairing Model and restrictions Strategies Repairing Code can The Basic Algorithm Repairing Coloring Work ments Graph Coloring and Repairing Tree-Scan sion Graph-Coloring Register Allocation with Hierarchi-                                                                                                                                                                                                                                   | 83<br>85<br>85<br>86<br>90<br>91<br>91<br>94<br>99<br>102<br>105<br>107<br>114                                             |

| 5       | 5.1<br>5.2<br>5.3<br>5.4<br>5.5<br>5.6<br>Dec                        | Graph 5.1.1 5.1.2 5.1.3 Tree-Sc 5.2.1 5.2.2 Biased Related Experin 5.5.1 5.5.2 Conclust oupled Aliasing                                                  | ith Encoding Constraints  Coloring with Repairing  Model and restrictions  Strategies  Repairing Code  an  The Basic Algorithm  Repairing  Coloring  Work  ments  Graph Coloring and Repairing  Tree-Scan  sion  Graph-Coloring Register Allocation with Hierarchi-                                                                                                                                                                                                                      | 83<br>85<br>86<br>90<br>91<br>91<br>92<br>105<br>105<br>107<br>114                                                         |

| 5       | 5.1<br>5.2<br>5.3<br>5.4<br>5.5<br>Dec<br>cal<br>6.1                 | Graph 5.1.1 5.1.2 5.1.3 Tree-Sc 5.2.1 5.2.2 Biased Related Experir 5.5.1 5.5.2 Conclust oupled Aliasing Backgro                                          | ith Encoding Constraints  Coloring with Repairing  Model and restrictions  Strategies  Repairing Code  an  The Basic Algorithm  Repairing  Coloring  Work  ments  Graph Coloring and Repairing  Tree-Scan  sion  Graph-Coloring Register Allocation with Hierarchige ound                                                                                                                                                                                                                | 83<br>85<br>85<br>86<br>90<br>91<br>94<br>99<br>102<br>105<br>107<br>114                                                   |

| 5       | 5.1<br>5.2<br>5.3<br>5.4<br>5.5<br>5.6<br>Dec                        | Graph 5.1.1 5.1.2 5.1.3 Tree-Sc 5.2.1 5.2.2 Biased Related Experir 5.5.1 5.5.2 Conclust oupled Aliasing Backgro Spilling                                 | ith Encoding Constraints  Coloring with Repairing  Model and restrictions  Strategies  Repairing Code  an  The Basic Algorithm  Repairing  Coloring  Work  ments  Graph Coloring and Repairing  Tree-Scan  sion  Graph-Coloring Register Allocation with Hierarchig  ound  g Test in Face of Aliasing                                                                                                                                                                                    | 83<br>85<br>85<br>86<br>90<br>91<br>94<br>99<br>102<br>105<br>107<br>114<br><b>115</b><br>116<br>120                       |

| 5       | 5.1<br>5.2<br>5.3<br>5.4<br>5.5<br>Dec<br>cal<br>6.1                 | Graph 5.1.1 5.1.2 5.1.3 Tree-Sc 5.2.1 5.2.2 Biased Related Experin 5.5.1 5.5.2 Conclust oupled Aliasing Backgro Spilling 6.2.1                           | ith Encoding Constraints  Coloring with Repairing  Model and restrictions  Strategies  Repairing Code  an  The Basic Algorithm  Repairing  Coloring  Work  ments  Graph Coloring and Repairing  Tree-Scan  sion  Graph-Coloring Register Allocation with Hierarchige  ound  g Test in Face of Aliasing  Checking Colorability via Smith's Simplification Test                                                                                                                            | 83<br>85<br>85<br>86<br>90<br>91<br>91<br>02<br>105<br>105<br>107<br>114<br><b>115</b><br>116<br>120<br>120                |

| 5       | 5.1<br>5.2<br>5.3<br>5.4<br>5.5<br>Dec<br>cal<br>6.1                 | oring w Graph 5.1.1 5.1.2 5.1.3 Tree-Sc 5.2.1 5.2.2 Biased Related Experin 5.5.1 5.5.2 Conclust oupled Aliasing Backgro Spilling 6.2.1 6.2.2             | ith Encoding Constraints  Coloring with Repairing  Model and restrictions  Strategies  Repairing Code  an  The Basic Algorithm  Repairing  Coloring  Work  ments  Graph Coloring and Repairing  Tree-Scan  sion  Graph-Coloring Register Allocation with Hierarchigound  g Test in Face of Aliasing  Checking Colorability via Smith's Simplification Test  Correct Spilling Test Handling Aliasing and Precoloring                                                                      | 83<br>85<br>86<br>90<br>91<br>94<br>99<br>102<br>105<br>107<br>114<br>116<br>120<br>120                                    |

| 5       | 5.1<br>5.2<br>5.3<br>5.4<br>5.5<br>5.6<br>Dec<br>cal .<br>6.1<br>6.2 | oring w Graph 5.1.1 5.1.2 5.1.3 Tree-Sc 5.2.1 5.2.2 Biased Related Experir 5.5.1 5.5.2 Conclust oupled Aliasing Backgro Spilling 6.2.1 6.2.2 6.2.3       | ith Encoding Constraints  Coloring with Repairing  Model and restrictions  Strategies  Repairing Code  an  The Basic Algorithm  Repairing  Coloring  Work  ments  Graph Coloring and Repairing  Tree-Scan  sion  Graph-Coloring Register Allocation with Hierarchi- g ound  Test in Face of Aliasing  Checking Colorability via Smith's Simplification Test  Correct Spilling Test Handling Aliasing and Precoloring  Improving Smith's Test with Live-Range Merging                     | 83<br>85<br>86<br>90<br>91<br>91<br>94<br>99<br>102<br>105<br>107<br>114<br><b>115</b><br>116<br>120<br>121<br>122         |

| 5       | 5.1<br>5.2<br>5.3<br>5.4<br>5.5<br>Dec<br>cal<br>6.1                 | Graph 5.1.1 5.1.2 5.1.3 Tree-Sc 5.2.1 5.2.2 Biased Related Experin 5.5.1 5.5.2 Conclust oupled Aliasing Backgre Spilling 6.2.1 6.2.2 6.2.3 Semi-E        | ith Encoding Constraints  Coloring with Repairing  Model and restrictions  Strategies  Repairing Code  an  The Basic Algorithm  Repairing  Coloring  I Work  ments  Graph Coloring and Repairing  Tree-Scan  sion  Graph-Coloring Register Allocation with Hierarchi- g ound  G Test in Face of Aliasing  Checking Colorability via Smith's Simplification Test  Correct Spilling Test Handling Aliasing and Precoloring  Improving Smith's Test with Live-Range Merging  lementary Form | 83<br>85<br>86<br>90<br>91<br>91<br>94<br>99<br>102<br>105<br>107<br>114<br><b>115</b><br>116<br>120<br>121<br>122<br>124  |

| 5       | 5.1<br>5.2<br>5.3<br>5.4<br>5.5<br>5.6<br>Dec<br>cal .<br>6.1<br>6.2 | Graph 5.1.1 5.1.2 5.1.3 Tree-Sc 5.2.1 5.2.2 Biased Related Experin 5.5.1 5.5.2 Conclust  oupled Aliasing Backgro Spilling 6.2.1 6.2.2 6.2.3 Semi-E 6.3.1 | ith Encoding Constraints  Coloring with Repairing  Model and restrictions  Strategies  Repairing Code  an  The Basic Algorithm  Repairing  Coloring  Work  ments  Graph Coloring and Repairing  Tree-Scan  sion  Graph-Coloring Register Allocation with Hierarchig  ound  Test in Face of Aliasing  Checking Colorability via Smith's Simplification Test  Correct Spilling Test Handling Aliasing and Precoloring  Improving Smith's Test with Live-Range Merging  lementary Form      | 83<br>85<br>86<br>90<br>91<br>94<br>99<br>102<br>105<br>107<br>114<br><b>115</b><br>116<br>120<br>121<br>122<br>124<br>124 |

|              | 6.4<br>6.5   | Experiments                                                       |     |

|--------------|--------------|-------------------------------------------------------------------|-----|

| ΙV           | 7 <b>I</b>   | Post Phases                                                       | 134 |

| 7            | Par          | allel Copy Motion                                                 | 136 |

|              | 7.1          | Parallel Copy Motion                                              | 137 |

|              |              | 7.1.1 Parallel Copies                                             | 137 |

|              |              | 7.1.2 Moving a Parallel Copy Out of an Edge                       | 139 |

|              |              | 7.1.3 Parallel Copy Motion Inside Basic Blocks                    |     |

|              | 7.2          | Permutation Motion and Region Recoloring                          | 141 |

|              |              | 7.2.1 Reversible Parallel Copies & Permutations                   |     |

|              |              | 7.2.2 Region Recoloring                                           |     |

|              | 7.3          | Applications                                                      |     |

|              |              | 7.3.1 Removing Parallel Copies from Critical Edges                |     |

|              |              | 7.3.2 Shrinking Parallel Copies in a Basic Block                  |     |

|              | 7.4          | Experiments                                                       |     |

|              |              | 7.4.1 The Impact of Copy Motion Out of Edges                      |     |

|              |              | 7.4.2 The Impact of Copy Motion in Basic Blocks                   |     |

|              |              | 7.4.3 All Together                                                |     |

|              | 7.5          | Conclusion                                                        | 156 |

| 8            | DI:          | nination of Parallel Copies Using Copy Motion on Data I           | Do  |

| 0            |              | dence Graphs                                                      | 158 |

|              | 8.1          | Data Dependence Graphs                                            |     |

|              | 0.1          | 8.1.1 Parallel Copies                                             |     |

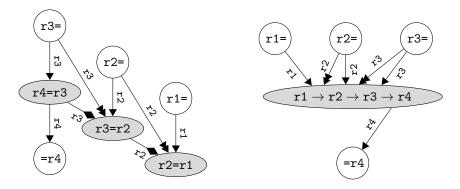

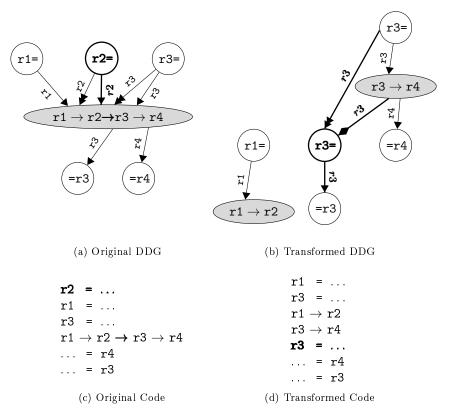

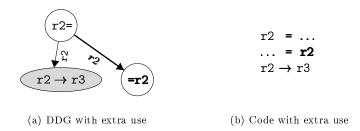

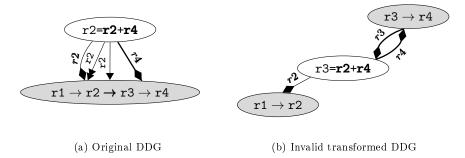

|              |              | 8.1.2 Parallel Copy Motion                                        |     |

|              | 8.2          | Copy Elimination on Data Dependence Graphs                        |     |

|              | 0.2          | 8.2.1 Downward Motion of Definitions                              |     |

|              |              | 8.2.2 Upward Motion of Uses                                       |     |

|              |              | 8.2.3 Code Motion Past Cyclic Parallel Copies                     |     |

|              |              | 8.2.4 Algorithm Complexity                                        |     |

|              |              | 8.2.5 Additional Remarks                                          |     |

|              | 8.3          | Experiments                                                       |     |

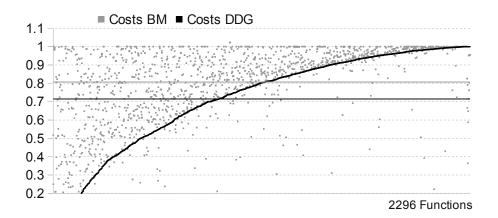

|              | 0.0          | 8.3.1 Copy Elimination after Full Coalescing                      |     |

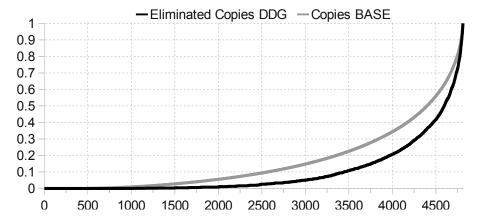

|              |              | 8.3.2 Copy Elimination after <i>Decoupled</i> Register Allocation |     |

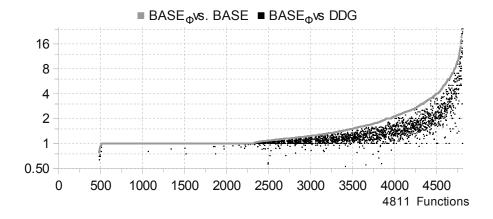

|              |              | 8.3.3 Coalescing versus DDG-Based Copy Elimination                |     |

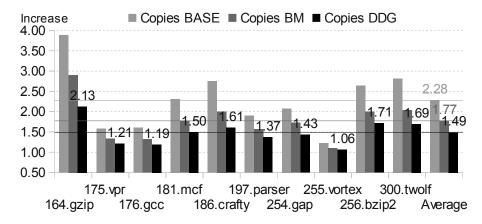

|              |              | 8.3.4 Runtime Behavior                                            |     |

|              | 8.4          | Related Work                                                      |     |

|              | 8.5          | Conclusion                                                        | 192 |

|              |              |                                                                   |     |

| $\mathbf{V}$ | $\mathbf{C}$ | onclusion                                                         | 194 |

| 9            | Cor          | nclusion                                                          | 195 |

| J            | 9.1          | Contributions                                                     |     |

|              | g.1          | 9.1.1 Spilling                                                    |     |

|              |              | 9.1.2 Coloring                                                    |     |

|              |              | 9.1.3 Post Phases                                                 |     |

|              |              | - STATE - AND TITOSON I I I I I I I I I I I I I I I I I I I       |     |

| $9.2.1 \\ 9.2.2$          | ctives       198         Spilling       198         Coloring       198         Post Phases       199 |

|---------------------------|------------------------------------------------------------------------------------------------------|

| List of Public            | ations 200                                                                                           |

| Bibliography              | 201                                                                                                  |

| A Appendix<br>A.1 Colorii | ng with Encoding Constraints                                                                         |

## Acronym

ABI application binary interface

**BF** brute force coalescer

CFG control flow graph

CISC complex instruction set computing

CSSA conventional static single assignment

$\mathbf{DDG}$  data dependence graph

**DFS** depth-first search

IG interference graph

ILP integer linear programming

${f IR}$  intermediate representation

IRC iterated register coalescer

ISA instruction set architecture

JIT just-in-time

**KERNELS** benchmarks from STMicroelectronics

LAO linear assembly optimizer

OPEN64 open source version of the SGI Pro64 compiler [49]

${\bf RISC}\,$  reduced instruction set computing

**RPO** reverse post-order

SSA static single assignment

SSI static single information

${f VLIW}$  very-long instruction word

# Part I Introduction

## Chapter 1

## Introduction

In computer science, compilation is the process that translates a source program into a destination program, that is equivalent in terms of behavior. Both programs may share their programming languages. Such process is called "source-to-source compilation". But it is not the common usage of compilers, the programs that perform the compilation. Indeed, compilers are generally used to translate machine-independent, usually human-written, programs into machine-depend programs. In their last phases, compilers have to deal with the actual constraints of the target machine, which, by definition, were not present in the original programs. This thesis focuses on this low-level aspect of compilation called "back-end compilation" and in particular on register allocation, which deals, among these architectural constraints, with the limited amount of fast storage space, i.e., the registers.

#### 1.1 Register Allocation

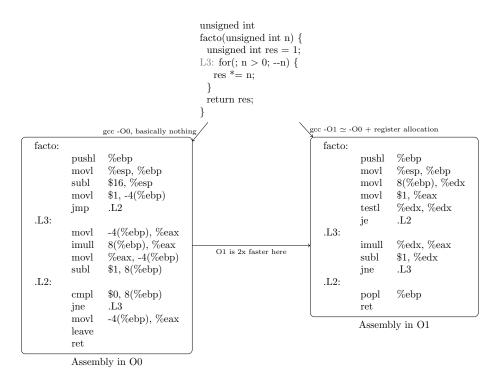

Register allocation consists in mapping the unbounded set of variables used in a low-level program representation to the limited number of registers available in the target architecture. When not all variables can be mapped to registers, some are stored in memory to reduce register demand. This eviction to memory is called *spilling*. Memory transfers are costly in execution time, power dissipation, and code size, thus a good register allocator should reduce spilling in order to preserve the gains of previous optimizations. Indeed, other optimizations have their own profitability model that may not match register allocation concerns. Moreover, according to Hennessy and Patterson [59], register allocation adds the largest single performance improvement to compiled programs. For instance, Figure 1.1 gives the assembly code produced for x86 for a function computing factorial. In this example, the assembly code generated with register allocation enabled is twice as fast as the assembly without. Indeed, without register allocation, the program accesses variables n and res via the stack, i.e., they are allocated in memory, whereas with register allocation, it directly uses registers. Thus, register allocation has been extensively studied in the past.

As a reminder, it is always beneficial to improve the performance of the program in the embedded world even when the reactivity of the system is not a concern. Indeed, if a program requires less computations, the frequency of

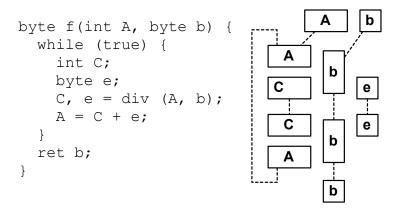

Figure 1.1: When enabling register allocation on gcc 4.4.3 for the x86 target, the generated assembly code is 2x faster for this example. In the x86 assembly code, the definition is the second operand of the instruction. For instructions with two arguments, like imull, the second operand is both read and written. The L3 label denotes the body of the original loop. Without register allocation, assembly in O0, n is accessed via memory location 8(%ebp) and res is accessed via memory location -4(%ebp). With register allocation, assembly in O1, accesses to the stack are eliminated as n is in register %edx and res is in register %edx.

the processor can be decreased without slowing down the application. On the other hand, if the frequency is not changed, the processor ends the computations earlier and can enter in idle mode sooner. In both cases, for the same amount of work, this spares the battery of the system.

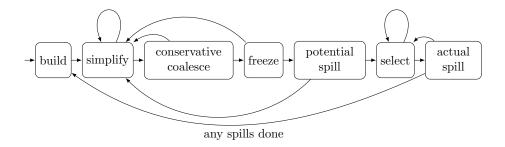

Until recently, compilers performed register allocation using variants of graph coloring, as developed by Chaitin et al. [33]. This method gives fairly-good results in practice. However, nowadays, compilers are used in many different contexts. In particular, they have to cope with memory and/or time constraints, as implied by just-in-time (JIT) compilation, that are not compatible with graph-coloring-based approaches. Indeed, these approaches are known to be memory consuming and quite slow.

In the past few years, some researchers proposed to decompose register allocation in two phases [3, 56]. The first phase decides where to place spilling instructions (load and store) so that a second phase that assigns registers to variables will not generate additional spill code. For that to be possible, register-to-register copies (move instructions) may need to be inserted. The underlying assumption that makes such a decoupling efficient is that move instructions are more likely to be cheaper than memory transfers. Decoupled register allocation

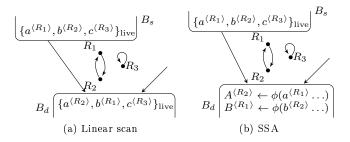

is often associated with static single assignment (SSA) form [37] as, in strict SSA, the way live-ranges are split, explicitly, makes the second phase always feasible. This is when all variables can be mapped to any register. The case of precoloring and register aliasing is more complex as we will see.

Many recent register allocation algorithms follow such a decoupled approach, see for example [3, 57, 58, 84, 85, 93, 95, 104]. This model has important advantages. First, the separation between these two phases yields simpler and more modular implementations: different spilling heuristics can easily be combined with different register assignments. As an example, about 20% of the lines of code of the machine-independent code generator of LLVM [68] are exclusively related to register allocation. Thus, from an engineering point of view, it is interesting to design register allocators that are modular. Second, the local register pressure, a property that is easy to infer in decoupled designs, simplifies other compiler optimizations, such as redundancy elimination, and code analysis.

#### 1.2 Motivations

Decoupled register allocation is an elegant approach to a complex problem. Its inherent qualities make it appealing for modern compilers. The feasibility of this approach has been well studied in the past few years, in particular by Hack [55], Pereira [83], and Bouchez [15]. In this thesis, we wanted to go beyond the feasibility aspects by proposing efficient solutions that may be applied to JIT compilation. Moreover, we wanted to address some pending questions. In particular, we focused on the following points.

A first aspect concerns the spilling phase. As already stated, SSA form is usually used in these allocators to ensure that, once the register pressure is low enough, graph coloring can be used for register assignment without additional spilling. However, how to perform the spilling phase itself, i.e., how to place load and store instructions, was not completely understood. In particular, the question we had was: does SSA help for spilling? We wanted to evaluate the impact, positive or negative, of SSA on the spilling model and the quality of the generated solution to derive good spilling heuristics.

A second aspect concerns the register assignment phase. As compilers are more and more embedded in the user environment, we wanted to supply fast and lightweight algorithms for register allocation. One of the questions we had was: is it possible to use the elegant formalism of decoupled approach to derive fast algorithms? This was clear in a simplified model, but less clear in the context of actual machines. Indeed, as Hack [55] showed, specific constraints of the instruction set architecture (ISA) can make the decoupling between the two phases more complicated. In some extreme cases, even extensive live-range splitting is not enough to handle complex ISA constraints. Moreover, it may even not be possible or desirable to apply this kind of splitting, depending on the compiler/architecture. In other words, a more precise question was: is it possible to cope with these constraints and still use the elegant formalism of decoupled approach to derive fast algorithms?

Another assumption concerns move instructions and spill instructions. As already stated, decoupled register allocation assumes that move instructions can be inserted to spare spill instructions. The direct question that we wanted to address was: is it really true that move instructions are less expensive than spill

instructions? Because of this assumption, it is likely that the number of move instructions generated increases compared to a non-decoupled approach. This led us to ask: is it possible to reduce this number of move a posteriori?

#### 1.3 Outline and Contributions

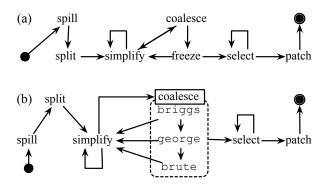

This thesis is organized in six contributions dispatched in three different parts. These parts follow the regular compilation flow of a decoupled register allocator: Part II deals with the spilling phase, Part III with the coloring phase, and Part IV with post phases. Before, Chapter 2 of Part I completes this introduction by defining all introduced notions, such as graph coloring, live-range, register pressure, and so on. To clarify the assumptions that we make, it also presents in details the assumptions made by existing decoupled register allocators and it discusses the problems induced by architectural constraints. The rest of the manuscript is organized as follows.

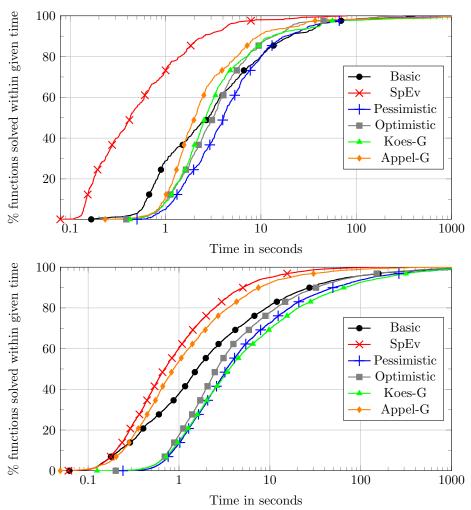

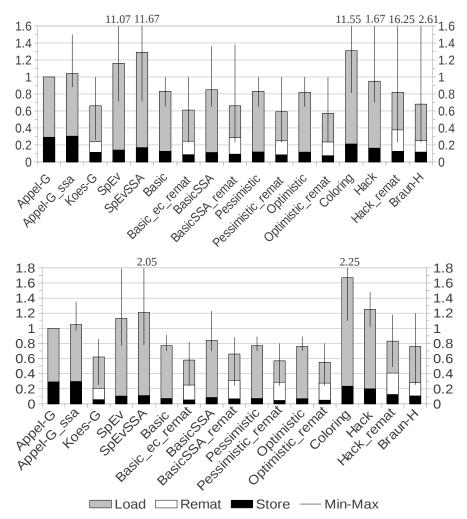

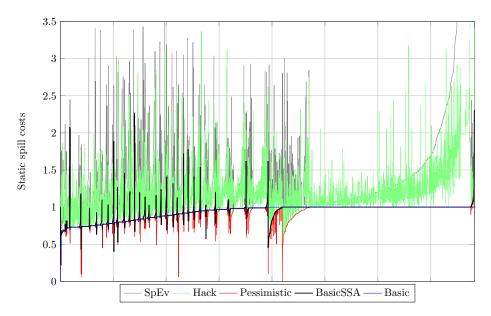

The first chapter of Part II, Chapter 3, evaluates the impact of SSA on the modeling of the spilling problem. Using a newly-defined integer linear programming (ILP) formulation, we show that SSA form complicates the problem and that a naive handling of its specificities may end up in very bad cases. We then introduce two different handling of this form and demonstrate that they are sufficient to catch up the gap with non-SSA spillers. Moreover, we show that, thanks to these models, spillers based on SSA can achieve even better performances for an equivalent complexity of the implied analysis.

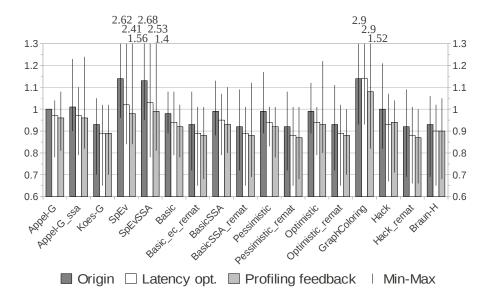

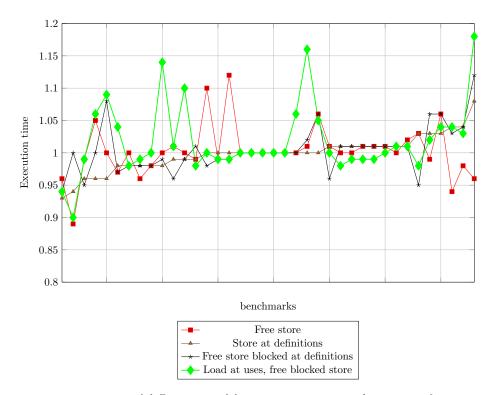

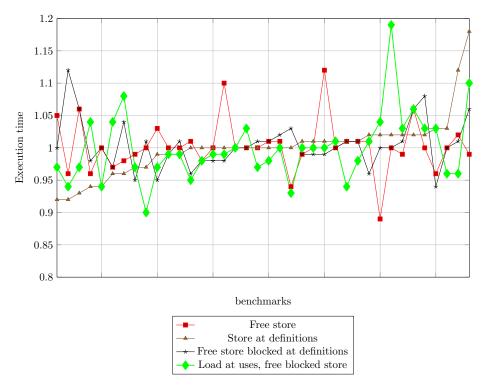

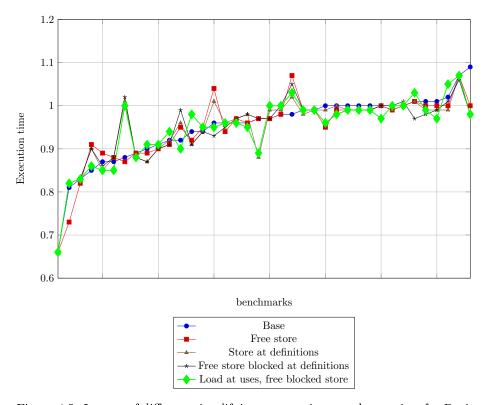

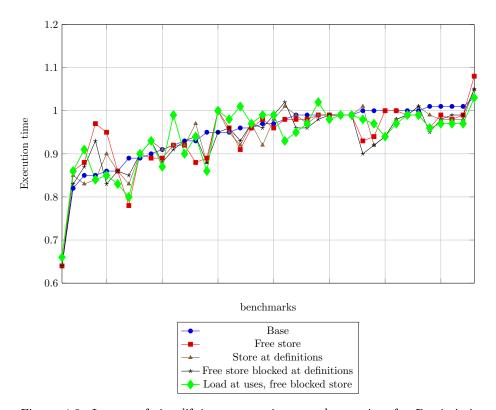

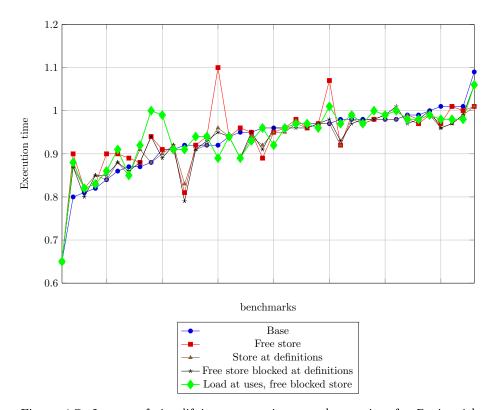

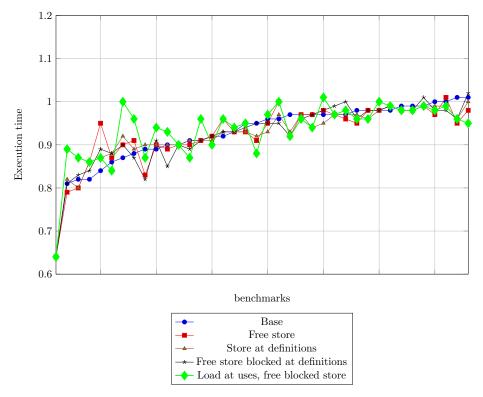

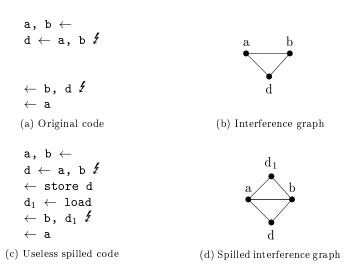

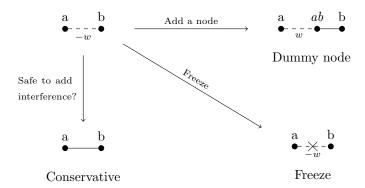

Chapter 4 comes back on the spilling problem but from an heuristic point of view. We review existing spilling criteria and heuristics and point out their advantages and weaknesses. Moreover, we evaluate empirically different simplifying assumptions that may help to derive simpler and faster heuristics, in particular in the JIT context. Finally, we propose a new cost model to help improving the runtime of the generated code. This chapter is the less elaborated one as it was done at the end of the thesis.

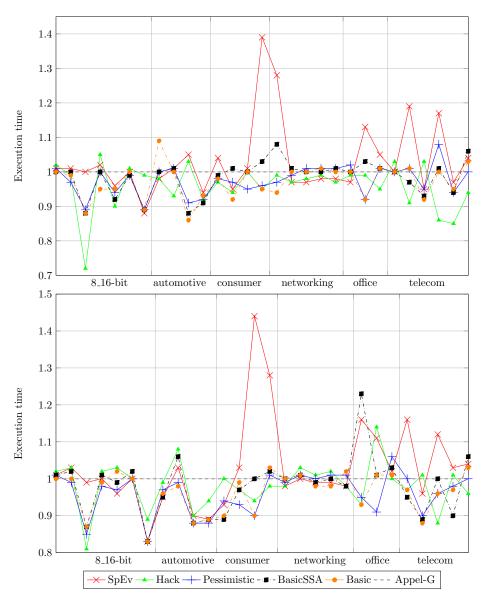

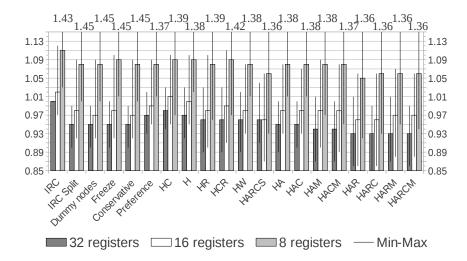

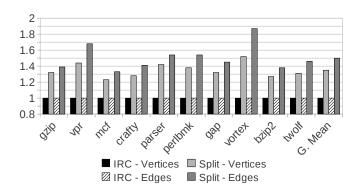

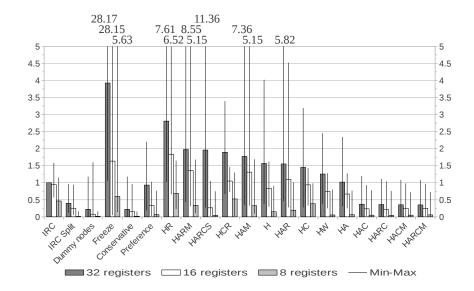

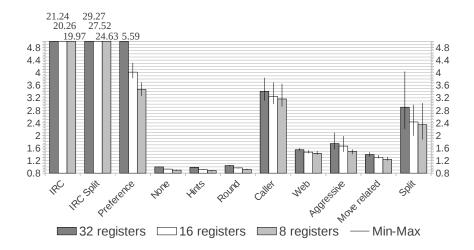

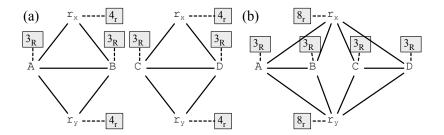

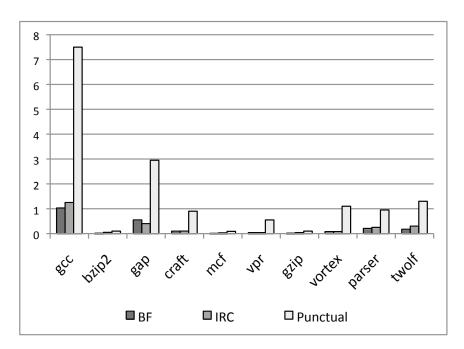

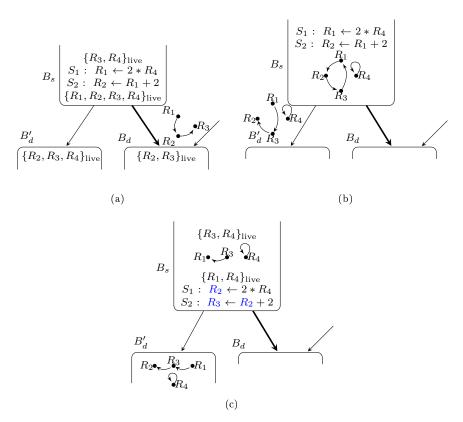

We then enter Part III, which deals with coloring. In a first chapter, Chapter 5, we give a formal model to deal with ISA and application binary interface (ABI) constraints in both graph-coloring-based and scan-based approaches without extensive live-range splitting. We introduce the concept of antipathies in graph-coloring-based approaches, a way to guide variables to be assigned to different registers, and describe different strategies to deal with them. These strategies require different implementation efforts, from very light to light, in existing approaches depending on the expected quality of the generated code. We define a new scan approach that takes advantages of the properties of SSA form, the tree-scan. We describe several methods to bias the coloring during any scan approach, including tree-scan, to limit the insertion of move instructions. We evaluate all our strategies in the state-of-the-art graph-coloring allocator, the iterated register coalescer (IRC) [51], and compare them to our tree-scan approach with different configurations of the bias methods. The evaluation focuses on the runtime, the compile time, the memory footprint, and the code quality with respect to move instructions. This evaluation includes also the latest scan-based approach, the preference-guided allocator [22]. Tree-scan proves to be a very aggressive register allocator, whose compile time and lightweight memory footprint make it appealing for JIT compilation.

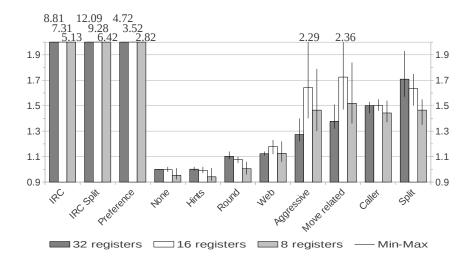

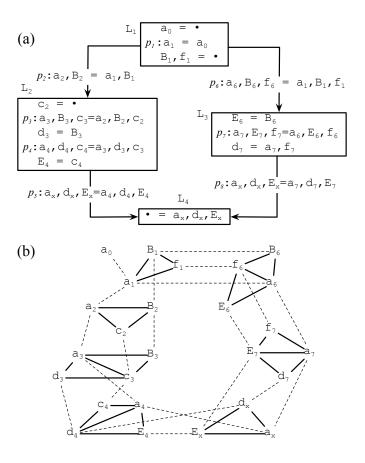

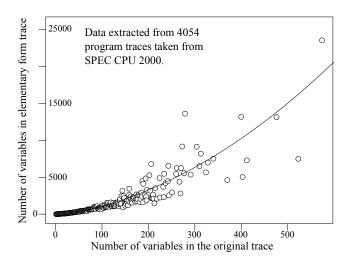

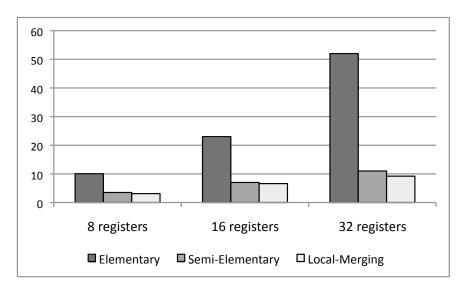

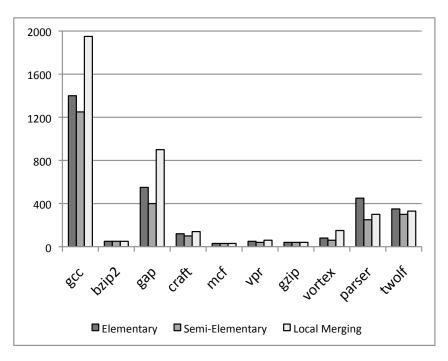

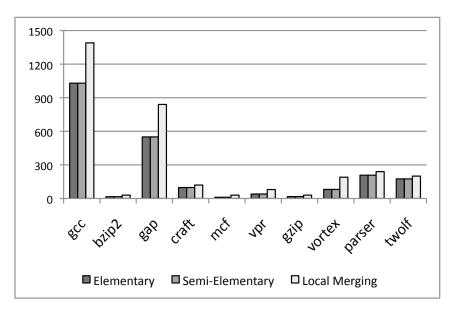

In Chapter 6, we then focus on register aliasing constraints. We show how the spilling test can be modified to take into account the particularities of such constraints. We then propose a new form of live-range splitting that we called the semi-elementary form. This form allows to decouple the spilling phase from the assignment phase, i.e., without any additional spill code, without requiring the extensive live-range splitting used so far. We demonstrate the benefits of this splitting in the context of graph-coloring-based approaches, in particular in terms of compile time and memory footprint, thus improving its applicability to JIT compilation.

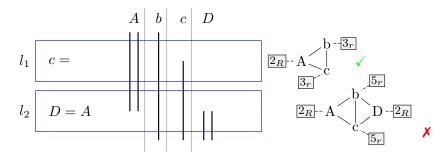

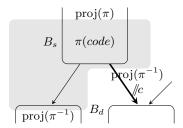

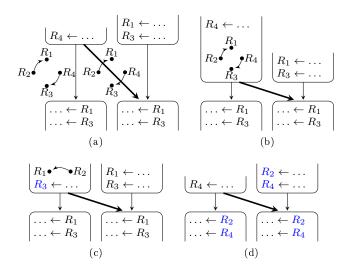

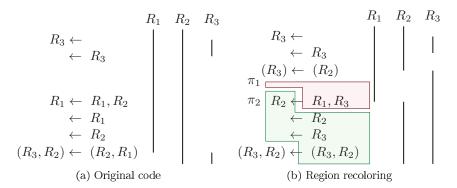

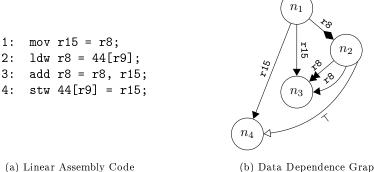

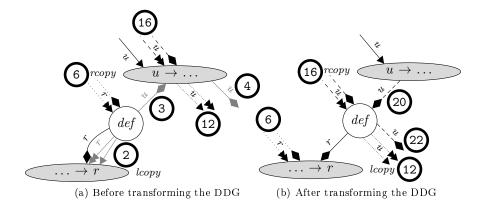

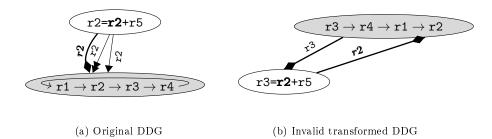

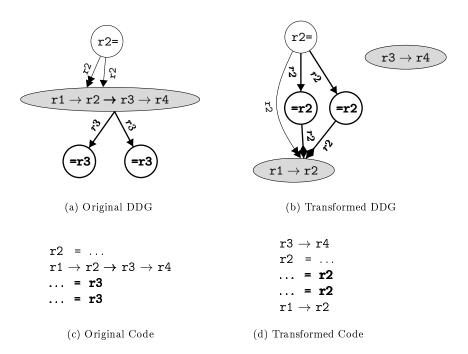

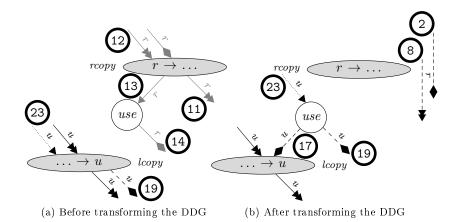

We then continue with Part IV, concerning post phases, i.e., optimization phases after register allocation. In Chapter 7, we extend the theoretical framework of Bouchez [15] proposed to avoid the extensive edge splitting induced, in particular, by decoupled approaches when going out SSA form. Our method, based on the formalism of parallel copy motion, turns out to be able to improve the quality of the generated code although it was not its initial goal. It defines a nice way to move move instructions, thanks to region recoloring. Then, Chapter 8 allows even more general region recoloring as it provides a framework to perform parallel copy motion directly on data dependence graphs (DDGs). Both methods can be stopped at any time and still producing correct code, making them appealing for JIT compilation as they can improve the code until a certain time budget is consumed.

Chapter 9 concludes this manuscript.

Note: For the experiments, STMicroelectronics provided the compiler, the associated tools, e.g., profiler, linker, and the target processor, an embedded very-long instruction word (VLIW) media processor, the ST231.

## Chapter 2

## Prerequisites and Hypotheses

This chapter presents and details the important notions that we use in this manuscript. We first start with the program representation, defining step by step the elements that form a program and how they work together. We then introduce the static single assignment form, quickly discussing its concepts and properties as they will be essential to understand the decoupled register allocation. The next section presents the liveness, an important notion in register allocation. Then, we present the different approaches to register allocation, both global and decoupled, and in particular their hypotheses.

#### 2.1 Program Representation

This section gathers the definitions of the notions related to a program, which is the input to the analysis and algorithms that we develop in this manuscript. In general, depending on the compiler, the input may be a source file, a complete application, a trace, etc. Whatever the input form is, the compiler front end translates it into an intermediate representation (IR). The choice of the IR depends on the goals of the compiler; a given IR facilitates some operations but may complicate others. In our case, we deal with a low-level description of a function or procedure represented by a control flow graph (CFG), which abstracts basic blocks and instructions, as defined hereafter.

#### 2.1.1 Code Operations

**Basic Block** A basic block is a sequence (in general maximal) of instructions with only one entry point and one exit point. Each block is assigned a *frequency* that represents how many times it is executed exactly or as an approximation. This information can be obtained by profiling or heuristics [5].

**Instruction** An instruction, also called *operation*, takes a list of *arguments* to perform a computation, according to its *label* (e.g., move, add, jump, function call), and stores the *results* in a list of *definitions*. The number and the type of the arguments/definitions depend on the computation. We will use the terms *temporaries* or *variables* to denote arguments and definitions that may be assigned to a register, i.e., that are *allocatable*. For instance, the label argument

of a goto instruction is not allocatable. From this point, unless it is specified, the definitions and arguments terms refer to the definitions and arguments that are allocatable. In this thesis, the arithmetic semantics of instructions is not relevant. However, will be of particular interest the following instructions:

- move: copy a variable to another one.

- store: copy a variable to a memory location.

- load: copy a memory location to a variable.

- jump: create a control flow to another basic block.

- call: jump to another function and return.

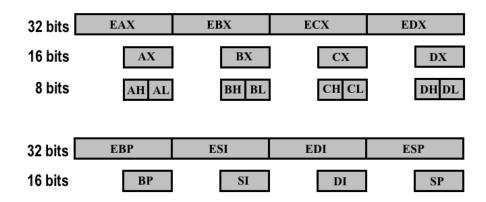

Allocation Constraints In this thesis, we focus on reduced instruction set computing (RISC) architectures. In such a configuration, all the instructions, but special ones, use at most two arguments and define at most one result. This representation is called 3-address code. Moreover, all definitions and arguments must be in register when they are defined or used. On the other hand, complex instruction set computing (CISC) architectures offer the capability to use or define a variable directly from/to a memory slot but they have constraints on the usage of the instruction set that depend on the target processor. On x86, for instance, the number of operands that can reside in memory for a given instruction is limited to one. Moreover, on such architectures, every instruction has only two operands: one read-only and one read-write. Such a representation is called 2-address code.

For some instructions, a special processing is needed to cope with constraints coming from the hardware. There are mainly two kinds of such instructions. The first kind is instructions that use their operands implicitly. The location of these operands is defined by the application binary interface (ABI). For instance, the ABI of the ST200 family specifies that the first argument of call instructions is in register 16, the second in register 17, and so on. The second kind is pseudo (or virtual) instructions, i.e., instructions that do not exist on the architecture. These instructions are translated by the compiler into a sequence of actual architecture instructions. For example, STxP70 has no division instructions. In general, these translations are performed before register allocation. However, some of them will be introduced during or just before register allocation and will need to be translated after. This is the case of the parallel copy (see below) and of the  $\phi$ -function (see Section 2.2.1).

**Parallel Copy** Parallel copies are virtual instructions that perform multiple move instructions at the same time. The moves represent the propagation of values performed by the parallel copy. The parallel semantics is fundamental, since performing moves in a sequential way with no care may cause a value to be erased before being copied to its proper destination, variable or register.

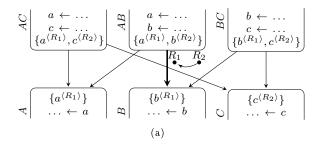

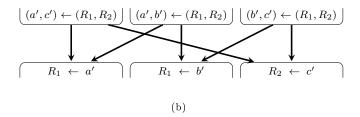

More formally, a parallel copy, denoted  $(d_1,\ldots,d_n) \leftarrow (a_1,\ldots,a_n)$ , assuming that all  $d_i$  are different, performs in parallel the n copies  $d_i \leftarrow a_i$ , which performs a move of variable  $a_i$  into variable  $d_i$ . A parallel copy can be represented as a directed graph, whose vertices are the variables involved in the parallel copy and there is an edge from  $a_i$  to  $d_i$  for each i. A particularity of this graph is that the in-degree of all vertices is at most 1 (such a graph is called windmill [92]). A parallel copy contains a duplication if it exists  $i \neq j$  such that  $a_i = a_j$ , i.e., if its graph representation has a node with an out-degree at least 2.

A parallel copy contains a *cycle* if so does its graph representation. A parallel copy is *regular* if its graph representation is a chain. A parallel copy is *cyclic* if its graph representation is a single cycle. A parallel copy is *reversible* if its graph representation is a disjoint union of chains and simple cycles, i.e., if it is the union of regular parallel copies and cyclic parallel copies (Spartan parallel copy [86]), in other words, if it has no duplication. It can be completed into a permutation.

Such instructions have to be eliminated prior to the end of the compilation process, since they do not exist on actual architectures. The elimination process consists in mapping the parallel copies into a sequence of move or swap instructions [13, 86]. If swap instructions are not available, this process needs an additional variable in case the parallel copy is a union of (disjoint) cycles.

Parallel copies are a key structure for decoupled register allocation as we will show in Section 2.3.

#### 2.1.2 Control Flow Graph (CFG)

The control flow graph is the object that abstracts the structure of the program, i.e., the basic blocks and the way the control flows between them.

General Structure A control flow graph G = (V, E) is a directed graph where nodes or vertices (V) represent basic blocks and where edges (E) represent the possible control flow between basic blocks. The source of an edge is called the *source block*, its destination the *destination block*. The edges that flow in (resp. out) a basic block are its incoming (resp. outcoming) edges. For a given basic block, the source blocks of its incoming edges are its *predecessors*, and the destination blocks of its outcoming edges are its *successors*.

A node represents an *entry block* if it has no predecessor and an *exit block* if it has no successor. These represent the possible starting points (resp. ending points) of the execution of the program (typically a function). From now on, we assume that there is only one entry block and only one exit block. If not, we create a virtual entry (resp. exit) block, predecessor of all entry blocks (resp. successor of all exit blocks).

Edges have a probability, which can also be profiled or heuristically estimated. This information can be combined with the frequency of the source block, to obtain the frequency of the edge. An edge is *critical* if its source block has several successors and its destination block has several predecessors. Algorithms for removing critical edges are standard [4], when it is possible.

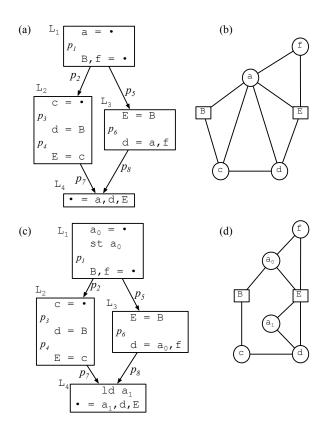

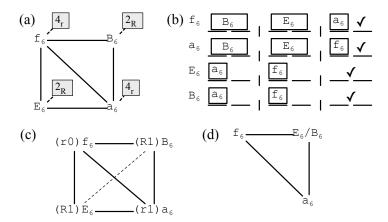

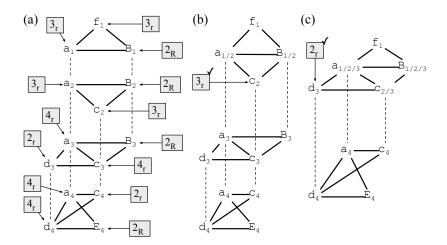

Figure 6.1(a) (Page 117) shows the CFG representation of a program.

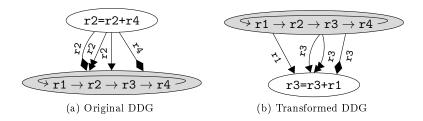

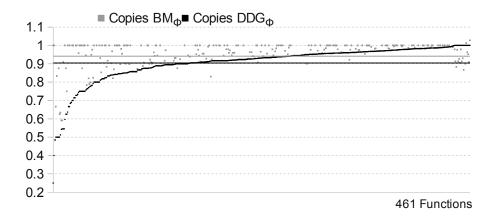

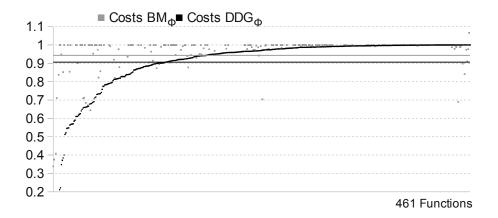

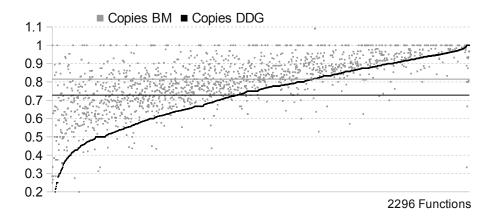

**Loops and Back-Edges** A cycle in the CFG corresponds to a "loop" (a cyclic behavior) in the program. Such loops are worth to mention because they usually represent the hot spots of the applications, i.e., the most executed parts. The way loops are structured, in particular how they are nested, has to do with the theory of *natural loops*, *reducible graphs*, and *loop nesting forests* [90]. We do not intend to develop this theory here, just to recall intuitive notions.