# Multifrontal Methods: Parallelism, Memory Usage and Numerical Aspects

Jean-Yves L'Excellent

# ▶ To cite this version:

Jean-Yves L'Excellent. Multifrontal Methods: Parallelism, Memory Usage and Numerical Aspects. Modeling and Simulation. Ecole normale supérieure de lyon - ENS LYON, 2012. tel-00737751v1

# HAL Id: tel-00737751 https://theses.hal.science/tel-00737751v1

Submitted on 2 Oct 2012 (v1), last revised 21 Dec 2012 (v2)

HAL is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# ÉCOLE NORMALE SUPÉRIEURE DE LYON, FRANCE

# Multifrontal Methods: Parallelism, Memory Usage and Numerical Aspects

# Jean-Yves L'Excellent

Chargé de Recherche, Inria

# MÉMOIRE D'HABILITATION À DIRIGER DES RECHERCHES

présenté et soutenu publiquement le 25 septembre 2012.

# Rapporteurs :

| Tim Davis,      | Professeur des universités, | University of Florida, Gainesville, Etats-Unis      |

|-----------------|-----------------------------|-----------------------------------------------------|

| Jocelyne Erhel, | Directeur de recherche,     | Inria Rennes Bretagne Atlantique                    |

| John Gilbert,   | Professeur des universités, | University of California, Santa Barbara, Etats-Unis |

# Jury:

| Tim Davis,    | Professeur des universités, | University of Florida, Gainesville, Etats-Unis      |

|---------------|-----------------------------|-----------------------------------------------------|

| Iain Duff,    | Professeur des universités, | Rutherford Appleton Laboratory, Angleterre          |

| John Gilbert, | Professeur des universités, | University of California, Santa Barbara, Etats-Unis |

| Yves Robert,  | Professeur des universités, | École Normale Supérieure de Lyon                    |

| Jean Virieux. | Professeur des universités. | Université Joseph Fourier, Grenoble I               |

#### Résumé:

La résolution de systèmes linéaires creux est critique dans de nombreux domaines de la simulation numérique. Beaucoup d'applications, notamment industrielles, utilisent des méthodes directes en raison de leur précision et de leur robustesse. La qualité du résultat, les fonctionnalités numériques, ainsi que le temps de calcul sont critiques pour les applications. Par ailleurs, les ressources matérielles (nombre de processeurs, mémoire) doivent être utilisées de manière optimale. Dans cette habilitation, nous décrivons des travaux poursuivant ces objectifs dans le cadre de la plateforme logicielle MUMPS, développée à Toulouse, Lyon-Grenoble et Bordeaux depuis une quinzaine d'années. Le cœur de l'approche repose sur une parallélisation originale de la méthode multifrontale : une gestion asynchrone du parallélisme, associée à des ordonnanceurs distribués, permet de traiter des structures de données dynamiques et autorise ainsi le pivotage numérique. Nous nous intéressons à l'ordonnancement des tâches, à l'optimisation de la mémoire et à différentes fonctionnalités numériques. Les travaux en cours et les objectifs futurs visent à résoudre efficacement des problèmes de plus en plus gros, sans perte sur les aspects numériques, et tout en adaptant nos approches aux évolutions rapides des calculateurs. Dans ce contexte, les aspects génie logiciel et transfert deviennent critiques afin de maintenir sur le long terme une plateforme logicielle comme MUMPS. Cette plateforme est à la fois nécessaire à nos travaux de recherche et utilisée en production; elle maximise ainsi les retours applicatifs qui valident nos travaux et permettent d'orienter nos recherches futures.

#### Mots-clés:

Matrices creuses, méthodes multifrontales, systèmes linéaires, solveurs directs, ordonnancement.

#### Abstract:

Direct methods for the solution of sparse systems of linear equations are used in a wide range of numerical simulation applications. Such methods are based on the decomposition of the matrix into the product of triangular factors, followed by triangular solves. In comparison to iterative methods, they are known for their numerical accuracy and robustness. However, they are also characterized by a high memory consumption (especially for 3D problems) and a large amount of computations. The quality of the computed solution, the numerical functionalities and the computation time are essential parameters, while the use of material resources (number of processors and memory usage) must be carefully optimized. In this habilitation thesis, we describe some work to pursue these objectives in the context of the sparse direct solver MUMPS, developed in Toulouse, Lyon-Grenoble and Bordeaux. The approach relies on an original parallelization of the multifrontal method for distributed-memory machines, in which an asynchronous management of parallelism associated with distributed scheduling algorithms allows for dynamic datastructures and numerical pivoting. We consider task scheduling, optimization of the memory usage, and various numerical functionalities. Ongoing and future work aim at efficiently solving problems that are always bigger, while maintaining numerical stability and adapting our approaches to the quick evolutions of computer platforms: increase of the number of computing nodes, increase of the number of cores per node, but decrease of memory per core. In this context, software engineering and technology transfer aspects become critical in order to maintain in the long term a software package like MUMPS. This software is both necessary to our research and widely used in industry, maximizing feedback that validates our work and provides future work directions.

#### **Keywords:**

Sparse matrices, multifrontal methods, linear systems, direct solvers.

# Acknowledgements

I am grateful to Tim Davis and John Gilbert for having agreed to report on this work, and for having undertaken such a long trip to be part of my jury. It has been a big honour to have you in Lyon. I also thank Jocelyne Erhel for reporting on this work; I am sorry you were not able to attend the defense in the end. Many thanks to Iain Duff, one of the pioneers in this research field, for having accepted to come to Lyon and preside over my jury. Thanks to Jean Virieux for his participation to my jury and for providing the applications' point of view. Thanks to Yves Robert for participating to my jury and helping with the organization of the defense.

I wish to thank my team leaders at Inria, Frédéric Desprez and Frédéric Vivien, who allowed me to pursue this project. I also thank Patrick Amestoy for having given me the motivation for an academic job and for our fruitful and long-term collaboration on this project. Many thanks to all MUMPS contributors. I especially thank my current close "MUMPS" colleagues, Emmanuel Agullo, Maurice Brémond, Alfredo Buttari, Abdou Guermouche, Guillaume Joslin, Chiara Puglisi, François-Henry Rouet, Mohamed Sid-Lakhdar, Bora Uçar and Clément Weisbecker, for their support for this habilitation.

I am grateful to my wife and family for their constant support.

# Contents

| In | trod | uction   |                                                                          | 1  |

|----|------|----------|--------------------------------------------------------------------------|----|

| 1  | Ger  | ieral B  | Background                                                               | 5  |

|    | 1.1  |          | ctical example                                                           | 5  |

|    |      | 1.1.1    | Dense factorizations                                                     | 5  |

|    |      | 1.1.2    | Sparse factorization and fill-in                                         | 6  |

|    |      | 1.1.3    | The multifrontal method                                                  | 6  |

|    |      | 1.1.4    | Multifrontal solve algorithm                                             | 8  |

|    |      | 1.1.5    | Sparse matrices and graphs                                               | 9  |

|    |      | 1.1.6    | Supernodes                                                               | 11 |

|    |      | 1.1.7    | Orderings and permutations                                               | 13 |

|    |      | 1.1.8    | Preprocessing with maximum weighted matching and scalings algorithms     | 14 |

|    | 1.2  | Theore   | etical formalism                                                         | 16 |

|    |      | 1.2.1    | LU decomposition                                                         | 17 |

|    |      | 1.2.2    | Fill-in and structure of the factor matrices                             | 17 |

|    |      | 1.2.3    | Elimination graph structures                                             | 18 |

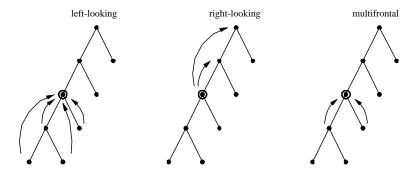

|    |      | 1.2.4    | Left-looking, right-looking and multifrontal methods                     | 21 |

|    | 1.3  | Practi   | cal issues                                                               | 24 |

|    |      | 1.3.1    | Three-phase approach to solve $Ax = b$                                   | 24 |

|    |      | 1.3.2    | Numerical accuracy and pivoting                                          | 24 |

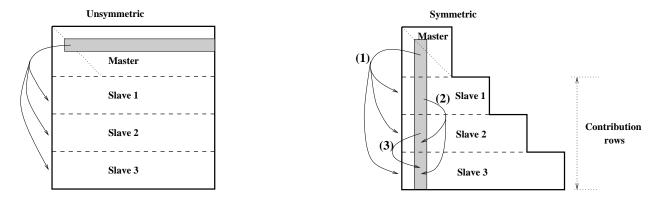

|    |      |          | 1.3.2.1 Unsymmetric case                                                 | 25 |

|    |      |          | 1.3.2.2 Symmetric case                                                   | 26 |

|    |      |          | 1.3.2.3 LINPACK vs. LAPACK styles of pivoting                            | 28 |

|    |      |          | 1.3.2.4 Static pivoting and iterative refinement                         | 28 |

|    |      | 1.3.3    | Memory management in the multifrontal method                             | 28 |

|    |      | 1.3.4    | Out-of-core approaches                                                   | 31 |

| 2  | ΔΡ   | Parallel | Multifrontal Method for Distributed-Memory Environments                  | 33 |

| _  | 2.1  |          | ing the multifrontal factorization to a parallel distributed environment | 33 |

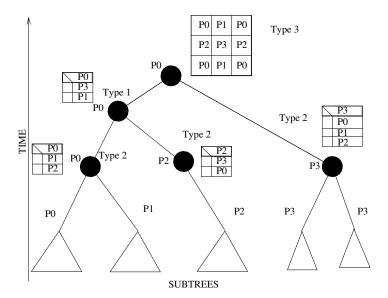

|    | 2.1  | 2.1.1    | Sources of parallelism                                                   | 33 |

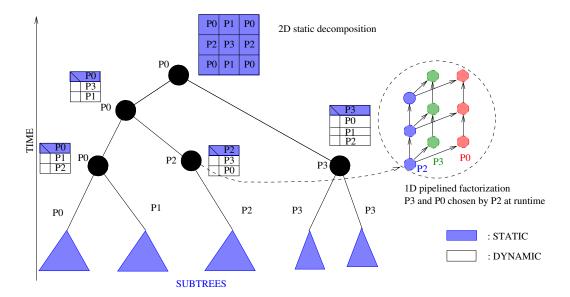

|    |      | 2.1.1    | 2.1.1.1 Description of type 2 parallelism                                | 34 |

|    |      |          | 2.1.1.2 Description of type 3 parallelism                                | 35 |

|    |      | 2.1.2    | Asynchronous communication issues                                        | 36 |

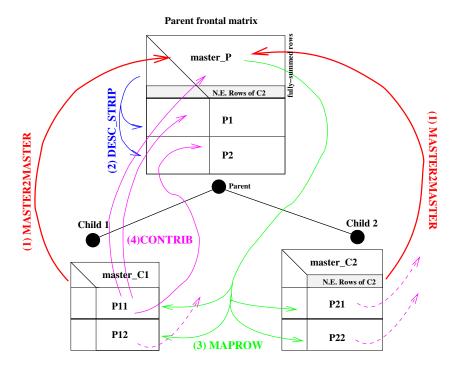

|    |      | 2.1.3    | Assembly process                                                         | 37 |

|    |      | 2.1.4    | Factorization of type 1 nodes                                            | 39 |

|    |      | 2.1.5    | Parallel factorization of type 2 nodes                                   | 40 |

|    |      | 2.1.6    | Discussion                                                               | 43 |

|    | 2.2  |          | selection                                                                | 44 |

|    |      | 2.2.1    | Pivoting and stability issues in a parallel asynchronous context         | 44 |

|    |      | 2.2.2    | Detection of null pivots and rank-revealing                              |    |

|   |     | 2.2.3         | Pivoting and out-of-core                                                 | 46       |

|---|-----|---------------|--------------------------------------------------------------------------|----------|

|   |     | 2.2.4         | Algorithm for pivot selection (symmetric indefinite case)                | 46       |

|   | 2.3 | Schur         | complement                                                               | 47       |

|   | 2.4 |               | on phase                                                                 |          |

|   | 2.5 |               | ced/condensed right-hand side in solve phase                             |          |

|   | 2.6 |               | minant                                                                   | 55       |

|   |     | 2.6.1         | Numerical aspects: avoiding underflows and overflows                     | 55       |

|   |     | 2.6.2         | Computing the sign of the determinant                                    | 56       |

|   |     | 2.6.2 $2.6.3$ | Special cases                                                            | 56       |

|   |     | 2.6.3 $2.6.4$ |                                                                          | 50<br>57 |

|   |     | 2.6.4 $2.6.5$ | Reduction in parallel environments                                       |          |

|   |     |               | Testing                                                                  | 58       |

|   |     | 2.6.6         | Complex arithmetic                                                       | 58       |

|   |     | 2.6.7         | Memory aspects                                                           | 59       |

|   | 2.7 | Concl         | uding remarks                                                            | 59       |

| 3 | Tas | k Sche        | duling for the Serial Multifrontal Method                                | 61       |

|   | 3.1 | Introd        | luction – Tree traversals and postorders                                 | 62       |

|   | 3.2 | Model         | s of assembly in the multifrontal method                                 | 63       |

|   | 3.3 | Posto         | rders to reduce the storage requirements                                 | 65       |

|   |     | 3.3.1         | Notations                                                                | 65       |

|   |     | 3.3.2         | Terminal allocation                                                      | 66       |

|   |     | 0.0.2         | 3.3.2.1 Working storage requirement                                      | 66       |

|   |     |               | 3.3.2.2 Total storage requirement (including factors)                    | 67       |

|   |     |               | 3.3.2.3 Liu's theorem and its application to reduce storage requirements | 67       |

|   |     | 3.3.3         | Early parent allocation                                                  | 68       |

|   |     | 3.3.4         | Flexible allocation                                                      | 69       |

|   |     | 0.0.1         | 3.3.4.1 Classical (non in-place) assembly scheme                         | 69       |

|   |     |               | 3.3.4.1.1 Working storage minimization                                   | 69       |

|   |     |               | 3.3.4.1.2 Total storage minimization                                     | 70       |

|   |     |               | 3.3.4.2 In-place assembly scheme                                         | 72       |

|   |     |               |                                                                          | 72       |

|   |     |               | 3.3.4.2.1 Working storage minimization                                   |          |

|   |     |               | 3.3.4.2.2 Total storage minimization                                     | 73       |

|   |     |               | 3.3.4.3 Max-in-place assembly scheme                                     | 73       |

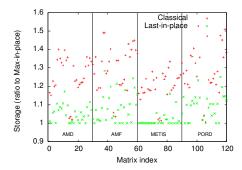

|   |     | 3.3.5         | Impact and summary of experimental results                               | 73       |

|   | 3.4 |               | rders to reduce the volume of I/O                                        | 75       |

|   |     | 3.4.1         | Stacks and $I/O$ volumes                                                 | 76       |

|   |     | 3.4.2         | Notations                                                                | 77       |

|   |     | 3.4.3         | Terminal allocation of the parent, classical assembly                    | 78       |

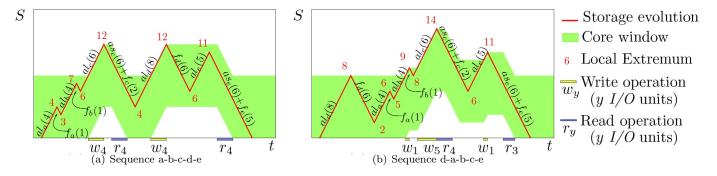

|   |     |               | 3.4.3.1 Illustrative example and formal expression of the I/O volume     | 78       |

|   |     |               | 3.4.3.2 Minimizing the I/O volume                                        | 80       |

|   |     | 3.4.4         | In-place assembly of the last contribution block                         | 81       |

|   |     | 3.4.5         | In-place assembly of the largest contribution block                      | 81       |

|   |     | 3.4.6         | Theoretical comparison of MinMEM and MinIO                               | 82       |

|   |     | 3.4.7         | Flexible parent allocation                                               | 83       |

|   |     | 3.4.8         | Experimental results                                                     | 85       |

|   |     |               | 3.4.8.1 Terminal allocation                                              | 85       |

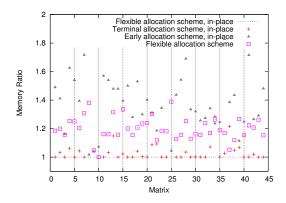

|   |     |               | 3.4.8.2 Flexible allocation                                              | 86       |

|   | 3.5 | Memo          | bry management algorithms                                                | 88       |

|   | 5.5 | 3.5.1         | In-core stack memory                                                     | 88       |

|   |     | 0.0.1         | 3.5.1.1 Recalling the classical and last-in-place assembly schemes       | 89       |

|   |     |               | 3.5.1.2 In-place assembly of the largest contribution block              | 89       |

|   |     |               | 3.5.1.2 In-place assembly of the largest contribution block              | 90       |

|   |     |               | O.O.I.O PICAIDIE AUCCAUCH OF THE HOUGH HIGHICES                          | 30       |

|   |      | 3.5.2         | Out-of-core stacks                                                                 |

|---|------|---------------|------------------------------------------------------------------------------------|

|   |      |               | 3.5.2.1 Dynamic cyclic memory management                                           |

|   |      |               | 3.5.2.2 Using information from the analysis: static top-down formulation 92        |

|   |      |               | 3.5.2.3 Application to the flexible allocation scheme                              |

|   |      | 3.5.3         | Limits of the models                                                               |

|   | 3.6  |               | iding remarks                                                                      |

|   | 5.0  | Concie        | iding remarks                                                                      |

| 4 | Tas  | k Sche        | duling in Parallel Distributed-Memory Environments 97                              |

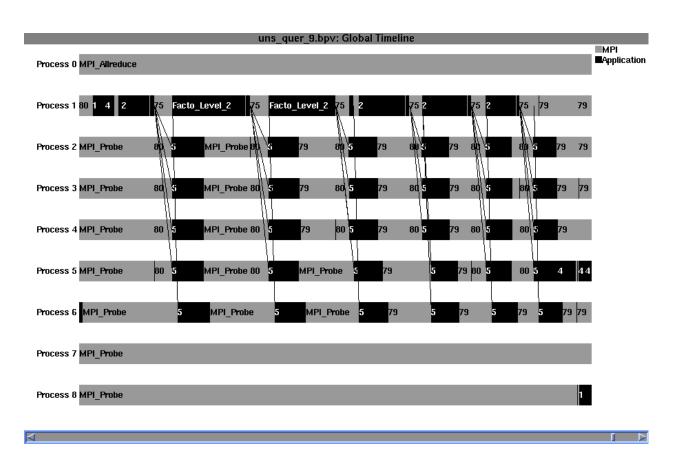

|   | 4.1  |               | ning accurate load estimates                                                       |

|   |      | 4.1.1         | Maintaining a distributed view of the load                                         |

|   |      | 1.1.1         | 4.1.1.1 Naive mechanism                                                            |

|   |      |               | 4.1.1.2 Mechanism based on load increments                                         |

|   |      |               |                                                                                    |

|   |      | 4.1.0         | 4.1.1.3 Reducing the number of messages                                            |

|   |      | 4.1.2         | Exact algorithm                                                                    |

|   |      | 4.1.3         | Experiments                                                                        |

|   |      |               | 4.1.3.1 Memory-based scheduling strategy                                           |

|   |      |               | 4.1.3.2 Workload-based scheduling strategy                                         |

|   |      | 4.1.4         | Concluding remarks                                                                 |

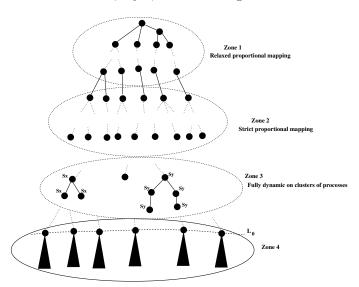

|   | 4.2  | Hybrid        | d static-dynamic mapping and scheduling strategies                                 |

|   |      | 4.2.1         | History – PARASOL project (1996-1999)                                              |

|   |      | 4.2.2         | Improvements (1999-2001)                                                           |

|   |      | 4.2.3         | Static tree mapping: candidate processors                                          |

|   |      | 1.2.0         | 4.2.3.1 Preamble: proportional mapping                                             |

|   |      |               | 4.2.3.2 Main ideas of the mapping algorithm with candidates                        |

|   |      | 4.2.4         |                                                                                    |

|   |      |               | Scheduling for clusters of SMP nodes                                               |

|   |      | 4.2.5         | Memory-based dynamic scheduling                                                    |

|   |      | 4.2.6         | Hybrid scheduling                                                                  |

|   | 4.3  | Memor         | ry scalability issues and memory-aware scheduling                                  |

| 5 | A P  | Parallel      | Out-of-Core Multifrontal Method 123                                                |

| Ŭ | 5.1  | A robi        | ast out-of-core code with factors on disks                                         |

|   | 0.1  | 5.1.1         | Direct and buffered (at the system level) I/O mechanisms                           |

|   |      | 5.1.2         | Synchronous and asynchronous approaches (at the application level)                 |

|   |      | 5.1.2 $5.1.3$ | Testing environment                                                                |

|   |      |               | <u> </u>                                                                           |

|   |      | 5.1.4         | Sequential performance                                                             |

|   |      | 5.1.5         | Parallel performance                                                               |

|   |      | 5.1.6         | Discussion                                                                         |

|   |      |               | Panel version                                                                      |

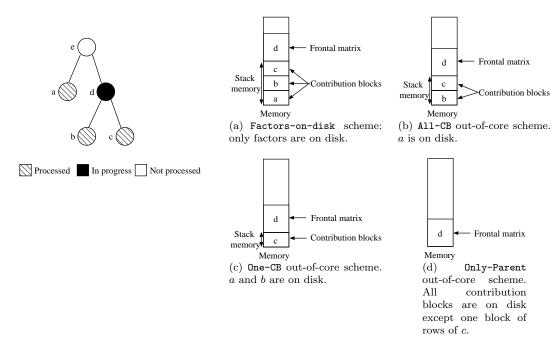

|   | 5.2  | Descri        | ption and analysis of models to further reduce the memory requirements             |

|   |      | 5.2.1         | Models to manage the contribution blocks on disk                                   |

|   |      | 5.2.2         | Analysis of the memory needs of the different schemes                              |

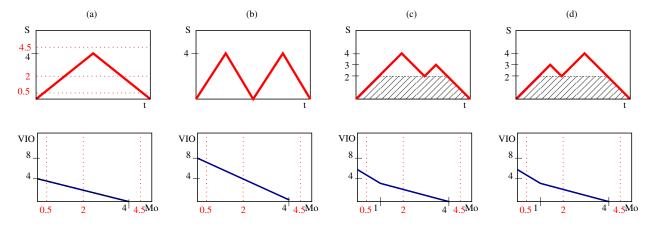

|   |      | 5.2.3         | Analysing how the memory peaks are reached                                         |

|   |      | 5.2.4         | Summary                                                                            |

|   | 5.3  |               | sion                                                                               |

|   | 0.0  | Concre        | 101011                                                                             |

| 6 | Solv | ving In       | creasingly Large Problems 137                                                      |

|   | 6.1  |               | el analysis                                                                        |

|   | 6.2  |               | addressing                                                                         |

|   | 6.3  |               | rd elimination during factorization                                                |

|   | 6.4  |               | ry and performance improvements of the solve algorithms (forward and backward sub- |

|   | 0.4  |               | ons)                                                                               |

|   |      |               | Reduction of workspace and locality issues                                         |

|   |      | 6/11          | Roduction of workensee and locality issues                                         |

| 7 | Cor | clusio | n          |                                                                        | 167   |

|---|-----|--------|------------|------------------------------------------------------------------------|-------|

|   | 6.8 | Concl  | usion and  | other work directions                                                  | . 163 |

|   | 6.7 | -      |            | lvers and grid computing                                               |       |

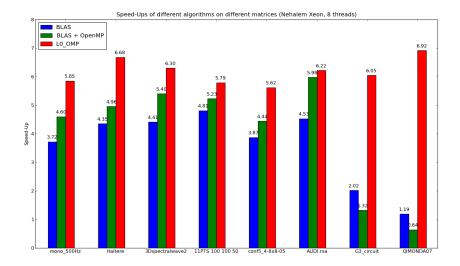

|   |     | 6.6.3  | OpenMI     | P: exploiting the parallelism resulting from the assembly tree         | . 161 |

|   |     |        | 6.6.2.4    | Discussion                                                             |       |

|   |     |        | 6.6.2.3    | Optimization of pivot search algorithm                                 |       |

|   |     |        | 6.6.2.2    | Improvements of the factorization algorithm for the pivot block        |       |

|   |     |        | 6.6.2.1    | Performance bottleneck observed                                        |       |

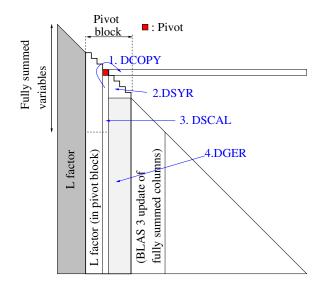

|   |     | 6.6.2  | OpenMI     | P: optimization of a symmetric factorization kernel                    |       |

|   |     |        | fork-join  | ı model                                                                | . 153 |

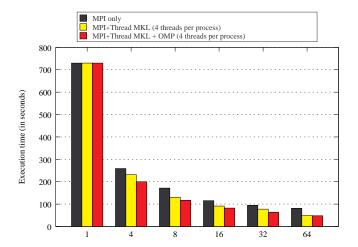

|   |     | 6.6.1  |            | readed BLAS libraries and OpenMP: preliminary experiments based on the |       |

|   | 6.6 | Facing | •          | cicore evolutions                                                      |       |

|   | 6.5 | Comm   | nunication | buffers                                                                | . 151 |

|   |     |        |            | on                                                                     |       |

|   |     | 6.4.2  | Perform    | ance                                                                   | . 144 |

# Introduction

We consider the solution of

$$Ax = b, (1)$$

where A is a large sparse square matrix (typically several millions of equations), and x and b are vectors or matrices. A and b are given and x is the unknown. Such systems of linear equations arise in a wide range of scientific computing applications from various fields, in relation with numerical simulation: finite element methods, finite difference methods, or numerical optimization. There are two main classes of methods to solve such problems: direct methods, based on a factorization of A in, for example, the form LU,  $LDL^T$ . or QR; and iterative methods, in which sparse matrix-vector products are used to build a series of iterates, hopefully converging to the solution. Direct methods are more robust and are often preferred in industrial applications. Among direct methods, multifrontal methods build the factorization of a sparse matrix by performing partial factorizations of smaller dense matrices. But multifrontal methods, and direct methods in general, require a larger amount of memory than iterative methods, because the factors of a sparse matrix have a higher density of nonzero elements than the original matrix. Furthermore, they result in an additional computational complexity especially in three-dimensional (3D) problems. This can be illustrated by a simple 7-point finite difference stencil for a 3D Laplacian equation. If N is the number of discretization points in each direction, the matrix A has  $N^3$  rows and  $N^3$  columns, with about  $7N^3$  nonzero elements. When nested dissections are used to reorder the variables of the problem and limit the size of the factors, the number of entries in the factor matrix is  $O(N^4)$  and the number of floating-point operations for the factorization is  $O(N^6)$  (see [42], for example). As a comparison, the matrix-vector product performed at each iteration of an iterative method is  $O(N^3)$ .

However, thanks to the increasing capacity (storage, performance) of modern supercomputers and thanks to significant progresses in direct methods, with robust software packages available ([3],[59],[116],[124],...), direct methods are often preferred by applications, even for 3D problems of several millions of equations. For such systems, the size of the graph representing the dependencies between the computations can be huge. In this context, it is critical but difficult to maintain a good numerical stability while making use of parallelism and targetting high performance. We focus in this thesis on robust and efficient parallel algorithms, taking into account the following objectives and constraints:

- 1. Large-scale high performance machines generally have their memory physically distributed. Therefore, the message-passing paradigm should be used. In the case of SMP<sup>1</sup> nodes or multicores, the shared-memory paradigm can also be used at the node level or at the multicore level.

- 2. Matrix factorizations are much more stable when numerical pivoting is allowed. Therefore, numerical pivoting should be used even in a parallel distributed environment. One difficulty with sparse matrices is that numerical pivoting results in a modification of the task dependency graph, which can then not be fully known beforehand. Furthermore, the stability of a pivot must be checked against other entries in the matrix, which is not trivial because it often requires costly interprocessor communications.

- 3. Architecture evolutions make it very hard or even impossible to perfectly predict the behaviour of current computing platforms, with several levels of caches, high performance redundant networks with

<sup>&</sup>lt;sup>1</sup>Symmetric MultiProcessors: a uniform memory shared by the different processors in the node.

a complex topology, some degree of heterogeneity between processors or at the network level, varying load in possibly multi-user environments, etc. Furthermore, the characteristics of our graph of tasks are not fully predictable when numerical pivoting is allowed (see previous point). Therefore, it is worth considering adaptive approaches, with so-called *dynamic scheduling*. In practice, we will show that static information could/should be used to reduce the space to be explored by the dynamic schedulers.

- 4. There are often time constraints in numerical simulation. Therefore, it is critical that the algorithms reduce the time for solution (or *makespan*) as much as possible on a given number of processors.

- 5. If the problem is large, a special attention must be paid to memory which is, if not correctly used, a very strong limiting factor for parallel direct methods. The order in which the tasks are scheduled has a strong impact not only on the makespan, but also on memory and unfortunately, more parallelism often leads to more global memory used. Therefore, it is crucial to take these two conflicting criteria into account when designing scheduling strategies for the computational tasks.

- 6. When memory is not large enough on the target machine, *out-of-core* approaches are necessary, in which the disk is used as the next level of memory hierarchy. In that case, the algorithms must decide what to write and when to write it. This generates I/O traffic and a special attention should be paid to limit it.

- 7. Parallelism from the graph of tasks obtained (a tree in our context) is generally not sufficient, and the largest tasks should themselves be parallelized (this has been sometimes been called mixed parallelism [50, 66]).

```

1: Initialization:

2: pool \leftarrow my share of the initial ready tasks

while (Global termination not detected) do

if a message of type state information is ready to be received then

5:

Receive the message (load information, memory information...);

Update the load and memory estimates of the relevant processor(s);

6:

else if an application-related message is ready to be received then

7:

Receive and process the message (task, data, ...), typically:

8:

- reserve some workspace

- perform some computations

- decrease a counter keeping track of unmet task dependencies

- insert a new ready task in the local pool of ready tasks

- send another application-related message

- etc.

else if (pool not empty) then

9:

10:

Extract a task T from the pool of ready tasks

if T is big then

11:

Assign parts of T to other processors (sending application-related messages);

12:

Process T in cooperation with the chosen processors (sending asynchronous application-related

13:

messages);

end if

14:

15:

Note that state information might have been sent, depending on local load or local memory

variations}

16: end while

```

**Algorithm 0.1**: Asynchronous approach retained (simplified).

With these objectives in mind, we have designed a fully asynchronous approach [24, 26] to process the graph of tasks during the factorization. The approach is based on message passing and the general scheme is

the one of Algorithm 0.1. A pool of ready tasks is maintained on each processor: an initial (static) mapping defines the local pool of tasks for each processor (tasks that can start without dependency), and a new task is inserted in one of the local pools when all its dependencies have been met. When a task is large, some other processors are assigned to help with that task, dynamically, depending on an estimate of the state of the other processors. Overall, there are two types of dynamic (distributed) scheduling decisions: (i) the selection of a new ready task from the local pool, line 10; (ii) the subdivision of the task and its mapping on some other processors, line 12. The processor responsible of a task will be called master for that task, while the processors chosen dynamically to help are called slave processors. In order for this scheme to work efficiently, two main questions must be answered, and will be discussed later in this document:

- 1. How to map and schedule the tasks and which decisions should be static and dynamic?

- 2. How to maintain distributed estimates of the state information (memory, workload) of the processors?

Even in serial environments, scheduling is crucial and impacts the amount and locality of the temporary data produced: each task produces temporary data that is consumed only when the task that depends on it is activated. This motivates theoretical studies on the order in which a graph of tasks should be processed to either:

- minimize the memory usage due to these temporary data, or

- minimize the I/O traffic, in the case those temporary data do not fit in the physical memory.

The work presented in this document is motivated by the needs from applications. An external use of our algorithms on large-scale academic and industrial applications is essential to validate our research, and to get feedback, which in turn motivates new research directions. In this context, an important aspect of this activity consists in making available the results of research under the form of a software package, MUMPS<sup>2</sup>, enabling users to solve new problems efficiently and accurately in various fields related to numerical simulation. This involves activities such as software engineering, development, validation, support and maintenance. Furthermore, each new functionality or research work has to be thought in a global software context, and not just for one particular combination of other functionalities. For example, the detection of null pivot rows/columns that we have recently implemented (for automatic detection of rigid modes or for FETI-like methods [86]) should work on the internal 1D, possibly out-of-core, parallel asynchronous pipelined factorizations, in symmetric and unsymmetric cases, including for cases where part of the column is not available on the processor in charge of the pivot selection. Therefore, when a new algorithm is designed and validated, a significant amount of work is needed to make it compatible with a large range of functionalities and thus available to a large range of applications.

Historically, this work on parallel multifrontal methods in distributed environments and the associated software developments that led to the successive versions of the research platform MUMPS were initiated in the scope of a European project called PARASOL (Long Term Research, Esprit IV framework, 1996-1999) and was inspired by an experimental prototype of an unsymmetric multifrontal code for distributed-memory machines using PVM [89] developed by Amestoy and Espirat [85]. That experimental prototype was itself inspired by the code MA41, developed by Amestoy during his PhD thesis [17] at CERFACS under the supervision of Duff. The PARASOL project led to a first public version of the software package MUMPS in 1999. Since then, after my arrival at INRIA in 2001, the research and developments have been mainly supported by CERFACS, CNRS, ENS Lyon, INPT(ENSEEIHT)-IRIT, INRIA and University of Bordeaux.

This document describes some aspects of the work of an overall project, which is the result of a team work with many contributors over the years, and was the object of many collaborations, PhD thesis and projects among which we can cite:

a central collaboration with Patrick Amestoy from INPT(ENSEEIHT)-IRIT since 1996,

<sup>&</sup>lt;sup>2</sup>See http://graal.ens-lyon.fr/MUMPS or http://mumps.enseeiht.fr.

- the PhD thesis of Abdou Guermouche (ENS Lyon, 2001-2004), Stéphane Pralet (INPT-CERFACS, 2002-2004), Emmanuel Agullo (ENS Lyon, 2005-2008), Mila Slavova (INPT-CERFACS, 2005-2009), François-Henry Rouet (INPT-IRIT, 2009-2012), Clément Weisbecker (INPT-IRIT, 2010-), Mohamed Sid-Lakhdar (ENS Lyon, 2011-)

- an NSF-INRIA project (2001-2004) aiming at mixing direct and iterative methods,

- the Grid TLSE project (2002-), initially funded by the ACI-Grid programme from the French ministry of research, then by ANR<sup>3</sup> projects,

- an Egide-Aurora cooperation with Norway (2004),

- the Solstice project (2007-2010) funded by ANR<sup>3</sup> programs,

- the Seiscope consortium (2006-) around Geoscience-Azur,

- contracts with industry: Samtech S.A. (2005-2006 and 2008-2010) and CERFACS/CNES (2005),

- two France-Berkeley projects (1999-2000 and 2008-2009),

- a French-Israeli "Multicomputing" project (2008-2010),

- an Action of Technological Development funded by INRIA (2009-2012),

- lots of discussions within the "MUMPS team" and informal collaborations with the academic and industrial users of MUMPS.

The document is organized as follows. Chapter 1 presents some general background on multifrontal methods, and provides the main principles of the approach we rely on. Chapter 2 shows how some algorithms, features and functionalities which appear simple in a sequential environment must be adapted in a parallel asynchronous scheme targeting distributed-memory environments. Chapter 3 discusses the problem of task scheduling when working with a limited memory in a serial environment. Two aspects are considered: (i) how to reduce the memory requirements of multifrontal methods? (ii) how to use the disk as a secondary storage and minimize I/O? Chapter 4 summarizes the major evolutions of the algorithms responsible of task mapping and scheduling in parallel distributed-memory environments. In Chapter 5, the use of disk-storage for problems where memory is not sufficient is discussed, while Chapter 6 shows that several other algorithmic and software bottlenecks also had to be tackled in order to process real-life large-scale problems efficiently. Finally to conclude we give some medium-term perspectives, together with their expected impact on applications.

<sup>&</sup>lt;sup>3</sup>Agence Nationale de la Recherche.

# Chapter 1

# General Background

In this chapter, we introduce some general concepts related to sparse direct solvers, and in particular multifrontal methods, that will be used or referred to in this document. We first adopt a practical point of view driven by a running example (Section 1.1) before introducing some theoretical formalism in Section 1.2. We discuss other practical related issues in Section 1.3.

# 1.1 A practical example

#### 1.1.1 Dense factorizations

Suppose that we want to solve a system of linear equations of the form Ax = b, where A is a square non-singular matrix of order n, b is the right-hand side, and x is the unknown. We take an example where the structure of the matrix is symmetric, and the numerical values are not, as illustrated by Equation (1.1).

$$\begin{pmatrix}

2 & 0 & 0 & 2 & 1 \\

0 & 1 & -1 & 0 & 0 \\

0 & -1 & 0 & -2 & 0 \\

4 & 0 & 2 & 14 & 0 \\

-6 & 0 & 0 & 0 & -2

\end{pmatrix}

\begin{pmatrix}

x_1 \\

x_2 \\

x_3 \\

x_4 \\

x_5

\end{pmatrix} =

\begin{pmatrix}

5 \\

1 \\

-2 \\

6 \\

-12

\end{pmatrix}$$

(1.1)

In dense linear algebra, this can be done by applying a variant of Gaussian elimination. The method first factorizes the matrix of the system (referred to as A) under the form A = LU, where L is lower triangular with ones on the diagonal and U is upper triangular, as shown in Equation 1.2. This can be done using Algorithm 1.1. At each step, a pivot is eliminated, the column of L is computed, and a rank-one update is performed. Such an algorithm is said to be right-looking because after the elimination of each pivot, we only modify the right-bottom part of the matrix, without accessing again the already computed factors.

$$\begin{pmatrix}

2 & 0 & 0 & 2 & 1 \\

0 & 1 & -1 & 0 & 0 \\

0 & -1 & 0 & -2 & 0 \\

4 & 0 & 2 & 14 & 0 \\

-6 & 0 & 0 & 0 & -2

\end{pmatrix} = \begin{pmatrix}

1 & 0 & 0 & 0 & 0 \\

0 & 1 & 0 & 0 & 0 \\

0 & -1 & 1 & 0 & 0 \\

2 & 0 & -2 & 1 & 0 \\

-3 & 0 & 0 & 1 & 1

\end{pmatrix} \begin{pmatrix}

2 & 0 & 0 & 2 & 1 \\

0 & 1 & -1 & 0 & 0 \\

0 & 0 & -1 & -2 & 0 \\

0 & 0 & 0 & 6 & -2 \\

0 & 0 & 0 & 0 & 3

\end{pmatrix} (1.2)$$

Once the LU factorization of A is obtained, one can solve the system Ax = b in two steps:

- The forward elimination, consisting in solving Ly = b for y. In our case we obtain  $y = (5, 1, -1, -6, 9)^T$ .

- The backward substitution, consisting in solving Ux = y for x, finally leading to the solution of our system of equations  $x = (1, 2, 1, 0, 3)^T$ .

```

1: for i=1 to n do

2: L(i:i)=1

3: L(i+1:n,i)=\frac{A(i+1:n,i)}{A(i,i)}

4: U(i,i:n)=A(i,i:n)

5: A(i+1:n,i+1:n)=A(i+1:n,i+1:n)-L(i+1:n,i)\times A(i,i+1:n)

6: end for

```

**Algorithm 1.1**: Factorization of a dense matrix A of order n under the form LU.

In dense matrix computations, L and U generally overwrite the matrix A, avoiding the use of additional storage for L and U. This results in Algorithm 1.2, where in the end A has been overwritten by (L-I)+U (the ones on the diagonal of L are not stored). If the matrix is symmetric, an  $LDL^T$  factorization is computed instead. More variants can be found in the literature, see for example [96].

```

1: for i=1 to n do

2: A(i+1:n,i) = \frac{A(i+1:n,i)}{A(i,i)}

3: A(i+1:n,i+1:n) = A(i+1:n,i+1:n) - A(i+1:n,i) \times A(i,i+1:n)

4: end for

```

**Algorithm 1.2**: Dense LU factorization overwriting matrix A.

# 1.1.2 Sparse factorization and fill-in

In order to exploit the sparsity of our initial matrix A, we want to avoid the storage of and computations on zeros. If we want to exploit the zeros of our matrix in the application of Algorithm 1.1, line 3 should only consider the nonzero entries from the lower part of column i, that is A(i+1:n,i); furthermore, the rank-one update at line 5 should only use the nonzero entries in vectors L(i+1:n,i) and A(i,i+1:n). One way to organize the operations only on nonzeros and manage the associated data structures is the so-called multifrontal method, which will be central to this thesis and introduced in Section 1.1.3.

Obviously, except in case of numerical cancellation, if an entry  $a_{ij}$  is nonzero in the original matrix,  $l_{ij}$  (if i > j) or  $u_{ij}$  (if  $j \ge i$ ) will also be nonzero. However, even if an entry is zero in the original matrix A, the corresponding entry can be nonzero in the factors, and this phenomenon is known as fill-in. This is illustrated in the example of Equation (1.2): both  $a_{45}$  and  $a_{54}$  are 0 in A but both  $l_{54}$  and  $u_{45}$  are nonzeros in L and U, respectively<sup>1</sup>. Those nonzeros first appeared when performing the rank-one update associated to pivot 1. In order to limit the amount of fill-in, the order in which the variables are eliminated is critical, as explained in Section 1.1.7.

#### 1.1.3 The multifrontal method

In the multifrontal method, instead of modifying directly the entries in A, we use dense matrices to perform and store the rank-one updates. Let us illustrate this process for the rank-one update of the first pivot. Starting from A we build a temporary matrix whose structure results from the nonzeros in the first row/column (indices 1, 4 and 5 of the original matrix) as follows:

$$A_1^{(145)} = \begin{pmatrix} 2 & 2 & 1\\ 4 & 0 & 0\\ -6 & 0 & 0 \end{pmatrix} \tag{1.3}$$

The numbers in parentheses refer to the indices of the variables in the numbering of the original matrix. We now perform the factorization of column 1 and the subtraction of the rank-one update inside that dense

<sup>&</sup>lt;sup>1</sup>This also occurs for the diagonal element in position (3,3). However, we consider that we will not try to exploit zeros on the diagonal.

matrix, avoiding some indirections that would arise by directly working on the sparse matrix A. In fact, this can be viewed as the application of the first step of Algorithm 1.2 to  $A_1^{(145)}$ , a dense  $3 \times 3$  matrix. After this operation,  $A_1^{(145)}$  is modified and overwritten by:

$$F_1^{(145)} = \begin{pmatrix} 2 & 2 & 1\\ 2 & -4 & -2\\ -3 & 6 & 3 \end{pmatrix} \tag{1.4}$$

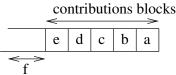

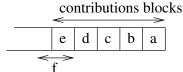

The matrix in which  $A_1^{(145)}$ , and then  $F_1^{(145)}$  is stored is called the *frontal matrix*, or *front*, associated with the first pivot (we also call it *pivot* 1):  $A_1^{(145)}$  is the assembled front and  $F_1^{(145)}$  is the partially factorized front. The Schur complement produced at the bottom-right part of  $F_1$ ,  $CB_1^{(45)} = \begin{pmatrix} -4 & -2 \\ 6 & 3 \end{pmatrix}$ , is called the *contribution block* of  $F_1^{(145)}$  associated with variables 4 and 5. It will be used later during the factorization process, in order to update some rows and columns in the matrix before variables 4 and 5 may be eliminated. The first row and the first column of  $F_1^{(145)}$  correspond to the factors associated with variable 1: row 1 of U

Similarly, we have for pivot 2

consists of 2, 2, and 1; column 1 of L consists of 1 (implicit), 2 and -3.

$$A_2^{(23)} = \begin{pmatrix} 1 & -1 \\ -1 & 0 \end{pmatrix}$$

and  $F_2^{(23)} = \begin{pmatrix} 1 & -1 \\ -1 & -1 \end{pmatrix}$  (1.5)

involving variables 2 and 3 in the numbering of the original matrix.  $CB_2^{(3)} = (-1)$  is the contribution block of  $F_2$  associated with variable 3.

Let us now define the arrowhead associated with a pivot p as the set of nonzero entries of the original matrix A that are part of  $A(p:n,p) \cup A(p,p+1:n)$  (part of the row and column of the pivot that are not factorized yet).

We consider the elimination of pivot 3 and extract the arrowhead of 3 to obtain the submatrix  $\begin{pmatrix} 0 & -2 \\ 2 & 0 \end{pmatrix}$  associated with variables 3 and 4. Because the elimination of pivot 2 has an impact on the value of pivot 3, we add into this matrix the update  $CB_2^{(3)}$  due to the elimination of pivot 2 and computed at step 2 and obtain the assembled front:

$$A_3^{(34)} = \begin{pmatrix} -1 & -2 \\ 2 & 0 \end{pmatrix}. \tag{1.6}$$

The first row and first column of  $A_3^{(34)}$  are said to be *fully-summed* because all possible updates from previous pivot eliminations have been incorporated into them. Therefore, pivot 3 can be factorized, leading to the factorized frontal matrix

$$F_3^{(34)} = \begin{pmatrix} -1 & -2 \\ -2 & -4 \end{pmatrix}$$

and  $CB_3^{(4)} = (-4)$ . (1.7)

Then, notice that the elimination of pivot 4 involves variable 5 because of the fill-in coming from the elimination of pivot 1 and available in the contribution  $CB_1^{(45)}$ :

$$A_4^{(45)} = \begin{pmatrix} 14 & 0 \\ 0 & 0 \end{pmatrix} + CB_1^{(45)} + CB_3^{(4)} = \begin{pmatrix} 6 & -2 \\ 6 & 3 \end{pmatrix}$$

(1.8)

In the summation above,  $CB_3^{(4)}$  is a  $1\times 1$  matrix only concerned by variable 4. Since variable 4 corresponds to the first variable of the resulting matrix, the unique element of  $CB_3^{(4)}$  is summed at position (1,1) of that resulting matrix.

It follows after factorization of pivot 4 in  $A_4^{(45)}$ :

$$F_4^{(45)} = \begin{pmatrix} 6 & -2 \\ 1 & 5 \end{pmatrix}$$

and  $CB_4^{(5)} = (5)$  (1.9)

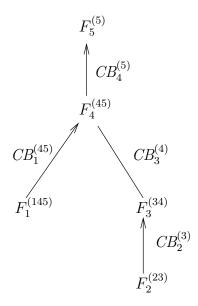

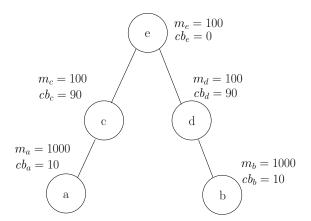

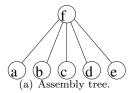

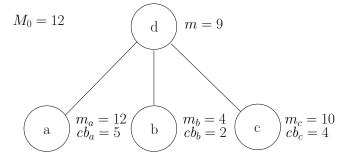

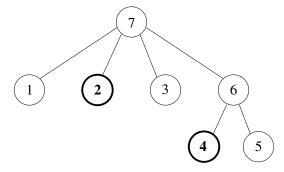

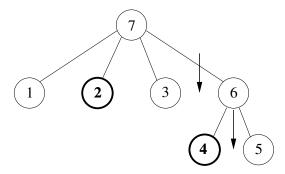

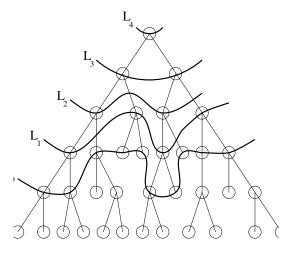

Figure 1.1: Dependencies between pivot eliminations when applying the multifrontal method to the  $5 \times 5$  matrix of Equation (1.1).  $F_i$  represents the *i*th frontal matrix and the *i*th node.

Finally,  $A_5^{(5)} = -2 + 5 = 3 = F_5^{(5)}$  and the factorization is complete. A closer look at the dependencies during this factorization shows the order of computations follows the tree of Figure 1.1. This tree is called *elimination tree* [128]; we will come back to this notion later. For the moment, note that at each node of the tree, we have computed one column of L (the diagonal element is equal to 1 and is not stored explicitly) and one row of U. In comparison to Equation (1.1) and Algorithm 1.1, zeros are not stored and operations on zeros have not been performed. This is at the cost of indirections during the assembly of each frontal matrix, where for each pivot p, we had to:

- build the symbolic structure of the frontal matrix associated with p,

- assemble nonzero entries from row A(p, p : n) and column A(p + 1 : n, p) of the initial matrix, forming the arrowhead of variable p, into  $F_p$ ,

- assemble the contribution blocks  $CB_j$  into  $F_p$ , for all children j of p; this operation is also called an extend-add operation, and it requires indirections<sup>2</sup>,

- eliminate pivot p, building the  $p^{th}$  row and  $p^{th}$  column of the factors and (except for the last pivot or root) a contribution  $CB_p$  used at the parent node.

#### 1.1.4 Multifrontal solve algorithm

The solve algorithm consists in a forward elimination, where the triangular system Ly = b is solved to obtain an intermediate right-hand side, followed by a backward substitution, where the triangular system Ux = y is then solved to obtain the solution x. In the multifrontal method, the columns of L and the rows of U are scattered in the elimination tree and are parts of the matrices  $F_i$  (see Figure 1.1). During the forward elimination, the tree is processed from bottom to top. At each step, part of the solution y is computed and the right-hand side b is then modified using the partial computed solution, as shown in Algorithm 1.3.

Applying this algorithm to our example can be decomposed as below, following the nodes of the tree:

$<sup>^{2}</sup>$ For example, in Equation (1.8), the + operator must be considered as an extend-add operation rather than a simple summation.

```

for i=1 to n do \{ \text{Work on front } i \}

Solve l_{ii}y_i = b_i for y_i

for all nonzeros l_{ki} in column i of L, k > i do \{ \text{Update right-hand side of trailing subsystem: } \}

b_k \leftarrow b_k - l_{ki}y_i

end for

```

**Algorithm 1.3**: Algorithm for the forward elimination. Remark that, in our case,  $l_{ii}$  is equal to one for all i.

```

• Node 1: y_1 = b_1 = 5, b_4 \leftarrow b_4 - l_{41}y_1 = -4, b_5 \leftarrow b_5 - l_{51}y_1 = 3

```

- Node 2:  $y_2 = b_2 = 1$ ,  $b_3 \leftarrow b_3 l_{32}y_2 = -1$

- Node 3:  $y_3 = b_3 = -1$ ,  $b_4 \leftarrow b_4 l_{43}y_3 = -6$

- Node 4:  $y_4 = b_4 = -6$ ,  $b_5 \leftarrow b_5 l_{54}y_4 = 9$

- Node 5:  $y_5 = b_5 = 9$ .

Concerning the backward substitution Ux = y, the solution is first computed at the root node:  $x_5 = u_{55}^{-1}y_5 = 3$ , then equation  $u_{44}x_4 + u_{45}x_5 = y_4$  results in  $x_4 = 0$  at node 4.  $x_1$  and  $x_3$  can then be computed independently using the equations  $u_{11}x_1 + u_{14}x_4 + u_{15}x_5 = y_4$  and  $u_{33}x_3 + u_{34}x_4 = y_3$ , respectively associated with nodes 1 and 3 of the tree. Finally,  $x_2$  is obtained from  $x_3$  using the equation  $u_{22}x_2 + u_{23}x_3 = y_3$  (node 2), leading to  $x = (1 \ 2 \ 1 \ 0 \ 3)^T$ . The process is summarized in Algorithm 1.4.

```

for i=n downto 1 do

{Compute known part of equation i} \alpha \leftarrow 0

for all nonzeros u_{ik} in row i of U, k > i do \alpha \leftarrow \alpha + u_{ik}x_k

end for

Solve u_{ii}x_i = y_i - \alpha for x_i

end for

```

**Algorithm 1.4**: Algorithm for the backward substitution.

It is important to notice that, at each step of the algorithm, only the factors at each node are used, preserving the data organization from the factorization. The algorithm naturally extends to multiple right-hand sides.

#### 1.1.5 Sparse matrices and graphs

A graph G = (V, E) is associated with a matrix A with symmetric pattern in such a way that

- V = 1, ..., n represents the list of variables of the graph, where n is the number of variables of the matrix;

- an edge  $(i,j), i \neq j$  from i to j belongs to E if  $a_{ij}$  is nonzero. Note that edges (i,i) are not considered.

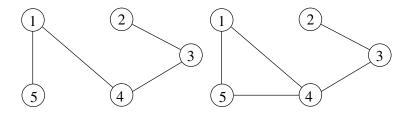

In general, such a graph is *directed*. However, for matrices with a symmetric structure, one may consider undirected edges  $\{i,j\}$ , together with an *undirected* graph. In Figure 1.2, we represent the undirected graph associated with the matrix of Equation (1.1), together with the graph associated with the matrix of factors (L+U).

Figure 1.2: Graph of the example matrix A (left) and graph of the filled matrix L+U (right). Fill-in has appeared between variables 4 and 5, corresponding to the elimination of pivot 1, then no other fill occurs during the elimination of pivots 2, 3, 4 and 5.

```

Initialization: G_0 = (E_0, V_0) is the graph associated with A

for i = 1 to n do

E_i \leftarrow E_{i-1}

Add edges to E_i to make all neighbours of i in G_{i-1} pairwise adjacent

Remove edges adjacent to i from E_i

V_i \leftarrow V_{i-1} \setminus \{i\} = \{i+1 \dots n\}

G_i \stackrel{def}{=} (E_i, V_i) is the elimination graph after step i

```

**Algorithm 1.5**: Elimination graphs associated with the factorization of a matrix A.

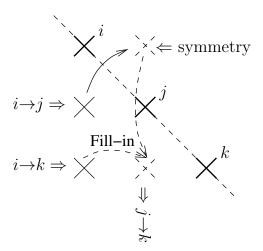

Following the concept of elimination graphs introduced in [138] and starting from the graph associated with A, the rank-one update associated with each pivot results in the addition of a clique between the nodes that were adjacent to the eliminated pivot: every two vertices among the neighbours of the pivot become connected by an edge. In our example, the clique introduced by the elimination of pivot 1 is a simple edge between nodes 4 and 5, corresponding to the fill between variables 4 and 5 in the factors. This is followed by the elimination of the current pivot and its adjacent edges. Starting from the graph of the original matrix  $G_0 = (E_0, V_0)$ , the process is described by Algorithm 1.5, where at each step, a graph  $G_i$  is built in which variable i has been eliminated. (Remark that  $G_n$  is empty). The filled graph is the graph  $G^+ = (V_0, \bigcup_{i=0}^n E_i)$ resulting from all the fill-in that appeared during the factorization. It is also the graph associated with the matrix of factors L + U (see Figure 1.2, right).

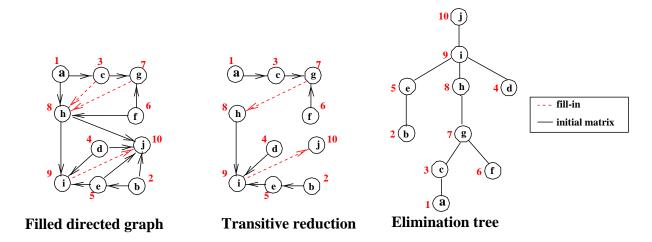

The notion of elimination tree can be deduced from the graph of the filled matrix (Figure 1.2, right) by:

- replacing undirected edges by directed edges following the order of elimination of the variables (1 2 3 4 5), and

- suppressing unnecessary dependencies; in the example, edge  $1 \to 5$  is suppressed because of the existence of the edges  $1 \to 4$  and  $4 \to 5$ . We keep the edges  $1 \to 4$ ,  $2 \to 3$ ,  $3 \to 4$ ,  $1 \to 4$  and  $4 \rightarrow 5$ .

In terms of graphs, remark that this corresponds to computing a so called transitive reduction of the directed graph associated to U (or  $L^T$ ). In our example, the elimination tree defined this way exactly corresponds to the tree of Figure 1.1. In the multifrontal approach, the fact that edge  $1 \rightarrow 5$  is suppressed corresponds to the fact that the contributions of variable 1 on variable 5, available in  $CB_1^{(45)}$  are passed from node 1 to node 5 not directly but via node 4. In practice, computing the full filled graph and its transitive reduction would be too costly so that other techniques must be applied (see for example [128]).

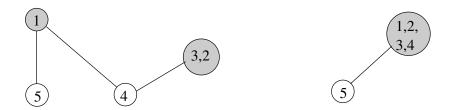

Finally, the notion of quotient graph model, first introduced for sparse symmetric matrix factorizations by [91] is very useful to both save storage and limit the computational complexity associated with the construction of elimination graphs. The sequence of elimination graphs is replaced by a sequence of quotient graphs. With quotient graphs, the clique information is implicitly represented by the pivot, which, instead of being eliminated and suppressed from the graph, becomes a special node sometimes called *element* (see [19]).

Figure 1.3: Quotient graphs after elimination of pivots 1, 2, and 3 (left) and after elimination of pivots 1, 2, 3, and 4 (right). On the left, the fill (clique) between 4 and 5 is implicitly represented by element 1.

Each new element absorbs the already formed elements adjacent to it: the collapsed elements together with each not yet eliminated variable form a partition of the original graph, to which a quotient graph can thus be associated (duplicate edges are suppressed). In our example, and starting from the graph of Figure 1.2 (left), the sequence of quotient graphs corresponding to the pivot eliminations is obtained as follows:

- 1. After elimination of pivot 1, {1} becomes an element.

- 2. After elimination of pivot 2, {2} becomes an element.

- 3. After elimination of pivot 3, {3} becomes an element and absorbs {2} because there was an edge between element {2} and variable 3; one obtains the quotient graph of Figure 1.3 (left).

- 4. After elimination of pivot 4, {4} becomes an element which absorbs element {3,2} and element {1}, that were adjacent to 4 (see Figure 1.3, right).

- 5. After elimination of pivot 5,  $\{5\}$  absorbs element  $\{4, 1, 3, 2\}$ .

The quotient graph model allows an efficient computation of the tree structure: each time an element i is absorbed by an element j, j becomes the parent of i. For example, after the elimination of pivot 4, because  $\{4\}$  absorbs elements  $\{3,2\}$  and  $\{1\}$ , 4 is the parent of 1 and 3 (where 3 became the parent of 2 at the moment of building element  $\{3,2\}$ ).

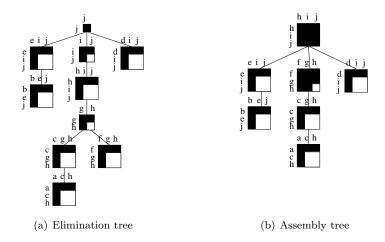

#### 1.1.6 Supernodes

Still considering symmetric matrices, a supernode [41] is a contiguous range of columns in the matrix of factors having the same lower diagonal nonzero structure. More precisely, in the graph associated with the matrix of factors (directed graph associated with  $L^T$ , or U), a supernode is such that the nodes associated with the matrix variables form a clique and have the same outgoing edges outside the clique. In our example, variables 4 and 5 can be amalgamated into a single supernode, leading to a  $2 \times 2$  frontal matrix  $F_{45}^{(45)}$  instead of the last two frontal matrices of the tree in Figure 1.1. The multifrontal method applies as before except that:

- both the arrowheads associated with variables 4 and 5 must be copied into the frontal matrix  $F_{45}$ ;

- both variables 4 and 5 are eliminated in the frontal matrix associated with the supernode (4, 5), instead of one variable for the frontal matrix of 4 and one variable for the frontal matrix of 5.

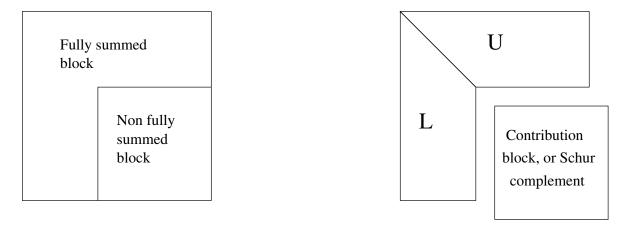

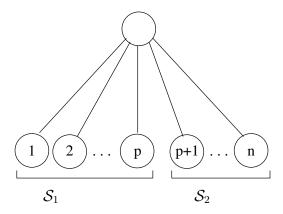

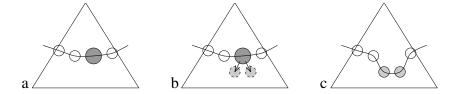

The notion of elimination tree is replaced by a so called assembly tree, as shown in Figure 1.4. Remark that we could also have defined a larger supernode by amalgamating variables 1, 4, and 5, suppressing another frontal matrix. This also illustrates that there is not a unique way to perform amalgamation and that this process might be different to enhance vectorization and/or parallelism. At each supernode, instead of eliminating just one variable, all the variables defined by the supernode are eliminated. In our example, the amalgamated node was the root node, but more generally, a frontal matrix has the shape of Figure 1.5. At

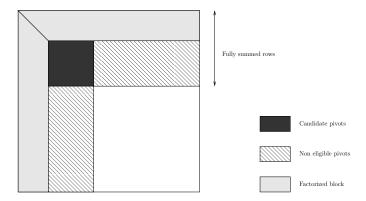

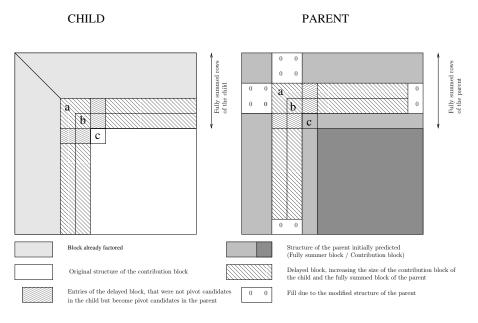

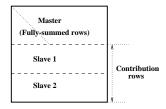

each frontal matrix, fully-summed block is factorized and the non fully-summed block (contribution block or Schur complement) is updated. The algorithms for the solve phase also naturally extend to supernodes, working on blocks of columns of L (resp. blocks of rows of U) during the forward (respectively backward) substitution.

Figure 1.4: Dependencies between pivot eliminations when applying the multifrontal method to the  $5 \times 5$  matrix of Equation (1.1). Variables 4 and 5 have been amalgamated into a single supernode.

Figure 1.5: Frontal matrix at a node of the tree before (left) and after (right) the partial factorization of the fully-summed block. Unsymmetric case (*LU* factorization).

Working on supernodes instead of individual variables is essential in order to speed-up the computations and use high-level BLAS [72] (Basic Linear Algebra Subprograms): supernodes lead to a higher flops to memory access ratio, and this allows a better usage of memory hierarchy and better performance thanks to the blocking techniques used in BLAS routines. Typically, BLAS 3 routines (TRSM, GEMM) will be used during the factorization. During the solve stage, BLAS 2 instead of BLAS 1 (respectively BLAS 3 instead of BLAS 2) routines will be used for a single (respectively multiple) right-hand-side vector(s). In practice, it is also worth relaxing the notion of supernodes by amalgamating nodes that introduce some extra computations on zeros: amalgamation reduces the amount of indirections and increases the sizes of the matrices used in BLAS.

# 1.1.7 Orderings and permutations

Different strategies exist to minimize the amount of fill-in, and thus decrease the amount of computation. Consider a permutation matrix P. The initial system Ax = b and the modified system  $(PAP^T)(Px) = (Pb)$  have the same solution x. Consider the permutation matrix P such that  $PAP^T$  leads to pivots in the order (2,3,4,5,1) (second pivot of the original matrix first, third pivot second, etc.). We thus have:

$$P = \begin{pmatrix} 0 & 1 & 0 & 0 & 0 \\ 0 & 0 & 1 & 0 & 0 \\ 0 & 0 & 0 & 1 & 0 \\ 1 & 0 & 0 & 0 & 0 \\ 0 & 0 & 0 & 0 & 1 \end{pmatrix} , \text{ and}$$

(1.10)

$$PAP^{T} = \begin{pmatrix} 1 & -1 & 0 & 0 & 0 \\ -1 & 0 & -2 & 0 & 0 \\ 0 & 2 & 14 & 4 & 0 \\ 0 & 0 & 2 & 2 & 1 \\ 0 & 0 & 0 & -6 & -2 \end{pmatrix} = \begin{pmatrix} 1 & 0 & 0 & 0 & 0 \\ -1 & 1 & 0 & 0 & 0 \\ 0 & -2 & 1 & 0 & 0 \\ 0 & 0 & 0.2 & 1 & 0 \\ 0 & 0 & 0.2 & 1 & 0 \\ 0 & 0 & 0 & -5 & 1 \end{pmatrix} \times \begin{pmatrix} 1 & -1 & 0 & 0 & 0 \\ 0 & -1 & -2 & 0 & 0 \\ 0 & 0 & 10 & 4 & 0 \\ 0 & 0 & 0 & 1.2 & 1 \\ 0 & 0 & 0 & 0 & 3 \end{pmatrix}$$

$$(1.11)$$

Notice that in that case, no fill-in occurs: the structures of L and U are included in the structure of A (not taking into account the diagonal, for which the sparsity will never be exploited). The objective of reordering techniques (or orderings) is precisely to find a permutation P that limits the amount of fill-in (and number of operations). In general, minimizing the fill-in is NP-complete [166] so heuristics have to be defined. The problem is easier seen in terms of graph, where we associate a graph to a matrix A as explained in Section 1.1.5.

An example of local heuristic to find such a permutation, or ordering, is the minimum degree, where at each step of Algorithm 1.5, we eliminate the pivot with smallest degree (or smallest adjacency size) and update the current elimination graph accordingly. The use of quotient graphs allows to run in-place, in the sense that quotient graphs do not require more storage than the initial matrix. The approximate minimum degree (AMD [19]) and the multiple minimum degree (MMD [125]) are variants of the minimum degree that use such an approach to be computationally efficient. The minimum fill algorithm [133, 147] is another local approach which attempts at eliminating at each step the pivot leading to the smallest fill, taking into account already existing edges in the elimination graph at the current step.

For large matrices, nested dissections [92] give better orderings, because they have a more global view of the graph. The way they work is the following: given a node separator S of the graph, and two disconnected domains  $D_1$  and  $D_2$ , the order of the variables in the permuted matrix is chosen to be  $D_1$ ,  $D_2$ , S. No fill can appear between  $D_1$  and  $D_2$  and the zero blocks remain during the factorization.  $D_1$  and  $D_2$  are partitioned recursively leading to a recursive block-bordered structure. Typically, once the subgraphs are small enough, a switch to a local heuristic becomes interesting again. After the switch to a local heuristic, the adjacency with halo variables may be taken into account [140].

There exist other heuristics. For example, the Cuthill-McKee algorithm consists in a breadth-first search traversal of the matrix graph that limits the envelope and bandwidth of the matrix, restricting the fill to this structure. In the breadth-first search, layers are built in such a way that there are no connections between layer i and layer i + 2. This way, the band structure can be seen as a tridiagonal block structure where entries in block (i, i + 1) represent the connections between layer i and layer i + 1. No fill-in can occur outside this tridiagonal block structure.

As indicated by their name, fill-reducing heuristics target the reduction of fill-in and thus the size of the factors. We indicate in Table 1.1 the size of the factors obtained with the following heuristics, that will be used as representatives of the different classes (local, global, or hybrid) of orderings all along this document:

- AMD: the Approximate Minimum Degree [19];

- AMF: the Approximate Minimum Fill, as implemented in MUMPS by P. Amestoy;

|          | METIS | SCOTCH | PORD   | AMF    | AMD    |

|----------|-------|--------|--------|--------|--------|

| GUPTA2   | 8.55  | 12.97  | 9.77   | 7.96   | 8.08   |

| SHIP_003 | 73.34 | 79.80  | 73.57  | 68.52  | 91.42  |

| TWOTONE  | 25.04 | 25.64  | 28.38  | 22.65  | 22.12  |

| WANG3    | 7.65  | 9.74   | 7.99   | 8.90   | 11.48  |

| xenon2   | 94.93 | 100.87 | 107.20 | 144.32 | 159.74 |

Table 1.1: Size of factors (millions of entries) as a function of the ordering heuristic applied. Bold and italic correspond to best and worse orderings, respectively, for each matrix.

|          | METIS   | SCOTCH   | PORD     | AMF      | AMD      |

|----------|---------|----------|----------|----------|----------|

| GUPTA2   | 2757.8  | 4510.7   | 4993.3   | 2790.3   | 2663.9   |

| SHIP_003 | 83828.2 | 92614.0  | 112519.6 | 96445.2  | 155725.5 |

| TWOTONE  | 29120.3 | 27764.7  | 37167.4  | 29847.5  | 29552.9  |

| wang3    | 4313.1  | 5801.7   | 5009.9   | 6318.0   | 10492.2  |

| xenon2   | 99273.1 | 112213.4 | 126349.7 | 237451.3 | 298363.5 |

Table 1.2: Number of floating-point operations (millions) as a function of the ordering heuristic applied. Bold and italic correspond to best and worse orderings, respectively, for each matrix.

- PORD: a tight coupling of bottom-up and top-down sparse reordering methods [156];

- METIS: we use here the routine METIS\_NODEND or METIS\_NODEWND from the METIS package [120], which is an hybrid approach based on multilevel nested dissection and multiple minimum degree;

- SCOTCH: we use a version of SCOTCH [139] provided by the author that couples nested dissection and (halo) Approximate Minimum Fill (HAMF), in a way very similar to [141].

Another goal of fill-reducing orderings is to reduce the number of operations and the effect of the above heuristics on the number of floating-point operations is reported in Table 1.2. Let us take the example of an  $LDL^T$  factorization with D diagonal and L lower triangular. Noting  $n_i$  the number of nonzero elements in column i of L, the size of the factors is  $\sum n_i$  and the number of floating-point operations is  $\sum (n_i + \frac{n_i \times (n_i + 1)}{2})$ , so that the objectives of floating-point operations and factor size reductions are somewhat related, as can be seen in Tables 1.1 and 1.2 for matrices WANG3 and TWOTONE for example, where METIS minimizes both the number of operations and the size of the factors. This is not always the case, for example AMD minimizes the size of the factors for matrix TWOTONE but not the number of operations (minimized with SCOTCH).

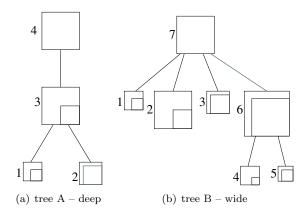

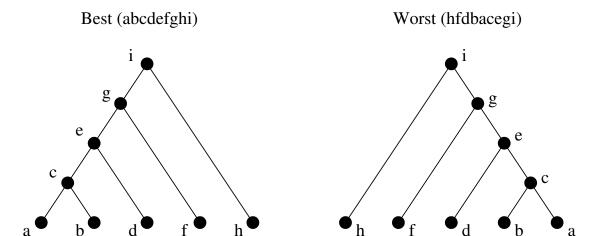

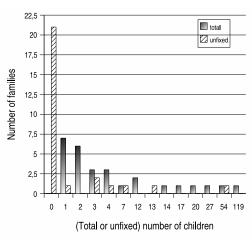

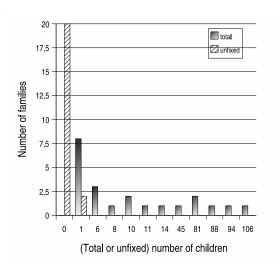

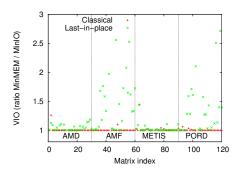

Note that although these heuristics mainly target the reduction of fill-in (and thus size of the factors) and the number of operations – see Tables 1.2 and 1.1, they also have a significant impact on the shape of the assembly tree and the parallelism (see, for example, [24]). Figure 1.6 summarizes the characteristics of the trees resulting from different orderings.

### 1.1.8 Preprocessing with maximum weighted matching and scalings algorithms

Let us assume that A is a nonsingular matrix with an unsymmetric nonzero pattern. Let us now consider a representation of A by a bipartite graph, where one set of nodes represents the rows and the other set represents the columns. An edge between a *row* node and a *column* node exists only if the corresponding entry in A is nonzero.

In that case, finding a maximum cardinality matching in the bipartite graph and permuting the row (or column) nodes accordingly corresponds to permuting the matrix to a zero-free diagonal. Using weighted matching algorithms allows one to obtain large values on the diagonal (by minimizing the sum or the product of diagonal entries). This has several advantages:

| Reordering technique | Shape of the tree | observations                                                                                                      |

|----------------------|-------------------|-------------------------------------------------------------------------------------------------------------------|

| AMD                  |                   | Deep well-balanced tree     Large frontal matrices on top of the tree                                             |

| AMF                  |                   | <ul> <li>Very deep unbalanced tree</li> <li>Small frontal matrices</li> <li>Very large number of nodes</li> </ul> |

| PORD                 |                   | <ul> <li>deep unbalanced tree</li> <li>Small frontal matrices</li> <li>Large number of nodes</li> </ul>           |

| SCOTCH               |                   | <ul> <li>Very wide well-balanced tree</li> <li>Large frontal matrices</li> <li>Small number of nodes</li> </ul>   |

| METIS                |                   | Wide well-balanced tree     Large number of nodes     Smaller frontal matrices (than SCOTCH)                      |

Figure 1.6: Shape of the trees resulting from various reordering techniques.

| Matrix   |               | Structural | LU       | Flops    | Backwd     |

|----------|---------------|------------|----------|----------|------------|

|          |               | symmetry   | $(10^6)$ | $(10^9)$ | Error      |

| TWOTONE  | OFF           | 28         | 235      | 1221     | $10^{-6}$  |

|          | $\mathbf{ON}$ | 43         | 22       | 29       | $10^{-12}$ |

| FIDAPM11 | OFF           | 100        | 16       | 10       | $10^{-10}$ |

|          | $\mathbf{ON}$ | 46         | 28       | 29       | $10^{-11}$ |

Table 1.3: Effect of weighted matching algorithms on the factorization of two unsymmetric matrices with MUMPS.

- better numerical properties and improved numerical behaviour: the linear system is easier to solve and the amount of numerical pivoting and of row/column interchanges is limited;

- more predictable data structures; in the extreme case of codes using static data structures, where runtime pivoting is very limited or even not done, many problems cannot be solved without preprocessing based on such column permutations;

- improved reliability of memory estimates;

- reduced amount of computations and fill-in in the factors, especially for approaches working on a symmetrized structure, that is where an explicit zero is introduced at position i, j in cases where  $a_{ij}$  is zero and  $a_{ji}$  is nonzero.

Duff and Koster [76, 77] provide effective algorithms together with more details on the application and effects of such techniques to sparse Gaussian elimination. Scaling arrays can also be provided on output of the weighted matching algorithm so that the diagonal entries of the permuted scaled matrix are all one, and off-diagonal entries are smaller, also improving the numerical properties. The linear system of Equation (1) becomes:

$$(D_r A Q D_c)(D_c^{-1} Q^T x) = D_r b,$$

where  $D_r$  and  $D_c$  are diagonal scaling matrices, and Q is a permutation matrix. Fill-reducing heuristics of Section 1.1.7 can then be applied, leading to:

$$(PD_rAQD_cP^T)(PD_c^{-1}Q^Tx) = PD_rb.$$

We illustrate in Table 1.3 the importance of weighted matching algorithms with such scaling on the behaviour of the MUMPS solver on two matrices. In this table, the symmetry is defined as the percentage of nonzero elements (i,j) in the (possibly permuted) matrix for which the element (j,i) is also nonzero. Clearly, the effect is negative when the matrix has a symmetric structure. In [78], Duff and Pralet show how maximum weighted matching algorithms can be useful to symmetric indefinite matrices: on top of the scaling arrays (see Table 1.4), matched entries are candidates for numerically good  $2 \times 2$  pivots – see Section 1.3.2.2, which the fill-reducing heuristics may then take into account structurally. One way to do that is to force those  $2 \times 2$  pivots to become supervariables. Significant improvements can be obtained, as shown in Table 1.5 for augmented matrices of the form  $K = \begin{pmatrix} H & A \\ A^T & 0 \end{pmatrix}$ .

# 1.2 Theoretical formalism

This section introduces some theoretical formalism and is complementary to the previous section. Reading it is not strictly necessary for the understanding of the rest of this document.

|           | Total     | time | Nb of entries in factors (millions) |      |             |      |

|-----------|-----------|------|-------------------------------------|------|-------------|------|

|           | (seconds) |      | (estimated)                         |      | (effective) |      |

| Scaling:  | OFF       | ON   | OFF                                 | ON   | OFF         | ON   |

| CONT-300  | 45        | 5    | 12.2                                | 12.2 | 32.0        | 12.4 |

| CVXQP3    | 1816      | 28   | 3.9                                 | 3.9  | 62.4        | 9.3  |

| STOKES128 | 3         | 2    | 3.0                                 | 3.0  | 5.5         | 3.3  |

Table 1.4: Influence of scaling from [78] on augmented matrices. The scaled matrix is DAD, where  $D = \sqrt{D_r D_c}$ .

|              | Total     | time | Nb of entries in factors in Millions |      |             |      |

|--------------|-----------|------|--------------------------------------|------|-------------|------|

|              | (seconds) |      | (estimated)                          |      | (effective) |      |

| Compression: | OFF       | ON   | OFF                                  | ON   | OFF         | ON   |

| CONT-300     | 5         | 4    | 12.3                                 | 11.2 | 32.0        | 12.4 |

| CVXQP3       | 28        | 11   | 3.9                                  | 7.1  | 9.3         | 8.5  |

| STOKES128    | 1         | 2    | 3.0                                  | 5.7  | 3.4         | 5.7  |

Table 1.5: Influence of preselecting  $2 \times 2$  pivots (with scaling).

# 1.2.1 LU decomposition

Given a sparse system of linear equations Ax = b, where  $A = (a_{ij})_{1 \le i,j \le n}$  is a sparse matrix of order n, and x and y are column vectors, we admit that a decomposition A = LU exists if the matrix is invertible (non-singular) even if in general it means swapping some columns. In this decomposition L is a lower triangular matrix whose diagonal values are equal to 1 and U is an upper triangular matrix.

Matrices L and U verify:  $a_{ij} = (LU)_{ij}$ ,  $1 \le i, j \le n$ . Considering the respective triangular structures of L and U, we can write:  $a_{ij} = \sum_{k=1}^{\min(i,j)} l_{ik} u_{kj}$ . Because  $l_{ii} \equiv 1$ , we have:

$$\begin{cases}

a_{ij} = \sum_{k=1}^{i-1} l_{ik} u_{kj} + u_{ij} & \text{if } i \leq j \\

a_{ij} = \sum_{k=1}^{j-1} l_{ik} u_{kj} + l_{ij} u_{jj} & \text{if } i > j

\end{cases}$$

(1.12)

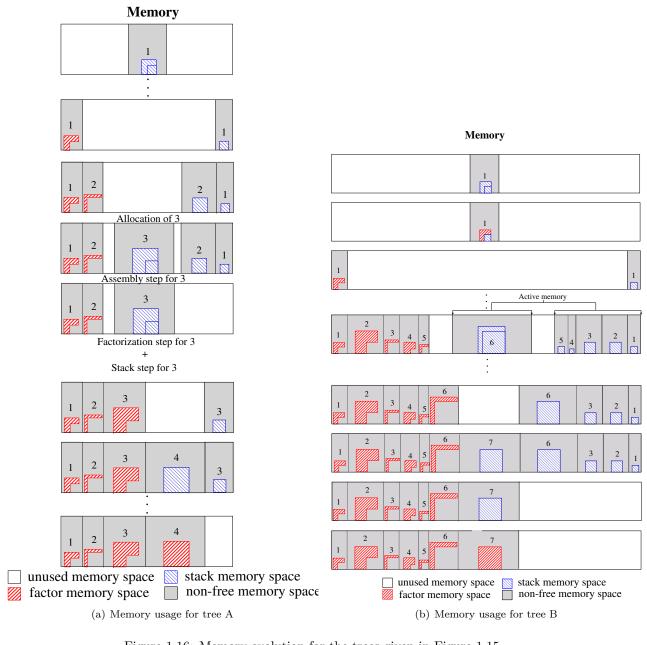

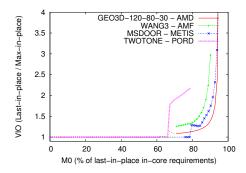

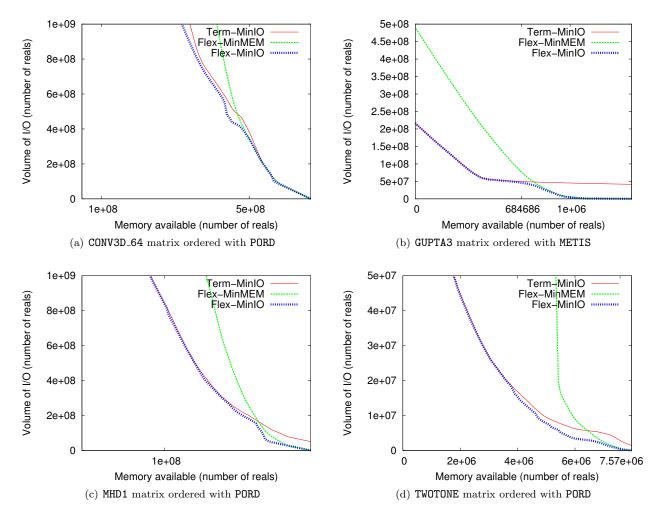

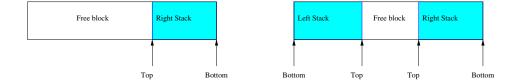

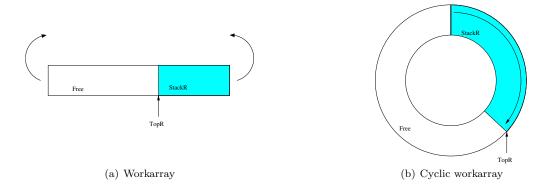

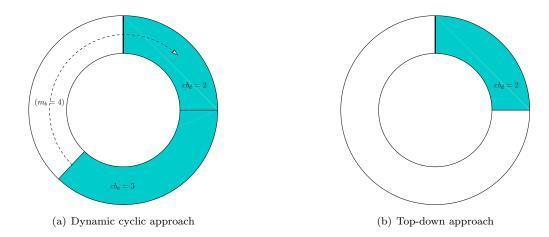

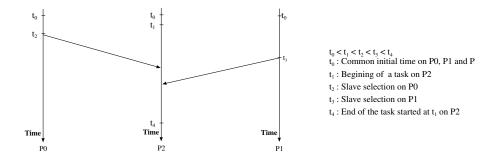

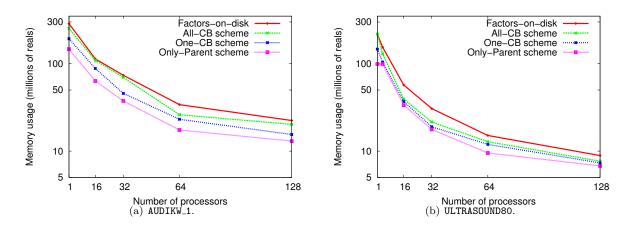

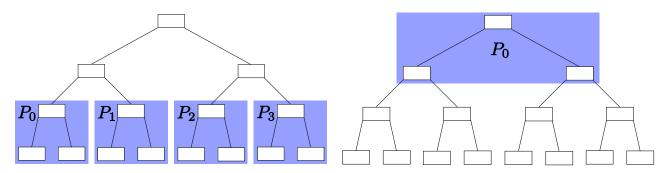

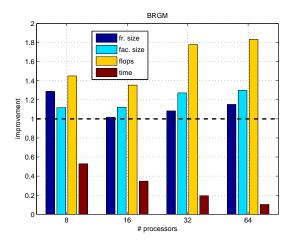

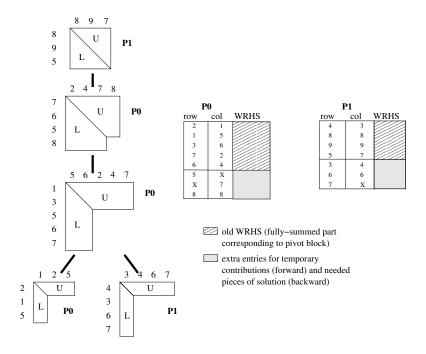

We deduce the following expression of the factors (remark that the notations i and k have been swapped):