## Design and implementation of an application specific multi-channel stimulator for electrokinetically-driven microfluidic devices

Jose Gomez Quinones

#### ▶ To cite this version:

Jose Gomez Quinones. Design and implementation of an application specific multi-channel stimulator for electrokinetically-driven microfluidic devices. Autre. Université de Grenoble; Inst.Tecno.y de Est.Sup.de Monterrey, 2011. Français. NNT: 2011GRENT104. tel-00662414v2

## HAL Id: tel-00662414 https://theses.hal.science/tel-00662414v2

Submitted on 11 Jul 2012

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

#### UNIVERSITÉ DE GRENOBLE

## **THÈSE**

Pour obtenir le grade de

#### DOCTEUR DE L'UNIVERSITÉ DE GRENOBLE

Spécialité : Micro et Nano Electronique

Arrêté ministérial: 7 aôut 2006

Et de:

## DOCTEUR DE L'INSITUTO TECNOLÓGICO Y DE ESTUDIOS SUPERIORES DE MONTERREY

Spécialité : Technologies de l'Information et Communications

Présentée par

## José I. GÓMEZ-QUIÑONES

Thèse dirigée par Olivier ROSSETTO et Sergio O. Martínez Chapa

préparée au sein Laboratoire de Physique Subatomique et de Cosmologie de L'École Doctorale d'Electronique, Electrotechnique, Automatique et Traitement du Signal et du Département de Génie Electrique et Informatique de l'Instituto Tecnológico y de Estudios Superiores de Monterrey

## Conception et Implémentation d'un Stimulateur Multi-Canal pour les Dispositifs Microfluidiques

Thèse soutenue publiquement le **10 octobre 2011**, devant le jury composé de :

#### Dr., Skandar, BASROUR

Professeur, Université de Grenoble, Président

Dr., Bruno, ALLARD

Chercheur et Professeur, Institut National des Sciences Appliquées , Rapporteur

Dr., Jesús, SANTANA-SOLANO

Chercheur et Professeur, CINVESTAV Unidad Monterrey, Rapporteur

Dr., Graciano, DIECK-ASSAD

Chercheur et Professeur, ITESM Campus Monterrey , Examinateur

Dr., Olivier, ROSSETTO

Maître de conferences à l'Université de Grenoble, LPSC, Directeur de thèse

Dr., Sergio O., MARTÍNEZ-CHAPA

Chercheur et Professeur, ITESM Campus Monterrey, Directeur de thèse

## Dedicatoria

Con todo mi amor para Bernarda, Ivette e Isabella Sue

\* \* \*

A Jesús, con todo mi respeto, cariño y amor, te extraño mucho papá...

## Agradecimientos

- A Dios, rector de mi vida, mi luz y mi salvación.

- Al Dr. Álvaro y Sra. Dorita por tratarme como a un hijo en todo momento, los quiero mucho. Gracias por apoyarme siempre.

- Mi mas sincero agradecimiento para mi asesor, Dr. Sergio O. Martínez Ch. por su grán apoyo, por su motivación y su guía. Gracias por confiar en mi. Gracias porque en muchas ocasiones tuvo más fé en mi que la que yo tenía en mi mismo.

- Al Dr. Graciano Dieck Assad por sus consejos y su grán ayuda en la revisión y corrección de este documento.

- A la Dra. Blanca Lapizco por su participación en el comité de tésis y por la excelente revisión que realizo a esta disertación

- Al Dr. Hugo Terashima y Dr. José Luis Gordillo por su apoyo durante mi estancia en el programa doctoral

- Al Dr. Farid Bautista D. por sus consejos, su apoyo y ayuda incondicional en todo momento.

- A la Dra. Martha Salomé por su apovo por sus consejos y por escucharme

- A Víctor Hugo Perez por su grán ayuda en muchos de los análisis contenidos en éste documento y a Hector Moncada, es un placer trabajar con ustedes.

- A mi tía Fanny Huffmann, a Cynthia y Christine por hacer muy placentera mi estancia en Europa, mi agradecimiento eterno

- A mi padrino Pepe y mi tía Isabel por apoyarme y darme ánimos siempre. Usted sabe padrino, verdad que si?

- A mis hermanos, Maricruz, José Francisco y América, los quiero mucho.

### Remerciements

Je voudrais vivement remercier tous ceux qui m'ont aidé á mener á bien mes travaux de recherche, et tout particuliérement:

- Le Professeur ROSSETO, Olivier pour sa grande aide et ses conseils précieux qu'il a eu pour moi, non seulement pour en tant qu'élève, mais aussi en tant qu'ami. En ce sens, j'aimerais lui exprimer ma reconnaissance éternelle.

- Les Professeurs BASROUR, Skandar et ALLARD, Bruno pour leur participation au jury et leur contribution très précieuse dans la correction de cette thèse.

- Mon ami et professeur, M. MICHEL, Guillaume de m'avoir ouvert les portes de la langue française et pour son grand soutien.

- M. Raymond et Mme. Nanou de m'avoir accueilli et considéré comme un membre de leur famille.

- Mon ami MARCOTTE, Galdric, pour ses grandes expressions d'amitié pendant mon séjour en France.

- Mon ami YAMOUNI, Mahfoud pour ses conseils, son soutien et son amitié.

- M. BOUVIER, Joel et RARBI, Fatah pour leur aide très précieuse dans la réalisation du prototype.

- Mes collègues du service électronique au Laboratoire de Physique Subatomique et de Cosmologie: messieurs BOULY, Jean-Luc, BOURRION, Olivier, BOSSON, Germain, SCORDILIS, Jean-Pierre, MUGGEO, Savino, FOGLIO, Robert, RICHER, Jean-Pierre et LAGORIO, Eric, pour leur aide pendant la réalisation de mon projet.

- M. KOX, Serge pour son sutien pendant mon séjour au LPSC.

- Merci aussi Ludovic pour ton amitié!

- Et pour finir, M. PETRONE, Charles et Alain pour leur soutien inconditionnel.

## Design and Implementation of an Application Specific Multi-Channel Stimulator for Electrokinetically-Driven Microfluidic Devices

by José I. Gómez Quiñones

#### Abstract

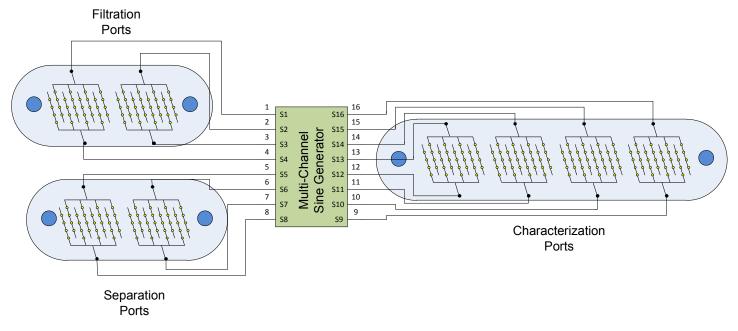

This dissertation presents the design and implementation of a 16-channel sinusoidal generator to stimulate microfluidic devices that use electrokinetic forces to manipulate particles. The generator has both, independent frequency and independent amplitude control for each channel. The stimulation system is based upon a CMOS application specific (ASIC) device developed using 0.35µm technology. Several generator techniques were compared based on frequency range, total harmonic distortion (THD), and on-chip area. The best alternative for the microfluidic applications is based in a triangle-to-sine converter and presents a frequency range of 8kHz to 21MHz, an output voltage range of 0V to 3.1V<sub>PP</sub>, and a maximum THD of 5.11%. The fabricated device, has a footprint of 1560μm×2030μm. The amplitude of the outputs is extended using an interface card, achieving voltages of 0V to 15V<sub>PP</sub>. The generator functionality was tested by performing an experimental set-up with particle trapping. The set-up consisted of a micromachined channel with embedded electrodes configured as two electrical ports located at different positions along the channel. By choosing specific amplitude and frequency values from the generator, different particles suspended in a fluid were simultaneously trapped at different ports. The multichannel stimulator presented here can be used in many microfluidic experiments and devices where particle trapping, separation and characterization is desired.

## List of Figures

| 1.1  | Examples of Lab-on-a-chip devices                                                 | 3  |

|------|-----------------------------------------------------------------------------------|----|

| 3.1  | Multiple-output direct-form digital oscillator                                    | 13 |

| 3.2  | Simplified diagram of DDFS and signal flow as shown in [1]                        | 15 |

| 3.3  | Ideal model for an OTA                                                            | 18 |

| 3.4  | 4OTA2C oscillator structure                                                       | 19 |

| 3.5  | 4OTA2C quadrature oscillator                                                      | 20 |

| 3.6  | Relaxation oscillator                                                             | 20 |

| 3.7  | Triangle to Sine Converter in Strong Inversion (TSC-SI)                           | 22 |

| 3.8  | Characteristics of Triangle to Sine Converter                                     | 23 |

| 3.9  | Triangle to Sine Converter in Weak Inversion (TSC-WI)                             | 24 |

| 4.1  | Schematic diagram of the electrical double-layer                                  | 29 |

| 4.2  | Shell models for simulated dielectrophoretic properties                           | 33 |

| 4.3  | Behavior of a particle under DEP force [2]                                        | 33 |

| 5.1  | Parallel processing of electrokinetic tasks                                       | 38 |

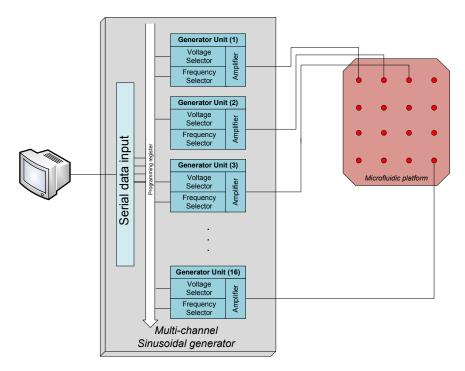

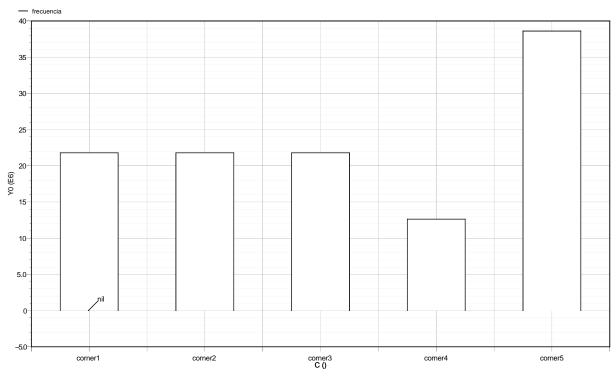

| 5.2  | Proposed multi-channel oscillator system                                          | 40 |

| 5.3  | Proposed strategy for the digital approach                                        | 41 |

| 5.4  | Block diagram of the data acquisition board                                       | 42 |

| 5.5  | Block diagram of the DDUO $\ \ldots \ \ldots \ \ldots \ \ldots \ \ldots \ \ldots$ | 42 |

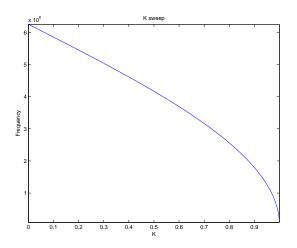

| 5.6  | K values sweep $\dots$                                                            | 43 |

| 5.7  | 12-bit system oscillator output at different frequencies                          | 43 |

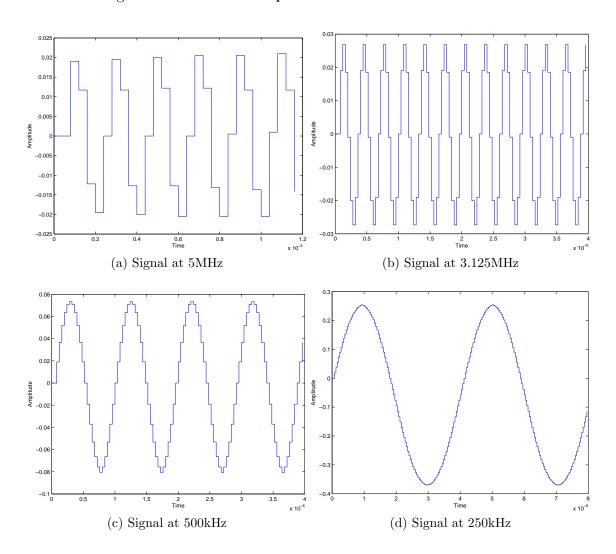

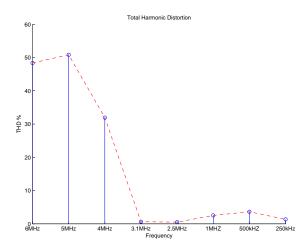

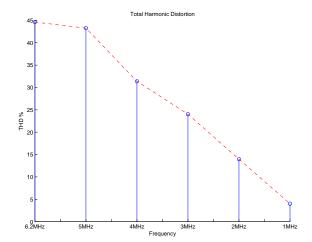

| 5.8  | THD measurements for a system of 12 bits                                          | 44 |

| 5.9  | 8-bit oscillator outputs at different frequencies                                 | 45 |

| 5.10 | THD measurements for a system of 8 bits                                           | 46 |

| 5 11 | DDFS Block Diagram                                                                | 47 |

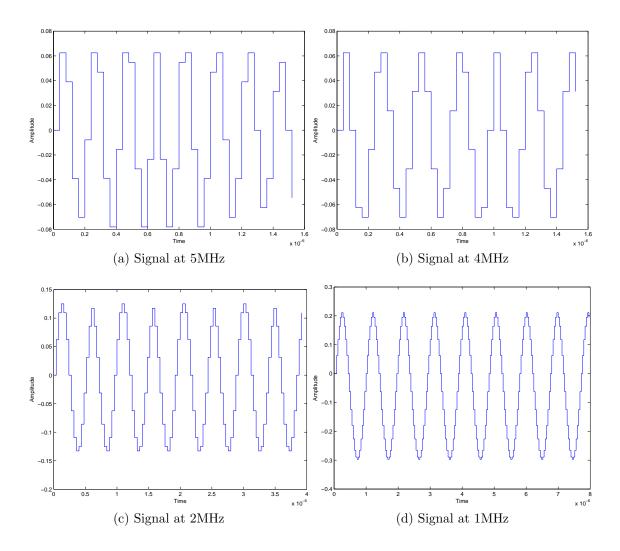

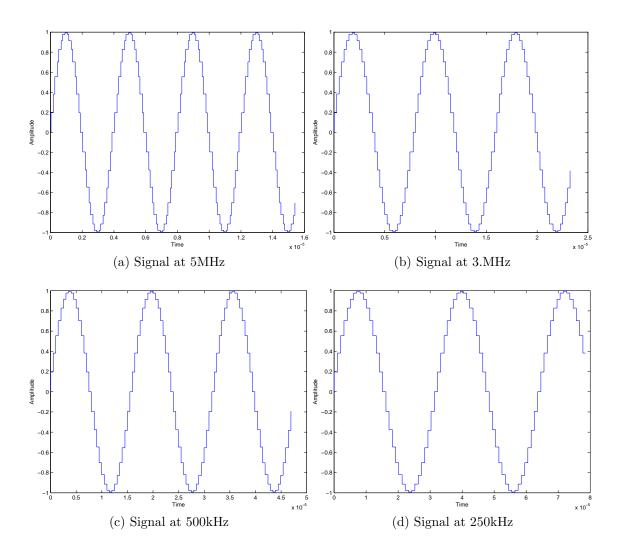

| 5.12 | Obtained signals with DDFS                                                        | 48 |

|------|-----------------------------------------------------------------------------------|----|

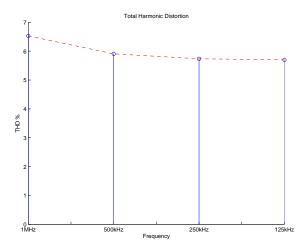

| 5.13 | THD for DDFS waveforms                                                            | 49 |

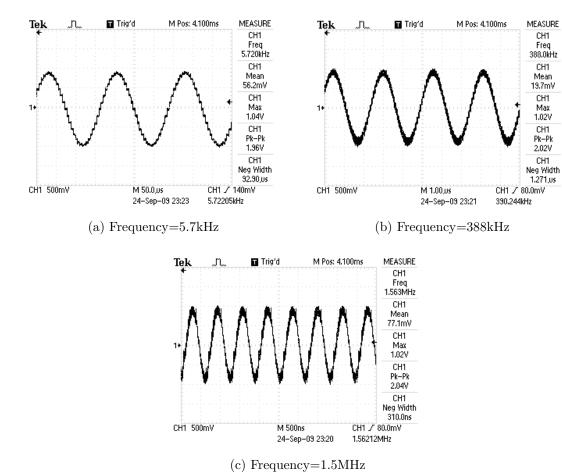

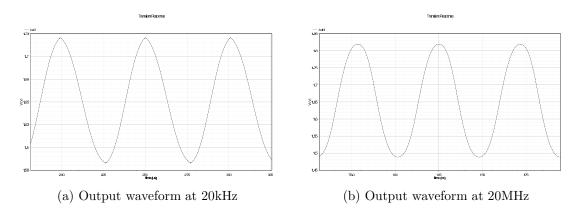

| 5.14 | Oscilloscope waveforms                                                            | 50 |

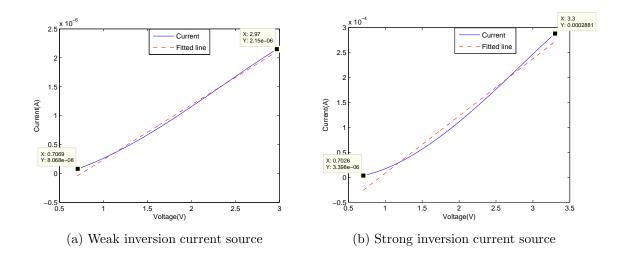

| 5.15 | V vs. I responses of current sources                                              | 53 |

| 5.16 | Change of $gm$ in VCO-OTA alpha oscillator                                        | 53 |

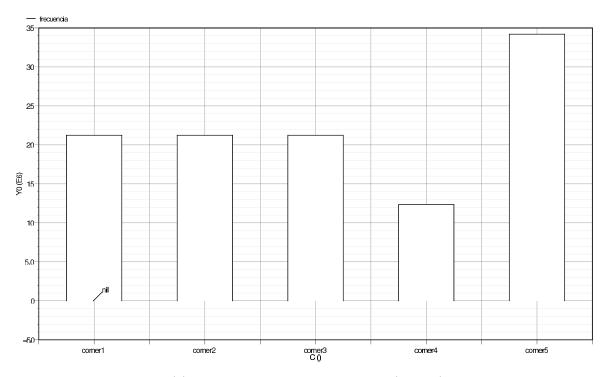

| 5.17 | Designed OTA for VCO-OTA alpha oscillator                                         | 54 |

| 5.18 | Switched capacitors system                                                        | 54 |

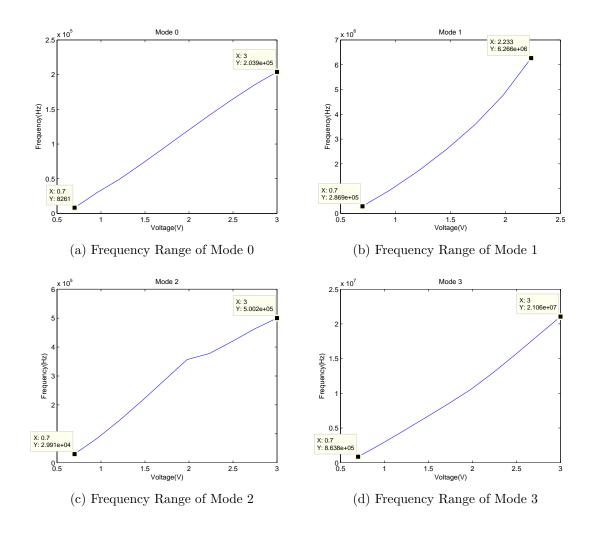

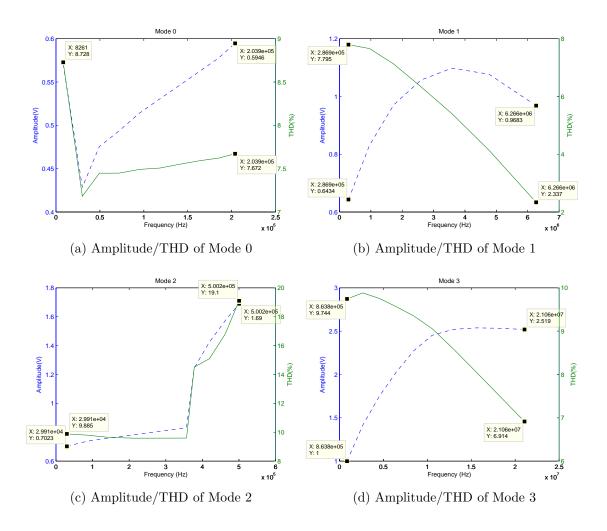

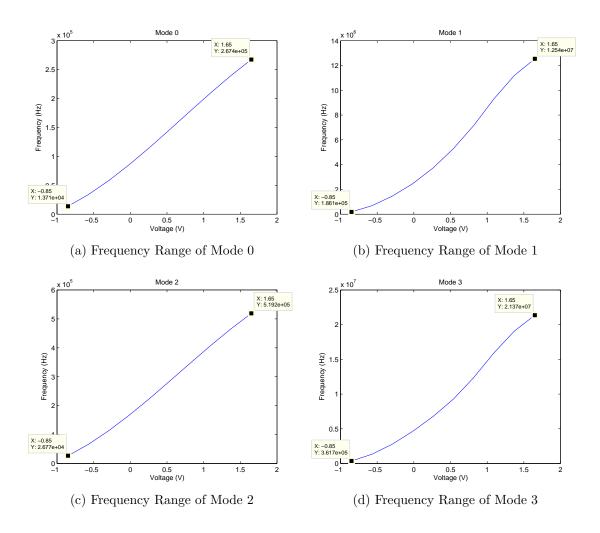

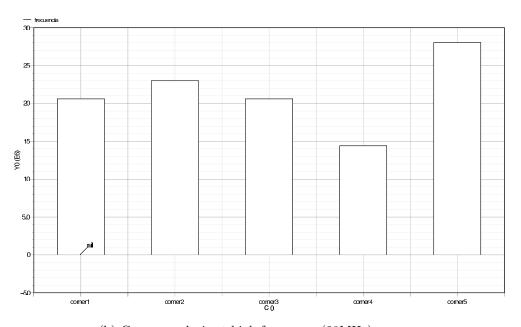

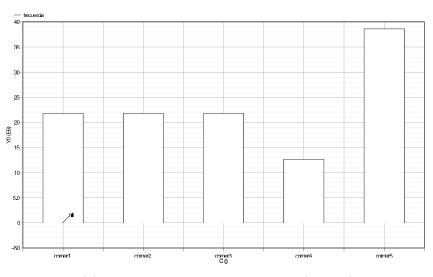

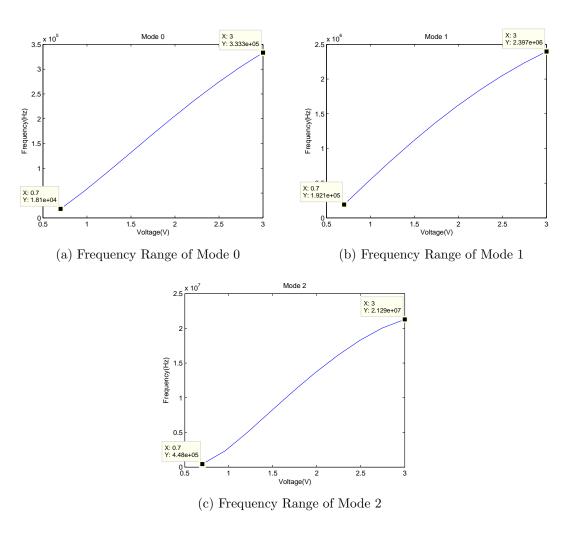

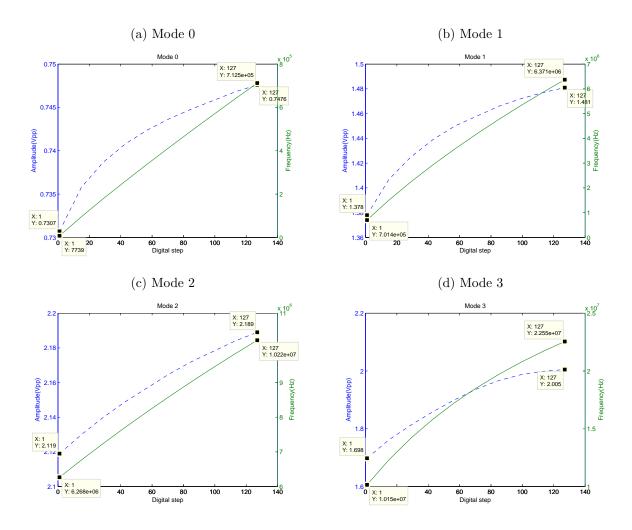

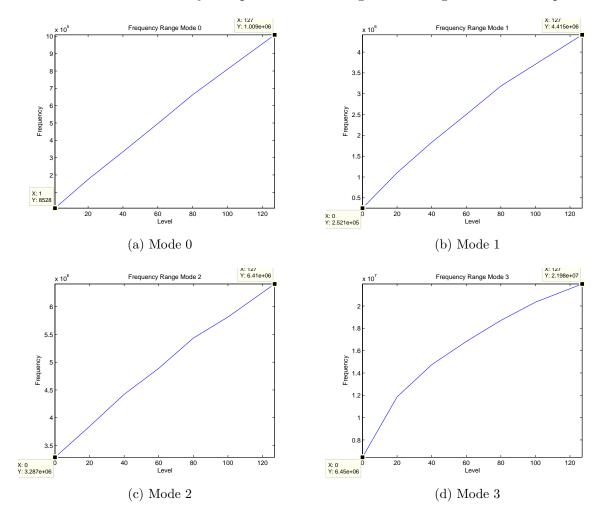

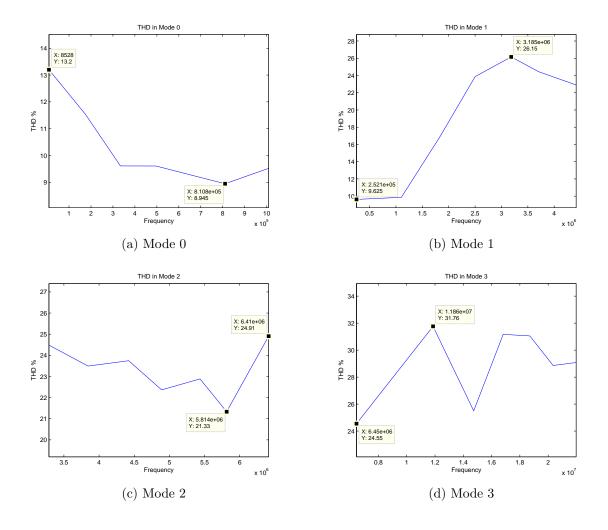

| 5.19 | Frequency ranges for the four operation modes of VCO-OTA-alpha $\ \ \ldots \ \ .$ | 55 |

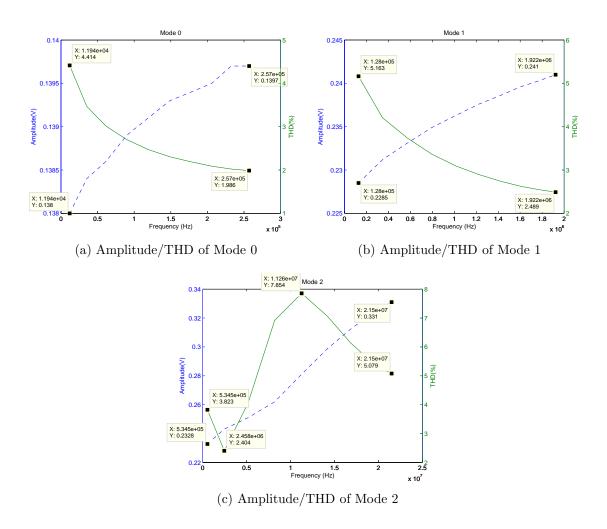

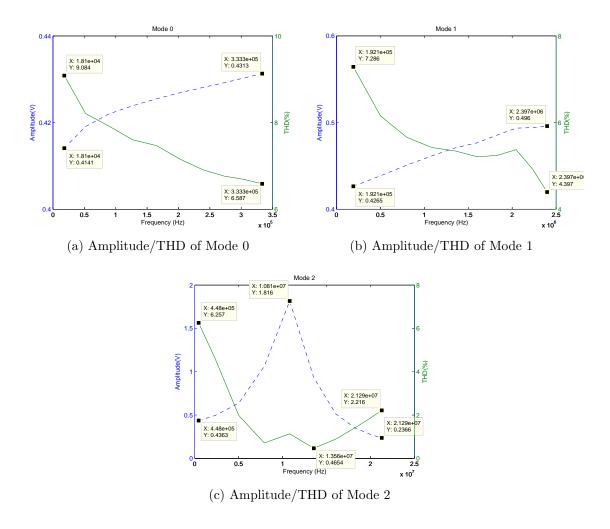

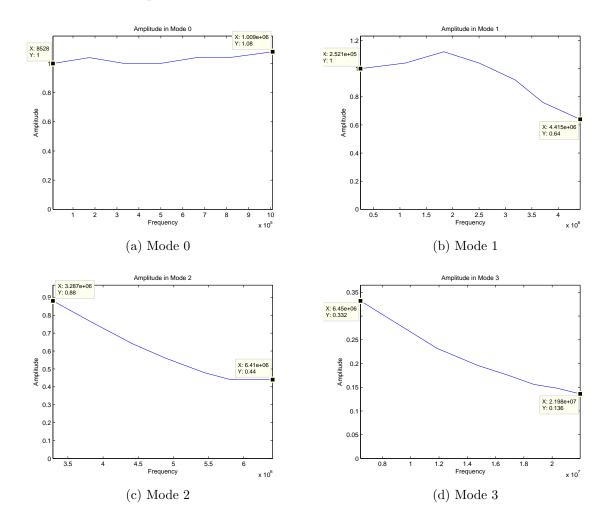

| 5.20 | Output characteristics for each operation mode of VCO-OTA-alpha $\ . \ . \ .$     | 56 |

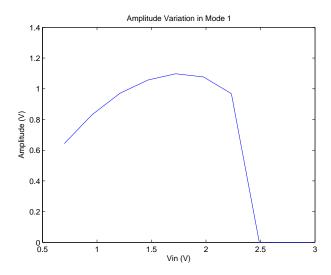

| 5.21 | Variation of amplitude for Mode 1 $\dots$                                         | 57 |

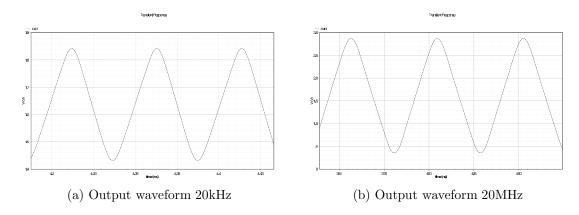

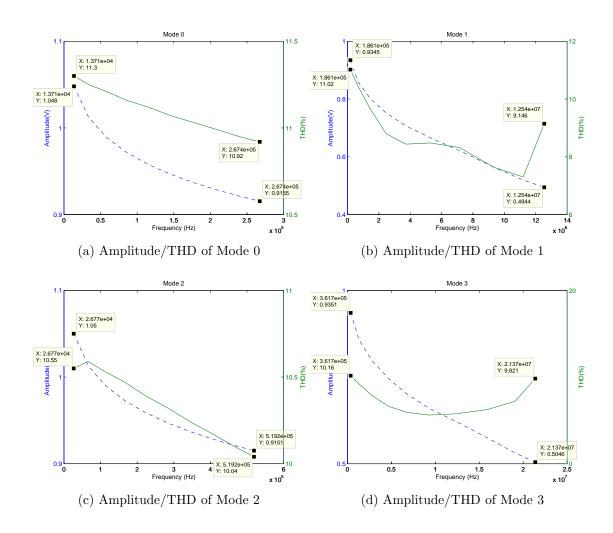

| 5.22 | Output waveforms of VCO-OTA alpha                                                 | 57 |

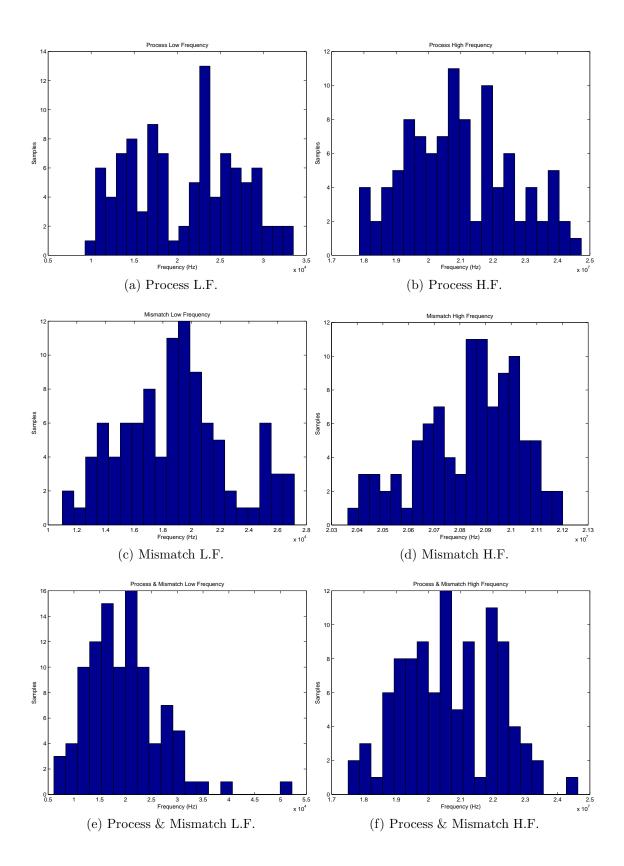

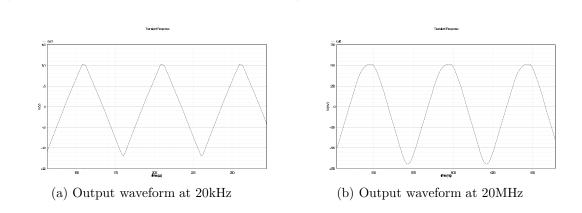

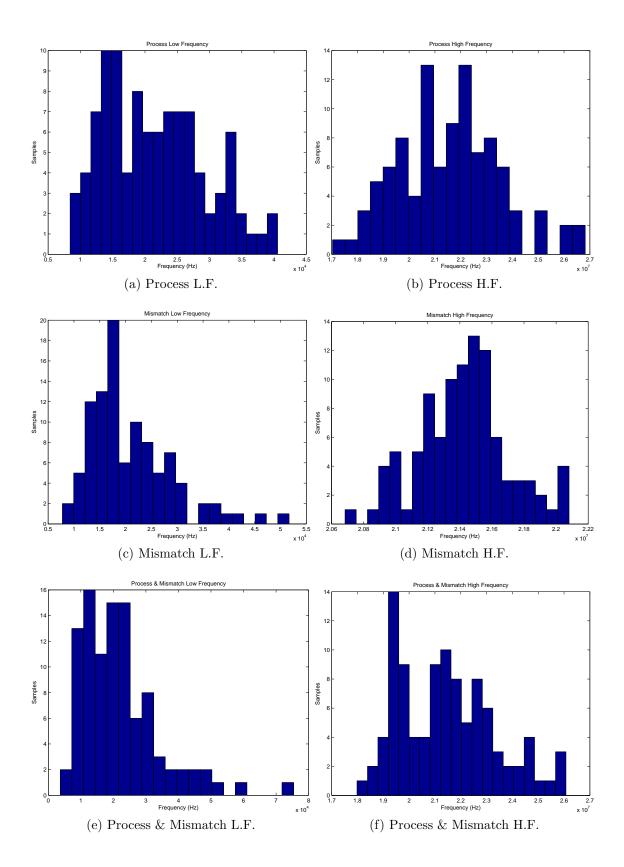

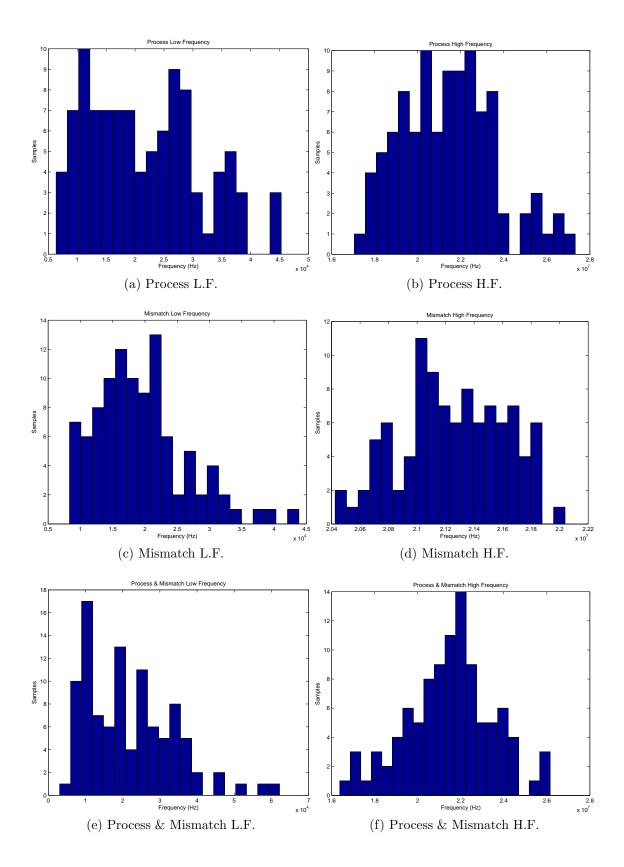

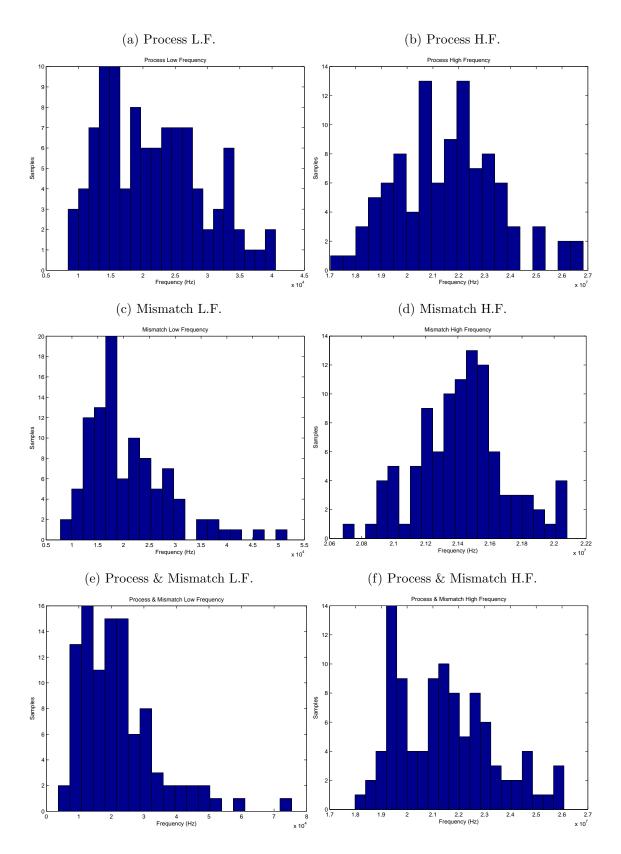

| 5.23 | Monte Carlo Results in Low and High Frequency for VCO-OTA-alpha $$                | 59 |

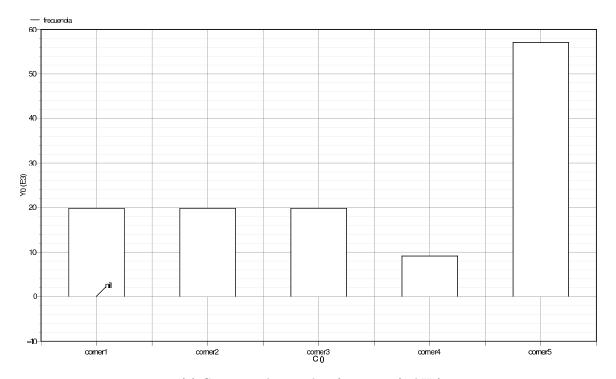

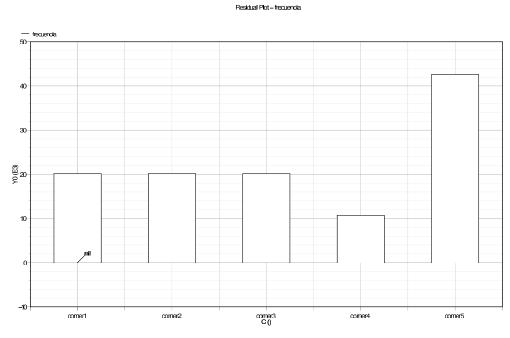

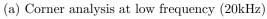

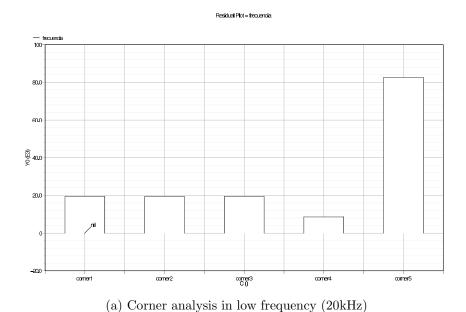

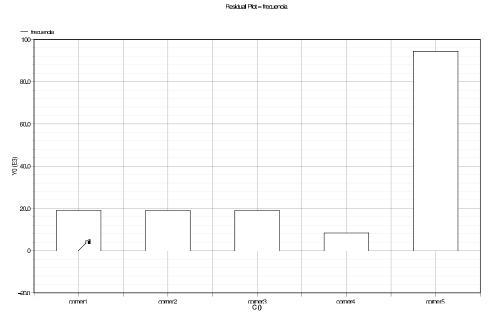

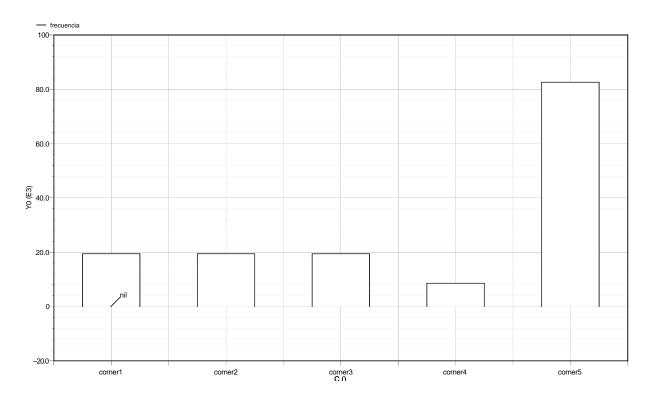

| 5.24 | Corner Analysis results                                                           | 61 |

| 5.25 | Designed OTA for VCO-OTA beta oscillator                                          | 63 |

| 5.26 | Frequency ranges for the four operation modes of VCO-OTA-beta                     | 64 |

| 5.27 | Output characteristics for each operation mode of VCO-OTA beta $\dots$            | 65 |

| 5.28 | Output waveforms of VCO-OTA beta                                                  | 65 |

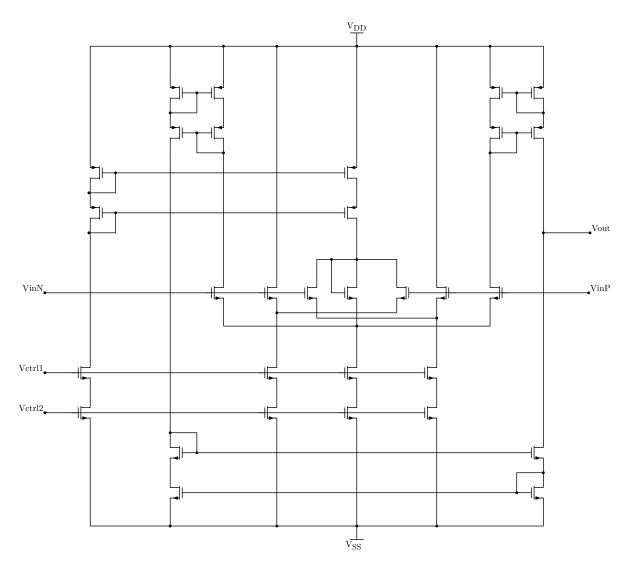

| 5.29 | Monte Carlo Results in Low and High Frequency for VCO-OTA-beta $ \ldots $         | 67 |

| 5.30 | Corner Analysis results for VCO-OTA beta                                          | 69 |

| 5.31 | Frequency ranges for the three operation modes of TSC-SI                          | 71 |

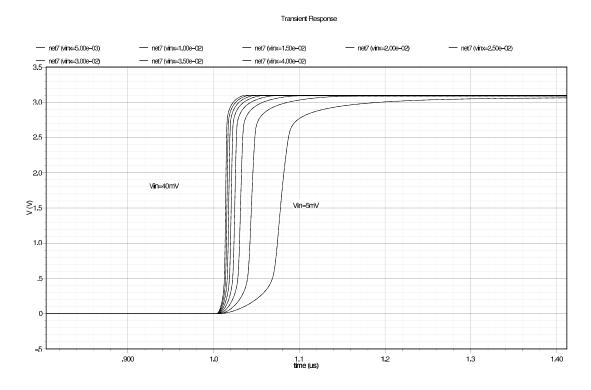

| 5.32 | Output waveforms of VCO TSC-SI                                                    | 72 |

| 5.33 | Output characteristics for each operation mode of TSC-SI                          | 73 |

| 5.34 | Monte Carlo Results in Low and High Frequency for TSC-SI                          | 74 |

| 5.35 | Corner Analysis results for VCO-TSC-SI                                            | 75 |

| 5.36 | Frequency ranges for the three operation modes of TSC-WI $\ldots$ .               | 76 |

| 5.37 | Output characteristics for each operation mode of TSC-WI $\dots$                  | 77 |

| 5.38 | Output waveforms of VCO TSC-WI                                                    | 78 |

| 5.39 | Monte Carlo Results in Low and High Frequency for TSC-WI                          | 79 |

| 5.40 | Corner Analysis results                                                           | 80 |

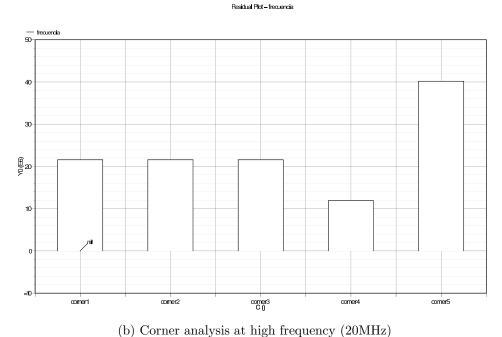

| 6.1  | Block diagram of the VCO                                                          | 83 |

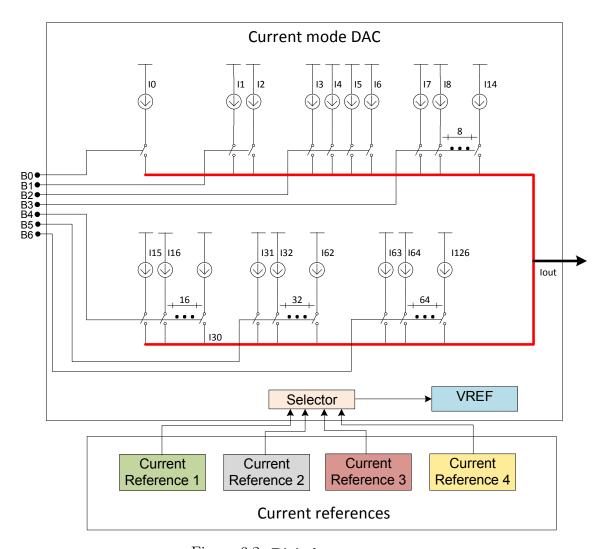

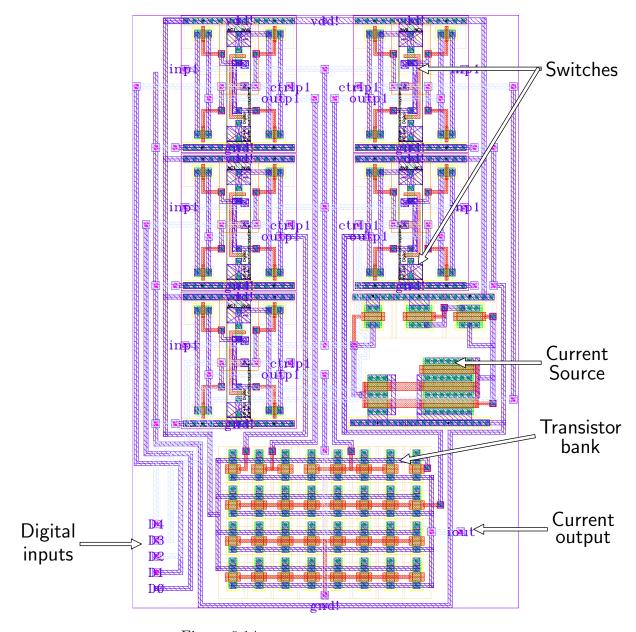

| 6.2  | Digital current source                                                            | 85 |

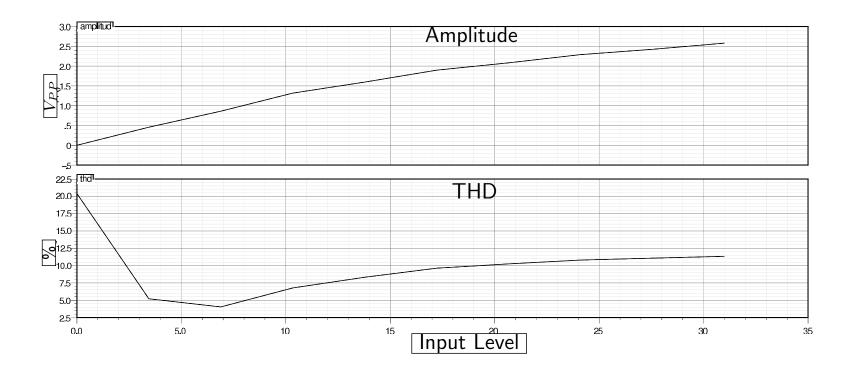

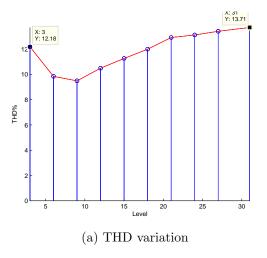

| 6.3  | Frequency ranges and amplitude variations for each operation mode                 | 86 |

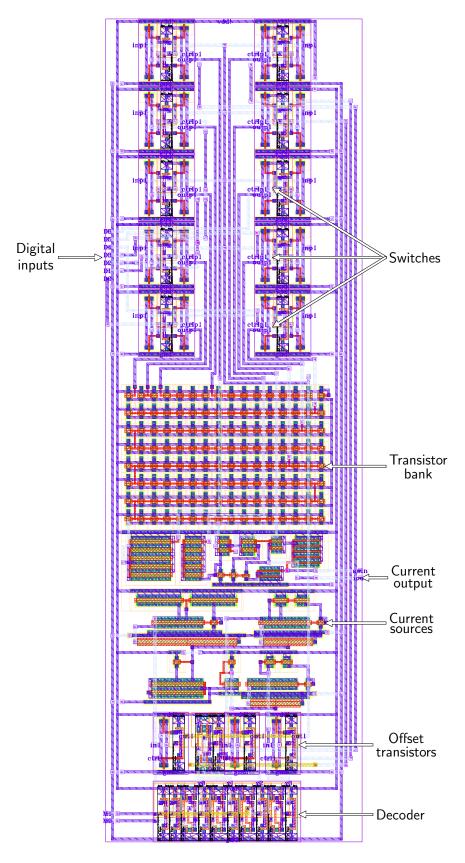

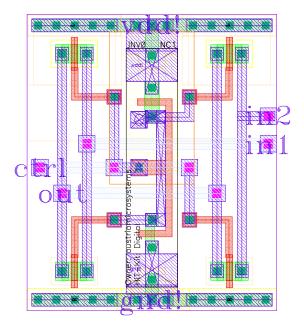

| 0.4  | Layout of the digitally controlled current source                                                                                                                      |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

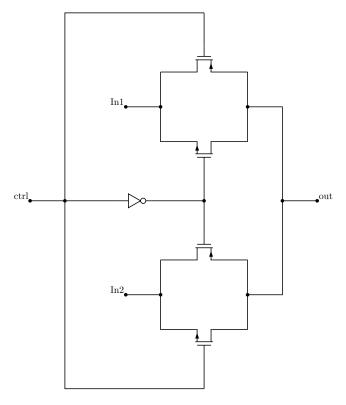

| 6.5  | <b>Dual switch</b>                                                                                                                                                     |

| 6.6  | Layout of the digital switch                                                                                                                                           |

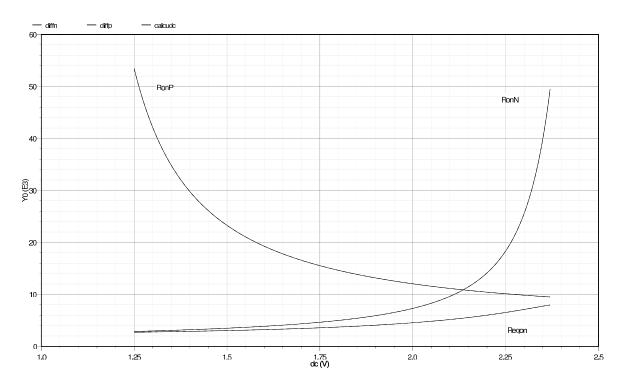

| 6.7  | On-resistance of one CMOS switch                                                                                                                                       |

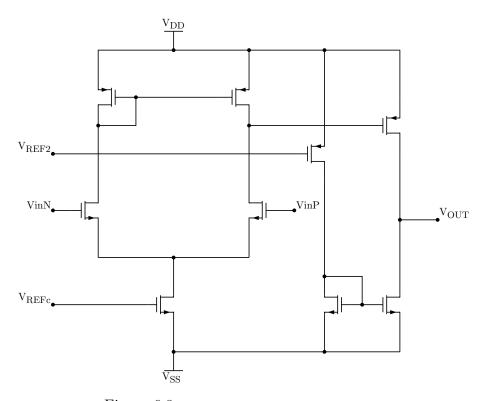

| 6.8  | Electric circuit of comparator                                                                                                                                         |

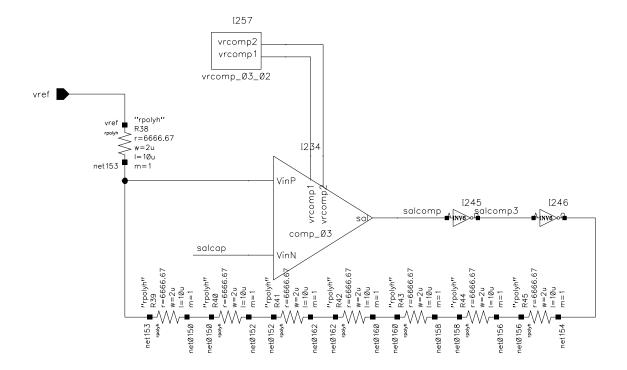

| 6.9  | Comparison module                                                                                                                                                      |

| 6.10 | Delay time in comparator for different input voltages                                                                                                                  |

| 6.11 | Layout of the comparator                                                                                                                                               |

| 6.12 | Differential pair and and THD control current source                                                                                                                   |

| 6.13 | Function of the THD control                                                                                                                                            |

| 6.14 | Layout of the THD control                                                                                                                                              |

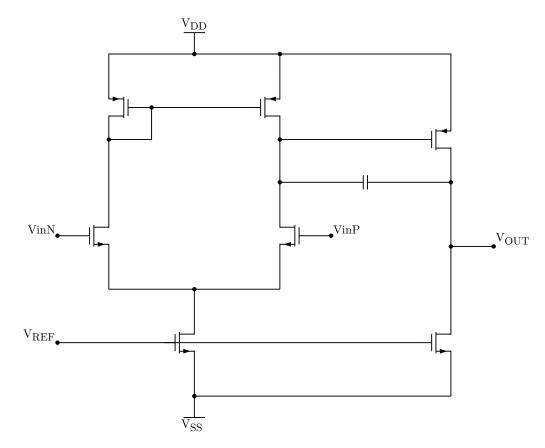

| 6.15 | Circuit of implemented OpAmp                                                                                                                                           |

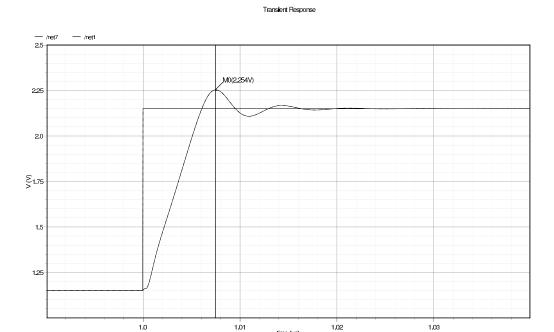

| 6.16 | <b>Step response</b>                                                                                                                                                   |

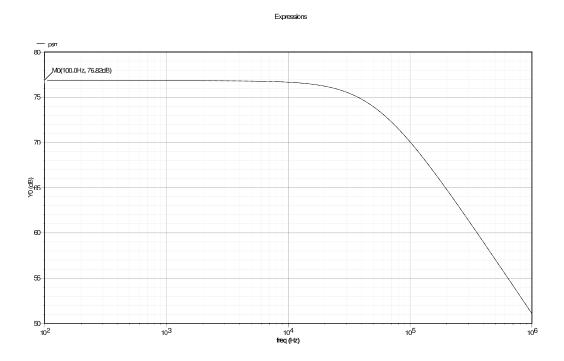

| 6.17 | Power Source Rejection Ratio (PSRR)                                                                                                                                    |

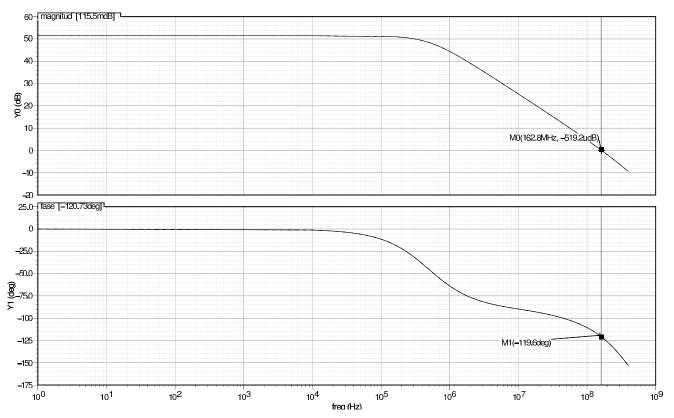

| 6.18 | Bandwidth and Phase                                                                                                                                                    |

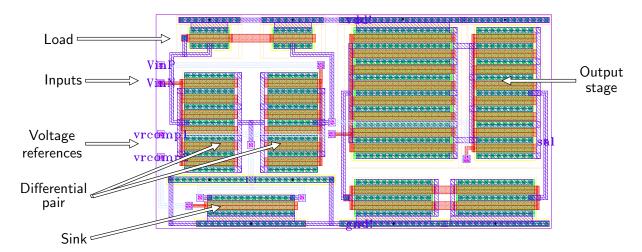

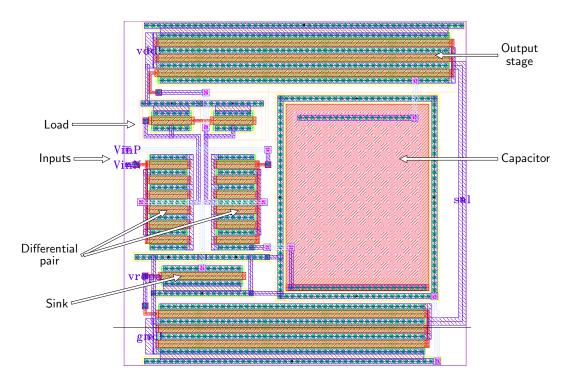

| 6.19 | Layout of the opamp                                                                                                                                                    |

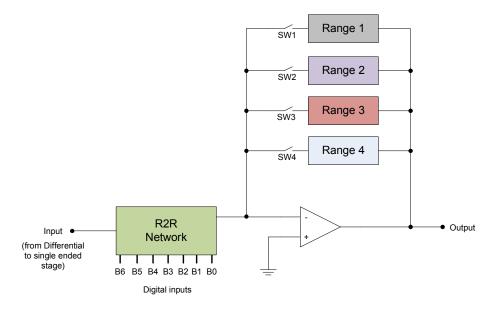

| 6.20 | Block diagram of the digital Gain Control module $\dots \dots \dots$   |

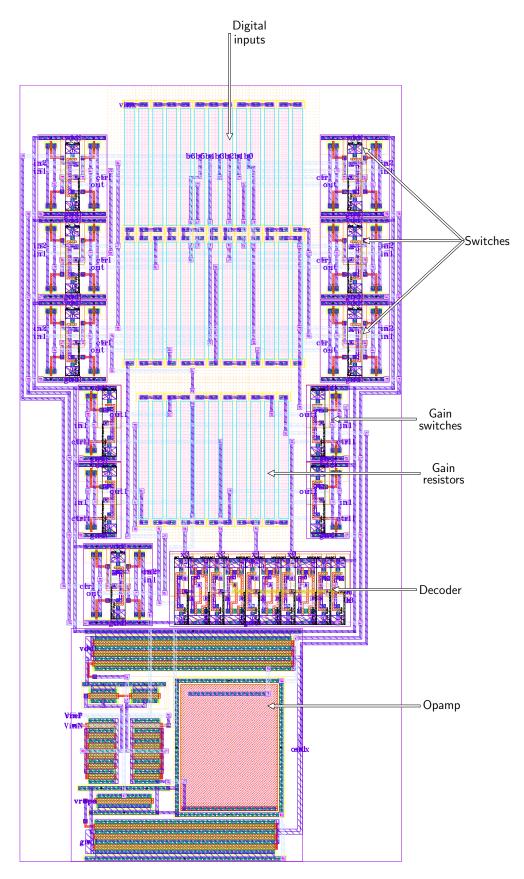

| 6.21 | Layout of the Digital gain control                                                                                                                                     |

| 6.22 | Monte Carlo Results in Low and High Frequency for the final design $\dots$ 106                                                                                         |

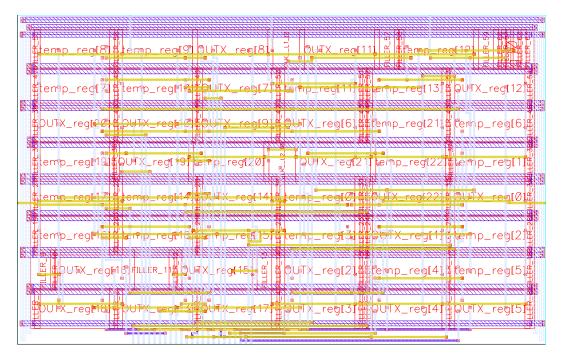

| 6.23 | Corner Analysis results, final design                                                                                                                                  |

| 6.24 | Block diagram of the Digital control interface                                                                                                                         |

| 6.25 | Programming word                                                                                                                                                       |

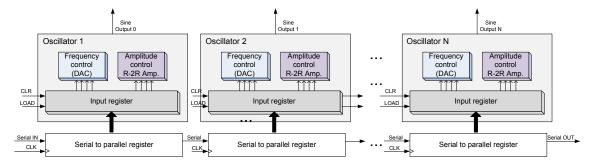

| 6.26 | Generated layout for the digital module                                                                                                                                |

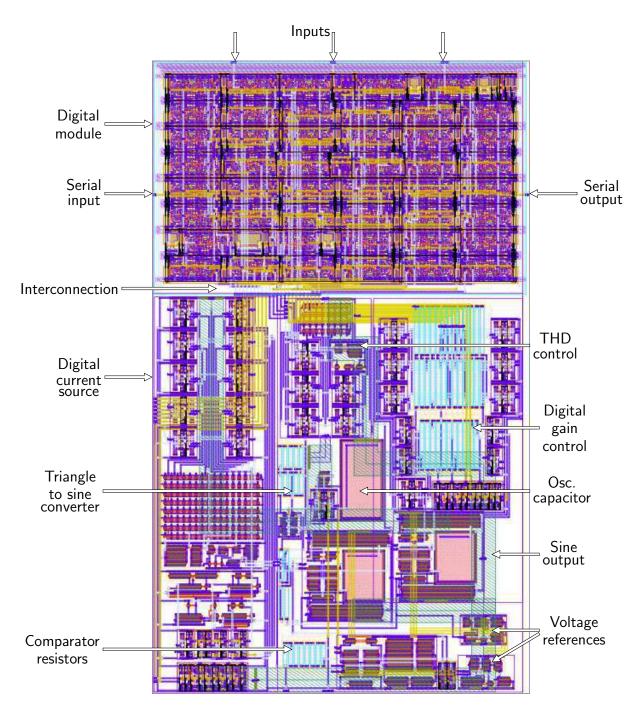

| 6.27 | Layout of the complete VCO                                                                                                                                             |

| 6.28 | Complete layout of the multi-channel sine generator                                                                                                                    |

| 6.29 | Flow diagram for the actions performed by the FPGA $\dots \dots \dots$ |

| 6.30 | Blocks of the interface board                                                                                                                                          |

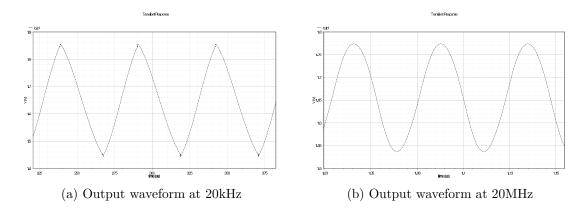

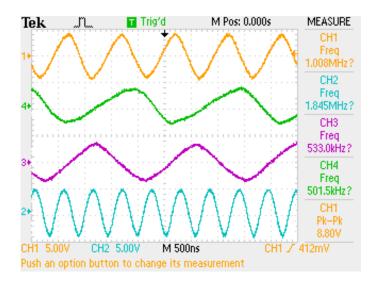

| 6.31 | Obtained waveforms as seen in the oscilloscope                                                                                                                         |

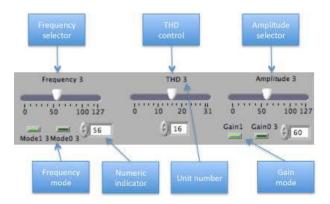

| 6.32 | Configuration module for one oscillator unit                                                                                                                           |

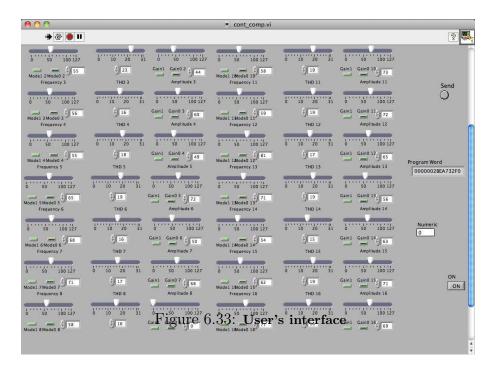

| 6.33 | User's interface                                                                                                                                                       |

| 7.1  | Measured frequency ranges                                                                                                                                              |

| 7.2  | Measured amplitude for each frequency range                                                                                                                            |

| 7.3  | Measured THD for each frequency range                                         |

|------|-------------------------------------------------------------------------------|

| 7.4  | Variations of TDH and signal's amplitude applying the THD control $$ $121$    |

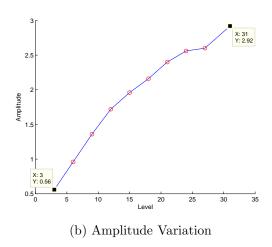

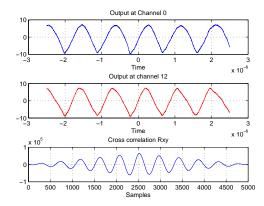

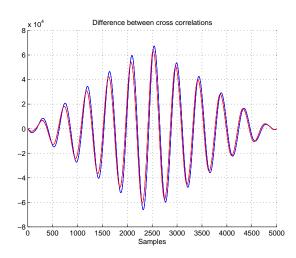

| 7.5  | Cross-correlation between channels                                            |

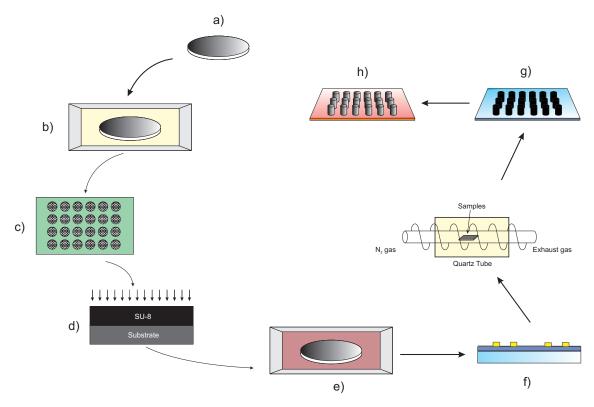

| 7.6  | SU-8 for C-MEMS                                                               |

| 7.7  | Electrodes inside the microchannel                                            |

| 7.8  | Microfluidic device                                                           |

| 7.9  | Preliminary steps                                                             |

| 7.10 | Experimental set-up                                                           |

| 7.11 | Real part of CM factor for both Live yeasts and Polystyrene beads $\dots$ 128 |

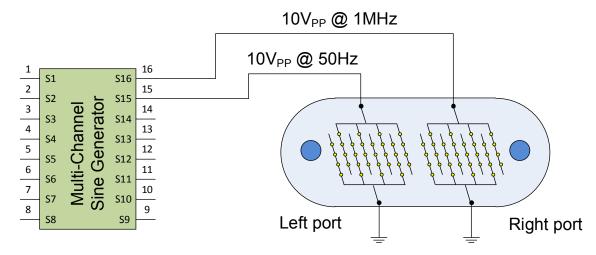

| 7.12 | Connections between Stimulator and microfluidic chip                          |

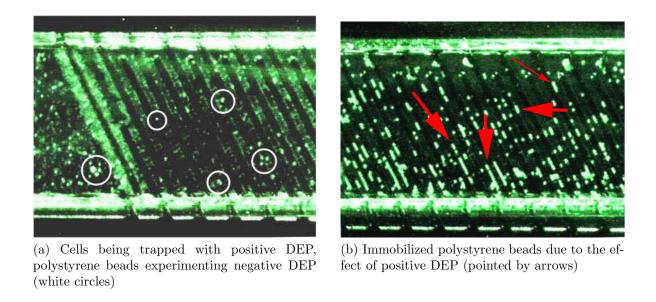

| 7.13 | Evoked DEP effects in microchannel                                            |

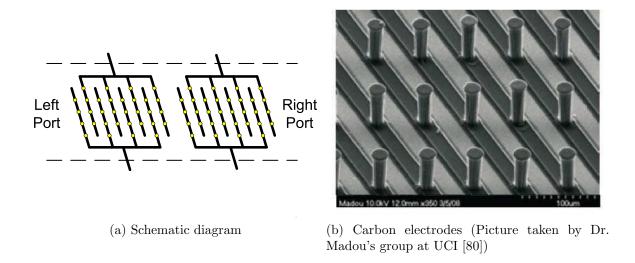

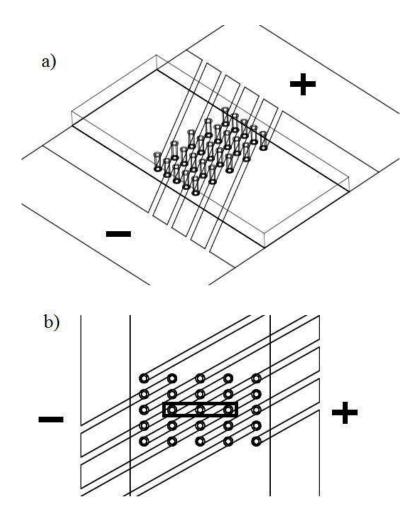

| 7.14 | Representation of embedded carbon electrodes                                  |

| 7.15 | Behavior of cells under DEP                                                   |

| 7.16 | Second experimental set                                                       |

| 7.17 | Dielectrophoretic effects observed in the microfluidic device                 |

| 7.18 | Zoomed view of positive DEP behavior                                          |

## List of Tables

| 2.1  | Summary of advances in Electrokinetic-driven devices                                                         | Ć   |

|------|--------------------------------------------------------------------------------------------------------------|-----|

| 3.1  | THD values for expressions 3.15 and 3.16                                                                     | 17  |

| 5.1  | Different K-values and their frequencies, 12-bits system                                                     | 43  |

| 5.3  | $ \label{lem:lementation} \textbf{Implementation and physical synthesis, Unstable Delta Dirac Algorithm}  .$ | 44  |

| 5.2  | Different $K$ -values and their frequencies, 8-bits system                                                   | 46  |

| 5.4  | Implementation and physical synthesis for the DDS Algorithm                                                  | 49  |

| 5.5  | Limits for Corner Analysis                                                                                   | 52  |

| 5.6  | Operation modes for VCO-OTA alpha                                                                            | 53  |

| 5.7  | Monte Carlo Results for Low and High Frequencies of VCO-OTA alpha                                            | 58  |

| 5.8  | Operation modes for VCO-OTA beta                                                                             | 62  |

| 5.9  | Monte Carlo Results for Low and High Frequencies of VCO-OTA beta $$ . $$                                     | 66  |

| 5.10 | Operation modes for TSC-SI                                                                                   | 71  |

| 5.11 | Monte Carlo Results for Low and High Frequencies of TSC-SI                                                   | 72  |

| 5.12 | Operation modes for TSC-WI                                                                                   | 76  |

| 5.13 | Monte Carlo Results for Low and High Frequencies of TSC-WI $\dots$                                           | 78  |

| 5.14 | Summary of reports for the analog oscillators                                                                | 81  |

| 5.15 | Comparison table of analog prototypes                                                                        | 82  |

| 6.1  | Characteristics of the digital current source                                                                | 84  |

| 6.2  | Characteristics of the digital current source (cont)                                                         | 84  |

| 6.3  | Electrical characteristics of comparator                                                                     | 92  |

| 6.4  | Delay time of comparator                                                                                     | 93  |

| 6.5  | Electrical characteristics of OpAmp                                                                          | 98  |

| 6.6  | Electrical characteristics of the Digital Gain Control                                                       | 103 |

| 6.7  | Monte Carlo Results for the final implementation                                                             | 105 |

7.1 Theoretical and measured frequency ranges of the multi-channel oscillator 118

## Contents

| A      | bstra | ct      |                                                                                  | 9  |

|--------|-------|---------|----------------------------------------------------------------------------------|----|

| Li     | st of | Figur   | es                                                                               | 14 |

| Li     | st of | Table   | S                                                                                | 16 |

| 1 Intr |       | oduct   | ion                                                                              | 1  |

|        | 1.1   | Lab C   | n a Chip concept                                                                 | 1  |

|        | 1.2   | Micro   | fluidics                                                                         | 3  |

|        | 1.3   | Justifi | cation                                                                           | 4  |

|        | 1.4   | Thesis  | organization                                                                     | 4  |

| 2      | Sta   | te of t | he art in stimulation systems for electrokinetically-driven microfluidic devices | 5  |

| 3      | The   | eoretic | al Background on Analog and Digital Oscillators                                  | 11 |

|        | 3.1   | Digita  | l approach                                                                       | 11 |

|        |       | 3.1.1   | Delta Dirac Unstable Oscillator (DDUO)                                           | 12 |

|        |       | 3.1.2   | Direct Digital Frequency Synthesis (DDFS)                                        | 14 |

|        |       | 3.1.3   | Total Harmonic Distortion (THD)                                                  | 16 |

|        | 3.2   | Analo   | g Approach                                                                       | 17 |

|        |       | 3.2.1   | OTA-C                                                                            | 18 |

|        | 3.3   | Triang  | gle to Sine Converters                                                           | 20 |

|        |       | 3.3.1   | Relaxation oscillator                                                            | 20 |

|        |       | 3.3.2   | Triangle to Sine Converter in strong inversion (TSC-SI)                          | 21 |

|        |       | 3.3.3   | Triangle to Sine Converter in weak inversion (TSC-WI)                            | 24 |

| 4      | The   | eoretic | al Background on Electrokinetic Phenomena                                        | 27 |

|        | 4.1   | Electr  | okinetic Forces                                                                  | 27 |

|        | 4.2   | Mover   | nent of charged particles in an insulating fluid                                 | 27 |

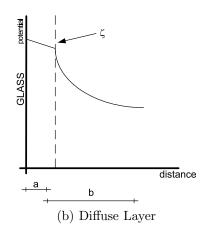

|        | 4.3   | The el  | ectrical double layer                                                            | 28 |

|        | 4.4   | Electr  | o-osmosis                                                                        | 29 |

|        | 4.5   | Electr  | ophoresis                                                                        | 30 |

|        |       | 4.5.1   | Capillary electrophoresis CE                                                     | 30 |

|        |       | 4.5.2   | Gel Electrophoresis                                                              | 30 |

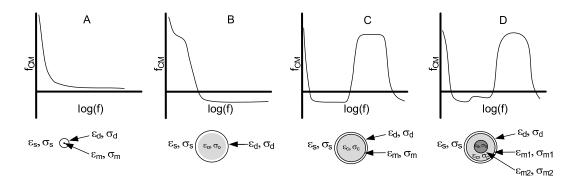

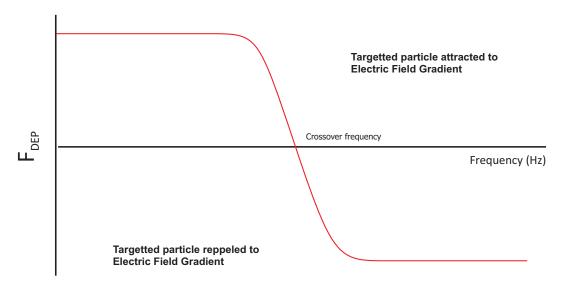

|        | 4.6   | Dielec  | trophoresis                                                                      | 31 |

|        |       | 461     | Electrode-based DEP                                                              | 34 |

|   |      | 4.6.2   | iDEP                                                                                              | 36  |

|---|------|---------|---------------------------------------------------------------------------------------------------|-----|

| 5 | Con  | npariso | on of Oscillator Approaches                                                                       | 37  |

|   | 5.1  | Solutio | on model                                                                                          | 37  |

|   | 5.2  | Digita  | solution evaluation                                                                               | 40  |

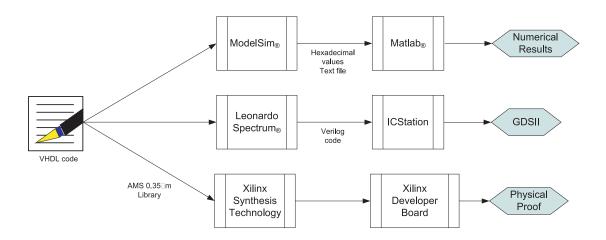

|   |      | 5.2.1   | Analysis of the Delta Dirac Unstable Oscillator (DDUO)                                            | 42  |

|   |      |         | 5.2.1.1 Remarks on the DDUO analysis                                                              | 44  |

|   |      | 5.2.2   | Analysis of the Direct Digital Frequency Synthesis algorithm $\ldots \ldots \ldots \ldots \ldots$ | 47  |

|   |      |         | 5.2.2.1 Remarks on the DDFS analysis                                                              | 48  |

|   | 5.3  | Analog  | g Solutions Evaluation                                                                            | 51  |

|   |      | 5.3.1   | Selection criteria                                                                                | 51  |

|   |      | 5.3.2   | VCO-OTA alpha                                                                                     | 52  |

|   |      |         | 5.3.2.1 Results                                                                                   | 55  |

|   |      | 5.3.3   | VCO-OTA beta                                                                                      | 62  |

|   |      |         | 5.3.3.1 Results                                                                                   | 62  |

|   |      | 5.3.4   | Triangle to Sine Converter                                                                        | 70  |

|   |      |         | 5.3.4.1 Relaxation oscillator                                                                     | 70  |

|   |      |         | 5.3.4.2 THD control                                                                               | 70  |

|   |      |         | 5.3.4.3 Triangle to sine converter in Strong Inversion (TSC-SI)                                   | 70  |

|   |      |         | 5.3.4.4 Results                                                                                   | 72  |

|   |      |         | 5.3.4.5 Triangle to Sine Converter in Weak Inversion (TSC-WI)                                     | 76  |

|   |      |         | 5.3.4.6 Results                                                                                   | 78  |

|   |      | 5.3.5   | Final results of the analog models                                                                | 81  |

|   | 5.4  | Conclu  | ısion                                                                                             | 82  |

| _ | _    |         |                                                                                                   |     |

| 6 | -    |         | tation of the Multiple-channel Stimulator on a 0.35µm CMOS Technology                             | 83  |

|   | 6.1  | _       |                                                                                                   | 84  |

|   | 6.2  | _       |                                                                                                   | 89  |

|   | 6.3  | •       |                                                                                                   | 91  |

|   | 6.4  |         | Control                                                                                           | 95  |

|   | 6.5  |         | •                                                                                                 | 98  |

|   | 6.6  | Ü       | l Gain Control                                                                                    |     |

|   | 6.7  |         | tion results                                                                                      | .05 |

|   | 6.8  |         |                                                                                                   | 108 |

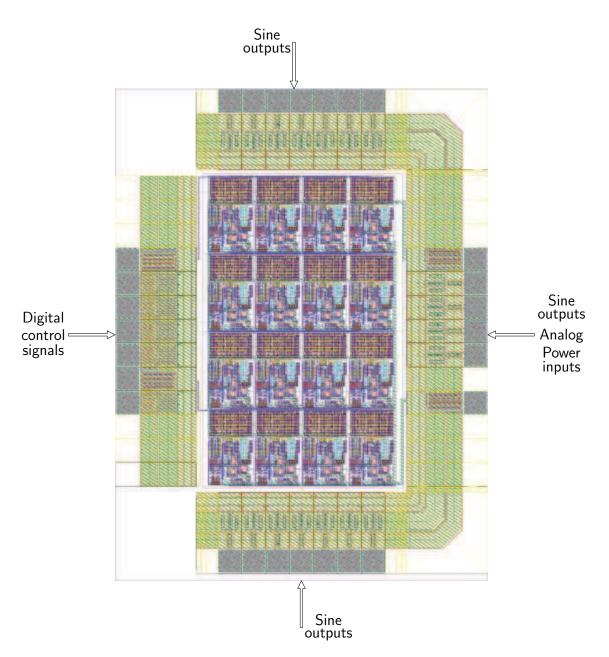

|   | 6.9  | Integra | ation of the complete system                                                                      | .11 |

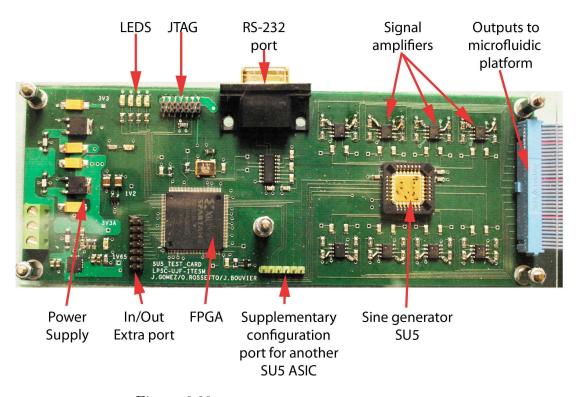

|   | 6.10 | Interfa | ce Card                                                                                           | 13  |

|   |      | 6.10.1  | Power supply                                                                                      | .13 |

|   |      | 6.10.2  | Digital stage                                                                                     | 13  |

|   |      | 6.10.3  | Analog output stage                                                                               | .14 |

|   | 6.11 | Graph   | ic Interface                                                                                      | .15 |

|   | 6.12 | Conclu  | sion on the implementation                                                                        | .16 |

| 7 | Elec | trical  | Testing of the Stimulator and its Evaluation in Particle Separation 1                             | 17  |

|   | 7.1  | Electri | c characterization                                                                                | 117 |

|   |     | 7.1.1  | Frequen    | cy range                         | . 117 |

|---|-----|--------|------------|----------------------------------|-------|

|   |     |        | 7.1.1.1    | Bandwidth                        | . 119 |

|   |     | 7.1.2  | THD m      | easurement                       | . 120 |

|   |     | 7.1.3  | Noise      |                                  | . 121 |

|   | 7.2 | Micro  | fluidic Ex | experiments                      | . 123 |

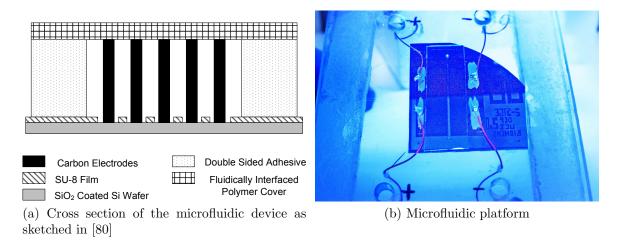

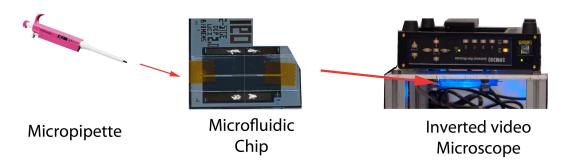

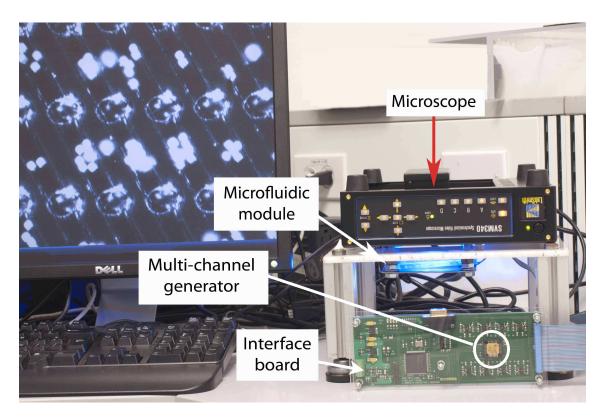

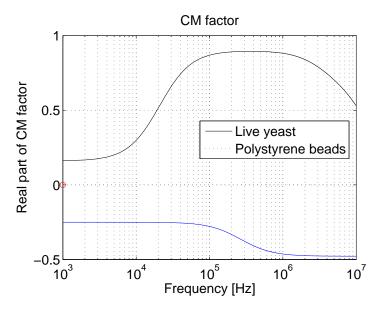

|   |     | 7.2.1  | Microflu   | ıidic device                     | . 123 |

|   |     | 7.2.2  | Experim    | nent I                           | . 126 |

|   |     |        | 7.2.2.1    | Materials and methods            | . 126 |

|   |     |        | 7.2.2.2    | Experimental results             | . 128 |

|   |     |        | 7.2.2.3    | Conclusions on the experiment I  | . 128 |

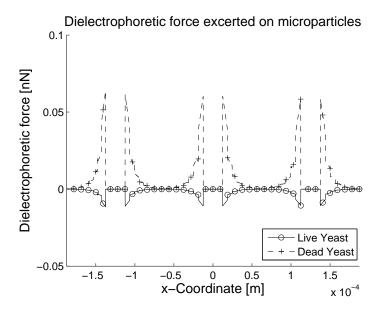

|   |     | 7.2.3  | Experim    | nent II                          | . 129 |

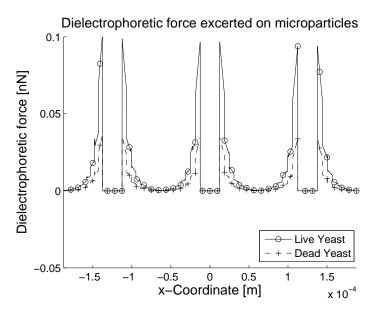

|   |     |        | 7.2.3.1    | Computational Modeling           | . 129 |

|   |     |        | 7.2.3.2    | Materials and methods            | . 133 |

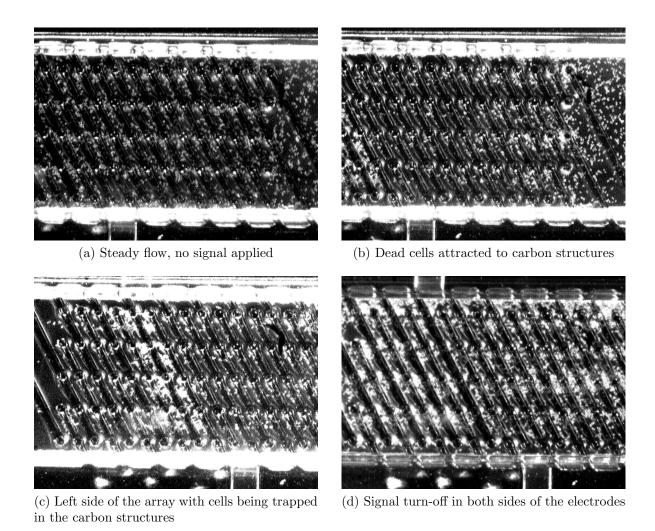

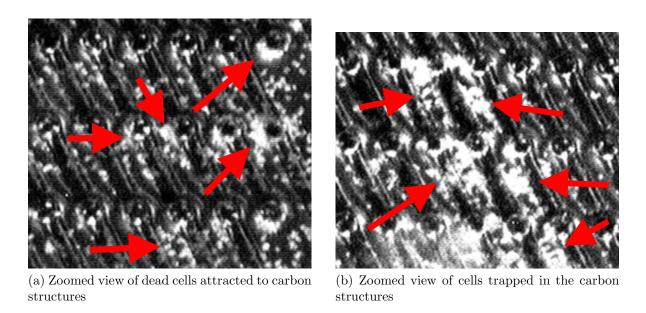

|   |     |        | 7.2.3.3    | Results                          | . 133 |

|   |     |        | 7.2.3.4    | Conclusions on the experiment II | . 135 |

| 8 | Cor | clusio | ns         |                                  | 137   |

| - | Q 1 | Future | n work     |                                  | 122   |

## Chapter 1

## Introduction

## 1.1 Lab On a Chip concept

In recent years we have seen an entire new generation of devices aiming to perform bio/chemical analysis at microscale: the concept of a Lab-on-a-chip (LOC). Advances of micro and nano devices have been reported in applications like biosensors, micro-actuators, micro-fluidics, micro-valves, micro-pumps, intelligent surgical tools, therapeutic systems and MEMS for biomolecular recognition [3].

The ultimate goal of miniaturized devices who interact with biological molecules is to transport, mix, detect and characterize a raw sample. Among the fundamental attributes of a LOC are:

- To have smaller sample volumes.

- To reduce the number of sample handling steps.

- In certain processes, to reduce the sample size leads to a reduction in the processing time or preparation of the sample.

- To decrease the human involvement in the processing of complex protocols.

- To allow the development of portable systems.

The lab on a chip or Micro-Total analysis systems (µTAS) [4] require miniaturized devices such as separators and bioreactors which cover an abundant field of study including air and water quality analyzers, medical diagnostics, DNA amplification, protein labeling etc.

One of the most promising applications of LOC's is clinical diagnostics. The LOC's with capability to deal with live cells which integrate mechanical, optical and electronic components are are known as BioMEMS. The main objective in clinical diagnostic BioMEMS devices is to develop devices capable to provide a rapid analysis of organic samples offering reliable results.

BioMEMS devices should posses the following characteristics:

**Small.** The size reduction gives freedom of action, avoiding the confinement of physician and/or patient to medical facilities.

**Fast.** One of the main goals is to have accurate results as soon as possible.

**Disposable.** At least the contact region with the organic samples should be easily disposable, avoiding bio-contamination.

**Inexpensive.** Even when we are talking about state of the art systems, their cost should not represent a major issue.

Mass production. The production process must assume that a considerable amount of devices reach the market in a short period of time.

**Integration.** The chip must be a collection of mechanic, electronic, optic systems capable of offering the complete diagnosis without the need of extra components.

Nowadays LOC devices have already been commercialized accomplishing a small number of functions, very often they require supplementary support equipment such as computers, microscopes, signal generators etc. For example, to detect three myocardial proteins produced in abnormal quantities once a hearth attack has taken place, Biosite presented a solution (Biosite chip)[5] allowing the portability and rapidity of results (15 mins while traditional systems need hours). The results of the analysis are given in a small diagnostic device (Figure 1.1a).

Another good example is the DNA LabChip of Agilent[6] capable of perform genotyping (the identification of an object from characteristics sequences of genes). This chip can also identify RNA and proteins although a fully integrated and miniaturized system is not available yet. The device must be used along with the Agilent 2100 Bioanalyzer to deliver results (Figure 1.1b).

The next step in LOC's evolution is their integration with intelligent systems. Even though several appliances perform several automatic tasks. In the near future LOC's will require essays of greater technical complexity integrating disposable microelectronic and microfluidic components, and also to be programmable, reconfigurable and reusable. In many ways, the LOC's are natural fit for a point-of-care (POC) diagnostics device<sup>1</sup>. The rapid POC testing could lead to fast intervention and its market is estimated to be over \$10 billion with important growth in cardiac and infectious diseases. POC diagnostic systems need to be simple devices with minimal or no ancillary equipment. Hence the need to provide intelligence to LOC instruments.

<sup>&</sup>lt;sup>1</sup>A diagnostic test performed near the patient without the need of a clinical lab [7]

(a) **Biosite chip.** A droplet of blood is placed in a special platform on the chip, the results of the analysis are given on an special appliance in just 15 mins. The diagnostic can determine whether or not a hearth attack has taken place.

(b) **Agilent.** This device permits the identification of specific genetic sequences, the process takes 10 mins and the results are given in a microcomputer.

Figure 1.1: Examples of Lab-on-a-chip devices.

#### 1.2 Microfluidics

In the 1990's MEMS and miniaturization opened the door to a new discipline: Microfluidics. Microfluidics can be defined as the study of flows that are simple or complex, mono or multi phasic, which are circulating in artificial microsystems [8]. The advantages of miniaturization allowed that many different microfluidic systems were fabricated, from electrophoretic separation systems to electro-osmotic pumping systems, micromixers, DNA amplifiers, cytometers and chemical microrreactors.

Microfluidics constitutes the real core of most labs-on-a-chip and has enabled the generation of new commercially successful products ranging from portable insulin delivery devices to high speed inkjet printers. Also, microfluidics represents the platform that has catapulted  $\mu TAS$  to be considered as one of the most promising research technologies for biology, chemistry and bioengineering.

Electrokinetics (EK) is rapidly gaining preferences as a microfluidic actuation mechanism, due to the fact that in many ways EK devices offer advantages over pumps and actuators with valves, gears and mechanical elements involving moving parts. EK induces micro-fluid or particle movements within a microchannel driven by an electric field. Moreover, using microdevices allows the generation of large electric field gradients using few volts to polarize closely-spaced electrodes.

#### 1.3 Justification

LOC platforms still have a long way to go for increasing speed and throughput in the delivery of results to allow practical implementations in health care institutions. The vast majority of current microfluidic platforms take use of conventional signal generator, such instruments must be stacked when more than one signal is desired. The broader impact of LOC's will come to the scene with the arrival of low power, small, cheap devices capable of offering cell/particle manipulation used in portable systems.

The objective of this research work is to design, fabricate and implement a device capable of generating a large number of independent sine signals with amplitude, frequency and THD (Total Harmonic Distortion) control at each port (output). The use of this microelectronic system will help in electrokinetic tasks providing of multiple independent signals without the need of further equipment. The fact of having multiple stimulation ports offers the possibility of the implementation of a wide range of protocols for particle separation and characterization. The device will be programmable via a serial port and will be fabricated in a standard CMOS 0.35µm process having specifications such as low power and small on-chip area to be included in a portable platform.

## 1.4 Thesis organization

Chapter 2 reviews the state of the art in devices for separation of particles. Chapter 3 examines the theoretical frame of digital and analog oscillator. While Chapter 4 reviews the corresponding electrokinetic theory. The design of the device as well as the analysis of the digital and analog prototypes and the evaluation that led us to choose the final prototype are discussed in Chapter 5. The implementation of the prototype and the details of the integrated circuit and its electric characteristics are reviewed in Chapter 6. Chapter 7 reviews the results obtained from the measurements to the outputs of the device and the outcome of an experiment of particle separation in which our integrated circuit delivered the required stimulation signals. Chapter 8 describes the conclusions of this dissertation project.

## Chapter 2

# State of the art in stimulation systems for electrokinetically-driven microfluidic devices

The use of electric fields to achieve transport, separation and analysis in microfluidic devices has been demonstrated in many applications. This chapter reviews the state of the art on devices that perform electrokinetic tasks making use of multiple excitation stimulus or perform manipulation of frequency and/or amplitude in their output signals.

Woolley et al.[9] demonstrated that high-speed DNA separations can be performed on microfabricated capillary electrophoresis (CE) channels arrays, establishing the feasibility of integrated devices for electrophoretic DNA analysis. In a later design[10], they improve the speed and throughput allowing analysis of 12 parallel samples in less than 160s. The first stage of the process is the injection phase performed by applying +80V. Immediately following injection, the separation phase was carried out by applying +1200V.

Wang et al.[11] demonstrated the manipulation of living cells including isolation, concentration of cells, trapping and positioning, levitation, linear motion and circulation of individual cells for characterization using dielectrophoresis. They used Friend murine erythroleukemia DS19 cells. Voltage signals between 1kHz and 100MHz were used and the cell levitation appeared at frequencies below 120kHz. The levitation height was found to depend on the frequency and magnitude of the applied voltages. The maximum levitation was 26µm at frequencies 1-60 kHz with an applied voltage of 1.75V. The cells exhibited antifield and cofield rotation occurred at frequencies of 160kHz and 50MHz. The cell entrapment occurred at frequencies above 140 kHz.

Youlan Li and Karan V.I.S Kaler[12] proposed a planar microelectrode array fabricated on a glass substrate to fractionate cells into purer subpopulations. They investigated the dielectrophoretic response of viable and nonviable canola cells. They performed variations in the applied voltage of  $9V_{PP}$  to  $16V_{PP}$  leaving the frequency fixed, and manipulations in frequency going from 10Hz to 10MHz.

Esther G. Cen et al.[13] designed and implemented a microchip with three types of microelectrodes of similar layouts but different functions. They implemented a system called Leviator-Rotator in which, different kinds of electrodes were excited to perform conveyance and electrorotation. The electrodes received stimulus of  $5V_{PP}$  to  $15~V_{PP}$  with a frequency from 1kHz to 10MHz, injected with a Sin-Cos modulator and an amplifier controlled by a PC. They have confirmed and validated the theoretical predictions demonstrating the manipulation and polarization using a single microchip.

Manaresi et al.[14] presented an 8×8 mm² chip implemented in a 0.25μm CMOS technology featuring 102,400 actuation electrodes in an array of 320×320. The system included an embedded memory for electrode programming and an optical sensor. The huge amount of electrodes permitted a displacement controlled by software of more than 10,000 individual living cells. Each electrode was energized by either an in-phase or counter-phase sinusoidal voltage signal according to programmed patterns. The electric field is modified according to the defined pattern producing dielectrophoresis (DEP) cages. The manipulation was tested using 50μm polystyrene beads. The actuation voltages where 3.3V with a frequency range from 100kHz to 10MHz.

Il Doh et al.[15] designed a high-throughput continuous cell separation chip using switched ac signals. They proposed a three electrode system in which sinusoidal electric fields of 5MHz and  $8V_{PP}$  are applied generating a non-uniform electric field. They reported ranges of purity of  $95.9\% \sim 97.3\%$  in the separation of viable and non-viable yeast cells.

A. Enteshari et al. [16] proposed a system to perform DEP analysis with programmable planar arrays called Lexel<sup> $\mathbb{M}$ </sup>. Their architecture is configurable via software and is adapted to implement various AC electrokinetic techniques with a two dimensional randomly addressable electrode array driven by one of four sinusoidal analog signals. The objective of this approach was to have a flexible microelectrode structure to be used as bio-analysis sensor for a low-power SoC. The chip has an array of  $120 \times 120$  electrodes in a  $1.6 \times 1.6$  mm<sup>2</sup> die, using a  $0.18 \mu m$  technology (TSMC CMOS process). The stimulating voltage is 3.3 V with a frequency range of 1 kHz to 5 MHz generated with phases of 0,  $\pi/2$ ,  $\pi$ ,  $3/2\pi$ ,  $2\pi$  rad/sec.

Byoung-Gyun Kim et al.[17] presented a chip with a  $2\times2$  micro-well array using silicon substrate and PDMS¹ channel structures for high-throughput biochemical cell-based assay applications. They propose a scheme for active positioning control of a single cell using DEP, applying signals of  $10V_{PP}$  at a frequency of 200Hz. They demonstrated the successful capture of  $15\mu$ m polystyrene beads applying negative DEP in the two-dimension micro well array. They performed accurate control of positioning/capturing cells one by one actively. With the proposed scheme, individual cell/microbead can be positioned and captured in each selected micro-well, and the total number of cells/microbeads in each micro-well can be easily controlled.

K. Wayne Current et al.[18] developed a high voltage integrated circuit to transport droplets on programmable paths. The chip creates DEP forces that move the droplets,

<sup>&</sup>lt;sup>1</sup>Polydimethylsiloxane

it has an array of nominally 100V electrode drivers and a maximum power of 1.87W. The operating power is a changing parameter because it is related to the electrokinetic force involved in the cell manipulation, the used structure, the shape of the channel, the electrode geometry etc. However, we will take this number as a power reference in our prototype. The programmable fluidic processor (PFP) of Wayne Current et al. can use both low and high voltage excitation. Since the volumes and masses of biological cells require various DEP forces, the PFP can control them by having variable electrode excitation, voltage amplitude, phase and frequency. They used square waves an all digital electronics to drive the electrodes. Analog circuitry for generating sinusoidal electrode excitations has been included in the same device.

Bang-Chih-Liu et al.[19] have incorporated a filtering microstructure and a dielectrophoresis force device. They applied individual input voltage with different frequency on the various rows of the microchip. The separation function could be achieved by attracting the target particles and releasing the unwanted ones. The circuit was designed to generate 16 output signals adopting crystal oscillators with ripple counter acting as frequency dividers to make it an adjustable and multi-output circuit. They reported their obtained results in the separation of glass beads from latex beads.

James T. Y. Lin et al.[20] designed a DEP microchip using standard one-layer metal process capable to perform cell concentration, transportation and separation, the chip's waveforms were composed of sinusoidal voltages of  $6V_{\rm PP}$  and 1MHz. The excitation was controlled with a DAC card. This DEP microchip demonstrated that collection, transportation and separation of a variety of particles on the same parallel electrode array was possible.

Ting-Chen Shih et al.[21] proposed and demonstrated a biochip integrating DEP traps and a programmable DEP array for the multisorting applications of biomolecules. The voltage on each individual electrode was preprogrammed and controlled in real time using LabView. With fluorescence labeling/detection and this chip, is possible to address sorting applications in a low concentration sample with better selectivity and robustness. Having programmed the potentials, a mobile probe bead can migrate to the desired outlet channel. The device was micromachined on a silicon wafer with micropyramid DEP traps and a  $5\times5$  DEP sorting array bonded with a PDMS lid.

Rodrigo Martinez-Duarte et al.[2] presented a multi-stage, multi-frequency carbon DEP device for filtering and separation with high throughput. The voltage and frequency of one of the four ports for CarbonDEP arrays can be controlled. The excitation module can deliver a signal amplitude of  $1V_{\rm PP}$  to  $13V_{\rm PP}$  with a resolution of 0.05V at frequencies up to  $12.5{\rm MHz}$ , having frequency resolution of  $2.98{\rm Hz}[22]$ . The sinusoidal signals are generated with a strategy called Direct Digital Frequency Synthesis (DDFS). They reported the separation of three different particles with no throughput degradation under an increment in the flow rate.

Honghua Liao et al. [23] proposed a system to perform traveling wave DEP based on SOPC (System on Programmable Chip). Four outputs with independent control of phase are available in the prototype. The traveling wave DEP electric field is created by the four outputs and is capable to drive biological particles to achieve separation in

a microchannel. The feasibility of the results is demonstrated by simulation results.

Maziyar Khorasani et al. [24] presented a high-voltage CMOS controller for microfluidics. This system is used to perform capillary electrophoresis on a 2cm.×1cm. glass chip. The controller offers four high-voltage output drivers capable to switch 300V, and its dc-dc converter can generate up to 68V using external passive components.

Heather Wake and Martin Brooke [25] performed low voltage electrophoresis (EP) on a CMOS chip. Their architecture operates with only a 5V power supply. They use 100 individually addressable electrodes to move the electric field with the sample as it travels along the separation area. Voltages ranging from 0.01V to 5V can be used over distances of  $36\mu$ m to 1.8 mm, yielding the ability to generate electric fields from 0.05V/cm to 1389V/cm.

A microfluidic-driving manipulation array was presented by Tzu-Yu Chao and Cheng-Hsien Liu [26] for the manipulation of microscale biological samples based on Alternating Current Electro-Osmosis Flow (ACEOF). Controlling the voltage and frequency the actuator can not only orient the microscale objects but also convey them. The controller of the array is set-up using a manual switch circuit board to operate the particle manipulation.

A fully integrated CMOS interface for cell manipulation and separation in LOC devices is proposed by Mohamed Amine Miled and Mohamad Sawan in [27]. Their interface includes all microelectronics circuitry for dielectrophoretic manipulation and capacitive detection. An embedded microcontroller to command frequency and phase is included. The device can perform rotation, translation and separation of cells. The circuit provides four different AC voltage signals with a maximum amplitude of 3.3V and a frequency range of 10MHz.

As we have seen, electrokinetic tasks rely on signal generators, most of the devices summarized in Table 2.1 are stimulated using external generators. From the dedicated stimulators we may note a great need of multiple and independent signals with control of amplitude and frequency. The incorporation of such stimulators to microfluidic devices can contribute in the integration of better diagnostic and portable appliances. Also the embedded circuitry reduces considerably the overall cost and power consumption of the equipment.

Currently none of the existing prototypes described in the bibliography present a compact design, low power and a large of stimulator ports allowing the manipulation of a large variety of cells/particles all those characteristics integrated in the same chip. The challenges at this point will be to have a device capable to offer multiple stimulation ports, with a wide range of frequencies to manipulate a large number of particles/cells. The invention must count on low power consumption and small size (in order to be portable), with the possibility of being mass produced. The research and prototype presented in this work addresses these features.

Table 2.1: Summary of advances in Electrokinetic-driven devices

| EK force | Voltage(V)                              | Frequency                     | Reference                                                | Tested on                                                       | ASIC | Year |

|----------|-----------------------------------------|-------------------------------|----------------------------------------------------------|-----------------------------------------------------------------|------|------|

| CE       | +80, +1200                              | DC                            | Wolley et al. [9],<br>[10]                               | pBR322<br>MspIDNA                                               | No   | 1997 |

| DEP      | 1-4                                     | 1KHz-10MHz                    | Xiao-Bo et al. [11]                                      | DS19                                                            | No   | 1997 |

| DEP      | 16                                      | 10Hz-10MHz                    | Youlan Li et al.[12]                                     | Viable and non-<br>viable canola<br>cells                       | No   | 2002 |

| DEP      | 1-10                                    | 10kHz-30MHz                   | Lifeng Zheng et al. [28]                                 | Latex beads,<br>Fluorescently<br>labeled $\lambda$ phage<br>DNA | No   | 2003 |

| DEP      | 5-15                                    | 1KHz-10MHz                    | Esther G. Cen et al. [13]                                | Canola proto-<br>plast                                          | Yes  | 2003 |

| DEP      | 3.3, 6.6, 9.9                           | 100KHz-<br>10MHz              | Nicolo Manaresi et<br>al. [14]                           | Eukaryotic cells <sup>1</sup>                                   | Yes  | 2003 |

| DEP      | 8                                       | 5MHz                          | Il Doh et al. [15]                                       | Viable and non-viable yeast cells (Sac-charomyces cerevisiae)   | No   | 2004 |

| DEP      | 3                                       | 1KHz-5MHz                     | A. Enteshari et al. [16]                                 | Polystyrene mi-<br>crobeads                                     | Yes  | 2005 |

| DEP      | 10                                      | 1MHz                          | Byoung-Gyun<br>Kim et al. [17]                           | Polystyrene mi-<br>crobeads                                     | No   | 2005 |

| DEP      | 10                                      | 200Hz                         | K. Wayne Current<br>et al. [18]                          | PBS <sup>2</sup> droplets                                       | Yes  | 2005 |

| DEP      | 4, 8                                    | 100Hz-370KHz                  | Bang-Chih Liu et<br>al. [19]                             | Separation of latex from glass beads                            | No   | 2005 |

| DEP      | 6                                       | 1MHz                          | James T. Y. Lin et al. [20]                              | Polystyrene microbeads, Pichia yeast cells, HeLa cells          | No   | 2007 |

| DEP      | 8                                       | 1MHz                          | Ting-Chen Shuh<br>et al. [21]                            | p50, conjugate<br><i>I-kappa-B-alpha</i><br>proteins            | No   | 2007 |

| DEP      | 1-13                                    | 3Hz-12.5MHz                   | R. Martinez-<br>Duarte et.al.<br>[2]                     | S. cerevisae                                                    | No   | 2008 |

| DEP      | N/A, Four phases 0°, 90°, 180° and 270° | N/A                           | Honghua Liao et<br>al. [23]                              | No test                                                         | Yes  | 2008 |

| CE       | 0-68                                    | DC                            | M. Khorazani<br>et.al. [24]                              | DNA sizer                                                       | Yes  | 2009 |

| EP       | 0.01-5                                  | DC                            | Heather Wake and<br>Martin Brooke<br>[25]                | No test                                                         | Yes  | 2009 |

| EO       | 2-10                                    | 1kHz, 10kHz,<br>50kHz, 100kHz | Tzu-Yu Chao and<br>Cheng-Hsien Liu<br>[26]               | Latex beads                                                     | No   | 2009 |

| DEP      | 0-3.3                                   | 1Hz-10MHz                     | Mohamed Amine<br>Miled and Mo-<br>hamad Sawan in<br>[27] | Microspheres                                                    | Yes  | 2010 |

## Chapter 3

## Theoretical Background on Analog and Digital Oscillators

This chapter provides a brief introduction to the theory of analog and digital oscillations, describing their main characteristics and operation principles.

From the State of the Art chapter we have seen that the global objective of the cited inventions is the integration of a Lab-on-a-Chip device. Many of them center their study in the creation of the microfluidic platform leaving the stimulation to external sources. A multi-stimulation device will offer the capability to perform different and new research protocols providing of independent signals to characterize, filter and displace cell populations simultaneously. Several alternatives were analyzed to implement the multi-signal generator IC to stimulate electrokinetic platforms. Those alternatives cover digital and analog schemes. The digital strategies are:

- Delta Dirac Unstable Oscillator (DDUO)

- Direct Digital Frequency Synthesizer (DDFS)

The analog implementations are:

- Operational Transconductance Amplifiers and Capacitors (OTA-C)

- Triangle to Sine Converter (TSC)

## 3.1 Digital approach

The digital sinusoidal oscillators are basic circuits in communications, music/voice synthesis, control, radar and digital signal processing systems. These oscillators exhibit the advantages of many digital systems:

- Flexibility

- High Stability

- Low cost

- Programmability

The control of sine waveforms can be a difficult task in analog systems, because they need to include discrete components such as resistors, capacitors or inductors to control waveform specs. Adding those elements increases the on-chip or physical area, limits IC performance to a range of frequencies. On the other side oscillators based on digital techniques allow a good control over the frequency, phase and even amplitude of generated sine waves.

Among the preferred implementations of digital sine waves by the designers are:

- ROM Look-Up Table A ROM is used to store the samples of the sinusoid and later the data is presented at specific-time intervals to produce the sinusoidal signal (we will reach to this specific approach later in this chapter).

- Cordic-Algorithm based Similar to the ROM look-up table technique but the samples of the sinusoid are generated interactively without being stored in a ROM.

- **Digital feedback with poles in the unit circle** Typically they offer simple hardware but they may also present long-term stability problems; in this chapter we analyzed an algorithm based on this method.

Numeric errors (e.g. truncation) lead to high THD, therefore to lower the distortion by increasing the number of bits can be increased in the system causing an upsurge in the space and consequently in power consumption. The dependence in the word size, the need of further circuitry (like DAC and post-filtering stages) and the computational power represent the major drawbacks of the digital sinusoidal oscillators.

#### 3.1.1 Delta Dirac Unstable Oscillator (DDUO)

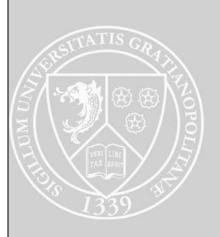

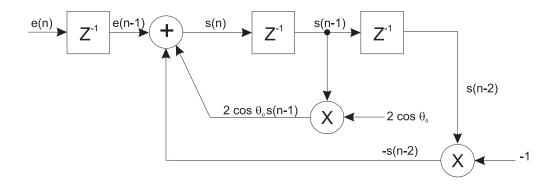

One efficient method to generate digital sinusoidal waveforms is the Delta Dirac Unstable Oscillator which is also called *Multiple-output direct-form digital oscillator* [29, 30]. This approach generates the sinusoidal signal in recursive fashion without the need of a ROM and is based in a second-order recursive digital filter with poles located over the z-plane's unit circle.

The oscillator presents very good high-frequency resolution and a large number of samples per cycle, with the advantage of approximately uniform frequency spacing between the generated samples. This is an essential characteristic in communication system applications such as frequency shift keying (FSK) and frequency division multiplexing (FDM).

In its simple form this digital oscillator is characterized by:

$$y(n) = \alpha \cdot y(n-1) - y(n-2) \quad n \ge 0$$

(3.1)

The output sample at time t = Tn is y(n) being T the sampling interval. The ideal discrete output y(n), and its angle  $\theta$  are:

$$y(n) = \sin(n\theta) \tag{3.2}$$

$$\theta = 2\pi f T \tag{3.3}$$

The number of samples in a complete sinusoidal waveform is:

$$N = \frac{2\pi}{\theta} \tag{3.4}$$

The ideal model of the oscillator is shown in Figure 3.1.

Figure 3.1: Multiple-output direct-form digital oscillator

The difference equations for the diagram of Figure 3.1 are:

$$x_2(n) = 2\cos\theta \cdot x_2(n-1) - x_2(n-2) \tag{3.5}$$

$$x_1(n) = x_2(n-1) (3.6)$$

The  $\mathbb{Z}$ -transform of Equation 3.6 is:

$$X_1(Z) = z^{-1}X_2(Z) + x_2(-1) (3.7)$$

we can see that the  $\mathbb{Z}$ -transform of  $x_2(n-2)$  is:

$$\mathcal{Z}\left\{x_2(n-2)\right\} = z^{-1}X_1(Z) + x_2(-2)$$

being  $x_2(-1)$  and  $x_2(-2)$  the initial conditions.

The  $\mathcal{Z}$ -transform of Equation 3.5 is:

$$X_2(Z) = \frac{x_2(-1)(z^{-1}) - x_2(-2)}{1 - 2\cos\theta \cdot z^{-1} + z^{-2}}$$

(3.8)

From the diagram of Figure 3.1 we could see that the  $\mathbb{Z}$ -transform of the output signals  $y_s(n)$  and  $y_c(n)$  can be written as:

$$Y_s(Z) = \sin \theta \cdot X_1(Z) \tag{3.9}$$

$$Y_c(Z) = (\cos \theta - z^{-1})X_1(Z) \tag{3.10}$$

Let  $x_2(-1) = 0$  and  $x_2(-2) = -1$  and substituting Equations 3.7 and 3.8 in eqns. 3.9 and 3.10 we get:

$$Y_s(Z) = \frac{z^{-1}\sin\theta}{1 - 2\cos\theta \cdot z^{-1} + z^{-2}}$$

(3.11)

$$Y_c(Z) = \frac{z^{-1}(\cos\theta - z^{-1})}{1 - 2\cos\theta \cdot z^{-1} + z^{-2}}$$

(3.12)

The inverse  $\mathcal{Z}$ -transform of Equations 3.11 and 3.12 are:

$$y_s(n) = \sin(n\theta) \tag{3.13}$$

$$y_c(n) = \cos(n\theta) \tag{3.14}$$

Note that this oscillator generates two components of a complex sinusoidal signal  $y_s(n)$  and  $y_c(n)$ .

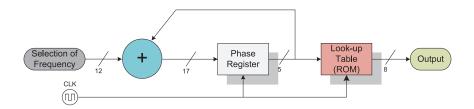

#### 3.1.2 Direct Digital Frequency Synthesis (DDFS)

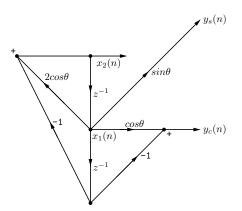

DDFS achieves fast frequency switching with very small steps, over a very wide band, linear phase and frequency shifting. In a Direct Digital Synthesizer (DDS), the output frequency, phase and amplitude can be easily, precisely and rapidly manipulated under digital control. Another advantage of DDFS is linear phase switching [31]. The DDS has the following basic blocks: a phase accumulator, a phase to amplitude converter (a sine ROM), a digital to analog converter and an output filter.

**Phase accumulator.** This structure consists of a j-bit frequency register which stores a phase increment word, followed by a j-bit full-adder and a phase register. The digital phase word is entered in the frequency register. At each clock pulse this data is added to the data previously stored in the register. The phase increment word is a phase angle step that is added to the previous value at each  $1/f_{CLK}$  to produce a linear increasing digital value.

Figure 3.2: Simplified diagram of DDFS and signal flow as shown in [1].

Phase to Amplitude Converter. It is implemented in a Read Only Memory (ROM) as a sine look up table which converts the digital phase information into the values of a sine wave. The numerical period of the sequenced samples called from the sine ROM will have the same value as the numerical period of the sequence generated by the phase accumulator. If the phase increment is large, the phase accumulator will step quickly through the sine look-up table to generate a high frequency sine wave. If the phase increment is small, the phase accumulator will take many more steps, generating a slower waveform [32]. The main problem with the DDFS approach is the power budget. One way of minimizing this parameter is to reduce the size of the ROM. Some implementations report the development of low power schemes with consumptions of 35mW [33], and 45mW at 55MHz [34]. Reference [22] implements a ROM stage inside a FPGA system rather than recording the complete set of coefficients of the sine wave. This takes advantage of the symmetry of the sine wave using only values from 0 to  $\pi/2$ .

Digital to Analog Converter (DAC). The resultant data is then passed through a DAC in order to develop a quantized analog sine wave in voltage or current. In DDS the DAC subsystem is very important. In wide output bandwidth DDSs, most spurs are generated less by digital errors (truncation or quantization errors) and more by analog errors in the D/A-converter such as clock feedthrough, intermodulation and glitch energy [1]. There are some ROM-less schemes that eliminates the power consumption due to memory. The DAC must be fast enough to generate high frequency sine waves. A DAC consumes a great amount of space and power in order to be fast enough to meet the requirements of conversion speed.

Low Pass Filter. The output is also exposed to sampling harmonics of the generated frequency. A final smoothing filter is needed to interpolate the samples. It is possible to reduce switching effects in both amplitude and phase responses while still having a sharp cutoff using an elliptic filter [35].

#### 3.1.3 Total Harmonic Distortion (THD)

A sinusoid generated by a digital synthesizer will produce samples with quantization and other errors inevitably. Therefore the generated waveform will approximate the real sine wave incorporating a certain amount of power falling into other frequencies. This spurious power cause disturbances in the shape of the sine signal referred as harmonic distortion. The main causes of harmonic distortion in the digital domain are:

- 1. Sample quantization.

- 2. Non-uniform sampling.

- 3. Interpolation error.

- 4. Calculations round-off.

An expression to measure the THD is proposed by [36], and it considers a quantized model of a zero-order filter and relates the THD with the number of discrete points in the generated wave (N). This expression is:

$$THD = \sqrt{\frac{\left(\frac{\pi}{N}\right)^2}{\sin^2\left(\frac{\pi}{N}\right)} - 1} \approx \frac{\pi}{\sqrt{3}N}$$

(3.15)

Another approach cited by [37] relates the number of points and quantized steps q:

$$THD = \sqrt{\left[1 + \frac{q^2}{6}\right] \left[\frac{\pi/N}{\sin(\pi/N)}\right]^2 - 1}$$

(3.16)

Shanerberger and Awad[38] in the early efforts of implementation of digital oscillators proposed the following expression to calculate the THD:

$$THD = \frac{E_T - E(f_0)}{E_T} \cdot 100\% \tag{3.17}$$

Where the energy of the signal can be computed as follows:

| $\mathbf{N}^a$ | THD $\%$ $^b$ | THD $\%$ 8 bits $^c$ | THD $\%$ 12 bits <sup>d</sup> |

|----------------|---------------|----------------------|-------------------------------|

| 4              | 48.342585     | 48.50844577          | 48.35296774                   |

| 5              | 37.772219     | 37.96865952          | 37.78452656                   |

| 6              | 31.084194     | 31.31303329          | 31.09854572                   |

| 7              | 26.445004     | 26.70710892          | 26.46146163                   |

| 8              | 23.028089     | 23.32389749          | 23.04668811                   |

| 9              | 20.402184     | 20.7319059           | 20.42294725                   |

| 11             | 16.624785     | 17.02246084          | 16.64991771                   |

| 12             | 15.219369     | 15.65093037          | 15.24669931                   |

| 13             | 14.034305     | 14.49962091          | 14.06383815                   |

| 25             | 7.266674      | 8.117520673          | 7.322748934                   |

| 26             | 6.986353      | 7.867242976          | 7.044636211                   |

| 48             | 3.780368      | 5.227870007          | 3.88666287                    |

| 94             | 1.929789      | 4.092648205          | 2.130303282                   |

| 126            | 1.439613      | 3.885359301          | 1.698957257                   |

Table 3.1: THD values for expressions 3.15 and 3.16

$$E_T = \frac{1}{N} \sum_{k=0}^{N-1} |X(k)|^2 \tag{3.18}$$

and the energy of the fundamental component is given by:

$$E(f_0) = \frac{2}{N} |X(f_0)|^2 \tag{3.19}$$

# 3.2 Analog Approach

The sinusoidal oscillators are present in most electronic applications. They are widely used in control systems, telecommunications systems, signal sources, music synthesis, measurement systems, digital AC bridges etc. Some of the advantages of analog implementation are:

- Low Total Harmonic Distortion (THD)

- Small on-chip space

- High stability

<sup>&</sup>lt;sup>a</sup>With a small N, the signal will present a high THD, the results were obtained with a zero order sample and hold register; the THD level can be improved if a high order filter is included in the design. A big N will demand a high frequency and consequently requires a clock speed at least equals to  $N \cdot freq$ .

<sup>&</sup>lt;sup>b</sup>Values calculated with eqn. 3.15

<sup>&</sup>lt;sup>c</sup>Values calculated with eqn. 3.16

$<sup>^</sup>d$ A small q number demands a big number of bits requiring a larger on-chip area

Two analog selections: OTA-C and triangle-to-sine converter were analyzed. Options that need several capacitors to make oscillations were discarded as they need more on chip space. Oscillators based on LC filters were discarded due to the difficulty in the implementation of on-chip inductors. The obtained results are discussed in this section.

#### 3.2.1 OTA-C

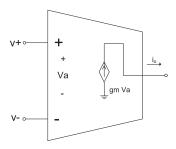

Figure 3.3: Ideal model for an OTA

The oscillators using Operational Transconductance Amplifiers (OTA) (Figure 3.3) and capacitors (OTA-C) have been shown to be very well suited for the generation of sinusoidal voltages. OTA based circuits have inherent programmability due to the fact that its transconductance gain can be electrically changed. OTA-C oscillators overcome the limitations in frequency and tunability of conventional opamp based oscillators

Among the advantages of OTA-C's we can find [39]:

- No additional constraints have to be imposed on their frequency response to compensate for local feedback-induced pole displacement.

- The transconductance can be electrically tuned with just varying the polarization current  $I_{POL}$  of the transistor

- It is possible to change the frequency in a continuous way

- Low harmonic distortion

It is possible to combine OTA's with capacitors to reach a second order characteristic equation:

$$s^2 - bs + \Omega_o^2 = 0 (3.20)$$

The main design goal is to achieve a separate control of b and  $\Omega$ . Having independent control on those variables provides a control over the frequency of operation without affecting the oscillation condition<sup>1</sup>.

<sup>&</sup>lt;sup>1</sup>A number of topologies have been studied and their advantages/disadvantages presented in [40]

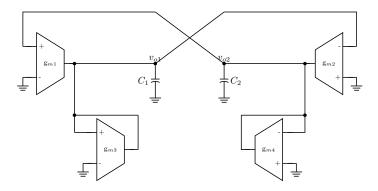

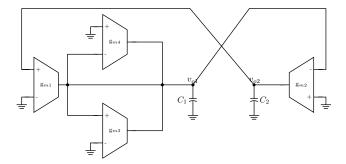

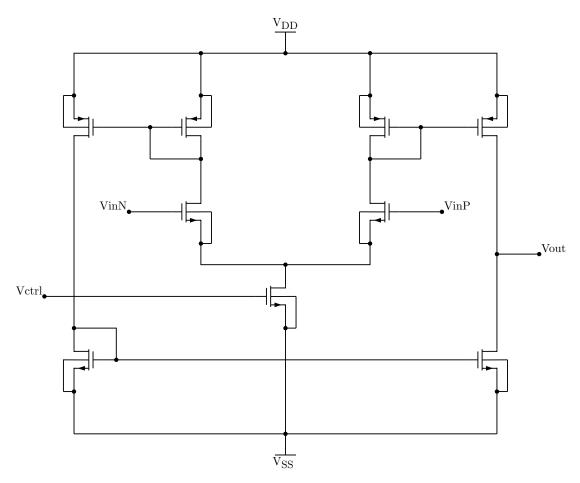

To achieve free running oscillation, the parameter b must be zero. However, in practical oscillators due to parasitic effects, the poles are displaced from the nominal positions,  $s_p = \pm j\Omega_o$ , to either the right or left side of the complex planes. For this reason, the oscillator must have its poles initially located inside the right-half complex frequency plane in order to get a self starting oscillation. Figure 3.4 presents the simplest structure to have independent control of b and  $\Omega$ .

Figure 3.4: 4OTA2C oscillator structure

The parameters for this structure are:

$$b = \frac{g_{m3}}{C_1} - \frac{g_{m4}}{C_2} \tag{3.21}$$

$$\Omega_o^2 = \frac{g_{m1}g_{m2} - g_{m3}g_{m4}}{C_1C_2} \tag{3.22}$$

There is a coupling between  $\Omega_o^2$  and b through  $g_{m3}g_{m4}$ . The solution to this inconvenience is to connect  $g_{m4}$  to the same node as  $g_{m3}$  in the called OTA-C quadrature oscillator[41]. Figure 3.5 illustrates this topology which is the selected structure for the analog oscillators developed in this dissertation.

Now, the parameters are:

$$b = \frac{g_{m3} - g_{m4}}{C_1} \tag{3.23}$$

$$\Omega_o^2 = \frac{g_{m1}g_{m2}}{C_1C_2} \tag{3.24}$$

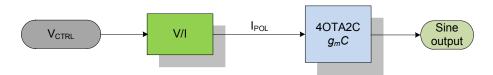

In the VCO's based in OTA-C configuration, the element responsible for the change in the oscillation frequency is the transconductance of every OTA's related to the  $\Omega_o^2$  variable. The transconductance can be modified with a simple change in the polarization current  $I_{POL}$  of the sink transistor.

Figure 3.5: 40TA2C quadrature oscillator

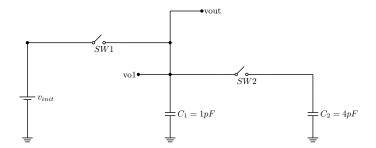

## 3.3 Triangle to Sine Converters

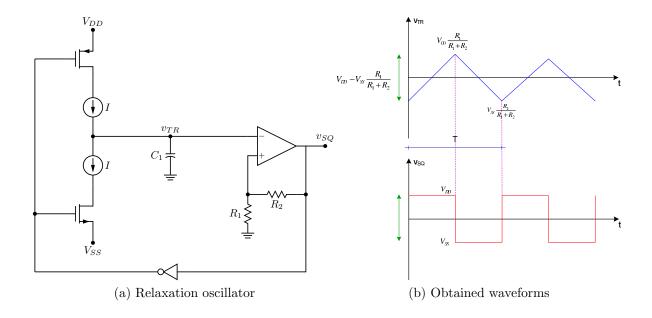

In many communications systems, phase locked loops (PLL) and function generators the conversion of triangle signals to sine waves represent a basic signal processing operation. A very precise triangle waveform can be generated using relaxation oscillators; the relaxation oscillator is constructed with current sources, a capacitor and a Schmitt Trigger Comparator, then the sinusoidal wave can be generated through a triangle-to-sine converter (TSC) [42]-[45].

#### 3.3.1 Relaxation oscillator

Figure 3.6: Relaxation oscillator

The Schmitt Trigger will commute in its upper limit  $V_{UL}$ , given by:

$$V_{UL} = V_{DD} \cdot \frac{R_1}{R_1 + R_2} \tag{3.25}$$

and the lower limit  $V_{LL}$  will be in:

$$V_{LL} = V_{SS} \cdot \frac{R_1}{R_1 + R_2} \tag{3.26}$$

The amplitude range at the output of the triangle generator is [46]:

$$\Delta v = (V_{DD} - V_{SS}) \cdot \frac{R_1}{R_1 + R_2} \tag{3.27}$$

We have the relation between voltage and current in a capacitor:

$$i = C \frac{\triangle v}{\wedge t} \tag{3.28}$$

Then, the time needed to go from  $V_{LL}$  to  $V_{UL}$  will be:

$$\Delta t = \frac{C}{i} \cdot (V_{DD} - V_{SS}) \cdot \frac{R_1}{R_1 + R_2} \tag{3.29}$$

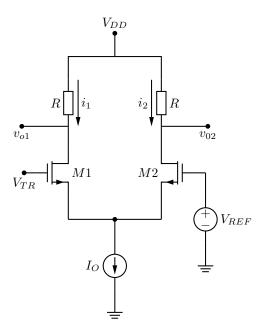

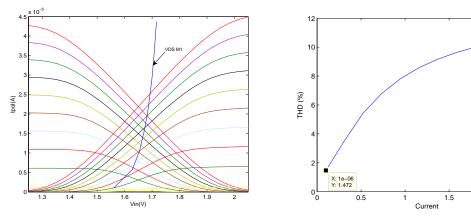

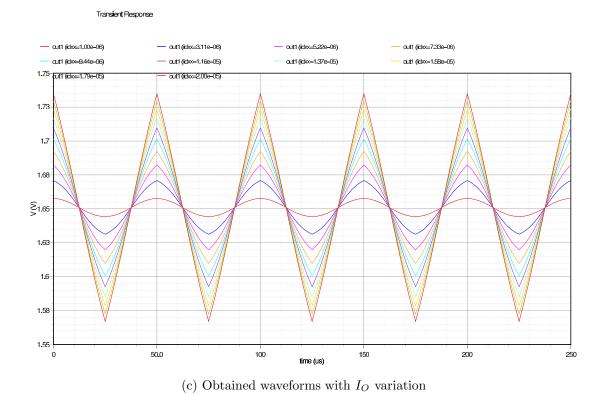

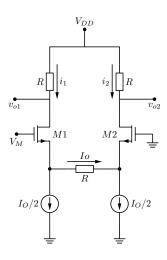

#### 3.3.2 Triangle to Sine Converter in strong inversion (TSC-SI)

The triangle to sine conversion can be implemented using a non-linear block; this structure can be implemented using the non-linear characteristic of a MOS transistor. Depending on the biasing current, the MOS transistor will operate in strong or weak inversion. The operation of the strong inversion approach is described next.