# Parallelization on graphic hardware: contributions to RNA folding and sequence alignment

Guillaume Rizk

#### ► To cite this version:

Guillaume Rizk. Parallelization on graphic hardware : contributions to RNA folding and sequence alignment. Computer Science [cs]. Université Rennes 1, 2011. English. NNT : 2011REN1S021 . tel-00634901

## HAL Id: tel-00634901 https://theses.hal.science/tel-00634901

Submitted on 24 Oct 2011

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

#### **DE RENNES 1**

sous le sceau de l'Université Européenne de Bretagne

pour le grade de

### **DOCTEUR DE L'UNIVERSITÉ DE RENNES 1**

Mention : Informatique

#### **Ecole doctorale Matisse**

présentée par

# **Guillaume Rizk**

préparée à l'unité de recherche IRISA Institut de Recherche en Informatique et Systèmes Aléatoires

Parallelization on graphic hardware: contributions to RNA folding and sequence alignment

#### Thèse soutenue à Rennes le 12 janvier 2011

devant le jury composé de :

Denis BARTHOU rapporteur

Thierry LECROQ rapporteur Sanjay RAJOPADHYE examinateur Gregory KUCHEROV examinateur Jean-Jacques CODANI examinateur Dominique LAVENIER directeur de thèse

#### Abstract

La bioinformatique nécessite l'analyse de grandes quantités de données. Avec l'apparition de nouvelles technologies permettant un séquençage à haut débit à bas coût, la puissance de calcul requise pour traiter les données a énormément augmenté. De plus, la puissance des CPU évolue comparativement moins vite, aboutissant à des temps d'exécution de plus en plus longs. En revanche, les processeurs graphiques (GPU) sont maintenant suffisamment programmables pour permettre de réaliser des calculs non graphiques, fournissant ainsi une puissance de calcul élevée bon marché. Cette thèse examine la possibilité d'utiliser les GPU pour des applications de bioinformatique. Dans un premier temps, ce travail s'intéresse au calcul des structures secondaires d'ARN. Ce problème est en général calculé par programmation dynamique, avec un algorithme qui pose de sérieux problèmes pour un code GPU: des relations de récurrence complexes et un accès mémoire compliqué. Nous introduisons une nouvelle implémentation tuilée qui fait apparaitre une bonne localité des accès mémoire, permettant ainsi un programme GPU très efficace. Cette modification permet également de vectoriser le code CPU et donc de faire une comparaison honnête des performances entre GPU et CPU. Dans un deuxième temps, ce travail aborde le problème d'alignements de séquences sur un génome de référence. Nous présentons une parallélisation GPU d'une méthode utilisant une indexation par graines. L' implémentation sur GPU n'étant pas efficace, nous nous tournons vers le développement d'une version CPU. Notre contribution principale est le développement d'un nouvel algorithme éliminant rapidement les nombreux alignements potentiels, basé sur le précalcul de portions de la matrice de programmation dynamique. Ce nouvel algorithme a conduit au développement d'un nouveau programme d'alignement très efficace. Notre travail fournit l'exemple de deux problèmes différents dont seulement un a pu être efficacement parallélisé sur GPU. Ces deux expériences nous permettent d'évaluer l'efficacité des GPU et leur place en bioinformatique.

Keywords : GPGPU, Next Generation Sequencing, mapping, RNA folding.

#### Abstract

Bioinformatics require the analysis of large amounts of data. With the recent advent of next generation sequencing technologies generating data at a cheap cost, the computational power needed has increased dramatically. However, CPU performance is not keeping up with this evolution, leading to unreasonable execution times and storage issues. On the other hand, Graphic Processing Units (GPU) are now programmable beyond simple graphic computations, providing high performance for general purpose applications at a low cost. This thesis explores the usage of GPUs for bioinformatics applications. First, this work focuses on the computation of secondary structures of RNA sequences. It is traditionally conducted with a dynamic programming algorithm, which poses significant challenges for a GPU implementation: complex data dependency scheme and memory access pattern. We introduce a new tiled implementation providing good data locality and therefore very efficient GPU code. We note that our algorithmic modification also enables tiling and subsequent vectorization of the CPU program. allowing us to conduct a fair CPU-GPU comparison. Secondly, this works addresses the short sequence alignment problem. We present an attempt at GPU parallelization using the seedand-extend paradigm. Since this attempt is unsuccessful, we then focus on the development of a program running on CPU. Our main contribution is the development of a new algorithm filtering candidate alignment locations quickly, based on the pre computation of tiles of the dynamic programming matrix. This new algorithm proved to be in fact more effective on a sequential CPU program and lead to an efficient new CPU aligner. Our work provides the example of both successful an unsuccessful attempts at GPU parallelization. These two points of view allow us to evaluate GPUs efficiency and the role they can play in bioinformatics.

Keywords : GPGPU, Next Generation Sequencing, mapping, RNA folding.

ii

# Résumé étendu

#### Contexte

La bio-informatique est le développement de méthodes informatiques permettant l'analyse de données biologiques. Les champs d'applications concernent par exemple l'analyse des séquences d'ADN qui constituent un génome, ou la comparaison et la prédiction des structures des protéines ou des séquences d'ARN. De plus, la quantité de données à analyser a augmenté de manière exponentielle au cours des dernière années.

En ce qui concerne le séquençage de l'ADN, les progrès ont été très rapides. la structure en double hélice a été découverte en 1953 par Watson et Crick. En 1977, le premier génome entier d'un organisme fut séquencé, celui du bacteriophage  $\phi X$  174 composé de 5386 bases. Le génome humain, composé de 3 milliards de paires de bases, a été séquencé en 2000 à un coût de plusieurs milliards de dollars. De nos jours, plusieurs milliards de paires de bases peuvent être séquencées pour quelques milliers de dollars.

En conséquence, la quantité de données à analyser est de plus en plus grande. D'un autre côté, la puissance de calcul des ordinateurs augmente, mais moins rapidement. Cela conduit à un allongement important des temps de traitement. Une solution pour réduire les temps de calcul est de paralléliser les calculs. La première solution est l'utilisation de CPU multi-coeurs ainsi que des clusters de CPU. Bien qu'efficace, cette solution est coûteuse. Une autre solution est l'utilisation de matériel haute performance spécialisé. Par exemple les FPGAs peuvent fournir une puissance de calcul très élevée, mais sont également très coûteux.

Une autre solution vient de l'utilisation des processeurs graphiques (GPU). Les GPUs sont des processeurs spécialement conçus pour accélérer l'affichage de graphismes complexes sur un écran. C'est une tâche avec beaucoup de parallélisme de données: des traitements identiques doivent être appliqués à tous les pixels et objets géométriques qui constituent l'image. Les GPU ont été conçus pour traiter efficacement ce type de calcul: ils comportent de nombreuses unités de calcul capables d'appliquer le même calcul à différentes données. A l'origine limités à des calculs graphiques de base, les GPU ont graduellement acquis la capacité d'effectuer des traitements de plus en plus complexes, afin que les programmeurs graphiques puissent développer des effets plus réalistes. Cette programmabilité accrue est arrivée à un point ou des calculs non graphiques ont aussi pu être exécutés sur des cartes graphiques, donnant naissance à un nouveau champ d'application, le calcul générique sur cartes graphiques (GPGPU en anglais). NVIDIA a introduit en 2006 le langage de programmation CUDA, spécialement conçu pour faciliter le développement de programmes GPGPU. Utiliser les GPUs pour exécuter des programmes non graphiques a plusieurs avantages. D'abord, une forte concurrence tirée par l'industrie du jeu vidéo a conduit à des GPUs bon marché, avec une puissance de calcul en constante augmentation. Tous les ordinateurs peuvent être équipés d'un GPU haut de gamme, augmentant considérablement sa puissance totale de calcul à faible coût.

Ensuite, les GPU sont naturellement bien adaptés pour tout problème avec un fort parallélisme de données, apparaissant dans de nombreux domaines de recherche scientifique. Par exemple en imagerie médicale, pour des simulations de dynamique des fluides, en finance, traitement du signal, ou encore pour la cryptanalyse. La bioinformatique comporte aussi beaucoup de parallélisme de données: l'analyse de données biologiques nécessite souvent d'appliquer le même calcul sur des données différentes. A priori, il semble donc naturel d'utiliser les GPU pour accélérer les programmes utilisés en bio-informatique.

## Objectifs

L'objectif de cette thèse est d'évaluer les capacités des GPU dans des applications de bio-informatique typiques, et de comparer les résultats obtenus avec une parallélisation plus traditionnelle sur CPU multi-coeurs. Pour cela notre étude se penche sur deux problèmes distincts, à la fois bien représentatifs de ce qui se fait en bio-informatique, et différents en termes de méthodes de calculs utilisés pour les résoudre. Le premier problème est l'étude de la prédiction de structure secondaire d'ARN. L'algorithme utilisé est un calcul intensif qui se prête *a priori* bien à une parallélisation sur GPU. Le second problème porte sur l'alignement de séquences de petite taille, générées par les nouvelles technologies de séquençage, sur un génome de référence. Le calcul est moins intensif et nécessite au contraire plus d'accès à la mémoire, en utilisant une structure de données élaborée. Ces deux problèmes représentent donc un spectre varié de ce que l'on peut trouver en bio-informatique, et leur étude permet de répondre à la problématique de cette thèse: les algorithmes utilisés en bio-informatique peuvent-ils être efficacement implémentés sur GPU ?

L'évaluation des GPU doit s'effectuer sur plusieurs niveaux. Le premier point important est le temps nécessaire au développement d'applications sur GPU. Les GPUs sont a priori plus simples à programmer que des FPGAs, mais plus difficiles que des CPU. Toutefois cela nécessite d'être confirmé en pratique. Deuxièmement, les temps d'exécutions doivent être mesurés et comparés à un code tournant sur CPU. Pour une comparaison honnête, il faut comparer le code GPU à un programme bien optimisé sur CPU, utilisant tous les coeurs disponibles ainsi que les instructions vectorielles qui augmentent significativement la puissance des CPUs. Enfin, les coûts d'achat et de fonctionnement des GPUs doivent aussi être évalués.

## Chapitre 1 : Architecture

la première étape pour savoir si les GPUs peuvent accélérer des programmes de bio-informatique est de connaître leur fonctionnement et l'architecture en détail, de déterminer les points faibles et points forts et de les comparer avec l'architecture CPU.

#### 1.1 Introduction

Le temps d'exécution total d'un programme dépend de plusieurs facteurs, communs aux architectures CPU et GPU. Nous pouvons distinguer trois caractéristiques principales: la puissance de calcul brute, la bande passante mémoire, et la latence.

La puissance brute détermine le nombre d'opérations qui peuvent être exécutées par unité de temps. Elle est généralement fournie par les constructeurs en nombre d'opérations par cycles d'horloge. La multiplication de ce chiffre par la fréquence fournit le nombre d'opérations par secondes, usuellement défini en milliards d'opérations flottantes par secondes, *GFLOPS* en anglais. Par exemple la puissance maximale d'un CPU Xeon X5482 est de 102.4 GFLOPS pour des opérations en 32 bits, en utilisant les instructions SSE et tous les coeurs disponibles. Pour une carte graphique Tesla C1060, la puissance maximale théorique est de 624 GFLOPS. Cela signifie que l'on peut s'attendre à facteur d'accélération de x6 en utilisant un GPU. Toutefois, le facteur d'accélération réel dépend bien évidemment de la fraction de cette puissance maximale que l'on arrive à exploiter en pratique.

Le deuxième facteur est la bande passante mémoire, *i.e.* la quantité de données transférée par unité de temps, exprimée en Goctets/sec (Go/sec). Schématiquement, les données sont transférées de la mémoire pour alimenter le processeur, puis dans l'autre sens pour stocker les résultats. Pour une Tesla C1060 et un CPU Xeon 5500, la bande passante maximale est respectivement de 102.4 Go/sec et 32.0 Go/sec. Le rapport entre la bande passante et la puissance brute détermine l'intensité arithmétique nécessaire pour exploiter au maximum les ressources disponibles. Par exemple pour la Tesla C1060, un programme doit effectuer au moins 24 opérations flottantes par accès mémoire pour atteindre la puissance de calcul maximale. Toutefois, si le jeu de données d'un algorithme tient dans la mémoire présente sur la puce, les données peuvent être chargées une seule fois de la mémoire principale et réutilisées plusieurs fois. Dans ce cas, la bande passante mémoire est moins souvent une limitation.

Le troisième point est la latence, le délai entre le lancement d'une opération et le moment ou le résultat est disponible. La latence concerne à la fois les les instructions processeurs, et les transactions mémoires. Dans un système purement séquentiel la latence est un problème important. C'est pourquoi les CPU intègrent de nombreux niveaux de mémoire cache pour diminuer la latence d'accès à la mémoire, et des systèmes complexes tel que l'exécution *out-of-order* des instructions. D'un autre côté, le parallélisme de tâches permet aussi de combattre efficacement les problèmes de latence: pendant qu'une tâche est en attente, une autre tâche est exécutée, les unités de calcul ne sont donc pas bloquées. C'est ce qui est utilisé par les GPU, et qui leur permettent de se passer de grandes quantités de mémoire sur la puce.

## 1.2 Comparaison CPU/ GPU

Nos expérimentations ont été effectuées sur un système 8 coeurs composé de deux quadcore Xeon E5430 fonctionnant à 2.66GHz. Chaque Xeon contient 32KB de cache L1 par coeur, et 6MB de cache L2 commun à deux coeurs. Ce CPU supporte le parallélisme de tâches, traditionnellement implémenté avec les threads POSIX ou avec l'API OpenMP. Il supporte aussi le parallélisme de données avec les instructions vectorielles SSE.

Nous avons utilisé l'architecture GPU CUDA de Nvidia, qui combine hautes performances et facilité de programmation avec le langage C for CUDA. En résumé, les GPUs échangent le grand nombre de transistors dédiés à la mémoire cache et aux mécanismes de contrôle de flux présent sur les CPUs contre plus d'unités de calculs. A la place, les GPU comptent sur le multithreading pour masquer la latence. Un programme GPU est un kernel, appelé sur un ensemble de trheads, répartis en un grille de blocs. les blocs sont subdivisés en *warps* de 32 threads qui s'exécutent en SIMD. Les threads d'un bloc peuvent être synchronisés et partager un petite mémoire rapide partagée de 16 Ko. Quelques points particuliers sont: (i) la bande passante maximale n'est atteinte que si les différents accès mémoire sont regroupés, ce qui nécessite que chaque thread accède à des données consécutives en mémoire, (ii) chaque multiprocesseur de la carte peut gérer au maximum 32 warps à la fois. L'occupation mesure le pourcentage de ce maximum qui est utilisé en pratique. Une occupation plus élevée permet en général de mieux utiliser les ressources de la carte, mais nécessite d'utiliser peu de registres par thread. (iii) La mémoire partagée est un point crucial pour obtenir une bonne performance, elle permet de stocker sur la puce des données susceptibles d'être utilisées par différents threads. Elle est gérée entièrement manuellement par le programmeur.

Les architectures CPU et GPU sont assez différentes dans le sens où le CPU contient beaucoup d'éléments dont le but est d'exécuter rapidement une tâche séquentielle, alors que le GPU est très lent s'il exécute une seule tâche. Comme le GPU compte sur le multi-threading pour ses performances, il requiert des milliers de threads pour fonctionner efficacement, contrairement au CPU qui est déjà très rapide avec un seul thread. Toutefois, il y aussi un certain nombre de similarités: un GPU est un ensemble de multiprocesseurs, chacun contenant une unité SIMD, un CPU est un ensemble de coeurs, chacun contenant également un unité SIMD. De plus, les architectures semblent converger: les GPU évoluent vers une programmation plus souple, tandis que les CPUs évoluent vers plus de parallélisme. Par conséquent, les GPUs ne font qu'anticiper ce qu'il sera nécessaire de faire pour les CPU de demain.

## Chapitre 2 : Prédiction de structure secondaire d'ARN

La prédiction des structures secondaires d'ARN est un problème étudié depuis longtemps par la communauté scientifique, et est utilisée régulièrement dans des pipelines de bio-informatique. C'est un algorithme de calcul intensif, dont le temps d'exécution pose problème pour des séquences de grande taille. Une parallélisation GPU n'a jusqu'à présent à notre connaissance jamais été tentée.

### 2.1 Introduction

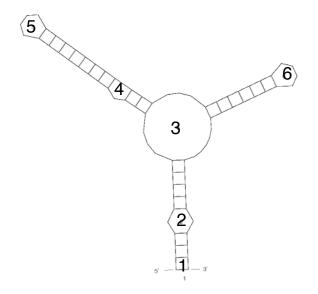

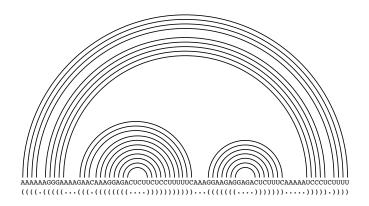

La molécule d'ADN est plus connue sous sa forme double brin qui forme une double hélice. Toutefois, la molécule d'ARN se trouve plus généralement en simple brin dans la cellule. Elle est composée de 4 nucléotides, aussi appelées bases: adenine (A), cytosine (C), guanine (G) et uracil (U). Deux nucléotides peuvent se lier formant ainsi une paire de bases, selon la règle de complémentarité de Watson et Crick: A avec U, G avec C, mais aussi la paire "bancale" plus instable G avec U. Les liaisons intra-moléculaires de ce simple brin d'ARN forcent la chaîne à se replier sur elle même en un ensemble de boucles de différent types : des épingles à cheveux, des hernies, des boucles internes ou multiples. Cette conformation 2D est appelée la structure secondaire, dont la connaissance est nécessaire à de nombreux problèmes de bio-informatique. Les algorithmes calculant cette structure ont une complexité en  $\mathcal{O}(n^3)$ , ce qui signifie que le temps d'exécution devient rapidement problématique pour des grandes séquences. L'algorithme le plus connu est celui de Zuker introduit en 1981, qui utilise un modèle thermodynamique précis pour mesurer la stabilité des différents éléments de la structure [85]. Il est encore largement utilisé aujourd'hui et disponible dans deux packages, ViennaRNA [29] et Unafold [56]. Notre objectif est de développer une implémentation GPU efficace de l'algorithme donnant les mêmes résultats que Unafold.

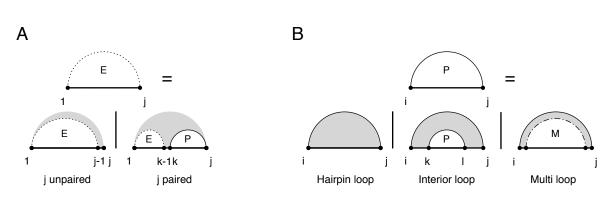

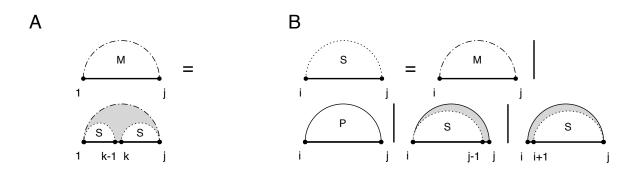

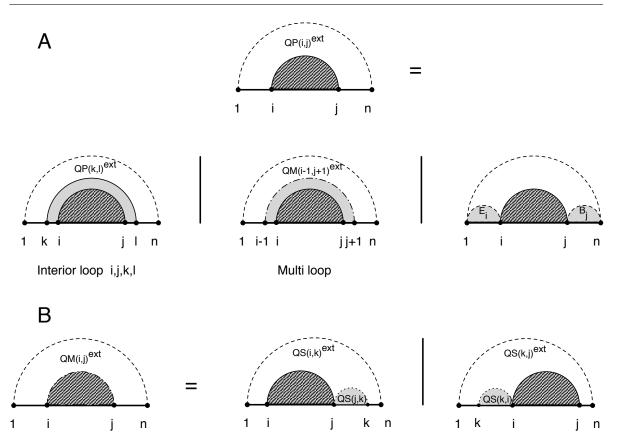

En résumé, l'algorithme de prédiction de structure fonctionne de la manière suivante. Il détermine la structure la plus stable, c'est à dire celle qui maximise un schéma de score fixé, ou plutôt, qui minimise l'énergie libre totale de la molécule d'ARN. L'énergie de la séquence entière se décompose facilement en la somme des énergies de ses sousstructures. Un modèle thermodynamique définit l'énergie des structures élémentaires en fonction de leur taille, type, et composition en nucléotides. Le problème est un problème d'optimisation: parmi toutes les structures possible, il s'agit de trouver celle d'énergie minimum. Ce problème est résolu par programmation dynamique: le problème entier est décomposé en sous-problèmes plus faciles à résoudre. Le problème est résolu pour des sous-séquences de la séquence principale, dont les solutions permettent ensuite de reconstituer les solutions pour des problèmes de plus en plus grands, jusqu'à obtenir la solution pour la séquence entière. L'algorithme introduit les 3 quantités  $QP_{i,j}, QM_{i,j}$  et  $QS_{i,j}$  qui représentent les solutions pour les sous-séquences  $i \dots j$  dans trois cas de figures différents.  $QP_{i,j}$  représente le score d'un séquence dont les extrémités sont appariées,  $QM_{i,j}$  une séquence contenant au moins deux paires de bases, et  $QS_{i,j}$  une séquence contenant au moins une paire de bases. Les relations de récurrence suivantes permettent de reconstruire de proche en proche la solution pour des séquences de plus en plus grandes :

$$QP_{i,j} = \begin{cases} Eh(i,j) \\ Es(i,j) + QP_{i+1,j-1} \\ \min_{\substack{\{k,l|i < k,l < j\} \\ QM_{i+1,j-1}}} Ei(i,j,k,l) + QP_{k,l} \\ \infty \end{cases} \end{cases} \quad i \cdot j \text{ est autorisée}$$

(2.1)

si paire  $i \cdot j$  interdite

$$QM_{i,j} = \min_{i < k < j} (QS_{i,k} + QS_{k+1,j})$$

(2.2)

$$QS_{i,j} = \min\{QM_{i,j}, \min(QS_{i+1,j}, QS_{i,j-1}), QP_{i,j}\}$$

(2.3)

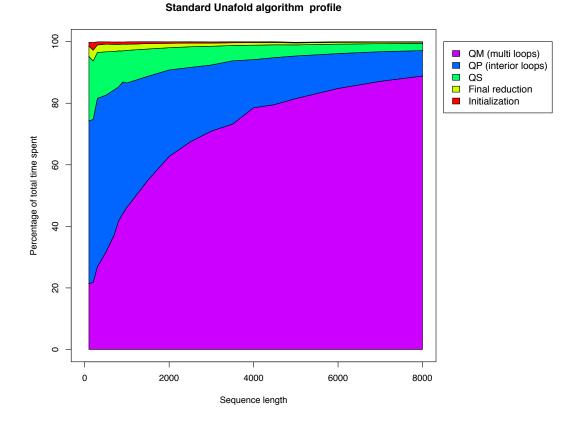

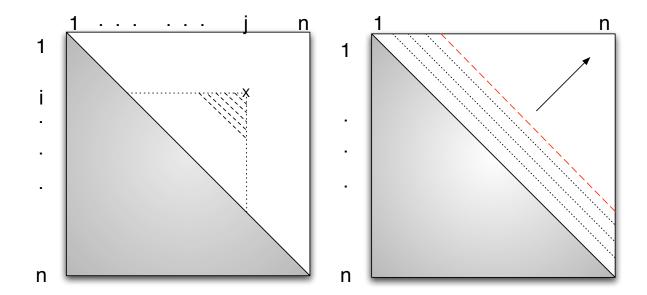

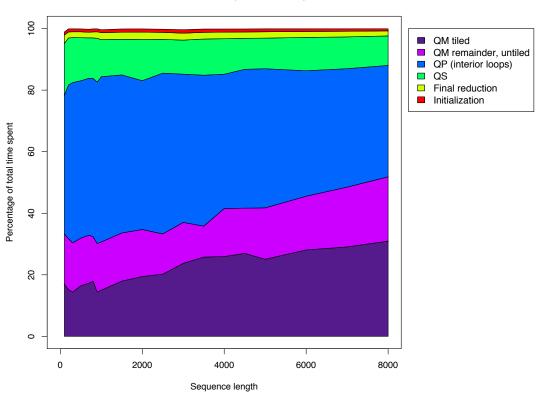

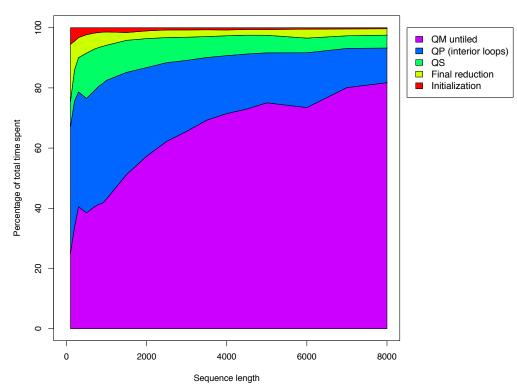

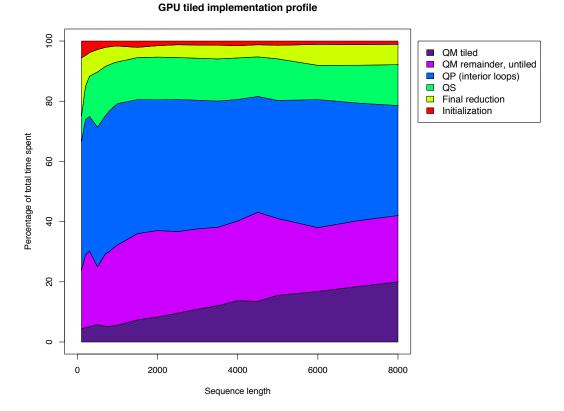

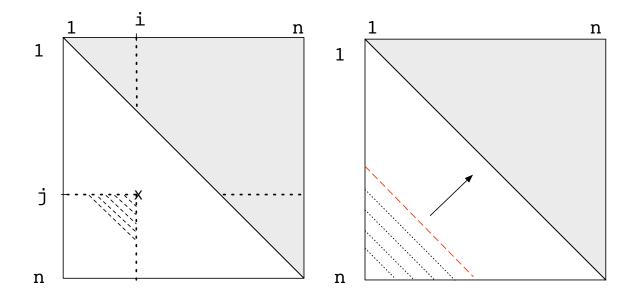

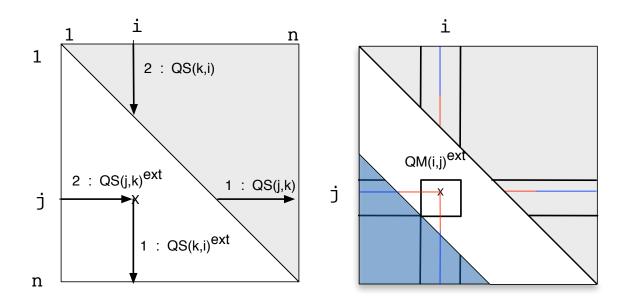

Les trois quantités  $QP_{i,j}, QM_{i,j}$  et  $QS_{i,j}$  définissent la matrice de programmation dynamique pour i, j variant entre 1 et n. C'est une matrice symétrique: on a  $QP_{i,j} = QP_{j,i}$ . Les équations de récurrence impliquent un schéma de dépendance des données et donc un certain ordre de calcul de cette matrice. En séquentiel, les calculs s'effectuent colonnes après colonnes de la gauche vers la droite, et chaque colonne de bas en haut. L'équation qui calcule  $QM_{i,j}$  est en  $\mathcal{O}(n^3)$ , les deux autres en  $\mathcal{O}(n^2)$ . Une mesure du temps passé dans les différentes parties du code montre que pour des séquences de taille 8000, plus de 80% du temps total est passé dans le calcul de QM. En revanche, pour des séquences de taille 1000, la répartition est respectivement de 30%,40% et 20% pour QM,QP et QS. Pour avoir une bonne accélération globale pour différentes taille de séquences, il faut donc accélérer efficacement ces 3 parties de l'algorithme. Pour des grandes séquences, l'accélération globale obtenue avec une parallélisation GPU va donc approcher l'accélération de la partie en  $\mathcal{O}(n^3)$ , qui calcule QM.

### 2.2 Principe de parallélisation

Les équations de récurrence impliquent une parallélisation a priori évidente des calculs: les différentes cases qui composent une diagonale i - j = constante peuvent être calculées en parallèle. Trois kernels sont conçus pour le calcul de  $QP_{i,j}, QM_{i,j}$  et  $QS_{i,j}$ , correspondant aux 3 équations de récurrences. Chaque kernel calcule une diagonale, avec un thread par case. La matrice complète est ensuite calculée séquentiellement avec une boucle sur toutes les diagonales. La synchronisation nécessaire entre chaque diagonale s'effectue donc naturellement entre l'exécution des différents kernels.

La partie la plus problématique concerne la parallélisation de la partie en  $\mathcal{O}(n^3)$  qui calcule QM. La parallélisation naïve par diagonale requiert en effet beaucoup de bande passante, car chaque case de la matrice nécessite l'accès à  $\mathcal{O}(n)$  données pour  $\mathcal{O}(n)$ calculs, et il n'y a pas de partage possible des accès entre les différentes cases d'une diagonale. En théorie, il pourrait y avoir une réutilisation des données, car une valeur QS(i,k) va être utilisée pour le calcul des différentes cases QM(i,j) avec  $j \in [k;n]$ . Cependant, le schéma de dépendance des données rend impossible d'en tirer avantage, car l'ensemble des cellules QM(i,j)  $j \in [k;n]$  sont situées sur différentes diagonales et donc calculées dans des appels kernels distincts.

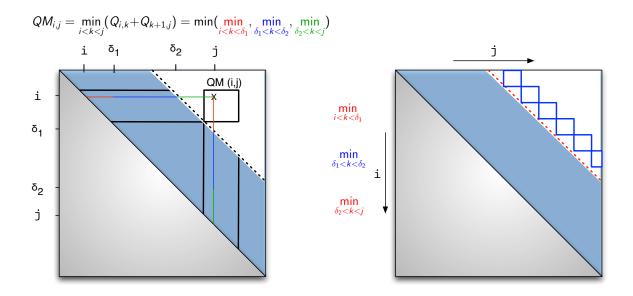

Nous avons développé une implémentation pavée qui fait apparaitre une bonne localité mémoire. L'observation clé est que le calcul d'une case est une minimisation sur i < k < j, qui peut être découpée en plusieurs parties. Notre approche est inspirée de l'implémentation systolique du problème de parenthésage optimal développé par Guibas-Kung-Thompson[27, 65]. L'idée est de décomposer et réordonner la réduction afin de faire apparaître une bonne localité mémoire et donc un code efficace sur GPU. Considérons que les cases jusqu'à une certaine diagonale  $d_0$  sont déjà calculées, c'est à dire toutes les cellules (i, j) telles que  $j < i + d_0$ . Pour  $(i_1, j_1)$  fixé en dehors de la zone connue, avec  $j_1 = i_1 + d_0 + T$ , T > 0, le calcul entier  $\min_{i_1 < k < j_1} (QS_{i_1,k} + QS_{k+1,j_1})$  n'est pas possible car de nombreuses valeurs QS sont encore inconnues.

Toutefois, il est possible de calculer une partie de la réduction pour laquelle les valeurs QS sont connues: pour  $\delta_1 < k < \delta_2$  avec  $\delta_1 = j - d_0$  et  $\delta_2 = i + d_0$ . Cela signifie qu'en enlevant la partie de la réduction qui viole la relation de dépendance des données, il est possible de calculer en parallèle dans un pavé un ensemble de cases de la matrice. Dans ce pavé, la bonne localité mémoire permet de charger en mémoire partagée du GPU les données nécessaires au calcul. Chaque thread va ensuite accéder à cette mémoire partagée pour effectuer ses opérations. De cette manière, les besoins en bande passante sont réduits d'un facteur égal à la taille du pavé (16 dans notre implémentation GPU). Le kernel n'est plus limité par la bande passante et peut au contraire exploiter au maximum les capacités de calcul du GPU. Le reste de la réduction est calculé de manière traditionnelle diagonale après diagonale.

Ce schéma de pavage est aussi applicable au code CPU. La bonne localité mémoire est aussi bénéfique sur un processeur traditionnel: elle garantit un faible nombre de défauts de cache. De plus, le code pavé rend relativement aisé une vectorisation du code avec les instructions SSE. Une implémentation sur CPU avec les instructions SSE a été développée. De plus, un second niveau de pavage permet une réutilisation des chargements mémoire au niveau des registres SSE. Le code CPU peut également facilement tirer partie d'une parallélisation multi-coeurs avec openMP en parallélisant sur les différentes cases ou pavés d'une diagonale. Cela permet une vectorisation efficace du code CPU, et donc une comparaison honnête des performances entre CPU et GPU.

#### 2.3 Résultats

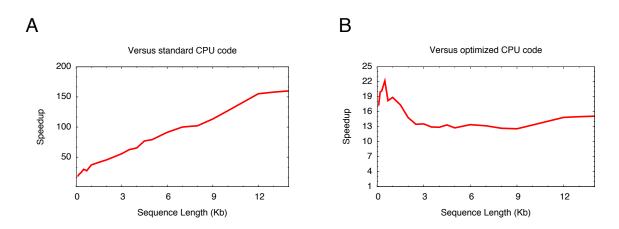

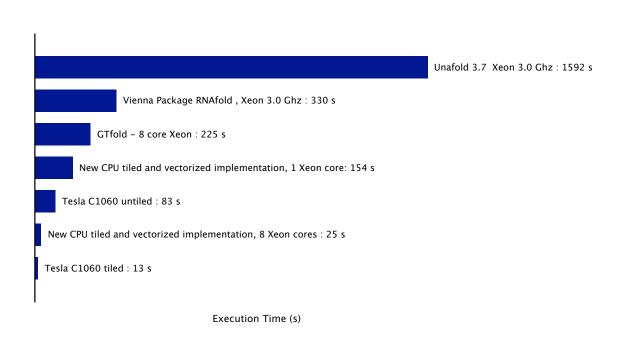

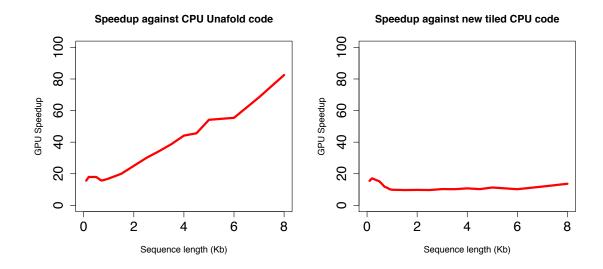

Pour des grandes séquences, le code pavé sur GPU est jusqu'à 150x plus rapide que le code séquentiel UNAfold disponible sur internet. Le code pavé et vectorisé sur CPU est quant à lui jusqu'à 12x plus rapide que UNAfold. Cette accélération provient à la fois de la bonne localité fournie par le pavage et de la vectorisation SSE. Le code CPU vectorisé et parallélisé sur 8 coeurs de CPU est quant à lui "seulement" deux fois plus lent que le code GPU.

Des algorithmes proches du calcul de la structure secondaire optimale existent, en particulier le calcul de structures sous-optimales et la fonction de partition [84, 58]. Nous avons également appliqué notre approche à ces algorithmes et avons obtenus des accélérations similaires.

Notre implémentation GPU pavée va faire l'objet d'un chapitre dans l'ouvrage de NVIDIA "GPU computing gems":

Rizk, G., Lavenier, D., and Rajopadhye, S. (2010). GPU computing Gems, chapter GPU accelerated RNA folding algorithm. Addison-Wesley Professional.

### 2.4 Discussion

Dans ce chapitre, l'objectif était de déterminer s'il était possible d'avoir une implémentation efficace sur GPU du calcul de la structure secondaire de l'ARN. Nous avons développée une première parallélisation "naïve" fortement limitée par la bande passante mémoire de la carte graphique. Nous avons ensuite développé une nouvelle approche pavée de l'algorithme qui fait apparaître une bonne localité mémoire, permettant de passer d'un code limité par la bande passante à un code limité par la puissance brute de la carte. L'accélération obtenue va jusqu'à 150x par rapport au programme UNAfold. Le réponse est donc positive, il est possible de paralléliser efficacement un algorithme de programmation dynamique complexe de l'envergure de l'algorithme de calcul de structure secondaire. Toutefois, le facteur 150x est à prendre avec des pincettes, il ne provient pas uniquement de l'accélération GPU, mais aussi de notre nouvelle approche pavée. Nous avons noté que cette nouvelle approche permettait également une bonne accélération du programme CPU, fournissant ainsi une comparaison honnête des performances entre GPU et CPU. L'accélération GPU par rapport à notre code vectorisé sur CPU est de 2x sur un système octo-coeurs. Cela correspond aux accélérations observées dans [40] quand le code CPU est bien vectorisé. Cela peut paraître une faible accélération mais constitue en réalité déjà une optimisation très intéressante pour les pipelines de bio-informatique nécessitant d'exécuter ce programme de manière intensive.

# Chapitre 3 : Alignement de séquences

L'alignement de séquences est un domaine majeur de la bio-informatique. Avec l'avènement des nouvelles générations de séquenceurs, le développement de nouveaux programmes d'alignements efficaces est plus que jamais une priorité. Dans ce chapitre l'objectif est de déterminer si une parallélisation GPU peut résoudre ce problème efficacement. Nous avons développé une stratégie qui élimine la plupart des alignements potentiels provenant de la phase d'indexation, avant qu'ils aient à être étendus par le coûteux algorithme de programmation dynamique de type Needleman-Wunsch. En revanche, cette approche rend difficile une implémentation GPU efficace. Il a donc été jugé préférable de développer et optimiser la version CPU du programme, qui a aboutit à la création d'un nouveau programme d'alignement, appelé GASSST.

### 3.1 Introduction

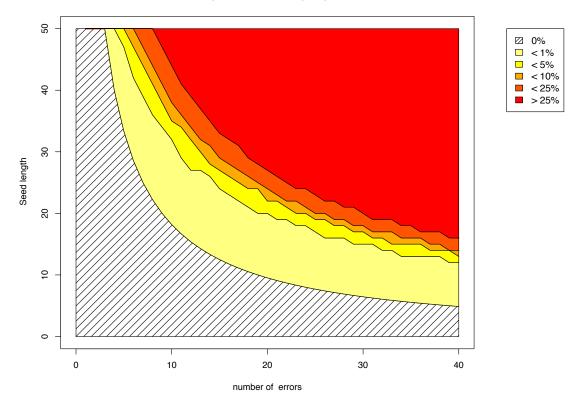

Les nouvelles technologies de séquençage (NGS) produisent de grandes quantités de données. Elles sont utilisées dans un large spectre d'applications, incluant le re-séquençage de génome, la détection de polymorphisme ou l'étude des éléments transcrits. Les données consistent en un grand nombre de petites séquences appelées *reads*. Un problème récurrent est de localiser ces reads dans un génome de référence, en autorisant quelques erreurs, mismatchs, insertions ou délétions. Pour cela, la stratégie *seed and extend* est la plus utilisée en pratique. L'idée est que des alignements significatifs vont inclure des régions avec une correspondance parfaite entre la séquence requête et la séquence de référence. Par exemple, tout alignement de 50 paires de bases avec 3 erreurs contient au moins 12 bases identiques consécutives. En conséquent, dans la stratégie *seed* and extend, seules les séquences partageant des k-mers identiques avec la référence sont considérées comme alignements potentiels. La détection de k-mers communs est par exemple effectuée en utilisant un index localisant tous les k-mers sur la séquence de référence. Ensuite, tous les k-mers chevauchants, appelés graines, de cette séquence sont extraits. Pour chaque graine l'index fournit une liste de positions dans la référence, qui sont autant d'alignements potentiels, appelés CAL pour candidate alignment location. Chaque alignement potentiel doit ensuite être "étendu" pour savoir s'il peut générer un alignement suffisamment similaire. Pour autoriser les insertions/délétions, cette étape est en générale effectuée avec un algorithme de programmation dynamique de type Needleman-Wunsch. Cette méthode bénéficie d'une bonne précision et d'une bonne sensibilité, mais est aussi extrêmement lente à cause du nombre très élevé de coûteuses instances de programmation dynamique à résoudre.

Les solutions utilisées dans la littérature pour accélérer cette stratégie sont l'utilisation de graines espacées ou multiples. C'est par exemple le cas des programmes BFAST [30], SHRiMP [71] et MAQ [44]. Une autre solution développée dans SHRiMP est la vectorisation en SSE du code de programmation dynamique. La principale méthode concurrent à la stratégie *seed and extend* est celle qui utilise un indexation basée sur une transformée de Burrows-Wheeler (BWT) [9]. La méthode utilise une technique appelée *backward search* [22] qui permet d'utiliser l'index pour obtenir des résultats similaires à une recherche utilisant un arbre des suffixes. Cette méthode est utilisée par les programmes Bowtie [38], SOAPv2 [47], et BWA [42]. L'avantage de cette méthode est des temps d'exécution très courts et peu de besoins de mémoire vive, mais elle ne fonctionne bien en général que pour des alignements avec un faible taux d'erreurs.

### 3.2 Principe

Notre objectif est la création d'un nouveau programme d'alignement efficace, fonctionnant dans un grand nombre de situations : avec des reads courts ou longs, et des taux d'erreurs faibles ou élevés. Nous avons exploré deux pistes pour le développement de cet algorithme. Premièrement, une approche par *filtrage*, et deuxièmement, une parallélisation sur GPU.

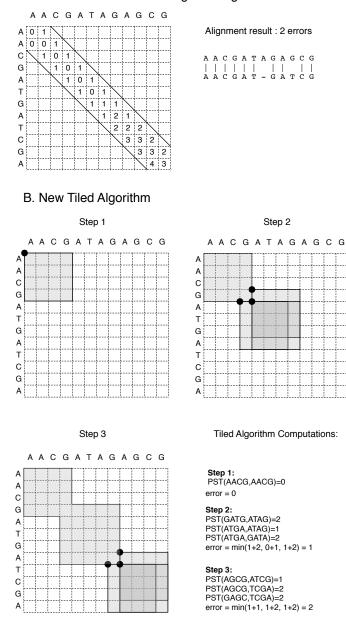

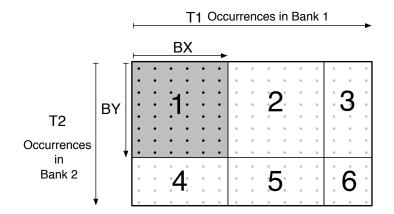

L'approche par *filtrage* vient de l'observation que la plupart des alignements candidats produits par la stratégie *seed and extend* ne génèrent pas de bons alignements. Seul un très faible pourcentage, généralement inférieur à 1%, conduit à des alignements significatifs. De plus, il n'est probablement pas nécessaire d'effectuer le complexe calcul de Needleman-Wunsch pour se rendre compte qu'un alignement va être mauvais. L'idée du filtrage est alors de mettre au point des tests consistant en calculs simples et rapides qui permettent d'éliminer rapidement les alignements candidats avec un faible score de similarité. Les alignements candidats qui passent ces filtres sont ensuite recalculés avec Needleman-Wunsch pour obtenir l'alignement complet. Le filtre que nous avons développé est basé sur l'utilisation de tables de scores pré-calculés qui contiennent le score d'alignement de Needleman-Wunsch de toutes les paires de mots de taille l. En stockant chaque score dans un octet, la taille de la table est de  $4^{2l}$  octets. En pratique, xii

nous utilisons l = 4 ce qui conduit à une table de 64Ko. C'est une table suffisamment petite pour tenir dans les premiers niveaux de cache du processeur et peut donc être accédée très rapidement dans un algorithme. Nous avons développé un nouvel algorithme qui réutilise cette table un grand nombre de fois pour calculer une approximation de l'algorithme de Needleman-Wunsch. En choisissant un schéma de score simple, i.e. 1 pour une erreur, mismatch, insertion ou délétion et 0 sinon, notre algorithme calcule une borne inférieure du score obtenu par Needleman-Wunsch. C'est à dire que l'algorithme détermine une borne inférieure du nombre d'erreurs présentes dans l'alignement. Nos mesures montrent que cette borne est calculée 10 à 100 fois plus vite que le score exact de Needleman-Wunsch. Son utilisation constitue donc un filtre très efficace pour éliminer rapidement des alignements candidats. Le fait que l'algorithme calcule une borne inférieure permet d'éliminer sans se tromper des alignements candidats avec trop d'erreurs. Aucun bon alignement n'est éliminé par le filtre, la sensibilité n'est donc pas diminuée. En revanche, certains alignements avec trop d'erreurs peuvent passer le filtre. Ceux-ci sont éliminés dans la phase finale de l'algorithme ou le calcul exact de Needleman-Wunsch est effectué sur les alignements candidats qui passent le filtre.

La deuxième piste explorée est la parallélisation sur GPU. Il y a deux possibilités pour cette parallélisation : soit la parallélisation de l'approche filtrée, soit la parallélisation de l'algorithme sans filtres. L'algorithme sans filtres est facile à paralléliser sur GPU, mais nos mesures ont montré que l'approche sans filtres est 10 à 100 fois plus lente que l'approche filtrée. Sa parallélisation GPU est donc inutile. L'algorithme filtré est rapide sur CPU, mais est en revanche très difficile à paralléliser efficacement sur GPU: l'utilisation de filtres introduit des divergences dans le traitement des différents alignements candidats: pour certains le calcul s'arrête dès le premier filtre, pour d'autres le traitement passe tous les tests. Le programme ne convient donc plus à un parallélisme de données ou les différents unités de calcul doivent effectuer exactement la même tache, comme c'est le cas sur GPU. Il convient par contre tout de même à un parallélisme de tâches, pour une parallélisation sur multi-coeurs. Pour cette raison nous avons donc décidé d'abandonner la parallélisation GPU de cet algorithme. En revanche, la nouvelle approche filtrée développée a permis la création d'un nouveau programme d'alignement efficace, appelé GASSST, pour *Global Alignment Short Sequence Search Tool*.

#### 3.3 Résultats

Les résultats du programme GASSST ont été comparés en particulier avec ceux des programmes BFAST et BWA qui sont actuellement les plus utilisés. Pour cela, des jeux de données simulés ont été utilisés. Des reads de différentes tailles et taux d'erreurs ont été généres à partir du génome humain. Pour chaque expérience, la sensibilité, la précision et le temps de calcul ont été mesurés. Des jeux de données réels ont aussi été utilisés, pour lesquels la sensibilité ne peut être qu'estimée. Ces évaluations ont montré que le programme GASSST est efficace dans beaucoup de situations différentes: pour des reads courts et longs, avec un taux d'erreurs autorisées dans les alignements faible ou élevé. GASSST est aussi rapide que BWA pour des reads courts avec un faible taux d'erreurs, et devient beaucoup plus sensible pour des taux d'erreurs plus élevés.

Le programme GASSST est disponible en licence CeCILL, et a été l'objet d'un article

dans la revue *bioinformatics* :

Rizk, G. and Lavenier, D. (2010). GASSST: global alignment short sequence search tool. Bioinformatics, 26(20), 2534–2540.

#### 3.4 Discussion

Dans ce chapitre, l'objectif était de déterminer si les GPU pouvaient être utilisés pour créer des algorithmes rapides d'alignement de séquences. Nous avons développé une approche par filtrage qui a donné de très bons résultats mais qui n'a pas pu être parallélisée sur GPU. Le dilemme pour la parallélisation GPU est le suivant: soit paralléliser l'approche non filtrée, qui est régulière et donc efficacement parallélisée sur GPU, mais qui est à la base très lente; soit essayer de paralléliser l'approche filtrée, qui est très rapide mais aussi très difficile à paralléliser. Les deux options menant à une impasse pour la parallélisation GPU, il apparaît donc impossible d'utiliser les GPU pour paralléliser la stratégie *seed and extend*.

## Chapitre 4 : Conclusion

#### 4.1 Contributions

Nous avons contribué à deux problèmes différents: le calcul de structures secondaires d'ARN et l'alignement de séquences générées par les nouvelles technologies de séquençage. Pour le premier problème, nous avons développé un code GPU qui va jusqu'à 150x plus vite que le programme UNAfold. Cela a été rendu possible par l'utilisation d'une méthode de pavage qui fait apparaître un bonne localité mémoire. Nous avons aussi développé un programme CPU qui exploite le pavage et vectorisé en SSE, qui est jusqu'à 10 x plus rapide que UNAfold. Nos méthodes ont également été appliquées au calcul des structures secondaires sous-optimales et au calcul de la fonction de partition. La méthode de pavage que nous avons développée est un bon exemple de ce qu'il faut faire pour obtenir des bonnes performances sur GPU. Tandis que notre première implémentation était limitée par la bande passante et n'utilisait donc qu'une faible fraction des capacités de calcul du GPU, la version pavée n'est plus limitée par la bande passante et utilise donc au maximum les capacités de calcul du GPU. Des méthodes similaires pourraient être utiles à d'autres applications GPGPU. Pour le second problème, l'alignement de séquences, nous avons développé un nouvelle approche filtrée basée sur l'utilisation de tables pré-calculées, qui a conduit à la création du programme GASSST fonctionnant sur CPU.

### 4.2 Perspectives

Pour le repliement d'ARN, il serait possible d'explorer des variations sur la méthode de pavage, apportant éventuellement encore un gain pour le GPU. Il serait également intéressant d'essayer d'appliquer notre méthode à des algorithmes similaires, par exemple ceux qui calculent les structures secondaires avec pseudo-noeuds, ou les algorithmes calculant d'autres classes de structures sous-optimales. Pour l'alignement de séquences, il semble possible d'optimiser davantage le programme GASSST. Dans un premier temps, il serait possible d'essayer des méthodes d'indexation plus élaborées, telles que des graines espacées. Il serait aussi utile d'étudier l'impact de l'utilisation de schéma de scores plus complexes pour notre approche de filtrage. Bien qu'il semble difficile pour la méthode actuelle d'intégrer des scores plus complexes (avec un coût différent pour le début ou l'extension d'une délétion), des méthodes approchées pourraient être développées. Plus généralement, il reste probablement de nombreuses pistes à explorer pour accélérer l'alignement de séquences. La stratégie seed and extend bénéficie d'une bonne sensibilité, mais souffre aussi d'une certaine lourdeur: elle génère un très grand nombre d'alignements candidats, générant beaucoup de calculs inutiles. Pour obtenir de meilleures performances, il semble nécessaire d'élaborer une stratégie radicalement différente.

### 4.3 Discussion

La problématique de cette thèse est de déterminer si les algorithmes utilisés en bioinformatique peuvent ou non être efficacement implémentes sur GPU. Par l'étude de deux problèmes différents, il nous est possible d'avoir un début de réponse à cette question. Pour les algorithmes de calcul intensif du type de l'algorithme de repliement d'ARN, les GPU peuvent fournir une implémentation efficace, même s'il peut être difficile d'exposer une bonne localité mémoire, nécessaire pour obtenir des bonnes performances. En revanche, pour le domaine du traitement des séquences en général, la réponse est non. Plusieurs facteurs en sont la cause: premièrement ils nécessitent en général la manipulation de grandes quantités de données, qui peuvent être longs à transférer sur GPU. Deuxièmement, l'intensité arithmétique ( le ratio entre le nombre d'opérations et la quantité de transactions mémoire) est en générale faible, ce qui conduit à une sous-utilisation de la puissance de calcul des GPUs. Troisièmement, des structures de données complexes sont souvent utilisées, qui requièrent des accès aléatoire à la mémoire, et donc induisent une faible bande passante sur GPU.

En ce qui concerne les performances, dans notre cas le code GPU est environ équivalent à 16 coeurs de CPU. C'est moins qu'espéré initialement, mais déjà un bon résultat si on compare le coût de fonctionnement d'un GPU et de 16 coeurs de CPU. Enfin, la question du temps de développement sur GPU est importante. Notre expérience a montré que les temps de développement sur GPU sont assez longs, du fait d'un grand nombre de paramètres à tester et optimiser. Bien que subjectif, car fortement dépendant de l'expérience de chacun, il nous semble plus simple de paralléliser pour des instructions vectorielles SSE que pour GPU. Comme les instructions vectorielles des CPU fournissent déjà un gain de performance significatif, il semble judicieux pour de nombreux algorithmes de commencer par une implémentation SSE que par un portage sur GPU.

# Contents

| Re       | ésum | lé étendu                                                                                                 | iii       |

|----------|------|-----------------------------------------------------------------------------------------------------------|-----------|

| In       | trod | uction                                                                                                    | 1         |

| 1        | Arc  | hitecture                                                                                                 | <b>5</b>  |

|          | 1.1  | Common concepts                                                                                           | 5         |

|          |      | 1.1.1 Throughput                                                                                          | 5         |

|          |      | 1.1.2 Bandwidth $\ldots$ | 6         |

|          |      | 1.1.3 Latency                                                                                             | 8         |

|          |      | 1.1.4 Analysis $\ldots$  | 8         |

|          | 1.2  | Platforms                                                                                                 | 9         |

|          |      | 1.2.1 CPU                                                                                                 | 9         |

|          |      | 1.2.2 GPU                                                                                                 | 10        |

|          |      | 1.2.3 CPU/GPU comparison                                                                                  | 13        |

| <b>2</b> | Opt  | imization case study: Smith Waterman algorithm                                                            | 15        |

|          | 2.1  | Smith Waterman algorithm                                                                                  | 15        |

|          | 2.2  | VLSI accelerators                                                                                         | 16        |

|          | 2.3  | FPGA accelerators                                                                                         | 16        |

|          | 2.4  | CPU vectorization                                                                                         | 17        |

|          | 2.5  | Cell                                                                                                      | 18        |

|          | 2.6  | GPU                                                                                                       | 18        |

|          | 2.7  | Four-Russians speedup                                                                                     | 19        |

|          | 2.8  | Discussion                                                                                                | 19        |

| 3        | RN.  | A folding                                                                                                 | <b>21</b> |

|          | 3.1  | Main algorithm                                                                                            | 21        |

|   |      | 3.1.1    | Problem Statement                                                                              | 21 |

|---|------|----------|------------------------------------------------------------------------------------------------|----|

|   |      | 3.1.2    | Recurrence equations                                                                           | 23 |

|   | 3.2  | Relate   | d work                                                                                         | 25 |

|   |      | 3.2.1    | Alternative approaches                                                                         | 25 |

|   |      | 3.2.2    | Parallelization                                                                                | 26 |

|   | 3.3  | Algori   | thm profiling                                                                                  | 27 |

|   | 3.4  | First i  | mplementation                                                                                  | 28 |

|   |      | 3.4.1    | General parallelization scheme                                                                 | 28 |

|   |      | 3.4.2    | $\mathcal{O}(n^2)$ part: Internal loops                                                        | 30 |

|   |      | 3.4.3    | $\mathcal{O}(n^3)$ part: Multi-loops                                                           | 30 |

|   | 3.5  | Multi    | loops second implementation                                                                    | 31 |

|   |      | 3.5.1    | Reduction split and reordering                                                                 | 31 |

|   |      | 3.5.2    | Tiling scheme                                                                                  | 32 |

|   |      | 3.5.3    | GPU implementation                                                                             | 32 |

|   | 3.6  | CPU r    | new implementation                                                                             | 34 |

|   | 3.7  | Result   | s                                                                                              | 36 |

|   |      | 3.7.1    | Tiled implementation                                                                           | 36 |

|   |      | 3.7.2    | Overall comparison                                                                             | 37 |

|   |      | 3.7.3    | Multi-GPU implementation                                                                       | 41 |

|   | 3.8  | Relate   | d algorithms                                                                                   | 41 |

|   |      | 3.8.1    | Sub-optimal foldings                                                                           | 41 |

|   |      | 3.8.2    | Partition function                                                                             | 47 |

|   | 3.9  | Applic   | ations                                                                                         | 49 |

|   |      | 3.9.1    | MicroRNAs Prediction                                                                           | 49 |

|   | 3.10 | Discus   | sion $\ldots$ | 50 |

| 4 | Sho  | rt Seq   | uence Alignment                                                                                | 53 |

|   | 4.1  | Proble   | m presentation                                                                                 | 53 |

|   |      | 4.1.1    | Problem definition                                                                             | 54 |

|   | 4.2  | State of | of the art                                                                                     | 55 |

|   |      | 4.2.1    | Seed Based Algorithms                                                                          | 55 |

|   |      | 4.2.2    | Algorithms based on suffix tries                                                               | 57 |

|   | 4.3  | Startir  | ng point                                                                                       | 57 |

|   | 4.4 | Prelim | inary work                          | 58  |

|---|-----|--------|-------------------------------------|-----|

|   |     | 4.4.1  | Profiling of the sequential code    | 58  |

|   |     | 4.4.2  | Major optimization: Tiled-NW filter | 59  |

|   |     | 4.4.3  | Analysis                            | 63  |

|   | 4.5 | GPU a  | approach                            | 63  |

|   |     | 4.5.1  | Parallelization scheme              | 63  |

|   |     | 4.5.2  | Key optimizations                   | 65  |

|   |     | 4.5.3  | Results                             | 67  |

|   | 4.6 | CPU a  | approach                            | 67  |

|   |     | 4.6.1  | Overview                            | 67  |

|   |     | 4.6.2  | Seed                                | 68  |

|   |     | 4.6.3  | Tiled-NW filter                     | 69  |

|   |     | 4.6.4  | Frequency vector filter             | 69  |

|   |     | 4.6.5  | Filters combination                 | 70  |

|   |     | 4.6.6  | Duplicate alignments                | 71  |

|   |     | 4.6.7  | Long reads                          | 71  |

|   |     | 4.6.8  | Extend                              | 73  |

|   |     | 4.6.9  | Task parallelism                    | 73  |

|   | 4.7 | Result | S                                   | 73  |

|   |     | 4.7.1  | Implementation                      | 73  |

|   |     | 4.7.2  | Evaluated Programs                  | 73  |

|   |     | 4.7.3  | Evaluation on real data             | 74  |

|   |     | 4.7.4  | Evaluation on simulated data        | 75  |

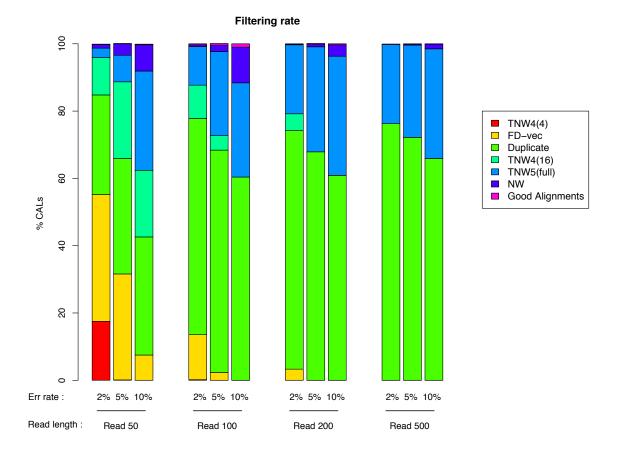

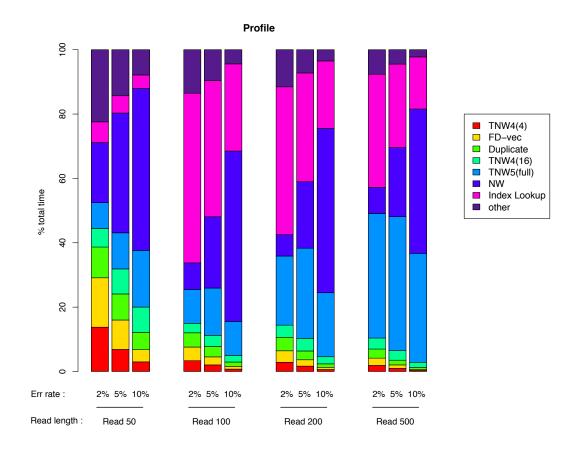

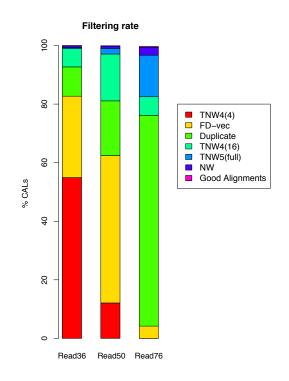

|   |     | 4.7.5  | Filter behavior analysis            | 77  |

|   |     | 4.7.6  | Hash table statistics               | 82  |

|   | 4.8 | Discus | sion                                | 84  |

| - | C   | ,      | , .                                 | 0 7 |

| 5 |     |        | onclusion                           | 87  |

|   | 5.1 |        | butions                             | 87  |

|   | 5.2 |        | sion                                | 88  |

|   |     | 5.2.1  | General design rules                | 88  |

|   | •   | 5.2.2  | GPU evaluation                      | 88  |

|   | 5.3 | Future | eworks                              | 91  |

| Appendix            | 92   |

|---------------------|------|

| Α                   | 93   |

| A.1 Theorem proof   | . 93 |

| A.2 Test Parameters | . 94 |

| Bibliography        | 98   |

| List of Figures     | 107  |

| List of Tables      | 109  |

| List of algorithms  | 111  |

# Introduction

#### Context

Bioinformatics deals with techniques to analyze biological data. Common fields include DNA or protein sequence alignments, analysis and comparison of protein or RNA structures. For all these fields, the amount of data available has been growing exponentially in the past decades.

As regards DNA sequencing, progress has been very fast. The double helix structure of the DNA was discovered in 1953 by Watson and Crick. The first organism to be sequenced was the bacteriophage  $\phi$  X 174 composed of 5386 bases in 1977. The first draft of the human genome, more than 3 billion base-pair long, was released in 2000 at a cost of several billion of dollars. With nowadays next generation sequencing technologies, several giga base-pairs can be sequenced in a single run for approximately 10K\$.

As a consequence, database size has grown exponentially. More and more data need to be analyzed. Furthermore, because of the dramatically decreasing sequencing costs and comparatively much slower evolution of storage capacity, it has sometimes become paradoxically cheaper to re-sequence than to store the sequence for later reuse. This stresses the need to analyze huge quantities of data on the fly, and store only interesting results. Moreover, CPU performance is not keeping up with this evolution. As a result, program execution takes more and more time and biologists are facing increasingly serious storage issues.

Contrary to the past, we cannot just wait for the next generation of processors to speed up slow sequential programs. In the past, ever increasing processor frequencies provided easy to use new processing power. This trend has now reached a dead-end, for two main reasons: the *memory wall* and the *power wall*. The former is the increasing gap between memory and processor speed, requiring larger and larger cache memories. The latter is the exponentially increasing power consumption as frequency increases.

The only way left to get more processing power is through parallelism. The first solution is the use of multi-core CPUs and clusters of computers. While effective, this is also an expensive solution. Another solution is the use of high performance specialized hardware. For example FPGAs are able to provide very high performance, but still suffer from high development costs.

Yet another solution comes from Graphic Processing Units (GPU). A GPU is a specialized processor designed to accelerate the rendering of graphics on screen. It is a highly data-parallel problem: identical computations need to be executed on many vertices and pixels. Therefore, GPUs were designed as massively data-parallel architectures: they are composed of many computational units able to apply the same computation efficiently on different input data. Moreover, from fixed basic graphic functionality, GPUs gradually included more and more programmability options to allow game programmers to generate more realistic effects. This programmability and flexibility came to a point where non-graphic computation became also possible, giving birth to General Purpose computing on Graphics Processing Units (GPGPU). NVIDIA introduced in November 2006 the CUDA programming language designed entirely to facilitate GPGPU on their GPUs.

Using GPUs for standard computation has many advantages. First, strong competition driven by the game industry lead to cheap GPUs, and ever-increasing processing power. Every standard computer can be fitted with a high-end GPU, dramatically increasing its total computational power at a low cost. Secondly, GPUs are naturally well suited for any massively data parallel problem, arising in many scientific research domains. This includes computational fluid dynamics, medical imaging, finance, signal processing, cryptanalysis. Bioinformatics also exhibits a lot of data parallelism: the analysis of large data sets often requires to apply the same computation on different data. A priori it therefore seems natural to use GPUs to speed up bioinformatics applications.

### Objectives

The objective of this thesis is to estimate GPU capabilities in typical bioinformatics applications. Our study focuses on two different problems, the computation of RNA structures and sequence alignments. Both have already been studied for a long time by the scientific community, but still poses computational issues, because of the rapid growth of biological data.

The fact that a problem shows a high level of data parallelism is not enough to predict that GPUs will be effective in practice. In fact, GPU architecture has many specificities that restrict the scope of possible applications. Our objective is also to evaluate the impact of these GPU specificities.

The evaluation of GPU has to be conducted on several different aspects. First, an important point is the development time required for an efficient GPU implementation. For instance, GPUs are a priori easier to program than FPGAs, but more difficult than CPUs. This needs to be evaluated in practice. Secondly, the execution speed. For a fair evaluation, GPU contribution needs to be compared with optimized CPU code. In particular, comparison with the vector computation units of CPU has to be conducted. Nowadays, all CPUs contain vector units able to provide small scale data parallelism, but still rarely used in practice. Then, the cost. Both the device initial cost and running costs need to be considered. The latter is directly dependent on power consumption, hence often evaluated as a performance per watt ratio.

Finally, the objective is more than just a GPU evaluation. It is also to develop, if possible, general methods to transform efficiently a program for an efficient GPU implementation. Techniques developed for the GPU implementation of the two problems studied here might prove to be useful for other unrelated problems using similar algorithmic schemes.

## Outline

**Chapter 1** - This first chapter explains the operating principles of the GPU hardware. Comparing it with the traditional CPU architecture enables to shed light on the strong and the weak points of GPUs. In a first part, the basic characteristics—computational power, latency, bandwidth—are introduced and detailed. Then, GPU specificities are explained.

**Chapter 2** - This chapter is an optimization case study of what can be done with various high performance hardware on a well known bioinformatic algorithm: the Smith-Waterman algorithm, which computes optimal sequence alignments. This review shows the advantages and drawbacks of different hardware and puts GPU performance in perspective. It also provides a state of the art of parallelization methods for dynamic programming algorithms.

**Chapter 3** - In this chapter, we present our first contribution: the GPU implementation of the RNA folding computation. This computation is conducted with a dynamic programming (DP) algorithm. Although other DP algorithms have already been successfully implemented on GPU, the RNA folding computation poses significant challenges: complex data dependency scheme and memory access pattern. We introduce here a new tiled implementation which provides highly efficient GPU implementation. This tiled scheme is also applied to a CPU implementation, fully optimized with the use of vectorized instructions. Algorithms computing sub-optimal foldings and partition function were also studied and implemented on GPU and vectorized on CPU.

**Chapter 4** - Our second contribution is developed in this chapter: the design of a new sequence alignment program. More precisely, the short read mapping problem, coming with the advent of next generation sequencing technologies, is targeted. After a state of the art of the short read mapping techniques, we introduce our attempt at GPU parallelization. Our main contribution is the development of a new algorithm filtering candidate alignment positions quickly, based on the precomputation of tiles of the dynamic programming matrix. This new algorithm proved to be in fact more effective on a sequential CPU program and lead to the creation of the GASSST software, standing for Global Alignment Short Sequence Search Tool.

# Chapter 1

# Architecture

Our objective is to accelerate bioinformatics programs through the use of highperformance commodity hardware: GPUs. The first step is to study the hardware in details, to know its weak and its strong points and to see how it competes with traditional CPU architectures.

First in section 1.1 the basic notions required to compare different architectures are detailed. We distinguish three main characteristics: raw power computation, memory bandwidth and latency. We explain how these characteristics impact the total execution time of a program and how they differ between GPU and CPU architectures.

Then in section 1.2 the CPU and GPU devices used in our work are presented. The different forms of parallelization provided by CPU are quickly explained, and GPU specificities are described. Finally GPU and CPU differences are discussed.

#### 1.1 Common concepts

The total execution time of a program depends on many factors. In this section, we will address the hardware point of view. For a given program, which hardware characteristics determine the speed at which it will be executed ?

We distinguish three main characteristics: raw power computation, memory bandwidth and latency. These features are important because they give the basis for comparing different architectures. If the performance of each architecture are known on each of these characteristics, and also how the execution speed of a program is related to them, we can determine the theoretical speedup which can achieved when moving from one architecture to another.

#### 1.1.1 Throughput

*Throughput* is the computational raw power of an architecture. It is the number of operations that can be executed within a given time. Architecture manufacturers usually give figures in operations per clock cycle. Sometimes *reciprocal throughput* is given, i.e. the average number of cycles it takes to perform an operation.

Some processors are designed to perform multiple operations on each clock cycle, greatly increasing their computational throughput. We distinguish three classes, possibly cumulative: scalar, vector and superscalar processors.

- Scalar processors. Instructions handle a single data item at a time, therefore the maximum number of operations per clock cycle is one.

- *Vector* processors. Each instruction operates simultaneously on many data items. The processor is therefore able to perform several operations at each clock cycle.

- Superscalar processors. Such processors can execute several different instructions on each clock cycle by dispatching instructions to several functional units contained in the processor. Again, the processor is able to perform several operations per clock, possibly of different kinds.

Current processors are usually both *superscalar* and *vector* processors, with several Arithmetic Logic Units (ALU), Floating Point Units (FPU), and vector units.

Multiplying operations per clock cycle by the clock rate returns operations per seconds, usually defined as Giga Floating point Operations per Seconds (GFLOPS) or GOPS for other operations.

Table 1.1 shows the throughput for different operations on several architectures. Figures are computed from the Nvidia and Intel optimization guides providing the throughput in operation per clock cycle [31, 63]. For the Xeon, we display the overall throughput when using the four cores of the CPU. Those are only theoretical maximum values and are sometimes in fact only obtained for very special cases.

For example the 38.4 GOPS of the Xeon for the 32-bit *add* (without using SSE) is obtained with the formula 4 cores  $\times 3.2$  Ghz  $\times 3$  execution units. The XeonX5482 is indeed able to dispatch an integer *add* to any of three execution units and therefore able to perform 3 integer *add* each cycle. This peak *add* throughput can be reached only if the processor finds 3 independent instructions in the code at each clock cycle, which is highly unlikely.

The GPU hardware possesses fixed function units for the computation of transcendental operations like *exp*, *log*, *cos*, ..., whereas those operations are evaluated through algebraic expressions in CPU. This explains the huge difference showed table 1.1 for *cos*: the Tesla C1060 is hundreds of times faster than the Xeon. Other than this special case, Tesla C1060 peak throughput is between 3 and 6 times that of the quad core Xeon using SSE for 32-bit operations. In practice the actual speedup will of course depends on how much of this peak throughput each architecture is able to harness.

Besides, computation throughput is not the only factor to consider, as we shall see next.

#### 1.1.2 Bandwidth

Bandwidth is the amount of data transferred per unit of time, usually expressed in Gbits/sec (Gb/s) or GBytes/sec (GB/s).

| Operation                     | Tesla C870 | Tesla C1060 | Xeon X5482     | Xeon X5482, with SSE |

|-------------------------------|------------|-------------|----------------|----------------------|

| 32-bit integer add            | 166.4      | 312         | 38.4           | 102.4                |

| 32-bit floating point add     | 166.4      | 312         | 12.8           | 51.2                 |

| 32-bit floating point divide  | 18 - 36    | 34 - 68     | $\approx 0.64$ | $\approx 2.56$       |

| 32-bit floating point cosinus | 41.6       | 78          | $\approx 0.15$ | -                    |

| 64-bit floating point add     | -          | 39          | 12.8           | 25.6                 |

| peak 32-bit GFLOPS, best case | 332.8      | 624         | 25.6           | 102.4                |

| peak 64-bit GFLOPS, best case | -          | 78          | 12.8           | 51.2                 |

Table 1.1. Instruction Throughput on GPU and CPU

Instruction Throughput is given in giga operations per seconds. Figures are inferred from NVIDIA and Intel optimization guides [31, 63]. The best GFLOPS case is attained with multiply-add operations. The claimed GFLOPS peak is sometimes 933 for the the Tesla C1060 when mixing multiply-add and mul operations, but this does not appear to work in practice, even on simple kernels [personal tests].

Table 1.2. Maximum theoretical and measured bandwidth

| Model                                             | peak in $\rm GB/s$ | Measured      | formula                                                |

|---------------------------------------------------|--------------------|---------------|--------------------------------------------------------|

| GPU C870                                          | 76.8               | 60.5          | 384 bit bus $\times$ 1.6Ghz / 8                        |

| GPU C1060                                         | 102.4              | 81.6          | 512 bit bus $\times$ 1.6Ghz / 8                        |

| GPU GTX280                                        | 140.8              | 114           | 512 bit bus $\times$ 2.2Ghz / 8                        |

| CPU Xeon 5400                                     | 10.6               | $\approx 4.5$ | 64 bit bus $\times$ 1.3Ghz FSB / 8                     |

| CPU Xeon 5500                                     | 32.0               | -             | 64 bit bus $\times$ 1.3Ghz FSB $\times$ 3 channels / 8 |

| PCI 2.0 16x                                       | 8                  | 5.7           | -                                                      |

| GPU C1060 shared memory <sup><math>a</math></sup> | 41.6               | -             | 32 bit $\times$ 0.65Ghz $\times$ 16 banks /8           |

| Xeon 5500 L1 cache <sup>b</sup>                   | 51.2               | -             | 128 bit $\times$ 3.2Ghz /8                             |

Bandwidth between memory and processor for several GPU and CPU models, and over the PCI link between GPU and CPU. Figures are given in GB/sec with  $GB=10^9$  bytes. Second column is actual measured bandwidth with handwritten benchmarks. Last column shows the formula used to compute the peak bandwidth.

<sup>a</sup> Bandwidth per GPU multiprocessor, C1060 has 30 MP.

<sup>b</sup> L1 bandwidth per CPU core.

Schematically, data transfers happen to feed the processor with data stored in the memory, and to store back results. The actual situation is however quite complex, because of the complex memory hierarchy in a typical system. Bandwidth can refer to transfers between main memory and processor, between L1 or L2 cache and processor, or between CPU and GPU main memory over the PCI bus.

Table 1.2 shows the maximal theoretical bandwidth for the memory to processor transfer of various GPU and CPU. GPU bandwidth is approximately ten times greater that Xeon 5400 bandwidth. However, with the new *nehalem* architecture, CPU bandwidth has also recently seen a large increase.

Depending on the arithmetic intensity (the ratio of arithmetic operations over memory operations) the memory bandwidth or the computational throughput can be the bottleneck. For example, with the Tesla C1060, according to peak throughput and bandwidth, a program has to perform at least 24 floating point operations per memory load/store to reach the full GFLOPS peak. However, if the working set of an algorithm fits in the on-chip storage, data can be loaded once and reused several times. In this case, main memory bandwidth is less often a limitation.

| GPU main memory<br>CPU main memory<br>Xeon 5482 L1 cache                                                       | Latency, in clock cycles<br>400-800<br>$\approx 100$<br>3<br>14 |

|----------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------|

| Xeon 5482 L2 cache<br>Xeon 5482 floating point add<br>Xeon 5482 floating point divide<br>Xeon 5482 integer add | $\begin{array}{r} 14 \\ \hline 3 \\ 6-20 \\ 1 \end{array}$      |

Table 1.3. Latency table

Indicative latency of different memories and some CPU instructions.

#### 1.1.3 Latency

Latency is the time delay between issuing an operation and receiving its result. It is usually expressed in nano-sec or in clock cycles.

First, it concerns any processor instructions, and tells the time it takes to finish some computation. In a non-pipelined system, latency of the instructions equals the reciprocal throughput. On the contrary, in a pipelined architecture, the processor does not have to wait for the result of an operation before issuing the next instruction. In this case, *latency* and *throughput* are different and should not be confused.

Secondly, latency concerns memory transactions: the time delay between asking for some data and actually receiving it. In this case latency greatly depends on the memory physical location: off-chip memory latency is several orders of magnitude higher than on-chip memory latency.

Table 1.3 gives the indicative latency of several different memory operations and instructions.

#### 1.1.4 Analysis

In a purely sequential system latency is a major issue. For example if an operand resides in main memory, the latency will be high and the processor will stall until it becomes available. Similarly, if some operand is the result of a previous computation, the processor will stall until this previous operation is complete.

The first solution to reduce memory-induced latency is the use of a hierarchical memory system: L1, L2 and sometimes L3 cache between the CPU registers and the main memory. Data used often will reside in small memory closer to the CPU and thus have lower access latency. Since this solution works well, CPU caches have seen their size increased a lot in the past few years.

A second solution to the latency problem is the *out-of-order* execution implemented in most CPUs. It consists in reordering differently instructions of a program: if some instruction is waiting for some operand, the processor will try to execute another upcoming instruction of the program. In that case, some latency is effectively hidden. This reordering depends on the amount of Instruction Level Parallelism (ILP) of the program—ILP measures how many instructions a program can perform simultaneously. In a series of dependent operations the processor will not be able to re-order instructions.

Yet another solution is to exploit task-parallelism. If a task is waiting for some data, the processor will execute instructions from another task—i.e. another thread—so that the processor is not stalled. This is implemented by Intel with their *hyper-threading* technology.

Likewise in the highly parallel GPU architecture, the hardware is often able to effectively hide most of the latency, as we shall see in next section detailing the GPU architecture.

#### 1.2 Platforms

In this section the CPU and GPU architectures used for our experiments are presented.

#### 1.2.1 CPU

#### Description

Experiments were mainly conducted on an 8-core system composed of two quad-core Xeon E5430. It was introduced by Intel in November 2007 and is based on a *core microarchitecture* using a 45nm fabrication process.

Each Xeon E5430 contains 4 CPU cores. There are 32KB of L1 data cache per core, and 6MB of L2 cache shared between two cores. The Xeon E5430 runs at 2.66Ghz, and some tests were also ran on the E5482 variant running at 3.2Ghz.

#### Task parallelism

**Definition 1.** Task parallelism is an execution scheme where multiple processing elements are working on different independent tasks.

This form of parallelization is handled by the different cores of the CPU. It is traditionally conducted with the POSIX threads (Pthreads) or OpenMP APIs.

#### Data parallelism

**Definition 2.** Data parallelism is an execution scheme where multiple processing elements are executing the same task on different data.

Current Intel processors exploit data parallelism with a set of instructions working with vectors, i.e. the same instruction is applied on each vector element. This is a Single Instruction Multiple Data (SIMD) system. The instruction set is called Streaming SIMD Extension (SSE). Xeon E5430 includes SSE up to version 4.1. Vectors are 128 bit wide, meaning that four 32-bit floating point operations can be handled simultaneously, or up to sixteen 8-bit integer operations.

The first way to implement SSE in a program is directly via the corresponding assembly code. It is obviously the most challenging approach, but potentially yielding the best results.

The second way is through the use of *intrinsics*. It is an API extension set built into the compiler giving access to the low-level SIMD instructions. It makes possible an easy implementation in a C/C++ program and, contrary to direct assembly code, relieves programmer from tedious register management.

The last way is via automatic vectorization handled by the compiler itself. This obviously does not work in all cases and is an ongoing field of research.

#### 1.2.2 GPU

The GPU architecture we used is the Compute Unified Device Architecture (CUDA) developed by NVIDIA. It combines high performance with the ease of use of a C-like environment with the C for  $CUDA^1$  programming language [63].

GPUs are massively parallel architectures providing cheap high performance computing, originally designed for image processing. Their first use for general computing were done through the use of graphic programming languages like openGL, which has the advantage of running on all graphic cards. However, this approach requires the painful work of mapping algorithms into graphic concepts and is not fully efficient. That is why GPU vendors have developed specific programming languages for general computation, CTM (Close To Metal) for AMD, C for CUDA for NVIDIA, and more recently OpenCL by the Khronos consortium which aims at providing one universal computation language for all graphic cards.

Shortly speaking, GPUs trade the high amount of transistors devoted to on-chip memory cache and flow-control in traditional CPUs for more processing units. Instead, they rely on multithreading to hide latency, which requires a high arithmetic intensity (many calculations per memory access) to work efficiently.

#### Description

Work was conducted with two generations of NVIDIA graphic cards, G80 and GT200. The latest Fermi architecture was not available at development time.

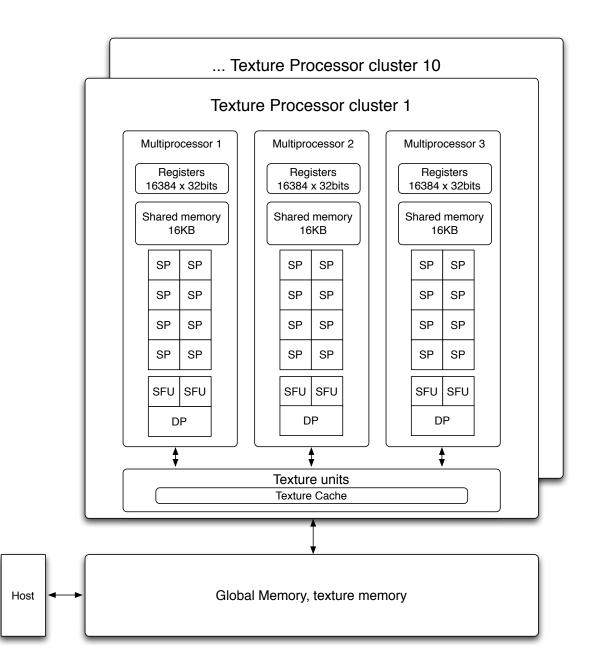

The GT200 is divided into 30 multiprocessors each being a SIMD unit of 8 32bit scalar processors (SP), as shown figure 1.1. Each multiprocessor also contains one double-precision execution unit, two special function units (SFU) dedicated to transcendental functions, and a single instruction fetch unit.