# Component-based Modeling of Heterogeneous Real-time Systems in BIP

Ananda Basu

# ▶ To cite this version:

Ananda Basu. Component-based Modeling of Heterogeneous Real-time Systems in BIP. Computer Science [cs]. Université Joseph-Fourier - Grenoble I, 2008. English. NNT: . tel-00527491

# HAL Id: tel-00527491 https://theses.hal.science/tel-00527491

Submitted on 19 Oct 2010

HAL is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# Université Joseph Fourier – Grenoble 1

# THÈSE

pour obtenir le grade de

# Docteur de l'Université Joseph Fourier

Spécialité : Informatique

préparée au laboratoire VERIMAG dans le cadre de l'École Doctorale (Mathématiques et Informatique)

présentée et soutenue publiquement par

# Ananda Shankar Basu

le 15 December 2008

# Modélisation à base de Composants de Systèmes Temps réel Hétérogènes en BIP (Component-based Modeling of Heterogeneous Real-time Systems in BIP)

### **JURY**

| Président          | Jean Bernard Stefani | INRIA                            |

|--------------------|----------------------|----------------------------------|

| Rapporteurs        | Janos Sztipanovits   | University of Vanderbuilt, USA   |

|                    | Mathai Joseph        | Tata Consultancy Services, India |

| Examinateurs       | Lothar Thiele,       | ETH, Zurich                      |

|                    | Marc Pouzet          | LRI, Paris Sud                   |

|                    | Marius Bozga,        | Verimag                          |

| Directeur de thése | Joseph Sifakis,      | Verimag                          |

# Contents

| Pı       | refac        |                                            | v  |  |  |  |

|----------|--------------|--------------------------------------------|----|--|--|--|

| Ι        | Co           | ncepts and Methodology                     | 1  |  |  |  |

| 1        | Introduction |                                            |    |  |  |  |

|          | 1.1          | State of the Art                           | 4  |  |  |  |

|          | 1.2          | Shortcomings                               | 6  |  |  |  |

|          |              | 1.2.1 Encompassing Heterogeneity           | 7  |  |  |  |

|          |              | 1.2.2 Achieving Constructivity             | 8  |  |  |  |

|          | 1.3          | Key Issues of Component-Based Construction | 9  |  |  |  |

|          | 1.4          |                                            | 10 |  |  |  |

|          | 1.5          |                                            | 11 |  |  |  |

| <b>2</b> | Cor          | ponent Composition in BIP                  | 13 |  |  |  |

|          | 2.1          | Basic Ideas                                | 13 |  |  |  |

|          |              | 2.1.1 Incrementality                       | 16 |  |  |  |

|          |              | 2.1.2 Compositionality                     | 17 |  |  |  |

|          |              | 2.1.3 Composability                        | 17 |  |  |  |

|          | 2.2          | Abstract Model of BIP                      | 17 |  |  |  |

|          |              | 2.2.1 The 3-Tier Architecture              | 18 |  |  |  |

|          |              | 2.2.2 Abstract Semantics                   | 18 |  |  |  |

|          | 2.3          | Concrete Model of BIP                      | 23 |  |  |  |

|          |              | 2.3.1 Modeling Behavior                    | 23 |  |  |  |

|          |              | 2.3.2 Modeling Interactions                | 24 |  |  |  |

|          |              | 2.3.3 Modeling Priority                    | 30 |  |  |  |

|          | 2.4          | Classification of Systems                  | 37 |  |  |  |

|          |              | 2.4.1 Timed Systems                        | 37 |  |  |  |

|          |              | 2.4.2 Synchronous Systems                  | 45 |  |  |  |

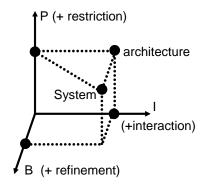

|          | 2.5          | The System Construction Space              | 47 |  |  |  |

|          | 2.6          | Distributed Model of BIP                   | 49 |  |  |  |

|          |              | 2.6.1 Basic Concepts                       | 50 |  |  |  |

|          |              |                                            | 53 |  |  |  |

ii *CONTENTS*

|    |     | 2.6.4  | Partial State Semantics with Oracles                                                   |            |

|----|-----|--------|----------------------------------------------------------------------------------------|------------|

|    |     |        |                                                                                        |            |

| II | Im  | plem   | entation: Language and Tool-chain                                                      | 59         |

| 3  | The | BIP    | Language                                                                               | 61         |

|    | 3.1 | Basic  | Language Elements                                                                      | 62         |

|    | 3.2 | Mode   | eling Atoms                                                                            | 63         |

|    |     | 3.2.1  | Port Type                                                                              | 63         |

|    |     | 3.2.2  | Atomic Type                                                                            | 63         |

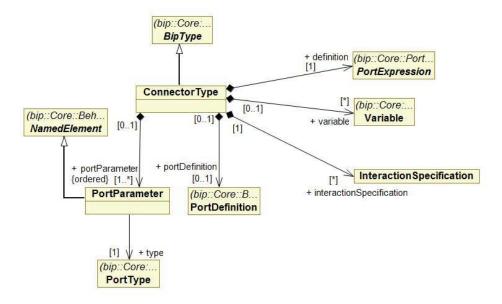

|    | 3.3 | Mode   | cling Connectors                                                                       | 67         |

|    |     | 3.3.1  | Connector Type                                                                         | 67         |

|    | 3.4 | Mode   | eling Compounds                                                                        | 70         |

|    |     | 3.4.1  |                                                                                        | 70         |

|    | 3.5 | Mode   | eling Priority                                                                         | 72         |

|    | 3.6 |        | eling Timed Systems: Timed Guards                                                      | 73         |

|    | 3.7 |        | 78                                                                                     | <b>7</b> 4 |

|    | 3.8 |        | age and System                                                                         | 75         |

|    | 3.9 |        | ession and Statement                                                                   | 77         |

| 4  | The | BIP    | Tool-Chain                                                                             | 79         |

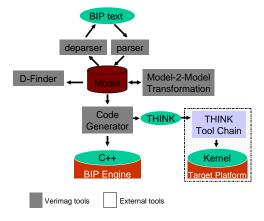

|    | 4.1 | Overv  | view of the Tool-Chain                                                                 | 79         |

|    | 4.2 | The I  | Frontend                                                                               | 80         |

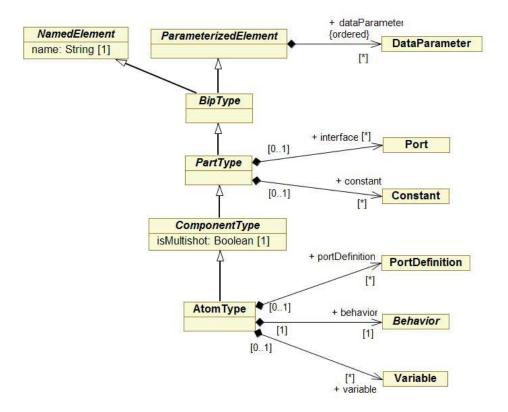

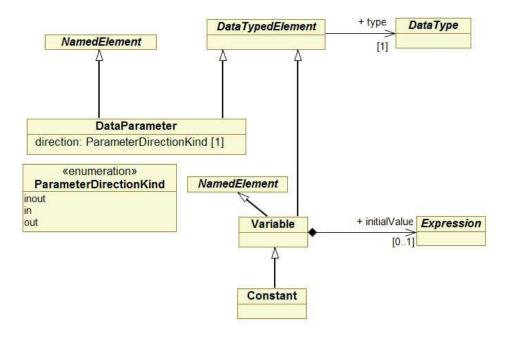

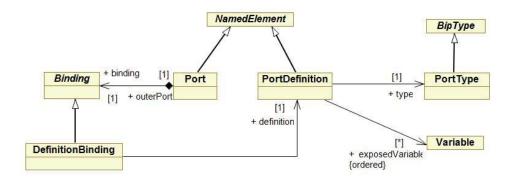

|    |     | 4.2.1  | BIP Meta Model                                                                         | 81         |

|    |     | 4.2.2  | Code Generator                                                                         | 82         |

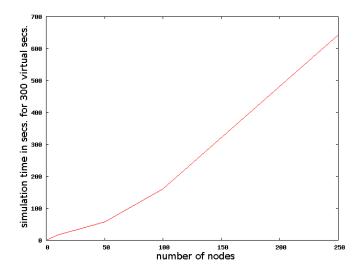

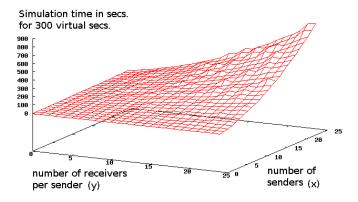

|    | 4.3 | The I  | Backend                                                                                | 82         |

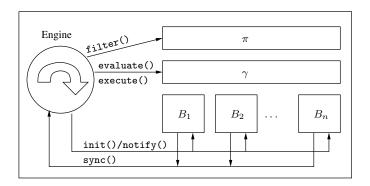

|    |     | 4.3.1  | Centralized Enumerative Engine                                                         | 83         |

|    |     | 4.3.2  | Centralized Symbolic Engine                                                            | 85         |

|    |     | 4.3.3  | Distributed engine                                                                     | 92         |

| II | I A | pplic  | rations                                                                                | 101        |

| ۲  |     |        |                                                                                        | 100        |

| 5  |     | e Stud |                                                                                        | 103        |

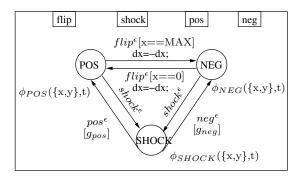

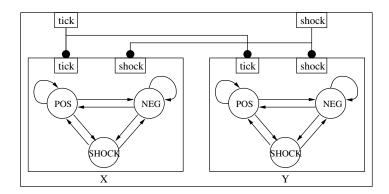

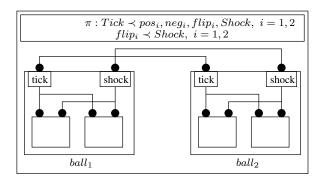

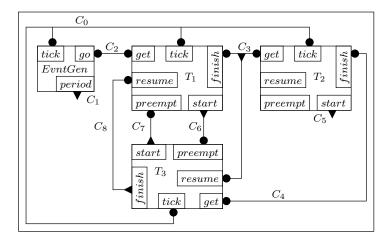

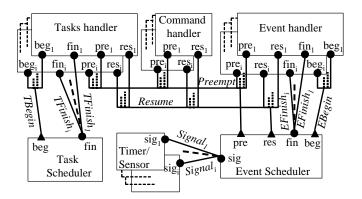

|    | 5.1 |        | eling Mixed HW/SW Systems                                                              | 103        |

|    |     | 5.1.1  | Modeling and Verification of Networked Systems – A Case Study on TinyOS-based Networks | 109        |

|    | 5.2 | Softm  | rare Componentization                                                                  | 103        |

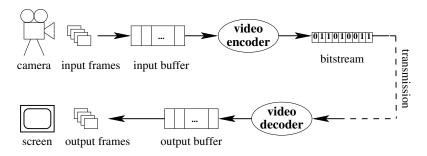

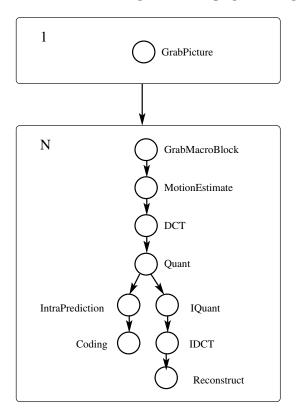

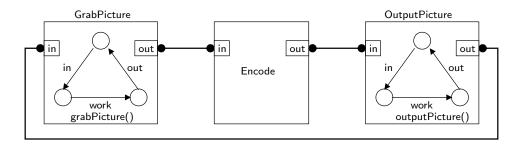

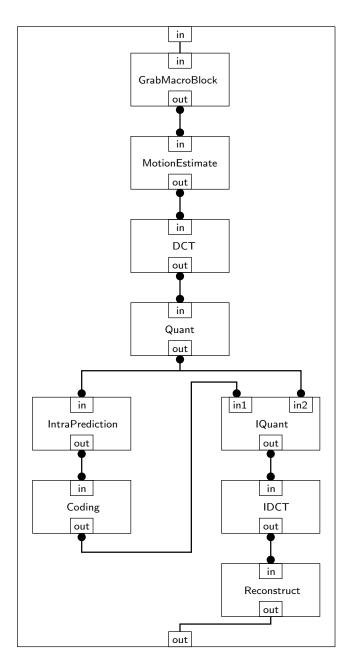

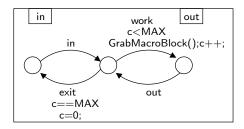

|    | J.∠ |        | MPEC encoder                                                                           | 115        |

| CONTENTS | iii |

|----------|-----|

| CONTENTS | 111 |

| IV | C   | onclus  | sions and Perspectives            | 121     |

|----|-----|---------|-----------------------------------|---------|

| 6  | Con | clusion | 1                                 | 123     |

|    | 6.1 | Object  | cives of the thesis               | <br>123 |

|    | 6.2 | Tasks   | Accomplished                      | <br>124 |

|    | 6.3 | Future  | e Work                            | <br>125 |

|    |     | 6.3.1   | Language Factory                  | <br>125 |

|    |     | 6.3.2   | Implementation for real platforms | <br>126 |

| ΒI | P G | ramma   | ur                                | 129     |

| ΒI | РМ  | eta M   | odel                              | 133     |

iv CONTENTS

# Preface

"Saraswati Mahabhaage Vidye Kamalalochane Vishwaroope Vishaalaakshi Vidyam dehi namosthuthe" (O, the great Goddess Saraswati, thou shower us with all the powers and glories of all knowledge that exist).

vi *CONTENTS*

# $$\operatorname{Part} \ I$$ Concepts and Methodology

# Chapter 1

# Introduction

A central idea in systems engineering is that complex systems are built by assembling components. Components are building blocks, and the concept of component-based modeling is common to all engineering disciplines. Components are usually characterized by abstractions that ignore implementation details and describe properties relevant to their composition, e.g., transfer functions, interfaces. It is possible to get larger components by "gluing" together simpler ones. Gluing or composition can be formalized as an operation that takes in components and their integration constraints. From these, it provides a description of a new, more complex composite component.

System designers deal with a large variety of components, each having different characteristics, from a large variety of viewpoints, each highlighting different dimensions of a system. A central problem is the meaningful composition of heterogeneous components to ensure their correct interoperation [HS06].

One fundamental source of heterogeneity is the composition of subsystems with different execution and interaction semantics. At one extreme of the semantic spectrum are fully synchronized components, which proceed in lockstep with a global clock and interact in atomic transactions. Such a tight coupling of components is the standard model for most synthesizable hardware and for synchronous real-time software. At the other extreme are completely asynchronous components, which proceed at independent speeds and interact non-atomically. Such a loose coupling of components is the standard model for most multi-threaded software. Between the two extremes, a variety of intermediate and hybrid models can be defined (e.g., globally-asynchronous locally-synchronous models).

Another fundamental source of heterogeneity is the use of models that represent a system at varying degrees of detail and are related to each other in an abstraction (or equivalently, refinement) hierarchy. A key abstraction in system design is the one relating application software to its implementation on a given platform. Application software is largely untimed, in the sense that it abstracts away from physical time. The application code running on a given platform, however, is a dynamic system that can be modeled as a timed or hybrid automaton [ACH<sup>+</sup>95]. The runtime state includes not only the variables of the application software, but also all variables that are needed to characterize its dynamic behavior, such as time variables and other quantities used to model resources. We need tractable theories to relate component-based models at application and implementation levels. In particular, such theories must provide means for preserving, in the implementation, all essential properties of the application software.

Unified frameworks encompassing heterogeneity in systems design have been developed through tools like Ptolemy [EJL<sup>+</sup>03] and Metropolis [BWH<sup>+</sup>03]. Other modeling paradigms for unifying interaction in heterogeneous systems have been proposed in [BGK<sup>+</sup>06, Arb05]. Nevertheless, in these works unification is achieved by reduction to a common low-level semantic model. Interaction mechanisms and their properties are not studied independently of behavior. We need a framework which is not just a disjoint union of sub-models, but one which preserves properties during model composition and supports meaningful analysis and transformations across heterogeneous model boundaries.

# 1.1 State of the Art

In this section, we provide a brief description of the current state of the art of component-based technology. We analyze the existing technology for different domains encompassing hardware, software and middleware. We see that component-based engineering is widely used in VLSI circuit design methodologies, and is supported by a large number of tools. Software component-based techniques have seen significant development, especially through the use of object technologies supported by languages such as C++, Java, and standards such as UML and CORBA. However, these techniques have not yet achieved the same level of maturity as has been the case for hardware. There exists a large body of literature dealing with components and their use for different purposes and in different context.

The following deal, one way or another, with issues related to component-based engineering:

- Software Design Description Languages [GS04, BFLL04], and Architecture Description Languages focusing on non-functional aspects [VPL99, AVCL02].

- System modeling languages such as UML [Sel04], as well as languages and notations specific to tools such as Simulink/Stateflow, SystemC

[RHG<sup>+</sup>01], Statecharts, Metropolis [BWH<sup>+</sup>03], Ptolemy [Lee03, BHLM02, EJL<sup>+</sup>03], IF-toolset [BGO<sup>+</sup>04] and PROMETHEUS tool [Gößl01].

The component framework proposed in this thesis extends and improves the ideas of the IF-toolset and PROMETHEUS tool.

The IF toolset [BGO<sup>+</sup>04], developed at Verimag, is one amongst the well known platforms for component modeling and validation. The IF toolset uses techniques such as partial order reduction and on-the-fly model-checking to explore the state space of the IF specification, giving access at the semantic level, to the corresponding labeled transition system (LTS). The latter can be analyzed using the tool suite CADP [JHA<sup>+</sup>96], including the minimization and comparison tool ALDEBARAN based on bisimulation, and the alternating-free  $\mu$ -calculus model-checker EVALUATOR.

The Prometheus tool [Gößl01], a prototype of a compositional modeling tool for real-time systems, was also developed at Verimag. It is based on priority functions as a model for coordination between processes. It also provides a high-level modeling language for specifying real-time processes as well as a scheduler. The language is sufficiently general to specify most frequently used scheduling policies. The possibility of defining and instantiating scheduler templates allow to establish a library of schedulers. Process templates simplify the specification of multiple occurrences of a process type with the same untimed transition structure, but different timing constraints. It uses IF as an intermediate format for timed asynchronous systems and integrates tools operating on different levels of abstraction.

Other developments in component-based modeling and programming technology are:

- Component models based on classical concepts of Component-Based Software Engineering (CBSE) like FRACTAL [Fra] and its implementations, e.g., THINK [FSLM02].

- Coordination language extension of programming languages such as Linda, Javaspaces, TSpaces, Concurrent Fortran, nesC [GLvB<sup>+</sup>03] and Polyphonic C<sup>‡</sup> [BCF02].

- Middleware standards such as IDL, Corba, Javabeans, .NET, RMI.

- Software development environments such as PCTE. SWbus, Softbench, Eclipse.

- Theoretical frameworks based on process algebras e.g., the Pi-Calculus [Mil98] or based on automata e.g., [RC03].

There is a difference between the notion of component in software engineering and the notion of component in hardware engineering. In the former, communication between the components are point to point, by function calls. Conventional function calls are blocking, in the sense that the

caller makes no progress until the callee completes. In addition, languages like NesC allows joint function calls, and Polyphonic  $C^{\sharp}$  offers declaration of asynchronous methods and synchronization patterns, allowing two or more methods to synchronize. However, in software models, the interconnect between the components is not always easy to determine due to polymorphism. The execution of the behavior of the components is made in the context of the threads, and components do not have any proper activity. The inability to statically determine the component interconnections and the thread module of execution leads to reduced analyzability of software models.

In hardware models, components are concurrent, have their own activity, and communication is through dedicated channels. The execution is inherently synchronous.

One of the requirements is to have a platform that encompasses the heterogeneous features of both paradigms, with clear separation between component behavior and interconnect.

# 1.2 Shortcomings

There are different requirements for a component-based construction methodology. Firstly, it has to be founded on rigorous semantics and provide concepts supporting separation of concerns, e.g., decoupling behavior from interaction. This is particularly absent in the case of modeling, as well as for middleware and software development standards, like CORBA. They use ad hoc mechanisms for building systems from components and offer syntax level concepts only.

Secondly, it needs to encompass heterogeneous descriptions, as most of the platforms and languages previously mentioned, support specific interaction mechanisms and computation models. For instance, software design frameworks are based on interaction by method call and do not allow direct modeling of atomic interaction mechanisms. On the contrary, other frameworks such as SystemC and Matlab/Simulink have built in mechanisms for synchronous execution, and are not adequate for describing asynchronous systems.

Thirdly, it also needs to encompass the description of timing and resource management, which are essential for non functional properties. Standards such as UML and AADL offer only syntactic sugar for time and scheduling policies. The lack of adequate semantic frameworks does not allow checking for inconsistency in timing requirements, or in the meaningful composition of scheduling policies.

And finally, a component-based construction framework should consider architectures as first class entities. The existing theoretical frameworks are too low level, since they only emphasize on behavioral aspects.

To meet the above requirements, we need component frameworks encom-

passing *heterogeneity* and allowing *constructivity* along the design process. We explain these concepts below.

## 1.2.1 Encompassing Heterogeneity

Heterogeneity is the property of systems built from components with different characteristics. Heterogeneity has several sources and manifestations, and the existing body of knowledge is largely fragmented into unrelated models and corresponding results.

System designers deal with a large variety of components, each having different characteristics. Two central problems are the meaningful composition of heterogeneous components to ensure their correct inter-operation, and the meaningful refinement and integration of heterogeneous viewpoints during the design process. For this, we need semantic frameworks encompassing heterogeneous composition. Superficial classifications may distinguish between hardware and software components, or between continuous-time (analog) and discrete-time (digital) components, but heterogeneity has two more fundamental sources: the composition of subsystems with different execution and interaction semantics; and the abstract view of a system from different perspectives.

Heterogeneity of Interaction Interactions are combinations of actions performed by system components in order to achieve a desired global behavior. Interactions can be *atomic* or *non-atomic*. For atomic interactions, the state change induced in the participating components cannot be altered through interference with other interactions. As a rule, synchronous programming languages and hardware description languages use atomic interactions. By contrast, languages with buffered communication (e.g., SDL) and multi-threaded languages (e.g., Java) generally use non-atomic interactions.

Both atomic and non atomic interaction may involve strong or weak synchronization. Strongly synchronizing interactions can occur only if all participating components agree (e.g., CSP rendezvous). Weakly synchronizing interactions are asymmetric; they require only the participation of an initiating action, which may or may not synchronize with other actions (e.g., outputs in Esterel [BC85]).

Heterogeneity in interactions may also arise due to the different number of participants. Interactions can be binary (point to point) or n-ary for  $n \geq 3$ . Interactions in CCS and SDL, function calls in most programing languages and message passing through channels are typical examples of binary interactions, while some high level modeling languages/platforms allow for n-ary synchronizations, e.g., Polyphonic C<sup> $\sharp$ </sup> [BCF02]. The implementation of n-ary interactions by using binary interaction primitives is a non-trivial problem.

Clearly, there exists no formalism supporting directly all these types of interaction.

Heterogeneity of Execution Presently, there is a lack of formalisms encompassing both synchronous and asynchronous execution. Synchronous execution is typically used in hardware, in synchronous programming languages, and in time-triggered systems. It considers that a system's execution is a sequence of global steps. It assumes synchrony, meaning that the environment does not change during a step, or equivalently, that the system is infinitely faster than its environment. In each execution step, all the system components contribute by executing some quantum of computation. The synchronous execution paradigm, therefore, has a built in strong assumption of fairness: in each step all components can move forward.

Asynchronous execution, by contrast, does not use any notion of global computation step. It is adopted in most distributed systems description languages such as SDL [IT00] and UML [Sel04], and in multi threaded programming languages such as ADA [ADA] and Java [Jav]. The lack of built in mechanisms for sharing computation between components can be compensated through scheduling mechanisms, e.g., priorities.

**Heterogeneity of Abstraction** System development involves the use of languages, models and physical implementations, representing a system and its components at different abstraction levels. For heterogeneity, a key abstraction is the one relating an application software to its implementation on a given platform.

Application software is *untimed* in the sense that it abstracts out physical time. The only references to physical time are time parameters of real time statements, such as timeouts and watchdogs. The expiration of watchdogs or timeouts is treated at the semantic level as an external event. The application code running on a given platform, however, is a dynamic system that can be modeled as a timed or hybrid automaton [Hen96]. The runtime state includes not only the variables of the application software, but also all variables that are needed to characterize its dynamic behavior such as time, quantity of resources e.g., memory and power. We need abstractions and theory relating application software to its implementations. In particular, such abstractions should guarantee the preservation of all essential properties of the application software.

### 1.2.2 Achieving Constructivity

Constructivity is the possibility to build complex systems that meet given requirements, from building blocks and glue components with known properties. Constructivity can be achieved by algorithms (compilation and synthesis), and also by architectures and design disciplines. In principle, component-

based frameworks should allow inferring system properties from properties of their structure. Currently, most of the existing validation techniques e.g, model-checking, need the construction of global models. We need theory, methods and tools for establishing, by construction, overall system correctness from component properties.

For dealing with heterogeneous systems, we need results in two complementary directions. First, we need construction methods for specific, restricted application contexts characterized by particular types of requirements and constraints, and/or by particular types of components and composition mechanisms. Clearly, hardware synthesis techniques, software compilation techniques, algorithms (e.g., for scheduling, mutual exclusion, clock synchronization), architectures (such as time-triggered; publish-subscribe), as well as protocols (e.g.,for multimedia synchronization) contribute solutions for specific contexts.

Second, we need theories that allow the incremental combination of the above results in a systematic process for system construction. Such theories would be particularly useful for the integration of heterogeneous models, because the objectives for individual subsystems are most efficiently accomplished within those models which most naturally capture each of these subsystems. As explained in this section, we need theory allowing constructivity and meeting the following requirements:

**Incrementality** This means that composite systems can be considered as the composition of smaller parts. Incrementality is necessary for progressive analysis and the application of compositionality rules.

**Compositionality** Compositionality rules allow inferring global system properties from the local properties of the components. An example is inferring global deadlock-freedom from the deadlock freedom of the individual components.

Composability Composability rules guarantee that a component's essential properties are not affected during the system construction process, i.e., even after gluing together the components, their essential individual properties are preserved. Composability means stability of component properties across integration, e.g., establishing noninterference for two scheduling algorithms used to manage two system resources.

# 1.3 Key Issues of Component-Based Construction

On exploring the current state of the art, and analyzing their shortcomings, it becomes clear that a component-based framework needs the following:

- Rigorous and general basis for real-time system design and implementation

- Concept of component and associated composition operators for incremental description and correctness by construction.

- Upliftment from frameworks based on single composition operator to those with families of composition operators.

- Enhanced expressiveness for modeling co-ordination mechanism such as protocols, schedulers, buses.

- Concept for real-time architecture encompassing heterogeneous paradigms and styles of computation e.g., synchronous vs. asynchronous execution; event driven vs. data driven computation; distributed vs. centralized execution.

- Automated support for component integration and generation of glue code meeting given requirements.

# 1.4 Our Contribution

We present in this thesis, the BIP component framework. The name BIP is derived from Behavior, Interaction and Priority, the three main foundations of this framework. BIP serves for modeling heterogeneous real-time components, and integrates results developed at Verimag over the past five years.

Its main characteristics are the following:

- It supports a component construction methodology based on the thesis that components are obtained as the superposition of three layers. The lower layer contains atomic components described by their behavior. The intermediate layer includes a set of connectors describing the interactions between transitions of the behavior. The upper layer is a set of priority rules describing scheduling policies for interactions. Layering implies a clear separation between behavior and structure (connectors and priority rules).

- It uses a parameterized composition operator on components. The product of two components consists in composing their corresponding layers separately. Parameters are used to define new interactions as well as new priority rules between the composed components [GS05, Sif05]. The use of such a composition operator allows incremental construction. That is, any compound component can be obtained by successive composition of its constituents. This is a generalization of the associativity/commutativity property for composition operators whose parameters depend on the order of composition.

- It encompasses heterogeneity. It provides a powerful mechanism for structuring interactions involving strong synchronization (rendezvous) or weak synchronization (broadcast). Synchronous execution is characterized as a combination of properties of the three layers. Finally, timed components can be obtained from untimed components by applying a structure preserving transformation of the three layers.

- It allows considering the system construction process as a sequence of transformations in a three-dimensional space: Behavior×Interaction×Priority. A transformation is the result of the superposition of elementary transformations for each dimension. This provides a basis for the study of property preserving transformations or transformations between subclasses of systems such as untimed/timed, asynchronous/synchronous and event-triggered/data-triggered.

# 1.5 Organization of the Report

The document is split into four parts, the first presenting the Concepts and Methodologies (Chapter 2), the second describing the Implementations (Chapter 3 and 4), the third presenting Case studies applying the methodology (Chapter 5), and the last part (Chapter 6) drawing the conclusions.

Chapter 2 presents the basic notions about components, their composition using glues, and the necessary properties for component-based construction of systems. It introduces the BIP component framework, describing its architecture and abstract semantics. A concrete model for BIP is then presented. We then provide a classification of systems, showing heterogeneous domains that can be modeled in the BIP framework. Later a distributed semantics for BIP is presented, relevant for its implementation on real distributed platforms.

The second part of this thesis, which describes the implementation, is presented in two chapters. Chapter 3 introduces the language developed for modeling systems in the BIP methodology. It presents in detail, the language constructs, illustrated with abstract grammar and lucid examples.

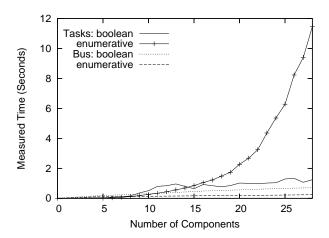

Chapter 4 presents the tool-chain that we have developed in Verimag, supporting the presented methodology. It also describes the other tools that can be associated with our tool-chain for specific purposes. It provides vivid description for different types of implementations, e.g., centralized and distributed, with benchmarks for comparing performance of different implementations.

In the third part (Chapter 5), we present two real applications that were modeled and executed in BIP. We describe modeling of two categories of systems. The first is a mixed HW/SW system, where we model and analyze wireless sensor network systems, with motes running NesC applications on TinyOS. The second is an example of componentization techniques for big

software systems. We model an MPEG4 encoder and analyze the pros and cons of componentization.

We conclude the document in Chapter 6, with an overview of the work and its future perspectives.

# Chapter 2

# Component Composition in BIP

We describe in this chapter, the basic notions about components and their composition. We introduce the BIP component framework and its formal semantics. We present an abstract model, followed by a concrete model of the methodology, with examples of modeling simple systems. We then present a distributed semantics of BIP. We give a classification of systems that can be modeled in BIP with examples of timed and synchronous systems. We conclude the chapter with a discussion on the system modeling space.

# 2.1 Basic Ideas

A *component* is a behavioral entity, having a well defined interface. It denotes an executable description whose runs can be modeled as sequences of actions. Tasks, processes, threads, functions, blocks of code can be considered as components.

A basic component, representing only behavior is called an *atomic* component. We denote atomic components graphically as boxes containing behavior inside. Behavior is represented by a labeled transition system (LTS).

**Definition 2.1.1 (Labeled Transition System)** A labeled transition system is a triple  $B = (Q, P, \rightarrow)$ , where Q is a set of states, P is a set of actions, and  $\rightarrow \subseteq Q \times P \times Q$  is a set of transitions, each labeled by an action.

For any pair of states  $q, q' \in Q$  and an action  $p \in P$ , we write  $q \xrightarrow{p} q'$ , iff  $(q, p, q') \in \to$ . If such q' does not exist, we write  $q \not\stackrel{p}{\to}$ .

A set of atomic components can be glued together producing a larger component, called a *compound* component. A *glue* combines a set of components. It is a set of operators mapping tuples of behavior into behavior.

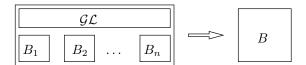

It restricts the combined behavior of the components by memoryless coordination in order to meet some global properties. Given  $B_1, B_2, \ldots B_n$  a set of atomic components, their composition with the glue  $\mathcal{GL}$  produces a transformed behavior B, as shown in figure 2.1, where

$$B = \mathcal{GL}(B_1, B_2, \dots B_n)$$

The glue is a separate layer, composing the underlying layer of behaviors. The behavior B is the product of the behaviors of  $B_1, B_2, \ldots B_n$ , with some restrictions implied by the meaning of the glue. The new component B can be further used for composition with other components.

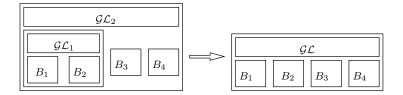

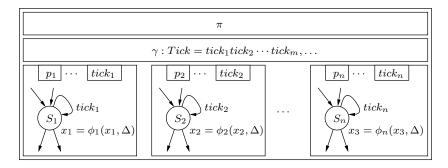

Figure 2.1: Component Composition.

Component-based design consists in building a component satisfying a given property from:

- a set of components  $B_1, B_2, \dots B_n$ , described by their behavior, and

- a set of glue operators  $\mathcal{GL} = \{gl_1, gl_2, \dots gl_n\}$

The meaning of a glue is defined by operational semantics. We provide below a definition for glue based on Structural Operational Semantic (SOS) [Plo81, AFV01] rules. The definition is adopted from [BS08b].

**Definition 2.1.2 (Glue Operator)** A glue operator is any behavior transformer defined by derivation rules of the form

$$\frac{\{q_i \xrightarrow{a_i} q_i'\}_{i \in I} \quad \{q_k \not\xrightarrow{a_k}_k\}_{k \in K}}{(q_1, \dots, q_n) \xrightarrow{a} (q_1', \dots, q_n')}$$

where

- $I, K \subseteq \{1, \dots n\}$

- $I \neq \emptyset$ ,  $I \cap K = \emptyset$

- $a = \bigcup_{i \in I} a_i$  is a transition of the composed component, and

- $q_i' = q_i \text{ for } i \notin I$ .

Premises of the form  $q \xrightarrow{a} q'$  are called positive, and those of the form  $q \not\xrightarrow{q}$  are called negative. That is:

- 1. a derivation rule has at most one positive premise for each component.

- 2. there is at least one positive premise.

- 3. a label can appear either in positive or in negative premises, but not in both, i.e., no contradictory premises.

A glue is a set of glue operators. The definition of a glue operator considers the transition of a compound component  $(\rightarrow)$  as a result of the transitions of its constituents  $(\rightarrow_i)$ .

Notice that glue is defined by stratified rules. The transition relations involved in the premises  $(\rightarrow_i)$  and the transition relation of the conclusion  $(\rightarrow)$  are different. For example, non-deterministic choice and sequential composition are not glue operators.

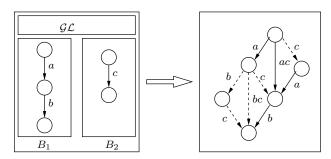

The composition of a set of behaviors by a glue gives a restricted behavior, contained in the product of their behaviors. This is illustrated with an example (figure 2.2). We have two behaviors,  $B_1$  and  $B_2$ , specified as labeled transition systems.

Figure 2.2: Composition with Glue.

The glue  $\mathcal{GL}$  is the set of the following operators

$$\frac{q_1 \xrightarrow{a} q_1'}{q_1 q_2 \xrightarrow{a} q_1' q_2} \quad \frac{q_1 \xrightarrow{a}_1 q_1' \qquad q_2 \xrightarrow{c}_2 q_2'}{q_1 q_2 \xrightarrow{ac} q_1' q_2'} \quad \frac{q_1 \xrightarrow{b}_1 q_1' \qquad q_2 \xrightarrow{c}_2}{q_1 q_2 \xrightarrow{b} q_1' q_2}$$

The composed behavior obtained after the application of the glue  $\mathcal{GL}$  is shown in the right. It shows the product of the two behaviors, where the only allowed transitions are the ones with a solid arrow. The dotted transitions are not legal and shows the maximal behavior allowed by the glues.

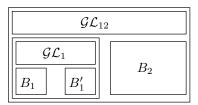

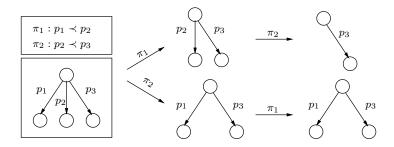

Our goal is to provide a methodology for component description and integration in a meaningful manner. The methodology must be incremental, i.e., components can be composed through a meaningful hierarchy of glues. For example, as shown in figure 2.3, components  $B_1$  and  $B'_1$  are composed with glue  $\mathcal{GL}_1$ , and the resulting component is integrated with  $B_2$  by  $\mathcal{GL}_{12}$  to produce the global system.

Constructivity is expressed by the following requirements:

Figure 2.3: Components and Glues.

# 2.1.1 Incrementality

Incrementality of construction means the following requirements:

# 2.1.1.1 Decomposition

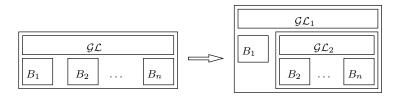

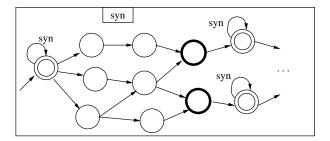

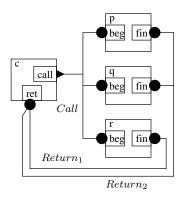

An n-ary glue operator could be obtained by successive application of a binary glue operator, as shown on figure 2.4. In general, we should be able to write

$$\mathcal{GL}(B_1,\ldots,B_n) = \mathcal{GL}_1(B_1,\mathcal{GL}_2(B_2,\ldots,B_n))$$

That is, any compound component can be obtained by successive composition of its atomic components.

Figure 2.4: Decomposition.

### 2.1.1.2 Flattening

It is the dual of the decomposition operation. Any given structure can be flattened to a component which is the composition of its atomic components by using a single glue operator.

$$\mathcal{GL}_1(B_1,\mathcal{GL}_2(B_2,\ldots)) = \mathcal{GL}(B_1,\ldots,B_n)$$

An example is shown in figure 2.5.

The combination of decomposition and flattening leads to incrementality. By the above two mechanisms, a given system of behavior can be partitioned into any required structure.

Figure 2.5: Flattening.

# 2.1.2 Compositionality

Compositionality means inferring global system properties from the properties of the individual system. It can be formally defined by rules of the form

$$\frac{\{B_i \models f_i\}_{i=1}^n}{\mathcal{GL}(B_1, \dots B_n) \models \widetilde{\mathcal{GL}}(f_1, \dots f_n)}$$

where  $f_i$  is a property of the component  $B_i$ ;  $\mathcal{GL}$  is a glue composing the components; and  $\widetilde{\mathcal{GL}}$  is an operator on properties depending on the glue  $\mathcal{GL}$ .

# 2.1.3 Composability

Composability guarantees that during the component construction process, all essential properties of subcomponents are preserved. It is defined by the following rule.

$$\frac{\{\mathcal{GL}_i\{B_j\}_{j\subseteq[1,n]} \models f_i\}_{i=1}^m}{\mathcal{GL}(B_1,\dots B_n) \models \bigwedge_{i=1}^m f_i}$$

where  $\mathcal{GL}_i$  is a glue satisfying a property  $f_i$  on the set of components  $\{B_j\}_{j\in[1,n]}$ ; and  $\mathcal{GL} = \bigcirc_{i=1}^m \mathcal{GL}_i$  is a composition of the glues.

# 2.2 Abstract Model of BIP

The BIP component framework presents the composition of behaviors using two kinds of glue, interactions and priorities. It is shown in [BS08b] that these encompass the universal glue presented in definition 2.1.2. The framework is based on a 3-tier architecture, the layers being Behavior, Interaction and Priority. It defines a mechanism for composition of behavior using the interaction and priority glues.

### 2.2.1 The 3-Tier Architecture

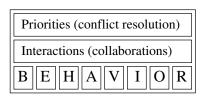

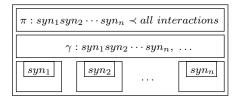

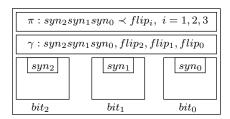

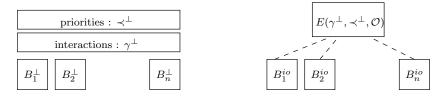

The BIP component framework uses an abstract layered model of components. A component consist of the superposition of three layers: *behavior*, *interaction* and *priority*, as shown in figure 2.6, where:

- 1. Behavior describes the dynamic behavior of a component. It consists of a set of labeled transition system. Each transition has a port, a guard and a function. Guards are conditions depending on local state. Ports characterize the component's ability to interact with a given environment.

- 2. Interactions describe architectural constraints on behavior. They are joint state changes of composed components used to coordinate their execution.

- 3. Priorities provide a mechanism for restricting the global behavior of the layers underneath by filtering amongst possible interactions. They help reducing non-determinism in the execution of the interactions between the components. They are useful for enforcing state invariant properties such as mutual exclusion and scheduling policies.

The interaction and priority layers are the glue operators for BIP. In the fol-

Figure 2.6: BIP Architecture.

lowing section, we give a formal description of each of the layers, introduced here.

# 2.2.2 Abstract Semantics

We provide a formalization of the BIP component model focusing on the individual layers of behavior, interaction and priority glue, and provide the operational semantics for composition of behavior with respect to interaction and priority layers.

**Definition 2.2.1 (Behavior)** A behavior B is a labeled transition system represented by a triple  $(Q, P, \rightarrow)$ , where Q is a set of control states, P is a set of communication ports,  $\rightarrow \subseteq Q \times P \times Q$  is a set of transitions, each labeled by a port.

For any pair of control states  $q, q' \in Q$  and a port  $p \in P$ , we write  $q \stackrel{p}{\to} q'$ , iff  $(q, p, q') \in \to$ . When the port is irrelevant, we simply write  $q \to q'$ . Similarly,  $q \stackrel{p}{\to}$  means that there exists  $q' \in Q$  such that  $q \stackrel{p}{\to} q'$ .

A port p of B is enabled iff B is at a state q and  $q \xrightarrow{p}$ . Otherwise, p is disabled.

We compose a set of n atomic components  $\{B_i = (Q_i, P_i, \rightarrow_i)\}_{i=1}^n$ , by using interactions and priorities. We assume that their respective sets of ports are pairwise disjoint, i.e., for any two  $i \neq j$  from 1..n we have  $P_i \cap P_j = \emptyset$ . We define the set  $P = \bigcup_{i=1}^n P_i$  of all ports in the system.

**Definition 2.2.2 (Interaction)** For a set of ports P, an interaction is a non-empty subset  $a \subseteq P$  of ports.

When we write  $a = \{p_i\}_{i \in I}, I \in 1...n$ , we suppose that for each  $i \in I$ ,  $p_i \in P_i$ . The interaction model is specified by a set of interactions  $\gamma \subseteq 2^P$ .

Interactions of  $\gamma$  can be enabled and disabled. An interaction a is enabled iff, for all  $i \in [1, n]$ , the port  $a \cap P_i$  is enabled in  $B_i$ . It is disabled if, there is an  $i \in [1, n]$ , the port  $a \cap P_i$  is disabled in  $B_i$ .

The enabledness of an interaction does not necessarily entails its execution, as it might be inhibited by another enabled interaction, in the priority model. We now provide the operational semantics for the composition of a system of behavior with respect to an interaction model. The composition is derived from the universal glue (2.1.2), consisting of only positive premises.

**Definition 2.2.3 (Composition for Interactions)** The composition of a set of components  $\{B_i\}_{i=1}^n$ , parameterized by a set of interactions  $\gamma \subseteq 2^P$ , is a transition system  $B = (Q, \gamma, \rightarrow_{\gamma})$ , where  $Q = \bigotimes_{i=1}^n Q_i$  and  $\rightarrow_{\gamma}$  is the least set of transitions defined by the rule

$$\frac{a = \{p_i\}_{i \in I} \in \gamma \qquad \{q_i \stackrel{p_i}{\rightarrow}_i q_i'\}_{i \in I} \qquad q_i' = q_i, \ \forall i \notin I}{(q_1, \dots, q_n) \stackrel{a}{\rightarrow}_{\gamma} (q_1', \dots, q_n')}$$

We write  $B = \gamma(B_1, \ldots, B_n)$ . The inference rule says that the obtained behavior  $\gamma(B_1, \ldots, B_n)$  can execute a transition  $a \in \gamma$ , iff for each  $i \in I$ , the action  $a \cap P_i$  is enabled in  $B_i$ ; the states of the transition system, that do not participate in the interaction a remain unchanged.

Observe that, it is possible for a composed behavior to further communicate on the ports initially provided by its constituent behaviors.

Notice that interactions are glue operators with positive premises only. Hence, in a behavior, more than one interactions can be enabled at the same time, introducing a degree of non-determinism. This can be restricted by priorities, which constitute the third layer in the proposed 3-tier BIP architecture.

Priorities are a powerful tool for restricting nondeterminism, and allows straightforward modeling of urgency and scheduling policies for real time systems. For example, execution constraints like run to completion and synchronous execution can be modeled by priority models on threads. Moreover, as the priority model is dynamic, it can advantageously overcome the static restrictions of other execution models, like process algebra.

A priority model is a memoryless controller. It filters the possible interactions from the interaction model, based on the current global state of the system. We provide below a definition of priority, followed by the composition of behavior using the priority glue.

**Definition 2.2.4 (Priority)** A priority is a relation  $\prec \subseteq \gamma \times Q \times \gamma$ , where  $\gamma$  is the set of interactions, and Q is the global set of states. We write  $a \prec_q a'$  for  $(a,q,a') \in \prec$ . Furthermore, we require that for all  $q \in Q$ ,  $\prec_q$  is a strict partial order on  $\gamma$ .  $a \prec_q a'$  means that interaction a has less priority than a' at state q.

A priority model  $\pi$  is a set of priorities. The composition using the priority glue is derived from the universal glue definition (2.1.2).

**Definition 2.2.5 (Restriction w.r.t Priority Model)** Given a behavior  $B = (Q, P, \rightarrow_{\gamma})$ , its restriction by the priority model  $\pi$  is the behavior  $B' = (Q, P, \rightarrow_{\pi})$  defined by the rule

$$\frac{q \xrightarrow{a}_{\gamma} q' \qquad \{q \xrightarrow{a'}_{\gamma}\}_{a \prec_{q} a'}}{q \xrightarrow{a}_{\pi} q'}$$

Notice that priorities are glue operators with only one positive premise and an arbitrary number of negative premises. The interaction and the priority glue encompass the universal glue.

Given a set of components  $B_1, \ldots, B_n$ , an interaction model  $\gamma$ , and a priority model  $\pi$ , the compound component is obtained by application of  $\gamma$  and  $\pi$ , i.e.,  $\pi\gamma(B)$ . An interaction is enabled in  $\pi\gamma(B)$  only if it is enabled in  $\gamma$  and maximal according to  $\pi$  among the enabled interactions in B.

Figure 2.7: Composition.

Given two components  $\pi_1\gamma_1(B_1)$  and  $\pi_2\gamma_2(B_2)$ , we can define a binary composition operator  $\parallel$  parameterized by the interaction model  $\gamma_{12}$ , and priority model  $\pi_{12}$  (figure 2.7). The layers of the composed component are

obtained by composing separately the individual layers of the composed components, and with the corresponding parameters of the composition operator. That is,

$$\pi_1 \gamma_1(B_1) \| \pi_2 \gamma_2(B_2) = \pi_1 \oplus \pi_2 \oplus \pi_{12}(\gamma_1 \cup \gamma_2 \cup \gamma_{12}(B_1, B_2))$$

The meaning of the priority composition operator  $\oplus$  will be defined later in section 2.3.3.

We now provide simple examples, illustrating the layered architecture of BIP and demonstrating component composition through the use of interaction and priority layers.

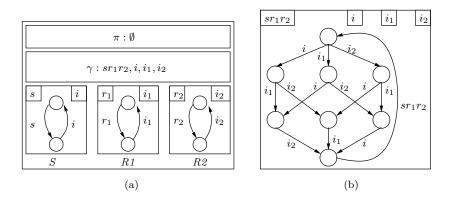

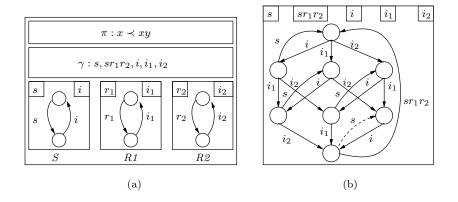

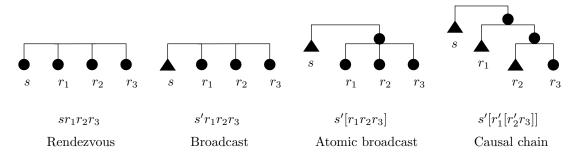

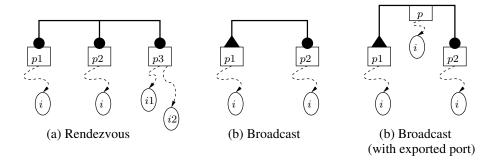

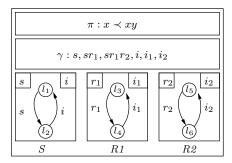

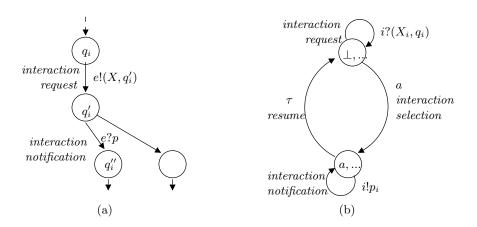

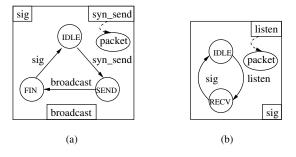

Example 2.2.6 (Rendezvous) Figure 2.8(a) shows three components, a sender (S) and two receivers (R1, R2). The sender has a port s for sending messages, and each receiver has a port  $r_i$  (i = 1, 2) for receiving messages. Additionally, the sender has a port i and the receivers have ports  $i_k$  (k = 1, 2) respectively, representing independent (internal) events. Rendezvous is modeled by specifying the interaction  $sr_1r_2$  in the interaction model of the composed system. This interaction synchronizes the s event of the sender with the  $r_i$  (i = 1, 2) events of the receivers, and hence a rendezvous. Note that the interaction model also contains the independent events of the sender and receivers. No priorities are necessary, hence the priority model is empty.

Figure 2.8: Rendezvous.

The equivalent behavior of the composition is shown in figure 2.8(b).

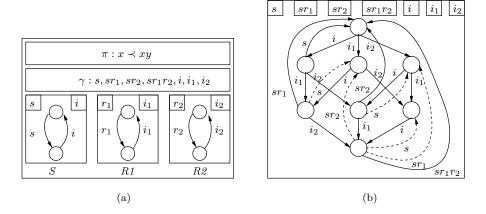

**Example 2.2.7 (Broadcast)** Figure 2.9(a) models a broadcast from the sender to the receivers. The interaction model contains the set of all interactions which synchronizes the send event of the sender with the receive event of the receivers, i.e., s,  $sr_1$ ,  $sr_2$ , and  $sr_1r_2$ . However, amongst the possible interactions, the one with the maximum number of receivers should be selected in a broadcast. To ensure this selection policy, a priority model

is specified, describing the (static) rule that an interaction (xy) containing another one (x) has higher priority over it.

Figure 2.9: Broadcast.

The behavior after the composition with interaction and priority model is shown in figure 2.9(b). The transitions inhibited by the priority model are shown by dotted arrows.

**Example 2.2.8 (Atomic Broadcast)** Figure 2.10(a) models an atomic broadcast. It is a specific type of a broadcast, where either all or none of the receivers synchronize with the sender. The synchronizing interactions are s and  $sr_1r_2$ . The priority model is required to enable the maximal interaction. The composed behavior is presented in figure 2.10(b).

Figure 2.10: Atomic Broadcast.

# 2.3 Concrete Model of BIP

# 2.3.1 Modeling Behavior

In the concrete model, an atomic component represents behavior B as a transition system, extended with variables and functions, represented by  $(X, P, S, \rightarrow)$ , where:

- P is a set of ports,  $P = \{p_1 \dots p_n\}$ .

- S is a set of control states  $S = \{s_1 \dots s_k\}$ . Control states denote places at which the components await for synchronization.

- X is a set of *variables* used to store (local) data. Variables may be associated to one or more ports. A variable associated to a port can be modified as a result of an interaction involving that port.

- $\rightarrow$  is a set of transitions modeling computation steps of components. Each transition is a tuple of the form  $(s_1, p, g_p, f_p, s_2)$ , representing a step from control state  $s_1$  to  $s_2$ , denoted as  $s_1 \xrightarrow{p,g_p,f_p} s_2$ .

Here p is a port through which an interaction is sought,  $g_p$  a pre-condition for interaction through p, and  $f_p$  is a computation step consisting of local state transformations.  $g_p$ , also known as the guard of the transition, is a boolean condition on X. The transition can be executed if the guard is true.

The semantics of execution of a transition is an atomic sequence of two micro-steps: 1) an interaction including p which involves synchronization between components with possible exchange of data, followed by 2) an internal computation specified by the function  $f_p$  on X. That is, if x is a valuation of X after the interaction, then  $f_p(x)$  is the new valuation when the transition is completed.

Formally, the behavior is a labeled transition system with moves of the form  $(s_1, x) \stackrel{\alpha}{\to} (s_2, x')$ , where  $s_1$  is a control state of the automaton and x is a valuation of its variables. The move  $(s_1, x) \stackrel{\alpha}{\to} (s_2, x')$  is possible if there exists a transition  $(s_1, p, g_p, f_p, s_2)$ , such that  $g_p(x) = true$ . As a result of the move, the set of variables are modified to  $x' = f_p(x)$ .

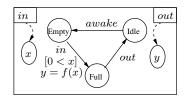

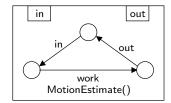

Figure 2.11: Component behavior

Figure 2.11 shows an atomic reactive component with two ports in, out, control states  $s_1$ ,  $s_2$ , and variables x, y. x and y are associated with the

ports in and out respectively. At  $s_1$ , the transition labeled in is possible if x > 0. When an interaction through in takes place, the variable x is eventually modified and a new value for y is computed by the action f(x). From control state  $s_2$ , the transition labeled out can occur. The omission of guard and function for this transition means that the associated guard is true and the internal computation micro-step is empty.

# 2.3.2 Modeling Interactions

Composition operators allow to build a system as a set of components that interact by respecting constraints of an interaction model. We propose a means for structuring interactions by using connectors.

A *Connector* is a set of ports of components which can be involved in an interaction. The number of interactions of a connector can grow exponentially to the number of ports. A connector is a macro notation for representing sets of related interactions in a compact manner. Graphically, connectors are represented as trees with ports at their leaves.

Based on the structure of interactions represented by connectors, they are classified as Simple Connector and Structured Connector.

## 2.3.2.1 Simple Connector

A simple connector is defined by a set of ports. An interaction of a simple connector is any non empty subset of its set of ports. For example, a simple connector consisting of the ports p1, p2 and p3 has seven possible interactions: p1, p2, p3, p1p2, p2p3, p1p3 and p1p2p3. Each non trivial interaction, i.e., interaction with more than one port, represents a synchronization between transitions labeled with its ports. We use the term connector to mean simple connectors.

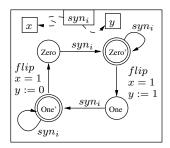

Following results in [GS05], we introduce a typing mechanism for the ports of a connector, in order to specify the feasible interactions of a connector, and in particular to express the following two basic modes of synchronization:

- Strong synchronization or rendezvous, when the only feasible interaction of a connector is the maximal one, i.e., containing all the ports.

- Weak synchronization or broadcast, when feasible interactions are all those containing a particular port which initiates the broadcast.

It is possible to represent any arbitrary interaction through a connector by structured combination of the above two basic synchronization protocols.

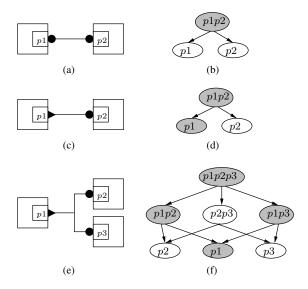

To characterize these protocols, we associate types with ports: *trigger* and *synchron*. A *trigger* is an active port, and can initiate an interaction without synchronizing with other ports. It is represented graphically by a triangle. A *synchron* port is passive, hence needs synchronization with other

ports, and is denoted by a circle. A feasible interaction of a connector is a set of its ports such that either it contains some trigger, or it is maximal, i.e., consisting of all the synchron ports. Example of sets of connectors and

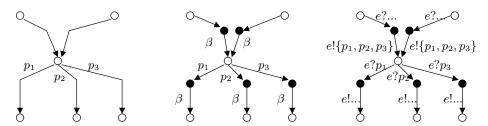

Figure 2.12: Connectors and their interactions.

their feasible interactions are shown in figure 2.12. By convention, triangles represent trigger and circles represent synchron ports. In the partially ordered set of interactions, the shaded nodes denote feasible interactions. In (a), the connector consists of the ports p1 and p2, both are of type synchron. In this connector, the only feasible interaction is p1p2, as shown in (b). It represents a rendezvous, meaning that both actions are necessary for the synchronization. In (c), the interaction between p1 and p2 is asymmetric as p1 is a trigger and can occur alone, even if p2 is not possible. Nevertheless, the occurrence of p2 requires the occurrence of p1. The feasible interactions are p1 and p1p2, shown in (d). In (e), the interactions between p1, p2 and p3 are also asymmetric. The interactions p1 can occur alone or synchronize with either or both p2 and p3, as shown in (f).

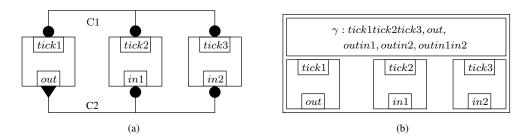

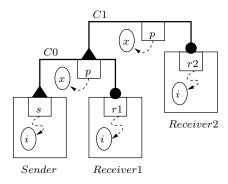

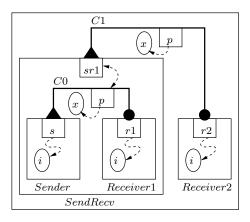

**Example 2.3.1 (Connectors)** Figure 2.13(a) shows an example of graphical representation of connectors in BIP. The corresponding layered notation is shown in figure 2.13(b). Connector C1 contains the ports tick1, tick2 and tick3. It assigns to each port the attribute synchron. Thus C1 represents the interaction describing a rendezvous between the ports tick1, tick2 and tick3. The only possible interaction in this case is tick1tick2tick3.

The other connector C2 consists of the ports out, in 1 and in 2, where the port out is assigned the attribute type trigger. The other ports are synchrons. C2 describes a broadcast from the port out to the ports in 1 and in 2. The set of possible interactions are out, out in 1, out in 2, and out in 1 in 2 (i.e., any

interaction containing the trigger port out). The complete set of interactions are included in the interaction model of figure 2.13(b).

Figure 2.13: Connector.

# 2.3.2.2 Structured Connector

So far we have seen a notation for connectors, which are essentially flat, i.e., having types (triggers and synchrons) associated to the individual ports only. However, connectors sometimes need to be structured, i.e., having types associated to groups of ports. This is necessary to represent some interactions, which otherwise cannot be represented by a flat connector. Consider for example the atomic broadcast (Example 2.2.8), where we need to restrict the feasible interactions to s and  $sr_1r_2r_3$ . It is impossible to represent this set of interactions through a simple connector as presented in the previous section.

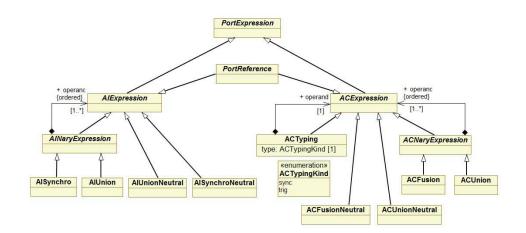

The representation of structured connectors require connectors to be treated as expressions with typing and other operations on groups of connectors. This led to the formalization of the algebra of connectors defined in [BS07b], as described below.

### Algebra of Connectors

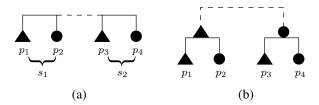

The Algebra of Connectors is a compact notation for algebraic representation and manipulation of connectors. The Algebra of Connectors  $\mathcal{AC}(P)$ , introduced in [BS07b], formalizes the concept of connectors supported by the BIP component model. It extends the notion of connectors to terms built from a set of ports by using a n-ary fusion operator and a unary typing operator for triggers and synchrons. Given two connectors involving sets of ports  $s_1$  and  $s_2$ , it is possible to obtain by fusion a new connector involving the set of ports  $s_1 \cup s_2$ , as shown in figure 2.14(a). It is also possible to structure connectors hierarchically, as shown in figure 2.14(b) where terms  $p_1p_2$  and  $p_3p_4$  are typed and then fused to obtains a new connector. The semantics of the algebra of connectors associates with a connector (a term)

Figure 2.14: Fusion (a) and structuring (b) of connectors.

the set of its feasible interactions. The algebra and its laws can be used to represent and handle symbolically, complex interaction patterns.

The Algebra of Connectors, as presented in [BS07b], has two operations: union and fusion. Union operation allows to combine several connectors into a single expression. Fusion represents synchronization of connectors by merging their interactions. We briefly introduce the syntax and semantics of the algebra of connectors as follows.

### **Syntax**

Let P be a set of ports, such that  $0,1 \notin P$ . The syntax of  $\mathcal{AC}(P)$  is defined by

$$s ::= [0] \mid [1] \mid [p] \mid [x] \quad (synchrons)$$

$$t ::= [0]' \mid [1]' \mid [p]' \mid [x]' \quad (triggers)$$

$$x ::= s \mid t \mid x \cdot x \mid (x),$$

$$(2.1)$$

for  $p \in P$ , and where  $\cdot$  is a binary operator called *fusion*, and  $[\cdot]'$  are unary *typing* operators.

Fusion is used to merge two connectors, whereas typing is used to form hierarchically structured connectors:  $[\cdot]'$  defines triggers (which can initiate an interaction), and  $[\cdot]$  defines synchrons (which need synchronization with other ports). In order to simplify notation, we often omit brackets on 0, 1, and ports  $p \in P$ , as well as ' $\cdot$ ' for the fusion operator.

### **Semantics**

The semantics of  $\mathcal{AC}(P)$  is given in terms of sets of interactions. Intuitively it consists in recursively applying the following rule: For a connector of the form  $[x_1]' \dots [x_n]'[y_1] \dots [y_m]$ , a possible interaction is a union of interactions from the sub-connectors  $x_1, \dots, x_n, y_1, \dots, y_m$ , comprising an interaction from at least one of the triggers  $x_1, \dots, x_n$ . When there are no triggers (n = 0), an interaction from every synchron sub-connector  $y_1, \dots, y_m$  is required to form an interaction of the complete connector. A formal definition

is given by the function  $\|\cdot\|:\mathcal{AC}(P)\to 2^{2^P}$ , defined by

$$\|0\| = \emptyset, \quad \|1\| = \{\emptyset\}, \quad \|p\| = \{\{p\}\}, \quad \left\|\prod_{i=1}^{n} [x_i]\right\| = \{\bigcup_{i=1}^{n} a_i \mid a_i \in \|x_i\|\},$$

$$(2.2)$$

$$\left\| \prod_{i=1}^{n} [x_i]' \prod_{j=1}^{m} [y_j] \right\| = \bigcup_{i \in [1,n]; J, K} \left\| [x_i] \prod_{j \in J} [x_j] \prod_{k \in K} [y_k] \right\|, \tag{2.3}$$

where for  $p \in P$ ,  $x_1, \ldots, x_n, y_1, \ldots, y_m \in \mathcal{AC}(P)$ , and the union in 2.3 is taken over all (potentially empty) subsets  $J \subseteq [1, n]$  and  $K \subseteq [1, m]$ .

$\mathcal{AC}(P)$  allows compact and intuitive representation of interactions, and captures explicitly the difference between broadcast and rendezvous. A full presentation of the properties of  $\mathcal{AC}(P)$  is given in [BS07b]. Figure 2.15 shows the  $\mathcal{AC}(P)$  notation for the connectors of examples 2.2.6, 2.2.7 and 2.2.8. Note the application of the typing operator to groups of ports, repre-

Figure 2.15:  $\mathcal{AC}(P)$  notation of connectors.

senting structured connectors. For atomic broadcast, the type synchron is attributed to the group of ports  $r_1r_2r_3$ , which can be seen as a sub-connector. The causal chain is another example of a structured connector.

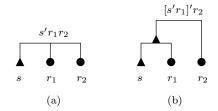

#### **Incremental Construction of Connectors**

The fusion and typing operators on connector allow for their incremental construction. Consider the broadcast from a sender port s to two receiver ports  $r_1$  and  $r_2$ , as shown in figure 2.16(a). The same set of interactions can be obtained incrementally by an equivalent structured connector, as shown in figure 2.16(b). It is constructed by first creating a broadcast from s to  $r_1$ , specified by  $s'r_1$ , and then by the adding the second receiver  $r_2$  through the structured connector  $[s'r_1]'r_2$ . Notice that both represents the same set of interactions,  $\gamma = \{s, sr_1, sr_2, sr_1r_2\}$ .

Figure 2.16: Incremental construction of connectors.

#### 2.3.2.3 Semantics of Composition by Connectors

#### Connector Guards and Transfer Functions

In BIP the execution of interactions may involve transfer of data between the synchronizing components. If  $\alpha$  is the interaction of a connector, we use a guard  $G_{\alpha}$  (boolean condition) and data transfer function  $F_{\alpha}$  to specify data transfer. Guard is a global condition, spanning over the variables of the interacting components. An enabled interaction is executable if its guard is true. The execution of the interaction leads to execution of the data transfer  $F_{\alpha}$  associated with it. As a result, the variables of the synchronizing components are updated. The mechanism for execution of guard and data transfer of a connector is formally presented below.

Consider the composition of n concrete components  $\{B_i\}_{i=1}^n$  parameterized by a set of connectors  $\gamma$ . The composed system is a concrete component  $B = (X, P, S, \rightarrow_{\gamma})$  with:

- A set of variables X, which is the union of the sets of variables of the composed components  $X = \bigcup_{i=1}^{n} X_{i}$ ,

- A set of interactions P defined by  $\gamma$ ,  $P = \{\alpha \alpha \text{ is an interaction in } \gamma\}$ ,

- A set of control states S, which is the Cartesian product of the sets of control states of the composed components  $S = \bigotimes_{i=1}^{n} S_{i}$ ,

- A set of transitions  $\rightarrow_{\gamma}$  of the form  $(s, \alpha, g, f, s')$ , where:

- $-s = (s_1, \ldots, s_n), s_i$  being a control state of the  $i^{th}$  component.

- $\alpha$  is a feasible interaction in  $\gamma$  associated with a guarded command  $(G_{\alpha}, F_{\alpha})$ , such that there exists a subset  $J \subseteq \{1, \ldots, n\}$  of components with transitions  $\{(s_j, p_j, g_j, f_j, s'_j)\}_{j \in J}$  and  $\alpha = \{p_j\}_{j \in J}$ .

- $-g = (\bigwedge_{i \in J} g_i) \wedge G_{\alpha}.$

- $-f = F_{\alpha}$ ;  $[f_j]_{j \in J}$ . That is, the computation starts with the execution of  $F_{\alpha}$  followed by the execution of all the functions  $f_j$  in some arbitrary order. The result is independent of this order as components have disjoint sets of variables.

$-s'(j) = s'_j$  if  $j \in J$ ; otherwise  $s'(j) = s_j$ . That is, the states from which there are no transitions labeled with ports in  $\alpha$ , remain unchanged.

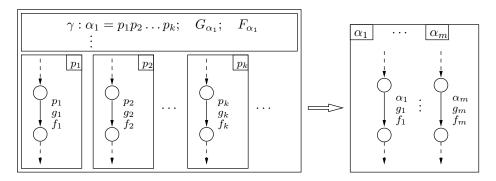

The composition of the concrete system is shown in figure 2.17.

Figure 2.17: Composition of concrete components.

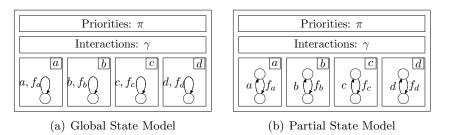

#### 2.3.3 Modeling Priority

For the concrete mode, a priority order  $\prec$  is represented by a priority rule. It is a tuple  $(C, \prec)$ , where C is a state predicate (boolean condition) characterizing the states where the priority applies. C also plays the role of a dynamic guard for the priority  $\prec$ .

A priority rule is textually expressed as  $C \to \prec$ . It means that when the state predicate is true and both the interactions specified in the priority are enabled, the higher order interaction is selected for execution. For static priorities, C is true and is omitted from the priority rule.

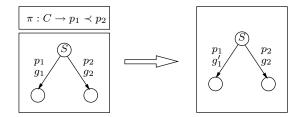

A priority model  $\pi$  consists of a set of priority rules,  $\{C_i \to \prec_i\}_{i=1}^m$ , with a disjoint set of state predicates, i.e., for any two  $i \neq j$ , we have  $C_i \cap C_j = \emptyset$ . Consider the behavior given by an automaton, as shown in the left of figure

Figure 2.18: Priority restriction.

2.18, with a non deterministic choice between two interactions  $p_1$  and  $p_2$ , from the control-state S. The corresponding guards are respectively  $g_1$  and  $g_2$ . Non-determinism is resolved by a priority rule  $C \to p_1 \prec p_2$ , which

selects the interaction  $p_2$  to be taken, when C holds, by disabling  $p_1$ . This is implemented by modifying the guard  $g_1$ , of the interaction with the lower priority, to  $g'_1$ , given by  $g'_1 = g_1 \wedge (C \Rightarrow \neg g_2)$ . The restricted behavior is shown in the right of the same figure. If the predicate C is true, the interaction  $p_1$  can occur only if  $p_2$  is disabled. However if C is false, the priority holds no more, and we have a non-deterministic choice between  $p_1$  and  $p_2$ .

The transformation of the underlying behavior through restriction is imposed by modifying the guards of all the interactions which are dominated by priority rules. For an interaction  $p_k$  dominated by priority rules from  $\pi$ , its modified guard is given as

$$g'_k = g_k \land \bigwedge_{C \to \prec \in \pi} (C \Rightarrow \bigwedge_{p_k \prec p_i} \neg g_i)$$

#### 2.3.3.1 Composition of Priorities

The restriction of a behavior B by the successive application of priorities  $\pi_1$  and  $\pi_2$  may not be the same. It can depend on the order of application of  $\pi_1$  and  $\pi_2$ . That is, in general

$$\pi_2(\pi_1(B)) \neq \pi_1(\pi_2(B))$$

Consider for example, the behavior in the left of figure 2.19, showing a transition system with interactions  $p_1$ ,  $p_2$  and  $p_3$ , possible from a control state. Consider the two priorities,  $\pi_1 : true \to p_1 \prec p_2$  and  $\pi_2 : true \to p_2 \prec p_3$ . The order of their application leads to different behavior, as evident from the figure. It is shown in [GS03] that non commutativity of priorities is due to the fact that the union of the priority orders is not a priority order.

Figure 2.19: Priority Composition is non-commutative.

To avoid this anomaly, we define for two priorities  $\pi_1$ ,  $\pi_2$ , their composition  $\pi_1 \oplus \pi_2$  as the least priority contained in  $\pi_1 \cup \pi_2$  (if it exists). Computing  $\pi_1 \oplus \pi_2$  amounts to computing the transitive closure of  $\pi_1 \cup \pi_2$ . The operation is partial. It is defined only if this is a strict partial order, i.e., no cycles.

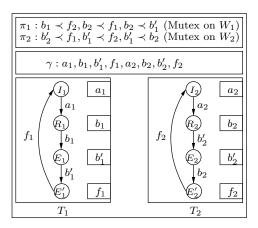

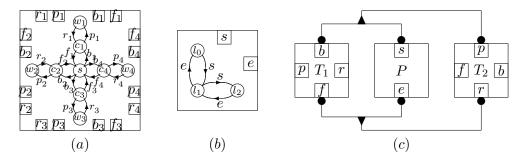

Priorities restrict the component behavior and do not add behavior. Components that are deadlock free, on restriction by the priority model continues to preserve the deadlock freedom. However, composition of priority models that leads to cyclic priority dependencies may result in deadlock situations. This is explained by the example in figure 2.20. The problem models two identical tasks  $T_1$  and  $T_2$ , using shared resources  $W_1$  and  $W_2$ . On arrival  $(a_1)$  the task  $T_1$  first acquires the resource  $W_1$  by the action  $b_1$ , and then  $W_2$  by the action  $b_1'$ . It releases both the resources upon finishing  $(f_1)$ .  $T_2$  has a similar behavior, except that it first acquires  $W_2$  (by  $b_2'$ ) and then  $W_1$  (by  $b_2$ ). We use priorities for mutual exclusion in the use of  $W_1$  and

Figure 2.20: Priority Composition leading to deadlock.

$W_2$  between  $T_1$  and  $T_2$ . The rules of the priority model  $\pi_1$  ensures exclusive use of  $W_1$ , and that of  $W_2$  by the priority model  $\pi_2$ .

We would now like to ensure the mutual exclusion of both resources by the combination of the two given priority models. However, the composition of the rule  $b_2 \prec b'_1$  of  $\pi_1$  and  $b'_1 \prec b_2$  of  $\pi_2$  is undefined (as it leads to a cycle). This reflects the existence of a possible deadlock when  $b'_1$  and  $b'_2$  are enabled.

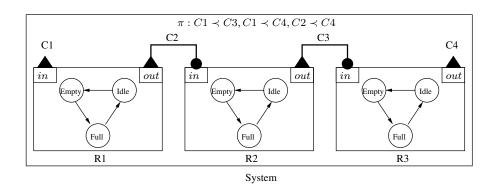

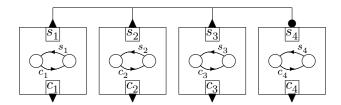

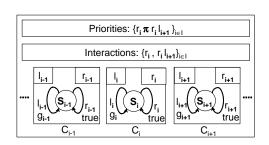

We now demonstrate through an example how an execution policy, e.g., synchronous execution, can be expressed with the help of priorities. As described in 1.2.1, synchronous execution adopts a strong fairness assumption, as in a computation step, all the components are offered the possibility to execute some quantum of computation. We show that synchronous execution can be obtained by appropriately restricting the behavior and interaction layers.

## Example 2.3.2 (Synchronous Execution)

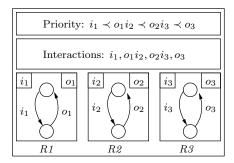

Consider the example of figure 2.21, a system which is a serial composition of three strongly synchronized components  $R_k$ , with port  $i_k$  (denoting an input action) and port  $o_k$  (denoting an output action), k = 1, 2, 3. Assume

Figure 2.21: Enforcing synchronous execution.

the components are reactive in the sense that they are triggered from some idle state when an input arrives, and eventually produces an output before reaching some idle state, from where a new input can be accepted. For the sake of simplicity, the components have simple cyclic behaviors with alternating inputs and outputs.

The interaction model consists of the interactions  $i_1$ ,  $o_1i_2$ ,  $o_2i_3$  and  $o_3$ . We assume that the system is closed, so the interactions  $i_1$  and  $o_3$  are autonomous. In the product of the behaviors restricted by the interaction model, each component can perform computation independently of the others, provided the constraints resulting from the interaction model are met. This corresponds to asynchronous execution.

The behavior can be constrained by the priority model in order to enforce synchronous execution, in the sense that a run of the system is a sequence of steps, each step corresponding to the treatment of an input  $i_1$  until an output  $o_3$  is produced. This can be enforced by the priority order  $i_1 \prec o_1 i_2 \prec o_2 i_3 \prec o_3$ . This order reflects the causality between the interactions of the system. In fact, if all the components are at some idle state, then all are awaiting for an input. Clearly, only  $i_1$  can occur to make  $R_1$  evolve to a state from which  $o_1 i_2$  can occur. This will trigger successively  $o_2 i_3$  and finally  $o_3$ . Notice that  $i_1$  cannot be executed as long as a computation takes place in some component.

We now provide a set of examples showing the application of priorities to enforce execution constraints on a system. We also provide generic models of task (both preemptable and non-preemptable), which are frequently used in a wide variety of applications.

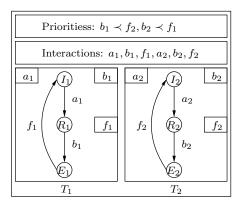

#### Example 2.3.3 (Mutual Exclusion)

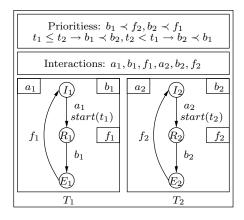

In this example, we show the enforcement of *mutual exclusion*, a very common execution constraint, needed when we have multiple components (tasks) sharing a single resource. In the example shown in figure 2.22, we have two identical tasks,  $T_1$  and  $T_2$ , modeled as BIP components. The control states of the *i*-th task are  $I_i$  (Idle),  $R_i$  (Ready) and  $E_i$  (Executing). The actions

(ports) are  $a_i$  (activate),  $b_i$  (begin) and  $f_i$  (finish). Each task is initialized to state  $I_i$ , from where it can voluntarily activate through the action  $a_i$  and become ready  $(R_i)$  for execution. The start of execution is marked by the action  $b_i$ , by which the task acquires the resource and moves to the execution state  $(E_i)$ . The interaction model does not enforce any restriction and con-

Figure 2.22: Enforcing Mutual Exclusion.

sists of all the independent actions of the tasks. Under mutual exclusion, a task cannot acquire the resource if the other task is already in the execution state. This is enforced by the priority model, which assigns the actions to obtain the resource, lower priority than the actions to release the resource, i.e.,  $b_1 \prec f_2$  and  $b_2 \prec f_1$ . For  $T_1$ , the priority  $b_1 \prec f_2$  prevents it from obtaining the resource, unless  $T_2$  releases it (by the action  $f_2$ ). Similarly,  $T_2$  is restricted by  $b_2 \prec f_1$ .

When both tasks are at state  $R_i$ , either of them can acquire the resource in a non-deterministic fashion. However, static priority rules can be used to prioritize the tasks in any desired order. For example,  $b_2 \prec b_1$  sets a higher priority for  $T_1$  to acquire the resource, compared to  $T_2$ .

Note that mutual exclusion can also be expressed by a restricted interaction model. The interactions:  $a_1$ ,  $b'_1f_2$ ,  $f_1$ ,  $a_2$ ,  $b'_2f_1$ ,  $f_2$ , would by maximal progress, enforce mutual exclusion. The interaction  $b'_if_j$  lets task i to obtain the resource, either by executing  $b_i$  alone, when task j is not in  $E_j$ , or by executing the synchronization  $b_if_j$ , where task j releases the resource to task i.

In this example we have shown the use of static priorities. The following examples illustrate the use of dynamic priorities.

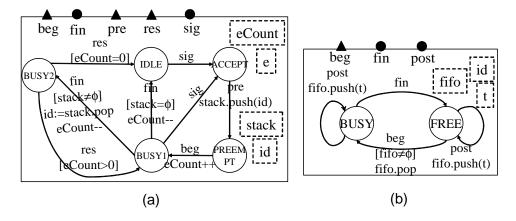

#### Example 2.3.4 (A FIFO Scheduler)

We provide another example showing the enforcement of a scheduling policy using the priority model. In particular, it shows the application of dynamic priorities. Figure 2.23 shows the model of scheduling two tasks under FIFO.

The tasks share a common resource, so we enforce mutual exclusion between the tasks, similar to the previous model (example 2.3.3). The behavior model

Figure 2.23: FIFO.

of a tasks is the same as in example 2.3.3. Except that each task has an additional clock variable  $t_i$ , used to measure the duration of its waiting time in the Ready state  $(R_i)$ . Moreover, on the action  $a_i$ , it executes the statement  $start(t_i)$ , which starts a timer on its clock variable  $t_i$ , to measures the time it has been waiting in  $R_i$ .

The FIFO constraints resolve the conflict between the processes competing for the acquisition of the common resource. Unlike a non-deterministic choice of the previous example, when both the tasks are ready, the task which has waited longer is allowed to get the resource. This is represented in the priority model by the following dynamic priority rules:  $b_1 \prec b_2$  if  $(t_1 \leq t_2)$ , and  $b_2 \prec b_1$  if  $(t_2 \leq t_1)$ .

The models of tasks we have seen so far are non-preemptable. We now propose models of preemptable tasks, needed for preemptive scheduling policies.

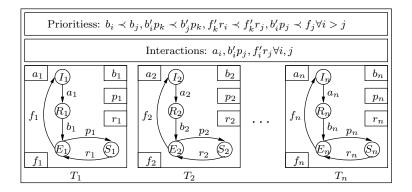

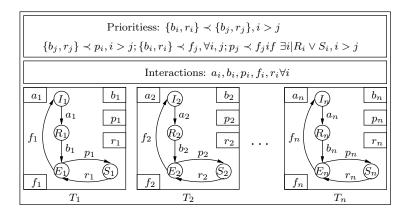

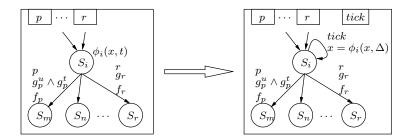

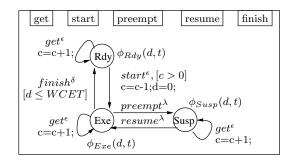

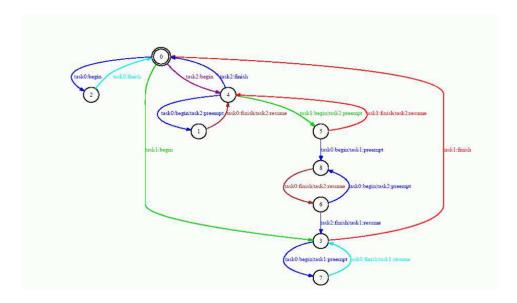

#### Example 2.3.5 (Fixed priority preemptive scheduling.)

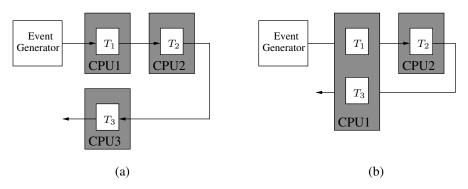

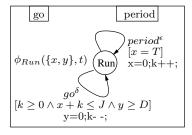

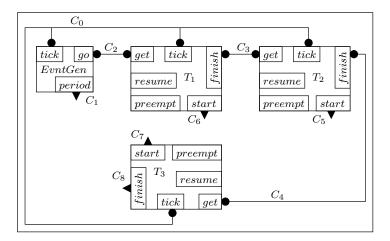

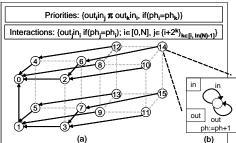

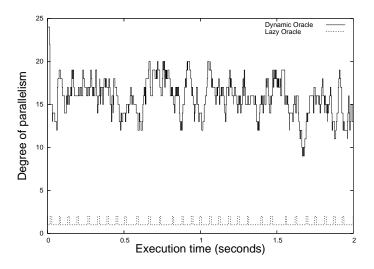

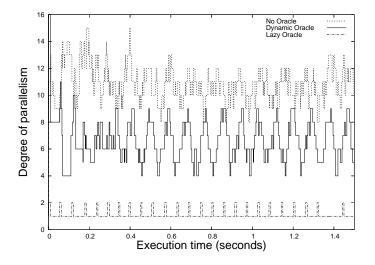

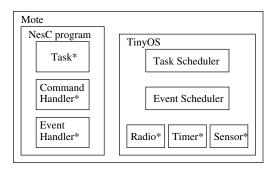

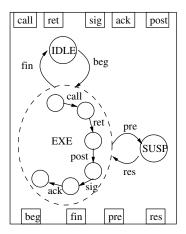

We model fixed priority scheduling with preemption for n tasks sharing a common resource (figure 2.24). The scheduler gives preference to low index tasks.