# Adéquation arithmétique architecture, problèmes et étude de cas

Arnaud Tisserand

#### ▶ To cite this version:

Arnaud Tisserand. Adéquation arithmétique architecture, problèmes et étude de cas. Informatique [cs]. Ecole normale supérieure de lyon - ENS LYON, 1997. Français. NNT: . tel-00445752

### HAL Id: tel-00445752 https://theses.hal.science/tel-00445752

Submitted on 11 Jan 2010

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

No d'ordre: 66

### **THÈSE**

présentée devant

#### L'ÉCOLE NORMALE SUPÉRIEURE DE LYON

pour obtenir

le Titre de Docteur de l'École Normale Supérieure de Lyon spécialité : Informatique au titre de la formation doctorale d'Informatique de Lyon

par ARNAUD TISSERAND

### ADÉQUATION ARITHMÉTIQUE ARCHITECTURE PROBLÈMES ET ÉTUDE DE CAS

Soutenue le 25 septembre 1997

Après avis de: Luigi DADDA

Daniel ETIEMBLE

Devant la commission d'examen formée de :

LUIGI DADDA

DANIEL ETIEMBLE

JEAN-MICHEL MULLER (Directeur de thèse)

MARC RENAUDIN YVES ROBERT

Aux zglshs et au papa des prostons  $A \ \mbox{mes amis} \\ A \ \mbox{ma famille}$

### Remerciements

Tout d'abord, je tiens à remercier les membres du jury:

Monsieur Luigi Dadda, Professeur au *Politecnico di Milano*, pour avoir accepté d'être rapporteur sur cette thèse. Son autorité et son expérience en arithmétique des ordinateurs furent des aides précieuses pour la correction du manuscrit.

Monsieur Daniel Etiemble, Professeur à l'Université Paris Sud, qui fut un rapporteur avisé. Sa grande compétence et sa clairvoyance sur les aspects des architectures des machines m'ont permis de bien mettre en valeur certains points de mon travail.

Monsieur Marc Renaudin, Maître de Conférence à Télécom Bretagne, pour son intérêt et son enthousiasme durant nos nombreuses réunions de travail et son aide durant la rédaction de la thèse. Pouvoir travailler avec des chercheurs de grande qualité est l'un des points les plus motivants pour un jeune chercheur. J'espère donc pouvoir continuer de travailler longtemps avec lui.

Monsieur Yves Robert, Professeur à l'Ecole Normale Supérieure de Lyon, pour son aide et sa disponibilité tout au long de ma formation à la recherche et de mes travaux de thèse.

Monsieur Jean-Michel Muller, Chargé de Recherche au CNRS, pour avoir accepté d'encadrer ma thèse. Ces quelques années passées au côté de Jean-Michel furent très enrichissantes professionnellement et personnellement. Il est un chercheur extrêmement brillant et un directeur de thèse formidable, à un point tel qu'il n'est pas possible de souhaiter meilleur encadrement pour une thèse.

Ensuite, je voudrais remercier chaleureusement toutes les personnes rencontrées ces dernières années: Bernard, Thierry, Richard, Olivier, Laure, Sandrine, Patrick, Bruno, Daniel, Olivier, Mathilde, Jean-Philippe, Xavier, Catherine, Martin, Laurent-Stéphane, Jean-Claude, Asger, Frédéric, Jean-Marc, Jacques-Olivier, Olivier, Johanne, Loïc, Laurent, Blaise, David, Anne, Bertrand, François, Frédéric, Pascal, Pierre, Philippe, Alain, Valérie, Sylvie, Jocelyne, Marie, Christelle, Eliane, Marie-Jeanne....

Enfin, pour finir, je tiens à remercier du fond du coeur ma famille qui m'a soutenue durant toutes ces années.

# Table des matières

| In | ntroduction 1 |                 |                                                                            |    |  |  |  |  |

|----|---------------|-----------------|----------------------------------------------------------------------------|----|--|--|--|--|

| 1  | Arr           | ondi e          | xact des fonctions élémentaires                                            | 7  |  |  |  |  |

|    | 1.1           | La no           | rme IEEE 754                                                               | 8  |  |  |  |  |

|    |               | 1.1.1           | Codage des nombres flottants dans la norme IEEE 754                        | 8  |  |  |  |  |

|    |               | 1.1.2           | Modes d'arrondi IEEE 754                                                   | 11 |  |  |  |  |

|    |               | 1.1.3           | Réalisation matérielle de l'arrondi exact des fonctions de base            | 12 |  |  |  |  |

|    |               | 1.1.4           | Avantages de la norme IEEE 754                                             | 16 |  |  |  |  |

|    | 1.2           | Arron           | di exact des fonctions élémentaires                                        | 17 |  |  |  |  |

|    |               | 1.2.1           | Evaluation des fonctions élémentaires                                      | 17 |  |  |  |  |

|    |               | 1.2.2           | Le dilemme du fabricant de tables                                          | 18 |  |  |  |  |

|    |               | 1.2.3           | Test exhaustifs sur les fonctions élémentaires en simple précision         | 20 |  |  |  |  |

|    |               | 1.2.4           | Tests aléatoires pour les précisions supérieures                           | 22 |  |  |  |  |

|    |               | 1.2.5           | Bornes supérieures                                                         | 24 |  |  |  |  |

|    |               | 1.2.6           | Coût du calcul des fonctions élémentaires en très haute précision          | 25 |  |  |  |  |

|    |               | 1.2.7           | Approche probabiliste du problème                                          | 26 |  |  |  |  |

|    | 1.3           | Mise $\epsilon$ | en œuvre de l'arrondi exact des fonctions élémentaires                     | 27 |  |  |  |  |

|    |               | 1.3.1           | La stratégie de Ziv                                                        | 28 |  |  |  |  |

|    |               | 1.3.2           | Une solution multi-niveaux pour l'arrondi exact des fonctions élémentaires | 28 |  |  |  |  |

|    |               | 1.3.3           | Vers une extension de la norme IEEE 754 aux fonctions élémentaires         |    |  |  |  |  |

|    | 1.4           | Concl           | usion                                                                      | 31 |  |  |  |  |

| 2  | Syst          | tème s          | emi-logarithmique                                                          | 35 |  |  |  |  |

|    | 2.1           | ·               |                                                                            |    |  |  |  |  |

|    |               | 2.1.1           | Représentation des nombres réels dans le système logarithmique             | 37 |  |  |  |  |

|    |               | 2.1.2           | Opérations de base dans le système logarithmique                           | 37 |  |  |  |  |

|    | 2.2           | Le sys          | tème semi-logarithmique                                                    | 39 |  |  |  |  |

|    |               | 2.2.1           | Représentation des nombres réels dans le système semi-logarithmique        | 40 |  |  |  |  |

|    |               | 2.2.2           | Particularités du système semi-logarithmique                               | 42 |  |  |  |  |

|    |               | 2.2.3           | Le système semi-logarithmique comme système logarithmique "à deux bases"   | 43 |  |  |  |  |

|    | 2.3           | Opéra           | tions dans le système semi-logarithmique                                   | 44 |  |  |  |  |

|    |               | 2.3.1           | Multiplication                                                             | 44 |  |  |  |  |

|    |               | 2.3.2           | Division                                                                   | 47 |  |  |  |  |

|    |               | 2.3.3           | Addition et Soustraction                                                   | 48 |  |  |  |  |

|    |               | 2.3.4           | Comparaisons                                                               | 50 |  |  |  |  |

|    |               | 2.3.5           | Conversions                                                                | 50 |  |  |  |  |

|    | 2.4           | Précis          | ion statique du système semi-logarithmique                                 |    |  |  |  |  |

|    |               | 2.4.1           | Erreur relative de représentation maximale (ERRMax)                        | 52 |  |  |  |  |

|    |               | 2.4.2           | Erreur relative de représentation moyenne (ERRMoy)                         | 54 |  |  |  |  |

|                  | 2.5   | Exemples d'application                                  |

|------------------|-------|---------------------------------------------------------|

|                  | 2.6   | Conclusion                                              |

| 3                | Ari   | thmétique en-ligne sur FPGA 59                          |

|                  | 3.1   | Arithmétique en-ligne                                   |

|                  |       | 3.1.1 Représentation redondante des nombres             |

|                  |       | 3.1.2 Opérateurs en-ligne élémentaires                  |

|                  |       | 3.1.3 Addition en-ligne                                 |

|                  |       | 3.1.4 Multiplication en-ligne et opérateurs dérivés     |

|                  |       | 3.1.5 Division et racine carrée en-ligne                |

|                  |       | 3.1.6 Evaluation de polynômes en-ligne                  |

|                  |       | 3.1.7 Conversions                                       |

|                  |       | 3.1.8 Normalisation                                     |

|                  | 3.2   | Bibliothèque réalisée                                   |

|                  | J     | 3.2.1 Les FPGA cibles                                   |

|                  |       | 3.2.2 Opérateurs réalisés                               |

|                  |       | 3.2.3 Contrôle des opérateurs en-ligne                  |

|                  |       | 3.2.4 Plateforme de test                                |

|                  | 3.3   | Applications                                            |

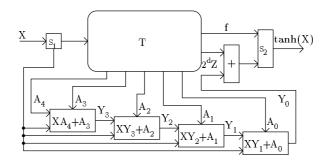

|                  | ა.ა   | 3.3.1 Réseaux de neurones MLP sur FPGA                  |

|                  |       |                                                         |

|                  | 3.4   |                                                         |

|                  | 3.4   | Conclusion                                              |

| 4                | Opé   | érateurs arithmétiques asynchrones 89                   |

|                  | 4.1   | Opérateurs asynchrones                                  |

|                  |       | 4.1.1 Le contrôle local                                 |

|                  |       | 4.1.2 Les avantages des circuits asynchrones            |

|                  |       | 4.1.3 Les types de circuits asynchrones                 |

|                  | 4.2   | Simulation des opérateurs arithmétiques asynchrones     |

|                  |       | 4.2.1 Modèle de circuit asynchrone pour la simulation   |

|                  |       | 4.2.2 Fonctionnement du simulateur                      |

|                  |       | 4.2.3 Caractéristiques mesurées                         |

|                  | 4.3   | Additionneurs asynchrones                               |

|                  | _     | 4.3.1 Additionneur séquentiel                           |

|                  |       | 4.3.2 Additionneur à retenue bondissante                |

|                  |       | 4.3.3 Additionneur à sélection de retenue               |

|                  | 4.4   | Modélisation probabiliste des additionneurs asynchrones |

|                  | 1.1   | 4.4.1 Introduction                                      |

|                  |       | 4.4.2 Modèle de base                                    |

|                  |       | 4.4.3 Modélisation par les fonctions génératrices       |

|                  |       | 4.4.4 Modélisation par les chaînes de Markov            |

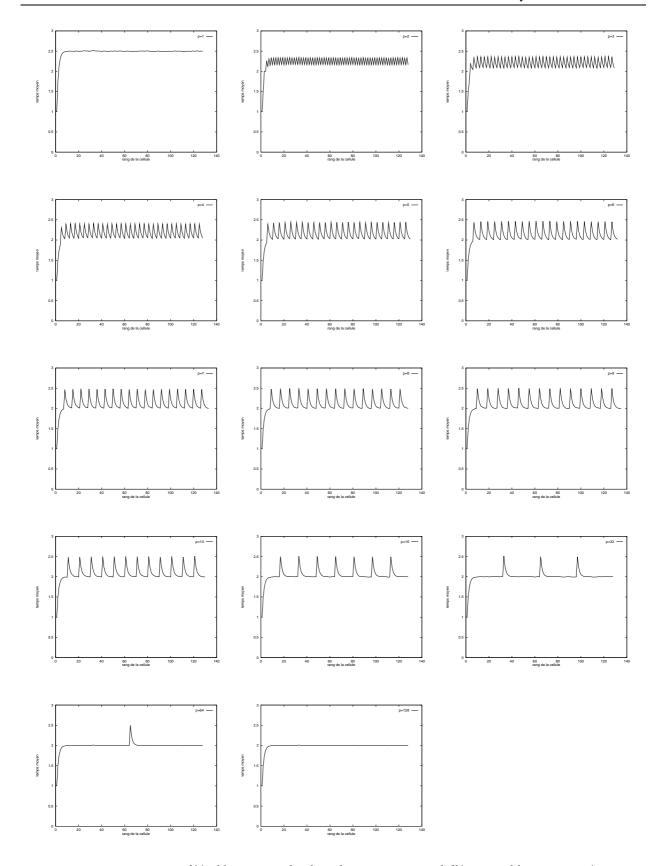

|                  | 4 5   | •                                                       |

|                  | 4.5   | Quelques autres opérateurs arithmétiques asynchrones    |

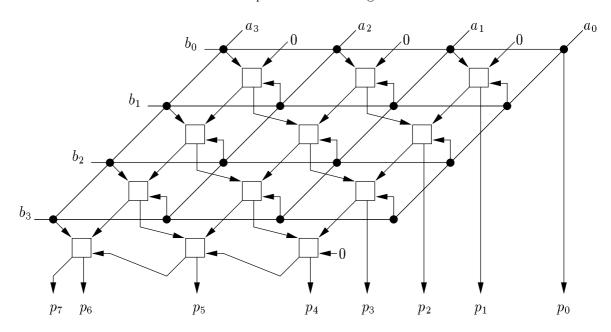

|                  |       | 4.5.1 Multiplieur de Braun                              |

|                  |       | 4.5.2 Diviseur de Guild                                 |

|                  | 4.6   | Conclusion et perspectives                              |

| $\mathbf{C}_{0}$ | onclu | usion 131                                               |

# Liste des figures

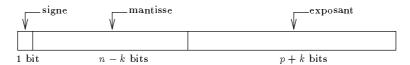

| 1.1<br>1.2<br>1.3<br>1.4 | Codage normalisé des nombres flottants                                                                                                                                                                    | 9      |

|--------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|

| 2.1<br>2.2               | Codage des nombres dans le système semi-logarithmique                                                                                                                                                     |        |

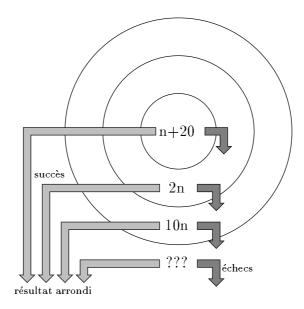

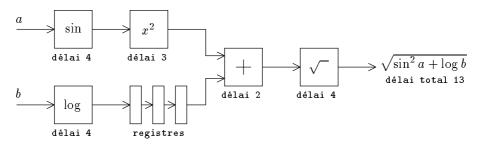

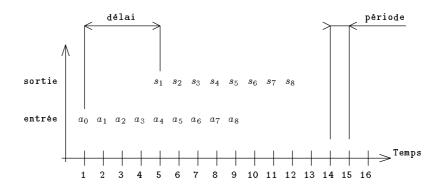

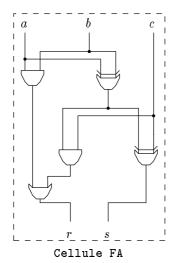

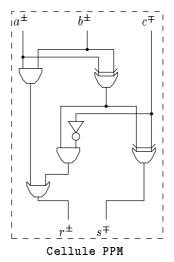

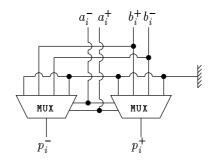

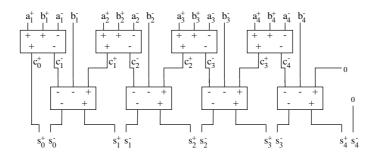

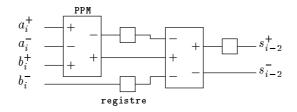

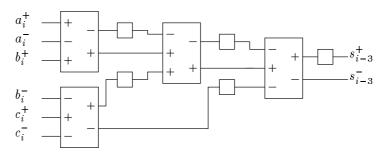

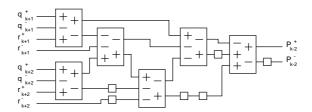

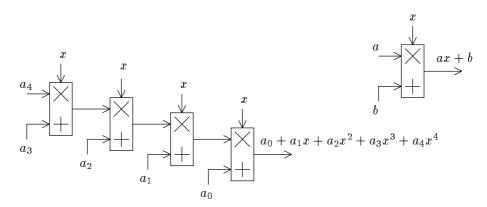

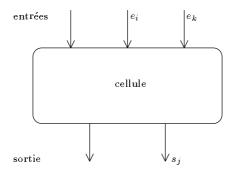

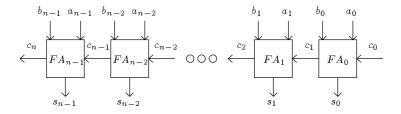

| 3.1<br>3.2<br>3.3<br>3.4 | Exemple de calcul en-ligne.       6         Délai et période d'un opérateur en-ligne.       6         Cellules FA et PPM.       6         Cellule réalisant le produit de 2 chiffres borrow-save.       6 | 1<br>5 |

| $\frac{3.5}{3.6}$        | Un additionneur borrow-save parallèle 4 bits                                                                                                                                                              | 7      |

| 3.7<br>3.8               | Additionneur en-ligne de trois nombres (délai 3)                                                                                                                                                          | 8      |

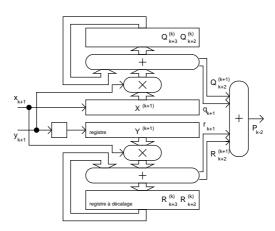

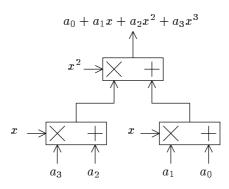

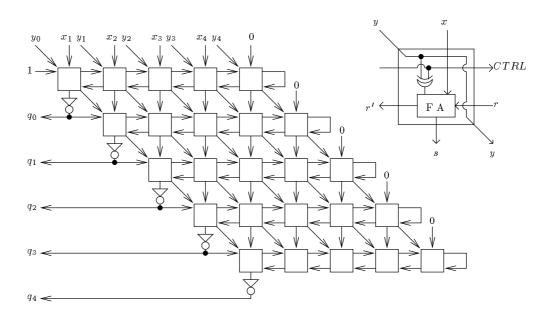

| $3.9 \\ 3.10 \\ 3.11$    | Additionneur final du multiplieur en-ligne de délai 3                                                                                                                                                     | 0      |

|                          | Evaluation de polynômes combinant une table et un polynômieur basé sur le schéma de Horner                                                                                                                |        |

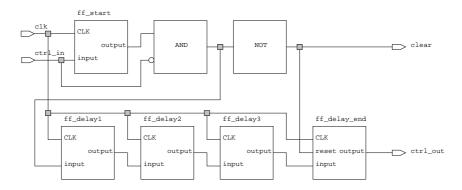

|                          | Cellule add_on_line.         70           Bloc de contrôle (délai 4).         75                                                                                                                          | 6      |

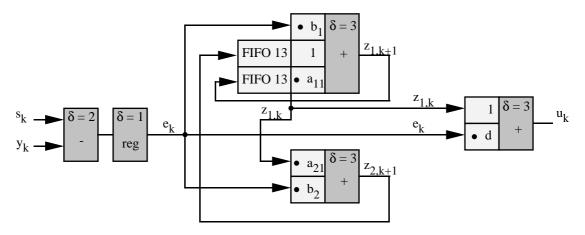

| 3.15                     | Schéma du régulateur PÍD réalisé                                                                                                                                                                          | 2      |

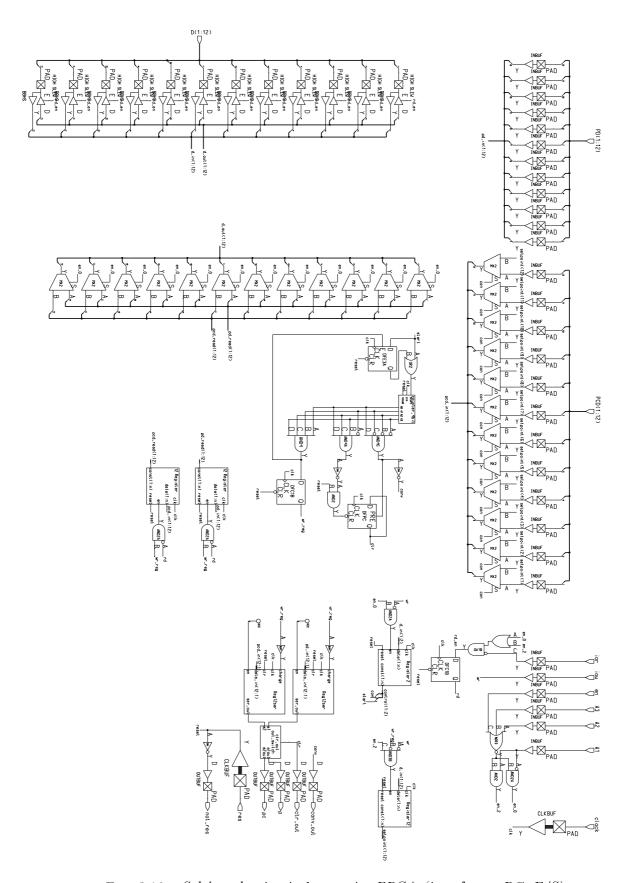

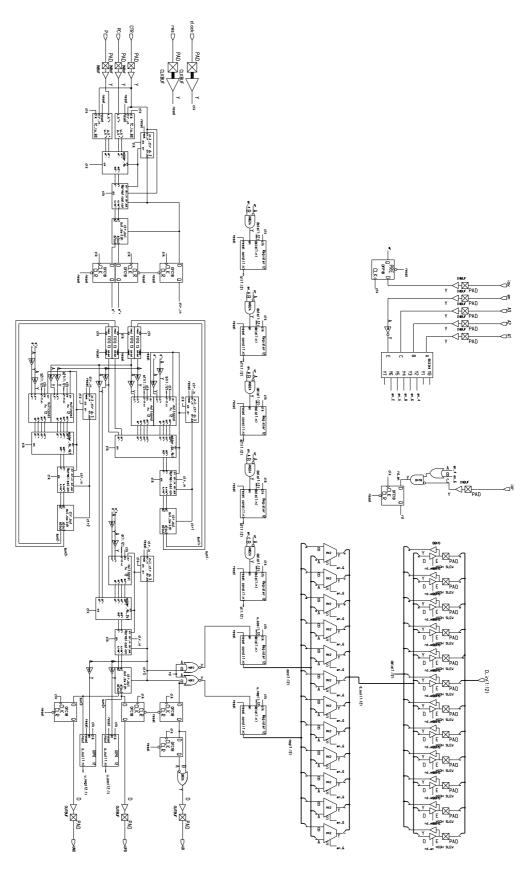

|                          | Schéma du circuit du second FPGA (régulateur PID)                                                                                                                                                         |        |

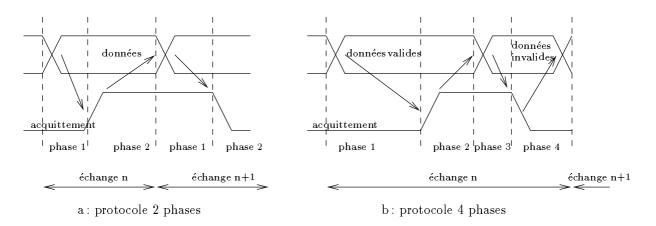

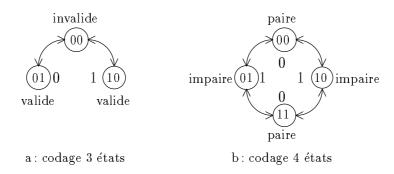

| 4.1                      | Protocoles de communication à 2 phases et à 4 phases                                                                                                                                                      | 2      |

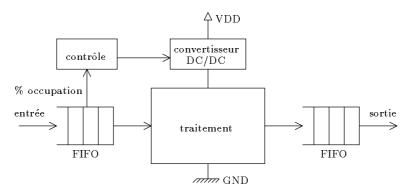

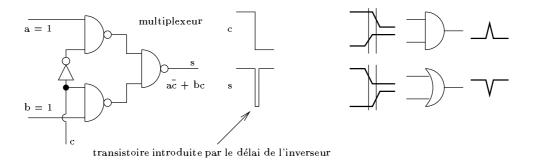

| 4.3<br>4.4               | Régulation de la tension d'alimentation en fonction de la charge (circuit Philips) 9. Aléas de fonctionnement statiques                                                                                   | 5      |

| $4.5 \\ 4.6$             | Modèle de cellule de notre simulateur                                                                                                                                                                     | 1      |

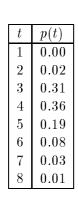

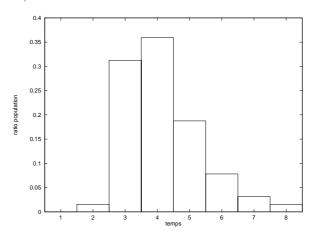

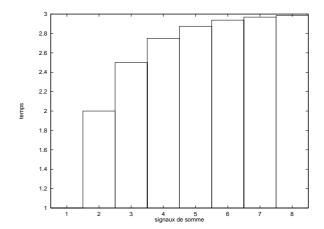

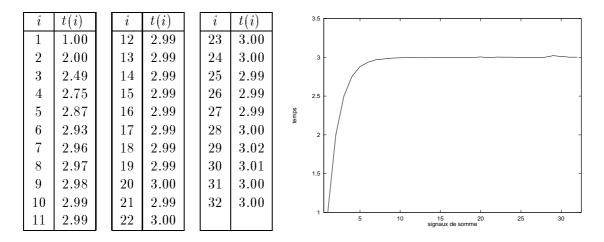

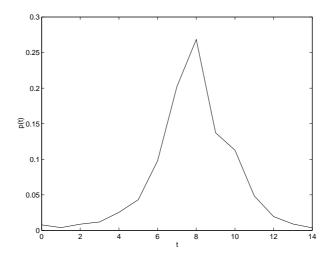

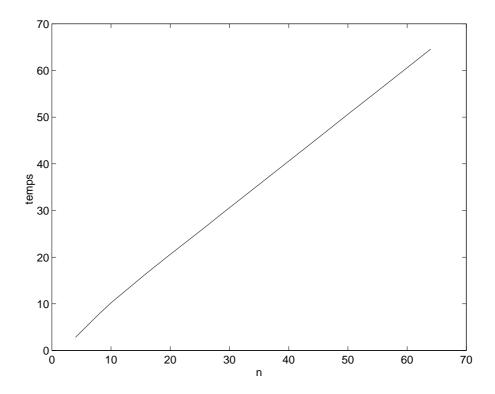

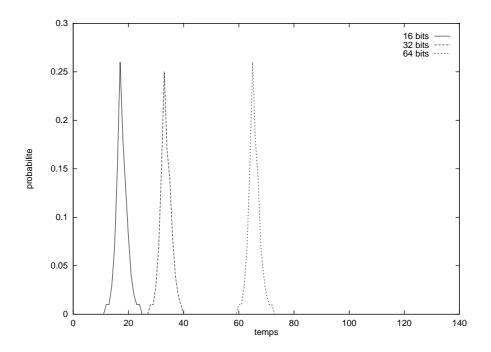

| 4.7<br>4.8               | Distribution du temps de calcul pour un additionneur séquentiel 8 bits (test exhaustif).10 Temps moyen d'établissement des bits de somme pour un additionneur séquentiel 8 bits (test exhaustif)          |        |

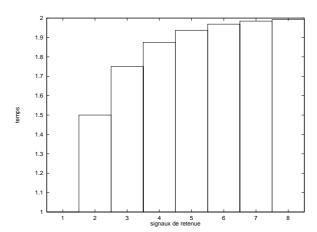

| 4.9  | Temps moyen d'établissement des bits de retenue pour un additionneur séquentiel 8        |     |

|------|------------------------------------------------------------------------------------------|-----|

|      | bits (test exhaustif)                                                                    | 102 |

| 4.10 | Distribution du temps de calcul pour un additionneur séquentiel 32 bits (tests aléa-     |     |

|      | toires)                                                                                  | 103 |

| 4.11 | Temps moyen d'établissement des bits de somme pour un additionneur séquentiel 32         |     |

|      | bits (tests aléatoires)                                                                  | 103 |

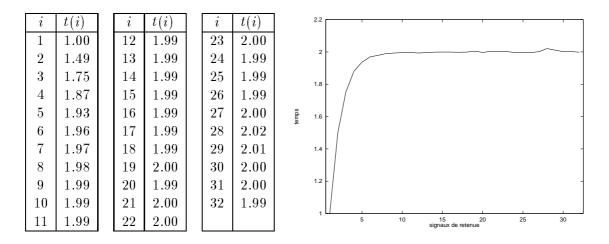

| 4.12 | Temps moyen d'établissement des bits de retenue pour un additionneur séquentiel          |     |

|      | 32 bits (tests aléatoires)                                                               | 104 |

| 4.13 | Valeur moyenne et écart-type du temps de calcul des additionneurs séquentiels de         |     |

|      | taille comprises entre 8 et 128                                                          | 105 |

| 4.14 | Influence des délais des sorties des cellules FA sur la moyenne du temps de calcul       |     |

|      | pour un additionneur séquentiel 128 bits                                                 |     |

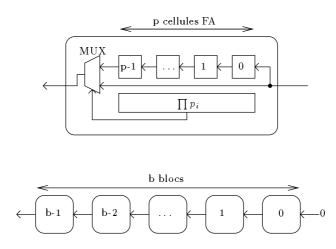

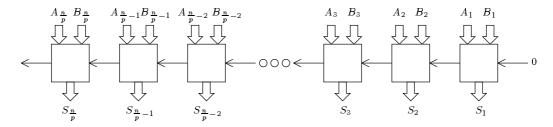

| 4.15 | Additionneur à retenue bondissante avec $b$ blocs de $p$ bits                            | 106 |

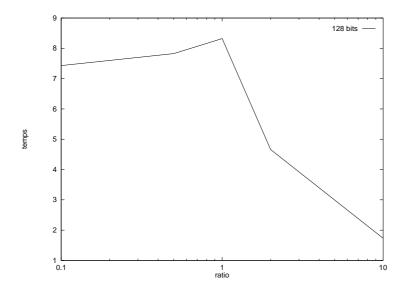

| 4.16 | Temps moyen de calcul pour différents délais des portes dans des additionneurs à         |     |

|      | retenue bondissante de taille 128 pour différents délais relatifs des portes             | 109 |

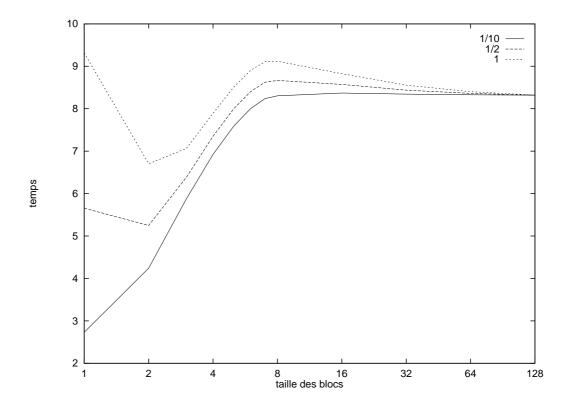

| 4.17 | Temps moyen d'établissement des bits de retenue pour différents additionneurs à          |     |

|      | retenue bondissante de taille 128                                                        | 110 |

| 4.18 | Valeur moyenne et écart type du temps de calcul de quelques additionneurs à retenue      |     |

|      | bondissante (délais égaux à 1)                                                           | 111 |

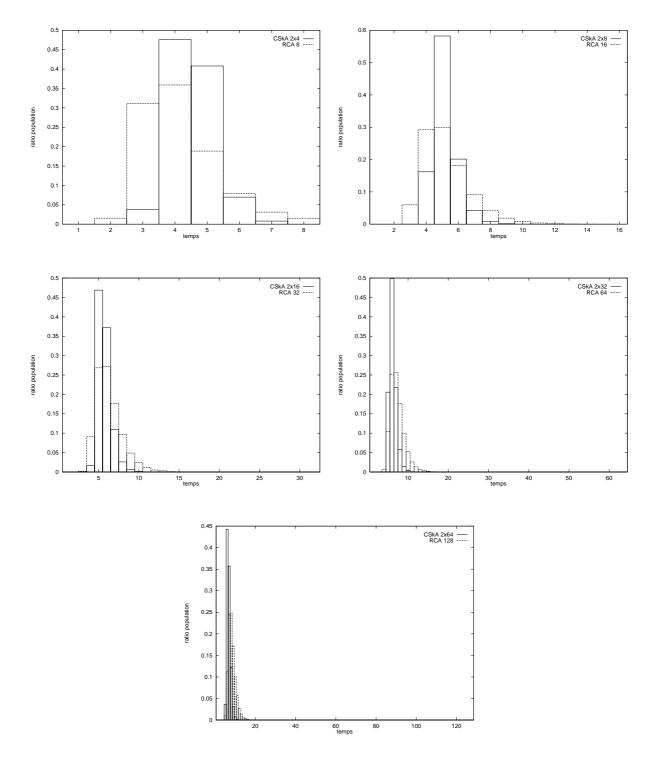

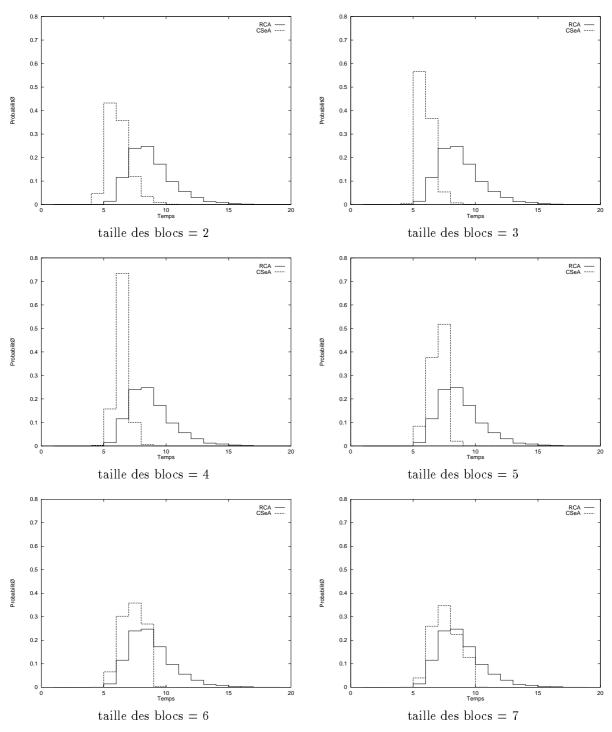

| 4.19 | Comparaison de la distribution du temps de calcul d'additionneurs à retenue bon-         |     |

|      | dissante (CSkA) et d'additionneurs séquentiels (RCA)                                     | 112 |

| 4.20 | L'architecture globale de l'additionneur à sélection de retenue                          | 113 |

| 4.21 | L'architecture d'un bloc de l'additionneur à sélection de retenue                        | 114 |

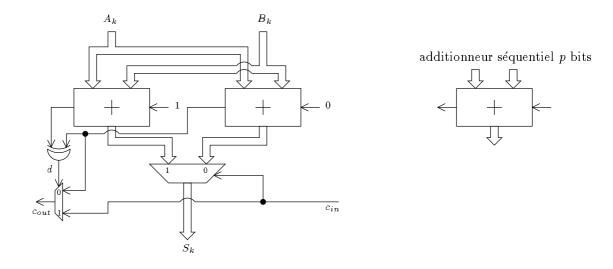

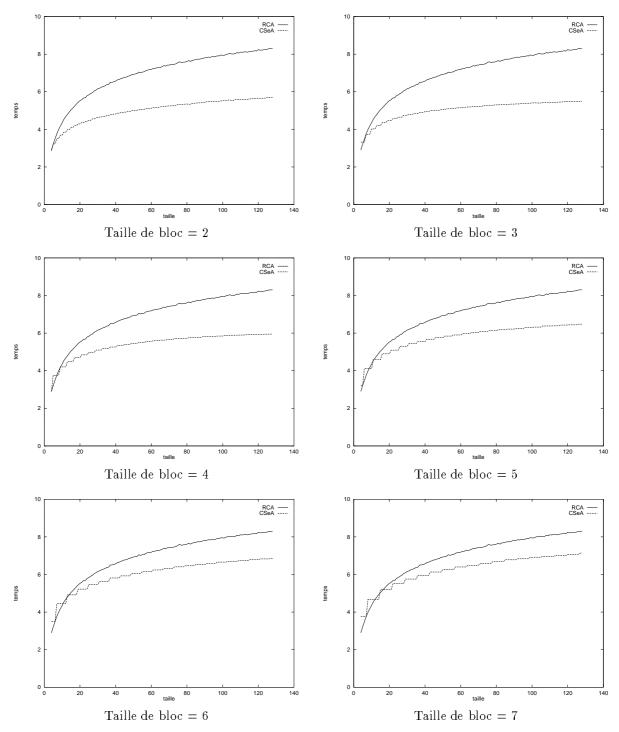

| 4.22 | Comparaison entre le temps de calcul moyen d'additionneurs à sélection de retenue        |     |

|      | et des additionneurs séquentiels de même taille                                          | 115 |

| 4.23 | Distribution du temps de calcul d'un additionneur à sélection de retenue de taille 128   |     |

|      | pour différents découpages avec comparaison de l'additionneur séquentiel de même         |     |

|      | taille.                                                                                  | 116 |

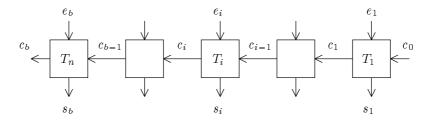

| 4.24 | Modèle de base du découpage en blocs d'un additionneur asynchrone                        | 118 |

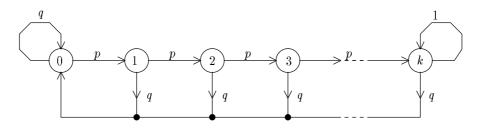

| 4.25 | Chaîne de Markov représentant un additionneur asynchrone                                 | 123 |

| 4.26 | Multiplieur de Braun $4 \times 4$                                                        | 124 |

| 4.27 | Distribution du temps de calcul d'un multiplieur de Braun de taille $8 \times 8$         | 125 |

| 4.28 | Temps moyen de calcul d'un multiplieur de Braun $n \times n$                             | 125 |

| 4.29 | Distribution du temps de calcul de différents multiplieurs de Braun $n \times n$ ( $n =$ |     |

|      | 16, 32, 64)                                                                              | 126 |

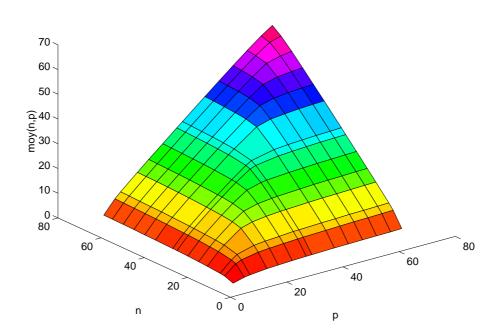

| 4.30 | Distribution du temps de calcul de différents multiplieurs de Braun $n \times p$ pour    |     |

|      | différentes valeurs de $n$ et de $p$                                                     | 127 |

| 4.31 | Diviseur de Guild 5 bits                                                                 | 128 |

|      |                                                                                          |     |

# Liste des tables

| 1.1          | Caractéristiques des formats flottants IEEE 754                                                                                                                                                                                                         | 10       |

|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| 1.2          | Valeurs représentables dans les formats IEEE 754                                                                                                                                                                                                        | 10       |

| 1.3          | Spécification IEEE 754 de l'addition flottante                                                                                                                                                                                                          | 11       |

| 1.4          | Règles permettant d'arrondir exactement la multiplication flottante (IEEE 754). La règle +1 signifie qu'il faut ajouter 1 à $\hat{p}_H$ pour obtenir l'arrondi exact de $p$ . L'absence                                                                 | 1.4      |

| 1.5          | de règle indique que $\hat{p}_H$ est l'arrondi souhaité                                                                                                                                                                                                 | 14<br>20 |

| 1.6          | Valeurs de $m$ pour la fonction $\sin x$ , avec des nombres flottants dont la taille de la mantisse $n$ varie entre 10 et 24, l'exposant varie entre -5 et 5 et avec le mode                                                                            | 20       |

|              | d'arrondi au plus près                                                                                                                                                                                                                                  | 21       |

| 1.7<br>1.8   | Valeurs de $m$ pour la simple précision $(n = 24)$                                                                                                                                                                                                      | 21       |

| 1.9          | avec arrondi au plus près et pour l'exposant $0. \dots \dots \dots \dots \dots$ .  Distribution des chaînes de 1 ou de 0 consécutifs qui provoquent le TMD lors du calcul de la fonction $\sin x$ pour différentes tailles de la mantisse (avec 0 comme | 22       |

| 1.10         | exposant et l'arrondi au plus près)                                                                                                                                                                                                                     | 23       |

|              | et avec 0 comme exposant pour l'arrondi au plus près. Résultats de tirages aléatoires uniformément répartis                                                                                                                                             | 24       |

| 1.11         | Majorants de $m$ pour le calcul de l'exponentielle dans les principaux formats de                                                                                                                                                                       | ۰.       |

| 1.12         | nombres flottants IEEE 754                                                                                                                                                                                                                              | 25<br>26 |

|              | ı                                                                                                                                                                                                                                                       |          |

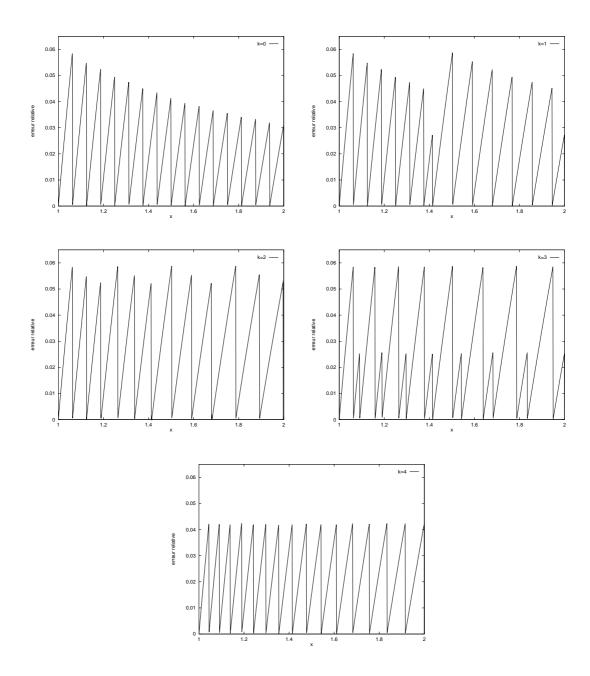

| 2.1          | ERRMax et ERRMoy du système semi-logarithmique et des systèmes flottants et logarithmiques pour différentes valeurs de $k$                                                                                                                              | 55       |

| 3.1          | Complexité en surface et en temps des principaux opérateurs                                                                                                                                                                                             | 62       |

| 3.2          | Représentation des chiffres en borrow-save                                                                                                                                                                                                              | 64       |

| 3.3          | Cellules élémentaires de la bibliothèque                                                                                                                                                                                                                | 75       |

| 3.4          | Opérateurs en-ligne de la bibliothèque                                                                                                                                                                                                                  | 75       |

| $4.1 \\ 4.2$ | Valeur moyenne et écart-type du temps de calcul de quelques additionneurs séquentiels. Influence des délais des sorties des cellules FA sur la moyenne et l'écart-type du                                                                               | 104      |

|              | temps de calcul pour un additionneur séquentiel 128 bits                                                                                                                                                                                                |          |

| 4.3          | Additionneurs à retenue bondissante de taille 8                                                                                                                                                                                                         |          |

| 4.4          | Additionneurs à retenue bondissante de taille 128                                                                                                                                                                                                       |          |

| 4.5          | Temps moyen de calcul de quelques additionneurs à sélection de retenue                                                                                                                                                                                  | 114      |

- 4.6 Distribution du temps de calcul d'un multiplieur de Braun de taille  $8\times 8.$  . . . . . . . . 125

- 4.7 Valeur moyenne et écart type du temps de calcul de différents multiplieurs de Braun. 126

### Introduction

ES premières générations de processeurs n'étaient capables d'évaluer matériellement que des additions et des multiplications (et encore, ces dernières étaient souvent obtenues par des additions successives), les autres opérations comme la division, la racine carrée et les fonctions élémentaires (sinus, cosinus, exponentielle...) étaient alors évaluées par des routines logicielles.

Les importants besoins en calcul scientifique et dans les applications spécialisées ont poussé les constructeurs de machines à intégrer de plus en plus de fonctionnalités arithmétiques directement dans leurs circuits intégrés pour obtenir de plus grandes performances. Les processeurs actuels sont des véritables "dévoreurs de nombres", leurs performances s'expriment en centaines de MFlops (Millions d'instructions flottantes par seconde). Par exemple, un processeur DEC Alpha 21164 est capable de commencer au moins une multiplication flottante et une addition flottante sur 53 bits à chaque cycle d'horloge à une fréquence de quelques centaines de MHz.

Les performances des unités de calcul de ces processeurs témoignent de l'effort de conception investi dans la réalisation de machines pour le calcul à hautes performances. En effet, il est aujour-d'hui possible d'effectuer plusieurs millions d'additions, de multiplications, de divisions, de racines carrées, de sinus, de cosinus..., en quelques secondes avec une machine coûtant moins de 10 000 F.

Ces importantes améliorations des performances des unités de calcul (sur des nombres entiers et réels) ont été rendues possibles grâce aux recherches effectuées dans de nombreux domaines, dont les principaux sont:

- La micro-électronique avec la diminution de la taille des gravures (technologies  $0.35, 0.25 \mu m$ ), l'augmentation des fréquences d'horloge, les optimisations des composants...

- L'architecture des ordinateurs avec des techniques de plus en plus sophistiquées de hiérarchie mémoire (les caches), de parallélisme (pipeline et multiplication des unités fonctionnelles), de prédictions dans les branchements...

- L'arithmétique des ordinateurs avec la mise au point et l'utilisation d'algorithmes de calcul et de systèmes de représentation des nombres de plus en plus performants.

La littérature en arithmétique des ordinateurs montre qu'en changeant notre façon de représenter les nombres et/ou en utilisant des algorithmes spécifiques de calcul, il est possible de réaliser des opérateurs matériels particulièrement efficaces. Dans cette thèse, nous nous sommes attachés à étudier certains liens qui existent entre l'arithmétique des ordinateurs et l'architecture des machines. Dans ce cadre, nous avons étudié les points suivants:

- L'arrondi exact des fonctions élémentaires;

- Le système semi-logarithmique de représentation des nombres;

- Le calcul en-ligne sur FPGA;

- Les opérateurs arithmétiques asynchrones.

#### L'Arrondi Exact des Fonctions Elémentaires

Le résultat d'un calcul dans le système virgule flottante (système classique pour la manipulation des nombres réels) n'est généralement pas représentable exactement en machine du fait de la représentation des nombres avec une précision limitée. Les calculs sont donc arrondis (le résultat retourné est l'un des deux nombres représentables en machine qui encadrent le résultat théorique). L'arrondi exact d'une opération arithmétique est obtenu en utilisant une technique qui permet de déterminer le résultat de l'opération comme si le calcul était effectué exactement, avec une précision infinie, puis arrondi. Les opérations flottantes de base (addition, soustraction, multiplication et division) sont exactement arrondies dans la plupart des machines actuelles (norme IEEE 754). L'arrondi exact des calculs permet de une meilleure portabilité des programmes ou de concevoir des preuves de certains algorithmes numériques par exemple.

Pour le moment, il n'existe pas de pareille exigence pour les fonctions élémentaires (sinus, cosinus, exponentielle, logarithme...). En effet, l'arrondi exact des fonctions élémentaires est un problème que l'on a pensé pratiquement insoluble pendant longtemps. Il consiste à déterminer la précision intermédiaire permettant de toujours pouvoir arrondir exactement les résultats du calcul des fonctions élémentaires. On sait depuis longtemps (1885) que le nombre de chiffres intermédiaires nécessaires à la réalisation de cet arrondi exact est fini, mais les grandes valeurs (10<sup>244</sup> bits en utilisant un résultat de 1975) trouvées jusqu'à présent laissaient penser que cet arrondi n'était pas pratiquement réalisable.

Nous présentons dans cette thèse, une méthode permettant d'arrondir exactement les fonctions élémentaires sans changer significativement le temps moyen de calcul de ces fonctions.

#### Le Système Semi-Logarithmique de Représentation des Nombres

Pour certaines applications, il est possible d'accélérer considérablement les calculs en utilisant des systèmes de représentation des nombres différents du système usuel. Par exemple, les systèmes redondants permettent d'effectuer des additions en temps constant. Ces systèmes sont utilisés dans la plupart des multiplieurs et des diviseurs actuels du fait du gain de vitesse qu'ils représentent.

Dans le système logarithmique, on représente les nombres réels par leur signe et le logarithme de leur valeur absolue écrite en virgule. Ce système permet d'effectuer très rapidement des multiplications et des divisions. Le système logarithmique s'est avéré très performants dans certaines applications en contrôle numérique et en traitement du signal et des images. Toutefois, l'implantation matérielle d'unités de calcul fonctionnant dans le système logarithmique n'est pas possible actuellement pour des nombres de taille supérieure à 24 bits. En effet, les opérations d'addition et de soustraction dans le système logarithmique nécessitent des tables à  $2^n$  entrées où n est le nombre de chiffres des nombres.

Nous proposons dans cette thèse un nouveau système de représentation des nombres réels baptisé système semi-logarithmique. C'est un système à mi-chemin entre le système virgule flottante et le système logarithmique. Nous présentons des algorithmes qui permettent d'effectuer les opérations de base (addition, soustraction, multiplication et division) dans ce système, ainsi que des algorithmes pour effectuer des conversions depuis et vers le système virgule flottante. En particulier, nous montrons en quoi ce système permet d'effectuer beaucoup plus rapidement des additions et des soustractions que le système logarithmique. Enfin, nous comparons la qualité de la représentation de ce système avec celle des systèmes virgule flottante et logarithmique.

#### Arithmétique En-Ligne sur FPGA

L'arithmétique en-ligne permet de réaliser des architectures de calcul où les chiffres circulent en série, chiffre après chiffre, les poids forts en tête. L'intérêt de cette arithmétique est de pouvoir calculer toutes les fonctions (en arithmétique série poids faibles en tête, il n'est pas possible de calculer certaines opérations comme la division ou le maximum) et d'obtenir des opérateurs de petite taille avec un nombre d'entrées/sorties plus faible que leur équivalents parallèles.

Nous présentons dans cette thèse la réalisation d'une bibliothèque d'opérateurs en-ligne pour des implantations sur des composants programmables FPGA (field programmable gate arrays). Cette association d'une arithmétique permettant de réaliser des opérateurs ayant une petite surface de circuit et très performants et d'un support matériel flexible semble être particulièrement efficace pour des applications de contrôle embarqué (collaboration avec l'équipe aérospatiale du Centre Suisse d'Electronique et de Microtechnique de Neuchatel et le département d'automatique de l'Ecole Polytechnique Fédérale de Lausanne) ou bien des applications de traitement du signal et des images (collaboration avec l'équipe de McCanny et Woods à la Queen's University of Belfast et l'équipe de M. Ercegovac à l'University of California at Los Angeles).

#### Les Opérateurs Arithmétiques Asynchrones

Les circuits intégrés asynchrones semblent être de plus en plus une alternative efficace aux circuits intégrés synchrones pour la réalisation de systèmes de calcul à très hautes performances. En effet, les circuits asynchrones ne posent pas certains problèmes de conception de plus en plus difficiles à résoudre pour les circuits synchrones.

Les opérateurs arithmétiques asynchrones permettent de calculer les fonctions arithmétiques (addition, multiplication, division...) avec un délai variable. Dans cette thèse, nous avons développé des opérateurs arithmétiques asynchrones dont le temps moyen de calcul est plus faible que le temps de calcul des équivalents synchrones. En particulier, nous présentons dans ce document l'étude de différents additionneurs asynchrones dont le temps moyen de calcul est en  $\mathcal{O}(\sqrt{\log n})$ . Ces opérateurs semblent particulièrement efficaces pour des implantations matérielles à faible consommation pour des applications embarquées ou des appareils portables. Dans ce domaine, nous étudions en collaboration avec de l'équipe de M. Renaudin au CNET les différents aspects liés à l'implantation et à l'utilisation de ces opérateurs.

# Arrondi exact des fonctions élémentaires

**CHAPITRE**

# 1 Arrondi exact des fonctions élémentaires

ES calculs effectués en machine sur les nombres réels sont en général entachés d'erreurs du fait de la précision limitée de la représentation de ces nombres dans l'ordinateur. Par exemple, en base 10, le résultat de la division  $\frac{10.0}{3.0}$  ne peut pas s'écrire sur un nombre fini de chiffres. On procède alors à une phase d'arrondi. C'est-à-dire que l'on décide de choisir l'un des deux nombres représentables qui encadrent le résultat exact. Différents modes d'arrondi sont possibles, comme l'arrondi par excès ou l'arrondi au plus près.

L'arrondi exact d'une opération est obtenu en utilisant des techniques qui permettent de déterminer le résultat comme si le calcul était effectué exactement, avec une précision "infinie", puis arrondi suivant le mode d'arrondi choisi. Les opérations qui répondent à cette spécification sont dites exactement arrondies.

La plupart du temps, les nombres réels sont représentés en machine en utilisant la norme IEEE 754. Cette norme spécifie le codage des nombres réels au niveau du bit. Elle spécifie aussi le codage de valeurs spéciales comme les dépassements de capacité et les résultats d'opérations indéterminés (comme le résultat de  $\sqrt{-1}$ , celui de  $\frac{0}{0}$  ou celui de  $\infty - \infty$ ). Ceci permet une compatibilité totale lors des échanges de données entre les machines. La norme IEEE 754 spécifie différents modes d'arrondi valides dans tous les formats de la norme (simple précision, double précision, formats étendus...).

Cette spécification conjointe du codage des données (nombres réels et valeurs spéciales) et des modes d'arrondi permet une spécification complète des opérations de base (addition, soustraction, multiplication, division et racine carrée). C'est probablement le point le plus important de la norme IEEE 754. En effet, les opérations ne sont plus dépendantes de leur réalisation pratique car leur comportement est complètement spécifié dans le cadre d'une véritable structure mathématique. On a alors une compatibilité totale des algorithmes d'une machine à l'autre. C'est-à-dire qu'un algorithme (où l'ordre des opérations est déterminé) donnera exactement le même résultat sur différentes machines compatibles avec la norme IEEE 754. Il y a aussi une compatibilité des codes sources correspondants à ces algorithmes, à condition que les compilateurs aient des comportements identiques sur les différentes plateformes de développement. Les contraintes mathématiques ainsi introduites peuvent permettre de réaliser des preuves sur les algorithmes numériques employés.

L'arrondi exact des fonctions arithmétiques (addition, soustraction et multiplication) et des fonctions algébriques (division et racine carrée) est toujours assez facilement réalisable en machine. En effet, pour ces opérations on sait déterminer la précision intermédiaire nécessaire pour arrondir exactement le résultat quelle que soit la précision finale demandée. On a cru pendant très long-temps que cet arrondi exact n'était pas pratiquement réalisable pour les fonctions élémentaires (sin, cos, exp, log, arctan...). La précision nécessaire lors des calculs intermédiaires pouvait être, pensait-on, si importante qu'elle interdit totalement une mise en œuvre effective de l'arrondi exact de ces fonctions pourtant si utiles en calcul scientifique.

Nous allons montrer dans ce chapitre que l'arrondi exact des fonctions élémentaires est tout à fait réalisable en pratique et que son coût n'est pas forcément si élevé que ce que l'on pouvait penser a priori. En effet, les tests que nous avons effectués montrent que les cas qui conduisent à des calculs intermédiaires en très grande précision sont rarissimes. Nous montrerons que dans la quasi totalité des cas, l'arrondi exact des fonctions élémentaires peut être réalisé en machine avec des techniques proches de celles de l'arrondi des opérations de base. Nous verrons aussi que dans les cas les plus extrêmes, cet arrondi est toujours possible et que la détection des cas "pathologiques" associés est très simple.

Dans la première partie de ce chapitre, nous présentons les différents aspects de la norme IEEE 754. Les principales caractéristiques de cette norme nous serviront tout au long de cette thèse. Nous décrirons en particulier l'arrondi des opérations de base afin de pouvoir effectuer des analogies et des comparaisons avec celui des fonctions élémentaires par la suite.

La deuxième partie de ce chapitre est dédiée au problème de l'arrondi exact des fonctions élémentaires. Dans ce cadre, nous présenterons des tests effectués sur certains formats de nombres flottants et une modélisation probabiliste du problème qui permettent de bien appréhender les mécanismes sous-jacents à ce problème. Nous rappellerons des résultats de théorie des nombres qui nous permettront de donner des bornes supérieures du temps d'exécution de nos algorithmes.

La dernière partie propose une ébauche de réflexion sur la mise en œuvre pratique (matérielle et/ou logicielle) de l'arrondi exact des fonctions élémentaires.

#### 1.1 La norme IEEE 754

Nous présentons ici les principales caractéristiques de la norme IEEE 754 qui spécifie la représentation des nombres réels en "virgule flottante", le comportement de certaines opérations arithmétiques et des conversions (conversions entre les différents formats). Cette présentation de la norme IEEE 754 nous servira dans d'autres parties de cette thèse.

Une bonne introduction sur l'arithmétique flottante du point de vue de l'utilisateur se trouve dans [Gol91]. Les bases de l'implantation matérielle des opérateurs flottants sont décrites dans [HP96]. Une étude générale plus détaillée des opérations arithmétiques et de leur réalisation matérielle se trouve dans [Omo94].

#### 1.1.1 Codage des nombres flottants dans la norme IEEE 754

La norme IEEE 754, établie en 1985 (cf [AI85]), spécifie la représentation interne des nombres réels en arithmétique flottante en base 2, ainsi que le comportement des opérations portant sur ces nombres (opérations mathématiques et conversions entre les différents formats). La norme IEEE 854 (cf [AI87]), rédigée par le même comité, fixe l'implantation de l'arithmétique flottante en base 2 et en base 10 et autorise de plus grandes libertés au niveau de la définition des formats des nombres. Dans la suite, nous ne nous intéresserons qu'à la norme IEEE 754 car c'est-t-elle qui est implantée sur la plupart des ordinateurs actuels.

Un nombre réel x est codé en arithmétique virgule flottante (en base 2) selon le codage:

$$x = s_x \times M_x \times 2^{e_x}$$

οù

•  $s_x$  est le signe de x. Plus précisément, le bit de signe s est égal à 0 si  $x \ge 0$  et 1 sinon, on a

LA NORME IEEE 754

alors  $s_x = (-1)^s$ . Les nombres flottants sont stockés selon le codage (signe, valeur absolue), la valeur absolue  $M_x 2^{e_x}$  étant stockée dans les deux champs suivants.

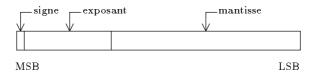

- $e_x$  est l'exposant de x. Il peut avoir n'importe quelle valeur entière dans l'intervalle  $[-e_{max} + 1, e_{max}]$ . En fait, on ne représente pas directement l'exposant mais l'exposant plus un biais de sorte que le champ exposant représente  $e_x + e_{max}$ . Ceci permet de représenter simplement les exposants négatifs sans recours à une notation spéciale comme le complément à la base et permet d'effectuer facilement des comparaisons entre deux nombres flottants. En effet, l'ordre des bits dans les champs (signe, exposant, mantisse), voir la Figure 1.1, pour les valeurs positives, coïncide avec l'ordre lexicographique. Ceci permet d'effectuer des comparaisons sur les nombres flottants en faisant comme si il s'agissait d'entiers. Les entrées du comparateur entier sont en complément à 2 ce qui permet d'effectuer directement la comparaison. Le plus petit et le plus grand exposant (biaisé) sont réservés pour le codage de valeurs spéciales (cf Tableau 1.2). Par exemple, en simple précision l'exposant biaisé est dans l'intervalle [1,254], les exposants 0 et 255 sont réservés pour le codage des valeurs spéciales. La valeur de  $e_{max}$  et la taille du champ exposant dépendent du type utilisé (cf Tableau 1.1).

- $M_x$  est la mantisse de x. Le nombre de chiffres de la mantisse étant limité, l'introduction de zéros à gauche de cette mantisse a tendance à diminuer la précision de la représentation. Par exemple, avec un système ayant 8 bits de mantisse, si le résultat exact d'une multiplication est 0.000000101101, alors la réécriture de ce résultat sur 8 bits dans le format cible entraîne une importante perte de précision car les derniers bits du résultat sont alors "perdus". Même si à chaque opération, l'erreur commise n'est pas très importante devant le résultat de l'opération, il est possible que lors d'une séquence d'opérations le résultat final ne soit plus significatif tant l'accumulation des erreurs est importante. Ainsi, on exige que le premier chiffre de la mantisse soit non nul. On parle alors de nombres normalisés  $(1 \le M_x < 2)$ . En base 2, le premier chiffre de la mantisse est donc obligatoirement égal à 1. En pratique ce bit, appelé bit implicite, n'est pas stocké physiquement (sauf dans les formats "étendus"). Le fait que les mantisses doivent être supérieures ou égales à 1 implique que le nombre 0 doit être codé d'une façon spéciale (cf Tableau 1.2). On appelle fraction f les bits de la mantisse effectivement stockés (sans le bit implicite). La taille du champ correspondant à la mantisse dépend du type utilisé (cf Tableau 1.1). Par exemple, en double précision la mantisse est de 53 bits mais seuls les 52 derniers sont effectivement stockés.

Fig. 1.1 – Codage normalisé des nombres flottants.

Exemple 1.1 Le nombre flottant simple précision (32 bits):

représente la valeur (les bits soulignés sont ceux des différents champs du nombre flottant) :

Le Tableau 1.1 donne la taille des différents champs et la valeur du biais pour chacun des formats définis par la norme IEEE 754.

| format           | mantisse (bits) | exposant (bits) | biais        | longueur totale (bits) |

|------------------|-----------------|-----------------|--------------|------------------------|

| simple           | 1+23            | 8               | 127          | 32                     |

| simple étendu    | $\geq 32$       | ≥ 11            | $\geq 1023$  | $\geq 40$              |

| double           | 1+52            | 11              | 1023         | 64                     |

| double étendu    | $\geq 64$       | $\geq 15$       | $\geq 16383$ | $\geq 80$              |

| double étendu PC | 1+64            | 15              | 16383        | 80                     |

| quad             | 112             | 15              | 16383        | 128                    |

Tab. 1.1 – Caractéristiques des formats flottants IEEE 754.

Du fait du nombre limité de chiffres, tous les réels ne sont pas représentables. Notons F l'ensemble des nombres réels représentables exactement dans le format utilisé.

En plus des valeurs numériques classiques (les éléments de F), la norme IEEE 754 définit d'autres catégories de valeurs pour gérer "proprement" les résultats d'opérations indéterminés (ex: division par 0), ainsi que les dépassements de capacité. Ces valeurs spéciales sont:

- $\{-\infty, +\infty\}$  Ces valeurs infinies représentent à la fois un dépassement de capacité positif ou négatif et les résultats respectifs des opérations  $\frac{a}{0+}$  et  $\frac{a}{0-}$  où  $a \in \mathbb{F}_+^*$ .

- $\{0^+, 0^-\}$  L'existence de deux codages différents pour 0 est la conséquence de la définition des deux valeurs  $-\infty$  et  $+\infty$ . On a  $0^+ = (-1) \times 0^-$ ; et  $0^+ = 0^-$  est vrai même si les codages de  $0^+$  et de  $0^-$  sont distincts.

- NaN (Not a Number) Cette valeur est utilisée pour coder les résultats indéterminés comme  $\sqrt{-1}$  et les résultats qui ne peuvent pas être réduits comme  $\frac{0}{0}$  ou  $\infty \infty$ .

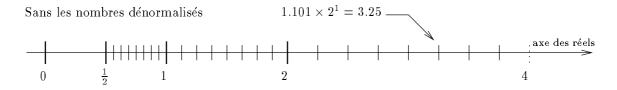

- les nombres dénormalisés Le nombre 0 est codé par l'ensemble des bits du mot machine à 0 (sauf éventuellement le bit de signe). L'exposant non biaisé de 0 est donc  $-e_{max}$  soit le plus petit exposant possible. Sur la Figure 1.2, on peut remarquer qu'il y a un saut important entre le plus petit nombre (en valeur absolue) représentable (de manière "normalisée") non nul et 0. On utilise les mots dont l'exposant est  $-e_{max}$  sans le "1" implicite pour obtenir un spectre plus régulier au voisinage de 0. Ce sont les nombres dénormalisés.

Le Tableau 1.2 donne le codage correspondant à chacune des catégories de valeurs (numériques ou spéciales) représentables dans la norme IEEE 754.

| signe | exposant                     | mantisse            | signification                     |

|-------|------------------------------|---------------------|-----------------------------------|

| 土     | $-e_{max} < e_x \le e_{max}$ | f                   | $\pm 1.\mathtt{f} 	imes 2^{e_x}$  |

| 土     | $e_x = -e_{max}$             | $\mathtt{f} \neq 0$ | $\pm 0.$ f $	imes 2^{-e_{max}+1}$ |

| 土     | $e_x = -e_{max}$             | f = 0               | ±0                                |

| 土     | $e_x = e_{max} + 1$          | f = 0               | $\pm \infty$                      |

|       | $e_x = e_{max} + 1$          | $\mathtt{f} \neq 0$ | NaN                               |

Tab. 1.2 - Valeurs représentables dans les formats IEEE 754.

LA NORME IEEE 754

Avec les nombres dénormalisés

Fig. 1.2 – Nombres positifs représentables en arithmétique flottante sur 3 bits de mantisse et 2 bits d'exposant avec et sans les nombres dénormalisés.

La gestion de l'apparition des valeurs spéciales peut se faire de deux façons différentes. Une première solution consiste à configurer l'unité flottante pour que l'exécution d'une opération problématique déclenche une interruption. La gestion se fait alors avec un mécanisme d'exception (à condition que la machine, le système d'exploitation et/ou le langage de programmation utilisés permettent de gérer effectivement ces exceptions). La deuxième solution consiste à ne pas interrompre le calcul même après une opération illégale. Le résultat retourné à l'utilisateur sera alors cohérent avec la spécification IEEE 754 des opérations mises en jeu. Le comportement des opérations est complètement spécifié vis à vis des valeurs spéciales. Par exemple, la valeur spéciale NaN se propage lors des calculs. Le Tableau 1.3 présente la spécification complète du résultat de l'addition flottante en fonction des valeurs de ses opérandes. On peut trouver dans [AI85, Dau96] les spécifications correspondantes pour les autres opérations.

| addition               | $-\infty$ | $a\in\mathbb{F}_{-}^{*}$ | 0-        | 0+        | $a \in \mathbb{F}_+^*$ | $+\infty$ | NaN |

|------------------------|-----------|--------------------------|-----------|-----------|------------------------|-----------|-----|

| $-\infty$              | $-\infty$ | $-\infty$                | $-\infty$ | $-\infty$ | $-\infty$              | NaN       | NaN |

| $b\in\mathbb{F}^*$     |           | $a + b$ ou $-\infty$     | b         |           | a + b                  | $+\infty$ | NaN |

| 0 <sup>+</sup>         | $-\infty$ | a                        | 0-        | 0+        | a                      | $+\infty$ | NaN |

| 0+                     | $-\infty$ | a                        | 0+        | $0^+$     | a                      | $+\infty$ | NaN |

| $b \in \mathbb{F}_+^*$ | $-\infty$ | a + b                    | b         | b         | $a+b$ ou $+\infty$     | $+\infty$ | NaN |

| $+\infty$              | NaN       | $+\infty$                | $+\infty$ | $+\infty$ | $+\infty$              | $+\infty$ | NaN |

| NaN                    | NaN       | NaN                      | NaN       | NaN       | NaN                    | NaN       | NaN |

Tab. 1.3 – Spécification IEEE 754 de l'addition flottante.

#### 1.1.2 Modes d'arrondi IEEE 754

La norme IEEE 754 donne, en plus des formats et des codages des valeurs numériques et spéciales, une spécification des modes d'arrondi afin de garantir la reproductibilité des calculs. Les opérations ne sont donc plus définies en fonction de caractéristiques physiques de l'architecture de calcul utilisée mais par un ensemble de contraintes mathématiques. C'est l'un des points important de la norme. En effet, pour une précision fixée (un format), un même calcul donne le même résultat

sur toutes les machines compatibles avec la norme. Les contraintes mathématiques ainsi introduites peuvent être utilisées pour la validation et la réalisation de preuves de certains algorithmes numériques.

On appelle nombre machine un nombre qui peut être représenté exactement dans le système virgule flottante utilisé. F est l'ensemble des nombres machine. En général, la somme, le produit ou le quotient de deux nombres machine n'est pas un nombre machine. Le résultat de l'opération doit être arrondi.

La norme définit 4 modes d'arrondi:

- vers  $-\infty$ :  $\nabla(x)$  est le plus grand nombre machine inférieur ou égal à x;

- vers  $+\infty$ :  $\triangle(x)$  est le plus petit nombre machine supérieur ou égal à x;

- vers  $0: \mathcal{Z}(x)$  vaut  $\nabla(x)$  si  $x \geq 0$  et  $\Delta(x)$  sinon;

- au plus près:  $\mathcal{N}(x)$  est le nombre machine le plus proche de x. Si x est exactement entre deux nombres machine, la norme impose que l'arrondi soit le nombre machine dont le bit de poids faible de la mantisse est nul.

La norme IEEE 754 impose que le résultat d'une opération arithmétique  $(+, -, \times \text{ ou } \div)$  ou de la racine carrée soit l'arrondi exact de l'opération. Si  $\diamond$  est le mode d'arrondi actif, alors le résultat de l'opération  $x \star y$  (où  $\star$  est  $+, -, \times$  ou  $\div$ ) ou  $\sqrt{x}$  doit toujours être  $\diamond(x \star y)$  ou  $\diamond(\sqrt{x})$ . L'unité flottante se comporte alors comme si le calcul était effectué exactement, avec une précision infinie, puis arrondi.

Les opérations qui vérifient cette propriété sont dites exactement arrondies. Cette propriété permet de garantir une compatibilité totale. C'est-à-dire, un même programme donnera les mêmes résultats sur toutes les machines compatibles avec la norme (si les compilateurs ne changent pas l'ordre des instructions). De plus, les opérations flottantes étant complètement spécifiées, on dispose d'une véritable structure mathématique qui peut permettre de réaliser des preuves des algorithmes numériques utilisés.

Le choix du mode d'arrondi peut être utilisé pour faire de l'arithmétique d'intervalles. On peut, en effet, calculer  $[\nabla(x), \Delta(x)]$  à chaque étape du calcul et ainsi obtenir un encadrement certain du résultat d'une séquence d'opérations [Kul77, KM81].

Pour le moment, il n'existe pas de spécification des fonctions élémentaires (sin, cos, exp, log, arctan...) dans la norme IEEE 754 (ou 854). Ceci est dû au fait que pendant longtemps on a cru que l'arrondi exact de ces fonctions n'était pas réalisable à un coût raisonnable. Nous montrerons dans la suite de ce chapitre que l'arrondi exact des fonctions élémentaires est effectivement réalisable, et qu'il est temps de songer à une extension de la norme actuelle à ces fonctions.

#### 1.1.3 Réalisation matérielle de l'arrondi exact des fonctions de base

Nous décrivons ici les grandes lignes de l'implantation matérielle de l'arrondi exact des fonctions arithmétiques (addition, multiplication) et évoquerons le cas de la division et de la racine carrée dans le cadre de la norme IEEE 754. Les algorithmes des opérations flottantes et les principes de base de l'arrondi exact de ces fonctions sont détaillés dans [Omo94]. Une bonne introduction sur ce sujet est faite par Goldberg dans [HP96]. Des algorithmes visant des implantations matérielles efficaces sont décrits dans [SBH89] et dans [QTF91]. Enfin, on trouve dans [YZ95] et [PZ95] la description de l'unité flottante du processeur UltraSPARC pour la multiplication et celle de la division et de la racine carrée, y compris la réalisation pratique des arrondis de ces fonctions.

LA NORME IEEE 754

#### Multiplication

Soient a et b les deux nombres flottants à multiplier. On note n le nombre de bits de la mantisse de a et de b. Le produit  $p = a \times b$  est donc composé de 2n bits et on a  $1 \leq p < 4$ . On décompose les bits de p en deux mots  $(p_H, p_L)$  de n bits chacun suivant le schéma suivant :

De  $p_L$ , on extrait l'information suivante:

- $\bullet$  g le bit de garde (guard bit) est le bit de poids fort de  $p_L$

- r le bit d'arrondi (round bit) est le deuxième bit de  $p_L$  à partir des poids forts

- s le bit persistant (sticky bit) qui est le OU logique des n-2 bits de poids faible de  $p_L$

La mantisse du résultat devant être normalisée, il faut commencer par rechercher le premier bit non nul du résultat, en modifiant éventuellement l'exposant en conséquence. Le produit p étant dans l'intervalle [1, 4[ seul le premier bit de poids fort de  $p_H$  peut être non nul. Si ce bit est nul alors l'exposant est correct mais il faut effectuer un décalage à gauche des bits de  $p_H$  et injecter  $\mathbf{g}$  comme bit de poids le plus faible dans le nouveau  $p_H$ . Les bits  $\mathbf{r}$  et  $\mathbf{s}$  restent inchangés. Si le premier bit de  $p_H$  est égal à 1 alors il faut incrémenter l'exposant, les bits  $\mathbf{r}$  et  $\mathbf{s}$  sont recalculés par les relations  $\mathbf{s} \leftarrow \mathbf{s} \lor \mathbf{r}$  et  $\mathbf{r} \leftarrow \mathbf{g}$ . Après cette phase permettant d'assurer la normalisation du résultat, on a un codage sur n+2 bits comme suit :

$$p_0$$

.  $p_{-1}$   $p_{-2}$   $p_{-3}$  ...  $p_{-n+1}$   $r$  s

On a donc un nouveau  $p_H$  et un nouveau  $p_L$  notés respectivement  $\hat{p}_H$  et  $\hat{p}_L$  ( $\hat{p}_L$  étant réduit à deux bits). Le but du bit de garde est de permettre la renormalisation sur n bits de la mantisse du résultat. Ce sont maintenant les valeurs respectives des bits  $\mathbf{r}$  et  $\mathbf{s}$  qui vont nous permettre de calculer l'arrondi exact du résultat.

Par exemple, dans le cas de l'arrondi vers  $+\infty$ , pour les valeurs positives, il est juste nécessaire de savoir si l'un des bits de  $\hat{p}_L$  est égal à 1. Si c'est le cas alors il faut ajouter 1 à la mantisse. Dans le cas contraire (tous valent 0), on a déjà l'arrondi vers le haut du résultat. Dans le cas de l'arrondi au plus près, les choses sont un peu plus complexes. En effet, il faut pouvoir distinguer les valeurs qui se trouvent de part et d'autre du milieu de l'intervalle formé par deux nombres machine consécutifs.

Le Tableau 1.4 résume les différents cas permettant de réaliser l'arrondi exact de la multiplication flottante IEEE 754.

Cette méthode permet d'implanter matériellement l'arrondi exact de la multiplication sur une surface relativement restreinte. En effet, il suffit d'un décaleur d'une position pour des mots de n bits, d'un additionneur sur n bits pour injecter les corrections du Tableau 1.4 et d'un petit arbre de cellules  $\mathtt{OU}$  pour calculer le sticky bit. Cependant, cette méthode n'est pas efficace en temps de calcul. Les étapes rajoutées pour arrondir le résultat peuvent causer une augmentation du nombre d'étages du pipeline de l'unité flottante. Dans [SBH89], Santoro, Bewick et Horowitz proposent des algorithmes qui permettent de réaliser l'arrondi exact de la multiplication plus rapidement. Par exemple, ils proposent un algorithme tenant compte de la sommation des produits partiels en

| mode d'arrondi | $p \ge 0$                                                                                  | p < 0                                                                                      |

|----------------|--------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------|

| $-\infty$      |                                                                                            | +1 si r V s = 1                                                                            |

| $+\infty$      | $+1 \operatorname{si} \mathbf{r} \vee \mathbf{s} = 1$                                      |                                                                                            |

| 0              |                                                                                            |                                                                                            |

| au plus près   | $+1 \operatorname{si} (\mathbf{r} \wedge \mathbf{s}) \vee (p_{n-1} \wedge \mathbf{r}) = 1$ | $+1 \operatorname{si} (\mathtt{r} \wedge \mathtt{s}) \vee (p_{n-1} \wedge \mathtt{r}) = 1$ |

TAB. 1.4 - Règles permettant d'arrondir exactement la multiplication flottante (IEEE 754). La règle +1 signifie qu'il faut ajouter 1 à  $\hat{p}_H$  pour obtenir l'arrondi exact de p. L'absence de règle indique que  $\hat{p}_H$  est l'arrondi souhaité.

notation redondante carry-save (chiffres dans {0,1,2} en base 2) pour calculer le sticky bit. Ceci permet d'effectuer rapidement la correction finale (le +1 du Tableau 1.4) directement en carry-save (sans devoir convertir en notation classique d'abord). Ils proposent aussi différentes stratégies permettant de recouvrir, le plus possible, le calcul de l'arrondi et les autres phases du calcul du produit. Dans [QTF91], Quach, Takagi et Flynn proposent des techniques pour réaliser rapidement l'arrondi exact de la multiplication dans le cas de multiplieurs utilisant, en interne, une notation redondante à chiffres signés. Dans [YZ95], on trouve la description de la multiplication flottante (avec son arrondi) du processeur UltraSPARC.

#### Addition

L'algorithme d'addition en virgule flottante est un peu plus complexe que celui de la multiplication. En effet, de nombreux cas de figures demandent des corrections plus ou moins complexes. Par exemple, la somme des deux opérandes peut s'écrire exactement sur beaucoup plus ou beaucoup moins de chiffres que n. Si, par exemple, l'un des opérandes est petit en valeur absolue devant l'autre (addition du style  $1+\epsilon$ ), l'addition des mantisses alignées peut éventuellement s'écrire exactement sur un grand nombre de chiffres (supérieur à n). Dans ce cas, on peut utiliser une technique similaire à celle de la multiplication pour arrondir. Un autre cas qui complique l'algorithme de l'addition flottante est celui de la soustraction de deux quantités proches. Il se produit alors ce que l'on appelle une cancellation. C'est-à-dire qu'après la soustraction, les premiers chiffres du résultat sont nuls. Lors de la phase de renormalisation il est possible de devoir ajouter des 0 artificiels dans les poids faibles du résultat. Tous ces cas ne sont pas très complexes à prendre en compte, mais ils compliquent considérablement la logique de contrôle de l'opérateur et nécessitent une part non négligeable du temps de calcul de l'opérateur.

On peut trouver dans [HP96] une bonne introduction sur la réalisation de l'arrondi de l'addition en virgule flottante. L'algorithme d'addition en virgule flottante, ainsi que son arrondi, est complètement décrit dans [Omo94]. Quach, Takagi et Flynn exposent dans [QTF91] un ensemble de remarques et d'algorithmes permettant de réaliser des opérateurs flottants d'addition avec arrondi exact très efficaces.

#### Division

On cherche le quotient q de a/b exactement arrondi, a et b étant deux nombres machine de n chiffres de mantisse. Le calcul du quotient peut se faire en utilisant l'une des deux grandes catégories

LA NORME IEEE 754

d'algorithmes classiques de division :

#### • Algorithmes itératifs utilisant la multiplication.

On a, par exemple, l'itération de Newton<sup>1</sup> appliquée à la division :

$$r^{(i+1)} = r^{(i)} \times (2 - br^{(i)})$$

qui converge vers  $\frac{1}{b}$  si  $r^{(0)}$  est bien choisi. Il suffit ensuite de multiplier ce résultat par a pour obtenir le quotient q.

On peut aussi utiliser l'itération de Goldschimdt [AEGP67], qui est :

$$a^{(0)} = a$$

$$\epsilon^{(0)} = 1 - b$$

$$a^{(i+1)} = a^{(i)} \times (1 + \epsilon^{(i)})$$

$$\epsilon^{(i+1)} = (\epsilon^{(i)})^{2}$$

Pour laquelle,  $a^{(i)}$  converge vers a/b pour peu que b soit compris entre 1/2 et 1.

Ces itérations étaient surtout utilisées dans les supercalculateurs (IBM360/91 et Cray). Plus récemment, les coprocesseurs arithmétiques Cyrix utilisent une combinaison de l'itération de Newton et d'une table pour la détermination du point de départ de l'itération (cf [Mat89] et [WF91]).

#### • Algorithmes basés sur des additions et des décalages.

L'algorithme en base 10, que l'on apprend à l'école primaire, est un algorithme fonctionnant par additions et décalages. Ces algorithmes consistent à obtenir une écriture du quotient  $0.q_1q_2...q_n$ , chiffre après chiffre, en utilisant une itération de la forme ( $\beta$  est la base):

$$\begin{cases} a^{(0)} = a \\ a^{(i+1)} = \beta a^{(i)} - q_{i+1}b \end{cases}$$

A chaque itération on obtient un nouveau chiffre  $q_{i+1}$  du quotient. Si on choisit  $\beta=2$ , il faut n itérations pour obtenir n bits du résultat, ce qui est assez lent pour les formats flottants ayant de grandes mantisses. En augmentant la base, en prenant  $\beta=2^k$ , on obtient k bits du quotient à chaque itération. Mais chacune des itérations devient de plus en plus complexe au fur et à mesure que  $\beta$  augmente. Le choix de la base "optimale" pour une implantation matérielle est très fortement dépendant de paramètres technologiques et de choix algorithmiques. Ceci explique la grande diversité des diviseurs flottants réalisés jusqu'ici.

C'est par exemple, un algorithme à base d'additions et de décalages du nom de SRT découvert indépendemment par Sweeney, Robertson et Tocher ([Rob58], [Toc58]) qui est utilisé dans les processeurs Pentium d'Intel (où  $\beta = 4$ , cf [Mul95]).

<sup>1.</sup> La méthode Newton permet de résoudre f(x) = 0 en construisant une suite  $x^{(i+1)} = x^{(i)} - \frac{f(x^{(i)})}{f'(x^{(i)})}$  où si  $x^{(0)}$  est suffisamment proche d'une racine simple  $\alpha$  de f alors  $x^{(i)}$  converge quadratiquement vers  $\alpha$ .

On trouve dans [Omo94, EL94, OF95] des informations sur la réalisation matérielle de la division flottante. Suivant la catégorie d'algorithmes utilisée, l'arrondi exact de la division est plus ou moins complexe.

Dans le cas des algorithmes à base d'additions et de décalages, on obtient à chaque itération les chiffres du quotient et le reste partiel. Pour arrondir, il suffit de calculer un bit de garde supplémentaire et de regarder le signe du reste. On trouve dans [PZ95] la description du diviseur flottant du processeur UltraSPARC (algorithme SRT en base 8).

Dans le cas des algorithmes itératifs utilisant la multiplication, l'arrondi est beaucoup plus complexe. En effet, l'itération de Newton converge non pas vers le quotient mais vers l'inverse du diviseur (1/b). Ensuite, il faut encore multiplier cet inverse par a pour obtenir le quotient. Il faut donc garantir l'arrondi de l'inverse de b puis celui du produit  $a \times \frac{1}{b}$ . En pratique, on calcule l'inverse de b avec  $2n + \alpha$  bits de précision (où  $\alpha$  est une petite constante), puis on calcule le produit  $a \times \frac{1}{b}$  et enfin, on arrondi ce dernier résultat sur n bits. On trouve dans [OF96] une excellente étude par la réalisation de l'arrondi exact de la division pour ce genre d'algorithmes.

#### Racine carrée

La racine carrée peut être calculée en effectuant des itérations de fonction semblables à celle de la division. Par exemple, en résolvant  $x^2 = a$  avec Newton on a:

$$x^{(i+1)} = \frac{1}{2} \times \left(x^{(i)} + \frac{a}{x^{(i)}}\right)$$

qui converge vers  $\sqrt{a}$  si  $x^{(0)}$  est bien choisi. En fait, il est souvent préférable de calculer  $\frac{1}{\sqrt{a}}$  en résolvant  $\frac{1}{x^2} = a$  puis de multiplier le résultat obtenu par a. On a donc l'itération :

$$x^{(i+1)} = \frac{x^{(i)}}{2} \times \left(3 - a(x^{(i)})^2\right)$$

On peut utiliser les mêmes techniques pour l'arrondi de la racine carrée que celles de la division. Les calculs de ces deux fonctions sont tellement proches au niveau algorithmique, qu'en pratique le calcul de la division et la racine carrée sont effectués sur un seul et unique opérateur flottant (voir par exemple [PZ95]).

#### 1.1.4 Avantages de la norme IEEE 754

Pour en finir avec la présentation de la norme IEEE 754, voici les points qui nous semblent importants dans cette norme.

- La totale spécification des opérations flottantes assure une réelle structure mathématique sur laquelle il possible de bâtir des preuves des algorithmes numériques employés.

- Les formats flottants standards permettent une totale portabilité des données. La spécification du codage de ces formats et des opérations flottantes permet la portabilité des codes. Ceci est probablement l'un des principaux apports de la norme IEEE 754. En effet, avant son apparition, la conception et le portage d'algorithmes numériques demandaient un travail considérable tant il y avait de systèmes flottants distincts et dont les comportements respectifs étaient radicalement différents. C'est ici que l'arrondi exact des fonctions joue son rôle.

• Enfin, la normalisation des données (formats) et des opérations permet la mise en œuvre d'algorithmes et d'architectures de plus en plus performants tout en restant totalement compatibles (coprocesseurs arithmétiques Cyrix par exemple).

#### 1.2 Arrondi exact des fonctions élémentaires

L'arrondi exact des fonctions arithmétiques  $(+, -, \times)$  et de certaines fonctions algébriques  $(\div, \sqrt{\ })$  est possible car on sait toujours déterminer quel est le nombre machine de n bits de mantisse qui doit être retourné, suivant le mode d'arrondi utilisé, au vu de la mantisse du résultat des calculs intermédiaires sur n bits plus des chiffres supplémentaires.

On va voir que dans le cas des fonctions élémentaires le problème est de pouvoir déterminer quelle est la précision intermédiaire nécessaire pour pourvoir arrondir exactement. Mais avant cela, nous devons étudier comment évaluer ces fonctions élémentaires.

Les travaux présentés ici sur l'arrondi exact des fonctions élémentaires ont été publiés dans [MT96, DMT96, LMT97] et ont été réalisés en collaboration avec J.M. Muller et V. Lefèvre.

#### 1.2.1 Evaluation des fonctions élémentaires

L'évaluation d'une fonction élémentaire f (sin, cos, exp, log ou arctan) au point x (l'argument de la fonction) nécessite généralement plusieurs étapes. En effet, les algorithmes permettant de calculer les fonctions élémentaires ne sont valides que dans de petits domaines. Il faut donc commencer par se ramener au domaine de convergence de l'algorithme, puis évaluer la valeur de la fonction en le nouvel argument, en déduire la valeur de la fonction en l'argument original et enfin arrondir le résultat. Les principaux algorithmes des différentes phases relatives à l'évaluation des fonctions élémentaires sont détaillés dans le livre de Jean-Michel Muller [Mul97].

Dans la suite, nous noterons n le nombre de chiffres de la mantisse du résultat final (après arrondi), m le nombre de chiffres de la mantisse du résultat intermédiaire qui sont nécessaires pour arrondir correctement celui-ci. Nous verrons que le problème de l'arrondi exact des fonctions élémentaires consiste à déterminer la valeur de m pour chaque fonction et chaque format de nombre flottant (simple précision, double précision...).

Voici l'ensemble des phases effectuées lors de l'évaluation d'une fonction élémentaire :

- ① La réduction d'argument. Cette première phase consiste à déduire de l'argument x l'argument réduit  $x^*$  qui appartient au domaine de convergence de l'algorithme utilisé pour calculer  $g(x^*)$ , où f(x) peut se déduire simplement de  $g(x^*)$  (dans la plupart des cas f = g).

- ② L'évaluation. La deuxième phase consiste en l'évaluation effective de  $g(x^*)$ .

- ③ L'arrondi final. En fait, avant d'effectuer l'arrondi proprement dit, il faut calculer f(x) à partir de  $g(x^*)$  (cette opération est en général triviale) et ensuite arrondir le résultat obtenu dans le bon format.

Il existe deux types de réduction d'argument. Le premier, la réduction additive, consiste à soustraire suffisamment de fois une constante bien choisie afin de garantir que  $x^*$  soit bien dans le domaine de convergence de l'algorithme. On a une réduction de la forme:

$$x^* = x - kC$$

où k est un entier et C une constante. Par exemple, pour certains algorithmes calculant des fonctions trigonométriques on a  $C = \frac{\pi}{8}$ .

Le deuxième type de réduction est la réduction multiplicative qui consiste à diviser l'argument initial par une constante bien choisie suffisamment de fois. On a alors une réduction de la forme:

$$x^* = \frac{x}{C^k}$$

où k est un entier et C une constante. Cette réduction est utilisée, par exemple, dans le cas du calcul de la fonction logarithme où un choix judicieux pour C est la base du système utilisé.

En pratique, la réduction multiplicative ne pose pas de problème majeur de précision. Par contre, dans le cas de la réduction additive, il peut se produire des cas de cancellation catastrophique si x est proche d'un multiple entier de C. La soustraction flottante de ces deux quantités va donner un résultat dont un grand nombre de bits de poids forts seront nuls. Il y a alors cancellation catastrophique si trop de bits de poids faibles ne sont plus significatifs par rapport à l'accumulation des erreurs des précédentes étapes du calcul. La renormalisation va donc introduire des zéros arbitraires dans les poids faibles de l'argument réduit. Il faut donc effectuer la réduction d'argument additive avec une précision intermédiaire plus grande que la précision nécessaire à la représentation de l'argument réduit. Différents algorithmes visant des implantations logicielles sont décrits dans [CW80]. On peut trouver dans [DMMM94] et [DMMM95] un algorithme permettant de réaliser matériellement la réduction d'argument additive avec une bonne précision.

Il existe deux catégories d'algorithmes d'évaluation des fonctions élémentaires. Tout d'abord, les algorithmes par additions et décalages comme CORDIC [Vol59, Wal90] ou BKM [BKM93, BKM94]. Ces algorithmes produisent une suite de valeurs qui converge vers le résultat. Les algorithmes de l'autre catégorie sont basés sur des approximations polynômiales ou rationnelles des fonctions. De nombreux exemples de ces différents types d'algorithmes sont décrits dans [Mul97]. Schulte et Swartzlander ont proposé dans [SS94] des algorithmes basés sur des approximations polynômiales permettant l'évaluation et l'arrondi exact des fonctions élémentaires  $2^x$  et  $\log_2 x$  en simple précision.

Avec ces algorithmes (additions et décalages ou par approximation), il est toujours possible d'évaluer une fonction élémentaire avec une précision relative meilleure que  $2^{-m}$  en base 2 quel que soit m. En fait, la fonction à évaluer doit respecter certaines conditions, mais dans le cas des fonctions qui nous intéressent (sin, cos, exp, log et arctan), ces conditions sont vérifiées.

Il est donc possible d'évaluer une fonction élémentaire usuelle avec autant de chiffres de mantisse que nécessaire. Reste maintenant à étudier le problème de l'arrondi exact du résultat de l'évaluation de ces fonctions.

#### 1.2.2 Le dilemme du fabricant de tables

Soient x un nombre machine, et y = f(x), où f est une fonction élémentaire (sin, cos, exp, log ou arctan). On désire arrondir exactement f(x) à n chiffres suivant l'un des quatre modes d'arrondi IEEE. Nous avons vu dans la section 1.2.1 qu'il était possible de calculer f(x) avec une erreur de  $2^{-m}$ . Le calcul intermédiaire (avant arrondi) se fait avec m chiffres de mantisse. Dans les cas

suivants, il n'est pas possible d'arrondir exactement f(x).

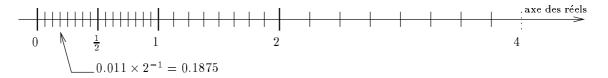

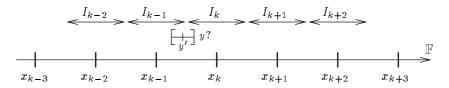

• pour l'arrondi au plus près:

$$\underbrace{\frac{m \text{ bits}}{1.xxxx \dots xx} 1000 \dots 00}_{\text{$n$ bits}} xxx \dots \qquad \text{ou} \qquad \underbrace{\frac{m \text{ bits}}{1.xxxx \dots xx} 0111 \dots 11}_{\text{$n$ bits}} xxx \dots$$

• pour l'arrondi vers  $+\infty$ ,  $-\infty$  ou 0: