# Design of a Radiofrequency Front-End module for "Smart Dust" sensor network

Javad Yavand Hasani

#### ▶ To cite this version:

Javad Yavand Hasani. Design of a Radiofrequency Front-End module for "Smart Dust" sensor network. Condensed Matter [cond-mat]. Université Joseph-Fourier - Grenoble I, 2008. English. NNT: . tel-00445302

## HAL Id: tel-00445302 https://theses.hal.science/tel-00445302

Submitted on 8 Jan 2010

HAL is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

#### UNIVERSITE JOSEPH FOURIER

|   | Ν° | at | trib | ué | par | la l | ldic | ioth | ièqi | ue |

|---|----|----|------|----|-----|------|------|------|------|----|

| L |    |    |      |    |     |      |      |      |      |    |

#### THESE

Pour obtenir le grade de

### DOCTEUR De L'Université Joseph FOURIER de Grenoble

Spécialité : Optique et RadioFréquences

Préparée à l'Institut de Microélectronique, Electromagnétisme et Photonique MINATEC Grenoble

Dans le cadre de l'Ecole Doctorale Electronique, Electrotechnique, Automatique, Télécommunication et Signal

Présentée et soutenue publiquement par

#### Javad YAVAND HASANI

Date: 07 décembre 2008

# Design of a Radiofrequency Front-End module for "Smart Dust" sensor network

Directeur de thèse : Fabien NDAGIJIMANA

Mahmoud KAMAREI

#### **JURY**

Dr. Tchanguiz RAZBAN-HAGHIGHIRapporteurDr. Abdolali ABDIPOURRapporteurDr. Michel BARIBAUDExaminateurDr. Forouhar FARZANEHExaminateurDr. Mahmoud SHAH ABADIExaminateurDr. Fabien NDAGIJIMANADirecteur de thèseDr. Mahmoud KAMAREIDirecteur de thèse

In Memory of My Father....

To My Mother

And

My Wiffe

I would like to thank my supervisors, Pprofessor Kamarei in University of Tehran, Iran, and Professor Ndagijimana, in University of Joseph Fourier, Grenoble, French. I appreciate the kindly helps of Professor Jean-Michel Fournier in the IMEP laboratory, especially in the first steps of my work. The helps of my friend, Maxim Bernier and the accommodations of Mr. Nicolas Carroa in measurement of the fabricated LNA is also appreciated. I am grateful of the jury members from Iran and French, for tolerating the efforts and attending in the defence session.

This work was supported in part by the Iranian Telecommunication Research Center (ITRC), under the contract number 500/2983.

## CONTENTS

| Chapter I   | RF Front End in Wireless Sensor Networks           | 1  |

|-------------|----------------------------------------------------|----|

|             | I.1 Wireless Sensor Network Overview               | 1  |

|             | I.1.1 WSN History                                  | 1  |

|             | I.1.2 WSN Applications                             | 1  |

|             | I.1.3 WSN Structure and Specifications             | 2  |

|             | I.1.4 Sensor Node Structure                        | 3  |

|             | I.1.5 Security and Reliability in WSN              | 5  |

|             | I.1.6 Power Source Limitation in WSN               | 5  |

|             | I.2 Transmitter and Receiver in WSN                | 8  |

|             | I.3 Transceiver Specs in Our Work                  | 9  |

|             | I.3.1 Semiconductor Technology Issues              | 9  |

|             | I.3.2 Transceiver Specifications in Our Work       | 10 |

| Chapter II  | MOS transistor model and layout issues             | 15 |

|             | II.1 MOS Modeling Overview                         | 15 |

|             | II.1.1 Professional Physical Models                | 16 |

|             | II.1.2 Table-Based Models                          | 16 |

|             | II.1.3 Simple Physical Models                      | 17 |

|             | II.2 Our Model for Intrinsic MOS Transistor        | 17 |

|             | II.2.1 I-V Characteristic                          | 17 |

|             | II.2.2 Capacitances Model                          | 20 |

|             | II.2.3 Small Signal Model                          | 27 |

|             | II.2.4 Noise Model                                 | 31 |

|             | II.3 Distributed Analysis                          | 33 |

|             | II.3.1 Distributed Model                           | 34 |

|             | II.3.2 Comparison With Lumped Model                | 37 |

|             | II.4 Layout Issues                                 | 39 |

|             | II.4.1 Proposed Layout                             | 40 |

|             | II.5 Our Comprehensive Model                       | 43 |

|             | II.5.1 Partial Transistor Model                    | 43 |

|             | II.5.2 Complete Transistor Model                   | 52 |

| Chapter III | Passive Elements Modeling and Design               | 59 |

| -           | III.1 Introduction                                 | 59 |

|             | III.2 Inductor Design                              | 59 |

|             | III.2.1 Inductors in mm-wave Band                  | 61 |

|             | III.2.2 Proposed Inductor Structure                | 62 |

|             | III.2.3 Inductor Model Development                 | 64 |

|             | III.3 Other Passive Elements                       | 77 |

|             | III.3.1 RF Pad Design and Modeling                 | 77 |

|             | III.3.2 T-Junction Model                           | 78 |

|             | III.3.3 Transmission Lines Design                  | 79 |

|             | III.3.4 Transistor Interconnections                | 80 |

| Chapter IV  | Low Noise Amplifier Design and Optimization        | 84 |

| <b>F</b>    | IV.1 CMOS LNA Design and Optimization Overview     | 84 |

|             | IV.1.1 CMOS LNA Circuits                           | 84 |

|             | IV.1.2 CMOS LNA Characteristics                    | 85 |

|             | IV.1.3 Other Issues in CMOS LNA Design             | 88 |

|             | IV.1.4 CMOS LNA Design and Optimization Principles | 89 |

|             | IV.1.5 CMOS LNA in Millimeter Wave Frequencies     | 90 |

|            | IV.2 Our LNA Circuit and its Analysis             | 92  |

|------------|---------------------------------------------------|-----|

|            | IV.2.1 LNA Analysis                               | 92  |

|            | IV.3 Our LNA Optimization Methodology             | 111 |

|            | IV.3.1 Step I: Analytic Optimization              | 112 |

|            | IV.3.2 Step II: Y-Parameter Optimization          | 113 |

|            | IV.3.3 Step IV: Post Layout Simulation            | 117 |

|            | IV.4 Practical Design and Fabrication             | 118 |

|            | IV.4.1 Design Process                             | 118 |

|            | IV.4.2 LNA Layout and Post Layout Simulation      | 122 |

|            | IV.4.3 Fabricated LNA and the Measurement Results | 127 |

| Chapter V  | Transceiver Design                                | 141 |

| _          | V.1 Transceiver Review                            | 142 |

|            | V.1.1 Heterodyne Architecture                     | 142 |

|            | V.1.2 Low-IF Architecture                         | 143 |

|            | V.1.3 Direct Conversion Architecture              | 145 |

|            | V.1.4 Transceiver Architecture for WSN            | 148 |

|            | V.2 Transceiver Design in Our Work                | 149 |

|            | V.2.1 Radio Link Design                           | 150 |

|            | V.2.2 Transceiver Architecture                    | 154 |

|            | V.2.3 The Receiver Architecture                   | 155 |

|            | V.3 The Transmitter Architecture                  | 175 |

| Chapter VI | Conclusion and Suggestions                        | 184 |

|            | VI.1 Conclusion                                   | 184 |

|            | VI.1.1 Device-Level Modeling                      | 184 |

|            | VI.1.2 Passive Elements Design and Modeling       | 186 |

|            | VI.1.3 LNA Design and Measurement Results         | 186 |

|            | VI.1.4 Designed Receiver and Transmitter          | 188 |

|            | VI.2 Suggestions                                  | 189 |

| Appendix A |                                                   | 192 |

| Appendix B |                                                   | 195 |

| Appendix C |                                                   | 203 |

| Appendix D |                                                   | 204 |

| Appendix E |                                                   | 207 |

#### **Preface**

ireless Sensor Network (WSN) concept was introduced in 1994 for the first time, aiming at the military application. Then WSNs were considered in many civil applications and many academic and industrial researches were attracted in to WSN concept. The word "Smart Dust" was introduced in the University of California, an imaginary infinitesimal sensor node that can be suspended in air.

This thesis is an attempt toward very small "Dust-Like" sensor node to be used eventually in a short range dense WSN. The planning of the thesis was performed as a co-supervision program between University of Tehran, Tehran, Iran and University of Joseph Fourier, Grenoble, France. Primary studies of the thesis started in University of Tehran and from 2005-2006, the program was continued in the IMEP laboratory, MINATEC, Grenoble.

The definition of the thesis is design of low-power fully integrated RF front end for a mm-wave sensor node. Until now, all of the reported works in WSN context (in our knowledge) were in the frequencies limited to few GHz. For the first time, we introduced the use of mm-wave band in WSN application, targeting the benefits of this band, specially higher network immunity and possibility of antenna-on-chip integration. To obtain low-cost sensor nodes, the STMicroelectronics 90nm Global Purpose (GP) process was considered and the related foundry design kit was provided. Since this thesis was the first attempt in this way, there were not any primary experiences, or guide lines or even predefined parameters and characteristics for the RF front end. Due to cost considerations and some other limitations, global purpose CMOS process was used, instead of RF CMOS process and this was source of many challenges in our work. Actually we were obliged to develop all of the required modeling and design procedure for passive elements, as well as the proper parasitic models for active devices.

Actually the objective of this thesis was investigating the possibility of low-power fully integrated RF front end best performances that are achievable in mm-wave band, in 90nm CMOS technology. This thesis was the first work of mm-wave design in 90nm CMOS technology in the laboratory and hence our work could not be based on the available experiences. On the other hand our planning was to use bulk CMOS technology and we have not access to any pre-designed RF components. Consequently we were obliged to develop proper models for all of active devices and passive elements and tune the models using the foundry design kit, whenever it was possible.

After developing the first versions of our MOS transistor and inductor model, we started the most crucial part of the receiver, i.e. low noise amplifier (LNA). In this way we designed a 3-mW LNA in 2006 and we sent it to be fabricated by STMicroelectronics. We developed a simple design and optimization tool, written in MATLAB, composed of active devices and passive elements models, as well as a simple, but accurate Cascode LNA analyser and designer. After LNA, we studied the other main parts of the transceiver, i.e. VCO, mixer and power amplifier. In 2006 the layout of primary designs of VCO and mixer was completed. Until end of 2007, the next time I returned back to France to perform the measurements, we overviewed and modified our models and design tools and finally a complete LNA design tool, with proper GUI<sup>1</sup> was developed. In the first version of our work, we used MoM

\_

<sup>&</sup>lt;sup>1</sup> Graphical User Interface

electromagnetic simulator of ADS software in passive elements modeling. In the next versions, we developed our extraction process for passive elements, based on the full wave simulations in Ansoft HFSS.

Since we developed all of our required passive elements as an individual library in the design kit, attached to the CADANCE environment, we could not use the standard layout control and check-up tools and unfortunately a mistake had occurred in the layout of input matching network of the LNA. Due to this mistake, measurement results showed some discrepancy with the simulation results, in some characteristics. However, when we introduced the same mistake in our post-layout simulation of our design tool, we obtained the results in very good agreement with the measurement results and this proved the accuracy of our models and design tool. In spite of the mistake, our LNA has acceptable performance, regarding its only 3-mW power consumption. In addition, the chip are of our LNA is a record, thanks to the line-type inductors we have developed and used in our design. Finally, using the modified version of our design tool, we completed the LNA design and excellent performance was achieved, in comparison the reported works. Although the last designed LNA was not fabricated, it was simulated in post-layout simulation facility of our design tool, in conjunction with the foundry design tool, for which the accuracy was proved by measurement results.

For other parts of the transceiver we studied and examined various possible designs. We investigate different topologies for VCO, mixer IF amplifier, power amplifier and base band circuits, using analysis and simulation. Analysis results showed that among various available VCO circuits, some of them are more preferable for ultra-low power applications. Power amplifier is the most challenging in low-power mm-wave transmitter, specially in CMOS technologies in which the passive elements have low quality factor and high loss. Trying to use high efficiency Class E power amplifiers, we developed novel design methodologies for this class of amplifiers. Unfortunately we encountered difficulties in driving the switches in few-mWs power amplifiers in mm-wave band and finally we used other solutions.

After primary designing the transceiver blocks, we studied the transceiver architectures that are suitable for our application. In this way, the definition of the radio link and a simple communication protocol were necessary. Since we were not supplied by a high-level system design team, we defined the required parameters using our experience of transceiver deign, as well as our experience of achievable performance of transceiver sub circuits. We proposed sub-harmonic mixer topology in the receiver and power-oscillator solution in the transmitter. Performance of the transceiver was evaluated by circuit-level simulation of the transceiver sub-circuits is the first step, and then system-level behavioral simulation in MATLAB, in the second step. The designed transceiver is ultra-low power, in comparison with the reported mm-wave transceivers.

The dissertation composed of six chapters, describing our research form device-level modeling to system level design. In Chapter a brief history of WSN development is presented. Structure of a sensor node in a typical WSN is described and main characteristics and requirements of a WSN are reviewed. Then the transceiver architectures are investigated and the main features of the transceivers in WSN are presented. Chapter II deals with the MOS transistor model. As mentioned, the foundry design kit available for our work was global purpose CMOS process and was not useful for our work. So we developed our MOS transistor model, not only to obtain a simple analytic model, but also a flexible model that can be integrated in our design tool. We developed our model with simple analysis of short-channel MOS device and the model parameters were extracted and tuned in comparison with the simulation results in the foundry design kit. Passive elements and back-end parasitic effects have been described and modelled in Chapter III. In this chapter, we have described the novel line-type inductor structure and its lumped-element modeling basis. The developed

inductor model comprises the losses due to the eddy currents in the substrates, the phenomena that has not been considered in reported models (is not necessary) for transmission lines and coplanar wave guides. Accurate lumped-element models of RF pads, T-Junctions and transistor interconnections have been developed in this chapter and the model parameters have been calculated from full wave electro magnetic simulation. Lumped element models are very important in post layout simulation and make possible to capture the distributed effects in circuit simulators.

Chapter IV has been dedicated for LNA design, optimization and measurement results. To achieve low power consumption, we chose single stage LNA. Then using our analysis and design methodology, we found that cascode topology is very well suited for our objectives: good noise figure, enough power gain and high reverse isolation in mm-wave band and hence good stability. The design and optimization method has been described. Post-layout simulation and measurement results have been presented and analyzed and have been compared with the reported works. Finally, in Chapter V we have exploited the experience obtained in the previous chapters, as well as the new suggestions in this chapter, to propose and design the structure of our transceiver. We have developed analysis guidelines to choose the proper VCO topology and even-harmonic mixer design and optimizations. The desinged transceiver has been simulated using system-level simulation in MATLAB and behavioral model of sub-blocks were obtained from simulation in the foundry design kit and post-layout simulation using our design tool. Finally, the conclusion of the thesis and some suggestions and propositions for future works, have been presented in Chapter VI.

## **List of Figures**

## Figures of Chapter I

- Fig. I-1. Basic block diagram of a wireless sensor node [9]

- Fig. I-2. The mote sensor node fabricated as integration of CMOS and MEMS technology for early generations of Smart Dust, at University of California, Berkeley. [8]

- Fig. I-3. Complete sensor nodes, with different possible levels of integration [9]

- Fig.I.4. SEM of the fully integrated sensor node, presented in [34]

- Fig. I-5. The outlook of modern CMOS technology [82].

## Figures of Chapter II

- Fig. II-1. Ids for two value of W=10 um and W=30 um, and different finger sizes

- Fig. II-2 The I-V characteristics of our model in comparison with the foundry design kit, Circle data are from design kit.

- Fig. II-3 The effect of number of gate fingers on the drain current, for in our model in comparison with the foundry design kit, Circle data are from design kit.

- Fig. II-4. Channel charge and its derivative calculated from (II-16) and (II-17), after our first and second modifications. Charges and derivatives have been normalized to  $W_{eff}L_{eff}C_{ox}$  and  $C_{ox}$ , respectively.

- Fig. II-5. The unified function of (II-23) and its first derivative, in comparison with the exponential equation of (II-17). Charges and derivatives have been normalized to  $W_{eff}L_{eff}C_{ox}$  and  $C_{ox}$ , respectively.

- Fig. II-6.  $V'_{ds}$  and  $V''_{ds}$  defined in (II-26) for q=2 and Vdsat=0.2

- Fig. II-7. Normalized bulk charge and its derivative calculated from (II-34), for n=3, Vth=0.27 and Vac=-0.5

- Fig. II-8.  $C_{gd}$  and  $C_{gg}$  of the transistor capacitances, calculated form our model, in comparison with the foundry design kit data

- Fig. II-9. Commonly used small signal model for MOS transistor core

- Fig. II-10.  $g_m$  versus  $V_{ds}$  for various  $V_{gs}$ , obtained from our model, in comparison with the 90nm CMOS foundry design kit. (On the figure, DK: Design Kit, MODEL: Our model in II-41))

- Fig. II-11.  $g_{ds}$  (a) and  $g_{mb}$  versus  $V_{ds}$  for various  $V_{gs}$ , obtained from our model, in comparison with the 90nm CMOS foundry design kit. (On the figure, DK: Design Kit, MODEL: Our model in II-41))

- Fig. II-12. Magnitude and phase of ζ<sub>m</sub>, calculated using (II-55) and for 90nm CMOS technology

- Fig. II-13. Dividing the saturated channel to Gradual Channel Region (GCR) and Velocity Saturation region (VSR) [72].

- Fig. II-14. Demonstration of the distributed effect in a MOS transistor

- Fig. II-15. Equivalent small signal representation for distributed model of MOS transistor

- Fig. II-16.  $Y_{11}$ ,  $Y_{12}$  and  $Y_{21}$  obtained from lumped model and distributed model, in comparison with the simulation in ADS for 90nm CMOS technology

- Fig. II-17. Y<sub>13</sub>, Y<sub>23</sub> and Y<sub>33</sub> obtained from lumped model and distributed model, in comparison with the simulation in ADS for 90nm CMOS technology

- Fig. II-18. The lumped small signal model, counterpart of the distributed model in Fig. II-15

- Fig. II-19. Distributive effect error measure, defined in (II-75), for various values of gate width, W(a) for single connection and (b) for double connection

- Fig. II-20. Manhattan Gate (a) and Manhattan Interconnect (b) implementation for MOS transistor layout. (Reproduced from [91])

- Fig. II-21. Single connection (a) and double connection (b) gate layout for MOS transistor

- Fig. II-22. Single connection multi finger gate structure, with guard ring close to the transistor core

- Fig. II-23. Single connection multi finger gate structure, with guard ring far from transistor core

- Fig. II-24. Double connection multi finger gate structure, with guard ring close to the transistor core

- Fig. II-25. Double connection multi finger gate structure, with guard ring from transistor core

- Fig. II-26. the layout of the partial transistor

- Fig. II-27. source/drain resistance representation for a short channel MOS device [40]

- Fig. II-28. Parasitic capacitances in intrinsic part of the partial transistor [51]

- Fig. II-29. Parasitic capacitances between gate, sorce/drain and guard ring pads (extrinsic part of the partial transistor)

- Fig. II-30. Equivalent circuit model for parasitic capacitances of the partial transistor

- Fig. II-31. Various substrate modeling techniques: single resistor [99] (a), three-resistor [40] (b) and five-resistor [24] (c)

- Fig. II-32. Substrate electrical model for the partial transistor in Fig. II-26

- Fig. II-33. Proposed substrate network as a RC circuit, derived from Fig. II-32.

- Fig. II-34. Simplified Y-parameter model for substrate model circuit of Fig. II-33

- Fig. II-35. Final partial transistor model, composed of intrinsic part, parasitic capacitances, substrate network and noise model

- Fig. II-36. Distributed model of the transistor, corresponding to the layout of Fig. II-25

- Fig. II-37. Distributed model of the transistor, used in analysis of the Fig. II-36

- Fig. II-38. Interconnects to the transistor pads (a) and related equivalent LC model as a  $\pi$  section (b)

## Figures of Chapter III

- Fig. III-1. Quality factor of 3.4nH inductor in bulk CMOS and High Resistivity (HR) SOI CMOS, optimized for 2.4 GHz [4].

- Fig. III-2. 6.75nH high Q spiral inductor, fabricated using CMOS compatible MEMS technology [11]

- Fig. III-3. Field distribution of microstrip and coplanar structures

- Fig. III-4. The simplified layer stack of STMicroelectronics 90nm CMOS technology [25]

- Fig. III-5. Three different line structure for inductors

- Fig. III-6. Simplified 3-dimensional view (a) and accurate cross section (b) of the line-type inductor structure, proposed in our work. The inductor is fabricated as a short-end transmission line with patterned shield layer.

- Fig. III-7. Field pattern of proposed inductor structure in Quasi-TEM region

- Fig. III-8. Electric field distribution in the vicinity of the short-end, obtained from full wave simulation in Ansoft HFSS

- Fig. III-9. Proposed model for line-type inductor: dividing the inductor to two sections (a), and RLGC scalable model of QTEM section and RLC model of short-end section (b)

- Fig. III-10. Accurate lumped element scalable model of QTEM section

- Fig. III-11. Modeling the loss due to the eddy currents in the substrate: (a) eddy currents representation, (b) equivalent circuit model and (c) simplified circuit model

- Fig. III-12. Calculation of the magnetic flux passing trough the lossy substrate, assuming that the magnetic field lines are in circular form

- Fig. III-13. Ration of the mutual inductance ( $M_{cs}$ ) over the line inductance ( $L_e$ ), calculated using (III-13), for h=3.8um and tc=3.6um

- Fig. III-14. Representation of the physical meaning of the elements in the vertical branch f the model in Fig. III-

- Fig. III-15. Electric field profile of an infinite length conductor above infinite ground plane (a) and of the inductor structure in our work

- Fig. III-16. Calculation of the capacitance between the ground sidewall and the centerline, using a supposition symmetric structure

- Fig. III-17. Metal layers modeling of ADS for MoM simulation: Currents in real metal layer(a), currents in sheet conductor model of ADS, MoM simulator (b) and currents in thick conductor model of ADS, MoM simulator

- Fig. III-18. Comparison of RLGC parameters of Quasi-TEM section, obtained from our model, MoM simulation in ADS and full wave simulation in HFSS (W=5um, Wg=30um, S=30um).

- Fig. III-19. 3-D view of Quasi-TEM section, simulated in ADS MoM field simulator.

- Fig. III-20. (a) Electric field and (b) magnetic field vectors of Quasi-TEM section, obtained from simulation in HFSS

- Fig. III-21. Inductance and quality factor of the 225pH line-type inductor, as a function of frequency

- Fig. III-22. Cross section (a) and top view (b) of RF pad and related ground ring, and 3-D view of the metal grid stack in the pad (c)

- Fig. III-23. Lumped element model of RF pad (a) and its simplified form (b)

- Fig. III-24. T-junction top view (a) and its equivalent lumped elements model (b)

- Fig. III-25. 3-D multi-layer structure of T-junction, used in HFSS full wave simulation

- Fig. III-26. Rendering 3-D structure of MOS transistor to HFSS, using our interface tool. (a) Complete structure and (b) Some of its incorporated metal and dielectric objects

## Figures of Chapter IV

- Fig. IV-1. Different classic techniques to produce resistive term in the input impedance of an LNA [24]

- Fig. IV-2. Noise cancelling basis has for a CS stage: Representative diagram (b) Practical circuit(a) [42]

- Fig. IV-3 (a) CG stage used in 60 GHz LNA [75] and (b) 60 GHz LNA with modified cascode stage [23].

- Fig. IV-4. Schematic of our single stage cascode LNA, input matching with serial (a) and parallel (b) inductor in the gate of input transistor.

- Fig. IV-5. Small signal model of the cascode LNA, with (a) and without (b) degenerating inductance. Subscribes U and L denotes for Upper and Lower transistors, respectively.

- Fig. IV-6. General form of input matching using two matching elements in gate (a) and implementation with LC network (b)

- Fig. IV-7. The equivalent circuit to calculate the output matching network (a) and the equivalent circuit to calculate the input impedance to the drain of CG stage (b) and CS stage (c)

- Fig. IV-8. Small signal model of common source (a) and common gate (b) stages

- Fig. IV-9. Circuits used in calculation of cascode LNA power gain

- Fig. IV-10. Small signal circuit and noise model of cascode LNA

- Fig. IV-11. The trans-conductance  $(g_m)$ , its second derivative and ratio of  $g_m$  over its second derivative, versus gate-source bias voltage

- Fig. IV-12. Cascode LNA optimization flowchart, based on analysis results, for input matching with series inductor (a) and input matching with LC network (b)

- Fig. IV-13. Terminated 4-Port network and its equivalent 2-port model

- Fig. IV-14. Noisy multi-port (a) and its equivalent noise-less multi-port network, with equivalent current and voltage noise sources at the input (b)

- Fig. IV-15. Post-layout model of cascode LNA, with parallel inductor in input matching network.

- Fig. IV-16. Captured view of our design tool

- Fig. IV-17. Two different using of line-type inductors: (a)Serial and (b) shunt configurations.

- Fig. IV-18. Figure-of-Merit of our cascode LNA with different DC power consumptions

- Fig. IV-19. S-Parameters of 3-mW, 30 GHz designed LNA

- Fig. IV-20. Power gain and noise figure of 3-mW, 30 GHz designed LNA

- Fig. IV-21. IIP3 and FOM, defined in (IV-102), for 3-mW, 30 GHz designed LNA

- Fig. IV.22. Top view and cross section of wide ground line (a) and high impedance transmission line with special dummies, designed to minimize the line impedance reduction due to dummies.

- Fig. IV-23. (a) Layer stack (vertical cross section) and (b) top view of RF pad

- Fig. IV.24. Layout of designed LNA. The vide area outside of LNA core will be field with dummies by automatic dummy insertion process

- Fig. IV.25. Inductance and quality factor of line-type inductors in the input matching network (IMN) and output matching network (OMN).

- Fig. IV.26. Post layout simulation of optimized 3-mW LNA after trimming of inductors length. S21 of post layout simulation has been compared with pre-layout simulation.

- Fig. IV.27. Noise figure of post layout simulation, in comparison with pre-layout simulation

- Fig. IV.28. Linearity and stability of the LNA, obtained from post layout simulation

- Fig. IV-29. The snap shot of the fabricated 4-mW LNA layout

- Fig. IV-30. S-Parameters of 4-mw LNA, obtained from post layout simulation

- Fig. IV-31. S-Parameters of 4-mw LNA, obtained from post layout simulation, after incorporating the mistake in the input matching network layout

- Fig. IV-32. Die photograph of the fabricated LNA. GSG (Ground-Signal-Ground ) and matching inductors(IMN and OMN) have been marked on the figure.

- Fig. IV-33. Calibration standards, used for wafer level calibration of on-wafer RF measurement system [106].

- Fig. IV-34. Measured S-parameters of our fabricated 4-mW LNA. Due to the mistake in the input matching network layout, S<sub>11</sub> has been shifted from 30 GHz and S<sub>21</sub> has been reduced.

- Fig. IV-35. Measured power gain of our fabricated 4-mW LNA

- Fig. IV-36. Schematic of the LNA circuit for post layout simulation in CADENCE with SpecreRF simulator

- Fig. IV-37. S-parameters, obtained from measurement, in comparison with post layout simulation using our design tool and the foundry design kit, attached to CADENCE.

- Fig. IV-38. Measured noise figure of the fabricated LNA, in comparison with post layout simulation using our design tool

- Fig. IV-39. Noise figure measurement with gain method (a) and Y-factor method (b) [107].

- Fig. IV-40. Compression point measurement of the fabricated LNA

## Figures of Chapter V

Fig. V-1. Basic block diagram of a heterodyne receiver

- Fig. V-2. Representation of image rejection in a low-IF architecture, in frequency domain [31].

- Fig. V-3. Two different implementation of Hartley low IF receiver: a) two phase-shifters with simple LO and [33] b) one phase-shifter with quadrature mixer [32].

- Fig. V-4. Architecture of Weaver low-IF receiver [25].

- Fig. V-5. Architecture of direct conversion transceiver [45].

- Fig. V-6. Self mixing of LO signal and the input signal with their leakages in a direct conversion receiver [6]

- Fig. V-7. Power spectral density for GMSK and CDMA modulations [52].

- Fig. V-8. Frequency synthesize techniques to avoid VCO pulling in a direct conversion transceiver. The circuit in (a) produces unwanted harmonic in the output [69]. The circuit in (b) solves this problem in expense of more complexity [45].

- Fig. V-9. Simple transceiver structure developed for WSN applications, with direct detection of RF signal using (a) envelope detector [71] and (b) regenerative sampling [72]

- Fig. V-10. Principle of OOK and BFSK modulations

- Fig. V-11. Proposed transceiver architecture with multi-slice IF amplifier and EHM in the receiver and power oscillator (PVCO) in the transmitter

- Fig. V-12. Schematic view of NMOS cross-coupled (a), complementary cross-coupled (b) and current reuse cross-coupled (c) oscillators

- Fig. V-13. Schematic view of Pierce oscillator (a), Miller oscillator (b) [107] and the oscillators proposed in our work: current reuse Pierce-like oscillator (c) and current reuse Miller-like oscillator (d)

- Fig. V-14. Small signal model of Pierce-like (a) and Miller-like (b) oscillators

- Fig. V-15. (a) Equivalent circuit and (b) small signal model of current reuse cross-coupled oscillator

- Fig. V-16. Loop gain of Pierce-like, Miller-like and current reused cross-coupled oscillators at 15GHz, designed with various DC powers using (V-12), (V-21) and (V-29), respectively.

- Fig. V-17. Loop gain of Pierce-like, Miller-like and current reused cross-coupled oscillators as a function of frequency, designed at 15GHz

- Fig. V-18. Phase noise of 1mW, 15GHz Pierce-like, Miller-like and current reused cross-coupled oscillators, simulated using foundry design kit and Spectre-RF simulator

- Fig. V-19. Wave forms of 1mW, 15GHz Pierce-like, Miller-like and current reused cross-coupled oscillators, simulated using foundry design kit and Spectre-RF simulator

- Fig. V-20. Conventional active CMOS mixer, the even harmonic mixer proposed in [96] and the even harmonic mixer in our work

- Fig. V-21. The operation principles of conventional active CMOS mixer and the active CMOS even harmonic mixer

- Fig. V-22. Representation of tail drive signal (LO signal) of active CMOS even harmonic mixer

- Fig. V-23. Normalized conversion gain of a 14GHz active EHM with different DC power consumptions, calculated using (V-42)

- Fig. V-24. S-Parameters of the deigned mixer, simulated in Spectre-RF simulator and CMOS 90nm foundry design kit, with PSS and PSP analysis

- Fig. V-25. Conversion gain of the deigned mixer, simulated in Spectre-RF simulator and CMOS 90nm foundry design kit, with PSS and PSP analysis

- Fig. V-26. Single Side Band (SSB) and Double Side Band (DSB) noise figure of the deigned mixer, simulated in Spectre-RF simulator and CMOS 90nm foundry design kit, with PSS and PSP analysis

- Fig. V-27. Power spectrum of the supply voltage in the deigned mixer, simulated in Spectre-RF simulator and CMOS 90nm foundry design kit, with PSS and PSP analysis

- Fig. V-28. Tail current of the designed mixer, obtained from simulation in Spectre-RF (a) and obtained from our simple analytic model (b)

- Fig. V-29. Schematic of the multi channel IF amplifier, in CADENCE environment

- Fig. V-30. Gain of IF amplifier channels when (a) channel I is active, (b) channel II is active, (c) channel III is active and (d) channel IV is active.

- Fig. V-31. The output noise voltage spectral density of the IF amplifier in maximum gain

- Fig. V-32. The envelope detector circuit schematic

- Fig. V-33. voltage transfer curve and power consumption of the designed envelope detector as a function of the IF signal amplitude, simulated using Spectre-RF

- Fig. V-34. BER of our receiver as a function of the received signal power

- Fig. V-35. An example of the simulation results of the receiver in MATLAB, for a 100-bit data stream and -87dBm received signal level

- Fig. V-36. Eye diagram of received base band signal, corresponding to a 100-bit data stream

- Fig. V-37. Schematic view of the power VCO circuit in our work

- Fig. V-38. Time domain wave forms of the transmitter, obtained from simulation in CADENCE using Spectre-RF simulator and the attached foundry design kit

- Fig. V-39. (a) power consumption and (b) phase noise of the designed power VCO

#### **List of Tables**

- TABLE I-1. Specifications of 3 fabricated chips for WSN applications [57].

- TABLE I-2. The energy costs of different operations in a typical sensor node [9].

- TABLE III-1. Elements of the Lumped Model of RF Pad

- TABLE IV-1. Recently published mm-wave LNAs in CMOS technology

- TABLE IV-2. Recently published Q and Ka band CMOS LNAs

- TABLE IV-3. Performance of the designed LNA at 31GHz, from post layout simulation

- TABLE IV-4. Comparison of our fabricated and designed LNA with the reported LNAs in 30GHz band

- TABLE IV-5. Comparison of our fabricated and designed LNA with the reported single stage LNAs in 30GHz band

- TABLE V-1. Summary of Reported WSN Transmitters

- TABLE V-2. Summary of Reported WSN Receivers

- Table V-3. Features of the Designed Radio Link

- TABLE V-4. Comparison of Recently Published Ka Band Mixers

- TABLE V-5. Summary of Designed Receiver Parameters

- TABLE V-6. Comparison of our Receiver with Reported mm-wave Receivers

## **Chapter I**

#### RF Front End in Wireless Sensor Networks

#### I.1. Wireless Sensor Network Overview

#### I.1.1. WSN History

A Wireless Sensor Network (WSN) is composed of a large number of sensor nodes, each node capable of sensing its environment, processing the acquired data and communication with other sensors. The design and implementation of a wireless sensor network requires confluence of many fields, including communication and RF technology, sampling technology, signal processing, networking, power management, embedded systems, information aggregation, and distributed computing [1].

The history of WSN comes back to 1994, when DARPA funded the research projects, Low Power Wireless Integrated Micro-sensor (LWIM) and SensorIT at University of California [2], [3]. In 1998 Wireless Integrated Network Sensors (WINS) project was reported by University of California, Los Angeles, aiming at development of Micro-Electro-Mechanical Sensors (MEMS), efficient circuit design and self-organizing networking [4]. Then they biased toward military and environmental applications. PicoRadio was the other WSN project, reported in 2000, at University of California, Berkley, to support the assembly of an ad hoc wireless network of self-contained mesoscale, low-cost, low-energy sensor and monitor nodes [5], [6].

Advances in microelectronic devices and systems realized the design of very small sensor nodes, with capability of sensing, computing and communication. Such a small platform was referred to as *motes*. Then sensor networks were targeted to use of extremely low cost micro sensors that can be suspended in air. The first attempt in this way was the DARPA/UC Berkeley research project, named "Smart Dust", in which 4mm<sup>3</sup> nodes was fabricated [7], [8]. Actually the genesis of Smart Dust was a workshop at RAND in1992 in which a group of academics, military personnel, and futurists were chartered to explore how technology revolutions would change the battlefield of 2025 [9]. The other *mote* sensor nodes were MICA2 and TelosA, developed by CrossBow and MoteIV corporations [10], [11]. Today, based on recently the amazing growth of sub-miniature, low-cost and low-powered hardware, the wireless sensor network is strongly researched for the various applications [1], [12]-[15].

#### I.1.1. WSN Applications

At a glance the application of WSN can be divided into two main category of civil and military applications. Industrial and manufacturing remote control, mechatronics and automation, distributed energy system control, emergency medical care, habitat monitoring, active volcano sensing, structural health monitoring, under ground mining, identification and personalization, aircraft health monitoring, environmental monitoring, environmental control in office buildings, robot control and guidance in automatic manufacturing, high security small homes, cultural property protection are examples of WSN civil applications[1], [16]-[22].

In disaster scene, use of WSN can greatly increase the rescue operation efficiency and rescue crew safety and can provide an intelligent rescue support framework [13], [18], [23]. In consumer electronic domain, WSN can form a warm atmosphere at home and boost the work efficiency in offices [24], [25].

In military applications, the use of these networks can limit the need for personnel involvement in usually dangerous reconnaissance missions. In addition sensor networks can enable a more civic use of landmines by making them remotely controllable and target specific, in order to prevent harming civilians [18], [26]. In tactical communication, Surveillance, Recognition & tracking, On-site, unattended, high-precision and real-time observation over a vast area, in security, intrusion detection and criminal hunting, WSN has been considered to have a good potential [27], [28].

Regarding so vast applications for WSN, many works in recent years have addressed the cooperation of new WSN's with existing networks, specially mobile ones, [29], [30].

#### I.1.2. WSN Structure and Specifications

Among the existing networks, the Mobile Ad hoc Networks (MANETs) are more similar to the WSNs. However there are some essential differences between them [18]:

Sensor nodes in a WSN can be several orders of magnitude higher than MANET.

Sensor nodes in a WSN are much cheaper than the nods in MANET.

Power resource of a WSN node is more limited.

WSN nodes have limited computational capability.

WSN nodes are more prone to failures.

The topology of a WSN varies more frequently than a MANET.

WSN nodes use normally a broadcasting paradigm, whereas MANET nodes use point-to-point communication.

The architecture of wireless sensor networks needs to accommodate three characteristics [16]:

Scalability: Large-scale wireless sensor networks rely on thousands of tiny sensors to observe and influence the real world. These sensors do not necessarily need to be active at all times, so sensors can be dynamically added to or removed from the network. A durable and scalable architecture would allow responses to changes in the topology with a minimum of update messages being transmitted.

Task Orientation: The sensor networks are always correlative with tasks at current stage. The tasks of wireless sensor networks range from the simplest data capturing and static-nodes to the most difficult data collecting, mobile-node sensor network. The sensor networks for different tasks behave totally differently sometimes. The software structure should be reasonably optimized and tailored, according to predefined task-set of each node, to be adapted to this distinction.

Light Weight: The computing and storage capabilities of sensor nodes are very limited. Lightweight operations, such as data aggregation, reduced message size, and a piggyback acknowledgment mechanism, must be applied to the architecture.

Traditionally, wireless sensor networks devices and corresponding network protocols are designed to handle a small amount of data and most sensor nodes can only sustain an effective data rate of tens of kilobytes/Sec [31]. However, with the increasing popularity of wireless sensor networks in a broad spectrum of applications, higher data transportation capability is in need. In particular, visual information (such as still image or video data) is very valuable in many applications. For instance, wireless devices with video camera can be used to provide video surveillance in battlefield network [32].

#### I.1.3. Sensor Node Structure

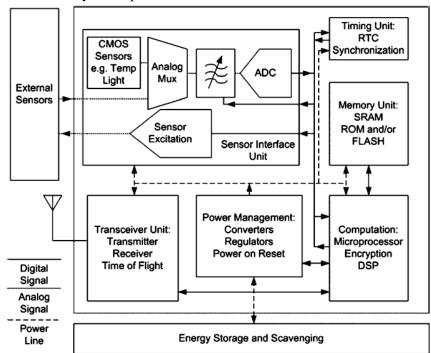

Basic block diagram of a wireless sensor node has been shown in Fig. I-1 [9]. A complete node consists of many blocks, most of which can be integrated onto a single standard CMOS die. Energy storage (batteries, large capacitors, or inductors), energy scavenging, and some sensors will likely be off-chip components. The primary integrated blocks include a sensor

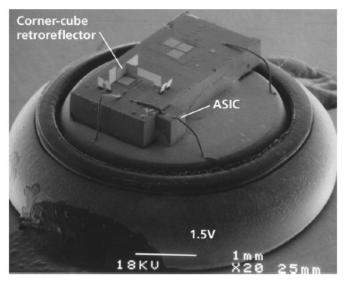

interface, memory, computation, power management, and an RF transceiver. Development of highly integrated sensor mote components started in the mid-1990s and resulted in multi-chip systems that could be assembled to create a mote. At UCLA, MEMS devices were combined with commercial CMOS chips that provided sensor control and readout as well as communication [9]. To minimize energy, passive optical communication was explored for early Smart Dust motes [33]. Fig. I-2 shows the sensor node fabricated as integration of CMOS and MEMS technology for early generations of Smart Dust, at University of California, Berkeley. This node comprises an bidirectional communication system with a MEMS optics chip containing a corner-cube retro-reflector on the large die, a CMOS application-specific integrated circuit (ASIC) for control on the 300 × 360 micron die, and a hearing aid battery for power. The total volume is 63 mm3. [8]. In the next generations highly integrated chips with a complete RF transceiver, microprocessor, ADC, and sensor interface have been reported [34], [35].

Most of the blocks in Fig. I-1 can be implemented in standard CMOS process, suitable for mote sensor node [36], [37]. However still some parts like off-chip battery, a crystal timing element, and an RF antenna, should be off-chip, resulting in a complete package at the centimetre scale. As an example, a  $\lambda/4$  patch antenna in the size of  $4\times5\times1.64$ mm<sup>3</sup> has been designed for mote sensors, operating at 10GHz [38]. A 6.8mmOD x 1.2mm, 3V and a 5.8mmOD x 1.6mm, 1.5V rechargeable Mn-Li cells has been used in the first and second Smart Dust generations, respectively [39]. Fig. I-3 shows complete sensor nodes, with different possible levels of integration. While the cost, size, and power consumption of off-the-shelf sensor nodes is far from optimal, a single-chip system may not be the most advantageous either and the most economical solution is likely to be a hybrid of integrated and assembled parts [9]. The device at the top of Fig. I-3 is the Mica sensor node [10] and the device at the bottom of Fig. I-3 represents a hypothetical 2-mm3 mote-on-a-chip combining cutting-edge process integration and circuit techniques. In [34] a fully integrated 1V wireless SoC that embeds not only a complete dual-band RF transceiver, but also a sensor interface for

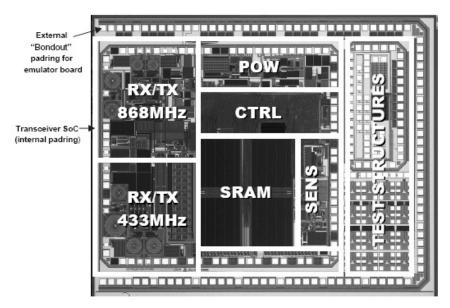

Fig. I-1. Basic block diagram of a wireless sensor node [9]

signal acquisition, a RISC microcontroller and memory-based control unit, and a power-management unit that can generate up to 2.4V for off-chip parts from a 1.0V to 1.6V AA battery, has been described. The RF front-end consists of two RX/TX channels targeting the 433MHz (ISM) and the 868MHz (SRD) European bands. With a different input adaptation scheme, the US 915MHz can also be covered. The RX and TX are built according to a two-step super-heterodyne architecture with LO frequencies set to 8/9 and 1/9 of the RF, and share a common PLL based on a 772MHz VCO and a division chain for the other LO signals. The VCO tank is built with two external high-Q inductors and an on-chip varactor. An integer-N synthesizer PLL uses a 12.8MHz quartz reference and allows the RF frequency to be adjusted with 12.5kHz steps. Scan Electron Micrograph (SEM) of the IC has been given in Fig. I-4. The IC has been implemented on standard digital 0.18μm CMOS and has a size of 3.5×4 mm², excluding the "bond-out" pad-ring.

Fig. I-2. The mote sensor node fabricated as integration of CMOS and MEMS technology for early generations of Smart Dust, at University of California, Berkeley. [8]

| Power   | Volume                 | 25<br>mm | Sensor(s)     | Processor            | Energy<br>Harvesting        | Energy<br>Storage                       | RF                | Antenna                    | Timing<br>Reference |

|---------|------------------------|----------|---------------|----------------------|-----------------------------|-----------------------------------------|-------------------|----------------------------|---------------------|

| Highest | 45,000 mm <sup>3</sup> | 60 mm    | Off-the-shelf | Atmel<br>Atmega 128L | None                        | 2 AA Batteries                          | ChipCon<br>CC1000 | Straight Wire              | Quartz Crystal      |

| Lowest  | 100 mm <sup>3</sup>    |          |               | Custom               | Off-the-shelf<br>Solar Cell | Off-the-shelf<br>Microbattery           | Custom<br>CMOS    | Dielectric Chip<br>Antenna | Quartz Crystal      |

| Low     | 2 mm³                  |          |               | Custom<br>CMOS       | Custom<br>Solar Cell        | Custom Thin-<br>film Lithium<br>Battery | Custom<br>CMOS    | Custom On-<br>Chip Antenna | MEMS<br>Resonator   |

Fig. I-3. Complete sensor nodes, with different possible levels of integration [9]

Fig.I.4. SEM of the fully integrated sensor node, presented in [34]

#### I.1.4. Security and Reliability in WSN

Remote wireless sensor networks are vulnerable to malicious attacks. While wired and infrastructure-based wireless networks have mature intrusion detection systems and sophisticated firewalls to block these attacks, wireless sensor networks have only primitive defences. Different types of attacks and risks for a WSN have been studied [40]. Beside the performance perturbation, malicious attackers can easily target the battery supplies and reduce network lifetimes from years to days [31].

Reliability is another important issue in WSN's. Information theoretic approach has been used to estimate the redundancy in a randomly deployed wireless sensor network and provide the Cramer-Rao bound on the error in estimating the redundancy in a wireless sensor network [41]. Simple source and channel codings, e.g. LDPC<sup>2</sup>, have been suggested for WSN's [42]. In AWGN<sup>3</sup> channels the LDPC performance is very close to the Shannon capacity. Also, LDPCs have gained more attention because of its parallelizable, and can be suitable for VLSI implementations [43].

#### I.1.5. Power Source Limitation in WSN

DC power source is the most critical section of a sensor node. Battery size determines the size and lifetime of a mote sensor node, consequently minimization of power consumption, not only maximizes the sensor life time, minimizes, but also minimizes its size [39].

Among the numerous technologies in terms of the materials used and chemistry and composition that can serve as the basis for rechargeable (or secondary) batteries, the Lithium ion (Li-ion) cells exhibit one of the highest energy densities among the commercially available types—i.e., specific energy density of 80–125 W h/kg (watt hour per kilogram) and volumetric energy of 200–450 W h/l (watt hour per litre). For instance, miniature Li-ion rechargeable battery sources as small as 0.08–0.155cc with capacity ratings of 3–25 mA h are readily available for biomedical implants. These batteries can also accommodate current pulses of 10–15 mA depending upon battery size, which makes them suitable for low power wireless devices [44]. Low-data-rate wireless sensor networks such as WiseNET are built

5

<sup>&</sup>lt;sup>2</sup> Low Data rate Parity-check Code

<sup>&</sup>lt;sup>3</sup> Additive White Gaussian Noise

with nodes that have to achieve from 2 to 7 years operating life on a 1.5V AA alkaline battery [34]. A AA battery contains roughly 250 uA-years of charge or about 12000 J. For some lithium chemistries, the internal leakage is low enough that supplying this charge as a current of 25 uA for a decade is possible while common alkaline chemistries have shorter lifetimes [9].

Energy scavenging and harvesting techniques, e.g. solar cells, have been proposed for sensor nodes [5]. Battery powered wireless sensor nodes can be recharged by harvesting energy from a solar cell [33] or a microwave Radio Frequency (RF) signal source [45]. In such nodes a wireless battery is used to convert wireless RF power into DC power. In [46] an specially designed wireless battery or *rectenna* has been designed, operating at 2.45GHz and the power conversion efficiency of 52% has been achieved for a 0dBm power level received by the antenna.

Aside from battery technology, various power saving methods have been developed for WSN's. Conventional power saving techniques have been investigated in [47] and [48]. Analytic models have been developed for analysis and optimization of power consumption in a WSN [49]. Power consumption in a WSN can be related to three levels of the network: Hardware, protocol and operating system [14]. In other reports this has been divided into Physical layer, Media Access layer (MAC) and Network layer [6].

#### **Power Saving in Protocol level**

Medium access protocols which accommodate dynamic voltage and frequency scaling, as well as dynamic or periodical sleeping, have been proposed for minimizing collusion, overhearing and idle listening [1]. Nodes synchronization in the network has important effect on the power consumption of the nodes. Conventionally used Reference Broadcasting Synchronization (RBS) in ad hoc networks, is not suitable for WSN's. In RBS high volume of message packets to be propagated upon the network that waste the energy of the nodes. Consequently new synchronization techniques have been proposed for WSN's [29]. Special clustering schemes for efficient energy consumption and energy aware routing protocols have been developed [50]-[52]. Using Multi-hop access, instead of single-hop access, effectively reduces the energy cost per bit [6]. Different channel codings (modulation) have been investigated in [42]. Various researches have been performed on Mica2 WSN node to evaluate different protocols [53]. In [54] a MAC protocol with Slot Periodic Assignment for Reception (SPARE MAC) has been presented that limits the energy waste due to packet overhearing, packet over-emitting, and idle listening. SPARE MAC is a Time Division Multiple Access (TDMA) based scheme, which implements a distributed scheduling solution that assigns time slots to each sensor for data reception and shares such assignments with neighboring nodes. Package duplication and multi-path package reception problems have been investigated in [55] and a protocol named Receiver Based Forwarding (RBF) has been presented.

#### I.1.5.1. Power Saving in Operating system level

In operating system level Dynamic Power Management (DPM) has been investigated in [14] and the sentry-based power management has been addressed, in which the nodes are partitioned dynamically into two sets: sentries and non-sentries. The sentries provide sufficient coverage for monitoring and communication services and non-sentries nodes sleep for a designated period of time. An application-driven power control has been proposed in [56] and three states: active, idle and sleep has been defined for nodes.

#### I.1.5.2. Power Saving in Hardware level

In our opinion, power consumption reduction in physical layer is the most important issue in the power saving of a sensor node. Special design and integration techniques have been used for reducing the power consumption of sensor nodes [57]. To give the scenes about the power consumption in existing wireless sensor nodes, we investigate some available and reported ones. Some commercial IC's have been presented by famous companies in the WSN domain [57]. CC2430 /2431 is a wireless sensor node, fabricated as fully integrated System-on-Chip (SoC) by Chipcon [58]. MC132121 series is another fully integrate sensor node, manufactured by Freescale Semiconductor company [59]. JNS121series are fully integrate wireless sensor nodes, presented by Janic company [60]. The main characteristics of these chips at the working frequency of 2.4GHz, have been tabulated in Table I-1 [57]. The interesting note in this table is that the power consumption in RX mode is more than that of TX mode. This also has been emphasised in [61], in which claimed that 50% of total power dissipation is in the transceiver, of which 80% is consumed in the receiver. Specifications of more RF chipsets, fabricated for WSN applications have been presented in [57]. Crossbow Company has a wide variety of mote sensor nodes, all having the DC power consumptions about the values in Table. I.1 [10]. These sensor nodes have been used in many recent WSN researches [53].

Although power dissipation for commercially available sensor motes is in the range of few tens of mA, such DC power is very high for Smart Dust projects. The desired average DC power consumption is below 100uW [5]. Such value may be achievable, if laser communication is used in a very simple sensor node [36], [33]. However in the case of to days low power radio communication technology, and for a complicated digital processor this seems to be an oxymoron.

Power dissipation in hardware level is divided into three sections: Analog and digital circuits, RF circuits and ADC converters. It is well known that the RF section consumes a largest amount of the energy in a low power communication system [57]. For the first ADC circuits, designed for the first generations of smart Dust, the reported specs were 360 PJ/S (Pico-Jules per sample) with the sampling rate of 100KS/Sec and 8-bit samples that is equivalent to the DC power of 3.6mW in full speed working. For the next generations of this

TABLE I-1

Specifications of 3 fabricated chips for WSN applications [57].

| Parameters                        | CC2430                               | MC1321x                    | JN5121                  |

|-----------------------------------|--------------------------------------|----------------------------|-------------------------|

| Operating Supply<br>Voltage (Vdd) | 2.0 ~ 3.6V                           | 2.0~3.4V                   | 2.2 ~ 3.6V              |

| MCU active and<br>RX mode (Icc)   | 27 mA                                | 37 mA                      | < 50 mA                 |

| MCU active and<br>TX mode (Icc)   | 25 mA                                | 30 mA                      | < 40 mA                 |

| Maximum Transit<br>Power          | 0 dBm                                | 2 dBm                      | l dBm                   |

| Power Down Mode<br>Current (Ipd)  | 0.9 uA                               | l uA                       | < 5 uA                  |

| Receiver<br>Sensitivity           | -94 dBm                              | <-94 dBm                   | -93 dBm                 |

| Microprocessor                    | 32 MHZ 8-bit<br>Low power 8051       | 40MHz<br>HCS08             | 16 MHZ<br>32-bit, RISC  |

| Memory                            | 32, 64, or 128 KB<br>Flash, 8 KB RAM | 1-4KB RAM<br>16-60KB Flash | 64 KB ROM,<br>96 KB RAM |

| ADC                               | 8-14 bit ADC                         | 8-10 bit ADC               | 4-12 bit ADC            |

| DAC                               |                                      |                            | 2-11 bit DAC            |

project the reported specs were 31 PJ/S with the sampling rate of 100KS/Sec and 8-bit samples in 0.25um CMOS process, that is equivalent to the DC power of 0.3 mW in full speed working. The DC power consumption of 0.26 mW has been reported in [6] for the processor section of a typical WSN node. In the fully integrated sensor node reported in [34], fabricated in 0.18um CMOS, the processor has two modes of operation: 32 KHz and 6.4 MHz. The required DC power is 60uA/MIPS, that is equal to less than 0.38 mW, in worst case. However the RX power consumption in this work is 2.1 mA with 1~1.6 V supply and the TX power is 27.6 or 32.3 mA, depending on the working frequency. The energy costs of different operations in a typical sensor node have been listed in Table I-2 [9]. However using new technologies, sub-mW CMOS transceivers have been emerged. More details of DC power consumption in RF sections will be given in the next section.

#### I.2. Transmitter and Receiver in WSN

As we mentioned earlier, a significant part of DC power in a sensor node is consumed by the transceiver. Consequently special attention should be paid for design and optimization of the RF parts. Here we present a preliminary discussion and the details analysis will be presented in Chapter V. Power consumption of the RF front end in a WSN node can be minimized in three levels: Protocol level, Structure level and circuit level.

The highest level is the protocol considerations. Note that the network protocol affects the total power consumption of the network, in two ways. One is the network-related issues, as pointed in the previous sections and the other is its direct influence on the transceiver. Parameters such as working frequency, modulation scheme and the transmitted signal nature are given by the protocol and directly affect the structure and power efficiency of the transceiver. As we explained, WSN's are inherently low data rate systems and hence low-data rate UWB<sup>4</sup> protocols may be useful for WSN's. Such protocols can be considered under the IEEE 802.15.4a standard [62]. Many works have been reported to implement UWB transceivers for WSN's [61], [63]-[67], however in [61] suggested that this standard is not sufficient for WSN applications. Most interest in WSN is very simple modulations, such as OOK<sup>5</sup>, BFSK<sup>6</sup> and PPM<sup>7</sup> [68]-[72].

The second level is the structure of the transceiver. Historically used heterodyne transceivers, Low-IF transceivers and Zero-IF (Direct Conversion) transceivers are possible choices for WSN applications [9], [34]. In addition, special transceiver architectures have been presented for low data rate UWB applications [62], [64], [73]. In recent years special

TABLE I-2

The energy costs of different operations in a typical sensor node [9].

| Operation                                                               | Lowest Energy Published | Commercially Available (off-the-shelf) |

|-------------------------------------------------------------------------|-------------------------|----------------------------------------|

| 8-Bit Analog-to-Digital<br>Conversion                                   | 0.031 nJ                | 13.5 nJ                                |

| 8-Bit Microprocessor<br>Instruction                                     | 0.012 nJ                | 0.20 nJ                                |

| Compute an 8-Bit, 1024<br>point FFT                                     | 80 nJ                   |                                        |

| Transmit and Receive one 8-<br>Bit sample via RF at up to 20<br>m Range | 32 nJ                   | 2500 nJ                                |

<sup>&</sup>lt;sup>4</sup> Ultra Wide Band

<sup>&</sup>lt;sup>5</sup> On - Off Keying

<sup>&</sup>lt;sup>6</sup> Binary Frequency Shift Keying

<sup>&</sup>lt;sup>7</sup> Pulse Position Modulation

simple transceiver structures have been developed for WSN applications [68], [70], [74]-[76]. Various structures will be compared in Chapter V.

The third level is the various circuits used in the transceiver. In recent years many circuits have been designed to be used in WSN transceivers. Some propose MEMS or other special technologies to achieve very low power [77], [78] and some other have emphasis on bulk CMOS technology [79], [80]. The technologies other than CMOS also have been considered in design of Class E power amplifiers for WSN's [81].

#### I.3. Transceiver Specifications

In this section we briefly describe the given specification for the transceiver we have designed and the semiconductor technology we have used in our work.

## I.3.1. Semiconductor Technology Issues

Until 1990 few experts believed that CMOS will be a credible RF technology. In 1980 first CMOS RF application emerged: A broadcasting FM radio in 2 um CMOS, however the performance is not acceptable [82]. Then during only one decade, CMOS technology was the best candidate for many below-10GHz RF applications. Generally specking, the speed of analog CMOS circuits climbs by roughly one order of magnitude every ten years. For example, the first 1.4-GHz MOS voltage-controlled oscillator (VCO) was reported in 1988, the first 10-GHz CMOS oscillator in 1999, and the first 104-GHz CMOS VCO in 2004 [83].

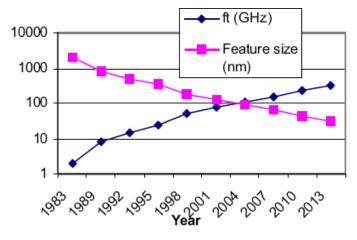

Today,  $f_T$  of CMOS transistors has passed 100GHz and CMOS technology experiences the millimeter wave designs. VCO in 114 GHz and LNA in up to 80GHz in 0.13um bulk CMOS have been reported in 2007 [84], [85]. Fig. I-5 shows the outlook of CMOS technology, implying that in the recent decade near-THz circuits will be emerged [82].

We will use STMicroelectronics 90 nm Global Purpose (GP) process in our work. The related foundry design we have used in our work supports only the digital design and hence all of the high frequency issues have been modelled and added specially for our work. Modelling of passive and even active devices have been done individually, using the foundry design kit as the reference. The layout for all the passive devices (except for the Resistors and MIM capacitors) and active devices (except for MOS transistor core) required in our work, have been designed individually, using the foundry Design Rule manual (DRM) data. Special attention has been paid to comply with the density design rule checks. The details will be given in Chapters II and III.

Fig. I-5. The outlook of modern CMOS technology [82].

Our design and optimization has been done in our design tools, we have developed specially for our work. However verifying simulations have been done using the foundry design kit attached to the CADENCE software, using the Spectre RF circuit simulator, Virtuse Layout Editor, Diva Layout Versus Schematic (LVS) check and Calibre extraction tool.

## I.3.2. Transceiver Specifications in Our Work

The unlicensed 57-64 GHz was opened as ISM<sup>8</sup> band for new short range, high data rate communications [86]. The ultimate objective of our project is to use this band in Smart Dust wireless sensor network. Using this band, the wireless sensor network will benefit the smaller sensor nodes and higher security. However many problems related to such high frequency must be solved. Our work has been defined to be done in 30GHz band, as a bridge to the ISM 60GHz band. Since our work is the preliminary step of the final project, other specification are not given and we will go toward the best possible results.

-

<sup>&</sup>lt;sup>8</sup> Industrial, Scientific and Medical

#### References

- [1] C. Hermann, W. Dargie, "Senceive: a middleware for a wireless sensor network," *In Proceedings of the IEEE International Conference on Advanced Information Networking and Applications (AINA 2008)*, pp. 612-619, March 2008.

- [2] Uday B. Desai, B. N. Jain, S. N. Merchant "Wireless sensor networks: where do we go?," Presented in the WSN Workshop, SPANN Lab., Bombay, April 2007.

Available [Online]: http://www.ee.iitb.ac.in/spann/WSN-Presentations/

- [3] K. Bult, A. Burstein, D. Chang, M. Dong, M. Fielding, E. Kruglick, J. Ho, F. Lin, T. H. Lin, W. J. Kaiser, H. Marcy, R. Mukai, P. Nelson, F. Newberg, K. S. J. Pister, G. Pottie, H. Sanchez, O. M Stafsudd, K. B. Tan, C. M. Ward, S. Xue, J. Yao, "Low power systems for wireless microsensors", *In Proceedings of the IEEE International Symposium on Low Power Electronics and Design*, pp. 17-21, 1996.

- [4] G. Asada, M. Dong, T. S. Lin, F. Newberg, G. Pottie, W. J. Kaiser, H. O. Marcy, "Wireless integrated network sensors: Low power systems on a chip," *In Proceedings of the 24th European Solid-State Circuits Conference (ESSCIRC '98)*, pp. 9-16, Sept. 1998.

- [5] J. M. Rabaey, M. J. Ammer, J. L. da Silva, D. Patel, S. Roundy, "PicoRadio supports ad hoc ultra-low power wireless networking," *IEEE Journal of Computer*, vol. 33, issue 7, pp. 42-48, July 2000.

- [6] J. Rabaey, J. Ammer, J. L. da Silva, D. Patel, "PicoRadio: Ad-hoc wireless networking of ubiquitous low-energy sensor/monitor nodes," *In Proceedings of the IEEE Computer Society Workshop on VLSI*, pp. 9-12, April 2000.

- [7] [On line] Available: http://robotics.eecs.berkeley.edu/~pister/SmartDust

- [8] B. Warneke, M. Last, B. Liebowitz, K. S. J. Pister, "Smart Dust: communicating with a cubic-millimeter computer," *IEEE Journal of Computer*, vol. 34, issue 1, pp. 44-51, Jan. 2001.

- [9] B. W. Cook, S. Lanzisera, K. S. J. Pister, "SoC Issues for RF Smart Dust," *Proceedings of the IEEE*, vol. 94, issue 6, pp. 1177-1196, June 2006.

- [10] Available [On line]: <a href="http://www.xbow.com">http://www.xbow.com</a>

- [11] Available [On line]: <a href="http://www.moteiv.com/products-reva.php">http://www.moteiv.com/products-reva.php</a>

- [12] Jo Youngtae, Park Chongmyung, Lee Joahyoung, Jung Inbum, "Energy effective time synchronization in wireless sensor network," *In Proceedings of the IEEE International Conference on Computational Science and its Applications (ICCSA 2007)*, pp. 547-553, Aug. 2007.

- [13] Kim Jungsook, Kim Dohyun, Sung Kyungbok, Iang Byungtae, "Safe driving system based on wireless sensor technology," *In Proceedings of the IEEE International Geo-science and Remote Sensing Symposium (IGARSS 2007)*, pp. 619-622, July 2007.

- [14] Yan Shen, Bing Guo, "Dynamic power management based on wavelet neural network in wireless sensor networks," *In Proceedings of the IEEE International Conference on Network and Parallel Computing Workshops* (NPC Workshops), pp. 431-436, Sept. 2007.

- [15] Han Xiaofeng, Cao Xiang, E. L. Lloyd, Shen Chien-Chung, "fault-tolerant relay node placement in heterogeneous wireless sensor networks," *In Proceedings of the IEEE International Conference on Computer Communications (INFOCOM 2007)*, pp. 1667-1675, May 2007.

- [16] Duan Shangwei, Yuan Xiaobu, "Exploring hierarchy architecture for wireless sensor networks management," *In Proceedings of the IEEE International Conference on Wireless and Optical Communications Networks*, pp. 6-10, April 2006.

- [17] Chen Wanming, Mei Tao, Liang Huawei, You Zhuhong, Li Shuai, M.Q.-H. Meng, "Environment-map-free robot navigation based on wireless sensor networks," *In Proceedings of the IEEE International Conference on Information Acquisition (ICIA '07)*, pp. 569-573, July 2007.

- [18] Dai Shijin, Jing Xiaorong, Li Lemin, "Research and analysis on routing protocols for wireless sensor networks," *In Proceedings of theIEEE International Conference on Communications, Circuits and Systems*, vol. 1, pp. 407-411, May 2005.

- [19] Sung Jongwoo, Ahn Sungjin, Park Taesoo, Jang Seonghun, Yun Dongheui, Kang Jonggu, Yoo Seong-eun, P. Chong, Kim Daeyoung, "Wireless sensor networks for cultural property protection," In Proceedings of the IEEE International Conference on Advanced Information Networking and Applications Workshops (AINAW 2008), pp. 615-620, March 2008.

- [20] J. Wall, G. Platt, G. James, P. Valencia, "Wireless sensor networks as agents for intelligent control of distributed energy resources," *In Proceedings of the IEEE International Symposium on Wireless Pervasive Computing (ISWPC '07)*, Feb. 2007.

- [21] J. J. Evans, "Wireless sensor networks in electrical manufacturing," *In Proceedings of the IEEE Electrical Insulation Conference and Electrical Manufacturing Expo*, pp. 460-465, Oct. 2005.

- [22] Bai Haowei M. Atiquzzaman, D. Lilja, "Wireless sensor network for aircraft health monitoring," *In Proceedings of the IEEE First International Conference on Broadband Networks (BroadNets 2004)*, pp. 748-750, 2004.

- [23] Lim Yeon-sup, Lim Sangsoon, Choi Jaehyuk, Cho Seongho, Kim Chong-kwon, Lee Yong-Woo, "A fire detection and rescue support framework with wireless sensor networks," *In Proceedings of the IEEE International Conference on Convergence Information Technology*, pp. 135-138, Nov. 2007.

- [24] M. Sartipi, F. Fekri, "Source and channel coding in wireless sensor networks using LDPC codes," *In Proceedings of the First Annual IEEE Conference on Sensor and Ad Hoc Communications and Networks* (SECON 2004), pp. 309-316, Oct. 2004.

- [25] Wang Ying, Zhou Guangrong, Li Tong, "Design of a wireless sensor network for detecting occupancy of vehicle berth in car park," *In Proceedings of the IEEE International Conference on Parallel and Distributed Computing, Applications and Technologies (PDCAT '06)*, pp. 115-118, Dec. 2006.

- [26] P. Frost Gorder, "Sizing up smart dust," *IEEE Journal of Computing in Science & Engineering* vol. 5, issue 6, pp. 6-9, Nov.-Dec. 2003.

- [27] Barry Horowitz, Jorg Libeherr, Stephen D. Patek, Jianping Wang, Altaf Bahora, Guangyu Dong, Phil Harton, Myong S. Sung, Evan Tschannen-Moran, Wittawat Tantisiriroj, "Systems and information engineering technical report: SIE-050004," University of Virginia, Available [Online]: <a href="http://www.sys.virginia.edu/techreps/2005/sie-050004.pdf">http://www.sys.virginia.edu/techreps/2005/sie-050004.pdf</a>

- [28] Manoj Kumar Dhaka, "WSN & ad hoc networking from defense perspective," Presented in the WSN Workshop, SPANN Lab., Bombay, April 2007. Available [Online]: <a href="http://www.ee.iitb.ac.in/spann/WSN-Presentations/">http://www.ee.iitb.ac.in/spann/WSN-Presentations/</a>

- [29] S. Krco, V. Tsiatsis, K. Matusikova, M. Johansson, I. Cubic, R. Glitho, "Mobile network supported wireless sensor network services," *In Proceedings of the IEEE International Conference on Mobile Ad hoc* and Sensor Systems (MASS 2007), pp. 1-3, Oct. 2007.

- [30] Ayman Sleman, Reinhard Moeller, "Integration of wireless sensor network services into other home and industrial networks; using device profile for web services (DPWS)," *In Proceedings of the IEEE International Conference on Information and Communication Technologies: From Theory to Applications* (ICTTA 2008), pp. 1-5, April 2008.

- [31] M. Brownfield, Gupta Yatharth, N. Davis, "Wireless sensor network denial of sleep attack," *In Proceedings of the Sixth Annual IEEE SMC Information Assurance Workshop (IAW '05)*, pp. 356-364, June 2005.

- [32] Wang Ju, M. Masilela, J. C. L. Liu, "Supporting video data in wireless sensor networks," *In Proceedings of the IEEE International Symposium on Multimedia*, 2007 (ISM 2007), pp. 310-317, 10-12 Dec. 2007.

- [33] B. A. Warneke, M. D. Scott, B. S. Leibowitz, Lixia Zhou; C. L. Bellew, J. A. Chediak, J. M. Kahn, B. E. Boser, K. S. J. Pister, "An autonomous 16 mm/sup 3/ solar-powered node for distributed wireless sensor networks," *Proceedings of IEEE, Sensors*, 2002.

- [34] V. Peiris, C. Arm, S. Bories, S. Cserveny, F. Giroud, P. Graber, S. Gyger, E. Le Roux, T. Melly, M. Moser, O. Nys, F. Pengg, P. –D. Pfister, N. Raemy, A. Ribordy, P. –F. Ruedi, D. Ruffieux, L. Sumanen, S. Todeschin, P. Volet, "A 1 V 433/868 MHz 25 kb/s-FSK 2 kb/s-OOK RF transceiver SoC in standard digital 0.18 /spl mu/m CMOS," *IEEE International Solid-State Circuits Conference (ISSCC 2005), Digest of Technical papers*, vol. 1, pp. 258-259Feb. 2005.

- [35] [Online] Available: <a href="http://www.chipcon.com">http://www.chipcon.com</a>

- [36] B. Atwood, B. Warneke, K. S. J. Pister, "Preliminary circuits for Smart Dust," In Proceedings of the IEEE Southwest Symposium on Mixed-Signal Design (SSMSD. 2000), pp. 87-92, Feb. 2000.

- [37] M. D. Scott, B. F. Boser, K. S. J. Pister, "An ultra low-energy ADC for Smart Dust," *IEEE Journal of Solid-State Circuits*, vol. 38, issue 7, pp. 1123-1129, July 2003.

- [38] P. Basset, F. Alfaro, D. Novosel, A. de la Plaza, D. Stancil, G. K. Fedder, "Chip-size antennas for implantable sensors and smart dust," *In Proceedings of the IEEE International Conference on Solid-State Sensors, Actuators and Microsystems, Digest of Technical Papers. (TRANSDUCERS '05)*, vol. 1, pp. 457-460, June 2005.

- [39] B. Warneke, B. Atwood, K. S. J. Pister, "Smart dust mote forerunners," *In Proceedings of the IEEE International Conference on Micro Electro Mechanical Systems (MEMS 2001)*, pp. 357-360, Jan 2001.

- [40] A. S. K. athan, Lee Hyung-Woo, Hong Choong Seon, "Security in wireless sensor networks: issues and challenges," *In Proceedings of the IEEE International Conference on Advanced Communication Technology (ICACT 2006)*, vol. 2, pp. 1043-1048, Feb. 2006.

- [41] Renita Machado, Sirin Tekinay, "Bounds on the error in estimating redundancy in randomly deployed wireless sensor networks," *In Proceedings of the IEEE International Conference on Sensor Technologies and Applications (SensorComm 2007)*, pp. 319-324, Oct. 2007.

- [42] M. Sartipi, F. Fekri, "Source and channel coding in wireless sensor networks using LDPC codes," *In Proceedings of the IEEE Conference on Sensor and Ad Hoc Communications and Networks (SECON 2004)*, pp. 309- 316, Oct. 2004.

- [43] Lin Li-Hsieh, Tsou Wen-An, Fan Long-Sheng, Wuen Wen-Shen, Wen Kuei-Ann, "An energy saving scheme for long range and high data rate wireless sensor networks," *In Proceedings of the IEEE International Symposium on Signal Processing and Information Technology*, pp. 214-219, Dec. 2007.

- [44] Li Pengfei, R. Bashirullah, "A wireless power interface for rechargeable battery operated medical implants," *IEEE Transactions on Circuits and Systems II: Express Briefs*, vol. 54, issue 10, pp. 912-916, Oct. 2007.