# Étude et optimisation de l'interaction processeurs-architectures reconfigurables dynamiquement

Ben Abdallah Faten

#### ▶ To cite this version:

Ben Abdallah Faten. Étude et optimisation de l'interaction processeurs-architectures reconfigurables dynamiquement. Micro et nanotechnologies/Microélectronique. Université Rennes 1, 2009. Français. NNT: . tel-00438608

# HAL Id: tel-00438608 https://theses.hal.science/tel-00438608

Submitted on 4 Dec 2009

HAL is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

$N^{\circ}$  d'ordre : 3539

d'accueil:

## THÈSE présentée

### DEVANT L'UNIVERSITÉ DE RENNES 1 pour obtenir

DOCTEUR DE L'UNIVERSITÉ DE RENNES 1 le grade de: Traitement du Signal et Télécommunications Mention:

> par Faten BEN ABDALLAH MANAI

Équipe Institut de Recherche en Informatique et Systèmes Aléatoires - CAIRN

École Mathématiques, Télécommunications, Informatique,

Doctorale: Signal, Systèmes et Électronique

Composante Universitaire : École Nationale Supérieure de Sciences Appliquées et de Technologie

# **ÉTUDE ET OPTIMISATION DE L'INTERACTION** PROCESSEURS-ARCHITECTURES RECONFIGURABLES DYNAMIQUEMENT

Soutenue LE 20 octobre 2009 devant la commission d'Examen

#### **COMPOSITION DU JURY:**

Président du Jury :

Guy GOGNIAT Professeur des Universités Université de Bretagne Sud

Rapporteurs:

Professeur des Universités Michel PAINDAVOINE Université de Bourgogne

Professeur des Universités Ridha BOUALLEGUE Université du 7 novembre Carthage

Examinateurs:

Maitre de Conférences Sébastien PILLEMENT Université de Rennes 1 Olivier SENTIEYS Professeur des Universités Université de Rennes 1 Université de Tunis ElManar Ammar BOUALLEGUE Professeur des Universités

C'est avec mon enthousiasme le plus vif et le plus sincère que je voudrais rendre hommage à tous ceux qui, à leurs manières, m'ont aidé à mener à bien cette thèse.

Je tiens tout d'abord à remercier mon directeur de thèse M. Olivier SENTIEYS, professeur à l'Université de Rennes 1, pour m'avoir accueilli au sein de son équipe de recherche et pour m'avoir fait découvrir et partager ses visions scientifiques. Je tiens à le remercier vivement pour sa sympathie, sa compréhension et le temps qu'il m'a consacré malgré ses charges nombreuses.

Mes remerciements vont également à mon directeur de thèse M. Ammar BOUALLEGUE, professeur à l'Université de Tunis El Manar, pour avoir accepté de me diriger et pour tous les conseils avisés qu'il m'a prodigués. Outre ses qualités scientifiques, j'ai beaucoup apprécié sa générosité et sa gentillesse hors pair.

Je tiens à exprimer ma profonde reconnaissance à M. Sébastien PILLEMENT, maitre de conférences à l'Université de Rennes 1, pour son encadrement précieux, ses encouragements et ses coups de booster qui ont favorisé le développement de cette thèse. Je le remercie sincèrement pour sa disponibilité et son suivi attentif de mes travaux, pour son esprit critique et pour sa convivialité.

Ma reconnaissance va aux membres du Jury pour avoir répondu volontiers et chaleu-

reusement présents et pour m'avoir fait l'honneur de participer à ma soutenance. Un merci particulier s'adresse à Monsieur Guy GOGNIAT, d'avoir accepté la présidence du jury. Sa participation est, pour moi, un honneur.

Je suis reconnaissante envers notamment Messieurs Michel PAINDAVOINE et Ridha BOUALLEGUE pour le temps qu'ils ont consacré à rapporter mes travaux et les différentes remarques et suggestions qu'ils ont faites.

Mes remerciements chaleureux vont aussi à toutes les personnes avec qui j'ai été amenée à discuter et à valider mes travaux de recherche et plus particulièrement, aux membres du groupe de travail CAIRN au sein de l'ENSSAT.

Une pensée particulière s'adresse à tous les amis qui ont contribué, de près ou de loin, à rendre mes séjours plus agréables et enrichissants ainsi que tout le personnel de l'ENSSAT et de l'ENIT pour le suivi pédagogique de ma thèse.

J'adresse toute mon affection à ma famille pour son amour, sa tendresse et ses encouragements depuis de nombreuses années. J'ai une pensée très tendre et très reconnaissante à l'égard de mes parents pour leur apport quotidien à la réalisation de ce travail. Ils m'ont toujours donné l'espoir d'aller de l'avant.

Le dernier et non le moindre des mercis, je le dédie à mon époux. Nejah les mots me manquent pour vous remercier. Grâce à vous, je suis non seulement une meilleure scientifique, mais je me considère aussi une meilleure femme.

# Table des matières

| In                           | trod                         | uction  |                 |                                                             | 1  |

|------------------------------|------------------------------|---------|-----------------|-------------------------------------------------------------|----|

|                              | Con                          | texte d | le l'étude      |                                                             |    |

|                              | Pro                          | blémati | ique de l'étude |                                                             |    |

|                              | Contributions                |         |                 |                                                             | 4  |

|                              | Plar                         | n du me | émoire .        |                                                             | 5  |

| Ι                            | Eta                          | t de l' | art             |                                                             | 7  |

|                              | A                            | Parad   | ligme des       | systèmes hybrides reconfigurables                           | 8  |

|                              |                              | A.1     | Reconfi         | guration dynamique                                          | 10 |

|                              |                              |         | A.1-1           | Reconfiguration dynamique totale                            | 10 |

|                              |                              |         | A.1-2           | Reconfiguration dynamique partielle                         | 11 |

|                              |                              |         | A.1-3           | Mécanismes d'optimisation de la reconfiguration dynamique . | 13 |

|                              |                              | A.2     | Granula         | arité de l'architecture reconfigurable dynamiquement        | 15 |

|                              | A.3 Critères de performances |         |                 | 18                                                          |    |

|                              |                              |         | A.3-1           | Accélération des traitements                                | 19 |

|                              |                              |         | A.3-2           | Consommation d'énergie                                      | 19 |

| B Intégration architecturale |                              |         | hitecturale     | 21                                                          |    |

|                              |                              | B.1     | Unité P         | eriphérique Reconfigurable                                  | 23 |

|                              |                              | B.2     | Unité re        | econfigurable en couplage point-à-point                     | 25 |

|                                                                    |              | B.3                                              | Coproce                             | sseur reconfigurable                                                 | 27 |

|--------------------------------------------------------------------|--------------|--------------------------------------------------|-------------------------------------|----------------------------------------------------------------------|----|

|                                                                    |              | B.4                                              | Unité fonctionnelle reconfigurable  |                                                                      |    |

|                                                                    | $\mathbf{C}$ | Bilan o                                          | an qualitatif des systèmes hybrides |                                                                      |    |

|                                                                    |              | C.1                                              | Outils e                            | t méthodes de développement                                          | 33 |

|                                                                    |              | C.2                                              | Aspect a                            | architectural                                                        | 39 |

|                                                                    | D            | Synthè                                           | ese                                 |                                                                      | 4  |

| II                                                                 | Mod          | lélisati                                         | on des a                            | architectures hybrides reconfigurables                               | 43 |

|                                                                    | A            | Modèl                                            | es consid                           | érés                                                                 | 44 |

|                                                                    |              | A.1                                              | Modélis                             | ation de l'application                                               | 44 |

|                                                                    |              | A.2                                              | Paramèt                             | res du modèle                                                        | 46 |

|                                                                    |              |                                                  | A.2-1                               | Paramètres applicatifs                                               | 46 |

|                                                                    |              |                                                  | A.2-2                               | Paramètres architecturaux                                            | 46 |

|                                                                    |              |                                                  | A.2-3                               | Paramètres algorithmiques                                            | 48 |

|                                                                    |              | A.3                                              | Métriqu                             | es de performances                                                   | 48 |

|                                                                    |              |                                                  | A.3-1                               | Accélération apportée par l'architecture hybride                     | 49 |

|                                                                    |              |                                                  | A.3-2                               | Taux de réduction de la puissance dissipée et efficacité énergétique | 51 |

| B Modélisation de la communication dans une architecture hybride . |              | e la communication dans une architecture hybride | 52                                  |                                                                      |    |

|                                                                    |              | B.1 Lois de communication                        |                                     | communication                                                        | 53 |

|                                                                    |              |                                                  | B.1-1                               | Latence de communication                                             | 53 |

|                                                                    |              |                                                  | B.1-2                               | Dissipation de puissance due aux communications                      | 55 |

|                                                                    |              | B.2                                              | * *                                 | cion des lois de communication aux architectures hybrides reables    | 58 |

|                                                                    |              |                                                  | B.2-1                               | Unité Fonctionnelle Reconfigurable Dynamiquement                     | 58 |

|                                                                    |              |                                                  | B.2-2                               | Coprocesseur Reconfigurable Dynamiquement                            | 60 |

|                                                                    |              |                                                  | B.2-3                               | Périphérique Reconfigurable Dynamiquement                            | 62 |

|                                                                    |              |                                                  | B.2-4                               | Couplage Point-à-Point Reconfigurable Dynamique-ment                 | 65 |

|                                                                    | $\mathbf{C}$ | Valida                                           | tion du n                           | nodèle                                                               | 65 |

|                                                                    | D            | Synthè                                           | ese                                 |                                                                      | 68 |

|                                                                    |              |                                                  |                                     |                                                                      |    |

69

IIIMéthodologies d'optimisation des architectures hybrides reconfigurables

| A               | Méthodologie d'Adéquation Algorithme Ar-chitecture Hybride AAAH |                                                                                           |                                                                                                |     |  |

|-----------------|-----------------------------------------------------------------|-------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|-----|--|

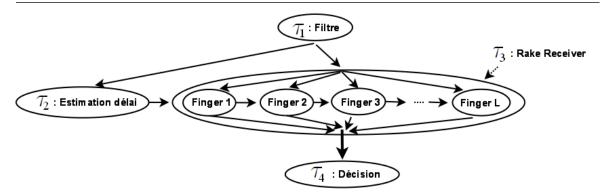

|                 | A.1                                                             | Exempl                                                                                    | le d'application de la méthodologie AAAH                                                       | 71  |  |

|                 |                                                                 | A.1-1                                                                                     | Présentation générale de WCDMA                                                                 | 71  |  |

|                 |                                                                 | A.1-2                                                                                     | Étude du portage du <i>Rake Receiver</i> dynamique sur une architecture hybride reconfigurable | 73  |  |

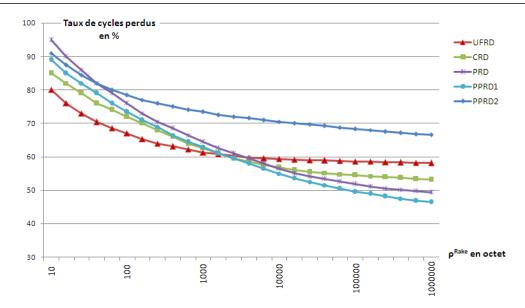

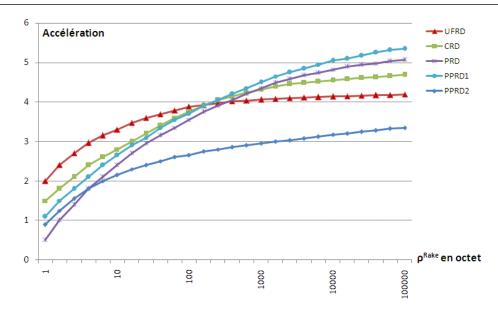

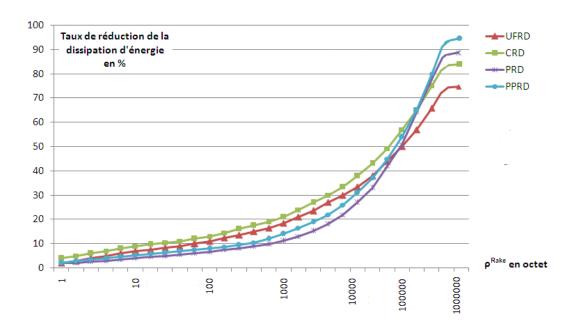

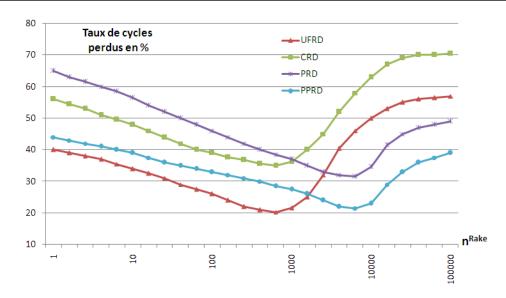

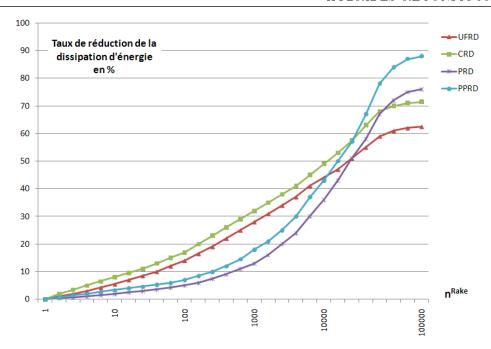

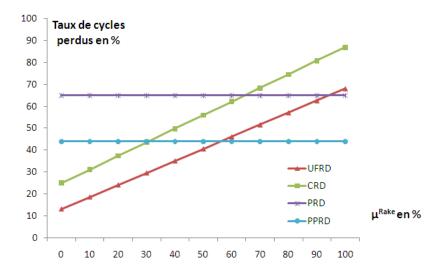

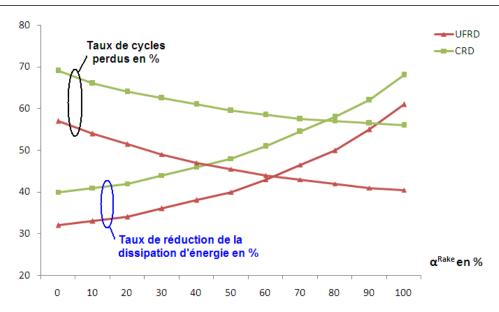

|                 | A.2                                                             | •                                                                                         | des paramètres applicatifs et algorithmiques sur les perford'une architecture hybride          | 75  |  |

|                 |                                                                 | A.2-1                                                                                     | Choix du couplage en fonction des paramètres applicatifs                                       | 75  |  |

|                 |                                                                 | A.2-2                                                                                     | Choix du couplage en fonction des paramètres algorithmiques                                    | 80  |  |

| В               |                                                                 | Méthodologie d'optimisation de la reconfiguration dynamique dans une architecture hybride |                                                                                                |     |  |

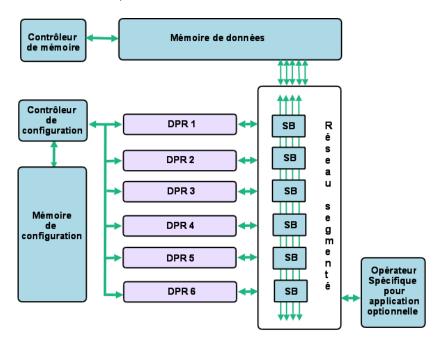

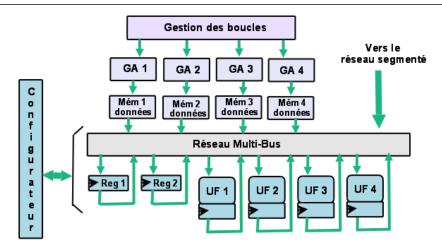

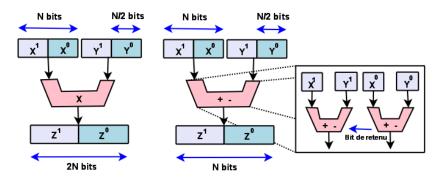

|                 | B.1                                                             | Archite                                                                                   | cture DART                                                                                     | 83  |  |

|                 |                                                                 | B.1-1                                                                                     | Présentation Générale de l'architecture                                                        | 83  |  |

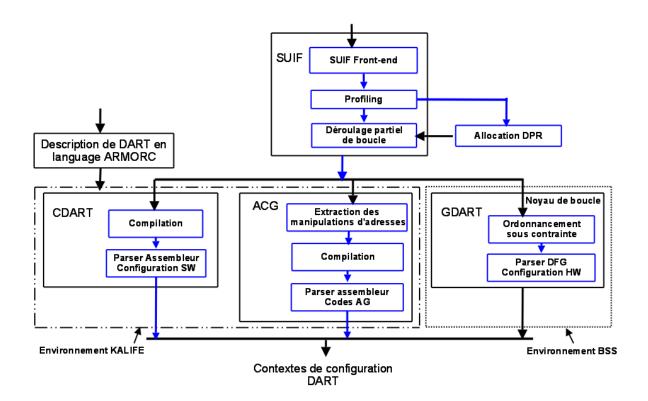

|                 |                                                                 | B.1-2                                                                                     | Le flot de conception de DART                                                                  | 87  |  |

|                 | B.2                                                             | Formulation de la problématique et présentation de la méthodologie . 89                   |                                                                                                |     |  |

|                 | B.3                                                             | B.3 Intégration de la méthodologie dans le flot de compilation d'une tecture hybride      |                                                                                                |     |  |

| С               | Synth                                                           | ièse                                                                                      |                                                                                                | 95  |  |

| IV Va           | lidatio                                                         | n                                                                                         |                                                                                                | 97  |  |

| A               | Présentation et analyse du système DVB-T/H                      |                                                                                           |                                                                                                |     |  |

|                 | A.1                                                             | Système                                                                                   | e DVB-T/H                                                                                      | 98  |  |

|                 | A.2                                                             | Analyse                                                                                   | e du démodulateur DVB-T/H                                                                      | 102 |  |

|                 | A.3                                                             | Portage                                                                                   | e du démodulateur DVB-T/H sur le cluster DART $\dots$                                          | 104 |  |

|                 |                                                                 | A.3-1                                                                                     | Mapping de la phase acquisition sur le cluster DART                                            | 105 |  |

|                 |                                                                 | A.3-2                                                                                     | Mapping de la phase "tracking" sur le cluster DART                                             | 109 |  |

| В               | Appli                                                           | Application de la méthodologie AAAH                                                       |                                                                                                |     |  |

|                 | B.1                                                             | Détermination des lois de communication                                                   |                                                                                                |     |  |

|                 | B.2                                                             | Déterm                                                                                    | ination de l'accélération et du taux de réduction d'énergie                                    | 117 |  |

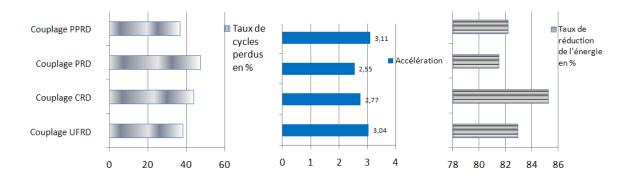

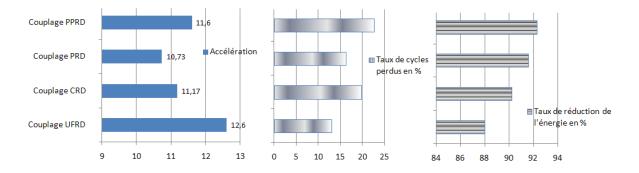

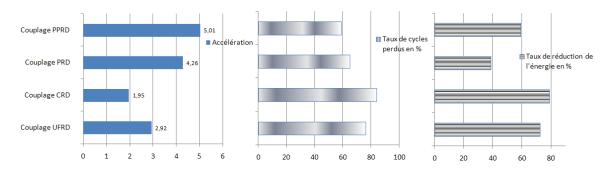

|                 |                                                                 | B.2-1                                                                                     | Application des modèles de couplage à la phase "acquisition"                                   | 119 |  |

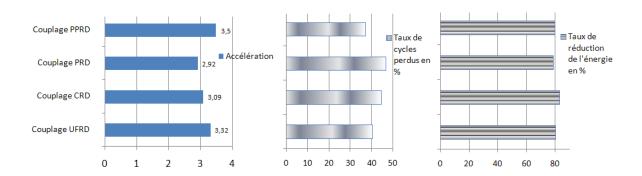

|                 |                                                                 | B.2-2                                                                                     | Application des modèles de couplage à la phase " $tracking$ " .                                | 127 |  |

| $^{\mathrm{C}}$ | Optin                                                           | nisation d                                                                                | le l'implémentation                                                                            | 130 |  |

| D       | Résultats de l'implémentation d'un démodulateur DVB-T/H multi-mode | 133 |

|---------|--------------------------------------------------------------------|-----|

| E       | Synthèse                                                           | 137 |

| Concl   | usions et perspectives                                             | 139 |

| Syn     | thèse des travaux                                                  | 139 |

| Pers    | spectives                                                          | 141 |

| Bibliog | graphie                                                            | 143 |

| Glossa  | ire                                                                | 155 |

#### CONTEXTE DE L'ÉTUDE

L'évolution des réseaux de télécommunications a permis, grâce à d'importants débits, l'apparition de nouveaux services orientés Traitement Du Signal et des Images (TDSI). Ces applications sont essentiellement orientées vers le traitement de flots de données et ont vu leurs besoins (notamment en termes de puissance de calcul) suivre une progression très importante, impliquant un volume important d'opérations arithmétiques à réaliser en temps réel.

Conjointement à l'évolution des normes de télécommunications, les concepteurs de circuits intégrés ont vu les capacités d'intégration des circuits augmenter de façon considérable leur offrant alors des possibilités d'implémentation de système complet sur une puce SOC pour (System On Chip). Le système sur puce est une solution technologique dédiée à l'intégration sur un même substrat de silicium d'un ensemble de composants de natures hétérogènes.

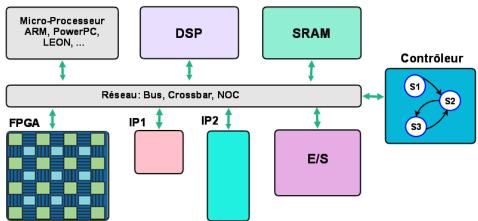

Un exemple de SoC hétérogène est présenté sur la figure 0-1 où chaque macro-bloc réalise une fonction spécifique. Généralement, le microprocesseur est chargé de la gestion des différentes tâches de l'application, le DSP (Digital Signal processor) est responsable de décharger le microprocesseur en assurant le traitement des motifs de calculs liés aux traitements du signal. Les composants spécifiques ASIC (Application Specific Integrated Circuits), intégrant des IP (Intellectual Property), sont mis en œuvre pour traiter efficacement les fonctions critiques (chronophages). Enfin, les composants re-

configurables de type Field Programmable Gate Array, FPGA assurent au circuit des possibilités d'évolution en redéfinissant complètement, ou partiellement, des caractéristiques de son architecture. La mémoire assure le stockage des données de l'application. La communication entre les différents composants du système est assurée par un réseau d'interconnexions (bus, bus hiérarchiques, crossbar, NoC (Network on Chip)...).

# Système sur Puce (SOC)

Figure 0-1 – Exemple d'un système sur puce (SOC) hétérogène. Le microprocesseur est chargé de l'agencement des différentes tâches de l'application. Le DSP est responsable de décharger le microprocesseur en assurant le traitement des motifs de calculs liés au traitement du signal. Les IP, sont mis en œuvre pour traiter efficacement les fonctions critiques et les composants reconfigurables de type FPGA assurent au circuit des possibilités d'évolution en redéfinissant complètement, ou partiellement, des caractéristiques de son architecture. La mémoire assure le stockage des données de l'application. La communication entre les différents composants du système est assurée par un réseau d'interconnexions (bus, bus hiérarchiques, crossbar, NoC...)

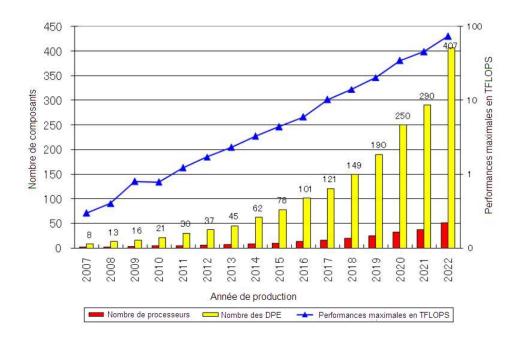

L'ITRS (International Technology Roadmap for Semiconductors) [1] prévoit que les performances de calcul des SoC pour les applications embarquées vont être multipliées par 100 entre 2009 et 2022 avec des besoins en puissance de calcul pouvant dépasser en 2022 les 70 TFLOPS. La croissance des besoins en puissance de calcul est soutenue par l'augmentation du nombre de processeurs et de composants calculatoires DPE (Data Processing Engine) dans le SoC (Figure 0-2).

La combinaison de ces deux évolutions (puissance de calcul et capacité d'intégration) place les concepteurs devant une multitude de solutions architecturales créant un espace de recherche de conception très grand.

D'autre part, les nouvelles contraintes de l'embarqué nécessitent d'autres caractéristiques du SoC tout aussi contraignantes. Les plus communes parmi celles ci sont le

Figure 0-2 – **Prévisions des performances de calcul des SoC [1]**. Les performances de calcul des SoC pour les applications embarquées vont être multipliées par 100 entre 2009 et 2022 avec des besoins en puissance de calcul pouvant dépasser en 2022 les 70 TFLOPS. La croissance des besoins de calcul est soutenue par l'augmentation du nombre des processeurs et des composants calculatoires DPE dans les SoC.

faible coût du circuit et la nécessité de concevoir des circuits ayant une faible consommation d'énergie.

## PROBLÉMATIQUE DE L'ÉTUDE

Dans le domaine des télécommunications si les SoC, tel que représentés sur la figure 0-1, sont parfaitement adaptés aux traitements des réseaux de télécommunications actuels, il en est tout autrement pour les réseaux de télécommunications futurs. En effet, la diversité des traitements devant être implantés impose l'intégration d'un très grand nombre de blocs dédiés. Le coût de ces systèmes devient dès lors très prohibitif, d'autant plus que la faible flexibilité des systèmes dédiés restreint leur durée de vie. Afin de pouvoir supporter les exigences des normes actuelles et futures, de nouvelles solutions architecturales ont vu le jour : les architectures hybrides reconfigurables. Il s'agit d'utiliser conjointement des processeurs d'usage général ou spécifiques, dont les performances atteignent aujourd'hui des niveaux très élevés (en million d'opérations

par seconde (MOPS) mais aussi en fonctionnalités d'entrées-sorties), et un ou plusieurs circuits reconfigurables dynamiquement. La reconfiguration dynamique permet de modifier, en cours d'exécution, partiellement ou complètement la fonctionnalité (sa configuration) du circuit.

Le besoin de caractérisation de ces architectures est alors important afin que le concepteur puisse identifier, suivant un certain nombre de critères, l'architecture en adéquation avec son domaine applicatif. Nous détaillons ci-après quelques challenges liés à ce domaine.

Quels sont les mécanismes qui permettent un échange optimal d'informations entre le processeur et l'ARD (Architecture Reconfigurable Dynamiquement)?

Comme les architectures hybrides reconfigurables se révèlent être une alternative pour l'accélération des applications TDSI, que peut-on espérer de l'amélioration des performances? Peut-on définir des métriques mesurant cette accélération? Existe-t-il une limite architecturale ou algorithmique à l'accélération?

Si ce type d'architectures permet une réduction de l'énergie dissipée par rapport à celle dissipée par le traitement sur le processeur seul, peut-on avoir une mesure quantitative de cette réduction? Si une application doit être implémentée sur ce type d'architectures, existe-t-il une méthode pour identifier les tâches qui doivent êtres mappées sur le composant reconfigurable dynamiquement ainsi que l'ordonnancement de leur exécution?

#### CONTRIBUTIONS

C'est à la problématique développée ci-dessus que nous nous proposons de répondre dans cette thèse.

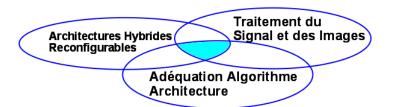

Le contexte de l'étude regroupe trois axes de recherche représentés à la figure 0-3 : le traitement du signal et des images, l'adéquation algorithme architecture et les architectures hybrides reconfigurables. Nos travaux se situent à l'intersection de ces trois axes.

Dans ce contexte, une première étape dans nos travaux est de proposer une méthodologie d'exploration de l'espace de conception des architectures hybrides reconfigurables. La conception des systèmes hybrides souffre de l'absence de modèles et de méthodes capables de quantifier leurs performances. Pour cela, nous avons développé des modèles flexibles et paramétrables pour les architectures hybrides reconfigurables ainsi que des

Figure 0-3 – Contexte de l'étude. Nos travaux se situent a l'intersection du traitement du signal et des images, de l'adéquation algorithme architecture et des architectures hybrides reconfigurables.

modèles d'estimation précis de leurs performances.

Par ailleurs, nous proposons une méthodologie d'adéquation algorithme architecture hybride (AAAH) qui permet de déterminer, pour une application donnée, le modèle de couplage CPU-architecture reconfigurable dynamiquement optimal.

En outre, nous proposons une méthodologie permettant d'exploiter efficacement les possibilités de reconfiguration dynamique. Nous intégrons cette méthodologie dans le flot de compilation d'une architecture hybride comportant le circuit reconfigurable dynamiquement DART conçu au sein de notre équipe de recherche.

Nous avons validé nos méthodologies par l'implémentation d'une application de calcul intensif : un démodulateur DVB-T/H multi-mode (c'est à dire basculant d'une configuration à une autre suivant les caractéristiques du canal de transmission et de l'état de la charge de la batterie) sur une architecture hybride couplant un cluster reconfigurable dynamiquement DART et un processeur de traitement de signal, le TMS320C6713.

#### PLAN DU MÉMOIRE

Le premier chapitre de ce document présente les systèmes hybrides reconfigurables. En explorant l'espace de conception de ces architectures, nous dressons un bilan qualitatif en mettant le point sur les paramètres ayant un impact sur les performances de ces systèmes. Ce chapitre commence par définir les concepts sous-jacent de ces architectures et montre les points d'intérêts des architecture reconfigurable dynamiquement. Le chapitre II est consacré à la modélisation des architectures hybrides reconfigurables. Nous développons dans un premier temps les modèles d'estimation de leurs

performances; Ensuite nous présentons un modèle de communication processeur - architecture reconfigurable dynamiquement permettant de représenter leurs comportements réalistes pour chaque type de couplage.

Au sein du troisième chapitre, une méthodologie d'adéquation algorithme architecture hybride est proposée. Cette méthodologie permet de déterminer, pour une application donnée, le modèle de couplage CPU-ARD optimal. Dans ce chapitre, nous montrons la généricité de notre méthode en l'appliquant à une implémentation d'un décodeur WCDMA (Wideband Code Division Multiple Access) sur un cluster reconfigurable dynamiquement de l'architecture DART.

Ce chapitre présente ensuite une méthodologie d'optimisation de l'implémentation sur l'architecture, visant à exploiter de façon optimale la reconfiguration dynamique. Cette méthodologie exploite les modèles d'estimation de performances démontrés dans le chapitre II.

La validation des approches proposées fait l'objet du quatrième chapitre où sont exposés les résultats de l'implémentation d'un démodulateur DVB-T/H multimode sur une architecture hybride reconfigurable composée d'un cluster reconfigurable dynamiquement DART et d'un DSP TMS320C6713. Ce démodulateur DVB-T/H permet de passer d'un mode DVB-T/H à un autre permettant d'accommoder la fiabilité et l'efficacité énergétique aux conditions de transmission du signal.

Finalement, en conclusion, nous effectuons une synthèse des contributions de ce travail de recherche et proposons différentes perspectives possibles.

#### CHAPITRE

# ETAT DE L'ART

#### Sommaire

| Jonnane      |                              |                                                                 |  |  |  |

|--------------|------------------------------|-----------------------------------------------------------------|--|--|--|

| A            | Par                          | Paradigme des systèmes hybrides reconfigurables 8               |  |  |  |

|              | A.1                          | Reconfiguration dynamique                                       |  |  |  |

|              | A.2                          | Granularité de l'architecture reconfigurable dynamiquement . 15 |  |  |  |

|              | A.3                          | Critères de performances                                        |  |  |  |

| $\mathbf{B}$ | B Intégration architecturale |                                                                 |  |  |  |

|              | B.1                          | Unité Périphérique Reconfigurable                               |  |  |  |

|              | B.2                          | Unité reconfigurable en couplage point-à-point 25               |  |  |  |

|              | B.3                          | Coprocesseur reconfigurable                                     |  |  |  |

|              | B.4                          | Unité fonctionnelle reconfigurable                              |  |  |  |

| C            | ${f Bila}$                   | an qualitatif des systèmes hybrides                             |  |  |  |

|              | C.1                          | Outils et méthodes de développement                             |  |  |  |

|              | C.2                          | Aspect architectural                                            |  |  |  |

| $\mathbf{D}$ | Syn                          | thèse                                                           |  |  |  |

|              |                              |                                                                 |  |  |  |

Les architectures hybrides reconfigurables ("Reconfigurable Computing" en terminologie anglo-saxone) [2] se révèlent être des plate-formes particulièrement adaptées pour les applications embarquées qui combinent du contrôle et du calcul intensif. Ces plate-formes comprennent des unités de calculs logicielles (processeurs généralistes, DSP (Digital Signal Processor), microcontrôleur, etc.) et matérielles (unités de calcul reconfigurables, IP, etc.).

Dans ce chapitre, nous introduisons les systèmes hybrides reconfigurables et nous examinons l'espace de conception de ces architectures. A travers l'état de l'art des systèmes hybrides, nous dressons un bilan qualitatif en mettant le point sur les paramètres ayant un impact sur les performances de ces systèmes.

# A PARADIGME DES SYSTÈMES HYBRIDES RECONFIGU-RABLES

Les processeurs possèdent un paradigme de calcul se basant sur une implémentation temporelle des traitements qualifiée de logicielle (ou "Software"). Ils utilisent un faible nombre de ressources de calcul (en général une UAL (Unité Arithmétique et Logique)) qui sont réutilisés dans le temps, et présentent donc l'avantage d'occuper peu de surface de silicium au détriment de leur performance en temps et en consommation d'énergie.

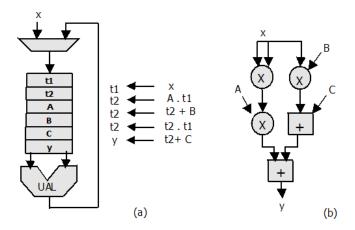

A l'inverse les implémentations spatiales sont réalisées sur des architectures qualifiées de matérielles (ou "Hardware") dans lesquelles chaque opérateur existe en différents points de l'espace et traite des opérandes directement câblées sur ses entrées. Ainsi, les différentes opérations à effectuer ne sont pas réalisées de manière séquentielle comme dans le cas de l'implémentation temporelle, mais de manière parallèle. Ces architectures présentent l'avantage d'être performantes en temps et en consommation d'énergie, au détriment d'une surface de silicium plus importante et d'une flexibilité inexistante. Le schéma de Horner (Figure 1-1) explicite le principe des implémentations temporelle et spatiale de l'équation de second degré  $y = A \times X^2 + B \times X + C$ .

Figure 1-1 – Exemple d'une implémentation temporelle (a) et spatiale (b) d'une équation second degré :  $y = A \times X^2 + B \times X + C$ . Dans le cas d'une implémentation temporelle, une ressource de calcul unique est partagée dans le temps entre les différentes opérations. A l'inverse, pour une implémentation spatiale, les opérations sont assignées à des opérateurs existants en différents points de l'espace.

Le concept sur lequel repose les architectures hybrides consiste à mixer les implémentations spatiales et temporelles. Une implémentation logicielle d'une partie de l'application possède l'avantage de lui procurer une flexibilité liée à la possibilité de re-programmation, contrairement à une implémentation matérielle figée mais qui a l'avantage de satisfaire plus facilement les contraintes de performances. La flexibilité est mieux exploitée quand la partie matérielle est une architecture reconfigurable. En effet, un circuit reconfigurable dispose de mécanismes matériels capables de redéfinir complètement, ou partiellement, les caractéristiques de l'architecture qu'elle implémente. Chaque configuration temporelle distincte est appelée contexte de reconfiguration. Un processus appelé "reconfiguration", consistant à charger un nouveau contexte dans l'unité reconfigurable, permet de changer sa fonctionnalité, ce qui permet d'implémenter efficacement différents traitements à des instants disjoints.

#### Deux types de reconfiguration existent :

- la reconfiguration statique CTR pour (Compile-Time Reconfiguration): où chaque application consiste en une ou plusieurs configurations (contextes). Pour reconfigurer un tel système, on doit l'interrompre pour procéder à sa reconfiguration et le redémarrer avec la nouvelle configuration. La reconfiguration statique peut être totale, c'est-à-dire que le contexte occupe la totalité des ressources matérielles du circuit, ou partielle dans le cas où les composants permettent de reconfigurer sélectivement une zone du circuit alors que le reste du système reste inactif tout en conservant ses informations de configuration. Le temps de reconfiguration dans ce cas dépend de la surface en termes d'éléments logiques du contexte à reconfigurer.

- la reconfiguration dynamique RTR pour (Run-Time Reconfiguration): où les phases de reconfiguration et d'exécution sont concurrentes. Ceci permet un gain considérable en temps de traitement par rapport à la reconfigurabilité statique. Par contre l'association d'une architecture reconfigurable dynamiquement avec un processeur nécessite des mécanismes plus sophistiqués pour la gestion des flux de reconfiguration.

Cette thèse se place plus particulièrement dans le cas des architectures reconfigurables dynamiquement. En effet, afin de répondre à l'ensemble des contraintes inhérentes aux applications de télécommunications actuelles et futures, à savoir la flexibilité, la haute performance et la faible consommation d'énergie, les architectures hybrides intègrent des circuits reconfigurables dynamiquement.

On parle alors de RSoC pour (*Reconfigurable Systems on Chip*) qui sont des systèmes hybrides reconfigurables sur une même puce. Ils combinent des cœurs de processeur, des blocs de mémorisation, des modules d'entrée/sortie I/O, ainsi que des blocs recon-

figurables sur un même substrat reliés par un réseau d'interconnexion. La différence majeure entre l'architecture d'un RSoC et celle d'un système sur puce classique réside dans la présence, au sein même du RSOC, d'une architecture reconfigurable dynamiquement.

Comme son intégration dans une architecture hybride s'avère intéressante en termes de performances et de coût de circuit, le circuit reconfigurable est souvent nommé "accélérateur". Il est caractérisé par la granularité de son chemin de données et par le type de sa reconfiguration dynamique. L'interaction entre le processeur CPU (CPU: Central Processing Unit) et l'architecture reconfigurable dynamiquement dépend étroitement de ces deux paramètres.

Nous montrerons dans ce qui suit la manière dont les caractéristiques du circuit reconfigurable affecte la conception des architectures hybrides reconfigurables.

#### A.1 Reconfiguration dynamique

Nous distinguons deux modes de reconfiguration dynamique selon la manière de construire les contextes, total ou partiel, qui sont introduits dans les sous-sections suivantes.

#### A.1-1 RECONFIGURATION DYNAMIQUE TOTALE

Pour la reconfiguration dynamique totale (*Global RTR* en terminologie anglo-saxone), chaque application est divisée en un ensemble de contextes de reconfiguration dont chacun occupe la totalité des ressources matérielles du composant.

Tout changement de contexte implique la reconfiguration totale du composant. Un plan de configuration unique peut être actif à un certain moment sur le circuit reconfigurable, mais le passage à un autre plan (on parle de multi-contexte) peut être très rapide (de l'ordre de quelques nano-secondes). Par exemple, le projet de recherche industriel de NEC [3], basé sur le principe de multiplexage temporel, affiche des temps de reconfiguration de l'ordre de 5 à 30 nano-secondes.

Afin d'assurer la superposition entre les phases de calcul et de reconfiguration, le futur contexte à traiter est pré-chargé. Dans ce sens, des architectures comme GARP [4] et CS 2000 [5] ont opté pour l'utilisation de la notion de cache de reconfiguration. Le cache de configuration consiste à stocker un nombre de configurations dans des mémoires (généralement en mémoire locale du composant) et de changer de contexte pendant l'exécution en un temps comparativement très faible par rapport à un chargement de

contexte à partir d'une mémoire externe. L'architecture CS2000 par exemple, possède un cache permettant de stocker une configuration et de reconfigurer le composant à partir de ce cache en un seul cycle. Le rapprochement entre les données de configuration et la ressource reconfigurable permet ainsi de réduire le temps de reconfiguration. Les performances sont alors nettement améliorées mais ceci se paie par une augmentation de la surface de silicium et de la consommation d'énergie.

#### A.1-2 RECONFIGURATION DYNAMIQUE PARTIELLE

Dans le mode de reconfiguration dynamique partielle (*Local RTR* en terminologie anglosaxone), on reconfigure sélectivement une zone du composant, ce qui réduit considérablement le temps de reconfiguration.

Cette approche permet de reconfigurer une zone de l'architecture pendant que le reste du composant poursuit son fonctionnement. Elle est basée sur le concept de "matériel virtuel" qui est similaire à l'idée de mémoire virtuelle. Plusieurs contextes peuvent être actifs à la fois sur le composant selon le nombre de zones actives. Le temps de reconfiguration d'un contexte sur une zone de ce composant est masqué par l'exécution d'un autre contexte sur une autre zone. Afin de réduire la latence de reconfiguration totale, la notion de différence est appliquée lorsque les changements à faire entre l'ancienne et la nouvelle configuration sont minimes. Dans ce cas, on charge dans le composant un bitstream correspondant à la différence entre les deux versions, ce qui réduit le temps de reconfiguration.

Cette approche a été utilisée par la famille Virtex II pro de Xilinx [6]. L'organisation générale consiste en une matrice de CLBs (Configurable Logic Block) structurée en colonnes intercalées avec des colonnes de blocs dédiés (mémoire BlockRAM, des blocs DSP, des cœurs de processeurs) et entourée par des blocs d'entrée/sortie programmables. La reconfiguration dynamique est basée sur la notion de modules. Cette dernière permet de reconfigurer dynamiquement un module formé d'un minimum de quatre colonnes de slices (sur toute la hauteur du composant) et un maximum allant jusqu'à la largeur totale du composant avec chaque fois des incréments de quatre colonnes. Toutes les ressources logiques (IO-Blocks, ressources de routage, BlockRAM, blocs DSP...) contenues dans la largeur du module considéré font partie de son bitstream.

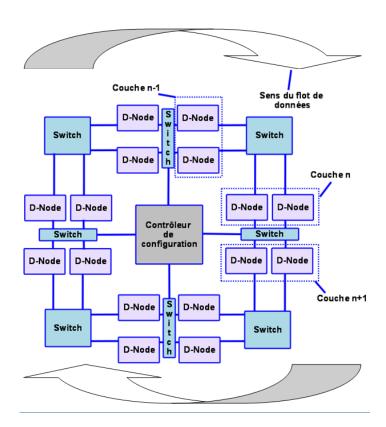

L'architecture Systolic Ring [7], présentée dans la figure 1-2, reprend le principe des FPGA (*Field Programmable Gate Array*) (grain fin), à savoir la présence d'une couche de configuration et d'une couche opérative. La brique de base de la couche opérative

est un composant nommé D-Node. Ce dernier consiste en un multiplieur et une UAL câblés travaillants sur des données de 16 bits stockées dans une file de registre. Le D-Node est apte, contrairement au CLB, à effectuer un éventail d'opérations principalement arithmétiques sur des flots de données. La couche de configuration est, comme pour les FPGA, une mémoire RAM permettant de stocker la configuration de tous les composants de la couche opérative. Une reconfiguration du D-Node est réalisée par une micro-instruction de 17 bits. La particularité ici réside dans la possibilité de modifier le contenu de cette mémoire en cours de traitement (c'est-à-dire de changer la fonctionnalité de tout ou d'une partie du réseau), grâce à l'utilisation d'un contrôleur de configuration.

Figure 1-2 – Systolic Ring est une architecture hybride à reconfiguration dynamique partielle. Elle est composée d'éléments de calcul appelés D-Nodes connectés en anneau. Le flot de données est propagé de D-Node en D-Node après reconfiguration dynamique. La reconfiguration d'un D-Node intervient pendant la phase de traitement des autres D-Node et permet une modification de sa fonctionnalité en un cycle d'horloge.

# A.1-3 MÉCANISMES D'OPTIMISATION DE LA RECONFIGURATION DY-NAMIQUE

Lorsque les phases de reconfiguration se succèdent très rapidement, le temps alloué au chargement du flot de configuration peut ne pas être suffisant pour assurer la dynamicité de la reconfiguration. Il existe différentes techniques pour réduire la latence liée à la reconfiguration dynamique.

Une approche pour réduire cette latence de re-configuration est de réduire le volume du contexte de reconfiguration. Des techniques de compression peuvent être introduites pour diminuer le volume des données de configuration qui doivent être transférées à l'ARD [8] et réduire par conséquent considérablement la taille du cache de reconfiguration et le temps de chargement du contexte. En effet, Atmel a doté les architectures AT40K [9] et AT6000 [10] d'un cache logique associé à un algorithme de compression du bitstream.

Une autre technique pour réduire de manière sensible le volume de données de configuration est de chercher à exploiter le parallélisme de données, c'est-à-dire d'utiliser la même configuration pour plusieurs cellules reconfigurables. Cette technique est exploitée par l'architecture Morphosys [11].

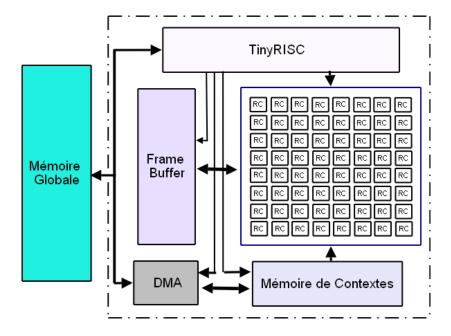

Le bloc reconfigurable est ici un tableau de 8x8 cellules reconfigurables RC (Reconfigurable Cell). Cette architecture est considérée à gros grain puisqu'elle opère sur des données de largeur 8 à 16 bits, bien que chaque RC intègre une unité à grain fin FGB (Fine Grain Bloc) qui est une sorte de petit FPGA opérant au niveau bit. Le circuit reconfigurable est configuré d'une mémoire de contexte contrôlée par un cœur de processeur RISC (Reduced Instruction Set Computer) (Tiny Risc), se chargeant par ailleurs de l'exécution des traitements séquentiels et de la gestion des transferts de données entre la mémoire principale et le bloc reconfigurable. Ces transferts se font par l'intermédiaire d'un contrôleur DMA qui a par ailleurs la charge d'assurer les transferts de données entre la mémoire principale et une mémoire tampon de trame (Frame Buffer) stockant les données manipulées par le bloc reconfigurable.

Puisque cette architecture cible principalement les traitements par blocs disposant d'un parallélisme de données important (par exemple codage d'image ou de vidéo), les configurations des RC varient peu à l'intérieur du tableau. Dès lors, le choix retenu pour Morphosys est de configurer toutes les cellules d'une même ligne ou colonne de la même façon. La figure 1-3 présente la version M2 de l'architecture Morphosys qui a été optimisée pour les applications de télécommunication sans fil.

Une autre approche, présentée dans [12] utilise la notion de pipeline afin que le char-

Figure 1-3 – Architecture bloc de Morphosys (M2). L'ARD, un tableau de cellules reconfigurables, est configuré par une mémoire de contexte contrôlée par un cœur TinyRISC.

gement de la reconfiguration soit chronométré de façon à se chevaucher le plus souvent possible avec les phases d'exécution du circuit.

Finalement, le processus de transfert de données du processeur hôte au matériel reconfigurable peut être modifié de façon à inclure un cache de configuration qui peut fournir une reconfiguration rapide. Par ailleurs, la taille et les caractéristiques de ce cache dépendent essentiellement de la solution du couplage entre le CPU et l'ARD envisagée.

Outre le type de reconfiguration dynamique, l'étude de la granularité du motif de calcul du circuit reconfigurable est primordiale car elle permet de comprendre ses performances potentielles et sa flexibilité et agit par voie de fait sur les choix effectués par les concepteurs des architectures hybrides reconfigurables. L'étude de la notion de la granularité des motifs de calcul des ARD et son impact sur la conception des architectures hybrides fera l'objet de la section suivante.

# A.2 GRANULARITÉ DE L'ARCHITECTURE RECONFIGURABLE DY-NAMIQUEMENT

Par granularité en entend "taille en bits de la donnée élémentaire manipulée". Les architectures à faible granularité, typiquement les FPGAs, manipulent des données de 1 à 4 bits (bien qu'il existe des architectures de FPGA intégrant des multiplieurs sur des mots de 18 bits).

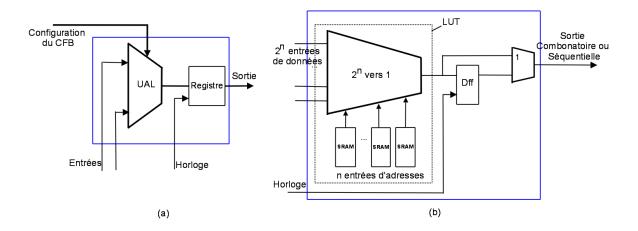

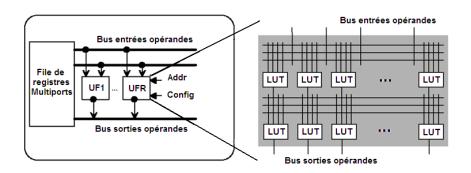

En effet, l'unité fonctionnelle (UF) de base d'une architecture reconfigurable à grain fin est la LUT (Look- $Up\ Table$ ). Il s'agit d'un bloc entièrement combinatoire programmable composé de n entrées  $E_0...E_{n-1}$  d'une sortie et d'un tableau vertical de  $2^n$  cellules mémoires connectées à un multiplexeur  $2^n$  vers 1. La LUT est capable de réaliser toutes les fonctions possibles à n entrées. Pour cela, des cellules mémoires sont programmées selon la table de vérité de la fonction donnée. De plus, afin de permettre la mise en oeuvre des fonctions séquentielles, des bascules D sont intégrées aux éléments de calcul et un multiplexeur situé en sortie de l'élément permet de choisir ou non cette option (figure 1-4 (b)).

Figure 1-4 – Architecture simplifiée d'un élément de calcul d'une architecture reconfigurable à grain épais (a) et à grain fin (b). Le CFB est basé sur au minimum une UAL dont un mot de configuration permet de sélectionner la nature de l'opération à réaliser sur ses entrées. La sortie du CFB est synchronisée par une horloge. L'élément de calcul grain fin est composé d'une ou plusieurs LUT associées à une ou plusieurs bascules. Un multiplexeur permet de choisir la sortie séquentielle ou combinatoire.

Les architectures à gros grain manipulent des unités fonctionnelles à 8 ou 16 bits voire même plus. L'unité fonctionnelle ou l'élément de calcul d'une architecture grain épais est le bloc fonctionnel configurable CFB (Configurable Fonctionnel Bloc). Il est

constitué au minimum d'une UAL et d'un registre de configuration (voir figure 1-4 (a)).

La granularité du bloc reconfigurable joue un rôle primordial pour les concepteurs au niveau des solutions proposées pour la conception d'une architecture hybride.

- Le temps de chargement d'une séquence de reconfiguration (appelée bitstream pour les architectures à grain fin) est directement proportionnel à la taille de la séquence.

Les architectures à gros grain nécessitent des séquences plus courtes que les architectures à grain fin, donc un temps de configuration plus faible.

- Une faible granularité procure une plus grande flexibilité d'adaptation du matériel à la structure de calcul souhaitée. De plus, le grand nombre d'interconnexions entre les unités rajoute un délai conséquent à l'exécution du module implanté (malgré des structures permettant de réduire ce délai, comme les chaînes de propagation de retenue que l'on peut trouver dans les FPGA).

- Les circuits reconfigurables à gros grain utilisent des unités fonctionnelles qui ressemblent à ceux du processeur. Ceci représente donc une bonne opportunité pour le partage de ressources à faible coût avec le processeur.

- Du point de vue de la consommation d'énergie, les composants reconfigurables à grain fin utilisent des ressources de mémorisation locales plus importantes et dissipent donc plus d'énergie que celles à grosse granularité.

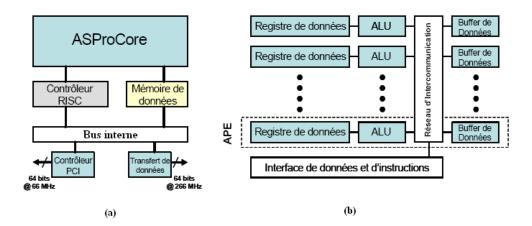

L'architecture lineDancer de Philips [13], une solution architecturale pour la radio logicielle et les applications sans fil, est une architecture hybride couplant un processeur SIMD (Single Instruction Multiple Data) avec une unité reconfigurable grain fin : le ASProCore. L'élément de calcul de base l'APE (Associative Processing Element) exécute la même opération logique ou arithmétique sur un bit. Si nous nous fixons l'APE comme brique de base du composant, la granularité est dans ce cas très fine et si nous considérons un nombre d'APE parallèles correspondants à la largeur du mot à traiter, la granularité est considérée comme adaptative (voir figure 1-5).

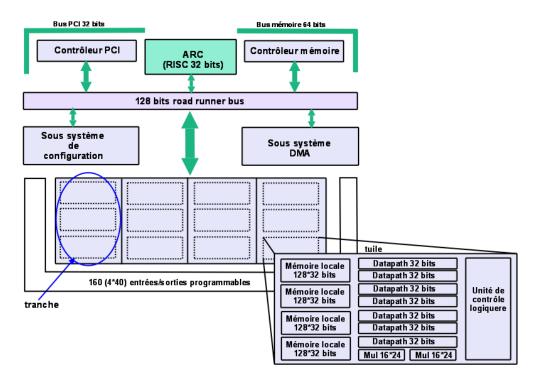

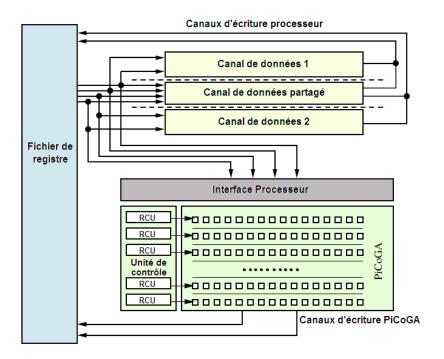

Un exemple d'architecture hybride implémentant des unités reconfigurables à une importante granularité est Chameleon Systems CS2000 [5]. Cette plate-forme intègre un processeur ARC (Advanced RISC Compuing) 32 bits et une unité de calcul reconfigurable RPF (Reconfigurable Processing Fabric) qui opère sur des données de largeur 32 bits. L'unité RPF est organisée en quatre tranches pouvant être reconfigurées indépendamment les unes des autres. Chaque tranche contient trois tuiles qui intègrent chacune sept unités de calcul sur 32 bits, deux multiplieurs 16\*24 bits, quatre mémoires locales et une unité de contrôle logique (figure 1-6).

Afin de supporter la multi-granularité des applications, quelques architectures hybrides

Figure 1-5 – **Architecture du** *LineDancer*. Cette architecture (a) couple un CPU SIMD avec une ARD grain fin le ASProCore. Le ASProCore (b) est composé d'éléments de calcul sur un bit appelés APE.

Figure 1-6 – L'architecture hybride CS2000. Cette architecture opère sur des données de largeur 32 bits. Elle intègre un processeur ARC et une unité de calcul reconfigurable RPF (Reconfigurable Processor fabric). L'unité RPF est organisée en quatre tranches pouvant être reconfigurées indépendamment les unes des autres. Chaque tranche contient trois tuiles qui intègrent.

comportent une architecture reconfigurable avec des unités fonctionnelles de différentes granularité. L'architecture Pleiades [14] conçue dans un souci de faible consommation

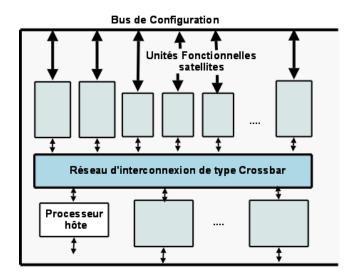

en est un exemple. Elle est basée sur un réseau d'interconnexion de type Crossbar qui relie un processeur hôte et des unités d'exécution de granularités différentes (satellites) ainsi que de la mémoire (figure 1-7). Cette architecture a été exploitée pour les terminaux mobiles 2.5 G et 3 G. En effet, les tâches qui cohabitent au sein d'un système mobile de ces générations manipulent des données de tailles très différentes avec des motifs de calculs et d'accès aux données eux aussi très variés. A titre d'exemple, un codeur source vidéo peut travailler par bloc sur des données arithmétiques peut être suivi d'un codage canal travaillant sur un flot de données binaire.

Figure 1-7 – **Architecture de Pleiade**. Pleiade est une architecture hybride basée sur un réseau d'interconnexion crossbar reliant un processeur hôte et des unités d'exécution de granularités différentes (satellites).

L'objectif des concepteurs des architectures hybrides est d'utiliser au mieux des ressources disponibles de la partie matérielle quel que soit le grain de son motif de calcul et en particulier celle de la reconfiguration dynamique afin de maximiser les performances.

Les performances d'une architecture hybride peuvent être analysées suivant plusieurs critères que nous nous proposons d'expliciter dans la section suivante.

#### A.3 Critères de performances

Afin de pouvoir évaluer les performances d'une architecture hybride reconfigurable, deux critères doivent être considérées : la puissance de calcul nécessaire à l'exécution d'une application et la dissipation d'énergie associée à cette exécution.

#### A.3-1 ACCÉLÉRATION DES TRAITEMENTS

Les besoins de traitement temps réel font que les temps d'exécution sur les architectures considérées doivent être inférieurs ou égaux à ceux imposées par les normes, appelés "contraintes temps réel".

Le temps d'exécution d'un tâche peut s'écrire comme une fonction de la latence L et de la cadence C. Pour un nombre d'échantillons traitées N, le temps d'exécution  $T_{exec}$  d'une tâche s'écrit :

$T_{exec} = L + \frac{N}{C} \tag{1-1}$

La latence L correspond au temps mis par l'architecture entre l'acquisition d'une entrée et la production de la première sortie. La cadence C caractérise le rythme auquel le système produit chacune de ses sorties (le nombre d'échantillons produits par seconde).

Les architectures hybrides trouvent principalement leur utilité dans l'accélération des traitements arithmétiques et logiques par rapport aux performances du processeur seul.

La loi d'Amdahl [15] définit l'accélération (le gain en vitesse d'une tâche) pouvant être obtenu par l'utilisation d'un dispositif d'amélioration donné. L'accélération sera le rapport :

$$Acceleration = \frac{T_{exec} \ sans \ amelioration}{T_{exec} \ avec \ amelioration}$$

(1-2)

La loi d'Amdhal reste incontournable dès qu'il s'agit de s'attaquer à l'optimisation d'un programme car cette loi s'applique dès que des portions de programme s'exécutent en parallèle sur différents processeur ou unités de calcul. La loi d'Amdhal s'exprime alors

$$Accleration = \frac{1}{P_s + \frac{1 - P_s}{N_n}} \tag{1-3}$$

Avec  $P_s$  = pourcentage s'exécutant en mode scalaire et  $P_p$  = pourcentage s'exécutant en parallèle  $(1 - P_s = P_p)$ , et  $N_p$  le nombre de processeurs.

#### A.3-2 Consommation d'énergie

La maîtrise de la consommation d'énergie est un enjeu majeur dans le domaine de l'embarqué. En effet, cette consommation engendre une dissipation thermique qui provoque un vieillissement prématuré des composants, et augmente le coût des systèmes de refroidissement, leur taille ainsi que leur poids constituant un handicap de dimensionnement dans le cas des applications portables.

#### Puissance et énergie dissipée

L'énergie consommée dans un intervalle de temps [a,b] est par définition l'intégrale de la puissance dissipée :  $E=\int_a^b P(t)dt$  où P(t)dt est la puissance dissipée à l'instant t. Cette puissance dissipée dans un circuit électronique se compose de la puissance statique due aux courants de fuite et de la puissance dynamique due aux commutations des transistors (passage de l'état bloqué à passant et inversement). La puissance dynamique dissipée est définie par :

$$P_{dynamique} = \sum_{i \in E} \alpha_i . F_{clk} . C_{eq_i} . V_{DD}^2 \quad \forall i \in \{Opr; \ Ctr; \ Mem; \ inter\}$$

(1-4)

avec

$$C_{eq_i} = A_i \cdot C_{s_i} \tag{1-5}$$

où E est l'ensemble des blocs du système (opérateurs,...),  $\alpha_i$  est le taux d'activité c-à-d le nombre de transitions par cycle d'horloge,  $F_{clk}$  est la fréquence de fonctionnement,  $C_{eq_i}$  est la capacité équivalente.  $V_{DD}^2$  est la tension d'alimentation.  $\alpha_i$  dépend des données traitées et de la technique de codage utilisée. Le  $C_{s_i}$  caractérise le circuit utilisé, il est fonction de la capacité moyenne surfacique du composant i  $C_{s_i}$  et de la surface moyenne du composant i  $A_i$ .

On voit dans l'équation 1-4 qu'il existe quatre paramètres pour diminuer l'énergie consommée et toutes les techniques de réduction de la puissance dynamique s'attaquent à l'un ou l'autre de ces facteurs.

Dans les circuits CMOS avec des finesses de gravures supérieures à  $0.13~\mu m$  la puissance dynamique représente 80-85~% de la puissance dissipée. Ainsi classiquement, la puissance statique est négligée. Du fait de la diminution de la technologie, la consommation statique devient de plus en plus importante et elle devrait même devenir prépondérante dans les années à venir. Il devient alors indispensable de prendre en compte cette dissipation statique qui dépend principalement des paramètres technologiques.

#### Efficacité énergétique

L'efficacité énergétique d'une architecture [16] est définie comme le nombre de millions d'opérations réalisées pour la consommation de 1 mW de puissance.

$$EE = \frac{N_{op}.F_{clk}}{P} \quad \left[ \frac{MOPS}{mW} \right] \tag{1-6}$$

Dans l'équation 1-6,  $N_{op}$  représente le nombre moyen d'opérations réalisées par cycle. Le produit  $N_{op}$ . $F_{clk}$  représente donc la puissance de calcul de l'architecture considérée et s'exprime en MOPS. P représente quant à elle la consommation de puissance sousjacente à l'exécution de  $N_{op}$  opérations par cycle.

L'efficacité énergétique représente le compromis performance/consommation de l'architecture. Il est à noter que cette métrique ne présage pas de la qualité en performance d'une architecture mais permet de mettre en avant les optimisations souhaitables pour obtenir des architectures efficaces du point de vue de la consommation.

Pour les architectures hybrides reconfigurables, les performances présentées ici dépendent essentiellement de l'intégration architecturale de la ressource reconfigurable dans la plate-forme du processeur hôte.

Nous présentons dans la section suivante un état de l'art des différentes architectures selon la manière de coupler le processeur et l'architecture reconfigurable dynamiquement.

#### B INTÉGRATION ARCHITECTURALE

Le problème de l'intégration architecturale est le fait de déterminer comment la ressource reconfigurable peut-être intégrée avec le processeur, et en particulier le niveau de couplage entre ces deux ressources. Le processeur a généralement en charge les structures de contrôle qui configurent la logique, lancent les traitements, gèrent les transferts de données ainsi que les interfaces. La position relative du cœur du processeur et de l'ARD détermine les délais de communications et de reconfigurations desquels dépendent étroitement les performances de l'architecture hybride.

Dans cette section, nous proposons d'aborder les différentes stratégies d'intégration architecturale existantes dans la littérature, en suivant la taxonomie couramment utilisée.

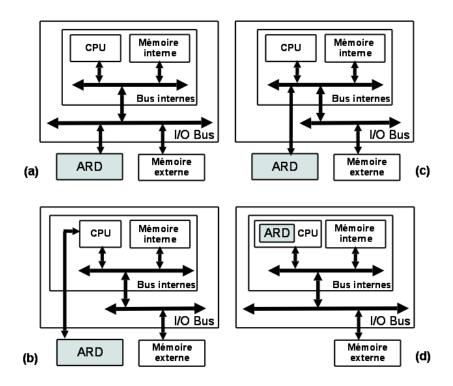

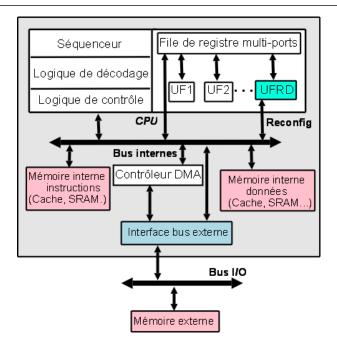

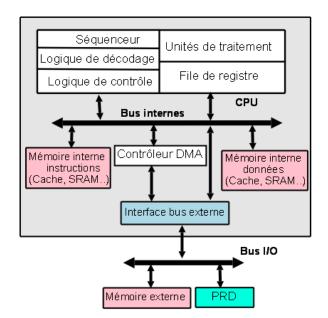

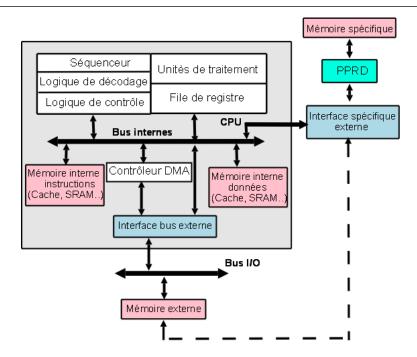

La figure 1-8 présente les modes de couplage entre CPU et ARD variant de "faiblement couplés" à "fortement couplés". Le premier mode (a), correspondant au niveau de couplage le plus faible, connecte l'ARD comme un périphérique. Le deuxième mode (b) couple plus étroitement l'ARD en la connectant au CPU à travers une interface ou bus spécifique. Le troisième mode (c) connecte l'ARD au bus interne du CPU (en mode coprocesseur). Pour le mode le plus étroit (d), la ressource reconfigurable est située sur les chemins de données internes du processeur au même titre qu'une unité entière ou flottante.

Figure 1-8 – Types de couplage processeur (CPU)- architecture reconfigurable dynamiquement (ARD). (a) couplage en mode périphérique; (b) couplage en mode point à point; (c) couplage en mode coprocesseur; (d) couplage en mode unité fonctionnelle.

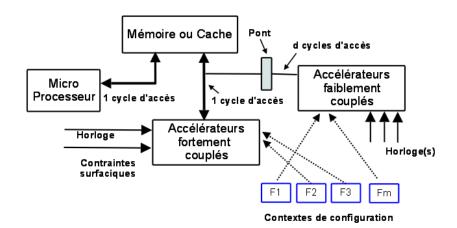

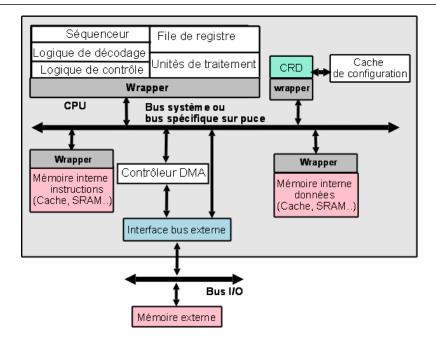

Quelques travaux (exemple [17] et [18]) combinent même deux niveaux de couplages dans une architecture hybride afin de bénéficier des avantages de chaque type d'intégration architecturale. La figure 1-9 présente le principe sur lequel repose ces architectures. En effet, les accélérateurs qui sont fortement couplés au processeur hôte ont un accès direct à la mémoire ou cache interne. Ils doivent tous fonctionner à une seule fréquence d'horloge qui correspond nécessairement à la plus faible entre les fréquences respectives des différentes ARD. Par contre, les accélérateurs faiblement couplés accèdent à la mémoire à travers un pont et donc chacun utilise sa propre fréquence d'horloge. Ainsi, implémenter une application donnée sur les architectures fortement couplées permet d'effectuer un accès mémoire en un seul cycle d'horloge mais au coût d'un fonctionnement à une fréquence d'horloge probablement plus faible. Inversement, une implémentation sur les architectures faiblement couplées permet une exécution avec des fréquences individuelles plus rapide avec un accès en mémoire sur plusieurs cycles.

Figure 1-9 – Principe d'une architecture combinant deux niveaux d'intégration architecturale. Les accélérateurs fortement couplés au processeur hôte ont un accès direct à la mémoire ou cache interne et doivent tous fonctionner à une seule fréquence d'horloge. Par contre, les accélérateurs faiblement couplés accèdent à la mémoire à travers un pont et utilise chacun sa propre fréquence d'horloge.

#### B.1 Unité Périphérique Reconfigurable

Les Unités Périphériques Reconfigurables sont les premiers types d'architectures d'accélérateurs matériels reconfigurables à être apparus dans la communauté du calcul reconfigurable. Cette approche propose l'intégration de la ressource reconfigurable en tant qu'unité périphérique du système hôte, en la connectant sur le bus périphérique (I/0) (voir figure 1-8 (a)). Dans ce type de couplage, le processeur peut donc communiquer avec le circuit reconfigurable, grâce à des instructions d'entrées-sorties permettant de déclencher les transactions de chargement des données et des contextes de reconfiguration. Ces transactions se font au moyen de transferts de blocs de données, dans lesquels la mémoire principale (externe) est partagée entre le processeur et le périphérique, la synchronisation se faisant au moyen d'interruptions matérielles.

De ce fait, ce type d'architecture offre de nombreux avantages.

- Un coût relativement faible, grâce à l'utilisation de composants matériels standardisés (circuit d'interfaces périphériques) et produits en gros volumes. Le coût final de la carte est en général imposé par le composant reconfigurable lui-même.

- Le fait d'interconnecter l'accélérateur matériel au travers d'un bus périphérique permet une grande flexibilité quant à son organisation matérielle interne (nombre et topologies des interconnexions, utilisation de mémoires locales, génération d'horloge flexible, etc.), permettant de dimensionner le système selon les besoins de l'application.

- En tant que périphérique, la reconfiguration dynamique ainsi que l'exécution de l'ap-

plication sur l'ARD est réalisée sans une supervision continue du CPU.

Dans ce type de topologie, l'accélérateur ne bénéficie pas de la hiérarchie mémoire du processeur (mémoire cache). Cependant, le fait qu'il soit connecté comme périphérique permet d'y intégrer ses ressources mémoire propres. Celles-ci sont en général formées par un ensemble de bancs mémoire indépendants qui permettent une latence d'accès réduite (<20ns) et offrent bande passante élevée (jusqu'à 800 Mbps).

La faiblesse du modèle de couplage en tant que périphérique réside dans leur système de communication : l'utilisation du bus d'entrées-sorties limite très fortement la performance des communications entre l'hôte et l'unité reconfigurable, pour les raisons suivantes :

- dans un système complet, les autres périphériques consomment également une part de la bande passante disponible, et de plus, les arbitrages entre périphériques, mémoire cache, et processeurs induisent des latences d'accès importantes, qui réduisent d'autant plus la bande passante disponible;

- les caractéristiques des périphériques actuels ne justifient que rarement l'existence de bus périphériques à hautes performances (exception faite des accélérateurs matériels de rendus 3D temps-réels).

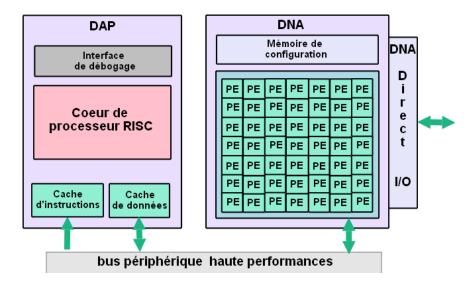

Afin de répondre aux besoins de la reconfiguration dynamique qui impose un chargement simultané des données nécessaires à l'exécution de l'application et des contextes de reconfiguration et donc une bande passante assez importante, et de palier aux limites de performances des bus périphériques standards (PCI, S-bus ou VME), des architectures hybrides avec un couplage en périphérique comme DAP-DNA [19] utilisent des bus spécifiques haute performance (Figure 1-10).

L'architecture conçue pour le traitement d'image intensif est composée d'un cœur RISC 32 bits DAP (Digital Application Processor) et d'une architecture reconfigurable dynamiquement nommée DNA (Distributed Network Architecture) contenant 955 PEs de 16 bits arrangés en forme de 2D Mesh (maillage 2D). Le DNA contient trois bancs mémoire pour le stockage des configurations. La communication entre le DAP et le DNA se fait à travers un bus périphérique haute performance "PCI Express" donnant un débit jusqu'à 8Go/s. Par contre, le transfert de données du DNA vers la mémoire externe (et vice-versa) se fait à travers quatre canaux d'interface (DNA Direct I/O) à 200 MHz chacun.

L'environnement de développement DAP/DNA-FW II permet, en partant d'une spécification de haut niveau d'une application (de type MATLAB/Simulink de MathWorks), d'assister le concepteur dans les différentes étapes du processus de développement jusqu'à l'implémentation sur le composant.

Figure 1-10 – L'architecture hybride DAP-DNA. Dans cette architecture, l'ARD (DNA) est couplé au CPU (DAP) sur le bus périphérique haute performance donnant un débit jusqu'à 8 Go/s. Le transfert de données du DNA vers la mémoire externe (et vice-versa) se fait à travers quatre canaux d'interface (DNA Direct I/O) à 200 MHz chacun.

#### B.2 Unité reconfigurable en couplage point-à-point

Dans un type de couplage point à point, le circuit reconfigurable est couplé directement au processeur à travers une interface ou un bus spécifique (Figure 1-8 (b)). Cette technique assure une bonne bande passante entre les deux ressources de calculs. De plus, il n'y a pas d'arbitrage à effectuer pour accéder au lien de communication. Le CPU a accès aux fonctionnalités qu'offre l'interface spécifique par l'intermédiaire de fonctions API (Application Programming Interface) qui permettent une utilisation transparente des ressources du reconfigurable.

Ce modèle permet de profiter des avantages que procure le modèle de couplage en périphérique aux architectures hybrides reconfigurable et en plus de s'affranchir de la latence élevée causée par le bus I/O.

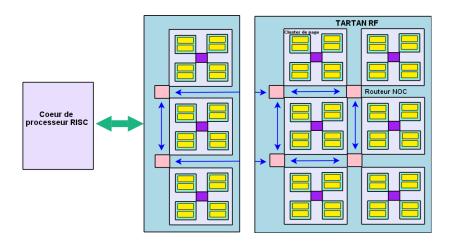

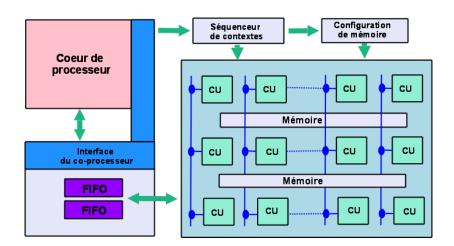

Pour ce mode de couplage CPU/ARD, l'architecture Tartan [20] utilise un bus spécifique de largeur 96 bits. Les données et les contextes de reconfiguration sont acheminés entre un cœur RISC synchrone et une ressource reconfigurable asynchrone RF (Reconfigurable Fabric) à travers des FIFO. La RF est une architecture clusterisée gros grain asynchrone. Un cluster de la RF est formé de 4x4 pages, chacune formée de 16 PE. Chaque PE est une UAL de 8 bits. La communication intra-cluster est ba-

sée sur un réseau d'interconnexion NOC (Network On Chip) asynchrone (Figure 1-11).

Figure 1-11 – Tartan est une architecture hybride avec un couplage CPU/ARD point à point entre le cœur RISC et la Reconfigurable Fabric (RF). La RF est une architecture clusterisée gros grain asynchrone. Un cluster de la RF est formé de 4 × 4 pages formée chacune de 16 PE. Chaque PE est une UAL de 8 bits. La communication intra-cluster est basée sur un réseau d'interconnexion NOC asynchrone.

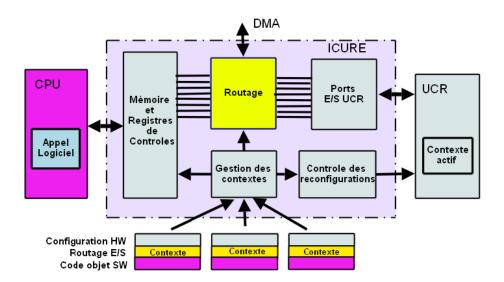

La solution de couplage en point à point souffre d'une latence d'acheminement des données non négligeable. Afin de palier à cette latence, quelques architectures hybrides utilisent des interfaces de communication spécifiques assurant l'accès de l'ARD à la mémoire externe de la puce. Dans ce cas, la mémoire doit être multi-ports. Pour d'autres, l'interface est formée par un ensemble de bancs mémoire indépendants (auxquels le CPU et l'ARD accèdent) permettant une latence d'accès réduite (<20ns) et offrant une bande passante élevée. C'est la cas pour l'architecture présentée dans [21]. En effet, le CPU et le reconfigurable sont connectés en point à point à travers ICURE une interface intelligente illustrée par la figure 1-12. L'interface ICURE comprend principalement une mémoire de données, un cache de contextes, une matrice de routage reconfigurable et un contrôleur de reconfiguration. Elle a pour rôle de faire communiquer de façon transparente un CPU avec une unité de calcul reconfigurable UCR (Unité de Calcul Reconfigurable) et de gérer intelligemment les processus de reconfiguration. Le CPU est connecté à ICURE par un bus d'adresses et un bus de données standards. L'interface ICURE est connectée à l'UCR au moyen de ses ports d'entrée/sortie (I/O) bidirectionnels et d'un lien de reconfiguration. La reconfiguration de l'UCR est effectuée par une unité de gestion dédiée située à l'intérieur de l'interface.

Figure 1-12 – Un CPU et une UCR (Unité de Calcul Reconfigurable) connectés en point à point à travers l'interface spécifique ICURE. L'interface ICURE comprend principalement une mémoire de données, un cache de contextes, une matrice de routage reconfigurable.

#### B.3 COPROCESSEUR RECONFIGURABLE

Dans le cas de couplage en coprocesseur reconfigurable, la zone reconfigurable dynamiquement est connectée au bus interne du processeur (Figure 1-8 (c)). Le bus interne peut être soit un bus système ou un bus spécifique sur puce tel que AMBA de ARM [22] ou CoreConnect d'IBM [23].

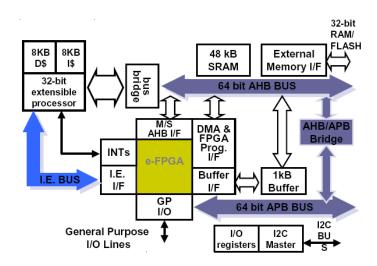

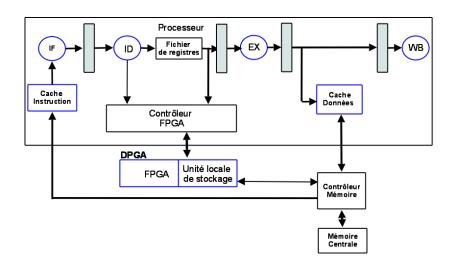

L'architecture présentée dans [24], conçue par STMicroelectronics [25] afin d'accélérer les traitements d'image, présente un processeur 32 bits couplé en mode coprocesseur à un e-FPGA (embedded-FPGA) à travers une interface spécifique sur bus AMBA (Figure 1-13). Cette architecture permet une accélération de 1.5 à 2 fois pour les algorithmes de reconnaissance de visage (face recognition).

Dans la reconfiguration dynamique, un chargement simultané des données nécessaires à l'exécution des tâches et des contextes de reconfiguration est possible. Pour le modèle de couplage en coprocesseur, ceci peut causer un goulot d'étranglement sur le bus interne. Afin de limiter l'accès à la hiérarchie mémoire au cours du chargement de la configuration, la plupart des architectures hybrides dotent l'ARD coprocesseur de sa propre mémoire de configuration (cache, SRAM...).

L'ARD est capable d'exécuter le traitement sans la supervision continue du processeur puisqu'il a accès à toute la hiérarchie mémoire du CPU (mémoire cache). Cependant,

Figure 1-13 – Une architecture hybride concue par STmicroelectronics avec coprocesseur reconfigurable. cette architecture présente un processeur 32 bits couplé à un e-FPGA à travers le bus sur puce AMBA

elle doit être initialisée par le CPU. Ce dernier doit aussi contrôler les accès mémoire en lui référençant les adresses source et destination ainsi que la taille des blocs mémoire. Il faut toutefois prévenir les problèmes de cohérence mémoire en utilisant un modèle de programmation : "'mémoire partagée"' ou "'passage de message"'.

Le chargement et l'exécution des contextes de configuration sur la partie reconfigurable sont contrôlés par le processeur en utilisant différentes techniques.

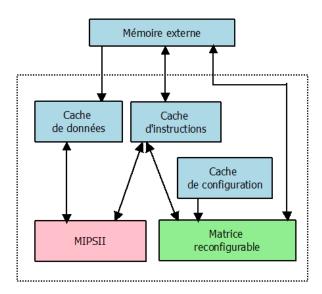

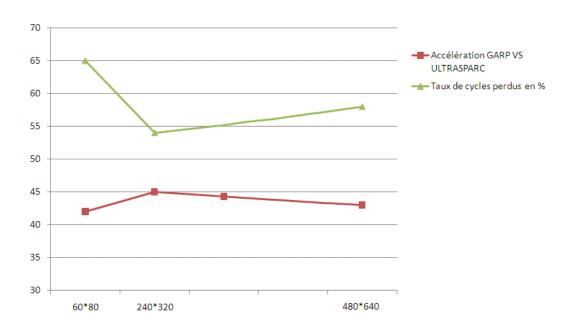

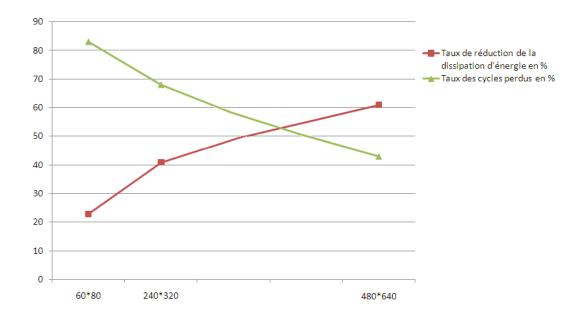

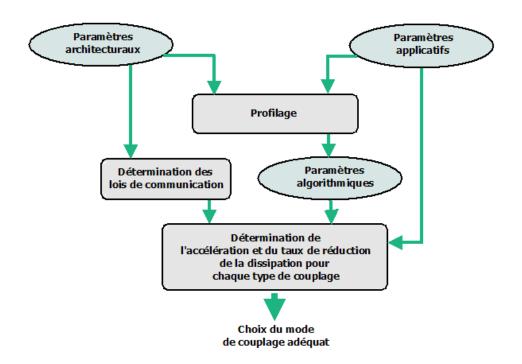

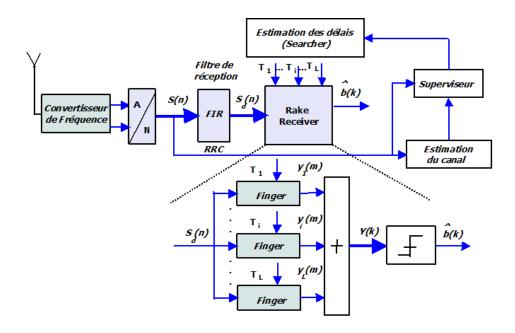

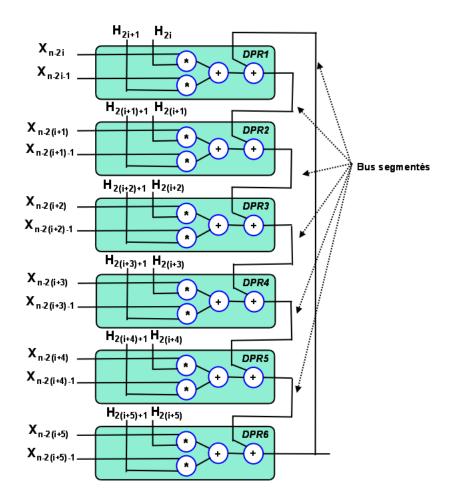

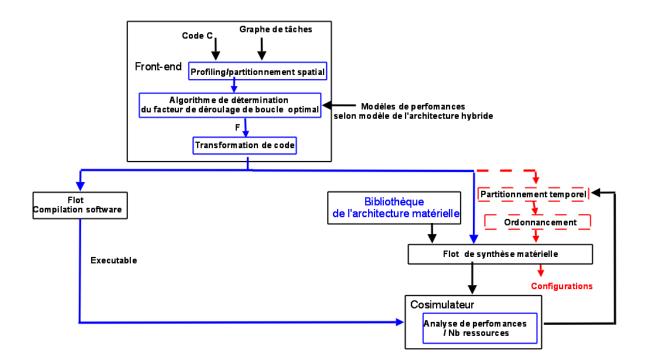

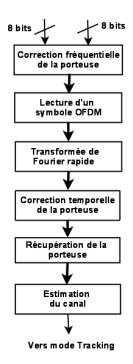

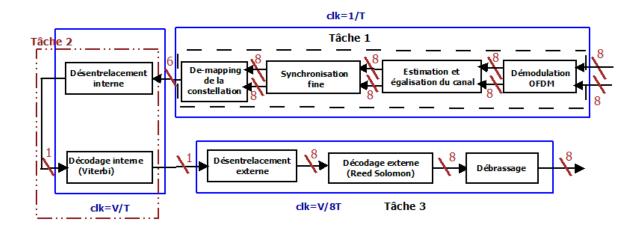

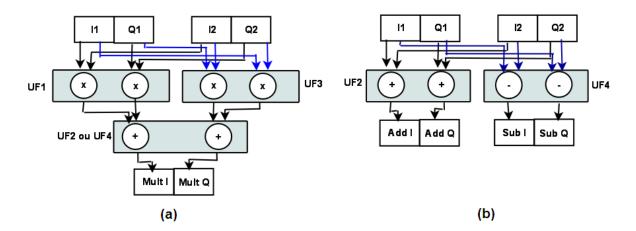

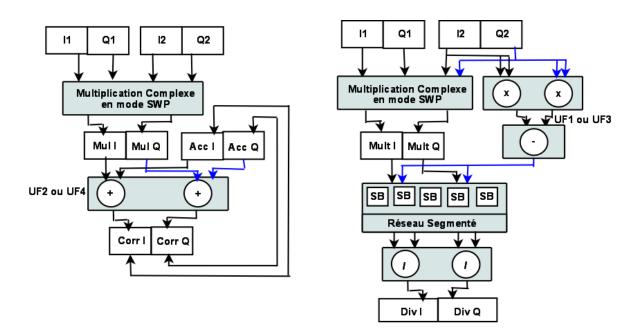

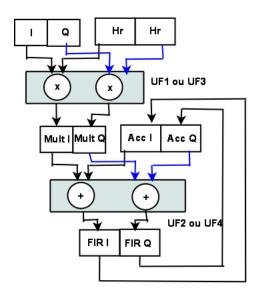

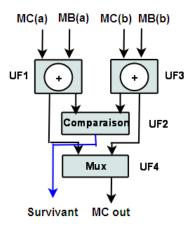

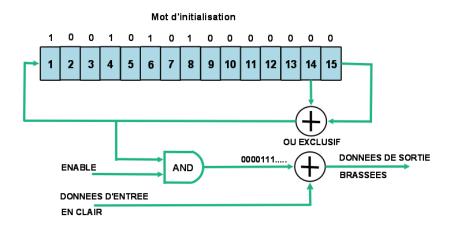

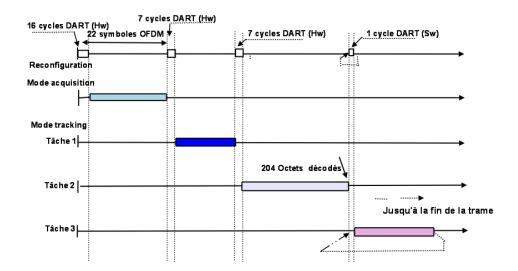

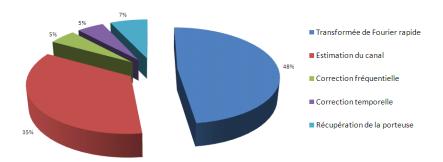

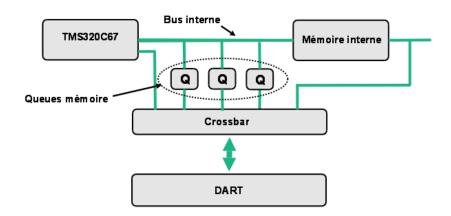

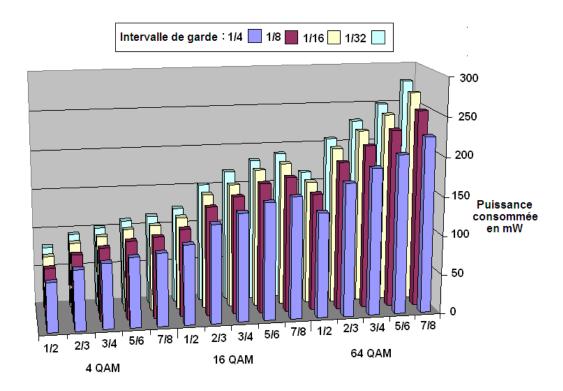

Dans l'architecture GARP [4], le jeu d'instructions du processeur (MIPS II) a été étendu afin de contrôler l'accès du bloc reconfigurable à sa hiérarchie mémoire. L'unité reconfigurable est sous la forme d'une matrice de blocs logiques organisée en 32 colonnes de 24 blocs chacune. Un des 24 blocs est un bloc de contrôle et les blocs restants sont des blocs logiques opérant sur des données de largeur deux bits (granularité fine). La matrice reconfigurable est aussi dotée d'un cache de configuration pouvant supporter quatre configurations pour chaque colonne. La reconfiguration à partir de ce cache ne prend que quatre cycles (Figure 1-14).