## Etude de méthodes et mécanismes pour un accès transparent et efficace aux données dans un système multiprocesseur sur puce

P. Guironnet de Massas

#### ▶ To cite this version:

P. Guironnet de Massas. Etude de méthodes et mécanismes pour un accès transparent et efficace aux données dans un système multiprocesseur sur puce. Micro et nanotechnologies/Microélectronique. Institut National Polytechnique de Grenoble - INPG, 2009. Français. NNT: . tel-00434379

### HAL Id: tel-00434379 https://theses.hal.science/tel-00434379

Submitted on 23 Nov 2009

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

#### INSTITUT POLYTECHNIQUE DE GRENOBLE

N° attribué par la bibliothèque

ISBN 978-2-84813-145-0

#### **THESE**

pour obtenir le grade de

#### **DOCTEUR DE L'Institut polytechnique de Grenoble**

Spécialité : Informatique

préparée au laboratoire TIMA

dans le cadre de l'Ecole Doctorale Mathématiques, Sciences et Technologies de l'Information, Informatique

présentée et soutenue publiquement

par

Pierre Guironnet de Massas

le 12 novembre 2009

Étude de méthodes et mécanismes pour un accès transparent et efficace aux données dans un système multiprocesseur sur puce

#### **DIRECTEUR DE THESE**

Frédéric Pétrot

#### **JURY**

- M. Jean-François Méhaut, Président

- M. Alain Greiner, Rapporteur

- M. Olivier Temam, Rapporteur

- M. Frédéric Pétrot, Directeur de thèse

- M. Olivier Franza, Examinateur

- M. Thierry Collette, Examinateur

# Étude de méthodes et mécanismes pour un accès transparent et efficace aux données dans un système multiprocesseur sur puce

Pierre Guironnet de Massas

20 novembre 2009

#### Remerciements

Je remercie en premier lieu mon directeur de thèse Frédéric Pétrot, chef de l'équipe SIS du laboratoire TIMA, pour le temps qu'il a consacré au suivi de mes travaux et à son expertise qui m'a souvent aidée à résoudre les problèmes rencontrés.

Je remercie également les membres du jury. Messieurs Olivier Temam, directeur de recherche à l'INRIA et Alain Greiner, directeur du département SoC au LIP6 d'avoir accepté d'être rapporteurs de ces travaux. Messieurs Thierry Collette, chef de service au CEA LIST et Olivier Franza, ingénieur chez Intel d'avoir été examinateurs de ma soutenance de thèse. Enfin je remercie monsieur Jean-François Méhaut d'avoir présidé le jury lors de ma soutenance de thèse.

Je tiens à remercier tous les collègues et amis qui m'ont soutenus, aidés durant ces trois années passées au laboratoire. Tout particulièrement Xavier Guérin et Patrice Gerin pour leur expertise technique sur les systèmes d'exploitation, langages de programmation et outils d'édition. Quentin Meunier pour son aide précieuse à la re-lecture d'articles, documents et manuscrit de thèse, ainsi que pour son aide sur les problèmes algorithmiques.

Je remercie également tous ceux qui m'ont consacré du temps pour les lectures et relectures du manuscrit de thèse, tout particulièrement ma compagne Amandine Brugière et mon père Eric de Massas, ainsi que Frédéric Rousseau, Paul Amblard et Olivier Muller qui m'ont permis de mener à bien ma soutenance de thèse.

Enfin, je remercie tous les membres du laboratoire TIMA qui m'ont accordé de leur temps pour partager avec moi leur expertise technique, scientifique ou administrative.

# Table des matières

| 1               | Intr | oduction                                                         | 1  |

|-----------------|------|------------------------------------------------------------------|----|

| 2 Problématique |      |                                                                  |    |

|                 | 2.1  | L'accès à la mémoire, un point clé                               | 5  |

|                 | 2.2  | Un accès efficace à la mémoire                                   | 6  |

|                 |      | 2.2.1 La latence d'accès                                         | 6  |

|                 |      | 2.2.2 La bande passante                                          | 6  |

|                 |      | 2.2.3 Consommation                                               | 7  |

|                 | 2.3  | Un accès transparent à la mémoire                                | 7  |

|                 |      | 2.3.1 Complexité des systèmes multiprocesseurs                   | 8  |

|                 |      | 2.3.2 Abstraction des détails de l'architecture                  | 8  |

|                 |      | 2.3.3 Accès transparent                                          | 9  |

|                 | 2.4  | Le contexte d'étude                                              | 9  |

|                 | 2.5  | Caches et cohérence : de nouvelles contraintes                   | 10 |

|                 |      | 2.5.1 Caches: simplicité et efficacité                           | 10 |

|                 |      |                                                                  | 10 |

|                 |      |                                                                  | 10 |

|                 | 2.6  |                                                                  | 11 |

|                 |      | 1                                                                | 11 |

|                 | 2.7  | Migration des données dans la puce                               | 12 |

|                 |      |                                                                  | 12 |

|                 |      |                                                                  | 12 |

|                 |      |                                                                  | 12 |

|                 |      | 2.7.4 La solution aux problèmes ou les problèmes de la solution? | 12 |

|                 | 2.8  | •                                                                | 13 |

|                 |      |                                                                  |    |

| Ι               |      |                                                                  | 15 |

| 3               | Cac  | hes et cohérence des données                                     | 17 |

|                 | 3.1  | Cache: minimiser la latence et la bande passante                 | 17 |

|                 |      |                                                                  | 17 |

|                 |      | 3.1.2 Choix des données, associativité et ordre d'évincement     | 18 |

|                 |      | 3.1.3 Le cache des instructions                                  | 18 |

|                 | 3.2  | Politiques de mise à jour mémoire                                | 18 |

|                 | 3.3  | 1                                                                | 19 |

|                 |      | 3.3.1 Bus: espionnage                                            | 20 |

|                 |      | • •                                                              | 21 |

|                 |      |                                                                  | 22 |

|                 |      |                                                                  |    |

| 4  | Prof | ocoles de cohérence, mise à jour mémoire                                              | 23 |

|----|------|---------------------------------------------------------------------------------------|----|

|    | 4.1  | Protocoles, caractéristiques et motivations                                           | 23 |

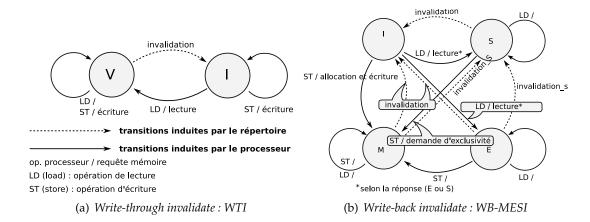

|    |      | 4.1.1 Le protocole <i>write-though invalidate</i> et ses avantages                    | 23 |

|    |      | 4.1.2 Protocoles comparés dans cette étude                                            | 24 |

|    | 4.2  | Expérimentations                                                                      | 27 |

|    |      | 4.2.1 Environnement de simulation et architecture matérielle                          | 27 |

|    |      | 4.2.2 Applications                                                                    | 28 |

|    |      | 4.2.3 Système d'exploitation                                                          | 31 |

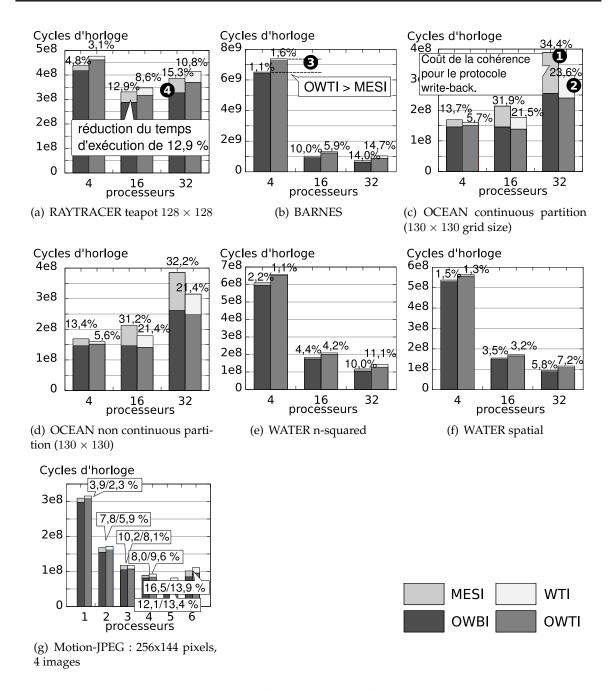

|    | 4.3  | Résultats et commentaires                                                             | 31 |

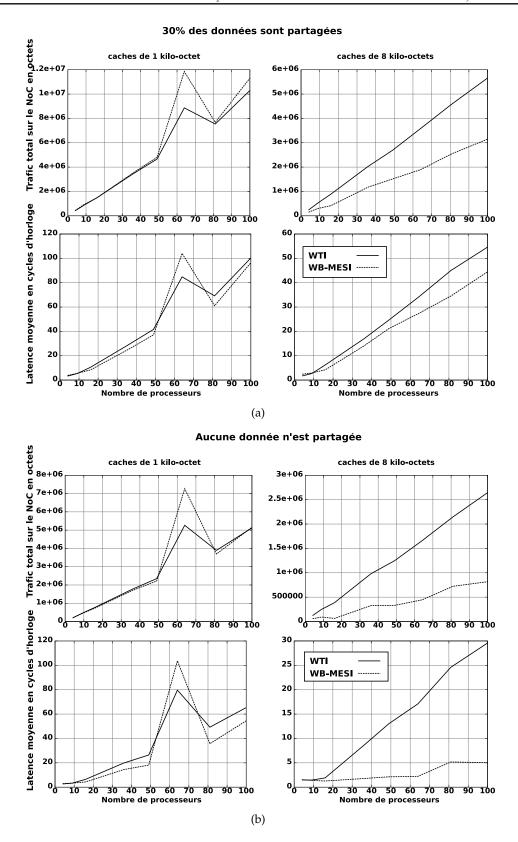

|    |      | 4.3.1 simple_test                                                                     | 31 |

|    |      | 4.3.2 Applications SPLASH-2 et MJPEG                                                  | 35 |

|    | 4.4  | Conclusion de l'étude                                                                 | 37 |

|    | 4.5  | Limitations de l'étude                                                                | 38 |

| 5  | Mét  | hodes d'évaluation et de comparaison des protocoles de cohérence                      | 39 |

|    | 5.1  | Modèles théoriques                                                                    | 39 |

|    | 5.2  | Simulations dirigées par les traces (trace driven)                                    | 39 |

|    |      | 5.2.1 Architectures monoprocesseurs                                                   | 39 |

|    |      | 5.2.2 Architectures multiprocesseurs et « effet papillon »                            | 40 |

|    | 5.3  | Simulations dirigées par les évènements (event driven)                                | 40 |

|    |      | 5.3.1 Précision et niveau d'abstraction                                               | 41 |

|    | 5.4  | Conception des systèmes et modélisation                                               | 41 |

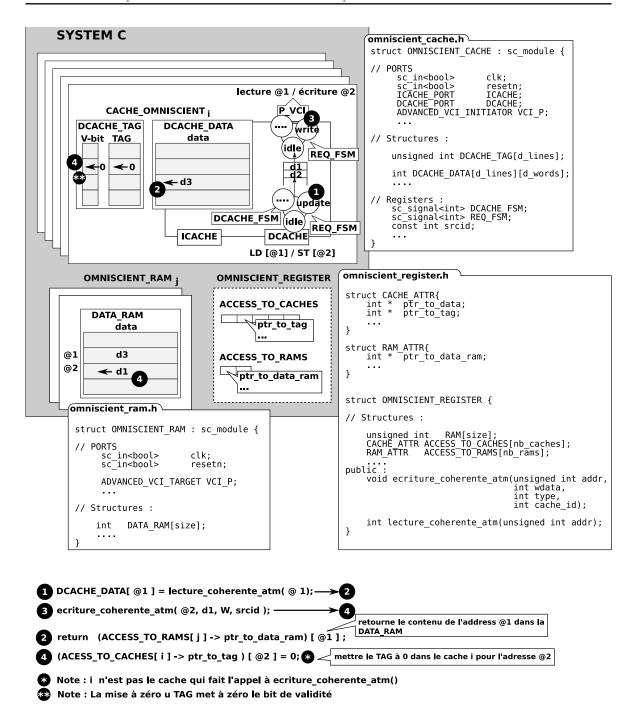

| 6  | Mét  | hode d'évaluation des protocoles mémoire : un cache omniscient                        | 43 |

| •  | 6.1  | Protocole omniscient : obtenir un meilleur cas d'évaluation                           | 43 |

|    | 6.2  | Protocole omniscient, détails de la solution                                          | 45 |

|    | ·    | 6.2.1 Actions élémentaires d'un protocole                                             | 45 |

|    |      | 6.2.2 Transaction omnisciente d'un protocole                                          | 47 |

|    |      | 6.2.3 Implémentation et situations de compétition                                     | 48 |

|    | 6.3  | Concernant la consistance mémoire                                                     | 50 |

|    | 6.4  | Détails de l'implantation des actions omniscientes pour des protocoles <i>write</i> - |    |

|    | 0.1  | through et write-back invalidate                                                      | 52 |

|    |      | 6.4.1 Implémentation des actions omniscientes                                         | 53 |

|    |      | 6.4.2 Coût d'implantation de la méthode                                               | 55 |

|    | 6.5  | Expérimentations, résultats et commentaires                                           | 55 |

|    | 0.0  | 6.5.1 simple_test                                                                     | 55 |

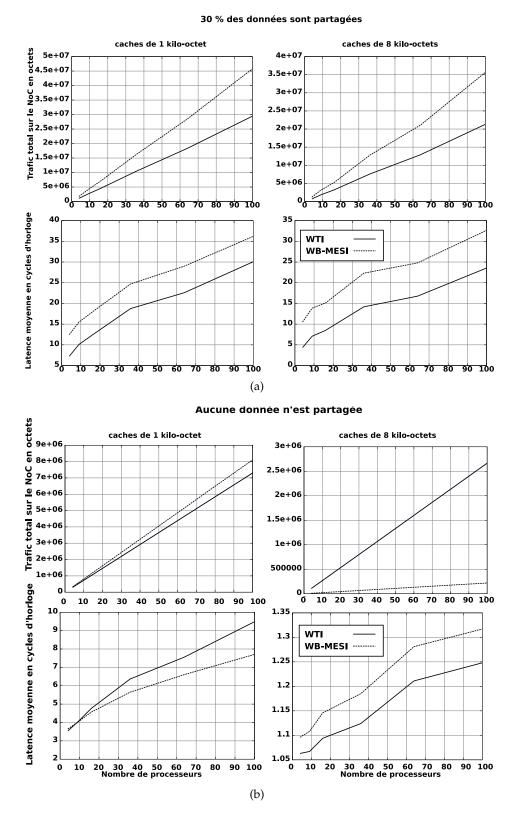

|    |      | 6.5.2 Applications SPLASH-2 et MJPEG                                                  | 58 |

|    | 6.6  | Limitations : une borne inférieure « approchée »                                      | 61 |

|    | 0.0  | 6.6.1 Le chemin d'exécution peut être modifié                                         | 61 |

|    | 6.7  | Conclusion de l'étude                                                                 | 62 |

|    |      |                                                                                       |    |

| II |      |                                                                                       | 63 |

| 7  | Méı  | noire, placement et gestion des données                                               | 65 |

|    | 7.1  | Architectures distribuées                                                             | 65 |

|    |      | 7.1.1 Placement et déplacement des données                                            | 66 |

|    |      | 7.1.2 Gestion de l'énergie                                                            | 68 |

|    | 7.2  | Architectures intégrées                                                               | 68 |

|    |      | 7.2.1 placement et déplacement des données                                            | 69 |

#### TABLE DES MATIÈRES

|    | 7.3               | Positionnement de nos travaux                                                                                                 | 70               |

|----|-------------------|-------------------------------------------------------------------------------------------------------------------------------|------------------|

| 8  | Mig               | ration des données et choix du placement idéal                                                                                | <b>7</b> 1       |

|    | 8.1               | Le partage des données                                                                                                        | 71               |

|    |                   | 8.1.1 Le partage des instructions                                                                                             | 71               |

|    |                   | 8.1.2 Persistance des données en cache                                                                                        | 72               |

|    |                   | 8.1.3 Le faux partage des données                                                                                             | 72               |

|    |                   | 8.1.4 Les données : un « tout »                                                                                               | 72               |

|    | 8.2               | CPI et placement des données                                                                                                  | 72               |

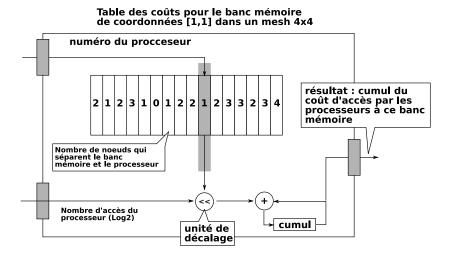

|    |                   | 8.2.1 Coût d'accès à une donnée                                                                                               | 74               |

|    |                   | 8.2.2 Minimisation du $\widetilde{CPI}$ à l'aide d'un placement optimal des données .                                         | 74               |

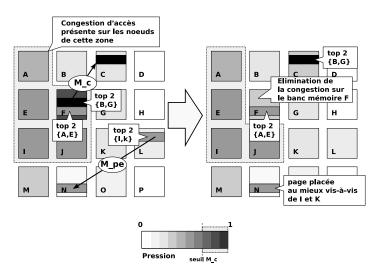

|    | 8.3               | Congestion d'accès : heuristique                                                                                              | 75               |

|    |                   | 8.3.1 Causes de la pathologie                                                                                                 | 75               |

|    |                   | 8.3.2 Solution mise en place                                                                                                  | 75               |

|    |                   | 8.3.3 Avantages                                                                                                               | 77               |

| 0  | Calu              | tion et implementation muonogée nouve la mienation demande que des dennées                                                    | 79               |

| 9  | 9.1               | ation et implantation proposée pour la migration dynamique des données  Déplacer les données dans le système : choix réalisés | 7 <b>9</b><br>79 |

|    | ,                 | 9.1.1 Granularité des déplacements                                                                                            | 80               |

|    |                   | 9.1.2 Choix d'une solution pour le transfert des données                                                                      | 80               |

|    | 9.2               | Implantation de la solution proposée                                                                                          | 80               |

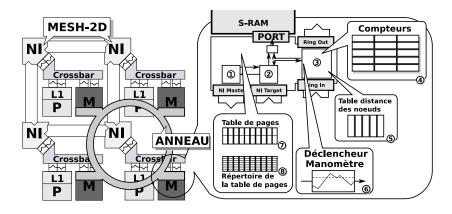

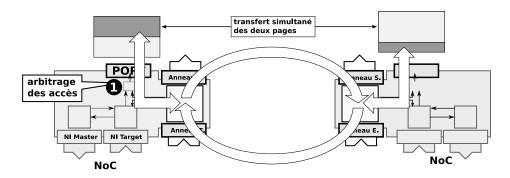

|    | <b>7.</b> <u></u> | 9.2.1 Architecture globale                                                                                                    | 80               |

|    |                   | 9.2.2 Adressage des données                                                                                                   | 81               |

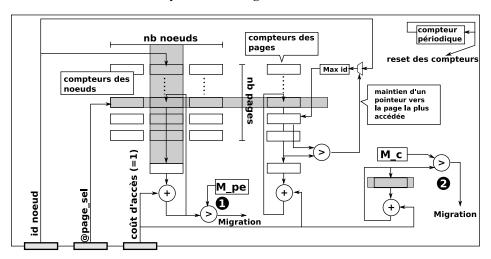

|    |                   | 9.2.3 Déclenchement de la migration                                                                                           | 83               |

|    |                   | 9.2.4 Placement des données et stabilité du système                                                                           | 84               |

|    |                   | 9.2.5 Transfert des données                                                                                                   | 85               |

|    |                   | 9.2.6 Réactivité du système et surcoût lié à la migration                                                                     | 86               |

|    |                   | 9.2.7 Évaluation approximative du surcoût en surface de l'implantation                                                        | 86               |

|    |                   | 9.2.8 Cohérence des traductions                                                                                               | 87               |

|    | 0.2               |                                                                                                                               | 90               |

|    | 9.3               | Expérimentations                                                                                                              |                  |

|    |                   |                                                                                                                               | 90               |

|    |                   | 9.3.2 Validation de la solution                                                                                               | 90               |

|    | 9.4               | 9.3.3 Évaluation de la solution                                                                                               | 91<br>94         |

|    |                   |                                                                                                                               |                  |

| 10 |                   | itations et pistes de recherche de l'étude de migration des données                                                           | 95               |

|    | 10.1              | Limitations de l'étude et problèmes potentiels                                                                                | 95               |

|    |                   | 10.1.1 Plus d'applications                                                                                                    | 95               |

|    |                   | 10.1.2 Passage à l'échelle                                                                                                    | 95               |

|    |                   | 10.1.3 Variation des paramètres                                                                                               | 96               |

|    | 10.2              | Améliorations et variantes de la solution actuelle                                                                            | 96               |

|    |                   | 10.2.1 Technique de déclenchement                                                                                             | 96               |

|    |                   | 10.2.2 Compteurs d'accès à base de filtres de Bloom                                                                           | 96               |

|    |                   | 10.2.3 Prise en compte du coût en latence                                                                                     | 97               |

|    | 10.3              | Pistes de recherches et travaux futurs                                                                                        | 98               |

|    |                   | 10.3.1 Support par le système d'exploitation                                                                                  | 98               |

|    |                   | 10.3.2 Passage à l'échelle et migrations en parallèle                                                                         | 99               |

| 11 | Con               | clusion                                                                                                                       | 101              |

12 Publications 105

# Liste des tableaux

|     | Coût en nœuds traversés dans chacun des protocoles                                  |    |

|-----|-------------------------------------------------------------------------------------|----|

| 6.1 | Nombre de lignes de code de chacun des composants                                   | 55 |

| 9.1 | Surcoût en quantité d'information des éléments mémorisants de la solution implantée | 87 |

| 9.2 | Paramètres des architectures modélisées, les paramètres (*) ne concernent que P_MIG | 90 |

Pierre de Massas vii

viii Pierre de Massas

# Table des figures

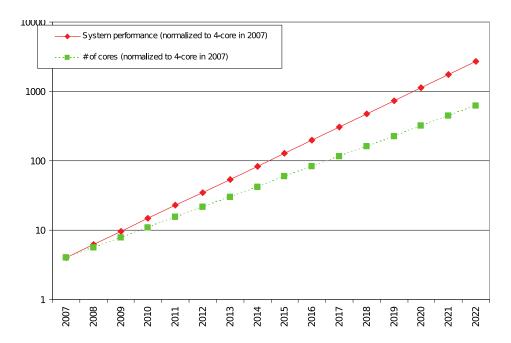

| 1.1                                           | Perspectives d'évolution du nombre de cœurs dans une puce et de la puissance de calcul (source ITRS 07 [ITR07])                                                                                                                                                                     | 3            |

|-----------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|

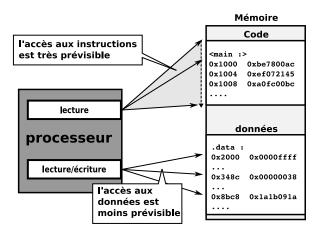

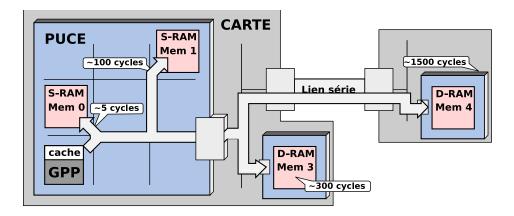

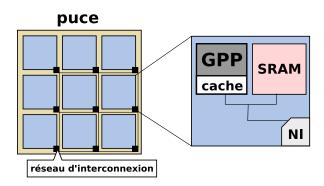

| <ul><li>2.1</li><li>2.2</li><li>2.3</li></ul> | Couple processeur-mémoire : l'accès aux instructions et aux données n'ont pas les mêmes caractéristiques de localité temporelle ou spatiale Latence indicative entre un processeur et des composants mémoire Architecture à processeurs homogènes embarquant de la mémoire partagée | 5<br>7<br>10 |

| 3.1                                           |                                                                                                                                                                                                                                                                                     | 18           |

| 3.2                                           | Différentes étapes de l'accès à un cache à correspondance directe                                                                                                                                                                                                                   | 19           |

| 3.3                                           | Espionnage des requêtes sur bus.                                                                                                                                                                                                                                                    | 20           |

| 3.4                                           | Principe des protocoles de cohérence faisant usage d'un répertoire                                                                                                                                                                                                                  | 21           |

| 4.1                                           | Automates d'états des protocoles implantés                                                                                                                                                                                                                                          | 25           |

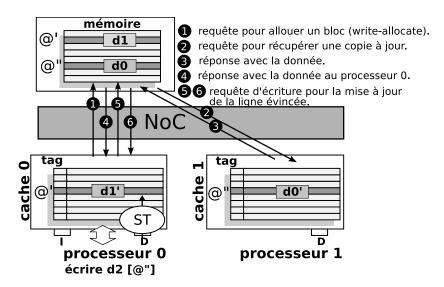

| 4.2                                           | Exemple d'un accès qui coûte $6.L_m$ cycles d'horloges dans le protocole WB-MESI. Les adresses $@'$ et $@"$ ciblent la même ligne dans le cache à correspon-                                                                                                                        | 2.           |

| 4.0                                           | dance directe.                                                                                                                                                                                                                                                                      | 26           |

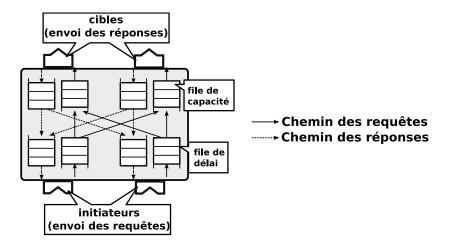

| 4.3                                           | Architecture du GMN, la file de délai a un temps de traversée constant, la file de capacité peut être traversée en 1 cycle                                                                                                                                                          | 27           |

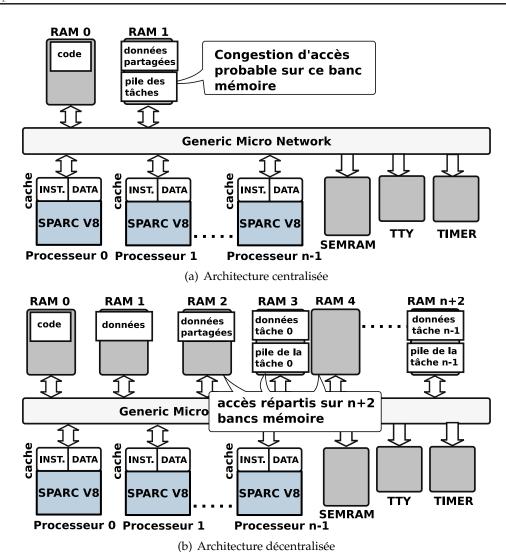

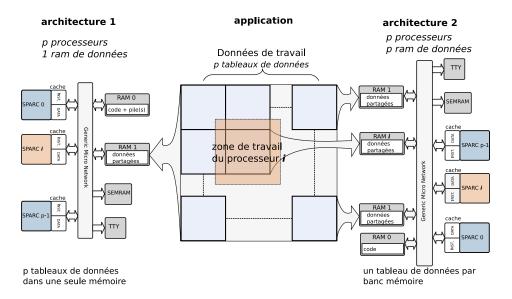

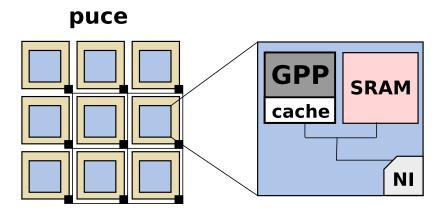

| 4.4                                           | Description des deux architectures utilisées                                                                                                                                                                                                                                        | 29           |

| 4.5                                           | Application de test et validation simple_test : répartition des données en fonction de l'architecture considérée                                                                                                                                                                    | 30           |

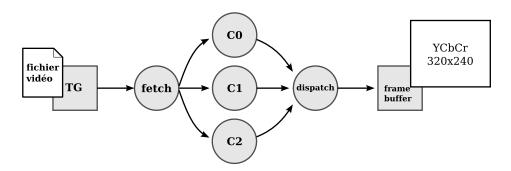

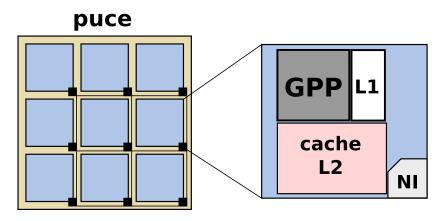

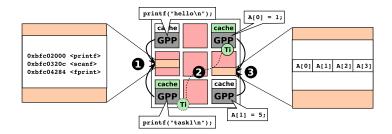

| 4.6                                           | Application mjpeg décrite à l'aide de tâches communicantes                                                                                                                                                                                                                          | 30           |

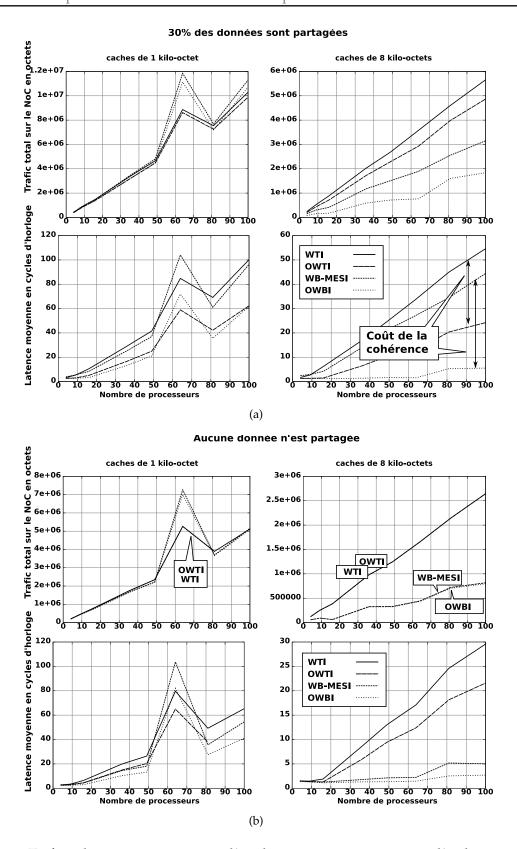

| 4.7                                           | Trafic et latence moyenne pour l'application simple_test sur l'architecture                                                                                                                                                                                                         |              |

|                                               | centralisée                                                                                                                                                                                                                                                                         | 32           |

| 4.8                                           | Trafic et latence moyenne pour l'application simple_test sur l'architecture décentralisée                                                                                                                                                                                           | 33           |

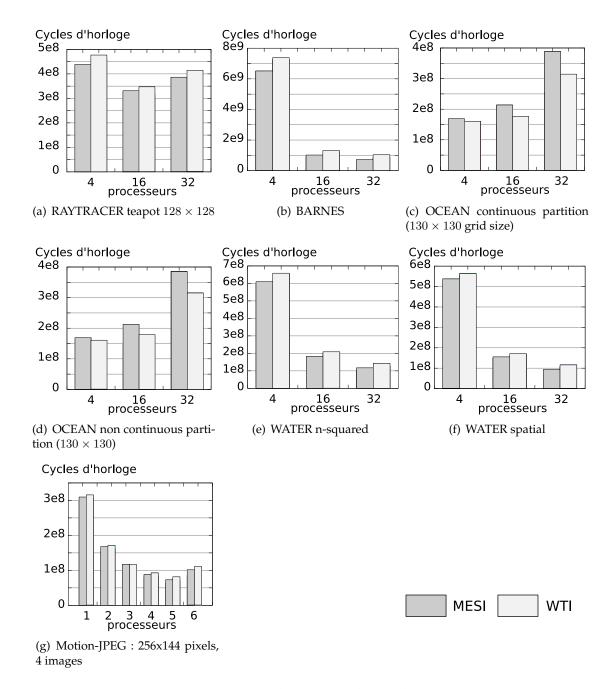

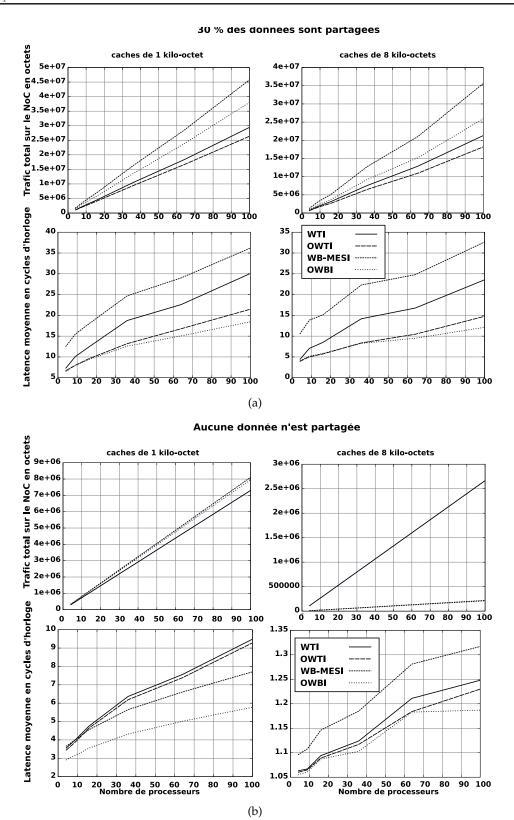

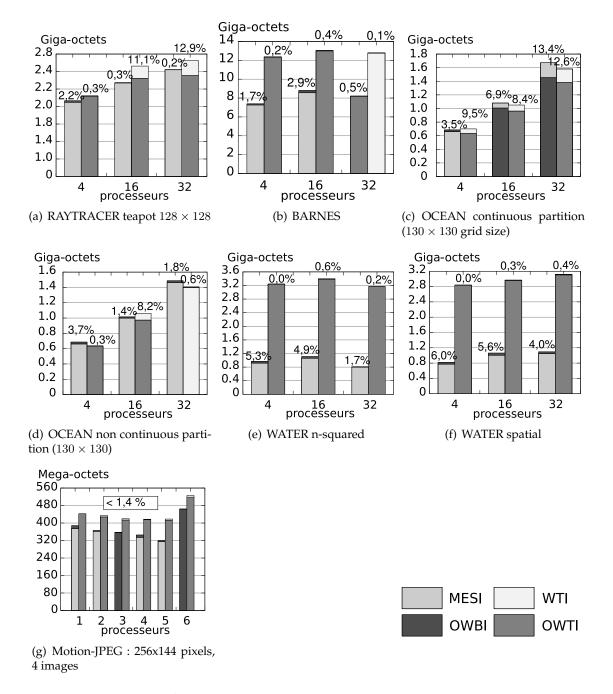

| 4.9                                           | Temps d'exécution des applications                                                                                                                                                                                                                                                  | 35           |

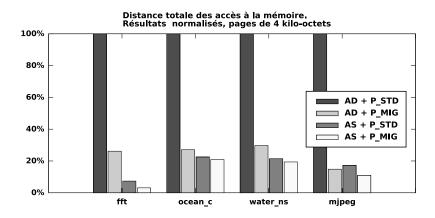

| 4.10                                          | Cumul du trafic généré, il inclue toutes les requêtes et toutes les réponses émises sur le réseau d'interconnexion                                                                                                                                                                  | 36           |

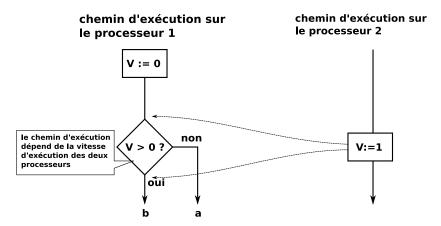

| 5.1                                           | Exemple où le contrôle du chemin d'exécution dépend des données                                                                                                                                                                                                                     | 40           |

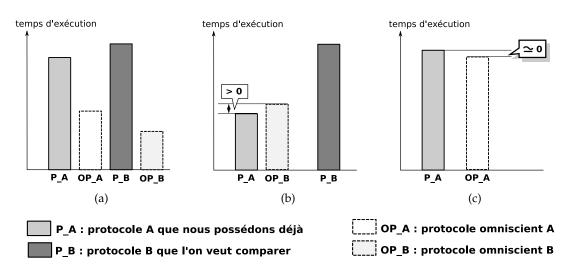

| 6.1                                           | Trois scenarii de comparaison possibles                                                                                                                                                                                                                                             | 44           |

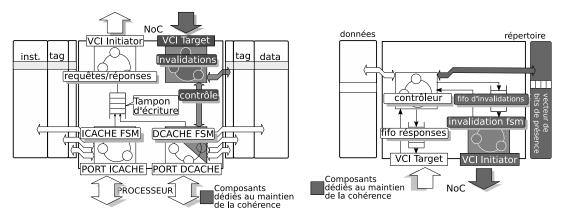

| 6.2                                           | Architecture des contrôleurs de cache et mémoire. En noir, les infrastructures nécessaires au maintien de la cohérence                                                                                                                                                              | 46           |

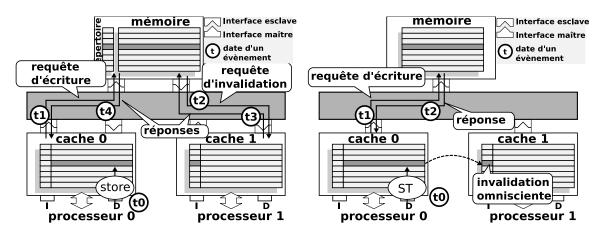

| 6.3                                           | Une instruction de rangement traitée par une architecture write-through avec                                                                                                                                                                                                        |              |

|                                               | deux protocoles de cohérence différents                                                                                                                                                                                                                                             | 47           |

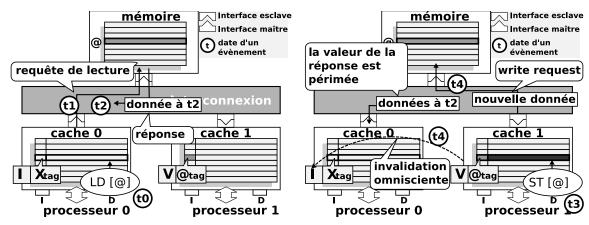

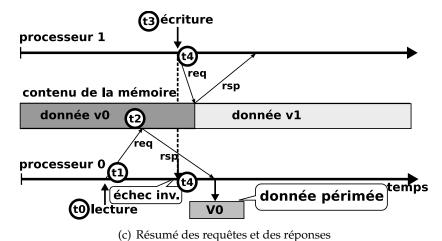

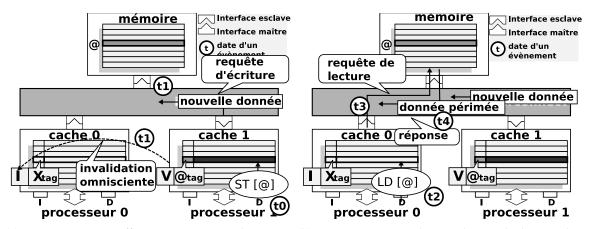

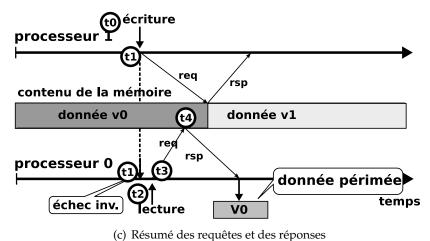

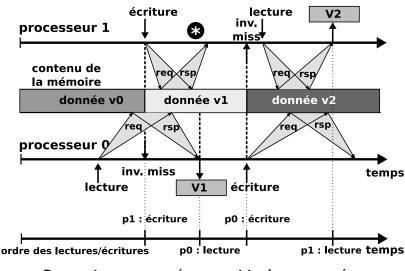

| 6.4        | Exemple d'une condition de compétition sur une lecture, la donnée lue en mémoire est incohérente à $t_4$                            | 49       |

|------------|-------------------------------------------------------------------------------------------------------------------------------------|----------|

| 6.5        | Exemple d'une compétition d'accès lors d'une écriture                                                                               | 50       |

| 6.6        | Application de notre solution pour les compétitions présentées dans les fi-                                                         |          |

| 0.0        | gures 6.4 et 6.5.                                                                                                                   | 51       |

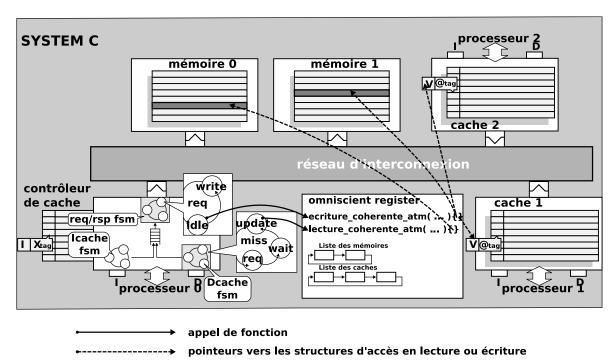

| 6.7        | Vue de l'architecture d'une plateforme pourvue de la cohérence omnisciente.                                                         | 53       |

| 6.8        | Structure de l'implantation d'un protocole de cohérence omniscient dans un                                                          |          |

|            | cache write-through                                                                                                                 | 54       |

| 6.9        | Trafic et latence moyenne pour l'application simple_test sur l'architecture                                                         |          |

|            | centralisée                                                                                                                         | 56       |

| 6.10       | Trafic et latence moyenne pour l'application simple_test sur l'architecture                                                         |          |

|            | décentralisée.                                                                                                                      | 57       |

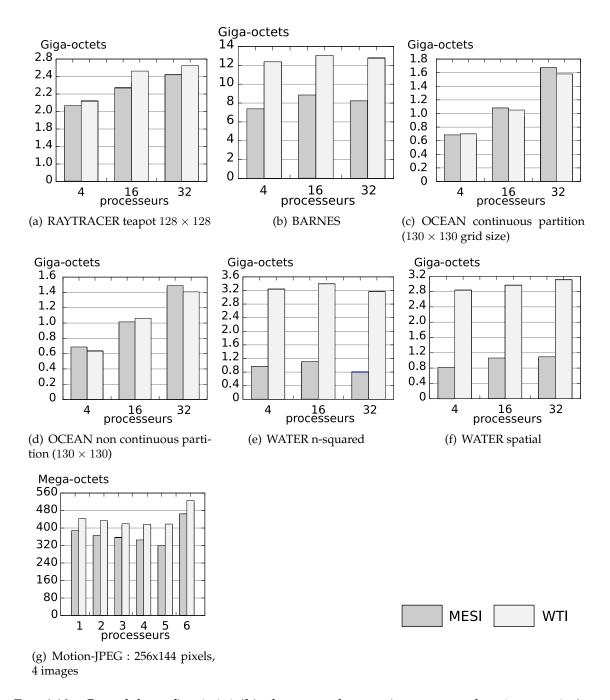

| 6.11       | Temps d'exécution total des applications                                                                                            | 59       |

| 6.12       | Cumul du trafic généré, il inclue toutes les requêtes et toutes les réponses                                                        |          |

|            | émises sur le réseau d'interconnexion                                                                                               | 60       |

| 7.1        | Exemple d'architecture distribuée comprenant quatre nœuds                                                                           | 66       |

| 7.2        | Exemple d'architecture intégrée comprenant quatre nœuds                                                                             | 68       |

| 8.1        | Illustration des différents types de partage des données                                                                            | 72       |

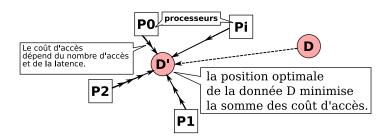

| 8.2        | Placement optimal de la donnée $D$ qui minimise le coût d'accès par les pro-                                                        |          |

|            | cesseurs $P_i$                                                                                                                      | 74       |

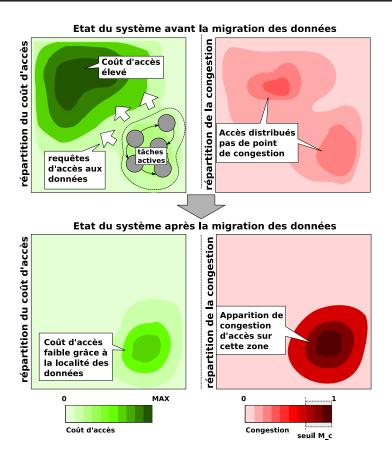

| 8.3        | Exemple où la migration des données crée un point de congestion                                                                     | 76       |

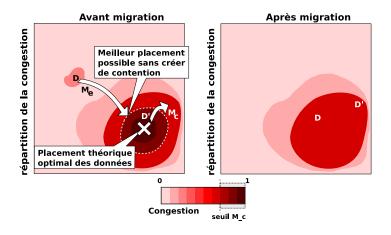

| 8.4        | Application de la solution pour éviter la congestion                                                                                | 76       |

| 9.1        | Architecture homogène à mémoire partagée et distribuée                                                                              | 80       |

| 9.2        | Mécanisme d'adressage des données.                                                                                                  | 82       |

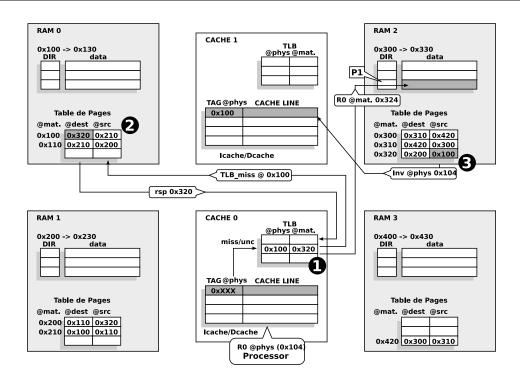

| 9.3        | Module de comptage des accès par nœud et par page                                                                                   | 83       |

| 9.4        | Exemple de migration de données pour diminuer la congestion $(M_c)$ , et rap-                                                       |          |

| o =        | procher les données $(M_{pe})$                                                                                                      | 84       |

| 9.5        | Module permettant de calculer le coût d'accès d'une page vis-à-vis de tous                                                          | 0.5      |

| 0.6        | les processeurs du système                                                                                                          | 85       |

| 9.6<br>9.7 | Transfert de deux pages entre deux nœuds                                                                                            | 86       |

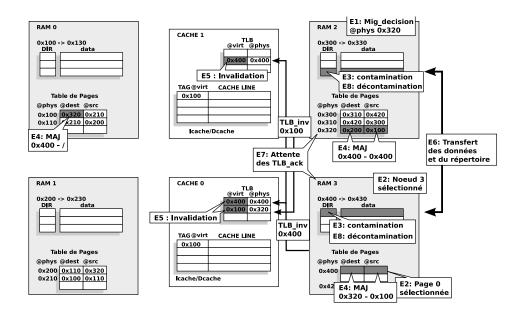

| 9.7<br>9.8 | Étapes de la migration de la page d'adresse matérielle 0x320 Évolution du placement des données dans l'application placement_test . | 88       |

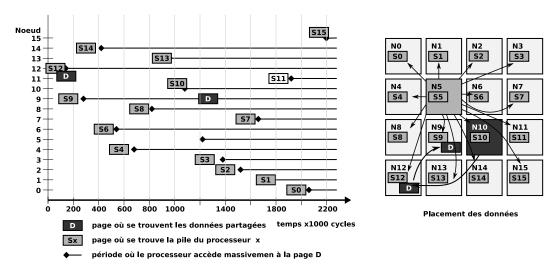

| 9.0<br>9.9 | 11 -                                                                                                                                | 91<br>93 |

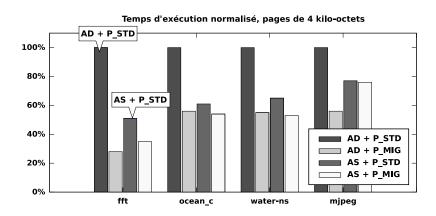

|            | Temps d'exécution normalisé des applications                                                                                        | 93       |

|            | •                                                                                                                                   | 24       |

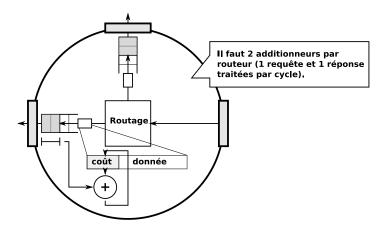

| 10.1       | Exemple d'implantation dans un routeur de la comptabilisation du temps de                                                           | _        |

|            | traversée                                                                                                                           | 98       |

# Chapitre 1

### Introduction

Epuis plus d'un demi-siècle, les systèmes informatiques n'ont cessé de progresser. Au début destinés à réaliser du calcul, ils ont très vite été détournés de leur usage premier pour s'intégrer dans tous les domaines de notre existence : finance, santé, loisirs, communications, transports, etc... L'homme demande toujours plus à ces systèmes, plus de vitesse, plus de puissance, un meilleur rendement énergétique, plus de fonctionnalités. Si bien qu'en l'espace d'une génération humaine nous sommes passés de simples calculateurs arithmétiques à des systèmes d'une puissance de calcul inimaginable alors, et offrant des possibilités applicatives très variées. Le cœur de ces systèmes est le couple processeur-mémoire auquel nous apporterons toute notre attention.

Les technologies d'intégration des systèmes informatiques ont permis d'intégrer toujours plus de transistors dans une même puce. La diminution de la taille des circuits permet également l'augmentation de leur fréquence de fonctionnement. Nous avons été témoins cette dernière décennie d'une évolution majeure dans la conception des processeurs et des systèmes informatiques : la généralisation d'architectures multiprocesseur.

Afin d'obtenir de meilleures performances, les architectes privilégient l'intégration de nombreux processeurs à l'usage d'un coeur unique très complexe. Au regard de la puissance de calcul, la complexité moindre de ces processeurs est largement compensée par l'exploitation du parallélisme à l'exécution.

Il y a principalement trois causes à cette évolution : une architecture des processeurs complexe qui conduit à des consommations d'énergie inacceptables, des limitations physiques à la montée en fréquence des systèmes et une capacité d'intégration en augmentation presque constante.

Les deux premières causes concernent surtout le domaine du calcul haute performance où la complexité des processeurs n'a cessé de croître depuis leur invention. Les architectes ont imaginé et implanté des techniques complexes tel que le *pipelining*, l'exécution dans le désordre des instructions ou encore le calcul superscalaire. De nouvelles améliorations de l'architecture offraient un gain faible vis-à-vis de la complexité de la solution et de l'effort fourni.

La montée en fréquence de ces systèmes n'est plus possible à cause essentiellement des fuites de courants associés [Naf06]. Pour s'affranchir de cette limitation, les concepteur multiplient le nombre de processeurs dans une même puce afin d'exécuter en parallèle plusieurs tâches.

La troisième cause concerne également le domaine des systèmes embarqués. La capacité à intégrer de multiples processeurs dans une même puce permet de faire face aux demandes des applications embarquées gourmandes en puissance de calcul. En effet, l'essor de la téléphonie mobile, des assistants personnels (PDA) et des technologies multimédia en général

a créé de nouveaux besoins : décodage vidéo, jeux interactifs en trois dimensions, décodage audio numérique, etc...

#### Des systèmes complexes

Si dans certains cas l'architecture des processeurs a été simplifiée, d'une manière générale le système a gagné en complexité. Cette évolution concerne également le logiciel. L'usage de mécanismes d'abstraction tels que les langages interprétés par des machines virtuelles, le recours à des techniques de génération de code ou tout simplement l'intégration d'un système d'exploitation ont simplifié le développement des applications. Néanmoins, cette simplification s'est faite au dépend de la simplicité de l'ensemble.

La première conséquence est une abstraction totale de l'architecture matérielle et l'impossibilité qu'a le programmeur d'exploiter facilement ces caractéristiques particulières. Nos travaux portent un intérêt tout particulier à cet aspect de l'évolution des systèmes.

#### Contraintes supplémentaires

Les systèmes embarqués ont profité de ces évolutions mais pâtissent également de l'augmentation de la complexité. A ceci s'ajoutent des contraintes qui leurs sont toutes particulières, comme la consommation d'énergie ou la surface de silicium restreinte. Ceci conduit à l'intégration du plus grand nombre possible de composants et périphériques dans la même puce. Nous y retrouvons maintenant en plus des processeurs : des mémoires, des périphériques d'entrée sortie ou des décodeurs vidéo. Ces puces deviennent de véritables systèmes sur puce ou SoC (*System on Chip*).

#### Les solutions du futur, tendances actuelles

D'après les prévisions ITRS [ITR07], il sera possible en 2020 d'intégrer 128 processeurs dans une même puce (cf. figure 1.1). Les architectes et concepteurs d'aujourd'hui proposent deux tendances à l'évolution des systèmes. La première tendance est la conception de systèmes très hétérogènes où chaque unité de calcul est optimisée pour une tâche précise [KTJR05]. Ils permettent une exécution optimisée des tâches logicielles ou matérielles d'un système, offrant ainsi une exécution rapide à moindre coût énergétique. Malgré cela, l'exploitation de tels systèmes est une tâche ardue, et leur complexité rebute bon nombre de programmeurs et de décideurs.

La deuxième tendance est l'intégration d'un grand nombre de processeurs identiques, simples et génériques dans une même puce avec une hiérarchie mémoire conçue pour simplifier l'accès aux données. Le défaut de cette solution est que pour une tâche spécifique les performances obtenues seront probablement en deçà de ce que peut fournir une architecture dédiée et spécifique à cette même tâche. Néanmoins, l'évolution rapide des besoins ainsi que la pluralité des tâches exécutées par un même système requiert une solution flexible tant en terme d'évolutivité que de capacité. De plus, la simplicité du modèle de programmation offert par ces architectures en font une solution idéale pour une exploitation efficace des ressources avec un effort et un coût minimum.

Dans le cadre de cette thèse nous sommes convaincus que cette deuxième tendance est la plus pertinente et nous parions qu'à l'avenir elle marquera l'évolution des systèmes.

FIG. 1.1 – Perspectives d'évolution du nombre de cœurs dans une puce et de la puissance de calcul (source ITRS 07 [ITR07]).

#### Problème général et objectifs de la thèse

Nos travaux se penchent sur l'aspect mémoire de ces architectures. Puisque l'avancement des tâches est conditionné par l'accès aux données et aux instructions, l'accès à la mémoire est un point critique de tout système informatique.

Ce problème peut être vu sous plusieurs angles différents : la latence des accès, la bande passante occupée, la complexité du modèle de programmation et la consommation d'énergie.

Nous abordons cette problématique en deux parties : Dans un premier temps nous présenterons une étude sur les caches et les protocoles de cohérence mémoire. Nous présenterons également une méthode pour les comparer et les évaluer. Dans un deuxième temps, nous décrirons une solution innovante pour déplacer les données sur le système. L'objectif est d'améliorer les latences d'accès tout en fournissant un accès transparent aux données.

#### Plan de la thèse

Dans le deuxième chapitre de cette thèse nous présentons les problématiques auxquelles ce travail apportera une réponse.

Le troisième chapitre est un état de l'art en matière de conception des mémoires cache et des protocoles de cohérence mémoire. On y présente également toutes les notions nécessaires à la compréhension de nos travaux. Le quatrième chapitre présente notre contribution liée aux problèmes de cohérence mémoire et de l'utilisation de certains protocoles dans le cadre des systèmes embarqués. Cette contribution sera étayée par des expérimentations et des résultats concluants.

Cette première partie a soulevé de nouveaux problèmes liés aux méthodes de comparaison et d'évaluation des protocoles de cohérence mémoire. Le chapitre suivant dresse un état de l'art lié à cette problématique. Le sixième chapitre développe une méthode d'évaluation

innovante basée sur la simulation précise au niveau du cycle d'horloge. Les expérimentations et résultats sont mis en comparaison avec ce qui a été obtenu dans le chapitre quatre.

Certaines limitations de l'utilisation des caches vont être soulevées dans la problématique. Dans le septième chapitre nous détaillons les techniques complémentaires basées sur la migration des données dans une puce. Cet état de l'art présente également des techniques de coopération des caches, qui s'intègrent parfaitement dans ce contexte. Les chapitre huit et neuf décrivent une nouvelle solution à la migration des données. Entièrement gérée en matériel, elle vient en complément de l'usage des caches et des mémoires cohérentes.

Dans le chapitre 10 nous présentons quelques limitations de ces travaux et des pistes de recherche pour les travaux futurs.

Le dernier chapitre reprend les questions posées dans la problématique et fait état des réponses apportées dans nos diverses contributions. Il résume l'ensemble de nos résultats et présente les conclusions de notre travail de thèse.

# **Chapitre 2**

# Problématique

Ous présentons dans ce chapitre les différents problèmes auxquels nous apporterons une réponse. Nous présentons d'abord le problème général afin de situer le contexte de nos travaux. Puis, nous présenterons en détail les sous-problèmes autour desquels s'articulent les différentes parties de ce manuscrit.

#### 2.1 L'accès à la mémoire, un point clé

Comme nous l'avons vu en introduction, le couple processeur-mémoire est le cœur de tout système informatique. La mémoire contient toutes les instructions exécutées et toutes les données accédées par un ou plusieurs processeurs (cf. fig. 2.1).

Toute instruction exécutée requiert donc au minimum un accès à la mémoire. Puisqu'elles sont exécutées dans l'ordre d'apparition du programme tant qu'aucun branchement ou déroutement n'a été effectué, il est très facile d'anticiper leur chargement à l'aide de composants spécialisés.

FIG. 2.1 – Couple processeur-mémoire : l'accès aux instructions et aux données n'ont pas les mêmes caractéristiques de localité temporelle ou spatiale.

Toutefois, à peu près une instruction sur cinq lit ou écrit une donnée en mémoire. Les adresses accédées dépendent du type de donnée (variable locale, variable dynamique, donnée statique), et de leur emplacement parmi un ensemble (case d'un tableau, champ d'une structure, variable spécifique). L'ordre des accès à ces données dépend du comportement

dynamique du programme, bien qu'il ne soit pas aléatoire, il est bien moins prévisible que l'ordre des accès aux instructions.

Les architectes et les concepteurs ont proposé d'innombrables solutions pour optimiser l'accès aux données, mais l'évolution des technologies les remet en cause à chaque nouvelle génération. En effet, l'amélioration des capacités de calcul des processeurs est bien plus rapide que la diminution des temps d'accès aux mémoires ou l'augmentation de leur débit.

L'accès aux données et à la mémoire en général constitue un point critique de tout système. Les architectes cherchent des solutions efficaces pour les problèmes d'accès à la mémoire. La notion d'efficacité varie en fonction des besoins et des contraintes. Nous définissons donc ci-dessous ce qu'est dans le cadre de nos travaux, un accès efficace à la mémoire.

#### 2.2 Un accès efficace à la mémoire

Nous définissons l'efficacité d'un accès mémoire par trois métriques différentes : la latence, la bande passante et l'énergie mise en œuvre.

#### 2.2.1 La latence d'accès

La latence d'accès ou temps d'accès se mesure en cycles d'horloge du processeur. Cette latence est due principalement à l'éloignement physique du banc mémoire auquel on souhaite accéder (cf. figure 2.2).

En général, l'organisation de la mémoire présente une hiérarchie. Les contraintes physiques et les coûts d'intégration imposent que les éléments placés à proximité des processeurs aient une capacité limitée. Par exemple, le banc des registres qui est accessible en un seul cycle d'horloge a une taille de quelques centaines d'octets seulement. Les caches et mémoires locales ont un accès de l'ordre du cycle d'horloge (1  $\sim$  5) mais ont une taille comprise entre quelques kilo-octets et quelques méga-octets. Les mémoires dynamiques (DRAM) dont la taille peut atteindre plusieurs giga-octets sont placées à l'extérieur de la puce et s'accèdent au mieux en une centaine de cycles d'horloge.

La distance n'est pas le seul élément qui influe sur la durée d'un accès. Le franchissement des interfaces joue également un rôle de premier ordre ; interface de bus, pont d'accès entre deux bus, contrôleurs et files d'attentes contribuent tous au temps d'accès global.

Certaines de ces interfaces permettent de changer de milieu physique ou de technologie (fibre optique), elles permettent par exemple d'accéder à un bus extérieur à la puce ou encore un lien série vers une autre carte. La latence de ces interfaces peut se mesurer en dizaines de cycles d'horloge.

L'enjeu majeur pour les architectes est de réduire la latence moyenne des accès. Une amélioration sensible de la latence moyenne aura une influence directe sur la vitesse d'exécution des applications.

Si l'espace d'adressage est réparti sur un ensemble de nœuds mémoire, les latences d'accès ne vont pas être uniformes pour toutes les données. De telles architectures sont de type NUMA (*Non Uniform Memory Access*).

#### 2.2.2 La bande passante

La bande passante d'un lien de communication (bus, NoC, lien série) se mesure en quantité de données transférées par unité de temps.

FIG. 2.2 – Latence indicative entre un processeur et des composants mémoire.

Si sur un lien de communication il n'y a qu'un seul composant capable d'émettre des requêtes, il suffit que la bande passante fournie soit supérieure au débit maximum que peut générer l'émetteur afin de garantir un temps de transfert sensiblement constant.

Si le lien de communication est partagé par plusieurs émetteurs potentiels, il est très probable que sa bande passante soit bien inférieure au débit maximum cumulé des émetteurs. Dès que la charge sur le lien dépasse un seuil critique, les latences d'accès croissent de façon exponentielle [PGJ+05]. Cette situation critique doit être évitée à tout prix sous peine de voir les performances du système s'effondrer.

Les architectes conçoivent le lien de communication en fonction des besoins, du type d'application, des performances souhaitées et des contraintes de coût. Le coût d'implantation d'un lien de communication est directement lié à la surface qu'il occupe.

Le coût en consommation de bande passante est également pris en compte lors de la conception de solutions pour améliorer l'efficacité des accès à la mémoire. Ceci s'applique aux solutions matérielles (cache, co-processeur, DMA) mais également aux solutions logicielles (flux de données, placement des variables et des structures, communications entre tâches).

#### 2.2.3 Consommation

Les systèmes embarqués ont la vocation d'être autonomes. Par conséquent, ils dépendent bien souvent d'une source d'énergie limitée (batterie), ou de faible capacité (solaire, cinétique, électromagnétique). De fait, il est impératif d'évaluer la consommation énergétique de ces systèmes et en amont, de concevoir des solutions économiques.

Les accès à la mémoire sont très gourmands en consommation d'énergie. Lors d'un accès à la mémoire, l'énergie est consommée d'un côté par les composants mis en œuvre (contrôleur de cache, contrôleur mémoire, bancs mémoire etc.), et d'un autre côté par le lien de communication.

### 2.3 Un accès transparent à la mémoire

La meilleure des solutions n'a aucun intérêt si les programmeurs ne sont pas capables de l'utiliser efficacement.

Les systèmes, composés d'une architecture matérielle et de couches logicielles, deviennent de plus en plus complexes à gérer par les programmeurs. Cette complexité a deux

origines orthogonales : l'avènement de la programmation parallèle et la montée en abstraction des vues du système. Toute solution concernant l'accès aux données doit prendre en compte cette complexité et ne pas en ajouter davantage.

#### 2.3.1 Complexité des systèmes multiprocesseurs

La tendance durable est l'intégration d'un nombre croissant de processeurs dans le système. Les écueils de la programmation d'un système multiprocesseur sont multiples :

- Paralléliser efficacement une ou plusieurs tâches. Certains algorithmes sont très difficiles à paralléliser.

- Synchroniser l'exécution parallèle des différentes tâches en évitant les interblocages, les zones critiques non protégées et toute situation de compétition au résultat imprévisible.

- Communiquer efficacement entre les différentes tâches et ne pas créer des points de congestion.

- Déboguer des erreurs qui ont bien (trop) souvent une reproductibilité aléatoire.

De plus, si la plateforme est hétérogène et possède de nombreux types de nœuds de calculs, l'exploitation efficace du parallélisme s'avère encore plus difficile.

Tout ceci rend la programmation parallèle efficace complexe. Toutefois, l'effort à fournir pour développer une application parallèle efficace reste néanmoins payant au vu du gain en performance généralement obtenu.

#### 2.3.2 Abstraction des détails de l'architecture

De nos jours, afin de simplifier la programmation et d'améliorer la portabilité des applications, les développeurs et concepteurs ont recours à des solutions qui permettent d'abstraire les détails de l'architecture. Cela va de l'usage de langages de haut niveau et de systèmes d'exploitations, à la virtualisation des systèmes ou l'utilisation de machines virtuelles.

Le revers de la médaille est que le programmeur n'est plus en mesure de maîtriser l'ensemble des composants, outils et services mis en jeu. Il n'est plus en mesure d'appréhender finement l'interaction entre le logiciel et le matériel. Par voie de conséquence, il n'est plus en mesure d'exploiter pleinement les mécanismes offerts par l'architecture afin de produire une application pleinement optimisée.

Par exemple considérons une application décrite dans un langage interprété par une machine virtuelle. Cette application s'exécute par ailleurs au sein d'un canevas complexe de composants aux interactions multiples.

Comment le programmeur peut-il garantir dans la pratique l'utilisation à bon escient de la mémoire? Comment peut-il s'assurer de l'efficacité des transferts de données et messages, de l'usage des contrôleurs DMA? A-t-il un moyen de placer les données de façon à en optimiser l'accès, diminuer les défauts de pages, la distance vis-à-vis du nœud de calcul? Ce sont des questions auxquelles il n'est pas simple de répondre et auxquelles beaucoup de programmeurs ne désirent pas répondre. En général l'objectif à atteindre est d'avoir un système fonctionnel à moindre coût de développement logiciel. La performance du système est léguée aux autres acteurs : les concepteurs du système, des composants utilisés et de l'architecture matérielle.

Les concepteurs de systèmes embarqués, à quelques exceptions près, ne sont plus épargnés par ce problème. Les appareils multimédia grand public tels que les PDA, téléphones mobiles, baladeurs mp3 ou encore les consoles de jeux vidéo, n'échappent pas au problème de la complexité.

#### 2.3.3 Accès transparent

Dans ce contexte il est donc impératif de ne pas reporter sur le programmeur le devoir d'exploiter des caractéristiques précises de l'architecture afin d'optimiser les accès mémoire. Nous définissons un accès transparent aux données comme la possibilité de manipuler efficacement les données d'un système sans avoir à prendre en compte les détails de l'architecture.

Ceci peut être fourni par certaines couches logicielles, ou bien, par le matériel. Cette dernière solution permet de garantir l'usage effectif de la solution mise en œuvre à tous les niveaux du logiciel : système d'exploitation, *middleware*, application.

L'enjeu de toute nouvelle solution permettant d'améliorer les accès mémoire est donc multiple, il doit réduire la latence moyenne des accès, être économe en bande passante, être aussi simple que possible à exploiter et avoir un impact positif ou négligeable sur la consommation d'énergie.

#### 2.4 Le contexte d'étude

Maintenant que les tendances d'évolution ont été montrées en introduction, que les contraintes auxquelles nous nous intéressons sont définies, nous pouvons précisément décrire notre contexte d'étude.

Nos travaux se concentrent sur des architectures multiprocesseurs, flexibles, potentiellement embarquées et simples à programmer. Par conséquent elles ont les caractéristiques suivantes :

**Homogène :** elles intègrent des processeurs simples et génériques (ARM, SPARC, MIPS, MicroBlaze, etc).

**Caches :** elles possèdent des petits caches qui sont une solution efficace et dont l'usage est transparent pour le programmeur. Leur taille est de quelques kilo-octets.

**Cohérence**: la cohérence des données est maintenue par le matériel, son coût d'implantation est justifié par une transparence des accès à la mémoire partagée.

**Mémoire embarquée:** en vue d'une intégration enfouie, toute ou partie de la mémoire est embarquée dans la puce. Elle est distribuée en bancs dans l'ensemble du système pour facilité l'intégration et limiter la congestion des accès.

**Mémoire partagée :** l'ensemble de l'espace d'adressage est partagé par tous les processeurs du système pour simplifier la programmation de l'ensemble.

**Réseau d'interconnexion :** afin de permettre un passage à l'échelle et de pouvoir intégrer plusieurs dizaines de processeurs et bancs mémoire, l'interconnexion est réalisée par un réseau point-à-point embarqué. Un tel réseau est un NoC<sup>1</sup>[GG00].

**Nœuds de calcul :** les composants seront organisés en nœuds de cacul comprenant au moins une mémoire et un processeur. Ces composants communiquent au travers d'un sous-réseau local de type crossbar.

Ci-dessous, nous aborderons cette problématique de façon détaillée sous trois angles différents mais complémentaires.

<sup>1</sup>Network on Chip

FIG. 2.3 – Architecture à processeurs homogènes embarquant de la mémoire partagée.

#### 2.5 Caches et cohérence : de nouvelles contraintes

Dans le contexte de notre étude, nous utilisons de la mémoire cache. Nous présentons ci-après les différents problèmes liés aux nouvelles contraintes des systèmes embarqués.

#### 2.5.1 Caches: simplicité et efficacité

Bien que les caches occupent une partie substantielle de la surface disponible dans une puce, leurs performances combinées à leur simplicité d'utilisation en font une des solutions privilégiées pour avoir des accès transparents et efficaces à la mémoire. L'utilisation des mémoires cache remonte à 1962 [BCP62], ils sont largement utilisées dans les architectures actuelles. L'usage des caches dans un système multiprocesseur où la mémoire est partagée implique la présence potentielle de copies des données. La cohérence des données est un problème majeur des systèmes multiprocesseurs.

#### 2.5.2 Cohérence des données

La cohérence des données peut être gérée de façon logicielle à la charge du programmeur qui, quand c'est nécessaire, vide les mémoires caches afin de garantir une mise à jour cohérente des données. Néanmoins, il est possible de garantir la cohérence des données avec des mécanismes matériels. Ainsi, le programmeur n'a plus à se soucier de la gestion des caches.

Le coût en surface du maintient de la cohérence par la matériel est entièrement justifié par son efficacité et par sa simplicité d'usage vis-à-vis de la programmation logicielle.

La plupart des systèmes multiprocesseurs non embarqués intègrent un protocole de cohérence gérée par le matériel et implanté au niveau des contrôleurs de caches et mémoires.

Comme nous le verrons dans le chapitre suivant, il existe une multitude de protocoles de cohérence. Néanmoins, l'accès aux données est un point critique du système et l'évolution des technologies remet sans cesse en cause les choix et les solutions des concepteurs. Les protocoles de cohérence implémentés en matériel n'échappent pas à cette évolution.

#### 2.5.3 Systèmes embarqués et nouvelles contraintes

Les technologies actuelles et à venir, permettent d'intégrer un grand nombre de processeurs dans une même puce. Pour les systèmes enfouis ou embarqués, les contraintes sur la surface et la consommation requièrent l'intégration de la plupart des composants et des périphériques au sein de la puce. Nous y retrouvons ainsi des modules mémoire, périphériques d'entrée-sortie, contrôleurs DMA, composants dédiés et plusieurs processeurs.

L'usage d'un NoC est une des solutions privilégiées pour assurer l'interconnexion de tous ces composants. L'avantage de ce type d'interconnexion est qu'il offre une bande passante cumulée presque illimitée. Puisque les mémoires sont intégrées à la puce, les transferts de données entre les caches et la mémoire bénéficient pleinement de la bande passante offerte par le NoC. De fait, celle-ci n'est plus un élément décisif lors de la conception d'un contrôleur de cache, d'autres éléments comme l'efficacité, la simplicité ou la consommation d'énergie deviennent prépondérants.

Au vu de ces nouvelles contraintes, ou plutôt, de la disparition d'une partie d'entre-elles, il convient de ré-évaluer certaines solutions au maintien de la cohérence mémoire.

Plus précisément, les protocoles de mise à jour mémoire de type *write-through* ont été très vite écartés à cause du trafic qu'ils généraient sur les liens d'interconnexion partagés (bus) ou sortant de la puce (multi-carte jusqu'alors).

Le problème auquel nous tenterons d'apporter une réponse est : est-il possible d'envisager une solution simple mais consommatrice de bande passante à la cohérence des caches ?

# 2.6 Évaluation et comparaison des protocoles de cohérence mémoire

Nous avons dans la section précédente, soulevé un problème vis-à-vis de la meilleure solution à implémenter dans notre contexte d'étude. Il se pose alors un deuxième problème : comment comparer deux solutions entre elles ?

Il n'est pas envisageable d'implémenter en matériel tous les protocoles de cohérence concurrents. Cela aurait un coût prohibitif en temps et en argent. Par conséquent, les architectes ont recours à une évaluation théorique des protocoles ou à la simulation de modèles.

#### 2.6.1 Modèles de simulation et niveaux d'abstraction

Grâce à la puissance de calcul des systèmes actuels, la simulation des protocoles de cohérence est la solution privilégiée de nos jours.

Néanmoins, le modèle de simulation pourra avoir une précision très variable. Il pourra être décrit très précisément au niveau du *bit* et du cycle d'horloge mais sa simulation sera lente, ou bien être abstrait permettant ainsi d'atteindre des vitesses de simulation élevées.

Il est très difficile d'abstraire un protocole de cohérence mémoire et d'obtenir des résultats précis qui prennent en compte toutes les implications des détails de l'architecture. En effet, les interactions entre le protocole de cohérence et l'accès aux données a des effets de bord non négligeables et difficiles à modéliser.

De plus, lorsque l'on compare des implantations de protocoles il est très difficile de savoir si la différence de performance observée est due aux caractéristiques intrinsèques du protocole, ou bien à la qualité de l'implantation qui en a été faite.

Utiliser des modèles de simulation permet de répondre en partie à la question posée. Néanmoins, il reste le problème suivant : comment comparer précisément des protocoles de cohérence, par nature très dynamiques, de façon à abstraire les détails de l'implantation mais tout en continuant de modéliser les effets de bord et les interactions?

#### 2.7 Migration des données dans la puce

L'usage de la mémoire cache ne répond pas à tous les problèmes liés aux accès mémoire et en pose de nouveaux.

#### 2.7.1 La pénalité d'échec

Dans un système comprenant des dizaines de nœuds de calcul et bancs mémoire, la distance entre un nœud et la donnée sur laquelle il travaille peut être très grande.

L'usage des caches ne permet pas de diminuer la pénalité d'échec, mais seulement d'en réduire le nombre. Les échecs en cache ont une pénalité d'accès (latence) élevée. Tenter de réduire indéfiniment le taux d'échec est une mauvaise solution car elle implique une croissance de la taille des caches dont le coût en surface et en temps d'accès deviendrait prohibitif.

Au lieu de réduire le taux d'échec, il serait intéressant de réduire la pénalité d'échec. Une telle solution pourra être complémentaire à l'usage des caches.

#### 2.7.2 La congestion sur un banc mémoire

Les caches permettent de réduire le nombre d'accès réalisés aux bancs mémoire. Néanmoins, un nombre élevé de processeurs accédant à des données se trouvant physiquement dans le même banc mémoire peut créer un point de congestion.

Un point de congestion aura des conséquences dramatiques sur l'ensemble du système. A l'instar de la congestion d'accès sur un bus, la congestion d'accès sur un banc mémoire augmente de façon dramatique la latence d'accès aux données.

Ce problème est d'autant plus pertinent que notre contexte d'étude se focalise sur les architectures multiprocesseurs à mémoire partagée. Il convient donc de trouver une solution à ce problème qui n'est résolu qu'en partie par l'usage de la mémoire cache.

#### 2.7.3 Surface utile

L'usage des caches pose un nouveau problème : l'occupation de surface utile. En effet, l'utilisation massive des caches réduit la surface utile de la puce à cause de la duplication massive des données. La surface occupée par les caches pourrait être mise à profit pour stocker des données à exemplaire unique, avoir des processeurs supplémentaires ou encore réduire la taille de la puce. L'idéal serait un système offrant les même performances d'accès que les caches tout en maximisant la surface utile de la puce.

#### 2.7.4 La solution aux problèmes ou les problèmes de la solution?

Une solution qui permet de répondre à ces trois problèmes à la fois est de déplacer les données entre les différents bancs mémoire afin d'optimiser leur placement. Dans un système idéal, les données manipulées par une tâche sont placées dans le banc mémoire qui se trouve à proximité. Dans notre contexte d'étude, nous ne faisons aucune hypothèse sur le logiciel. Il est fort probable que les tâches en cours d'exécution ne soient pas confinées à un seul processeur, et qu'elles migrent en fonction de la charge des nœuds et des décisions du système d'exploitation.

Quelle que soit la solution envisagée, il faudra répondre à trois questions fondamentales : quand ? ou ? et comment ?

**Quand :** le déplacement des données peut se faire *a priori* (anticipation) ou *a posteriori* (réaction). Cette dernière solution est très certainement la plus simple à réaliser mais en contre partie, le déplacement des données risque d'être toujours en retard. Au contraire, si l'on est en mesure d'anticiper de façon juste le comportement dynamique de l'application, il sera possible de réagir au bon moment pour déplacer les données utilisées. Toute la difficulté est là, comment anticiper le comportement d'une tâche lorsque l'on n'a aucune hypothèse sur son implantation?

**Où:** si dans le système les tâches travaillent uniquement sur des données privées, il est aisé de répondre à la question : les données doivent être placées au plus proche de la tâche qui les utilise. Dans un système multi-tâche et multiprocesseur, les données peuvent être partagées par plusieurs tâches s'exécutant sur plusieurs processeurs simultanément. Où doit-on placer les données afin d'améliorer les performances de l'ensemble du système ? Si l'on place systématiquement les données au « centre » de la puce, ne risque-t-on pas de créer des points de congestion ?

**Comment :** même si l'on arrive à répondre convenablement aux questions précédentes, comment réaliser le transfert des données ? Dois-t-on utiliser une solution logicielle ou bien une solution gérée par le matériel ? Comment anticiper ou détecter le besoin de migrer des données ?

#### 2.8 Conclusion

Nous avons soulevé ici un grand nombre de problèmes liés à notre contexte d'étude. Dans le cadre des systèmes multiprocesseurs à mémoire partagée et distribuée, intégrée dans la puce, comment fournir un accès transparent et efficace aux données? L'efficacité touche trois aspects : la latence d'accès, la simplicité d'usage et finalement l'énergie consommée lors des accès mémoire.

Ce problème global va être abordé par trois aspects disjoints mais complémentaires : l'étude des protocoles de cohérence des caches, une méthode de comparaison et d'évaluation des protocoles de cohérence, et enfin le placement ou déplacement des données dans le système.

Nous pouvons ainsi énumérer les principaux problèmes qu'il conviendra de résoudre :

- L'évolution des contraintes dans les systèmes embarqués remet-elle en cause les choix réalisés quand aux protocoles de cohérence des données à utiliser?

- L'utilisation d'un protocole de cohérence simple, write-through invalidate est-elle envisageable dans les systèmes multiprocesseurs intégrés?

- Comment comparer précisément des protocoles de cohérence de façon à abstraire les détails de l'implémentation mais tout en continuant de modéliser les effets de bord et les interactions?

- Comment placer ou déplacer les données sur une puce afin d'améliorer l'efficacité des accès ?

- Comment réduire la pénalité d'échec d'accès aux caches ?

# Première partie

# **Chapitre 3**

### Caches et cohérence des données

Ans ce chapitre nous aborderons les notions de base concernant les caches. Nous passerons en revue les différentes solutions proposées pour le maintien de la cohérence des données dans un système. Finalement, nous nous positionnerons vis-à-vis de ces solutions et des multiples travaux de la communauté scientifique sur le sujet.

#### 3.1 Cache: minimiser la latence et la bande passante

La mémoire cache a été inventée en 1962 [BCP62] comme un moyen de diminuer efficacement la latence d'accès aux données. Elle est également utilisée [Goo83] pour diminuer la bande passante utilisée sur les liens de communication.

Un cache est une mémoire d'accès rapide (S-RAM par exemple) située à proximité de l'unité de calcul d'un processeur. Le cache contient un sous ensemble (copie) des données présentes en mémoire.

#### 3.1.1 Accès au cache

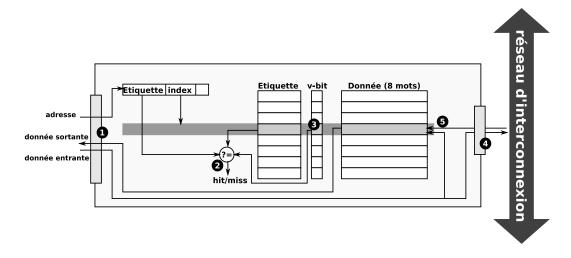

Lorsque le processeur a besoin d'accéder à une donnée (lecture ou écriture) il envoie la requête au cache  $\bullet$  (cf. figure 3.1). Le contrôleur vérifie la présence de la donnée en cache à l'aide d'une comparaison  $\bullet$  avec l'étiquette ou TAG de la ligne sélectionnée par l'index ll vérifie également l'état et la validité de la ligne à l'aide des bits de contrôle  $\bullet$ . Si les tests réussissent, l'accès est un succès (hit) sinon, c'est un échec (miss).

En général (cela dépend de la politique de mise à jour mémoire), en cas de *hit* la requête est traitée localement. Si c'est une lecture, la donnée est fournie au processeur au cycle d'exécution suivant (quelques cycles pour les caches de grande taille). Si c'est une écriture, la donnée est mise à jour ainsi que les bits de contrôle.

Lors d'un *miss*, la requête est envoyée **4** à la mémoire. Pour les lectures, la donnée reçue sera fournie au processeur mais elle sera également placée dans le cache. Les communications entre le cache et la mémoire se font à la granularité de la ligne. Ainsi, pour placer la nouvelle ligne en cache il faudra potentiellement évincer une donnée **5** et mettre à jour le *TAG* et les bits de contrôle.

<sup>&</sup>lt;sup>1</sup>bits de poids fort de l'adresse

<sup>&</sup>lt;sup>2</sup>portion de bits contiguë à l'étiquette

FIG. 3.1 – Différentes étapes de l'accès à un cache à correspondance directe.

#### 3.1.2 Choix des données, associativité et ordre d'évincement

Lors d'un évincement, le choix de la ligne à remplacer dépend de l'algorithme choisi. Lorsqu'un cache est à correspondance directe (*direct mapped*) la question ne se pose pas et l'emplacement est choisi par son index (cf. figure 3.1).

Dans un cache associatif (partiellement ou totalement), le choix de la ligne peut être fait au hasard, dans un ordre FIFO<sup>3</sup> ou LRU<sup>4</sup>. Chacun de ces algorithmes a ses avantages et inconvénients, le plus performant mais également le plus coûteux à implanter est le LRU.

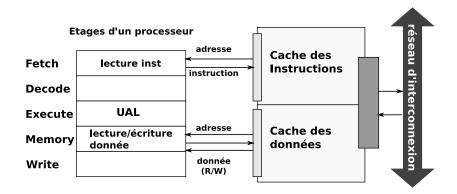

#### 3.1.3 Le cache des instructions

Un processeur peut requérir deux types de données (au sens physique) : des instructions et des données (au sens programme). La plupart des architectures courantes sont de type Harvard où l'accès aux instructions et aux données se fait à des caches différents (figure 3.2) par des ports différents. Ceci permet à un processeur à plusieurs étages (*pipeline*) de ne pas avoir des conflits d'accès au cache par les étages responsables de la lecture d'une instruction et de l'accès aux données.

Dans ce type d'architecture, le cache des instructions et le cache des données sont séparés et fonctionnent de façon indépendante. Néanmoins, le contrôleur de cache peut n'avoir qu'une seule interface sur le réseau. En cas de conflit, les requêtes aux données sont en général prioritaires.

### 3.2 Politiques de mise à jour mémoire

En cas d'écriture, il existe deux politiques de mise à jour mémoire : *write-through* et *write-back*.

*Write-through*: lors d'une écriture, la requête est toujours propagée à la mémoire. Ainsi, la mémoire possède à tout instant la dernière valeur écrite par le processeur. Si lors de l'écriture

<sup>&</sup>lt;sup>3</sup> *first-in first-out* : premier arrivé, premier servi

<sup>&</sup>lt;sup>4</sup>Least Recently Used, le moins récemment utilisé

FIG. 3.2 – Architecture Harvard, les accès aux instructions et aux données se font indépendamment.

la donnée est en cache, celle-ci est également mise à jour.

Un avantage de cette politique c'est que lors d'un échec en lecture, la ligne de cache qui est évincée n'a pas besoin d'être recopiée en mémoire.

*Write-back*: dans le cas d'une écriture, si la donnée est présente dans le cache alors la requête est traitée localement. Un bit de contrôle permet d'indiquer que cette ligne est modifiée (noté M ou D pour *Dirty*). Aucun accès à la mémoire n'est nécessaire, on économise ainsi de la bande passante sur le lien de communication.

Si la donnée n'est pas en cache, on applique en général une politique *write-allocate*. Dans ce cas, la donnée est préalablement lue en mémoire et mise en cache; elle est ensuite modifiée localement.

Lors d'un échec en lecture (ou d'écriture avec allocation) il faut écrire la ligne évincée en mémoire si celle-ci est marquée comme étant modifiée. Cette écriture peut toutefois être réalisée après la lecture de la ligne afin de débloquer au plus tôt le processeur.

#### 3.3 Cohérence des données

Comme nous l'avons vu dans le problématique (cf. section 2.5.1, page 10), un des problèmes majeur des systèmes multiprocesseurs est le maintien de la cohérence des données. Nous n'aborderons pas ici la cohérence des données faite de manière logicielle car celle-ci a été écartée de notre contexte d'étude. Afin de maintenir la cohérence des données dans un système, il y a deux façons de procéder :

**Diffusion des écritures :** lorsqu'un processeur émet une écriture, la valeur est diffusée dans le système et toutes les copies sont mises à jour. Cette technique est rarement utilisée car sa mise en œuvre est complexe à cause de certaines difficultés et limitations. En effet, la propagation des données à chaque écriture consomme de la bande passante. De plus, les conflits d'accès au cache par les requêtes provenant du processeur et celles reçues de l'extérieur peuvent nuire aux performances du système.

**Invalidations lors des écritures :** lorsqu'un processeur émet une écriture, toutes les copies du système sont invalidées. Nous sommes dans un schéma « plusieurs lecteurs, un seul écrivain ». Cette technique est de loin la plus utilisée de part sa simplicité de mise en œuvre et

d'un certain nombre d'avantages. Le premier avantage est une économie substantielle de la bande passante. En effet, seul un nombre restreint des données invalidées seront à nouveau accédées par les nœuds concernés (*miss* en cache). Deuxièmement, l'invalidation d'une ligne mémoire se fait très simplement par la mise à zéro des bits de contrôle du TAG. De plus, afin de minimiser l'interférence entre les accès du processeur local et les invalidations en provenance des autres caches, le contrôleur peut avoir un double du *TAG* pour traiter efficacement les invalidations (cf. figure 3.3).

Nous ne détaillerons pas davantage les tenants et aboutissants de ces deux façons de procéder. Dans nos travaux nous supposons l'usage d'un protocole à invalidations.

Nous présentons ici les différentes techniques gérées par le matériel pour maintenir la cohérence des données. Il existe deux grandes familles d'interconnexion, les bus et les autres (point-à-point). Pour chacune de ces familles il existe une technique appropriée.

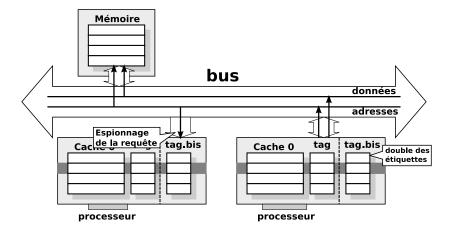

#### 3.3.1 Bus: espionnage

Les bus sont un moyen d'interconnexion simple et peu coûteux à mettre en œuvre. C'est un moyen de communication partagé par tout les intervenants, c'est-à-dire qu'il ne peut y avoir qu'un seul composant à la fois qui puisse émettre une requête.

Lorsqu'un composant émet une requête les autres peuvent néanmoins « l'observer » comme on peut le voir dans la figure 3.3. Cet espionnage (*snooping*) du bus est utilisé pour maintenir la cohérence des données. Ainsi, les caches vont continuellement espionner les requêtes qui transitent sur le bus. En cas d'une écriture ils peuvent décider d'invalider leur copie ou mettre à jour la valeur. En cas de lecture, ils peuvent changer l'état de partage de la copie ou encore émettre sur le bus la version modifiée qu'ils possèdent.

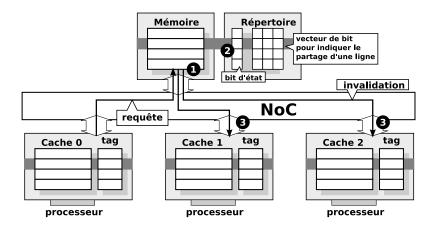

FIG. 3.3 – Espionnage des requêtes sur bus.