## Modèle de Gestion Hiérarchique Distribuée pour la Reconfiguration et la Prise de Décision dans les Équipements de Radio Cognitive

Loig Godard

#### ▶ To cite this version:

Loig Godard. Modèle de Gestion Hiérarchique Distribuée pour la Reconfiguration et la Prise de Décision dans les Équipements de Radio Cognitive. Micro et nanotechnologies/Microélectronique. Université Rennes 1, 2008. Français. NNT: . tel-00355352

## HAL Id: tel-00355352 https://theses.hal.science/tel-00355352

Submitted on 22 Jan 2009

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

Nº d'ordre : 3850

## **Thèse**

présentée devant

l'Université de Rennes 1

pour obtenir le titre de

## Docteur de l'université de Rennes 1

spécialité : Électronique

# Modèle de Gestion Hiérarchique Distribuée pour la Reconfiguration et la Prise de Décision dans les Équipements de Radio Cognitive

par Loïg GODARD

Soutenue le 18 / 12 / 2008 devant la commission d'examen :

Rapporteurs M. Apostolos Kountouris Ingénieur de recherche Orange Labs

M. Jean-Luc Dekeyser Professeur des universités Université de Lille

Examinateurs Mme Fabienne Uzel-Nouvel Maître de conférence INSA

M. Olivier Sentievs Professeur des universités Université Rennes 1

M. Christophe Moy Professeur SUPELEC

M. Jacques Palicot Professeur SUPELEC

**SUPELEC**

Institut d'Électronique et de Télécommunications de Rennes Signal, Communication et Electronique Embarquée

## Remerciements

En premier lieu, je tiens à remercier Christophe MOY pour m'avoir encadré durant mes trois années de thèse et éclairé de ses précieux conseils. Je tiens aussi à remercier Jacques Palicot, responsable de l'équipe SCEE, pour m'avoir accueilli et avoir pris de son temps pour participer à diverses discutions relatives à cette thèse. Ces discussions, lors desquelles chacun exprimait son point de vue et qui finissaient par prendre Christophe à partie pour trancher pour l'une ou l'autre des propositions, m'ont énormément apportées d'un point de vue personnel. Je les remercie tous deux pour m'avoir permis de prendre part à diverses activités en dehors du simple cadre de cette thèse en me faisant toute confiance sur ma possibilité d'effectuer ces activités en parallèle avec mon travail de thèse.

Je tiens également à remercier l'ensemble des membres de mon jury avoir accepté de juger et évaluer ces travaux de thèse. Je remercie sincèrement Olivier Sentieys, Professeur des universités Université Rennes 1 à l'ENSSAT de Lannion d'avoir présidé le jury lors de ma soutenance. Je remercie également Apostolos Kountouris Ingénieur de recherche Orange Labs ainsi que Luc Dekeyser Professeur des universités Université de Lille pour l'attention qu'ils ont accordés à la lecture de ce manuscrit ainsi que pour leur participation au jury. Je remercie aussi Fabienne Uzel-Nouvel Maître de conférence à l'INSA de rennes pour avoir pris de son précieux temps pour assister à ma soutenance.

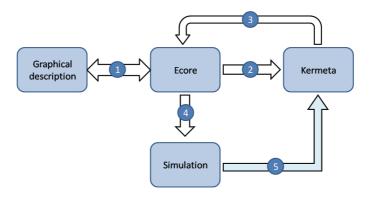

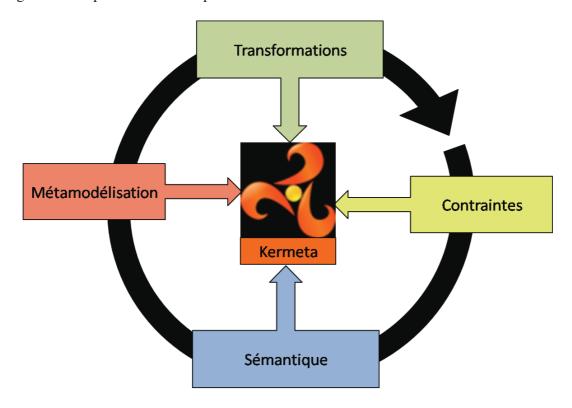

En outre je remercie aussi particulièrement Didier Vojtisek ainsi que Gilles Perrouin, membres de l'équipe Triskell à l'INRIA Rennes, pour m'avoir initié à Kermeta et avoir toujours répondu présent lors de l'élaboration du simulateur HDCRAM.

Pour finir je remercie l'ensemble des membres de l'équipe SCEE (permanents, post-doctorants et doctorants) pour leur bonne humeur au quotidien et à la bonne ambiance générale au sein de l'équipe qui m'ont beaucoup apportés tant sur le plan personnel que professionnel. Ainsi, j'aimerais remercier particulièrement Yasser l'imperturbable et grand maître rush péon, Olivier le graphiste qui a égayé notre bureau de son art, Amor pour sa joie de vivre, Julien le bout en train, Fred le maître de la compilation du noyau Free BSD, Nico, Fanch, Jérôme, Mihai et Marius pour leur convivialité et leur accueil. Je tiens aussi à remercier l'ensemble du personnel SUPELEC, tant le 5050 pour leur intervention rapide sur les problèmes informatiques que les secrétaires pour leurs rapidité dans la gestion des diverses tâches administratives. Je tiens aussi à remercier le personnel de l'équipe de restauration de la Sodex'ho pour leur bonne humeur et leur sourire au quotidien

Je ne pourrais terminer ces remerciements sans y faire mention de ma famille et de mes amis qui m'ont soutenu et épaulé durant ces trois années de thèse. Un grand merci à tous.

## Table des matières

| A  | crony | mes & A | Abréviations                                                            | 1  |

|----|-------|---------|-------------------------------------------------------------------------|----|

| In | trodu | ction   |                                                                         | 5  |

| 1  | La r  | adio lo | gicielle                                                                | 13 |

|    | 1.1   | La nai  | ssance du concept de Radio Logicielle                                   | 13 |

|    |       | 1.1.1   | Définition et généralités                                               | 13 |

|    |       | 1.1.2   | Contraintes et besoins pour les architectures Radio Logicielle .        | 17 |

|    |       | 1.1.3   | Quelques exemples de travaux industriels et académiques                 | 18 |

|    | 1.2   |         | ormes matérielles et architectures logicielles pour la radio logicielle | 19 |

|    |       | 1.2.1   | Les ressources matérielles                                              | 19 |

|    |       | 1.2.2   | Composition hétérogène de la plateforme d'exécution                     | 24 |

|    |       | 1.2.3   | Exemples de projets "historiques" de la RL                              | 26 |

|    |       | 1.2.4   | Gestion logicielle des ressources hétérogènes                           | 27 |

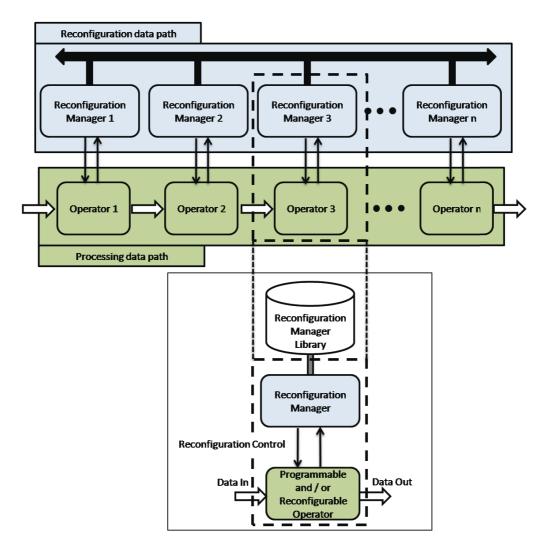

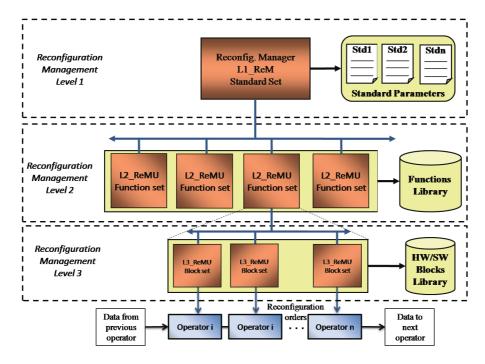

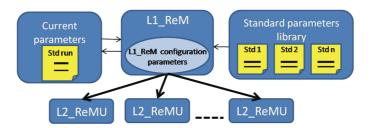

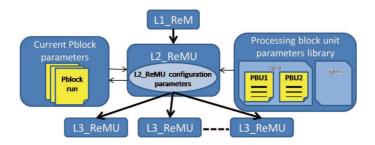

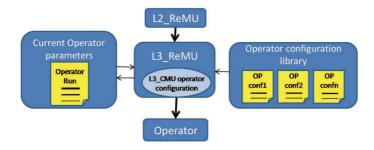

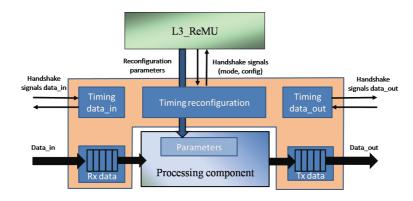

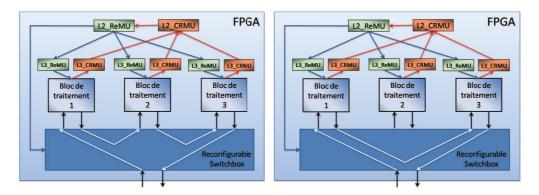

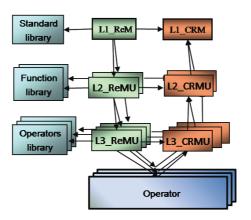

|    | 1.3   | Une an  | rchitecture logicielle de gestion de reconfiguration : le HDReM         | 29 |

|    |       | 1.3.1   | Présentation                                                            | 29 |

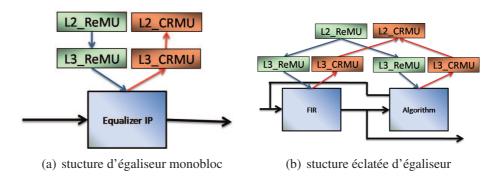

|    |       | 1.3.2   | Opérateurs de traitement                                                | 36 |

|    |       | 1.3.3   | Exemples de réalisations                                                | 37 |

|    | 1.4   | Concl   | usion                                                                   | 44 |

| 2  | La r  | adio co | ognitive                                                                | 45 |

|    | 2.1   | La nai  | ssance du concept Radio Cognitive                                       | 45 |

|    |       | 2.1.1   | Définition et généralités                                               | 45 |

|    |       | 2.1.2   | Contraintes et besoins pour les architectures Radio Cognitives .        | 48 |

|    | 2.2   | Les be  | esoins d'un équipement radio cognitif                                   | 53 |

|    |       | 2.2.1   | Les différents moteurs d'intelligence possibles                         | 53 |

|    |       | 2.2.2   | Les architectures de gestion cognitive                                  | 58 |

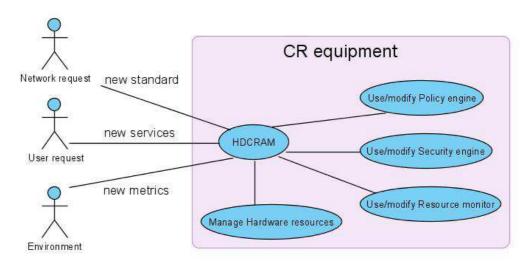

|    | 2.3   | Une an  | rchitecture radio cognitive : le HDCRAM                                 | 60 |

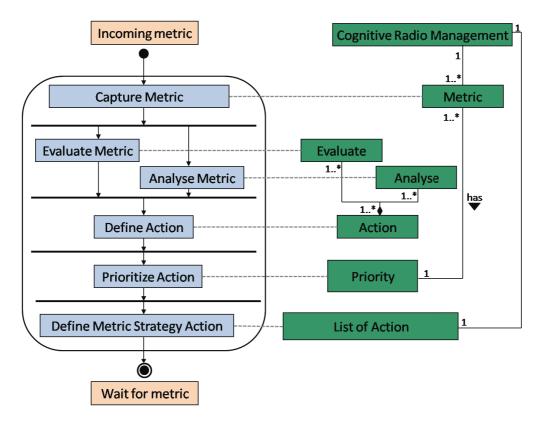

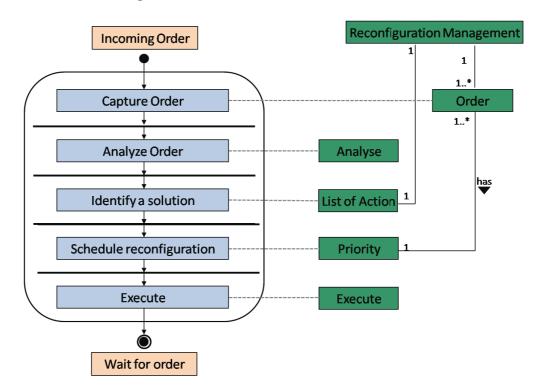

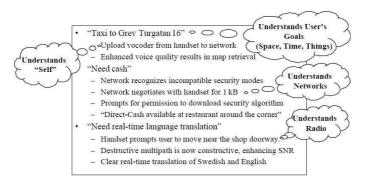

|    |       | 2.3.1   | Du rôle de chaque partie                                                | 62 |

|    |       | 2.3.2   | De l'acquisition des données à la réaction du système                   | 64 |

|    |       | 2.3.3   | Détail du fonctionnement de l'architecture                              | 66 |

|    |       | 2.3.4   | Exemples d'application                                                  | 69 |

|    | 2.4   | Concl   |                                                                         | 73 |

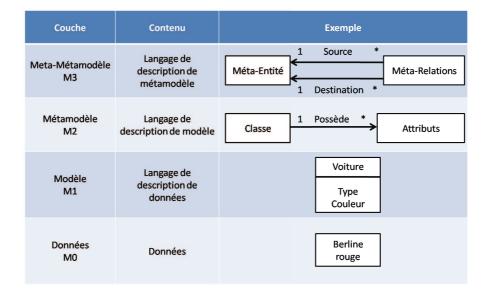

| 3  | Unı   | métamo  | odèle exécutable                                                        | 75 |

|    | 3.1   | Une ne  | ouvelle approche de conception                                          | 75 |

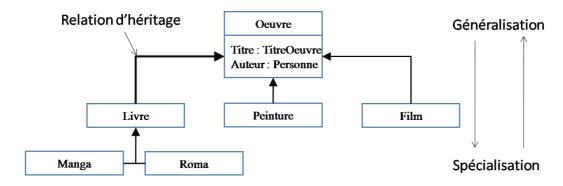

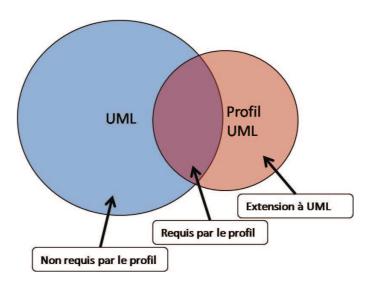

|    |        | 3.1.1 Le langage orienté objet                                |  |  |    | 76  |

|----|--------|---------------------------------------------------------------|--|--|----|-----|

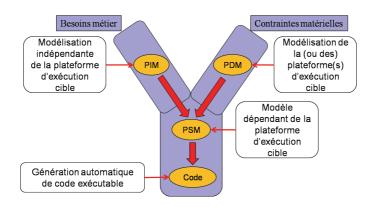

|    |        | 3.1.2 L'approche MDA                                          |  |  |    | 77  |

|    | 3.2    |                                                               |  |  | 81 |     |

|    |        | 3.2.1 Modélisation UML                                        |  |  |    | 82  |

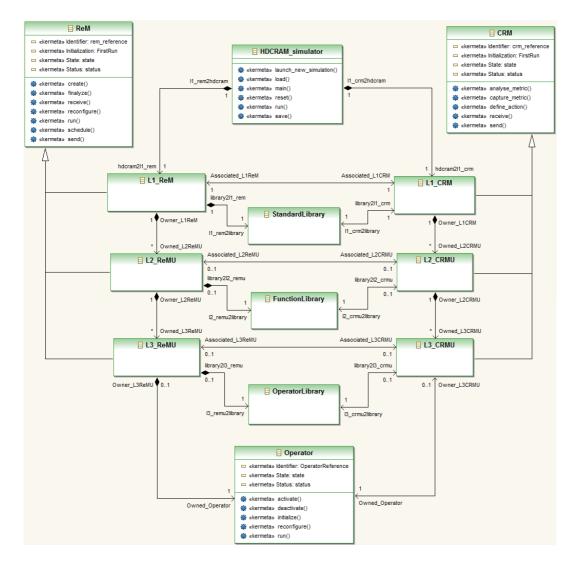

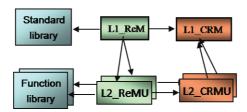

|    |        | 3.2.2 Métamodèle HDCRAM                                       |  |  |    | 86  |

|    |        | 3.2.3 Vers un métamodèle exécutable                           |  |  |    | 93  |

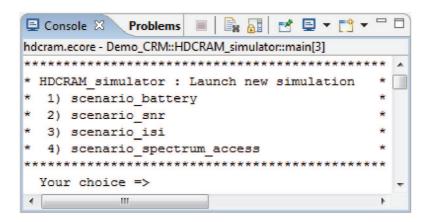

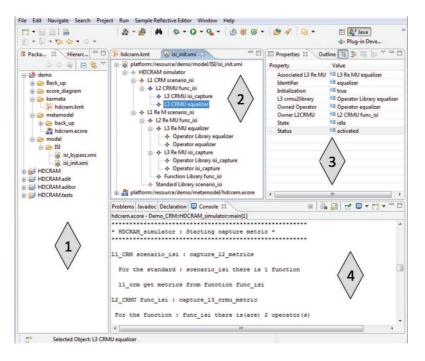

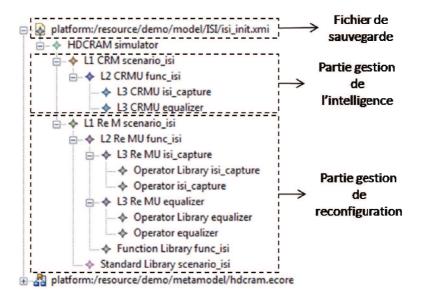

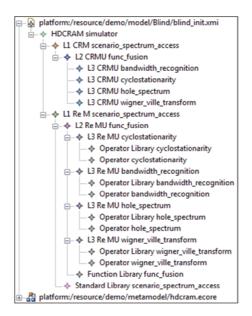

|    | 3.3    | Le simulateur HDCRAM                                          |  |  |    | 95  |

|    |        | 3.3.1 Création du métamodèle exécutable HDCRAM à l'aid        |  |  |    |     |

|    |        | 3.3.2 Résultat : un métamodèle exécutable                     |  |  |    | 96  |

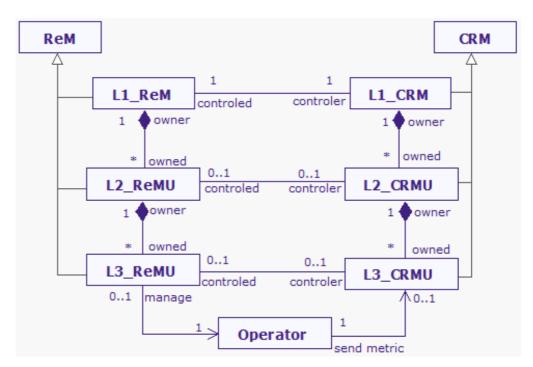

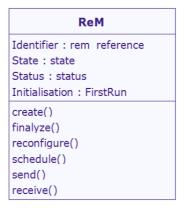

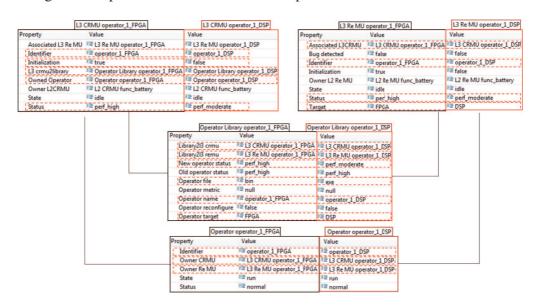

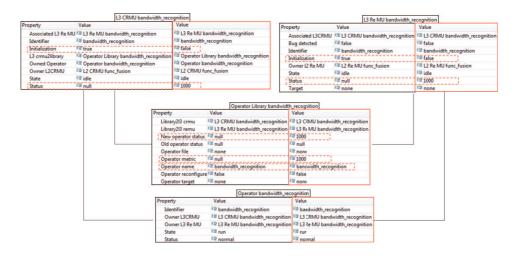

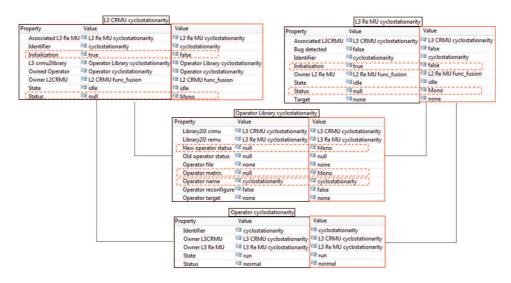

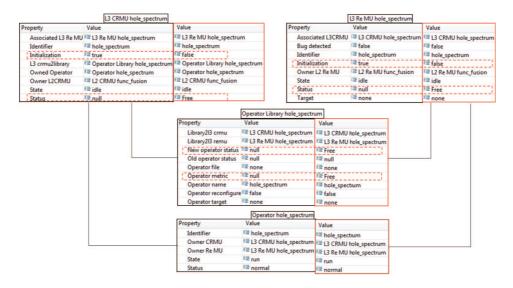

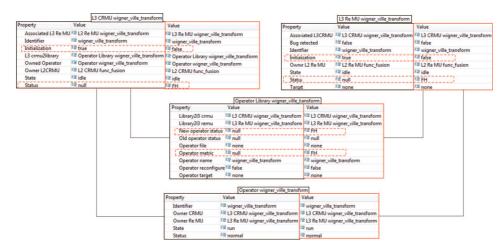

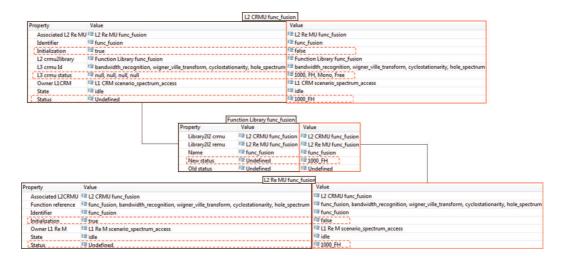

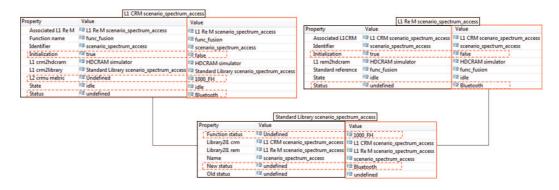

|    |        | 3.3.3 Classes ReM                                             |  |  |    | 99  |

|    |        | 3.3.4 Classes CRM                                             |  |  |    | 102 |

|    |        | 3.3.5 Super Classe Operator                                   |  |  |    | 103 |

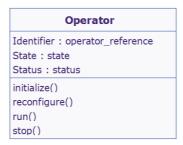

|    |        | 3.3.6 Déploiement du métamodèle exécutable                    |  |  |    | 105 |

|    | 3.4    | Conclusion                                                    |  |  | •  | 108 |

| 4  | Scén   | arios                                                         |  |  |    | 111 |

|    | 4.1    | Introduction                                                  |  |  |    | 111 |

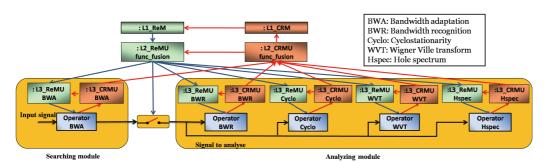

|    | 4.2    | Présentation de l'environnement de travail                    |  |  |    | 113 |

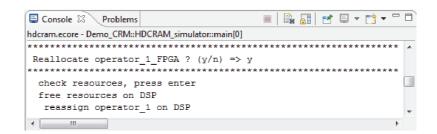

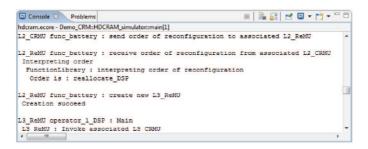

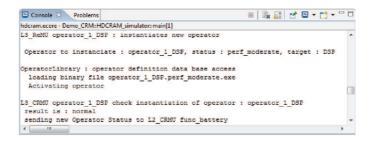

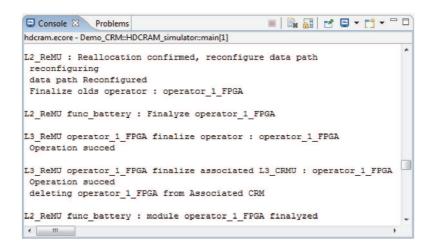

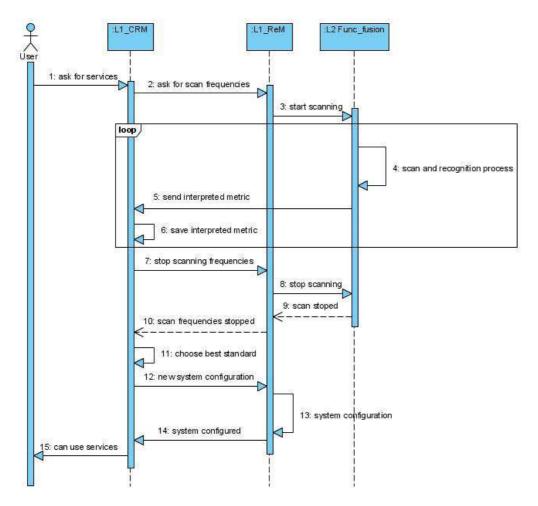

|    | 4.3    | Scénario1: Reconfiguration d'un chemin de données             |  |  |    | 114 |

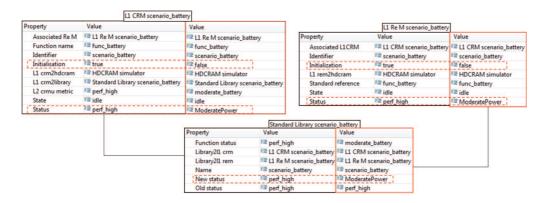

|    | 4.4    | Scénario2 : Adaptation aux variations de niveau de batterie . |  |  |    | 125 |

|    | 4.5    | Scénario3: accès opportuniste au spectre                      |  |  |    | 140 |

|    | 4.6    | Synthèse des scénarios                                        |  |  |    | 151 |

|    | 4.7    | Conclusion                                                    |  |  |    | 152 |

| Co | onclus | sion générale                                                 |  |  |    | 153 |

| Aı | nexes  | s                                                             |  |  |    | 157 |

| Li | ste de | s tableaux                                                    |  |  |    | 189 |

| Li | ste de | s figures                                                     |  |  |    | 191 |

| Co | ontrib | utions de l'auteur                                            |  |  |    | 195 |

| Bi | bliogr | aphie                                                         |  |  |    | 199 |

## **Acronymes & Abréviations**

La signification d'une abréviation ou d'un sigle n'est souvent indiquée que lors de sa première apparition dans le texte. Il existe dans la plupart des cas une abréviation en français et une abréviation en anglais. Dans les deux cas, les deux abréviations sont données une première fois et nous employons ensuite l'abréviation la plus usuelle, celleci étant le plus souvent celle en anglais.

| 3G   | 3 <sup>e</sup> Génération de téléphonie mobile |

|------|------------------------------------------------|

| 4G   | 4 <sup>e</sup> Génération de téléphonie mobile |

| ANFR | Agence Nationale des Fréquences                |

| API  | Application Programming Interface              |

ARCEP Autorité de Régulation des Communications Électroniques et des

Postes

ASIC Application Specific Integrated Circuit

ASIP Application Specific Instruction set Processor

ASSP Application-Specific Standard Product

ATSC Advanced Television Systems Committee

BTS Base Transceiver Station

CAN Convertisseur Analogique Numérique

CEPT Conférence Européenne des Postes et Télécommunications

CIM Computation Independent Model

CNA Convertisseur Numérique Analogique

CORBA Common Object Request Broker Architecture

CR Cognitive Radio

CRM Cognitive Radio Management

CRMU Cognitive Radio Management Unit

CSA Conseil Supérieur de l'Audiovisuel

DSA Dynamic Spectrum Access

DSP Digital Signal Processor

DTMB Digital Terrestrial Multimedia Broadcast

DVB Digital Video Broadcasting

EDGE Enhanced Data rates for GSM Evolution FCC Federal Communications Commission

FI Fréquence intermédiaire FIR Finite Impulse Response

FPGA Field Programmable Gate Array

GALS Globally Asynchronous Locally Synchronous

GIPS Giga Instruction per second

GPP General Purpose Processor

GPRS General Packet Radio Service

GPS Global Positionning System

GSM Global System for Mobile communications

HDCRAM Hierarchical and Distributed Cognitive Radio Management HDREM Hierarchical and Distributed Reconfiguration Management

HSDPA High Speed Downlink Package Access

INTERRAP Integration of Reactive Behavior and Rational Planning

IP Intellectuel Property

ISDB Integrated Services Digital Broadcasting

ISI Intersymbol Interference

MDA Model Driven Architecture

MDE Model Driven Engineering

MEMS Micro Electro Mechanical Systems

NoC Network on Chip

OCL Object Constraint Language

OS Operating System

OFDM Orthogonal Frequency Division Multiplexing

OMG Object Management Group

P-HAL Physical-Hardware Abstraction Layer

PIM Platform Independent Model

PSM Platform Specific Model

QAM Quadrature Amplitude Modulation

QoS Quality of Service

REM Reconfiguration Management

REMU Reconfiguration Management Unit

RC Radio Cognitive RF Radiofréquence

RFI Request For Information

RKRL Radio Knowledge Representation Language

RL Radio Logicielle

RLR Radio Logicielle Restreinte

RR Règlement des Radiocommunications

RTOS Real Time Operating System SSC Shared Spectrum Company

SCA Software Communication Architecture

SDR Software Defined Radio

TNS Traitement Numérique du Signal

UIT Union internationale des télécommunications UMTS Universal Mobile Telecommunications System

UML Unified Modeling Language

Very-High-Speed Integrated Circuit Hardware Description Lan-VHDL

guage

Wireless Fidelity ou IEEE802.11b WiFi Wireless Local Area Network WLAN

## Introduction

L'ère des radiocommunications que nous connaissons actuellement a connu ses débuts en 1876 avec l'invention du téléphone fixe par le Canadien Graham Bel, suivie onze ans plus tard par la découverte des ondes radios par le physicien allemand Heinrich Hertz et l'établissement par Guglielmo Marconi des premières liaisons radio en 1895 sur un peu plus de 2 km et en 1901 à travers l'Atlantique. Les bases étaient ainsi posées pour permettre l'établissement de communications fixes dans un premier temps puis mobiles. C'est en 1985 que la Commission Européenne imposa la norme GSM. Deux années plus tard fut signé le MOU (*Mémorandum Of Understanding*) par les exploitants des réseaux de treize pays européens pour la mise en œuvre du système cellulaire numérique européen. Il faut attendre 1991 pour que la première communication entre un abonné fixe et un mobile soit réalisée, avec le succès planétaire que l'on connait depuis.

Depuis l'effervescence ne cesse de croître et a engendré de nouveaux besoins en terme d'exigence. Un exemple en termes de nouveau service est l'explosion d'internet qui a amené naturellement la convergence vers l'internet mobile. Les limites de la norme GSM sont alors atteintes. En effet le débit de 9,6 kilobits par seconde (kb/s) défini à l'origine est loin d'être satisfaisant pour couvrir les nouveaux besoins de transferts de données et constitue un frein à la diffusion de contenus multimédias. De nouvelles normes sont alors mises au point telles que le GPRS (débit de 115 kb/s), EDGE (débit de 384 kb/s), l'UMTS dans sa version dite R99, pour Release 1999, (débit allant de 384 kb/s pour tout le monde en mode mobile et jusqu'à 2 Mb/s en situation "fixe") ou encore UMTS HSDPA qui garantit les débits de 2 Mb/s initialement prévus pour l'UMTS. L'ensemble de ces valeurs est présenté dans le tableau suivant.

**TAB. 2:** Norme de téléphonie mobile et débits

| Norme                | GSM  | GPRS | EDGE  | UMTS (R99) | UMTS (HSPA) |

|----------------------|------|------|-------|------------|-------------|

| Technologie          | 2G   | 2.5G | 2.75G | 3G         | 3.5G        |

| Année d'utilisation  | 1990 | 2003 | 2005  | 2004       | 2006        |

| Débit maximum (kb/s) | 9.6  | 171  | 384   | 2000       | 3600        |

| Débit réel (kb/s)    | 9.6  | 30   | 177   | 384        | 3400        |

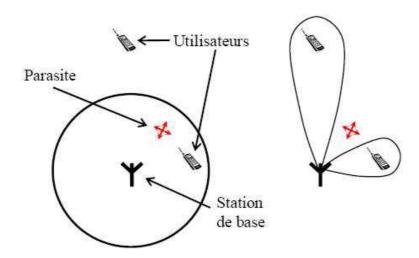

La croissance du nombre d'utilisateurs (en France : de 11 millions en avril 1999 à plus de 52 millions en septembre 2007, plus de 3 milliards d'abonnés dans le monde fin 2007) ainsi que l'apparition de nouvelles normes conduisent à une situation problématique dans la gestion du spectre des radiofréquences (RF) avec un fort encombrement

et la présence d'interférences entre les systèmes. En 2002 l'organisme de régulation et de gestion du spectre aux États-Unis, la *Federal Communications Commission* (FCC), a créé un groupe de réflexion devant travailler sur la pénurie des ressources fréquentielles.

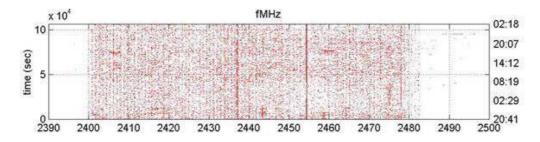

Les mesures préliminaires effectuées par ce groupe mettent en évidence le besoin de plus de flexibilité dans la gestion du spectre. En effet, alors que certaines bandes sont intensivement utilisées d'autres ne le sont que peu ou pas du tout, comme le montrent les trois figures suivantes qui ont été réalisées par la *Shared Spectrum Company* (SSC [1]) dans la ville de New York le premier septembre 2004.

FIG. 1: Mesures d'occupation de la bande 2390 MHz - 2500 MHz

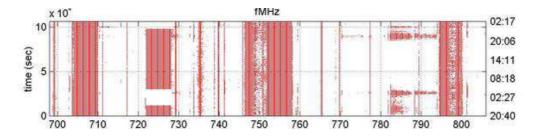

Il apparaît très nettement sur la figure 1 une occupation très importante des bandes de fréquences s'étendant de 2,39 à 2,5 GHz alors que la figure 2 montre une sous-occupation de la bande allant de 700 à 800 MHz aux mêmes heures. Par conséquent, il serait envisageable de mettre en œuvre des accès de type opportuniste permettant l'occupation de ces trous dans les bandes de la figure 2 par des utilisateurs des bandes de la figure 1.

FIG. 2: Mesures d'occupation de la bande 700 MHz - 800 MHz

Ceci est à pondérer par le fait que les bandes non occupées ne sont pas forcément non utilisées. Comme les bandes réservées pour la radio-astronomic, les radars météo, etc. De même, est-ce qu'une bande radar peut être considérée comme inutilisée dans des endroits ou le radar ne porte pas ? Il ne faut surtout pas la perturber avec d'autres signaux. Cette nouvelle possibilité d'utilisation des ressources spectrales pourrait donc apparaître à condition que les politiques d'accès à cette ressource le permettent. L'attribution des ressources spectrales suit en effet depuis une centaine d'années une approche immuable. Ceci en raison principalement des technologies électroniques qui permettaient de mettre en œuvre les liens radio. En effet, jusqu'à présent une allocation statique des fréquences

était systématiquement utilisée : chaque application (ou service) a une bande qui lui est alloué définitivement et exclusivement. On peut par exemple citer la bande 88-108 MHz pour la radio FM ou encore 925-960 MHz pour le GSM 900. Ces bandes ne sont pas attribuées au hasard et sont règlementées à différents niveaux. L'organisation responsable au niveau mondial est le Règlement des Radiocommunications (RR) de l'UIT (Union internationale des télécommunications) qui affecte les bandes de fréquences à des services définis par grandes catégories [Transmission de données, télémesure, télécommande, Téléphonie (y compris la radiodiffusion sonore), Télévision (vidéo), etc.]. Au niveau européen, la Conférence Européenne des Postes et Télécommunications (CEPT) permet de coordonner les différents pays membres pour la normalisation des radiocommunications. En France, c'est le rôle de l'Agence Nationale des Fréquences (ANFr) d'allouer les fréquences. Cette allocation est faite en accord avec :

- les départements ministériels ayant des besoins propres (Défense, Intérieur, Aviation civile, Météo, Espace, etc.),

- le conseil supérieur de l'audiovisuel (CSA) pour la diffusion audiovisuelle,

- l'autorité de régulation des communications électroniques et des postes (ARCEP) pour les communications électroniques).

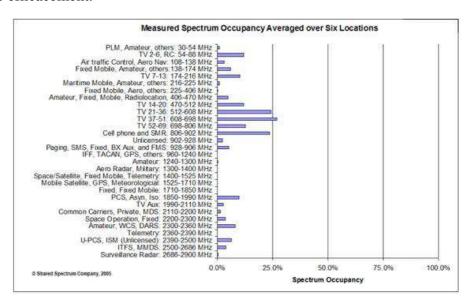

La figure 3 montre de façon évidente qu'une grande partie du spectre radio n'est pas utilisée efficacement.

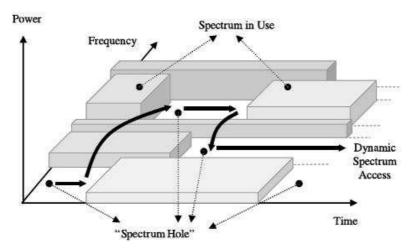

FIG. 3: Mesures d'occupation du spectre dans six villes des ÉTATS-UNIS

Il est donc clair que la pénurie des fréquences n'est qu'artificielle et peut être régulée par une nouvelle politique d'accès plus flexible. En effet, à un moment et à un endroit donné, en parcourant le spectre entièrement, il est possible de trouver une bande de fréquences non utilisée par son propriétaire. Par la mise en service de moyens spécifiques tels que l'accès dynamique au spectre (Dynamic Spectrum Access ou DSA), il serait alors possible d'accéder à cette ressource non utilisée. On appel cela l'accès opportuniste au spectre et il permet un accès dynamique au spectre en vue d'optimiser l'utilisation. Les moyens qui permettraient sa mise en œuvre sont divers tels que la détection de bandes de fréquences libres par le terminal de communication [2], l'identification par géolocalisation [3], [4] ou encore l'identification par signal de contrôle [5].

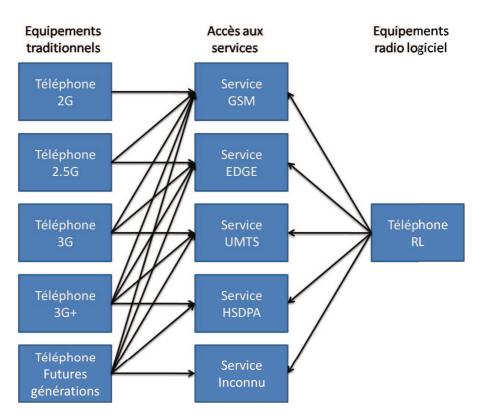

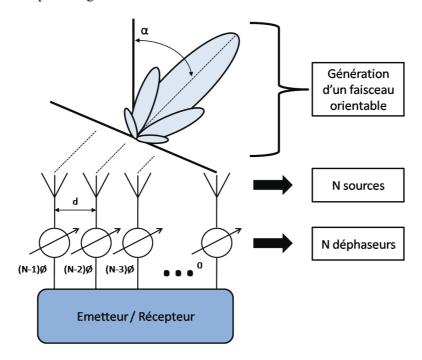

Quelle que soit la méthode retenue afin d'exploiter ces bandes de fréquences libres, le terminal radio devra posséder une interface de communication reprogrammable afin de s'adapter aussi bien en termes de fréquence, de débit, de modulation, etc. Cette possibilité de reprogrammation est permise par une approche flexible du traitement radio apportée par la radio logicielle (RL) [6], [7]. L'approche RL a pour idéal la numérisation du traitement radio juste après l'antenne de réception réciproquement la conversion numérique/analogique avant l'antenne à l'émission. Cette numérisation permet d'une part de rassembler toutes les différentes chaines de traitements spécifiques à un standard radio sur des unités d'exécution communes au lieu de composants spécifiques à chaque fonction de chaque chaîne. D'autre part les logiciels utilisés peuvent être mis à jour ou de nouvelles versions peuvent être téléchargées afin de corriger un bogue ou de permettre l'utilisation de nouvelles fonctionnalités voire d'un nouveau standard radio. En effet, une chaîne de traitement entièrement numérisée permet d'utiliser des processeurs de traitements généraux qui peuvent effectuer une multitude de traitements différents. Ces processeurs exécutent des logiciels et peuvent donc, suivant le logiciel utilisé, effectuer un traitement pour l'un ou l'autre des standards radios. Il est possible de faire une analogie avec le monde informatique qui, avec un ensemble de composants identiques, peut exécuter des applications diverses suivant le logiciel qu'ils exécutent (traitement de texte, lecteur video, jeu, etc.). Cependant, afin de permettre l'utilisation d'une telle technologie dans un équipement radio il faut mettre en place une architecture permettant la gestion de reconfiguration de l'équipement de manière efficace : c'est un point central d'étude de la RL.

Suivant le type de traitement radio à effectuer il est nécessaire d'utiliser différents composants matériels. En effet technologiquement, nous sommes encore loin de pouvoir faire effectuer tous les traitements nécessaires par un seul composant généraliste de type processeur comme ceux proposés par Intel, AMD ou encore IBM. Ceci est encore plus critique dans un contexte embarqué sous fortes contraintes de consommation. Ainsi, certains traitements nécessitent plus de ressources de calcul que d'autres ou encore plus de mémoire. Des composants de traitement différents répondent à cette variété de contraintes. Une plateforme regroupant des unités de traitement de différentes natures (GPP, DSP, FPGA, etc.) est dite hétérogène. Si l'on fait abstraction des difficultés techniques de réalisation et de programmation d'une telle plateforme s'ouvre une nouvelle perspective pour les équipements radio. En effet, un équipement radio logiciel peut donc se reconfigurer à volonté afin de supporter les différents standards existants aussi bien que ceux à venir. La question qui en découle ensuite est : "serait-il possible de permettre à un tel équipement de décider de lui-même de ses paramètres opérationnels afin de s'adapter aux variations de son environnement en temps réel ?" Cette question est traitée

par l'approche nommée Radio Cognitive<sup>1</sup> (RC ou CR en anglais pour *Cognitive Radio*). Une telle faculté donnerait notamment à l'équipement radio la possibilité de trouver des solutions aux nouveaux problèmes de communication posés par les nouvelles contraintes d'utilisation du spectre radio. La FCC a en effet édité de nouvelles règles d'utilisation du spectre dans ses "rulemaking" [8]. Ces règles proposaient pour la première fois de modifier la règle de l'utilisation d'une bande de fréquence à usage unique. Cette nouvelle perspective d'utilisation des ressources spectrales offre donc la possibilité à un équipement de découvrir une bande non utilisée à un moment et un endroit donné pour l'occuper sur une période restreinte, on parle alors d'utilisateur secondaire. Cette agilité est en partie permise par la radio logicielle qui s'est penchée sur les problèmes de reconfiguration ainsi que sur le remplacement de circuits dédiés par des circuits généralistes contrôlés par du logiciel. La RL peut donc servir de base technologique à la radio cognitive qui doit permettre l'adaptation d'un équipement mobile à l'environnement suivant l'application, de façon transparente pour l'utilisateur. En effet, l'adaptation est permise par un contrôle total des ressources matérielles ainsi qu'une architecture permettant de modifier tout ou partie des ressources de traitement en fonction des besoins.

Ainsi, nous pensons que la meilleure piste d'étude pour répondre à ces enjeux est d'utiliser une architecture basée sur l'approche RL et de lui ajouter les fonctionnalités lui permettant d'une part, de prendre conscience de son environnement et d'autre part de prendre des décisions de changement de fonctionnement suivant l'évolution de son environnement. Nous avons donc défini une architecture de gestion cognitive basée sur une architecture de gestion RL que nous présentons dans ce mémoire. Cette architecture présente une séparation des flots de données, des flots de contrôle ainsi que des flots cognitifs. Cette séparation permet de limiter le risque d'apparition de goulots d'étranglement, en termes d'échanges de données, au sein de la structure et représente une approche totalement originale.

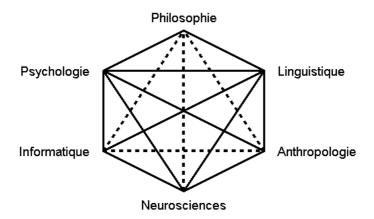

Les structures permettant la mise en œuvre de l'approche RC sont actuellement à l'étude dans de nombreux laboratoires et génèrent un réel investissement de la part des partenaires industriels en vue des retombées économiques espérées. Chacun met en avant sa spécificité pour la résolution d'un type de problème au sein de cette approche. En effet, la RC présente un vaste champ de recherche étendu à plusieurs disciplines scientifiques. On nommera par exemple les sciences inspirées du monde biologique, les science informatiques, les science cognitives ou encore de traitement du signal. Actuellement, deux types de démarches sont à l'étude pour la répartition de l'intelligence. L'une est orientée réseaux (network centric) et l'autre terminal (terminal centric). Il est clair que les technologies actuelles ne permettent pas l'utilisation de ressources de traitement trop importantes dans un équipement de type embarqué (gestion de l'énergie, taille/poids de l'équipement, puissance de calcul, etc.) et que l'on peut donc privilégier l'implantation de l'intelligence dans le réseau. Néanmoins, nous pensons qu'à son échelle, un équipe-

<sup>&</sup>lt;sup>1</sup>le terme généralement utilisé dans la littérature française est radio intelligente. Néanmoins, pour la simple raison que l'on parle de science cognitive, je ferai référence à cette approche par le terme Radio Cognitive

ment radio peut bénéficier de l'implantation d'une intelligence (même restreinte) afin de contrôler ses propres ressources. Cela devient d'ailleurs de plus en plus nécessaire au fur et à mesure que la mobilité augmente, ce qui va dans le sens de l'évolution actuelle.

Nous avons donc conçu une architecture de gestion permettant d'introduire dans la conception d'un équipement RC les moyens :

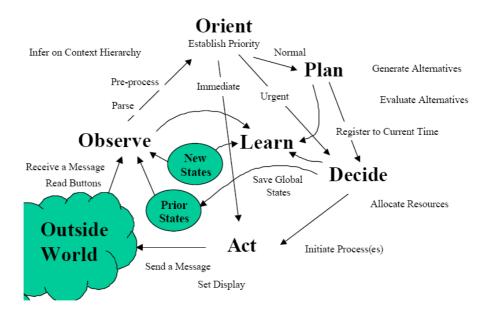

- de capture ainsi que d'interprétation de métriques,

- de prise de décision de reconfiguration suivant l'évolution des métriques,

- de gestion de la reconfiguration de l'équipement RC.

Ces moyens eux-même ne font pas partie de cette étude mais concernent d'autres thèses au sein de l'équipe. Reste à résoudre la question du choix du langage ou de l'approche de conception/modélisation. Une des contraintes principales dans le monde de la RC est la diversité des activités de recherche. Il est donc difficile de fusionner les avancées d'un domaine avec un ou plusieurs autres car à chaque domaine correspondent un langage et une modélisation spécifique. Nous avons donc décidé de modéliser notre architecture dans le langage de modélisation offrant les perspectives les plus prometteuses dans le monde de l'ingénierie et de haut niveau d'abstraction : UML (Unified Modeling Language). Ce choix de modélisation a été pris afin de permettre la compréhension et la réutilisation par l'ensemble de la communauté de notre architecture. La modélisation orientée objet (dont UML est la formalisation), issue des sciences informatiques, permet de représenter les principes de fonctionnement d'une architecture par la définition des relations entre objets la constituant. De plus, l'approche orientée objet (voire orientée composant) en permettant la modélisation de briques réutilisables avec leurs interfaces est particulièrement adaptée à la modélisation d'équipements RC dont les composants sont reprogrammables. Néanmoins, bien qu'apportant une plus value très importante à la conception, la modélisation UML n'étant pas simulable, il n'est pas possible d'y valider la structure opérationnelle des objets utilisés dans notre architecture RC. Nous avons alors eu recours à l'utilisation d'un métalangage de programmation permettant de simuler le comportement de notre architecture, tout en conservant un formalisme UML. Ceci est une autre originalité très marquée de ce travail de thèse.

## Problématique de l'étude

La problématique de l'étude présentée dans ce document est la suivante :

"les technologies étant devenues matures pour supporter la RL, est-il possible d'offrir une **architecture de gestion cognitive** d'un équipement (téléphone, PDA, station de base etc.) permettant de prendre en compte les évolutions de l'environnement, de les intégrer dans un processus d'adaptation amenant à une reconfiguration de tout ou partie de l'équipement afin de satisfaire aux besoins utilisateurs de façon transparente?"

Il existe très peu ou pas d'études actuellement sur ce type d'architecture de gestion avec ce niveau d'ambition, permettant de tirer partie des spécificités des plateformes hétérogènes d'exécution. L'architecture retenue devra présenter une réactivité élevée aux changements de contextes, une possibilité de reconfiguration étendue, une connaissance et un contrôle total de ses ressources de traitement ainsi qu'une interface radio générique permettant l'échange (demande, envoi) d'informations avec le réseau ou d'autres équipements à proximité.

#### Plan du mémoire

Nous présenterons dans le premier chapitre de ce mémoire une architecture répondant aux besoins de la radio logicielle après avoir présenté le concept de Radio Logicielle ainsi que quelques architectures de l'état de l'art.

- La naissance du concept de Radio Logicielle

- Plateformes matérielles et architectures logicielles pour la radio logicielle

- Une architecture logicielle de gestion de reconfiguration : le HDReM

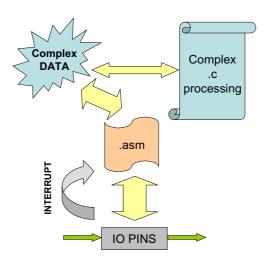

Après avoir présenté la partie radio logicielle nous allons nous intéresser au cœur de ce travail de thèse qui est la création d'une architecture de gestion pour un équipement RC. l'un des premiers objectifs était de définir les besoins d'une architecture RC suivant les réalités du domaine. Nous y avons répondu après une étude sur le concept RC ainsi que sur les besoins qu'il entraîne, par une architecture que nous avons nommé HDCRAM (Hierarchical and Distributed Cognitive Radio Management). Ainis, les trois chapitres suivant vont permettre au lecteur de suivre l'évolution de notre démarche qui est illustrée par la figure 4.

Le deuxième chapitre identifie les étapes ayant mené à la réalisation de HDCRAM avec:

- La naissance du concept Radio Cognitive

- Les besoins d'un équipement radio cognitif

- Un gestionnaire d'architecture radio cognitive : le HDCRAM

Dans un troisième temps, nous avons modélisé cette architecture dans le but de s'abstraire des contraintes matérielles et de capitaliser notre savoir faire comme illustré dans la deuxième ligne de la figure 4. Pour ce faire, nous avons utilisé un langage de modélisation de haut niveau. L'évolution de cette modélisation est de permettre une simulation fonctionnelle en s'assurant que le système simulé est le même que celui que nous avons spécifié. Pour ce faire, nous avons eu recours à un métalangage de programmation. Cette étape s'est conclue par la création d'un simulateur HDCRAM comme illustré dans la dernière ligne de la figure 4. Ce simulateur est présenté dans le troisième chapitre avec :

| Objectives                                     | Means                                              | Results          |  |

|------------------------------------------------|----------------------------------------------------|------------------|--|

| Description of : •Functionalities •Reality     | CR equipment<br>specifications<br>State of the art | HDCRAM           |  |

| Symbolic representation of the reality         | Language<br>(UML)                                  | HDCRAM Metamodel |  |

| Verification/Refinement of the functionalities | Design specific<br>language<br>(Kermeta)           | HDCRAM Simulator |  |

FIG. 4: De la conceptualisation de HDCRAM à sa définition par un métalangage de programmation

- Une nouvelle approche de conception

- Le langage UML

- Le simulateur HDCRAM

Le simulateur HDCRAM nous a permis ensuite d'effectuer une exploration comportementale d'HDCRAM en fonction de divers scénarios RC dont certains seront présentés ici dans le quatrième chapitre :

- Présentation de l'environnement de travail

- Scénario1 : Reconfiguration d'un chemin de données

- Scénario2 : Adaptation aux variations de niveau de batterie

- Scénario3 : accès opportuniste au spectre

Nous montrons grâce à ces scénarios qu'HDCRAM répond bien à tous les besoins de gestion (remontée de métrique, prise de décision, répercussion de la reconfiguration) en offrant tous les services nécessaires au bon fonctionnement d'un équipement RC. La conclusion propose une synthèse des travaux présentés pour amener à une discussion sur les perspectives. Les annexes se composent d'une présentation sommaire d'un métalangage de programmation exécutable nommé Kermeta ainsi que du délivrable complet présentant la synthèse des travaux effectués par le groupe de travail du projet D sur la radio flexible dans le cadre du réseau d'excellence NEWCOM.

## **CHAPITRE**

## La radio logicielle

1

#### **Sommaire**

| 1.1 | La nai  | ssance du concept de Radio Logicielle                          | 13 |

|-----|---------|----------------------------------------------------------------|----|

|     | 1.1.1   | Définition et généralités                                      | 13 |

|     | 1.1.2   | Contraintes et besoins pour les architectures Radio Logicielle | 17 |

|     | 1.1.3   | Quelques exemples de travaux industriels et académiques        | 18 |

| 1.2 | Platefo | ormes matérielles et architectures logicielles pour la radio   |    |

|     | logicie | lle                                                            | 19 |

|     | 1.2.1   | Les ressources matérielles                                     | 19 |

|     | 1.2.2   | Composition hétérogène de la plateforme d'exécution            | 24 |

|     | 1.2.3   | Exemples de projets "historiques" de la RL                     | 26 |

|     | 1.2.4   | Gestion logicielle des ressources hétérogènes                  | 27 |

| 1.3 | Une ar  | chitecture logicielle de gestion de reconfiguration : le HDReM | 29 |

|     | 1.3.1   | Présentation                                                   | 29 |

|     | 1.3.2   | Opérateurs de traitement                                       | 36 |

|     | 1.3.3   | Exemples de réalisations                                       | 37 |

| 1.4 | Conclu  | ısion                                                          | 44 |

## 1.1 La naissance du concept de Radio Logicielle

## 1.1.1 Définition et généralités

En approche classique, un équipement radio ne peut supporter qu'un faible nombre de standards car cela implique la juxtaposition d'un grand nombre de circuits dédiés, plusieurs étant nécessaire pour chaque standard. De plus leur architecture est figée à la conception. L'idée de radio logicielle a pour idéal la numérisation du signal juste après l'antenne, ce qui permet le traitement des opérations (sélection du canal, filtrage, décimation, etc.) en logiciel. Il serait ainsi possible d'utiliser n'importe quel standard de communication par simple chargement de logiciel. Née dans le milieu de la recherche militaire à la fin des années 70, la RL est introduite dans la communauté scientifique pour des applications de télécommunications civiles en 1991 par J. Mitola. C'est en 1995

qu'un *Request For Information* (ou RFI) sur la radio logicielle appliquée aux réseaux de téléphonie mobile sera lancé par Bellsouth et présentera le signe du démarrage d'une activité accrue dans le domaine. L'année suivante verra le jour de ce qui deviendra plus tard (en 1999) le *Software Defined Radio Forum* [9] (ou SDR Forum) réunissant une centaine de contributeurs internationaux dont le but est de promouvoir le développement, le déploiement et l'utilisation de la radio logicielle pour les systèmes sans fils.

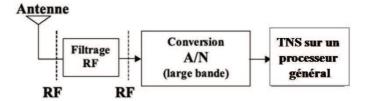

Comme le montre la figure 1.1, l'approche classique [10], ici dans le cas d'un récepteur, utilise un ensemble de composants spécialisés à un type de traitement. Tout ceci est à dupliquer pour chaque standard que doit supporter un équipement.

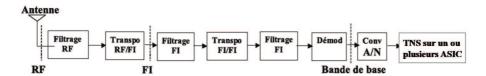

FIG. 1.1: Architecture superhétérodyne d'un récepteur pour un standard

Afin d'obtenir le maximum de performance pour le minimum de consommation électrique, un concepteur utilise des circuits conçus sur mesure pour un type d'application ciblé. Ce genre de composant est optimisé pour un unique type de traitement et ne peut évoluer après la conception afin de prendre en compte de nouveaux cas d'utilisation. Actuellement, au sein des équipements radio, les chaînes de transmission permettant l'accès aux standards existants sont conçues à base de tels composants nommés Circuit Intégré Spécialisé (ou ASIC pour Application Specific Integrated Circuit en anglais). Cette approche pour la conception des équipements radio multi-standards, utilise donc un ensemble de composants dédiés à un unique standard. Établir une liaison à l'aide de l'un ou l'autre des standards revient à activer les ASIC de la chaîne correspondant à ce standard. Un changement de standard revient à une commutation de chaîne d'ASIC. Avec ce type de méthode nommée "méthode Velcro", il est nécessaire de réaliser physiquement une chaîne de transmission différente pour chaque standard que l'on veut rendre accessible par l'équipement. Actuellement, en plus des réseaux déjà présentés auparavant dans le tableau 2, un équipement mobile doit pouvoir se connecter à des services de localisation (type GPS voir galileo un jour), des réseaux sans fils tels que le bluetooth ou le wi-fi (bientôt le wi-max), des moyens de réception TV numérique (DVB pour les européens, ATSC pour les américains, ISDB pour les japonais ou encore DTMB pour les chinois). Si l'on ajoute à cette prolifération du nombre de standards de communication l'incompatibilité des réseaux sans fils entre les différents pays on comprend aisément les problèmes de conception des nouveaux équipements radio. En effet, non seulement les nouveaux équipements se doivent de supporter les nouveaux standards ainsi que les nouvelles fonctionnalités dues à la convergence des médias (internet, musique, vidéo ...) mais ils se doivent aussi d'offrir la rétrocompatibilité avec les anciens standards. En effet, prenons le cas de la norme 3G, l'ensemble du territoire n'est pas encore couvert. Il serait donc inimaginable de demander à l'utilisateur de posséder plusieurs téléphones portables afin d'utiliser celui qui convient à sa localisation. Le problème est que l'intégration des anciens standards a un coût en terme de surface de silicium et que l'intégration de nouveaux standards dans un équipement radio amène donc à une hausse de ce coût. Or, un équipement radio possède une taille finie et le marché révèle une forte attirance des utilisateurs pour les téléphones de plus en plus compacts. Et, bien que la technologie permette une intégration de plus en plus fine des composants (la gravure en 32 nm pour les processeurs Intel par exemple est attendue pour 2009), l'ensemble des standards existants, ajoutés aux incompatibilités de ces équipements dans différents pays, font qu'il n'est plus envisageable de concevoir de manière classique un équipement regroupant toutes ces normes. De plus, ce type de conception n'est pas évolutif et n'autorise pas la prise en compte de nouveaux standards. Ceci relève un autre problème qui est la nécessité pour l'utilisateur de changer d'équipement à chaque saut technologique afin de bénéficier des dernières avancées. Ce problème touche aussi les fournisseurs qui doivent mettre à jour les équipements au sein des stations de base afin d'offrir ces nouveaux services. Á plus long terme, on peut aussi imaginer que les équipements radio effectueront en permanence ce que l'on appel un handover vertical, c'est à dire passer d'un standard de communication à un autre sans interruption dans la communication, afin d'améliorer leur QoS ou la charge du réseau. On comprend alors l'intérêt pour toutes les parties (utilisateur et fournisseur) de l'intégration au sein d'un équipement de radiocommunication d'une unique chaîne de traitement, entièrement numérique comme illustré par la figure 1.2.

FIG. 1.2: Architecture de radio logicielle idéale

Cette évolution permet de se libérer de la contrainte actuelle qui est : à chaque standard un circuit dédié. On dispose alors effectivement d'un unique circuit à usage général contrôlé par du logiciel qui permet de réaliser, par traitement numérique du signal (TNS), tous les traitements de tous les standards. En effet, un équipement basé sur cette approche peut être mis à jour par modification ou ajout de nouveaux logiciels et voir ses paramètres opérationnels reconfigurés. Tout comme l'on change le fonctionnement d'un ordinateur en chargeant un nouveau logiciel ou que l'on améliore ses performances par mise à jour de logiciels. On peut aussi envisager de mettre en commun les moyens de traitement de toutes les couches protocolaires, de la couche applicative à la couche physique. Ceci permet d'envisager des optimisations inter-couches de manière beaucoup plus simple et intégrée. Néanmoins ceci est une vision plutôt ultime du concept. Prenons l'exemple d'un utilisateur émettant un appel de type visioconférence dans une zone couverte par la 3G. Si pour une raison quelconque il devait sortir de la couverture il faudrait que l'équipement puisse se reconfigure dynamiquement et sans pertes de données afin de basculer la communication en mode audio simple. Effectuer ce type de reconfiguration en temps réel sans aucune perte semble encore difficile actuellement. Ainsi nous pensons que l'équipement devra offrir la possibilité de créer suivant les besoins une deuxième chaîne de traitement et basculer la communication afin de permettre le handover vertical. Ce traitement se rapproche du traitement classique avec le basculement physique entre deux standards hormis le fait que l'on peut se contenter d'environ deux fois la puissance de calcul nécessaire pour un standard (cas du standard le plus exigeant) afin d'offrir l'accès à un ensemble de standards pouvant être élevé, comme indiqué précédemment. En outre, l'espace utilisé par la chaîne de traitement non utilisée peut être libérée pour effectuer un autre traitement de type ponctuel. De plus cette radio logicielle idéale reste inaccessible dans la plupart des cas au vu des technologies actuelles [11]. En effet, afin de rendre ce concept réalisable il faudrait bénéficier de convertisseurs analogique/numérique disposant d'une dynamique (écart entre la puissance minimale et la puissance maximale) d'entrée trop importante pour les technologies actuelles. De plus, comme le montre [12] la puissance de traitement numérique nécessaire pour effectuer les traitements en bande de base, ainsi que la consommation sont un réel verrou technologique pour les circuits généralistes actuels. En effet, cette étude estime des performances nécessaires de 10 GIPS<sup>1</sup> pour le GSM jusqu'à 100 GIPS pour l'UMTS. Bien que les dernières générations de processeurs de type Intel Core 2 Extreme QX9775 soient capables de fournir une puissance d'environ 131 GIPS il n'est pas envisageable de les voir utilisés à court terme dans les stations de bases (de part leur consommation ou encore leur dissipation thermique) et encore moins dans les équipements mobiles (consommation, encombrement ou encore dissipation thermique).

Ces verrous technologiques peuvent être levés par l'adoption d'une architecture dite pragmatique [12]. Ainsi, avant une évolution future des technologies vers cette radio logicielle idéale, une étape doit être franchie avec l'adoption d'une radio logicielle dite restreinte (RLR ou SDR en anglais pour *Software Defined Radio*). Un exemple d'architecture RLR est présenté par la figure 1.3.

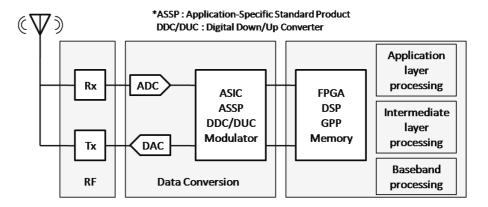

FIG. 1.3: Architecture de radio logicielle restreinte

Une telle structure présente différents segments technologiques au sein d'une même architecture matérielle. On trouve ainsi une partie analogique (que l'on tend à remplacer progressivement) et une partie numérique que l'on veut rendre de plus en plus importante. La numérisation se rapproche donc de plus en plus de l'antenne afin de converger vers la RL idéale. Ainsi, les circuits spécialisés (figés à la conception) sont remplacés par des circuits programmables permettant l'exécution d'applications logicielles. On peut

<sup>&</sup>lt;sup>1</sup>Giga Instruction per second

noter aussi que de gros efforts sont menés également pour rendre la partie analogique conservée de plus en plus souple [13], mais ces recherches, dépassant le cadre de cette thèse, elles ne seront pas abordées ici.

#### 1.1.2 Contraintes et besoins pour les architectures Radio Logicielle

Les contraintes liées aux architectures RLR sont nombreuses et nécessitent encore des efforts de recherche conséquents. L'une des plus importantes concerne la nature de la plateforme matérielle d'exécution cible de l'application radio conçue en logiciel ou tout du moins en numérique. En effet, une telle structure se devant d'être reconfigurable, elle se doit de disposer de ressources flexibles associant les contraintes liées aux domaines des radiocommunications ainsi que celles du domaine de l'embarqué (dans une moindre mesure pour les stations de base). Dans une approche de conception radio logicielle, une chaîne de transmission radio n'est plus constituée de composants exclusivement dédiés à un type de traitement. Il s'agit d'une suite de traitements informatiques exécutés sur des calculateurs pour faire des opérations de traitement du signal. La complexité des calculs à effectuer oblige à utiliser différents types de calculateurs mais l'approche radio logicielle est plus qu'une simple abstraction du matériel sous-jacent à l'application. C'est une approche de développement d'applications d'une façon fiable et modulaire qui permet le maximum de réutilisation des parties logicielles et matérielles d'implantation en implantation tout en laissant la possibilité de modifier les paramètres opérationnels. Les plateformes les plus adaptées à ce type de traitement sont avantageusement hétérogènes car constituées de divers éléments ayant des capacités et présentant des avantages complémentaires :

- les processeurs généraux (GPP),

- les processeurs de traitement numérique (DSP),

- les circuits spécialisés (ASIC, ASIP, Hardware accelerator),

- les circuits intégrés programmables (FPGA).

De plus une plateforme basée sur la RLR se doit de supporter le matériel de traitement RF et FI nécessaire pour effectuer le traitement du signal radio avec les ressources de calcul. Cela revient à définir une structure modifiable possédant une interface standardisée. La conception de telles plateformes est loin d'être triviale. Actuellement, le concepteur doit recourir à de nombreux logiciels et langages de programmation spécialisés lui permettant de programmer les différents composants. Il n'existe pas non plus d'environnement de travail unique permettant de concevoir de tels systèmes. Il faut aussi avoir conscience des problèmes inhérents à ce type de plateformes hétérogènes comme les différences entre chaque composant telles que :

- les vitesses de traitement différentes,

- l'équilibrage des charges de traitement,

- la gestion des ressources disponible,

- ou encore l'acheminement des données dans l'architecture.

En outre, le marché de la téléphonie mobile étant extrêmement porteur, il est normal de trouver un nombre non négligeable de constructeurs d'équipement présentant chacun un grand nombre d'équipements visant différents marchés. Dans un tel contexte, il est donc essentiel de concevoir des systèmes modulaires pouvant s'adapter à différentes plateformes et possédant des interfaces de communication standardisées. On voit donc très clairement l'intérêt de se pencher sur les sciences informatiques qui sont depuis longtemps confrontées à ce type de problème et de requérir l'utilisation de langages d'abstraction permettant de masquer les différences matérielles.

## 1.1.3 Quelques exemples de travaux industriels et académiques

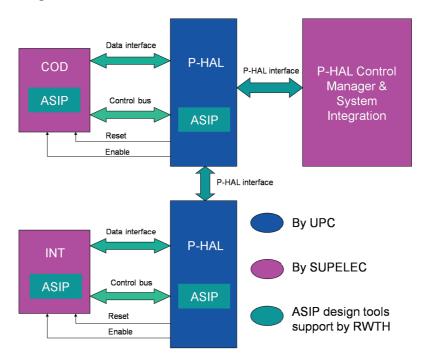

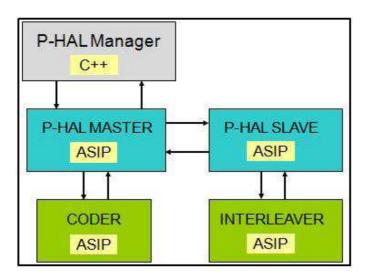

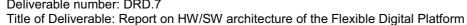

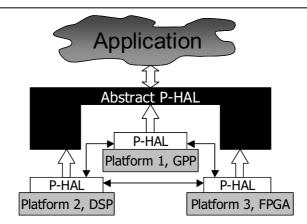

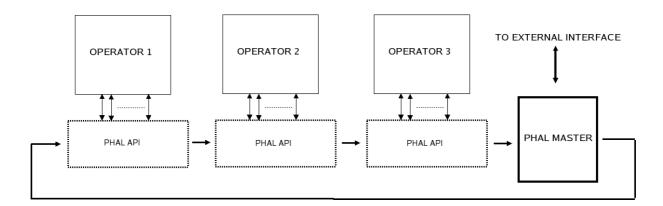

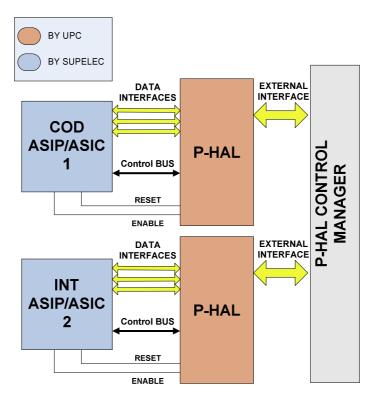

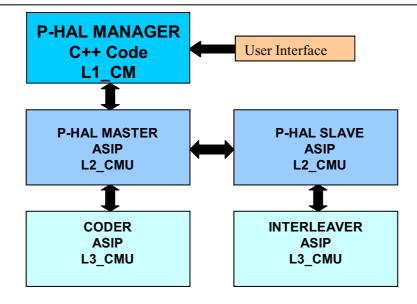

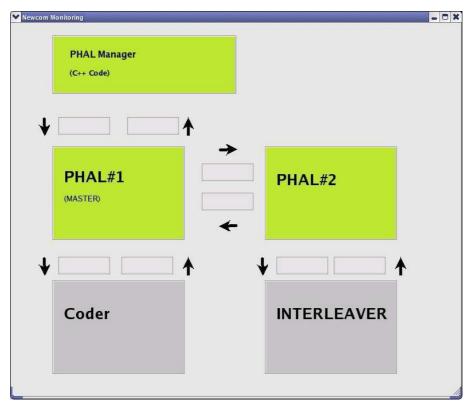

L'hétérogénéité présentée précédemment est l'une des première préoccupations pour un concepteur d'équipement RLR : l'abstraction des contraintes d'implantation matérielle vis-à-vis de l'application radio (qui sera logicielle). Cette abstraction peut être créée par une couche intermédiaire entre le matériel et le logiciel. Ainsi, les investissements de l'armée américaine, principal moteur de la recherche dans ce domaine, a permis la définition du SCA. Le SCA, véritable référence internationale qui sera présentée plus en détail dans 1.2.4, propose un environnement facilitant le déploiement d'une architecture radio sur une plateforme matérielle quelle qu'elle soit. D'autres solutions existent comme notamment le P-HAL [14] proposé par l'Université Polytechnique de Catalogne (UPC) en Espagne. Le PHAL, qui sera présenté dans 1.3.3, propose une approche plus générale que le SCA pour la conception d'équipements RLR. Il permet non seulement une abstraction entre le matériel et le logiciel mais est aussi un flot de conception outillé. Ces outils sont en cours de conception [15].

Au niveau industriel, suite à ses travaux effectués au MIT, Vanu Bose, à créé la société Vanu Inc² en 1998 qui est aujourd'hui considérée comme un modèle de start up aux USA. Cette société développe et commercialise des stations de base à base de processeurs généraux de type Pentium [16]. Beaucoup de sociétés sont apparues afin de proposer des services aux concepteurs pour utiliser l'architecture logicielle SCA. On peut notamment citer le CRC (Communication Research Center of Canada) dont SCARI-Open [17] et la suite de logiciels SCARI, ont été les tous premiers environnements respectant les directives du SCA. D'autres sociétés fournissent soit des composants logiciels de l'architecture SCA ou soit des outils permettant de développer des éléments radio compatible avec le SCA, tels que Zeligsoft [18] ou encore PrismTech [19].

À la pointe de la recherche universitaire, on peut citer les laboratoires tels que Virginia Tech aux USA avec par exemple les travaux du professeur Jeffrey Reed [20], [21] ou

<sup>&</sup>lt;sup>2</sup>http://www.vanu.com/

encore les professeurs Ryuji Kohno [22] de la Yokohama National University et Hiroshi Harada [23] de la National Institute of Information and Communications Technology au Japon. En europe citons également l'Université de Karlsruhe avec le professeur F. Jondral et le Trinity Collège de Dublin avec le professeur L. Doyle. En France, Eurecom développe des plateformes RL (PLATON), le CEA conçoit des SoC et NoC pour la RL (FAUST et MAGALI). Notre équipe SCEE de SUPELEC et de l'IETR est aussi reconnue au niveau internationnal sur la thématique RL.

Au niveau collaboratif, de nombreux travaux européens ont traités des cas liés à la CR on peut nommer TRUST [24], SUNBEAM [25] le principal d'entre eux étant le projet End-to-End Reconfigurability (E2R) [5] qui a regroupé tous les principaux acteurs du domaine.

## 1.2 Plateformes matérielles et architectures logicielles pour la radio logicielle

#### 1.2.1 Les ressources matérielles

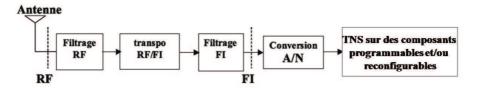

Lorsque l'on parle de plateformes dédiées à la RLR, la première idée associée est la flexibilité des ressources matérielles présentes. Cette flexibilité est la capacité de changement de contexte (changement de service, changement de traitement) offerte à un équipement et introduit les notions de reconfigurabilité, d'adaptabilité ou encore de modularité. À l'origine, les traitements radio étaient effectués sur des ASIC, ces derniers présentent de hautes performances de traitement mais leur manque de flexibilité est un lourd handicap dans le cadre d'une utilisation en RLR. À l'opposé, les circuits de type processeurs généralistes sont extrêmement flexibles. Néanmoins cette flexibilité présente un surcoût non négligeable comme des performances de calcul brutes moins élevées et une consommation énergétique plus importante. Il existe deux types de flexibilité dont nous allons parler maintenant :

- la flexibilité matérielle

- la flexibilité logicielle

#### Flexibilité matérielle : les circuits logiques programmables

Dans le domaine embarqué (mais aussi en électronique en général), les concepteurs sont limités par la taille maximale de silicium disponible pour la réalisation des fonctions logiques au sein d'un équipement. Dans le cadre d'une utilisation spécifique et non flexible, les ressources sont dimensionnées dans un ASIC de façon très précise afin de sa-

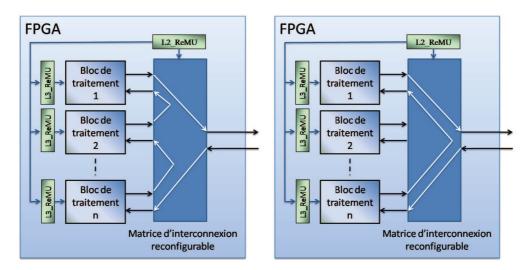

tisfaire les contraintes d'exécution. À l'opposé, dans une utilisation plus généraliste, les ressources sont spécifiées au pire cas et sont donc régulièrement (suivant l'ordonnancement des tâches et les possibilités de parallélisme) sous-utilisées. Les problèmes majeurs sont la consommation de ces ressources non utilisées en terme de puissance énergétique et d'occupation de surface de silicium. La consommation énergétique peut être limitée en appliquant des techniques qui permettent une gestion fine de l'horloge afin d'activer ou non certaines parties de l'architecture matérielle ou encore en mettant en place des techniques de basse consommation [26]. L'apparition de nouvelles technologies de circuits logiques programmables comme les FPGA et leurs dernières évolutions, permet de juguler ces problèmes de contraintes de surface. Comme présenté par la figure 1.4 ces circuits logiques programmables permettent de reconfigurer les ressources matérielles en fonction du type de traitement à effectuer. Cette approche offrant la flexibilité matérielle permet donc de dimensionner les ressources suivant les besoins et ce de manière dynamique (en temps réel) ou de manière statique.

FIG. 1.4: Flexibilité matérielle apportée par les nouvelles technologies

Cette reconfigurabilité offre une évolutivité importante du circuit par la possibilité d'ajouter de nouvelles fonctionnalités au cours du temps, ce qui permet une grande flexibilité d'utilisation. En effet, jusqu'à présent la flexibilité matérielle était utilisée en phase de développement comme souplesse à la conception et, par exemple, permettait à moindre coût de tester différentes solutions. Aujourd'hui on commence à étendre cette utilisation en cours de fonctionnement ou à l'allumage. Il existe deux types de reconfigurations: reconfiguration hors ligne ou off-line et reconfiguration en fonctionnement on-the-fly. La première demande une interruption du service en cours afin de procéder à la reconfiguration et nécessite un reset matériel avant une remise en fonctionnement, elle peut aussi être utilisée lors d'une phase d'initialisation. Le reset est appliqué afin de de s'assurer du contexte de départ de l'application (état des mémoires, des données stockées dans les registres, des données en entrée et en sortie, etc.). La reconfiguration off-line requérant une interruption de service, la notion de temps de reconfiguration n'est pas critique. Le deuxième type de reconfiguration s'effectue sans interruption du service en cours d'utilisation et peut donc être fortement soumise aux contraintes du temps réel suivant les cas d'application. Afin de permettre une reconfiguration sans interruption de service, il est nécessaire d'utiliser une reconfiguration dite dynamique. La reconfiguration dynamique, à l'inverse d'une reconfiguration statique, implique une reconfiguration sans interruption de service.

Il a été souligné dans [27] que l'on pouvait distinguer deux types de reconfiguration dynamique : la reconfiguration dynamique avec dépendance de données et sans dépendance de données. La dépendance de données entraîne comme problématique la sauvegarde des données de traitement entre deux reconfigurations. L'aspect critique dans une reconfiguration dynamique est le temps de reconfiguration. Ce temps dépend de la taille du fichier de reconfiguration mais aussi de la vitesse de l'interface de communication. Lorsque l'application le permet (temps entre deux traitements consécutif) ou si l'on se place dans un contexte de reconfiguration statique on peut faire appel à une reconfiguration totale du circuit. Par contre si les contraintes de temps sont très strictes, on comprend qu'il est préférable de réduire au maximum le temps de reconfiguration du matériel et donc réduire la taille du fichier de reconfiguration. Ceci peut être fait grâce à l'utilisation de circuits permettant la reconfiguration d'une partie de ce circuit et non de sa totalité.

La technologie utilisée dans certains FPGA (notamment ceux de la famille Virtex de chez Xilinx) permet la reconfiguration d'une partie du composant sans perturber le fonctionnement de l'ensemble [28]. Ainsi, si plusieurs opérateurs sont instanciés sur un même FPGA, il est possible de venir reconfigurer l'un d'eux sans perturber le fonctionnement des autres. La conception d'un système permettant ce type de reconfiguration se fait par séparation en deux parties du système à instancier sur le FPGA. L'une appelée partie statique qui représente la partie non modifiée par un changement de contexte et l'autre est appelée partie reconfigurable. Le but étant de réduire au maximum la partie reconfigurable comme présenté dans [29]. On génère ainsi un fichier de reconfiguration pour FPGA (appelé bitstream) ne contenant que les informations relatives à la zone reconfigurable. Il est possible d'aller encore plus loin que cette technique appelée reconfiguration partielle en générant un bitstream ne contenant que les changements réels entre deux contextes d'exécution. Cette technique est appelée reconfiguration partielle par différence. Ce qui fait une économie non négligeable en termes de poids de fichier ce qui induit :

- une occupation mémoire réduite,

- un temps de reconfiguration réduit (moins de ressources à reconfigurer).

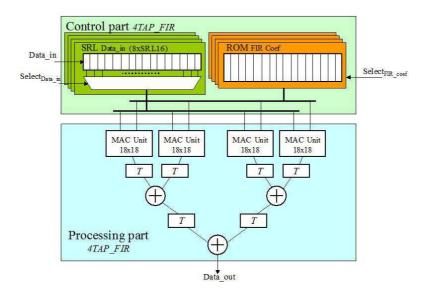

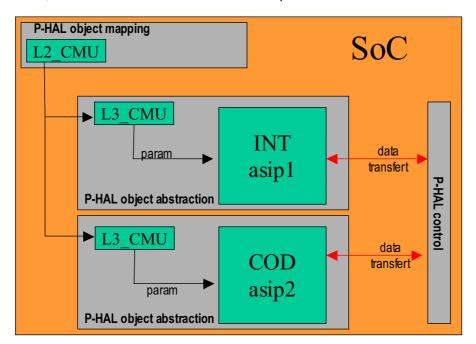

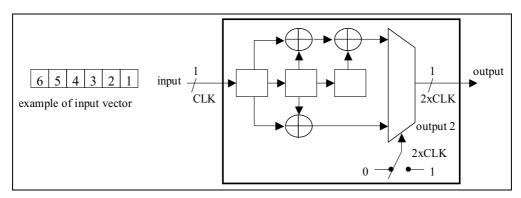

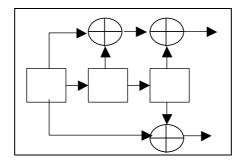

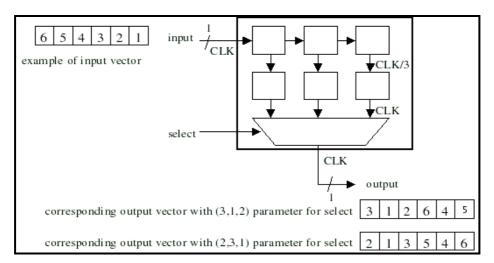

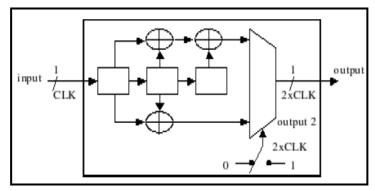

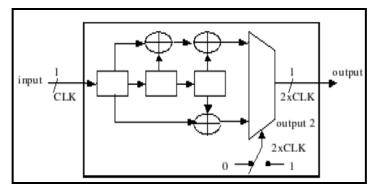

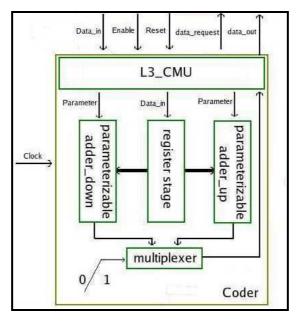

Le tableau suivant, illustrant un exemple de FIR (Finite Impulse Response) présenté en détail dans la partie 1.3.3 et optimisé pour une reconfiguration rapide, est fourni à titre d'exemple.

Il est néanmoins nécessaire de faire appel à un flot de conception spécifique et de définir une zone reconfigurable dynamiquement au sein du FPGA. Plus de détails sur ce type de matériel et sur les méthodologies de conception sont donnés en annexe du mémoire de thèse de J.P. Delahaye [30].

**TAB. 1.1:** Comparaison reconfiguration totale / reconfiguration partielle

| Virtex-II 2000         | Bitstream total | Bitstream partiel minimal |

|------------------------|-----------------|---------------------------|

| Taille du bitstream    | 830 ko          | 2 ko                      |

| Temps de configuration | 16,6 ms         | 40 μs                     |

#### Flexibilité logicielle : les processeurs logiciels

La flexibilité logicielle permet de faire abstraction des spécificités matérielles par l'utilisation d'un langage de programmation de haut niveau (type C/C++) et d'un compilateur dédié à l'architecture d'exécution. Elle permet aussi la modification d'une application s'exécutant sur une cible technologique par simple changement de code applicatif. Ce type de flexibilité est supporté par des architectures telles que les GPP, les DSP et ce que l'on appelle les processeurs logiciels (Microblaze [31] chez Xilinx ou Nios [32] chez Altera ou encore le processeur Leon [33]) qui peuvent être implantés sur des FPGA. L'introduction dans le domaine des équipements radio de la flexibilité logicielle est une évolution majeure à laquelle l'avènement de la radio logicielle a fortement contribué. En effet, les temps de conception et de validation dédiés aux circuits spécifiques font qu'il est extrêmement difficile de respecter les contraintes de temps de mise sur le marché d'un équipement. Le coût est également exhorbitant et ne peut être rentabilisé que dans le cas d'un succès pour un marché de masse. De plus lors de la conception, il faut s'assurer du bon fonctionnement de l'équipement dans de multiples environnements afin de limiter les taux de retours, il est donc nécessaire de bien concevoir le banc de test. Il est évident que si l'équipement possédait la capacité de pouvoir être modifié en cours de fonctionnement et ce sans remplacement d'aucune partie matérielle, les temps de mise sur le marché seraient drastiquement revus à la baisse. De plus si cette modification permettait une possible amélioration d'un ou plusieurs services cela deviendrait très avantageux à la fois du coté client et du coté constructeur (plus besoin de changer de matériel pour bénéficier des améliorations). Cette avancée est offerte par l'utilisation de logiciels au sein d'équipements radio. Il est évident que cette révolution à déjà commencé puisqu'il est possible pour les utilisateurs de télécharger dans leur équipement radio de nouveaux jeux, de nouvelles sonneries, de nouvelles applications, etc. Mais cela est loin de concerner la couche physique. Outre les contraintes technologiques qu'il faut lever, la régulation devra aussi faire sa révolution. La certification des équipements notamment en sera complètement remise en cause. Afin de profiter pleinement des apports de la radio logicielle pour améliorer la répartition dans l'attribution des ressources spectrales, la politique d'attribution des fréquences commence déjà à être modifiée comme en atteste [8] bien que ceci ne constitue que les premiers pas.

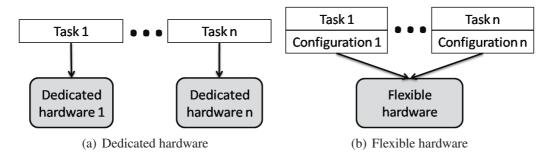

Dans un avenir plus lointain, il reste encore à franchir un pas vers le téléchargement de nouvelles normes radio et leur exécution au sein de l'équipement. C'est sur cette avancée majeure que repose le concept de la RL dans son sens le plus futuriste. Ainsi, un

équipement pourrait par exemple faire la demande de téléchargement d'une norme afin de permettre l'établissement d'une communication dans une certaine zone géographique. Il ne serait ainsi plus nécessaire de fournir à la conception la rétrocompatibilité avec les standards existants. De même qu'il ne serait plus nécessaire de prévoir des chaînes de conception d'équipements dédiées pour des zones géographiques précises. En effet, comme le montre la figure 1.5 un équipement possédant la flexibilité logicielle permet l'adaptation de l'équipement à l'évolution des différents standards radios existant et à venir. Ceci est vrai dans le cas où le matériel n'a aucune limitation. On le comprend bien, la flexibilité logicielle n'a pas vraiment de limites, au contraire du matériel sur lequel le logiciel s'exécute . On peut notamment nommer la limitation de mémoire disponible (pour le stockage des données mais aussi des fichiers de configuration téléchargés), la puissance de calcul disponible, la limite en consommation, le coût des composants, etc. La limitation de mémoire était un problème crucial il y a encore 5 ans dans un téléphone. Mais ce problème peut être considéré maintenant résolu grâce aux progrès fait dans ce domaine ces dernières années et dont le succès a fait baisser les prix significativement.

FIG. 1.5: L'apport de la flexibilité logicielle

Les concepteurs ne doivent cependant pas négliger les problèmes liés à cette approche qui implique l'utilisation massive de logiciel au sein d'équipements RL. En effet, de par la possibilité offerte de téléchargement permettant la modification d'organes importants du système, les risques pour l'intégrité de l'équipement sont réels et doivent faire l'objet d'études afin de minimiser ces risques et d'éviter les modifications non au-

torisées. Ce type de contrainte est particulièrement fort pour les systèmes dédiés aux domaines où les télécommunication se doivent d'être sûre (militaires, transports, ou encore sécurité pulblique). Ces risques sont multiples et déjà bien connus du monde de l'informatique tels que :

- bogues logiciels,

- incompatibilité entre divers logiciels,

- confidentialité (le système devient ouvert),

- introduction de virus informatiques par téléchargement,

- ou encore failles logicielles.

Il est évident que la façon de concevoir les futurs équipements radios va être fortement modifiée par la mise en place de services logiciels. Néanmoins on ne peut pas dire que les bases sont entièrement nouvelles. Ainsi, nous pouvons compter sur le savoir faire déjà présent des concepteurs de logiciels pour le monde informatique. En effet, il n'est plus besoin de démontrer la faisabilité de conception de logiciels s'exécutant sur un parc matériel hétérogène de par les ressources à disposition chez chaque utilisateur. Les défis sont cependant nombreux puisqu'il va falloir appliquer cette flexibilité logicielle dans le domaine embarqué où les contraintes sont élevées.

## 1.2.2 Composition hétérogène de la plateforme d'exécution

La problématique de fond, abordée en introduction, reste qu'il est peu probable de voir apparaître à court terme un équipement radio logicielle idéal. S'appuyant uniquement sur la flexibilité logicielle et les processeurs généralistes, cette approche est extrêmement consommatrice en énergie et reste improbable avec les technologies actuelles. Un contre exemple est la réalisation de BTS GSM à base de processeurs Pentium de la société VANU Inc, mais son faible volume de vente après une dizaine d'années de commercialisation peut susciter des interrogations quant à l'efficacité de la solution proposée. On s'oriente donc vers la conception d'équipements pour la RLR utilisant à la fois une flexibilité logicielle et une flexibilité matérielle. Cette démarche, comme présentée précédemment, nécessite l'utilisation de plateformes dites hétérogènes afin d'effectuer les différents traitements inhérents aux radiocommunications. Bien que cela ne soit pas le but de ce document de se pencher sur l'étude de telles plateformes, il est intéressant de les présenter afin d'appréhender la complexité de conception puisque notre contribution sera à intégrer dans le flot de conception d'équipements RC. La figure 1.6 montre une architecture RLR classique composée de trois étages de traitement.

Situé après l'antenne, l'étage RF, entièrement réalisé en analogique, permet de faire l'acquisition du signal capté par l'antenne et d'en sélectionner la partie désirée en jouant le rôle de filtre passe bande. Une amplification faible bruit de ce signal est ensuite effectuée avant traitement par la partie suivante. Ensuite, un échantillonnage en fréquence

FIG. 1.6: Plateforme SDR classique

intermédiaire (FI) sera réalisé dans la partie "Data Conversion". L'étage FI a pour but d'améliorer la sélectivité (par des filtres dont les flancs sont le plus raide possible de façon à rejeter au mieux les résidus des canaux adjacents) et la sensibilité (par une amplification la plus linéaire possible afin de garder un gain constant) du récepteur. La troisième partie est la partie appelée traitement en bande de base qui est réalisée à l'aide de circuits numériques et qui est donc en grande partie reconfigurable afin de s'adapter aux différents traitements. Cette partie effectuant le traitement en bande de base regroupe les opérations telles qu'estiamation de canal, égalisation, synchronisation décodage canal, etc. On peut également regrouper avec les traitements de la couche physique ceux des couches protocolaires supérieures et notamment la couche applicative. Elle peut impliquer du traitement du signal très exigeant pour le traitement video par exemple. Ce rapprochement de traitements permet d'envisager des optimisations inter-couches également (cross-layer design).

Finalement, il apparaît qu'une plateforme pour la RLR se compose d'une partie analogique et d'une partie numérique. Un concepteur doit donc pouvoir interfacer ces deux mondes et concevoir des systèmes performants pouvant être reconfigurés suivant les besoins. Avec une telle complexité et hétérogénéité, on comprend que les procédés permettant d'effectuer les reconfigurations ne seront pas aisés à mettre en place. En effet, lors d'une reconfiguration il va falloir pouvoir acheminer les données de reconfiguration afin de cibler les ressources se devant d'être reconfigurées. Ceci doit être effectué en prenant en compte les différences de temps de traitement entre chaque circuit utilisé, de même que la prise en compte du temps effectif de reconfiguration pour ne pas perturber le traitement en cours.

## 1.2.3 Exemples de projets "historiques" de la RL

Nous venons de présenter le type de ressources nécessaires à la conception de systèmes pour la RLR. Nous avons aussi défini les difficultés de mise en œuvre et d'utilisation de plateformes hétérogènes. Nous allons maintenant présenter deux projets "historiques" de la RL qui font référence : SpeakEasy [34] et SpectrumWare [35].

#### **SpeakEasy**

Débuté en 1991, le projet militaire SpeakEasy, fut le premier projet pour la radio logicielle. Il avait été initié afin de palier les problèmes d'incompatibilités entre les moyens de communication des différentes branches de l'armée américaine. Ce projet était très ambitieux puisqu'il avait pour objectif de permettre l'établissement de 10 formes d'ondes différentes à partir d'un seul équipement. En 1994, une démonstration fut faite qui révéla la réussite du projet. Le problème était l'encombrement de l'équipement puisque celui-ci occupait tout l'arrière d'un camion et sa complexité de conception (il intégrait plusieurs centaines de processeurs). Il a été conçu pour être un système multibandes dans une gamme de 2 à 400 MHz. Les leçons qui ont été tirées de ce prototype furent qu'il faut apporter un soin particulier à l'établissement d'un environnement ouvert afin de permettre le développement rapide de nouvelles applications. En effet, le logiciel s'exécutant sur cette plateforme était codé en code assembleur spécifique au matériel utilisé, ce qui était donc loin d'offrir une portabilité étendue. Un autre point soulevé est qu'il était "surdimensionné" on peut comprendre par là que le prototype devait manquer de flexibilité afin de s'adapter à de futures contraintes. De plus, l'établissement d'un tel équipement a été extrêmement coûteux puisqu'il était composé des produits les plus avancés disponibles sur le marché à l'époque.

#### **SpectrumWare**

SpectrumWare est un projet de recherche du MIT débuté en 1994 et qui a pour but de révéler le potentiel d'implantation portables (au sens de l'implantation sur plusieurs plateformes) pour la radio logiciel. L'architecture retenue était composée d'un front-end mettant en œuvre la partie RF et la conversion analogique/numérique et numérique/analogique. La partie traitement était implémentée sur un PC sous Linux. La différence notable avec le projet SpeakEasy était l'attention portée sur la portabilité du logiciel et sa réutilisation en utilisant un système d'exploitation (OS pour Operating System) dédié et une conception basée sur une approche logicielle orientée objet. Ainsi le choix du matériel à utiliser découlait du logiciel utilisé. Ce qui est ressorti de cette étude fut que bien que n'étant pas la plateforme la plus puissante du moment, en effet, l'utilisation d'un OS et une conception orientée objet induisent indubitablement des latences (ou

*overhead*), la progression en terme de puissance de calcul, d'espace de stockage et de rapidité d'exécution des ressources matérielles dans le futur la feront devenir beaucoup plus attractive.

Une évolution sera portée à ce prototype en 1998 par une séparation du signal de traitement et du signal de contrôle et de configuration. Ce qui a pour but d'améliorer encore la portabilité et la réutilisabilité logicielle.

### 1.2.4 Gestion logicielle des ressources hétérogènes

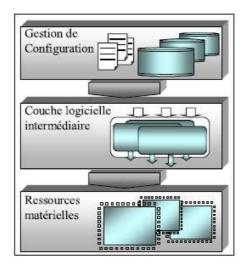

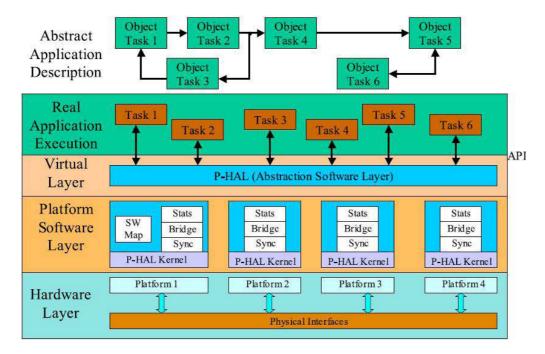

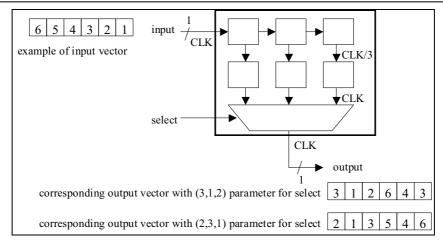

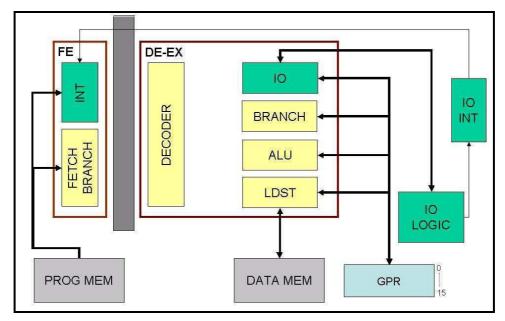

Cette nouvelle approche qu'est la RLR introduit on l'a vu, une forte utilisation de logiciels au sein de la plateforme d'exécution. Il va donc falloir mettre en place une interface entre la couche logicielle et la couche physique afin de permettre le contrôle et la reconfiguration des ressources. Ce type d'approche est illustré par la figure suivante qui extraite de [30].

FIG. 1.7: Gestion logicielle des ressources hétérogènes

Vu l'hétérogénéité du parc d'équipement, il est nécessaire de développer des logiciels pouvant s'exécuter sur des plateformes différentes. Il faut donc fournir à chaque équipement un moyen d'interpréter les instructions du logiciel et de permettre le routage des informations (données et contrôle de reconfiguration) jusqu'aux ressources matérielles spécifiques. Ceci est réalisé grâce à une couche logicielle intermédiaire qui permet un interfaçage entre le monde logiciel et matériel. De plus il est nécessaire de proposer une architecture logicielle ouverte, des interfaces de programmation standardisées (ou API pour *Application Programming Interface*) et permettre la réutilisation des modules de traitement dans différents contextes d'exécution. Il y a néanmoins un coût non négligeable à payer pour l'utilisation d'une telle couche. Ce surcoût s'applique au niveau de l'occupation mémoire, aux latences engendrées pour l'acheminement des données ou

encore à l'accroissement de la consommation. Ceci est néanmoins le prix à payer afin de permettre la conception d'un équipement pouvant exécuter un ensemble d'applications permettant l'établissement d'une quelconque communication radio par reconfiguration matérielle. Au-delà de cette couche logicielle, il va aussi falloir prendre en compte la granularité de reconfiguration offerte à l'équipement. En effet, on peut distinguer deux types de reconfigurations matérielles : la reconfiguration gros grain, et la reconfiguration grain fin. Plus la granularité est élevée et plus le nombre de composants reconfigurés est important mais plus la flexibilité diminue. Il va donc falloir prendre en compte dans la conception le fait que des circuits à granularités différentes cœxistent au sein du même équipement afin d'organiser au mieux le chargement des codes et des configurations.

Nous allons présenter la proposition qui fait référence au niveau international en tant que couche logicielle aidant à la conception de systèmes pour la RLR : le SCA [36].

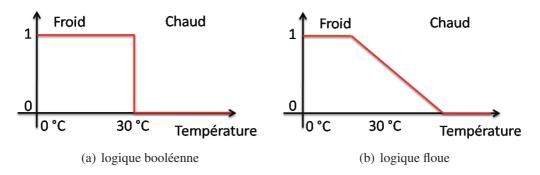

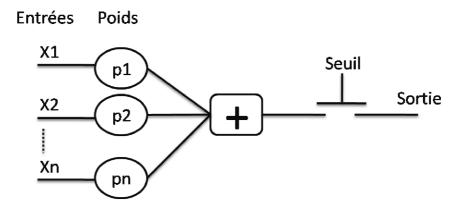

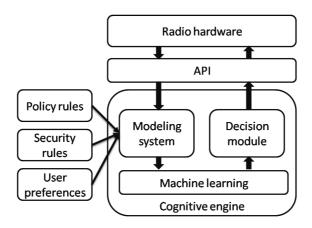

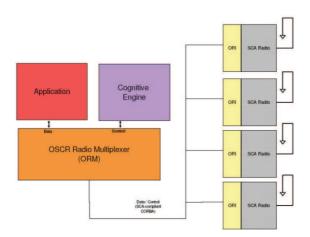

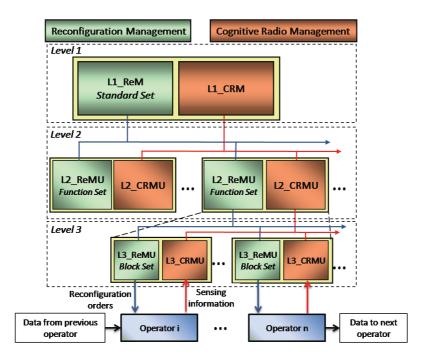

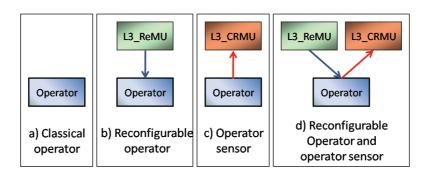

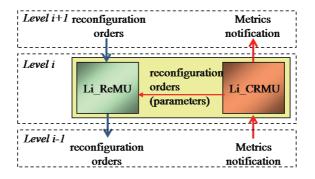

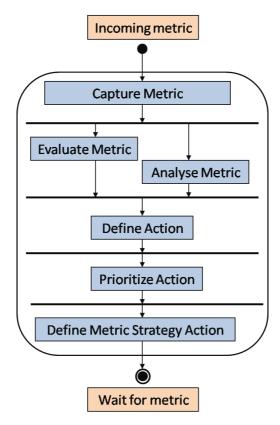

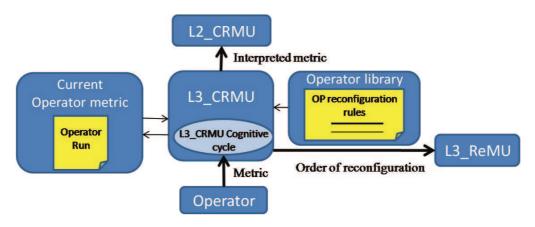

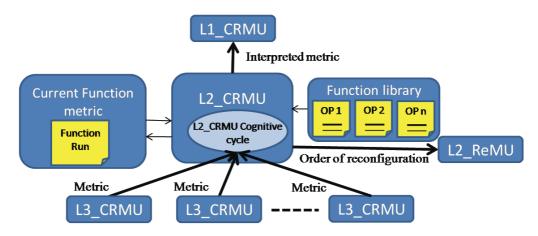

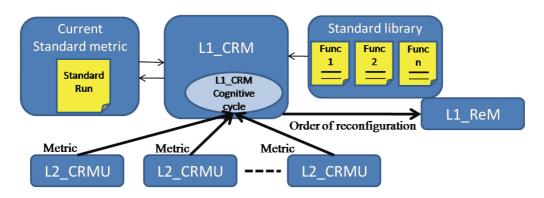

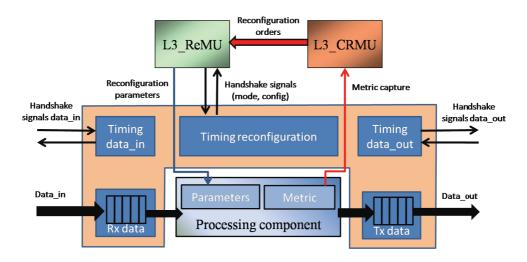

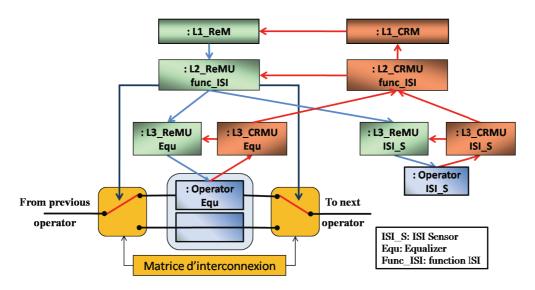

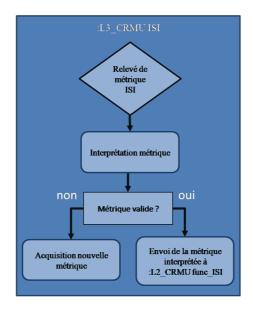

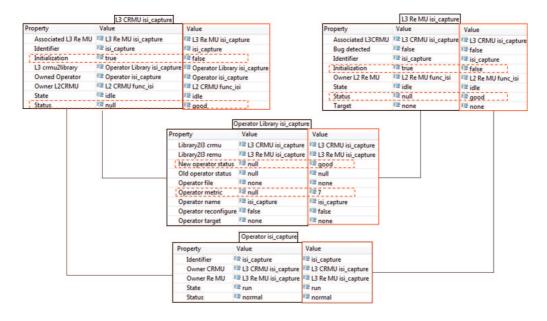

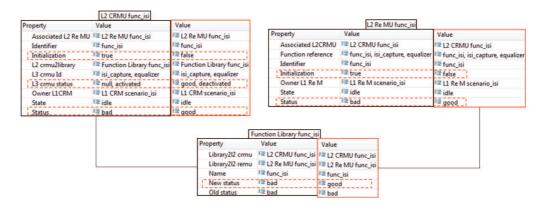

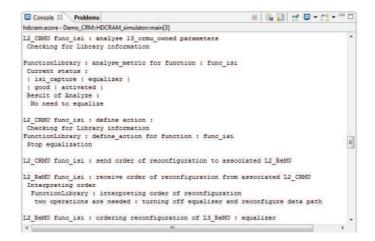

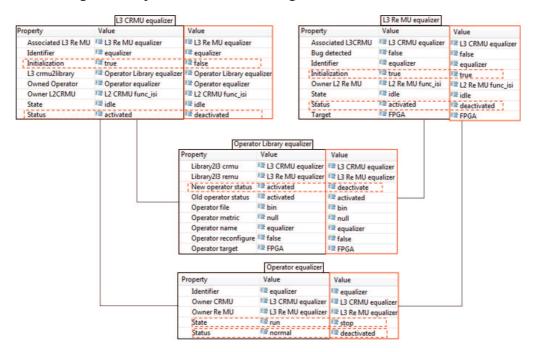

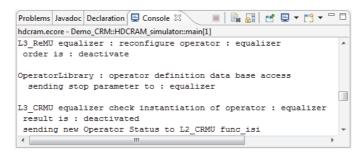

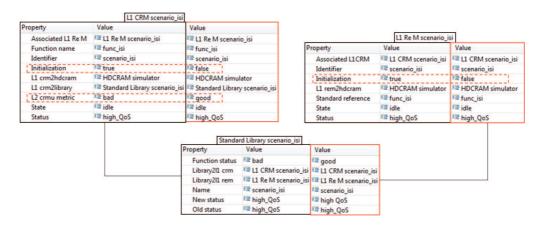

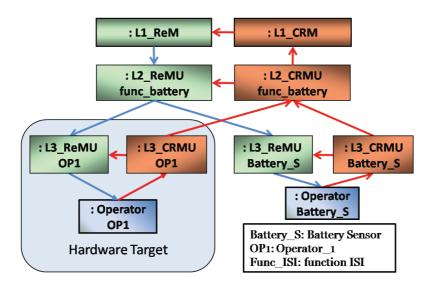

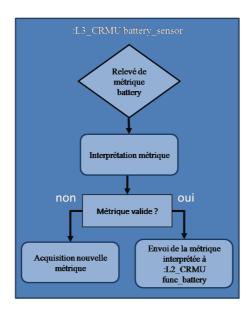

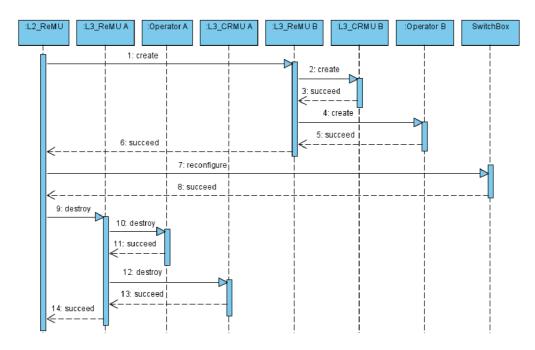

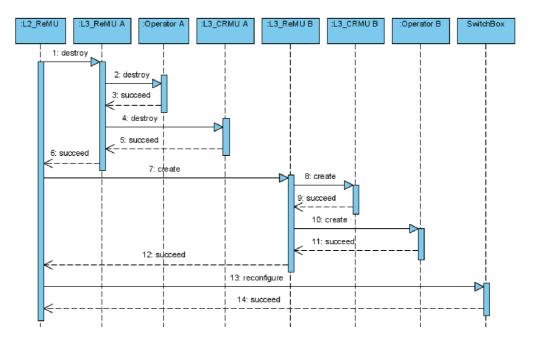

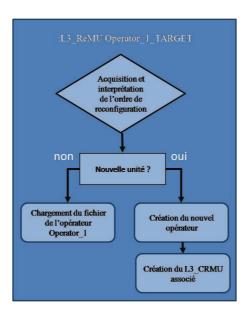

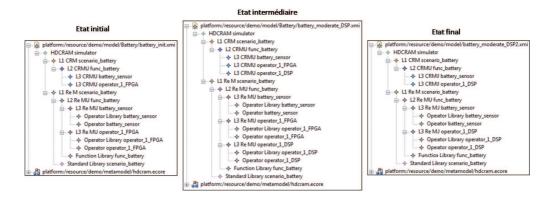

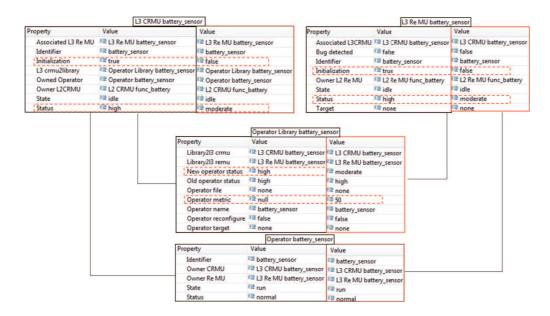

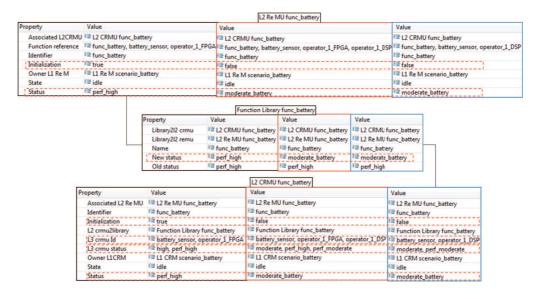

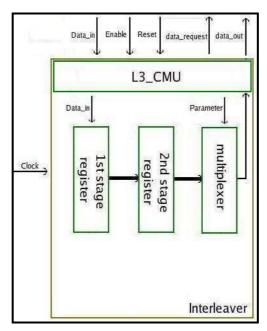

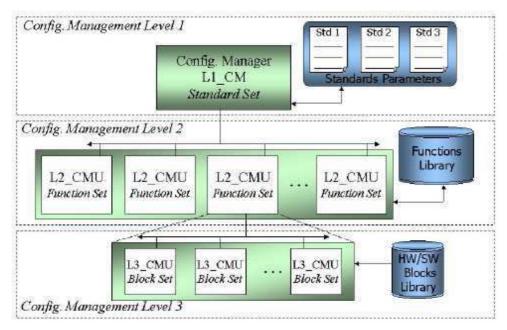

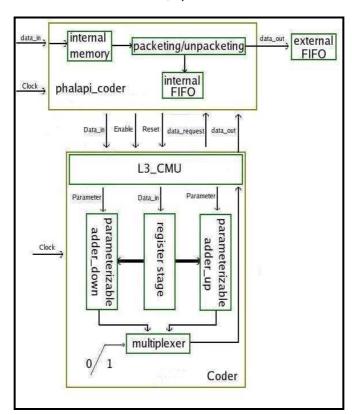

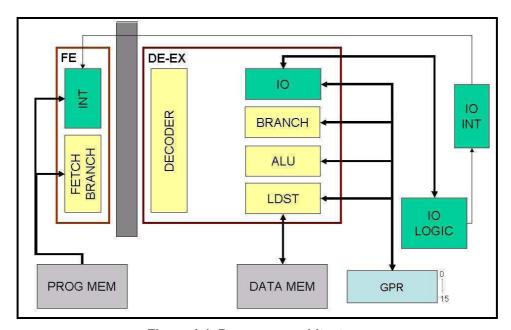

#### **Software Communication Architecture**