# Synthèse logique à base de règles pour les compilateurs de silicium

Stéphane Hanriat

#### ▶ To cite this version:

Stéphane Hanriat. Synthèse logique à base de règles pour les compilateurs de silicium. Modélisation et simulation. Institut National Polytechnique de Grenoble - INPG, 1986. Français. NNT: . tel- 00322203

### HAL Id: tel-00322203 https://theses.hal.science/tel-00322203

Submitted on 17 Sep 2008

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# THESE

Présentée à

# L'Institut National Polytechnique de Grenoble

pour obtenir le grade de DOCTEUR de l'INPG spécialité "Informatique"

par

## Stéphane HANRIAT

SYNTHESE LOGIQUE A BASE DE REGLES POUR LES COMPILATEURS DE SILICIUM

å

Thèse soutenue le 29 septembre 1986 devant la commission d'examen.

D. ETIEMBLE

Président

V. C. HAMACHER

P. BAYLE

Examinateurs

J. FREHEL

#### INSTITUT NATIONAL POLYTECHNIQUE DE GRENOBLE

Président :

Daniel BLOCH

Année universitaire 1985-1986

Vice-Présidents: B. BAUDELET R. CARRE H. CHERADAME J.M PIERRARD

#### Professeurs des Universités

| BARIBAUD        | Michel        | ENSERG  |   | JOUBERT     | Jean-Claude  | ENSIEG  |

|-----------------|---------------|---------|---|-------------|--------------|---------|

| BARRAUD         | Alain         | ENSIEG  |   | JOURDAIN    | Geneviève    | ENSIEG  |

| BAUDELET        | Bernard       | ENSIEG  |   | LACOUME     | Jean-Louis   | ENSIEG  |

| BEAUFILS        | Jean-Claude   | ENSEEG  |   | LESIEUR     | Marcel       | ENSHG   |

| BESSON          | Jean          | ENSEEG  |   | LESPINARD   | Georges      | ENSHG   |

| BLIMAN          | Samuel        | ENSERG  |   | LONGEQUEUE  | Jean-Pierre  | ENSIEG  |

| BLOCH           | Daniel        | ENSIEG  |   | LOUCHÈT     | François     | ENSEEG  |

| BOIS            | Philippe      | ENSHG   |   | MASSELOT    | Christian    | ENSIEG  |

| BONNETAIN       | Lucien        | ENSEEG  |   | MAZARE      | Guy          | ENSIMAG |

| BONNIER         | Etienne       | ENSEEG  |   | MOREAU      | René         | ENSHG   |

| BOUVARD         | Maurice       | ENSHG   |   | MORET       | Roger        | ENSIEG  |

| BRISSONNEAU     | Pierre        | ENSIEG  |   | MOSSIERE    | Jacques      | ENSIMAG |

| BRUNET          | Yves          | ENSIEG  |   | OBLED       | Charles      | ENSHG   |

| BUYLE-BODIN     | Maurice       | ENSERG  |   | PARIAUD     | Jean-Charles | ENSEEG  |

| CAILLERIE       | Denis         | ENSHG   |   | PAUTHENET   | René         | ENSIEG  |

| CAVAIGNAC       | Jean-François | ENSIEG  |   | PERRET      | René         | ENSIEG  |

| CHARTIER        | Germain       | ENSIEG  |   | PERRET      | Robert       | ENSIEG  |

| CHENEVIER       | Pierre        | ENSERG  |   | PIAU        | Jean-Michel  | ENSHG   |

| CHERADAME       | Hervé         | UERMCPP | • | POLOUJADOF  | F Michel     | ENSIEG  |

| CHERUY          | Arlette       | ENSIEG  |   | POUPOT      | Christian    | ENSERG  |

| CHIAVERINA      | Jean          | UERMCPP |   | RAMEAU      | Jean-Jacques | ENSEEG  |

| COHEN           | Joseph        | ENSERG  |   | RENAUD      | Maurice      | UERMCPP |

| COUMES          | André         | ENSERG  |   | ROBERT      | André        | UERMCPP |

| DURAND          | Francis       | ENSEEG  |   | ROBERT      | François     | ENSIMAG |

| DURAND          | Jean-Louis    | ENSIEG  |   | SABONNADIER |              | ENSIEG  |

| FONLUPT         | Jean Jean     | ENSIMAG |   | SAUCIER     | Gabrielle    | ENSIMAG |

| FOULARD         | Claude        | ENSIEG  |   | SCHLENKER   | Claire       | ENSIEG  |

| GANDINI         | Alessandro    | UERMCPP |   | SCHLENKER   | Michel       | ENSIEG  |

| GANDIN          | Claude        | ENSIEG  |   | SERMET      | Pierre       | ENSERG  |

| GENTIL          | Pierre        | ENSERG  |   | SILVY       | Jacques      | UERMCPP |

| GUERIN          | Bernard       | ENSERG  |   | SOHM        | Jean-Claude  | ENSEEG  |

|                 | Pierre        | ENSEEG  |   | SOUQUET     | Jean-Louis   | ENSEEG  |

| GUYOT<br>IVANES | Marcel        | ENSIEG  |   | TROMPETTE   | Philippe     | ENSHG   |

| JAUSSAUD        | Pierre        | ENSIEG  |   | VEILLON     | Gérard       | ENSIMAG |

| มหนออกบน        | I ICII C      | LIVILG  |   |             |              |         |

#### Professeurs Université des Sciences Sociales (Grenoble II)

**CHATELIN** Françoise BOLLIET Louis

#### Chercheurs du C.N.R.S

| CARRE<br>CAILLET    | René<br>Marcel     | Directeur de recherche | DAVID<br>DEPORTES    | René<br>Jacques       | Maitre de recherche |

|---------------------|--------------------|------------------------|----------------------|-----------------------|---------------------|

| FRUCHART<br>JORRAND | Robert<br>Philippe | "<br>"                 | DRIOLE<br>EUSTATHOPO | Jean<br>ULOS Nicolas  | ••                  |

| LANDAU              | loan               |                        | GIVORD               | Dominique             |                     |

|                     |                    |                        | JOUD                 | Jean-Charles          | "                   |

| ALLIBERT            | Colette            | Maitre de recherche    | KAMARINOS<br>KLEITZ  | Georges · Michel      | ,                   |

| ALLIBERT<br>ANSARA  | Michel<br>Ibrahim  | u ·                    | LEJEUNE              | Gérard                | **                  |

| ARMAND              | Michel             | 11                     | MERMET               | Jean                  | "                   |

| BINDER              | Gilbert            | U<br>U                 | MUNIER               | Jacques               | "                   |

| BONNET              | Roland             | "                      | SENATEUR             | Jean-Pierre<br>Michel |                     |

| BORNARD<br>CALMET   | Guy<br>Jacques     | "<br>"                 | SUERY<br>WACK        | Bernard               | u                   |

# Personnalités agrées à titre permanent à diriger des travaux de recherche (Décision du conseil scientifique)

#### E.N.S.E.E.G

|                                                                 |                                                                   |                                                                        |                            |                                                               | •                                                           |

|-----------------------------------------------------------------|-------------------------------------------------------------------|------------------------------------------------------------------------|----------------------------|---------------------------------------------------------------|-------------------------------------------------------------|

| DERNARD<br>CAILLET<br>CHATILLON<br>CHATILLON<br>COULON<br>DIARD | Claude<br>Marcel<br>Catherine<br>Christian<br>Michel<br>Jean-Paul | FOSTER<br>GALERIE<br>HAMMOU<br>MALMEJAC<br>MARTIN GARIN<br>NGUYEN TRUO |                            | RAVAINE<br>SAINFORT<br>SARRAZIN<br>SIMON<br>TOUZAIN<br>URBAIN | Denis<br>Paul<br>Pierre<br>Jean-Paul<br>Philippe<br>Georges |

|                                                                 |                                                                   | <u>j</u>                                                               | e.N.S.E.R.G                |                                                               |                                                             |

| BOREL<br>CHOVET                                                 | Joseph<br>Alain                                                   |                                                                        |                            | DOLMAZON<br>HERAULT                                           | Jean-Marc<br>Jeanny                                         |

| •                                                               | į.                                                                | -                                                                      | E.N.S.I.E.G                |                                                               |                                                             |

| BORNARD<br>DESCHIZEAUX<br>GLANGEAUD                             | Guy<br>Pierre<br>François                                         | KOFMAN<br>LEJEUNE                                                      | Walter<br>Gérard           | MAZUER<br>PERARD<br>REINISCH                                  | Jean<br>Jacques<br>Raymond                                  |

|                                                                 |                                                                   |                                                                        | E.N.5.H.G                  |                                                               |                                                             |

| ALEMANY<br>BOIS                                                 | Antoine<br>Daniel                                                 | DARVE<br>MICHEL                                                        | Félix<br>Jean-Marie        | ROWE<br>VAUCLIN                                               | Alain<br>Michel                                             |

|                                                                 |                                                                   | E                                                                      | .N.S.I.M.A.G               |                                                               |                                                             |

| NERT<br>CALMET                                                  | Didier<br>Jacques                                                 | COURTIN<br>COURTOIS<br>DELLA DORA                                      | Jacques<br>Bernard<br>Jean | FONLUPT<br>SIFAKIS                                            | Jean<br>Joseph                                              |

| ,                                                               |                                                                   | <u>u</u>                                                               | E.R.M.C.P.P                |                                                               |                                                             |

|                                                                 |                                                                   | CHARUEL                                                                | Robert                     |                                                               |                                                             |

|                                                                 |                                                                   |                                                                        | C.E.N.G                    |                                                               |                                                             |

| CADET<br>COEURE<br>DELHAYE<br>DUPUY                             | Jean<br>Philippe<br>Jean-Marc<br>Michel                           | JOUVE<br>NICOLAU<br>NIFENECKER                                         | Hubert<br>Yvan<br>Hervé    | PERROUD<br>PEUZIN<br>TAIEB<br>VINCENDON                       | Paul<br>Jean-Claude<br>Maurice<br>Marc                      |

|                                                                 |                                                                   | Labora                                                                 | toires extérieurs :        |                                                               |                                                             |

|                                                                 |                                                                   |                                                                        | C.N.E.T                    |                                                               | . •                                                         |

| DEMOULIN<br>DEVINE                                              | Eric                                                              | GERBER                                                                 | Roland                     | MERCKEL<br>PAULEAU                                            | Gérard<br>Yves                                              |

|                                                                 |                                                                   |                                                                        |                            |                                                               |                                                             |

#### ECOLE NATIONALE SUPERIEURE DES MINES DE SAINT-ETIENNE

Directeur

: Monsieur M. MERMET

Directeur des Etudes et de la formation : Monsieur J. LEVASSEUR : Monsieur J. LEVY

Directeur des recherches Secrétaire Général

: Mademoiselle M. CLERGUE

#### Professeurs de lère Catégorie

Gestion

Physique

Métallurgie Métallurgie

COINDE GOUX LEVY LOWYS MATHON RIEU

Alexandre Claude Jacques Jean-Pierre Albert Jean

Gestion Mécanique - Résistance des matériaux Chimie

SOUSTELLE Michel FORMERY Philippe

Mathématiques Appliquées

#### Professeurs de 2ème catégorie

HABIB **PERRIN** VERCHERY **TOUCHARD**  Michel Michel Georges Bernard

Informatique Géologie Matériaux

Physique Industrielle

#### Directeur de recherche

**LESBATS**

Pierre

Métallurgie

#### Maîtres de recherche

**BISCONDI** DAVOINE FOURDEUX **KOBYLANSKI** LALAUZE LANCELOT LE COZE THEVENOT TRAN MINH

Michel Philippe Angeline André René Francis Jean François Canh

Métallurgie Géologie Métallurgie Métallurgie Chimie Chimie Métallurgie Chimie Chimie

#### Personnalités habilitées à diriger des travaux de recherche

DRIVER **GUILHOT THOMAS**

Julian Bernard Gérard

Métallurgie Chimie Chimie

#### Professeur à l'UER de Sciences de Saint-Etienne

**VERGNAUD**

Jean-Maurice

Chimie des Matériaux & chimie industrielle

| * |   |  |   |  |

|---|---|--|---|--|

|   | ) |  | • |  |

|   |   |  |   |  |

|   |   |  |   |  |

|   |   |  |   |  |

|   |   |  |   |  |

|   |   |  |   |  |

|   |   |  |   |  |

|   |   |  |   |  |

|   |   |  |   |  |

|   |   |  |   |  |

|   |   |  |   |  |

|   |   |  |   |  |

|   |   |  |   |  |

|   |   |  |   |  |

|   |   |  |   |  |

|   |   |  |   |  |

|   |   |  |   |  |

|   |   |  |   |  |

|   |   |  |   |  |

|   |   |  |   |  |

|   |   |  |   |  |

|   |   |  |   |  |

|   |   |  |   |  |

|   |   |  |   |  |

|   |   |  |   |  |

|   |   |  |   |  |

|   |   |  |   |  |

|   |   |  |   |  |

|   |   |  |   |  |

|   |   |  |   |  |

|   |   |  |   |  |

|   |   |  |   |  |

|   |   |  |   |  |

|   |   |  |   |  |

|   |   |  |   |  |

|   |   |  |   |  |

|   |   |  |   |  |

A qui le veut...

|   | , |  |   |  |

|---|---|--|---|--|

|   |   |  | • |  |

|   |   |  |   |  |

|   |   |  |   |  |

|   |   |  |   |  |

|   |   |  |   |  |

|   |   |  |   |  |

|   |   |  |   |  |

|   |   |  |   |  |

| • |   |  |   |  |

|   |   |  |   |  |

|   |   |  |   |  |

|   |   |  |   |  |

|   |   |  |   |  |

|   |   |  |   |  |

|   |   |  |   |  |

|   |   |  |   |  |

|   |   |  |   |  |

|   |   |  |   |  |

|   |   |  |   |  |

|   |   |  |   |  |

|   | 1 |  |   |  |

|   | , |  |   |  |

|   |   |  |   |  |

|   |   |  |   |  |

#### Remerciements

Je tiens à exprimer toute ma reconnaissance à Madame Gabrièle Saucier, Professeur à l'ENSIMAG, pour m'avoir accueilli dans son laboratoire de recherche, et pour avoir encadré mon travail et diriger mes recherches avec compétence tout au long de ces deux dernières années.

Je tiens à remercier

Monsieur **Daniel ETIEMBLE**, Professeur à l'Université Pierre et Marie Curie, d'avoir accepter d'être rapporteur de cette thèse et de me faire l'honneur d'en présider le jury,

Monsieur **Pierre Bayle**, Responsable du calcul scientifique à l'Electronique Serge Dassault, ainsi que,

Monsieur **Jean Frehel**, Responsable de la CAO THOMSON CSF à Saint Egrève,

d'avoir accepté de faire partie de ce jury.

Je remercie tous particulièrement Monsieur V. Carl Hamacher, Professeur à l'Université de Toronto, pour avoir étudier le texte de cette thèse en français, et accepter d'en être également le rapporteur.

Que tous mes collègues du Laboratoire **Circuits et Systèmes** trouvent ici l'expression de ma profonde sympathie pour les remarques constructives dont ils m'ont fait profiter, et pour le climat agréable qu'ils ont su faire régner au sein de l'équipe.

Je remercie également Mac Intosh pour les nombreuses heures qu'il m'a permis de passer en sa compagnie, ainsi que le service de reprographie de l'IMAG pour la prise en charge du tirage de cette thèse.

# SYNTHESE LOGIQUE A BASE DE REGLES POUR LES COMPILATEURS DE SILICIUM

#### SOMMAIRE

#### **INTRODUCTION**

- I. SYNTHESE A BASE DE REGLES POUR LA LOGIQUE COMBINATOIRE.

- I.1. Rappels sur la logique combinatoire.

- **1.2.** Les structures "cible" pour la synthèse combinatoire et les critères d'optimisation.

- I.2.1. La synthèse à base de réseaux programmables.

- I.2.2. La synthèse combinatoire en logique aléatoire.

- I.2.3. La synthèse combinatoire en portes complexes.

- I.3. La minimisation logique à base de règles.

- I.3.1. Position du problème et état de l'art.

- 1.3.2. Un système de règles pour la minmisation locale d'une fonction complète.

- 1.3.2.1. Règles pour la mise sous forme normale d'une expression.

- I.3.2.2. Règles pour la minmisation locale.

- 1.3.2.3. Propriété invariante dans l'application des règles.

- 1.3.2.4. Contrôle de l'application des règles.

- 1.3.2.5. Exemple d'application de règles.

- 1.3.3. La minimisation locale des fonctions partiellement spécifiées.

- 1.3.4. Un système de règles pour la minimisation globale.

- I.3.4.1. Règles d'expansion globale.

- 1.3.4.2. Règle d'intersection généralisée.

- 1.3.4.3. Règles d'élimination de la redondance.

- 1.3.4.4. Contrôle de l'application des règles.

- 1.3.5. Le test d'inclusion : une approche formelle.

- 1.3.5.1. Approche classique pour le test d'inclusion.

- 1.3.5.2. Le test d'inclusion par la preuve formelle de tautologie.

#### II. LA SYNTHESE AUTOMATIQUE DE CONTROLEUR.

- II.1. Modélisation d'un contrôleur.

- II.1.1. Description d'un contrôleur par un graphe de contrôle.

- II.1.2. Séguencement et émission des commandes.

- II.2. Conformité d'un contrôleur décrit par un graphe de contrôle.

- II.2.1. Blocage dans l'évolution d'un contrôleur.

- II.2.2. Evolution parallèle dans un graphe d'états.

- II.3. La synthèse automatique d'un contrôleur décrit par un graphe d'états.

- II.3.1. La génération des équations.

- II.3.1.1. Les équations des commandes.

- II.3.1.2. Les équations de séquencement.

- II.3.2. Implémentation des équations.

- II.3.3. La synthèse en codage 1 parmi n.

- II.3.4. La synthèse en codage compact.

- II.4. Optimisation du codage par un système de règles.

- III. ASYL: UN OUTIL D'ASSISTANCE A LA SYNTHESE LOGIQUE

- III.1. Description générale du système ASYL.

- III.2. Exemples de contrôleurs synthétisés par le système ASYL.

- III.2.1. Exemple 1 : un contrôle de gestion d'un protocole d'échange.

- III.2.2. Exemple 2 : un contrôleur de trafic.

- III.3. Conclusion sur le système ASYL.

Références bibliographiques.

#### **INTRODUCTION:**

La conception assistée par ordinateur de circuits intégrés complexes a pris un essor magistral depuis quelques années. Ceci n'est pas dû au hasard, mais correspond bien à la nécessité de rabaisser les coûts de production en concevant vite et bien, de façon sûre et systématique. L'augmentation de la fiabilité dans la conception d'un circuit intégré passe forcément par la réduction de l'intervention humaine, et donc par l'utilisation d'outils logiciels offrant aux concepteurs une assistance efficace. Le facteur de rapidité est également primordial. Certains secteurs industriels font de plus en plus usage de circuits spécialisés pour des applications spécifiques (ASIC), et il devient impératif de pouvoir concevoir ces circuits rapidement et au moindre coût.

Dans cette étude, nous abordons un domaine très actuel de la conception assistée par ordinateur de circuits intégrés, celui de la compilation de silicium. La compilation de silicium est un environnement d'outils logiciels permettant d'obtenir de façon quasi automatique le dessin des masques d'un circuit à partir de descriptions structurelles ou fonctionnelles. Dans cet environnement, nous distinguons deux types d'outils : les assembleurs et les compilateurs de silicium.

#### Les assembleurs de silicium :

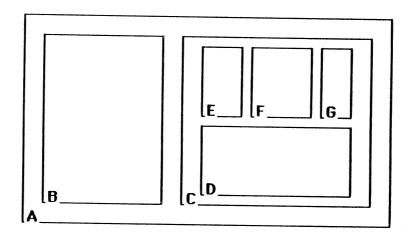

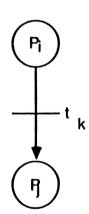

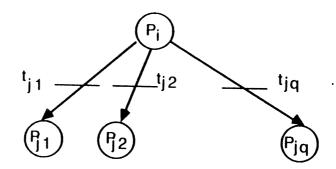

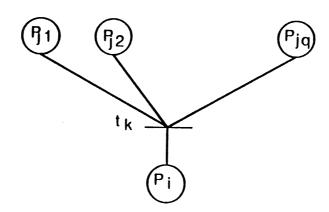

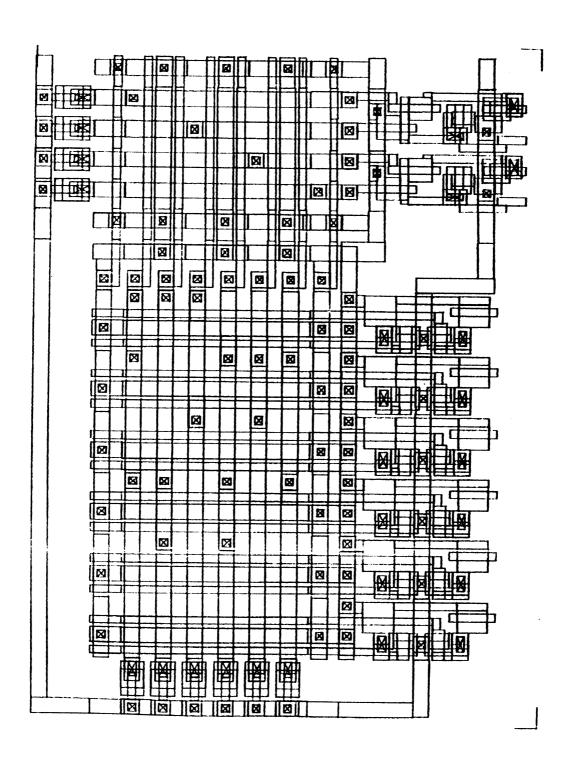

Les assembleurs de silicium sont des outils de génération automatique de dessin de circuits décrits comme un assemblage hiérarchique de blocs. Un bloc est soit un assemblage d'autres blocs, soit une structure régulière (PLA, RAM, ROM, registre, etc...), soit encore une cellule de base localement optimisée appartenant à une bibliothèque de cellules propre à une technologie donnée. L'assemblage hiérarchique de blocs est décrit de façon structurelle (figure 1) dans un langage adapté [LIM82] [MON85]. Les avantages liés à l'utilisation des assembleurs de silicium sont nombreux : le concepteur décrit et manipule les blocs de son circuit à l'aide de procédures dont l'exécution engendre la géométrie et le dessin du circuit. Il bénéficie alors des possibilités des langages de programmation de haut niveau :

- Manipulation de descriptions condensées donc facilement modifiables.

- Paramétrisation des procédures permettant d'engendrer des représentations différentes d'un circuit à partir d'une même description paramétrée différemment.

L'utilisation des assembleurs de silicium permet d'engendrer des circuits complexes à structure régulière, pour lesquels le facteur de régularité (nombre total de transistors divisé par le nombre de transistors effectivement dessinés) est très élevé.

Figure 1 : Description structurelle hiérarchique

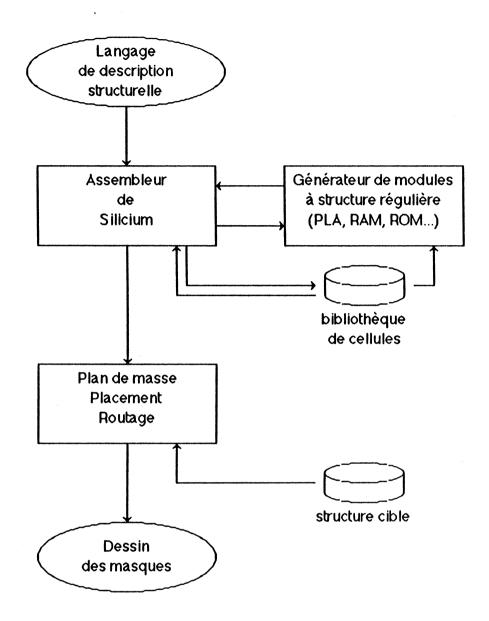

Dans un langage d'assemblage, un circuit est décrit en spécifiant sa structure, c'est à dire ses sous-circuits et leurs interconnexions. Il est donc nécessaire de disposer d'un ensemble d'outils qui s'articulent autour du langage de description structurelle, assurant les fonctions de génération du plan de masse, placement et routage sur la structure hôte (structure sans contraintes -full custom-, réseaux prédiffusés).

Figure 2 : environnement d'un assembleur de silicium.

#### Les compilateurs de silicium :

La description d'un circuit dans le contexte des assembleurs de silicium est constituée de procédures d'assemblage, chaque procédure correspondant à un bloc structurel du circuit. L'aspect fonctionnel du circuit n'est donc jamais pris en compte dans les descriptions, et les assembleurs de silicium n'ont donc aucun effort de synthèse à faire pour engendrer le dessin d'un circuit.

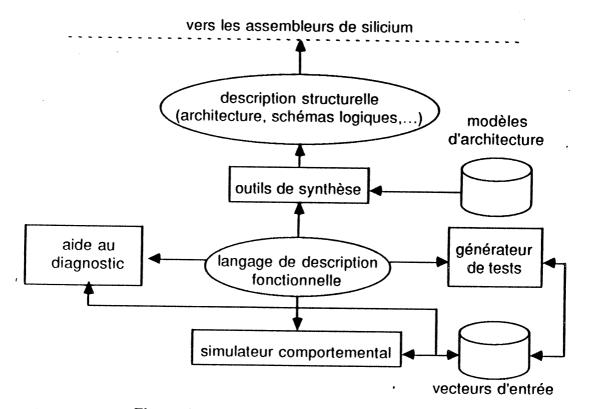

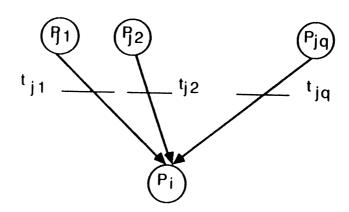

Les compilateurs de silicium sont des outils logiciels qui opèrent sur des descriptions fonctionnelles d'un circuit [SOU83] [BLA85]. Le compilateur de silicium engendre la structure d'un circuit à partir de son comportement, selon des modèles d'architecture donnés. Il applique des méthodes de synthèse à partir de descriptions comportementales. L'environnement de la compilation de silicium convient aux diverses méthodologies de conception (conception ascendante ou descendante) en offrant au concepteur un contrôle permanent à chacune des étapes de la synthèse. La sûreté de conception est également accrue, le concepteur étant libéré du risque d'erreur dû au traitement manuel d'un grand nombre de tâches fastidieuses. L'intérêt primordial des techniques de compilation de silicium réside dans l'utilisation de langages de description comportementale pour spécifier les circuits. On peut ainsi bénéficier, en plus des outils de synthèse, d'outils qui s'articulent autour de ces langages de haut niveau (figure 3) tels que les générateurs de tests fonctionnels, les outils de simulation comportementale, d'aide au diagnostic, etc... Le concepteur peut donc valider le comportement de son circuit avant d'en effectuer la synthèse.

Figure 3: Environnement d'un compilateur de silicium.

#### Les outils de synthèse dans la compilation de silicium :

Les principaux outils de synthèse peuvent se classer de la manière suivante :

- Les outils de synthèse combinatoire.

- Les outils de synthèse séquentielle (synthèse de partie contrôle).

- Les outils de synthèse de partie opérative.

#### Les outils de synthèse combinatoire :

Ces outils effectuent la synthèse logique d'un ensemble de fonctions Booléennes. Le principal problème que doivent résoudre les outils de synthèse combinatoire est celui de la minimisation multi-critères, c'est à dire la minimisation dont les critères d'optimalité sont déterminés par la structure cible (logique aléatoire, portes complexes, réseaux prédiffusés, PLA, ROM, ...).

#### Les outils de synthèse de contrôleur :

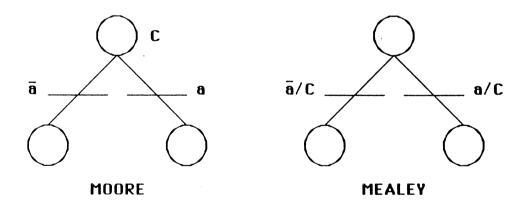

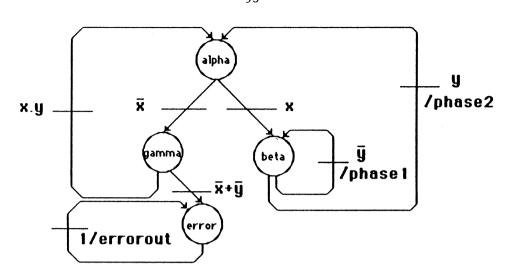

Ces outils synthétisent un contrôleur (partie contrôle de microprocesseur ou de circuit spécifique) à partir de sa description fonctionnelle qui est :

- soit une description du jeu d'instruction de la machine à contrôler exprimée à un niveau de transfert de registres. Ce type de description convient plutôt à une synthèse en microprogrammation, pour laquelle chaque instruction est interprétable par une séquence de microinstructions [NAG82].

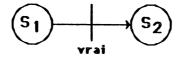

- -soit une description du graphe de contrôle en vue d'une synthèse dite cablée, pour laquelle chaque état du graphe est physiquement représenté au niveau de la machine implantée [BRO81] [PAP85].

#### Les outils de synthèse de partie opérative :

Partant de la description algorithmique (opérations arithmétiques et de transfert entre registres) qui caractérise le fonctionnement d'un circuit [HAF82] [KOW85], ces outils élaborent un schéma logique de la partie opérative selon certains modèles architecturaux. La synthèse est réalisée en extrayant dans la description les chemins de données, ainsi que le degré de parallélisme, c'est à dire les actions qui peuvent être exécutées pendant un même cycle de la machine [THO83] [JAM85].

L'objet de cette thèse est l'étude des outils de synthèse intégrables dans l'environnement des compilateurs de silicium. Nous nous intéressons aux outils de synthèse de circuits combinatoires et de contrôleurs. Notre approche s'inspire des récents progrès dans le domaine d'application de l'intelligence artificielle, en particulier celui de la conception de circuits VLSI [KOW85]. Cette approche se caractérise par la prise en compte de l'expérience des concepteurs au sens large, des "styles" de conception, des contraintes réalistes imposées par la technologie. On ne recherche plus la solution "optimale" dans un contexte donné, mais une solution viable selon les vœux d'un concepteur.

Les recherches sur la compilation de silicium au sein du laboratoire *Circuits et Systèmes* s'articulent autour du langage de description et de simulation fonctionnelles du système CADOC [CRA85]. Les outils de synthèse sont vus comme des serveurs du système CADOC, apportant une assistance "intelligente" aux concepteurs, aux différentes étapes de la conception. Les deux serveurs présentés dans cette thèse réalisent la synthèse de circuits combinatoires et de contrôleurs sur des cibles variées (PLA, ROM, logique aléatoire, portes complexes). L'accent étant mis sur la diversité des cibles et donc des critères d'optimisation, une approche à base de règles a été recherchée. Ceci permet d'associer à chaque structure cible un jeu de règles, prenant en compte l'enrichissement de l'expérience des concepteurs.

La première partie de la thèse concerne la synthèse combinatoire. Les principales structures cibles sont présentées ainsi que les critères d'optimisation qui en dépendent. Le problème de la minimisation logique d'un ensemble de fonctions Booléennes est traité en détail, et un système de règles pour la minimisation relative à une implantation sur PLA est proposé.

La seconde partie est consacrée à la synthèse de contrôleur. Les problèmes de modélisation et de conformité sont abordés, et une méthode de synthèse paramétrable par le type des points de mémorisation est décrite.

Un logiciel d'Assistance à la SYnthèse Logique (ASYL) a été écrit en PASCAL (15000 lignes) et est opérationnel sur les VAX et microVAX sous le système d'exploitation VMS. Ce système constitue une application pratique des principes de synthèse combinatoire et séquentielle exposés dans cette thèse.

# **PARTIE** I

# SYNTHESE AUTOMATIQUE A BASE DE REGLES POUR LA LOGIQUE COMBINATOIRE

#### I.1. RAPPELS SUR LA LOGIQUE COMBINATOIRE

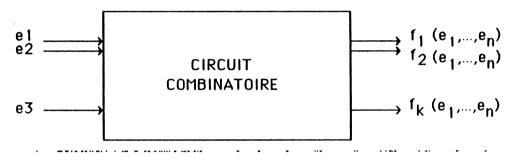

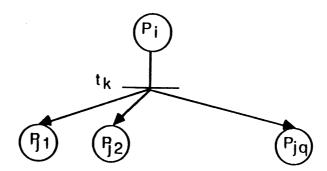

Un circuit combinatoire se caractérise par la connaissance de sa fonction d'entrées/sorties, c'est à dire l'ensemble des fonctions Booléennes [KUN65] qui définissent les valeurs des sorties du circuit pour toutes les combinaisons possibles de ses entrées (figure 4). Une fonction Booléenne à n entrées doit donc être définie pour les 2<sup>n</sup> états possibles de ses entrées.

Figure 4: Circuit combinatoire.

En raison des différences de terminologie qui apparaissent dans la littérature, nous allons rappeler les principes et les définitions qui sont à la base de tout ce qui va suivre.

Une fonction Booléenne peut prendre ses valeurs dans l'ensemble (0,1,ø). La pseudo valeur ø signifie 1 ou 0 indifféremment.

#### Définition 1.

Une fonction Booléenne qui prend ses valeurs dans (0,1) est dite complète ou complètement spécifiée.

#### Définition 2.

Une fonction Booléenne qui prend ses valeurs dans (0,1,ø) est dite phi-booléenne, ou incomplète ou encore incomplètement spécifiée.

Il est à noter que les circuits combinatoires ne réalisent physiquement que des

fonctions complètement spécifiées. L'usage de la pseudo valeur ø ne peut intervenir qu'au niveau de la spécification.

#### Définition 3.

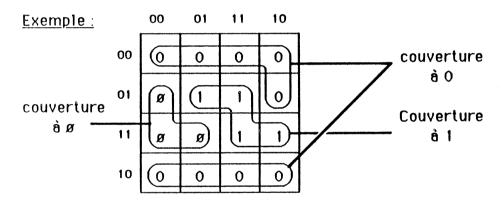

La couverture à 0, à 1, ou à ø d'une fonction Booléenne est l'ensemble des combinaisons des variables d'entrée pour lesquelles la fonction vaut 0, 1, ou ø. La couverture à ø est également appelée couverture indifférente.

Une fonction Booléenne complète peut être décrite par l'une de ses couvertures à 1 ou à 0, l'autre étant comprise comme le complément de l'une. Une fonction incomplète peut être décrite par deux parmi ses trois couvertures à 0, à 1, et à ø, la troisième couverture est alors le complément de l'union des deux autres.

Toute couverture d'une fonction Booléenne peut être exprimée par une expression Booléenne construite à partir des variables de la fonction et d'un certains nombre d'opérateurs appelés opérateurs logiques. Les opérateurs binaires les plus fréquemment utilisés sont l'union (ou, +), l'intersection (et, .). L'unique opérateur logique unaire est la négation (non, ¬).

#### Définition 4.

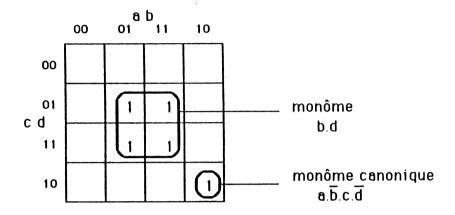

Un **monôme** est une expression Booléenne composée du produit de une ou plusieurs variables apparaissant sous forme normale (x) ou complémentée ( $\neg$ x). ex :  $x_1.\neg x_2.x_3$  est un monôme.

#### Définition 5.

Un monôme est dit canonique dans une fonction si toutes les variables apparaissant dans la fonction apparaissent dans sa constitution.

ex:  $x_1.\neg x_2.x_3$  est un monôme canonique dans  $f(x_1, x_2, x_3)$ .

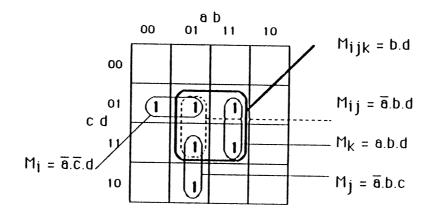

Figure 5 : Illustration des définitions 4 et 5.

#### Définition 6.

Une expression Booléenne exprimée sous la forme d'une somme de monômes est appelée **polynôme**. On dit aussi que l'expression est sous sa forme normale. ex : E  $(a, b, c, d) = b.d + a.\neg b.c.\neg d$  (figure 5).

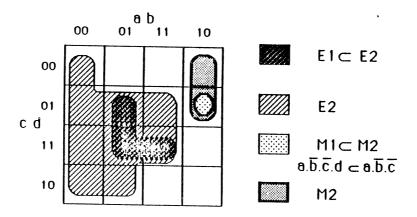

#### Définition 7.

Une expression Booléenne  $E_1$  est incluse dans une expression Booléenne  $E_2$  si et seulement si il existe une expression Booléenne  $E_3$  telle que :  $E_2 = E_1 + E_3$ .

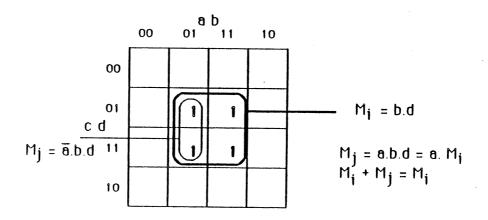

Remarque 1 : Un monôme  $M_1$  est inclus dans un monôme  $M_2$  si les variables de  $M_2$  apparaissent sous la même forme dans  $M_1$ .

Remarque 2 : si  $M_1$  est inclus dans  $M_2$  , alors  $M_1 + M_2 = M_2$ .

Figure 6: Inclusion d'une expression dans une autre.

#### Définition 8.

La taille d'un monôme M de p variables dans une fonction de n variables est égale au nombre de monômes canoniques inclus dans M, soit 2<sup>n-p</sup>.

'ex : dans la figure 5, le monôme b.d a une taille égale à  $2^{4-2} = 4$ .

#### Définition 9.

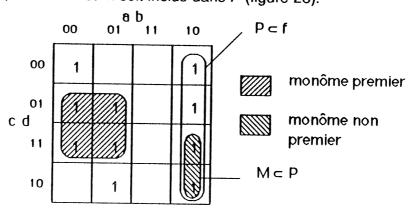

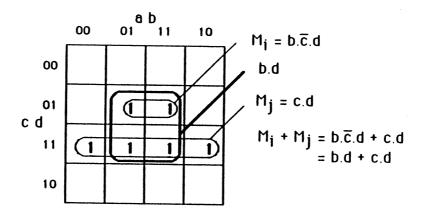

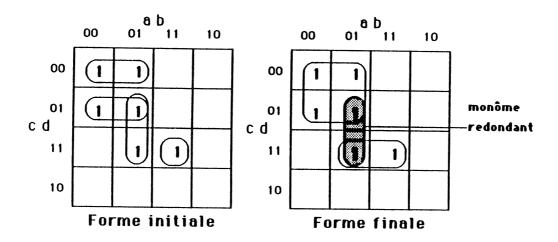

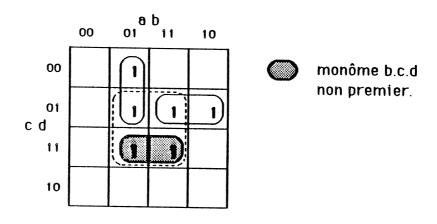

Un monôme M est dit **premier** dans une fonction f s'il n'existe pas de monôme P≠M tel que P soit inclus dans f et M soit inclus dans P (figure 23).

Figure 7 : Illustration de la définition 9.

Le lecteur peut se rapporter à [KUN65] pour de plus amples détails et des définitions plus formelles concernant l'algèbre de Boole.

# I.2. LES STRUCTURES "CIBLE" POUR LA LOGIQUE COMBINATOIRE ET LES CRITERES D'OPTIMISATION

Nous allons présenter les différentes structures pour l'implémentation des circuits combinatoires. Les méthodes de synthèse logique étant dépendantes de la technologie, nous exposons les critères d'optimisation relatifs à chacune des structures "cible".

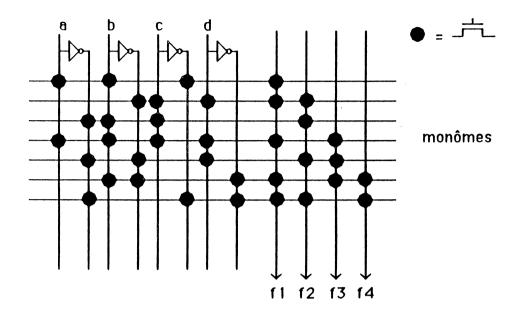

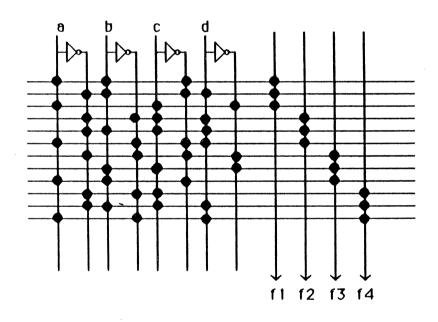

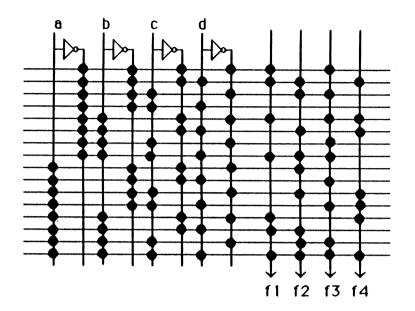

#### 1.2.1. La synthèse à base de réseaux programmables.

On désigne par réseau logique programmable une structure logique constituée de deux matrices, permettant d'implémenter un ensemble de fonctions Booléennes des mêmes variables et exprimées par des polynômes. La première matrice (étage ET) réalise les monômes, c'est à dire les produits de variables complémentées ou non, la seconde matrice (étage OU) réalise les fonctions comme des sommes de monômes. Le PLA (figure 8) est un réseau logique dont les deux matrices sont programmables. Le PAL (figure 9) est un réseau logique dont seul l'étage ET est programmable. Dans un PAL, l'étage OU est préprogrammé de telle sorte qu'un monôme n'est connecté qu'à une seule fonction. Contrairement au PAL, la ROM (read only memory) est un réseau logique dont seul l'étage OU est programmable. L'étage ET d'une ROM réalise un décodeur, c'est à dire un ensemble de monômes canoniques (figure 10).

Figure 8 : Un PLA.

Figure 9: Un PAL.

Figure 10: Une ROM.

#### Les critères d'optimisation pour la synthèse à base de réseaux logiques :

Dans tous les cas, l'optimalité d'un circuit combinatoire est liée à la surface occupée sur le silicium ainsi qu'aux performances du circuit, c'est à dire ses temps de réponse et sa dissipation thermique (consommation). Dans le cas des réseaux logiques programmables, les performances dépendent pour une technologie donnée, de trois paramètres qui sont :

- la charge des entrées,

- la charge des monômes,

- la charge des sorties.

La charge d'une entrée est le nombre de transistors qui lui sont connectés. La charge d'un monôme est le nombre de transistors qui le connectent aux sorties. La charge d'une sortie est le nombre de transistors qui lui sont connectés. D'une façon générale, on admet que les performances d'un réseau logique programmable sont meilleures, d'autant que le nombre de transistors qu'il contient est petit.

En ce qui concerne la surface, elle dépend du nombre d'entrées **n**, du nombre de sorties **k**, et du nombre de monômes **p**. En première approximation, on peut la calculer ainsi :

#### $S = p \cdot (2n+k)$

Si l'on admet que la minimisation ne porte pas sur le nombre d'entrées et de sorties du circuit, on déduit que la surface du réseau est directement liée au nombre de monômes.

#### \* Cas de la ROM.

Une ROM réalise des fonctions exprimées comme une somme de monômes canoniques (1<sup>ere</sup> forme de Lagrange). Pour une combinaison des variables d'entrées, il n'existe qu'un seul monôme canonique vrai. Ainsi, pour une fonction donnée, un monôme canonique est soit obligatoire, soit interdit. Du fait de la non existence de redondance dans les formes canoniques, on ne peut pas parler de minimisation logique dans une ROM. La seule minimisation possible dans une ROM est d'ordre topologique, et consiste à supprimer dans l'étage de décodage les monômes qui n'apparaissent dans aucune des fonctions.

#### \* Cas du PAL.

Dans un PAL, chaque fonction est réalisée indépendamment des autres. Si un monôme doit apparaître dans q fonctions, il sera dupliquer q fois dans le PAL. Il est évident que le PAL ne présente aucun intérêt en tant que partie d'un circuit intégré, mais il existe en tant que circuit programmable pour la réalisation de cartes. La capacité d'accueil d'un PAL est déterminée par le nombre de fonctions, le nombre total de monômes, et le nombre de monômes par fonctions. Ainsi, la minimisation logique pour une synthèse sur PAL est une réduction locale du nombre de monômes dans chacune des fonctions à implémenter. La minimisation locale d'une fonction Booléenne est exposée en II.3.

#### \* Cas du PLA.

Le PLA est très largement utilisé dans la conception de circuits intégrés du fait qu'il implémente de façon régulière un ensemble de fonctions combinatoires sur une surface généralement inférieure à celle de la ROM équivalente [GRA83]. La minimisation logique pour une synthèse sur PLA est une réduction globale du nombre

total de monômes, dans laquelle toutes les fonctions à implanter sont considérées simultanément. La minimisation globale d'un ensemble de fonctions Booléenne est exposée en II.3. Indépendamment de la minimisation logique, les PLA peuvent être minimisés topologiquement afin de gagner en surface. En effet, la grande majorité des PLA est constituée de matrices "creuses" entraînant des pertes considérables de surface. Aussi, des techniques d'optimisation topologique [PAI84] [PER82] ont été développées pour récupérer les zones "creuses" (sans transistors) par des méthodes de compactage, de pliage, ou bien de triangularisation du PLA initial.

#### 1.2.2. La synthèse combinatoire en logique aléatoire.

La synthèse en logique aléatoire consiste à implanter un circuit combinatoire à l'aide d'un réseau d'opérateurs interconnectés. Les opérateurs peuvent réaliser des fonctions logiques simples (portes AND, OR, NAND, NOR, INV...) ou bien des fonctions plus complexes (décodeur, multiplexeur...). Pour réaliser un circuit combinatoire en logique aléatoire, le concepteur dispose d'une bibliothèque d'opérateurs qui est liée à la structure d'accueil (circuits TTL pour la conception de cartes, bibliothèque de cellules pour les réseaux prédiffusés...).

Figure 11 : circuit combinatoire en logique aléatoire.

#### Les critères d'optimisation pour la synthèse en logique aléatoire :

Si le nombre de couches logiques dans un réseau logique programmable est toujours égal à 2, ce n'est plus le cas ici. En logique aléatoire, le nombre de couches

logiques est égal au nombre maximum d'opérateurs qu'un chemin reliant une entrée à une sortie peut traverser. Le temps de réponse du circuit est donc directement lié au temps de propagation dans les opérateurs, et la minimisation du nombre de couches logiques est donc un premier critère d'optimalité.

Le second critère d'optimalité est lié à la surface du circuit. La surface occupée dépend du nombre d'opérateurs, mais également du nombre d'interconnexions entre ces opérateurs. Réduire le nombre de connexions facilite toujours l'implantation, qu'elle soit manuelle (dessin au micron) ou bien automatisée (placement et routage sur des structures à contraintes telles que les réseaux prédiffusés).

Minimiser le nombre d'opérateurs n'a de sens que relativement à une bibliothèque donnée. Il serait dommage de réaliser un multiplexeur avec des portes si l'opérateur multiplexeur existe déjà dans la bibliothèque. Ainsi, il est nécessaire que les algorithmes de minimisation pour la synthèse en logique aléatoire soient paramétrables par un ensemble d'opérateurs disponibles.

#### \* Les méthodes de synthèse en logique aléatoire :

Dés le début des années 60, la C.A.O s'est intéressée à la synthèse en logique aléatoire. Les premières méthodes proposées se limitaient à la synthèse en portes NAND ou NOR. Dietmeyer et Schneider [DIE63] proposent une méthode de factorisation pour la synthèse en portes NAND ou NOR, respectant les limitations sur le nombre d'entrées des opérateurs et basée sur l'équivalence suivante :

NOR (a, b, c, d) = NOR (NOR (NOR (a, b)), c, d).

Cette technique consiste à réduire le nombre d'opérateurs par la génération de facteurs communs.

#### exemple:

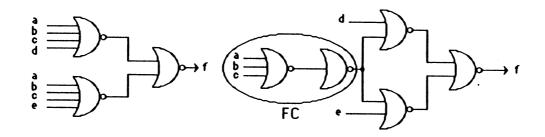

Considérons la fonction de 5 variables f = NOR (NOR (a, b, c, d), NOR (a, b, c, e)), devant être réalisée avec des portes NOR à 3 entrées maximum. La décomposition de cette fonction se fait à l'aide du facteur commun FC = NOR (NOR (a, b, c)).

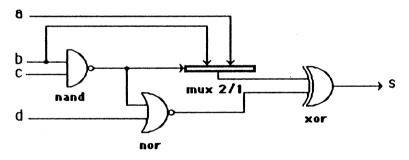

Figure 12: synthèse en NOR par factorisation.

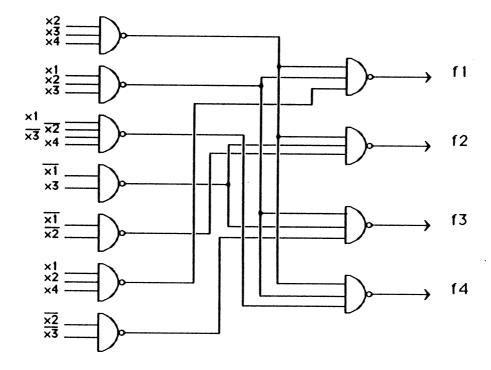

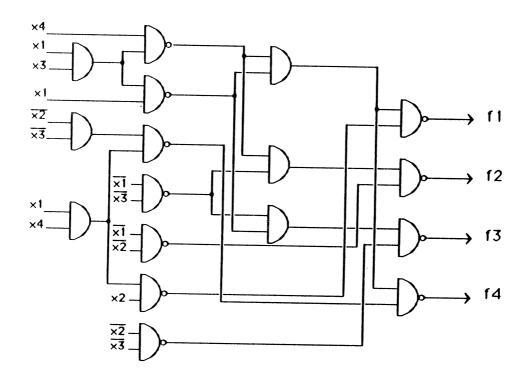

Ces principes de factorisation ont été étendus à la synthèse multi-fonctions à partir d'une représentation en deux couches ET/OU minimisée (figure 13) [SU71] [HAN85]. La figure 14 représente le circuit de la figure 13 synthétisé par factorisation pour des opérateurs à deux entrées et pour une sortance (nombre d'entrées connectées à une sortie) maximale égale à 2.

Figure 13: Circuit sur 2 couches sans contraintes.

Figure 14 : le même circuit synthétisé sous contraintes.

Dans [SCH68] et [CER74], les auteurs présentent des techniques de synthèse paramétrées par un ensemble de modules fonctionnels. Les méthodes procèdent par décomposition des fonctions à réaliser en termes d'assemblage de modules fonctionnels.

Les techniques de recherche opérationnelle, notamment la programmation en nombre entier ont également permis de résoudre les problèmes de la synthèse logique sous contraintes. Cette approche est celle présentée par Muroga dans [MUR72] et [MUR76]. La formulation en un problème de programmation en nombre entier permet de prendre en compte tous les choix du concepteur, quant aux types d'opérateurs à employer et aux contraintes à respecter. Une fois le problème formulé, sa résolution est éffectuée par une méthode de recherche opérationnelle appelée "méthode de l'énumération implicite", à travers une fonction de coût, définie par le concepteur en fonction des critères d'optimisation souhaités. Si le problème admet une solution, alors cette solution est un optimum global , relativement à la fonction de coût.

Si une telle approche est d'un intérêt évident sur le plan théorique, elle l'est

beaucoup moins sur le plan pratique en raison de performances médiocres quant au temps d'exécution nécessaire à la résolution du problème. A titre indicatif, le temps de calcul sur un IBM 360 nécessaire pour obtenir d'une fonction de 4 variables un réseau optimal avec 5 portes NOR et 16 connexions, est de 3500 secondes [MUR76]. La figure 14 représente une solution optimale pour un additionneur 1 bit en portes NOR avec les critères d'optimisation suivants :

- la minimisation du nombre de portes,

- la minimisation du nombre de connexions.

Figure 15 : cellule optimale en NOR d'un additionneur 1 bit.

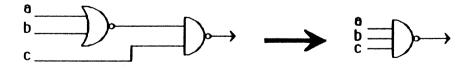

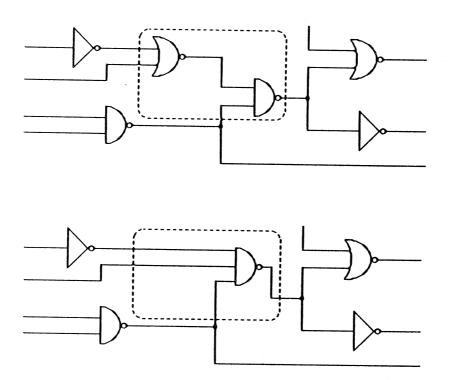

Depuis le début des années 80, de nouvelles techniques pour la synthèse en logique aléatoire apparaissent, qui s'écartent des méthodes algorithmiques classiques, en optant pour des approches orientées vers les systèmes experts et les systèmes de règles. Les méthodes les plus significatives à retenir sont construites sur le principe de transformations locales. Le circuit optimisé est obtenu à partir des fonctions minimisées, auxquelles on applique une série de transformations locales formulées par des règles [DAR80] [GEU85].

Figure 16 : règle de transformation locale.

Figure 17: transformation locale appliquée à un circuit.

Les méthodes basées sur des optimisations locales sont efficaces et conviennent à la synthèse de gros circuits. De plus, un concepteur expert peut aisément formuler les contraintes à respecter, et affiner la synthèse par l'adjonction de nouvelles règles caractérisant son savoir faire.

# 1.2.3. La synthèse combinatoire en portes complexes.

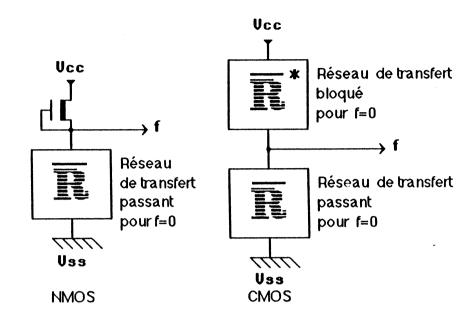

La synthèse en portes complexes est une synthèse combinatoire de bas niveau, pour laquelle les fonctions logiques sont réalisées à l'aide de réseaux d'interrupteurs (transistors MOS) [CAL62].

Figure 18: Portes complexes en technologie NMOS et CMOS.

#### Les critères d'optimisation pour la synthèse en portes complexes :

L'optimalité d'une porte complexe dépend de la surface qu'elle occupe sur le silicium et de ses performances. Les performances sont principalement liées au nombre de transistors en série et en parallèle dans le réseau. La surface dépend du nombre total de transistors, mais aussi du dimensionnement des transistors. Plus il y a de transistors en série ou en parallèle dans un réseau, plus grand doivent ils être dimensionnés, rendant ainsi l'implantation sur silicium plus difficile. Pour faire de la synthèse en portes complexes, il est donc nécessaire de minimiser le nombre total de transistors, mais aussi le nombre de transistors en série ou en parallèle.

Une méthode de minimisation d'un réseau de transfert est présentée dans [SAU85], qui procède de la façon suivante :

1/ l'expression de la fonction de transfert étant sous la forme d'un polynôme minimisé logiquement, un réseau initial série-parallèle est construit, dans lequel chaque monôme est représenté par un chemin (figure 19) ;

2/ Un algorithme de partitionnement engendre ensuite un ordonnancement optimisé des variables et des chemins série-parallèles du réseau, pour le transformer

en un réseau arborescent, par le fusionnement de certains transistors sur une extrémité du réseau (figure 20) ;

3/ le réseau est ensuite transformé en un réseau non série-parallèle, par le fusionnement de transistors sur l'autre extrémité du réseau, en vérifiant que les chemins créés ne changent pas la fonction de transfert (figure 21).

### exemple:

Considérons la fonction  $f = \neg x_1 \cdot \neg x_3 + x_2 \cdot \neg x_4 + x_1 \cdot \neg x_2 \cdot x_3$ .

### \* étape 1.

Le polynôme minimal de la fonction de transfert de  $\mathbf{f}$  est obtenu par minimisation logique de  $\neg \mathbf{f}$ .

$$\neg f = x_1.x_2.x_4 + \neg x_1.x_3.x_4 + x_1. \neg x_2. \neg x_3 + \neg x_1. \neg x_2.x_3$$

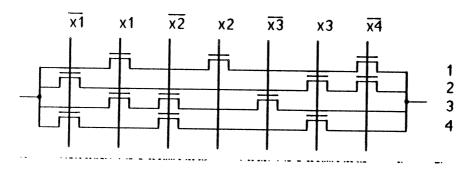

Figure 19 : Réseau initial série-parallèle.

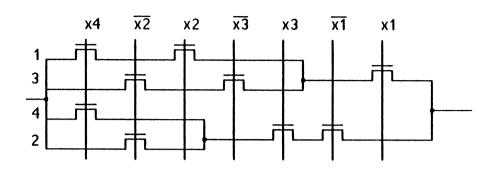

### \* étape 2.

L'ordonnancement optimal (qui permet un gain maximum en nombre de transistors) est le suivant :

- pour les variables :  $x_4$ ,  $\neg x_2$ ,  $x_2$ ,  $\neg x_3$ ,  $x_3$ ,  $\neg x_1$ ,  $x_1$

- pour les lignes : 1, 3, 2, 4

Figure 20 : Réseau série-parallèle optimal.

Le gain obtenu après le fusionnement des transistors est de 25 %.

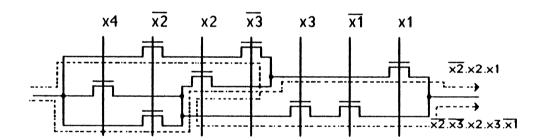

### \* étape 3.

On peut fusionner les transistors contrôlés par la variable  $x_4$  sur l'extrémité gauche du réseau. Les nouveaux chemins introduits par ce fusionnement ne modifie pas la fonction de transfert car ils sont impossibles (caractérisés par des monômes toujours faux).

Figure 21: Réseau final non série-parallèle.

Le gain finalement obtenu après les trois étapes est de 8/12 = 33 %.

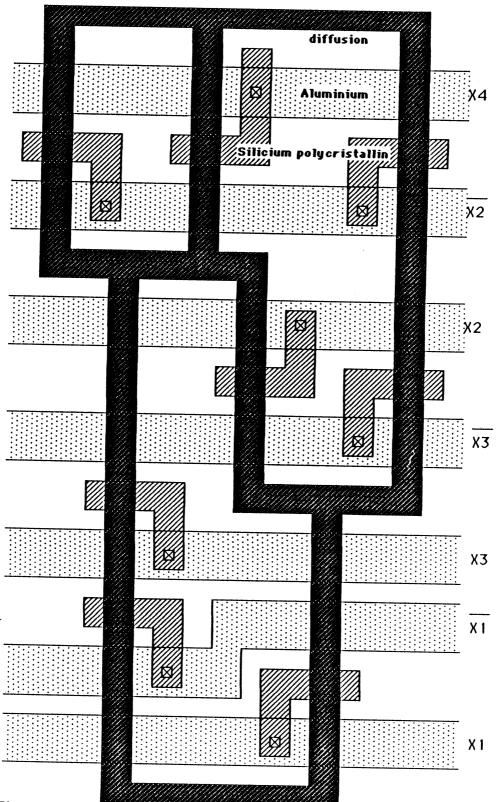

La synthèse en portes complexes s'avère intéressante pour les petits circuits combinatoires, car si la surface d'implantation n'est pas toujours inférieure à celle du PLA équivalent après minimisation topologique, les performances sont meilleures (fonction de 5 variables : porte complexe NMOS : 7,5 ns ; PLA NMOS : 16 ns). De plus, l'implantation des réseaux de transistors bien structurés est automatisable en

utilisant des techniques d'implantation en lignes ou en blocs de diffusion [SAU85]. Ces méthodes s'adaptent parfaitement à la synthèse multi-fonctions en conservant un même ordonnancement des entrées à travers les différentes fonctions.

Les techniques d'implantation, de minimisation logique et topologique de portes complexes ont fait l'objet de nombreuses études ; le lecteur intéressé peut consulter [THU83] pour de plus amples informations.

Figure 22: Implantation en lignes de diffusion du réseau de la figure 20. (transistors non dimensionnés)

# I.3. LA MINIMISATION LOGIQUE A BASE DE REGLES

Ce chapitre est consacré à l'étude d'une nouvelle approche au problème de la minimisation logique. Le premier paragraphe positionne le problème et donne l'état de l'art dans le domaine. Les paragraphes suivants concernent notre manière de résoudre le problème de la minimisation logique en s'appuyant sur un système de règles. Le logiciel ASYL a mis en application les règles de minimisation, et a permis d'en vérifier l'efficacité relativement aux résultats obtenus et aux temps de calcul consommés.

### I.3.1. Position du problème et état de l'art

Le problème de la minimisation logique s'est posé au début des années 50, à une époque où le matériel était coûteux. Il était alors indispensable de développer des techniques permettant d'implémenter une ou plusieurs fonctions Booléennes avec un nombre minimum de ressource (diodes, relais, transistors, portes,...). La minimisation logique devenait à partir de cette époque un sujet de recherche de toute première importance.

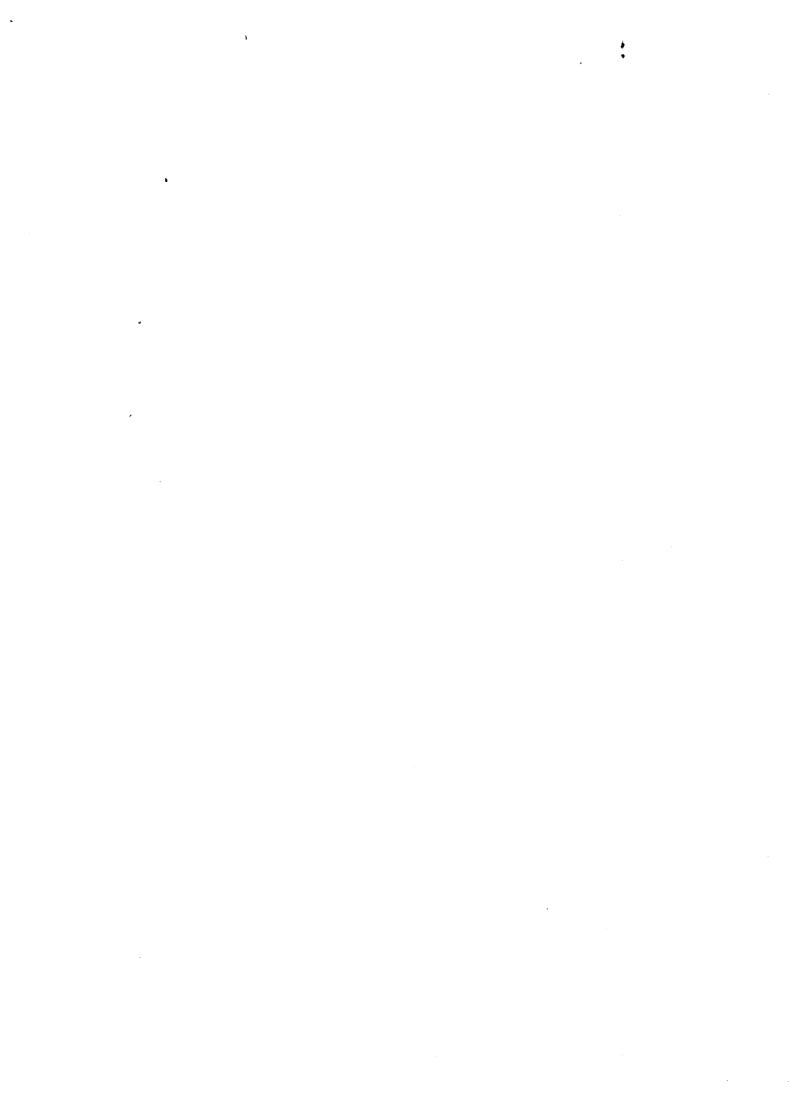

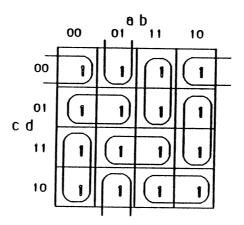

La première technique manuelle de minimisation logique qui est apparue à cette époque est celle des tableaux de Karnaugh (figure 23), qui permet de minimiser des fonctions de moins de 5 variables. Des techniques automatisables et plus sophistiquées ont été introduites par Quine et Mac Cluskey [MCC65], puis par Tison qui mit au point la théorie des consensus et son application à la minimisation logique [TIS65] [TIS67]. Ces dernières méthodes procèdent en deux étapes qui sont :

- la génération de tous les monômes premiers (définition 9) de la fonction,

- l'extraction d'une couverture première irrédondante.

Le principe d'extraction d'une couverture première irrédondante permet d'obtenir une solution optimale au sens du nombre total de monômes. Elle s'obtient en sélectionnant parmi tous les monômes premiers de la fonction, un ensemble de taille minimale dans lequel aucun monôme n'est redondant.

Les méthodes de génération de tous les monômes premiers ont été rendues plus efficaces au cours des années suivantes [SLA70], mais malgré cela, le caractère

combinatoire du problème rend ces techniques totalement impraticables pour des fonctions dépassant une taille moyenne (moins de 12 variables).

Figure 23 : Minimisation à partir d'un tableau de Karnaugh.

Dans le début des années 70, la minimisation logique n'est plus aussi essentielle qu'auparavant pour de nombreux concepteurs, en raison d'une forte diminution du coût des composants. Néanmoins, elle retrouve un intérêt primordial avec le développement de circuits compacts à forte densité d'intégration du type microprocesseurs ou bien circuits spécialisés (ASIC). La taille des problèmes combinatoires évoluant avec la complexité des circuits et les capacité d'intégration, de nouvelles méthodes sont développées, qui conduisent à des solutions presque optimales.

Les programmes les plus classiques pour la minimisation logique multi-fonctions sont MINI [HON74], PRESTO [BRO81], ESPRESSO-IIC [BRA85], McBOOLE [DAG85], MOM [AGR85] et PHIPLA [LAA85]. Ces programmes sont tous de type algorithmique, basés sur des considérations heuristiques pour limiter les problèmes dus à l'explosion combinatoire (croissance exponentielle du temps CPU avec le nombre de variables). Malgré ces heuristiques, certains programmes ne peuvent encore traiter des problèmes dépassant 12 à 16 variables. C'est le cas des programmes PHIPLA et MOM qui opèrent sur la forme canonique des fonctions (2<sup>n</sup> monômes pour n variables).

Notre approche du problème de la minimisation logique est complètement différente dans sa formulation à base de règles et dans ses objectifs. Dans le but de pouvoir minimiser des systèmes combinatoires de grande taille (50 variables d'entrée

et 100 fonctions), nous avons défini des règles de transformation qui garantissent l'obtention d'un résultat final sans redondance, mais pas nécessairement optimal.

# I.3.2. Un système de règles pour la minimisation locale d'une fonction complète.

La minimisation locale concerne la réduction d'une seule fonction Booléenne, indépendamment de toute autre fonction. Les règles que nous avons définies pour la minimisation locale transforment l'expression de la couverture à 1 de la fonction à minimiser en une somme quasi minimale de monômes premiers. Ces règles ont été étudiées de façon à respecter les deux conditions suivantes :

- 1/ On ne doit pas évaluer la forme canonique (2<sup>n</sup> monômes pour n variables) de la fonction à minimiser, contrairement aux méthodes de Quine-Mc Cluskey.

- 2/ On ne doit pas engendrer tous les monômes premiers ( $\leq 3^n$ /n pour n variables) de la fonction à minimiser, contrairement à la méthode classique des consensus.

### 1.3.2.1. Règles pour la mise sous forme normale d'une expression:

Le premier ensemble de règles intervient pour la réécriture d'une expression Booléenne quelconque en un polynôme logiquement équivalent. Ceci est obtenu en réduisant la portée des opérateurs de négation à une variable simple, et en développant les factorisations.

Soient  $E_i$ ,  $E_j$ ,  $E_k$ ,  $E_l$  des expressions Booléennes quelconques.

Règles pour la réduction de la portée des opérateurs de négation :

Règle 1: non (non  $(E_i)$ ) -->  $E_i$

Règle 2: non  $(E_i.E_j)$  --> non  $(E_i)$  + non  $(E_j)$

Règle 3: non  $(E_i + E_j)$  --> non  $(E_i)$  . non  $(E_j)$

Règles pour le développement des factorisations :

Règle 4:  $E_i \cdot (E_j + E_k)$  -->  $E_i \cdot E_j + E_i \cdot E_k$

Règle 5:  $(E_i + E_j) \cdot (E_k + E_l) --> E_i \cdot (E_k + E_l) + E_j \cdot (E_k + E_l)$

Ces règles sont appliquées sur l'expression à transformer jusqu'à ce qu'aucune d'elles ne puisse l'être.

# I.3.2.2. Règles pour la minimisation locale:

Ces règles transforment une somme de monômes quelconque en une somme quasi minimale de monômes premiers.

Considérons une fonction Booléenne complètement spécifiée f définie par sa couverture à 1 comme une somme de p monômes  $M_1, M_2, ..., M_p$ ; et posons  $EM = (M_1, M_2, ..., M_p)$ .

Soient  $M_i$ ,  $M_j$  deux monômes de EM, et x une variable Booléenne. La négation de x est notée  $\neg x$ .

### Règles primaires de transformation :

Les règles primaires de transformation sont dérivées des règles élémentaires du calcul formel Booléen. Ce sont des règles de faible complexité, qui engendrent des transformations locales à fort gain.

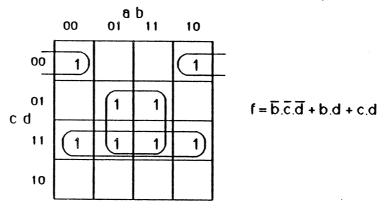

Règle 6 : règle de tautologie.

si  $M_j = x$  et si  $M_j = \neg x$  alors f est une tautologie (a +  $\neg a = 1$ ).

Losque cette règle est appliquée, le processus de minimisation est interrompu, la fonction f étant formellement toujours vraie (figure 24).

Figure 24 : Règle de tautologie.

### Règle 7: règle d'exclusion d'un terme nul.

si il existe un monôme  $M_i$  de Em tel que dans sa constitution, apparaissent la variable x et son complément  $\neg x$ , alors  $M_i$  est un terme toujours nul  $(x.\neg x=0)$  et est supprimé de EM.

De tels monômes peuvent apparaître après le développement des factorisations dans l'application des règles 1 à 5.

### Règle 8 : règle d'identité.

si  $M_i = M_j$ , alors  $M_j$  est supprimé de EM (a + a = a).

Le gain associé à l'application de cette règle est de 1 monôme.

### Règle 9 : règle d'adjacence.

si il existe une variable x telle que  $M_j = x.N$  et  $M_j = \neg x.N$ , où N est un monôme, alors  $M_j$  et  $M_j$  sont adjacents (N =  $M_j + M_j$ ) et

- M<sub>j</sub> est supprimé de EM,

- Mi est remplacé dans EM par N. (figure 25)

Le gain associé à l'application de la règle d'adjacence est de 1 monôme et de 1 variable dans le monôme  $M_{\rm i}$ .

Figure 25 : Règle d'adjacence.

### Règle 10 : règle d'inclusion.

si il existe un monôme N tel que  $M_j = M_i.N$ , alors  $M_j$  est inclus dans  $M_i$   $(M_i + M_j = M_i)$  et

- M<sub>j</sub> est supprimé de EM. (figure 26).

Le gain associé à l'application de cette règle est de 1 monôme.

Figure 26: Règle d'inclusion.

### Règle 11 : Règle d'expansion locale.

si il existe une variable x et deux monômes N et P tels que  $M_j = \neg x.N.P$  et  $M_j = x.P$ , alors la variable  $\neg x$  peut être supprimée dans  $M_j$  ( $\neg a.b.c + a.c = b.c + a.c$ ). (figure 27). Le gain associé à l'application de cette règle est de 1 variable dans le monôme  $M_j$ .

Figure 27 : Règle d'expansion locale.

L'application des règles 6 à 11 ne résoud que partiellement le problème de la minimisation locale d'une fonction complète en engendrant des monômes qui ne sont pas toujours premiers. D'une part, la qualité du résultat peut s'avérer insuffisante et d'autre part, il n'est pas toujours possible de prouver formellement qu'une fonction est une tautologie.

#### exemple 1:

$$f = \neg a. \neg c. \neg d + \neg a. \neg c.d + \neg a.b.d + a.b.c.d$$

L'application des règles 6 à 11 va engendrer la solution minimisée suivante :

$$f = \neg a. \neg c + \neg a.b.d + b.c.d.$$

(figure 28).

On n'a pu détecter la présence du monôme redondant ¬a.b.d.

Figure 28

### Exemple 2:

$$f = \neg a.b. \neg c + a. \neg c.d + b.c.d$$

Aucune des règles 6 à 11 n'est applicable et on ne peut détecter la redondance de la variable c dans le monôme b.c.d (figure 29).

Figure 29.

### Exemple 3:

f=¬b.¬c.¬d+¬a.¬c.d+b.c.d+a.c.¬d+¬a.¬b.c+¬a.b.¬d+a.b.¬c+a.¬b.d Là encore, aucune des règles 6 à 11 n'est applicable, et on ne peut pas prouver formellement que f est une tautologie (figure 30).

Figure 30.

### Règles secondaires de transformation :

Les règles secondaires ont été définies dans le but d'améliorer la qualité de la minimisation locale et de pouvoir faire de la preuve formelle de tautologie. Ces règles sont complémentaires des règles primaires décrites précédemment, et doivent forcément leur être associées pour être opérationnelles. L'association des règles primaires et secondaires engendre pour toute fonction complète, une somme de monômes premiers quasi minimale. Les règles secondaires de transformation s'appuient sur la théorie des consensus du premier ordre [TIS65].

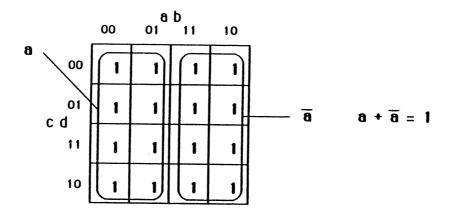

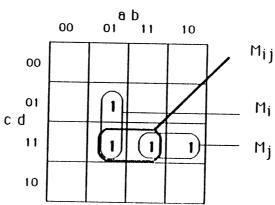

### Définition 10:

Soient deux monômes  $M_j$  et  $M_j$ . On appelle consensus du premier ordre entre  $M_j$  et  $M_j$ , le monôme de plus grande taille  $M_{ij}$  tel que :

- M<sub>ij</sub> est inclus dans M<sub>i</sub> + M<sub>j</sub>,

- $M_{ij}$  n'est pas inclus dans  $M_i$ ,

- $M_{ij}$  n'est pas inclus dans  $M_{ij}$  (figure 31).

Remarque : Par propriété de l'inclusion, si  $M_{ij}$  est le consensus entre  $M_i$  et  $M_j$ , alors

$$\mathsf{M}_{ij} + \mathsf{M}_i + \mathsf{M}_j = \mathsf{M}_i + \mathsf{M}_j$$

Figure 31 : Consensus du premier ordre entre deux monômes.

Les règles 12 à 14 sont des règles génératrices de nouveaux monômes, consensus entre des monômes existant dans l'ensemble EM. Les consensus ainsi

engendrés ne doivent en aucun cas être ajoutés à l'ensemble EM ; ils ne servent qu'à faire d'éventuelles simplifications.

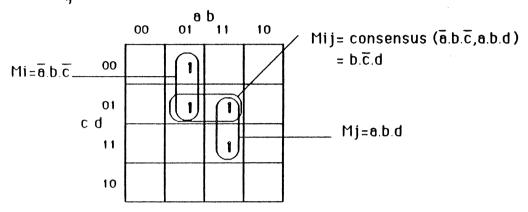

### Règle 12 : Règle d'identité par consensus.

Si il existe un consensus  $M_{ij}$  entre deux monômes  $M_i$  et  $M_j$  de EM, et si  $M_{ij}$  appartient à EM, alors  $M_{ii}$  est redondant et est supprimé de EM (figure 32).

Figure 32 : Règle d'identité par consensus.

### Règle 13 : Règle d'absorption par consensus.

Si il existe un consensus  $M_{ij}$  entre deux monômes  $M_i$  et  $M_j$  de EM, et si il existe  $M_k$  dans EM tel que  $M_{ij}$  soit inclus dans  $M_k$ , alors  $M_k$  est redondant et est supprimé de EM (figure 33).

Figure 33 : Règle d'absorption par consensus.

### Remarque:

Par définition du consensus,  $M_{ij}$  est inclus dans  $M_i + M_j$  donc  $M_i + M_j + M_k = M_i + M_j + M_{ij} + M_k$   $M_k \text{ est inclus dans } M_{ij} \text{ donc } M_k + M_{ij} = M_{ij}$   $\text{donc } M_i + M_j + M_k = M_i + M_j + M_{ij}$   $= M_i + M_j$

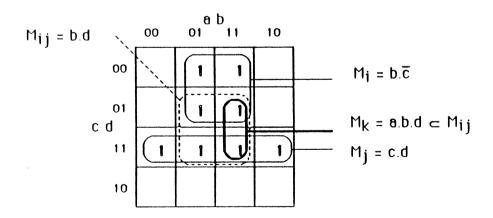

# Règle 14 : Règle d'adjacence par consensus.

Si il existe un consensus  $M_{ij}$  entre deux monômes  $M_i$  et  $M_j$  de EM, et si il existe  $M_k$  dans EM tel que  $M_{ij}$  et  $M_k$  ( $M_{ij}$  +  $M_k$  =  $M_{ijk}$ ) sont adjacents, alors  $M_k$  peut être remplacé dans EM par  $M_{iik}$  (figure 34).

Figure 34 : Règle d'adjacence par consensus.

### Remarque:

Par définition du consensus,  $M_{ij}$  est inclus dans  $M_i + M_j$  donc  $M_i + M_j + M_k = M_i + M_j + M_{ij} + M_k$   $M_k \text{ et } M_{ij} \text{ sont adjacents, donc } M_k + M_{ij} = M_{ijk}$  donc  $M_i + M_j + M_k = M_i + M_j + M_{ijk}$

# 1.3.2.3 Propriété invariante dans l'application des règles.

Les règles 6 à 14 ont été établies dans le but d'effectuer la minimisation logique d'une fonction Booléenne complètement spécifiée d'une façon efficace en temps de calcul consommé et en occupation de place mémoire. La solution finale est obtenue dans EM lorsqu'il n'y a plus aucune règle applicable. Tout au long du processus de minimisation, l'assertion suivante est invariante :

- Chaque fois qu'une règle de transformation est appliquée, la taille du problème diminue, soit par l'exclusion d'un monôme de l'ensemble EM, soit par l'exclusion d'une variable dans un monôme de EM.

On peut donc affirmer que les place mémoire nécessaire à la réduction d'une expression est bornée par le nombre de monômes et par le nombre de variables dans les monômes du polynôme initial qui caractérise l'expression. Cette propriété nous permet d'installer le jeu de règles et le système qui contrôle leur application sur des ordinateurs dont la capacité mémoire est restreinte (micro ordinateurs).

# 1.3.2.4. Contrôle de l'application des règles:

Le coût de l'évaluation des parties gauches des règles n'est pas le même pour toutes les règles. Il est évident que les règles de consensus (12 à 14) sont beaucoup plus coûteuses à reconnaître que les règles primaires (6 à 11). Pour cette raison, le lecteur peut remarquer que les règles primaires d'adjacence (9) et d'expansion locale (11) sont des cas particuliers des règles de consensus ; nous les avons volontairement différenciées afin d'accroître l'efficacité du système. Ainsi, dans l'application des règles, les règles primaires sont prioritaires sur les règles secondaires car leur rapport coût de l'évaluation sur gain apporté par la transformation est meilleur.

L'efficacité de la minimisation peut encore être améliorée par l'introduction d'une heuristique dans le contrôle de l'application des règles. Cette heuristique consiste à faire en sorte que les premières règles appliquées entraînent les plus gros gains, c'est à dire des exclusions de monômes par adjacence ou bien par inclusion.

### I.3.2.5. Exemple d'application de règles:

Nous donnons ici une manière possible de résoudre le problème de la preuve de tautologie pour la fonction de la figure 30. L'ordre d'application des règles dans cet exemple est tout à fait arbitraire et indifférent, le but recherché étant d'aboutir à l'application de la règle 6 (a  $+ \neg a \rightarrow 1$ ).

$$f = \neg a. \neg b. \neg c + \neg a.b. \neg d + a.b.c + a. \neg b.d + a. \neg c. \neg d + b. \neg c.d + \neg a.c.d + \neg b.c. \neg d$$

$$f = \sum_{(i=1 \ \grave{a} \ 8)} M_i \quad \text{(figure 35)}$$

Figure 35: forme initiale.

- (M<sub>1</sub>, M<sub>2</sub>)  $\rightarrow$  règle 14 : consensus (M<sub>1</sub>, M<sub>2</sub>)=¬a.¬c.¬d adjacent à M<sub>5</sub>  $M_5 \text{ expansé en } \neg \text{c.} \neg \text{d}$

- $(M_1, M_6) \rightarrow \text{règle 14}: \text{consensus } (M_1, M_6) = \neg a. \neg c.d \text{ adjacent à } M_7$   $M_7 \text{ est expansé en } \neg a.d$

- $(M_2,\,M_3) \to \text{règle 14}: \text{consensus } (M_2,\,M_3) = \text{b.c.} \neg \text{d} \text{ adjacent à } M_8$   $M_8 \text{ est expansé en c.} \neg \text{d}$

- $(M_3,\,M_6)$   $\rightarrow$  règle 14 : consensus  $(M_3,\,M_6)$ =a.b.d adjacent à  $M_4$   $M_4 \text{ est expansé en a.d} \qquad \qquad \text{(figure 36)}$

Figure 36 : forme obtenue après 4 transformations.

$(M_2, M_7) \rightarrow \text{règle 11}: (expansion locale) M_2 est expansé en a.d.$

$(M_4,\,M_5) \rightarrow \text{règle 13}: \text{consensus } (M_4,\,M_5) = \text{a.c absorbe } M_3 = \text{a.b.c}$

$(M_5, M_7) \rightarrow \text{règle 13}: \text{consensus } (M_5, M_7) = \neg a. \neg c \text{ absorbe } M_1 = \neg a. \neg b. \neg c$

$(M_4,\,M_7) \rightarrow \text{règle 9}: M_4 \text{ adjacent à } M_7,\,\,M_4 \text{ est expansé en d, } M_7 \text{ est supprimé.}$

$(M_4, M_6) \rightarrow \text{règle 10}: M_6 \text{ inclus dans } M_4, M_6 \text{ est supprimé}.$

$(\mathsf{M}_5,\,\mathsf{M}_8)\quad \rightarrow \quad \text{ règle 9 : } \mathsf{M}_5 \text{ adjacent à } \mathsf{M}_8$

$M_5$  est expansé en  $\neg d$ ,  $M_8$  est supprimé. (figure 37)

Figure 37 : forme obtenue après 6 transformations.

$(M_4,\,M_5) \quad \rightarrow \quad \text{ règle 6 : } M_4 + M_5 = 1\text{, f est une tautologie}.$

### 1.3.3. La minimisation locale des fonctions partiellement spécifiées.

Les règles qui vont suivre sont des règles additionnelles aux règles 6 à 14, qui permettent la minimisation locale des fonctions phi-booléennes. Elles s'appliquent sur les monômes des couvertures à 1 et à phi de la fonction, mais ne modifient que la couverture à 1.

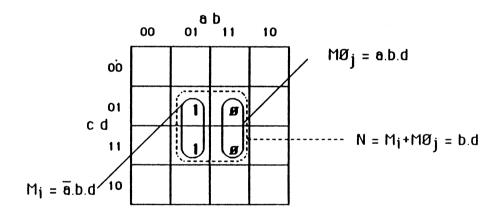

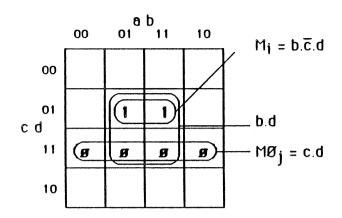

Soient EM =  $(M_1, M_2,...,M_p)$  un ensemble de monômes caractérisant la couverture à 1 de la fonction f à minimiser, et EMØ =  $(MØ_1,MØ_2,...,MØ_q)$  un ensemble de monômes caractérisant la couverture indifférente de f.

### Règle 15 : règle d'adjacence phi-booléenne.

Si il existe une variable x et un monôme n tels que  $M_j=x.N$  et  $M\varnothing_j=\neg x.N$ , alors  $M_i$  est adjacent à  $M\varnothing_j$  et est remplacé dans EM par N (figure 38).

Le gain associé à l'application de cette règle est de 1 variable dans le monôme Mi.

Figure 38 : règle d'adjacence phi-booléenne.

### Règle 16 : règle d'expansion locale phi-booléenne.

si il existe une variable x et deux monômes N et P tels que  $M_i = \neg x.N.P$  et  $M\emptyset_j = x.P$ , alors la variable  $\neg x$  peut être supprimée dans  $M_i$  ( $\neg a.b.c + a.c = b.c + a.c$ ). (figure 39). Le gain associé à l'application de cette règle est de 1 variable dans le monôme  $M_i$ .

Figure 39 : règle d'expansion locale phi-booléenne.

Règle 17 : règle d'assignation à une tautologie.

Si  $M_i = x$  et si  $M \mathcal{O}_j = \neg x$ , alors f peut être assignée à une tautologie (figure 40). L'application de cette règle stoppe le processus de minimisation phi-booléenne.

Figure 40 : Règle d'assignation à une tautologie.

### Règle 18 : règle d'adjacence phi-booléenne par consensus.

Si il existe un consensus  $M\varnothing_{ij}$  entre  $M\varnothing_i$  et  $M\varnothing_j$ , et si il existe  $M_k$  dans EM tel que  $M_k$  et  $M\varnothing_{ij}$  sont adjacents ( $M\varnothing_{ij}+M_k=M_{ijk}$ ), alors  $M_k$  est remplacé dans EM par  $M_{ijk}$ . Le gain associé à l'application de cette règle est de 1 variable dans  $M_k$ .

Figure 41 : règle phi-booléenne d'adjacence par consensus.

### Remarques:

- Losqu'aucune des règles 6 à 18 n'est applicable sur les ensembles EM et EMØ d'une fonction phi-booléenne, la solution minimisée est dans EM et EMØ n'est pas modifié.

- Les règles phi-booléennes 15 à 18 respectent l'assertion définie en II.3.2.3.

- Les règles phi-booléennes 15 à 18 sont des règles complémentaires des règles 6 à 14, et doivent leur être associées pour être opérationnelles. En effet, les transformations provoquées par l'application des règles phi-booléennes peuvent rendre possible de nouvelles simplifications dans l'ensemble EM par les règles 6 à 14.

**\***

### 1.3.4. Un système de règles pour la minimisation globale.

La minimisation globale d'un système combinatoire (minimisation multi-fonction) est basée sur une observation simultanée de toutes les fonctions à implémenter. Le but recherché est de couvrir l'ensemble des fonctions avec un nombre minimal de monômes.

Classiquement, on procède par la génération de tous les monômes premiers pour chacune des fonctions, et pour toutes les combinaisons possibles de produits de fonctions. On sélectionne ensuite parmi les monômes premiers générés, une couverture première irrédondante, tout comme pour la minimisation locale. Pour minimiser un ensemble de p fonctions, il faut calculer les monômes premiers de :

$$\sum_{i=1}^{p} C_{p}^{i}$$

fonctions.

La génération des monômes premiers qui croît de façon exponentielle (3<sup>n</sup>/n) avec le nombre de variables, croît aussi de façon exponentielle avec le nombre de fonctions, car :

$$\sum_{i=1}^{p} C_{p}^{i} = 2^{p} - 1$$

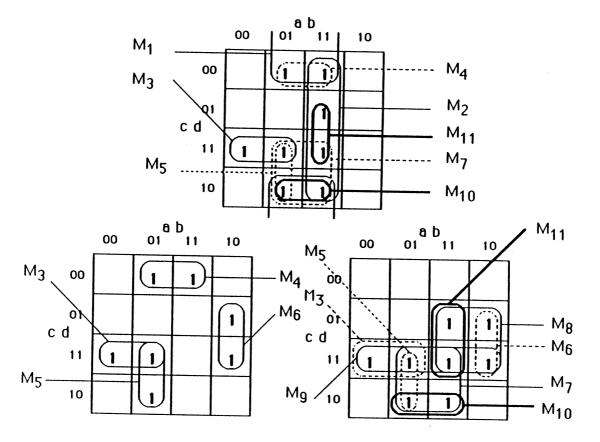

Ainsi, ces méthodes ne peuvent pas traiter des problèmes dont la taille dépasse une huitaine de fonctions [ARE78]. Notre objectif étant de minimiser des systèmes combinatoires de 50 variables et de plus de 100 fonctions, nous avons défini un système de règles qui constitue une approche efficace pour la minimisation globale, en garantissant l'obtention d'une solution sans redondance mais pas nécessairement optimale au sens du nombre total de monômes [HAN86].

Les règles pour la minimisation globale d'un ensemble de fonctions Booléennes ont été définies de façon à engendrer une solution globalement optimisée à partir des formes localement minimales de chacune des fonctions du système. Cette manière de procéder est particulièrement efficace lorsque l'on peut faire apparaître dans plusieurs fonctions des mêmes sous expressions (polynômes) localement optimisées. Dans le cas contraire, on est amené à expanser l'ensemble EM des monômes obtenus par

minimisation locale des fonctions, en lui ajoutant des monômes générés par intersections généralisées, rendant ainsi plus complexe et coûteuse la sélection d'une couverture minimale irrédondante. Ainsi, le système de règles que nous proposons est peu adapté au traitement des fonctions dont la forme globalement optimale est presque canonique (monômes de petite taille et presque tous disjoints) et dont les formes localement minimales ne le sont pas (monômes de grosse taille et peu disjoints). En effet, dans ce type de problème, les monômes intéressants pour la forme globalement optimale n'apparaissent pas dans les formes localement minimales, et doivent être retrouvés par des intersections généralisées.

L'intérêt d'une approche à base de règles pour la minimisation Booléenne est que l'on peut définir des jeux de règles différents pour les divers types de systèmes combinatoires à minimiser. Il serait tout à fait envisageable de définir un jeu de règles adapté à la minimisation des systèmes dont la forme optimale est presque canonique. Il suffirait alors d'analyser le système combinatoire initial pour déterminer le jeu de règles le plus adapté à sa minimisation.

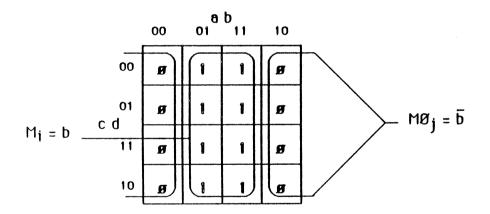

Soit un système combinatoire  $\mathbf{F}=(f_1,f_2,...,f_{\mathsf{m}})$  à minimiser globalement. On note  $\mathbf{C1}(f_{\mathsf{k}})$  l'expression de la couverture à "1" de la fonction  $f_{\mathsf{k}}$  et  $\mathbf{CØ}(f_{\mathsf{k}})$  celle de sa couverture indifférente. Contrairement à la minimisation locale, les règles proposées ne font plus la distinction entre fonctions complètes et fonctions incomplètes.

Soit  $EM=(M_1, M_2, ..., M_p)$  l'ensemble initial des p monômes obtenus en minimisant localement les expressions des couvertures à "1" et à "ø" de chacune des fonctions de F.

Soit  $EA=(A_1,A_2,...,A_p)$  l'ensemble associé à EM des apparitions d'un monôme dans F, définies par :

- $-A_i = (A1_i, AO_i)$

- ${\rm A1_i}$  est l'ensemble des fonctions  $f_{\bf k}$  de F telles que  ${\rm M_i}$  est inclus dans  ${\rm C1}(f_{\bf k})$ ,

- $\mathsf{A} \mathcal{O}_\mathsf{i}$  est l'ensemble des fonctions  $f_\mathsf{k}$  de F telles que  $\mathsf{M}_\mathsf{i}$  est inclus dans

$$C1(f_k) \cup CO(f_k)$$

.

### I.3.4.1. Règles d'expansion globale:

Les règles d'expansion globale sont les règles génératrices des ensembles  $A1_i$  et  $A\varnothing_i$  pour chaque monôme  $M_i$  de EM. L'application de ces règles à un monôme  $M_i$  permet de déterminer l'ensemble des fonctions  $f_k$  de F dans lesquelles  $M_i$  peut apparaître, soit en tant que contribution à la couverture à "1" ( $M_i$  inclus dans  $C1(f_k)$ ), soit en tant que contribution à l'union des couvertures à "1" et à "ø" ( $M_i$  inclus dans  $C1(f_k) \cup C\varnothing(f_k)$ ).

### Règle 19 : règle d'expansion globale.

Si il existe  $M_i$  dans EM et  $f_k$  dans F tels que

$M_i$  est inclus dans  $C1(f_k)$ ,

alors  $f_{\mathbf{k}}$  est rajoutée dans  $A1_{\mathbf{i}}$ .

Règle 20 : règle d'expansion globale phi-booléenne.

${f SI}$  il existe  ${f M_i}$  dans  ${f EM}$  et  $f_{f k}$  dans  ${f F}$  tels que

$M_i$  n'est pas inclus dans  $C1(f_k)$ ,

et  $M_i$  est inclus dans  $C1(f_k) \cup C\emptyset(f_k)$ ,

alors  $f_{\mathsf{k}}$  est rajoutée dans  $\mathsf{A} \varnothing_{\mathsf{i}}$ .

#### Exemple:

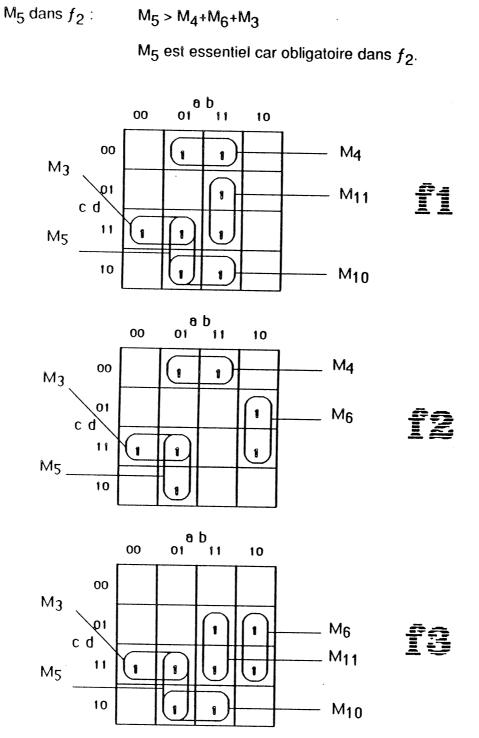

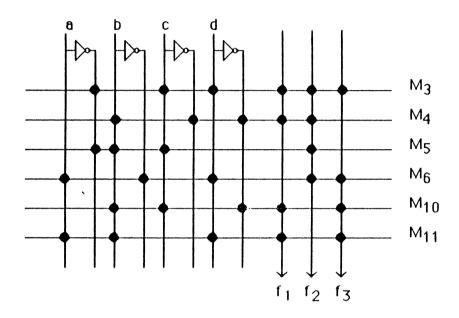

Soit  $F=(f_1, f_2, f_3)$  un ensemble de trois fonctions des variables a, b, c et d.

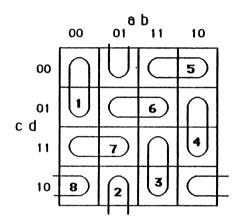

Les formes localement minimales obtenues par applications des règles de minimisation locale sont représentées en figure 42.

C1

$$(f_1) = b.\neg d + a.b + \neg a.c.d$$

CØ  $(f_1) = 0$

C1

$$(f_2) = b.\neg c.\neg d + \neg a.b.c + a.\neg b.d + \neg a.c.d$$

$C\emptyset (f_2) = 0$

C1

$$(f_3) = b.c + a.d + c.d$$

$C\emptyset (f_3) = 0$

Figure 42: Formes localement minimales de  $f_1$ ,  $f_2$ ,  $f_3$ .

L' ensemble initial de monômes EM est donc :

$\mathsf{EM} = (\mathsf{b}.\neg\mathsf{d},\,\mathsf{a}.\mathsf{b},\,\neg\mathsf{a}.\mathsf{c}.\mathsf{d},\,\mathsf{b}.\neg\mathsf{c}.\neg\mathsf{d},\,\neg\mathsf{a}.\mathsf{b}.\mathsf{c},\,\mathsf{a}.\neg\mathsf{b}.\mathsf{d},\,\mathsf{b}.\mathsf{c},\,\mathsf{a}.\mathsf{d},\,\mathsf{c}.\mathsf{d})$

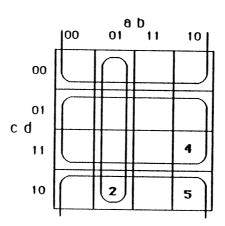

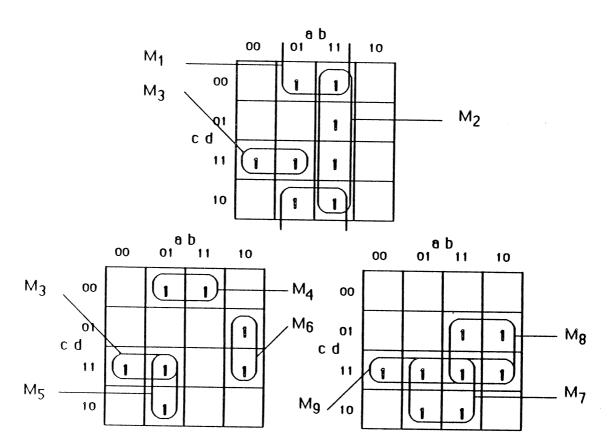

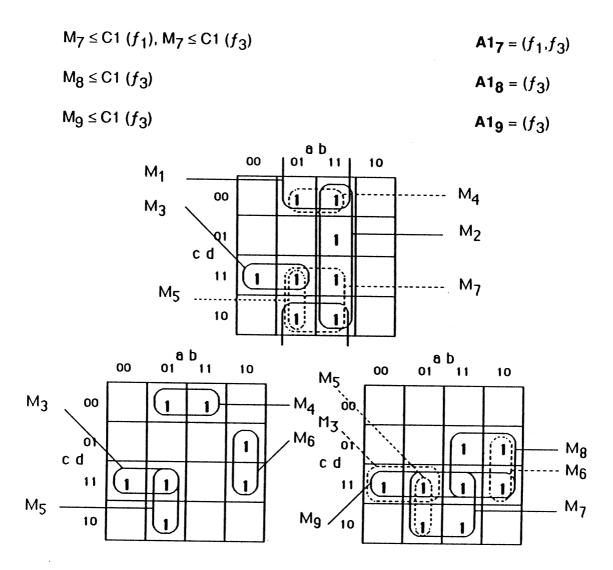

L'application des règles d'expansion globale va constituer l'ensemble EA de la façon suivante (le symbole ≤ représente l'inclusion) :

| $M_1 \leq C1 \; (f_1)$                                       | $A1_1 = (f_1)$           |

|--------------------------------------------------------------|--------------------------|

| $M_2 \leq C1 \; (f_1)$                                       | $A1_2 = (f_1)$           |

| $M_3 \le C1 \ (f_1), M_3 \le C1 \ (f_2), M_3 \le C1 \ (f_3)$ | $A1_3 = (f_1, f_2, f_3)$ |

| $M_4 \le C1 (f_1), M_4 \le C1 (f_2)$                         | $A1_4 = (f_1, f_2)$      |

| $M_5 \le C1 \ (f_1), M_5 \le C1 \ (f_2), M_5 \le C1 \ (f_3)$ | $A1_5 = (f_1, f_2, f_3)$ |

| $M_6 \le C1 \ (f_2), M_6 \le C1 \ (f_3)$                     | $A1_6 = (f_2, f_3)$      |

Figure 43 : formes globalement expansées de  $f_1, f_2, f_3$

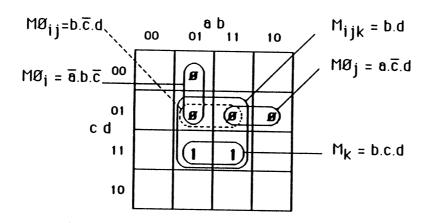

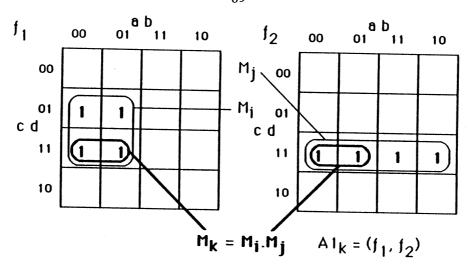

# I.3.4.2. Règle d'intersection généralisée:

La règle d'intersections généralisées est une règle de production dont le rôle est d'engendrer de nouveaux monômes susceptibles d'être plus intéressants (monômes pouvant apparaître dans un plus grand nombre de fonctions) dans la synthèse que ceux contenus initialement dans l'ensemble EM. Cette règle est expansive dans le sens où elle est la seule règle dont l'application fait croître la taille de l'ensemble EM, rendant ainsi l'extraction d'une couverture minimale plus complexe. De ce fait, elle doit être guidée par une heuristique de manière à limiter l'expansion de EM. La règle

d'intersections généralisées s'appuie sur la propriété suivante :

### \* Propriété :

Soit  $M_j$  et  $M_j$  deux monômes de EM, tels que :  $M_j.M_j \neq 0$ .

Si on note  $M_k$  le produit de  $M_i$  par  $M_j$ , alors

(figure 44)

#### Preuve:

Soit

$$f_k \in A1_i \cup A1_j$$

on a:  $M_i \leq C1$  ( $f_k$ ) et  $M_j \leq C1$  ( $f_k$ ).

donc  $M_i.M_j \leq C1$  ( $f_k$ )

donc  $f_k \in A1_k$ .

Soit  $f_k \in A0_i \cup A0_j$

on a:  $M_i \leq C0$  ( $f_k$ ) et  $M_j \leq C0$  ( $f_k$ ).

donc  $M_i.M_j \leq C0$  ( $f_k$ )

# Règle 21 : règle d'intersections généralisées.

Sill existe

$$M_k = \prod_{M_i \in P (EM)} M_i \neq 0$$

alors  $A1_k = \bigcup_{M_i \in P (EM)} A1_i$  et  $A\emptyset_k = \bigcup_{M_i \in P (EM)} A\emptyset_i$

$M_i \in P (EM)$

et après expansion des ensembles  $\mathbf{A1_k}$  et  $\mathbf{AO_k}$  par applications des règles 19 et 20.

$\mathbf{M_k}$  peut être ajouté à  $\mathbf{EM}$ .

donc  $f_k \in AO_k$ .

et  $A_k = (A1_k, A\emptyset_k)$  peut être ajouté à EA.

Figure 44 : Illustration de la propriété d'intersection

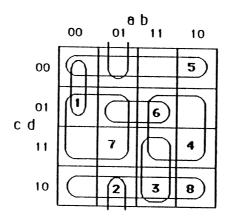

Dans notre exemple (figures 42 et 43), la règle d'intersections généralisées va engendrer les monômes suivants :

$M_{10} = M_1.M_7$   $M_{11} = M_2.M_8$   $A1_{10} = (f_1, f_3)$   $A1_{11} = (f_1, f_3)$

Figure 45 : Forme de F après intersections généralisées.

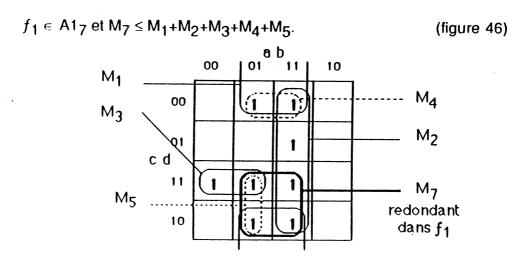

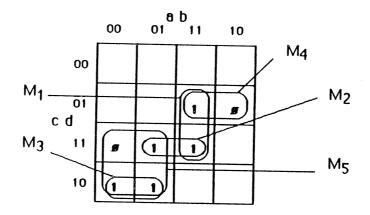

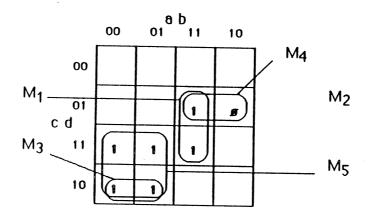

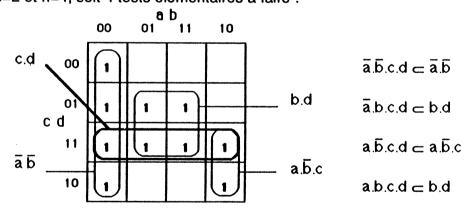

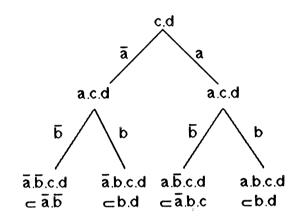

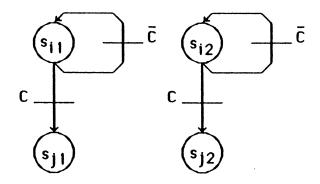

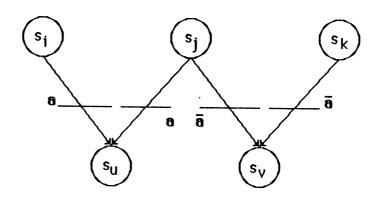

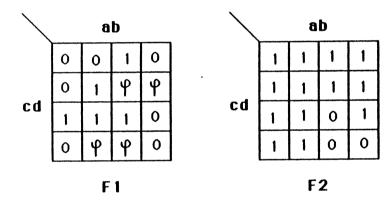

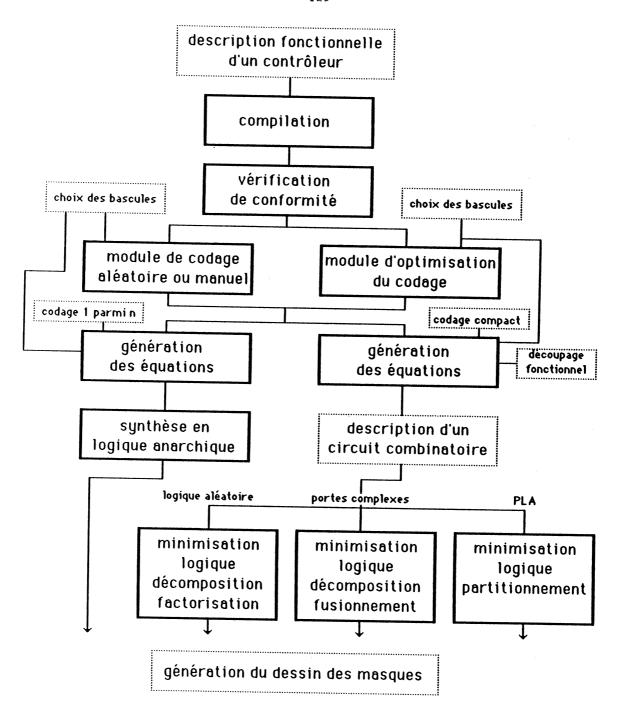

### 1.3.4.3. Règles d'élimination de la redondance :