# PAOLA: un système d'optimisation topologique de P.L.A

Tomas Perez Segovia

### ▶ To cite this version:

Tomas Perez Segovia. PAOLA: un système d'optimisation topologique de P.L.A. Modélisation et simulation. Institut National Polytechnique de Grenoble - INPG, 1985. Français. NNT: . tel-00316330

# HAL Id: tel-00316330 https://theses.hal.science/tel-00316330

Submitted on 3 Sep 2008

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

présentée à

# l'Institut National Polytechnique de Grenoble

pour obtenir le grade de DOCTEUR DE 3ème CYCLE «Informatique»

par

# PEREZ SEGOVIA Tomás

000

PAOLA: UN SYSTEME D'OPTIMISATION TOPOLOGIQUE DE P.L.A.

**OOO**

Thèse soutenue le 25 octobre 1985 devant la commission d'examen.

G. MAZARÉ Président

F. ANCEAU

J.L. LARDY Examinateurs

G. NOGUEZ

|  | y |  | <b>:</b> |   |

|--|---|--|----------|---|

|  |   |  |          |   |

|  |   |  |          |   |

|  |   |  |          |   |

|  |   |  |          | ; |

|  |   |  |          |   |

|  |   |  |          |   |

|  |   |  |          |   |

|  |   |  |          |   |

|  |   |  |          |   |

|  |   |  |          |   |

# INSTITUT NATIONAL POLYTECHNIQUE DE GRENOBLE

### Année universitaire 1982-1983

Président de l'Université : D. BLOCH

Vice-Président : René CARRE

Hervé CHERADAME Marcel IVANES

## PROFESSEURS DES UNIVERSITES:

| ANCEAU François         | E.N.S.I.M.A.G. |

|-------------------------|----------------|

| BARRAUD Alain           | E.N.S.I.E.G.   |

| BAUDELET Bernard        | E.N.S.I.E.G.   |

| BESSON Jean             | E.N.S.E.E.G.   |

| BLIMAN Samuel           | E.N.S.E.R.G.   |

| BLOCH Daniel            | E.N.S.I.E.G.   |

| BOIS Philippe           | E.N.S.H.G.     |

| BONNETAIN Lucien        | E.N.S.E.E.G.   |

| BONNIER Etienne         | E.N.S.E.E.G.   |

| BOUVARD Maurice         | E.N.S.H.G.     |

| BRISSONNEAU Pierre      | E.N.S.I.E.G.   |

| BUYLE BODIN Maurice     | E.N.S.E.R.G.   |

| CAVAIGNAC Jean-François | E.N.S.I.E.G.   |

| CHARTIER Germain        | E.N.S.I.E.G.   |

| CHENEVIER Pierre        | E.N.S.E.R.G.   |

| CHERADAME Hervé         | U.E.R.M.C.P.P. |

| CHERUY Arlette          | E.N.S.I.E.G.   |

| CHIAVERINA Jean         | U.E.R.M.C.P.P. |

| COHEN Joseph            | E.N.S.E.R.G.   |

| COUMES André            | E.N.S.E.R.G.   |

| DURAND Francis          | E.N.S.E.E.G.   |

| DURAND Jean-Louis       | E.N.S.I.E.G.   |

| FELICI Noël             | E.N.S.I.E.G.   |

| FOULARD Claude          | E.N.S.I.E.G.   |

| GENTIL Pierre           | E.N.S.E.R.G.   |

| GUERIN Bernard          | E.N.S.E.R.G.   |

| GUYOT Pierre            | E.N.S.E.E.G.   |

| IVANES Marcel           | E.N.S.I.E.G.   |

| JAUSSAUD Pierre         | E.N.S.I.E.G.   |

| JOUBERT Jean-Claude     | E.N.S.I.E.G.   |

| JOURDAIN Geneviève      | E.N.S.I.E.G.   |

| LACOUME Jean-Louis      | E.N.S.I.E.G.   |

| LATOMBE Jean-Claude     | E.N.S.I.M.A.G. |

E.N.S.H.G. **LESSIEUR Marcel** E.N.S.H.G. **LESPINARD** Georges E.N.S.I.E.G. LONGEQUEUE Jean-Pierre E.N.S.I.M.A.G. **MAZARE Guy** E.N.S.H.G. **MOREAU René** E.N.S.I.E.G. **MORET Roger** E.N.S.I.M.A.G. **MOSSIERE Jacques** E.N.S.E.E.G. **PARIAUD Jean-Charles** E.N.S.I.E.G. **PAUTHENET René** PERRET René E.N.S.I.E.G. E.N.S.I.E.G. **PERRET Robert** E.N.S.H.G. PIAU Jean-Michel **POLOUJADOFF Michel** E.N.S.I.E.G. E.N.S.E.R.G. **POUPOT Christian** E.N.S.E.E.G. RAMEAU Jean-Jacques U.E.R.M.C.P.P. **RENAUD Maurice** U.E.R.M.C.P.P. **ROBERT André ROBERT François** E.N.S.I.M.A.G. E.N.S.I.E.G. **SABONNADIERE** Jean-Claude E.N.S.I.M.A.G. **SAUCIER Gabrielle** E.N.S.I.E.G. **SCHLENKER Claire** E.N.S.I.E.G. **SCHLENKER Michel** E.N.S.E.R.G. **SERMET Pierre** U.E.R.M.C.P.P. **SILVY Jacques** E.N.S.E.E.G. **SOHM Jean-Claude** SOUQUET Jean-Louis E.N.S.E.E.G. E.N.S.I.M.A.G. **VEILLON Gérard ZADWORNY François** E.N.S.E.R.G.

#### **PROFESSEURS ASSOCIES**

BASTIN Georges E.N.S.H.G.

BERRIL John E.N.S.H.G.

CARREAU Pierre E.N.S.H.G.

GANDINI Alessandro U.E.R.M.C.P.P.

HAYASHI Hirashi E.N.S.I.E.G.

# PROFESSEURS UNIVERSITE DES SCIENCES SOCIALES (Grenoble II)

BOLLIET Louis Chatelin Françoise

### PROFESSEURS E.N.S. Mines de Saint-Etienne

RIEU Jean SOUSTELLE Michel

#### CHERCHEURS DU C.N.R.S.

FRUC'IART Robert VACHAUD Georges

Directeur de Recherche Directeur de Recherche

.../...

**ALLIBERT Michel** Maître de Recherche ANSARA Ibrahim Maître de Recherche **ARMAND Michel** Maître Recherche BINDER Gilbert **CARRE** René Maître Recherche de **DAVID** René Maître de Recherche **DEPORTES Jacques DRIOLE Jean** Maître de Recherche **GIGNOUX** Damien **GIVORD Dominique GUELIN Pierre HOPFINGER Emil** Maître de Recherche Maître de Recherche JOUD Jean-Charles **KAMARINOS Georges** Maître de Recherche **KLEITZ Michel** Maître de Recherche LANDAU loan-Dore Maître de Recherche LASJAUNIAS J.C. MERMET Jean Maître de Recherche **MUNIER Jacques** Maître de Recherche **PIAU Monique PORTESEIL Jean-Louis THOLENCE Jean-Louis VERDILLON André**

# CHERCHEURS du MINISTERE de la RECHERCHE et de la TECHNOLO-GIRE (Directeurs et Maîtres de Recherches, ENS Mines de St. Etienne)

| LESBATS Pierre    | Directe | ır de | Recherche |

|-------------------|---------|-------|-----------|

| BISCONDI Michel   | Maître  | de    | Recherche |

| KOBYLANSKI André  | Maître  | de    | Recherche |

| LE COZE Jean      | Maître  | de    | Recherche |

| LALAUZE René      | Maître  | de    | Recherche |

| LANCELOT Francis  | Maître  | de    | Recherche |

| THEVENOT François | Maître  | de    | Recherche |

| TRAN MINH Canh    | Maître  | de    | Recherche |

# PERSONNALITES HABILITEES à DIRIGER des TRAVAUX de RE-CHERCHE (Décision du Conseil Scientifique)

| ALLIBERT Colette      | E.N.S.E.E.G. |

|-----------------------|--------------|

| BERNARD Claude        | E.N.S.E.E.G. |

| BONNET Rolland        | E.N.S.E.E.G. |

| CAILLET Marcel        | E.N.S.E.E.G. |

| CHATILLON Catherine   | E.N.S.E.E.G. |

| CHATILLON Christian   | E.N.S.E.E.G. |

| COULON Michel         | E.N.S.E.E.G. |

| DIARD Jean-Paul       | E.N.S.E.E.G. |

| EUSTAPOPOULOS Nicolas | E.N.S.E.E.G. |

| FOSTER Panayotis      | E.N.S.E.E.G. |

|                       |              |

.../...

E.N.S.E.E.G. **GALERIE Alain** E.N.S.E.E.G. HAMMOU Abdelkader E.N.S.E.E.G. (CENG) **MALMEJAC** Yves E.N.S.E.E.G. MARTIN GARIN Régina E.N.S.E.E.G. **NGUYEN TRUONG Bernadette** E.N.S.E.E.G. **RAVAINE Denis** SAINFORT E.N.S.E.E.G. (CENG) E.N.S.E.E.G. **SARRAZIN** Pierre E.N.S.E.E.G. SIMON Jean-Paul **TOUZAIN** Philippe E.N.S.E.E.G. E.N.S.E.E.G. (Laboratoire des **URBAIN** Georges ultra-réfractaires ODEILLON) E.N.S. Mines Saint Etienne **GUILHOT Bernard** E.N.S. Mines Saint Etienne THOMAS Gérard E.N.S. Mines Saint Etienne **DRIVER Julien** E.N.S.E.R.G. **BARIBAUD Michel** E.N.S.E.R.G. **BOREL Joseph CHOVET Alain** E.N.S.E.R.G. E.N.S.E.R.G. **CHEHIKIAN Alain** E.N.S.E.R.G. **DOLMAZON Jean-Marc** E.N.S.E.R.G. **HERAULT Jeanny** E.N.S.E.R.G. **MONLLOR** Christian E.N.S.I.E.G. **BORNARD Guy** E.N.S.I.E.G. **DESCHIZEAU Pierre GLANGEAUD** François E.N.S.I.E.G. E.N.S.I.E.G. **KOFMAN Walter LEJEUNE Gérard** E.N.S.I.E.G. E.N.S.I.E.G. MAZUER Jean E.N.S.I.E.G. **PERARD Jacques** E.N.S.I.E.G. **REINISCH Raymond ALEMANY Antoine** E.N.S.H.G. E.N.S.H.G. **BOIS Daniel** E.N.S.H.G. **DARVE Félix** E.N.S.H.G. MICHEL Jean-Marie E.N.S.H.G. **OBLED Charles ROWE Alain** E.N.S.H.G. E.N.S.H.G. **VAUCLIN Michel** E.N.S.H.G. **WACK Bernard BERT Didier** E.N.S.I.M.A.G. E.N.S.I.M.A.G. **CALMET Jacques** E.N.S.I.M.A.G. **COURTIN Jacques** E.N.S.I.M.A.G. **COURTOIS Bernard DELLA DORA Jean** E.N.S.I.M.A.G. E.N.S.I.M.A.G. **FONLUPT Jean** E.N.S.I.M.A.G. SIFAKIS Joseph U.E.R.M.C.P.P. **CHARUEL Robert CADET Jean** C.E.N.G. C.E.N.G. (LETI) **COEURE Philippe**

.../...

**DELHAYE Jean-Marc** C.E.N.G. (STT) **DUPUY Michel** C.E.N.G. (LETI) JOUVE Hubert C.E.N.G. (LETI) NICOLAU Yvan C.E.N.G. (LETI) NIFENECKER Hervé C.E.N.G. PERROUD Paul C.E.N.G. **PEUZIN Jean-Claude** C.E.N.G. (LETI) **TAIEB Maurice** C.E.N.G. **VINCENDON Marc** C.E.N.G.

## **LABORATOIRES EXTERIEURS**

DEMOULIN Eric C.N.E.T.

DEVINE C.N.E.T. (R.A.B.)

GERBER Roland C.N.E.T.

MERCKEL Gérard C.N.E.T.

PAULEAU Yves C.N.E.T.

GAUBERT C. I.N.S.A. Lyon

«Caminante, son tus huellas el camino, y nada más; caminante, no hay camino, se hace camino al andar.»

Antonio Machado

a Tatiana a Carminda a Marta a Rodolfo

|   |   |  |  | • |   |  |

|---|---|--|--|---|---|--|

|   |   |  |  |   |   |  |

|   |   |  |  |   |   |  |

|   | • |  |  |   |   |  |

|   |   |  |  |   |   |  |

|   |   |  |  |   |   |  |

|   |   |  |  |   |   |  |

|   |   |  |  |   |   |  |

| • |   |  |  | · |   |  |

| • |   |  |  |   |   |  |

| • |   |  |  |   |   |  |

| • |   |  |  |   | • |  |

| • |   |  |  |   |   |  |

|   | • |  |  |   |   |  |

|   |   |  |  |   |   |  |

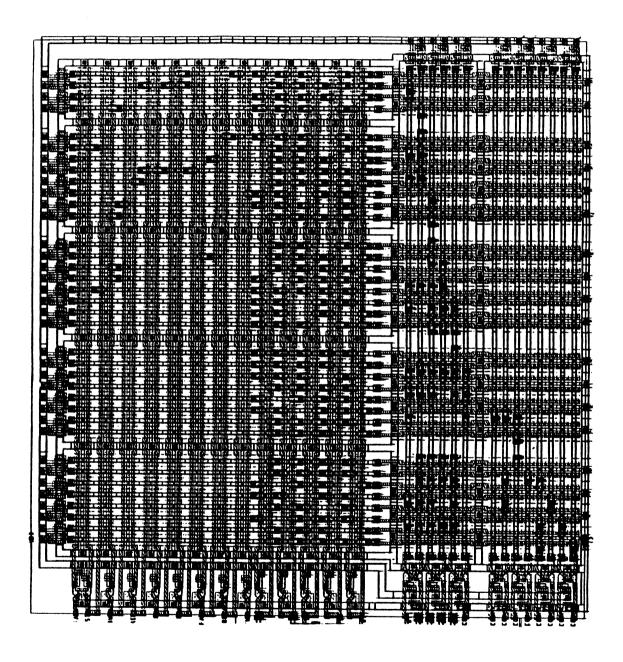

# RESUME

Lors de la conception des circuits intégrés VLSI, les Réseaux Logiques Programmables (P.L.A.) permettent le dessin automatique des masques à partir d'une description logique. La surface occupée par ces PLAs peut, dans certains cas, s'averer prohibitive; d'où l'intérêt des méthodes d'optimisation topologique de ceux-ci.

Après avoir défini les différentes représentations possibles des PLAs, nous présentons l'état de l'art en ce qui concerne l'optimisation topologique des PLAs.

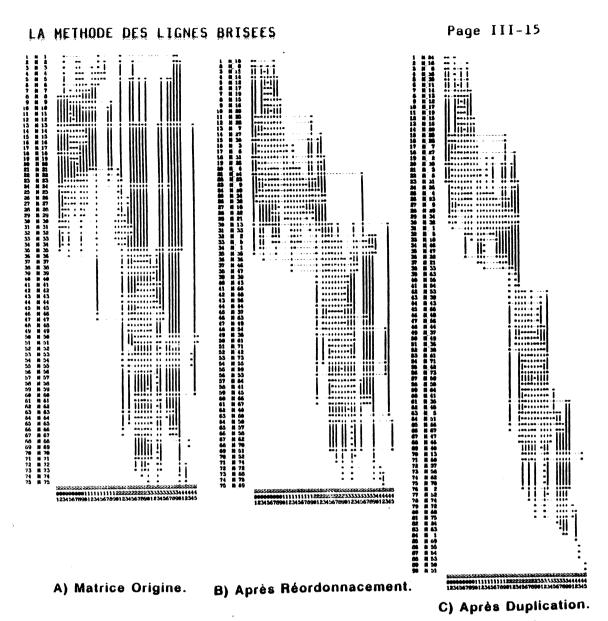

La méthode des "Lignes Brisées" est ensuite détaillée en insistant sur les heuristiques choisies ainsi que sur les intéractions qui existent entre l'étape d'optimisation et l'étape de tracé des connexions internes.

On termine par une présentation globale du sytème PAOLA d'optimisation topologique et dessin de PLAs.

# MOTS-CLES:

Programmable Logic Array, Conception Assistée par Ordinateur, Conception de Circuits Intégrés, V.L.S.I., Heuristiques, Optimisation Topologique.

#### RERCIEMENTS

Je voudrais exprimer toute ma reconaissance à :

- Monsieur **F. ANCEAU** professeur à l'I.N.P.G. qui a bien voulu m'acceuillir au sein de l'équipe de Recherche en Architecture des Ordinateurs et qui est à la base du projet PAOLA,

- Monsieur **G.MAZARE**, professeur E.S.I.M.A.G, qui m'a fait l'honneur de présider le jury de cette Thèse,

- Monsieur J.L. LARDY chef du département M.C.C au C.N.E.T. Grenoble pour l'aide qu'il m'a donné pendant la rédaction de ce mémoire, ainsi que pour avoir accepté de faire partie de ce jury,

- Monsieur G. NOGUEZ professeur à l'université PARIS VI pour avoir accepté de faire partie de ce jury,

- Monsieur S. CHUQUILLANQUI avec qui ce travail à été réalisé,

- Messieurs A. GUYOT et J. P. SCHOELLKOPF pour les nombreuses discussions que nous avons eu ensemble,

- toute l'équipe de Recherche en Architecture des Ordinateurs pour leur soutient pendant si longtemps,

- au CNET Grenoble qui à mis à ma disposition tous les moyens nécessaires à le rédaction de cette thèse,

- et enfin à Monsieur IGLESIAS, et avec lui toute l'équipe de reprographie de l'IMAG, pour son travail soigné et sa gentillesse.

|  | ) |  | , |  |

|--|---|--|---|--|

|  |   |  | • |  |

|  |   |  |   |  |

|  |   |  |   |  |

|  |   |  |   |  |

|  |   |  |   |  |

|  |   |  |   |  |

|  |   |  |   |  |

|  |   |  |   |  |

|  |   |  |   |  |

|  |   |  |   |  |

|  |   |  |   |  |

|  |   |  |   |  |

|  |   |  |   |  |

|  |   |  |   |  |

|  |   |  |   |  |

.

TABLE DES MATIERES

# TABLE DES MATIERES

# TABLE DES MATIERES

| CHAPITRE | E I                 | INTRODUCTION                                 |

|----------|---------------------|----------------------------------------------|

|          | I.A<br>I.A.1<br>I.B | LA CONCEPTION DES CIRCUITS INTEGRES          |

|          | I.B.1               | LES PLAS                                     |

|          | I.B.1.a             | Représentation Fonctionelle                  |

|          | I.B.1.b             | • • • • • • • • • • • • • • • • • • • •      |

|          | I.B.1.c             | Représentation Symbolique.                   |

|          | I.B.1.d             | Représentation Structurelle                  |

|          | I.B.1.e             | •                                            |

| CHAPITRE | 11                  | OPTIMISATION DES PLAS                        |

|          | II.A                | INTRODUCTION                                 |

|          | II.B                | MINIMISATION LOGIQUE                         |

|          | II.C                | OPTINISATION TOPOLOGIQUE                     |

|          | II.D                | LE PLA CLASSIQUE                             |

|          | II.E                | MODIFICATION DES CONNECTEURS                 |

|          | II.F                | PARTITIONNEMENT DES MATRICES                 |

|          | II.G                | PLACEMENT LATERAL DES CONNECTEURS            |

|          | II.H                | OPTIMISATION PAR TRIANGULARISATION 27        |

|          | II.I                | OPTIMISATION PAR LINEARISATION DE LA MATRICE |

|          |                     | OU                                           |

|          | II.J                | OU                                           |

|          | II.K                | OPTIMISATION EN LIGNES BRISEES               |

|          | II.L                | OPTIMISATION EN LIGNES BRISEES               |

| CHAPITRE | 111                 | LA METHODE DES LIGNES BRISEES                |

|          | III.A               | INTRODUCTION                                 |

|          | III.B               | INTRODUCTION                                 |

|          | III.B.1             | Les Monômes                                  |

|          | III.B.2             | Couverture D'un Segment                      |

|          | III.B.3             |                                              |

|          | III.C               |                                              |

|          | III.D               | ORDONNACEMENT DES MONOMES                    |

|          | III.D.1             |                                              |

|          |                     | .a Nombre De Transistors Controlés (NBT) 52  |

|          |                     | b DELTA (Longueur De La Couverture Du        |

|          |                     | Monôme)                                      |

|          | 111.0 1             | c Distance Barycentre Moyenne (B-M).         |

|          |                     |                                              |

|          |                     |                                              |

|          |                     |                                              |

|          | 111.U.L             | .f Choix Par Taille De Trou 54               |

# TABLE DES MATIERES

| " III.D.    | l.g Choix Par Distance Bord-Trou Vertical       |

|-------------|-------------------------------------------------|

|             | Pondérée                                        |

| III.D.      |                                                 |

| III.D.      |                                                 |

| III.E       | COMPACTAGE DES MATRICES                         |

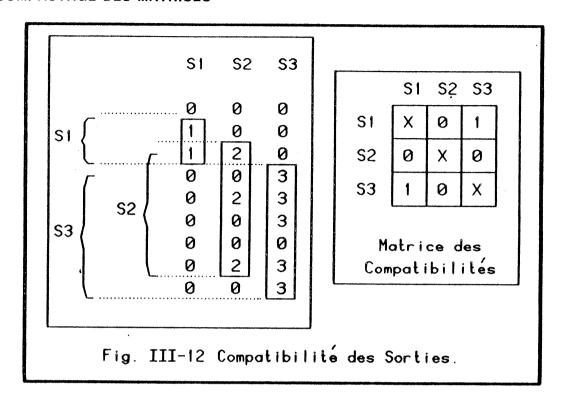

| III.E.      | 1 Regroupement Des Sorties 60                   |

| III.F       | TRAITEMENTS COMPLEMENTAIRES 61                  |

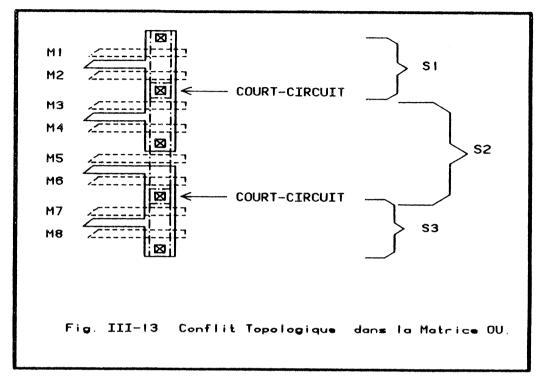

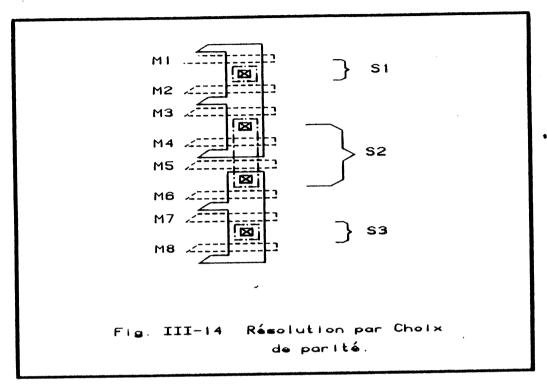

| III.F.      | 1 Conflits Topologiques Dans La Matrice OU 62   |

| III.F.      |                                                 |

| III.F.      | 3 Connecteurs En Haut Et En Bas 66              |

| III.F.      | 4 Problèmes Liés Au Tracé Des Connexions        |

|             | Internes                                        |

| III.G       | GENERATION DU DESSIN DES MASQUES ET TRACE       |

|             | INTERNE DES CONNEXIONS                          |

| III.H       | RESULTATS-CONCLUSION                            |

| CHAPITRE IV | PRESENTATION DU SYSTEME PAOLA                   |

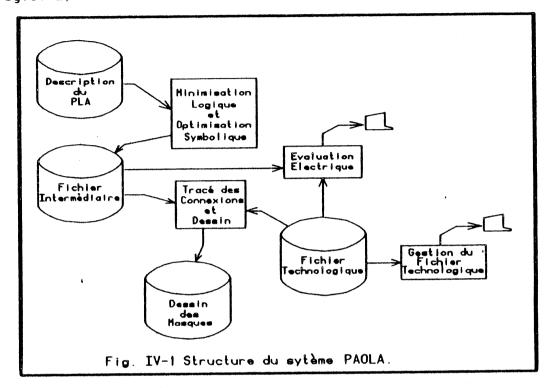

| IV.A        | DESCRIPTION GENERALE                            |

| IV.B        | MODULE D'OPTINISATION TOPOLOGIQUE 78            |

| IV.C        | MODULE D'EVALUATION ELECTRIQUE                  |

| IV.D        | MODULE DE TRACE DES CONNEXIONS ET DE DESSIN DES |

|             | MASQUES                                         |

| IV.E        | MODULE DE GESTION DU FICHIER TECHNOLOGIQUE . 80 |

| IV.F        | EXTENSIONS POUR D'AUTRES TECHNOLOGIES 80        |

| IV.G        | CONCLUSION                                      |

| 2.,,2       |                                                 |

| BIBLIOG     | RAPHIE                                          |

|             | REFERENCES RIBI TOCRAPHIQUES 85                 |

# CHAPITRE I INTRODUCTION

; •

# I.A LA CONCEPTION DES CIRCUITS INTEGRES

La réalisation des circuits intégrés comporte deux étapes bien distinctes : la conception et la fabrication.

La conception des circuits intégrés consiste à fournir un jeu de dessins des masques à partir de spécifications, qui peuvent être plus ou moins rigoureuses, decrivant la fonctionalité du circuit.

Ces dessins de masques décrivent entièrement le circuit. Ils servent à la création des masques, le circuit etant fabriqué à partir de ces masques.

L'introduction de l'automatisation (par le biais de l'informatique) dans la conception était consideré, il y quelques années comme un moyen d'accelerer celle-ci ainsi que d'augmenter sa fiabilité. Aujourd'hui cette informatisation est le seul moyen par lequel peuvent être concus des circuits comportant des centaines de milliers de transistors.

La complexité atteinte dans les nouveaux circuits intégrés à très grande echelle (VLSI) impose, pour leur conception, l'utilisation de méthodes strictes et rigoureuses pour pouvoir appréhender cette complexité, ainsi que l'utilisation d'outils de plus en plus puissants d'aide à la conception.

Ces méthodes de conception s'appuient sur la croissance exponentielle de la complexité d'un problème. Autrement dit il est plus facile de résoudre N problèmes simples qu'un seul problème dont la taille est N fois plus grande.

La première devise des concepteurs de circuits VLSI est DIVISER POUR REGNER.

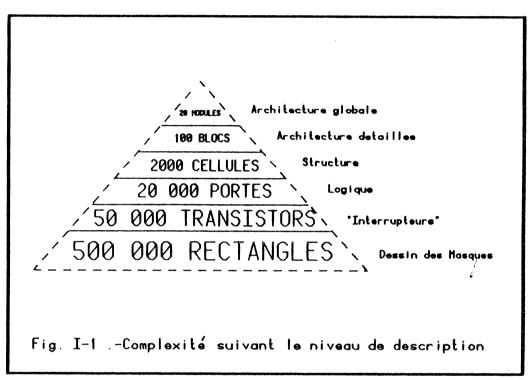

Par ailleurs, il est impossible d'appréhender ensemble tous les aspects d'un circuit VLSI. Il faut donc faire des abstractions, et pratiquement les niveaux sur lesquels les problèmes se traitent sont les suivants :

- le niveau fonctionnel

- le niveau architectural

- le niveau comportemental

- le niveau structurel

- le niveau logique

- le niveau «interrupteur» (pour les circuits MOS)

- le niveau électrique

#### - le niveau topologique

Leurs frontières, leur ordre ou même leur non recouvrement ne sont pas toujours très bien établis. Mais ce découpage permet de réduire la complexité des problèmes à manipuler (fig. I.1), et surtout de manipuler des aspects différents du même circuit sans les mélanger. Ainsi lorsqu'on spécifie l'architecture d'un circuit on se soucie peu des problémes électriques de celui-ci.

Ainsi la conception d'un circuit intégré est la transformation d'une description fonctionelle en une description du dessin des masques. Cette transformation se fait par etapes successives, et cette manière de procéder s'appelle la conception descendante ou conception hierarchique.

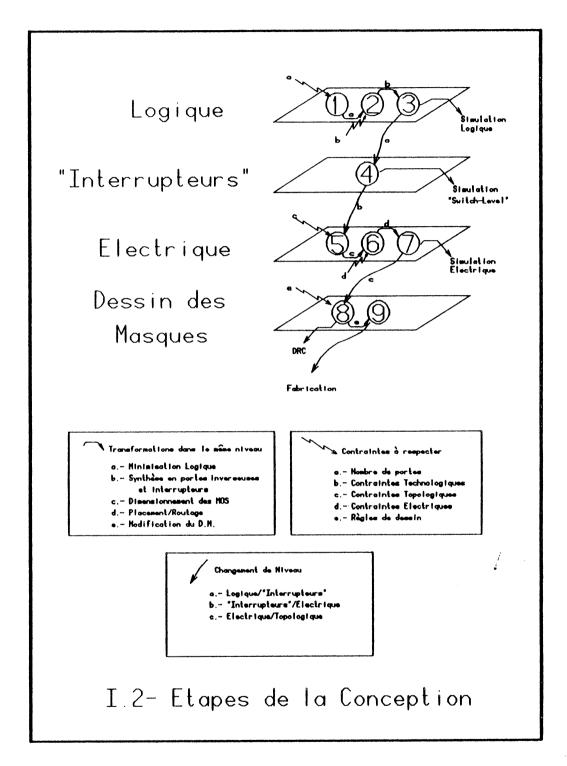

Deux types de traitement s'effectuent à chaque niveau :

- le passage d'un niveau au niveau suivant comme le passage d'un schéma logique à un réseau de transistors. Ce passage consiste à ajouter de l'information puisque chaque niveau comporte toute l'information des niveaux supérieurs plus des informations qui lui sont propres. Chaque niveau doit donc satisfaire toutes les contraintes des niveaux supérieurs plus celles particulières à ce niveau.

- des transformations au sein de ce niveau,

- \* des prises en compte de contraintes propres à ce niveau comme le dimensionnement des transistors ou la minimisation logique

- \* des préparations pour passer au niveau suivant tels que la synthèse en portes inverseuses.

Parmi les contraintes qui doivent être respectées on peut citer

- la conformité fonctionelle du circuit.

- la conformité comportementale du circuit (consommation, vitesse, etc..).

- le respect des règles de dessin d'une technologie particulière.

- la surface du circuit doit être la plus faible possible (pb. de rendement en production).

- les coûts de conception, de correction et de test en production doivent être les plus faibles possibles.

Lorsqu'il est impossible de satisfaire des contraintes à un niveau donné il faut les faire «remonter» au(x) niveau(x) supérieur(s) pour y trouver une solution. Dans la conception de circuits performants il est courant de délaisser momentanement la conception descendante.

Une troisième méthode indispensable dans la conception des systèmes VLSI est la REGULARITE qui consiste à utiliser autant que possible un petit nombre d'objets qui, diposés judicieusement, permettent par un jeu d'assemblage la réalisation du plus grand nombre possible d'éléments fonctionnels. Cette régularité gagne à être utilisée avec des outils informatiques d'assemblage. Une «bibliothèque» de cellules doit être définie ainsi que leur règles d'assemblage et éventuellement un logiciel qui se chargera de l'assemblage suivant ces règles.

Le fait d'utiliser la régularité permet de diminuer fortement le temps de conception car celle-ci est réduite à l'assemblage des cellules. La fiabilité en est augmentée du fait de la verification implicite ou explicite des règles d'assemblage.

Ceci se traduit, dans le cas de la conception descendante, par une automatisation des niveaux inférieurs comme le dessin des masques [JER-83], la génération entière de blocs fonctionnels de grande taille tels que les parties opératives [SCH-83], [DON-84] et même la synthèse compléte d'automates à partir d'une description fonctionnelle [FOR-83] et [FLA-84].

Cette méthode est très puissante, mais elle entraine dans la plupart des cas une augmentation importante de la surface finale du circuit ainsi qu'une réduction des performances électriques. Pour pallier à ces inconvénients on utilise souvent des optimiseurs qui réalisent des transformations au sein d'un même niveau.

Pour ceci une myriade d'outils d'aide à la conception ont été créés ou adaptés. Ces outils vont des éditeurs graphiques aux «compilateurs» de silicium en passant par les vérificateurs, les optimiseurs et les bases de données.

On appelle Conception Assistée par Ordinateur l'ensemble de ces méthodes et de ces outils.

Cette thèse présente un de ces outils de C.A.O. spécialisé dans l'optimisation de certaines structures régulières : les Reseaux Logiques Programmables ou PLA.

# I.A.1 Optimisation Locale Et Optimisation Globale

La réduction de la complexité par découpage se traduit dans la conception des C.I. par la division du circuit en «blocs». Pour que ce découpage puisse se maintenir aux différents niveaux il est généralement réalisé sur les descriptions de haut niveau. Il faut relier les différents blocs entre eux par ce que nous appellerons des connexions, reliant des connecteurs appartenant à des blocs différents.

La surface des circuits détermine, entre autres, le rendement en production. Il est donc très important de faire des optimisations pour réduire la surface, tant au niveau des blocs comme au niveau des connexions. Pour ceci il faut donc réaliser :

- un bon placement de ces blocs pour réduire les connexions

- une adaptation topologique de ces blocs [VAN-79].

- une distribution adéquate des points de connexion (connecteurs) de chaque bloc

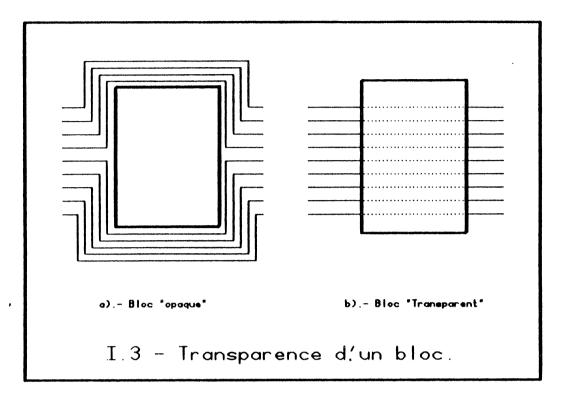

D'où la necessité de faire un plan de masse du circuit s'appuyant sur une évaluation de la surface, de la forme et de la position des connecteurs de chaque bloc. Dans la génération du plan de masse on doit tirer profit de la «déformabilité» (ou de la «dureté») et de la «transparence» des blocs [REI-82].

La déformabilité caractérise la faculté de choisir la forme (et donc la surface) d'un bloc. Elle dépend de la structure interne de celui-ci. Les blocs génerés automatiquement sont plus «durs» que les blocs dessinés manuellement (pour peu que la forme soit déterminée avant de faire le dessin).

La transparence d'un bloc est la capacité de celui-ci à se laisser traverser par des connexions externes. Elle est utilisée pour réduire la longueur des connexions entre blocs (fig. I-3).

L'emplacement des connecteurs doit être fait d'aprés le plan de masse et doit permettre une réduction de la longueur des connexions ainsi que du nombre de croisements entre celles-ci.

Suivre cette méthodologie d'optimisation globale suppose que :

- les évaluations, tant de forme que de surface, soient réalistes. Ceci ne peut se faire qu'avec l'aide de concepteurs très expérimentés ou des outils qui «contiennent» cette expérience.

- chaque bloc doit être concu pour un circuit particulier, ce qui limite l'utilisation des bibliothèques de blocs.

- la conception doit se faire d'une manière hierarchique.

Le résultat donne des circuits très performants dont le rendement en production est élevé.

Néanmoins, il est courant, soit pour des raisons de coût de conception soit par manque d'outils adaptés, d'utiliser l'optimisation locale au niveau des blocs. Les blocs sont alors concus plus ou moins indépendamment les uns des autres, placés dans le circuit et interconnectés par des programmes de tracé automatique de connexions. Géneralement cette méthode se traduit par une grande perte de surface en connexions.

INTRODUCTION LES PLAS

### I.B LES PLAS

Les Reseaux Logiques Programmables (PLAs) sont des structures régulières qui, générés par des logiciels particuliers, permettent le passage automatique d'une description logique au dessin des masques. Ils implémentent des fonctions logiques combinatoires, et ils présentent les caractéristiques suivantes :

- une structure logique simple

- une structure électrique simple

- et une structure topologique très simple.

Donc des règles simples de transformation. Ce qui rend la programmation des «transformateurs» ou générateurs (de dessins de masques) de PLAs extrèmement simple. C'est pourquoi ils sont devenus très vite des éléments largement utilisés dans la conception des circuits intégrés.

Il ne faut pas les confondre avec les FPLAs (Field Programmable Logic Array) ou avec les PALs (Programmable Array Logic) qui eux sont des circuits complets, en boîitiers MSI, réalisés à base de PLAs.

# I.B.1 Les Différentes Représentations Des PLAs

Les PLAs étant des structures définies à plusieurs niveaux, ils ont des représentations particulières à chacun de ces niveaux. Il est important de bien les différencier car des traitements distincts peuvent y être associés.

Ces différentes représentations sont :

#### I.B.1.a Représentation Fonctionelle.

Il est possible de décrire une fonction logique non pas par des équations mais par sa réponse à certaines valeurs des entrées. Dans ce cas on se sert d'un double tableau où on indique à chaque ligne la valeur des sorties face à chaque combinaison des entrées (fig. I-4).

Lorsque la valeur d'une entrée n'est pas specifiée ou qu'elle est définie comme  $\emptyset$  (phi) dans une ligne, les sorties ne dependent pas de cette entrée. Une combinaison d'entrées absente implique que les sorties peuvent prendre n'importe quelle valeur. Ces caractéristiques permettront au niveau logique une certaine liberté d'action lors des transformations logiques.

Cette représentation fonctionelle peut définir n'importe quel circuit logique combinatoire.

INTRODUCTION LES PLAS

| Α | В | С | F1 | F2 |

|---|---|---|----|----|

| 0 | 0 | × | 1  | ×  |

| 0 | 1 | × | 0  | X  |

| 1 | 0 | × | 0  | ×  |

| 1 | 1 | × | 1  | ×  |

| × | 0 | О | ×  | 0  |

| × | 0 | 1 | ×  | 1  |

| × | 1 | О | ×  | Î  |

| × | 1 | f | ×  | 0  |

# I.B.1.b Représentation Logique.

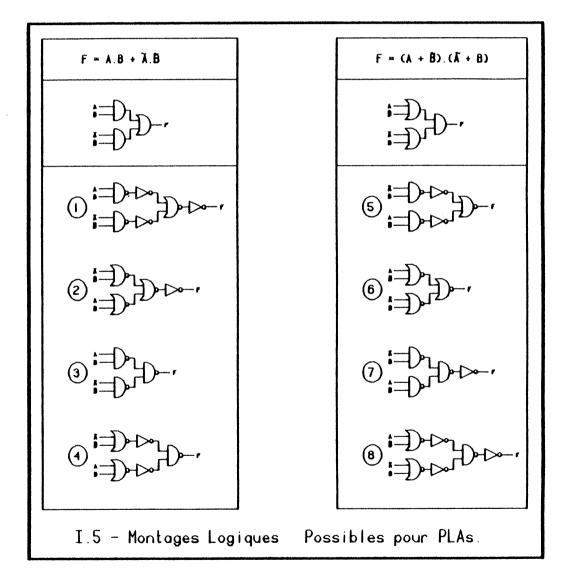

Il existe deux types de PLAs implémentant chacune une des deux formes canoniques (ou de Lagrange) des fonctions logiques.

Or toutes les fonctions logiques peuvent être décrites sous ces deux formes. Il en résulte que toutes les fonctions logiques peuvent être implémentées par des PLAs.

Ces formes canoniques sont :

- \* la somme des produits des entrées et de leur complément.

- \* le produit des sommes des entrées et de leur complément.

Dans le premier cas le PLA est composé de :

- un ensemble d'inverseurs pour génerer le complément de chaque entrée

- d'un ensemble de portes réalisant la fonction ET (produit) entre les entrées et leur complément.

- d'un ensemble de portes réalisant la fonction OU (somme) entre les diférentes sorties de l'étage precedent./

On appelle termes-produits ou plus simplement monômes les sorties du deuxième étage.

Dans le deuxième cas les deux ensembles ET et OU sont permutés.

Dans les technologies actuelles de fabrication des circuits intégrés il est impossible de réaliser directement des portes ET et des portes OU. Il est donc nécessaire de les transformer, au niveau logique, suivant les règles de De Morgan en portes inverseuses : soit en portes NON-ET (NAND) soit en portes NON-OU (NOR) plus des inverseurs.

Parmi les huit montages possibles (fig. I-5), deux sont pratiquement utilisés : le montage NOR-NOR et le montage NAND-NAND : ils présentent un nombre minimal de portes.

Le choix parmi ces deux structures est fait soit au niveau de la technologie utilisée pour la réalisation du circuit, soit par des contraintes électriques ou topologiques, soit par les performance souhaitées du PLA. Les PLAs peuvent être décrits comme toute fonction logique par :

- un tableau de vérité

- un ensemble d'équations logiques (ou un schéma logique équivalent), minimisées ou non.

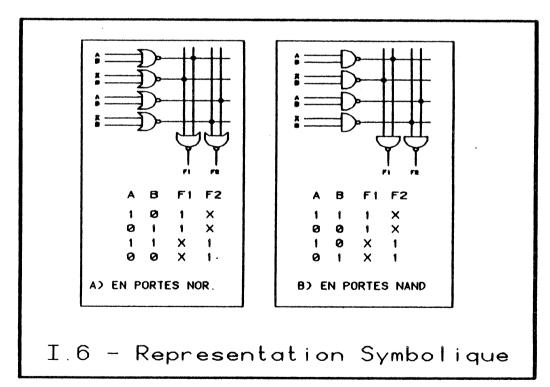

# I.B.1.c Représentation Symbolique.

Lorsque la structure logique des PLAs est connue, il est possible de la représenter d'une manière symbolique par exemple à l'aide d'un double tableau (fig. I-6) où chaque ligne correspond à un monôme. Dans le premier sous-tableau chaque colonne correspond à une entrée et dans la deuxième chaque colonne correspond à une sortie. Si le monôme M est génère à partir de l'entrée E on placera la valeur de l'entrée dans l'élément [M, E] du premier sous-tableau, dans le cas contraire on placera la valeur Ø (phi). L'utilisation du monôme M dans la génération de la sortie S sera représentée par une valeur particulière de l'élément [S, M] du deuxième sous-tableau.

Cette représentation utilise des valeurs ternaires dans le premier sous-tableau et binaires dans le deuxième. Dans le cas des PLAs elle peut être identique à la représentation fonctionelle, mais elle suppose connue la structure logique de ceux-ci.

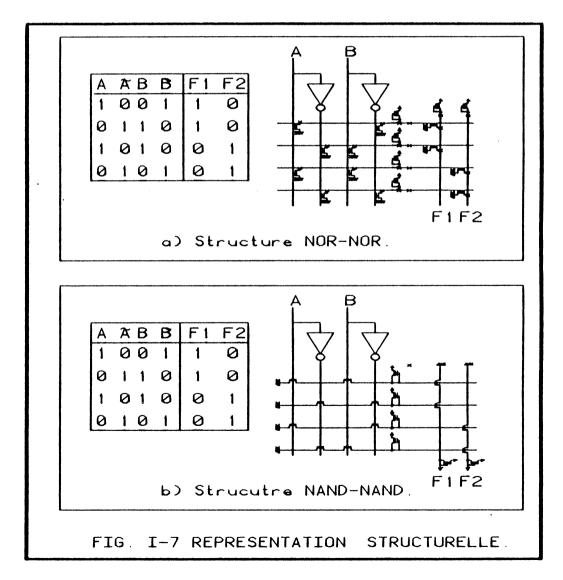

## I.B.1.d Représentation Structurelle.

Les PLAs sont réalisés par un réseau de décodeurs «un vers deux» (inverseurs) plus deux matrices de transistors soit en série (structure NAND-NAND), soit en parallèle (structure NOR-NOR).

L'utilisation de la valeur directe d'une entrée dans la génération d'un monôme correspond au placement d'un transistor entre cette entrée et le monôme. Si c'est la valeur inverse, le transistor sera placé entre le monôme et la sortie de l'inverseur correspondant.

Si la position des lignes des entrées et de leur inverse est détermininée on peut représenter la première matrice de transistors par un tableau à 2 \* NE colonnes et NM lignes (fig. I-7). Chaque ligne correspondant à un monôme et chaque colonne à une entrée directe ou inverse. L'élément [M, E] du tableau aura la valeur VRAI si il existe un transistor entre l'entrée (directe ou inverse) E et le monôme M. Dans le cas contraire sa valeur sera FAUX.

# INTRODUCTION LES PLAS

De même la deuxième matrice de transistors sera représentée par un tableau associé au premier où sera codée la présence de transistors suivant le même schèma.

Cette représentation ne contient que les informations de connexion entre transistors, entrées, sorties et monômes.

# I.B.1.e Représentation Topologique.

| A Ã B B 1 0 0 1 0 1 1 0 1 0 0 1 | F1 F2<br>1 0<br>1 0<br>0 1 |                                                                                                            |

|---------------------------------|----------------------------|------------------------------------------------------------------------------------------------------------|

| A A B B                         | F1 F2 T                    | CELLULE AVEC TRANSISTON MATRICE ET                                                                         |

| -                               |                            | CELLULE SAMS TRAMSISTOR MATRICE ET  CELLULE AVEC TRAMSISTOR MATRICE OU  CELLULE SAMS TRAMSISTOR MATRICE OU |

| FIG. I-8                        | DESCRIPTION                | TOPOLOGIQUE.                                                                                               |

On peut aussi représenter le dessin des masques des matrices à l'aide de deux tableaux binaires. Chaque élément du tableau représente une cellule (ou point PLA) contenant ou non un transistor. Les cellules des deux matrices peuvent être différentes ou identiques (à une rotation prés). On sait alors que chaque cellule comprend (pour des PLAs à structure NOR-NOR en technologie N-MOS grille en silicium polycristallin):

- une ligne en aluminium correspondant aux monômes (dans la matrice ET) ou aux sorties (dans la matrice OU).

- une ligne en silicium polycristallin correspondant aux entrées (matrice ET) ou aux monômes (matrice OU).

- une ligne en diffusion correspondant aux lignes de masse.

- éventuellement un transistor et un contact.

Il peut être intéressant dans certains cas d'ajouter un troisième type de cellule qui symbolise les lignes de rappel de masse.

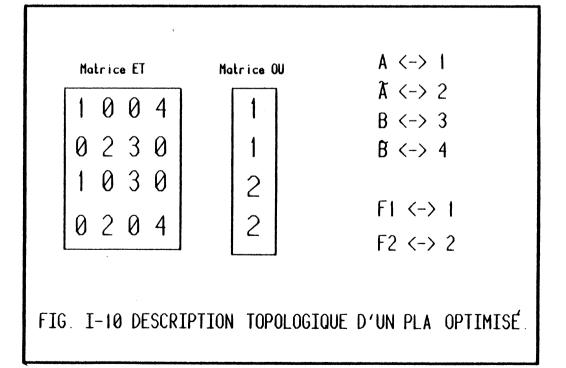

| Matrice ET 1 0 0 4 | Matrice OU | A <-> 1<br>A <-> 2   |

|--------------------|------------|----------------------|

| 0 2 3 0            |            | B <-> 3<br>B <-> 4   |

| 1030               | 0 2        |                      |

| 0 2 0 4            | 0 2        | F1 <-> 1<br>F2 <-> 2 |

Dans cette représentation chaque colonne est associée soit à une entrée (matrice ET) soit à une sortie (matrice OU).

Pour pouvoir représenter clairement un PLA optimisé suivant la méthode des lignes brisées (cf. Chapitre III), nous avons dû faire une modification à cette représentation. Elle consiste à définir dans chaque élément des tableaux contenant un transistor le numéro de l'entrée ou de la sortie associée (fig. I-9).

Ceci permet la représentation des PLAs qui contiennent plusieurs entrées ou plusieures sorties dans la même colonne, les deux matrices étant disjointes.

Dans les technologies N-MOS la structure NOR-NOR occupe une surface plus importante de silicium, mais permet une réponse plus rapide que la structure NAND-NAND; elle est donc pratiquement la seule utilisée.

Par contre dans la technologie C-MOS statique la structure NAND-NAND est souvent utilisée dans des circuits qui ne nécessitent pas de grandes performances temporelles tels que les montres à quartz ou les calculatrices.

Toutes ces représentations, faites à base de deux tableaux, définissent les PLAs à des niveaux différents.

# CHAPITRE II OPTIMISATION DES PLA

### OPTIMISATION DES PLAS INTRODUCTION

### II.A INTRODUCTION

Les principaux avantages des PLAs par rapport à la logique anarchique (ou aléatoire) sont les possibilités de génération et de dessin automatiques. Ils réduisent le temps de conception, facilitent les corrections éventuelles [FLE-75] et diminuent fortement les risques d'erreurs.

La dissociation des caractéristiques logiques, électriques et topologiques simplifie la vérification :

- La simulation logique peut se faire sur une description structurelle (tableau binaire) sans tenir compte des caractéristiques électriques ou topologiques.

- La simulation électrique se réduit à la simulation du chemin le plus long a travers le PLA. Ce chemin critique peut se déduire directement de la description structurelle du PLA puisque il existe une conformité complète entre la représentation structurelle, le schéma électrique et le dessin des masques.

- finalement la conformite des masques avec les règles de dessin technologiques est facilement obtenue avec une bonne définition des cellules de base et de leurs méthodes d'assemblage.

Néanmoins les PLAs présentent un inconvénient de taille : la surface qu'ils occupent est beaucoup plus importante que leur équivalent en logique aléatoire. Ceci est dû à leur structure régulière qui impose des contraintes topologiques au niveau du point PLA, donc au niveau du bloc tout entier.

Pour diminuer cet inconvènient on peut faire appel à deux traitements différents mais complémentaires :

- la minimisation logique qui conssiste à trouver la forme logique minimale pour réaliser une fonction logique donnée.

- l'optimisation topologique qui s'attaque à la surface de silicium nécessaire à la réalisation de ces fonctions logiques.

Les méthodes de minimisation logique existent depuis longtemps [MCC-57] et ont été améliorées ou adaptées à la résolution de problèmes de grande taille. Par contre l'optimisation topologique n'est apparue qu'avec l'avenèment des circuits intègrés de moyenne complexité, et plus particulièrement des microprocesseurs, vers les débuts des années 1970. A cette époque elle faisait partie de l'art des concepteurs, mais avec l'augmentation de la capacité d'intégration des C.I. cet art s'est transformé en une série de techniques et ces techniques en méthodes.

### OPTIMISATION DES PLAS MINIMISATION LOGIQUE

#### II.B MINIMISATION LOGIQUE

Une boîte noire définie par son comportement logique peut être réalisée par une quantité immense de fonctions logiques de manière équivalente. La minimisation logique conssiste à trouver parmi ces fonctions équivalentes celle qui comprend le nombre le plus faible d'opérateurs logiques.

Les méthodes classiques de minimisation logique utilisent comme opérateurs les fonctions ET, OU et NON. Mais dans la pratique ces opérateurs logiques sont souvent différents. Ainsi le concepteur de systèmes a pour opérateurs les boîtiers du commerce, par exemple la famille de circuits TTL, des FPLA ou des PAL. Dans la conception des circuits intègrés les opérateurs peuvent être

- soit les portes inverseuses NON-ET (NAND) et NON-OU (NOR)

- soit les transistors (interrupteurs).

Les méthodes classiques, étant clairement définies et simples d'utilisation, sont utilisées universellement aujourd'hui avec des post-traitements pour les adapter à chaque problème particulier. Mais le besoin de nouvelles méthodes propres à chaque type d'opérateurs se fait sentir, particulièrement dans le cas des PLAs optimisés topologiquement.

#### II.C OPTIMISATION TOPOLOGIQUE

Une optimisation topologique performante, en réduisant considèrablement la surface des PLAs, permet d'augmenter leur domaine d'utilisation. C'est pour ceci que plusieurs méthodes d'optimisation topologique ont été proposées.

Ces méthodes forment trois familles :

- les méthodes qui sans faire une réelle optimisation du PLA modifient l'emplacement des connecteurs pour améliorer le cablage externe.

- les méthodes qui optimisent localement le PLA

- les méthodes qui réalisent l'optimisation du PLA en tenant compte de leur environnement à l'intérieur d'un circuit.

Aprés avoir défini le PLA non optimisé que nous appellerons «PLA CLASSIQUE» et qui nous servira d'élément de comparaison, nous présenterons les différentes méthodes d'optimisation topologique connues à ce jour.

#### OPTIMISATION DES PLAS LE PLA CLASSIQUE

### II.D LE PLA CLASSIQUE

Le PLA classique implémente une forme canonique (optimisée ou non) des fonctions logiques à réaliser. Nous ne nous intéresserons qu'à la forme NOR-NOR qui est pratiquement la seule utilisée dans les technologies N-MOS classiques [MEA-80].

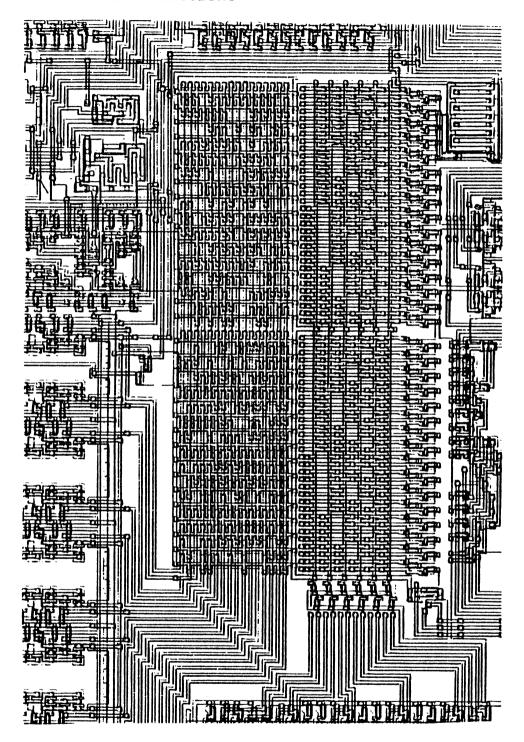

Fig. II - 1. - PLA Classique.

Il est formé de deux matrices rectangulaires (fig. II-1), les entrées étant parallèles aux sorties et perpendiculaires aux Termes-Produits. La surface du PLA classique est :

S = (KE \* E + (KS + KR1/PO) \* S) \* (KM + KR2/PE) \* M

#### avec

- E: nombre d'entrées

- S: nombre de sorties

- M : nombre de monômes

- KE: pas des entrées

- KS: pas des sorties

- KM : pas des monômes

- KR1 : pas des rappels de masse dans la matrice OU

- KR2 : pas des rappels de masse dans la matrice ET

PE : nombre de monômes entre deux rappels de masse (matrice ET)

PO: nombre de sorties entre deux rappels de masse (matrice OU)

Le PLA classique a toutes ses entrées et sorties du même côté. Les connecteurs d'entrée sont distants de KE et les connecteurs de sortie de KS. Il nécessite donc un cablage externe pour amener ces signaux au pas déterminé par le dessin du point PLA (fig. IÎ-2).

L'ordre des connecteurs d'entrée et de sortie n'est pas fixé et il peut être utilisé pour simplifier le cablage externe, mais il ne modifie en rien la surface du PLA.

Les programmes de génération de masques de PLAs classiques sont simples et se limitent généralement a placer des cellules-point avec transistor et des cellules-point sans transistor, des cellules de rappel de masse et à gèrer leurs symétries et rotations. Dans ce cas les lignes en silicium polycristallin traversent complètement les matrices et ajoutent des capacités superflues ce qui augmente inutilement le temps de propagation du PLA.

Il existe aussi des programmes plus astucieux qui génèrent des lignes de poly de longueur strictement nécessaire.

Fig. II - 2. - PLA Classique dans son environnement.

### II.E MODIFICATION DES CONNECTEURS

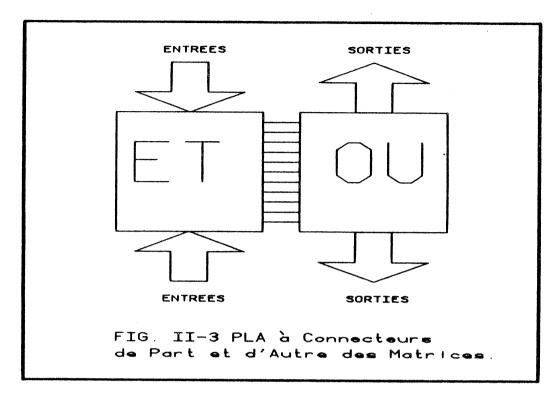

Etant donné que les lignes d'entree (en poly) et les lignes de sortie (en alu) traversent entièrement le PLA, il est facilement envisageable de placer les connecteurs soit en haut, soit en bas du PLA (fig. II-3).

# OPTIMISATION DES PLAS MODIFICATION DES CONNECTEURS

La surface des matrices n'est pas modifiée, mais l'enveloppe doit prendre en compte l'emplacement des éventuels amplificateurs d'entrée et/ou sortie. La surface globale peut alors être modifiée, et, en fonction de la forme de ces amplificateurs on peut soit gagner soit perdre en surface. De toutes facons le principal intérêt de cette méthode est de disposer judicieusement ces connecteurs pour réduire le tracé des interconnexions externes.

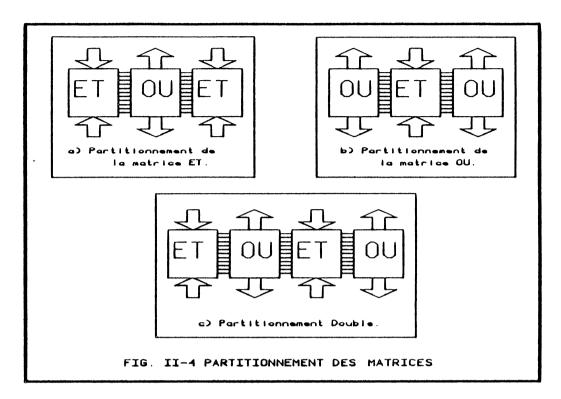

#### II.F PARTITIONNEMENT DES MATRICES

Cette méthode conssiste à réaliser un PLA avec deux matrices OU, placées de part et d'autre de la matrice ET (fig. II-4). On obtient ainsi deux groupes de sorties à des emplacements géographiques différents, ce qui permet d'éviter un grand nombre de croisements de fils à l'extèrieur du PLA.

De la même facon le partitionnement peut se faire sur la matrice ET ou même sur les deux. Le PLA résultant est à peine plus grand que l'équivalent «CLASSIQUE» à cause des interfaces supplémentaires entre les matric.s (principalement une rangée de contacts). Les PLAs monomatrices [VAR-84] et [VAR-85] constituent un cas extrême du partitionnement des matrices.

On trouve un PLA à deux matrices OU dans le microproceseur INTEL-8085 pour le décodage des instructions. La première matrice OU génère les commandes pour l'automate des temps, tandis que la deuxième définit à quelles classes appartient l'instruction en cours de décodage.

### OPTIMISATION DES PLAS PLACEMENT LATERAL DES CONNECTEURS

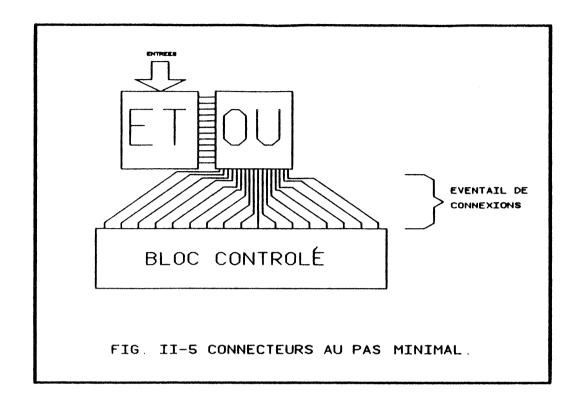

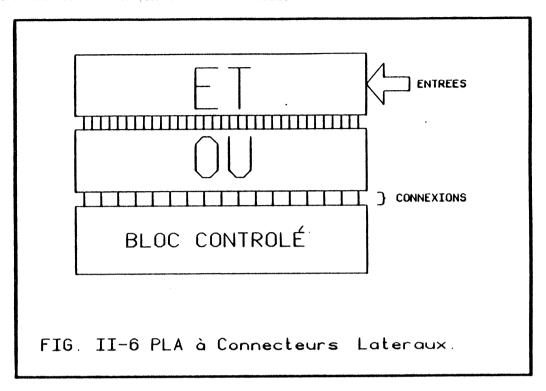

#### II.G PLACEMENT LATERAL DES CONNECTEURS

Dans toutes les méthodes précédentes l'accès aux entrées et sorties se fait sur le pas interne des lignes en poly ou alu, c'est à dire que les connecteurs sont pratiquement juxtaposés et, même si leur ordonnancement correspond avec celui des connexions externes, il faut une certaine surface pour amener ces dernières sur les connecteurs (fig. II-5). Ceci est principalement vrai lorsque le PLA génère un grand nombre de commandes pour un ou plusieurs blocs de grande taille. Il est alors intéressant de disposer les connecteurs de sortie sur le côté du PLA et non sur les extrémités (fig.II-6). Si le nombre de monômes est supérieur au nombre de sorties on dispose alors d'une grande latitude pour placer les connecteurs.

Un tracé interne des connexions doit alors être réalisé, et ce tracé interne impose :

- que les lignes de poly soient les plus courtes possible pour libérer de la place à l'intérieur du PLA.

- un réordonnancement judicieux des segments de sortie (lignes en alu) pour faciliter le cablage interne.

- un allongement éventuel du PLA pour accéder aux segments de sortie qui restent inaccessibles.

- le tracé des connexions internes doit se faire soit en diffusion soit en poly (pour une techologie N-MOS classique), ce qui augmente la capacité et la résistance des lignes de sortie et augmente donc le temps de propagation du PLA.

# OPTIMISATION DES PLAS PLACEMENT LATERAL DES CONNECTEURS

Cette méthode permet, en disposant les amplificateurs de sortie sur le côté du bloc PLA, d'avoir des contraintes topologiques moins importantes dans le dessin des premiers et donc de réduire un peu la surface du PLA.

Un exemple de ce type d'optimisation peut être trouvé dans le microprocesseur INS-8072 de National Semiconductors où l'emplacement des connecteurs de sortie correspond presque exactement à la position de leur utilisation dans la partie opérative du circuit.

Cette même méthode peut être aussi appliquée aux entrées d'un PLA, mais avec des contraintes plus importantes car :

- en général, la matrice ET a un taux de remplissage beaucoup plus important que la matrice OU,

- l'utilisation des lignes d'alu pour le cablage interne impose de placer les transistors de charge de la matrice ET entre les deux matrices augmentant un peu la surface globale.

Mais si le nombre d'entrées latérales est restreint ce type d'optimisation peut permettre une réduction importante de la longueur de certaines lignes.

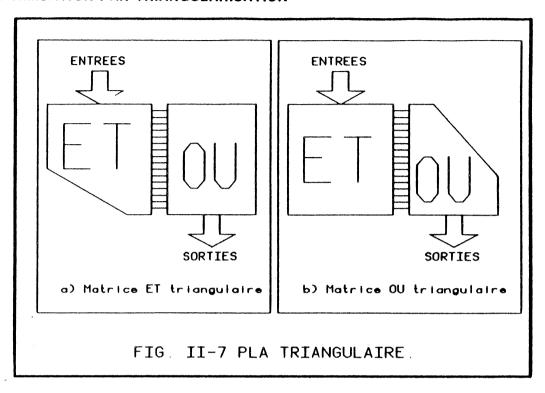

#### II.H OPTIMISATION PAR TRIANGULARISATION

Cette méthode d'optimisation se base sur le fait qu'il existe toujours dans le pla des points sans transistors. Il est alors facile de permuter des entrées, des sortie ou des monômes pour repousser dans un coin le plus grand nombre possible de points vides (donc inutiles) qui seront supprimés sur le dessin des masques.

Trois algorithmes d'optimisation triangulaire on été proposés dans [PER-79], mais leurs performances trés médiocres et surtout l'impossibilité de fixer les connecteurs d'entrée et sortie nous ont fait abandonner cette voie.

La génération de PLAs triangulaires se fait comme pour un PLA classique, la suppression des points inutiles se faisant «manuellement» sur un éditeur implanté. Le PLA résultant présente une enveloppe «biseautée» dans les coins ou les points inutiles ont été regroupés et supprimés (fig.II-7).

Le gain en surface dépend du contenu du PLA et est rarement superieur à 10 ou 20%. Mais le principal inconvénient réside dans la forme des zones libérées qui est irrégulière et donc n'est utilisable que pour y placer de la logique anarchique.

La position des connecteurs des entrées et des sorties est déterminée par l'optimisation et ne peut donc pas être utlisée pour améliorer le cablage externe. Il est toutefois possible de fixer l'emplacement des connecteurs d'entrée et/ou de sortie, mais l'optimisation y perd beaucoup en performance.

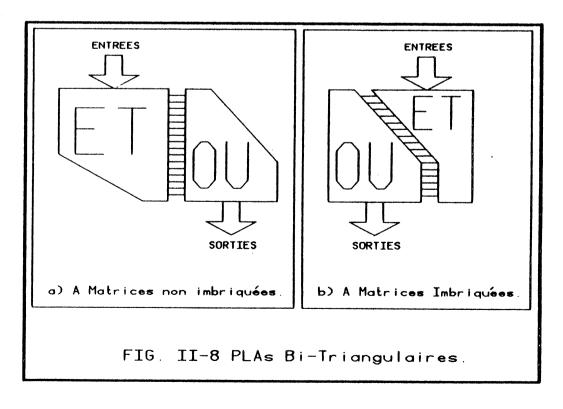

Dans certains cas la forme triangulaire des matrices peut être utilisée pour imbriquer les deux matrices, mais ceci suppose que la forme des zones librées dans les deux matrices soient semblables (fig. II-8). Le résultat est alors similaire au pliage simple des lignes et colonnes (voir chapitre II.J).

#### Page II-11

### OPTIMISATION DES PLAS OPTIMISATION PAR TRIANGULARISATION

L'optimisation triangulaire a été utilisée dans la conception du microprocesseur SC/MP de National Semiconductors. Dans ce circuit la surface libérée à été utilisée pour placer la gestion des interruptions qui est une des parties des microprocessuers où une conception topologique regulière est la plus difficile à réaliser.

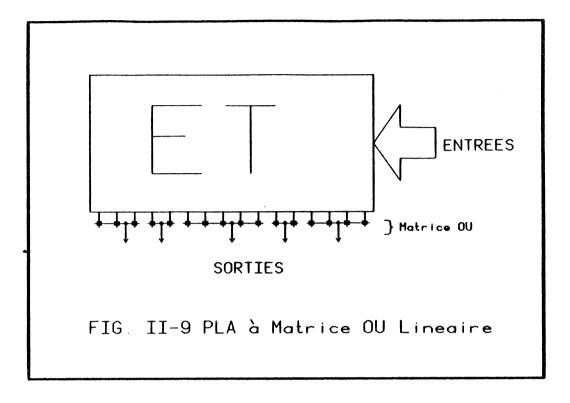

#### II.I OPTIMISATION PAR LINEARISATION DE LA MATRICE OU

Lorsque la matrice OU comporte un trés faible taux de remplissage et un nombre important de sorties, l'utilisation d'un PLA classique entraine un gaspillage énorme de surface. Si, en plus, l'environnement du PLA permet la disposition latérale des connecteurs de sortie, l'optimisation par linéarisation de la matrice OU permet un gain trés important de surface.

Cette optimisation conssiste en :

- une duplication des monômes qui attaquent plusieurs sorties pour obtenir un PLA où chaque monôme n'attaque qu'une seule sortie.

- un réordonnancement des monômes pour faire en sorte que tous les monômes impliqués dans une même sortie soient contigus.

- le placement des segments de sortie en une seule colonne.

- et finalement, le positionnement latéral des connecteurs de sortie.

La hauteur du PLA (par rapport au PLA classique) augmente du nombre de duplications plus une fraction qui dépend de la distance entre rappels de masse dans la matrice ET. Il faut donc prévoir dans le plan de masse du circuit l'emplacement nécessaire au PLA.

Par contre l'ordre des connecteurs de sortie n'est pas modifié lors de l'optimisation. Il comporte donc tous les avantages des PLAs à sorties latérales.

Le gain en surface dépend évidemment du contenu de la matrice OU, mais dans les cas les plus intéressants (sans duplication de monômes) le gain est de :

(KM + KR2/PE)\*M\*(KS + KR1/PO)\*(S-1)

C'est à dire que la nouvelle matrice OU contient une seule colonne au lieu de S. La taille de la matrice OU étant réduite au minimum, le temps de propagation sera inférieur à celui du PLA classique équivalent.

Il est intéressant de coupler cette méthode avec des procèdés de minimisation logique travaillant sortie par sortie et non globalement sur toutes les fonctions.

# OPTIMISATION DES PLAS OPTIMISATION PAR LINEARISATION DE LA MATRICE OU

La programmation de cette méthode est trés simple.

Un exemple de PLA linéaire se trouve dans le cicuit MC2 de Hewlett-Packard où il décode l'état de l'automate de séquencement pour générer certaines commandes de la partie opérative.

#### II.J OPTIMISATION PAR PLIAGE (FOLDING)

Il existe dans la litérature deux types d'optimisation designées sous le nom de «FOLDING» (pliage).

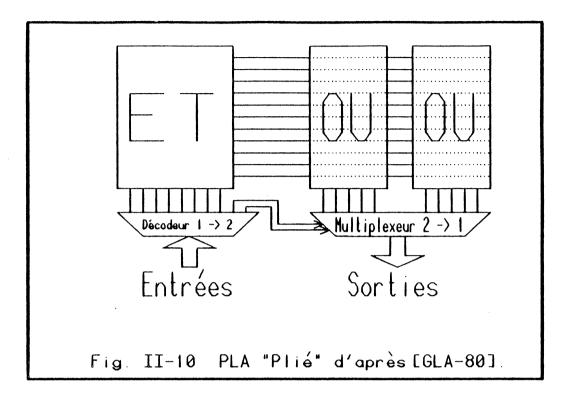

La première [GLA-80] conssiste à la réaliser des PLAs contenant une matrice ET à NE - 1 entrées, deux matrices OU (à NS sorties chacune) plus un réseau de NS multiplexeurs deux vers un commandé par l'entrée non utilisée dans la matrice ET. Topologiquement les deux matrices OU sont imbriquées. La figure II-10 présente ce type de «pliage». D'après Glasser et Penfield [GLA-80], les avantages sont : la possibilité de modifier la forme du PLA et réduire son temps de réponse et sa consommation.

Le deuxième type de pliage (folding) profite du faible taux de remplissage (nb. de transistors/nb. de points) des matrices. Il conssiste :

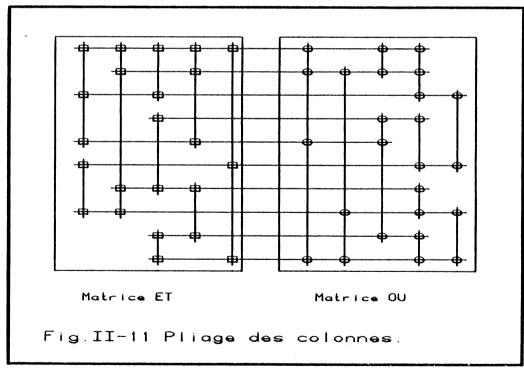

Pour le pliage de colonnes à placer dans une même colonne deux ou plusieurs entrées et/ou sorties (fig. II-11).

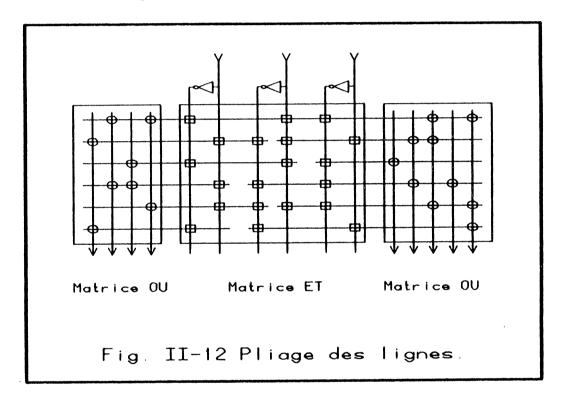

- Pour le pliage de lignes à placer dans une même ligne deux ou plusieurs monômes (fig. II-12).

La première référence à ce type d'optimisation a été présentée par [GRE-76] sous le nom de «segmentation», Greer introduit aussi la notion de PLA monomatrice qui sera reprise ultérieurement [VAR-84]. Schmookler [SCH-80] l'utilise pour «comprimer» des Unités Arithmétiques et Logiques réalisées à base de PLAs. Wood [WOO-79] est le premier à introduire le terme «folding» (pliage) qui désignait l'utilisation

- 1. d'une colonne pour placer deux entrées ou sorties.

- d'une ligne pour placer deux monômes.

Actuellement cette méthode est appelée pliage simple (simple folding) par opposition au pliage multiple. Le pliage complet d'un PLA qu'il soit fait au niveau des lignes ou des colonnes réduit de moitié la surface du PLA. Le pliage mixte (lignes et colonnes) complet réduit la surface au quart de la surface initiale. D'où l'intérêt croissant que suscite cette méthode d'optimisation.

L'optimisation par pliage est une méthode d'optimisation locale.

Luby et al. [LUB-82] démontrèrent que le problème du pliage des PLAs est un problème NP-complet, ce qui implique qu'il est impensable de trouver un résultat optimal avec des temps de calcul réalistes et ceci sur des exemples de moyenne et grande taille. Les algorithmes existants resolvent donc :

- soit des sous-problèmes dont la compléxité n'est plus exponentielle, mais qui présentent de grandes restrictions; alors une résolution optimale peut être trouvée.

- soit le problème complet mais avec des heuristiques particulières; alors l'optimalité des solutions ne peut pas être assurée.

- soit un problème de taille limitée où une solution optimale peut être trouvée dans un temps important mais non prohibitif [GRA-82].

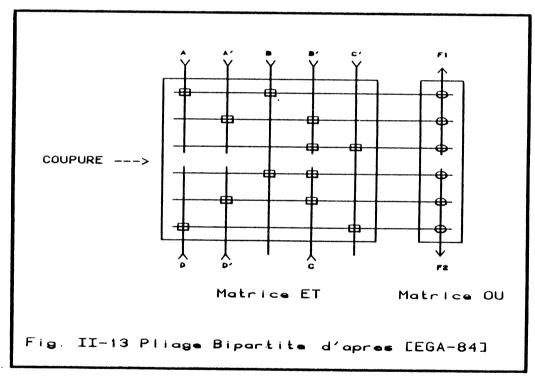

Dans le premier cas on trouve le pliage bipartite [EGA-82], [HU-83] où les «coupures» si elles existent sont placées dans la même ligne (colonne) voir fig. II-13.

Dans ce cas la recherche des solutions peut être faite par un parcours d'arbre optimisé pour trouver des solutions rapidement [EGA-82].

Dans le deuxième cas plusieurs heuristiques ont été présentées avec une étude des limites de ces méthodes [LIU-83]. Certains découpent le problème en sous-problèmes en mettant en jeu plusieurs heuristiques [SUW-81], tandis que d'autres traitent le problème dans son ensemble [HAC-82/a], [LUB-82], [DE-83].

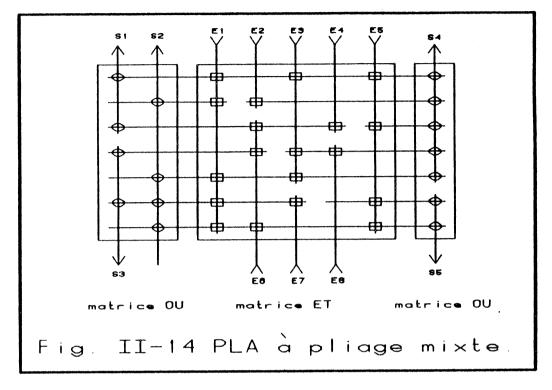

Le pliage mixte conssiste à faire sur le même PLA du pliage de lignes et du pliage de colonnes (fig. II-14). Dans ce cas les résultats dépendent non seulement du contenu du PLA, mais de l'ordre

dans lequel les deux pliages ont été réalisés.

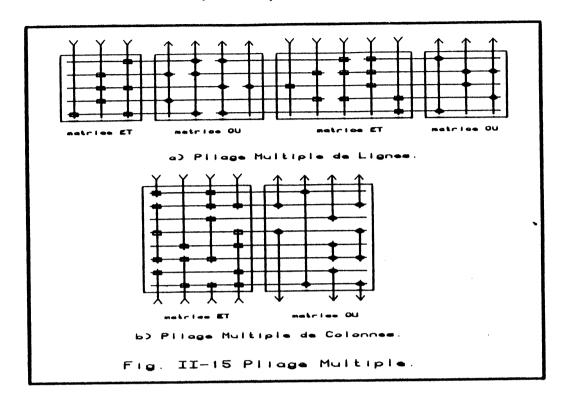

Le pliage multiple (multiple folding), consite à placer non pas deux, mais plusieurs entrées et/ou sorties (monômes) dans la même colonne (ligne) fig. II-15. Ceci permet une réduction beaucoup plus importante de la surface. Néammoins de nouvelles contraintes apparaissent :

- le fait d'introduire un pliage multiple rend plus complexes les programmes de dessin des masques.

- la nécessité d'un tracé interne de connexions pour amener les fils d'entrée ou de sortie sur le bord du PLA.

- la conformité au niveau des règles de dessin implique que l'optimisation et le tracé interne des connexions doivent se faire en tenant compte des règles de dessin. Ces contraintes doivent donc «remonter» aux niveaux supérieurs.

Dans un premier temps, ces problèmes ont été complètement ignorés [PAI-81], [HAC-81], puis, on a introduit des coupages du PLA pour le tracé interne [DEM-83/c] ce qui n'est pas une solution acceptable. Il est aussi possible de faire appel à un quatrième niveau d'interconnexion (deuxième metal ou polycide) [DEM-84].

Jusqu'à présent aucun dessin de masques d'un PLA optimisé par pliage multiple n'ayant été présenté (seulement des dessins à main levée), on peut supposer que ces problèmes n'ont pas été encore résolus.

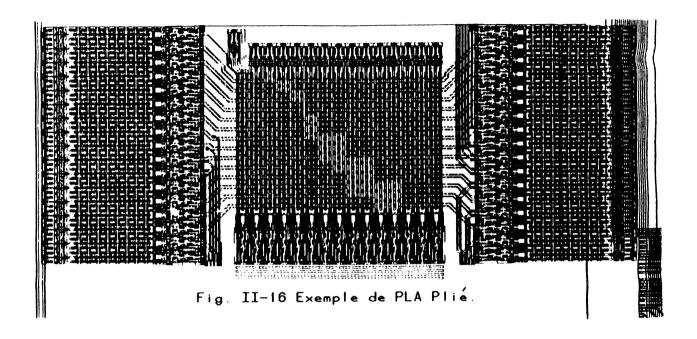

Dans tous les algorithmes de pliage la position des connecteurs d'entrée et sortie est déterminée par les programmes d'optimisation ce qui implique un tracé externe pour relier les entrées et sorties du PLA aux blocs concernés. généralement ce cablage externe occupe toute la surface (sinon plus) qui a été gagnée par l'optimisation du PLA (fig. II-16).

Et même si certains résultats sont très intéressants [HAC-82/b], le tracé externe des connexions entraîne une augmentation globale de surface et non pas une réduction [STE-82].

Un algorithme de pliage avec contraintes à été présenté [DEN-83/b] mais les auteurs n'ont pas insisté sur ses performances...

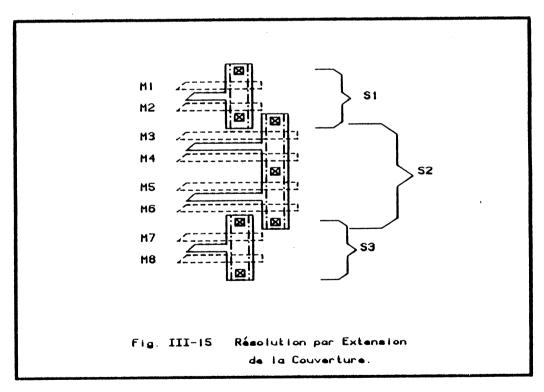

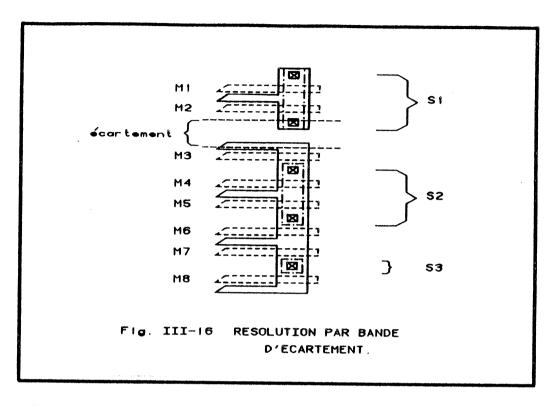

#### II.K OPTIMISATION EN LIGNES BRISEES

L'optimisation par lignes brisées conssiste à placer autant de segments que possible dans une même colonne.

La méthode peut être vue soit comme approche différente du pliage multiple de colonnes, soit comme une généralisation des méthodes suivantes :

- optimisation par accès latéral.

- optimisation linéaire.

# OPTIMISATION DES PLAS OPTIMISATION EN LIGNES BRISEES

- optimisation par partitionnement des matrices.

De la première méthode il utilise l'accès latéral aux entrées et aux sorties avec en plus le tracé des connexions internes. Elle ressemble à l'optimisation linéaire pour ce qui est de la possibilité de dupliquer des monômes et car plusieurs segments d'entrée (ou de sortie) peuvent partager une même colonne. En fait les PLAs linéaires sont un cas extrême des PLAs à lignes brisées. Le découpage des matrices permet, en plus, une optimisation particulière pour chaque groupe d'entrées ou de sorties.

Elle introduit des caractéristiques nouvelles :

- l'emplacement des connecteurs d'entrée et sortie (latéral ou non) est défini par l'utilisateur.

- l'optimisation se faisant à partir de ces emplacements, la connectabilité du PLA est assurée.

- la duplication des monômes est contrôlée.

Cette méthode est décrite dans le chapitre suivant.

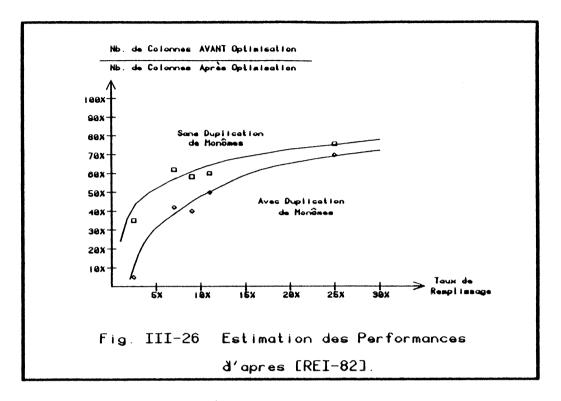

Le PLA résultant a une hauteur au moins égale à son équivalent en PLA calssique, mais une largeur qui peut être beaucoup plus faible. Les gains en surface dépendent du contenu du PLA, mais surtout du taux de remplissage des matrices. Il est donc possible de prévoir statistiquement, et avec une marge d'erreur de 5 à 10% la taille du

### OPTIMISATION DES PLAS OPTIMISATION EN LIGNES BRISEES

PLA optimisé en ne connaissant que le taux de remplissage de celui-ci [REI-83].

L'optimisation par lignes brisées comporte aussi quelques inconvénients :

- le nombre de solutions possibles augmente sous forme exponentielle avec le nombre d'entrées, de sorties et de monômes, il est donc impensable de trouver un optimum dans un temps polynomial. Les algorithmes devront donc être heuristiques et le résultat sera quasi-optimal.

- la régularité topologique étant «cassée», le dessin des PLAs à lignes brisées est beaucoup plus complexe qu'avec les autres méthodes d'optimisation.

- la nécéssité d'un tracé interne de connexions entre chaque «sortie» optimisée et le connecteur associé.

De part ses caractéristiques cette méthode convient à l'optimisation des matrices OU des décodeurs ou générateurs de commandes ainsi qu'aux entrées de condition dans les PLAs de séquencement.

Le gain en surface de cette méthode varie en fonction du contenu du PLA entre :

### OPTIMISATION DES PLAS OPTIMISATION EN LIGNES BRISEES

- 1. 30 et 50% pour des PLAs réalisant à la fois du séquencement et de la génération de commandes.

- 2. jusqu'a 70% pour des PLAs de décodage.

Dans le microprocesseur Z-80 de ZILOG le décodage des instructions est réalisé par un PLA à lignes brisées tant dans la matrice ET que dans la matrice OU. Avec toutefois une particularité : certains segments s'étendent sur plusieurs colonnes. Dans cet exemple le gain en surface est de 42% par rapport à son équivalent classique, sans compter le gain au niveau du cablage externe.

#### II.L OPTIMISATION PAR MONOMES ARBORESCENTS

L'optimisation par monômes arborescents tient une place particulière dans la famille des méthodes d'optimisation topologique des PLAs car elle modifie leur structure logique. Certains parlent de logique structurée [SHI-79] plutôt que de PLAs optimisés, et c'est en effet une é`ape intérmédiaire entre les PLAs et la logique aléatoire.

Les PLAs à monômes arborescents sont réalisés par des portes logiques complexes (NON-OU-ET) au lieu des deux niveaux NOR-NOR ou NAND-NAND.

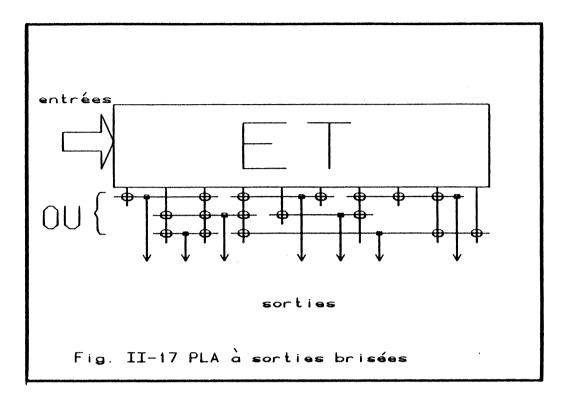

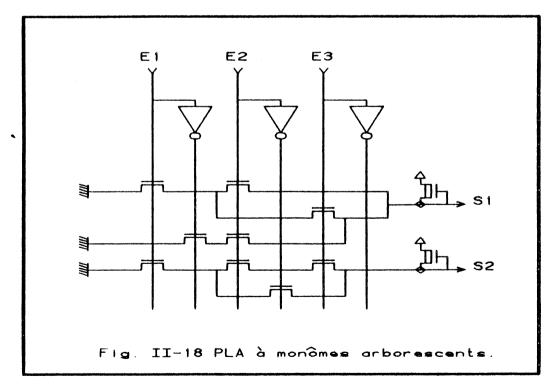

Ce type de PLA comporte une matrice unique avec des sorties latérales (fig. II-18), et est équivalent à une structuration d'un ensemble de portes complexes ayant des entrées commmunes. Leur

### OPTIMISATION DES PLAS OPTIMISATION PAR MONOMES ARBORESCENTS

principal inconvénient est dû à la mise en série de transistors, ce qui provoque un accroissement du temps de réponse du PLA. Ils ne seront donc utilisés tels quels que dans des circuits ou dans des blocs fonctionnels où le temps de réponse peut être important [GUY-79].

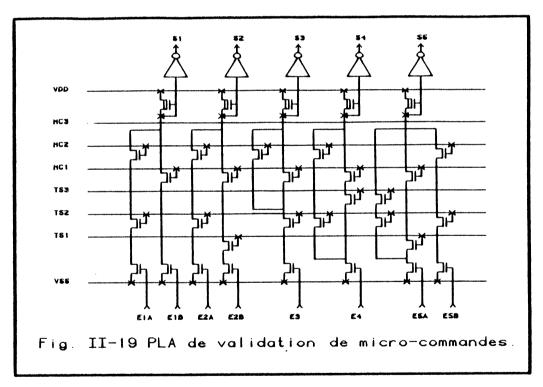

Il existe toutefois certaines conditions où les PLAs à monômes arborescents peuvent présenter des avantages supérieurs aux autres types de PLAs. C'est particuliérement le cas de la validation temporelle de commandes par un ensemble de signaux de temps dans certaines architectures de microprocesseurs [OBR-81]. Dans ce cas le nombre de transistors à mettre en série ne dépasse pas trois pour des circuits à deux niveaux d'intérprétation. Dans ce cas, les signaux temporels parcourent tout le PLA, les commandes à valider accédent latéralement, et les commandes validées sortent du côté opposé (fig. II-19). Ceci impose que les commandes et les signaux temporels soient valides à l'état haut car il n'y a pas de décodeurs (inverseurs) en entrée.

Les PLAs à monômes arborescents ressemblent aux PLAs linéaires, mais le fait de fusionner les deux matrices en une seule réduit fortement la puissance consommée car il n'y a que NS portes au lieu de NM + NS, de plus, l'état actif des sorties étant à l'état bas, il n'y a que les sorties actives qui consomment à un instant donné.

Ce type d'optimisation à été utilisé dans la conception des deux PLAs du microprocesseur MOM.400 [GUY-79], [PER-79] et [MAR-78]. Le premier réalisant le décodage des instructions, le deuxième validant temporellement les commandes. les microprocesseurs Z-80 et Z-8000 de ZILOG présentent aussi des structures similaires quoique leurs

# OPTIMISATION DES PLAS OPTIMISATION PAR MONOMES ARBORESCENTS

Page II-22

concepteurs les ont décrits comme une structuration de la logique anarchique [SHI-79].

# CHAPITRE III LA METHODE DES LIGNES BRISEES

### LA METHODE DES LIGNES BRISEES INTRODUCTION

#### III.A INTRODUCTION

Dans ce chapitre nous présentons la méthode d'optimisation topologique appelée «PAR LIGNES BRISEES».

Le but de cette méthode est de réduire la surface des PLAs de manière globale dans un circuit. Il faut donc laisser au concepteur la liberté complète dans la disposition des connecteurs d'entrée/sortie, ceci en vue d'un cablage externe le plus simple possible ou pourquoi pas, de connecter le PLA avec les blocs voisins par simple aboutement. Ce principe impose que l'optimisation se fasse à partir des contraintes dûes aux emplacements de ces connecteurs.

Il faut aussi permettre une certaine souplesse dans la forme du PLA pour l'adapter topologiquement au sein du circuit auquel il appartient. L'optimisation devra donc se faire sous contrôle du concepteur.

Etant donné que les PLAs ont une structure régulière, l'optimisation topologique peut se faire sur une représentation symbolique du PLA. Nous avons choisi la représentation structurelle qui permet la manipulation au niveau des transistors, et d'où il est aisé d'en déduire les equipotentielles. La génération des dessins des masques étant aussi relativement simple.

Nous avons donc abordé l'optimisation topologique en même temps que le dessin des PLAs optimisés et le tracé interne des connexions.

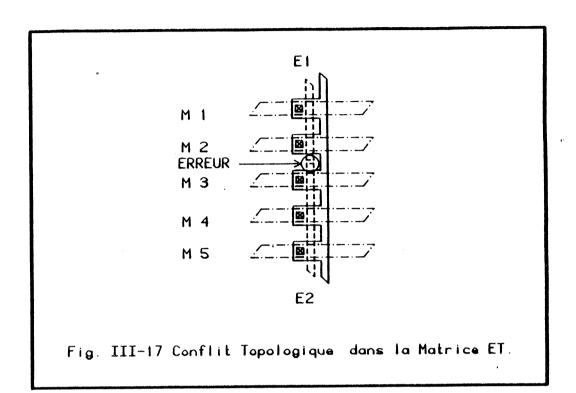

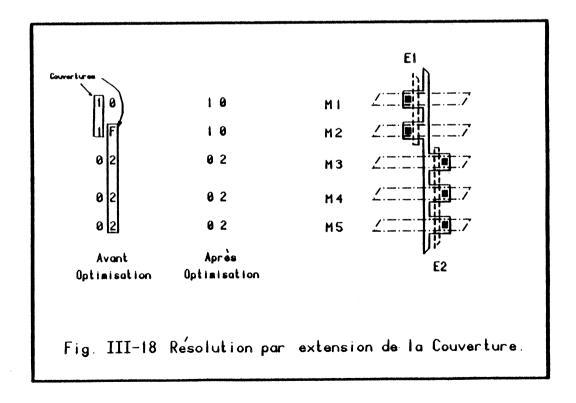

Certains problèmes concernant le dessin des masques et le .tracé des connexions internes étant impossibles à résoudre dans la phase de dessin, nous avons dû introduire des contraintes supplémentaires au niveau de l'optimisation symbolique.

L'optimisation des PLAs se réalise en quatre phases :

- l'ordonnancement des monômes, qui est une étape primordiale pour l'optimisation.

- la duplication des monômes, qui permet de modifier la forme du PLA par un allongement et un rétrécissement de celui-ci.

- le compactage des matrices où l'optimisation proprement dite est réalisée.

- les traitements complémentaires qui préparent les matrices pour la génération des masques et pour le tracé des connexions internes.

L'optimisation peut être réalisée sur une matrice où sur les deux.

### LA METHODE DES LIGNES BRISES DEFINITIONS ET CONVENTIONS

#### III.B DEFINITIONS ET CONVENTIONS

Nous allons décrire ici les concepts utilisés dans l'application de la méthode des LIGNES BRISEES.

#### III.B.1 Les Monômes.

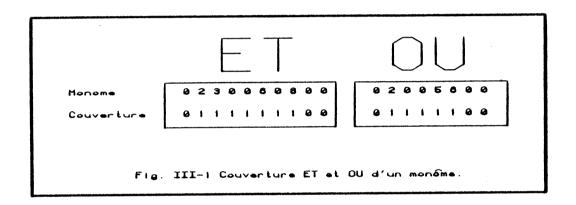

Un monôme est défini comme un double vecteur ayant une partie ET et une partie OU. La partie ET du monôme comporte NE élèments dont la valeur est :

- «E» si ce monôme comporte un transistor associé à l'entrée «E».

- \* ZERO pour les autres élèments.

De même la partie **OU** du monôme comporte **NS** élèments dont la valeur est :

- \* «S» si le monôme est associé via un transistor à la sortie . «S».

- \* ZERO autrement.

par exemple le monôme suivant

020056/12005

est géneré par les entrées 2, 5 et 6, et partage des transistors avec les sorties 1, 2 et 5. Une permutation des élèments de la partie ET ou des élèments de la partie OU ne modifie pas la fonction logique du monôme et donc ne modifie pas celui-ci. On peut dire que les monômes suivants sont identiques :

1 0 3 0 5 6/ 1 0 3 4 0 et 0 1 3 5 6 0/ 1 3 4 0 0

On ne peut avoir deux fois la même valeur du même côté du monôme. Ceci reviendrait à dire qu'il connecté deux fois à la même entrée ou à la même sortie.

Les monômes sont différenciés par leur ordre dans la matrice.

#### III.B.2 Couverture D'un Segment

La couverture ET (CET) d'un monôme est la partie du monôme delimitée par les deux transistors extrèmes de la partie ET du monôme,

Page III-3

# LA METHODE DES LIGNES BRISEES DEFINITIONS ET CONVENTIONS

de même la couverture OU d'un monôme est l'ensemble de points entre le premier et le dernier transistor (bornes incluses) du monôme.

CET[m] = (CPT[m], CDT[m])

avec

CPT[m] = numéro de la colonne de la matrice ET où

le premier transistor du monôme m est placé.

CDT[m] = numéro de la colonne de la matrice ET où

le dernier transistor du monôme m est placé.

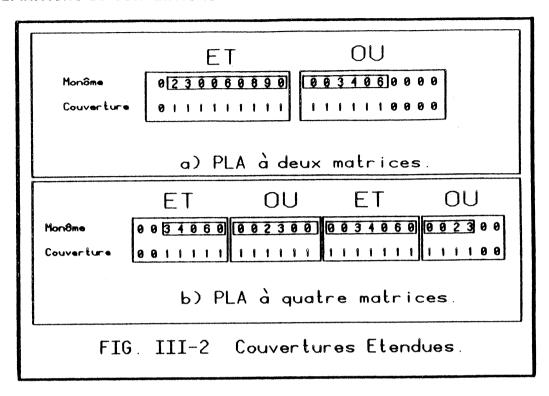

La couverture ET étendue d'un monôme pour un PLA à deux matrices est le segment qui part du premier transistor du monôme et qui finit sur le bord de la matrice ET qui juxtapose la matrice OU.

La couverture OU étendue d'un monôme pour un PLA à eux matrices est le segment qui part du bord intérieur de la matrice OU et qui finit sur le dernier transistor du monôme.

Dans un PLA à plusieurs matrices, la couverture étendue d'un monôme est celle déjà décrite pour les matrices externes; pour les matrices internes la couverture étendue d'un monôme est le segment du monôme qui relie les deux bords, droit et gauche, de la matrice.

Il faut souligner que la couverture d'un monôme comprend tous les transistors du monôme dans la matrice plus les points (cellules) intermédiaires. La couverture étendue comprend la couverture du monôme plus tous les points (vides) jusqu'au(x) bord(s) de la matrice.

Le nombre de points contenus dans la couverture d'un monôme est au minimum égal au nombre de transistors du monôme (dans la matrice considérée), et au maximum au nombre de colonnes de la matrice. Ce nombre dépend de la position (colonne) des entrées dans la matrice ET et des sorties dans la matrice OU.

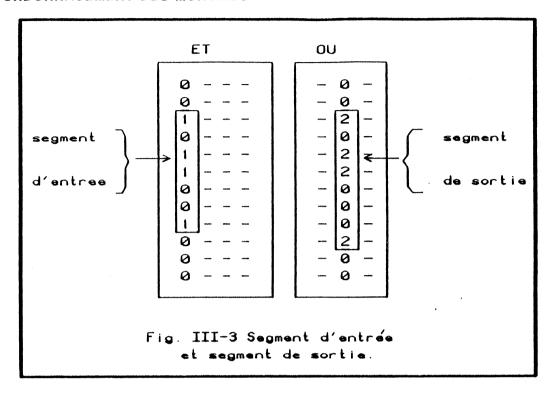

### III.B.3 Segment D'Entrée, Segment De Sortie.

Un segment d'entrée est le segment associé à une entrée, limitée par le premier et dernier transistor de cette entrée. Le segment d'entrée est égal à la couverture de l'entrée.

La même définition s'applique aux segments de sortie.

Physiquement un segment d'entrée correspond à une ligne en silicium polycristallin couvrant tous les transistors que cette entrée attaque ainsi que les points nécessairement vides entre ceux-ci.

Un segment de sortie correspond à une ligne d'aluminium qui relie tous les drains des transistors qui génèrent cette sortie.

les segments d'entrée et de sortie couvrent au moins autant de points que de transistors leur sont associés, et au maximum ils couvrent toute une colonne de la matrice.

Nous parlerons de couverture d'une entrée ou d'une sortie pour désigner l'extension du segment :

- soit jusqu'à un des bords (supérieur ou inférieur) de la matrice.

- soit jusqu'aux deux bords.

- soit jusqu'à un point déterminé généralement face au connecteur de cette entrée ou sortie.

#### III.C ORDONNACEMENT DES MONOMES

C'est dans cette phase que la position des connecteurs est prise en compte, et c'est l'ordonnancement des monômes qui conditionnera l'aptitude à compacter les matrices.

Les entrées d'un PLA attaquent des monômes, ces derniers attaquent à leur tour les sorties. Pour optimiser un PLA à partir des connecteurs il faut que les monômes attaqués par une entrée soient disposés prés du connecteur de cette entrée. De même les monômes qui attaquent une sortie doivent être disposés prés du connecteur de cette sortie.

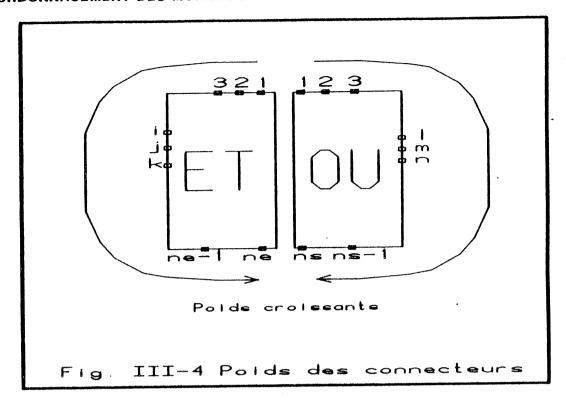

Nous commencons donc par donner un poids à chaque sortie en fonction de l'ordre de son connecteur (fig. III-4). On détermine le barycentre de chaque monôme de la manière suivante :

et on trie les monômes suivant leur barycentre.

Ainsi chaque monôme se trouve placé dans une position moyenne entre les sorties qui lui sont connectées.

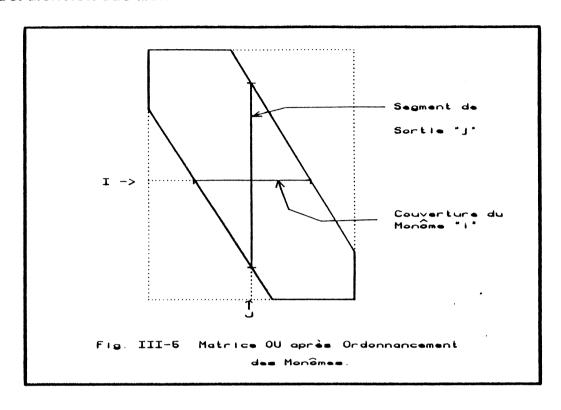

La taille des segments de sortie est réduite globalement. Le but de cet ordonnancement est la «diagonalisation» de la matrice OU.

Le réordonnancement des monômes tel qu'il vient d'être présenté se réalise sur la matrice OU. Mais chaque monôme ayant aussi une partie dans la matrice ET, il faut que ce réordonnancement soit répercuté sur cette dernière. C'est à dire que si on déplace la partie OU d'un monôme, il faut faire de même pour sa partie ET, et vis-versa.

Ce réordonnancement peut aussi se faire en fonction de la position des entrées. pour ceci il faut donc calculer le barycentre en fonction de celles-ci au lieu des sorties, ou pourquoi pas, en tenant compte en même temps des entrées et des sorties.

Si on fait un ordonnancement simple, soit à partir des entrées, soit à partir des sorties, on privilègie une matrice par rapport à l'autre. On obtiendra alors une matrice bien optimisée, l'autre l'étant moyennement ou pas du tout.

Mais, si l'ordonnancement se fait en tenant compte à la fois des entrées et des sorties, on obtiendra un PLA dont les deux matrices sont mal optimisées. C'est pourquoi cette dernière option ne sera pratiquement pas utilisée.

Les PLAs ayant normalement une matrice OU beaucoup plus creuse que la matrice ET, il est donc nécessaire de pouvoir privilégier la première plutôt que la dernière.

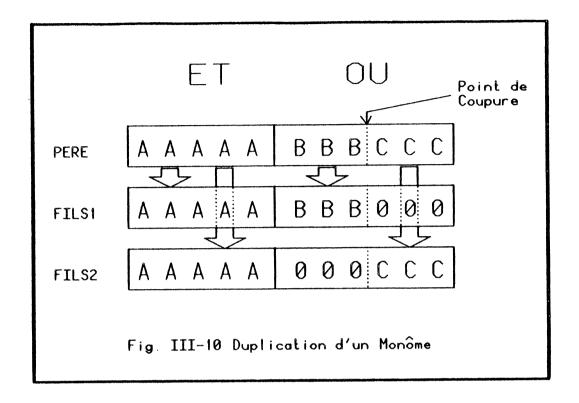

#### III.D DUPLICATION DES MONOMES

Il faut noter que le placement barycentrique regroupe les transistors autour de la diagonale de la matrice (Fig. I-5), et si jamais tous les transistors sont placés sur cette diagonale, le compactage pourra être complet (sur une seule colonne). Donc tous les moyens qui aident à la diagonalisation des matrices permettront un compactage plus important.

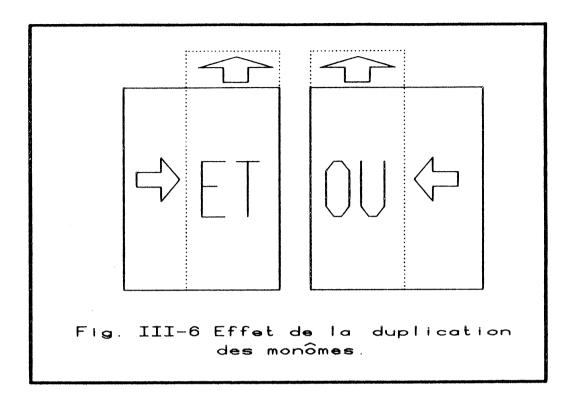

La diagonalisation de la matrice ET ne peut être améliorée sans modifier sa structure logique, par contre il est possible de rendre la matrice OU plus diagonale en dupliquant des monômes.

Ceci se réalise de la manière suivante :

- il faut d'abord choisir le monôme à dupliquer.

- on crée un nouveau monôme dont la partie ET est identique à la partie ET du monôme à dupliquer.

- on détermine un point de la couverture OU du monôme à dupliquer.

- la partie OU à gauche de ce point est dupliquée dans le monôme fils et mise à zéro dans le monôme père.

- on calcule le barycentre des deux monômes et les deux monômes complets (partie ET et partie OU) sont positionnés dans les matrices en fonction de leur barycentre.

### LA METHODE DES LIGNES BRISEES DUPLICATION DES MONOMES

Cette duplication allonge le PLA dans le sens de la hauteur, mais la couverture des nouveaux monômes ainsi que celle des sorties associées seront plus faibles. La réduction des segments de sortie va peut être permettre le placement de deux sorties sur une même colonne (ou niveau). L'allongement du PLA peut améliorer sa connexion avec le bloc contrôlé.

La difficulté de cette phase consiste à choisir le monôme qui une fois dupliqué permettra effectivement de gagner une colonne, ainsi que le point de coupure.

#### III.D.1 Choix Du Monôme A Dupliquer.

Le choix de ce monôme est crucial pour les performances du compactage. La détermination du monôme à dupliquer doit se faire sur un critère rapidement calculable car il doit être déterminé pour tous les monômes du PLA.

Nous avons testé plusieurs critères de choix que nous présentons ci-dessous.

### III.D.1.a Nombre De Transistors Controlés (NBT).

Page III-9

### LA METHODE DES LIGNES BRISEES DUPLICATION DES MONOMES

Plus un monôme controle de transistors (sorties), plus sa couverture est importante, donc plus une duplication de celui-ci améliorera la diagonalisation de la matrice OU. On obtient donc le premier critère :

choisir le monôme i tel que

$$NBT[i] = max (NBT[j])$$

pour j = [1..NM]

avec

pour k = [1..NS]

### III.D.1.b DELTA (Longueur De La Couverture Du Monôme).

D'un autre côté il semble normal que la duplication d'un monôme qui a une grande couverture permette une meilleure diagonalisation qu'un monôme à faible couverture. On définit alors la longueur de la couverture d'un monôme de la manière suivante :

$$DELTA[m] = CDT[m] - CPT[m]$$

Le choix se fait alors sur le monôme qui a la couverture la plus importante.

### III.D.1.c Distance Barycentre Moyenne (B-M).

On peut définir le facteur d'équilibre d'un monôme comme la distance entre son barycentre et le point milieu de sa couverture.

$$EQ[m] = \{(CDT[m] - CPT[m]/2\} - BAR[m]\}$$

Les monômes équilibrés (ou centrés) auront donc un facteur d'équilibre proche de zéro, tandis que les monômes déséquilibrés auront une valeur plus importante. Le choix du monôme à duliquer peut se porter sur le monôme le plus déséquilibré.

#### III.D.1.d Facteur D'Occupation (FO).

## LA METHODE DES LIGNES BRISEES DUPLICATION DES MONOMES

Il peut exister deux monômes ayant même couverture et même facteur d'équilibre, mais avec un nombre différent de transistors. Par exemple :

monôme [i] 0 2 3 4 5 0 0

monôme [j] 0 2 0 0 5 0 0

Dans ce cas les deux monômes ont la même couverture et le même barycentre, mais la duplication du deuxième entraînera une réduction plus importante des segments de sortie 2 et 5.

On définit alors le facteur d'occupation comme la somme de la longueur de la couverture et du nombre de transistors.

FO[m] = DELTA[m] + NBT[m]

Le choix se fait alors sur le monôme qui présente le facteur d'occupation le plus important.

## III.D.1.e Facteur D'Utilisation (FU).

On peut trouver le cas où le facteur d'occupation ne donne pas satisfaction. Soient les monômes

monôme[i] = 0 0 3 0 0 0 0 B 0 et

monôme[j] = 0 0 0 4 5 6 7 0 0

Ils ont tous les deux le même facteur d'occupation, mais manifestement la duplication du monôme i rendra la matrice plus diagonale que celle du monôme j.

On définit alors le facteur d'utilisation comme :

#### FU[m] = NBT[m]/DELTA[m]

Ce qui représente le «remplissage» de la couverture du monôme. Le choix doit alors se faire sur le monôme à plus faible facteur d'utilisation.

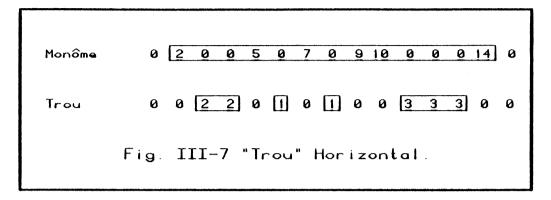

## III.D.1.f Choix Par Taille De Trou.

On désigne par «TROU HORIZONTAL» un ensemble de points vides contigus à l'intérieur de la couverture du monôme.

Page III-11

# LA METHODE DES LIGNES BRISEES DUPLICATION DES MONOMES

On définit alors :

TROU[m] = Nb. de points vides contigus dans la couverture de m

Le choix par taille de trou consiste à prendre le monôme qui comporte le trou le plus grand et qui donnera par la duplication deux monômes fils très distants.

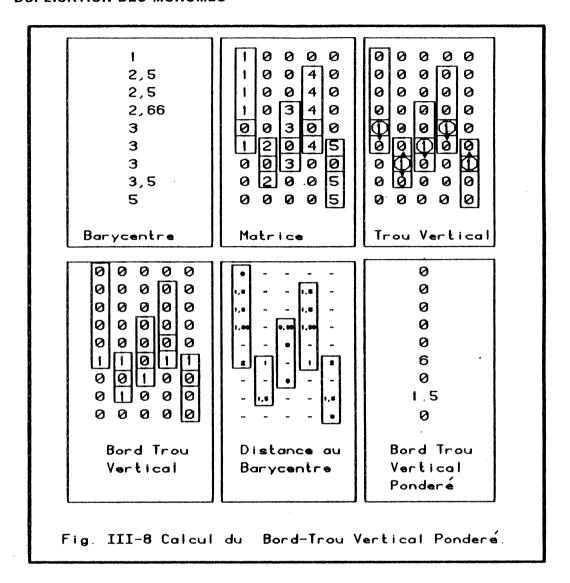

## III.D.1.g Choix Par Distance Bord-Trou Vertical Pondérée.

On peut aussi considèrer les trous des sorties qui sont connectées à chaque monôme. Dans ce cas on peut se limiter aux trous contigus au premier ou au dernier transistor de la sortie.

On calcule alors pour chaque monôme et pour chaque sortie du monôme le «bord-trou» correspondant. On pondère cette valeur en fonction de la distance de la sortie avec le barycentre du monôme.

On calcule la matrice des trous verticaux :

TV[m,s] = nb. de points vides contigus verticalement au point M, S si ce point est vide et si il appartient à la couverture (verticale) de la sortie s, zéro autrement.

à partir de celle-ci on détermine la matrice des bords-trous-verticaux

BTV[m, s] = TV[m, s+1] si le point [M, S] contient le premier transistor de la sortie s,

= TV[m, s-1] si le point [M, S]contient le dernier transistor de la sortie s,

= zéro autrement.

finalement, pour chaque monôme

DBTVP[m] = SOMME (BTV[m,s] \* |(bary[m] - s)|)pour s = 1 à S

Le monôme à dupliquer est alors celui qui a le DBTVP plus important.

Ce critère favorise les monômes, qui étant connectés à des sorties très éloignées, allongent beaucoup les segments de ces sorties.

Ce critère doit être évalué entièrement à chaque duplication de monôme. Il est donc très coûteux en temps de calcul.

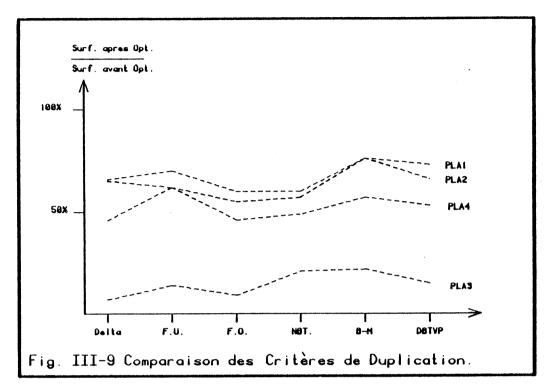

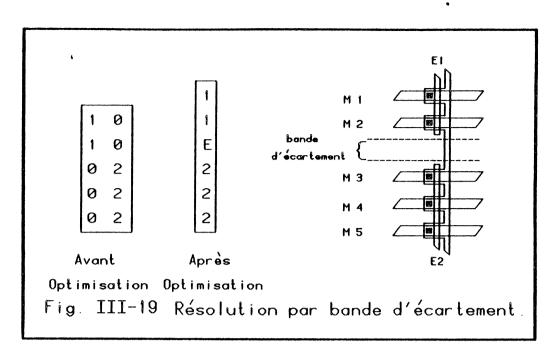

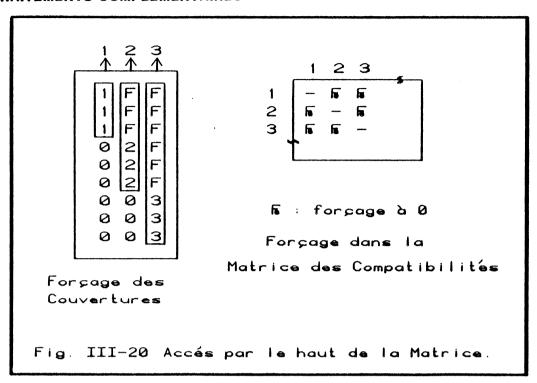

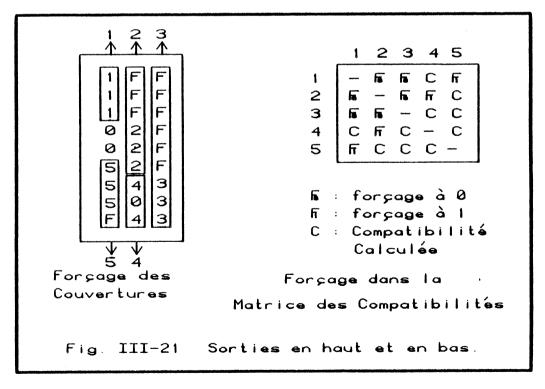

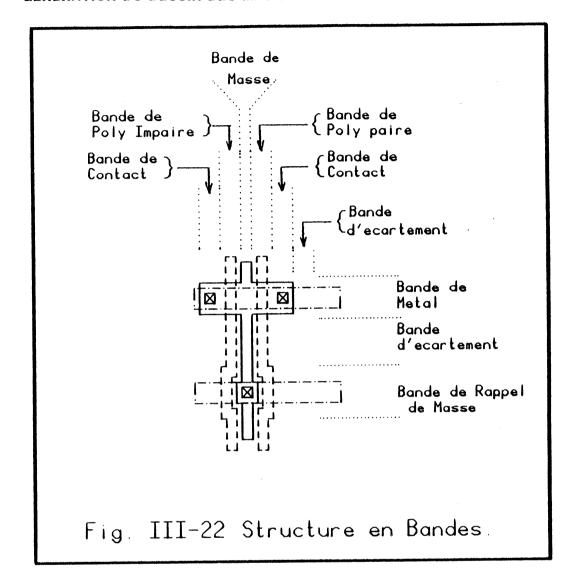

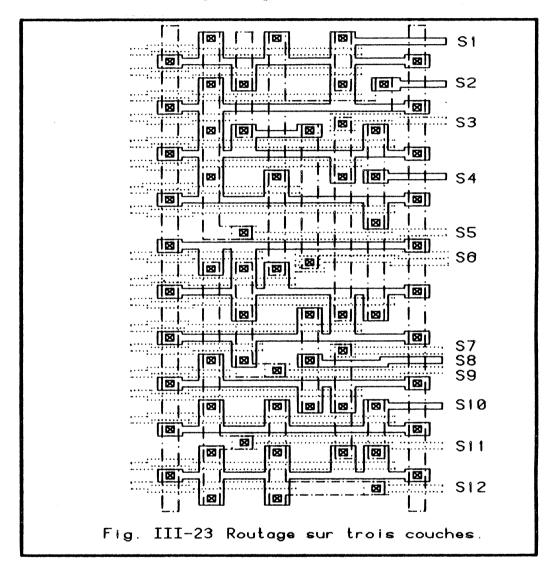

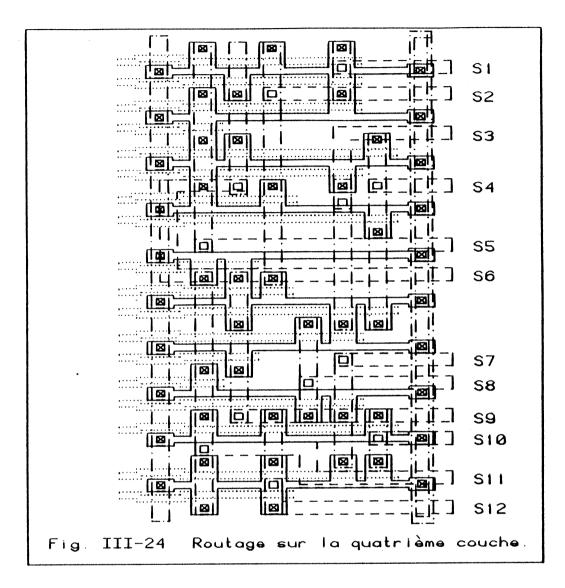

## III.D.2 Comparaison Des Critères De Choix.