# Conception Robuste dans les Technologies CMOS et post-CMOS

Lorena Anghel

#### ▶ To cite this version:

Lorena Anghel. Conception Robuste dans les Technologies CMOS et post-CMOS. Micro et nanotechnologies/Microélectronique. Institut National Polytechnique de Grenoble - INPG, 2007. tel-00185993

## HAL Id: tel-00185993 https://theses.hal.science/tel-00185993

Submitted on 7 Nov 2007

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

## **Institut Polytechnique Grenoble**

## Habilitation à Diriger des Recherches

n° ISBN: 978-2-84813-106-1

#### Spécialité Micro et Nano Electronique

#### Préparée au Laboratoire TIMA

Techniques de l'Informatique et de la Microélectronique pour l'Architecture des ordinateurs

Dans le cadre de l'Ecole Doctorale

Electronique, Electrotechnique, Automatique, Télécommunications, Signal

Présentée par

#### Lorena ANGHEL

Titre:

## Conception robuste dans les technologies CMOS avancées et post-CMOS

Présidente du jury : Nadine Guillemot, PR, Grenoble INP

#### Rapporteurs:

B. Courtois, DR CNRS, Laboratoire CMP, CNRS-INPG-UJF

Pascal Fouillat, PR, Laboratoire IMS, Universités de Bordeaux

Jean Arlat, DR CNRS, Laboratoire LAAS-CNRS, Universités de Toulouse

#### **Examinateurs:**

Michael Nicolaidis, DR CNRS, Laboratoire TIMA, CNRS-INPG-UJF Mario Diaz-Nava, PhD, STMicroelectronics, Grenoble

#### Remerciements

Je tiens tout particulièrement à exprimer ma profonde reconnaissance et gratitude à Mr Michael Nicolaidis, ex-responsable de l'équipe RIS du laboratoire TIMA jusqu'au 2001, pour la confiance qu'il m'a témoignée depuis bientôt dix ans. Ses conseils, son soutien, son franc parler, permanents tout au long de ces années et son excellence scientifique ont joué un rôle crucial dans ce travail. Je lui suis très reconnaissant d'avoir accepté de superviser mon HDR.

Un grand merci à Mr. Pascal Fouillat, Professeur à ENSEIRB, Université Bordeaux 1 et à M. Jean Arlat, DR au Laboratoire LAAS-CNRS de Toulouse, qui ont répondu favorablement à ma requête pour être les "deux rapporteurs externes de l'Académie de Grenoble" de cette HDR. J'ai sollicité leur concours connaissant leur compétence et la qualité scientifique de leurs travaux.

Des remerciements particuliers vont à Mr Bernard Courtois qui a accepté de rapporter « en tant que rapporteur local de l'Académie de Grenoble » sur mon travail de recherche. En tant qu'ancien Directeur du laboratoire TIMA, il suit depuis dix ans mes travaux de recherche. Je tiens à lui exprimer mes plus sincères remerciements pour ses précieux conseils, nos discutions diverses et variées, les nombreuses opportunités qu'il m'a offert au cours de ces années.

Tous mes remerciements à Mme Nadine Guillemot pour avoir trouvé le temps et accepté la Présidence de ce jury d'habilitation.

Je remercie également M. Mario Diaz-Nava, d'avoir accepté de faire partie de ce jury, pour ses conseils. Ma reconnaissance va aussi à Mr Raoul Velazco l'actuel responsable du groupe QLF que j'ai intégré suite au départ de Michael pour son aventure, la start-up IRoC Tehcnologies. Raoul a été un des premiers lecteurs de ce manuscrit, ces connaissances en français étant meilleures que les miennes et très appréciées au bon moment ... Une grande partie de ces travaux de recherche et d'enseignement n'aurait pas pu être possibles sans les conseils, le soutien permanent et constant de Mr Régis Leveugle.

Le travail présenté dans ce mémoire est un travail collectif. Mes remerciements vont à ceux qui m'ont accompagné dans cette aventure intellectuelle depuis plusieurs années : Susi Saleh, Nadir Achouri, Elefterios Kolonis, Claudia Rusu, Dan Alexandrescu, Cristiano Lazzari, Trinh Trong Dang. J'espère leur avoir apporté au moins autant qu'ils m'ont apporté. Sans eux, ce document n'existerait pas. Je remercie mes collègues du TIMA, administratifs et enseignants, les collègues de l'ENSERG, avec qui je partage les problèmes et les plaisirs quotidiens.

Enfin, mes remerciements vont bien sur à mon cher époux et à toute ma famille qui sont toujours là et supportent le rythme de vie que je leur impose.

## **Table de Matières**

| TA | TABLE DE MATIERES3                                                                          |                |  |  |  |

|----|---------------------------------------------------------------------------------------------|----------------|--|--|--|

| A٦ | VANT-PROPOS                                                                                 | 5              |  |  |  |

| 1. | . CHAPITRE 1 INTRODUCTION GENERALE                                                          | 7              |  |  |  |

|    | 1.1. Vers des systèmes integres ultimes a base de CMOS                                      | 7              |  |  |  |

|    | 1.2. LES DEFIS DE LA CONCEPTION INTEGREE EN TECHNOLOGIES CMOS ULTIMES                       | 8              |  |  |  |

|    | 1.2.2. Bruit sur les rails d'alimentation                                                   | 10             |  |  |  |

|    | 1.2.3. Variation du processus technologique                                                 | 12             |  |  |  |

|    | 1.2.4. Vieillissement des transistors induit par NBTI                                       | 15             |  |  |  |

|    | 1.2.5. Les techniques de réduction de la puissance                                          | 16             |  |  |  |

|    | 1.2.6. Effets des particules ionisantes et des neutrons atmosphériques                      | 16             |  |  |  |

|    | 1.2.7 Défauts permanents                                                                    | 19             |  |  |  |

|    | 1.3. Defis des Nanotechnologies                                                             | 19             |  |  |  |

| Cl | CHAPITRE 2 TECHNIQUES DE TOLERANCE AUX FAUTES DANS LES CMOS ULT                             | IMES ET        |  |  |  |

| N  | NANOELECTRONIQUE                                                                            | 22             |  |  |  |

|    | 2.1. TECHNIQUES DE TOLERANCE AUX FAUTES TRANSITOIRES ET DE DELAI DANS LES CMOS ULTIM        | ES22           |  |  |  |

|    | 2.1.1. TECHNIQUES DE TOLERANCE AUX FAUTES TRANSITOIRES ET DE DELAI AU NIVEAU BLOC FONC      | CTIONNEL.23    |  |  |  |

|    | 2.1.1.1. Tolérance aux fautes matérielles par l'utilisation du C-element                    | 23             |  |  |  |

|    | 2.1.1.2. Tolérance aux fautes HW/SW par la redondance temporelle                            |                |  |  |  |

|    | 2.2. ANALYSE DES CIRCUITS AUTO-CONTROLABLES FACE AUX FAUTES TEMPORELLES ET A NIVEAUX        | ζ              |  |  |  |

|    | INDETERMINES                                                                                | 30             |  |  |  |

|    | 2.3. TOLERANCE AUX FAUTES DANS LA NANO-ELECTRONIQUE                                         | 30             |  |  |  |

|    | 2.3.1. Nanoélectronique - Technologie à très grande densité de défauts                      | 31             |  |  |  |

|    | 2.3.2. Techniques d'auto-réparation à l'aide de BIST et BISR                                | 32             |  |  |  |

|    | 2.3.2.1. Techniques d'auto-réparation au niveau de colonne/bit de données                   | 34             |  |  |  |

|    | 2.3.2.3. Approches diversifiées d'auto-réparation                                           | 36             |  |  |  |

|    | a. Autoréparation basée sur la polarité des erreurs                                         | 36             |  |  |  |

|    | b. Auto-réparation basée sur la reconfiguration dynamique combinant la réparation au niveau | de la          |  |  |  |

|    | colonne de donnés et des blocs de données                                                   | 38             |  |  |  |

|    | c. Autoréparation dynamique combinée avec des codes ECC                                     | 40             |  |  |  |

|    | 2.3.3. Autoréparation au niveau cellule mémoire ou cellule logique simple                   | 41             |  |  |  |

|    | 2.4. Bilan du chapitre                                                                      | 43             |  |  |  |

|    | 2.5. Perspectives                                                                           | 43             |  |  |  |

| Cl | CHAPITRE 3 EVALUATION PREDICTIVE DU COMPORTEMENT DES CIRCUITS COM                           | <b>1PLEXES</b> |  |  |  |

| FA | ACE AUX FAUTES                                                                              | 45             |  |  |  |

|    | 3.1. Introduction                                                                           | 45             |  |  |  |

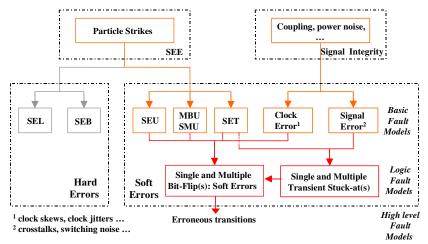

|    | 3.2 Model es de fautes et niveaux d'arstractions                                            | 50             |  |  |  |

| 3.3. LIEN ENTRE LES NIVEAUX D'ANALYSE                                   | 53 |  |  |

|-------------------------------------------------------------------------|----|--|--|

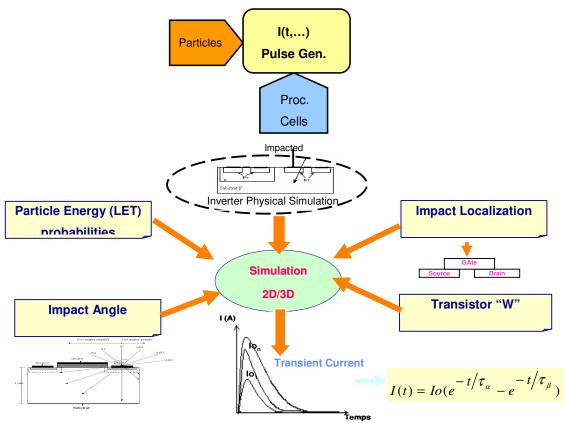

| 3.4. EVALUATION DE SENSIBILITE AU NIVEAU PHYSIQUE                       | 55 |  |  |

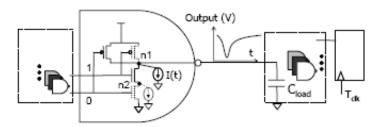

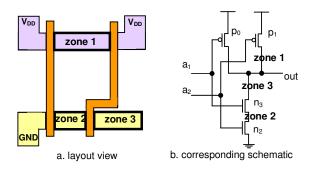

| 3.5. EVALUATION DE LA SENSIBILITE AU NIVEAU ELECTRIQUE (SPICE)          | 57 |  |  |

| 3.6. EVALUATION DE LA SENSIBILITE AU NIVEAU LOGIQUE                     | 60 |  |  |

| 3.7. EVALUATION DE LA SENSIBILITE AU NIVEAU RTL ET SYSTEME              | 62 |  |  |

| 3.8. BILAN DU CHAPITRE                                                  | 63 |  |  |

| 3.9. Perspectives                                                       | 63 |  |  |

| CHAPITRE 4. SYSTEMES COMPLEXES FIABLES A BASE DE NANOTECHNOLOGIES       | 65 |  |  |

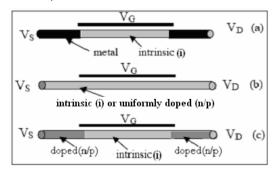

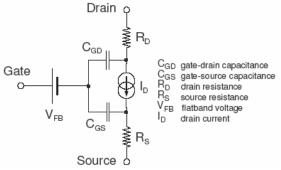

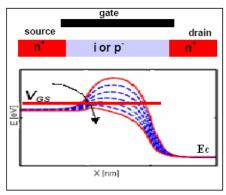

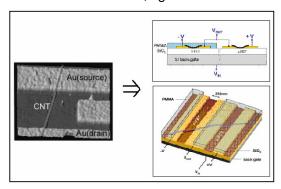

| 4.1. Du nanotube de carbone au transistor CNTFET                        | 66 |  |  |

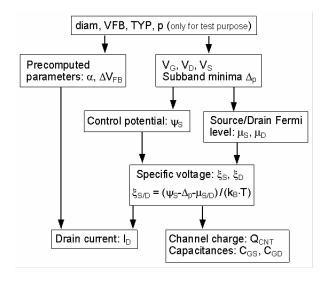

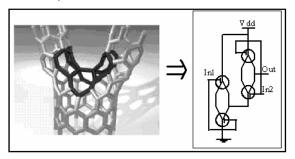

| 4.2. NANOTUBES DE CARBONE : MODELE COMPACT                              | 69 |  |  |

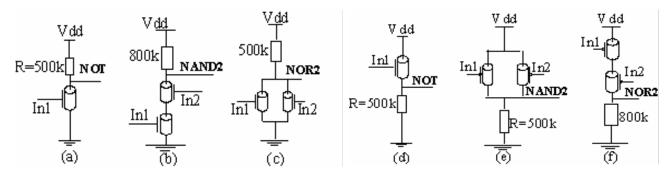

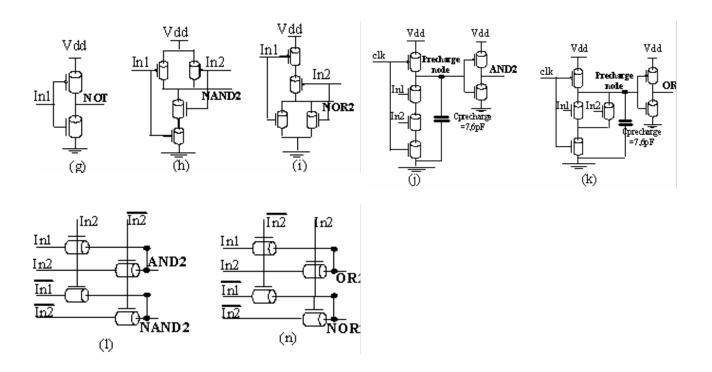

| 4.3. NANOTUBES DE CARBONE : PORTES LOGIQUES ET ELEMENTS DE MEMORISATION | 71 |  |  |

| 4.4. SIMULATION DES PORTES LOGIQUES A BASE DE CNTFET                    | 73 |  |  |

| 4.5. OUTILS DE SIMULATION DE DEFAUTS ET FAUTES PARAMETRIQUES            | 76 |  |  |

| 4.6. PERSPECTIVES: AUTRES OUTILS DE CAO POUR LES NANOTECHNOLOGIES       | 77 |  |  |

| CHAPITRE 5. CONCLUSION ET PERSPECTIVES                                  | 80 |  |  |

| REFERENCES                                                              | 82 |  |  |

| DEUXIEME PARTIE                                                         | 85 |  |  |

| CURRICULUM VITAE DETAILLE                                               |    |  |  |

### **Avant-propos**

Ce document est rédigé en vue de l'obtention d'un diplôme d'habilitation à diriger des recherches de l'Institut National Polytechnique de Grenoble. Il résume les activités de recherche et d'enseignement auxquelles je me suis consacrée depuis une dizaine d'années : depuis ma thèse de doctorat au laboratoire TIMA entre 1997 et 2000 dans l'équipe RIS (Reliable Integrated Systems) ensuite pendant mon année d'Attaché Temporaire à l'Enseignement et à la Recherche à l'Université Joseph Fourier et enfin par les travaux de recherche en tant que Maître de Conférences à l'INPG Ecole Nationale Supérieure d'Electronique et Radioélectricité et chercheur au laboratoire TIMA au sein du groupe QLF (Qualifications of Circuits). Il intègre également les activités de recherche que j'ai effectuées lors de deux mobilités aux Etats-Unis en 2004 et en 2005 au sein de deux compagnies EDA et semiconducteurs : Intel Corporation et Zenasis Corporation.

En parallèle, j'ai exercé une activité d'enseignement très conséquente. Depuis 1998, j'enseigne la conception numérique VLSI ASIC et/ou FPGA, la conception de systèmes embarqués à différents niveaux d'abstraction, langages de modélisation informatiques, architectures des ordinateurs et des équipements pour les télécommunications, le test et la testabilité des circuits électroniques numériques, la tolérance aux fautes, dans différentes écoles d'ingénieurs de l'INPG (comme ENSIMAG, ENSERG, Département de Télécommunications, Mastère Nanotech), à l'Université Joseph Fourier de Grenoble ainsi que dans le cadre du Master Recherche Pro CSINA, ainsi que la Formation Continue de l'INPG et d'autres formations spécifiques auprès des industriels.

Ce mémoire présente dans sa première partie un résumé de mes travaux de recherche, menés en collaboration avec les doctorants que j'ai co-encadrés ou que j'encadre en ce moment (Nadir Achouri, Susi Saleh, Eleftherios Kolonis, Cristiano Lazzari, Trong-Trinh Dang, Claudia Rusu) et avec les nombreux stagiaires qui se sont succédés au laboratoire TIMA. Cette partie est structurée en plusieurs chapitres: Dans le chapitre introductif, je présente les défis techniques et technologiques actuels induits par l'avancement technologique de ces dernières années pour les systèmes embarqués complexes. En effet les nouvelles technologies en silicium présentent une augmentation sans précédent du nombre et des types de défauts permanents et de phénomènes transitoires qui requièrent la mise en place d'une approche globale de prédiction du taux de défaillances lors des premières étapes de conception. Cette évaluation doit être

accompagnée par la mise en place de techniques de robustesse ou de tolérance aux fautes à faible coût d'implémentation.

Le chapitre 2 présente les travaux de recherche concernant les techniques de tolérance aux fautes permanentes et transitoires destinées aux nouvelles technologies de silicium (ciblant les technologies en dessous des 32nm) ainsi qu'aux futures technologies de remplacement du silicium, les nanotechnologies. A ce jour, les analyses ITRS <sup>1</sup> des nanotechnologies prévoient la fabrication de ces technologies avec une très grande densité de défauts, de plusieurs ordres de grandeurs plus élevée que les technologies de silicium d'aujourd'hui.

Le chapitre 3 présente l'approche de prédiction du taux de défaillances des systèmes intégrés complexes. Des méthodologies de simulation de fautes concernant tous les niveaux d'abstraction sont présentées, tant pour les circuits numériques que pour les circuits analogiques, ainsi que la mise en place d'outils de simulation automatique.

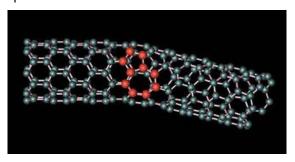

Dans le chapitre 4, je présente des activités de recherche beaucoup plus récentes, articulées autour de la modélisation et de la simulation des structures simples et complexes à base de nanotubes de carbone en vue d'une analyse prédictive de fonctionnement sans défaillances. Ensuite les systèmes complexes et les outils de CAO pour les Nanotechnologies sont présentés. Ce thème de recherche concerne l'étude théorique, la simulation et, à plus long terme, la réalisation par des procédés nano-technologiques de systèmes exhibant une dynamique complexe, dont la richesse de comportement est le résultat des interactions d'un nombre très élevé d'éléments relativement simples. Ce chapitre conclut la première partie du mémoire, en indiquant des perspectives possibles pour mes activités de recherche.

La deuxième partie du mémoire décrit sous la forme d'un CV étendu mes activités de recherche et d'enseignement ainsi que mes responsabilités administratives et collectives au sein de l'Institut National Polytechnique de Grenoble et à l'Ecole Nationale Supérieure d'Electronique et RadioElectricité. Cette partie inclut un recueil de mes principales publications scientifiques de ces dernières années.

-

<sup>&</sup>lt;sup>1</sup> ITRS - International Technology Roadmap for Semiconductors

### 1. Chapitre 1 Introduction générale

#### 1.1. Vers des systèmes intégrés ultimes à base de CMOS

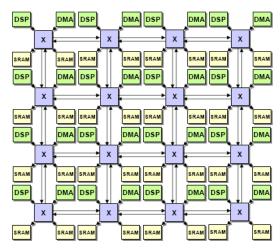

Le marché des télécommunications, du multimédia, de l'automobile, de l'avionique et d'autres applications sécurisées continue à croître à un rythme soutenu avec l'apparition d'applications diverses et complexes qui réclament une puissance de calcul de plus en plus importante tout en ayant un niveau de fiabilité et de sécurité de plus en plus élevé [1]. Au cœur de ces applications, se trouvent aujourd'hui des systèmes embarqués sur silicium organisés en plateformes de calcul à faible consommation (ceci étant une contrainte primordiale dans les nouvelles technologies), dont la capacité de calcul en termes de nombre d'opérations par seconde, double approximativement à chaque nouvelle génération technologique, suivant en cela la « loi de Moore ». Ils utilisent des architectures distribuées comportant plusieurs processeurs exécutant des tâches complexes (par exemple de traitement de signal), des centaines de mémoires de tailles différentes, des ASICs très rapides exécutant des fonctions spécifiques et d'autres composants exotiques [2]. Face aux coûts de développement extrêmement élevé, aux contraintes de consommation et de performance très poussées, au manque de souplesse quant à la programmation de nouveaux algorithmes et aux étapes de vérification très fastidieuses, les architectures intégrées reconfigurables s'imposent comme un nouveau concept architectural capable de répondre à ces défis. Il est prévu qu'à partir de la technologie 45nm les architectures matérielles ressembleront de plus en plus aux solutions de type réseaux programmables, étant composées d'un ensemble de processeurs et de mémoires identiques reliés par des réseaux de communication programmables [3][4] (voir figure 1); ceci afin de respecter les contraintes des cycles de développement et fabrication de plus en plus courts tout en apportant une certaine réduction du « time to market », ainsi que diverses contraintes système (consommation, flexibilité d'applications, puissance de calcul, etc...).

Figure 1. Architecture d'un Network on Chip NOC (Courtesy Arteris)

En outre, toutes ces applications doivent faire face aux défis sans précédent de la conception microélectronique bas niveau, entre autres les dispersions technologiques ainsi que les phénomènes parasites multiples.

## 1.2. Les défis de la conception intégrée en technologies CMOS ultimes

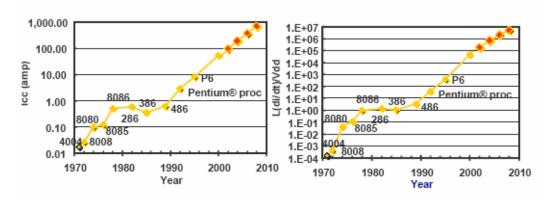

L'évolution des technologies CMOS en dessous des 90 nm, la forte diminution des tensions d'alimentation et l'augmentation de la fréquence de fonctionnement apportent de nombreux défis aux concepteurs micro électroniciens. Parmi les plus importants nous trouvons :

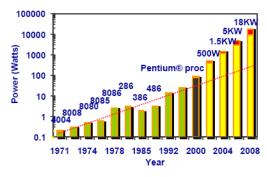

- a) l'augmentation de la puissance consommée due ces dernières années aussi à la consommation statique (voir figure 2),

- b) la diminution de la fiabilité et du rendement de production provoqués par la variabilité des paramètres des procédés de fabrication et par l'augmentation du nombre de phénomènes parasites [6].

Figure 2. a) Augmentation de la puissance consommée pour des microprocesseurs [5]

b) Puissance statique vs puissance dynamique.

Malgré l'existence de solutions ponctuelles concernant la maîtrise de la puissance consommée et la gestion de la variabilité, les technologies proches de 32nm apporteront une rupture dans le style de conception connu, notamment à cause de la nature des composants de base qui change profondément, mais aussi à cause des multiples phénomènes parasites ignorés auparavant et qui se rajoutent et se corrèlent avec les défis classiques.

Si en technologie 45nm, il est encore possible de concevoir des ASICs à partir des librairies de cellules standards pré caractérisées, en utilisant des flots de conception « classiques » il est certain qu'au delà de cette technologie, ces phénomènes nouveaux et corrélés deviendront bloquants, rendant obsolètes certaines de ces méthodes. Les techniques de conception statistiques adressant tous les niveaux d'abstraction commencent à faire leur apparition mais il semblerait qu'au-delà de la technologie 32 nm elles seront insuffisantes, et produiront des pertes en performances inacceptables.

Outre la variabilité des procédés, les circuits intégrés complexes sont de nos jours soumis à des phénomènes parasites pouvant induire des erreurs logiques et de timing, conduisant à des erreurs de fonctionnement inacceptables.

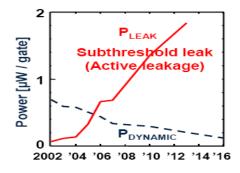

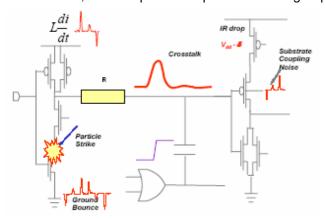

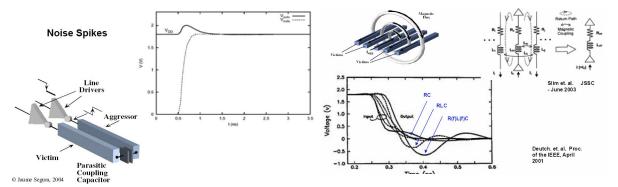

La figure 3 présente le panorama de ces phénomènes transitoires (bruit sur les lignes d'alimentation, nommé IR drop, Ground bounce et Ldi/dt, le bruit de substrat, les crosstalks et les couplages de toutes sortes, et les impacts des particules énergétiques).

Figure 3. Panorama de phénomènes transitoires autres que les variations du procédé.

Dans la suite du document est donnée une brève présentation de ces phénomènes.

#### 1.2.1. Couplages (crosstalks)

Les règles de conception du « layout » devenant de plus en plus complexes et la densité d'intégration de plus en plus élevée, les performances d'un élément de design dépendent des éléments voisins, et sont dans la plupart des cas influencées par le couplage capacitif et inductif entre les éléments et les interconnexions proches (phénomène connu sous le nom de « crosstalk »). Ces couplages affectent généralement le timing d'un circuit, et peuvent provoquer des erreurs de timing pendant le fonctionnement du circuit.

La figure 4 montre les fluctuations de tension dans le cas d'un fil victime du crosstalks [7] .

Figure 4. Phénomène du crosstalk

Figure 5 Influence du modèle RLC sur la tension du fil victime

Les modèles actuels sont dans la plus part de temps simplistes et ne prennent pas en compte les variations de la capacité et de l'inductance avec la fréquence de fonctionnement (voir figure 5), ce qui conduit à une mauvaise estimation de ce phénomène et à une correction inadéquate lors des étapes de placement-routage. La mise en œuvre de structures de layout régulières bien maîtrisées et caractérisées pourrait résoudre une partie de ces problèmes, mais globalement les crosstalks resteront une source majeure de bruit parasite dans un circuit complexe.

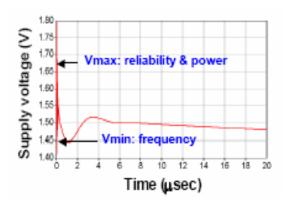

#### 1.2.2. Bruit sur les rails d'alimentation

La chute de tension sur les lignes d'alimentation (« voltage drop » ou  $\Delta V_{DD}$  ) et son équivalent sur la masse nommé aussi « ground bounce » est représenté par des chutes ou des pics de tension pouvant aller jusqu'au 30-40% de la valeur nominale de l'alimentation. Ils sont généralement induits par une commutation simultanée de plusieurs cellules logiques et/ou transistors (voir figure 6). Il est prévu que la valeur de cette perturbation augmente de 15% à chaque nouvelle technologie. [8]

Figure 6. Phénomène du  $\Delta V_{DD}$

Il est difficile, voire impossible, d'estimer correctement cette chute de tension par simulation ou par l'analyse temporelle, d'autant plus que la vraie activité du circuit n'est connue qu'à la fin du cycle de conception, en présence d'une application. Les conséquences évidentes de ce phénomène sont une augmentation du temps de propagation des portes. A ce jour on considère que 10% de variation de V<sub>DD</sub> peut induire 10-20% de pertes de performances en ce qui concerne le temps de propagation des portes [8].

Le couplage inductif est aussi très significatif (bruit Ldi/dt) principalement à cause de l'augmentation significative de la vitesse de fonctionnement (figure 7).

Figure 7. Bruit Ldi/dt

Ce problème était complètement ignoré auparavant lors des étapes d'analyses du bruit. Les technologies de Cuivre (Cu) génèrent une augmentation des inductances des fils métalliques, ainsi le bruit Ldi/dt sera un autre problème majeur pour les technologies CMOS ultimes, car les conséquences sur le fonctionnement global du système, une fois de plus, conduiront à une augmentation des délais des portes et du timing du circuit en général La figure 8 présente les prédictions ITRS [9] des phénomènes  $\Delta V_{DD}$  et Ldi/dt

Figure 8 Prédiction du ΔV<sub>DD</sub> et Ldi/dt (réprises par S. Borkar, DAC 2003 [8])

#### 1.2.3. Variation du processus technologique

Les phénomènes de variabilité des paramètres des transistors au sein de la puce deviennent prépondérants : d'un point à l'autre d'un même circuit, les caractéristiques des transistors varient dans des proportions considérables, ce qui conduit entre autres à une variation des tensions de seuil des transistors d'un même circuit intégré, et par conséquent à la variation du temps de propagation des différents chemins. Les courants ION et IOFF varient également, conduisant à l'augmentation de la puissance consommée (surtout statique). Les temps de propagation des interconnexions varient également, car les interconnexions sont affectées elles aussi par la variabilité, principalement à cause du mauvais ponçage, qui modifie les propriétés physiques des interconnexions (par exemple, en augmentant localement la résistance).

Aujourd'hui il devient extrêmement important de considérer toutes les variations possibles, au sein d'un même circuit (« intra die variations ») mais également les variations d'un circuit à l'autre sur la même plaquette (« inter die variations »), ou d'un lot de plaquettes à l'autre, ou bien d'une ligne de fabrication à l'autre dans le cas de plusieurs lignes de fabrication alignées. Ces variations atteignent des valeurs très élevées dans les technologies 32nm.[11]

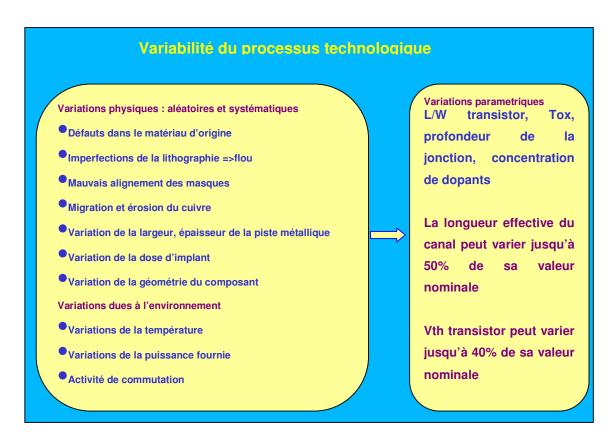

Plusieurs sources de variations ont été identifiées. Elles sont présentées dans la figure suivante (figure 9) :

Figures 9 Sources possibles de PV et les conséquences sur les transistors

Les variations du processus de fabrication peuvent être dues à plusieurs raisons, nous pouvons mentionner la gravure, la lithographie et la CMP<sup>1</sup> comme étapes technologiques pouvant induire des variations, mais la dose d'implant peut également fluctuer, ainsi que les éléments dus à l'environnement (température, V<sub>DD</sub>, etc).

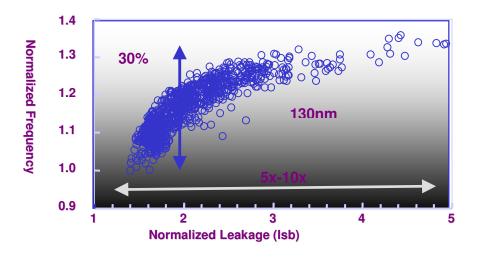

Pour la technologie 130 nm [12] la variation du processus de fabrication induit une variation de la fréquence allant jusqu'à 30% de la fréquence nominale, pour une distribution de courants de fuite jusqu'à 10 fois le courant de fuite nominal. Ceci aura pour conséquence une diminution importante du rendement de fabrication, car les fabricants vont écarter les composants de haute et basse fréquence ayant des courants de fuite importants.

<sup>&</sup>lt;sup>1</sup> CMP - Chemical Metal Polishing

Figure 10. L'impact du PV sur la fréquence et sur le courant de fuite ([12])

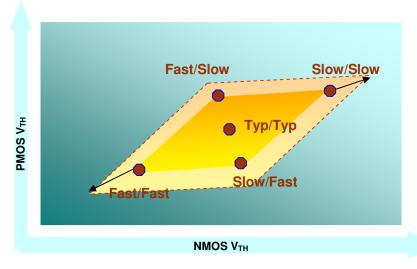

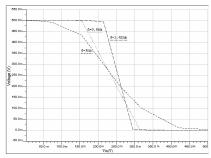

Les fondeurs fournissent généralement des valeurs différentes pour le fonctionnement des transistors NMOS et PMOS. Il s'agit des corners, fast/fast, slow/slow, fast/slow, slow/fast, et typical/typical (figure 11).

Figure 11. Types de caractérisations des composants

En principe, les composants conçus et fabriqués en « corner fast/fast » ont une fréquence de fonctionnement maximale, ayant donc les meilleures performances, mais ils consomment le plus, alors que les mêmes composants conçus en « corner slow/slow » consomment peu, mais leur fréquence maximale est aussi plus faible. Au delà de 65nm la variation des délais de chemins de propagation augmente considérablement, en augmentant ainsi « la distance » de fonctionnement entre le corner fast/fast et slow/slow (figure 11). Ce qui résulte en une distribution encore plus large des fréquences de fonctionnement et de puissance consommée. Par conséquent beaucoup de circuits ne respecteront pas les spécifications de

fréquence et de puissance ce qui aura donc un impact considérable sur le rendement de fabrication.

En technologie 32 nm il n'est plus possible de caractériser le comportement d'un circuit par des simulations « pire cas / meilleur cas » comme c'était le cas encore en 45nm. Les rendements technologiques deviendront nuls si des techniques spécifiques ne sont pas appliquées: Les approximations utilisées pour réaliser les dessins de masques à lithographie optique avec des géométries proches de la longueur d'onde de la lumière, combinées avec les incertitudes pendant la fabrication du composant feront que des nombreux transistors sur la puce ne sont pas fonctionnels du tout.

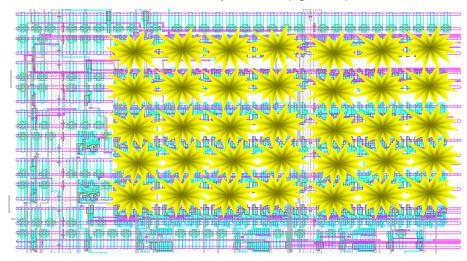

Des techniques de layout régulier s'imposent comme méthodologie de conception, ceci pas seulement pour des raisons de réduction du PV, crosstalks mais également pour répartir uniformément les zones de forte densité de puissance (figure 12).

Figure 12. Densité de puissance sur un layout régulier (source P Gelsinger, Intel [12])

#### 1.2.4. Vieillissement des transistors induit par NBTI

Le vieillissement des transistors par l'effet de type NBTI (Negative Bias Temperature Instability) est un phénomène qui a pour conséquence une diminution progressive du courant direct des transistors, particulièrement aux PMOS, de la tension de seuil des transistors. Les délais de commutation des portes augmentent, conduisant donc à une augmentation du temps de propagation des chemins. Ce phénomène est bien connu depuis longtemps par les ingénieurs spécialistes du processus de fabrication. Les nouvelles technologies apportent une recrudescence de ce phénomène, et aujourd'hui pour les technologies au delà de 90nm on estime que chaque dizaine d'années d'opération se traduit par 15-25% d'augmentation du temps de propagation des portes [6]. Ce phénomène est à

son tour générateur des fautes de délai en fonctionnement normal. Des mesures de détection et correction de ce problème commencent à voir le jour [16].

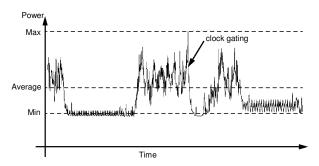

#### 1.2.5. Les techniques de réduction de la puissance

Afin de réduire la puissance consommée, dynamique ou statique, plusieurs techniques ont vu le jour, et ceci depuis quelques années déjà. Les plus connues et les plus employées sont les techniques de type « Clock gating » pour la réduction de la puissance dynamique et l'utilisation du « sleep transistor » pour la réduction de la puissance statique. Les deux techniques donnent des bons résultats permettant une diminution significative de la puissance consommée.

SL VDD sleep control transistor

VDDV

LOW-Vth MOSFET

VSSV

SL VSSV

sleep control transistor

VSSV

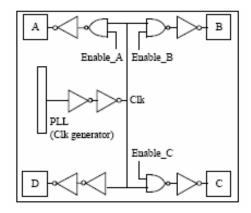

Figure 13. Technique « Clock Gating »

Figure 14. Technique « Sleep Transistor »

Malheureusement les deux techniques induisent à leur tour des phénomènes parasites dans le circuit. La technique « clock gating » provoque un bruit supplémentaire sur les rails d'alimentation. La technique « sleep transistor », qui consiste en la coupure ou la réduction de l'alimentation d'une partie d'un circuit à un  $V_{DD}$  min (surtout s'il n'est pas en activité, ou bien s'il est en mode de fonctionnement de faible vitesse) entraı̂ne un ralentissement des cellules y compris en mode de fonctionnement normal induisant une vulnérabilité supplémentaire aux fautes de délai.

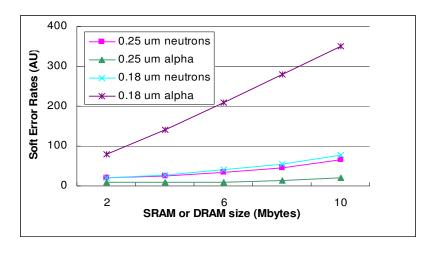

#### 1.2.6. Effets des particules ionisantes et des neutrons atmosphériques

Les technologies nanométriques avancées sont susceptibles de subir une augmentation importante du taux d'erreurs soft de type "SEU" - inversions de bits dans les points mémoires d'un circuit occasionnées suite à l'ionisation directe ou indirecte résultant de l'impact d'une particule énergétique (telles que les particules alpha et les neutrons atmosphériques) avec les zones sensibles du circuit, par les particules ionisantes ou

« SET » (impulsions transitoires induites par les particules ionisantes et les neutrons atmosphériques).

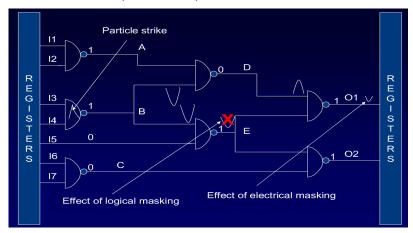

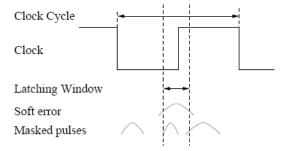

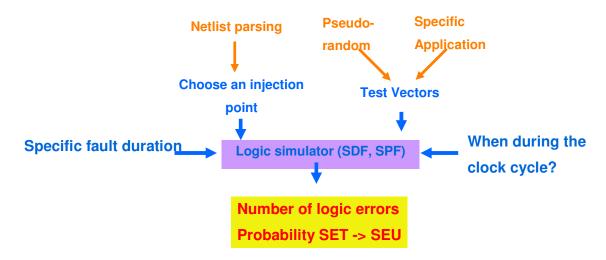

Le phénomène de fautes transitoires (SET et SEUs) produites par les particules ionisantes représentait un problème pour les circuits intégrés utilisés dans les environnements sévères, tels que le spatial ou les réacteurs nucléaires. De plus, seuls les circuits de mémorisation étaient supposés sensibles. Malheureusement, la miniaturisation reporte les problèmes des erreurs soft sur toutes les parties d'un circuit intégré (mémoires, latches, portes logiques) et ceci même en environnement terrestre naturel. La cause est la réduction du niveau de l'alimentation V<sub>DD</sub>, et des dimensions des dispositifs, qui se traduisent en une diminution des capacités des nœuds d'un circuit. Ainsi, la charge stockée sur un nœud (Q=C\*VDD) étant doublement affectée, l'inversion du niveau logique nécessitera une charge collectée sensiblement plus faible. Une augmentation de la sensibilité aux SEU est observée dans les circuits de mémorisation. Cependant, les parties combinatoires considérées dans le passé pratiquement insensibles sont maintenant aussi affectées. Outre la réduction de la charge stockée dans les nœuds d'un circuit logique, il existe deux autres facteurs qui affectent la sensibilité des parties logiques. A cause de la miniaturisation, la durée de commutation d'une porte logique T<sub>I</sub> devient inférieure à la durée de l'impulsion transitoire D<sub>TR</sub> induite par l'impact des particules (pouvant aller jusqu'à quelques centaines de picosecondes). La conséquence est que ces impulsions ne sont plus filtrées par les portes logiques et vont se propager, sans aucune atténuation dans les réseaux de portes logiques, jusqu'aux sorties du circuit où elles peuvent être capturées par les bascules de sortie. Une impulsion est capturée par les bascules, si son instant d'arrivée à son entrée coïncide avec le front actif de l'horloge. Alors, la probabilité de capturer une impulsion d'une durée donnée augmente proportionnellement à la fréquence d'horloge.

L'étude publiée par Tezzaron [1] met en évidence que les mémoires sont très sensibles à ces phénomènes. En faisant une moyenne du taux de défaillances dues à l'impact des particules sur un grand nombre des résultats publiés, il en résulte que pour les mémoires « modernes », le taux de SER¹ (Single Event Rate ou taux d'erreurs logiques) par unité de temps) à Mbit pourrait être considéré entre 1000 et 5000 FIT² (Failures in Time, 1 FIT équivaut à une défaillance tous les 109 h par composant). La même étude démontre une augmentation du nombre d'erreurs de façon exponentielle avec la réduction de V<sub>DD</sub>. Par ailleurs, cette réduction a une influence bien plus importante que la miniaturisation géométrique, car elle contribue à hauteur de 75% à l'augmentation de la sensibilité aux SEUs pour la même surface de circuit.

<sup>&</sup>lt;sup>1</sup> SER – Single Error Rate

<sup>&</sup>lt;sup>2</sup> FIT – Failure in Time

Pour conclure sur cette partie, les phénomènes évoqués plus haut peuvent se manifester comme des fautes transitoires ou intermittentes conduisant à leur tour à des erreurs logiques ou de timing si leur propagation conduit vers une bascule ou s'ils apparaissent sur le chemin critique ou sous critique d'un circuit.

L'augmentation de la probabilité des fautes transitoires (quelque soit leur cause, externe ou interne) conduisant à des erreurs fonctionnelles et de délai, rend nécessaire leur détection et/ou leur tolérance dans un nombre croissant de circuits intégrés. Ces solutions existent déjà depuis fort longtemps dans la majorité des applications critiques (applications spatiales et systèmes à haute disponibilité, ...). Aujourd'hui, avec le grand intérêt pour les applications communicantes et à forte sécurité, ce besoin touche aussi des systèmes n'ayant pas traditionnellement mis en oeuvre ce type de techniques. Les solutions architecturelles actuelles basées sur des plateformes reconfigurables considérablement affectées par les erreurs de délais et plus généralement par le bruit interne et externe, rendant la communication si peu fiable, semblable à celles du début de l'ère Internet. Pour maintenir les niveaux de fiabilité, sécurité et disponibilité exigés par les utilisateurs, on peut s'attendre, dans les années qui viennent, à un déploiement massif des nouvelles techniques de tolérance aux fautes à faible coût dans tous les domaines de l'électronique mobile : ordinateurs portables, téléphones portables, agenda électronique, etc...

De telles applications étant cependant soumises à nombreuses contraintes de conception, des compromis devront être établis entre l'amélioration de fiabilité et l'éventuelle dégradation des autres paramètres (coût, consommation, fréquence de fonctionnement, ...).

Dans les années 1997-2001, dans une série des tables rondes organisées dans des conférences internationales IEEE (ITC, DATE, VTS, FTCS28), publiées également dans des revues scientifiques (deux tables rondes dans IEEE Design & Test of Computers) et dans des articles présentés dans des conférences IEEE du domaine (DATE, VTS), les chercheurs du groupe de recherche RIS du laboratoire TIMA et moi-même (à l'époque en début de thèse de doctorat), étions les premiers à prédire que les techniques de tolérance aux fautes à faible coût devraient être adoptées dans les années à venir dans la conception des circuits destinés à des applications terrestres commerciales. La raison evoquée était le besoin de l'amélioration de la fiabilité des composants microélectroniques, considerablement affectée par le rapprochement des limites ultimes des technologies des circuits intégrés CMOS ainsi que l'amélioration des rendements de fabrication. Suite à ces prédictions, nous avons été parmi les premiers à initier la recherche de telles solutions. Les travaux que j'ai entrepris dans le cadre de ma thèse de doctorat concernent le développement des techniques de tolérance aux fautes au niveau du bloc fonctionnel,

nécessitant un faible coût matériel et une faible dégradation de la vitesse. Ces techniques ont été ensuite industrialisées lors de la création de la société IRoC Technologies, une start-up du laboratoire TIMA, mais elles ont aussi été reprises et adaptées/optimisées par deux de grands acteurs de l'industrie des semi-conducteurs, les compagnies Intel [14] et ARM [13], ainsi que par des industriels du domaine aéronautique et spatial [15].

#### 1.2.7 Défauts permanents

Dans la course vers la miniaturisation et vers la réduction de la puissance consommée, les nouvelles technologies s'orientent vers l'utilisation des nouvelles structures de transistors (transistors à grille multiple, ou à grille métallique, etc...), des procédés de fabrication changés ou améliorés (utilisation du SOI et du silicium étiré), ou bien l'introduction de nouveaux matériaux d'isolation (diélectrique HiK). L'utilisation de ces procédés à grande échelle passe à nouveau par une phase d'augmentation du nombre de défauts permanents. Ceci, couplé à la complexité des circuits, nous amène à la réalité suivante : nous nous trouvons aujourd'hui devant l'incapacité de produire des programmes de test courts assurant une couverture satisfaisante pour tous les types de défauts engendrés. De plus, l'identification de ces défauts nécessite des temps de calcul ATPG ainsi que les temps de test effectifs irréalistes.

Des approches de tolérance aux défauts de fabrication en ligne seront envisagés, ayant à la base des mécanismes d'auto-détection et auto-reconfiguration, à faible coût d'implémentation. Dans les années 2000-2004 j'ai été impliquée dans le projet européen IST FRACTURE qui a eu pour but de proposer des techniques de réparation intégrée pour des technologies à grande densité de défauts, notamment les technologies du silicium ultimes et les nanotechnologies, que je présente par la suite. Plusieurs articles de ont été publiés dans des conférences et journaux, témoignant mon implication dans ce domaine.

### 1.3. Défis des Nanotechnologies

La poursuite de la miniaturisation dans les technologies microélectroniques, facteur principal de la « révolution » informatique, atteindra d'après les prédictions ses limites ultimes aux alentours de l'an 2015. Les raisons sont aussi bien techniques (courant de fuite, intégrité du signal, échauffement du à la dissipation de puissance, capacités de stockage, …), qu'économiques (coût des chaînes de fabrication, estimées à plusieurs dizaines de milliards de dollars pour l'an 2010). Même en atteignant ces limites de miniaturisation (aux alentours de 50 nm de largeur de canal), l'efficacité énergétique du calcul restera de 9 ordres de grandeur inférieur à la limite thermodynamique (3 x 10<sup>18</sup> additions par Joule en température

ambiante). Le rapprochement à un tel niveau d'efficacité permettra une augmentation extraordinaire de la puissance de calcul.

Des efforts considérables sont investis au sein de grands groupes de recherche académiques et industriels du monde entier afin de mettre en place et développer les technologies qui remplaceront les technologies à base des transistors MOS. Des alternatives à faible coût pointent à l'horizon avec la sophistication rapide des procédés de synthèse chimique des composants électroniques et de leurs interconnections, afin de créer des systèmes très complexes et à faible coût. Même si la plupart des nouvelles solutions à base de nanotechnologies (e.g., composants à un électron [22][23], automates cellulaires quantiques, nanotubes de carbone [24], composants moléculaires, semiconductor nanowires [25], chemically assembled electronic nanocomputers (CAEN) [26][27]) sont encore dans le domaine de la recherche, des améliorations significatives se sont produites quant à l'assemblage de ces composants en portes logiques et matrices de mémoires [28] afin de produire des systèmes de calcul beaucoup plus puissants que ce que nous sommes capables de produire en CMOS, ayant une puissance consommée beaucoup plus faible, et une vitesse de fonctionnement plus élevée. Il est prévu que ces systèmes vont intégrer des trillions de composants dans des réseaux homogènes, réguliers, ayant une structure de réseau programmable [28].

Par contre, pour une telle densité d'intégration, les systèmes de calcul doivent pouvoir fonctionner en dépit des instabilités des composants infiniment petits et des imperfections du processus de fabrication. Les fautes permanentes qui peuvent survenir sont intimement liées au processus de fabrication d'un certain composant. Des processus de fabrications différents vont générer des densités de défauts différentes. Par exemple, si les composants ainsi que leurs interconnections sont fabriqués par la synthèse chimique, la densité de défauts pourrait être très importante. D'autre part, les fautes transitoires provoquées par l'environnement physique et par les conditions d'opération de ces composants ne sont pas nécessairement liées au processus de fabrication mais pourront être à leur tour en nombre très important. Les architectures nanoélectroniques du futur doivent être capables de tolérer un nombre extrêmement élevé de défauts de fabrication et de fautes transitoires. Aujourd'hui il n'y a pas de composants nanoélectroniques qui s'imposent et qui pourraient être adoptés sans hésitation afin de remplacer les technologies de silicium et de continuer la production de systèmes de calcul complexes, et par conséquent nous ne connaissons pas non plus toutes les causes des fautes transitoires et permanentes. Même si des recherches récentes ont montré la faisabilité des structures et circuits simples à base de

nanotechnologies, beaucoup de débats existent de nos jours sur l'adoption des meilleures nanotechnologies pour les nano processeurs du futur.

Pour la plupart de solutions proposées dans la littérature, la densité de défauts prédite pourrait être aussi élevée que 10<sup>-2</sup> défaillances/Mbit ce qui signifie qu'à une échelle de matrice régulière d'éléments de type mémorisation, elle pourrait être aussi élevée que quelques cellules de mémoire défaillantes pour chaque 100 cellules de mémoire.

La conception d'architectures tolérant les défauts pour les nanotechnologies est par conséquent inévitable. De la même façon des outils de conception et de validation pour des structures à base de ces nanotechnologies doivent être mis en place afin de permettre la conception de systèmes complexes sans ruptures au niveau des méthodologies de conception.

En plus de cette évidence d'autres questions apparaissent :

- Comment adapter à ces nouvelles technologies les méthodes de conception et les outils d'aujourd'hui?

- Comment réaliser des systèmes complexes fiables à partir des composants avec un comportement fortement probabiliste ?

- Quelle est la meilleure architecture pour organiser ces composants? Faudrait-il utiliser des architectures synchrones ou asynchrones, avec des mémoires et de la logique combinatoire, ou seulement avec des mémoires, ou bien seulement avec des matrices de primitives...? Les modèles d'application ainsi que les outils de synthèse devront être revus?

Dans ce contexte, nous avons débuté en 2004 (grâce à la participation au projet ACI Nanosys) une étude de faisabilité d'architectures complexes à base de CNTFET, en prenant en compte la très faible fiabilité de ces dispositifs. Nous avons commencé par une étude de fonctionnalité de transistors CNTFET, en prenant en compte des modèles compatibles SPICE, créés par des centres de recherche partenaires du projet à l'aide de langages de modélisation HDL, ensuite nous nous sommes concentrés sur l'étude du comportement des portes logiques à base de ces transistors en analysant leurs caractéristiques en présence de fautes permanentes et transitoires, et enfin nous nous sommes concentrés sur des techniques de tolérance aux fautes matérielles à faible coût pour ces portes. Dans le futur proche, nos recherches s'orienteront vers la proposition d'outils d'analyse de fiabilité basés sur l'injection de fautes, et d'outils de conception de systèmes complexes ciblant des structures régulières.

# Chapitre 2 Techniques de tolérance aux fautes dans les CMOS ultimes et nanoélectronique

Face à l'augmentation importante du nombre de fautes transitoires et permanentes pouvant conduire à des erreurs de timing et d'application tel qu'il a été décrit au premier chapitre, nous nous attachons à développer des techniques de tolérance aux fautes. Ce travail est divisé en plusieurs parties. Tout d'abord nous allons présenter les solutions de tolérance aux fautes visant les fautes transitoires, suivi par les techniques d'auto-détection et auto-réparation ciblant les défauts de fabrication, capables de couvrir des fautes multiples, quelles que soient leur origines, plutôt destinées aux futures nanotechnologies à densité de défauts plus élevé.

## 2.1. Techniques de tolérance aux fautes transitoires et de délai dans les CMOS ultimes

Les techniques traditionnelles de tolérance aux fautes destinées aux applications critiques utilisées dès le début de l'ère informatique ont pour base la triplication, appelée aussi TMR (Triple Modular Redundancy). Elles sont très coûteuses en surface et en puissance consommée et généralement inacceptables en tant que telles pour les applications à faible valeur ajoutée, tels que celles utilisées dans les systèmes grand public. D'autres techniques classiques sont implémentées autour des mémoires et consistent généralement en des codes ECC (Error Correcting Codes) eux aussi assez coûteux.

Des solutions à moindre coût doivent donc être envisagées, comme par exemple les techniques basées sur le durcissement local d'une zone sensible (par « sizing »), ou au niveau micro architecture en utilisant le filtrage des fautes transitoires, ou les codes détecteurs/correcteurs d'erreurs à faible coût, ou bien des techniques multi-niveaux combinant la détection d'erreurs avec le recouvrement souvent implémenté à un autre niveau d'abstraction (micro architecture ou même logiciel), ou mieux encore au niveau architecture en utilisant une reconfiguration qui remplace des parties défaillantes par des parties redondantes.

Depuis peu de temps, la plupart des applications de type microprocesseur contiennent des mécanismes de détection de fautes transitoires, implémentés en particulier dans les mémoires externes, cache, ou le banc de registres. D'autres applications, surtout les plus critiques, vont vers un durcissement de certaines bascules faisant partie des composants effectuant des tâches critiques, ou de quasiment toutes les bascules et circuits combinatoires, en plus des mémoires. C'est le cas des composants ASIC mais aussi des éléments de type CLB des composants programmables de type FPGA.

Dans la suite du document, je présente les résultats les plus significatifs dans ce domaine concernant à la fois les techniques de tolérance aux fautes basées sur la correction immédiate de fautes transitoires ou sur une combinaison de détection et reprise pour les technologies nanométriques CMOS. Elles seront suivies par des techniques de réparation et de tolérance aux fautes plutôt adaptées aux technologies post-CMOS.

## 2.1.1. Techniques de tolérance aux fautes transitoires et de délai au niveau bloc fonctionnel

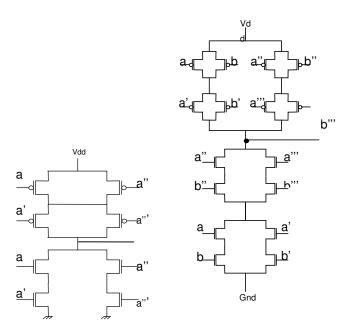

#### 2.1.1.1. Tolérance aux fautes matérielles par l'utilisation du C-element

Nous avons tout d'abord étudié une technique de tolérance aux fautes dont le coût matériel est similaire au coût des techniques classiques de détection d'erreurs en proposant une approche capable de tolérer les fautes transitoires et les bit-flips affectant les bascules. Les mêmes techniques permettent de tolérer les fautes transitoires et de délai dans les circuits combinatoires se situant en amont et capturées par les bascules.

#### Cette approche est basée sur l'observation suivante :

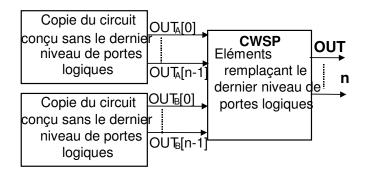

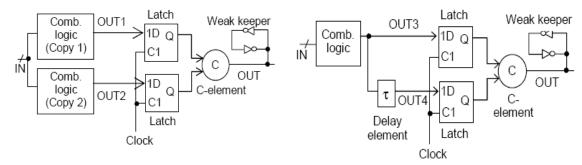

Généralement, une technique de détection d'erreurs permet de distinguer les sorties correctes d'un circuit des sorties erronées. Etant donné que, pour les fautes transitoires ou délai, les sorties d'un circuit sont erronées pendant une période limitée de temps, tandis que pour le reste du temps elles prennent les valeurs correctes respectives, il suffirait de n'observer et n'utiliser que les sorties correctes du circuit, ce qui semblerait trivial. Pour mettre cette idée en pratique, nous avons placé aux sorties d'un circuit dupliqué des portes spécifiques (nommées CWSP¹) recevant des entrées dupliquées (voir figure 2.1).

-

<sup>&</sup>lt;sup>1</sup> CWSP - Code Word State Preserving Element, connu en logique dynamique sous le nom de C-element

Figure 2.1. Circuit tolérant les perturbations basé sur la duplication

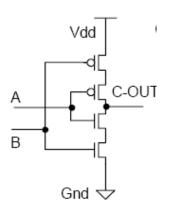

L'élément CWSP est en effet une porte dont le but est de produire une sortie en haute impédance si ses entrées ne sont pas identiques (figure 2.2 qui présente le cas d'une porte dynamique de type inverseur).

Ces portes peuvent être facilement obtenues en dupliquant les transistors d'une porte standard. Dans le cas d'un inverseur cette transformation donne la porte connue sous l'appellation de "C-element" (figure 2.2). Le tableau de vérité de cette porte est présenté dans le tableau 2.1.

| Α | В | C-OUT             |  |

|---|---|-------------------|--|

| 0 | 0 | 1                 |  |

| 1 | 1 | 0                 |  |

| 0 | 1 | Valeur précédente |  |

|   |   | mémorisée         |  |

| 1 | 0 | Valeur précédente |  |

|   |   | mémorisée         |  |

Figure 2.2. C-element en inverseur simple

Tableau 2.1 Tableau de vérité du C-élement

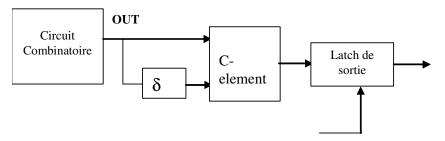

Le résultat est un circuit tolérant aux fautes, mais ayant un coût égal à la duplication au lieu de la triplication, dans le cas du TMR. Afin de réduire le coût matériel de cette technique, nous avons remplacé les signaux produits par deux blocs dupliqués par des signaux produits par le même bloc mais dé-corrélés dans le temps (voir figure 2.3.). La décorrélation temporelle étant obtenue en utilisant des éléments de délai, le coût matériel devient beaucoup plus faible que dans le cas de la duplication.

Figure 2.3. Tolérance aux fautes à l'aide du C element - réduction du coût d'implémentation

Cette réduction du coût matériel est obtenue au détriment d'une augmentation de la période d'échantillonnage de la sortie OUT ou quasiment de la période de l'horloge égale cette foisci à  $2D_{TR}$ . Nous avons noté avec  $D_{TR}$  la durée de l'impulsion transitoire qu'on se propose de tolérer, étant mesurée à un seuil fixé de  $V_{DD}/2$ . Selon les expérimentations que nous avons effectuées, il en résulte que cette réduction est modérée (au maximum 10%).

A titre d'exemple, dans le cas d'un multiplieur Booth Walace 32 bits implémenté en technologie CMOS 0.35 μm, le coût en surface de cette technique est de 2.4 %, tandis que le ralentissement de la vitesse de fonctionnement est de 6.5 % (en considérant des fautes transitoires d'une durée de 450 picosecondes). Dans le cas d'un additionneur Brent et Kung 32bits, nous aurons pour la même technologie et la même impulsion transitoire un coût en surface de 21.2 % et un ralentissement de la vitesse de 19.4%.

Cette approche a été reprise en 2005 par Intel, voir figure 2.4 et 2.5 dans [14], en exploitant les bascules dupliquées déjà existantes dans les circuits (chaînes de bascules du type "scan-path" nécessaires pour le test de fabrication et le diagnostic), afin de protéger un certain nombre de bascules des processeurs Itanium de chez Intel contre les « erreurs soft ».

Figure 2.4 C element et la duplication du circuit

Figure 2.5 C element dans une implémentation à moindre coût

La même idée d'implémentation a été utilisée en avril 2007 [16] pour créer des circuits de détection et la tolérance en ligne de délais provoqués par le vieillissement de transistors à cause de l'effet NBTI.

Ces travaux sont présentés en détail dans mon manuscrit de thèse et ont été publiés dans les conférences : 1999 IEEE VLSI Test Symposium (VTS 1999), 1999 IEEE International On-Line Testing Workshop (IOLTW 1999), 2000 Symposium on Integrated Circuits and Systems Design (SBCCI 2000).

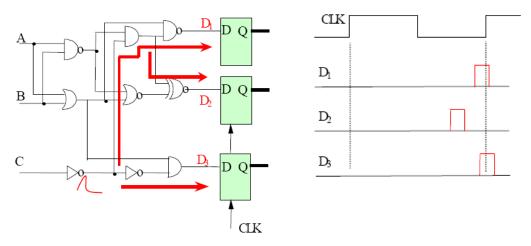

#### 2.1.1.2. Tolérance aux fautes HW/SW par la redondance temporelle

Les modules incluant les chemins critiques du circuit ne peuvent pas supporter les pertes de performance induites par les techniques précédentes. Pour ces modules rapides, d'autres techniques doivent être envisagées, en se basant sur la redondance temporelle au niveau de la détection des erreurs produites à la fois par les fautes transitoires et par les fautes de timing.

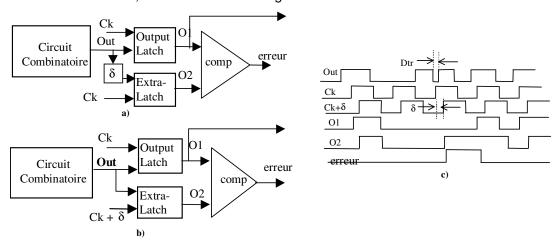

L'approche utilisée exploite à nouveau la redondance temporelle en ciblant non seulement les fautes transitoires et les fautes de "timing" dans les circuits combinatoires, mais aussi les transitoires et les bit filps dans les bascules. La redondance temporelle est implémentée au niveau des bascules, comme le montre la figure 2.6.

Figure 2.6. a), b) – Schéma de détection de fautes transitoires utilisant un latch supplémentaire et un comparateur; 1c) Schéma de détection des fautes transitoires correspondant à l'implémentation b).

Les avantages de cette approche sont : un faible coût en surface, car elle ne comporte que'une duplication des bascules et un comparateur final, et un impact négligeable sur la

vitesse de fonctionnement, car la bascule dupliquée capture les sorties du circuit combinatoire après que les entrées de ce circuit sont changées mais avant que ce changement soit propagé jusqu'aux sorties de ce circuit. La bascule qui capture la sortie O est régie par une horloge dont la fréquence est la même que dans le cas d'un circuit sans protection. De cette façon, il n'y a pas besoin de diminuer la vitesse de fonctionnement.

Ces techniques nécessitent un faible surcoût matériel et n'entraînent aucune perte de vitesse. A titre d'exemple, dans le cas d'un multiplier Booth Wallace 32 bits implémenté en technologie CMOS 0.35 micron, le coût matériel de cette technique est de 1.3 %, tandis que le ralentissement de la vitesse de fonctionnement est nul.

Il est à noter que ces techniques de détection HW pourraient être combinées avec des procédures de recouvrement afin de corriger les fautes transitoires ou de délai. Ces techniques de recouvrement peuvent être implémentées localement en HW pur ou bien en SW au niveau système (avec les tâches de validation qui s'imposent).

Ces travaux sont aussi décrits en détail dans mon manuscrit de thèse et ont été présentés dans les conférences : 1999 IEEE International On-Line Testing Workshop (IOLTW 1999), 2000 Symposium on Integrated Circuits and Systems Design (SBCCI 2000) et 2000 Design Automation and Test in Europe (DATE 2000), recevant le prix du meilleur papier dans la section test.

Ces techniques de détection de fautes ont été utilisées pour la création d'un processeur durci SPARC sur 32 bits Leon (CoolRisc) et ont fait l'objet d'un transfert technologique vers la société iRoC Technologies en 2001.

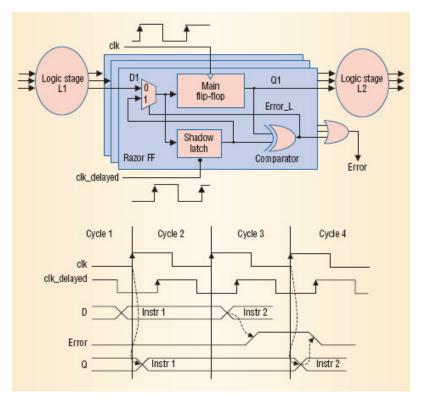

Cette même approche a été utilisée récemment par la société ARM [13] dans le développement de l'architecture RAZOR, capable de détecter et corriger les fautes temporelles. Les architectes d'ARM en collaboration avec l'université de Michigan ont entre autres démontré que cette architecture peut être exploitée pour réduire la consommation d'un circuit jusqu'à 44% par rapport à un circuit standard (figure 2.7). Cette réduction a été obtenue en diminuant la tension d'alimentation et en détectant et corrigeant les erreurs de "timing" dues à l'augmentation des délais du circuit induites par cette diminution. ARM fait actuellement une promotion très active de cette approche dans sa politique de communication concernant la fiabilité de ses futurs processeurs.

Figure 2.7 Technique « Razor » de correction de fautes de timing

Des nouvelles techniques de détection de fautes transitoires et de délais dérivant de celles qui ont été présentées précédemment sont aujourd'hui en cours d'étude dans notre groupe de recherche au laboratoire TIMA. Ces techniques sont des version optimisées en puissance consommée ainsi qu'en impact sur la vitesse, et plus adaptées aux besoin du moment. Elles ont été proposées dans un projet ANR « FARE » (Appel d'offre Architectures du Futur 2007).

#### 2.1.1.3. Tolérance aux fautes par durcissement des latches

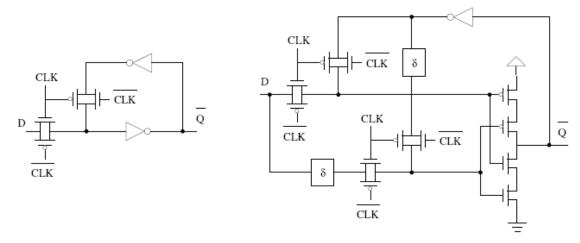

Des techniques de transformation des bascules en éléments insensibles aux délais et aux fautes transitoires internes ou venant de l'extérieur, ont fait l'objet d'une attention particulière dans notre groupe de recherche. Pour ce faire nous avons exploité les avantages du C-élement, décrit précédemment, en utilisant ce circuit à l'intérieur d'un latch D combiné avec des blocs de délai (voir figure 2.8).

Figure 2.8. Latch D simple et latch D durci par l'utilisation du C élement

Cette structure présente une très bonne robustesse aux fautes transitoires d'une durée pouvant atteindre jusqu'à 500 ps avec un coût d'implémentation raisonnable, beaucoup plus faible que la triplication. Par exemple dans le cas d'un processeur MIPS, ce surcoût matériel est de 58%. Ces travaux se sont poursuivis dans le cadre de la thèse de Cristiano Lazzari, et ont fait l'objet de deux publications dans les conférences IEEE LATW et IEEE IOLTS en 2004. D'autres approches de durcissement des points de mémorisation sont en cours dans notre groupe de recherche. Deux stagiaires ont été encadrés en 2006 sur ces travaux de recherche pendant leur stage d'ingénieur. Ces nouvelles techniques utilisent les courants de fuite pour transformer des bascules standard en bascules durcies, sans augmenter le nombre des transistors de la cellule. Ainsi la nouvelle cellule durcie est plus compacte que la meilleure solution connue (DICE), qui était elle le résultat des travaux de recherche du groupe RIS du laboratoire TIMA.

#### 2.1.1.4 Tolérance aux fautes transitoires sur des matrices de mémoire

Mes travaux de recherche sur la tolérance aux fautes ont compris aussi un séjour de 3 mois au sein de la compagnie Intel, à Santa Clara, CA, USA pendant l'été 2005. Lors de ce séjour j'ai eu l'opportunité de travailler sur l'analyse et l'implémentation de codes optimaux de détection et correction de fautes sur des mémoires de faible taille (register files) de deux architectures radicalement différentes (Itanium et Pentium M), sous contraintes de consommation statique.

## 2.2. Analyse des circuits auto-contrôlables face aux fautes temporelles et à niveaux indéterminés

Un nombre significatif d'implémentations de circuits auto-contrôlables a été proposé dans le passé et ces implémentations offrent 100 % de détection dans le cas de fautes de collage logique. Dans l'étude que nous avons menée le but était de pouvoir utiliser ces circuits pour la détection en ligne de fautes transitoires et de fautes de timing, mais aussi pour la détection en ligne de fautes qui impliquent des valeurs logiques indéterminées sur le site d'occurrence de la faute. Il s'agissait donc de déterminer l'efficacité des implémentations existantes des circuits auto-contrôlables en présence de ces fautes. On a démontré que ces implémentations s'avèrent moins efficaces pour les fautes considérées, prédominantes dans les technologies CMOS ultimes. Afin de pouvoir évaluer l'efficacité de ces circuits face à ces fautes, nous avons développé un modèle de fautes généralisant le modèle de collage logique. En utilisant ce modèle comme outil d'analyse, nous avons formalisé la plus large classe de circuits 'sûrs en présence de fautes' qui préserve cette propriété face aux modèles de fautes prédominants dans les technologies submicroniques avancées, appelé circuits 'à chemins sensibilisés sûrs'. Pour les circuits 'sûrs en présence de fautes' qui ne font pas partie de cette classe, l'efficacité de détection peut être compromise. Plusieurs solutions de remplacement des redondances inefficaces ont été proposées dans le cadre de ma thèse de doctorat, offrant ainsi une meilleure efficacité de détection par rapport aux circuits sûrs en présence de fautes logiques, et ceci à moindre coût matériel.

Les résultats de ce travail, formalisés dans une série des théorèmes, ont abouti à l'analyse la plus générale du comportement des circuits auto-contrôlables face aux fautes prédominantes dans les technologies submicroniques avancées. Elles ont par ailleurs abouti à des solutions de détection concurrentielle d'erreurs en ligne efficaces pour ces technologies. Ces travaux ont été présentés dans la conférence IEEE VLSI Test Symposium 2000 (VTS2000). Une extension de ces travaux est en cours et a fait l'objet d'un stage Mastère Recherche en 2005-2006 et vise l'étude du comportement des circuits auto-contrôlables en technologie 90nm et une comparaison avec les technologies de l'état de l'art.

### 2.3. Tolérance aux fautes dans la nano-électronique

Tout en poursuivant nos travaux dans le domaine de la tolérance aux fautes temporaires, nous les avons étendus au domaine de la tolérance aux fautes pour des technologies à hautes densités de défauts. Ces travaux visent le domaine des CMOS ultimes,

concernant les fautes permanentes et plus particulièrement les nanotechnologies.

#### 2.3.1. Nanoélectronique - Technologie à très grande densité de défauts

Des efforts considérables sont consentis au sein des grands groupes académiques et industriels de recherche du monde entier afin de mettre en place et développer les technologies qui remplaceront les technologies du silicium MOS arrivant aux limites ultimes aux alentours des années 2015. Un certain nombre de solutions commencent à apparaître, mais qui sont encore dans le domaine de la recherche, grâce aux améliorations significatives produites au niveau de l'assemblage de ces composants en portes logiques et matrices de mémoires [28] afin de produire des systèmes de calcul beaucoup plus puissant que ceux que nous sommes capable de produire en CMOS, avec une puissance consommée beaucoup plus faible, et une vitesse de fonctionnement plus élevée. Il est prévu que ces systèmes vont intégrer des centaines de milliards de composants dans des réseaux homogènes, régulières, ayant une structure de réseau programmable. [28]

Nous avons évoqué dans le premier chapitre la grande densité de défauts qui est annoncée pour ces technologies. La conception des architectures tolérant les défauts pour les nanotechnologies est par conséquent inévitable. La tâche est d'ampleur car, à cause des concentrations de défauts élevées (par exemple, 35 % des dispositifs défaillants, prévu par ITRS ou bien plus d'un ordre de grandeur pour des les cellules mémoire par rapport à la densité de défauts d'aujourd'hui), les défauts affecteront aussi bien les parties fonctionnelles que les parties redondantes. Elles invalident de cette façon un principe de base des techniques de tolérance aux fautes qui considère que les défauts n'affectent pas les parties fonctionnelles et les parties redondantes en même temps.

Par conséquent, afin de pouvoir utiliser ces technologies dans des applications réelles, nous devrons disposer d'approches innovantes permettant de tolérer ou de réparer des densités des défauts très élevées. Dans ce contexte, un axe important des nos travaux concerne ce problème, dont les techniques les plus significatives de nos recherches seront brièvement présentées par la suite.

En partant de l'hypothèse que les structures à base de nanotechnolgies vont intégrer des trillions de composants dans des réseaux homogènes, régulièrs, ayant une structure de réseau programmable, nous avons développé un certain nombre de techniques que nous avons validé par la suite dans des technologies CMOS avancés sur des architectures de type mémoire. De la même façon, pour établir la validation et l'étude de l'efficacité des

techniques proposées nous avons considéré différentes sortes de fautes affectant la matrice des cellules de mémoire en partant des fautes de type collage à zéro et à un, circuit ouvert, court circuits, fautes unidirectionnelles, fautes transitoires, couplages, etc.

#### 2.3.2. Techniques d'auto-réparation à l'aide de BIST et BISR

#### a. BIST et BISR

Les dernières avancées dans le domaine des techniques de tolérance aux fautes pour les mémoires classiques développées en CMOS ultime se situent essentiellement au niveau de l'auto-test intégré ou Built-In Self Test (BIST). Le BIST est une technique dans laquelle la génération des vecteurs de test et l'analyse des résultats est effectuée à l'intérieur du circuit. Cette approche a l'avantage de se passer d'un équipement de test externe coûteux, de réduire le temps de test en exploitant les parallélismes structurels et fonctionnels qu'offrent les architectures BIST et permet enfin de tester les circuits à leur fréquence nominale. Ainsi, le test intégré permet la détection des mémoires défaillantes en phase de production ou durant leur fonctionnement normal. Mais au fur et à mesure que les densités de défauts augmentent, l'action de détection n'est plus suffisante si l'on veut maintenir des niveaux acceptables de rendement en production. Dans ce cas le test reste certes nécessaire pour détecter les défaillances, mais doit être suivi par une action de réparation.

La réparation des mémoires était traditionnellement contrôlée de l'extérieur en connectant les blocs de mémoires non défaillantes au bus des données en remplacement des blocs défaillants déconnectés (Hard Repair), à l'aide du laser ou en brûlant électriquement des fusibles (ou des anti-fusibles). Plusieurs désavantages sont liés à cette méthode. Premièrement, les composants utilisés ne font pas partie de la technologie standard CMOS, ce qui implique des coûts en surface importants. De plus, l'implémentation de ces composants de réparation contribue aussi à la baisse du rendement de production. Un autre inconvénient est que ce type de réparation ne peut être utilisée pour les mémoires embarquées à cause des problèmes d'observabilité et de contrôlabilité. Aussi, l'action de réparation ne peut être effectuée qu'une seule fois, généralement en phase de production, ce qui limite la fiabilité de la mémoire pendant le fonctionnement normal du système. Enfin, son coût est élevé, surtout lorsque les technologies laser sont employées.

La dernière avancée dans le domaine de la réparation mémoire, comme pour le cas du test, est l'auto réparation intégrée ou Built-In Self-Repair (BISR). Le BISR est une technique qui est associée au BIST qui rajoute une étape de localisation des fautes, la

sélection des unités redondantes en cas de reconfiguration pour le remplacement des unités défaillantes, et la connexion de ces unités redondantes au bus de données. L'utilisation du BISR est très adaptée aux mémoires embarquées à faible observabilité et contrôlabilité (à cause de l'accès limité). Elle est aussi intéressante pour éviter le coût résultant d'une reconfiguration basée sur l'utilisation du laser. Enfin, le BISR permet de corriger à la fois les défauts de fabrication et les défauts opérationnels puisqu'il peut être utilisé à tout moment pendant la vie du circuit.

Il existe cependant plusieurs contraintes qu'il faut prendre en considération lorsqu'on veut développer une solution BISR. Il faut veiller à réduire le plus possible le coût en surface du circuit de réparation, implémenter des algorithmes de réparation qui utilisent efficacement les ressources redondantes pour faire face à des distributions variées de fautes, minimiser l'impact sur le temps de l'accès à la matrice de cellules, réduire le temps globale de test/réparation et faciliter l'interfaçage avec le BIST. Plutôt que optimiser l'ensemble de ces exigences, la solution sera de trouver des compromis, entre l'efficacité de la réparation, le surcoût en surface, et la pénalité en vitesse.

#### b. Evaluation des techniques d'autoréparation intégré

Avant d'aller plus loin dans la présentation des diverses techniques de réparation intégrées que nous avons développées, nous parlerons d'une technique d'évaluation de l'efficacité de réparation que nous avons mise en place. L'évaluation de l'efficacité d'une technique de réparation est une démarche très importante, qui permet soit d'écarter ou d'améliorer une approche développée, soit tout simplement de la caractériser en fonction de différents paramètres (nombre d'unités redondantes utilisées, densités de défauts, ...).

Déterminer l'efficacité d'une technique de réparation en présence d'une certaine densité de défauts est un problème qui s'est souvent posé en termes de formalismes mathématiques. La difficulté d'une approche mathématique, réside dans le fait qu'il faut établir des équations analytiques qui reflètent le comportement de la technique de réparation cible. Ainsi, plus la technique de réparation est complexe et plus la recherche de ces équations est fastidieuse. De plus, la complexité de l'approche analytique ne dépend pas uniquement de l'algorithme de réparation mais aussi du modèle de distribution des fautes qu'on veut adopter, et qui ne manque pas d'être compliqué dès qu'on veut utiliser les distributions de fautes les plus réalistes.

Afin de s'affranchir de ces inconvénients, j'ai développé une recherche qui propose une approche de validation prédictive des fautes basée sur l'injection statistique de fautes et leur simulation. Cette approche est une alternative à l'élaboration de formules analytiques

difficiles à mettre en œuvre plus particulièrement pour les techniques de réparation complexes. Etant donné le nombre important de simulations à réaliser, nous avons construit un outil automatisé de validation, capable de tenir compte de la plupart des techniques de réparation et des types de redondances existantes dans l'industrie.

Deux types d'évaluations de l'efficacité ont été considérés, une évaluation au niveau de l'instance mémoire et une évaluation sur un ensemble de mémoires d'un même wafer. Pour cette dernière, des modèles d'amas de fautes ont été adoptés afin d'approcher le plus possible la réalité. Le modèle d'amas de fautes considère que si une cellule mémoire contient un défaut, la probabilité que ses voisines soient aussi défaillantes est plus élevée que la probabilité moyenne de défauts. C'est-à-dire que souvent les imprécisions du procédé de fabrication n'affectent pas une cellule isolée mais un voisinage de cellules. Ce modèle est implémenté dans le logiciel d'injection des fautes stochastiques en modifiant la probabilité de fautes induite par son voisinage. Ces modèles, ainsi que l'outil qui les implémente, sont présentés en détail dans le manuscrit de thèse de M. N Achouri et ont fait l'objet d'une collaboration avec la compagnie IRoC Technologies sur la durée du projet européen IST FRACTURE (2000-2004). L'outil a été ensuite utilisé pour la validation des techniques d'autoréparation que nous allons présenter par la suite.

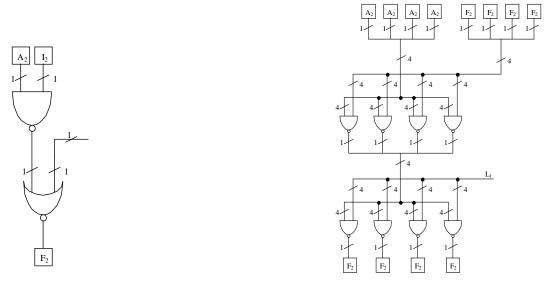

#### 2.3.2.1. Techniques d'auto-réparation au niveau de colonne/bit de données

Pour simplifier l'analyse du problème et optimiser le coût en surface, une première approche récursive a été proposée dans le cadre de la thèse de Nadir Achouri réalisée en collaboration avec la compagnie IRoC Technologies, permettant de reconfigurer les données de la mémoire quelque soit la distribution des fautes sur les parties régulières et/ou redondantes.

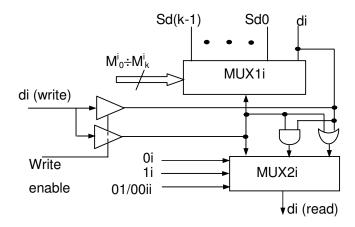

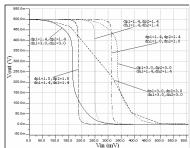

Afin d'améliorer l'efficacité de réparation de cette première approche, un mécanisme de reconfiguration dynamique a été envisagé, qui permet de sélectionner de plus petites tailles d'unités réparables sans modifier la structure de la mémoire (figure 2.9). Nous avons également élaboré des fonctions de reconfiguration capables de manipuler des colonnes redondantes singulières (sous ensemble d'une unité responsable de générer un bit de donnée) pour minimiser le coût dû aux ressources redondantes.

Figure 2.9. Schéma de principe d'auto-réparation au niveau colonne/bit de donnée

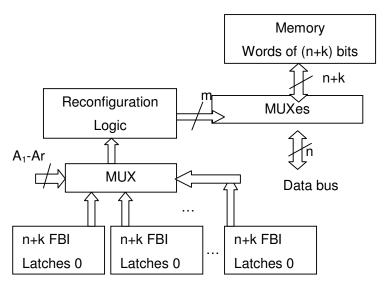

Dans le schéma donné dans la figure 2.9, pendant la phase de test BIST, on utilise r bits d'adressage ( $A_1$  à  $A_r$ ) afin de sélectionner l'ensemble des bascules contenant l'information d'erreur (nommées FBI dans la figure 2.9) correspondant à la colonne erronée pour chaque valeur d'adresse. Donc pour chacune des valeurs de  $R = 2^r$ , un ensemble différent de bascules stocke l'information d'éventuelle présence de fautes. Pendant l'opération normale du système, les adresses  $A_1$ ,  $A_2$ , ...,  $A_r$ , sont surveillées afin de déterminer quels blocs de bascules seront sélectionnés pour la reconfiguration de la mémoire.

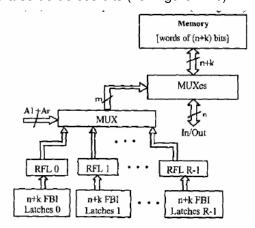

Dans un but d'augmentation de la vitesse, on peut utiliser la fonction de reconfiguration R fois (les blocs RFL<sub>0</sub>, RFL<sub>1</sub>, ... RFL  $_{R-1}$ ), et utiliser des multiplexeurs contrôlés par les bits d'adresses A<sub>1</sub>, A<sub>2</sub>, ..., A<sub>r</sub> à la sortie de ces bits (voir figure 2.10).

Figure 2.10 Schéma rapide de réparation dynamique

Dans ce dernier cas, le coût de la reconfiguration est un peu plus élevé car nous utilisons R blocs de reconfiguration au lieu d'un seul, le gain étant plus important en vitesse de

fonctionnement, car les entrées et les sorties des fonctions de reconfigurations sont fixées pendant la réparation.

Pour résumer, la version dynamique divise la mémoire en 2<sup>r</sup> parties qui peuvent être sélectionnées par une valeur spécifique des bits d'adresses r. Ces parties de mémoire sont réparées en connectant dynamiquement les bits erronés aux bits en réserve disponibles, en fonction de la distribution de fautes pour chaque partie de mémoire.

#### 2.3.2.3. Approches diversifiées d'auto-réparation

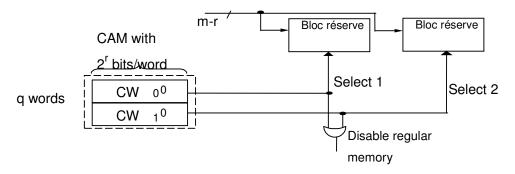

L'idée de base de cette approche consiste en l'utilisation d'une première technique de tolérance aux fautes pour réparer la plupart des défauts, puis l'utilisation d'une seconde technique pour réparer les défauts restants. Une telle approche distribue les ressources redondantes entre plusieurs techniques de tolérance aux fautes. A cause d'une telle organisation chaque technique de tolérance aux fautes disposera de moins de ressources redondantes pour le même nombre total de ressources redondantes. Sa justification est alors basée sur le fait qu'il faut réparer toutes les fautes affectant une mémoire sinon cette mémoire est déclarée non réparable. Considérons en effet une mémoire composée de plusieurs blocs. Une densité de défauts donnée résulte d'une distribution du nombre de défauts telle que seulement quelques blocs de la mémoire sont affectés par un nombre de défauts beaucoup plus élevé que la moyenne et donc beaucoup plus élevé que la plupart des blocs de la mémoire. Etant donné qu'on doit réparer toutes les parties de la mémoire et qu'on ne connaît pas à l'avance quels blocs vont être touchés par un grand nombre fautes, nous devons attribuer à chaque bloc une redondance suffisante afin d'effectuer la réparation avec succès. La situation devient critique lorsqu'on dispose d'un grand nombre de blocs mémoire, car cela va augmenter la probabilité d'avoir quelques blocs de mémoire avec un nombre de défauts beaucoup plus élevé que celui touchant la majorité des blocs. Dans ce cas, il sera plus efficace de disposer pour chaque bloc d'un niveau de redondance capable de réparer un nombre de défauts modéré, pour réparer ainsi la majorité des blocs, puis ajouter des redondances pour remplacer les quelques blocs affectés par un plus grand nombre de fautes. Nous avons développé trois types d'architectures de réparations basées sur ce principe. Il s'agit de l'autoréparation basée sur la polarité des erreurs, de l'autoréparation basée sur la combinaison colonne et bloc et sur l'utilisation des codes ECC et réparation ligne.

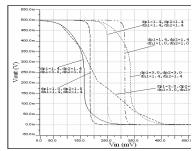

#### a. Autoréparation basée sur la polarité des erreurs

L'idée de base qui régit ces techniques est de combiner entre elles des unités défaillantes pour générer des unités fonctionnelles, au lieu de remplacer les unités

défaillantes par des unités correctes comme il a été question auparavant. Cette approche devrait mieux fonctionner dans le cas de très hautes densités de défauts dans lequel il est difficile de disposer d'unités non erronées. La combinaison est basée sur le fait que dans la majorité de situations, les cellules fautives ne vont pas occuper exactement les mêmes positions dans deux unités différentes. La difficulté d'appliquer un tel schéma de réparation réside dans la sélection des cellules correctes dans chaque unité. Une première technique utilise une approche basée sur les polarités d'erreurs produites à la sortie de chaque bloc mémoire en combinant les unités ayant la même polarité d'erreurs. Cette combinaison se fera à l'aide des fonctions de reconfiguration qui masquent une polarité d'erreur spécifique aux deux unités combinées.