### Mécanismes Matériels pour des TransfertsProcesseur Mémoire Sécurisés dans lesSystèmes Embarqués

Reouven Elbaz

### ▶ To cite this version:

Reouven Elbaz. Mécanismes Matériels pour des Transferts Processeur Mémoire Sécurisés dans les Systèmes Embarqués. Micro et nanotechnologies/Microélectronique. Université Montpellier II - Sciences et Techniques du Languedoc, 2006. Français. NNT: . tel-00142209

### HAL Id: tel-00142209 https://theses.hal.science/tel-00142209

Submitted on 17 Apr 2007

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# Universite Montpellier II Sciences et Techniques du Languedoc

### <u>THESE</u>

pour obtenir le grade de

#### DOCTEUR DE L'UNIVERSITE MONTPELLIER II

Discipline : Génie Informatique, Automatique et Traitement du Signal Formation Doctorale : Systèmes Automatiques et Microélectroniques Ecole Doctorale : Information, structures, Systèmes

présentée et soutenue publiquement

pai

#### Reouven ELBAZ

Le 12 Décembre 2006 à Montpellier

## Mécanismes Matériels pour des Transferts Processeur Mémoire Sécurisés dans les Systèmes Embarqués

## Hardware Mechanisms for Secured Processor-Memory Transactions in Embedded Systems

#### **JURY**

| M. Jean Claude Bajard, Professeur, Université de Montpellier II,                 | Président du jury  |

|----------------------------------------------------------------------------------|--------------------|

| M. Viktor Fischer, Professeur, Université de St Etienne,                         | Rapporteur         |

| M. Olivier Sentieys, Professeur, Université de Rennes I,                         | Rapporteur         |

| M. Joan Daemen, Docteur, Société STMicroelectronics,                             | Examinateur        |

| M. Pierre Guillemin, Société STMicroelectronics,                                 | Examinateur        |

| M. Jean Baptiste Rigaud, Maître de Conférence, Centre Microélectronique de Prove | ence, Examinateur  |

| M. Gilles Sassatelli, Chargé de Recherche CNRS, LIRMM – UMII,                    | Examinateur        |

| M. Lionel Torres, Professeur, Université de Montpellier II,                      | Directeur de Thèse |

# Universite Montpellier II Sciences et Techniques du Languedoc

### <u>THESE</u>

pour obtenir le grade de

#### DOCTEUR DE L'UNIVERSITE MONTPELLIER II

Discipline : Génie Informatique, Automatique et Traitement du Signal Formation Doctorale : Systèmes Automatiques et Microélectroniques Ecole Doctorale : Information, structures, Systèmes

présentée et soutenue publiquement

pai

### Reouven ELBAZ

Le 12 Décembre 2006 à Montpellier

## Mécanismes Matériels pour des Transferts Processeur Mémoire Sécurisés dans les Systèmes Embarqués

# Hardware Mechanisms for Secured Processor-Memory Transactions in Embedded Systems

#### **JURY**

| M. Jean Claude Bajard, Professeur, Université de Montpellier II,                 | Président du jury  |

|----------------------------------------------------------------------------------|--------------------|

| M. Viktor Fischer, Professeur, Université de St Etienne,                         | Rapporteur         |

| M. Olivier Sentieys, Professeur, Université de Rennes I,                         | Rapporteur         |

| M. Joan Daemen, Docteur, Société STMicroelectronics,                             | Examinateur        |

| M. Pierre Guillemin, Société STMicroelectronics,                                 | Examinateur        |

| M. Jean Baptiste Rigaud, Maître de Conférence, Centre Microélectronique de Prove | ence, Examinateur  |

| M. Gilles Sassatelli, Chargé de Recherche CNRS, LIRMM – UMII,                    | Examinateur        |

| M. Lionel Torres, Professeur, Université de Montpellier II                       | Directeur de Thèse |

A Tiffanie, à mes Parents, Et à ma Grand-mère Myriam,

### Remerciements

Je souhaite remercier en premier lieu « ma » Tiffanie, qui a su me supporter (dans tous les sens du terme) au cours de ces trois ans. Il n'y a pas de mots pour exprimer l'importance que tu as eu dans l'élaboration de ces travaux, et je ne parle même pas des heures passées sur des démonstrations mathématiques.

Ensuite mes remerciements vont à mes parents, Marie France et Haïm Elbaz, qui ont toujours su me témoigner leur amour inconditionnel, et bien évidemment à mes frères et sœurs, Shmouël, Yossi, Déborah, Tsyona et Meyer qui malgré la distance ont toujours marqué leur présence et leur soutien.

Ces travaux de thèse ont été réalisés dans le cadre d'un projet régional (PACA 2003-08) impliquant la société STMicroelectronics, le LIRMM (Laboratoire d'Informatique de Robotique et de Microélectronique de Montpellier) et le CMP (Centre Microélectronique de Provence – Ecole des Mines de St Etienne). Dans ce contexte, j'ai été amené à travailler avec de nombreuses personnes, j'espère ne pas en oublier.

Un immense merci à Pierre Guillemin qui au cours de ces trois ans a été mon responsable chez STMicroelectronics. Toujours présent, il n'a jamais économisé son temps et ses précieux conseils qui m'ont permis de poursuivre mes travaux de manière autonome. J'ai vraiment apprécié travailler à ses côtés et je vais regretter notre collaboration. Merci Pierre.

Je remercie également mon directeur de thèse, Lionel Torres, ainsi que Gilles Sassatelli du LIRMM qui ont su me faire confiance et me donner ma chance. Leurs encouragements et leurs remarques constructives m'ont permis de valoriser efficacement mes travaux. La bonne ambiance qui régnait lors de nos réunions a énormément contribué à ma motivation.

Ensuite, je remercie Michel Bardouillet de STMicroelectronics pour ces discussions particulières et animées qui m'ont amené à pousser ma réflexion toujours plus loin.

Merci à mon maître en design (et en jeux de mots), Albert Martinez de STMicroelectronics, qui a fait preuve d'une patience et d'une pédagogie époustouflante. Toujours disponible, j'ai énormément appris à ses côtés.

Je remercie également Claude Anguille de STMicroelectronics, avec qui j'ai travaillé durant la première année de thèse. Une année certes, mais durant laquelle il m'a beaucoup appris, en particulier concernant le travail d'équipe.

Je remercie le Professeur Viktor Fischer du Laboratoire Hubert Curien de St Etienne et le Professeur Olivier Sentieys de l'Université de Rennes 1 qui ont accepté d'être les rapporteurs de mes travaux de thèse.

Je suis particulièrement reconnaissant envers Joan Daemen de STMicroelectronics de m'avoir fait l'honneur de sa participation à mon jury de thèse. Par ailleurs, ses conseils prodigués au cours de ma thèse m'ont été d'une grande aide dans la compréhension de la cryptographie.

Je remercie grandement le Professeur Jean Claude Bajard du LIRMM de m'avoir fait l'honneur de présider mon jury de thèse.

Je remercie Jean Baptiste Rigaud du CMP pour avoir pris part à mon jury de thèse ainsi que pour ses encouragements au cours de ma thèse.

Le contexte « multi labo » dans lequel s'est déroulé ma thèse m'a amené à beaucoup voyager entre Rousset, Marseille et Montpellier, et je tiens à remercier particulièrement deux personnes qui ont tout fait pour me simplifier la vie. La géniale Evelyne Arrighi de STMicroelectronics : on a à peine le temps de penser aux démarches à entreprendre qu'elle a déjà tout fait!!!! Et Elisabeth Petiot du LIRMM, qui, même lorsqu'elle n'était plus responsable des missions du département microélectronique, était toujours présente pour répondre à mes questions dans la bonne humeur. Encore merci à vous deux, si tout le monde pouvait être comme vous....

Ensuite je tiens à remercier toute l'équipe d'AST (STMicroelectonics): Stéphan Courcambeck (merci pour ton temps), William Orlando, Christian Schwarz, Sarah Hoffman, Jean Nicolaï, Klaus Rischmuller (merci pour tous tes conseils en termes de communications), Bernard Kasser et Norah Cowman.

Une « spéciale dédicace » à mes collègues de pause AST : Sophie Gabriele, Guillaume Petitjean et Lionel Martin ainsi qu'à mes amis thésards AST : Simon Conseil et William Ketchantang. Je crains de ne jamais retrouver une telle ambiance.

Je remercie les thésards du LIRMM; je commence par mes colocataires de box : Robin et Nicolas qui ont su durant mon absence, défendre vaillamment mon bureau dans un hall où les places se font rares. Je pense également à Nicolas, Jean Baptiste (tu n'es pas thésard mais ça passe pour cette fois), Alin, Nabil, Fabrice, Benoit, Daniel, Jean Denis, Jean Etienne, Lionel, Julien, Annissa, Alex, Alex, Abdellah, Olivier, Zequin (Eric), Nicolas, Mickael, Laurent et Marion. Merci également à Nurten pour son aide de dernière minute.

Je remercie également mon compagnon de toujours et mon complice « musical » Vincent Kerzérho ainsi que son amie Anne Laure. Je remercie mon ami Wael Gouja ainsi que tous les autres : Boris, Daniele, Severine, Nadine et Franck, Arnaud, Maxime, Nizar, Romain, Christian, Seb...

Je ne peux terminer ces remerciements, sans remercier infiniment Dany et Alexandre Herrmann pour leur accueil toujours chaleureux lors de mes nombreux séjours à Montpellier.

### Résumé

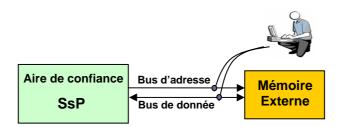

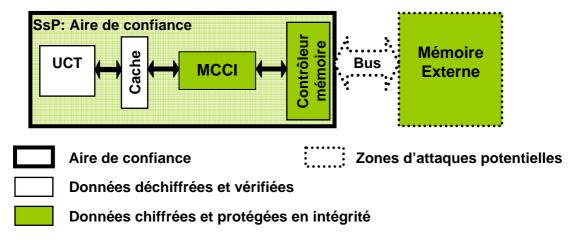

Les systèmes embarqués actuels (téléphone portable, assistant personnel...) ne sont pas considérés comme des hôtes de confiance car toute personne y ayant accès, sont des attaquants potentiels. Les données contenues dans ces systèmes peuvent être sensibles (données privées du propriétaire, mot de passe, code d'un logiciel...) et sont généralement échangées en clair entre le Système sur Puces (SoC – System on Chip) et la mémoire dans laquelle elles sont stockées. Le bus qui relie ces deux entités constitue donc un point faible : un attaquant peut observer ce bus et récupérer le contenu de la mémoire, ou bien a la possibilité d'insérer du code afin d'altérer le fonctionnement d'une application s'exécutant sur le système. Afin de prévenir ce type d'attaque, des mécanismes matériels doivent être mis en place afin d'assurer la confidentialité et l'intégrité des données. L'approche conventionnelle pour atteindre cet objectif est de concevoir un mécanisme matériel pour chaque service de sécurité (confidentialité et intégrité). Cette approche peut être implantée de manière sécurisée mais empêche toute parallélisation des calculs sous-jacents.

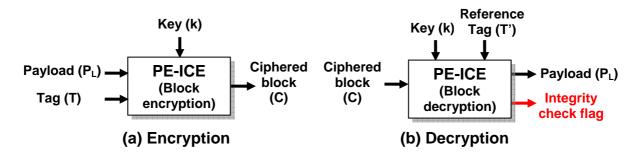

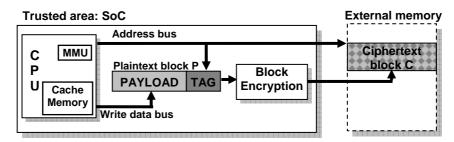

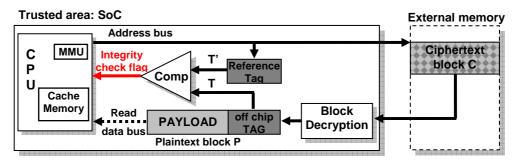

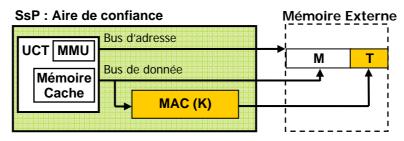

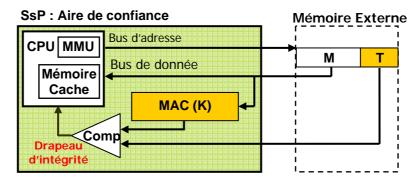

Les travaux menés au cours de cette thèse ont dans un premier temps, consisté à faire une étude des techniques existantes permettant d'assurer la confidentialité et l'intégrité des données. Dans un deuxième temps, nous avons proposé deux mécanismes matériels destinés à la sécurisation des transactions entre un processeur et sa mémoire. Un moteur de chiffrement et de contrôle d'intégrité parallélisé, PE-ICE (Parallelized Encryption and Integrity Checking Engine) a été conçu. PE-ICE permet une parallélisation totale des opérations relatives à la sécurité aussi bien en écriture qu'en lecture de données en mémoire. Par ailleurs, une technique basée sur une structure en arbre (PRV-Tree – PE-ICE protected Reference Values) comportant la même propriété de parallélisation totale, a été spécifiée afin de réduire le surcoût en mémoire interne impliqué par les mécanismes de sécurité.

### **Abstract**

Today's embedded systems are considered as non trusted hosts since the owner, or anyone else who succeeds in getting access, is a potential adversary. The bus between the System on Chip (SoC) and the external memory is one of the weakest points of such systems because external memories contain sensitive data (end users private data, software code...) which are usually exchanged in clear form over the bus. Therefore an adversary may probe this bus in order to read private data or to retrieve software code (data confidentiality concern). Another possible attack relies on code injection (data integrity concern). Thus, hardware mechanisms must be designed to ensure data confidentiality and integrity. The conventional way to reach such a goal is to implement a dedicated hardware engine for each security service. Being secured, this approach prevents parallelizability of the underlying computations.

In this thesis, after a study of existing techniques and engines guaranteeing data confidentiality and integrity, two hardware mechanisms dedicated to the security of processor-memory transactions are proposed. First, a Parallelized Encryption and Integrity Checking Engine (PE-ICE) has been designed to provide an effective solution to ensure both security services to data. PE-ICE allows full parallelizations on processor read and write operations while optimizing the hardware resources required. Then, a technique based on a tree structure (PRV-Tree – PE-ICE protected Reference Values) with the same property of full parallelization, is specified to decrease the on-chip memory overhead implied by security mechanisms.

# **Contents**

| List of Figures                                        | 9  |

|--------------------------------------------------------|----|

| List of Tables                                         | 13 |

| Introduction                                           | 17 |

| Chapter 1: The cryptographic tool                      | 23 |

| 1-1. Definitions                                       | 23 |

| 1-2. Kerckhoffs' Principles                            | 25 |

| 1-3. Encryption Techniques                             | 26 |

| 1-3.1. Secret-Key Cipher (a.k.a. Symmetric-Key Cipher) | 26 |

| 1-3.1.1. Principle                                     | 26 |

| 1-3.1.2. Stream Ciphers                                | 27 |

| 1-3.1.2.1. Principle                                   | 27 |

| 1-3.1.2.2. One Time Pad: The Perfect Stream Cipher     | 28 |

| 1-3.1.2.3. Modern Stream Ciphers                       | 28 |

| 1-3.1.2.4. Advantages and Drawbacks                    | 31 |

| 1-3.1.3. Block Ciphers                                 | 31 |

| 1-3.1.3.1. Principle                                   | 31 |

| 1-3.1.3.2. The Shannon Principles                                       | 32 |

|-------------------------------------------------------------------------|----|

| 1-3.1.3.3. Block Cipher Structures                                      | 32 |

| 1-3.1.3.4. Example: AES                                                 | 33 |

| 1-3.1.3.5. Advantages and Drawbacks                                     | 38 |

| 1-3.1.3.6. Modes of Operation                                           | 39 |

| 1-3.2. Public-Key Encryption                                            | 45 |

| 1-3.2.1. Principle                                                      | 45 |

| 1-3.2.2. Example: RSA                                                   | 46 |

| 1-3.2.3. Advantages and Drawbacks                                       | 47 |

| 1-3.3. Security of Encryption Techniques                                | 48 |

| 1-4. Data Integrity Checking Techniques                                 | 50 |

| 1-4.1. Integrity Checking Process Principle                             | 50 |

| 1-4.2. Hash Functions                                                   | 51 |

| 1-4.3. Unkeyed Hash Functions a.k.a. Modification Detection Codes (MDC) | 52 |

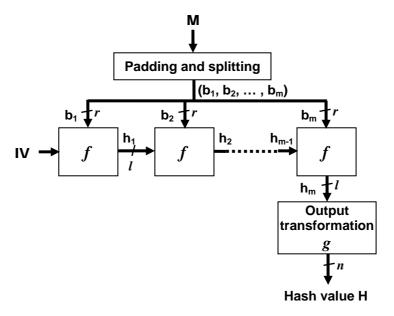

| 1-4.3.1. Principle                                                      | 52 |

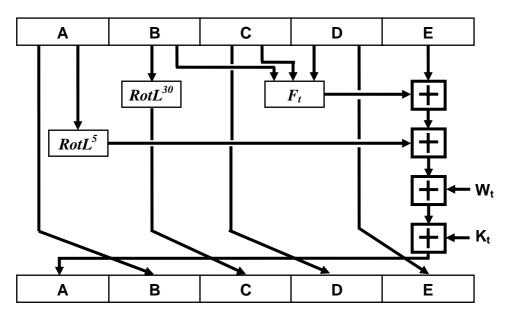

| 1-4.3.2. Example: SHA-1                                                 | 53 |

| 1-4.3.3. Message Authentication Schemes Based on MDC                    | 55 |

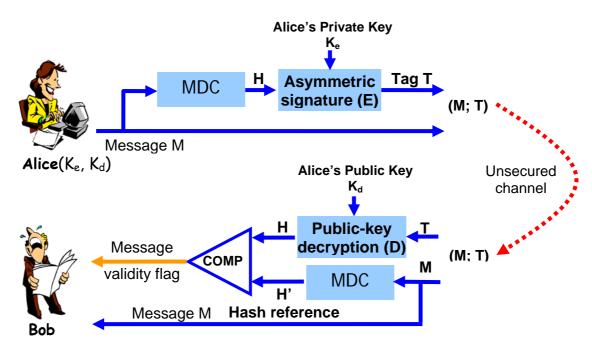

| 1-4.3.3.1. MDC and Asymmetric Signature                                 | 56 |

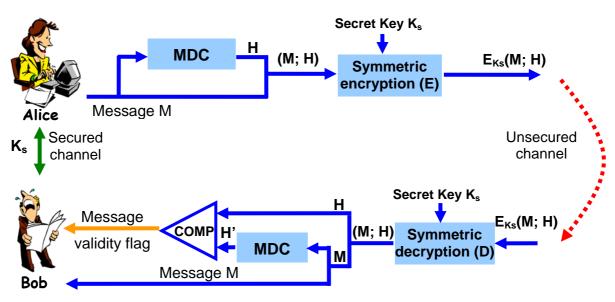

| 1-4.3.3.2. MDC and Symmetric Encryption                                 | 57 |

| 1-4.4. Keyed Hash Functions and MAC Algorithms                          | 58 |

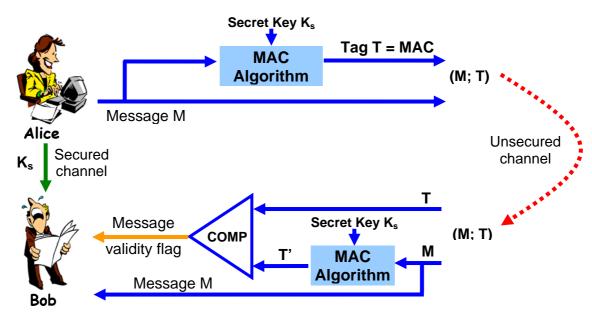

| 1-4.4.1. Principle                                                      | 58 |

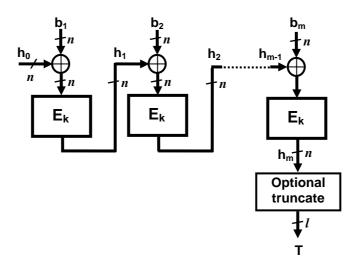

| 1-4.4.2. Example: CBC-MAC                                               | 59 |

| 1-4.5. The Birthday Attacks                                             | 60 |

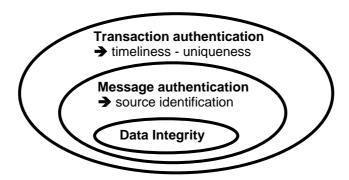

| 1-4.6. Transaction Authentication                                       | 61 |

| 1-5. Conclusion                                                         | 61 |

|                                                                         |    |

| Chapter 2: Security Concerns                                            | 63 |

| 2-1. Software Copy Protection                                           |    |

| 2-2. The Threat Model                                                   |    |

| 2-2.1. Security Level and Adversaries Classification                    |    |

| 2-2.2. Considered Attacks                                               |    |

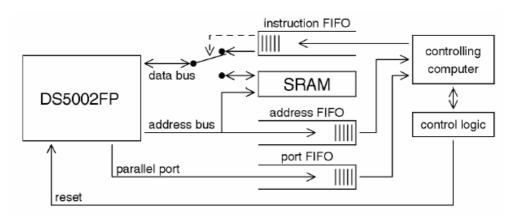

| 2-2.3. Attack conducted on a Commercial Device: The DS5002FP            |    |

| 2-3. System on Chip Context                                             | 70 |

| 2-3.1. Memory Accesses                                                     | 70 |

|----------------------------------------------------------------------------|----|

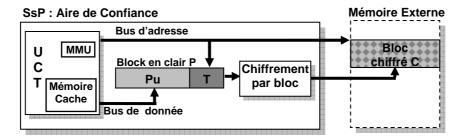

| 2-3.2. Basic Principles for the Hardware Mechanisms for Data Security      | 72 |

| 2-3.2.1. Hardware Mechanisms for Data Security Localization                | 72 |

| 2-3.2.2. Bus Encryption Principle                                          | 72 |

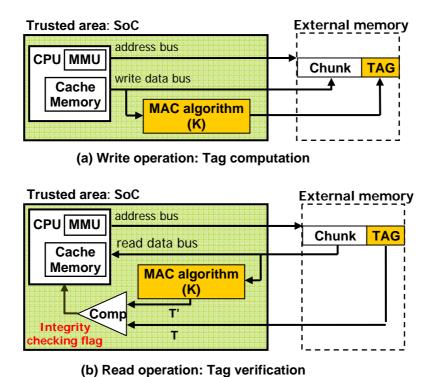

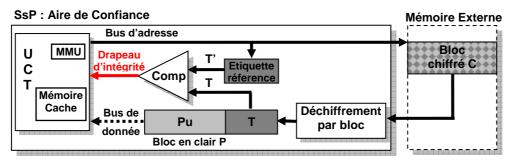

| 2-3.2.3. Principle of Memory (Content) Integrity Verification              | 73 |

| 2-3.3. Run-Time Performance Degradation Considerations                     | 75 |

| 2-3.3.1. Data Properties                                                   | 75 |

| 2-3.3.2. Sources of Time Performance Degradation                           | 75 |

| 2-4. Conclusion                                                            | 76 |

| Chapter 3: Related Works                                                   | 79 |

| 3-1. Hardware Engine for Bus Encryption                                    | 79 |

| 3-1.1. Direct Encryption                                                   | 80 |

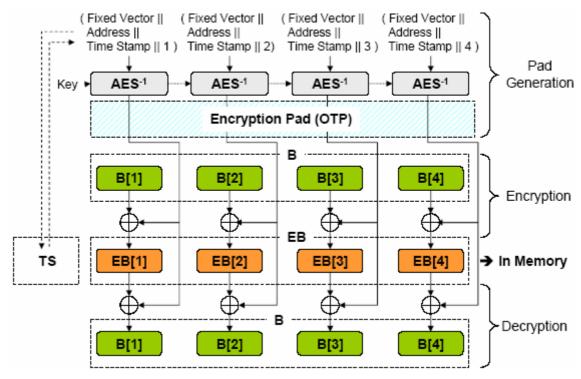

| 3-1.2. One Time Pad (OTP)                                                  | 82 |

| 3-1.3. Summary                                                             | 85 |

| 3-2. Memory Integrity Verification Engines                                 | 86 |

| 3-2.1. Integrity Checking Engines Based on MAC algorithms                  | 87 |

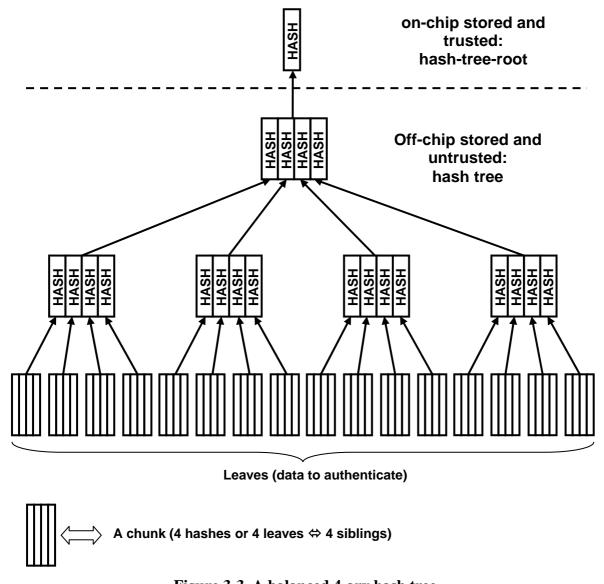

| 3-2.2. Hash Trees                                                          | 88 |

| 3-2.3. Summary                                                             | 91 |

| 3-3. Memory Encryption and Authentication: Techniques and Related Works    | 91 |

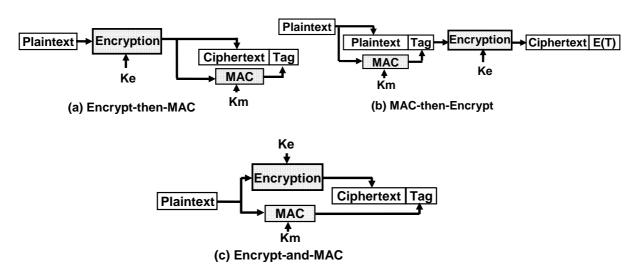

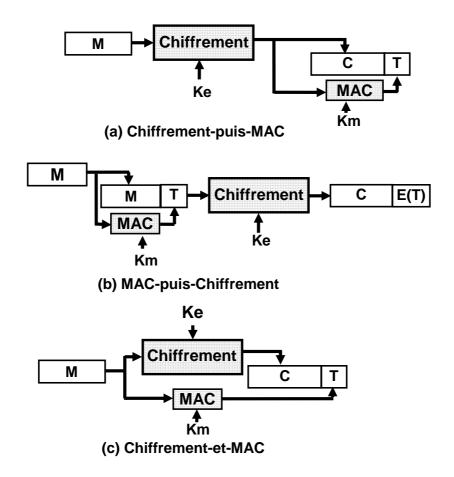

| 3-3.1. The Conventional Way: Generic Composition Schemes                   | 91 |

| 3-3.1.1. Principle                                                         | 91 |

| 3-3.1.2. Off-Chip Memory Protection Engines Based on Generic Composition   | 93 |

| 3-3.1.2.1. AEGIS                                                           | 93 |

| 3-3.1.2.2. SP – Secret Protected                                           | 93 |

| 3-3.1.2.3. XOM                                                             | 94 |

| 3-3.1.2.4. Summary                                                         | 94 |

| 3-3.2. AREA: Added Redundancy Explicit Authentication                      | 95 |

| 3-3.3. Authenticated Encryption Modes                                      | 96 |

| 3-3.3.1. Authenticated Encryption Modes with Non-Parallelizable Operations | 97 |

| 3-3.3.1.1. CCM - Counter CBC-MAC                                           |    |

| 3-3.3.1.2. EAX - Encrypt Authenticate Translate                            | 97 |

| 3-3 3 1 3 PCFB - Propagating Cipher Feedback                               | 98 |

| 3-3.3.1.4. IACBC - Integrity Aware Cipher Block Chaining                 | 98  |

|--------------------------------------------------------------------------|-----|

| 3-3.3.1.5. XCBC-XOR                                                      | 99  |

| 3-3.3.2. Parallelizable Authenticated Encryption modes                   | 99  |

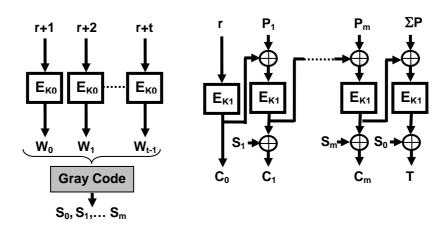

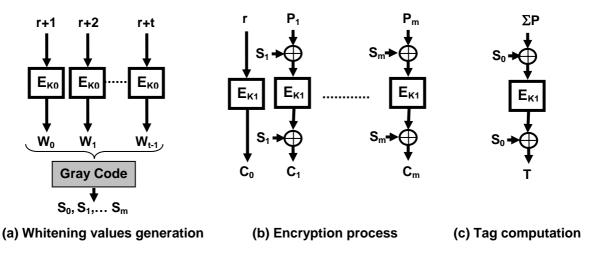

| 3-3.3.2.1. IAPM – Integrity Aware Parallelizable Mode                    | 99  |

| 3-3.3.2.2. XECB-XOR                                                      | 100 |

| 3-3.3.2.3. OCB – Offset Code Book                                        | 100 |

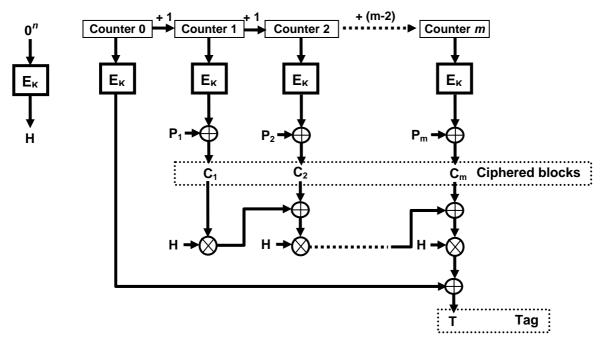

| 3-3.3.2.4. GCM – Galois Counter Mode                                     | 101 |

| 3-3.3.2.5. CWC – Carter-Wegman authentication with Counter               | 102 |

| 3-3.3.2.6. CS – Cipher State                                             | 103 |

| 3-3.3.3 Discussion                                                       | 103 |

| 3-4. Conclusion                                                          | 104 |

|                                                                          |     |

| Chapter 4: PE-ICE - Parallelized Encryption and Integrity Check          | C   |

| Engine                                                                   | 107 |

| 4-1. General Overview                                                    | 108 |

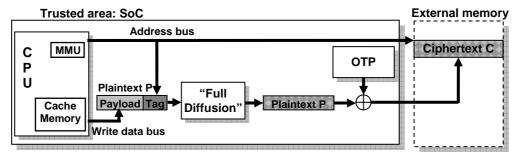

| 4-2. Adding the Integrity Checking Capability to Block Encryption        | 108 |

| 4-2.1. The Diffusion Property of Block Ciphers                           | 108 |

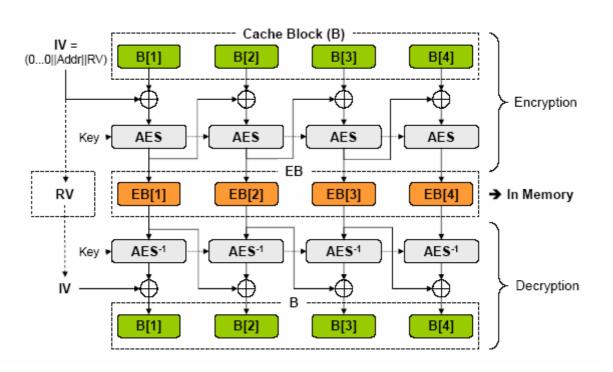

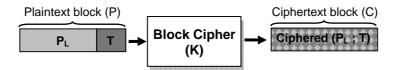

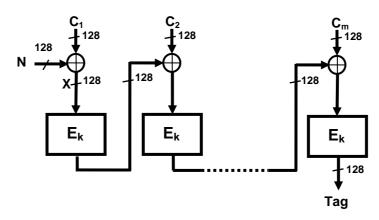

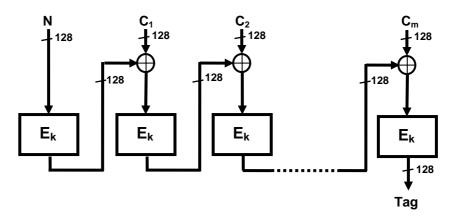

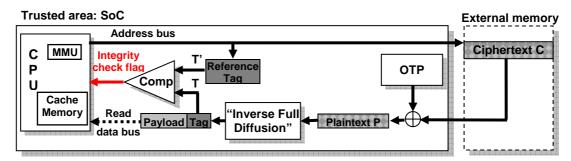

| 4-2.2. PE-ICE Encryption and Integrity Checking Process                  | 109 |

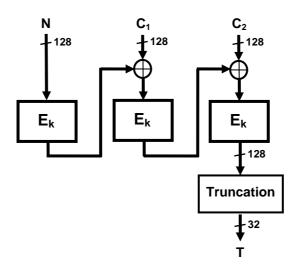

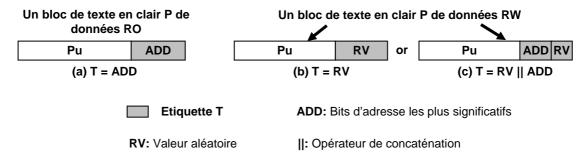

| 4-2.3. The Tag Generation                                                | 110 |

| 4-3. Encryption Mode and Chunk Definition                                | 112 |

| 4-4. Protecting the Physical Address Space vs. the Virtual Address Space | 113 |

| 4-5. Security Considerations                                             | 114 |

| 4-5.1. Active Attacks                                                    | 114 |

| 4-5.2. Confidentiality and Passive Attacks                               | 116 |

| 4-5.3. PE-ICE Encryption Key Requirements                                | 117 |

| 4-6. Physical Address Computation                                        | 118 |

| 4-7. Memory consumption                                                  | 120 |

| 4-8. Summary                                                             | 120 |

| 4-8.1. Definitions                                                       | 120 |

| 4-8.2. PE-ICE Parameters                                                 | 121 |

| 4-8.3. PE-ICE Pseudo Codes                                               | 122 |

| 4-9 Conclusion                                                           | 124 |

| Chapter 5: PE-ICE Implementation                 | 127 |

|--------------------------------------------------|-----|

| 5-1. PE-ICE Configurations                       | 127 |

| 5-1.1. PE-ICE-128                                | 128 |

| 5-1.1.1. Layout of a PE-ICE-128 Line             | 128 |

| 5-1.1.2. Security Limitations                    | 129 |

| 5-1.1.3. Memory Consumption                      | 130 |

| 5-1.1.4. Computation of a Chunk Physical Address | 130 |

| 5-1.2. PE-ICE-160                                | 130 |

| 5-1.2.1. Layout of a PE-ICE-160 Line             | 131 |

| 5-1.2.2. Security Limitations                    | 131 |

| 5-1.2.3. Memory Consumption                      | 131 |

| 5-1.2.4. Computation of a Chunk Physical Address | 131 |

| 5-1.3. PE-ICE-192                                | 132 |

| 5-1.3.1. Layout of a PE-ICE-192 Line             | 132 |

| 5-1.3.2. Security Limitations                    | 132 |

| 5-1.3.3. Memory Consumption                      | 133 |

| 5-1.3.4. Computation of a Chunk Physical Address | 133 |

| 5-2. Hardware Design and Latencies               | 134 |

| 5-2.1. The AMBA-AHB Bus                          | 134 |

| 5-2.2. Design Principle                          | 135 |

| 5-2.3. Latencies                                 | 138 |

| 5-2.3.1. PE-ICE-128 Latencies                    | 138 |

| 5-2.3.2. PE-ICE-160 Latencies                    | 140 |

| 5-2.3.3. PE-ICE-192 Latencies                    | 143 |

| 5-2.4. Silicon Area Usage                        | 144 |

| 5-2.5. Latency Optimization                      | 145 |

| 5-3. Performance Evaluation                      | 147 |

| 5-3.1. SoC Designer Tool Set                     | 147 |

| 5-3.2. Simulation Platform Modeling              | 148 |

| 5-3.3. Simulation Framework                      | 149 |

| 5-3.4. Results                                   | 149 |

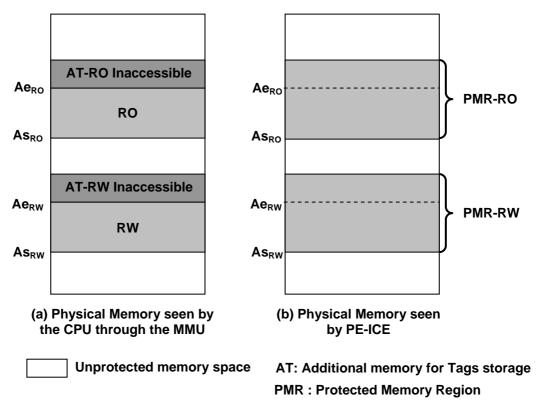

| 5-4. Implementation Use Case                     | 153 |

| 5-4.1 Protected Memory Region and Key Management | 153 |

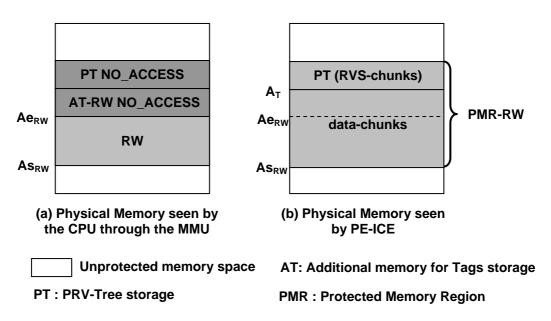

| 5-4.2. Physical Memory Management                                   | 154 |

|---------------------------------------------------------------------|-----|

| 5-5. Comparison With a Generic Composition Scheme                   | 155 |

| 5-5.1. The Generic Composition Scheme: AES and CBC-MAC              | 156 |

| 5-5.1.1. Secure Implementation of GC                                | 156 |

| 5-5.1.2. Optimized Definition of the Generic Composition Scheme     | 157 |

| 5-5.1.3. Security Considerations                                    | 159 |

| 5-5.1.4. Memory Consumption                                         | 159 |

| 5-5.1.5. Latencies                                                  | 159 |

| 5-5.1.6. Hardware Cost                                              | 160 |

| 5-5.1.7. Run-Time Performance                                       | 161 |

| 5-5.2. Comparison between GC and PE-ICE                             | 163 |

| 5-6. Conclusion                                                     | 164 |

|                                                                     | _   |

| Chapter 6: PRV-Tree - Secure Off-chip Storage of Reference Ran-     | dom |

| Values                                                              | 167 |

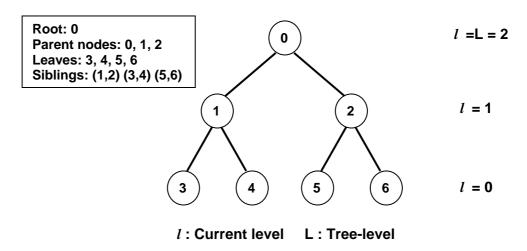

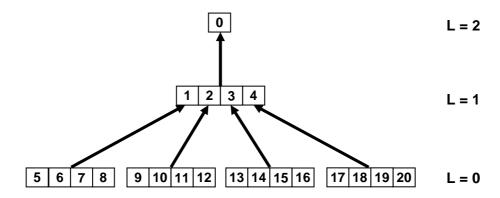

| 6-1. <i>m</i> -ary Balanced Tree                                    | 168 |

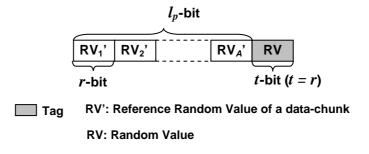

| 6-2. Secure Storage Principle of the Reference Random Values        | 169 |

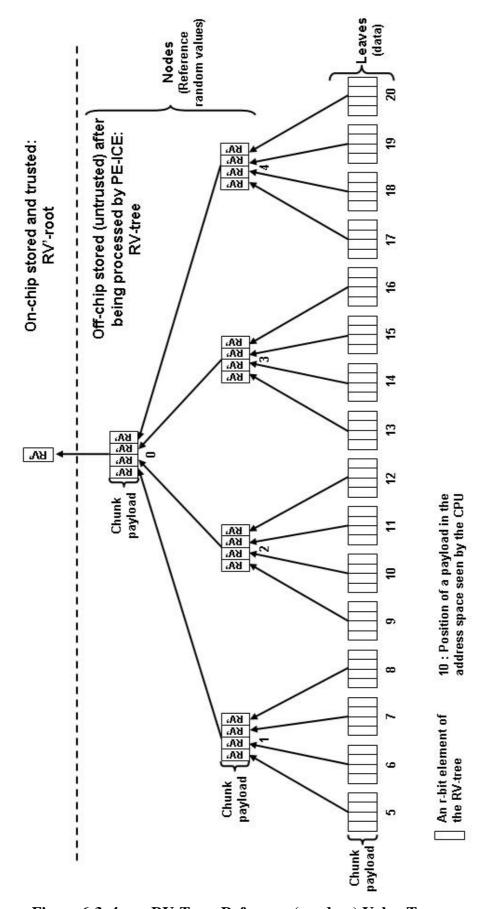

| 6-3. PRV-Tree scheme (PE-ICE protected of the Reference Value Tree) | 171 |

| 6-3.1. Principle                                                    | 171 |

| 6-3.2. Physical Address Computation                                 | 173 |

| 6-3.3. Off-chip Memory Consumption                                  | 175 |

| 6-4. Comparison between PRV-Trees (PE-ICE-160) and Hash Trees       | 176 |

| 6-5. Implementation Use Case                                        | 178 |

| 6-6. Other applications of PRV-Tree                                 | 179 |

| 6-7. Conclusion                                                     | 180 |

| Chapter 7: Conclusion                                               | 183 |

| 7-1. Contributions                                                  | 183 |

| 7-2. Further Works                                                  | 185 |

| 7-3. Further Idea: PE-ICE-OTP                                       | 185 |

| French Summary: Mécanismes Matériels pour des Transactions          |     |

| Processeur-Bus Sécurisées dans les Systèmes Embarqués               | 189 |

| References                         | 219 |

|------------------------------------|-----|

| Bibliography Relative to the Study | 229 |

# **List of Figures**

| Figure 1-1  | Secret-key (a.k.a. symmetric key) cipher principle                        | . 26 |

|-------------|---------------------------------------------------------------------------|------|

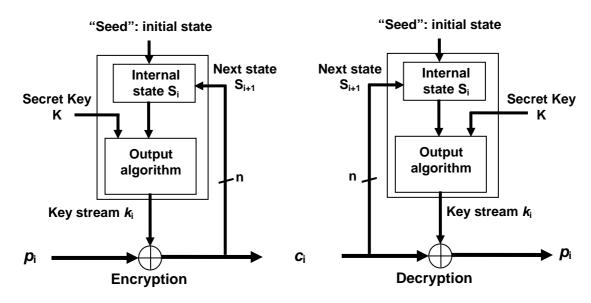

| Figure 1-2  | Stream cipher principle                                                   | . 27 |

| Figure 1-3  | Key stream generators model of modern stream ciphers                      | . 29 |

| Figure 1-4  | Synchronous stream ciphers                                                | . 29 |

| Figure 1-5  | Self -synchronous stream ciphers                                          | . 30 |

| Figure 1-6  | Block ciphers principle                                                   | . 31 |

| Figure 1-7  | Block ciphers structure                                                   | . 32 |

| Figure 1-8  | AES Encryption process: 10 rounds of 4 operations: SubBytes - ShiftRows - |      |

|             | MixColumns - AddRoundKey                                                  | . 34 |

| Figure 1-9  | State array input and output                                              | . 34 |

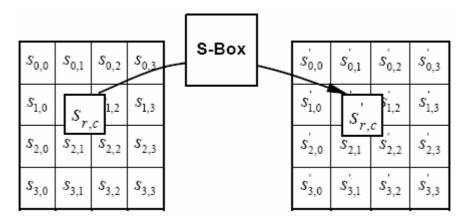

| Figure 1-10 | SubBytes: the S-box is applied on each byte of the State array            | . 35 |

| Figure 1-11 | The S-box: substitution value for a byte <i>xy</i>                        | . 35 |

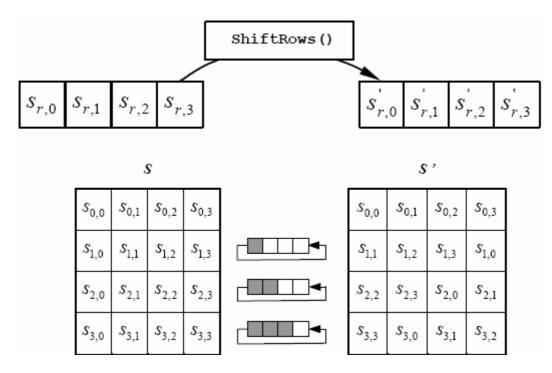

| Figure 1-12 | ShiftRows: the last three rows of the state array are cyclically shifted  | . 36 |

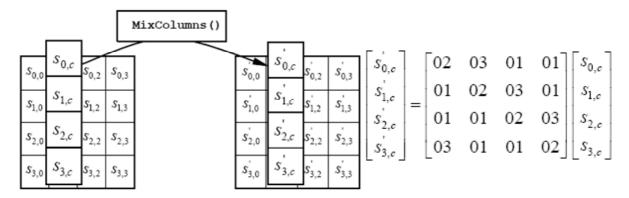

| Figure 1-13 | MixColumns multiplies each column of the State array by a constant matrix | . 36 |

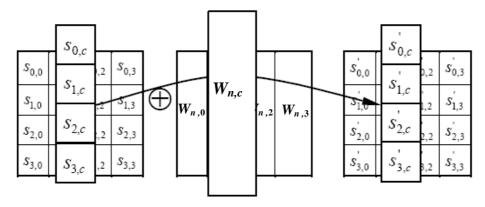

| Figure 1-14 | AddRoundKey: Xor operation between each column of the State array and the | ;    |

|             | corresponding column in the round key matrix                              | . 37 |

| Figure 1-15 | Computation of a round key                                                | . 37 |

| Figure 1-16 | The ECB (Electronic Code Book) mode                                       | . 40 |

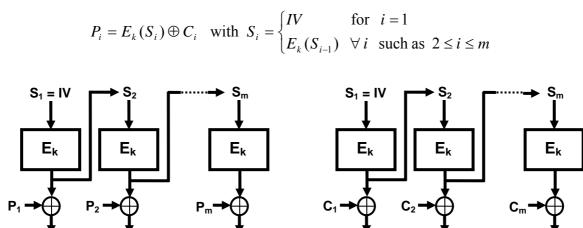

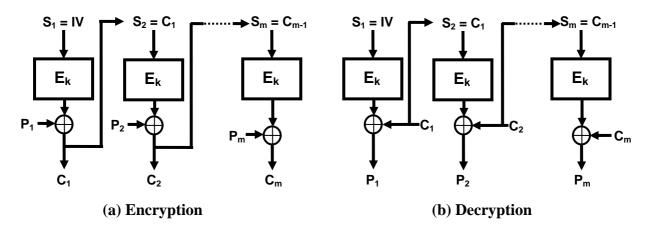

| Figure 1-17 | The CBC (Cipher Block Chaining) mode                                      | . 40 |

| Figure 1-18 | The CTR (Counter) mode                                                    | . 42 |

| Figure 1-19 | The OFB (Output FeedBack) mode                                            | . 43 |

| Figure 1-20 | The CFB (Cipher FeedBack) mode                                               | 44     |

|-------------|------------------------------------------------------------------------------|--------|

| Figure 1-21 | Public-key cipher principle.                                                 | 45     |

| Figure 1-22 | Man-in-the-middle attack principle                                           | 48     |

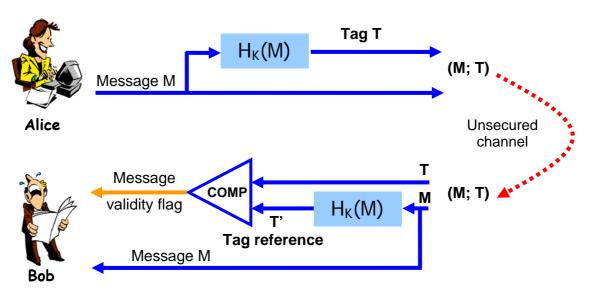

| Figure 1-23 | Integrity checking process principle                                         | 50     |

| Figure 1-24 | Model of iterative hash functions                                            | 52     |

| Figure 1-25 | The compression function (f) of SHA-1                                        | 54     |

| Figure 1-26 | Message authentication using a MDC and asymmetric signature                  | 56     |

| Figure 1-27 | Message authentication using a MDC and symmetric encryption                  | 57     |

| Figure 1-28 | Message authentication using MAC algorithms                                  | 58     |

| Figure 1-29 | General model for CBC-MAC                                                    | 59     |

| Figure 1-30 | Taxonomy of security services required to prevent active attacks             | 61     |

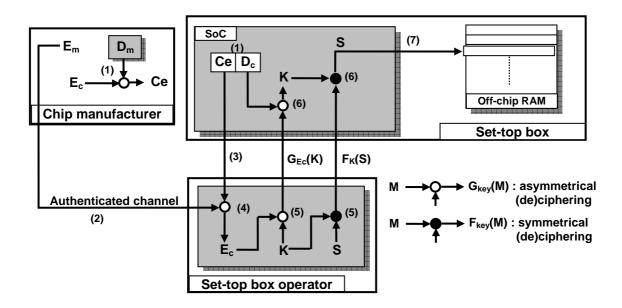

| Figure 2-1  | Secure software download for software copy protection                        | 65     |

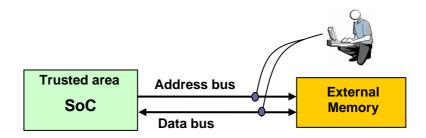

| Figure 2-2  | Board level attack based on bus probing and on data injection                | 67     |

| Figure 2-3  | Principle of the DS5002FP CPU attack with a read-out device connected to the | the    |

|             | bus                                                                          | 69     |

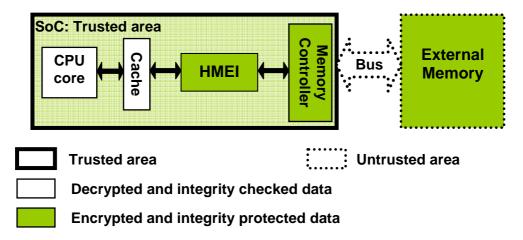

| Figure 2-4  | Localization on the SoC of the hardware mechanisms providing data            |        |

|             | confidentiality and authentication services                                  | 72     |

| Figure 2-5  | Integrity checking principle of external memory                              | 74     |

| Figure 3-1  | Direct encryption scheme (AES-CBC) proposed in the first version of the      |        |

|             | AEGIS processor.                                                             | 81     |

| Figure 3-2  | One-Time Pad encryption scheme (AES-CTR) proposed in the last version of     | of the |

|             | AEGIS processor.                                                             | 83     |

| Figure 3-3  | A balanced 4-ary hash tree                                                   | 88     |

| Figure 3-4  | The conventional way to provide data confidentiality and integrity:          | 92     |

| Figure 3-5  | IACBC - Integrity Aware Cipher Block Chaining                                | 99     |

| Figure 3-6  | IAPM - Integrity Aware Parallelizable Mode                                   | 100    |

| Figure 3-7  | GCM -Galois Counter Mode (The message to encrypt is a multiple of the blo    | ock    |

|             | length of the underlying block cipher)                                       | 102    |

| Figure 4-1  | PE-ICE general overview                                                      | 108    |

| Figure 1.2  | The diffusion property of block ciphers                                      | 100    |

| Figure 4-3  | PE-ICE Encryption and Integrity checking process                           | 110   |

|-------------|----------------------------------------------------------------------------|-------|

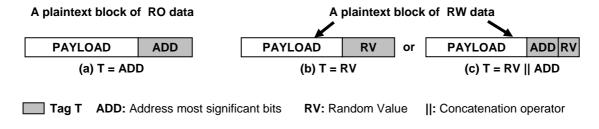

| Figure 4-4  | Plaintext blocks and tag composition before encryption                     | 112   |

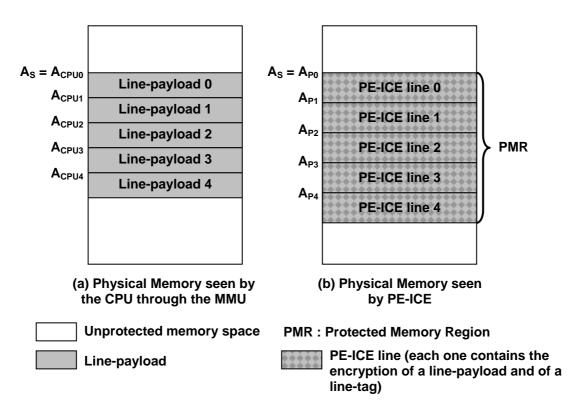

| Figure 4-5  | Off-chip Memory layout - Reorganization of the Protected Memory Region     | S     |

|             | (PMR) in PE-ICE line by PE-ICE and shifting of the physical address. Exam  | nple  |

|             | depicted is a PMR containing five PE-ICE lines (⇔five line-payloads seen l | by    |

|             | the CPU)                                                                   | 118   |

| Figure 4-6  | PE-ICE operations on a payload of RO data contained in a chunk             | 122   |

| Figure 4-7  | PE-ICE operations on a RW data of a size smaller or equal to the payload   |       |

|             | contained in a chunk                                                       | 123   |

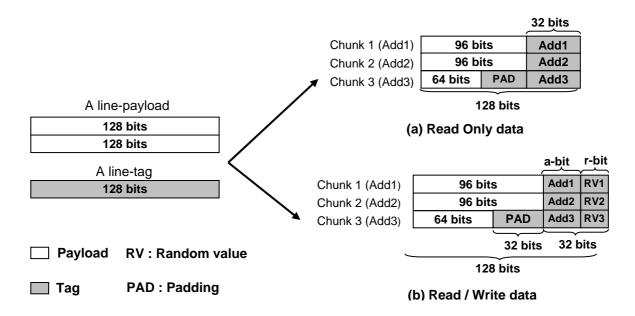

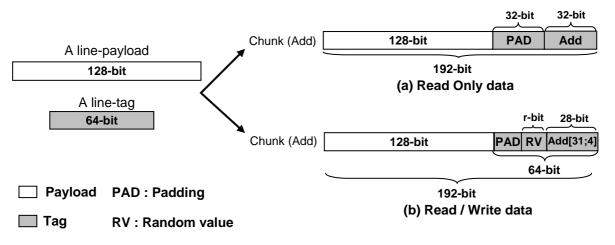

| Figure 5-1  | Layout of a PE-ICE-128 line before encryption                              | 128   |

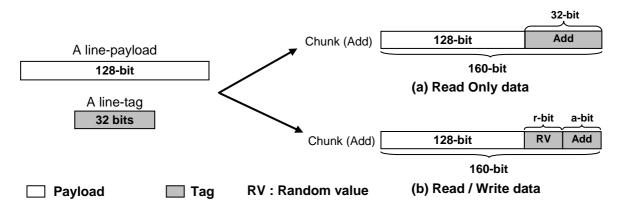

| Figure 5-2  | Layout of a PE-ICE-160 line before encryption                              | 131   |

| Figure 5-3  | Layout of a PE-ICE-192 line before encryption                              | 132   |

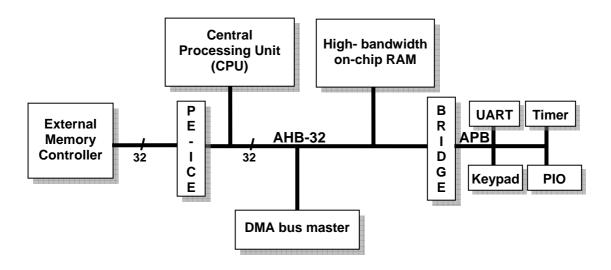

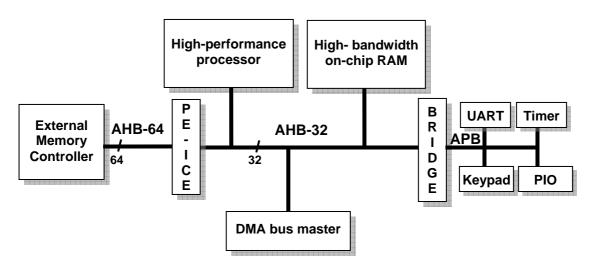

| Figure 5-4  | PE-ICE-128 localization on an AMBA-AHB bus                                 | 134   |

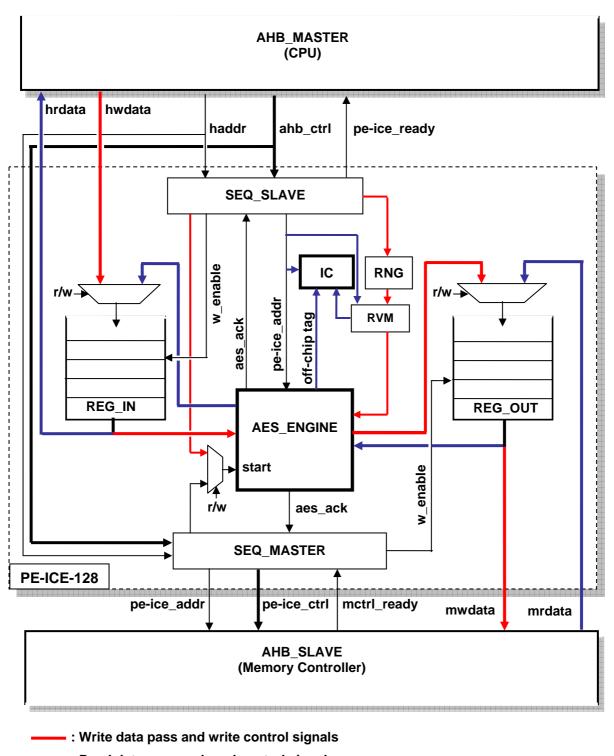

| Figure 5-5  | PE-ICE design principle on an AMBA-AHB bus                                 | 136   |

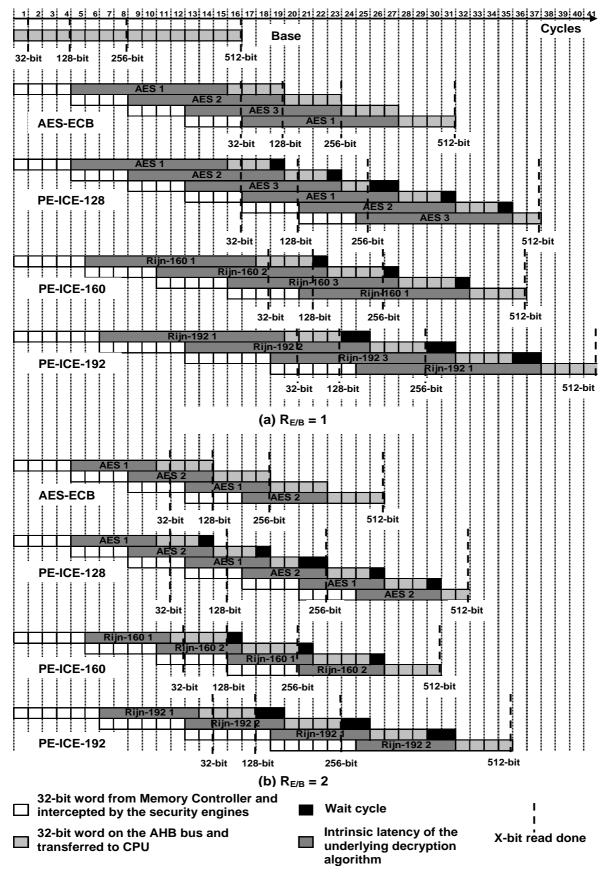

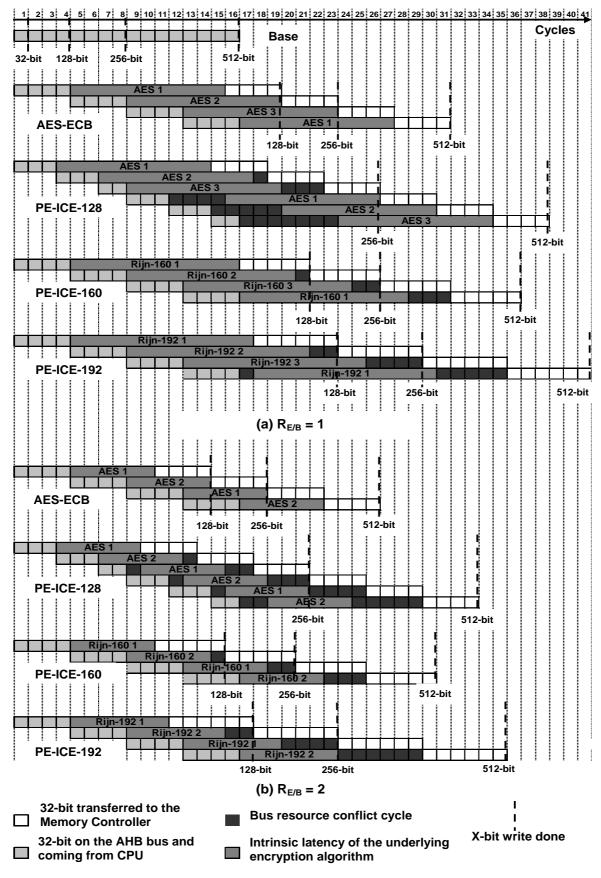

| Figure 5-6  | Latencies introduced on the AHB bus by the different PE-ICE configuration  | s and |

|             | by the AES-ECB engine on read operations                                   | 141   |

| Figure 5-7  | Latencies introduced on the AHB bus by the different PE-ICE configuration  | s and |

|             | by the AES-ECB engine on write operations                                  | 142   |

| Figure 5-8  | Architecture using 64-bit processor memory bus                             | 145   |

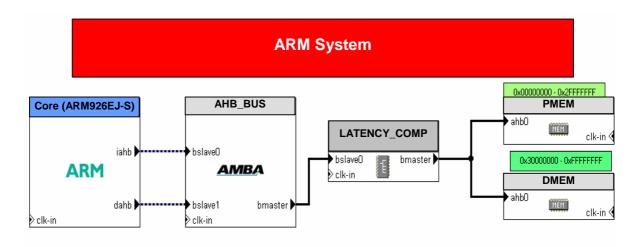

| Figure 5-9  | Generic architecture of the simulation platforms                           | 148   |

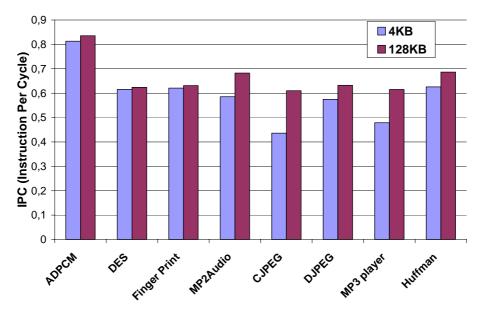

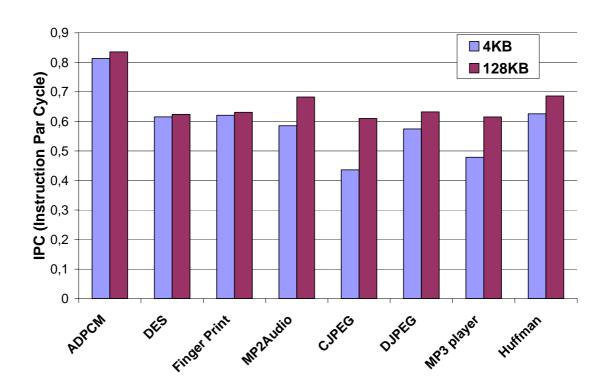

| Figure 5-10 | Simulation results for the Base platform                                   | 150   |

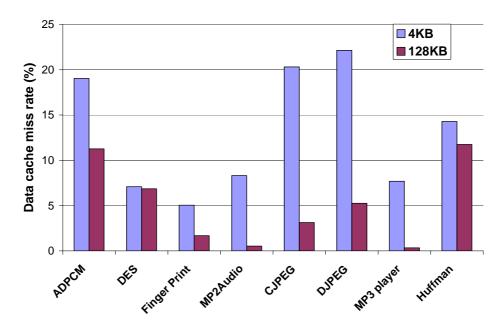

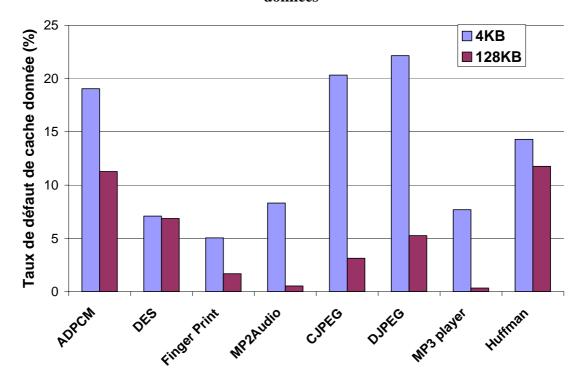

| Figure 5-11 | Data cache miss rate for the set of benchmarks used for the performance    |       |

|             | evaluation and for two different data cache sizes (4KB and 128KB)          | 150   |

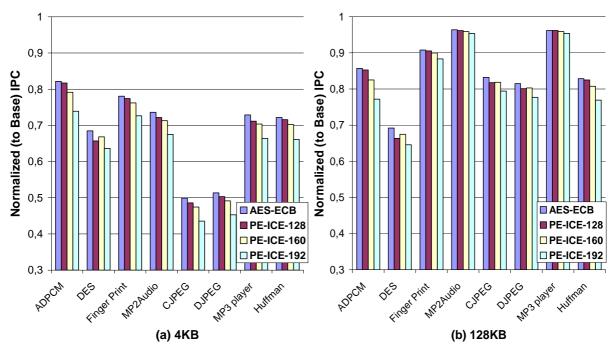

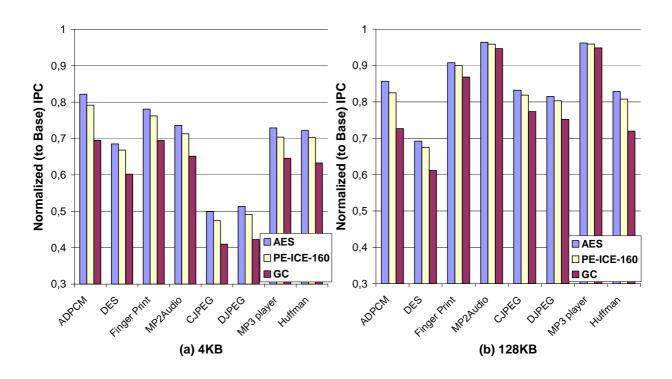

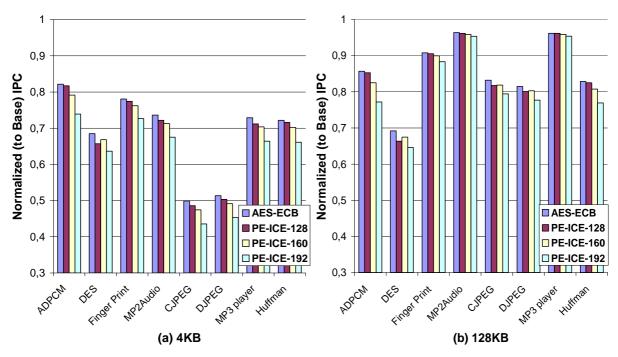

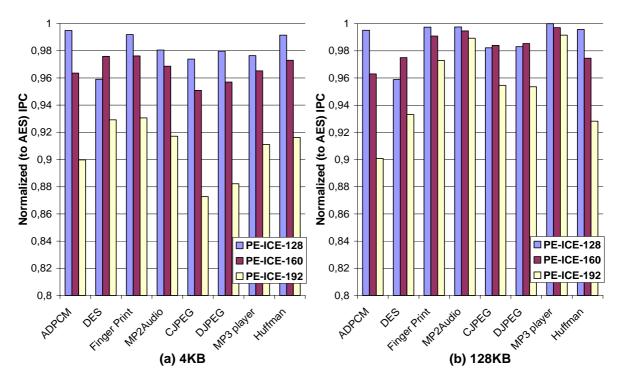

| Figure 5-12 | Run-time overhead of AES encryption and of the PE-ICE configurations for   | two   |

|             | data cache sizes (4KB and 128KB)                                           | 151   |

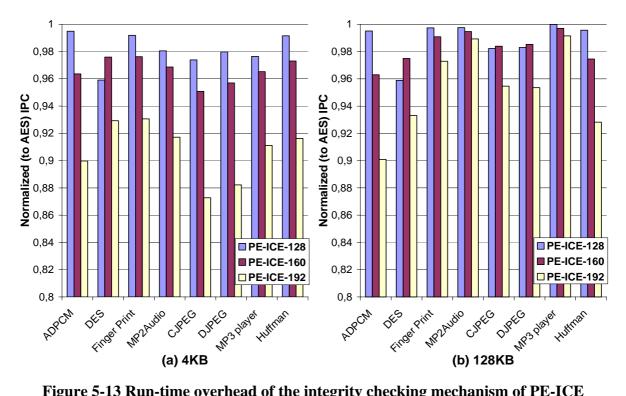

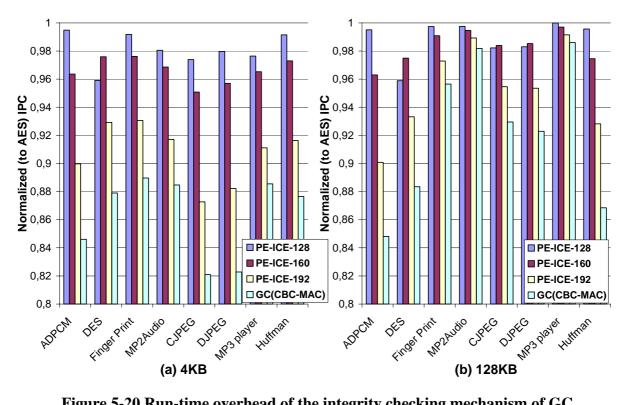

| Figure 5-13 | Run-time overhead of the integrity checking mechanism of PE-ICE            |       |

|             | configurations compared to AES-ECB encryption alone for two data cache s   | sizes |

|             | (4KB and 128KB)                                                            | 152   |

| Figure 5-14 | Tables used by PE-ICE to identify the Protected Memory Regions and to sel  | ect   |

|             | the correct encryption key                                                 | 154   |

| Figure 5-15 | Physical memory management for PE-ICE implementation                       | 155   |

| Figure 5-16 | Insecure implementation of the CBC-MAC algorithm                           | 156   |

| Figure 5-17 | Secure implementation of the CBC-MAC algorithm                          | 157 |

|-------------|-------------------------------------------------------------------------|-----|

| Figure 5-18 | CBC-MAC implemented in the proposed generic composition scheme (GC) .   | 158 |

| Figure 5-19 | Run-time overhead of GC, of the AES-ECB engine and of PE-ICE-160 for tw | o'  |

|             | data cache sizes (4KB and 128KB)                                        | 161 |

| Figure 5-20 | Run-time overhead of the integrity checking mechanism of GC             | 162 |

|             |                                                                         |     |

| Figure 6-1  | A balanced binary tree (2-ary tree)                                     | 168 |

| Figure 6-2  | An RVS-chunk before PE-ICE encryption (for $t = r$ )                    | 169 |

| Figure 6-3  | 4-ary RV-Tree: Reference random Value Tree                              | 172 |

| Figure 6-4  | Principle of computation of parent chunk addresses on a 4-ary tree      | 174 |

| Figure 6-5  | Physical memory management for PE-ICE with PRV-Tree                     | 178 |

| Figure 6-6  | Table_RW used by PE-ICE to identify the Protected Memory Regions of RW  | ,   |

|             | data and to retrieve parent chunks in memory                            | 179 |

|             |                                                                         |     |

| Figure 7-1  | PE-ICE-OTP Principle                                                    | 186 |

# **List of Tables**

| 1 able 3-1 | Summary of the existing memory encryption engines                               | 80 |

|------------|---------------------------------------------------------------------------------|----|

| Table 3-2  | Summary of solutions achieving memory integrity checking                        | 91 |

| Table 3-3  | Summary of the memory protection engine (encryption and integrity checking)     |    |

|            | based on generic composition                                                    | 95 |

|            |                                                                                 |    |

|            |                                                                                 |    |

| Table 4-1  | Security limitations of PE-ICE regarding active attacks led on a chunk evaluate | d  |

|            | in chances to succeed                                                           | 15 |

| Table 4-2  | Summary of the parameters defining PE-ICE                                       | 21 |

|            |                                                                                 |    |

| Table 5-1  | Security limitations offered by PE-ICE-128 and by PE-ICE-160 regarding activ    | e  |

|            | attacks led on a chunk and evaluated in chances to succeed for an adversary 1   | 29 |

| Table 5-2  | Security limitations offered by PE-ICE-192 regarding active attacks led on a    |    |

|            | chunk and evaluated in chances to succeed for an adversary                      | 33 |

| Table 5-3  | Additional latencies introduced by PE-ICE-128 and by the AES-ECB engine or      | l  |

|            | an AMBA-AHB bus for the operations requested by an ARM9E core 1                 | 39 |

| Table 5-4  | Additional latencies introduced by PE-ICE-160 and by the AES-ECB engine or      | l  |

|            | an AMBA-AHB bus for the operations requested by an ARM9E core 1                 | 40 |

| Table 5-5  | Additional latencies introduced by PE-ICE-192 and by the AES-ECB engine or      | l  |

|            | an AMBA-AHB bus for the operations requested by an ARM9E core                   | 43 |

| Table 5-6  | Additional latencies introduced by the PE-ICE configurations and by the AES-  |   |

|------------|-------------------------------------------------------------------------------|---|

|            | ECB engine on an AMBA-AHB bus for the operations requested by an ARM9E        |   |

|            | core with a bus width of 64-bit                                               | 5 |

| Table 5-7  | Number of AES cores to implement for PE-ICE and the AES-ECB engine when       |   |

|            | the off-chip memory bus width is of 64-bit                                    | 7 |

| Table 5-8  | Architectural parameters of the simulation platforms                          | 9 |

| Table 5-9  | Average performance slowdown implied by the AES-ECB engine                    | 1 |

| Table 5-10 | Average performance slowdown implied by the integrity checking mechanism of   |   |

|            | PE-ICE compared to AES-ECB encryption alone                                   | 2 |

| Table 5-11 | Security limitations offered by the CBC-MAC scheme                            | 9 |

| Table 5-12 | Additional latencies introduced by GC on an AMBA-AHB bus                      | 0 |

| Table 5-13 | Average performance slowdown implied by the AES-ECB engine                    | 2 |

| Table 5-14 | Average performance slowdown implied by the integrity checking mechanism of   |   |

|            | GC - CBC-MAC - compared to AES-ECB encryption alone                           | 2 |

| Table 5-15 | PE-ICE and GC (Generic Composition scheme) comparison: evaluation of the      |   |

|            | cost of the integrity checking mechanisms of the two approaches when compared |   |

|            | to the AES-ECB encryption163                                                  | 3 |

| Table 6-1  | PRV-Tree with PE-ICE-160 for different <i>r</i> -values                       | 6 |

| Table 6-2  | Memory bandwidth consumption of tree schemes for two different sizes of the   | _ |

| 2          | RW memory section to protect against replay, 16MB and 256 MB                  | 7 |

|            | , been to protest against replay, rotting and mo time                         |   |

### Introduction

Not a day passes in our lives without someone using an embedded system: PDA, mobile phones, MP3 players, set-top box, video equipments... The range of services provided by every single embedded system tends to widen rapidly and applications like on-line banking transactions, web browsing, email, application / game download become common on mobile devices. As a consequence the amount of sensitive information such as private data — bank information, passwords, email, photos... — or intellectual property — software, digital multimedia content... — contained or transiting in those devices also increases. The issue is that today's embedded systems are considered as untrustworthy hosts [1] since the owner, or anyone else who succeeds in getting access, is a potential adversary. Thus, one of the challenges for the high-technology industry in the development of pervasive computing is the ability to ensure secured computation and storage.

The attacks conducted on embedded systems [2] challenge several security services such as data confidentiality, data integrity and system availability. Data confidentiality ensures that data stored in or transiting through embedded systems are only read by authorized parties while data integrity guarantees that those data are not tampered with, deleted or altered by malicious entities. Availability refers to the requirement of ensuring the access to the device to the user without unexpected delay or obstacle.

Software attacks like viruses are the most famous threat because they regularly affect our desktop computers. Viruses turned up in embedded systems in 2004 with the worm called Cabir which infected mobile phones running Symbian Operating System (OS) and which propagated itself via Bluetooth. According to McAfee Virus Library, there were 120 types of Cabir variants [3] in 2005. The industry started to work on this issue with the Trustzone Project [4] from ARM and through consortiums such as the Trusting Computing Group [5] (TCG, formerly Trusting Computing Platform Alliance, TCPA) whose goal is to define

secured processing architectures. However, all these efforts do not consider hardware-based (physical) attacks and work under the assumption that the communication channels between the processor chip and the other components are secure despite the fact that data exchanges are often done in clear. The well known cracking of the Xbox gaming console shows that designing computing systems with such an assumption leads to simple physical attacks. In [6], the hacker Andrew "bunnie" Huang, explained his approach to break the Xbox security features and demonstrated that one of the weakest points of computing systems are buses because they offer a low-cost spot for attacks.

Thus, in this thesis we focus on physical non-invasive<sup>1</sup> attacks – or board level attacks – conducted on buses between the System on Chip and off-chip volatile memory or directly in the memory – typically Random Access Memory (RAM). The objectives of the adversary can be the unauthorized use or the illegal distribution of intellectual properties or – what is more inconvenient for end users – to discover or to corrupt private data retrieved on buses or directly in memory. Thus, our goal is to provide a private and authenticated tamper resistant environment for application execution. This means we must ensure the confidentiality of the off-chip memory content during storage or execution to prevent the leakage of any sensitive information and its integrity to forbid execution of intentionally altered data.

Smartcards offer a countermeasure against such attacks by putting all processing and storage elements in a single chip. Another common solution is secure co-processors which encapsulate the components handling sensitive computations and data in a tamper-resistant and tamper-responsive package, such as the IBM 4578 [7]. However, these solutions are not suited for embedded systems because the latter require an expensive and large package to be able to provide a high performance system while the former do not allow storing a large amount of code and data and do not offer a high computing power.

A trade-off between the above mentioned countermeasures is to limit the trust boundaries to the SoC and to embed memory protection apparatus on-chip. This concept was introduced by Best with bus-encryption microprocessor [8, 9, 10] in 1979: data are encrypted before being outputted off-chip and are only decrypted once on-chip. However, encryption only ensures data confidentiality but does not provide tamper-detection mechanisms to guarantee data integrity. Later on, several research works [11, 12, 13, 14] considered this additional

\_

<sup>&</sup>lt;sup>1</sup> In this work we do not consider the non-invasive attacks called side-channel attacks. They are based on the analysis of the system behavior (power consumption, execution time, supply voltage, temperature, radiation ...) to draw conclusion on the cryptographic functions or on the secret values on which the security of the underlying computing systems rely and which require specific countermeasures.

issue to offer a private and authenticated tamper resistant environment to software execution. They achieved this task by providing both security services – data confidentiality and integrity – separately. The shortcoming of such an approach is the serialization of the computation of the underlying cryptographic algorithms on write or on read operations introducing non-parallelizable latencies on off-chip memory accesses. Moreover, the hardware resources needed are not optimized since the implementation of a dedicated engine for each security service is required.

**Objectives**: In this thesis, the goal is to provide a private and authenticated tamper resistant environment to applications running in embedded processors. The attacks targeted are the physical attacks conducted at the board level, more specifically bus probing and memory tampering (code and data injection). The designed hardware mechanisms must ensure the confidentiality and the integrity of the off-chip memory content while considering the constraints relative to the processor context – particularly random access of variable sizes – to optimize hardware resources, memory access latencies and the memory bandwidth consumption at run-time.

**Contributions**: In order to reach the above mentioned objectives, we explore added redundancy and randomness to block encryption to provide data integrity in addition to confidentiality. Two hardware mechanisms are proposed:

- (1) PE-ICE *Parallelized Encryption and Integrity Checking Engine* is a dedicated solution to guarantee data confidentiality and integrity of the external memory content with the following features:

- Full parallelization of the encryption and integrity checking process on write and read operations.

- Implementation of a single encryption algorithm to provide both security services: data confidentiality and integrity.

In this thesis, the architecture of PE-ICE and its security limitations are defined. Moreover PE-ICE is evaluated in terms of latencies introduced on memory accesses, of hardware resources required for its SoC implementation and of run-time performance degradation.

- (2) PRV-Tree *PE-ICE protected Reference Values Tree* is a scheme allowing to securely store off-chip the meta-data used by PE-ICE and thus to propose an efficient solution against a specific kind of attacks (replay). PRV-Tree offers the following advantages when compared to existing solutions by using the same hardware as PE-ICE:

- Full parallelization of the underlying operations on read and write operations

- Reduction of the memory bandwidth consumption

In this thesis the concept of PRV-Tree is detailed and its advantages are highlighted through concrete application examples.

The security of our schemes relies on the use of a well known and studied block encryption algorithm (Rijndael [15]) and on the essential assumption that the System on Chip is trusted.

The thesis is organized as follows.

Chapter 1 introduces the cryptographic tool by defining the security service objectives and by describing the cryptographic function useful to provide such security services and discussed in the rest of the thesis.

Chapter 2 provides the threat model and defines the considered attack scenarios. Moreover we show through an example of attack that performing memory encryption only is not sufficient and could lead to simple attacks challenging data confidentiality. We also present the bus encryption and the memory content (integrity) verification principles. Finally this chapter deals with the issue of implementing cryptographic functions in a System on Chip.

Chapter 3 first relates the existing memory encryption engines and the memory verification schemes embedded on-chip. Then the techniques providing both data confidentiality and authentication are described and the related implementations in our application domain considering the same security perimeter (SoC trusted) are presented.

Chapter 4 defines the architecture of the proposed engine PE-ICE (Parallelized Encryption and Integrity Checking Engine). In this chapter we show how to add the integrity checking capability to block encryption. Moreover we describe PE-ICE processing on read and write operations, and the PE-ICE security limitations and memory consumptions are discussed.

Chapter 5 proposes several PE-ICE configurations which depend on the underlying block cipher and evaluates their implementation on a commercial on-chip bus and processor core.

Moreover, a comparison with a conventional scheme (data confidentiality and integrity separately provided by dedicated engines) is discussed.

Chapter 6 proposes a scheme called PRV-Tree (PE-ICE Protected Reference Value Tree) to eliminate the on-chip memory overhead implied by the PE-ICE countermeasure against a specific kind of attacks (replay). The advantages of PRV-Tree compared to existing solutions (Hash Trees) are finally discussed.

Chapter 7 concludes this thesis by summarizing the contributions. Further works are also detailed and a new research idea is proposed to improve the mechanisms reported in the thesis.

# Chapter 1: The cryptographic tool

**Cryptology** is the science of secret. Two sub-disciplines compose cryptology: **cryptography** which is the science of keeping secrets and **cryptanalysis** which is the science of breaking those secrets.

This chapter presents the techniques provided by cryptography to allow secured communications and the existing attacks proposed by cryptanalysis to circumvent such techniques. The first section gives general term definitions. Then, section 1-2 exposes Kerckhoffs' principles which define what a secure cryptosystem is. Section 1-3 and section 1-4 respectively describe techniques for data encryption and for data integrity checking.

#### 1-1. Definitions

Cryptography is a study of techniques dedicated to provide security services to implement information security. Such security services are confidentiality, authentication, data integrity and non-repudiation (definition taken from [16]):

**Confidentiality** is a service used to keep the content of information from all but those authorized to have it. Secrecy is a term synonymous with confidentiality and privacy. There are numerous approaches to providing confidentiality, ranging from physical protection to mathematical algorithms which render data unintelligible.

**Data integrity** is a service which addresses the unauthorized alteration of data. To ensure data integrity, one must have the ability to detect data manipulation by unauthorized parties. Data manipulation includes such things as insertion, deletion, and substitution.

**Authentication** is a service related to identification. This function applies to both entities and information itself. Two parties entering into a communication should identify each other. Information delivered over a channel should be authenticated as to origin, date of origin, data content, time sent, etc. For these reasons this aspect of cryptography is usually subdivided into two major classes: entity authentication and data origin authentication. Data origin authentication implicitly provides data integrity (for if a message is modified, the source has changed).

**Non-repudiation** is a service which prevents an entity from denying previous commitments or actions. When disputes arise due to an entity denying that certain actions were taken, a means to resolve the situation is necessary. For example, one entity may authorize the purchase of property by another entity and later deny such authorization was granted. A procedure involving a trusted third party is needed to resolve the dispute.

In the context of this thesis, non-repudiation is not applicable as the system on chip is the only active entity in a processor-memory communication system; therefore such a service issue is not dealt with in this dissertation. In the following, when the term data integrity is used, data origin authentication is implicitly checked. In this chapter, differences between these two notions are highlighted when required.

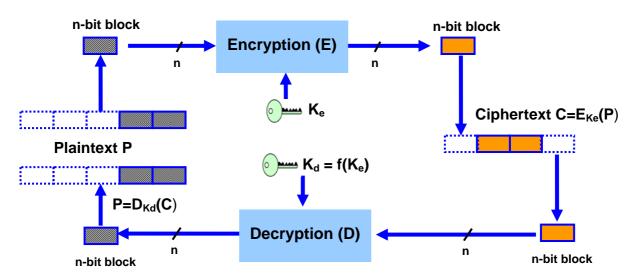

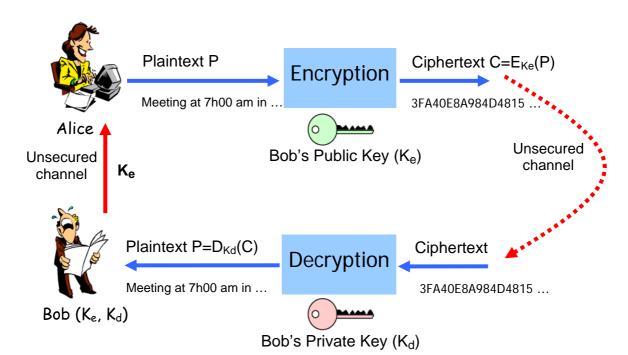

**Encryption** is the transformation process which makes a message, called **plaintext**, unintelligible. The resulting text of such a transformation is called **ciphertext**. Encryption operations are mathematical functions used to ensure the confidentiality of a message (but not only). **Decryption** is the operation which allows to retrieve the plaintext from the ciphertext. Both encryption and decryption primitives use a **key** which specifies the particular transformation respectively from plaintext to ciphertext and from ciphertext to plaintext.

In the following, the encryption function using the key  $K_e$  will be noted as  $E_{Ke}$ . Hence if P is the message to encrypt, then  $E_{Ke}(P)$  is the encryption of P using the key  $K_e$ . It results in a ciphertext C such as  $C = E_{Ke}(P)$ . Similarly, the decryption function using the key  $K_d$  will be

noted as  $D_{Kd}$  and the plaintext P is recovered by applying  $D_{Kd}$  on the ciphertext C:  $P = D_{Kd}(C)$ . Encryption techniques are exposed in section 1-3.

The **integrity checking process** is the set of operations which allows to verify the data integrity of a message during its storage or transmission. Such a process is described in section 1-4.

A **cryptosystem** is a set of algorithms used to provide the above mentioned security services and particularly confidentiality. It is usually composed of three algorithms: one for the key (or keys) generation, one for encryption noted E and one for decryption noted D.

A **cryptanalyst** studies techniques allowing to retrieve secret information on which the robustness of a cryptosystem - e.g. the key - relies. In the following a malicious cryptanalyst is referred to as an **adversary** or an **attacker**. The term **eavesdropper** is used when the attack only involves monitoring of the communication channel.

Two families of attacks have to be considered:

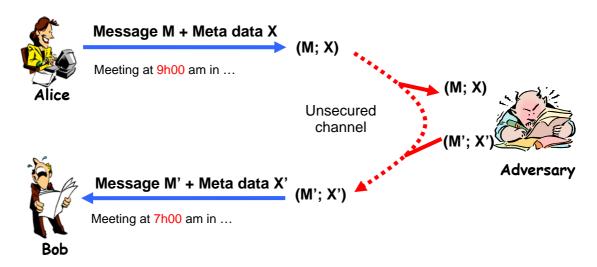

- Active attacks which allow message deletion or corruption, data injection or replay.

- Passive attacks which consist in observing ciphertext on the communication channel (eavesdropping).

# 1-2. Kerckhoffs' Principles

In 1883, Auguste Kerckhoffs defined six principles to design a secure cryptosystem [17]:

- 1. The system should be, if not theoretically unbreakable, unbreakable in practice;

- 2. It must not be required to be secret, and it must be able to fall into the hands of the enemy without inconvenience;

- 3. Its key must be communicable and retainable without the help of written notes, and changeable or modifiable at the will of the correspondents;

- 4. the cryptogram should be transmissible by telegraph;

- 5. the encryption/decryption apparatus should be portable and operable by a single person;

6. it is necessary - given the circumstances that command its application - that the system be easy to use, requiring neither mental strain nor the knowledge of a long series of rules to observe.

All of Kerckhoffs' requirements are still valid today. Among them we can notice that the second principle states that all algorithms used in a cryptosystem should be public knowledge.

## 1-3. Encryption Techniques

The first purpose of encryption techniques is to provide the confidentiality security service. The second and the third of Kerckhoffs' principles implicitly mean that the robustness of an encryption scheme relies on a secret: the key. If this secret is shared by all persons who use a cipher to communicate in a private way, this cipher is called symmetric or secret-key cipher. On the other hand, if the secret is only known by the intended recipient of the encrypted message, the cipher used is called asymmetric or public-key cipher.

# 1-3.1. Secret-Key Cipher (a.k.a. Symmetric-Key Cipher)

#### **1-3.1.1.** Principle

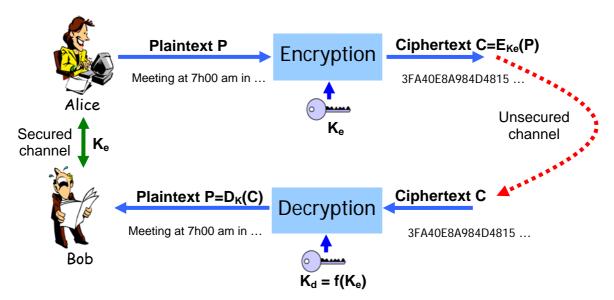

Figure 1-1 Secret-key (a.k.a. symmetric key) cipher principle

The entities using cryptosystems based on this family of ciphers to communicate must agree on a secret. This secret is the encryption key  $K_e$  and the decryption key  $K_d$ . This is why they are called secret-key ciphers. Moreover, such ciphers are also referred to as symmetric-key cipher since they mostly use the same key for encryption and for decryption ( $K_e = K_d$ ) or because  $K_e$  is easily computable from  $K_d$  and vice-versa.

Example of utilization: Alice and Bob want to communicate over an unsecured channel (Figure 1-1). They first choose together a secret key  $K_e$ . Then Alice encrypts the message with a symmetric-key cipher and  $K_e$  and sends it to Bob. Bob receives the ciphertext and uses the same symmetric-key cipher and  $K_e$  (or computes  $K_d$  from  $K_e$ ) to retrieve the plaintext.

Symmetric ciphers are designed to provide fast computation on encryption and on decryption. However the previous example highlights the main drawback of symmetric-key cryptosystems which is to securely agree on a secret key prior to establishing the communication.

Secret-key algorithms are divided into two families: stream ciphers and block ciphers.

#### 1-3.1.2. Stream Ciphers

## 1-3.1.2.1. Principle

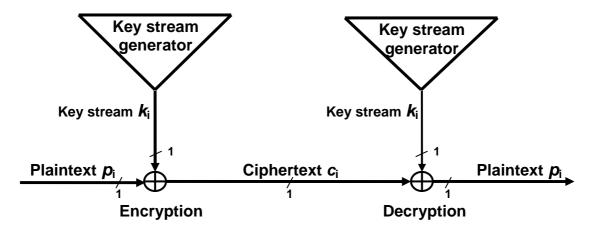

Figure 1-2 Stream cipher principle

The concept of stream ciphers was first introduced by Gilbert Vernam [18] in 1917. He proposed to encrypt a message character by character with a previously-prepared key of the

same size as the message. The reverse procedure should be applied to the ciphertext to retrieve the plaintext; i.e. the same key has to be applied character by character on the ciphertext.

Modern stream ciphers are inspired by such a principle and are composed of two parts (Figure 1-2): a key stream generator and a XOR operator. The key stream generator provides a bit stream  $k_i$ ; the encryption proper is performed by the XOR operator which combines  $k_i$  and the plaintext  $p_i$  one bit at a time. It results in the ciphertext  $c_i$  as follows:

$$c_i = p_i \oplus k_i$$

.

The decryption process is also a XOR operation between the same bit stream as the one used for encryption and the ciphertext  $c_i$ . In the light of the XOR operator property ( $k_i \oplus k_i = \text{Id}^2$ ), the result of the decryption is the plaintext:

$$p_i = c_i \oplus k_i$$

.

# 1-3.1.2.2. One Time Pad: The Perfect Stream Cipher

One type of stream ciphers has been proved theoretically unbreakable by Shannon [19]: the One-Time Pad (OTP). OTP uses a secret key stream randomly generated and at least as long as the plaintext. Hence the sole information that a cryptanalyst could guess, is the length of the plaintext. However, generating a random bit stream as long as the plaintext and transmitting it to the intended recipient of the message are two difficult tasks which make OTP implementation unaffordable.

#### 1-3.1.2.3. Modern Stream Ciphers

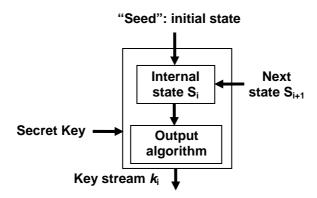

In order to overcome the OTP issues, key stream generators of modern stream ciphers use algorithms which produce a pseudo random key stream  $k_i$  from an internal state  $S_i$  and a secret key as depicted in Figure 1-3. The internal state is initialized by a small data called "seed" and all the cryptographic complexity of such a scheme resides in the output algorithm. The objective is to make a bounded adversary think that the key stream generator output is

-

<sup>&</sup>lt;sup>2</sup> Id is the identity function.

random. However the resulting key stream is obviously not truly random and the unbreakable provability of OTP is no longer valid for such stream ciphers.

Figure 1-3 Key stream generators model of modern stream ciphers

Modern stream ciphers are also called state ciphers since the generated key stream sequences depend on the internal state of the key stream generator. The internal state is initialized with the seed and the way it is updated leads to define two kinds of stream ciphers: synchronous stream ciphers and self-synchronous stream ciphers.

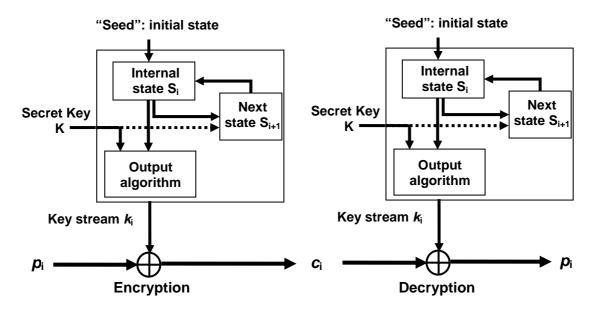

Figure 1-4 Synchronous stream ciphers

Concerning *synchronous stream ciphers* the internal state of the key stream generator changes independently of the ciphertext, it is only a function of the previous state and possibly of the secret key (Figure 1-4). Therefore, the sender and the recipient of an encrypted message must be synchronized: each state - defining a given key stream sequence - must correspond to the same section of the message during encryption and decryption. If some

encrypted message bits are lost during transmission, the key stream will be shifted in comparison to the ciphertext and the result of the decryption will be wrong. Additional mechanisms must be foreseen to re-synchronize the system and to avoid impacting the whole message deciphering. An advantage of such a class of stream ciphers concerns error propagation. If an error occurred on one or several bits during transmission, only the decryption of this or those bits will produce a wrong result. Unfortunately, this advantage becomes a drawback from a security point of view. Indeed an adversary, who changes bits in the ciphertext, knows how the plaintext is impacted.

Figure 1-5 Self -synchronous stream ciphers

Concerning *self-synchronous stream ciphers*, the evolution of the internal state of the key stream generator depends on the *n* previous ciphertext bits (Figure 1-5). Therefore on decryption, the key stream generator will be automatically synchronized with the key stream generator used during encryption after receiving *n* bits of ciphertext. Such a class of stream ciphers propagates transmission errors but in a limited way. Suppose that an error occurred and that the erroneous bits were used to decide the next internal state of the key stream generator. As internal states depend only on the *n* previous ciphertext bits, only the next key stream sequence and, as a consequence, the decryption of the corresponding ciphertext will be impacted by the error.

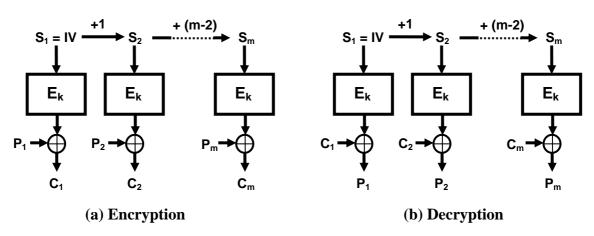

Stream ciphers are usually constructed by using block ciphers as output algorithms. Examples of stream ciphers are therefore presented in the section dedicated to block cipher modes of operation (3.1.3.6.).

#### 1-3.1.2.4. Advantages and Drawbacks

The main advantages of stream ciphers are their speed and their low hardware complexity. In addition, they are relevant for applications for which error propagation is not acceptable (synchronous stream ciphers) or must remain limited (self-synchronous stream ciphers). However designing a secure stream cipher is a difficult task. The fact that two key streams must never be used twice in the same cryptosystem is one security critical point. Suppose that two plaintext messages  $P_1$  and  $P_2$  are encrypted with the same key stream  $K_S$ , the resulting ciphertexts will be respectively  $C_1 = P_1 \oplus K_S$  and  $C_2 = P_2 \oplus K_S$ . Hence,  $P_1 \oplus P_2 = C_1 \oplus C_2$ , which gives information to cryptanalysts to perform attacks [16]. Moreover, a key stream generator using a secret key K and always initialized with the same seed will produce each time the same key stream. Therefore, an attacker may replay an old ciphertext with the certainty that it will be correctly decrypted. Such attacks highlight the fact that the seed or the secret key must be changed on each initialization of the output algorithm.

#### 1-3.1.3. Block Ciphers

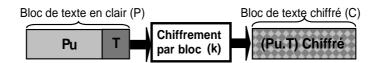

#### 1-3.1.3.1. Principle

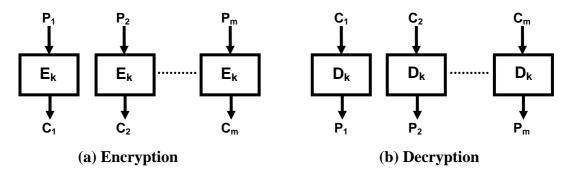

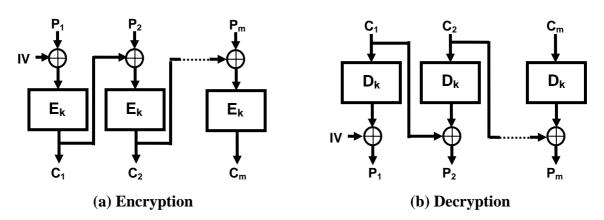

Figure 1-6 Block ciphers principle

A block cipher is an encryption scheme which first splits the plaintext into n-bit blocks, and then encrypts each block separately using a secret key  $K_e$  (Figure 1-6). The result of the encryption of an n-bit block of plaintext is a ciphertext block of the same length. The

decryption process works analogously deciphering the ciphertext n-bit block by n-bit block using  $K_d$ .

#### 1-3.1.3.2. The Shannon Principles

Shannon [19] identified two properties for cipher operations to be secure: *confusion* and *diffusion*. In Shannon's original definitions, *confusion* makes the relation between the key and the ciphertext as complex as possible. An ideal confusion makes each bit of the ciphertext dependent on all bits of the key. *Diffusion* refers to the property that redundancy in the statistics of the plaintext is dissipated in the statistics of the ciphertext. Theoretically, to reach such a goal, each bit of the ciphertext must depend on all bits of the plaintext.

In the same paper, Shannon introduced the notion of substitution-permutation networks also called product ciphers. Product ciphers iterate simple operations like substitution – to add confusion - and permutation – to add diffusion. The objective of combining simple transformations which do not individually provide a high level of security is to obtain strong cipher.

Most modern block ciphers are based on the product cipher principle.

# Round Key 1 Round Key 2 Round Secret Key Round Key 3 Round Secret Key Round Key 3 Round N-1 Round Key N-1 Round N-1 Round Key N-1 Round N-1 Round N-1 Round N-1 Round N-1 Round N-1 Round N-1

#### 1-3.1.3.3. Block Cipher Structures

Figure 1-7 Block ciphers structure

A block cipher is divided into two parts: the key schedule and the data path.

The data path follows the product cipher principle: it is composed of a function (or a set of functions) called a round that is repeated a fixed number of times. It takes the plaintext as input, and outputs the ciphertext after the fixed number of rounds Nr.

The key schedule processes the secret key and derives from it the round keys used in each data path round. The derivation of the key is necessary to add confusion: it increases the dependency of each bit of the ciphertext upon all bits of the secret key.

The first round of the data path (Figure 1-7) takes the plaintext and the first round key as inputs, and then the following rounds take the previous round output and the corresponding round key as inputs.

In order to illustrate block cipher theory, the following section describes the last block encryption algorithm standardized by the NIST (National Institute of Standard and Technology): AES (Advanced Encryption Standard).

#### 1-3.1.3.4. Example: AES

The Rijndael [15] algorithm was developed by Joan Daemen and Vincent Rijmen to answer the call for bock cipher standardization from the NIST. It was adopted as the new standard after a standardization process of five years. It was then called AES [20] (Advanced Encryption Standard) and replaced the famous DES [21] (Data Encryption Standard) for which the key length became too small to resist a brute force attack<sup>3</sup> [22].

The AES algorithm processes 128-bit data blocks using cipher keys with lengths of 128, 192 and 256 bits. In the following, the AES structure is detailed only for 128-bit keys; such a configuration is referred to as AES-128. For more information on the other configurations refer to [15, 20].

## The encryption data path:

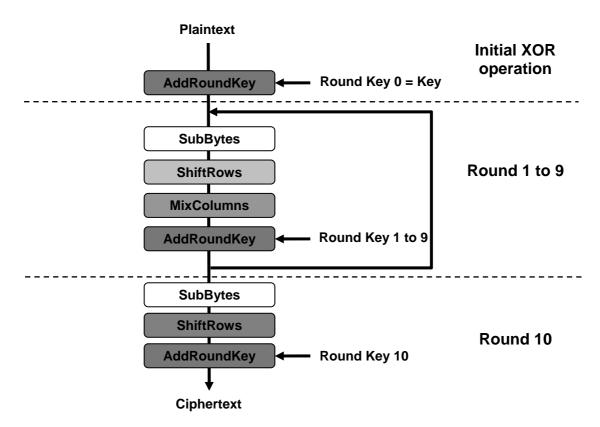

the plaintext block and the secret key. A round is made of four operations: SubBytes, ShiftRows, MixColumns and AddRoundKey, except the last round of the data path which does not include the MixColumns transformation (Figure 1-8).

The AES-128 data path is an iteration of 10 rounds after a first XOR operation between

-

<sup>&</sup>lt;sup>3</sup> A brute force attacks consists in trying all possible keys to find out all plaintext / ciphertext pairs, see section 3.3

Figure 1-8 AES Encryption process: 10 rounds of 4 operations: SubBytes - ShiftRows - MixColumns - AddRoundKey

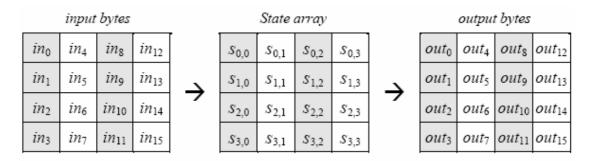

Those operations are performed on a 4x4 array of bytes called the State. At the start of the cipher the State array is filled by the plaintext bytes  $-in_0$ ,  $in_1$ ,  $in_2$ , ...,  $in_{15}$  – as shown in Figure 1-9 (taken from [20]).  $S_{r,c}$  is a byte of plaintext in the State array, the suffixes r and c refer respectively to the row and the column to which it belongs. Then the State is processed by the data path and at the end of the last round it is copied to the output array (Figure 1-9) to produce the ciphertext -  $out_0$ ,  $out_1$ ,  $out_2$ , ...,  $out_{15}$ .

Figure 1-9 State array input and output

Figure 1-10 SubBytes: the S-box is applied on each byte of the State array

|   |   | У  |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |

|---|---|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|

|   |   | 0  | 1  | 2  | 3  | 4  | 5  | 6  | 7  | 8  | 9  | a  | b  | С  | d  | е  | f  |

| х | 0 | 63 | 7с | 77 | 7b | f2 | 6b | 6f | с5 | 30 | 01 | 67 | 2b | fe | d7 | ab | 76 |

|   | 1 | ca | 82 | с9 | 7d | fa | 59 | 47 | f0 | ad | d4 | a2 | af | 9с | a4 | 72 | c0 |

|   | 2 | b7 | fd | 93 | 26 | 36 | 3f | f7 | CC | 34 | a5 | е5 | f1 | 71 | d8 | 31 | 15 |

|   | 3 | 04 | с7 | 23 | с3 | 18 | 96 | 05 | 9a | 07 | 12 | 80 | e2 | eb | 27 | b2 | 75 |

|   | 4 | 09 | 83 | 2c | 1a | 1b | 6e | 5a | a0 | 52 | 3b | d6 | b3 | 29 | e3 | 2f | 84 |

|   | 5 | 53 | d1 | 00 | ed | 20 | fc | b1 | 5b | 6a | cb | be | 39 | 4a | 4c | 58 | cf |

|   | 6 | d0 | ef | aa | fb | 43 | 4d | 33 | 85 | 45 | f9 | 02 | 7f | 50 | 3с | 9f | a8 |

|   | 7 | 51 | a3 | 40 | 8f | 92 | 9d | 38 | f5 | bc | b6 | da | 21 | 10 | ff | f3 | d2 |

|   | 8 | cd | 0с | 13 | ec | 5f | 97 | 44 | 17 | с4 | a7 | 7е | 3d | 64 | 5d | 19 | 73 |

|   | 9 | 60 | 81 | 4f | dc | 22 | 2a | 90 | 88 | 46 | ee | b8 | 14 | de | 5е | d0 | db |

|   | a | e0 | 32 | 3a | 0a | 49 | 06 | 24 | 5c | с2 | d3 | ac | 62 | 91 | 95 | e4 | 79 |

|   | b | e7 | c8 | 37 | 6d | 8d | d5 | 4e | a9 | 6с | 56 | f4 | ea | 65 | 7a | ae | 08 |

|   | С | ba | 78 | 25 | 2e | 1c | a6 | b4 | С6 | e8 | dd | 74 | 1f | 4b | bd | 8b | 8a |

|   | d | 70 | 3е | b5 | 66 | 48 | 03 | f6 | 0e | 61 | 35 | 57 | b9 | 86 | c1 | 1d | 9е |

|   | е | e1 | f8 | 98 | 11 | 69 | d9 | 8e | 94 | 9b | 1e | 87 | e9 | се | 55 | 28 | df |

|   | f | 8c | a1 | 89 | 0d | bf | е6 | 42 | 68 | 41 | 99 | 2d | 0f | b0 | 54 | bb | 16 |

Figure 1-11 The S-box: substitution value for a byte xy

SubSytes is a non-linear byte substitution applied on each byte of the State array using a substitution table, the S-box (Figure 1-10 - taken from [20]). Each byte  $S_{r,c}$  of the State array is represented by two digits xy which are used to address the S-box (Figure 1-11 - taken from [20]). The pointed value replaces  $S_{r,c}$  in the State array. The S-box is constructed by performing two transformations: taking the multiplicative inverse of the State array in the Galois Field  $GF(2^8)$  and applying an affine transformation over GF(2). Non-linearity is provided by the first one which minimizes the correlation between the input and the output and the second one increases the algebraic structure complexity of the operation. Both transformations are invertible; hence the S-box is invertible.

Figure 1-12 ShiftRows: the last three rows of the state array are cyclically shifted of *r*-byte

The *ShiftRows* transformation acts on the last three rows of the State array. They are cyclically shifted of a number equal to the value of the suffix r as shown in Figure 1-12 (taken from [20]). The objective of ShiftRows is to introduce diffusion through rows.

Figure 1-13 MixColumns multiplies each column of the State array by a constant matrix

The *MixColumns* transformation multiplies each column of the State array by a constant matrix (Figure 1-13 – taken from [20]). Considering each column as a polynomial over  $GF(2^8)$ , such transformation amounts to a multiplication modulo  $x^4 + 1$  with  $a(x) = x03 x^3 + x01 x^2 + x01 x + x02$ . The objective of MixColumns is to introduce diffusion through columns.

The AddRoundKey transformation is a simple bitwise XOR operation between each column of the State array and the corresponding column  $W_{n,c}$  in the Round Key matrix (provided by the key schedule) with n indicating the number of the round (Figure 1-14 – taken from [20]):

$$[S'_{0,c}, S'_{1,c}, S'_{2,c}, S'_{3,c}] = [S_{0,c}, S_{1,c}, S_{2,c}, S_{3,c}] \oplus W_{n,c}$$

for  $0 \le c \le 3$

Figure 1-14 AddRoundKey: Xor operation between each column of the State array and the corresponding column in the round key matrix

#### The key schedule:

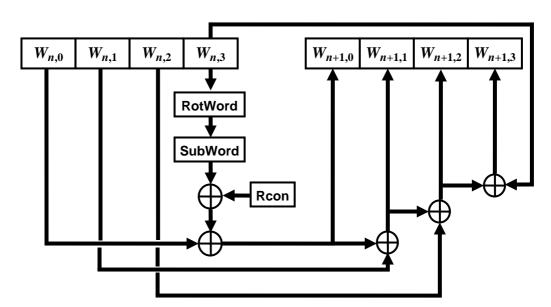

Figure 1-15 Computation of a round key

The key schedule provides the Round key required in each round of the data path; such a process is called the *key expansion*. The secret key is said to be expanded in *Nr* (number of rounds) round keys. For the AES-128 *Nr* is equal to 10. The architecture of the key schedule

is depicted in Figure 1-15. Round key 0 is the secret key and is used for the first XOR operation with the plaintext before the first round of the data path.

RotWord and SubWord are two transformations used in the key schedule. RotWord takes a word ( $a_0 \, a_1 \, a_2 \, a_3$ ) as input, cyclically permutes the bytes composing it, and outputs the word ( $a_1 \, a_2 \, a_3 \, a_0$ ). SubWord takes a word as input and applies the S-box to each of the four bytes. Rcon [1 to 10] is a constant array of ten words [20].

A Round key (n) is composed of four words  $W_{n,i}$ , with n as the suffix of the corresponding Round key and i as the position of the word in the Round Key.