## Flexible and Scalable Algorithm/Architecture Platform for MP-SoC Design of High Definition Video Compression Algorithms

M. Bonaciu

#### ▶ To cite this version:

M. Bonaciu. Flexible and Scalable Algorithm/Architecture Platform for MP-SoC Design of High Definition Video Compression Algorithms. Micro et nanotechnologies/Microélectronique. Institut National Polytechnique de Grenoble - INPG, 2006. Français. NNT: . tel-00086779

### HAL Id: tel-00086779 https://theses.hal.science/tel-00086779

Submitted on 19 Jul 2006

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

#### INSTITUT NATIONAL POLYTECHNIQUE DE GRENOBLE

| N°         | att | ribu | ıé p | ar l | a bi | blio | thè | que          |

|------------|-----|------|------|------|------|------|-----|--------------|

| $-1$ _ $1$ | -1  | _1.  | _1_  | _1_  | _1_  | 1_1  |     | $ _{\perp} $ |

#### THESE

pour obtenir le grade de

#### **DOCTEUR DE L'INPG**

Spécialité : Micro et Nano Electronique

préparée au Laboratoire TIMA dans le cadre de l'Ecole Doctorale « Electronique, Electrotechnique, Automatique, Télécommunications, Signal »

présentée et soutenue publiquement

par

#### **Marius Petru BONACIU**

le 4 Juillet 2006

#### Titre:

Plateforme flexible pour l'exploitation d'algorithmes et d'architectures en vue de la réalisation d'application vidéo haute définition sur des architectures multiprocesseurs mono puces

Directeur de thèse: Ahmed Amine JERRAYA

#### Jury:

M. Frédéric PÉTROT , Président

M. Eugenio VILLAR , Rapporteur

M. Christophe WOLINSKI , Rapporteur

M. Ahmed Amine JERRAYA , Directeur de thèse

M. Omar HAMMAMI , Examinateur

M. Peter NOWOTTNICK , Examinateur

## For my family

### Thanks

I want to thank Mr. Ahmed Amine JERRAYA, research director at CNRS and the leader of the SLS group from TIMA Laboratory, for directing my thesis. I want to thank him for helping me to discover the world of chips design, and to increase my knowledge in software design and video design. Moreover, I thank him for the time he spent providing me useful advices, either professional or personal, for supporting me in the difficult moments, and for trusting in my capabilities and me, since the beginning of our collaboration.

I thank Mr. Bernard COURTOIS, research director at CNRS and the director of the TIMA Laboratory, for providing me the possibility to do my thesis in this laboratory.

I want to thank Mr. Frédéric PÉTROT for accepting to be the president of the jury, with the occasion of my defense. Additionally, I thank him for all the interesting technical discussions that we had during my thesis.

I want to thank Mr. Eugenio VILLAR, Mr. Christophe WOLINSKI, Mr. Omar HAMMAMI and Mr. Peter NOWOTTNICK for accepting to be part of the jury for my defense. I want to thank all of them for their advices and remarks, regarding the thesis report, and those posed during the defense.

Big thanks go to Nacer-Eddine ZERGAINOH and Lorena ANGHEL, for their help during my first days at TIMA, and all their advices and directions that they provided during my entire thesis.

I want to specially thank Sonja AMADOU, for all her effort and time spent to correct my thesis report, specially the French part. I want to thank for her moral support, and all her advices. Not at last, I thank her for the hours of joking and laughing about all sorts of things. And yes, beer beats the wine.

Milioane de multumiri merg catre colegii mei romani din TIMA, pe care imi permit sa-i consider prieteni: Kati (zana zambareata), Cosmin (geniul nano-tevilor), Iuli (printesa kung-fu), Florin (bucale), Florin (olteanu), Bogdan (Star-Craft), Adi (vijelie), Claudia and Marius (casa de piatra si bafta in continuare), Vladimir (baga tare ardelene), Adina and Iulia (printesele din epilog). Am lasat-o la final pe Gabriela, careia vreau sa-i multumesc pentru tot suportul ei.

I want to thank all my colleagues from the SLS group: Abdel, Adriano, Aimen, Alex, Amer, Arif, Arnaud, Benaoumeur, Fred, Ferid, Giedrius, Hao, Ivan, Lobna, Lorenzo, Patrice, Pierre, Sang-Il, Sami, Wander, Wassim, Xi, Xavier, Yanick, Youngchul, Youssef and many others (I apologize if I forgot somebody). We have shared many months or years of our lives under the same scope, to become smarter and better persons. I will never forget you.

Many thanks to my colleagues from the other groups: Achraf, Ahcene, Amel, Fredi, Guillaume, Kamel, Luis, Manu, Sophie, and soooooo many others. We have shared a lot of coffee, many parties and trips, moments that have spiced up these 3 years of thesis. Thank you.

In final, vreau sa multumesc familiei mele. Fara voi, nu as fi reusit. Gandul ca sunteti alaturi de mine imi da putere sa trec peste momentele grele, si fac momentele frumoase si mai frumoase. Va iubesc, si am sa va iubesc mereu. Va multumesc din tot sufletul.

Plateforme flexible pour l'exploitation d'algorithmes et d'architectures en vue de la réalisation d'application vidéo haute définition sur des architectures multiprocesseurs mono puces

## Sommaire

| 1 | Introduction                                                              | 1  |

|---|---------------------------------------------------------------------------|----|

| 2 | L'algorithme d'encodage vidéo MPEG4                                       | 7  |

|   | Exploration d'algorithme et d'architecture á un haut niveau<br>bstraction | 11 |

| 4 | L'implémentation d'architecture pour l'encodeur MPEG4                     | 15 |

| 5 | Conclusions                                                               | 19 |

#### 1 Introduction

Ces dernières années, la complexité des puces a augmenté exponentiellement. La possibilité d'intégrer plusieurs processeurs sur la même puce représente un gain important, et a mène au concept du système multiprocesseur hétérogène sur puce (MP-SoC). Cet aspect a permis d'amplifier de manière significative la puissance de calcule fourni par ce type de puce. Il est même devenu possible d'intégrer des applications complexes sur une seule puce, applications qui nécessitent beaucoup de calculs, de communications et de mémoires.

Dans cette catégorie, on peut trouver les applications de traitement vidéo, comme la famille MPEG. En autre, ces algorithmes ont connu une évolution continue. Si les premières applications (ex. MJPEG, MPEG1) contenaient des algorithmes relativement simples, les nouvelles applications (ex. MPEG4, H264) contiennent des algorithmes complexes. Le travail présenté dans ce document est concentré sur l'algorithme de l'encodage vidéo MPEG4.

Des architectures MP-SoC complexes doivent être mises en application, afin d'assurer les demandes de fonctionnalité de l'encodeur vidéo MPEG4 (ex. codage en temps réel). Par la nature de l'algorithme, la fonctionnalité peut être dynamique (ex. la quantité de calculs exigée dépend de la nature de la vidéo d'entrée) et dépendante des paramètres/besoins de l'application (ex. résolution vidéo). De plus, en fonction du domaine d'application visé (ex. portables, home-cinema), différentes restrictions algorithmique et architecturales sont imposées. Le concepteur est donc confronté à la tâche difficile de trouver et de mettre en application la bonne solution, choisissant dans un grand espace de solutions possible. Aussi, l'implémentation d'algorithme et d'architecture est un processus long et difficile. Tous ces aspects compliquent le processus de conception et de mise en application de l'encodeur vidéo MPEG4 sur une architecture MP-SoC, ce qui augmente le délai de mise sur le marché et diminue considérablement la qualité des résultats.

Afin d'obtenir un encodeur vidéo MPEG4 sur une architecture MP-SoC, il y a 3 défis majeurs que le concepteur doit relever :

#### 1) l'implémentation de l'algorithme de l'encodeur vidéo MPEG4

En raison de la grande complexité de l'algorithme de l'encodeur MPEG4, une quantité significative de code doit être écrit. L'application finale de l'encodeur MPEG4 pourrait être choisie en fonction des différents domaines d'applications (ex. portables) ou de configurations (ex. résolution vidéo), exigeant tous une fonctionnalité d'algorithme différente. Par ailleurs, en mettant l'algorithme d'encodage MPEG4 dans une architecture multiprocesseurs, le besoin de différentes fonctionnalités parallèles et «pipelines» pourrait s'imposer. Implémenter différents algorithmes d'encodeur MPEG4 pour chacun de ces cas représente un effort considérable an temps et en main d'oeuvre.

#### 2) trouver les configurations correctes d'algorithme et d'architecture

Afin d'obtenir une architecture MP-SoC efficace contenant l'algorithme de l'encodeur MPEG4, le concepteur doit trouver et utiliser les bonnes configurations d'algorithme et d'architecture. Pur les deux, il existe un grand nombre de paramètres/configurations à partir desquels le concepteur doit choisir les meilleurs. De, les configurations d'algorithme sont dépendantes des demandes du client, mais également des configurations choisies pour l'architecture. La même situation sont pour les configurations d'architecture, dont certaines dépendent des demandes du client", mais aussi des configurations choisies pour l'algorithme.

Comme simple exemple, il pourrait être nécessaire d'utiliser en fonction de la résolution vidéo (paramètre d'algorithme), un nombre et un type spécifiques de processeurs fonctionnant en parallèle (paramètres d'architecture) pour assurer la puissance de calcul requise. Ceci impose l'adaptation de l'algorithme pour ce niveau de parallélisme (paramètre d'algorithme), qui pourrait augmenter les demandes de trafic pour l'architecture de communication (paramètre d'architecture). Si ce n'est pas possible, le concepteur pourrait être amené à diminuer la qualité d'image codée (paramètre d'algorithme). Cette modification réduira la puissance de calcul requise, menant probablement au besoin de réduire le nombre de processeurs (paramètres d'architecture), ce qui pourrait exiger de réadapter l'algorithme pour un autre niveau de parallélisme (paramètre d'algorithme), et ainsi de suite. Il est à noter que, les bons paramètres d'algorithme sont directement liés aux paramètres d'architecture, et vice-versa. C'est pourquoi, toutes les explorations devraient se concentrer sur ces deux

aspects (algorithme et architecture) à la fois. Prise en considération d'un seul de ces aspects n'est pas toujours suffisante.

Ce procédé d'exploration, qui doit être répété plusieurs fois, prend beaucoup de temps. Ceci est dû au fait que :

- a) Le concepteur pourrait avoir à implémenter manuellement et re-implémenter plusieurs fois les modèles d'algorithme et d'architecture, en utilisant des configurations spécifiques d'un algorithme/architecture choisies dans un grand espace de solutions, et vérifier chaque fois si les résultats obtenus arrivent à fournir les résultats d'exécutions requis. Ceci représente un travail difficile et répétitif, et prend beaucoup des temps.

- b) En grande partie, la simulation des modèles d'algorithme et d'architecture utilisés dépend du niveau d'abstraction auquel les modèles d'algorithme et d'architecture sont décrits. Au niveau RTL (Register Transfer Level), le temps de simulation est très long.

- c) La précision des résultats de simulation dépend également du niveau d'abstraction utilisé. Cependant, elle représente une aspect critique quelque soit le niveau d'abstraction utilisé, pour rassurer le concepteur au sujet de la qualité de ses résultats et mesures.

#### 3) implémentation de l'architecture RTL qui contient l'application de l'encodeur MPEG4

Implémenter manuellement l'architecture MP-SoC pour l'encodeur MPEG4, jusqu'au niveau RTL, pourrait nécessiter plusieurs mois de temps de travail. En raison de la grande quantité de détails architecturaux de bas niveau qui doit être prise en considération (ex. les interfaces, les signaux, les protocoles, des synchronisations, décodage d'adresses, les arbitres, etc.), et du fait que cette architecture doit "servir" de façon pertinente à la bonne fonctionnalité de l'algorithme. Par exemple, si *Tâche1* doit envoyer des données à *Tâche2*, l'architecture doit faire de telle sorte que ceci va fonctionner correctement. A tout ce temps de travail est ajouté le temps nécessaire pour simuler, valider et corriger l'architecture obtenue, processus qui pourrait doubler le temps pour obtenir l'architecture finale. Comme il

sera montré dans ce document, le temps total a pris presque 6 mois pour notre expérimentation. Ainsi, dans le cas où l'architecture et l'algorithme auraient été implémenté à partir d'un mauvais choix de configurations, il est possible que le processus entier de développement doive être recommencé afin d'utiliser une autre configuration. Ceci augmentera le délai de mise sur le marché, et en réalité il pourrait représenter l'échec du projet.

En outre, le concepteur pourrait devoir implémenter l'application de l'encodeur MPEG4 sur différents types d'architectures. Par exemple, il doit implémenter l'algorithme de l'encodeur MPEG4 plus l'architecture MP-SoC entière, ou il doit juste implémenter l'encodeur MPEG4 sur une architecture MP-SoC déjà existante. Le concepteur devra donc se familiariser avec plusieurs flots de conception spécifiques à chacun de ces cas.

Les contributions présentées dans ce document sont 3 solutions qui pourraient aider à réduire ces 3 problèmes :

#### 1) Encodeur MPEG4 Parallèle

Puisque l'encodeur MPEG4 est une application qui nécessite une grande quantité de calculs, l'intégration sur des architectures parallèle/pipeline pourrait être nécessaire. Nous devons être capables d'adapter facilement l'algorithme en fonctions des différentes fonctionnalités parallèle/pipeline. De plus, pour chacune de ces architectures, l'algorithme devrait être facilement adaptable pour différents paramètres algorithmiques (ex. résolution vidéo, qualité, précision d'évaluation de mouvement, bitrates, etc.).

Ce document présente un encodeur MPEG4 flexible, qui peut être facilement adapté pour différents types de paramètres d'algorithme, mais également différents niveaux de parallélisme/pipeline.

## 2) Exploration à haut niveau d'algorithme et d'architecture pour l'encodeur MPEG4 avec des paramètres taillés sur mesure

Pour trouver les configurations optimales d'algorithme et d'architecture, le concepteur doit être capable d'examiner et d'explorer rapidement différentes configurations. Ceci est possible si :

- a) Le concepteur peut automatiquement obtenir les modèles d'algorithme et d'architecture nécessaires à l'exploration de l'espace des solutions.

- b) Le temps nécessaire pour faire les mesures de performance est diminué en faisant l'exploration d'architecture à un haut niveau d'abstraction, et pas au niveau RTL, en ignorant beaucoup de détails d'architecture de bas niveau. Ainsi, en ne prenant pas en compte tous les détails, les simulations deviennent plus rapides.

- c) La précision d'estimation est assurée en estimant les temps de calculs et les temps de communications.

Ce document propose une méthode d'exploration d'algorithme et d'architecture à haut niveau pour l'encodeur MPEG4 avec des paramètres taillés sur mesure, qui pressentent les avantages décrits précédemment. En utilisant cette approche, plusieurs configurations d'algorithme et d'architectures peuvent être explorées plus vite qu'avec à une exploration faite au niveau RTL. Aussi, à un haut niveau d'abstraction, en ignorant beaucoup de détails de bas niveau, la vitesse de simulation, validation et correction est sensiblement augmentée.

# 3) Flot commun utilisé pour l'implémentation rapide de l'encodeur MPEG4 sur différents types d'architectures

Quand l'encodeur MPEG4 doit être mis en application dans un MP-SoC, l'architecture visée peut être complètement nouvelle, ou déjà existante (habituellement une architecture basée sur des processeurs). Utiliser différents flots d'implémentations pour ces deux cas pourrait se révéler inefficace. Ceci est dû principalement par le besoin de transférer les résultats après chaque étape de développement entre des environnements multiples (outils), l'incompatibilité entre les outils et les spécifications, les limitations d'outils, etc. L'obtention du résultat final pourrait demander beaucoup de temps, et pourrait générer une quantité significative d'erreurs.

Ce document propose un flot commun pour l'implémentation de l'encodeur MPEG4 sur MP - SoC pour différents types d'architectures. De plus, parce que plusieurs étapes de ce flot sont automatisées, il aide à obtenir les résultats finaux en peu de temps. En utilisant

cette approche, plusieurs architectures MP-SoC complètes au niveau RTL ont été obtenues. En outre, en utilisant le même flot, l'encodeur MPEG4 a également été implémenté sur une architecture quadri-processeurs déjà existante.

#### 2 L'algorithme d'encodage vidéo MPEG4

La norme de l'encodeur MPEG4 a été développée par le Motion Picture Experts Group autour de 1994. Depuis, beaucoup de variantes de MPEG4 ont été réalisées, dont les plus populaires sont OpenDivX, DivX et XviD. Entre chacune de ces réalisations, il y a quelques différences en ce qui concerne les précisions de calculs et la qualité d'image compressée. Cette variation peut exister, parce que les spécifications MPEG4 ne limite pas de façon stricte les calculs de toutes les étapes dans l'algorithme. Cette souplesse est une des nombreuses raisons pour les quelles le MPEG4 est devenu si populaire.

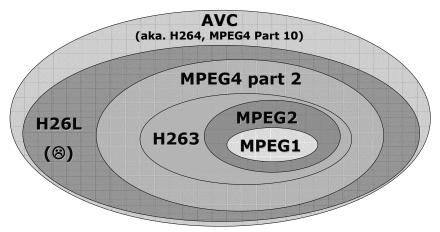

Une autre raison pour laquelle le MPEG4 est populaire est sa capacité de compression. Les expériences pratiques ont prouvé que tandis que l'encodeur vidéo MPEG2 (utilisé dans le DVD) compresse un film de 2 heures dans 4.7Gbytes, le MPEG4 est capable de compresser le même film sur un CD-ROM de 700Mbytes. Il est vrai qu'avec le MPEG2, la qualité d'image obtenue est meilleure qu'avec le MPEG4, mai la qualité d'image obtenu est acceptable. Par contre, l'inconvénient de l'encodeur MPEG4 est sa complexité algorithmique. Comparant l'algorithme du MPEG4 à celui du MPEG2, la complexité du MPEG4 est environ 3 fois plus grande que le MPEG2. Mais, cet inconvénient ne nuit pas au succès du MPEG4.

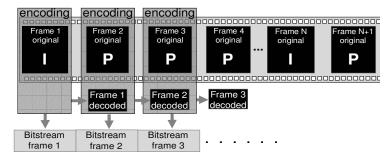

Le principe sous-jacent est de comprimer seulement les différences spatio-temporelles entre les images consécutives. Ainsi, au lieu de sauvegarder une image complète, l'algorithme sauvegarde seulement les différences entre cette image et l'image précédente. Ces différences sont déterminées en utilisant des algorithmes complexes, et le résultat de l'algorithme est un film fortement comprimé, connu sous le nom de MPEG4 bitstream. Même le facteur de compression peut être modifié basé sur les préférences des utilisateurs, en augmentant ou en diminuant la qualité d'images stockées dans le bitstream.

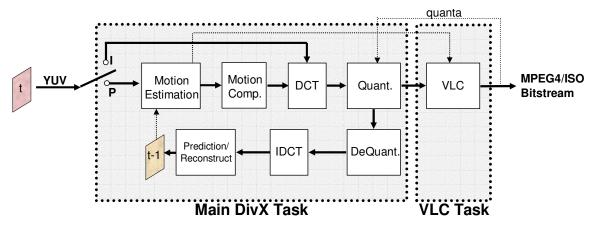

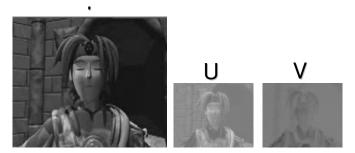

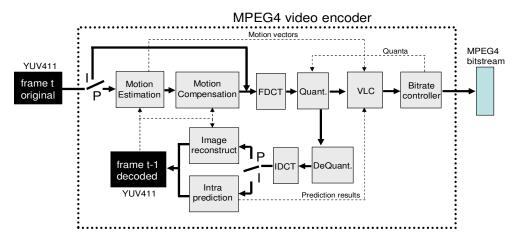

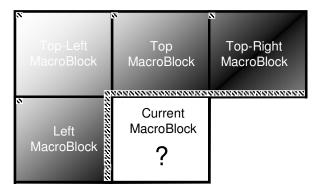

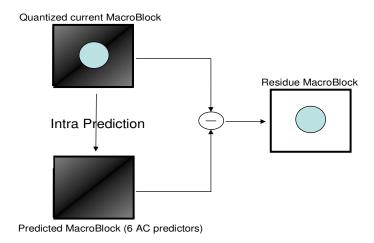

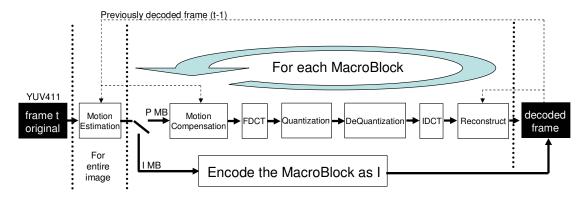

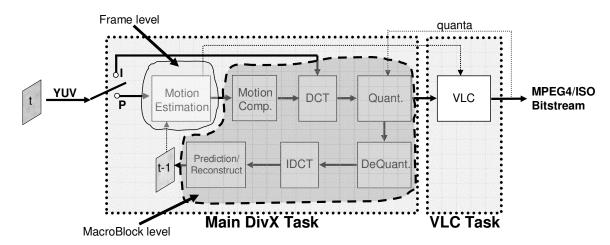

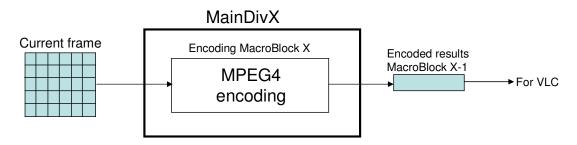

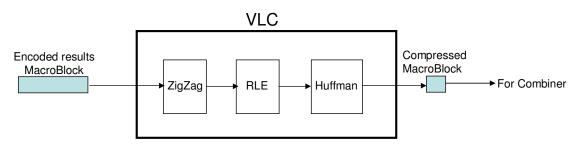

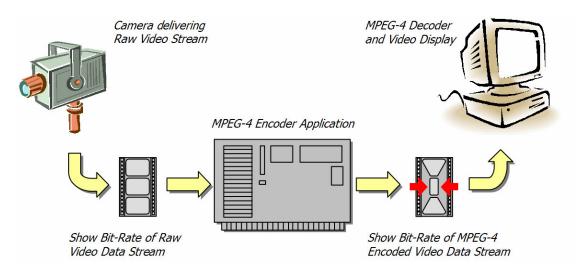

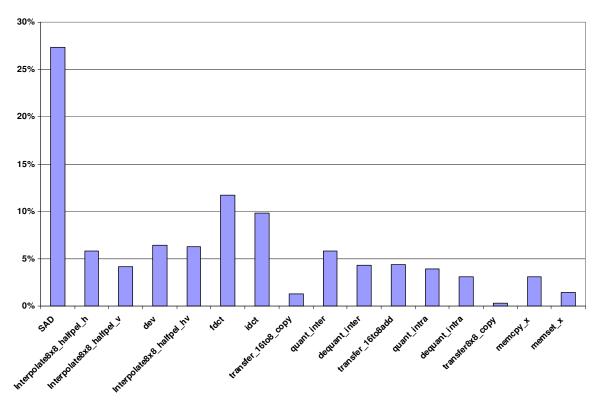

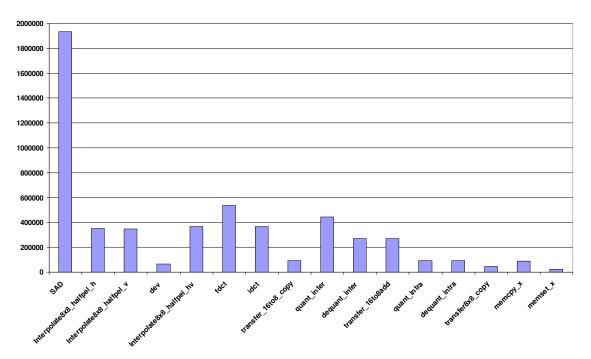

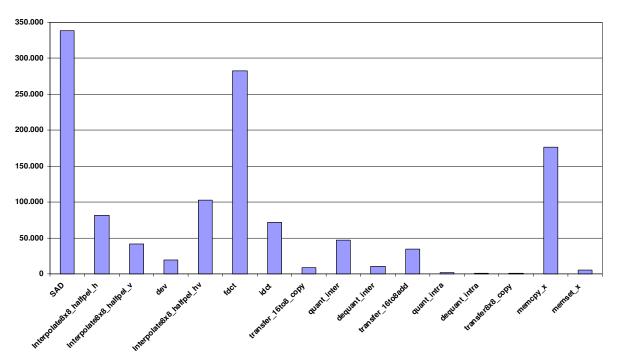

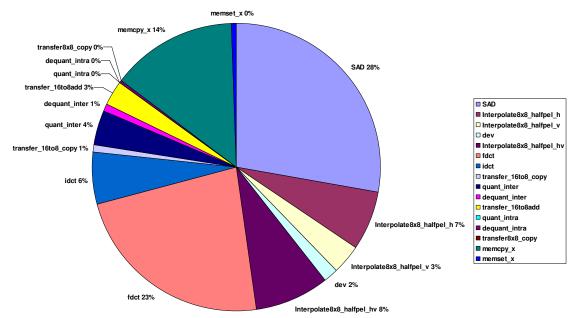

Un diagramme simplifié de l'algorithme d'encodage MPEG4 est présenté dans la Figure 1. Le but de chaque fonction sera détaillé plus tard dans ce document. Ces fonctions peuvent être distribués en 2 catégories : les fonctions de traitement d'image (groupées dans la tâche *MainDivX*), et les fonctions de compression (groupées dans la tâche *VLC*). La tâche

*MainDivX* reçoit l'image courante non compressée, et détermine les différences spatiotemporelles entre cette image et l'image précédente de la vidéo. Ces résultats (qui ne sont pas encore compressée) sont envoyés à la tâche *VLC*, qui les comprime, pour obtenir à la fin le MPEG4 bitstream final. La taille du bitstream MPEG4 est habituellement beaucoup plus petite que la taille d'image originale en entrée.

Figure 1. Diagramme de l'algorithme d'encodage MPEG4

Par sa nature, l'algorithme d'encodeur MPEG4 est un algorithme séquentiel. Cependant, le comportement de chacune de ses fonctions internes dépend fortement de vidéo à l'entrée et des paramètres de l'algorithme utilisé. Dans le cas où la vidéo d'entrée contient des images et des séquences complexes (ex. quelqu'un qui court dans la forêt), l'algorithme exécutera plus de calculs. Dans le cas où la vidéo d'entrée contient des images et des séquences simples (ex. une interview devant un mur blanc), l'algorithme exécutera moins de calculs. En réalité, le concepteur ne devrait pas faire ses implémentations basées sur un seul type de vidéo d'entrée. L'algorithme MPEG4 devrait être capable de supporter n'importe quels types de vidéo, complexe ou simple.

Il y a beaucoup de paramètres d'algorithme, proposés par les spécifications ISO de MPEG4, avec lesquelles le concepteur a la possibilité d'ajuster les comportement/résultats de l'algorithme. Ces paramètres sont : résolution, frame\_rate, bitrate, précision de l'estimation de mouvement, surface de recherche de mouvement, images Progressives/Entrelacées, détection de changement de scène, intervalle de quantification, type de quantification, rate\_delay, etc. Chacun de ces paramètres a un impact, plus ou moins im-

portant, sur les résultats et le comportement d'algorithme. De plus, en ajustant un de ces paramètres, aucune modification de code de l'algorithme ne devrait être exigée.

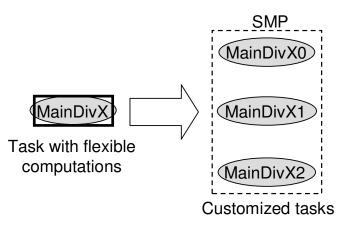

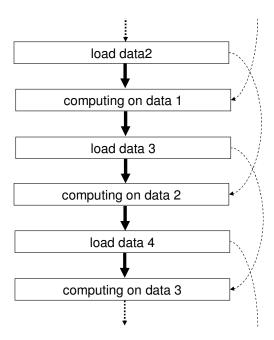

Cependant, quand l'algorithme est destiné pour supporter une fonctionnalité parallèle/pipeline (habituellement requise pour des architectures multiprocesseur), le code séquentiel de l'algorithme doit être réécrit pour supporter ce parallélisme/pipeline. En changeant le niveau de parallélisme/pipeline, il y a un risque que le code doive encore être réécrit pour cette nouvelle exigence. Pour éviter cela, nous avons adapté l'algorithme original MPEG4 séquentiel pour supporter différents niveaux de parallélisme/pipeline en rajoutant un paramètre additionnel qui contient le niveau désiré du parallélisme. En modifiant ce paramètre, le code de l'algorithme ne change pas, seulement son comportement.

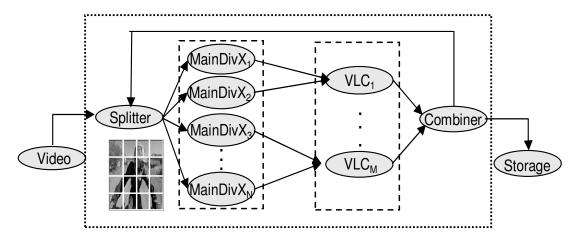

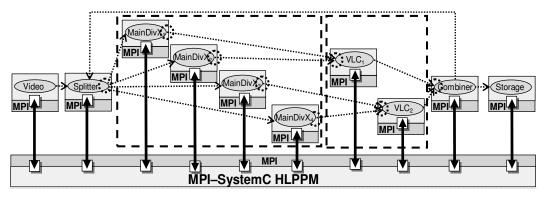

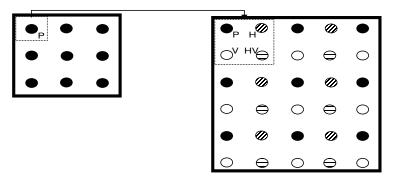

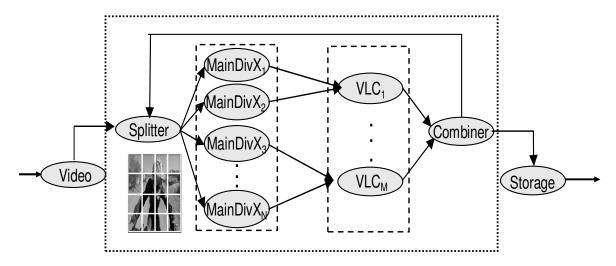

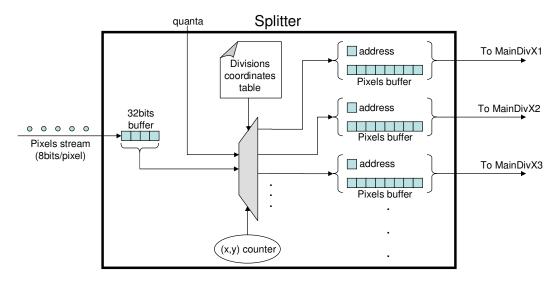

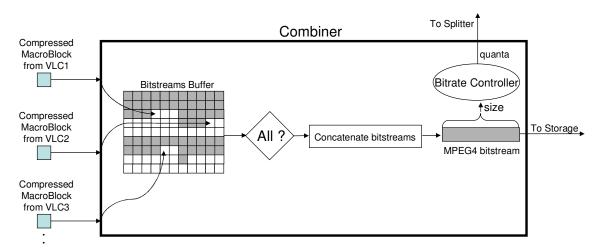

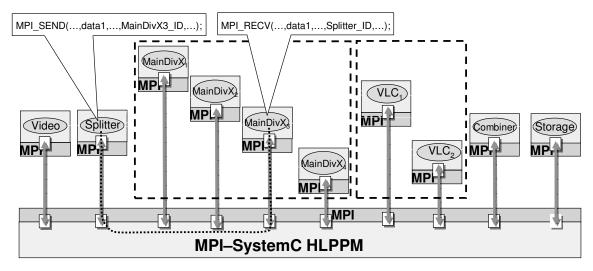

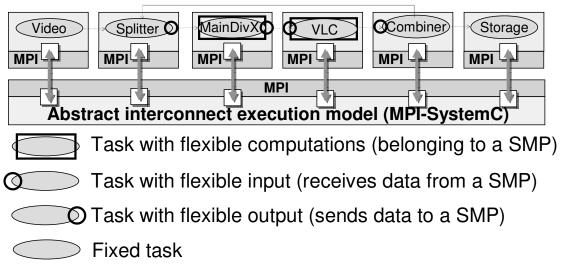

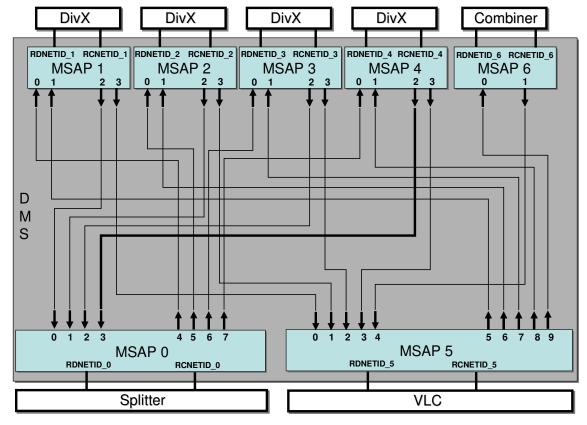

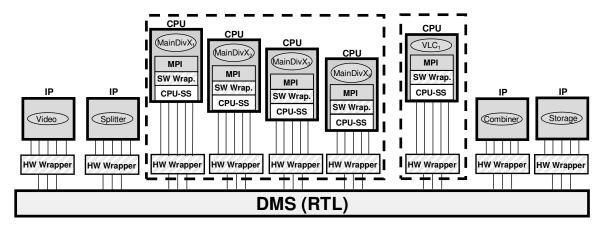

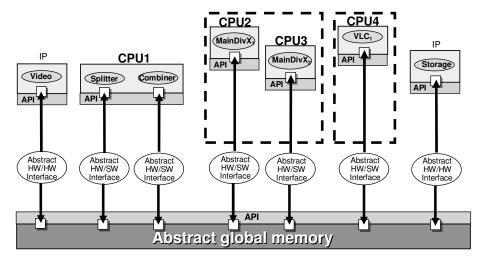

Ceci a été possible en découpant les images d'entrée dans des sub-images multiples (secteurs), et en exécutant plusieurs instances de la même tâche *MainDivX* et *VLC* pour ces secteurs (Figure 2). De plus, pour chacun de ces instances, un comportement pipeline a été ajouté. L'image est fournie par une tâche de test *Video*, image qui sera découpée en plusieurs secteurs par une tâche *Splitter*. Chacun de ces secteurs est traité par une tâche *MainDivX*. Leurs résultats sont ensuite comprimé par plusieurs tâches *VLC*, chacune d'elles obtenant une "petite partie" du MPEG4. Enfin, la tâche *Combiner* reçoit toutes ces "petites parties", les trie et les enchaîne finalement pour obtenir le MPEG4 bitstream final, correspondant à l'image courante. Après, ce bitstream est envoyé à une autre tâche de test, appelée *Storage*, qui simule le comportement d'un support de stockage (ex. HDD).

Figure 2. Structure général d'algorithme MPEG4 parallélise/pipeline

Ainsi, l'algorithme se comporte comme plusieurs SMP (MainDivX-SMP et VLC-SMP). Cependant, il est à noter que, quand l'image est divisée en un seul secteur, l'algorithme se comportera comme l'algorithme séquentiel, ce qui est utile lorsque le concepteur ne veut pas utiliser de parallélisme dans l'algorithme.

Comme résultat, nous avons obtenu un algorithme MPEG4 flexible, qui supporte tous les paramètres imposés par les spécifications ISO de MPEG4, en plus de nos paramètres additionnels utilisés pour ajuster le comportement de l'algorithme pour différents niveaux de parallélisme/pipeline. Ainsi, l'algorithme peut être facilement adapté et utilisé pour l'exploration de différentes architectures MP-SoC contenant différents nombres de processeurs.

#### 3 Exploration d'algorithme et d'architecture á un haut niveau d'abstraction

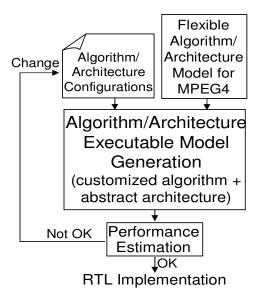

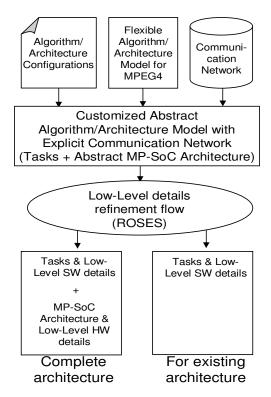

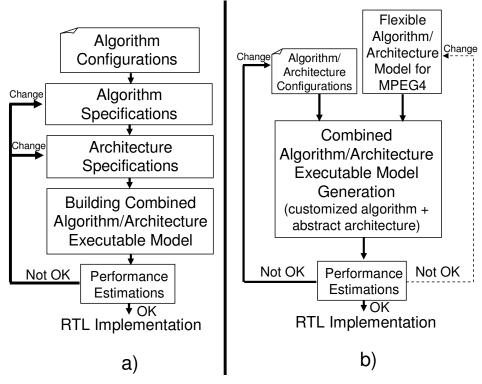

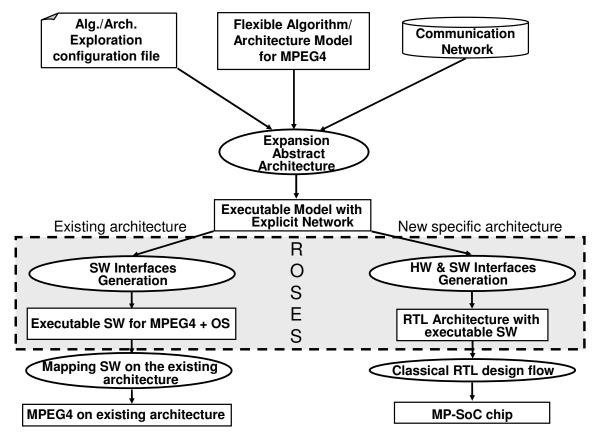

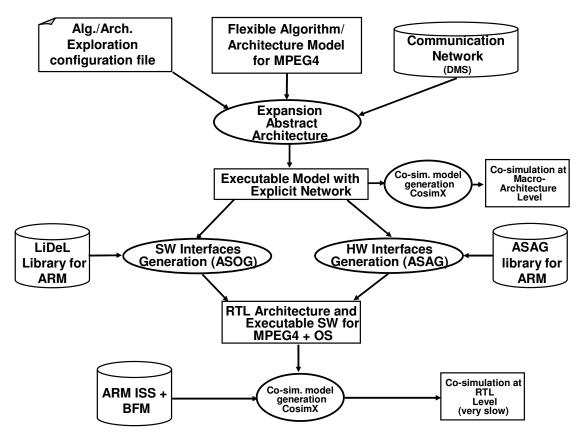

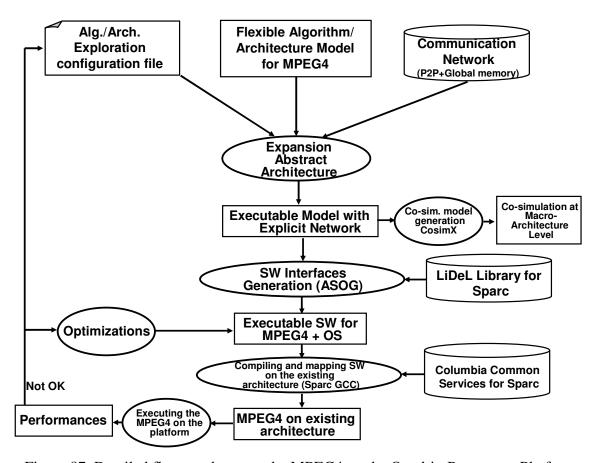

Implémenter une architecture MP-SoC jusqu'au niveau RTL (ce qui nécessite temps de conception très long), à partir d'un ensemble de paramètres mal choisis (ex. nombres/type de processeurs, ou topologie de communication), pourrait être onéreux. N'importe quelle modification des paramètres utilisés pourrait nécessiter des modifications complexes d'algorithme et d'architecture, ou dans le pire des cas l'obligation de re-implémenter complètement l'algorithme et l'architecture. Peu de produits peuvent justifier un tel budget de conception, et une solution pour augmenter les performances est de faire l'exploration d'algorithme et d'architecture à un haut niveau d'abstraction, avant l'étape d'implémentation de l'architecture RTL. La Figure 3 présente notre flot d'exploration d'algorithme et d'architecture à un haut niveau d'abstraction.

Figure 3. Exploration d'algorithme et d'architecture a un haut niveau d'abstraction

Les entrées de ce flot sont un ensemble de paramètres de Configurations d'Algorithme/Architecture (que le concepteur veut explorer) et un Modèle Flexible d'Algorithme/Architecture pour l'Encodeur MPEG4. En utilisant ce modèle et les configurations d'algorithme/architecture, différents Modèles Exécutable Taillés sur Mesure d'Algorithme/Architecture peuvent être obtenus. Chaque fois que les Configurations d'Algorithme/Architecture sont changées, un nouveau Modèle Exécutable Taillé sur Mesure

d'Algorithme/Architecture peut être obtenu. Enfin, ce modèle est utilisé pour des évaluations de performances. Si les résultats obtenus ne satisfont pas aux exigences du concepteur, il doit réadapter les Configurations d'Algorithme/Architecture, et régénérer un nouveau Modèle Exécutable Taillé sur Mesure d'Algorithme/Architecture. Cette itération sera répètee jusqu'à ce que le concepteur trouve une solution de Configurations d'Algorithme/Architecture pour laquelle les performances estimées répondent aux exigences. Plus tard, ces configurations seront utilisées pour l'implémentation d'architecture RTL.

Les *Configurations d'Algorithme/Architecture* (Figure 4) contient un ensemble de paramètres distribués en 2 catégories : Paramètres d'algorithme et Paramètres d'architecture.

| Paramètres d'algorithme                | Paramètres d'architecture             |

|----------------------------------------|---------------------------------------|

| Niveau de Parallélisme/Pipeline        | Nombre de processeurs                 |

| Résolution vidéo                       | Type de processeurs                   |

| Frame_rate                             | Partitionnement HW/SW                 |

| Bitrate                                | Topologie de communication            |

| Key_frame                              | Type d'arbitrage                      |

| Précision de l'estimation de mouvement | Taille de messages                    |

| Surface de recherche de mouvement      | Taille de données                     |

| Mode Progressif/Entrelacer             | Latence de transfert de données       |

| Détection de changement de scène       | Latence d'initialisation de transfert |

| Intervalle de quantification           | Latence de fin de transfert           |

|                                        |                                       |

Figure 4. Configurations d'algorithme et d'architecture à explorer

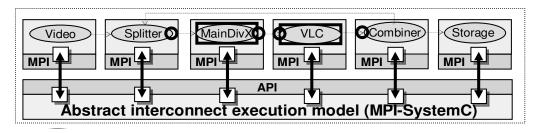

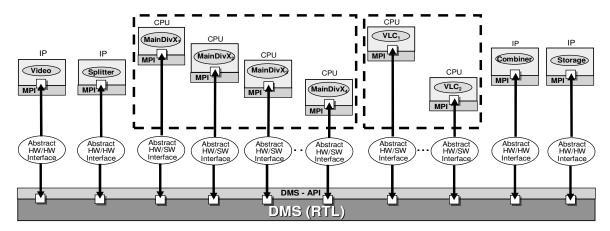

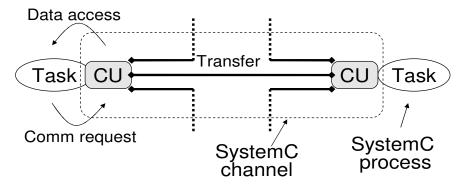

Le Modèle Flexible d'Algorithme/Architecture pour MPEG4 (Figure 5) représente un modèle template à haut niveau (décrit en utilisant une langage macro) à partir duquel différents modèles taillés sur mesure peuvent être obtenus (par une macro génération). Ce modèle est constitué de plusieurs modules SystemC, contenant les tâches de l'algorithme MPEG4 flexible présenté avant. Ces tâches communiquent en utilisant un Modèle d'Exécution d'Interconnections Abstrait, qui est en charge de la gestion des communications et les synchronisations entre les tâches. Tous les détails de bas niveau (ex. OS, Adaptateurs, RTL signale, etc.) sont complètement abstraits. Plus de détails au sujet de ce modèle sont présentés plus tard dans ce document.

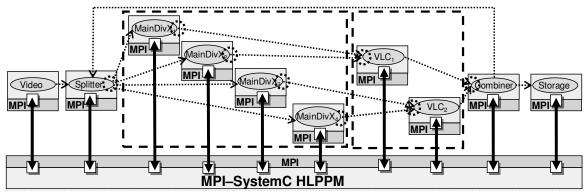

Figure 5. Modèle Flexible Algorithme/Architecture pour l'encodeur MPEG4

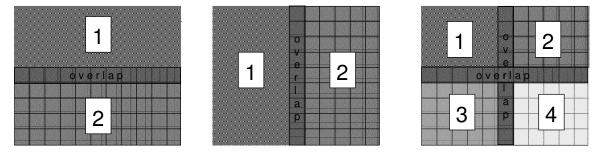

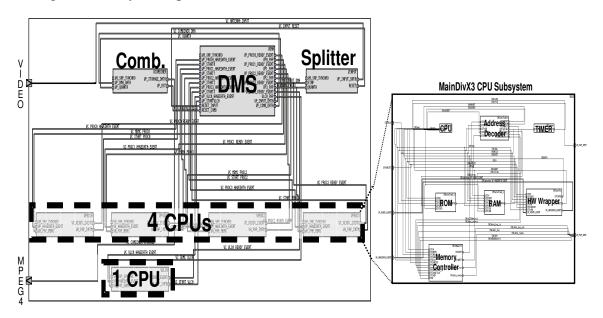

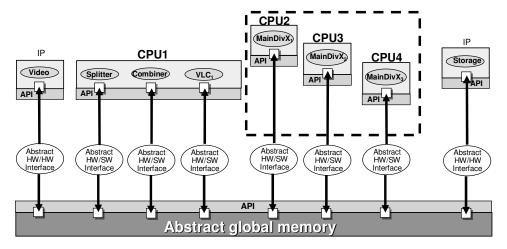

En utilisant ce modèle et les configurations d'algorithme/architecture, différents modèles taillés sur mesure peuvent être obtenus. Un exemple obtenu d'un tel modèle est présenté dans la Figure 6. Dans ce cas, un modèle exécutable a été macro-généré contenant 4 tâches *MainDivX* et 2 tâches *VLC*. Le code appartenant à chacune des tâches de l'application a été adapté basé sur les paramètres d'algorithme choisis (ex. résolution vidéo, bitrate), et les aspects architecturaux (ex. types de processeurs, tailles de messages) ont été taillés sur mesure basé sur les paramètres d'architecture. En d'autres termes, ce modèle représente un modèle d'algorithme/architecture fixe et déjà taillé sur mesure en tenant compte des préférences du concepteur.

Figure 6. Modèle Exécutable Taillé sur Mesure d'Algorithme/Architecture pour l'Encodeur MPEG4 utilisé pour les évaluations de performances

Afin de faire les évaluations de performances, des annotations de temps seront employées pour les calculs et communications, des temps qui dépendent fortement des configurations d'algorithme/architecture utilisées. Par l'exécution de ce modèle taillé sur mesure et annotée avec le temps d'exécution, une estimation de ses performances peut être déterminée. Si ces performances ne répondent pas aux exigences, le concepteur va réadapter les *Configurations d'Algorithme/Architecture*, obtenant un nouveau *Modèle Taillé sur Mesure*

d'Algorithme/Architecture avec les résultats d'évaluation de performances, de ce nouveau modèle.

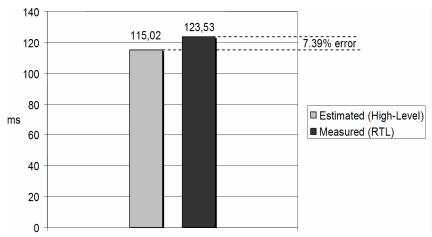

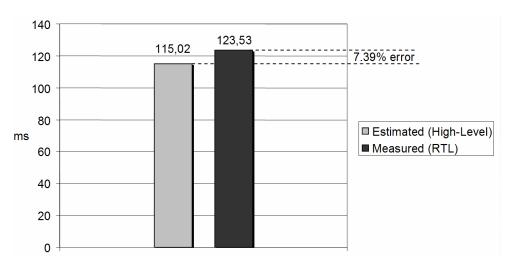

En utilisant cette approche, différentes configurations des architectures pour l'encodeur MPEG4 ont été explorées avec succès en peu de temps, pour différentes résolutions vidéo, frame\_rates, bitrates, nombre de processeurs, types de processeurs, configurations de communication, etc. Cette exploration s'est avérée sensiblement plus rapide comparée à l'exploration au niveau RTL. Ainsi, les performances estimées à haut niveau se sont avérées assez proches des performances mesurées au niveau RTL, ce qui confirme la possibilité d'utiliser cette approche pour nos expériences. Les points suivants one été réalisés :

- a) La nécessité d'explorer un grand espace de solution a été facilitée en générant automatiquement différents Modèles Exécutable Taillés sur Mesure d'Algorithme/Architecture. Ceux-ci peuvent être obtenus à partir d'un *Modèle Flexible d'Algorithme/Architecture pour MPEG4* unique, qui a fourni la possibilité générer automatiquement l'architecture abstraite basée sur un ensemble de *Configurations d'Algorithme/Architecture* choisies par le concepteur.

- b) Une simulation rapide est possible en faisant l'exploration d'architecture à un haut niveau d'abstraction. En ignorant beaucoup de détails d'architecture des bas niveaux dans le Modèle Exécutable Taillé sur Mesure d'Algorithme/Architecture, la simulation devient rapid.

- c) Pour satisfaire au besoin de résultats précis d'estimations, on utilise l'*Exploration d'Algorithme/Architecture a un Haut Niveau d'Abstraction* qui fournit des résultats d'estimations avec une précision élevée en termes des temps de calculs et des communications, par annotations basés sur les *Configurations d'Algorithme/Architecture*. De plus, l'exploration capture les calculs et les communications fonctionnant ensemble, pour estimer les exécutions du système entier.

#### 4 L'implémentation d'architecture pour l'encodeur MPEG4

Lorsqu'il implémente l'encodeur MPEG4 dans un MP-SoC, le concepteur a deux possibilités :

- a) Il peut implémenter l'architecture MP-SoC complète de l'encodeur. Dans ce cas, le concepteur doit implémenter les tâches de l'algorithme MPEG4 ainsi que les détails logiciels de plus bas niveau (i.e. OS) qui assurent la fonctionnalité des tâches de plus haut niveau sur les processeurs. De plus, il doit implémenter l'architecture MP-SoC avec tous les détails matériels de bas niveau (ex. adaptateurs, sous-système de processeurs). Les résultats obtenus doivent ensuite être exécutés pour une validation finale par une approche de co-simulation précise au cycle près.

- b) l'encodeur MPEG4 peut être implémenté sur une architecture déjà existante. Dans ce cas, le concepteur doit implémenter seulement les tâches de l'algorithme d'encodage MPEG4 ainsi que les détails logiciels de bas niveau. L'implémentation matérielle n'est plus nécessaire puisque l'architecture existe déjà. Pour la validation finale, les résultats seront exécutés nativement sur l'architecture existante.

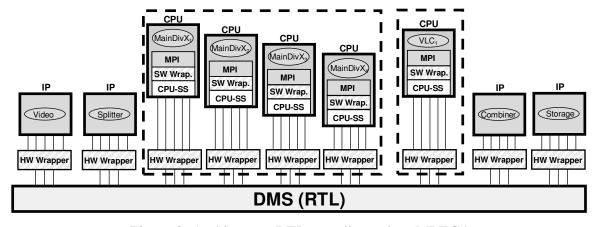

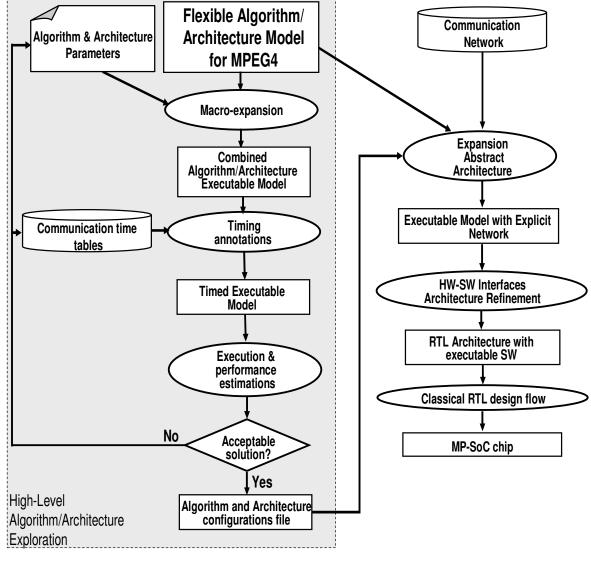

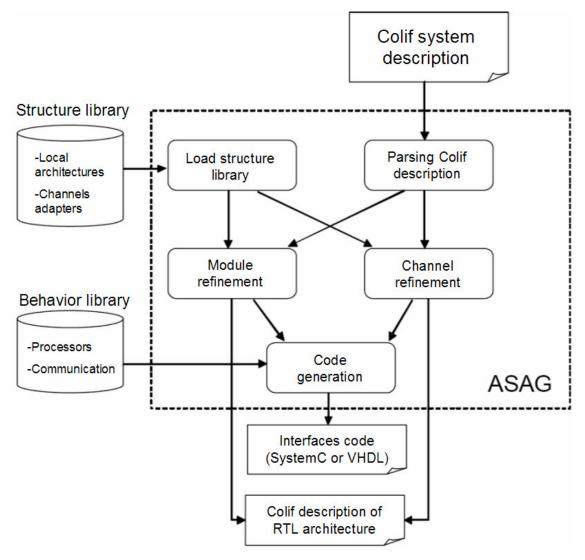

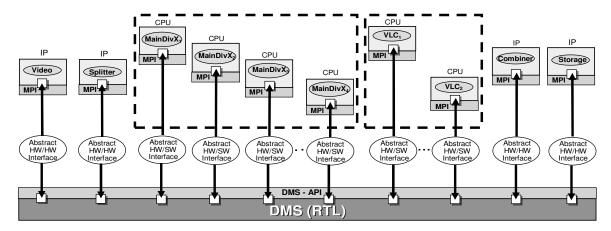

Dans le cadre de notre approche, pour ces deux possibilités, nous pouvons utiliser comme entrées les mêmes spécifications d'algorithme et d'architecture. Il s'agit plus exactement de la même *Configuration d'Algorithme/Architecture* obtenue après la phase d'exploration algorithme/architecture de haut niveau présentée précédemment, et du même *Modèle Flexible d'Algorithme/Architecture pour encodeur MPEG4* (Figure 7).

Figure 7. Flot proposé pour l'implémentation de l'encodeur MPEG4 sur différentes architectures

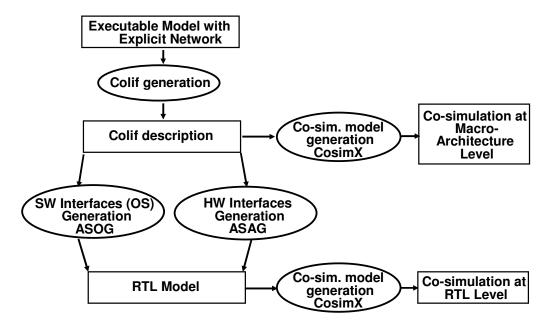

Toute comme dans le cas de l'exploration algorithme/architecture, un modèle taillé sur mesure devra être obtenu. La seule différence est, dans ce cas, que le modèle obtenu utilisera maintenant un réseau de communication explicite en tant qu'infrastructure d'interconnections, un réseau de communication provenant d'une bibliothèque contenant différents types de réseaux de communication. Le modèle obtenu est appelé *Modèle Abstrait Taillé sur Mesure d'Algorithme/Architecture avec Réseau Explicite*. Un exemple de tel modèle est présenté à la Figure 8.

Figure 8. Modèle Abstrait Taillé sur Mesure d'Algorithme/Arch. avec Réseau Explicite

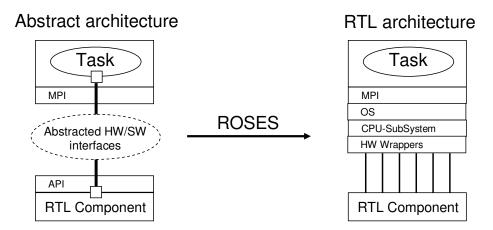

Comme nous pouvons le remarquer, les tâches des applications ont été personnalisées et sont prêtes, ainsi que le réseau de communication. Dans Figure 8, nous avons utilisé le réseau de communication DMS, qui sera décrit en détail plus loin dans ce document. Les seuls objets qui sont encore abstraits sont les interfaces HW/SW et HW/HW qui contiennent les détails d'implémentation de bas niveau du logiciel et du matériel.

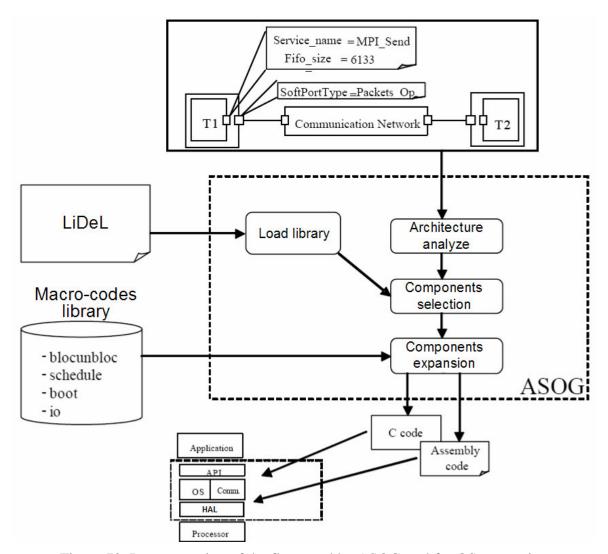

Pour obtenir ces détails de bas niveau, nous avons utilisé le flot ROSES développé au laboratoire TIMA par le groupe SLS. Ce flot reçoit comme entrée l'architecture abstraite mentionnée ci-dessus et utilise plusieurs outils internes afin d'obtenir/raffiner et valider les détails de bas niveau logiciels et matériels. Plus de détails au sujet de ce flot seront présentés ultérieurement dans ce document.

Selon l'architecture ciblée, il est possible d'obtenir deux types de résultats :

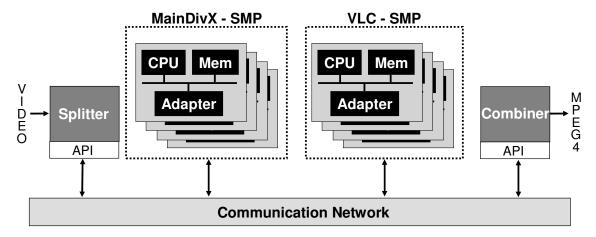

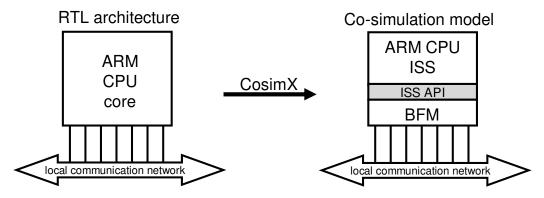

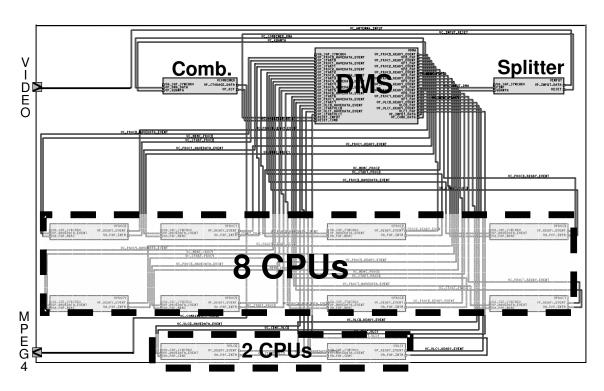

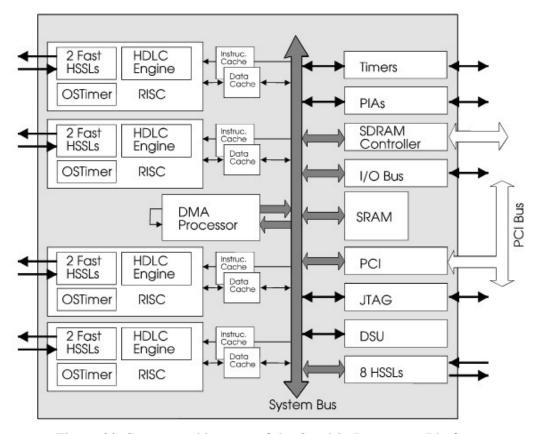

a) Il est possible d'obtenir une architecture MP-SoC complète au niveau RTL et qui contient l'algorithme d'encodage MPEG4. Dans ce cas, le flot ROSES est utilisé afin d'obtenir tous les détails de bas niveau, HW et SW. Le résultat final, appelé architecture RTL, contient les tâches des l'application avec les détails logiciels de bas niveau (i.e. OS, aussi connu sous le nom d'adaptateurs logiciels), ainsi que la totalité de l'architecture MP-SoC au niveau RTL qui contient le réseau de communication, adaptateurs HW, sous-systèmes CPU (architecture locale du processeurs avec composants auxiliaires RTL). La figure 9 illustre une architecture de MP-SoC obtenue au niveau RTL qui contient l'encodeur MPEG4.

Figure 9. Architecture RTL pour l'encodeur MPEG4

Le modèle complet est un modèle exécutable décrit en SystemC et ses performances peuvent être mesurées en utilisant une co-simulation classique précise au niveau cycle. Le principal désavantage est que la co-simulation est très lente. Selon nos expériences, il a fallu plus de 4 heures pour co-simuler le processus d'encodage d'une seule image du film. L'avantage est qu'il est possible d'analyser le comportement de n'importe quel composant de l'architecture.

b) Si l'encodeur MPEG4 doit être implémenté sur une architecture existante, seules les tâches de l'application et les détails logiciels de bas niveau doivent être obtenus. Lors de nos expériences, l'architecture existante était une plateforme quadriprocesseurs, contenant 4 processeurs Sparc. Sur une telle architecture, il est suffisant de faire une compilation croisée des tâches et des détails logiciels de bas niveau et ensuite d'allouer et d'exécuter les fichiers binaires résultants sur la plateforme. Puisque l'application est entièrement exécutée nativement, ceci confère comme avantage que les mesures de vitesse d'exécution et de performance sont élevées (temps réel). Le principal désavantage est la difficulté d'analyser le comportement des composants matériels. Cependant, ceci n'affecte pas l'analyse du logiciel et les postoptimisations du logiciel.

#### 5 Conclusions

L'implémentation d'encodeurs vidéo, un encodeur MPEG4 par exemple, dans des MP-SoC est souvent nécessaire dans de nombreuses applications : télécommunication mobile, home cinéma, vidéo surveillance, etc. Etant donné que chacune de ces applications imposent différents algorithmes, contraintes architecturales et besoins, l'implémentation d'encodeur MPEG4 dans un MP-SoC doit faire face à de nombreux défis.

Ce document a présenté une nouvelle approche qui a été utilisée avec succès pour l'implémentation d'un encodeur MPEG4 dans un MP-SoC avec différentes configurations d'algorithmes et d'architectures. Ceci a été possible grâce à notre solution, parce que:

- a) un Algorithme d'Encodeur MPEG4 Flexible a été implémenté avec 2 SMP pour des tâches nécessitant beaucoup de calcul. Cet algorithme peut être facilement paramétré (ex. résolution, frame-rate, bitrate, précision de l'estimation de mouvement, type de quantification, etc.) et aussi parallélisé, en ajustant simplement le niveau de parallélisme dans chacun de SMP. De cette manière, l'algorithme obtenu peut-être facilement configuré pour plusieurs besoins de l'application, mais également pour différentes architectures avec un petit ou un grand nombre de processeurs.

- b) une Exploration d'Algorithme/Architecture à un Haut Niveau d'Abstraction avec des paramètres taillés sur mesure a été utilisée afin d'explorer rapidement plusieurs configurations d'algorithmes/architectures. Ceci nous a permis de trouver les bons paramètres satisfaisant aux besoins bien avant l'implémentation de l'architecture RTL. En faisant l'exploration à un niveau élevé, beaucoup de détails de l'architecture de bas niveau ont été complètement abstraits, rendant la simulation d'autant plus rapide. En outre, les modèles de simulation ont été automatiquement obtenus à partir d'un unique *Modèle d'Algorithme/Architecture Flexible pour l'Encodeur MPEG4*, à partir duquel beaucoup de models de simulation à haut niveau peuvent êtres obtenus automatiquement en utilisant une approche de macro génération. L'estimation de performance a été réalisée en insérant des annotations de temps pour les calculs et les communications dans les modèles de simulation résultants. A partir de notre ex-

périence, la précision de cette approche d'exploration de haut niveau s'est montrée suffisamment proche des mesures réelles à bas niveau, ce qui a donc confirmé la possibilité d'utiliser notre approche pour cette application.

c) une approche à base de composants a été utilisée pour l'implémentation de l'encodeur MPEG4 aussi bien sur des architectures MP-SoC complètes, que sur des architecture existantes. Cette approche est basée sur le flot ROSES, développée dans le Groupe SLS du laboratoire TIMA. Le principal objectif de ce flot est de raffiner les détails de bas niveaux (interfaces Matériel/Logiciel) qui étaient abstraits lors de l'exploration algorithme/architecture de haut niveau. En utilisant le flot présenté dans ce document, l'encodeur MPEG4 a été implémenté avec succès dans plusieurs architectures MP-SoC au niveau RTL. La même approche a été utilisée pour l'implémentation de l'encodeur MPEG4 sur une architecture quadri-processeurs existante, pour différentes résolutions, frame-rate, bitrates, etc.

Basé sur l'approche présentée dans ce document, plusieurs autres applications vidéo ont également été implémentées avec succès : encodeur MPEG1, décodeur MPEG1, décodeur MPEG2 et décodeur MPEG4. Ceci a été possible en adaptant le *Modèle d'Algorithme/Architecture Flexible pour MPEG4* pour supporter des paramètres supplémentaires de type d'algorithmes et d'encodeur/décodeur. Il est également prévu d'étendre cette approche au format H.264. Toutefois, l'extension de cette approche vers d'autres domaines d'applications que la vidéo reste un sujet de recherche ouvert pour un travail futur.

## Flexible and Scalable Algorithm/Architecture Platform for MP-SoC Design of High Definition Video Compression Algorithms

Marius Petru BONACIU

TIMA Laboratory, SLS Group

## Summary

| 1 |     | Introduction                                                                                           | 1      |

|---|-----|--------------------------------------------------------------------------------------------------------|--------|

|   | 1.1 | Introduction about the MP-SoC as a solution for the implementation of vidapplications on a chip        |        |

|   | 1.2 | Motivations                                                                                            | 3      |

|   | 1.3 | Objectives                                                                                             | 6      |

|   |     |                                                                                                        |        |

|   | 1.4 | State of the art                                                                                       |        |

|   |     | Contributions                                                                                          |        |

|   | 1.  | 5.1 Flexible modeling style to describe the algorithm and architecture specifications to MPEG4 encoder |        |

|   | 1.  | 5.2 High-Level algorithm/architecture exploration for MPEG4 encoder with custom                        | 10     |

|   |     | parameters                                                                                             | 10     |

|   | 1.  | 5.3 Common flow used for the implementation of MPEG4 encoder on different targe architectures          |        |

|   | 16  | Document outline                                                                                       | 12     |

|   | 1.0 | Document outline                                                                                       | ••• 12 |

| 2 |     | MPEG4 video encoder algorithm                                                                          | 13     |

|   | 0.1 | _                                                                                                      |        |

|   |     | Introducing the MPEG4 video encoder                                                                    |        |

|   |     | Usual method of using the MPEG4 video encoder                                                          |        |

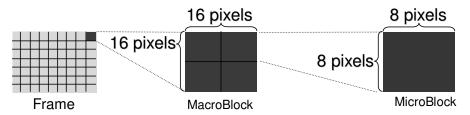

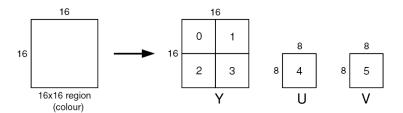

|   |     | 7.3 Describing the YUV411 video format used as input by the MPEG4 video encode.                        |        |

|   |     | Presenting the structure of the MPEG4 video encoder algorithm                                          |        |

|   |     | 7.5 Different types of encoding principles used for the video's frames                                 |        |

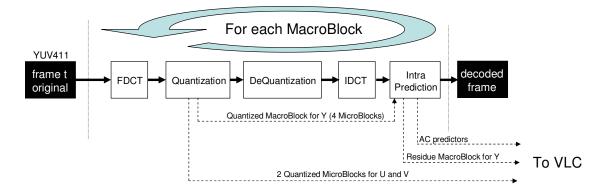

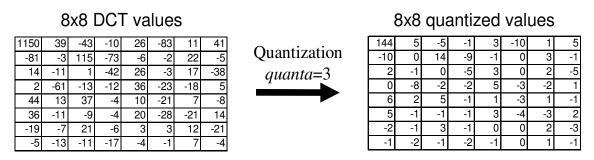

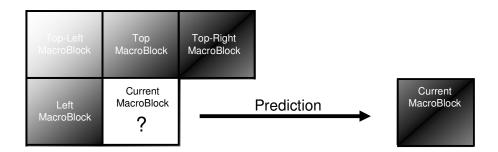

|   | 2.2 | Describing the encoding principle for an I frame                                                       | 20     |

|   |     | 2.1 Introducing the concept of encoding an I frame                                                     |        |

|   |     | 2.2 Representation of the algorithm and functions used for encoding an I frame                         |        |

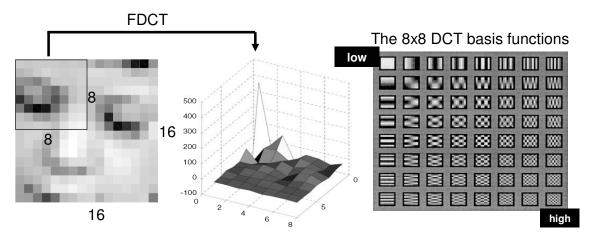

|   |     | 2.3 Describing the Fast Discrete Cosine Transformation (FDCT)                                          |        |

|   | 2.  | 2.4 Describing the Quantization function                                                               |        |

|   | 2.  | 2.5 Describing the DeQuantization function                                                             |        |

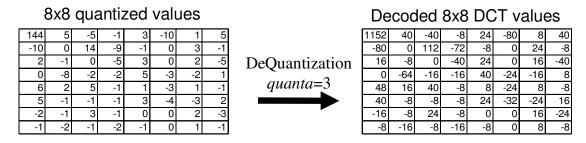

|   | 2.  | 2.6 Describing the Inverse Discrete Cosine Transformation (IDCT)                                       | 24     |

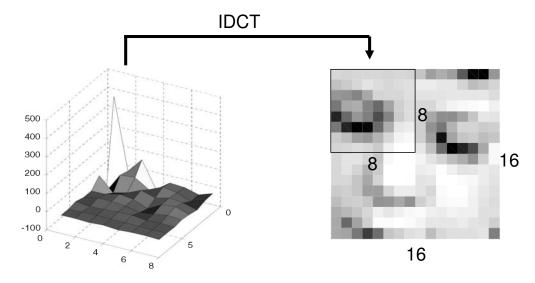

|   | 2.  | 2.7 Describing the Intra Prediction function                                                           |        |

|   | 2.3 | Describing the encoding principle for a P frame                                                        | 28     |

|   |     | 3.1 Introducing the concept of encoding the P frame                                                    | 28     |

|   |     | R.2 Representation of the algorithm and functions used for encoding a P frame                          |        |

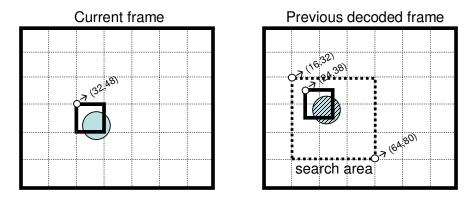

|   |     | 3.3 Describing the Motion Estimation function                                                          |        |

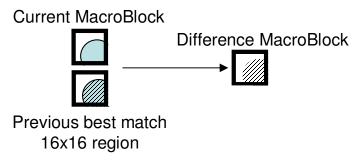

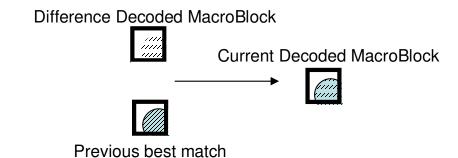

|   |     | 3.4 Describing the Motion Compensation function                                                        |        |

|   |     | 2.5 Describing the FDCT, Quantization, DeQuantization and IDCT functions for the                       |        |

|   |     | MacroBlock                                                                                             |        |

|   | 2.  | 3.6 Describing the Reconstruction function                                                             |        |

|   | 2.4 | Detailed description of the VLC and Bitrate Controller                                                 | 35     |

|   | 2.  | Description of the compression phase done by the MPEG4 video encoder                                   | 35     |

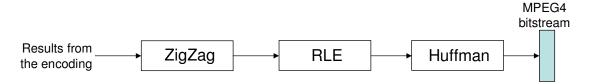

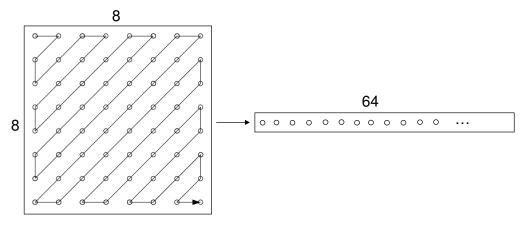

| 2.4.2   | Applying ZigZag reordering on a MacroBlock                                                              | 35          |

|---------|---------------------------------------------------------------------------------------------------------|-------------|

| 2.4.3   | Compressing the ZigZag-ed MacroBlock using RLE and Huffman compression                                  | 36          |

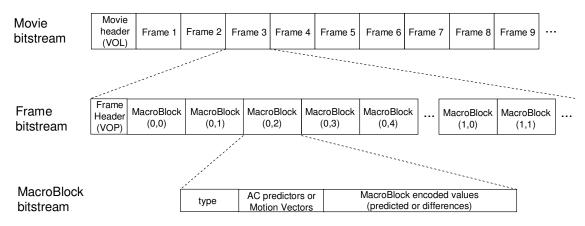

| 2.4.4   | Structure of the MPEG4 bitstream                                                                        | 37          |

| 2.4.5   | Quantization adjustment by Bitrate Controller for the next frame encoding                               | 38          |

| 2.5 MF  | PEG4 algorithm parameters                                                                               | 38          |

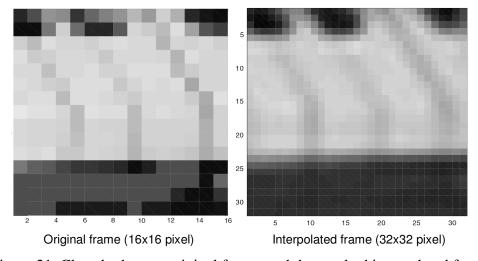

| 2.5.1   | Image resolution parameter                                                                              |             |

| 2.5.2   | Frame rate parameter                                                                                    | 39          |

| 2.5.3   | Keyframe rate parameter                                                                                 | 40          |

| 2.5.4   | Compression rate (bitrate) parameter                                                                    |             |

| 2.5.5   | Quantization range parameter                                                                            |             |

| 2.5.6   | Rate control delay parameter                                                                            |             |

| 2.5.7   | Computations precision parameter                                                                        |             |

| 2.5.8   | Scene change detection parameter                                                                        |             |

| 2.5.9   | Compression mode parameter                                                                              |             |

| 2.5.10  |                                                                                                         |             |

| 2.6 Co  | nclusions                                                                                               | 45          |

| 3 Fle   | exible modeling style to represent the Combined Algorithm/                                              |             |

|         | rure Model for MPEG4                                                                                    | . 47        |

|         | callelism/pipeline support for the MPEG4 video encoder algorithm                                        |             |

| 3.1.1   |                                                                                                         |             |

| 3.1.2   | Objectives                                                                                              |             |

| 3.1.3   | State of the art                                                                                        |             |

| 3.1.4   | Contributions                                                                                           |             |

|         | oposed MPEG4 video encoder supporting different parallel/pipeline                                       |             |

|         |                                                                                                         | 52          |

| 3.2.1   | fligurations                                                                                            |             |

| 3.2.1   | Presenting the approach used for inserting parallelism and pipeline support into the MPEG video encoder |             |

| 3.2.2   | Describing the method used for dividing the input image into multiple smaller are                       |             |

| 3.2.2   | required for the parallelized MainDivX tasks                                                            |             |

|         |                                                                                                         |             |

|         | xible Architecture with 2 SMPs                                                                          |             |

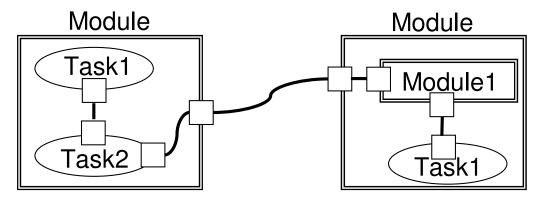

|         | Global view of the Flexible Architecture with 2 SMPs                                                    |             |

| 3.3.2   | Describing the functionality of the Splitter                                                            |             |

| 3.3.3   | Describing the functionality of the MainDivX                                                            |             |

| 3.3.4   | Description of the functionality of the VLC                                                             |             |

| 3.3.5   | Describing the functionality of the Combiner                                                            |             |

|         | mbined Algorithm/Architecture Executable Model                                                          | 63          |

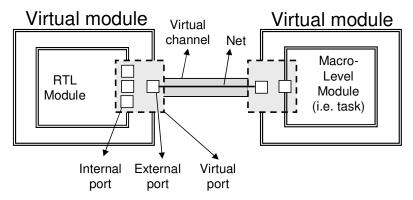

| 3.4.1   | Concept of Combined Algorithm/Architecture Executable Model                                             | 63          |

| 3.4.2   | SystemC used for the description of the Combined Algorithm/Architecture Executable Model                | 66          |

| 3.4.3   | Combined Algorithm/Architecture Executable Model using MPI-SystemC HLPP                                 |             |

| 3.5 Fle | xible Algorithm/Architecture Model for MPEG4                                                            | <b> 7</b> 0 |

| 3.5.1   | Concept of tasks with Flexible Computations                                                             |             |

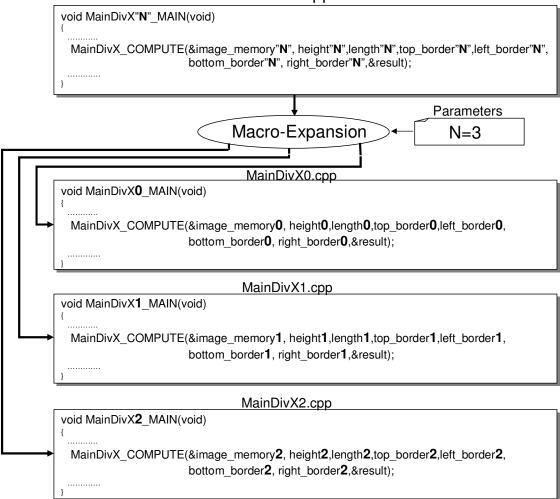

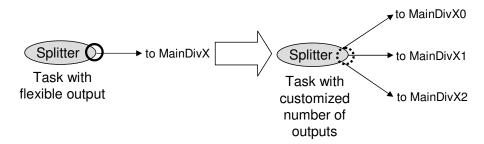

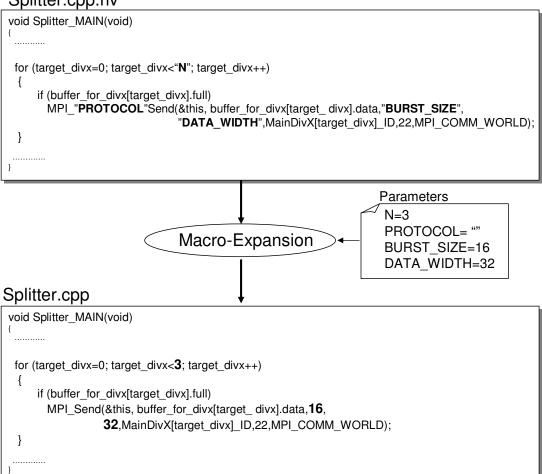

| 3.5.2   | Concept of tasks with Flexible Output                                                                   | 73          |

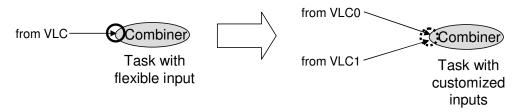

| 3.5.3   | Concept of tasks with Flexible Input                                                                    |             |

| 3.5.4   | Flexible Algorithm/Architecture Model for MPEG4                                                         |             |

| 3.5.5   | Algorithm and Architecture configurations                                                               | 78          |

| 3.6 Co                                                                                                              | nclusions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 8                                         |

|---------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------|

| Hi                                                                                                                  | gh-Level Algorithm/Architecture Exploration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 8                                         |

|                                                                                                                     | inciple of the High-Level Algorithm/Architecture Exploration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                           |

| 4.1.1                                                                                                               | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                           |

| 4.1.2                                                                                                               | Solution space for MPEG4 encoder on MP-SoC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                           |

| 4.1.3                                                                                                               | State of the art - classical exploration flow                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                           |

| 4.1.4                                                                                                               | Contribution of the proposed High-Level Algorithm/Architecture Exploration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                           |

| 4.2 Hi                                                                                                              | gh-level Algorithm/Architecture Exploration flow for MPEG4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 8                                         |

| 4.2.1                                                                                                               | Obtaining the Timed Executable Model required for performance estimations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                           |

| 4.2.2                                                                                                               | Performance estimations and architecture exploration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 9                                         |

| 4.2.3                                                                                                               | Validation of the high-level simulation results                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | وِ9                                       |

| 4.3 Ex                                                                                                              | periments and results analysis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 9                                         |

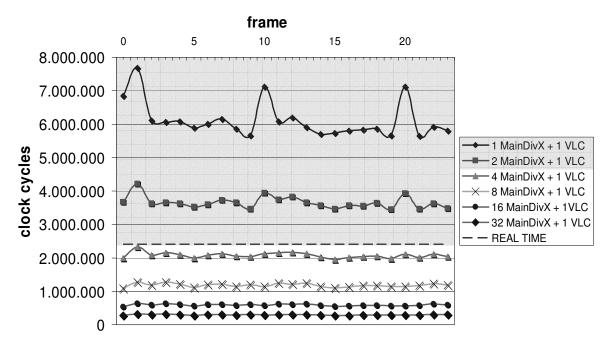

| 4.3.1                                                                                                               | Performance estimated for QCIF, using ARM7, 60MHz                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                           |

| 4.3.2                                                                                                               | Performance estimated for QCIF, using ARM946E-S, 4kI\$, 4kD\$, 60MHz                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                           |

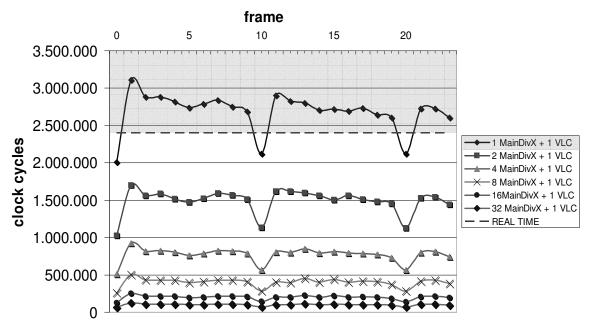

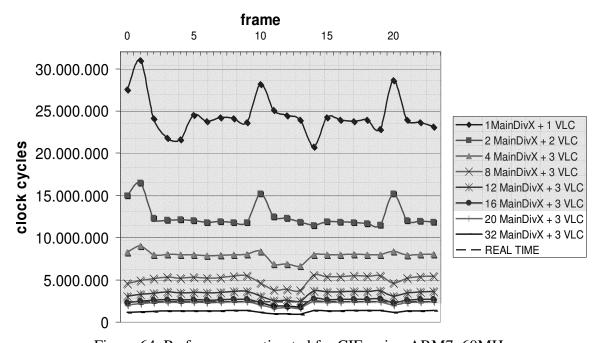

| 4.3.3                                                                                                               | Performance estimated for CIF, using ARM7, 60MHz                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                           |

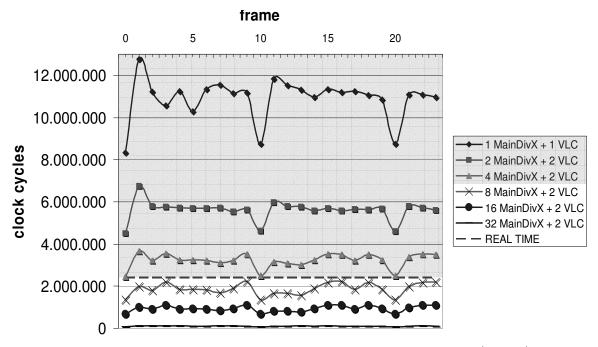

| 4.3.4                                                                                                               | Performance estimated for CIF, using ARM946E-S, 4kI\$, 4kD\$, 60MHz                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                           |

|                                                                                                                     | Results analysis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                           |

| 4.3.5                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                           |

| 4.4 Co  M.                                                                                                          | PEG4 video encoder architecture implementation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 10<br>10                                  |

| M. M. S.1 Int                                                                                                       | PEG4 video encoder architecture implementation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 10 10 cture                               |