### Génération Automatique de Modèles de Simulation pour la Validation de Systèmes Hétérogènes Embarqués

A. Sarmento

#### ▶ To cite this version:

A. Sarmento. Génération Automatique de Modèles de Simulation pour la Validation de Systèmes Hétérogènes Embarqués. Micro et nanotechnologies/Microélectronique. Université Joseph-Fourier - Grenoble I, 2005. Français. NNT: . tel-00010903

#### HAL Id: tel-00010903 https://theses.hal.science/tel-00010903

Submitted on 8 Nov 2005

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

## UNIVERSITE JOSEPH FOURIER- GRENOBLE I SCIENCES, TECHNOLOGIE & MEDECINE

| N  | ° at | tribı | ıé p | oar l | a b | iblio | othè | que | ; |

|----|------|-------|------|-------|-----|-------|------|-----|---|

| /_ | _/_  | _/_   | _/_  | _/_   | _/_ | _/_   | _/_  | _/_ | _ |

#### THESE

pour obtenir le grade de

#### DOCTEUR DE l'UNIVERSITE JOSEPH FOURIER

Spécialité : Microélectronique

préparée au laboratoire TIMA dans le cadre de l'Ecole Doctorale d'« Electronique, Electrotechnique, Automatique, Télécommunications, Signal »

par

#### Adriano Augusto DE MORAES SARMENTO

le 28 octobre 2005

Titre:

Génération automatique de modèles de simulation pour la validation de systèmes hétérogènes embarqués

\_\_\_\_\_

Directeur de Thèse : Ahmed Amine Jerraya Codirecteur : Wander Oliveira Cesario

#### **JURY**

M. Frédéric Pétrot , Président

M. El Mostapha Aboulhamid , Rapporteur

M. Jean-Paul Calvez , Rapporteur

M. Ahmed Amine Jerraya , Directeur

M. Wander Oliveira Cesário , Codirecteur

M. Philippe Kajfasz , Examinateur

#### Remerciements

Cette thèse est dédiée aux nombreuses personnes qui m'ont aidé pendant le long séjour que j'ai passé en France. D'abord je voudrais remercier Andrea et José pour avoir parcouru ce chemin avec moi. Leur amour, tendresse et patience ont été essentiels pour que je puisse finir cette thèse, surtout pendant les moments plus difficiles. Je vous aime.

Je remercie mes parents Teresinha et Osvaldo pour leur amour et soutien. Grâce à eux j'ai été capable de faire une thèse. Leurs conseils, leurs vies et surtout leur soutien m'ont beaucoup inspiré.

Je remercie également mon frère Carlos et ma belle sœur Verônica pour leur amitié et soutien, ainsi que le cadeau le plus important qu'ils m'ont offert : ma très belle nièce Gabi.

Je tiens à remercier mon oncle José Costa pour m'avoir encouragé pendant toute ma vie et pour m'avait traité comme si j'avais été son fils.

Je n'ai peux pas oublier de remercier ma belle mère Lilia qui nous a toujours aidé et m'a souvent gâté en me préparant la délicieuse mousse aux fruits de la passion. Mes remerciements vont également à mon beau père Teo, ma belle sœur Carol et à mon très beau petit neveu Luca.

J'adresse mes remerciements au couple João et Mariana pour leur amitié et pour tout ce qu'ils ont fait pour que la soutenance puisse avoir lieu. Si je suis arrivé à soutenir ma thèse, c'est grâce à leur gentillesse et patience. Je profite pour m'excuser des nombreux problèmes auxquels ils ont dû faire face pour déposer mon dossier. Je souhaite à tous les deux bon courage et bonne continuation.

Merci à ma chère Sonja! Elle a toujours été présente pour m'aider et pour soutenir mon moral. Sa gaieté va beaucoup me manquer.

Un grand merci à Patricia Ouhamou et Fred Hunsinger pour les très bons moments qu'on a vécu ensemble dans le bureau 422. Je vous remercie aussi pour avoir corrigé les nombreuses fautes de français de ma thèse. De plus vous m'avez beaucoup appris sur la culture française.

Un merci spécial à ma chère Lobna. On est passé par les mêmes problèmes, surtout la définition de nos sujets de thèse, mais on a bien survécu et on a passé des bons moments. Je suis très content que tu vas bientôt soutenir ta thèse. Je te souhaite bonne chance et bonne continuation

Je remercie également les autres thèsards du groupe SLS: Arnaud, Aimen, Benaoumeur, Ivan, Lorenzo Pieralisi, Marcio, Marius, Wassim, Youssef et Youngchul. Nos discussions m'ont beaucoup aidé à mieux comprendre le monde très complexe des systèmes embarqués. Bonne courage pour la suite.

Un grand remerciement à Damien, Gabriela et Arif pour leur gentillesse lorsque je suis arrivé dans le groupe SLS.

Je ne peux pas oublier de dire merci à tout les « stars » du foot : Aimen, Benaoumeur, Fred, Wassim, Youssef, Ferid, Kamel et Nacer.

Je voudrais remercier Frédéric Rousseau pour m'aider au début de ma thèse lorsqu'on a partagé le même bureau et surtout pour ses conseils tout au long de mon séjour ici qui ont beaucoup enrichi cette thèse.

Un merci spécial à Madame Comtat qui m'a très bien accueilli quand je suis arrivé à Grenoble. Je remercie également mes amis de l'Alliance Française : Jochen, Erika, Lina, John, Roberta et Lorenzo. J'espère qu'on pourra se revoir bientôt quelque part dans le monde. Je remercie énormément Geneviève, Hubert et leur famille pour leur amitié et pour tout ce qu'ils ont fait pour nous. On vous attend à Recife. Mes remerciements vont aussi aux très bons amis Daniel, Oana et Andrei. Il n'y a que de bons moments dans ces trois années qu'on a vécu ensemble dans le même bâtiment Merci aux amis brésiliens Cristiano et Patricia. Bon retour au Brésil et j'espère vous rencontrer bientôt. Enfin un grand merci à Carmen, Fernando et João Pedro et tout les amis qui sont au Brésil.

Je tiens à remercier tous les membres du jury pour leurs remarques qui ont beaucoup contribué pour améliorer cette thèse. Je remercie M. Mostapha Aboulhamid et M. Jean-Paul Calvez de leur gentillesse d'avoir accepté d'être rapporteurs de cette thèse.

Merci à Wander Cesário pour toutes les contributions techniques qu'il a apporté à ce travail. Je te souhaite bonne chance dans ton nouveau poste.

Je voudrais remercier M. Ahmed Amine Jerraya, directeur de recherche au CNRS, de m'avoir donné l'opportunité de faire une thèse ici dans le groupe SLS. Puisse ce travail être à l'hauteur de son encadrement. J'espère que cette thèse apporte quelque chose d'important aux travaux du groupe.

### Table des Matières

| Chapitre 1 : Problématique de la Conception de Systèmes Hétérogènes Embarqués               |    |

|---------------------------------------------------------------------------------------------|----|

| 1.1 Contexte: Conception de Systèmes Hétérogènes Embarqués                                  | 2  |

| 1.2 Difficultés de la Conception de Systèmes Hétérogènes Embarqués                          |    |

| 1.2.1 Intégration de Systèmes Hétérogènes Embarqués                                         |    |

| 1.2.2 Validation de Systèmes Hétérogènes Embarqués                                          |    |

| 1.3 Objectif: Génération de Modèles de Simulation pour la Validation de Systèmes Hétérogèn  |    |

| Embarqués                                                                                   |    |

| 1.4 Contributions                                                                           |    |

| 1.4.1 Modèle d'Adaptateur de Communication pour la Cosimulation des Systèmes Hétérogène     | _  |

|                                                                                             |    |

| 1.4.2 Flot de Génération Automatique de Modèles de Simulation pour la Validation de Système |    |

| Hétérogènes Embarqués                                                                       |    |

| 1.5 Plan du Mémoire                                                                         |    |

| Chapitre 2 : Validation de Systèmes Hétérogènes Embarqués                                   |    |

| 2.1 Introduction                                                                            |    |

| 2.2 Systèmes Hétérogènes Embarqués                                                          |    |

| 2.2.1 Concepts de Base pour la Spécification des Systèmes                                   |    |

| Module                                                                                      |    |

| Interface de Communication                                                                  |    |

| Protocole de Communication                                                                  |    |

| Interconnexion Interconnexion                                                               |    |

| Modèle d'exécution                                                                          |    |

| 2.2.2 Niveaux d'Abstraction des Modules                                                     |    |

| Niveaux d'Abstraction du Logiciel                                                           |    |

| Niveaux d'Abstraction du Matériel                                                           |    |

| 2.2.3 Niveaux d'Abstraction de la Communication                                             |    |

| Le Niveau Service                                                                           |    |

| Le Niveau Message                                                                           |    |

| Le Niveau Message  Le Niveau Transactionnel (TLM)                                           |    |

| Le Niveau Transactionner (TENI)  Le Niveau Transfert (BCA)                                  |    |

| Le Niveau RTL                                                                               |    |

| 2.2.4 Flot de Conception de Systèmes Hétérogènes Embarqués                                  |    |

| 2.2.5 Flot de Validation de Systèmes Hétérogènes Embarqués                                  |    |

| 2.3 Méthodes de Validation de Systèmes Hétérogènes Embarqués                                |    |

| 2.3.1 Critères de Classification des Méthodes de Validation                                 |    |

| Coût pour Construire le Modèle                                                              |    |

| Flexibilité                                                                                 |    |

| Capacité d'Utilisation aux Différentes Etapes de Validation                                 |    |

| Précision                                                                                   |    |

| Vitesse                                                                                     |    |

| 2.3.2 Vérification Formelle                                                                 |    |

| 2.3.3 Prototypage Matériel                                                                  |    |

| 2.3.4 Cosimulation                                                                          |    |

| 2.4 Validation de Systèmes Hétérogènes Embarqués par Cosimulation                           |    |

| 2.4.1 Etat de l'Art de la Cosimulation.                                                     | 33 |

| Cosimulation Multi Modèles de Calcul                                                        |    |

| Cosimulation Multi Langages                                                                 |    |

| Cosimulation Multi-Niveaux                                                                  |    |

| 2.4.2 Modèle Conceptuel de Cosimulation pour Systèmes Hétérogènes Embarqués                 |    |

| Bus de Cosimulation                                                                         |    |

| Interfaces de Cosimulation                                                                  |    |

| 2.4.3 Critères d'Evaluation de Modèles d'Adaptateurs de Communication                       | 38 |

| Flexibilité                                                                                 | 38 |

| Réutilisation des Composants de Base                                                                                                        |    |

|---------------------------------------------------------------------------------------------------------------------------------------------|----|

| Performance                                                                                                                                 |    |

| 2.4.4 Etat de l'Art - Modèles d'Adaptateurs de Communication                                                                                |    |

| Modèles Basés sur Bus                                                                                                                       |    |

| Modèles Basés sur Protocoles Standard                                                                                                       |    |

| Modèles Basés sur l'Assemblage de Composants avec Architecture Fixe                                                                         |    |

| <ul> <li>2.4.5 Modèles de Cosimulation à travers un Flot de Validation de Systèmes Hétérogènes Embarqués</li> <li>2.5 Conclusion</li> </ul> |    |

| Chapitre 3 : Modèle d'Adaptateur de Communication pour la Cosimulation de Systèmes Hétérogènes                                              | 43 |

| EmbarquésEmbarqués                                                                                                                          | 17 |

| 3.1 Introduction                                                                                                                            |    |

| 3.2 Utilisation d'Architectures Abstraites pour la Spécification des Systèmes Hétérogènes Embarqués.                                        |    |

| 3.2.1 Concepts de Base des Architectures Abstraites                                                                                         |    |

| Environnement d'Exécution                                                                                                                   |    |

| Interfaces Abstraites                                                                                                                       |    |

| 3.2.2 Architectures Abstraites dans un Flot de Conception de Systèmes Hétérogènes                                                           | 51 |

| 3.2.3 La Relation Entre Les Architectures Abstraites et Les Modèles de Simulation                                                           |    |

| Modèle de Simulation pour l'Environnement d'Exécution – Le Bus de Cosimulation                                                              |    |

| Modèle de Simulation pour les Interfaces Abstraites – Les Adaptateurs de Communication et de                                                |    |

| Simulateur                                                                                                                                  | 53 |

| 3.3 Modèle d'Adaptateur de Communication Basé sur les Services                                                                              | 53 |

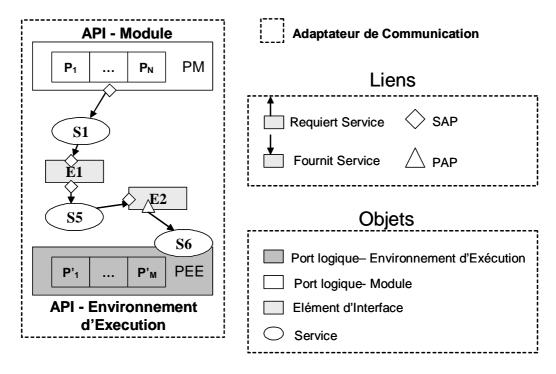

| 3.3.1 Composants du Modèle d'Adaptateur Basé sur les Services                                                                               | 54 |

| Service                                                                                                                                     | 54 |

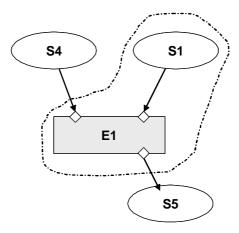

| Elément d'Interface                                                                                                                         | 54 |

| Port Logique                                                                                                                                |    |

| Point d'Accès aux Services                                                                                                                  |    |

| Point d'Accès aux Ports                                                                                                                     |    |

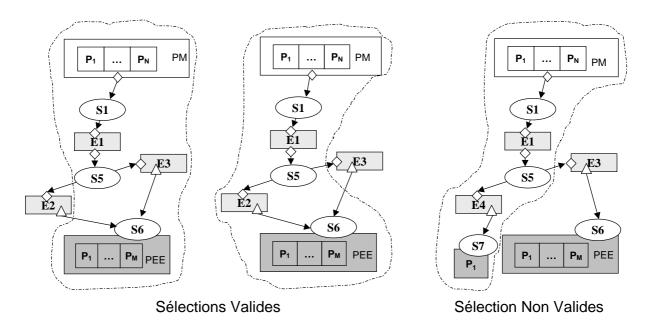

| 3.3.2 Composition des Adaptateurs de Communication                                                                                          |    |

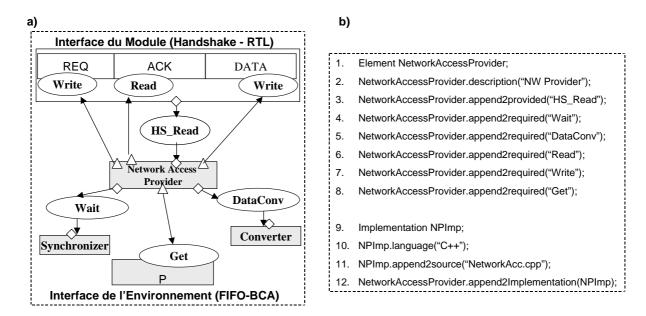

| Graphe de Dépendance de Services                                                                                                            |    |

| La Construction des Graphes de Dépendance de Services                                                                                       |    |

| 3.4 Implémentation d'Interfaces Abstraites en Utilisant le Modèle Basé sur les Services                                                     |    |

| 3.4.1 Exemple d'Application : Le Moteur de Recherche de Séquence de Caractères WSS                                                          |    |

| 3.4.2 L'Architecture Abstraite du WSS                                                                                                       |    |

| 3.4.3 Les Adaptateurs de Communication du WSS en Utilisant le Modèle Basé sur Services                                                      |    |

| 3.5 Modélisation de Systèmes Hétérogènes Embarqués                                                                                          |    |

| 3.5.1 Colif : Un Langage de Spécification pour les Systèmes Hétérogènes                                                                     |    |

| Concepts de Base                                                                                                                            |    |

| Architectures Abstraites en Colif                                                                                                           |    |

| Modèle d'Objets de Colif                                                                                                                    |    |

| Détails d'Implémentation                                                                                                                    |    |

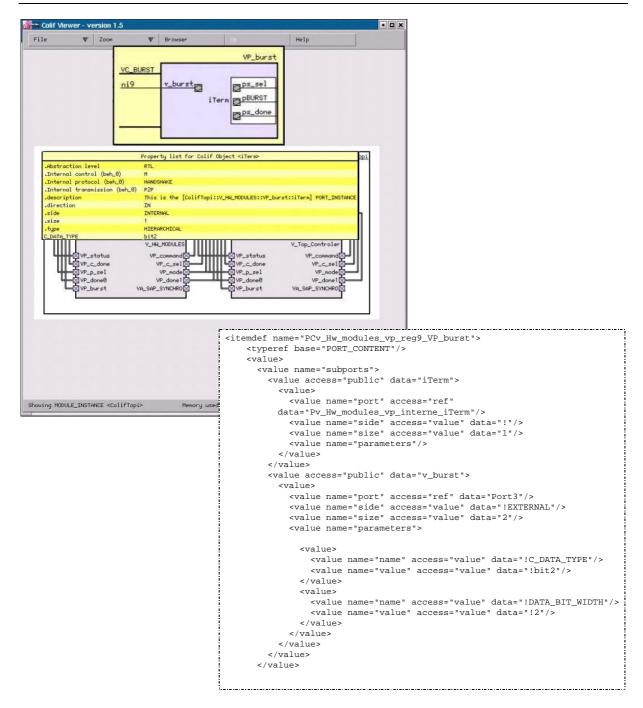

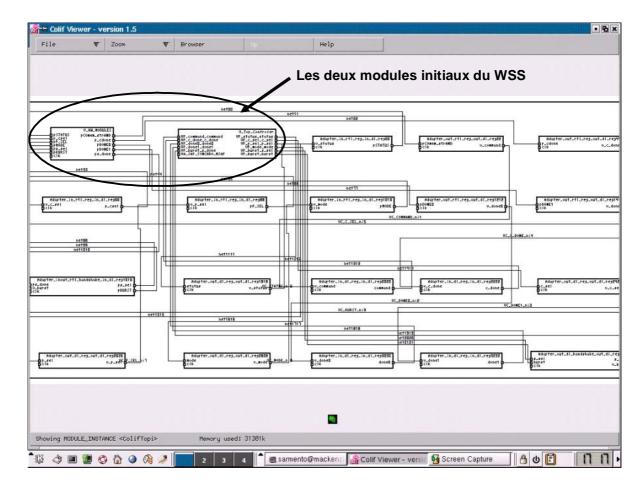

| Exemple : Visualisation du WSS spécifié en Colif                                                                                            |    |

| Concepts de Base                                                                                                                            |    |

| Détails d'Implémentation                                                                                                                    |    |

| Exemple : Description d'un Elément d'Interface du WSS                                                                                       |    |

| 3.6 Intégration du Modèle Basé sur les Services au Flot de Conception de Systèmes Hétérogènes                                               | /0 |

| Embarqués ROSES                                                                                                                             | 71 |

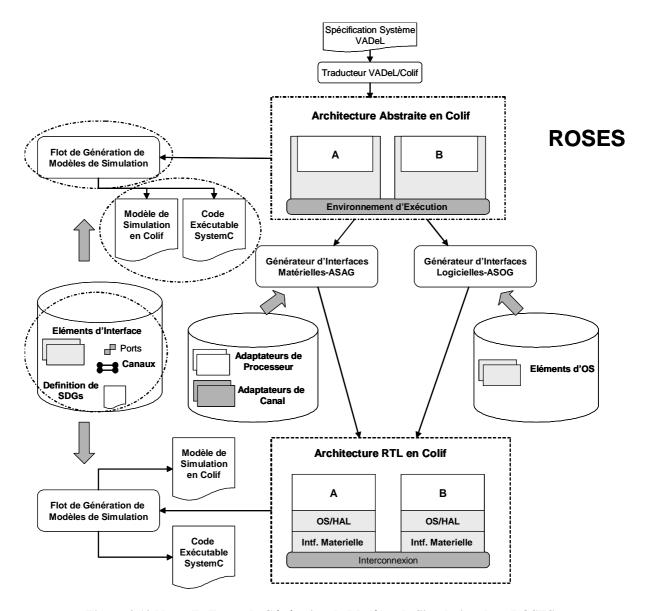

| 3.6.1 Présentation du Flot ROSES                                                                                                            |    |

| 3.6.2 Les Outils de ROSES                                                                                                                   |    |

| Générateur d'Interfaces Matérielles – ASAG                                                                                                  |    |

| Générateur d'Interfaces Logicielles – ASOG                                                                                                  |    |

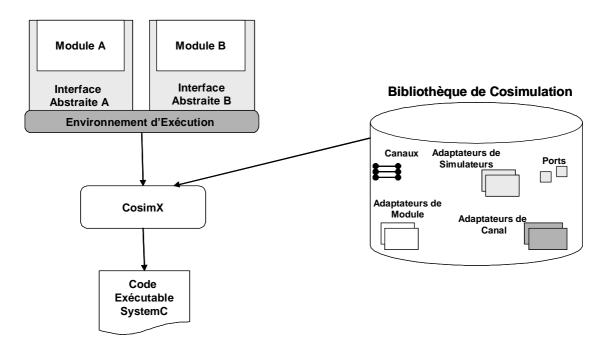

| Générateur de Modèles de Simulation –CosimX                                                                                                 |    |

| 3.6.3 Les Problèmes du Flot ROSES                                                                                                           |    |

| 3.6.4 L'Utilisation des Graphes de Dépendance de Services pour Modéliser les Interfaces                                                     |    |

| Logicielles/Matérielles                                                                                                                     | 75 |

| 3.7 Conclusion                                                                                                                              |    |

| Chapitre 4 : Génération Automatique de Modèles de Simulation pour Systèmes Hétérogènes Embarqués                                            |    |

| 4.1 Introduction                                                                                                                            |    |

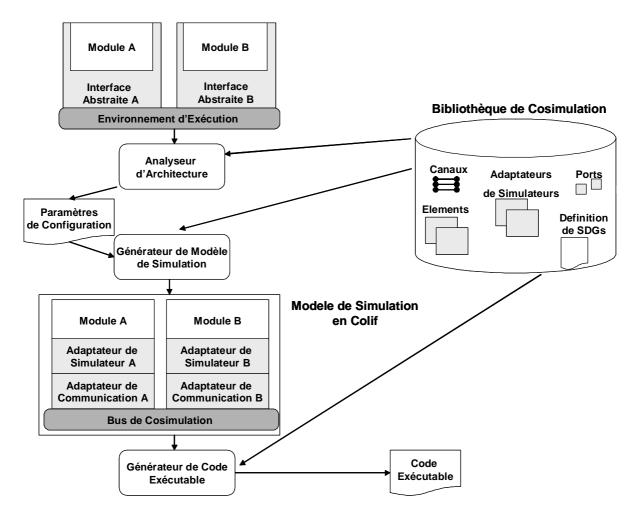

| 4.2 Flot de Génération de Modèles de Simulation pour Systèmes Hétérogènes Embarqués                                                         | 78 |

| 4.2.1 Composants du Flot de Génération de Modèles de Simulation                                                                             | 79 |

|         | yseur d'Architecture                                                                     |         |

|---------|------------------------------------------------------------------------------------------|---------|

|         | othèque de Cosimulation                                                                  |         |

|         | rateur de Modèle de Simulation                                                           |         |

| Géné    | rateur de Code Exécutable                                                                |         |

| 4.2.2   | Enchaînement des Etapes du Flot de Génération de Modèles de Simulation                   |         |

|         | Bibliothèque de Cosimulation                                                             |         |

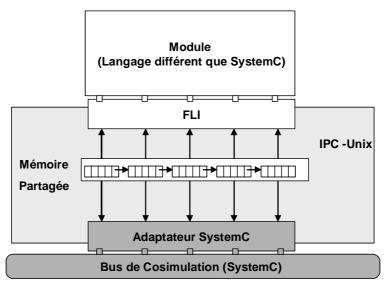

| 4.3.1   | La Réalisation des Adaptateurs de Simulateur                                             |         |

| 4.3.2   | La Réalisation des Bus de Cosimulation                                                   |         |

| 4.3.3   | La Réalisation des Eléments d'Interface                                                  |         |

| 4.3.4   | La Réalisation des Ports Logiques                                                        |         |

|         | tails d'Implémentation des Outils Développées pour la Génération Automatiques de Modèles |         |

|         | 1                                                                                        |         |

| 4.4.1   | Analyseur d'Architecture                                                                 |         |

| 4.4.2   | Générateur de Modèle de Simulation                                                       |         |

|         | chitecture du Générateur de Modèle de Simulation                                         |         |

|         | rateur d'Adaptateur de Simulateur                                                        |         |

|         | rateur d'Adaptateur de Communication                                                     |         |

|         | ration des Adaptateurs de Communication à l'Aide de l'Outil ASOG                         |         |

|         | rateur de Colif                                                                          |         |

| 4.4.3   | Générateur de Code Exécutable                                                            |         |

|         | rties du Flot                                                                            |         |

| 4.5.1   | Les Fichiers Générés par les Outils du Flot                                              |         |

| 4.5.2   | Exemple : Un Modèle de Simulation en Colif et Un Adaptateur de Communication Généro      | és pour |

| le WSS  |                                                                                          |         |

|         | égration du Flot de Génération Automatique de Modèles de Simulation au ROSES             | 97      |

| 4.6.1   | Le Flot Utilisé par CosimX Pour Générer des Modèles de Simulation                        |         |

| 4.6.2   | 1                                                                                        |         |

|         | nclusion                                                                                 |         |

|         | Résultats Expérimentaux                                                                  |         |

|         | roduction                                                                                |         |

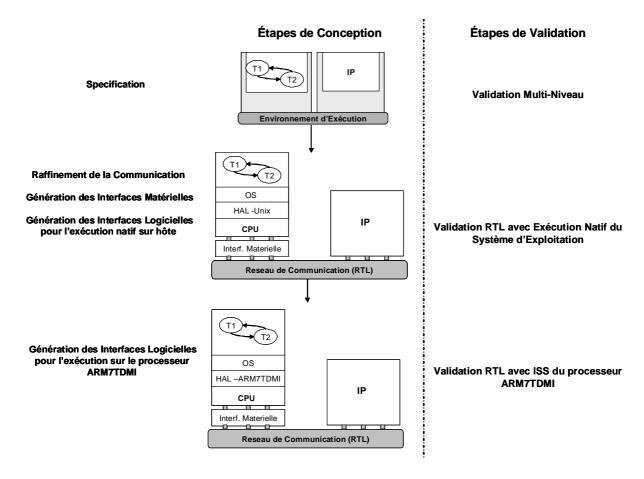

|         | Flot de Validation Utilisé dans les Expérimentations                                     |         |

|         | Modem VDSL                                                                               |         |

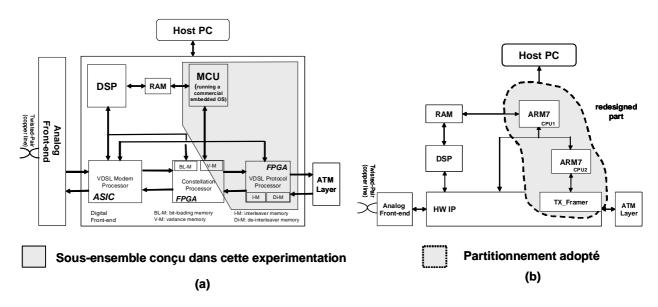

|         | ésentation du Modem VDSL                                                                 |         |

|         | Architecture Abstraite du Modem VDSL                                                     |         |

|         | alidation Multi-Niveaux du Modem VDSL                                                    |         |

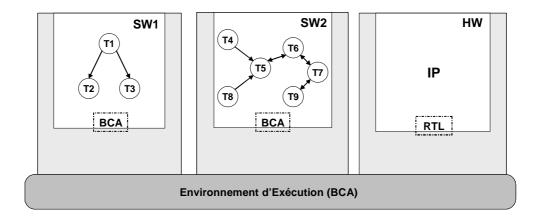

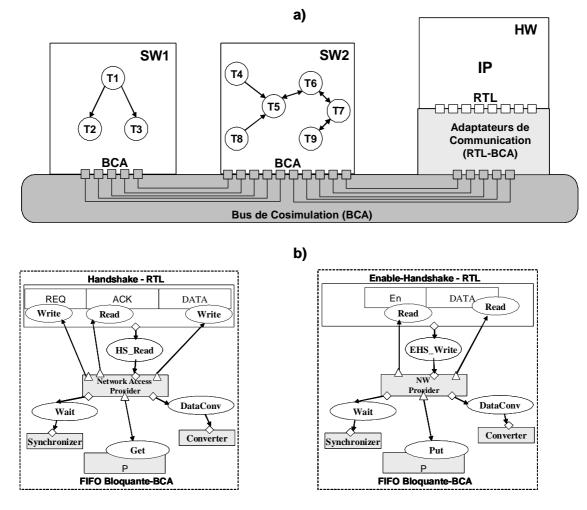

|         | odèle de Simulation Multi-Niveaux                                                        |         |

|         | ltats de la Validation Multi-Niveaux                                                     |         |

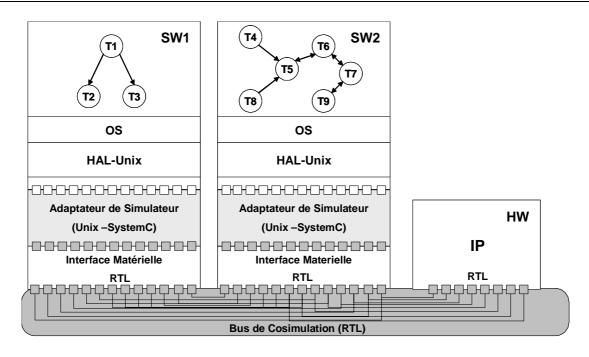

|         | alidation RTL du Modem VDSL avec l'Exécution Native du Système d'Exploitation            |         |

|         | odèle de Simulation RTL- Exécution Native du Système d'Exploitation                      |         |

|         | tats de la Validation RTL- Exécution Native du Système d'Exploitation                    |         |

|         | alidation RTL du Modem VDSL avec ISS                                                     |         |

|         | odèle de Simulation RTL-ISS                                                              |         |

|         | tats de la Validation RTL-ISS                                                            |         |

|         | valuation des résultats                                                                  |         |

|         | Encodeur MPEG-4                                                                          |         |

|         | ésentation de l'Encodeur MPEG-4                                                          |         |

|         | Architecture Abstraite de l'Encodeur MPEG-4                                              |         |

|         | alidation Multi-Niveaux de l'Encodeur MPEG-4                                             |         |

|         | odèle de Simulation Multi-Niveaux                                                        |         |

|         | tats de la Validation Multi-Niveaux                                                      |         |

|         | alidation RTL de l'Encodeur MPEG-4 avec l'Exécution Native du Système d'Exploitation     |         |

|         | odèle de Simulation RTL- Exécution Native du Système d'Exploitation                      |         |

|         | tats de la Validation RTL- Exécution Native du Système d'Exploitation                    |         |

|         | alidation RTL de l'Encodeur MPEG-4 avec ISS                                              |         |

|         | odèle de Simulation RTL-ISS                                                              |         |

|         | Itats de la Validation RTL-ISS                                                           |         |

|         | valuation des résultats                                                                  |         |

|         | aluation de la Génération Automatique de Modèles de Simulation dans les Cas Présentés    |         |

|         | es Avantages du Modèle d'Adaptateur de Communication Basé sur les Services Par Rapport   |         |

| d'Autre | s Approches                                                                              | 121     |

| Flexibilité                                                                                       | 121 |

|---------------------------------------------------------------------------------------------------|-----|

| Réutilisation des Composants de Base                                                              | 122 |

| Performance                                                                                       |     |

| 5.5.2 Les Limitations du Modèle d'Adaptateur de Communication Basé sur Services                   | 122 |

| 5.5.3 Les Avantages Globaux du Flot de Génération Automatique de Modèles de Simulation            | 123 |

| Réduction de Temps de Validation                                                                  | 123 |

| Validation Multi-Niveaux                                                                          | 123 |

| Validation à Plusieurs Etapes de la Conception                                                    | 123 |

| 5.5.4 Les Limitations Globaux du Flot de Génération Automatique de Modèles de Simulation          | 124 |

| 5.5.5 Les Avantages et Limitations du Flot de Génération Automatique de Modèles de Simulation Par |     |

| Rapport à CosimX                                                                                  | 124 |

| Les Entrées pour la Génération                                                                    | 124 |

| La Bibliothèque de Cosimulation                                                                   | 125 |

| La Flexibilité du Processus de Génération                                                         | 125 |

| Le Temps de Génération                                                                            | 125 |

| Les Sorties de la Génération.                                                                     | 126 |

| 5.6 Conclusion                                                                                    | 126 |

| Chapitre 6 : Conclusion et Perspectives                                                           | 127 |

| Bibliographie                                                                                     | 131 |

## **Liste des Figures**

| Figure 1-1 Représentation d'un système hétérogène embarqué                                              | 3     |

|---------------------------------------------------------------------------------------------------------|-------|

| Figure 1-2 Génération de Modèles de Simulation Partant d'une Spécification Abstraite des Interfaces de  |       |

| Communication du Système Hétérogène Embarqué                                                            | 5     |

| Figure 2-1 Concepts de Base de Systèmes                                                                 |       |

| Figure 2-2 Exemple de Module décrit en SystemC                                                          |       |

| Figure 2-3 Exemple de Port Hiérarchique                                                                 |       |

| Figure 2-4 Différence entre API et Protocole de Communication                                           |       |

| Figure 2-5 Différence entre Modèle d'exécution et Modèle de Calcul                                      |       |

| Figure 2-6 Exemple de Flot de Conception de Systèmes Hétérogènes Embarqués                              | 24    |

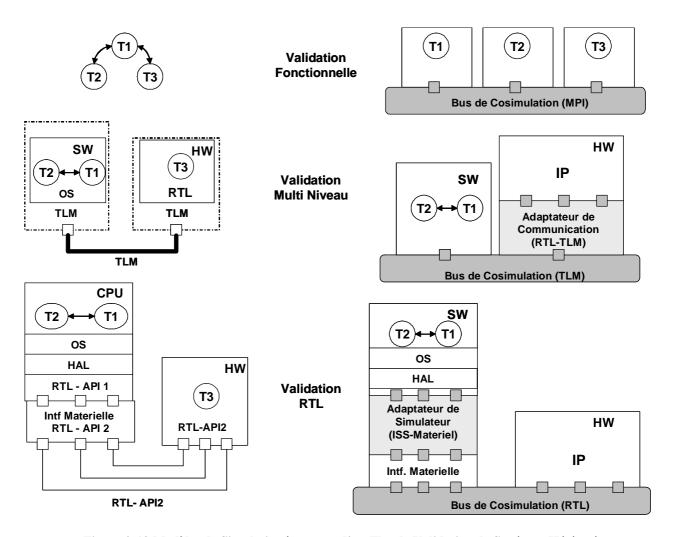

| Figure 2-7 Exemple de Flot de Validation de Systèmes Hétérogènes Embarqués                              | 26    |

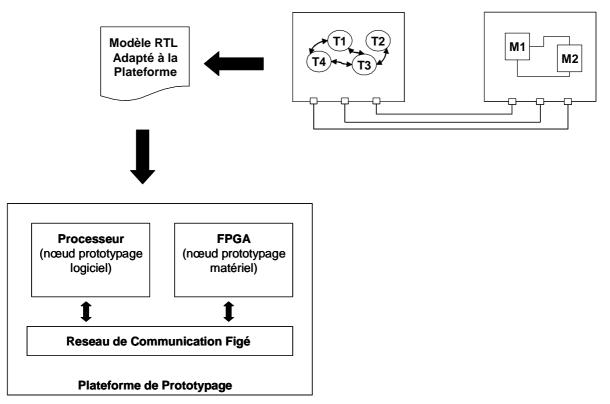

| Figure 2-8 Validation par Prototypage Matériel                                                          | 31    |

| Figure 2-9 Validation Par Cosimulation                                                                  | 32    |

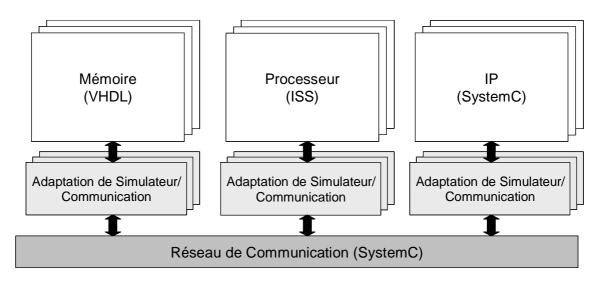

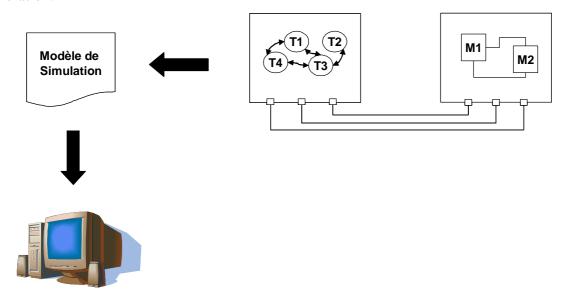

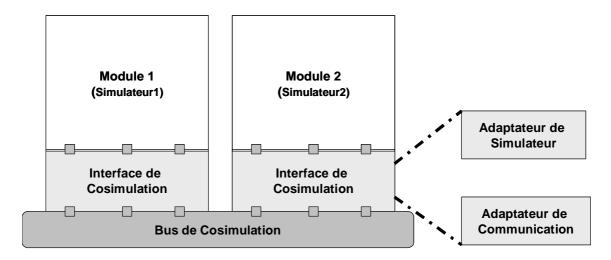

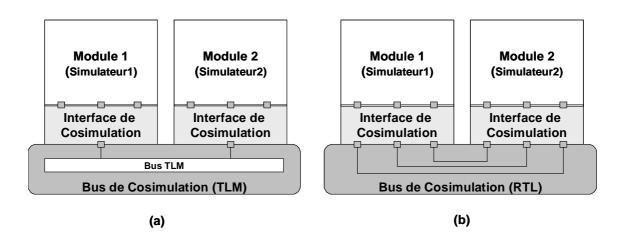

| Figure 2-10 Modèle de Cosimulation pour Systèmes Hétérogènes Embarqués                                  |       |

| Figure 2-11 (a) Bus de Cosimulation au Niveau Transactionnel (b) Bus de Cosimulation au Niveau RTL      |       |

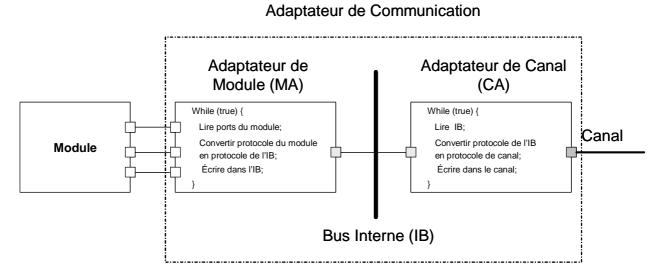

| Figure 2-12 Modèle d'Adaptateur de Communication Utilisé Par CosimX                                     | 43    |

| Figure 2-13 Modèles de Simulation à travers d'un Flot de Validation de Systèmes Hétérogènes Embarqués   |       |

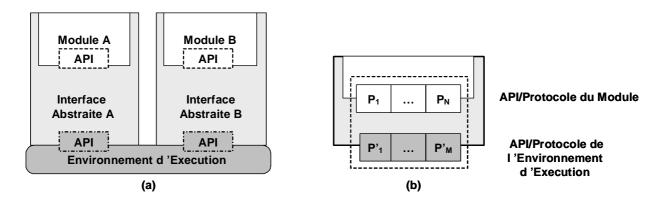

| Figure 3-1 (a) Architecture Abstraite (b) Interface Abstraite                                           |       |

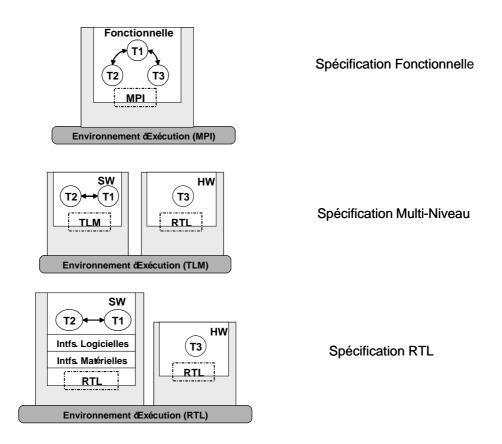

| Figure 3-2 Les Architectures Abstraites à Travers un Flot de Conception                                 |       |

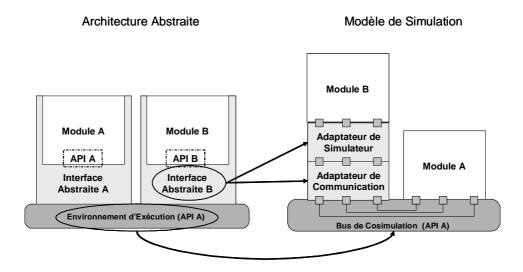

| Figure 3-3 Architecture Abstraite Versus Modèle de Simulation                                           |       |

| Figure 3-4 Graphe de Dépendance de Services.                                                            |       |

| Figure 3-5 Implémentation des Services Strictement Nécessaires Pour l'Adaptation                        | 57    |

| Figure 3-6 Principe de Sélection des Eléments d'interface/Ports Logiques et Services pour Composer un   |       |

| Adaptateur de Communication                                                                             |       |

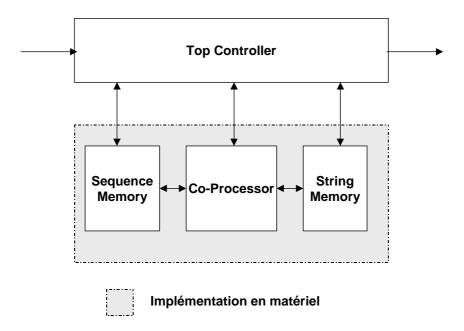

| Figure 3-7 WSS -Un Moteur de Recherche de Chaînes de Caractères                                         |       |

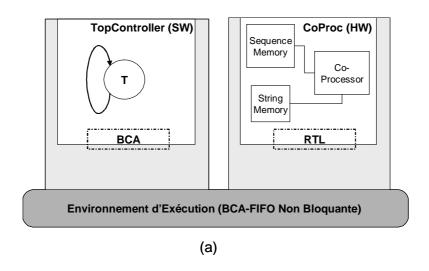

| Figure 3-8 (a) L'Architecture Abstraite du WSS (b) L'Interface RTL du Module CoProc                     | 61    |

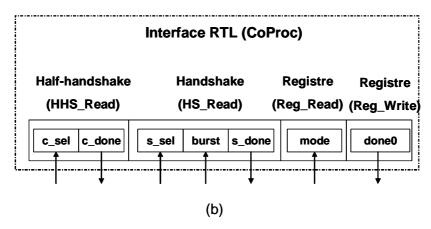

| Figure 3-9 (a) Adaptateur pour Permettre la Communication Entre le TopController et le StringMemory (b) |       |

| Adaptateur pour Permettre la Communication Entre le TopController et le Sequence Memory                 |       |

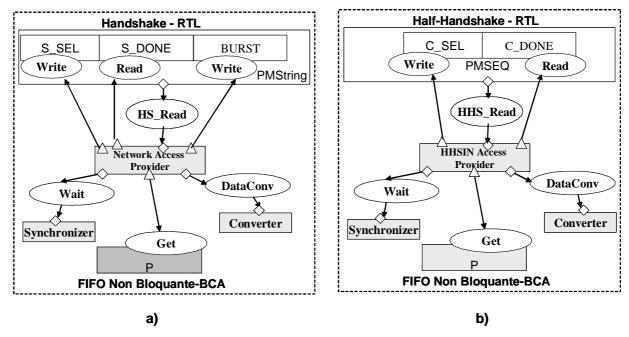

| Figure 3-10 Adaptateurs pour Permettre la Communication Entre le TopController et le CoProcessor        | 64    |

| Figure 3-11 Concepts de Base de Colif                                                                   |       |

| Figure 3-12 Colif et Architectures Abstraites                                                           |       |

| Figure 3-13 Modèle d'Objets de Colif                                                                    |       |

| Figure 3-14 Visualisation du WSS en Colif                                                               |       |

| Figure 3-15 (a) Adaptateur de Communication du WSS (b) Description d'un Elément d'Interface en Lidel    |       |

| Figure 3-16 Flot de Conception de Systèmes Hétérogènes Embarqués –ROSES                                 |       |

| Figure 4-1 Flot de Génération de Modèles de Simulation pour Systèmes Hétérogènes Embarqués              |       |

| Figure 4-2 Architecture des Adaptateurs de Simulateur                                                   |       |

| Figure 4-3 Réalisation d'un Elément d'Interface en Utilisant le Langage de Macro Rive                   |       |

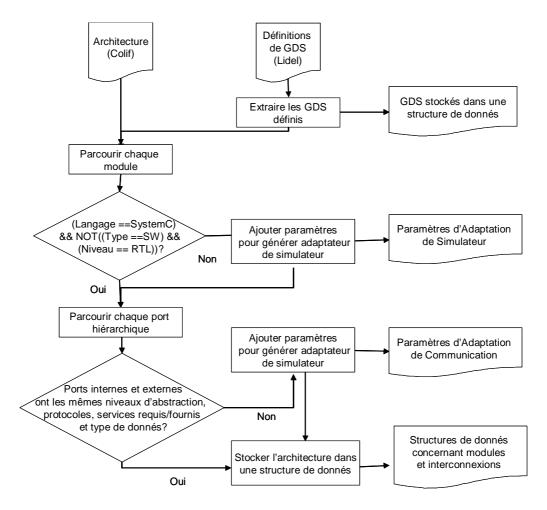

| Figure 4-4 Flot d'Analyse d'Architecture                                                                |       |

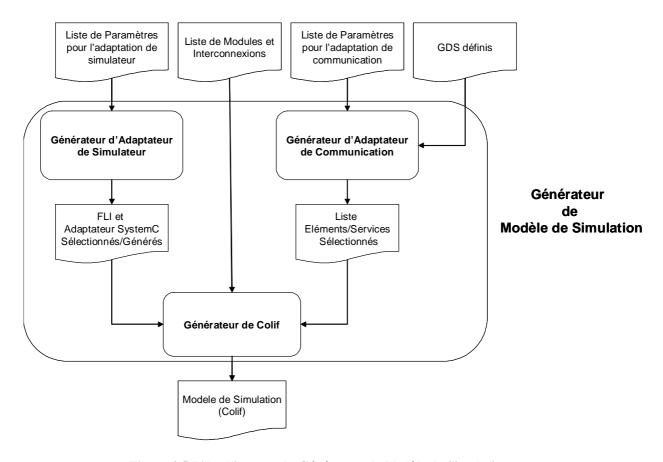

| Figure 4-5 L'Architecture du Générateur de Modèle de Simulation                                         |       |

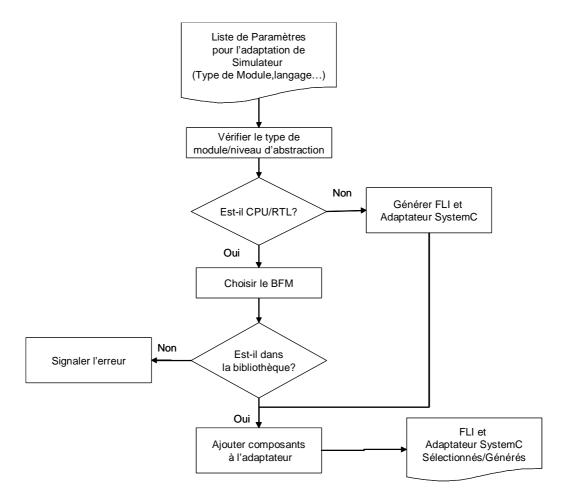

| Figure 4-6 Flot de Génération d'Adaptateurs de Simulateur                                               | 90    |

| Figure 4-7 Mécanisme de Sélection des Eléments d'Interface                                              |       |

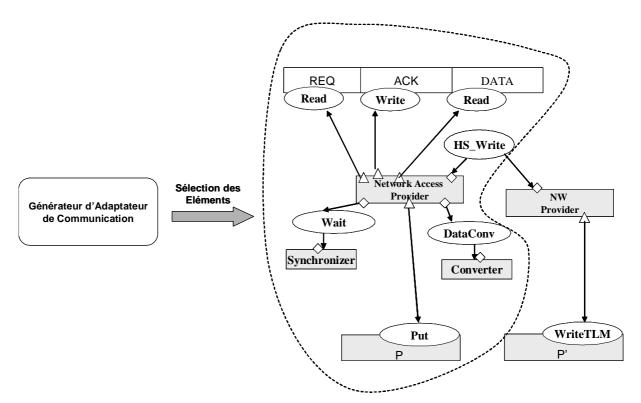

| Figure 4-8 Flot de Génération de Code Exécutable                                                        |       |

| Figure 4-9 Modèle de Simulation du WSS en Colif                                                         |       |

| Figure 4-10 Code SystemC d'un Adaptateur de Communication du WSS                                        |       |

| Figure 4-11 Flot de Génération de Modèles de Simulation par CosimX                                      |       |

| Figure 4-12 Nouvelle Façon de Génération de Modèles de Simulation dans ROSES                            |       |

| Figure 5-1 Flot de Validation Utilisé Pour les Expérimentations                                         |       |

| Figure 5-2 a) Modem VDSL b) Partitionnement Adopté pour Concevoir le VDSL                               |       |

| Figure 5-3 L'Architecture Abstraite du Modem VDSL                                                       |       |

| Figure 5-4 a) Modèle de Simulation Multi-Niveau du VDSL b) Exemples des Adaptateurs de Communication    |       |

| Générés                                                                                                 |       |

| Figure 5-5 Modèle de Simulation du VDSL - Exécution Native du Système d'Exploitation                    |       |

| Figure 5-6 Modèle de Simulation du VDSL avec ISS -ARM7                                                  |       |

| Figure 5-7 a) L'Encodeur MPEG-4 b) Partitionnement de l'Application                                     |       |

| Figure 5-8 L'Architecture Abstraite de l'Encodeur MPEG-4                                                |       |

| Figure 5-9 Modèle de Simulation Multi-Niveaux de l'Encodeur MPEG-4                                      | . 115 |

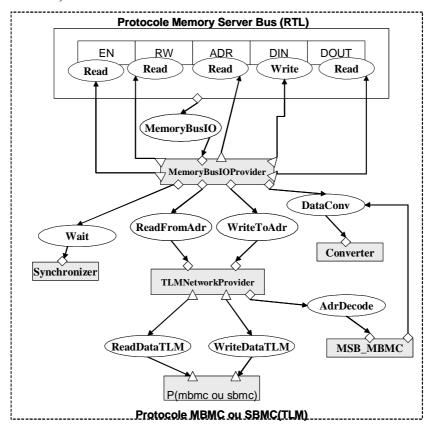

| Figure 5-10 Adaptateur de Communication pour Permettre le Transfert des Données entre Memory Server,     |       |

|----------------------------------------------------------------------------------------------------------|-------|

| VPROC et VLC                                                                                             | 116   |

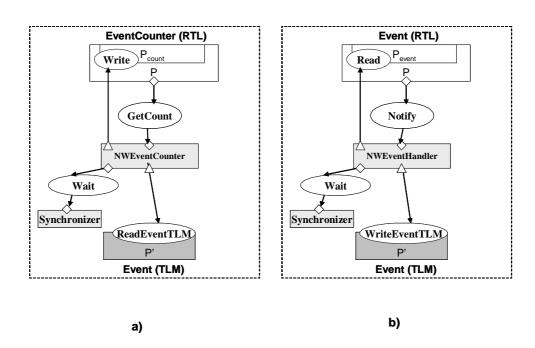

| Figure 5-11 Adaptateurs de Communication pour Permettre la Synchronisation de Transfert de Données entre | e     |

| Memory Server, VPROC et VLC                                                                              | 117   |

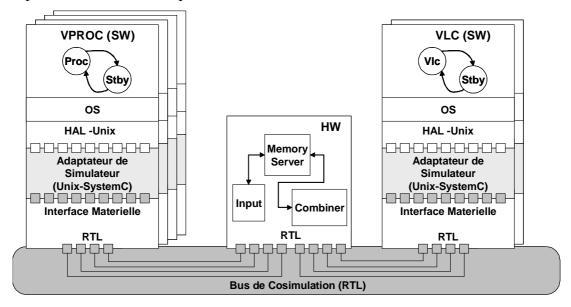

| Figure 5-12 Modèle de Simulation de l'Encodeur MPEG-4 – Exécution Native du Système d'Exploitation       | . 119 |

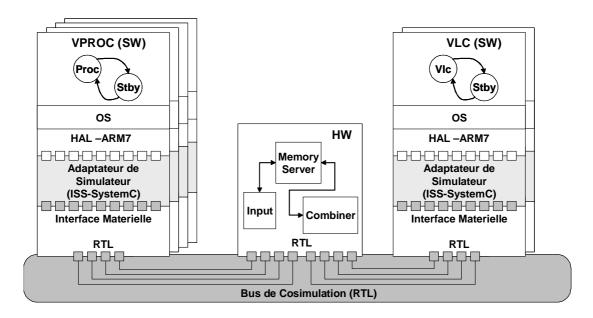

| Figure 5-13 Modèle de Simulation de l'Encodeur MPEG-4 avec ISS -ARM7                                     | 120   |

## Chapitre 1 : Problématique de la Conception de

## Systèmes Hétérogènes Embarqués

| 1.1   | Contexte: Conception de Systèmes Hétérogènes Embarqués                                              | . 2 |

|-------|-----------------------------------------------------------------------------------------------------|-----|

| 1.2   | Difficultés de la Conception de Systèmes Hétérogènes Embarqués                                      | . 2 |

| 1.2.1 | Intégration de Systèmes Hétérogènes Embarqués                                                       | . 3 |

| 1.2.2 | 2 Validation de Systèmes Hétérogènes Embarqués                                                      | . 3 |

| 1.3   | Objectif: Génération de Modèles de Simulation pour la Validation de Systèmes Hétérogènes Embarqué   | s4  |

| 1.4   | Contributions                                                                                       | . 5 |

| 1.4.1 | Modèle d'Adaptateur de Communication pour la Cosimulation des Systèmes Hétérogènes Embarqués        | . 5 |

| 1.4.2 | 2 Flot de Génération Automatique de Modèles de Simulation pour la Validation de Systèmes Hétérogène | es  |

| Emb   | arqués                                                                                              | . 6 |

| 1.5   | Plan du Mémoire                                                                                     | . 7 |

|       |                                                                                                     |     |

#### 1.1 Contexte: conception de systèmes hétérogènes embarqués

Cette thèse s'inscrit dans le contexte de la conception des systèmes hétérogènes embarqués monopuces. Ce type de système, est adapté pour implémenter une application spécifique en respectant entre autres des contraints de performance, de consommation d'énergie, et de surface.

Les systèmes embarqués sont, généralement, composés de parties logicielles et matérielles. La partie logicielle concerne le logiciel qui s'exécute sur un processeur, alors que la partie matérielle consiste en un composant matériel qui implémente une fonctionnalité spécifique (ASIC). Dans les années 90, ces systèmes présentaient une architecture relativement simple, généralement un processeur et quelques composants matériels communicant via un unique protocole de communication. Actuellement, ils sont beaucoup plus complexes. Ils sont, généralement, composés de plusieurs processeurs et composants matériels, communicant via des schémas de communication très sophistiqués. De plus, pour respecter les contraintes de l'application, ces systèmes sont implémentés sur une seule puce, raison pour laquelle ils sont souvent appelés SoC (venant de l'anglais System-on-Chip).

Les systèmes embarqués monopuces sont largement utilisés dans différents secteurs d'activité tels que : la télécommunication, l'aérospatiale, les jeux électroniques, l'automobile, etc. La conception de tels systèmes est complexe en raison de l'hétérogénéité des composants et des schémas de communication utilisés. Cette hétérogénéité rend difficile aussi la validation de tels systèmes. En fait, la validation représente, actuellement, 50 à 80% du temps de conception d'un système hétérogène embarqué monopuce.

# 1.2 Difficultés de la conception de systèmes hétérogènes embarqués

La Figure 1-1 est une représentation conceptuelle d'un système hétérogène embarqué. Ce système peut être composé de plusieurs types de processeurs (microcontrôleurs et DSPs par exemple), plusieurs composants matériels (des mémoires, des IPs, etc.) qui communiquent par divers protocoles de communication (FIFO, handshake, etc.) et utilisent différentes topologies de communication (bus, point à point, multipoint, etc.). En plus, les différentes parties de ces systèmes peuvent être spécifiées en différents langages de spécification et niveaux d'abstraction. Cette diversité de composants et de schémas de communication est nécessaire la plupart du temps pour respecter les contraintes de l'application et le processus de

conception. Cependant, cela va poser deux problèmes majeurs lors de la conception de systèmes hétérogènes embarqués. Le premier est relatif à l'intégration de tous ces composants pour qu'ils puissent travailler ensemble pour implémenter l'application cible. Le deuxième concerne la validation du système, puisque la génération d'un modèle de simulation (dans le cas où nous utilisons la simulation comme méthode de validation) qui utilise des composants hétérogènes est un processus complexe.

Figure 1-1 Représentation d'un système hétérogène embarqué

#### 1.2.1 Intégration de systèmes hétérogènes embarqués

L'intégration des composants passe par le ciblage du logiciel sur les processeurs utilisés ainsi que l'adaptation de la communication entre tous les composants matériels. Cette intégration concerne aussi les différents modèles de simulation des composants utilisés lors de la validation. La Figure 1-1 montre ce type d'intégration. Les composants qui adaptent la communication peuvent fournir plusieurs fonctionnalités telles que : adaptation de niveau d'abstraction, synchronisation, adaptation de types de donnés, adaptation de protocole de communication, etc. L'implémentation de cette adaptation est complexe car elle met en œuvre plusieurs connaissances et détails pouvant appartenir à des domaines différents. En plus, la spécification du système hétérogène embarqué peut changer plusieurs fois pendant sa conception. Cela veut dire que si l'adaptation n'est pas faite d'une façon flexible et qui facilite la réutilisation des composants, l'effort et le temps d'intégration seront significatifs.

#### 1.2.2 Validation de systèmes hétérogènes embarqués

La validation consomme une grande partie du temps de conception dans le cas des systèmes hétérogènes embarqués. Autrement dit, elle représente le goulot d'étranglement du processus de conception. La validation doit être faite dans toutes les étapes de la conception, prenant en compte l'hétérogénéité des composants selon l'étape de conception. Initialement, par exemple, les composants peuvent être décrits par différents langages de spécification et à différents niveaux d'abstraction.

Pour effectuer la validation, un modèle de simulation global du système doit être construit. Ce modèle peut utiliser plusieurs simulateurs différents et doit accommoder les différents protocoles de communication, niveaux d'abstraction, langages de spécification et types de données. Dans le cas où plusieurs simulateurs sont mis en œuvre par la simulation globale on parle de cosimulation. Cela implique que des interfaces de cosimulation doivent être implémentées aussi pour adapter les composants et éventuellement les simulateurs. Ces interfaces font partie aussi du modèle de simulation. La construction de tels modèles à chaque étape de conception est un processus long et fastidieux. En conséquence, souvent ce modèle n'est construit que lors des étapes très avancées de la conception, ce qui occasionne des coûts et des délais de conception significatifs.

# 1.3 Objectif: Génération de modèles de simulation pour la validation de systèmes hétérogènes embarqués

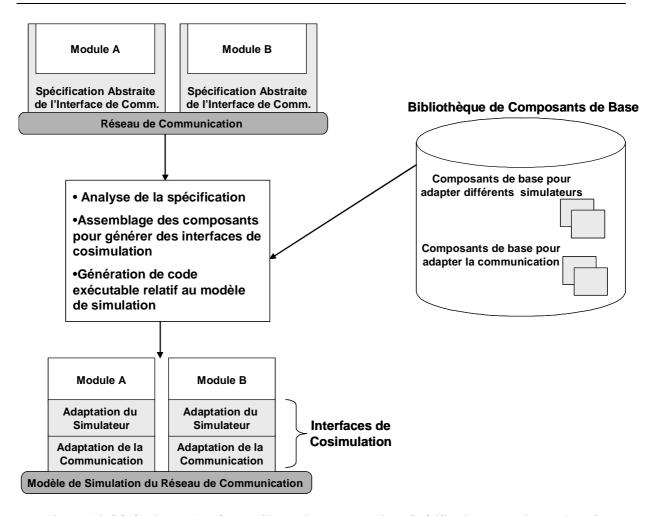

L'objectif principal de ce travail est de réduire le temps de validation de systèmes hétérogènes embarqués par la génération automatique de modèles de simulation de tels systèmes. En réduisant le temps de validation, le temps d'intégration sera également diminué en conséquence. Cette génération est faite partant d'une spécification du système qui reflète les besoins d'adaptation et d'une bibliothèque de composants de base qui sont assemblés pour former le modèle de simulation. La Figure 1-2 présente l'approche proposé. Les modules du système sont spécifiés en abstrayant leurs interfaces de communication. Les interfaces de communication sont décrites en précisant leurs besoins d'adaptation, sans aucun détail sur leurs réalisations. Partant de cette spécification, un modèle de simulation est généré qui intègre tous les modules en adaptant les différents langages de spécification (représenté dans la Figure 1-2 pour l'adaptation de simulateurs), et différents aspects de la communication (représenté dans la Figure 1-2 pour l'adaptation de communication) telles que : les niveaux d'abstraction, les protocoles de communication et les types de données. Les différents types d'adaptation sont réalisés en utilisant une bibliothèque de composants de base. La génération est accomplie à travers l'analyse de la spécification, l'assemblage de composantes de base nécessaires à la réalisation des adaptations et la production de code exécutable.

Figure 1-2 Génération de Modèles de Simulation Partant d'une Spécification Abstraite des Interfaces de Communication du Système Hétérogène Embarqué

#### 1.4 Contributions

Ce travail apporte deux contributions : (1) la définition d'un modèle d'adaptateur de communication pour la cosimulation des systèmes hétérogènes embarqués ; (2) la proposition et l'implémentation d'un flot de génération automatique de modèles de simulation pour les systèmes hétérogènes embarqués.

## 1.4.1 Modèle d'adaptateur de communication pour la cosimulation des systèmes hétérogènes embarqués

Le but d'un adaptateur de communication est de mettre en correspondance des composants ayant différents protocoles de communication et niveaux d'abstraction. L'adaptateur de communication facilite, donc, l'intégration des composants hétérogènes dans la cosimulation. La réalisation de tels adaptateurs manuellement est un travail fastidieux et, selon l'application, complexe. La définition d'un modèle qui puisse représenter ces

adaptateurs en vue de les générer automatiquement devient un point clé pour l'accélération du processus d'intégration de composants hétérogènes. Un tel modèle doit être assez générique et flexible pour permettre l'intégration des composants ayant n'importe quel protocole/niveau d'abstraction, et faciliter la réalisation des adaptateurs performants. En plus, le modèle doit favoriser la réutilisation de composants de base de l'adaptateur pour réduire le temps de conception de celui-là. Les modèles proposés dans la littérature présentent un domaine d'application restreint : ils imposent des restrictions par rapport aux protocoles/niveaux d'abstraction en réduisant ainsi la flexibilité; ou bien les adaptateurs modélisés possèdent une architecture fixe, ce qui pénalise la flexibilité, la réutilisation et la performance car les composants de base sont trop gros (cela augmente l'effort du concepteur pour les réaliser) et parfois incluent des fonctionnalités qui ne sont pas nécessaires.

Nous proposons dans ce travail, un modèle d'adaptateur de communication basé sur les services. Un adaptateur de communication est représenté par un graphe (appelé graphe de dépendance de services) contenant des composants de base qui peuvent fournir et/ou requérir des services. Ces composants sont liés par la relation de dépendance entre les services requis et fournis par chaque composant. Ce modèle facilite: (1) l'implémentation des adaptateurs flexibles puisque le modèle n'impose aucune contrainte par rapport aux protocoles/niveaux d'abstraction; (2) la réutilisation des composants de base car ceux-ci sont représentés par les services nécessaires pour l'adaptation; (3) et implicitement la construction des adaptateurs performants parce que ceux-ci ne contiendront que les services nécessaires pour sa fonction d'adaptation. Ce modèle a été appliqué pour valider deux systèmes hétérogènes – le modem VDSL et l'encodeur MPEG-4, et les résultats ont montré un gain de flexibilité et de réutilisation de composants de base apporté par le modèle. Cela a représenté une réduction importante du temps de validation de ces deux systèmes. Les résultats ne montrent pas le gain de performance, mais cela est implicite parce que les adaptateurs ne contient que les services nécessaires pour leur fonction d'adaptation.

## 1.4.2 Flot de génération automatique de modèles de simulation pour la validation de systèmes hétérogènes embarqués

La génération automatique des modèles de simulation pour des systèmes hétérogènes accélère le temps de validation. La mécanique de génération doit être capable de générer rapidement des modèles de simulation pour chaque étape du flot de conception des systèmes. En plus, le flot de génération doit être assez flexible pour qu'un changement de langage de spécification

ou de langage de code exécutable n'implique que la modification de quelques parties du flot. Plusieurs travaux portent aujourd'hui sur la génération automatique des modèles de simulation pour la validation des systèmes hétérogènes embarqués. Pourtant, les solutions existantes soit sont bien adaptées pour certaines étapes du flot de conception, soit ne sont pas assez flexibles.

Nous proposons et implémentons un flot de génération automatique de modèles de simulation pour les systèmes hétérogènes embarqués. Partant d'une spécification du système et d'une bibliothèque de composants de base, nous générons le code exécutable qui implémente le modèle de simulation. Ce flot est divisé en trois parties distinctes: (1) l'analyse de l'architecture où nous analysons les besoins d'adaptation entre les composants; (2) la génération du modèle de simulation dans une représentation intermédiaire; (3) la génération de code exécutable relatif au modèle de simulation du système. Le flot est flexible, car le changement de langage de spécification initiale ou de langage du code exécutable n'implique que la modification de quelques outils qui font partie du flot. Ce flot a été appliqué pour les deux expérimentations et a généré rapidement des modèles de simulation pour chaque étape du flot de conception. La génération automatique de modèles de simulation proposée dans ce travail a représenté une réduction significative du temps de validation de ces deux systèmes. En plus le flot proposé a été intégré dans le flot de conception des systèmes développé par le groupe SLS, pour améliorer la solution de génération automatique de modèles de simulation préexistant.

#### 1.5 Plan du mémoire

Ce document est structuré comme suit. Le chapitre 2 présente les concepts de base de systèmes hétérogènes embarqués, ainsi qu'une étude sur leur validation. Le chapitre 3 décrit le modèle d'adaptateur de communication pour la cosimulation des systèmes hétérogènes proposé dans ce travail. Le chapitre 4 présente le flot de génération des modèles de simulation. Le chapitre 5 présente les résultats obtenus des expérimentations que nous avons effectué pour valider nos contributions. Le chapitre 6 donne nos conclusions et les perspectives de ce travail.

# Chapitre 2: Validation de systèmes hétérogènes embarqués

| 2.1 |                                                                                                 |      |

|-----|-------------------------------------------------------------------------------------------------|------|

| 2.2 |                                                                                                 |      |

| 2   | 2.2.1 Concepts de Base pour la Spécification des Systèmes                                       |      |

|     | Module                                                                                          |      |

|     | Interface de Communication                                                                      |      |

|     | API de Communication                                                                            |      |

|     | Protocole de Communication                                                                      | . 14 |

|     | Interconnexion                                                                                  | . 15 |

|     | Modèle d'exécution                                                                              |      |

| 2   | 2.2.2 Niveaux d'Abstraction des Modules                                                         | . 16 |

|     | Niveaux d'Abstraction du Logiciel                                                               | . 17 |

|     | Niveaux d'Abstraction du Matériel                                                               |      |

| 4   | 2.2.3 Niveaux d'Abstraction de la Communication                                                 | . 19 |

|     | Le Niveau Service                                                                               |      |

|     | Le Niveau Message                                                                               |      |

|     | Le Niveau Transactionnel (TLM)                                                                  |      |

|     | Le Niveau Transfert                                                                             | . 23 |

|     | Le Niveau RTL                                                                                   |      |

|     | 2.2.4 Flot de Conception de Systèmes Hétérogènes Embarqués                                      |      |

|     | 2.2.5 Flot de Validation de Systèmes Hétérogènes Embarqués                                      |      |

| 2.3 | 1                                                                                               |      |

| 2   | 2.3.1 Critères de Classification des Méthodes de Validation                                     | . 27 |

|     | Coût pour Construire le Modèle                                                                  |      |

|     | Flexibilité                                                                                     |      |

|     | Capacité d'Utilisation aux Différentes Etapes de Validation                                     |      |

|     | Précision                                                                                       |      |

|     | Vitesse                                                                                         |      |

|     | 2.3.2 Vérification Formelle                                                                     |      |

|     | 2.3.3 Prototypage Matériel                                                                      |      |

|     | 2.3.4 Cosimulation                                                                              |      |

|     | Validation de Systèmes Hétérogènes Embarqués par Cosimulation                                   |      |

| 4   | 2.4.1 Etat de l'Art de la Cosimulation                                                          |      |

|     | Cosimulation Multi Modèles de Calcul                                                            |      |

|     | Cosimulation Multi Langages                                                                     |      |

|     | Cosimulation Multi-Niveaux                                                                      |      |

| 2   | 2.4.2 Modèle Conceptuel de Cosimulation pour Systèmes Hétérogènes Embarqués                     |      |

|     | Bus de Cosimulation                                                                             |      |

|     | Interfaces de Cosimulation                                                                      |      |

| 2   | 2.4.3 Critères d'Evaluation de Modèles d'Adaptateurs de Communication                           |      |

|     | Flexibilité                                                                                     |      |

|     | Réutilisation des Composants de Base                                                            |      |

|     | Performance                                                                                     |      |

| 2   | 2.4.4 Etat de l'Art - Modèles d'Adaptateurs de Communication                                    |      |

|     | Modèles Basés sur Bus                                                                           |      |

|     | Modèles Basés sur Protocoles Standards                                                          |      |

|     | Modèles Basés sur l'Assemblage de Composants avec Architecture Fixe                             |      |

|     | 2.4.5 Modèles de Cosimulation à travers un Flot de Validation de Systèmes Hétérogènes Embarqués |      |

| 2.5 | Conclusion                                                                                      | . 45 |

#### 2.1 Introduction

Ce chapitre explique la complexité du processus de validation lors de la conception de systèmes. Pour cela, nous commençons par aborder les caractéristiques spécifiques de systèmes hétérogènes embarqués. Nous verrons comment ces caractéristiques rendent difficile la validation et par conséquence la conception de tels systèmes. Ensuite, plusieurs méthodes de validation seront discutées. Enfin, la dernière partie de ce chapitre sera consacrée à la méthode de validation par cosimulation, qui est le sujet auquel nous apportons nos contributions dans ce travail.

#### 2.2 Systèmes hétérogènes embarqués

Les systèmes embarqués sont de plus en plus hétérogènes. Cette hétérogénéité peut avoir plusieurs aspects, comme : types de composant (CPU, Mémoire, ASIC, etc.), protocoles de communication utilisés (FIFO, handshake, etc.), types de données échangées ou même la nature de composants (électroniques, mécanique, optique, etc.). En plus, pour concevoir de tels systèmes, il faut d'abord les spécifier. Ces spécifications peuvent contenir des composants décrits en différents langages ou à différents niveaux d'abstraction, ce qui ajoute un aspect d'hétérogénéité de plus.

Une autre caractéristique très particulière aux systèmes embarqués par rapport à d'autres systèmes électroniques concerne leurs contraintes de temps de mise sur le marché. Dans ce contexte, il faut absolument réduire le temps de conception et de validation de tels systèmes. Dans les sections qui suivent, nous allons examiner de plus près les systèmes embarqués ainsi que les étapes nécessaires pour les concevoir et les valider.

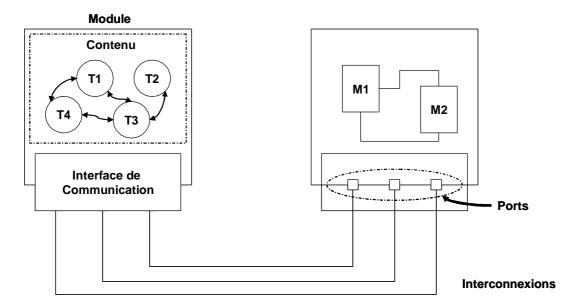

#### 2.2.1 Concepts de base pour la spécification des systèmes

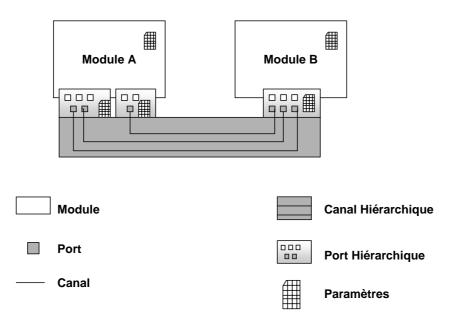

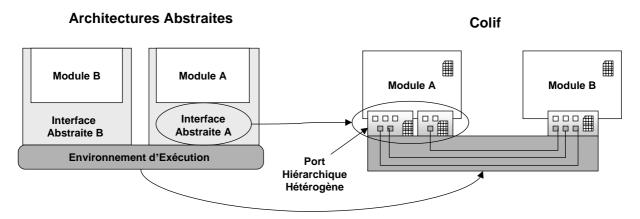

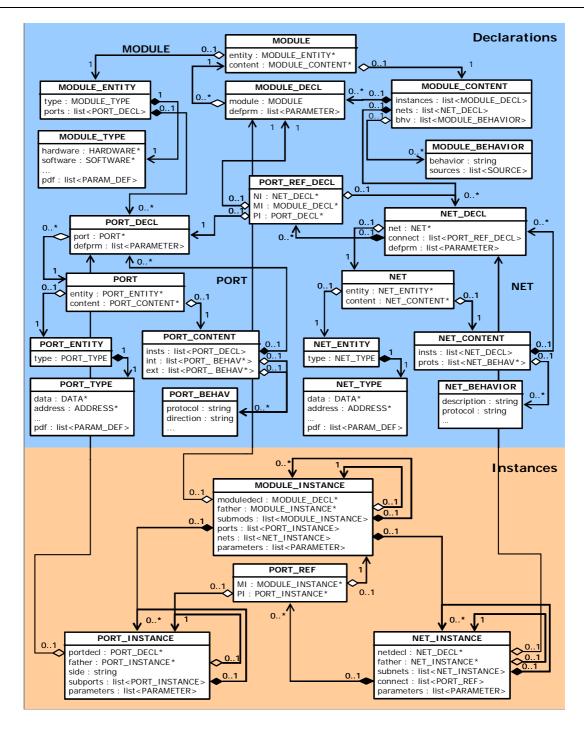

Les concepts de base qui sont présentés ici peuvent s'appliquer aux systèmes hétérogènes électroniques d'une manière générale, et pas seulement à ceux qui sont embarqués. Trois concepts sont fondamentaux pour la spécification des systèmes hétérogènes : le module, l'interface de communication et l'interconnexion. Leur composition forme ce que nous appelons un système. Nous pouvons définir qu'un système est une entité formée par un ensemble de modules interconnectés qui communiquent entre eux via des interfaces de communication comme le montre la Figure 2-1 Par la suite, nous expliquons non seulement ces trois concepts fondamentaux, mais aussi d'autres liés aux systèmes qui seront utilisés tout au long de ce travail.

Figure 2-1 Concepts de Base de Systèmes

#### Module

Un module est une entité qui implémente une ou plusieurs fonctionnalités et qui communique avec l'environnement externe en utilisant une interface de communication. Un module est composé de deux parties distinctes : le contenu et l'interface.

Le contenu représente la fonctionnalité ou le comportement du module. C'est dans le contenu que réside le calcul effectué par le module. Ce contenu peut être représenté par des unités de calcul comme des tâches ou des processus (le module à gauche de la Figure 2-1), ou sinon par d'autres modules qui implémentent le comportement (le module à droite de la Figure 2-1). Si le contenu du module est composé d'autres modules, le module est dit hiérarchique. Ceci étant, un système peut être vu comme un module hiérarchique. La Figure 2-2 présente un exemple de module décrit en SystemC. Le contenu de ce module est implémenté par une tâche (thread) nommé  $HS\_Write$ .

L'interface permet au module de communiquer avec le reste du système. Pour cela, l'interface est connectée au réseau d'interconnexions du système.

```

1.

class Adapter_out_rtl_handshake_bca_fifo: public sc_module {

2.

public :

3.

void HS_Write();

sc_in<bool> s_sel;

4.

5.

Interface de

sc_out<bool> s_done;

6.

sc_in<bit2> burst;

7.

va_out_bca_fifo<int> v_burstv

Communication

8.

sc_in_clk sclk;

SC_CTOR(Adapter_out_rtl_handshake_bca_pipe){

9.

10.

SC_THREAD(HS_Write);

11.

sensitive_pos << sclk;

12.

13.

14.

void Adapter_out_rtl_handshake_bca_fifo::HS_Write(){

15.

while (true) {

17.

if(s_sel.read()) {

18.

int data;

19.

DataConv(burst.read(),data);

20.

v_burst.Put(data);

s done.write(true);

11.

Contenu

13.

}else {

s_done.write(false);

14.

15.

}

16.

wait();

17.

}

18. };

19.

```

Figure 2-2 Exemple de Module décrit en SystemC

#### **Interface de communication**

Une interface de communication est un ensemble de points d'accès permettant à un module de communiquer avec le reste du système.

Selon le type d'implémentation du module (comme nous verrons plus tard), ces points d'accès peuvent être représentés par des fonctions de communication (pour le cas d'implémentation logicielle) ou par des ports physiques (pour le cas d'implémentation matérielle). Comme simplification, dans ce travail nous adoptons le terme « ports » pour designer ces point d'accès indépendamment du type d'implémentation du module.

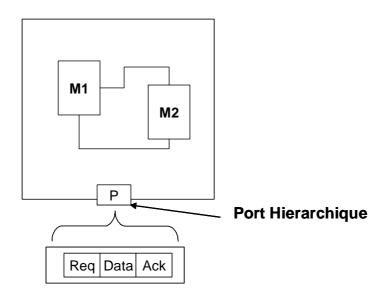

Un port peut être élémentaire ou hiérarchique (c'est-à-dire englobant plusieurs ports ayant une même sémantique comme, par exemple, appartenant au même protocole de communication). Un exemple de port élémentaire est présenté par la Figure 2-2. Nous pouvons voir que le module décrit en SystemC possède cinq ports élémentaires (s\_sel,

s\_done, burst, v\_burst et sclk). La Figure 2-3 montre un exemple de port hiérarchique. Dans cet exemple, le module doit envoyer une donnée au reste du système en utilisant le protocole de communication *Handshake*. Le module envoie d'abord une requête (port *Req*), puis la donnée (port *Data*) et enfin il reçoit un acquittement (port *Ack*). L'interface du module peut être spécifiée en utilisant les trois ports nécessaires au protocole ou en les regroupant dans un seul port hiérarchique *P*.

Figure 2-3 Exemple de Port Hiérarchique

#### **API de communication**

L'ensemble des actions associés aux ports constitue ce que nous appelons l'API (venant de l'anglais Application Programming Interface) de communication du module. La connaissance de l'API de communication d'un module est essentielle au concepteur pour qu'il sache comment un module peut interagir avec le reste du système. En effet, lors de la sélection par le concepteur d'un module qui va faire partie d'un système, il suffit de connaître la fonctionnalité générale du module et son API de communication. Les détails de l'implémentation et de la fonctionnalité peuvent être ignorés. En connaissant l'API de communication d'un module, le concepteur sait comment ce module peut être accédé par les autres modules du système.

L'API de communication d'un module varie selon le niveau d'abstraction auquel l'interface de celui-ci est décrite. Nous verrons, plus tard, que l'API peut faire abstraction de plusieurs aspects de la communication tels que : type de donnée, adressage, temps, etc. Ainsi, dans un niveau d'abstraction plus élevé, une API peut être composée de primitives comme *Print (file)*, où le type de donnée et l'adressage sont abstraits, tandis que dans un niveau plus

bas, l'API peut être composée par exemple d'une primitive pour lire un octet dans une adresse donnée (*Read (byte, address)*).

#### Protocole de communication

Un protocole de communication est un ensemble de règles qui définit la façon avec laquelle les données sont échangées sur un canal de communication. Ces règles peuvent englober plusieurs aspects de la communication comme : l'API de communication, le format des données, l'encodage des bits, la synchronisation des horloges, les mécanismes de correction et détection des erreurs de transmission et le routage des données [Sys04]. Handshake (rendez-vous), FIFO (file d'attente) et MPI (passage de message) sont des exemples de protocoles de communication connus.

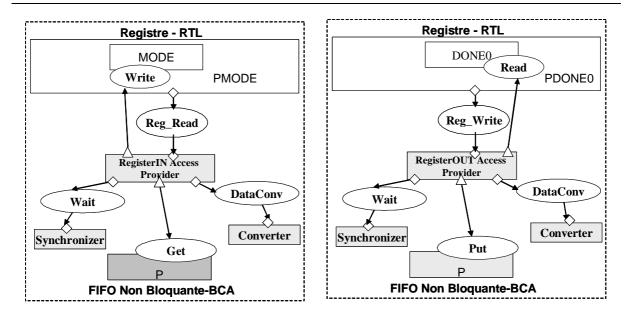

FIGURE 17 FIGURE

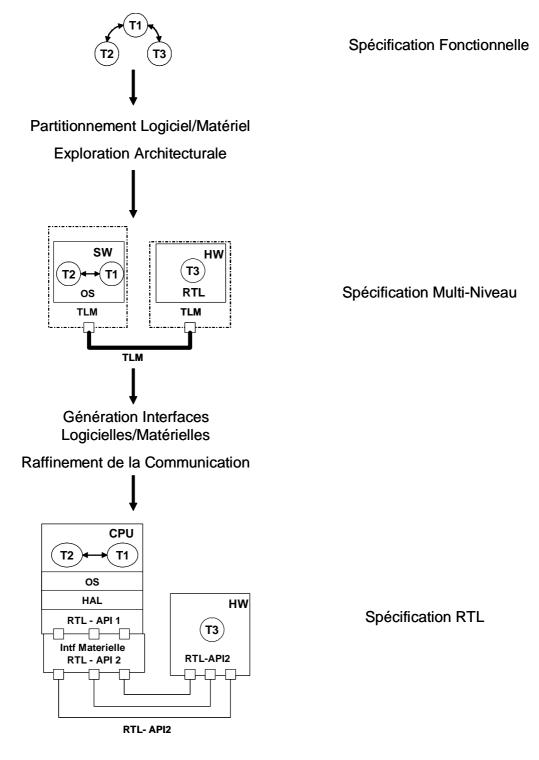

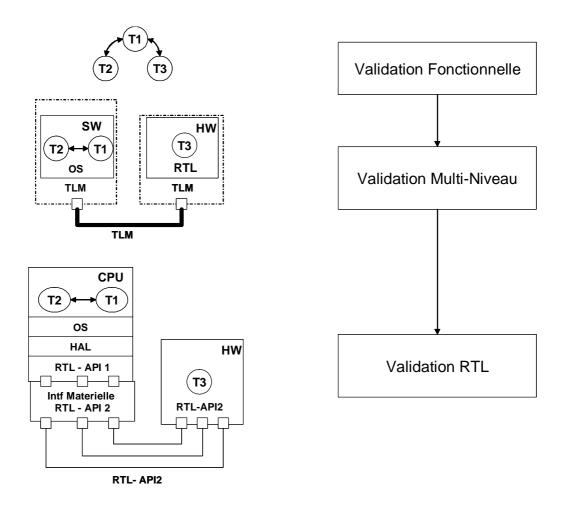

Figure 2-4 Différence entre API et Protocole de Communication

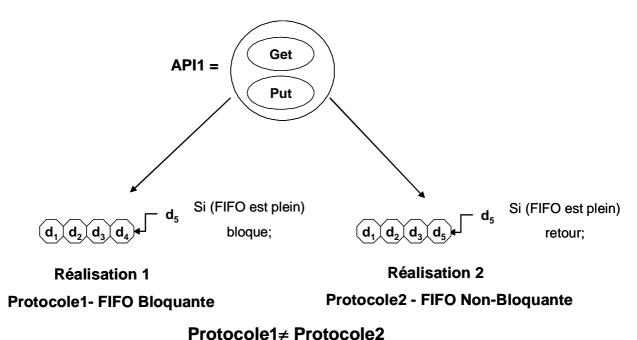

Le terme protocole de communication est souvent confondu avec l'API de communication. Ce dernier correspond aux primitives (actions) définies pour la communication. Alors que le premier est plutôt lié à la réalisation de la communication. La façon avec laquelle une API va être réalisée en utilisant les ressources disponibles définit le protocole de communication [Gra05]. La Figure 2-4 montre la différence entre les deux concepts. L'API possède les primitives *Get* pour lire une donnée et *Put* pour écrire une donnée. Mais cette API peut être réalisée en utilisant deux protocoles différents. Le premier

est une *FIFO* bloquante, où l'écriture d'une donnée bloque l'exécution du module si le tampon est plein ; et le deuxième est une *FIFO* non bloquante, où l'écriture d'une donnée n'implique pas le blocage du module si le tampon est plein.

#### Interconnexion

L'interconnexion relie des ports entre eux. Elle est chargée de transporter les données entre les modules. Comme le but principal de l'interconnexion est de permettre la communication entre les modules, elle est souvent désignée par le terme canal de communication. Les interconnexions permettent, en fait, la mise en relation de plusieurs modules pour rendre leur fonctionnement interdépendant [Tsi03]. Cette mise en relation se situe au niveau des interfaces de communication.

Les concepts qui définissent une interconnexion sont [Kri05] :

- Le média qui véhicule l'information (par exemple des fils physiques ou réseaux)

- Le type de données transmises (par exemple des données génériques ou données avec représentation fixe),

- Le comportement (la procédure utilisée pour acheminer les données à travers le média).

Selon le niveau d'abstraction et le modèle d'exécution, ces trois concepts peuvent se présenter différemment pour les canaux de communication. Pour des niveaux d'abstraction plus élevés, le canal de communication peut se présenter comme un canal abstrait qui contient des procédures de routage des donnés et d'arbitration et qui transporte des types de données complexes tels que des images. Tandis que pour les niveaux plus bas, le canal de communication peut correspondre à des fils physiques qui transportent des bits.

#### Modèle d'exécution

Le modèle d'exécution d'un module concerne la réalisation du module. Si le module est réalisé par un programme qui s'exécute sur un processeur, son modèle d'exécution est dit logiciel. Tandis que si le module est réalisé en utilisant un bloc matériel (ASIC), nous disons que le modèle d'exécution de ce module est matériel.

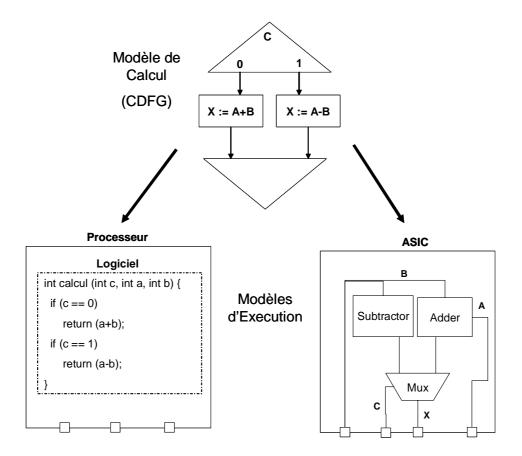

Le terme modèle d'exécution doit être différencié du terme modèle de calcul. Le deuxième consiste en une représentation du comportement (calcul) d'un module, alors que le premier concerne la façon dont ce comportement sera réalisé. Plusieurs travaux concernant les modèles de calcul existent dans la littérature. Quelques exemples de modèles de calcul sont : FSM, CDFG [Ora86], Réseau de Petri [Pet81], Evénement Discret [Buc90], Processus

de Kahn [Kan74], etc. Un modèle de calcul peut avoir plusieurs modèles d'exécution comme le montre la Figure 2-5. Dans ce cas, la fonctionnalité représentée par le modèle de calcul (CDFG) peut être réalisée soit par une fonction logicielle qui s'exécute sur un processeur, soit par un module hiérarchique matériel.

Figure 2-5 Différence entre Modèle d'exécution et Modèle de Calcul

Le modèle d'exécution détermine aussi comment un module communique avec le reste du système. Un module logiciel communique à travers des appels de fonctions logicielles. Alors que pour un module matériel, la communication est faite par moyen des ports physiques. Comme nous pouvons le remarquer, les deux modèles d'exécution utilisent différents concepts pour la communication. Lors de la conception d'un système, le concepteur doit implémenter des interfaces (comme nous le verrons plus tard) pour adapter la communication entre ces deux modèles d'exécution.

#### 2.2.2 Niveaux d'abstraction des modules

La séparation de la partie de calcul de celle de la communication du module permet une certaine indépendance entre ces deux parties. Lors de la conception d'un système hétérogène embarqué, le calcul et la communication peuvent être raffinés de façon indépendante. Le terme raffinement utilisé ici désigne le processus de transformation d'une entité (de calcul ou de communication) vers un niveau d'abstraction plus proche de l'implémentation finale. Dans ce travail, nous allons traiter les niveaux d'abstraction du calcul et de la communication séparément. Cette section est consacrée à analyser les niveaux d'abstraction de la partie de calcul du module. Comme le modèle d'exécution d'un module peut être logiciel ou matériel, nous traitons les deux cas. Nous verrons que selon le modèle d'exécution d'un module, les niveaux d'abstraction traitent des concepts bien différents.

#### Niveaux d'abstraction du logiciel

L'exécution du comportement d'un module logiciel se fait par l'interprétation d'un ensemble d'instructions (programme). Cette interprétation est faite par une plateforme (ou un environnement) d'exécution. Selon le niveau d'abstraction du logiciel, cet environnement se présente d'une façon différente. Il peut être représenté soit par un environnement logiciel tel qu'un système d'exploitation ou un *middleware*, soit par une plateforme matérielle comme un processeur. Généralement, un module logiciel s'exécute sur plusieurs couches d'environnement d'exécution où la dernière est toujours le processeur.

Le niveau d'abstraction d'un module logiciel concerne l'abstraction des opérations sur les données (calcul) effectuées par ce module. Ce niveau d'abstraction dépend, en effet, de l'ensemble des opérations (API) fournies par l'environnement d'exécution juste au dessous du module logiciel. Prenons comme exemple un environnement d'exécution qui fournit des opérations pour manipuler des matrices. L'API de cet environnement d'exécution peut posséder des opérations comme MultiplierMatrice (Matrice A, Matrice B) pour multiplier deux matrices. Le module logiciel qui s'exécute sur cet environnement est décrit à un niveau d'abstraction très élevé. Un autre exemple est quand l'environnement d'exécution fournit des opérations telles que *LOAD/ STORE* de données de/sur la mémoire, le calcul va être décrit dans un niveau d'abstraction très bas. Nous pouvons voir que l'API fournie par le premier environnement fait une abstraction totale de la plateforme matérielle d'implémentation (le processeur), tandis que l'abstraction faite par l'API du deuxième est presque inexistante. Plus les détails du processeur sont cachés, plus élevé est le niveau d'abstraction du calcul d'un module logiciel.

Par la suite, nous présentons les différents niveaux d'abstraction auxquels un module logiciel peut être décrit :

- -Niveau Application Dans ce niveau, l'abstraction de la plateforme matérielle est totale. Les détails d'implémentation tels que le parallélisme et la synchronisation entre les différentes unités de calcul sont implicites à ce niveau. Normalement, le module logiciel est décrit en utilisant un langage de programmation de haut niveau comme C++, Java, ADA, etc. L'API de manipulation des matrices, mentionnée avant, est un exemple du type d'API fournie à ce niveau.

- -Niveau OS À ce niveau, le concepteur prend en compte la présence d'un système d'exploitation pour réaliser le calcul. L'utilisation d'un système d'exploitation rend la synchronisation et la gestion de ressources partagées entre les unités de calcul explicites. Pourtant, l'implémentation du système d'exploitation est toujours abstraite. Des détails tels que la réalisation de l'ordonnancement des unités de calcul ou de la gestion des périphériques sont cachés. Un module logiciel décrit au niveau OS consiste en un ensemble d'appels au système d'exploitation. Un exemple d'API fournie à ce niveau est le *thread* POSIX [But97].

- -Niveau HAL L'API fournie à ce niveau consiste en un ensemble d'opérations qui permettent d'abstraire les accès physiques au matériel (HAL vient de l'anglais Hardware Abstraction Layer). L'implémentation du système d'exploitation est fixée, mais il reste quelques détails de la plateforme matérielle cachés comme le processeur cible, l'architecture mémoire, etc. Un module logiciel décrit au niveau HAL contient des opérations qu'abstraient les fonctions de base d'accès au matériel tel que l'initialisation (*boot*), le changement de contexte, les entrées/sorties de base, la gestion des interruptions et l'accès aux périphériques. L'API HAL de RISC OS est un exemple d'API à ce niveau-là [RisO2].

- **-Niveau ISA** Le niveau ISA (venant de l'anglais Instruction Set Architecture) correspond à la spécification du logiciel en un langage assembleur relatif à un processeur cible. Le logiciel est décrit en utilisant des opérations tels que *LOAD* et *STORE*. Les accès physiques au matériel sont explicites. Le jeu d'instructions du processeur est l'API fournie à ce niveau.

#### Niveaux d'abstraction du matériel

Différemment au modèle d'exécution logiciel, l'exécution d'un module matériel ne passe pas par l'interprétation séquentielle d'un ensemble d'instructions. L'exécution du

comportement d'un module matériel correspond vraiment à la réalisation du calcul par une plateforme matérielle.

Pour le modèle d'exécution matériel, nous pouvons distinguer les deux niveaux d'abstraction principaux :

-Niveau Comportemental — À ce niveau, la fonctionnalité du module est décrite, mais les ressources nécessaires pour accomplir sa réalisation sont abstraites. C'est-à-dire, aucune hypothèse n'est faite sur l'implémentation physique. Généralement, le concepteur utilise des langages HDL (venant de l'anglais Hardware Description Language) tels que VHDL, Verilog ou SystemC pour décrire un module à ce niveau. Ces langages offrent au concepteur des opérations de calcul de très haut niveau qui sont comparables à ceux des langages de programmation tels que : C++, Java, etc.

-Niveau RTL − À ce niveau, les détails de synchronisation physiques sont pris en compte, les ressources matérielles sont allouées et assignées aux différentes parties de calcul du module, et l'exécution du comportement du module est réordonnancé. Comme la description d'un module à ce niveau-là peut être très complexe, il existe plusieurs outils qui font la synthèse de haut niveau pour faciliter le passage du niveau comportemental au RTL [Gaj91].

#### 2.2.3 Niveaux d'abstraction de la communication

Ainsi que le comportement du module, la partie de communication peut être décrite à plusieurs niveaux d'abstraction. Les paramètres qui définissent le niveau d'abstraction de la communication sont les suivants :

**-Données Transmises** – la granularité des données transmises pendant une opération de communication joue un rôle important en ce qui concerne le niveau d'abstraction de la communication. Normalement, dans les niveaux plus élevés, les données transmises consistent en types abstraits et plus complexes comme une image par exemple. Alors que pour les niveaux plus bas comme RTL, la communication est faite par l'envoi/réception des bits.

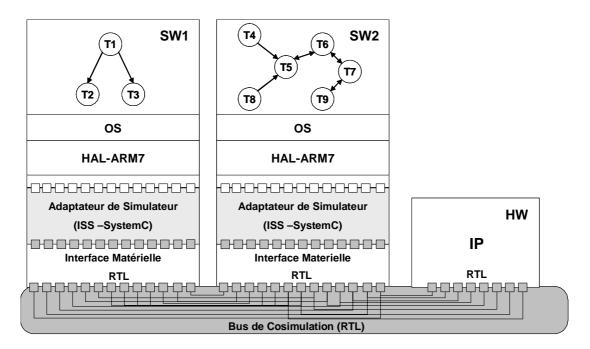

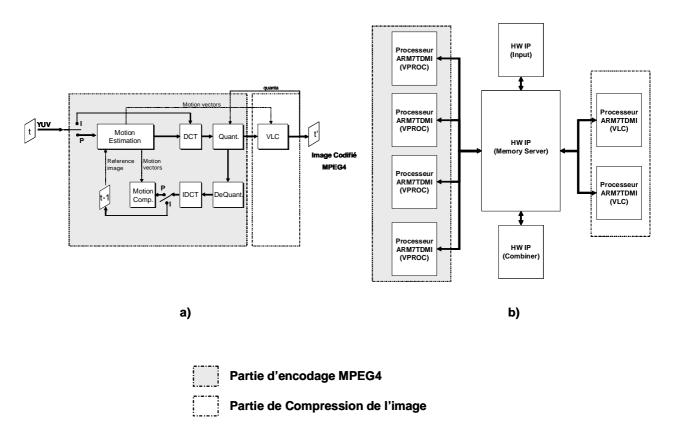

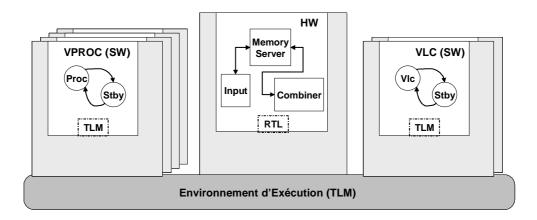

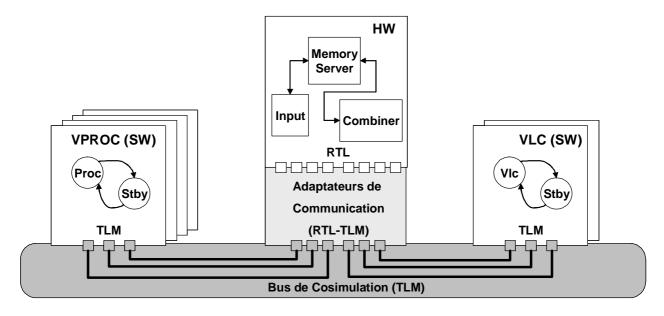

-Temps – Le modèle de temps utilisé pour l'échange de données influence également le niveau d'abstraction de la communication. Le modèle de temps peut utiliser une horloge logique ou physique. Avec l'horloge logique, le temps n'avance que s'il y a un échange de données entre deux ou plusieurs modules. L'horloge logique nous donne, effectivement, ce que nous appelons l'ordre partiel des événements d'échange de