## Construction de Modèles Réduits et Vérification Symbolique de Circuits Industriels décrits au Niveau RTL

E. Dumitrescu

#### ▶ To cite this version:

E. Dumitrescu. Construction de Modèles Réduits et Vérification Symbolique de Circuits Industriels décrits au Niveau RTL. Micro et nanotechnologies/Microélectronique. Université Joseph-Fourier - Grenoble I, 2003. Français. NNT: . tel-00003667

## HAL Id: tel-00003667 https://theses.hal.science/tel-00003667

Submitted on 31 Oct 2003

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

### **THÈSE**

pour obtenir le grade de

#### DOCTEUR DE L'UNIVERSITÉ JOSEPH FOURIER

Discipline: MICROÉLECTRONIQUE

ÉCOLE DOCTORALE ELECTRONIQUE, ELECTROTECHNIQUE, AUTOMATIQUE, TÉLÉCOMMUNICATIONS, SIGNAL

présentée et soutenue publiquement par

#### EMIL DUMITRESCU

le 7 Octobre 2003

# CONSTRUCTION DE MODÈLES RÉDUITS ET VÉRIFICATION SYMBOLIQUE DE CIRCUITS INDUSTRIELS DÉCRITS AU NIVEAU RTL

Directeur de thèse : Dominique BORRIONE

#### JURY

Rapporteurs Mr Hans EVEKING, Prof. Université de Darmstadt Mr Charles ANDRÉ, Prof. Université de Nice

Examinateurs Mr Nicolas HALBWACHS, Directeur de Recherche CNRS

Mr Christian BERTHET, ST-Microelectronics

Directeur de thèse Mme Dominique BORRIONE, Prof. Université Joseph Fourier

Thèse préparée àu Laboratoire **Techniques de l'Informatique et de la** Microélectronique pour l'Architecture des ordinateurs (TIMA)

#### Remerciements

Je souhaite m'adresser en premier lieu aux membres du jury de thèse. Je remercie donc Messieurs Hans EVEKING et Charles ANDRE pour avoir accepté le travail de rédaction des rapports de pré-soutenance. Merci pour la relecture approfondie du manuscrit, ainsi que pour leurs remarques constructives et leurs encouragements.

Je remercie Messieurs Nicolas HALBWACHS et Christian BERTHET pour m'avoir fait l'honneur de faire partie de ce jury.

Je remercie enfin Mme Dominique BORRIONE. Toute ma reconnaissance pour son accueil exceptionnel au sein de l'équipe VDS, son soutien et sa patience, et pour l'ensemble des opportunités qu'elle m'a offertes pendant toutes ces années.

Je souhaite maintenant adresser toute ma sympathie à mes collègues du laboratoire TIMA, en particulier aux membres (encore présents, ou absents à ce jour) de l'équipe VDS. C'est à eux que je dois des moments inoubliables, passés dans un cadre aussi bien amical, bienveillant et drôle, que passionné, encourageant et enrichissant pour mon travail. Un grand merci donc à Menouer BOUBEKEUR, Diana TOMA, Julien SCHMALTZ, Ghiath AL-SAMMANE, Eric GASCARD, Philippe GEORGELIN et Cyrille CHAVET.

Je remercie Pierre OSTIER pour son expérience de chercheur qu'il n'a pas hésité à partager, ainsi que pour son assistance en tant qu'ingénieur système (notamment lors d'incidents matériels, produits les week-ends ou tard le soir, à l'époque où je rédigeais ce manuscrit). Mais je lui dois surtout une sacrée dose d'encouragements, de conseils (de toute sorte...), de bonne humeur, de soutien et d'amitié. Je garde un souvenir très agréable de cette longue période durant laquelle nous avons partagé le même bureau...

Un grand merci (en forme de saxophone ténor) à Claude LE FAOU. Merci pour ses conseils, son aide bienveillante, sa disponibilité et sa patience (envers nous tous d'ailleurs). Mais Claude a été pour nous plus que tout cela. C'est grâce à lui qu'il existe un moment privilégié dans chaque journée, nous permettant de nous retrouver tous autour d'un excellent café (dont il a conservé le secret des fournisseurs). J'ajoute mon grief vis-à-vis de son départ à la retraite...

Mes remerciements à Bénédicte FLUXA, et toute ma gratitude pour l'aide qu'elle m'a apportée depuis son arrivée au sein de l'équipe VDS.

Un grand merci à Eduard (Ed) CERNY et à Christian BERTHET, pour leur soutien et leurs encouragements durant mes différents "séjours" à ST-Microelectronics. J'ajoute que le temps passé là-bas a été extrêmement profitable pour l'avancement de mon travail de thèse. J'adresse également mes remerciements et mes amitiés à Sébastien FRANCOIS, Stéphane BREFORT, Laurence ALBACETE, Philippe DEBAUD, Danielle JACOB, Bruno DENIS, Xavier CHBANI, Fabrice PICHAT, Karim DAHMANE et Nathalie DESCHAMPS.

Enfin, je remercie les membres de l'équipe CAD du département EECS de l'Université de Californie à Berkeley pour leur accueil chaleureux durant mon séjour dans leur équipe, en tant qu'invité. Merci à Robert BRAYTON, Flora OVIEDO, Adrian ISLES, Sriram KRISHNAN, Sriram RAJAMANI, Sunil KHATRI et Luciano LAVAGNO.

# Table des matières

| Intr | Introduction |       |                                                                                                                                            |    |

|------|--------------|-------|--------------------------------------------------------------------------------------------------------------------------------------------|----|

| Par  | rtie         | I :   | Représentation et Algorithmes                                                                                                              | 9  |

| 1 I  | Rep          | résen | tation symbolique des machines d'états finis                                                                                               | 11 |

| 1    | 1.1          | Intro | $\operatorname{duction} \dots \dots$ | 11 |

| 1    | 1.2          | Le m  | odèle de machine d'états finis                                                                                                             | 13 |

|      |              | 1.2.1 | Notions préliminaires                                                                                                                      | 13 |

|      |              | 1.2.2 | Application à l'exemple                                                                                                                    | 15 |

| 1    | 1.3          | Tech  | niques de représentation                                                                                                                   | 15 |

|      |              | 1.3.1 | Représentation Booléenne                                                                                                                   | 15 |

|      |              | 1.3.2 | Représentation symbolique                                                                                                                  | 17 |

|      |              | 1.3.3 | Modèle hiérarchique de Mealy                                                                                                               | 19 |

|      |              | 1.3.4 | Représentation symbolique de l'exemple                                                                                                     | 20 |

| 1    | 1.4          | Parce | ours symbolique d'une machine d'états finis                                                                                                | 21 |

|      |              | 1.4.1 | Image et pré-image d'un ensemble d'états                                                                                                   | 22 |

|      |              | 1.4.2 | Ensembles d'états : représentation et évaluation                                                                                           | 23 |

|      |              |       | 1.4.2.1 Les Diagrammes de Décision Binaire                                                                                                 | 23 |

|      |              |       | 1.4.2.2 Les techniques de résolution Sat                                                                                                   | 24 |

|      |              | 1.4.3 | Mise en œuvre                                                                                                                              | 25 |

|      |              | 1.4.4 | Retour sur le calcul de l'image : relationnel ou fonctionnel?                                                                              | 28 |

|      |              |       | $1.4.4.1  \text{La méthode relationnelle}  \dots  \dots  \dots  \dots  \dots$                                                              | 29 |

|      |              |       | $1.4.4.2  \text{La méthode fonctionnelle}  \dots  \dots  \dots  \dots  \dots$                                                              | 31 |

|      |              | 1.4.5 | Tour d'horizon des techniques de parcours symbolique                                                                                       | 32 |

|      |              | 1.4.6 | Conclusion                                                                                                                                 | 34 |

| <b>2</b> | Spé                | cificati | ion : système et environnement                                        | <b>35</b>  |

|----------|--------------------|----------|-----------------------------------------------------------------------|------------|

|          | 2.1                | Introd   | luction                                                               | 35         |

|          | 2.2                | Spécif   | ications logiques - la logique temporelle                             | 36         |

|          |                    | 2.2.1    | La logique temporelle CTL*                                            | 37         |

|          |                    | 2.2.2    | Logiques temporelles à utilisation industrielle                       | 39         |

|          |                    |          | 2.2.2.1 Le sous-ensemble $\forall$ -CTL                               | 39         |

|          |                    |          | 2.2.2.2 La logique linéaire LTL $^+$ et le macro-langage FQL          | 39         |

|          |                    |          | 2.2.2.3 La logique arborescente CTL et le macro-langage SUGAR .       | 41         |

|          | 2.3                | Spécif   | ications opérationnelles                                              | 43         |

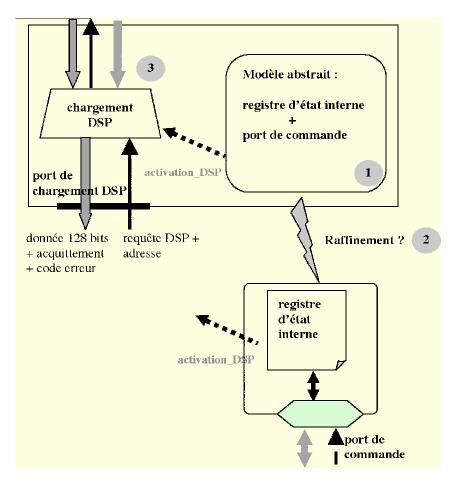

|          |                    | 2.3.1    | Modèles abstraits                                                     | 43         |

|          |                    | 2.3.2    | Modèles de référence                                                  | 45         |

|          |                    | 2.3.3    | Moniteurs                                                             | 45         |

|          |                    | 2.3.4    | Spécification de l'environnement                                      | 47         |

|          | 2.4                | Algori   | ithmes de preuve                                                      | 48         |

|          |                    | 2.4.1    | Restriction du modèle symbolique pour la preuve                       | 50         |

|          |                    | 2.4.2    | Preuve de spécifications logiques                                     | 52         |

|          |                    |          | 2.4.2.1 Preuve des formules CTL                                       | 53         |

|          |                    |          | 2.4.2.2 Exemple : preuve de propriétés de l'arbitre à trois entrées . | 54         |

|          |                    |          | 2.4.2.3 Preuve des formules LTL                                       | 55         |

|          |                    |          | 2.4.2.4 Exemple : Preuve d'une spécification logique linéaire         | 59         |

|          |                    | 2.4.3    | Preuve de spécifications opérationnelles                              | 61         |

|          |                    |          | 2.4.3.1 Modèles abstraits : preuve de raffinement                     | 61         |

|          |                    |          | 2.4.3.2 Exemple : preuve de raffinement par rapport à un modèle       |            |

|          |                    |          | abstrait                                                              | 61         |

|          |                    |          | 2.4.3.3 Modèles de référence : preuve d'équivalence                   | 63         |

|          |                    |          | 2.4.3.4 Exemple : preuve d'équivalence séquentielle                   | 65         |

|          |                    |          | 2.4.3.5 Moniteurs: preuve d'invariants                                | 68         |

|          |                    |          | 2.4.3.6 Exemple : spécification d'un moniteur et preuve d'invariants  | 69         |

|          |                    | 2.4.4    | Prise en compte des spécifications d'environnement                    | 70         |

|          | 2.5                | Discus   | ssion                                                                 | 70         |

|          |                    |          |                                                                       |            |

| ъ        | - <b>-</b> - 4 : - | тт .     | Charléaire de Mérie estiva                                            | 70         |

| P.       | artie              | : 11 :   | Stratégies de Vérification                                            | 73         |

| 3        | Stra               | atégies  | s de preuve                                                           | <b>7</b> 5 |

|          | 3.1                | Le bes   | soin de stratégies                                                    | 75         |

|          | 3.2                | Appro    | oche structurelle                                                     | 77         |

|          |                    | 3.2.1    | Méthode descendante                                                   | 77         |

|          |                    |          | 3.2.1.1 Décomposition simple                                          | 77         |

|   |                                                          |                                                 | 3.2.1.2                                    | Raisonnement "Je suppose-tu garantis"                                                                                          | . 79   |  |

|---|----------------------------------------------------------|-------------------------------------------------|--------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------|--------|--|

|   |                                                          |                                                 | 3.2.1.3                                    | Décomposition de la preuve de raffinement                                                                                      | . 84   |  |

|   |                                                          | 3.2.2                                           | Méthode                                    | e ascendante                                                                                                                   | . 88   |  |

|   |                                                          | 3.2.3                                           | Exploite                                   | r la symétrie                                                                                                                  | . 89   |  |

|   | 3.3                                                      | Appro                                           | che comp                                   | ortementale                                                                                                                    | . 90   |  |

|   |                                                          | 3.3.1                                           | Retour s                                   | ur la spécification d'environnement                                                                                            | . 90   |  |

|   |                                                          | 3.3.2                                           | La parti                                   | tion comportementale                                                                                                           | . 91   |  |

|   | 3.4                                                      | Exten                                           | sion de la                                 | partition comportementale : partition fonctionnelle grâce à                                                                    |        |  |

|   |                                                          | la sim                                          | ulation sy                                 | mbolique                                                                                                                       | . 92   |  |

|   |                                                          | 3.4.1                                           | Modes o                                    | pératoires                                                                                                                     | . 92   |  |

|   |                                                          | 3.4.2                                           | Définitio                                  | ns                                                                                                                             | . 94   |  |

|   |                                                          | 3.4.3                                           | Calcul d                                   | u modèle réduit                                                                                                                | . 95   |  |

|   | 3.5                                                      | Concl                                           | usion                                      |                                                                                                                                | . 98   |  |

| 4 | $\mathbf{Mis}$                                           | e en œ                                          | euvre et                                   | ${f Application}$                                                                                                              | 101    |  |

|   | 4.1                                                      | Introd                                          | uction                                     |                                                                                                                                | . 101  |  |

|   | 4.2                                                      | Le sta                                          | ndard IEI                                  | EE 1076.6 pour la synthèse RTL                                                                                                 | . 102  |  |

|   | 4.3                                                      | Sémantique du sous-ensemble IEEE pour la preuve |                                            |                                                                                                                                |        |  |

|   |                                                          | 4.3.1                                           | Extracti                                   | on d'un modèle symbolique                                                                                                      | . 107  |  |

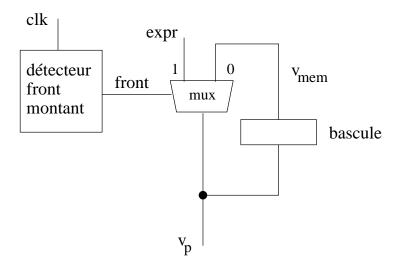

|   |                                                          |                                                 | 4.3.1.1                                    | Détection du schéma de synchronisation                                                                                         | . 107  |  |

|   |                                                          |                                                 | 4.3.1.2                                    | Détection des variables d'état                                                                                                 | . 108  |  |

|   |                                                          |                                                 | 4.3.1.3                                    | Extraction des fonctions de transition et de sortie                                                                            | . 108  |  |

|   |                                                          | 4.3.2                                           | Retour s                                   | ur la sémantique du cycle de simulation                                                                                        | . 111  |  |

|   |                                                          |                                                 | 4.3.2.1                                    | Gestion des verrous                                                                                                            | . 115  |  |

|   | 4.4                                                      | Mise e                                          | n œuvre d                                  | le la stratégie de vérification basée sur la simulation symboliq                                                               | ле 118 |  |

|   | 4.4.1 Description des séquences de simulation symbolique |                                                 | ion des séquences de simulation symbolique | . 118                                                                                                                          |        |  |

|   | 4.5                                                      | Applie                                          | ${ m cation}: { m v} \epsilon$             | rification formelle d'un circuit industriel                                                                                    | . 121  |  |

|   |                                                          | 4.5.1                                           | Introduc                                   | ${\rm tion} \dots \dots$ | . 121  |  |

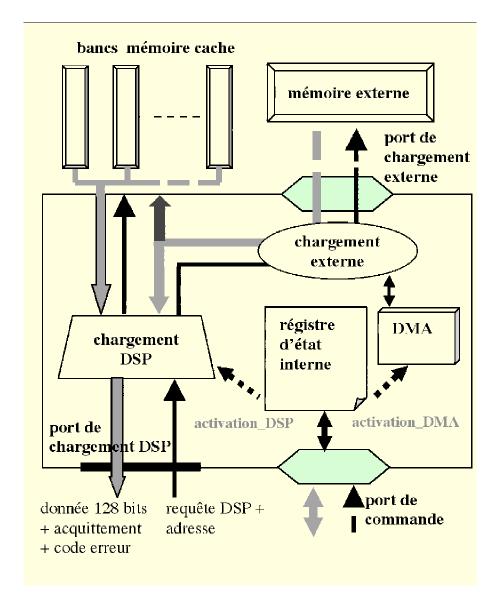

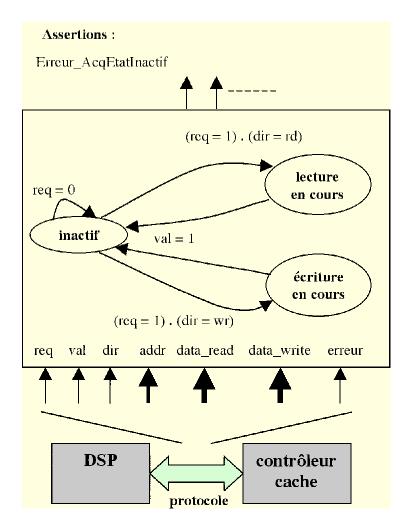

|   |                                                          | 4.5.2                                           | Etude de                                   | e cas : un contrôleur de cache d'instructions                                                                                  | . 121  |  |

|   |                                                          |                                                 | 4.5.2.1                                    | Présentation de l'architecture                                                                                                 | . 121  |  |

|   |                                                          |                                                 | 4.5.2.2                                    | Le modèle VHDL                                                                                                                 | . 123  |  |

|   |                                                          |                                                 | 4.5.2.3                                    | Spécification formelle du contrôleur de cache                                                                                  | . 123  |  |

|   |                                                          |                                                 | 4.5.2.4                                    | Vérification par l'approche ascendante                                                                                         | . 126  |  |

|   |                                                          |                                                 | 4.5.2.5                                    | Vérification par application de la partition fonctionnelle .                                                                   | . 131  |  |

| C | onclu                                                    | ısion e                                         | t perspe                                   | $\operatorname{ctives}$                                                                                                        | 135    |  |

| Aı           | nnex  | <b>ce</b>                                                                   | 137 |

|--------------|-------|-----------------------------------------------------------------------------|-----|

| $\mathbf{A}$ | Des   | cription VHDL des moniteurs utilisés                                        | 139 |

|              | A.1   | Moniteur permettant de vérifier la propriété DSP-4                          | 139 |

|              | A.2   | Moniteur permettant de vérifier les propriété de correction du port de com- |     |

|              |       | mande                                                                       | 141 |

| В            | Mod   | délisation abstraite                                                        | 143 |

|              | B.1   | Modèle abstrait utilisé pour le signal $activation\_DSP$                    | 143 |

|              | B.2   | Modèle abstrait décomposé utilisé pour le signal $activation\_DSP$          | 144 |

| Bi           | bliog | graphie                                                                     | 145 |

#### Introduction

Dans le contexte du développement des circuits numériques, le niveau de description communément utilisé pour la conception et accepté à la fois par les outils de simulation, de synthèse et de vérification est le niveau "transfert de registres" (RTL). Par conséquent, la vérification de descriptions RTL est une étape à la fois prédominante et incontournable. La complexité croissante des circuits réalisés requiert des méthodes complémentaires pour appuyer la simulation, dans le but de renforcer la fiabilité de la conception du circuit. La vérification de modèles est une technique de preuve formelle qui a émergé au cours des dernières années, et qui a pu être appliquée avec succès à des projets industriels. Par conséquent, cette technique a été mise en œuvre au sein de nombreux outils commerciaux ou du domaine public. A l'heure actuelle, la vérification formelle de descriptions RTL bénéficie d'un cadre automatisé et relativement facile d'utilisation. Pourtant, les limites imposées par sa complexité exponentielle rendent son utilisation problématique. Etant donné un circuit de taille importante et une propriété à vérifier, il est impossible, pour un utilisateur non expert, de prévoir si l'évaluation de la propriété pourra se faire dans les limites des ressources (temps et mémoire) disponibles. De ce fait, l'application de la vérification de modèles est aujourd'hui limitée à des circuits de taille très réduite<sup>1</sup>, ne contenant pas plus de quelques centaines de registres.

L'usage de spécifications plus abstraites et exécutables permettrait de décrire les caractéristiques essentielles du circuit que l'on souhaite élaborer, tout en limitant la complexité de la représentation. C'est dans ce contexte que la vérification de modèles serait plus efficace. Une étape de génération telle que la synthèse "de haut niveau" permettrait d'obtenir une description RTL synthétisable à partir d'une telle spécification. Cette étape devrait préserver la correction de toutes les propriétés déjà vérifiées sur la spécification. A ce jour, la synthèse "de haut niveau", lorsqu'elle est applicable, ne garantit pas que la description RTL produite vérifie de la même façon les propriétés évaluées sur la spécification initiale. Il est donc nécessaire de procéder aussi à la vérification de la description RTL résultante. Ainsi, la mise en œuvre de méthodes efficaces de vérification pour le niveau RTL demeure un sujet de grande actualité.

Au niveau RTL, les méthodes fondamentales de vérification de modèles ne permettent pas d'aboutir à des résultats dans des délais raisonnables. C'est pourquoi l'intervention manuelle de l'ingénieur de vérification est essentielle, pour guider la vérification afin d'éviter l'explosion combinatoire : il doit apporter sa connaissance sur le circuit vérifié, sur les

<sup>&</sup>lt;sup>1</sup>à l'échelle industrielle...

formules temporelles à écrire, et suggérer une stratégie adéquate de réduction de complexité de la description manipulée.

Une partie du travail de cette thèse a été menée dans un contexte industriel. A travers cette expérience, qui a permis de comparer différents outils de vérification de modèles, commerciaux et du domaine public, l'étude a été axée sur le développement de méthodes permettant d'utiliser cette technique de manière plus efficace. La principale contribution de ce travail porte sur la réduction, manuelle ou non, du modèle vérifié. La vérification compositionnelle est un concept répandu, permettant de décomposer le circuit vérifié suivant un critère structurel, suggéré par la hiérarchie de modules du circuit vérifié. Nous avons appliqué cette technique dans un cadre général, et nous l'avons adaptée à une situation réelle très importante : lorsque le module vérifié est très complexe, tout en étant un nœud terminal de la hiérarchie de modules, la décomposition structurelle devient inapplicable quoique nécessaire. En nous appuyant sur une connaissance a priori du circuit vérifié ainsi que sur sa description, nous présentons et illustrons une approche, intitulée méthode ascendante, permettant d'identifier ses fonctionnalités sous la forme de blocs fonctionnels, et de les vérifier ensuite selon l'approche compositionnelle classique.

La décomposition de la vérification peut également se faire dans le domaine comportemental. Encore une fois, en s'appuyant sur une connaissance a priori du circuit, on identifie différents scénarios d'exécution, spécifiés uniquement à l'état initial (mise sous tension) du circuit vérifié. Cette approche permet d'engendrer autant de modèles réduits que de scénarios d'exécution, pouvant être vérifiés séparément.

Notre principale contribution a été l'extension de ce raisonnement comportemental. Le comportement de certains circuits peut être décomposé de façon séquentielle. Dans une approche classique de fonctionnement, l'environnement doit produire une séquence de valeurs sur certaines entrées du circuit afin de mettre ce dernier dans un mode de fonctionnement "normal". Cette opération peut être synonyme de remise à zéro, ou encore de programmation du circuit afin de lui transmettre un nouveau paramétrage. Une fois la remise à zéro effectuée, ou le paramétrage terminé, le circuit entre dans le mode de fonctionnement "normal".

Cette méthode de décomposition est appelée partition fonctionnelle. Sa mise en place s'appuie sur la technique de simulation symbolique. Elle a été appliquée sur un circuit de taille importante et a permis d'obtenir des résultats très prometteurs en matière de réduction.

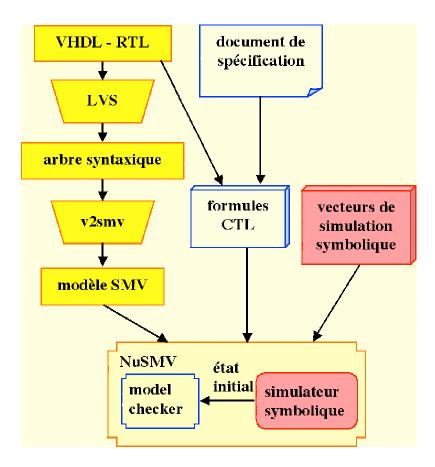

A partir de circuits décrits dans le langage VHDL, l'expérimentation des techniques de preuve offertes par les différentes outils de vérification de modèles s'est appuyé sur un outil d'extraction de machines d'états finis qu'il a été nécessaire de mettre en œuvre.

Ce document est divisé en deux parties principales. La première partie, intitulée Représentation et Algorithmes, présente le niveau propositionnel booléen, utilisé pour la représentation des circuits numériques et pour parcourir leur espace d'états. Ensuite, on présente les techniques de spécification formelle rencontrées dans l'industrie et les algorithmes de preuve associés. On discute également des techniques automatiques de réduction du modèle pour la preuve. Ces techniques fondamentales sont ensuite comparées du point de vue de leur efficacité, de leur pouvoir d'expression et de l'aisance de leur manipulation.

La deuxième partie de ce document, intitulée Stratégies de vérification, est consacrée

aux stratégies d'application de la vérification de modèles sur des circuits industriels. A ce niveau, il s'agit de manipulations à caractère plus ou moins systématique qui requièrent l'intervention de l'utilisateur (en la personne de l'ingénieur de vérification). Après la présentation des techniques compositionnelles directes et des raisonnements associés, on introduit le principe de la méthode ascendante, méthode illustrée en détail au chapitre 4 de ce document. On discute ensuite de l'application des techniques comportementales, et on formalise la partition fonctionnelle, l'étape de réduction basée sur la simulation symbolique.

Enfin, le dernier chapitre de ce document présente la mise en œuvre des stratégies introduites et des outils développés. Tout d'abord, on introduit le sous-ensemble du langage VHDL sur lequel nous avons travaillé, et on expose les concepts de base de l'extraction de machines d'états à partir des descriptions conformes à ce sous-ensemble. L'étape d'extraction est discutée du point de vue de la sémantique de simulation du langage VHDL.

La suite est consacrée au traitement d'un exemple industriel de taille importante : un contrôleur de cache d'instructions conçu par la société ST-Microelectronics et que nous avons pu étudier. Ce module a été vérifié au sein d'une équipe de développement, dans le cadre d'un projet industriel de vérification. Puis, dans un but purement expérimental, il a été vérifié selon plusieurs approches et à l'aide de différents outils de vérification. Cette démarche est exposée sur une partie des propriétés de ce module, et ses résultats sont ensuite discutés.

| INTRODUCTION |  |

|--------------|--|

|              |  |

|              |  |

|              |  |

|              |  |

# Première partie

# Représentation et Algorithmes

# Chapitre 1

# Représentation symbolique des machines d'états finis

#### 1.1 Introduction

Comme dans toute pratique scientifique ou technique, le modèle constitue le pilier central dans le processus de conception d'un circuit numérique. C'est le liant qui confère à la fois forme, intelligibilité et communicabilité aux longues étapes de raisonnement qui précèdent sa réalisation. L'approche de modélisation raisonnablement rodée aujourd'hui est axée sur le modèle conceptuel d'un système à états, inséré dans un environnement adapté. Dans un tel système, un seul état, appelé état courant, est actif à un instant donné. Les transitions(changements d'état) sont déclenchées lorsqu'un événement attendu se produit dans l'environnement. En particulier, cet événement peut signifier "passage du temps", mis en oeuvre par un mécanisme appelé horloge. Ainsi, toute étape dans le flot de conception est centrée autour d'un tel modèle, dont la "qualité" formelle varie, en s'améliorant au fur et à mesure que l'on s'approche du résultat final. La spécification produit un modèle semiformel de système à transitions, souvent à la fois abstrait et incomplet. Ce modèle sert de base au codage. Le résultat est une description HDL <sup>1</sup> ayant une sémantique formelle pour la simulation, mais sur laquelle le concepteur préférera garder une vue proche de son modèle spécifié. Un ensemble de fonctions logiques sont extraites de cette description, qui constituent un modèle formel pour la vérification et/ou la synthèse.

Tout au long de ce processus constitué de raffinements successifs, se pose le problème de la *validation*. Une fois la spécification effectuée, elle est aussitôt mise en doute : "ma spécification correspond-elle vraiment à ce que je souhaite réaliser?". Puis, une fois le circuit manuellement codé "est-ce que ma description est restée fidèle à sa spécification?". Des techniques de raisonnement et de preuve peuvent donner une réponse à ces questions, à condition que le modèle qui leur est fourni et qui sert de base à ce raisonnement soit décrit de manière formelle.

Le modèle formel le plus adapté à la conception de circuits numériques ainsi qu'à la preuve par vérification de modèles est celui de Machine d'Etats Finis (que l'on abrégera FSM) de MEALY. Ce chapitre est consacré au rappel du modèle hiérarchique de MEALY,

$<sup>^1{\</sup>rm abr\'eg\'e}$  en anglais :  $Hardware\ Description\ Language$

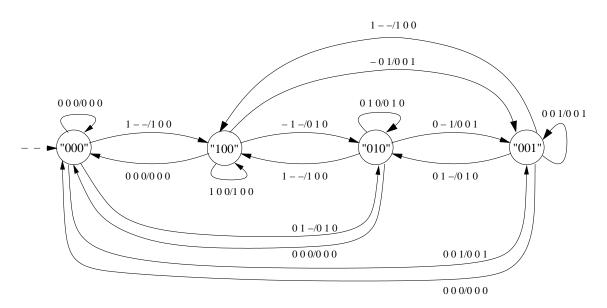

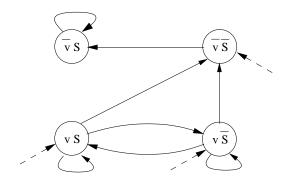

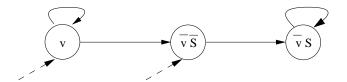

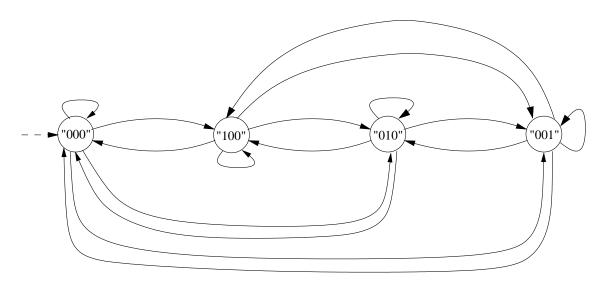

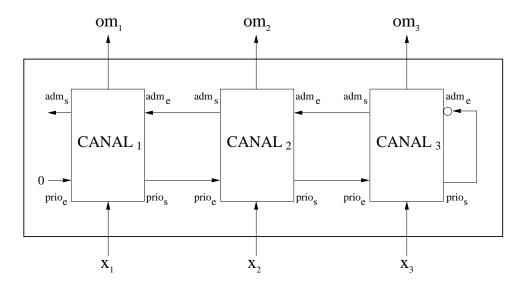

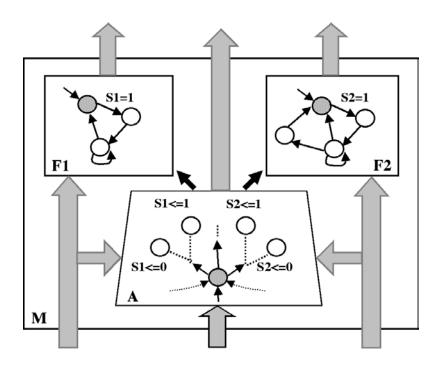

Fig. 1.1 – Arbitre à trois entrées

ainsi que de sa représentation symbolique dans la logique propositionnelle. Sont présentées ensuite les étapes de calcul symbolique qui constituent la base des algorithmes de preuve formelle. Il est également fait rappel des méthodes de représentation qui ont permis d'étendre le champ d'application de la vérification de modèle vers la preuve de circuits industriels.

Dans ce chapitre, la présentation des différents concepts est illustrée à l'aide de l'exemple ci-dessous : le modèle d'un arbitre, mettant en oeuvre un mécanisme de priorités, avec l'intention de servir l'ensemble de ses clients d'une manière équitable.

Exemple : un arbitre à trois entrées. La figure 1.1 présente le graphe de transition d'un arbitre qui gère les requêtes de trois clients différents. Ces clients sont classés par ordre de priorité du premier (le plus prioritaire) au troisième (le moins prioritaire). Cet exemple est inspiré de [62]. A chaque instant, cet arbitre lit et renvoie un symbole composé de trois chiffres binaires. Le symbole d'entrée représente l'état (demandeur ou non) de chacun de ses clients. Ainsi, le symbole "000" est lu si aucun client n'est demandeur d'accès. Si les clients 2 et 3 sont demandeurs en même temps, l'arbitre lira le symbole "011". Selon à la fois la valeur du symbole d'entrée et les décisions prises au cours du passé, cet arbitre donne une réponse d'acceptation : le symbole "000" est renvoyé si aucun client n'a reçu de permission d'accès; si l'autorisation est accordée au client 1, l'arbitre renvoie le symbole "100". Cet arbitre met en œuvre l'exclusion mutuelle d'accès pour ses trois clients : tous les symboles sortants contiennent au maximum un seul chiffre "1". Le concepteur a également souhaité que le traitement des requêtes entrantes se fasse de manière équitable, condition qui n'est remplie que partiellement. Les étiquettes associées aux états de cette machine montrent le symbole sortant précédemment envoyé. Ainsi, l'étiqueté d'état "001" signifie que le client 3 a reçu précédemment la permission d'accès et sera de ce fait moins prioritaire que les clients 2 et 1. A la mise sous tension, l'arbitre se trouve dans l'état "000". Pour chacun des états,

une et une seule transition associée est toujours active. Chaque transition est étiquetée avec le symbole lu en entrée qui provoque son activation, suivi par le symbole de réponse renvoyé vers l'environnement. L'emploi du caractère '-' (signifiant valeur indifférente) permet de manipuler des ensembles de symboles d'entrée et de regrouper plusieurs transitions ayant le même symbole sortant. Par exemple, l'étiquette "- 0 1/0 0 1" représente les transitions "0 0 1/0 0 1" et "1 0 1/0 0 1".

#### 1.2 Le modèle de machine d'états finis

#### 1.2.1 Notions préliminaires

Les notations adoptées sont inspirées de [38]. Les fondements théoriques des machines d'états finis sont présentés dans [42, 56]. Cette section rappelle les définitions nécessaires pour la suite de ce document.

**Définition 1.1 (Machine d'états finis)** Une machine d'états finis déterministe est un n-uplet

$$\mathcal{M} = \langle \mathcal{X}, \mathcal{O}, \mathcal{S}, \sigma_0, \mathcal{F}_t, \mathcal{F}_o \rangle$$

où  $\mathcal{X}$  est un ensemble fini de symboles d'entrée,  $\mathcal{O}$  est un ensemble fini de symboles de sortie,  $\mathcal{S}$  est un ensemble fini d'états, et  $\sigma_0 \in \mathcal{S}$  est appelé l'état initial de  $\mathcal{M}$ .  $\mathcal{F}_t : \mathcal{X} \times \mathcal{S} \to \mathcal{S}$  représente la fonction de transition d'état de  $\mathcal{M}$  et  $\mathcal{F}_o : \mathcal{X} \times \mathcal{S} \to \mathcal{O}$  représente sa fonction de sortie.

Tout le long de ce document, sauf avis contraire, nous nous restreignons aux machines d'états finis  $\mathcal{M}$ :

- déterministes :  $\mathcal{F}_t$  doit être une fonction : elle associe à un couple de valeurs donné  $\langle \xi, \sigma \rangle \in \mathcal{X} \times \mathcal{S}$  une unique valeur de  $\mathcal{S}$ ;

- complètes : à la fois  $\mathcal{F}_t$  et  $\mathcal{F}_o$  sont définies sur la totalité de l'ensemble  $\mathcal{X} \times \mathcal{S}$ .

Si  $\mathcal{F}_t$  est une relation telle que  $\exists \xi \in \mathcal{X}, \exists \sigma, \sigma'_1, \sigma'_2, \sigma'_1 \neq \sigma'_2 : \sigma'_1 = \mathcal{F}_t(\xi, \sigma)$  et  $\sigma'_2 = \mathcal{F}_t(\xi, \sigma)$ , la machine est non-déterministe.

Habituellement, une machine d'états  $\mathcal{M}$  est associée à une échelle discrète de temps. Ainsi, on associe l'instant "0" avec l'état initial  $\sigma_0$  et on dit qu'à l'instant "0",  $\mathcal{M}$  se trouve dans l'état  $\sigma_0$ . A tout instant T,  $\mathcal{M}$  peut se trouver dans un état  $\sigma_T \in \mathcal{S}$ .

**Définition 1.2 (Configuration courante)** A tout instant T, une machine  $\mathcal{M}$  se trouve dans une configuration  $C_T = \langle \xi_T, \sigma_T, o_T \rangle$  telle que  $\xi_T \in \mathcal{X}$ ,  $\sigma_T \in \mathcal{S}$ ,  $o_T \in \mathcal{O}$  et  $\mathcal{F}_o(\xi_T, \sigma_T) = o_T$ .

**Définition 1.3 (Etat successeur)** Soient  $\sigma, \sigma' \in \mathcal{S}$  deux états d'une machine  $\mathcal{M}$ . On dit que  $\sigma'$  est un successeur de  $\sigma$ ,  $\sigma \to \sigma'$  si et seulement si  $\exists \xi \in \mathcal{X} : \sigma' = \mathcal{F}_t(\xi, \sigma)$ .

**Définition 1.4 (Exécution)** Une exécution d'une machine d'états  $\mathcal{M}$  est une séquence finie ou non de configurations  $(C_0, C_1, C_2, ...)$  telle que  $\forall k \in \mathbb{N}$  où  $C_k = \langle \xi_k, \sigma_k, o_k \rangle$ ,  $\sigma_{k+1} = \mathcal{F}_t(\xi_k, \sigma_k)$ .

**Définition 1.5 (Configuration atteignable)** Une configuration  $C = \langle \xi, \sigma, o \rangle$  est atteignable dans une machine  $\mathcal{M}$  s'il existe une exécution  $(C_0, ...C)$  où  $C_0 = \langle \xi_0, \sigma_0, o_0 \rangle$  est une configuration dans laquelle  $\mathcal{M}$  est à son état initial  $\sigma_0$ .

#### Définition 1.6 (Machines d'états compatibles) Soient

$\mathcal{M}_1 = \langle \mathcal{X}_1, \mathcal{O}_1, \mathcal{S}_1, \sigma_{01}, \mathcal{F}_{t1}, \mathcal{F}_{o1} \rangle$  et  $\mathcal{M}_2 = \langle \mathcal{X}_2, \mathcal{O}_2, \mathcal{S}_2, \sigma_{02}, \mathcal{F}_{t2}, \mathcal{F}_{o2} \rangle$  deux machines d'états finis éventuellement non-déterministes. On dit que  $\mathcal{M}_1$  et  $\mathcal{M}_2$  sont compatibles si et seulement si elles ont la même interface :  $\mathcal{X}_1 = \mathcal{X}_2$  et  $\mathcal{O}_1 = \mathcal{O}_2$ .

**Définition 1.7 (Etats équivalents)** Deux états  $\sigma_1 \in \mathcal{M}_1$  et  $\sigma_2 \in \mathcal{M}_2$  sont dits équivalents,  $\sigma_1 \equiv \sigma_2$ , si et seulement si  $\mathcal{M}_1$  et  $\mathcal{M}_2$  sont compatibles et  $\forall \xi \in \mathcal{X}_1, \mathcal{F}_{o1}(\xi, \sigma_1) = \mathcal{F}_{o2}(\xi, \sigma_2)$ .

**Définition 1.8 (Equivalence séquentielle)** Deux machines d'états finis  $\mathcal{M}_1$  et  $\mathcal{M}_2$  sont dites séquentiellement équivalentes  $\mathcal{M}_1 \equiv \mathcal{M}_2$  si et seulement si les conditions suivantes sont satisfaites :

- $\mathcal{M}_1$  et  $\mathcal{M}_2$  sont compatibles;

- leurs états initiaux respectifs sont équivalents :  $\sigma_{01} \equiv \sigma_{02}$ ;

- $\forall \sigma_1 \in \mathcal{S}_1 \ et \ \sigma_2 \in \mathcal{S}_2, \ si \ \sigma_1 \equiv \sigma_2 \ alors \ \forall \xi \in \mathcal{X}_1, \mathcal{F}_{t1}(\xi, \sigma_1) \equiv \mathcal{F}_{t2}(\xi, \sigma_2).$

Comportements non-déterministes. Du point de vue conceptuel, nous ne ferons pas de distinction entre une machine déterministe et une machine non-déterministe. Il est en effet possible de modéliser un comportement non-déterministe à l'aide d'une machine d'états déterministe, grâce à l'emploi d'un ensemble auxiliaire  $\mathcal{ND} \neq \emptyset$  de symboles d'entrée, appelés des pseudo-entrées. Ainsi, une machine d'états finis non-déterministe  $\mathcal{M}_{nd} = \langle \mathcal{X}, \mathcal{O}, \mathcal{S}, \sigma_0, \mathcal{G}_t, \mathcal{F}_o, \rangle$  où  $\mathcal{G}_t$  est une relation de transition, peut être représentée par une machine déterministe  $\mathcal{M}_d = \langle \mathcal{X} \times \mathcal{ND}, \mathcal{O}, \mathcal{S}, \sigma_0, \mathcal{F}_t, \mathcal{F}_o, \rangle$ . La fonction de transition de la machine déterministe  $\mathcal{M}_d$  sera définie par  $\mathcal{F}_t : \mathcal{X} \times \mathcal{ND} \times \mathcal{S} \to \mathcal{S}$ .  $\mathcal{G}_t$  est la projection de  $\mathcal{F}_t$  parallèlement à  $\mathcal{ND}$ .

Ce procédé de modélisation du non-déterminisme introduit une contrainte d'unicité qui s'applique aux ensembles des pseudo-entrées : lorsque deux machines d'états sont comparées, leurs ensembles de pseudo-entrées respectifs doivent être disjoints. Les critères de compatibilité et d'équivalence séquentielle s'étendent facilement au cas non-déterministe.

Une relation typique entre deux machines d'états finis contenant du non-déterminisme est la simulation :

**Définition 1.9 (Relation de simulation entre états)** Soient  $\mathcal{M}_1$  et  $\mathcal{M}_2$  deux machines d'états finis compatibles, éventuellement non-déterministes. L'état  $\sigma_2 \in \mathcal{S}_2$  simule l'état  $\sigma_1 \in \mathcal{S}_1$ ,  $\sigma_2 \leq_s \sigma_1$ , si et seulement si :

```

-\sigma_1 \equiv \sigma_2;

```

<sup>-</sup>  $\forall \sigma'_1 \in \mathcal{S}_1, \forall \langle \xi, nd_1 \rangle \in \mathcal{X}_1^{nd} \text{ tel que } \sigma'_1 = \mathcal{F}_{t1}(\langle \xi, nd_1 \rangle, \sigma_1) :$  $\exists \sigma'_2 \in \mathcal{S}_2, \exists nd_2 \text{ tels que } \langle \xi, nd_2 \rangle \in \mathcal{X}_2^{nd} \text{ et } \sigma'_2 = \mathcal{F}_{t2}(\langle \xi, nd_2 \rangle, \sigma_2) \text{ et } \sigma'_2 \preceq_s \sigma'_1$

$<sup>{}^{2}\</sup>forall \xi \in \mathcal{X}, \forall \sigma \in \mathcal{S}, \sigma' \in \mathcal{G}_{t}(\xi, \sigma) \Leftrightarrow \exists nd \in \mathcal{ND}, \sigma' = \mathcal{F}_{t}(\xi, nd, \sigma)$

Définition 1.10 (Relation de simulation entre machines d'états finis) Soient  $\mathcal{M}_1$  et  $\mathcal{M}_2$  deux machines d'états finis éventuellement non-déterministes. La machine  $\mathcal{M}_2$  simule  $\mathcal{M}_1$ ,  $\mathcal{M}_2 \leq_s \mathcal{M}_1$  si et seulement si  $\sigma_{02} \leq_s \sigma_{01}$

**Remarque.** Lorsque deux machines d'états  $\mathcal{M}_1$  et  $\mathcal{M}_2$  sont déterministes, la relation de simulation  $\mathcal{M}_2 \leq_s \mathcal{M}_1$  est synonyme d'équivalence séquentielle.

#### 1.2.2 Application à l'exemple

Le modèle  $\mathcal{ARB} = (\mathcal{X}, \mathcal{O}, \mathcal{S}, \sigma_0, \mathcal{F}_t, \mathcal{F}_o)$  représente la machine d'états finis de la figure 1.1 :

```

\mathcal{X} = \{000, 001, 010, 011, 100, 101, 110, 111\}

\mathcal{O} = \{000, 010, 100, 001\}

\mathcal{S} = \{000, 001, 010, 100\}, \ \sigma_0 = 000

\mathcal{F}_t = \{((000, 000), 000), ((000, 1 - -), 100), ((000, 01 -), 010), ((000, 001), 001), \\ ((100, 000), 000), ((100, 100), 100), ((100, -1 -), 010), ((100, -01), 001), \\ ((010, 000), 000), ((010, 010), 010), ((010, 0 - 1), 001), ((010, 1 - -), 100), \\ ((001, 000), 000), ((001, 001), 001), ((001, 01 -), 010), ((001, 1 - -), 100)\}

```

Dans le cas particulier de cet arbitre, nous avons  $\mathcal{F}_t = \mathcal{F}_o$ .

#### 1.3 Techniques de représentation

#### 1.3.1 Représentation Booléenne

Dans l'exemple du paragraphe précédent, les états et les transitions sont représentés de manière *explicite*, par simple énumération. En pratique, ceci constitue un inconvénient important. La plupart des systèmes d'aujourd'hui, qu'ils soient décrits manuellement ou générés de manière automatique, ont un ensemble d'états de taille astronomique. Non seulement ces systèmes sont et seront impossibles à représenter de manière explicite, mais il sera également impossible de tirer quelque conclusion que ce soit concernant leur comportement.

La représentation symbolique constitue une approche alternative permettant d'aborder ce problème. Basée sur la logique propositionnelle de premier ordre, l'approche symbolique permet de manipuler non pas des états individuels mais des ensembles d'états. Construire une représentation symbolique d'une machine d'états finis  $\mathcal{M}$  revient à réécrire l'ensemble de ses composants à l'aide de termes de la logique propositionnelle.

Tout terme de la logique propositionnelle est construit à partir d'un ensemble de propositions atomiques  $\mathcal{P}$ . Cet ensemble inclut les valeurs constantes booléennes,  $\mathbb{B} = \{faux, vrai\}$  ainsi qu'un ensemble de variables prenant chacune des valeurs dans l'ensemble  $\mathbb{B}$ . Dans un souci de concision, les éléments de  $\mathbb{B}$  seront associés aux valeurs entières "0" et "1". Un terme a donc une des formes suivantes :

- toute autre proposition atomique  $p \in \mathcal{P}$  est un terme;

- si  $t_1$  et  $t_2$  sont des termes, alors  $t_1.t_2$  et  $t_1+t_2$  sont également des termes. Les opérateurs "." et "+" dénotent respectivement la conjonction et la disjonction ;

- si t est un terme, alors  $\bar{t}$ , la négation de t est aussi un terme;

Les opérateurs "implication" ( $\Rightarrow$ ) et "équivalence" ( $\Leftrightarrow$ ) sont dérivés des opérateurs logiques de base, employés ci-dessus. Ainsi, quels que soient les termes  $t_1$  et  $t_2$ , l'expression  $t_1 \Rightarrow t_2$  est identique à  $\bar{t}_1 + t_2$ . De même, l'expression  $t_1 \Leftrightarrow t_2$  est identique à  $t_1.t_2 + \bar{t}_1.\bar{t}_2$ .

La représentation symbolique d'une machine  $\mathcal{M}$  passe par une étape préliminaire de construction d'un modèle booléen associé. Cette étape constitue un rapprochement du niveau conceptuel bi-valué de réalisation physique des circuits numériques actuels. On construit tout d'abord des correspondants booléens pour les ensembles  $\mathcal{X}$ ,  $\mathcal{O}$  et  $\mathcal{S}$ . Leurs éléments sont associés de manière injective avec des n-uplets formés sur  $\mathbb{B}$ . Pour que cette correspondance puisse être réalisée, la taille minimale de ces n-uplets doit être respectivement :

$$m = \lceil log_2|\mathcal{X}| \rceil$$

$p = \lceil log_2|\mathcal{O}| \rceil$   $n = \lceil log_2|\mathcal{S}| \rceil$

où  $|\mathcal{X}|$ ,  $|\mathcal{O}|$  et  $|\mathcal{S}|$  dénotent les cardinaux des ensembles  $\mathcal{X}$ ,  $\mathcal{O}$  et  $\mathcal{S}$ , et [x] dénote le plus petit nombre entier tel que le nombre réel  $x \leq [x]$ .

Ensuite, on définit les variantes binaires des fonctions  $\mathcal{F}_t$  et  $\mathcal{F}_o$ . Dans la suite, les ensembles  $X = \{x_1, x_2, ..., x_m\}$ ,  $O = \{o_1, o_2, ..., o_p\}$  et  $S = \{s_1, s_2, ..., s_n\}$  contiennent des propositions atomiques. Leurs éléments sont appelés respectivement variables booléennes d'entrée, de sortie et d'état. On note  $\langle x_m \rangle = \langle x_1, x_2, ..., x_m \rangle$  le vecteur de taille m construit à partir des éléments de X. Les vecteurs  $\langle o_p \rangle$  et  $\langle s_n \rangle$  sont construits de façon similaire. Le vecteur  $\langle x_m \rangle \bullet \langle s_n \rangle$  de taille m + n est obtenu par concaténation des éléments des vecteurs  $\langle x_m \rangle$  et  $\langle s_n \rangle$ .

#### Définition 1.11 (Modèle Booléen d'une machine d'états finis) Soit

$\mathcal{M} = \langle \mathcal{X}, \mathcal{O}, \mathcal{S}, \sigma_0, \mathcal{F}_t, \mathcal{F}_o \rangle$  une machine d'états finis.  $M = \langle X, O, S, s_0, F_t, F_o \rangle$  est une représentation booléenne de  $\mathcal{M}$  s'il existe trois fonctions d'encodage injectives  $E_X : \mathcal{X} \to \mathbb{B}^m$ ,  $E_O : \mathcal{O} \to \mathbb{B}^p$ ,  $E_S : \mathcal{S} \to \mathbb{B}^n$  telles que

- $s_0 = E_S(\sigma_0)$

- $F_t: \mathbb{B}^m \times \mathbb{B}^n \to \mathbb{B}^n$  fonction de transition vérifie :  $\forall \xi \in \mathcal{X}, \forall \sigma \in \mathcal{S}, F_t(E_X(\xi), E_S(\sigma)) = E_S(\mathcal{F}_t(\xi, \sigma))$  :

- $F_o: \mathbb{B}^m \times \mathbb{B}^n \to \mathbb{B}^p$  fonction de sortie vérifie  $\forall \xi \in \mathcal{X}, \forall \sigma \in \mathcal{S}, F_o(E_X(\xi), E_S(\sigma)) = E_O(\mathcal{F}_o(\xi, \sigma)).$

Les fonctions d'encodage  $E_X$ ,  $E_O$  et  $E_S$  sont injectives mais pas forcément surjectives, car on a les inégalités  $|\mathcal{X}| \leq |\mathbb{B}^m|$ ,  $|\mathcal{O}| \leq |\mathbb{B}^p|$  et  $|\mathcal{S}| \leq |\mathbb{B}^n|$ .

Soient X, O, S les images par les fonctions d'encodage des ensembles  $\mathcal{X}$ ,  $\mathcal{O}$  et  $\mathcal{S}$ .  $X = E_X(\mathcal{X}) \subseteq \mathbb{B}^m$ ,  $O = E_O(\mathcal{O}) \subseteq \mathbb{B}^p$ ,  $S = E_S(\mathcal{S}) \subseteq \mathbb{B}^n$ .

$X,\ O$  et S ne sont la plupart du temps que des sous-ensembles booléens stricts de  $\mathbb{B}^m,\ \mathbb{B}^n$  et  $\mathbb{B}^p$ . Cependant, il n'est pas réaliste de considérer qu'un circuit à m variables booléennes d'entrée accepte seulement un sous-ensemble de valeurs de  $\mathbb{B}^m$ . Une définition possible de  $F_t$  sur l'intégralité de l'ensemble  $\mathbb{B}^m \times \mathbb{B}^n$  serait :

$$F_t(x,s) = \begin{cases} E_S(\mathcal{F}_t(\xi,\sigma)) & \text{si } \exists \xi, \sigma : x = E_X(\xi) \text{ et } s = E_S(\sigma) \\ s & \text{sinon} \end{cases}$$

Cette définition de  $F_t$  spécifie qu'aucun changement d'état ne se produit si x ou s n'ont pas d'antécédent dans  $\mathcal{X}$  et  $\mathcal{S}$ . En ce qui concerne la fonction  $F_o$ , la solution généralement adoptée dans la pratique consiste à renvoyer une valeur "par défaut" pour toutes les combinaisons x et s non définies.

Moyennant l'emploi d'un langage de description adéquat, la redéfinition des fonctions de transition et de sortie s'effectue d'une manière naturelle : le concepteur laisse les transitions n'ayant pas de correspondant dans  $\mathcal{M}$  non-spécifiées ; de façon similaire, une fonction de sortie renvoie une valeur par défaut choisie par le concepteur, sauf si ses arguments ont des antécédents dans  $\mathcal{X}$  et  $\mathcal{S}$ .

Dans la suite, on emploiera exclusivement des fonctions de transition, et de sortie définies sur l'intégralité de  $\mathbb{B}^m \times \mathbb{B}^n$ .

#### 1.3.2 Représentation symbolique

Dans la représentation symbolique de M, aussi bien les états individuels que les ensembles d'états sont exprimés grâce à leur fonction caractéristique.

**Définition 1.12 (Représentation symbolique d'un état)** Soit  $\sigma \in \mathcal{S}$  un état de la machine  $\mathcal{M}$ . Le codage de  $\sigma$  dans M,  $E_S(\sigma) \in \mathbb{B}^n$  est un vecteur de n valeurs booléennes. La représentation symbolique de  $\sigma$  est donnée par la fonction caractéristique  $\chi_{\sigma}$ :

$$\chi_{\sigma}(\langle s_1, s_2, ..., s_n \rangle) = \prod_{i=1}^{n} (s_i \Leftrightarrow E_S^i(\sigma))$$

où  $E_S^i$  est la i-ème composante du vecteur  $E_S$  de taille n.

En manipulant les encodages de  $\sigma$  et  $\sigma'$  donnés par la fonction  $E_S$ , grâce aux vecteurs de variables d'état courant  $\langle s_n \rangle$  et prochain état  $\langle s'_n \rangle$ ,  $\sigma'$  est un successeur de  $\sigma$  s'écrit :

$$\langle s_n' \rangle = F_t(\langle x_m \rangle, \langle s_n \rangle) \tag{1}$$

soit en termes de la logique propositionnelle :

$$T(\langle x_m \rangle, \langle s_n \rangle, \langle s_n' \rangle) = \prod_{i=1}^n s_i' \Leftrightarrow F_t^i(\langle x_m \rangle, \langle s_n \rangle)$$

(2)

Le terme T défini par (2) est appelé une relation de transition. C'est une fonction caractéristique qui représente toutes les combinaisons légales dans M de valeurs sur les vecteurs d'entrée, état courant et prochain état.

**Définition 1.13 (Modèle symbolique d'une machine d'états)** Le modèle symbolique d'une machine d'états  $\mathcal{M}$  est un n-uplet  $M = \langle X, O, S, T, F_o, \chi_0 \rangle$  contenant les ensembles de variables d'entrée, de sortie et d'état X, O et S, une relation de transition  $T : \mathbb{B}^m \times \mathbb{B}^n \times \mathbb{B}^n \to \mathbb{B}$ , une fonction de sortie  $F_o : \mathbb{B}^m \times \mathbb{B}^n \to \mathbb{B}^p$  et une fonction caractéristique  $\chi_0$  qui représente l'état initial de M.

**Définition 1.14 (Machines d'états symboliques composables)** Soient  $M_A = \langle X_A, S_A, O_A, T_A, \chi_{0A} \rangle$  et  $M_B = \langle X_B, S_B, O_B, T_B, \chi_{0B} \rangle$  deux modèles symboliques. On dit que ces modèles sont composables si et seulement si  $O_A \cap O_B = \emptyset$ .

Définition 1.15 (Produit synchronisé de deux machines d'états symboliques) Soient  $M_A = \langle X_A, S_A, O_A, T_A, \chi_{0A} \rangle$  et  $M_B = \langle X_B, S_B, O_B, T_B, \chi_{0B} \rangle$  deux modèles symboliques composables. Le produit synchronisé de  $M_A$  avec  $M_B{}^3$ , noté  $M_A || M_B$  est la machine symbolique  $M_{prod} = \langle X_{prod}, S_{prod}, O_{prod}, T_{prod}, \chi_{0prod} \rangle$  où  $X_{prod} \subseteq X_A \cup X_B$ ,  $S_{prod} = S_A \cup S_B$ ,  $O_{prod} \subseteq O_A \cup O_B$ ,  $T_{prod} = T_A$ .  $T_B$  et  $\chi_{0prod} = \chi_{0A}$ .  $\chi_{0B}$ .

Le modèle de machine d'états décrit à l'aide d'une relation de transition est connu sous le nom de modèle de Kripke. La relation de transition est construite de manière à regrouper tous les couples d'états adjacents. Cette caractéristique lui permet de représenter des systèmes non-déterministes, ce qui confère plus de généralité au modèle de Kripke. Dans l'équation (2), la relation de transition T est calculée à partir d'une fonction booléenne de transition. Elle correspond donc à un système déterministe. Cependant, le fait de se restreindre à l'étude des systèmes déterministes n'entraîne pas de perte de généralité. En effet, tout modèle non-déterministe peut être transformé en un modèle déterministe équivalent.

**Propriétés de la représentation symbolique.** L'emploi des fonctions caractéristiques permet de manipuler des ensembles arbitraires d'états d'une machine, quelle qu'en soit la cardinalité. Ainsi, toutes les opérations de manipulation des ensembles possèdent un correspondant booléen dans le domaine symbolique. La représentation symbolique d'un ensemble  $\mathcal{E}$  d'états appartenant à une machine  $\mathcal{M}$  satisfait les propriétés suivantes :

- $-\chi_{\mathcal{E}}(\langle s_1, s_2, ..., s_n \rangle) = 0 \text{ lorsque } \mathcal{E} = \emptyset;$

- l'union des ensembles  $\mathcal{E}_1$  et  $\mathcal{E}_2$  s'exprime par l'opération "ou" logique.  $\chi_{\mathcal{E}_1 \cup \mathcal{E}_2}(\langle s_1, s_2, ..., s_n \rangle) = \chi_{\mathcal{E}_1}(\langle s_1, s_2, ..., s_n \rangle) + \chi_{\mathcal{E}_2}(\langle s_1, s_2, ..., s_n \rangle);$

- l'intersection des ensembles  $\mathcal{E}_1$  et  $\mathcal{E}_2$  s'exprime par l'opération "et" logique.  $\chi_{\mathcal{E}_1 \cap \mathcal{E}_2}(\langle s_1, s_2, ..., s_n \rangle) = \chi_{\mathcal{E}_1}(\langle s_1, s_2, ..., s_n \rangle) \cdot \chi_{\mathcal{E}_2}(\langle s_1, s_2, ..., s_n \rangle)$ ;

- le complément de l'ensemble  $\mathcal{E}$  par rapport à  $\mathcal{S}$  s'exprime par l'opération "non" logique :  $\chi_{\mathcal{S}\setminus\mathcal{E}} = \chi_{\mathcal{S}}.\overline{\chi_{\mathcal{E}}}$ . Dans le cas particulier où  $|\mathcal{S}| = 2^n$ , la fonction d'encodage  $E_{\mathcal{S}}$  devient une bijection. Tout élément de  $\mathbb{B}^n$  possède un antécédent dans  $\mathcal{S}$ . On a donc  $\chi_{\mathcal{S}} = \chi_{\mathbb{B}^n} = 1$  et le complément de l'ensemble  $\mathcal{E}$  devient  $\chi_{\mathcal{S}\setminus\mathcal{E}} = \bar{\chi_{\mathcal{E}}}$ .

On manipule délibérément l'état  $\sigma$  et l'ensemble contenant un unique élément  $\{\sigma\}$  comme s'il s'agissait du même objet, en termes de représentation par fonction caractéristique.

Il existe une correspondance étroite entre le modèle symbolique d'une machine d'états finis et un circuit numérique séquentiel. Les variables d'entrée et de sortie du modèle correspondent aux ports entrants et sortants du circuit. Un modèle booléen met en œuvre des fonctions pour calculer les nouvelles valeurs des variables de sortie et d'état. Ces fonctions sont reproduites dans un circuit à l'aide de réseaux de portes logiques, réalisant chacune une fonction logique élémentaire. Quant aux variables d'état, elles ont pour correspondant électronique les mémoires (bascules).

<sup>&</sup>lt;sup>3</sup> aussi appelé composition parallèle de M<sub>A</sub> et M<sub>B</sub>

Le temps étant considéré discret, toute transition (changement de valeur d'au moins une variable d'état) est déclenchée par les événements successifs produits par une horloge. Physiquement, un port entrant spécial intitulé horloge est connecté à toutes les bascules du circuit. Les événements produits sur le signal d'horloge déterminent le changement de valeur de toutes les mémoires.

Le modèle booléen d'une machine d'états constitue le point d'entrée dans les outils de vérification formelle. Cependant, pour des raisons pratiques liées à la manipulation de circuits réels, structurés ou non, il est utile d'étendre la définition d'un modèle booléen de façon à inclure les notions de variable locale et de hiérarchie. Le modèle hiérarchique de MEALY effectue cette extension.

#### 1.3.3 Modèle hiérarchique de Mealy

**Définition 1.16 (Modèle de Mealy hiérarchique)** Une machine hiérarchique de Mealy est un n-uplet  $MH = \langle X, O, S, L, \chi_0, F_t, F_o, F_L, COMP \rangle$ , où X, O, S sont respectivement des ensembles de variables d'entrée, de sortie, d'état. L'ensemble L, de taille k, contient les variables locales de la machine hiérarchique MH.  $\chi_0(s_1,...s_n)$  est la fonction caractéristique qui représente l'état initial de MH. La fonction  $F_t: \mathbb{B}^m \times \mathbb{B}^n \times \mathbb{B}^k \to \mathbb{B}^n$  est la fonction de transition de MH:

$$\langle s_1, s_2, ..., s_n \rangle = F_t(x_1, ..., x_m, s_1, ..., s_n, l_1, ... l_k).$$

(3)

La fonction  $F_o: \mathbb{B}^m \times \mathbb{B}^n \times \mathbb{B}^k \to \mathbb{B}^p$  est la fonction de sortie de MH:

$$\langle o_1, o_2, ..., o_p \rangle = F_o(x_1, ..., x_m, s_1, ..., s_n, l_1, ... l_k).$$

(4)

La fonction  $F_L: \mathbb{B}^m \times \mathbb{B}^n \times \mathbb{B}^k \to \mathbb{B}^k$  est la fonction qui calcule les valeurs des variables locales de MH:

$$\langle l_1, l_2, ... l_k \rangle = F_L(x_1, ..., x_m, s_1, ..., s_n, l_1, ... l_k).$$

(5)

$COMP = \{mh_1, mh_2, ..., mh_q\}$  est un ensemble de taille q dont les éléments sont des machines MH.

Les machines  $mh_i$  sont appelées des composants de MH. Les variables d'entrée de chaque composant  $mh_i$  correspondent obligatoirement à un sous-ensemble de  $X \cup L$ . De même, les variables de sortie des  $mh_i$  correspondent à un sous-ensemble de  $L \cup O$ . Par ailleurs, si  $O_i, O_j \subset L \cup O$  sont les ensembles de sorties de deux composants  $mh_i$  et  $mh_j$ , alors  $O_i \cap O_j = \emptyset$ .

Toute machine hiérarchique peut être transformée en un modèle booléen en appliquant les étapes suivantes :

- 1. pour chaque  $mh_i$  dont l'ensemble COMP est vide, remplacer dans les fonctions  $F_t$  et  $F_o$ , les variables locales  $l_i$  par leur fonction  $F_L^i$  correspondante;

- 2. dans MH, remplacer tous les composants mh dont l'ensemble COMP est vide par leur contenu. Puis, retour à l'étape 1.

Remarque. La définition du modèle hiérarchique de Mealy permet, grâce aux variables locales  $l_1, ..., l_k$ , de combiner certains composants  $mh_i$  et  $mh_j$  de façon à créer des dépendances fonctionnelles circulaires - boucles combinatoires - entre les variables de ces composants. Ce scénario n'est pas admissible dans le contexte de la modélisation des circuits numériques. Comme l'ajout de hiérarchie au sein d'une machine MH se fait manuellement, la vérification d'absence de boucles combinatoires doit être systématique.

#### 1.3.4 Représentation symbolique de l'exemple

La représentation symbolique de la machine  $\mathcal{ARB}$  passe par l'étape de construction d'un modèle booléen ARB. On calcule tout d'abord les cardinaux des ensembles de variables X, O et S:

$$m = |X| = \lceil \log_2 |\mathcal{X}| \rceil = 3$$

$$p = |O| = \lceil \log_2 |\mathcal{O}| \rceil = 2$$

$$n = |S| = \lceil \log_2 |\mathcal{S}| \rceil = 2$$

permettant de construire un codage booléen de  $\mathcal{ARB}$  de taille minimale. Ainsi,  $X = \{x_1, x_2, x_3\}$ ,  $S = \{s_1, s_2\}$  et  $O = \{o_1, o_2\}$ . Un choix possible des fonctions d'encodage  $E_X$ ,  $E_S$  et  $E_O$  serait le suivant :

$$E_{X} = \{(000, \langle 000 \rangle), (001, \langle 001 \rangle), (010, \langle 010 \rangle), (011, \langle 011 \rangle), (100, \langle 100 \rangle), (101, \langle 101 \rangle), (110, \langle 110 \rangle), (111, \langle 111 \rangle)\}$$

$$E_{S} = \{(000, \langle 00 \rangle), (001, \langle 01 \rangle), (010, \langle 10 \rangle), (100, \langle 11 \rangle)\}$$

$$E_{O} = E_{S}$$

où  $\langle 00 \rangle$  représente le codage booléen de l'état initial  $\sigma_0 = 000$  de  $M_{arb}$ . Les fonctions  $F_t$  et  $F_o$  se déduisent à partir de  $\mathcal{F}_t$  et  $\mathcal{F}_o$  et  $E_S$ :

```

\begin{split} F_t &= \{ ((\langle 00 \rangle, \langle 000 \rangle), \langle 00 \rangle), ((\langle 00 \rangle, \langle 1--\rangle), \langle 11 \rangle), ((\langle 00 \rangle, \langle 01-\rangle), \langle 10 \rangle), \\ &\quad ((\langle 00 \rangle, \langle 001 \rangle), \langle 01 \rangle), ((\langle 11 \rangle, \langle 000 \rangle), \langle 00 \rangle), ((\langle 11 \rangle, \langle 100 \rangle), \langle 11 \rangle), \\ &\quad ((\langle 11 \rangle, \langle -1-\rangle), \langle 10 \rangle), ((\langle 11 \rangle, \langle -01 \rangle), \langle 01 \rangle), ((\langle 10 \rangle, \langle 000 \rangle), \langle 00 \rangle), \\ &\quad ((\langle 10 \rangle, \langle 010 \rangle), \langle 10 \rangle), ((\langle 10 \rangle, \langle 0-1 \rangle), \langle 01 \rangle), ((\langle 10 \rangle, \langle 1--\rangle), \langle 11 \rangle), \\ &\quad ((\langle 01 \rangle, \langle 000 \rangle), \langle 00 \rangle), ((\langle 01 \rangle, \langle 001 \rangle), \langle 01 \rangle), ((\langle 01 \rangle, \langle 01-\rangle), \langle 10 \rangle), \\ &\quad ((\langle 01 \rangle, \langle 1--\rangle), \langle 11 \rangle) \} \end{split}

```

La fonction  $F_t$  est en fait un vecteur de deux fonctions  $\langle F_t^1, F_t^2 \rangle$ . Leur expression booléenne se déduit directement de la description relationnelle de  $F_t$ :

$$\begin{split} F_t^1(s_1,s_2,x_1,x_2,x_3) &= \bar{s}_1.\bar{s}_2.x_1 + \bar{s}_1.\bar{s}_2.\bar{x}_1.x_2 + s_1.s_2.x_1.\bar{x}_2.\bar{x}_3 + s_1.s_2.x_2 + \\ &s_1.\bar{s}_2.\bar{x}_1.x_2.\bar{x}_3 + s_1.\bar{s}_2.x_1 + \bar{s}_1.s_2.\bar{x}_1.x_2 + \bar{s}_1.s_2.x_1 \\ F_t^2(s_1,s_2,x_1,x_2,x_3) &= \bar{s}_1.\bar{s}_2.x_1 + \bar{s}_1.\bar{s}_2.\bar{x}_1.\bar{x}_2.\bar{x}_3 + s_1.s_2.x_1.\bar{x}_2.\bar{x}_3 + s_1.s_2.\bar{x}_2.x_3 + \\ &s_1.\bar{s}_2.\bar{x}_1.x_3 + s_1.\bar{s}_2.x_1 + \bar{s}_1.s_2.\bar{x}_1.\bar{x}_2.\bar{x}_3 + \bar{s}_1.s_2.x_1 \end{split}$$

Les termes symboliques représentant les états de ARB sont déterminés par les fonctions caractéristiques :

$\chi_{\langle 00\rangle}(s_1,s_2)=\bar{s}_1.\bar{s}_2$   $\chi_{\langle 01\rangle}(s_1,s_2)=\bar{s}_1.s_2$   $\chi_{\langle 10\rangle}(s_1,s_2)=s_1.\bar{s}_2$   $\chi_{\langle 11\rangle}(s_1,s_2)=s_1.s_2$  conformément à la définition 1.12. Le prédicat représentant l'état initial de ARB est  $\chi_0(s_1,s_2)=\bar{s}_1.\bar{s}_2$ .

Soit  $S' = \{s'_1, s'_2\}$  l'ensemble de variables permettant de désigner les états successeurs dans ARB. Par application de l'équation 2, la représentation propositionnelle de la relation de transition T de ARB:

$$T = (s_1' \Leftrightarrow F_t^1(s_1, s_2, x_1, x_2, x_3)).(s_2' \Leftrightarrow F_t^2(s_1, s_2, x_1, x_2, x_3))$$

La fonction de sortie de  $ARB$  est  $F_o = F_t$ .

**Remarque.** En réalité, le codage minimal choisi pour les valeurs de sortie de ARB peut se révéler incommode pour le processus de conception. Le système de l'exemple met en œuvre une fonctionnalité d'arbitrage pour trois clients distincts. Chaque client communique à l'arbitre sa requête, par l'intermédiaire d'une variable d'entrée  $x_i \in X$ . A chaque instant t, l'arbitre analyse l'ensemble des trois requêtes et décide de donner l'accès à un seul parmi ses clients. Cette réponse est donnée à travers les variables de sortie  $o_1$  et  $o_2$ .:

- $-\langle o_1, o_2 \rangle = \langle 0, 0 \rangle$ : aucun client n'a d'autorisation d'accès;

- $-\langle o_1, o_2 \rangle = \langle 0, 1 \rangle, \langle o_1, o_2 \rangle = \langle 1, 0 \rangle$  ou  $\langle o_1, o_2 \rangle = \langle 1, 1 \rangle$ : autorisation d'accès à l'instant t accordée pour le client 3 ou 2 ou 1.

Ainsi, chaque client doit lire et décoder les valeurs  $o_1$  et  $o_2$  pour déterminer si une autorisation lui a été accordée. Cependant, une solution plus pratique et élégante aurait consisté à gérer séparément les autorisations d'accès, en utilisant une variable d'état et de sortie par client. La machine ARB' pour cette solution alternative aurait un ensemble de variables d'état  $S = \{s_1, s_2, s_3\}$  et de sortie  $O = \{o_1, o_2, o_3\}$  telles qu'à tout instant, une et une seule variable d'état et de sortie aurait la valeur 1. Dans ce cas, on construit trois fonctions de transition à partir de la description de ARB: les symboles des alphabets d'état S et de sortie O peuvent être reconstitués par concaténation des valeurs possibles de  $s_1, s_2, s_3$  et  $o_1, o_2, o_3$  Compte-tenu du fait que seules quatre combinaisons sur  $s_1, s_2$  et  $s_3$  sont acceptables, conformément à l'ensemble S, les fonctions de transition  $F_t^1, F_t^2$  et  $F_t^3$  peuvent être simplifiées :

$$F_t^1(s_1, s_2, s_3, x_1, x_2, x_3) = x_1.(\bar{s}_1 + s_1.\bar{x}_2.\bar{x}_3)$$

$$F_t^2(s_1, s_2, s_3, x_1, x_2, x_3) = x_2.(\bar{s}_2.(\bar{x}_1 + s_1) + s_2.\bar{x}_1.\bar{x}_3)$$

$$F_t^3(s_1, s_2, s_3, x_1, x_2, x_3) = x_3.(\bar{s}_3.(\bar{x}_2 + s_2).(\bar{x}_1 + s_1) + s_3.\bar{x}_1.\bar{x}_2)$$

Les termes symboliques représentant les états de ARB' sont déterminés par les fonctions caractéristiques :

$$\chi_{\langle 000\rangle}(s_1, s_2, s_3) = \bar{s}_1.\bar{s}_2.\bar{s}_3 \qquad \chi_{\langle 100\rangle}(s_1, s_2, s_3) = \bar{s}_1.\bar{s}_2.\bar{s}_3 \chi_{\langle 010\rangle}(s_1, s_2, s_3) = \bar{s}_1.s_2.\bar{s}_3 \qquad \chi_{\langle 001\rangle}(s_1, s_2, s_3) = \bar{s}_1.\bar{s}_2.s_3$$

Le prédicat représentant l'état initial de ARB est  $\chi_0(s_1, s_2, s_3) = \bar{s}_1.\bar{s}_2.\bar{s}_3$  et les fonctions de sortie de ARB' sont identiques aux fonctions de transition.

#### 1.4 Parcours symbolique d'une machine d'états finis

Le modèle symbolique d'une machine d'états sert de point de départ pour la preuve de propriétés dans les outils actuels de vérification de modèles. La preuve que le modèle M satisfait la propriété P s'appuie sur quelques opérations de base, exprimées sur des termes de la logique propositionnelle. Typiquement, on calcule l'ensemble d'états de M (exprimé par une fonction caractéristique) dans lesquels P est vraie. Ce calcul se fait de manière

incrémentale avec une granularité égale à une transition dans M. Les opérations de base sont le calcul de *l'image* et la  $pr\acute{e}$ -image d'un ensemble d'états.

La mise en œuvre des opérations d'image et de pré-image utilise les fonctions caractéristiques de la relation de transition du modèle symbolique et de l'ensemble d'états de départ. Leur efficacité repose donc sur la facilité de représentation, de manipulation et d'évaluation de ces fonctions. D'autre part, il s'avère que la construction de la relation de transition T à partir d'un circuit industriel est une opération bien trop coûteuse. En pratique, il semble plus réaliste de partitionner T en plusieurs sous-produits, ou bien d'en garder une représentation implicite, sous forme d'un ensemble de relations atomiques  $s'_i \Leftrightarrow F^i_t(\langle x_m \rangle, \langle s_n \rangle), \forall i = 1..n$ . Il s'agit des approches relationnelle ou fonctionnelle pour le calcul d'image.

Cette section passe en revue les définitions de l'image et de la pré-image, ainsi que les aspects liés à la représentation et l'évaluation des ensembles d'états durant ce calcul. Suivra une présentation de l'état de l'art des approches relationnelle et fonctionnelle du calcul d'image.

#### 1.4.1 Image et pré-image d'un ensemble d'états

**Définition 1.17 (Image d'une fonction booléenne)** Soit  $f_m: \mathbb{B}^n \to \mathbb{B}^m$  une fonction vectorielle à m composantes, dépendant chacune de n variables booléennes,  $\langle y_m \rangle = f_m(\langle x_n \rangle)$ , où  $\langle y_m \rangle$  et  $\langle x_n \rangle$  sont des vecteurs de variables de taille m et n. L'image  $\mathrm{Im}_{G_{f_m}}$  de  $f_m$  est le sous-ensemble de tous les vecteurs booléens de taille m que  $f_m$  peut produire. La fonction caractéristique de ce sous-ensemble est donnée par :

$$\chi_{\text{IMG}_{f_m}}(y_1, y_2, ..., y_m) = \exists x_1, x_2, ..., x_n : \prod_{i=1}^m (y_i \Leftrightarrow f_m^i(\langle x_n \rangle))$$

Dans le cadre du parcours symbolique d'une machine d'états M, la notion d'image s'applique au calcul des successeurs d'un ensemble d'états. On parle alors d'image d'un ensemble d'états E à travers la relation de transition T de M:

**Définition 1.18 (Image et pré-image d'un ensemble d'états)** Soit M le modèle symbolique d'une machine d'états finis. Soit E un sous-ensemble de  $\mathbb{B}^n$ , représenté par sa fonction caractéristique  $\chi_E$ . L'image  $\mathrm{IMG}(\chi_E,T)$  de E à travers la relation de transition T de M est un sous-ensemble de  $\mathbb{B}^n$  dont la fonction caractéristique est :

$$\chi_{\mathrm{IMG}(\chi_E,T)}(\langle s_n' \rangle) = \exists \langle x_m \rangle \in \mathbb{B}^m, \exists \langle s_n \rangle \in \mathbb{B}^n : T(\langle x_m \rangle, \langle s_n \rangle, \langle s_n' \rangle).\chi_E(\langle s_n \rangle)$$

(6)

La pré-image est l'opération duale de l'image qui permet de calculer l'ensemble  $PREImG(\chi_E, T)$  des états prédécesseurs de E:

$$\chi_{\text{PreImG}(\chi_E,T)}(\langle s_n \rangle) = \exists \langle x_m \rangle \in \mathbb{B}^m, \exists \langle s_n' \rangle \in \mathbb{B}^n : T(\langle x_m \rangle, \langle s_n \rangle, \langle s_n' \rangle).\chi_E(\langle s_n' \rangle)$$

(7)

Par application successive de calculs d'image on parcourt progressivement l'ensemble des états atteignables de M. Ce calcul démarre à partir de son état initial. Soit  $S_0 = \{\langle s_0 \rangle\} \subset$

$\mathbb{B}^n$  l'ensemble contenant l'état initial de M. A chaque pas i on calcule  $\chi_{S_i}$ , la fonction caractéristique de l'ensemble d'états  $S_i$  accessibles à partir de  $s_0$  en au plus i transitions :

$$\chi_{S_{i+1}} = \chi_{S_i} + \chi_{\mathrm{IMG}(\chi_{S_i}, T)} \tag{8}$$

La suite  $S_0, S_1, ..., S_i$ , ... est croissante. Comme M contient un nombre fini d'états,  $(S_i \subset \mathbb{B}^n$  quelle soit la valeur de i) cette suite converge. En d'autres termes, il existe une valeur k à partir de laquelle les états successeurs de  $S_k$  sont tous inclus dans  $S_k$ : IMG $(S_k, T) \subseteq S_k$ . Donc, l'équation (8) admet un point fixe. Cette solution est la fonction caractéristique  $\chi_{S_k}$  représentant tous les états de M pouvant être atteints à partir de  $\langle s_0 \rangle$ .

**Définition 1.19 (Invariant)** Si les états atteignables  $S_k$  de M satisfont la propriété P, alors  $\chi_{S_k} \Rightarrow P$ . On dit que P est un invariant dans M.

#### 1.4.2 Ensembles d'états : représentation et évaluation

Les opérations d'image et de pré-image sont la clef de voûte de la technique de vérification symbolique de modèles. L'efficacité de leur mise en oeuvre constitue encore aujourd'hui l'objet de nombreux travaux de recherche. L'image en tant que représentation propositionnelle d'un ensemble d'états peut être manipulée comme une fonction booléenne. En réalité, lorsque le modèle parcouru est extrait d'un circuit industriel, cette fonction dépend d'un nombre très grand de variables et son expression est souvent extrêmement complexe. Par ailleurs, la grande majorité des problèmes de vérification de modèles nécessitent un calcul itératif de point fixe, enchaînant plusieurs calculs d'image. La condition d'arrêt d'un algorithme de point fixe s'exprime sur des ensembles d'états : si  $S_i = S_{i+1}$  alors un point fixe a été atteint et le calcul peut s'arrêter. Etant donné que  $S_i \subseteq S_{i+1}$ , cette même condition peut se transcrire sous la forme  $S_{i+1} \setminus S_i = \emptyset$ , où en termes de fonctions caractéristiques :

$$\chi_{S_{i+1}}.\bar{\chi}_{S_i} = 0 \tag{9}$$

Dans ce contexte, deux problèmes très importants se posent lors du parcours symbolique d'un modèle :

- construire une représentation booléenne compacte des fonctions caractéristiques  $\chi_{S_i}$ ;

- trouver, si possible, au moins une combinaison de valeurs montrant que l'équation (9) n'est pas une tautologie. Dans le cas contraire, un point fixe a été atteint. Ce problème est connu sous le nom de SAT. Dans la théorie de la complexité des algorithmes il sert de base pour la définition de la classe des problèmes NP-complets.

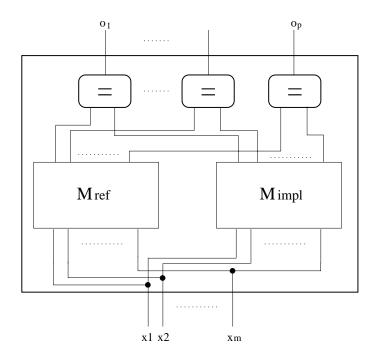

Dans le cadre du calcul symbolique d'image, deux principales directions ont été explorées pour la représentation et l'évaluation des fonctions booléennes.