# Architectures de cellules de commutation monolithiques intégrables sur semi-conducteurs "bi-puce" et "mono-puce" pour convertisseurs de puissance compacts

#### Abdelilah El Khadiry

#### ▶ To cite this version:

Abdelilah El Khadiry. Architectures de cellules de commutation monolithiques intégrables sur semi-conducteurs "bi-puce" et "mono-puce" pour convertisseurs de puissance compacts. Micro et nanotechnologies/Microélectronique. Université Paul Sabatier - Toulouse III, 2014. Français. NNT: . tel-01020587

### HAL Id: tel-01020587 https://theses.hal.science/tel-01020587

Submitted on 8 Jul 2014

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# **THÈSE**

#### En vue de l'obtention du

# DOCTORAT DE L'UNIVERSITÉ DE TOULOUSE

#### Délivré par :

Université Toulouse 3 Paul Sabatier (UT3 Paul Sabatier)

#### Présentée et soutenue par : Abdelilah EL KHADIRY

Le vendredi 7 février 2014

#### Titre:

Architectures de cellules de commutation monolithiques intégrables sur semi-conducteurs "bi-puce" et "mono-puce" pour convertisseurs de puissance compacts

ED GEET : Composants et Systèmes de gestion de l'Énergie

#### Unité de recherche:

LAAS-CNRS & LAPLACE

#### Directeur(s) de Thèse:

M. Frédéric RICHARDEAU, Directeur de recherche LAPLACE / Toulouse M. Abdelhakim BOURENNANE, Maître de conférences LAAS-CNRS / Toulouse

#### Rapporteurs:

M. Stéphane LEFEBVRE, Professeur CNAM / ENS - Cachan M. Dominique PLANSON, Professeur AMPERE / Lyon

#### Autre(s) membre(s) du jury:

M. Bruno ALLARD, Professeur INSA / Lyon

M. Stéphane AZZOPARDI, Maître de conférences (HDR) IMS / Bordeaux

M. Patrick AUSTIN, Professeur UPS / Toulouse

M. Thierry BOUCHET, Ingénieur ADIS - INNOVATION / Meyreuil (invité)

« La connaissance s'acquiert par l'expérience, tout le reste n'est que de l'information »

[Albert Einstein]

à mes parents, à ma femme, à mon frère et sœurs, et à tous ceux que je ne nomme pas, mais qui se reconnaîtront

#### Remerciements

Les travaux de recherches de ce mémoire de thèse ont été réalisés au sein du groupe Intégration des Systèmes de Conversion d'Energie (ISGE) du Laboratoire d'Analyse et d'architecture des Systèmes (LAAS) en collaboration avec le groupe Convertisseurs Statiques (CS) du Laboratoire Plasma et Conversion d'Energie (Laplace).

A ce titre, je souhaite remercier Messieurs Raja CHATILA, Jean Louis SANCHEZ (à qui je rends hommage) et Jean ARLAT directeurs successifs pour m'avoir accueilli au sein du LAAS ainsi que Monsieur Christian LAURENT directeur du Laplace. Je tiens à remercier également Madame Marise BAFLEUR et Monsieur Frédéric MORANCHO, responsables successifs du groupe ISGE, de m'avoir ouvert les portes de leur équipe et permis d'entreprendre ce travail. Je tiens à remercier également Monsieur Alain CAZARRE directeur de l'école doctorale Génie Electrique, Electronique et Télécommunications (GEET).

J'adresse mes plus sincères remerciements à mes directeurs de thèse, Messieurs Frédéric RICHARDEAU et Abdelhakim BOURENNANE. Merci pour leur confiance et pour m'avoir donné l'opportunité de réaliser cette belle expérience et travailler sur un sujet si passionnant. J'ai été impressionné par leurs compétences scientifiques et j'ai beaucoup apprécié leurs qualités humaines. C'était vraiment un réel plaisir de travailler avec vous.

Je tiens à remercier également Madame Marie BREIL-DUPUY pour son soutien et ses encouragements ainsi que pour les nombreux échanges scientifiques dans le cadre de ces travaux.

Je remercie les membres du jury : Monsieur Bruno ALLARD, qui m'a fait l'honneur de le présider, Messieurs Stéphane LEFEBVRE et Dominique PLANSON, qui ont accepté, en qualité de rapporteur, d'examiner ce travail. Je remercie également Messieurs Patrick AUSTIN, Stéphane AZZOPARDI, Thierry BOUCHET qui ont accepté d'examiner mes travaux.

Ces travaux n'auraient pas pu être réalisés sans l'aide des membres de l'équipe TEAM. Je les remercie tous pour le travail qu'ils réalisent, en particulier Eric IMBERNON (partie process technologique), Samuel CHARLOT et David COLIN (partie assemblage). Pour les mêmes raisons, je souhaite remercier les membres de l'équipe I2C, notamment Nicolas MAURAN (partie caractérisations électriques).

Merci à tout le LAAS et le Laplace et en particulier à toute l'équipe ISGE du LAAS et à toute l'équipe CS du Laplace. Merci aux membres permanents que j'ai côtoyés avec plaisir durant ces années de thèse.

Mes remerciements vont également à l'ensemble des personnes travaillant dans les différents services du laboratoire, je pense à Claude LAFFORE, Camille CAZENEUVE, Claire BARDET, Ascension DE SOUSA BERDAT et Christian BERTY.

Un grand merci à Gaëtan TOULON, tu as toujours été présent pour répondre à mes questions portant le plus souvent sur des problèmes de simulations 2D sous Sentaurus, ainsi que pour les échanges scientifiques que nous avons pu avoir. Merci également à Moustapha Zerarka qui m'a initié à la simulation 2D pendant la période de mon stage. Merci aussi à

Zhifeng Dou pour son aide dans la partie simulations 3D sous COMSOL ainsi que Sébastien VINNAC pour sa contribution dans la partie packaging.

A titre plus personnel, je remercie toutes les personnes que j'ai eu le plaisir de côtoyer durant ces trois année de thèse, en particulier mes amis Youssef EL BASRI, Said HOUMADI (ti-foi-ce-ke-je-feu-dirrr) et sa femme Amelia, Ayoub RIFAI, Amel ALI SLIMANE, Carlos CARREJO, Audrey CHAPELLE, Nicolas DUFOUR, Gautier PETIT, Brieux DURAND, Ahmet LALE, Adem LALE, Sylvain NOBLECOURT, Emmanuel MARCAULT, Adrien RAMOND, HONG Liu, Romain MONTHEARD, Youness LAROUSSI, Sabeha Fettouma ZEDEK,, Fares CHOUCHANE, Franc CHBILA, Hajer MAKHLOUFI, Walid BOURENNANE, Imad BOURENNANE, Olga BUSHUEVA, Michael BRESSAN, Paul DURAND ESTEBE, Veljko TOMASEVIC, Valentina CASTAGNOLA, Youssouf GUERFI, Sami ABADA, Thi Ty Mai DINH, Nizar Khalifa SALLEM, Anais MARTIN... je m'excuse auprès de ceux que je n'ai pas cités.

Une pensée à mes amis au Maroc Yassir, Ahmed et Noureddine à Paris.

Enfin je voudrais remercier infiniment les membres de ma petite famille qui m'ont beaucoup soutenu et cru en moi et grâce à eux je suis arrivé là : mon père Abdesselam, ma mère Radia, ma femme Safae, mon frère Rachid et sa femme Asmae, ma grande sœur Fatima (ada ila l jara fi kabadi) et son mari Abdessadak, ma petite sœur Rajae et mes deux adorables neveux Aymane et Alae.

# Table des matières

| INTE  | RODUCTION GENERALE                                                                                   | 1          |

|-------|------------------------------------------------------------------------------------------------------|------------|

| СНА   | PITRE 1: L'AMELIORATION DE LA FIABILITE ET DES                                                       |            |

| PER   | FORMANCES ELECTRIQUES DES CONVERTISSEURS PAR L'INTEGRATION                                           | 5          |

| 1.1   | Introduction                                                                                         | 9          |

| 1.2   | L'INTEGRATION HYBRIDE                                                                                | 9          |

| 1.3   | L'INTEGRATION MONOLITHIQUE                                                                           | 27         |

| 1.4   | OBJECTIF DE LA THESE                                                                                 | 37         |

| 1.5   | STRATEGIE DE TRAVAIL ET STRUCTURATION DU MEMOIRE                                                     | 40         |

| 1.6   | CONCLUSION                                                                                           | 41         |

| Вівц  | OGRAPHIE DU CHAPITRE 1                                                                               | 42         |

|       | PITRE 2 : APPROCHES D'INTEGRATION MONOLITHIQUES                                                      |            |

| DES   | CONVERTISSEURS STATIQUES SUR SILICIUM                                                                | 47         |

| 2.1   | Introduction                                                                                         | 51         |

| 2.2   | CHOIX DE LA STRUCTURE RC-IGBT POUR LA VALIDATION DES APPROCHES D'INTEGRATION "BI-PUCE" ET            |            |

| "мо   | NO-PUCE"                                                                                             | 51         |

| 2.3   | ETUDE PAR SIMULATIONS 2D D'UNE STRUCTURE RC-IGBT A BANDES P <sup>+</sup> ET N <sup>+</sup> ALTERNEES | 59         |

| 2.4   | APPROCHE D'INTEGRATION MONOLITHIQUE "BI-PUCE" (DEUX AIGUILLEURS DE COURANT)                          | 70         |

| 2.5   | APPROCHE D'INTEGRATION MONOLITHIQUE "MONO-PUCE" (CONVERTISSEUR COMPLET)                              | 86         |

| 2.6   | CONCLUSION                                                                                           | 93         |

| Вівц  | IOGRAPHIE DU CHAPITRE 2                                                                              | 94         |

| СНА   | PITRE 3: ASSEMBLAGE DES PUCES MULTI-POLES SUR SUBSTRAT DBC/SMI                                       | 97         |

| 3.1   | Introduction                                                                                         |            |

| 3.2   | ASSEMBLAGE DES PUCES SILICIUM DE PUISSANCE SUR SUBSTRAT                                              | 101        |

| 3.3   | CONCLUSION                                                                                           | 128        |

| Вівц  | IOGRAPHIE DU CHAPITRE 3                                                                              | 129        |

|       | PITRE 4 : REALISATION TECHNOLOGIQUE DES PUCES ET                                                     |            |

| CAR   | ACTERISATION ELECTRIQUE DES TECHNIQUES D'ASSEMBLAGE SUR SUBSTRAT                                     | 131        |

| 4.1   | Introduction                                                                                         | 135        |

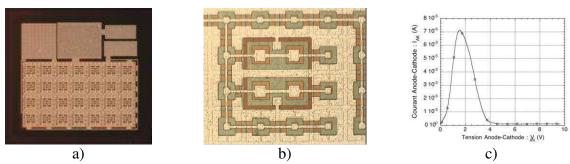

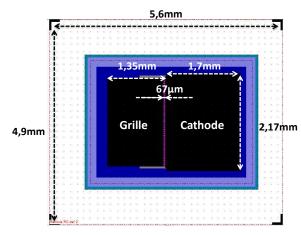

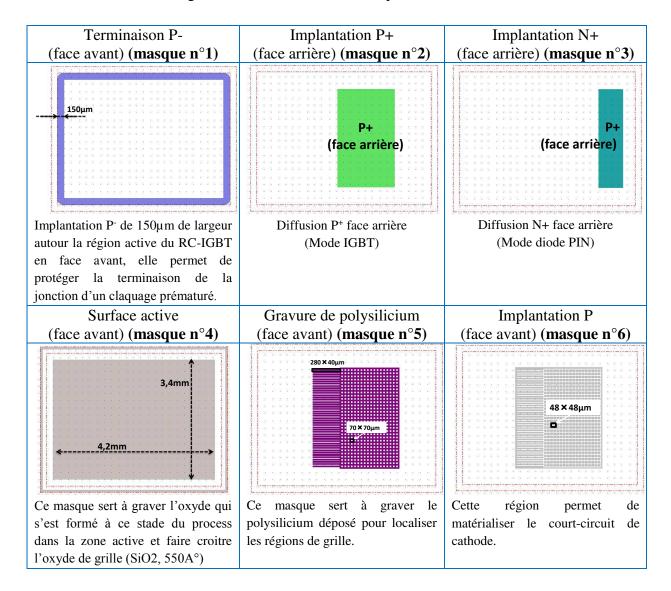

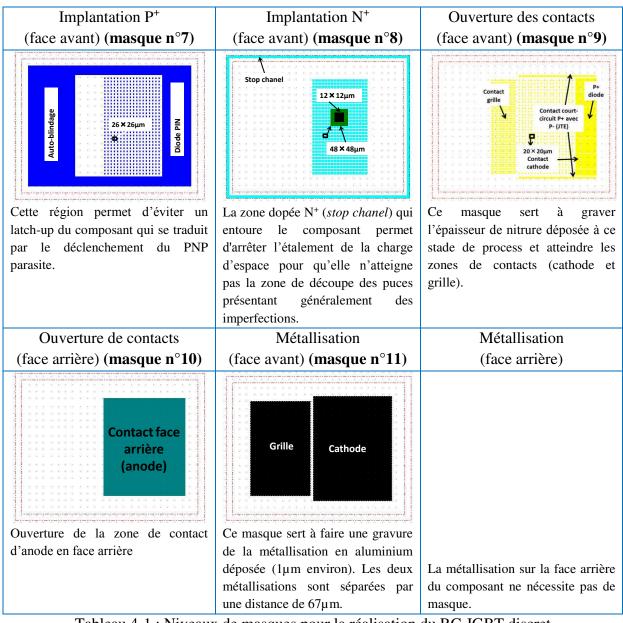

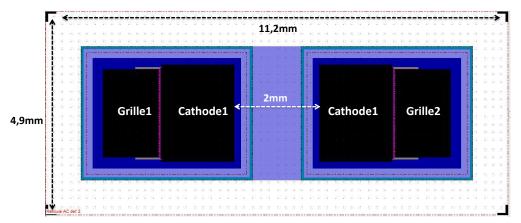

| 4.2   | CONCEPTION DE LA TOPOLOGIE DE SURFACE DES PUCES                                                      | 135        |

| 4.3   | ETAPES TECHNOLOGIQUES DE REALISATION DES PUCES TRI-POLES A ANODE COMMUNE ET DES PUCES RC-IO          | <b>GBT</b> |

| DISCI | RETES                                                                                                | 144        |

| 4.4   | CARACTERISATIONS SOUS POINTES DES PUCES RC-IGBT ET ANODE COMMUNE                                     | 146        |

| 4.5   | TEST DE REPORT DES PUCES "FACTICES" SIC SUR SUBSTRAT PCB                                             | 149        |

| 4.6   | REPORT DI  | ES PUCES REALISEES SUR SUBSTRAT PCB | 154 |

|-------|------------|-------------------------------------|-----|

| 4.7   | Conclusion | ON                                  | 158 |

| Вівц  | OGRAPHIE D | OU CHAPITRE 4                       | 159 |

|       |            |                                     |     |

| CON   | CLUSION (  | GENERALE                            | 161 |

|       |            |                                     |     |

| ANN   | EXE 1      |                                     | 165 |

|       |            |                                     |     |

| ANN   | EXE 2      |                                     | 169 |

|       |            |                                     |     |

| ANN   | EXE 3      |                                     | 171 |

|       |            |                                     |     |

| Вівц  | OGRAPHIE A | NNEXES                              | 174 |

|       |            |                                     |     |

| LISTI | E DES PUB  | LICATIONS                           | 175 |

|       |            |                                     |     |

| RESU  | JME        |                                     | 177 |

|       |            |                                     |     |

| ABS   | ΓRACT      |                                     | 178 |

## Introduction générale

Dans de nombreux secteurs d'applications tels que la domotique, l'automobile ou le ferroviaire..., l'électronique de puissance est fortement présente, depuis la naissance de cette discipline il y a plus de 50 ans. Les progrès, mais aussi les besoins en terme d'intégration (i.e. miniaturisation et compacité), n'ont pas cessé de s'accroitre. Cette électronique adresse le domaine du traitement de l'énergie électrique entre une source et une charge et plus généralement entre deux sources susceptibles d'échanger un flux de puissance : transformation des formes d'ondes (AC/DC, DC/AC), adaptation de niveau et régulation (DC/DC, AC/AC), isolement galvanique haute-fréquence (DC/AC/DC) constituent les grandes familles de fonctions de l'électronique de puissance.

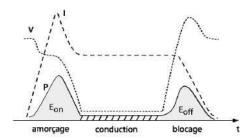

Les convertisseurs reposent sur des composants électroniques de puissance jouant le rôle d'interrupteurs "imparfaits" reliés entre eux sous forme de cellules à travers des fils de connexion (wire bonds) et des substrats métallisés. Ces interrupteurs sont des dispositifs à semi-conducteurs discrets de surface proportionnelle avec le calibre en courant. En fonctionnement nominal (i.e. non accidentel), ces composants se trouvent sur deux états statiques : l'état passant, où l'on cherche la plus forte densité de courant à température maximale de jonction donnée, cela revient à dire que l'on cherche la plus faible résistance spécifique (Ω.cm²), et l'état bloqué, où le composant doit supporter la tension appliquée à ses bornes et présenter un courant de fuite stable en température pour éviter l'emballement thermique de la puce. Le passage d'un état à l'autre concerne le régime transitoire de commutation. Sur les deux états (mais surtout l'état passant) et sur un cycle de commutation, le composant interrupteur est le siège de pertes de puissance électrique se traduisant par l'échauffement de la puce et par un affaiblissement du rendement du convertisseur de manière d'autant plus forte que la densité de puissance traitée sera élevée. La commutation est aussi une source de perturbations électromagnétiques rayonnées et conduites dans les circuits de conversion incluant l'alimentation et la connexion à la terre (ou masse de référence), la charge et les drivers mais qui pourra être maîtrisée d'autant plus que le circuit sera compact et donc intégré. Cette intégration est aussi un point de passage obligé pour tirer parti des performances des technologies silicium rapides (MOS, CoolMOS et IGBT moyenne tension) impliquant des mailles de commutation et de commande à faible impédance de connexion série et à faible capacité parasite par rapport à la terre ou à la masse de référence.

A partir de cette brève description, on peut d'ores et déjà situer les efforts d'amélioration dans ce domaine. Ces efforts se sont concentrés d'une part sur le composant de puissance luimême pour réduire ses pertes en conduction et commutation, sa taille, étendre sa gamme d'utilisation en courant et en tension, sa robustesse en saturation et avalanche. D'autre part, ces efforts se sont concentrés sur l'encapsulation globale des composants de puissance dans des boitiers de plus en plus sophistiqués pour assurer leur bonne isolation et leur conductivité électrique et l'évacuation de la chaleur dissipée ainsi que leur protection contre les agressions de l'environnement extérieur.

Pour les applications de faible puissance, les progrès sont spectaculaires. Ces progrès sont le fruit du transfert et de l'adaptation des technologies de la microélectronique sur les puces de

puissance silicium sous la forme d'une intégration monolithique intra-dispositif donc tout silicium. Les puces silicium intègrent le convertisseur électrique complet avec sa commande et sa protection, cette technologie est connue sous le nom "Smart Power" (et aussi Smart MOS) et qui repose sur des composants de puissance à conduction latérale. Hélas, la généralisation de cette technologie pour les applications des moyennes et fortes puissances n'est pas possible, car cette gamme de puissance nécessite, en technologie silicium, des composants à conduction verticale (typiquement, des composants tels que l'IGBT, VDMOS et les diodes PIN). Dans ce domaine, les progrès ont concerné surtout l'amélioration des techniques d'assemblage hybride multi-puce sur substrat isolant métallisé pour augmenter la fiabilité des convertisseurs, améliorer la dissipation de la chaleur et minimiser l'impédance de connexion parasite des mailles de commutation de puissance et des mailles de commande. Des solutions d'intégration pour des secteurs de grand volume (fabrication collective en un nombre réduit d'étapes pour augmenter le gain en productivité) sur boîtier standard ou à l'inverse pour des applications de "niche" très spécifiques (sorte d'ASIC, selon une approche Fab-less ...). Pour des besoins de miniaturisation "ULTIME" et de non intrusivité (reverse difficile, rendre difficile la copie ou la contrefaçon) sur des fonctions auxiliaires, l'intégration fonctionnelle totale ou mixte sur silicium constitue une voie prometteuse pour le développement des nouveaux dispositifs dans le domaine des moyennes puissances.

Ce mode d'intégration est introduit au LAAS (Laboratoire d'Analyses et d'Architectures des Systèmes) depuis une quinzaine d'années à travers le groupe ISGE (Intégration des Systèmes de Gestion d'Energie). Les travaux de recherches menés dans ce groupe ont conduit au développement d'une filière technologique dite "flexible" permettant de réaliser des composants et des fonctions de puissance de plus en plus complexes simultanément avec le même process technologique. Ceci, a ouvert la voie à une collaboration avec le groupe CS (Convertisseurs Statiques) du laboratoire Laplace (Laboratoire Plasma et Conversion d'Energie) pour développer de nouvelles fonctionnalités de commutation de puissance intégrables directement sur la puce. Dans le cadre de cette collaboration, des travaux antérieurs basés sur ce mode d'intégration fonctionnelle ont vu le jour. Ces travaux de collaboration ont débuté par la thèse de Marie Breil en 1997 sur l'étude de l'association MOS-Thyristor auto-amorçable et blocable donnant lieu au premier thyristor-dual monolithique. Dans cette première thèse, le principe de l'intégration fonctionnelle consiste à associer des briques « fonctionnelles » intégrées, ou cellules élémentaires semi-conductrices, pour obtenir la fonctionnalité complète. Ce mode d'intégration a été par la suite utilisé dans le cadre de la thèse de Florence Capy en 2009 au développement d'un thyristor dual disjoncteur qui est un interrupteur monolithique réversible en courant à auto-commutation. Cette fonction est synthétisée à partir d'un thyristor classique (ou d'un IGBT) en le dotant de fonctions annexes permettant la gestion de l'auto-amorçage et de l'auto-blocage.

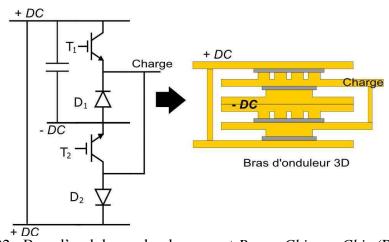

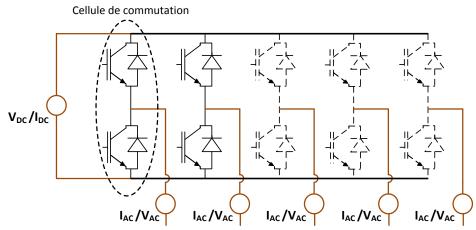

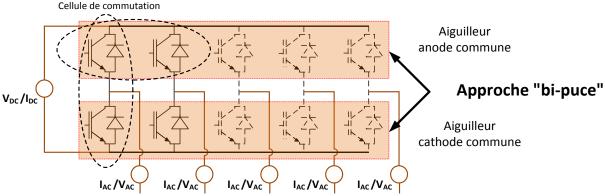

Le travail présenté dans cette thèse se situe aussi dans le contexte de cette collaboration, il vise à développer des approches d'intégration monolithiques sur silicium de convertisseurs statiques génériques (AC/DC ou DC/AC) fonctionnant dans la gamme de la faible et moyenne puissance. En partant d'une fonction de conversion d'énergie générique décrite par une topologie de circuit, on en déduit une architecture d'interrupteurs intégrables verticalement dans le cristal puis le travail consiste à optimiser le dispositif élémentaire au sein de ce réseau d'interrupteurs en mutualisant le maximum de régions et d'électrodes tout en minimisant les

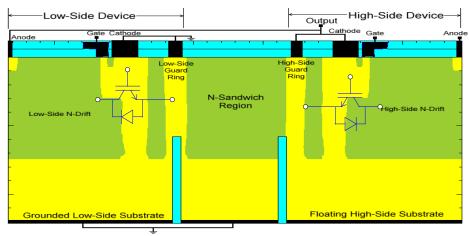

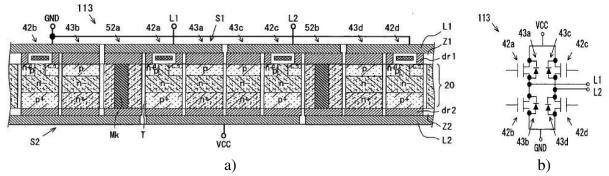

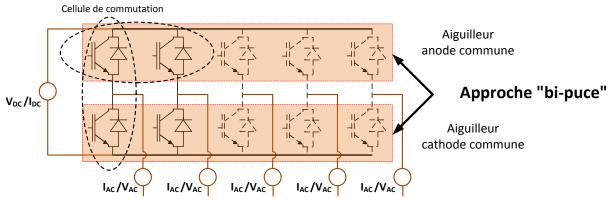

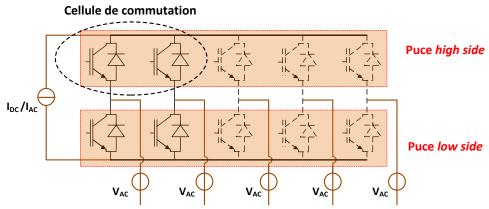

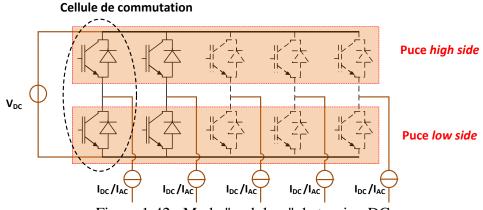

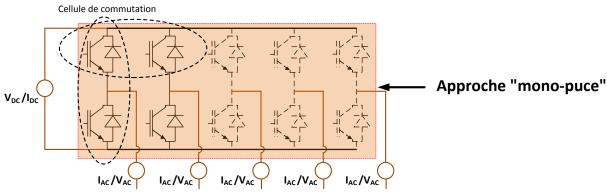

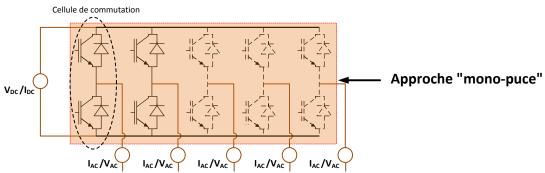

couplages jugés parasites pour le fonctionnement considéré ici globalement à l'échelle du convertisseur. Nous verrons dans ce mémoire que les architectures en question ne s'apparentent pas toujours à une cellule de commutation monolithique mais plutôt à une demicellule intégrable dans une puce. Dans ce cas, une étape supplémentaire d'hybridation dite bipuce (2 x ½ cellule = deux puces) est nécessaire et permet également de faire apparaître des degrés de liberté intéressants au niveau des possibilités de report, d'interconnexion en 3D et même de fonctionnalisation des zones de contact inter-puces. Le passage à une architecture "complète" de cellules de commutation intégrables au sein d'une seule puce (solution dite "mono-puce", plus complexe) est présenté en fin de mémoire et constitue un axe de recherche prioritaire, à court-terme pour les protagonistes.

Qu'il s'agisse d'une intégration monolithique "bi-puce" ou "mono-puce", un intérêt évident de cette approche est que le nombre de puces en jeu ne dépend pas du nombre total d'interrupteurs, ce qui permet de réduire le nombre d'étapes de report de puces sur substrat. Cette intégration permet aussi une réduction voire la suppression des fils de *bonding* d'interconnexion. Ceci va sans doute permettre une amélioration des performances électriques des convertisseurs statiques fonctionnant dans cette gamme de puissance. Cela aura un impact sur la miniaturisation de la fonction de puissance et la réduction du coût de production.

#### Le mémoire est organisé comme suit:

- Dans le premier chapitre, nous exposons la problématique et le contexte de cette étude ainsi que nos motivations pour l'exploration de cette voie. En s'appuyant sur un exemple de module convertisseur hybride standard 2D, nous détaillons ses points forts et ses points faibles. Nous faisons un état de l'art des solutions apportées par la voie de l'intégration hybride 3D ainsi que celles apportées par la voie de l'intégration monolithique sur silicium.

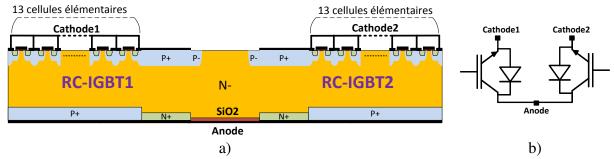

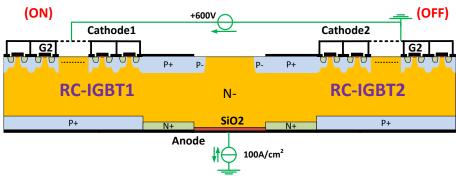

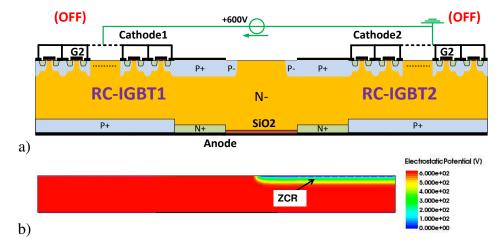

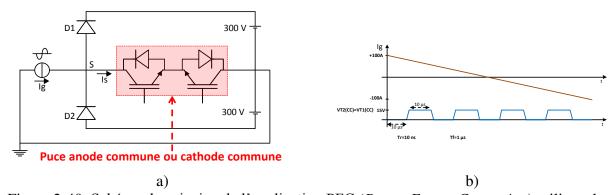

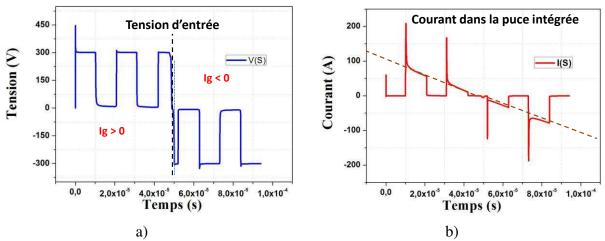

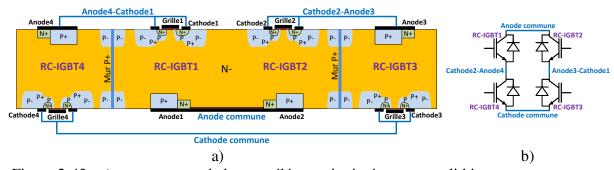

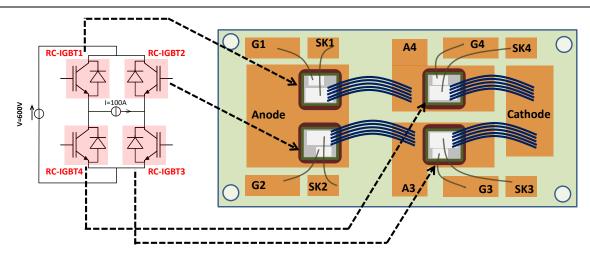

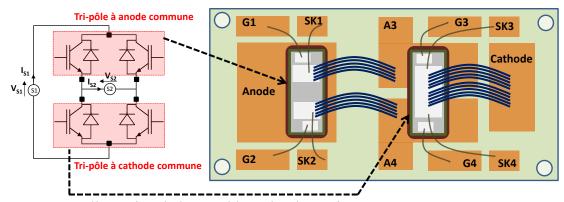

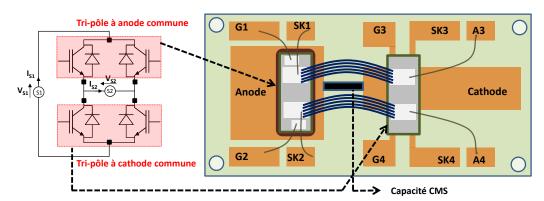

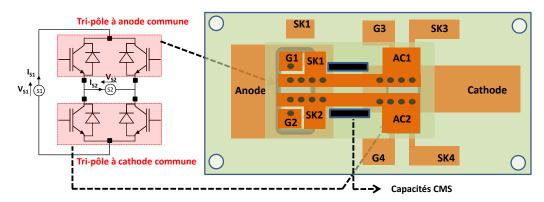

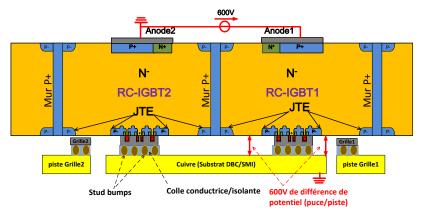

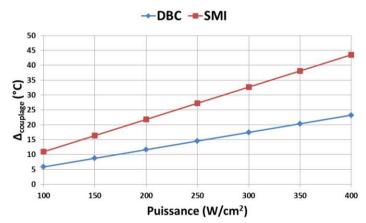

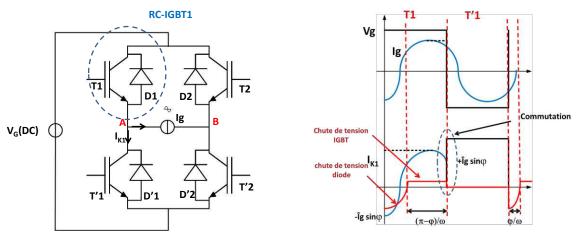

- Le deuxième chapitre constitue le cœur de notre travail, nous le commençons par une étude par simulations 2D du composant de référence RC-IGBT (Reverse Conducting IGBT) IGBT à conduction en inverse, ce composant bidirectionnel en courant est le meilleur dispositif générique répondant également à notre cahier des charges, il sera optimisé et adapté aux applications de base (onduleur de tension, redresseur de tension passif ou actif et finalement en hacheur). Nous abordons ensuite la première approche d'intégration dite "bi-puce", comme son nom l'indique, cette approche est basée sur deux versions de puces complémentaires et génériques. Une première puce multi-interrupteurs à anode commune/face arrière de la puce intégrant la totalité des interrupteurs qui composent la partie high-side du convertisseur et une deuxième puce multi-interrupteurs à cathode commune/face avant de la puce intégrant cette fois la partie low-side du convertisseur. Pour chaque version de puce, nous validons son fonctionnement en statique et nous associons ensuite les deux puces pour simuler leur fonctionnement en mode onduleur de tension, redresseur de tension et hacheur. Nous passons ensuite à la deuxième approche d'intégration dite "mono-puce", cette fois et comme son nom l'indique aussi, l'ensemble des composants qui composent le convertisseur (partie highside et low-side) est intégré au sein d'un même cristal pour donner naissance à une

macro-puce monolithique et multi-interrupteurs, qui représente à elle seule, un convertisseur complet. L'étude est faite par simulations physique/électrique 2D à l'aide de l'outil de simulation par éléments finis Sentaurus TCAD.

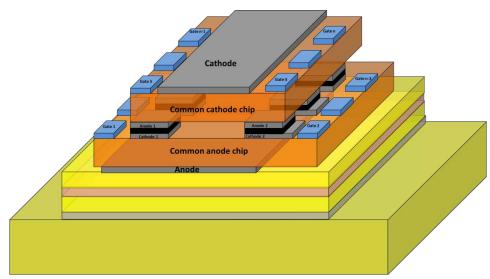

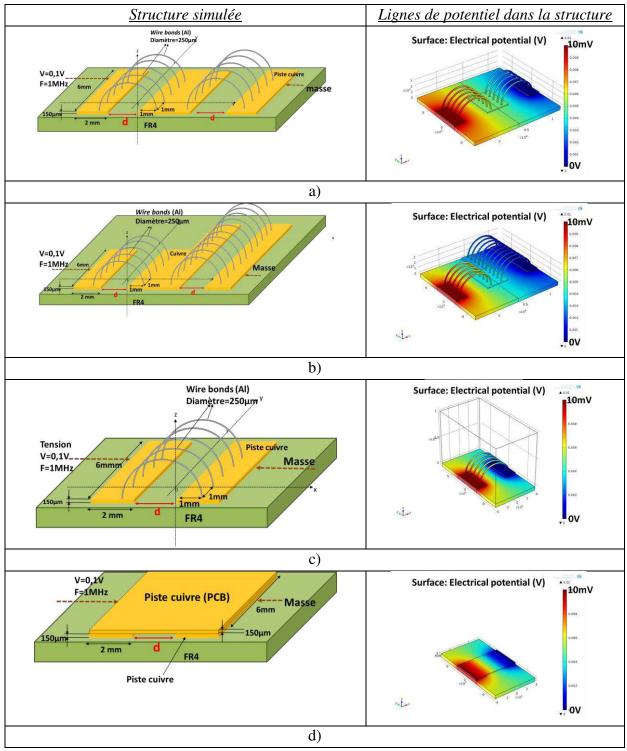

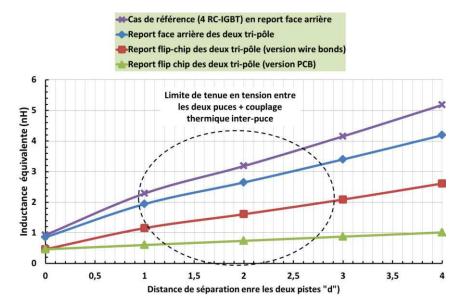

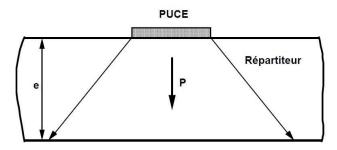

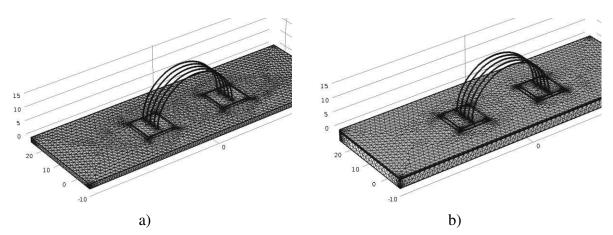

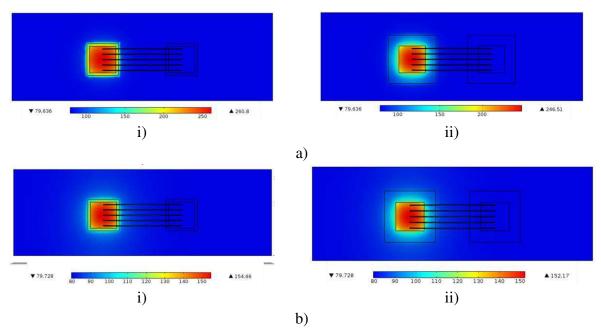

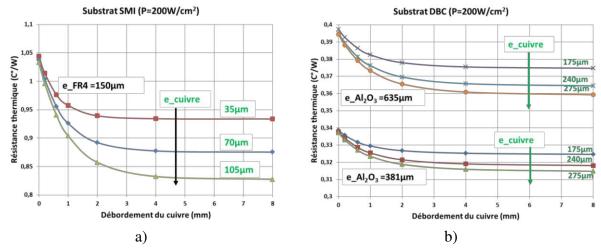

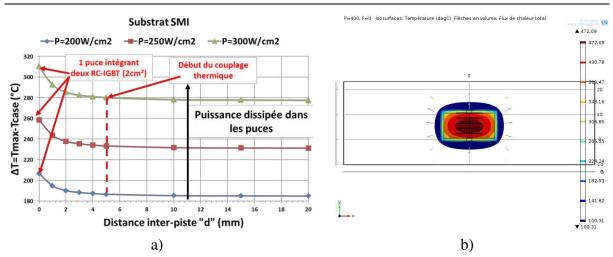

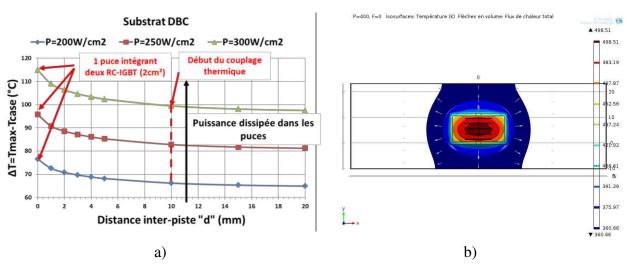

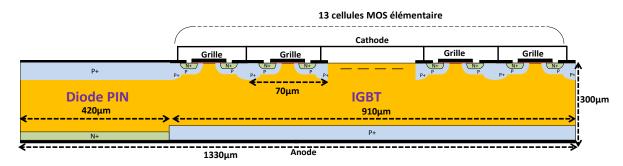

- Dans le troisième chapitre, nous nous intéressons à l'étude des différentes techniques d'association de la puce à anode commune et de la puce à cathode commune sur substrat DBC/SMI en comparant les performances électriques de chaque technique employée avec la technique de référence utilisant des composants discrets. Le gain apporté par les différentes techniques d'association en terme d'inductance parasite sera évalué à l'aide de l'outil de simulations par éléments finis 3D Comsol *multiphysics*. Une étude thermique sera aussi faite sous le même outil de simulations afin d'évaluer l'élévation de la température dans les puces due à leur rapprochement sur un substrat et nous concluons sur l'effet de cette élévation sur l'intégration d'une manière générale. Nous conclurons le chapitre en présentant l'assemblage 3D de la solution "mono-puce" qui réunit les avantages constatés lors des études précédentes.

- Le quatrième et dernier chapitre est consacré à l'aspect réalisation technologique, dessin des masques sous CADENCE, étapes technologiques de réalisation de chaque puce multi-interrupteurs et résultats de caractérisations électriques des puces fonctionnelles ainsi que des assemblages réalisées.

Nous finirons ce manuscrit par une conclusion générale sur ce travail et ses perspectives.

Chapitre 1 : L'amélioration de la fiabilité et des performances électriques des convertisseurs par l'intégration

| 1.1   | Introduction                                                                              | . 9 |

|-------|-------------------------------------------------------------------------------------------|-----|

| 1.2   | L'INTEGRATION HYBRIDE                                                                     | . 9 |

| 1.2.1 | MODULES DE PUISSANCE STANDARDS: L'INTEGRATION HYBRIDE 2D                                  | 10  |

| 1.2.1 | .1 La maturité industrielle des modules de puissance 2D                                   | 11  |

| 1.2.1 | .2 Les modes de défaillance des modules de puissance 2D                                   | 12  |

| a)    | Fiabilité et coût des modules de puissance 2D                                             | 12  |

| b)    | Inductances parasites des fils de bonding                                                 | 14  |

| c)    | Capacités parasites et courant du mode commun                                             | 17  |

| 1.2.2 | SOLUTIONS HYBRIDES EXISTANTES                                                             | 18  |

| 1.2.2 | .1 Technologie <i>Press Pack</i>                                                          | 18  |

| 1.2.2 | .2 Evolution vers les technologies d'intégration hybride3D                                | 19  |

| a)    | Technologie Metal-Posts Interconnected Parallel Plates (MPIPPs)                           | 19  |

| b)    | Technologie Solder bumps interconnect                                                     | 20  |

| c)    | Technologie Dimple Array Interconnect (DAI)                                               | 21  |

| d)    | Technologie Embedded Power (EP)                                                           | 22  |

| e)    | Technologie Power Overlay (POL)                                                           | 23  |

| f)    | La technologie 3D NextFET™ :                                                              | 24  |

| 1.2.2 | .3 Autres technologie 3D en cours de développement                                        | 24  |

| a)    | Technologie d'interconnexions par des micro-poteaux                                       | 24  |

| b)    | Technologie Power Chip-on-Chip (PCoC)                                                     | 25  |

| 1.2.2 | .4 Synthèse des solutions hybrides 3D                                                     | 26  |

| 1.3   | L'INTEGRATION MONOLITHIQUE                                                                | 27  |

| 1.3.1 |                                                                                           |     |

| 1.3.2 | INTEGRATION "SMART POWER" ET HVIC :                                                       | 28  |

| 1.3.3 | INTEGRATION MONOLITHIQUE FONCTIONNELLE                                                    | 29  |

| 1.3.3 | .1 Définition                                                                             | 29  |

| 1.3.3 | .2 Evolutions de l'intégration fonctionnelle                                              | 30  |

| 1.3.3 | .3 Les progrès technologiques au profit de l'intégration fonctionnelle                    | 31  |

| 1.3.4 | VERS UNE INTEGRATION DES CELLULES DE COMMUTATION DES CONVERTISSEURS SUR LE MEME CRISTAL:. | 32  |

| 1.3.4 | .1 Solutions d'intégration monolithique sur le silicium                                   | 33  |

| a)    | Première solution :                                                                       | 33  |

| b)    | Deuxième solution :                                                                       | 34  |

| 1.3.4 | .2 Approches d'intégration monolithique utilisant des matériaux grand gap (GaN)           | 35  |

| 1.3.4 | .3 Approche non monolithique basée sur l'assemblage 3D                                    | 36  |

| 1.4   | OBJECTIF DE LA THESE                                                                      | 37  |

| 1.5   | STRATEGIE DE TRAVAIL ET STRUCTURATION DU MEMOIRE                                          | 40  |

| 1.6   | CONCLUSION                                                                                | 41  |

#### 1.1 Introduction

En électronique de puissance, un grand intérêt est porté actuellement sur l'intégration des systèmes de puissance. Cette intégration n'est pas une fin en soi, le but est d'optimiser leur compacité et leur coût de fabrication d'une part et d'améliorer la fiabilité et les performances des fonctions de conversion d'énergie d'autre part. L'utilisation de matériaux mutualisés et multifonctionnels permet, en effet, de réduire le nombre d'étapes différentes d'un process, de gagner en fiabilité et en réduction des coûts.

Plusieurs modes d'intégration sont usuellement rencontrés. Ces modes d'intégration changent en fonction de l'application visée et surtout de la gamme de puissance mise en jeu. On distinguera en particulier l'intégration hybride de l'intégration monolithique. La première est caractérisée par l'association au sein d'un même module de plusieurs composants, puces et/ou fonctions alors que la deuxième est caractérisée par l'association de plusieurs composants et/ou fonctions au sein d'un même cristal sous la forme d'une seule puce.

Ce premier chapitre mettra notre étude dans son contexte et définira son objectif. Le premier paragraphe est dédié au mode d'intégration hybride des convertisseurs statiques, nous abordons ce mode d'intégration par la technologie d'hybridation planaire 2D. Ce mode d'intégration est très répandu et très utilisé dans le milieu industriel pour les applications de forte et moyenne puissance. En s'appuyant sur un exemple, nous définirons les constituants des modules de puissance 2D, nous présenterons ses points forts et nous détaillerons ses modes de défaillance. Ce mode d'intégration sera considéré comme notre point de départ et constituera pour nous, tout au long de ce manuscrit, une référence pour mener des comparaisons avec nos approches d'intégration qui seront détaillées et étudiées dans les deuxième et troisième chapitres. Ensuite, nous donnerons un état de l'art des solutions basées sur le mode d'intégration hybride 3D. La troisième partie de ce chapitre est dédiée à l'intégration monolithique et fonctionnelle sur puce, nous donnerons un état de l'art sur ce mode d'intégration pour les faibles puissances, et nous nous intéresserons particulièrement aux avancées décrites dans la littérature sur l'intégration de cellules de commutation. Nous définirons par la suite notre contribution et nos motivations dans la dernière partie de ce chapitre.

#### 1.2 L'intégration hybride

La première grande famille de l'intégration en électronique de puissance est appelée intégration hybride, dans laquelle, la partie active du convertisseur est constituée de plusieurs puces silicium intégrées sur un même substrat formant à la fois le support mécanique, une partie des connexions électriques, l'isolation électrique et l'évacuation de la chaleur. Dans cette famille, l'intégration hybride 2D constitue la technologie ayant atteint un bon stade de maturité industrielle. Nous proposons de définir ce mode d'intégration et nous détaillons ses propriétés en s'appuyant sur des considérations électriques en priorité, thermiques et fiabilité par la suite.

#### 1.2.1 Modules de puissance standards: l'intégration hybride 2D

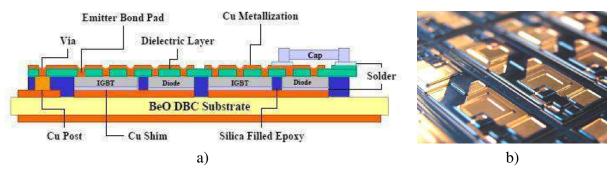

Nous nous plaçons dans le cas des modules de puissance des convertisseurs statiques qui assurent les fonctions de conversion d'énergie (AC/DC ou DC/AC) dans le domaine des applications des moyennes et fortes puissances (quelques centaines de kW à quelques MW). Ces modules nécessitent des composants semi-conducteurs de puissance à conduction verticale généralement de type VDMOS, IGBT et diodes de puissance caractérisés par leur grand calibre en courant tout en présentant une faible chute de tension à l'état passant ( $\approx$  2V pour les IGBT ayant une densité de courant de 200A/cm² sous 600V) et leur grande tenue en tension (jusqu'à 6kV). Les composants de puissance à conduction latérale ne sont pas adaptés pour cette gamme de puissance à cause de leur faible densité de courant admissible sur le plan thermique ou ce qui revient au même à leur forte résistance spécifique. Aujourd'hui, ce type de module est basé essentiellement sur l'intégration hybride dans une conception planaire i.e. 2D (Figure 1-1).

Figure 1-1: Exemple d'un module convertisseur en technologie hybride 2D [1] a) modules encapsulés, b) module ouvert

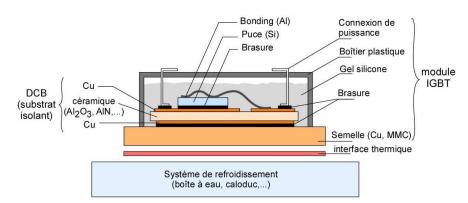

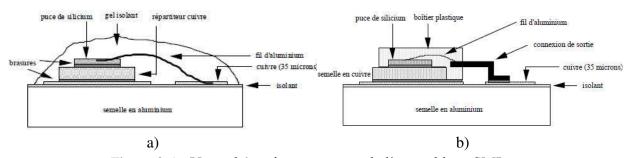

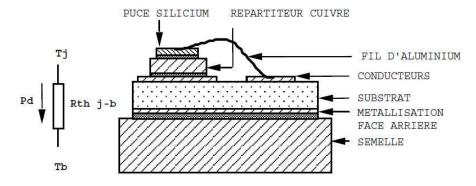

Les puces dans ce type de module sont mises en parallèle pour satisfaire les contraintes de fort courant et de forte puissance, la face arrière de ces puces est brasée et reportée sur une couche en cuivre d'un substrat en alumine ou en nitrure d'aluminium de type DBC (*Direct Bond Copper*). La Figure 1-2 illustre le principe d'assemblage des modules de puissance 2D.

Figure 1-2 : Principe d'assemblage standard d'un module de puissance intégré 2D à IGBT sur substrat DBC [2]

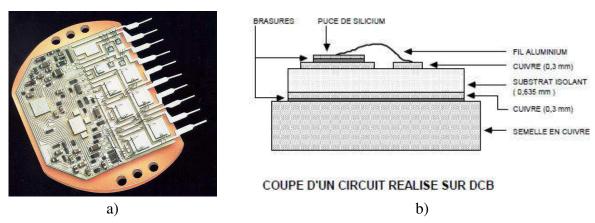

Le substrat DBC est en fait composé de deux couches en cuivre de même épaisseur pour des raisons mécaniques et séparées par un isolant électrique. Le rôle du substrat DBC est

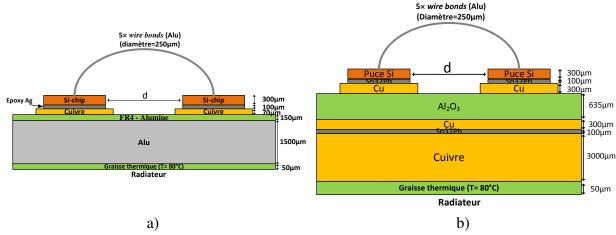

d'assurer les contacts électriques en face arrière des puces et l'isolation électrique entre les points de tenue en tension dans le module ainsi que l'évacuation de la chaleur dissipée dans les puces. Le substrat a aussi pour rôle d'assurer la tenue mécanique globale de la structure. Plusieurs types de substrat autre que le substrat DBC sont disponibles sur le marché et qui sont exploités en fonction des niveaux de densité de puissance, de température et de tenue aux cyclages thermique. On trouve les substrats métallisés isolés SMI en cuivre / aluminium et FR4 chargé en alumine pour la basse tension et la faible puissance ou encore, les substrats AMB (*Active Metal Brazing*) où une couche d'aluminium est soudée sur un substrat en Si<sub>3</sub>N<sub>4</sub> lui-même reporté sur une semelle en AlSiC pour les applications à fortes contraintes thermique et thermomécanique. Ces substrats ont la même fonction dans un module de puissance qu'un substrat de type DBC dont le rôle est décrit avec des performances différentes. Nous nous limiterons dans ce manuscrit aux deux technologies de substrat DBC et SMI qui seront abordées et étudiées ultérieurement par simulation 3D sous COMSOL dans le troisième chapitre.

Le substrat DBC qui évacue la chaleur dissipée dans les puces semi-conductrices est brasé à son tour sur une semelle en cuivre ou en AlSiC possédant de bonnes caractéristiques thermiques pour acheminer la chaleur vers un dissipateur thermique (le radiateur). Le radiateur est en contact avec la semelle à travers une couche de graisse thermique (ou composé plastique d'interface). Pour des raisons de sécurité, le radiateur est généralement connecté à la terre pour des installations au sol ou à la masse du véhicule / avion pour un système mobile. Un gel passivant est versé ensuite sous vide à l'intérieur du module puis polymérisé de manière à protéger ses constituants contre la corrosion et les agressions de l'environnement extérieur, le tout est ensuite fermé par un boitier en plastique.

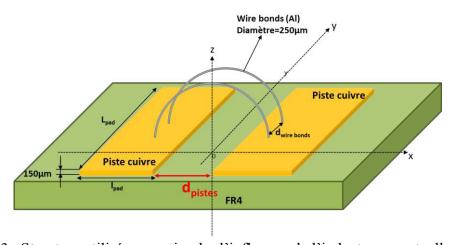

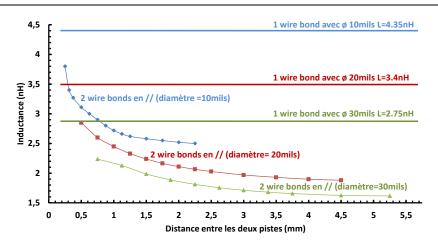

Les interconnexions en face avant entre les puces (et entre les puces et les connecteurs externes) dans ce type de module planaire sont réalisées par des fils de connexion (*wire bonds*) en aluminium, parfois en cuivre ou en co-lamination Al/Cu, généralement de diamètres importants (≈ 250μm) et en nombre suffisant en parallèle afin de distribuer les forts courants les traversant et réduire leur impédance parasite. Le nombre de ces fils utilisés est proportionnel au courant qui circule dans les puces semi-conductrices de puissance. La maximisation du nombre de fils de câblage en parallèle permet une meilleure distribution des lignes de courant, une moindre contrainte thermique et surtout une moindre impédance parasite de maille de commutation. Il existe également un compromis sur le diamètre de fil, entre résistance linéique, la rigidité mécanique obtenue et le niveau d'endommagement de la couche de métal lors de l'opération de soudure à ultrason. Raison pour laquelle des fils de diamètre inférieur à 125μm et supérieur à 500μm ne sont pas utilisés aujourd'hui.

#### 1.2.1.1 La maturité industrielle des modules de puissance 2D

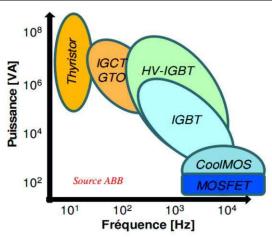

La maitrise des techniques d'assemblage de la conception 2D des modules de puissance (brasure, câblage...) fait d'elle aujourd'hui une technologie de production massive. Sa maturité industrielle s'exprime par l'étendue des puissances balayées par les modules 2D (Figure 1-3) et à travers la standardisation des dimensions des modules [3], dans le but de rendre ces modules intégrables et interchangeables dans n'importe quelle structure. A partir de

la Figure 1-3, on peut remarquer que cette technologie couvre les domaines des applications des faibles, moyennes et de fortes puissances.

Figure 1-3 : Etendue des puissances balayées par les modules hybrides 2D [4]

La technologie employée pour la conception des modules de puissance selon cette approche 2D offre une certaine simplicité de mise en œuvre puisque tous les modules intégrant une isolation électrique, peuvent être reportés sur le même refroidisseur qui sert aussi de support mécanique à l'ensemble des composants actifs du module 2D.

#### 1.2.1.2 Les modes de défaillance des modules de puissance 2D

D'un point de vue électrique, les points faibles les plus importants des modules de puissance planaires 2D sont dus essentiellement au type d'interconnexion par les fils de bonding utilisés. Nous allons détailler dans ce paragraphe l'ensemble des problèmes de la technologie 2D. D'un point de vue thermique, cette technologie ne permet pas un refroidissement double face des composants. En effet, le refroidissement ne peut se faire qu'en face arrière des puces en suivant la trajectoire : face arrière des puces  $\rightarrow$  brasures  $\rightarrow$  substrat  $\rightarrow$  brasure  $\rightarrow$  semelle  $\rightarrow$  graisse thermique  $\rightarrow$  radiateur. Le refroidissement par la face avant des puces dans les modules 2D est très limité (convection naturelle).

#### a) Fiabilité et coût des modules de puissance 2D

La tendance actuelle consiste à mettre de plus en plus d'équipements électroniques dans des applications embarquées (aéronautique, ferroviaire, automobile etc.) pour lesquelles la fiabilité et le coût constituent un enjeu majeur pour les concepteurs et les exploitants.

#### • Fiabilité des fils de câblage

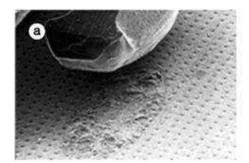

Durant les cycles de fonctionnement des puces de puissance en mode interrupteurs électriques, les fils de câblage subissent des excursions thermiques successives causées par des phases transitoires d'injection de puissance et par l'environnement extérieur. Ils sont également le siège d'une très forte densité de courant pouvant dépasser les 50A/mm² sur une longueur de 10mm. Ces variations de la température répétées engendrent des contraintes thermomécaniques sur le fil de câblage dues à la différence des CTE (coefficient de dilatation thermique) entre les matériaux en contact dans le module, en particulier entre les fils de câblage et les métallisations d'un côté et la puce silicium de l'autre. Cela conduit au vieillissement de la métallisation et de l'interface au pied du fil de câblage puis au décollement du fil [5][6][7]. Cette défaillance se manifeste typiquement par une levée du fil de câblage (lift-off, Figure 1-4a), voire une fissuration (Figure 1-4b) et même une rupture dans la zone de courbure (*cracking*). Le courant qui traverse les puces se concentre aux niveaux des fils de câblage et fait apparaître des points chauds, ce phénomène accentue et favorise le décollement des fils.

Un autre mode de défaillance qui peut se produire, surtout pour des diamètres importants, lors de la mise en place des fils de câblage sur les métallisations des puces concerne cette foisci la puce elle-même. En effet, des paramètres inappropriés de l'opération de câblage (pression, durée...) peuvent endommager la métallisation des puces de puissance (Figure 1-5).

Figure 1-4 : Deux modes de défaillance des fils de câblage a) levée d'un fil de câblage (*lift-off*), b) fracture d'un pied de fil de câblage [6] (fissuration puis cracking)

Figure 1-5 : Dégradation d'une métallisation d'une puce durant le procédé *wedge bonding* (photographie *Advanced Power Technology Europe*)

#### • Coût de l'opération du câblage :

Outre le coût des fils de câblage eux-mêmes, il est bien connu que l'opération de câblage en électronique de puissance nécessite beaucoup de temps, elle est donc couteuse. En effet, c'est une opération qui se fait point par point malgré l'automatisation du procédé de mise en œuvre du câblage.

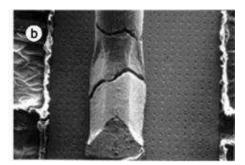

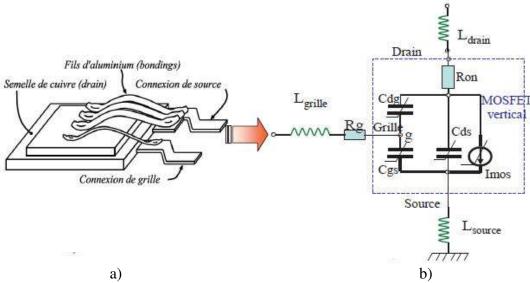

#### b) Inductances parasites des fils de câblage

Quelle que soit la nature du matériau du fil de câblage, et quel que soit le type d'association des composants (parallèle ou série), ce fil possède une impédance qui présente un comportement résistif et un second comportement inductif. Les effets parasites de la connectique par le fil de câblage apparaissent et peuvent dégrader le comportement électrique du convertisseur et ainsi limiter son aire de sécurité. Le comportement inductif peut être vu électriquement comme une inductance équivalente de chaque fil de câblage, la valeur de cette inductance dépend des dimensions géométriques du fil ainsi que des propriétés électriques de son matériau. La valeur de cette inductance parasite pour chaque fil de câblage est comprise généralement entre 6nH et 16nH [8]. La Figure 1-6 illustre le cas d'un MOSFET encapsulé dans son boitier avec le modèle électrique équivalent faisant apparaître les éléments inductifs parasites.

Figure 1-6 : Inductances parasites des interconnexions par les fils de câblage a) mise en évidence de la connectique interne d'un boîtier d'un MOSFET vertical [9] b) modèle équivalent simplifié du MOSFET vertical (pas de diode body, bipolaire et JFET) avec les inductances parasites du câblage

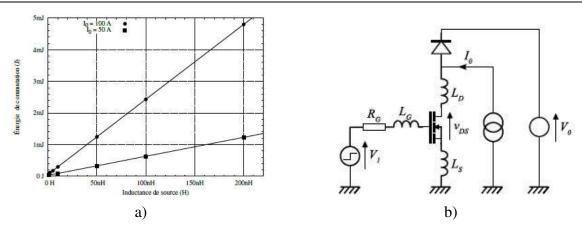

L'inductance parasite est responsable du ralentissement du temps de commutation de l'interrupteur de puissance à l'amorçage (couplage circuit – grille) et d'une surtension au blocage. Cela a pour conséquence de rajouter des pertes supplémentaires en commutation. Ces pertes en commutation deviennent de plus en plus importantes avec l'augmentation du niveau de courant de commutation (Figure 1-7).

Figure 1-7 : a) évolution des pertes en commutation en fonction de l'inductance parasite et du niveau de courant de commutation, b) circuit de mesures [9]

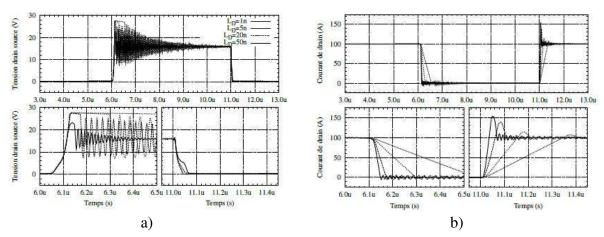

La réduction de ces pertes passe par la réduction de la fréquence de découpage des interrupteurs, cela nécessite un circuit de filtrage d'une taille bien souvent prépondérante à l'échelle du convertisseur complet. Pour travailler avec des fréquences de découpage élevées tout en ayant des pertes en commutation acceptables, une réduction de la valeur de l'inductance parasite est recherchée, pour ce faire, une augmentation du nombre de fils de câblage en parallèle est nécessaire au prix d'une opération de câblage plus coûteuse. De plus, l'inductance parasite entraîne aussi des surtensions oscillantes au niveau de l'interrupteur de puissance lors de son blocage (Figure 1-8). Celles-ci peuvent dans certains cas, atteindre voire dépasser la tension limite de tenue en tension du composant de puissance indiquée par le fabricant, amenant une possible destruction.

Figure 1-8 : Influence de l'inductance du drain sur la commutation à l'ouverture et à la fermeture : a) tension drain-source, b) courant drain (simulations).

Les deux petites figures placées en bas des figures a) et b) sont des agrandissements [9]

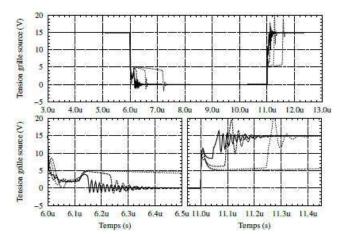

Les surtensions provoquées sont aussi responsables des perturbations sur les signaux de commande des grilles des interrupteurs générés par les *drivers* [9][10][11] en particulier par l'inductance résiduelle de contre-réaction présente entre la grille et la connexion de source – kelvin (Figure 1-9).

Figure 1-9 : Influence de l'inductance de sources sur la tension de commande  $V_{GS}$  (simulation) [9]

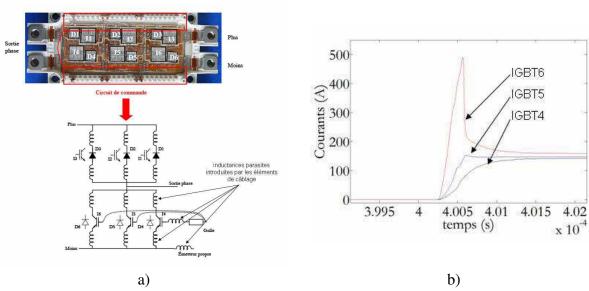

Enfin, les inductances parasites de plusieurs puces en parallèle provoquent un déséquilibre au niveau des courants circulant dans les puces lors des commutations [9][11]. La Figure 1-10 montre un module de puissance Sixpak 1200V – 450A (Eupec) composé de trois puces IGBT en parallèle et de trois diodes en parallèle. Les résultats de simulation sous les logiciels InCA<sup>TM</sup> et Saber<sup>TM</sup> mettent en évidence ce déséquilibre des courants à la fermeture dans trois puces IGBT en parallèle [12]. Ce déséquilibre inhérent à la dissymétrie du câblage filaire et à la dispersion des paramètres physiques des puces (gain et durée de vie des porteurs minoritaires en particulier) conduit l'utilisateur à devoir ralentir la commutation ou à appliquer un *derating* en courant suffisant pour permettre à chaque puce de rester dans son aire de sécurité. L'association de puces réalisée par hybridation conduit toujours à un *derating* sur les performances électriques.

Figure 1-10: a) bras d'onduleur d'un module de puissance Sixpack 1200V - 450A (Eupec), b) déséquilibre des courants à la fermeture dans trois puces IGBT en parallèle [12]

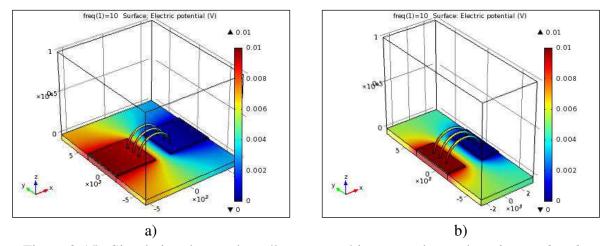

#### c) Capacités parasites et courant du mode commun

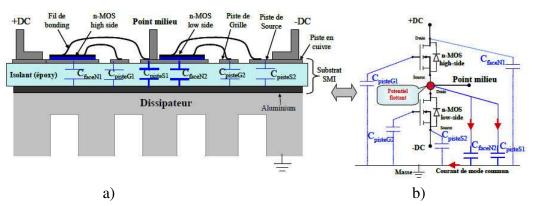

La structure des substrats (diélectrique pris en sandwich entre deux couches métalliques conductrices) utilisés pour le report de puces actives dans les modules de puissance, fait apparaitre des capacités parasites. En effet, la couche conductrice en face avant du substrat est généralement gravée pour recevoir plusieurs composants d'un convertisseur dans le même module de puissance et permettre l'interconnexion de ces derniers pour constituer la fonction de conversion souhaitée. La face arrière du substrat métallique est connectée électriquement à la semelle par la brasure ou directement au radiateur par bridage mécanique. De ce fait, des capacités parasites sont formées entre les pistes en cuivre de la face avant du substrat et la semelle en cuivre dans le cas d'un substrat de type DBC ou en aluminium dans le cas d'un substrat de type SMI. La Figure 1-11a illustre les capacités parasites qui apparaissent dans l'exemple d'une cellule de commutation (bras d'onduleur) formée par deux transistors de puissance de type N-MOS reportés sur un substrat de type SMI. La Figure 1-11b montre le schéma électrique équivalent du module qui fait apparaître les capacités parasites dans les différentes régions du module, au niveau des zones de report des puces et au niveau des zones de "pad" des électrodes. Les capacités Cface correspondent aux pistes en cuivre servant au report des puces de puissance avec la semelle en aluminium, et Cpiste correspondent aux capacités parasites des autres pistes en cuivre dans le module avec la semelle (par exemple, les pistes qui servent à la prise de contacts électriques des grilles.

Figure 1-11 : Capacités parasites dans un bras d'onduleur classique [2]

Dans le cas des convertisseurs de types onduleur ou redresseur par exemple, les composants interrupteurs utilisés fonctionnent en régime de commutation pour un découpage des grandeurs électriques. De ce fait, et dans le cas de l'exemple d'un bras d'onduleur (Figure 1-11), le point du milieu est soumis à de forte variations de potentiel dv/dt conduisant à la circulation d'un courant de mode commun [13][14] non souhaité vers la masse (les chemins de propagation de ce courant sont indiqués par des flèches rouges dans la Figure 1-11b. La valeur de ce courant dépend de la valeur du dv/dt [14] ainsi que des valeurs des capacités parasites apparaissant par le report de la puce *low side* (drain en face arrière de la puce) et de la broche de connexion de la charge. La densification du courant et la miniaturisation des puces et de leur connexion est donc un facteur important pour réduire ces capacités parasites et ainsi avoir une moindre pollution EMI et un allègement du filtre associé.

#### 1.2.2 Solutions hybrides existantes

Les modes de défaillances de la technologie hybride 2D décrits dans le paragraphe précédent sont liés principalement au type d'interconnexion filaire par les fils de câblage imposant une limitation électrique. Une deuxième limitation est aussi due au refroidissement par la seule face arrière des puces dans le module 2D. De ce fait, cette technologie ne permet pas d'obtenir des modules de puissance avec une densité de puissance élevée et des performances électromagnétiques suffisantes pour la montée en puissance et en fréquence. Un autre désavantage de ces modules est qu'ils n'intègrent pas, de manière la plus rapprochée à la puce, le *driver*. Ces derniers devant donc être placés à l'extérieur du module et connectés par câblage conduisant à des perturbations supplémentaires sur la commande

Pour faire face aux limitations de la technologie de conception 2D, les efforts des chercheurs et industriels se sont concentrés pour développer des techniques et des solutions d'assemblage des puces de puissance sur substrat permettant de réduire, supprimer ou remplacer les fils de câblage par d'autres types d'interconnexion (pistes métalliques, bumps...) moins résistifs et moins inductifs, assurant également une plus grande compacité du module. Nous distinguons deux types de technologie : la technologie *Press Pack* et les technologies d'assemblage 3D.

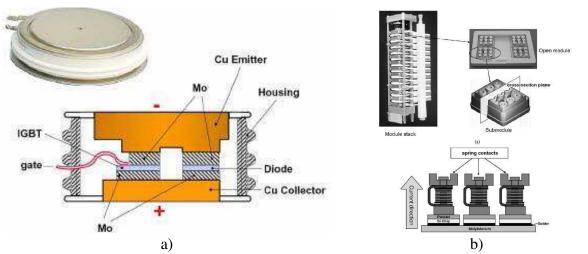

#### 1.2.2.1 Technologie Press Pack

La technologie *Press Pack* développée par Fuji, Toshiba et ABB n'utilise pas les fils de câblage (sauf pour la commande), elle est basée sur une interconnexion par pression exercée entre la métallisation des puces et des flasques en cuivre nickelés à l'intérieur du boitier (Figure 1-12a). Des pièces intermédiaires en molybdène réduisent les contraintes thermomécaniques sur les métallisations des puces. Cette technique est utilisée à l'origine pour l'encapsulation des composants en wafer tels que les diodes, thyristors et les GTOs fort courant pour des applications qui mettent en jeu des très fortes puissances (systèmes de traction, HVDC...). La Figure 1-12b montre une variante où la mise en pression des puces est réalisée individuellement par un ressort, des rondelles souples et une pièce de centrage sur une face de la puce. L'autre face peut être mise en contact par pression (comme sur le boîtier Fuji) ou par brasure (boitier ABB). Bien que plus complexe mécaniquement au niveau de l'assemblage, cette technique semble permettre une mise en pression plus homogène sur chaque puce.

Chapitre 1: L'amélioration de la fiabilité et des performances électriques des convertisseurs par l'intégration

Figure 1-12 : a) boitier *Press Pack* b) *stack* IGBT *press-pack* 100kV - 1500A (photographie ABB)

Le désavantage de cette technologie vient de l'absence d'isolement du boîtier et de son coût de fabrication élevé à cause de la complexité de l'assemblage ainsi que du possible endommagement par écrouissage des plages de métallisation Al aux niveaux des puces par la pression exercée sur elles. Ceci peut expliquer la non-généralisation de cette technologie sur des modules contenant plusieurs puces.

#### 1.2.2.2 Evolution vers les technologies d'intégration hybride 3D

Plusieurs technologies d'intégration hybride 3D ont été développées et continuent à se développer pour augmenter les performances électriques et thermiques des modules de faible et moyenne puissance. Bien que peu de ces technologies soient commercialisées nous citons les principales d'entre elles dans ce paragraphe.

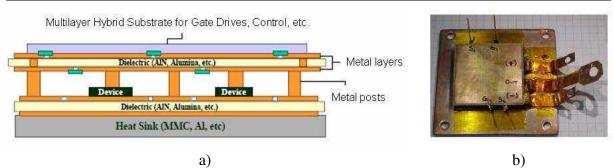

#### a) Technologie Metal-Posts Interconnected Parallel Plates (MPIPPs)

Cette technologie est basée sur l'insertion de poteaux en cuivre qui jouent le même rôle assuré par les fils de câblage en technologie 2D (Figure 1-13a), les contacts puces/poteaux sont réalisés en utilisant des brasures [8][15] ce qui suppose une préparation des métallisations. Les poteaux doivent être de longueur suffisante pour éviter tout risque de claquage entre la puce et le substrat métallique de connexion en face avant. La Figure 1-13b montre un module 3D utilisant cette technologie. Chacun des poteaux utilisés dans cette technologie présente une inductance parasite d'une valeur de 1,2 nH [15][16] contre une valeur comprise entre 6nH et 16nH [8] pour un fil de connexion.

Chapitre 1: L'amélioration de la fiabilité et des performances électriques des convertisseurs par l'intégration

Figure 1-13 : Module de puissance MPIPPs a) vue schématique en coupe, b) prototype d'assemblage réalisé [8]

La diminution de la valeur de l'inductance parasite de l'interconnexion va permettre une réduction significative des surtensions générées par les interrupteurs de puissance au blocage. Cette technologie présente un deuxième avantage thermique grâce à la dissipation de la chaleur à travers les poteaux vers la face avant du module, ce qui permet une évacuation de la chaleur par les deux faces du module [17]. Toutefois, l'évacuation principale de la chaleur se fait au niveau de la face arrière des puces en contact avec le substrat relié thermiquement au refroidisseur. Cet assemblage implique un excellent alignement dans le plan horizontal de l'ensemble des poteaux entre les puces et le substrat en face avant lors du brasage. Le montage "tout rigide" des pièces de connexion est un des points faibles de cette technologie. Une solution peut être de remplacer le substrat rigide en face avant par un PCB Flex ou du polyimide métallisé, aux dépens d'une bien moindre capacité d'évacuation de la chaleur par la face avant. Cette variante est présentée dans le paragraphe suivant.

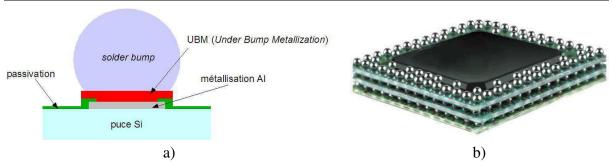

#### b) Technologie Solder Bumps Interconnect

Cette technologie repose sur l'introduction de billes de type *solder bumps* déposées par refusion sur la métallisation des puces de puissance (généralement en aluminium suivie d'une finition Ti/Cr Or) (Figure 1-14) [18]. Les grandes dimensions de ces billes (de quelques dizaines de microns à quelques centaines de microns) fabriquées en alliage d'étain, argent ou en or donnent des propriétés électriques en termes d'inductance parasite et résistance beaucoup plus faibles que celles des fils de câblage [19][20][21]. Ceci a même ouvert la voie à cette technologie pour son utilisation en microélectronique pour améliorer la taille des assemblages et leurs performances électriques et thermiques. Les bonnes propriétés des billes brasées ont poussé des fabricants de semi-conducteurs comme *International Rectifier* [22] et *Fairchild* [23] à développer des composants de puissance en se basant sur la technologie *solder bump*.

Figure 1-14 : Assemblage micro-électronique 3D avec la connectique s*older bumps* a) vue schématique en coupe [24], b) puce contenant des billes de brasure [25]

Figure 1-15 : Module de puissance *Flip chip on Flex* utilisant la technologie *solder bump* [26] a) vue schématique en coupe, b) prototype d'assemblage réalisé

La Figure 1-15 montre un module de puissance de la technologie *Flip chip* on flex utilisant la technologie d'interconnexion *solder bumps*. Un substrat flexible en face avant du module est utilisé pour compenser la différence entre les épaisseurs des puces reportées. Il est constitué d'un film de polyimide sur lequel deux feuillards de cuivre sont laminés (50µm d'épaisseur) [15]. L'injection d'un polymère (*underfill*) dans l'interface puces/*solder bumps* permet la passivation et surtout l'amélioration de la connectique en réduisant les contraintes au niveau du joint de brasure par la redistribution de celles-ci entre la puce, le substrat, l'*underfill* et le joint de brasure [27][28][29]. L'utilisation d'un substrat métallisé souple en polyimide ne permet pas un bon transfert de chaleur par la face avant et le report à un dissipateur ne présenterait pas d'intérêt. Ce substrat étant davantage réservé au report des drivers, condensateurs de découplage et circuits de protection.

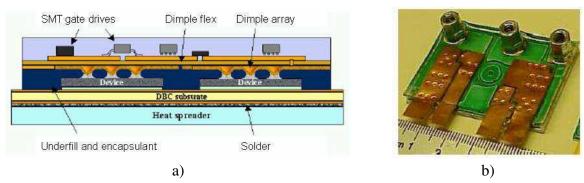

#### c) Technologie Dimple Array Interconnect (DAI)

La technologie *Dimple Array Interconnect* repose sur une interconnexion de type *solder bumps* au niveau de la face avant des puces de puissance et sur des déformations localisées, sorte d'excroissance se rapprochant d'une forme de *bump*, d'une plaque en cuivre flexible dont l'épaisseur est comprise entre 50µm et 400µm. Les déformations de la plaque flexible permettent de former les *bumps* et réaliser le contact par la refusion d'une brasure locale (Figure 1-16) [15][19]. Comme dans la technologie *Solder Bump Interconnect*, un *underfill* est déposé entre le substrat DBC et la plaque flexible pour améliorer la fiabilité de celle-ci et éviter les contaminants.

Figure 1-16 : Module de puissance utilisant la technologie *dimple array interconnnect* a) vue schématique en coupe, b) prototype d'assemblage réalisé [8]

Figure 1-17 : Assemblage réalisé par une technologie *Flex* et *Sintering* (frittage).

Les performances électriques de cette technologie sont comparables avec celles de la technologie *solder bump* [19]. Cependant, cette technologie n'a pas encore atteint un stade de maturité industrielle à cause de la difficulté de la réalisation des déformations localisées. Une variante ou plus précisément une alternative consiste à réaliser le contact du substrat souple sur les puces par frittage. La Figure 1-17 montre un assemblage réalisé de cette manière : un film souple en polyimide ou polyamide métallisé est ensuite reporté sur les puces par un process *Sintering* (frittage d'une pâte d'Ag à 250°C) réalisant simultanément le contact en surface de puce et en face arrière sur un DBC [30].

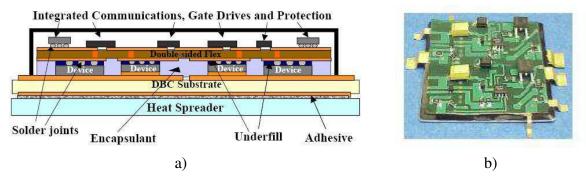

#### d) Technologie Embedded Power (EP)

La technologie *Embedded Power* (Figure 1-18) développée par le CPES est basée sur la réalisation par un processus d'électrodéposition d'une couche en cuivre supplémentaire sur les métallisations préparées en face avant des puces semi-conductrices de puissance. Cette épaisseur peut atteindre 125µm [31]. Cette technique permet la suppression de la brasure qui représente une zone de fragilité dans les modules de puissance [32]. Elle repose aussi sur l'enfouissement des puces dans une céramique ou plus simplement dans une couche de PCB, jouant un rôle de support mécanique pour les métallisations électro-déposées et assure l'isolation électrique.

Figure 1-18 : Module de puissance utilisant la technologie *Embedded Power* a) vue schématique en coupe, b) prototype d'assemblage réalisé [40]

Cette technologie permet une diminution considérable de l'inductance parasite par rapport à la technologie planaire 2D basée sur l'utilisation des fils de connexion [31]. D'un point de vue thermique, la dissipation de la chaleur dans les puces de puissance se fait essentiellement par la face arrière du module et partiellement par la face avant du module grâce aux métallisations en cuivre électro-déposées [33]. Néanmoins cette technologie souffre de problème de fiabilité dus à la différence des CTE entre les différents matériaux utilisés.

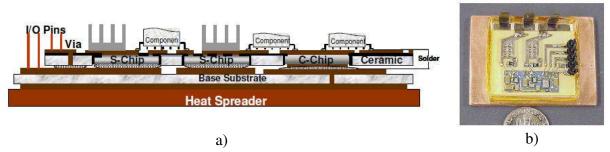

#### e) Technologie *Power Overlay* (POL)

La technologie *Power Overlay* a été développée par le conglomérat américain *General Electric* [34], les puces sont brasées en face arrière sur un substrat DBC et les interconnexions en face avant des puces sont réalisées à travers des vias monolithiques en cuivre distribuées sur les métallisations préparées des puces. Le processus technologique consiste à laminer un film souple de diélectrique sur la face avant des puces dans le module, des ouvertures sur ce film sont ensuite réalisées en utilisant un laser, puis une couche en cuivre est déposée par électrodéposition sur l'ensemble et enfin celle-ci est gravée pour réaliser les contacts souhaités. La Figure 1-19 montre une vue de principe en coupe d'un module de puissance utilisant cette technologie et un prototype récemment réalisé par Siemens et Continental VDO (procédé SIPLIT<sup>TM</sup>).

Figure 1-19 : Module de puissance utilisant la technologie *Power Overlay* a) vue schématique en coupe, b) prototype d'assemblage réalisé [15]

Cette technologie présente des performances électriques et thermiques similaires à celle de la technologie *Embedded Power* [34]. Technologiquement, elle présente aussi les mêmes problèmes de fiabilité dus à la différence des CTE entre matériaux utilisés.

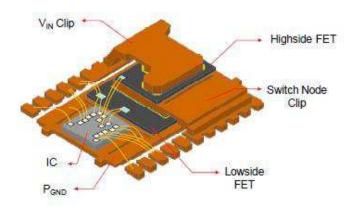

#### f) La technologie 3D NextFET<sup>TM</sup>:

Cette technologie quasi-3D développée par Texas Instrument consiste à empiler les deux MOSFET (*low-side et high-side*) d'un bras d'onduleur à travers une couche métallique (Figure 1-20). Le module contient aussi la puce de contrôle. Cette technique permet de réduire l'inductance parasite et la résistance d'interconnexion entre les deux MOSFET et travailler avec des fréquences élevées (jusqu'à 2MHz). Cette architecture est bien adaptée aux structures *Synchronous Buck* Mosfet (dévolteur) où la puce *low side* est le siège d'un courant efficace bien plus élevé que la puce *high side* et donc de surface supérieure. Cette propriété autorise un astucieux *stacking* des deux puces avec un débord inférieur périphérique utile pour l'accès à la grille et à la source kelvin de la puce *low side*.

Figure 1-20 : Module Stack in NextFET<sup>TM</sup> Power Bloc [35]

#### 1.2.2.3 Autres technologie 3D en cours de développement

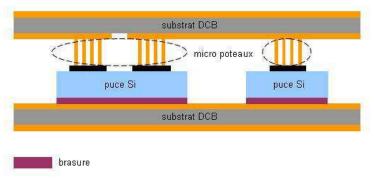

#### a) Technologie d'interconnexions par des micro-poteaux

Cette technique développée et étudiée dans le cadre d'un projet ANR 3DPHI [24], est basée sur des interconnexions de type brasure sur la face arrière des puces, et des micropoteaux pour réaliser les interconnexions en face avant des puces. En effet, cette technique utilise le principe des assemblages par couches planaires utilisés en micro-électronique, l'idée est d'ajouter une partie de l'interconnexion des puces semi-conductrices sur les puces ellesmêmes, sous la forme de micro poteaux, voire de nano poteaux (Figure 1-21).

Figure 1-21 : Assemblage 3D d'un convertisseur de puissance avec la technologie micropoteaux [24]

Les micro-poteaux ont des dimensions en section carrée de 50µm x 50µm jusqu'à 300µm x 300µm, de hauteur maximale 75µm, et distantes de 50µm à 300µm [24]. Ces faibles dimensions ont pour but de minimiser la résistance électrique, l'inductance parasite et la résistance thermique des connectiques. Toutefois, cette technique ne permet pas de réaliser des interconnexions entre les deux substrats DBC pour fermer la maille de commutation.

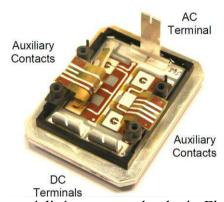

#### b) Technologie Power Chip-on-Chip (PCoC)

Le concept *Power-Chip-On-Chip* 3D ayant fait l'objet d'études au G2ELab à Grenoble a été proposé et détaillé dans le cadre de la thèse d'E. Vagnon [36]. Le principe de cette technique est basé sur l'empilement des puces de puissance les unes sur les autres (Figure 1-22) en se basant sur des contacts de type *Press Pack*. Cet empilement des électrodes et des puces selon le principe PCoC n'utilise pas les fils de *bonding*, ce qui va permettre de réduire au minimum les effets parasites des interconnexions au niveau de la maille de commutation, ceci conduira à un gain important en termes de comportements électriques et électromagnétiques [36].

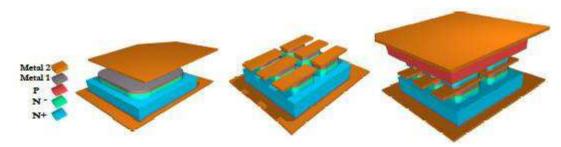

Dans ce cadre, une généralisation de ce concept 3D a été proposée [1]. Plusieurs puces sont co-intégrées et séparées par un diélectrique sur le même substrat silicium avec une électrode commune en face arrière, cette généralisation nécessite un investissement important de développement des étapes technologiques de réalisation et des techniques spécifiques de terminaisons verticales de jonction des puces de puissance adaptées au concept PCoC [37][38]. Le principe de cette co-intégration est mécaniquement très complexe en termes de montage et de maintien des performances dans le temps. Ce principe est illustré pour le cas de diodes (Figure 1-23) [39].

Figure 1-22 : Bras d'onduleur selon le concept *Power Chip-on-Chip* (PCoC) [36]

Figure 1-23 : Vue schématique du package *Power Chip-on-Chip* à l'aide des terminaisons en tension verticales - exemple d'une diode, de six diodes à cathode commune et d'un redresseur polyphasé à six bras [1].

Figure 1-24 : Application du concept DRIM *Cooler* pour des diodes PIN dans un assemblage *Power Chip-on-Chip* [1]

D'un point de vue thermique, ce concept (avec les techniques d'intégration hybride 3D disponibles actuellement) ne permet pas un refroidissement de toutes les puces empilées, seules les puces en contact avec le substrat dans le module sont refroidies par leur face arrière à travers le substrat. D'autres travaux ont porté sur le développement d'une approche de refroidissement originale appelée DRIM *Cooler* [1][38] adaptée au concept PCoC introduisant des fluides isolants (Figure 1-24) mais qui ne permet pas de conclure sur l'intérêt et la pertinence de cette approche, là encore pour des questions de faisabilité technologique.

#### 1.2.2.4 Synthèse des solutions hybrides 3D

Les solutions technologiques hybrides 3D permettent d'avoir un gain électrique et électromagnétique significatif par rapport à la technologie 2D. Néanmoins, elles présentent des niveaux de complexité de réalisation différents en fonction de la technologie employée. Seules les deux technologies 2D et *Press Pack* sont commercialisées à grande échelle à l'heure actuelle. Les technologies *Embedded Power* et *Power Overlay* sont en phase de préindustrialisation pour la faible puissance et les applications automobiles hybrides. Les autres technologies 3D en cours de développement (PCoC et micro-poteaux) sont prometteuses mais nécessitent davantage un travail de développement surtout sur le plan technologique pour atteindre un bon niveau de maturité. Un bon compromis entre la complexité de l'assemblage, ses performances électriques et thermiques, sa fiabilité et son coût est recherché.

Les différentes solutions hybrides 3D sont adaptées à une gamme de puissance qui varie en fonction de la technologie utilisée, le Tableau 1- 1 résume les gammes de puissances adaptées pour chaque technologie.

| Technologie hybride                          | Tension    | Courant | Commercialisation |

|----------------------------------------------|------------|---------|-------------------|

| Technologie 2D                               | <6kV       | <1,2kA  | Oui               |

| Technologie Press Pack                       | 6,5kV      | >1kA    | Oui               |

| Technologie MPIPPs                           | 400V       | 10A     | Non               |

| Technologie Solder bumps (Flip chip on flex) | <1kV, <50A | 6,5A    | Non               |

| Technologie DAI                              |            |         | Non               |

| Technologie EP                               |            |         | Non               |

| Technologie POL                              |            |         | Non               |

| Technologie des micro-poteaux                | ND         |         | Non               |

| Technologie PCoC                             |            |         | Non               |

Tableau 1-1: Gamme de puissance adaptée pour chaque technologie [40]

Le choix de la technologie dépend de l'application et de la gamme de puissance visée. La technologie 2D reste la plus adaptée aux applications de très fortes puissances telles que la traction ferroviaire suivies par la technologie *Press Pack* et la technologie POL, les autres technologies sont plutôt adaptées aux applications des moyennes et faibles puissances.

En complément de ces évolutions technologiques hybrides, nous allons voir dans la section suivante que pour les faibles et moyennes puissances, une seconde grande famille d'intégration intervient dans la même perspective d'amélioration des performances électriques des convertisseurs :"l'intégration monolithique".

#### 1.3 L'intégration monolithique

Ce mode d'intégration a connu également une forte évolution en parallèle avec l'intégration hybride. Le concept de cette intégration repose sur le principe d'intégrer dans le même cristal (par exemple le silicium) plusieurs composant et/ou fonctions, de favoriser ou limiter les couplages de manière à créer les fonctions souhaitées.

# 1.3.1 Historique et domaines d'applications de l'intégration monolithique

Jusqu'à la fin des années 80, l'intégration monolithique faisait uniquement référence à la fabrication des composants de puissance discrets [41]. Les efforts de recherche portaient uniquement sur l'amélioration des performances électriques et l'augmentation des puissances commutées par unité de surface. Cette famille d'intégration est basée sur la compréhension des mécanismes physiques mis en jeu, ainsi que sur la reproductibilité des processus technologiques de fabrication et, bien entendu, sur la mise au point de nouveaux composants. Ces composants traduisent la volonté d'obtenir des dispositifs plus rapides, plus fiables et qui présentent des bonnes caractéristiques électriques statiques pour couvrir un large domaine applicatif (capacité en courant, tension blocable, faible chute de tension à l'état passant et faible courant de fuite à l'état bloqué).

Les progrès technologiques dans le domaine de la microélectronique des faibles signaux et de traitement de l'information VLSI (Very Large Scale Integration) [42][43] ont fortement

participé à l'évolution de l'intégration monolithique des composants de puissance. Et ce, malgré que les performances à optimiser pour les composants de puissance soient différentes de celles des circuits intégrés. La technologie MOS dans les dispositifs de puissance représente un point de convergence avec le domaine du traitement de signal.

Le mode d'intégration monolithique couvre le domaine des faibles et moyennes puissances. Il existe deux approches d'intégration monolithiques possibles et elles sont en grande partie fonction de l'application visée. La première approche concerne les deux technologies "Smart *power*" [41][44][45] (aussi désignée Smart MOS) et HVIC (*High Voltage Integrated Circuit*) [41][46]. Ces deux technologies sont bien adaptées au domaine des faibles puissances. La seconde approche est plutôt destinée et adaptée aux domaines des applications moyennes puissances, elle est connue sous le nom "Intégration monolithique fonctionnelle".

## 1.3.2 Intégration "Smart Power" et HVIC :

Ces deux technologies donnent le même produit final qui est un circuit intégré de puissance, la différence entre elles est liée essentiellement au mode de conduction de l'élément de puissance utilisé et aux gammes de courant et de tension traitées :

- En "Smart-Power", la conduction électrique dans le composant de puissance (généralement seul) est verticale (VDMOS...) ou latérale (LDMOS...).

- Pour les HVIC, la conduction électrique dans les composants de puissance est forcément latérale (très souvent de type LDMOS).

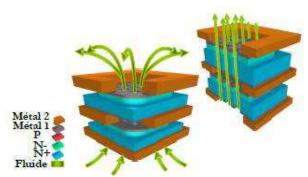

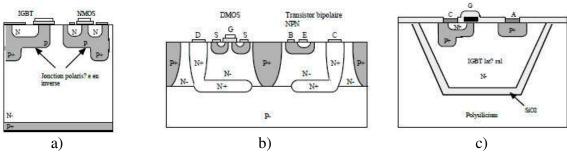

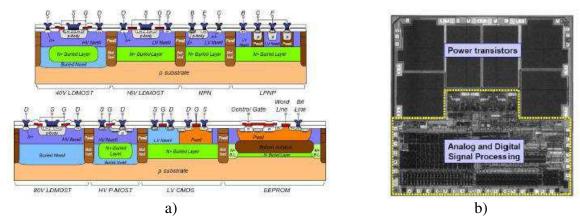

Les HVICs sont des circuits multi-sorties conçus pour supporter des tensions qui peuvent aller jusqu'à quelques centaines de volts mais qui présentent des faibles densités de courant limitées par la conduction latérale des puces. Au contraire, les composants "Smart Power" peuvent transiter des courants de plusieurs ampères avec des tensions blocables nettement inférieures à celles de la technologie HVIC. Pour ces deux modes d'intégration, la partie logique et analogique du circuit est réalisée en technologie NMOS, CMOS ou bipolaire et elle doit être parfaitement isolée du composant de puissance qui subit des fortes contraintes en terme de courant, tension, di/dt et dv/dt. Dans ce contexte, on distingue trois principaux modes d'isolation: l'auto-isolation par écrantage électrostatique (auto-blindage), l'isolation par jonction et l'isolation par un diélectrique (Figure 1-25). Deux exemples de circuits intégrés de type Smart Power et un exemple de circuit de type HVIC sont illustrés dans la Figure 1-26

Figure 1-25 : Techniques d'isolation de composants de puissance verticaux et latéraux [47], a) auto-isolation, b) isolation par jonction, c) isolation par diélectrique

Figure 1-26 : a) *Smart Power* : exemples d'intégration de différents types de composants (CMOS, DMOS, bipolaire) dans un même substrat [41], b) HVIC : exemple d'intégration de transistors de puissance et de circuits de traitement du signal analogique et numérique sur la même puce [48]

# 1.3.3 Intégration monolithique fonctionnelle

#### 1.3.3.1 Définition

L'intégration fonctionnelle est le deuxième mode d'intégration monolithique. Elle est basée sur un agencement particulier des couches semi-conductrices du composant de puissance pour obtenir une nouvelle fonctionnalité au sein d'un dispositif de puissance sans atteindre la complexité des fonctions obtenues avec les composants de type "Smart Power" et HVIC. Les dispositifs réalisés en intégration fonctionnelle permettent d'obtenir des fonctionnalités spécifiques de contrôle et de protection en associant plusieurs éléments de base. Il s'agit dans ce mode d'intégration de maîtriser et d'exploiter les interactions électriques entre les différentes régions du cristal de manière à faire émerger de nouvelles fonctionnalités qu'il serait plus complexe ou bien de moindre performance à réaliser en discret. Le transistor bipolaire permet de bien appréhender la notion d'interactions entre les différentes couches semi-conductrices puisque l'effet 'transistor bipolaire' ne peut intervenir que s'il existe une région commune (la région de la base du transistor bipolaire) entre deux jonctions et non par l'assemblage de diodes tête bêche. De la même façon, la structure du thyristor n'est pas réalisée à partir de l'association discrète de deux transistors bipolaires mais par leur imbrication monolithique. Cette structure, constituée de quatre couches P/N/P/N est

considérée comme l'un des tous premiers exemples de l'intégration fonctionnelle. Une étape supplémentaire a été franchie par le développement des principales phases de conception du triac en s'appuyant sur une analyse physique très fine du comportement de la structure. La structure du triac peut être considérée, au premier ordre, comme l'imbrication de deux thyristors.

### 1.3.3.2 Evolutions de l'intégration fonctionnelle

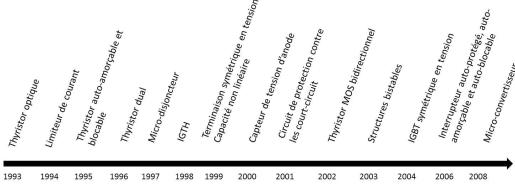

Le prolongement des travaux de recherche a donné naissance à tout un ensemble de composants et structures de puissance dont les fonctionnalités électriques sont basées sur des associations bipolaire/bipolaire. Ces associations consistent à intégrer de manière monolithique et de façon astucieuse des diodes de redressement, des diodes Zener, des résistances et des thyristors réalisés sur des structures verticales dont les caractéristiques physiques et géométriques déterminent une application spécifique ASD (Application Specific Discrete). Les applications visent principalement des fonctions de commande d'interrupteur et de sa protection. L'introduction des technologies MOS dans le domaine de l'intégration fonctionnelle a offert un degré de liberté supplémentaire en permettant la combinaison des effets MOS et des interactions de type bipolaire. Ainsi, de nombreuses solutions d'associations de type MOS/Bipolaire ont permis de créer de nouveaux dispositifs de puissance tel que l'IGBT, le MCT (MOS Controlled Thyristor) et le MGT (MOS Gated Thyristor). Le MGT étant une structure de type IGBT optimisée afin de fonctionner en mode thyristor se bloquant par le passage par zéro de la tension. Il existe maintenant un certain nombre de composants discrets de type MGT en quatre ou cinq couches tels que: DGMOT (Dual Gate Mos Thyristor), le DG-BRT, DG EST ou encore le MGCT. D'autres travaux de recherches menés récemment au LAAS basés sur ce mode d'intégration visant à l'intégration d'IGBT bidirectionnels par une intégration double-face de substrat silicium [49][50]. Notons également l'émergence d'une intégration plus poussée des fonctions de protection contre certains phénomènes provoquant un dysfonctionnement du circuit tel que : court-circuit, forte énergie dissipée, décharges électrostatiques (ESD) fort di/dt et dv/dt. La Figure 1-27 montre l'évolution de composants/fonctions au fil du temps au LAAS.

Figure 1-27 : Evolution de l'intégration fonctionnelle au LAAS

## 1.3.3.3 Les progrès technologiques au profit de l'intégration fonctionnelle

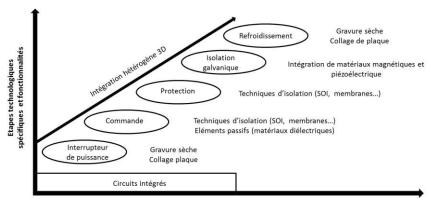

Cette augmentation de la complexité des fonctions de puissance a nécessité un développement parallèle des étapes technologiques de réalisation. Ce développement conjoint entre les fonctions intégrables et les étapes technologiques spécifiques, est illustré sur la Figure 1-28.

Figure 1-28 : Evolution des fonctions intégrables liées au développement des étapes technologiques spécifiques

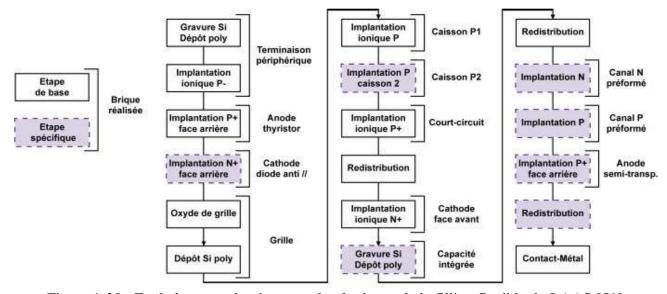

La réalisation technologique de ces nouvelles fonctions de puissance intégrées est aujourd'hui basée sur des filières technologiques dites "flexibles" comme celle développée dans la plateforme technologique du LAAS (Figure 1-29).

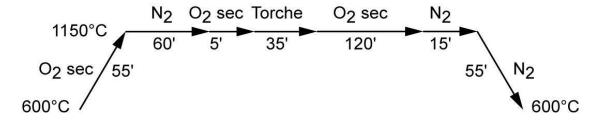

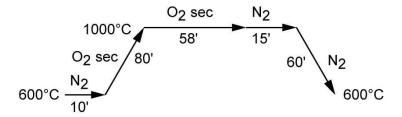

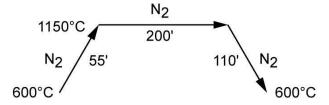

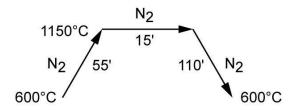

Figure 1-29 : Enchainement des étapes technologiques de la filière flexible du LAAS [51]

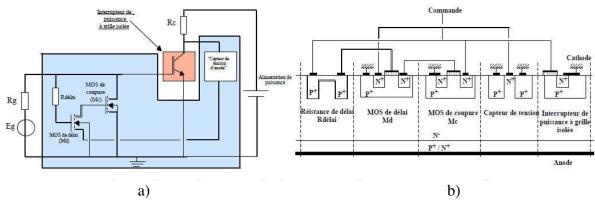

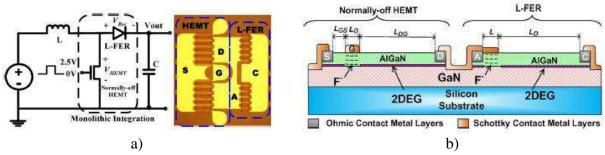

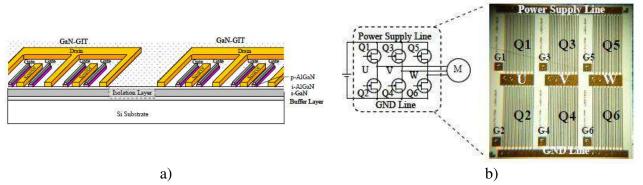

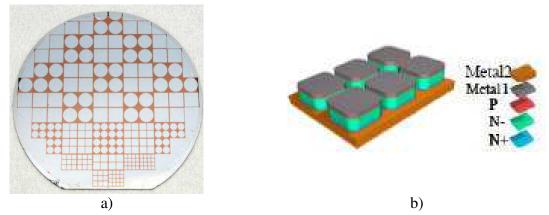

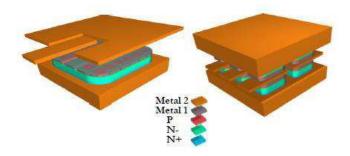

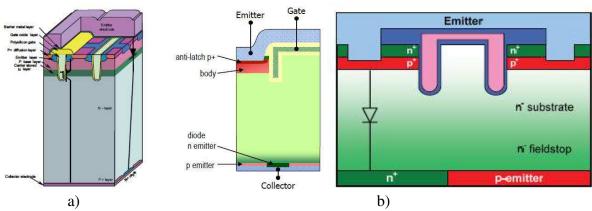

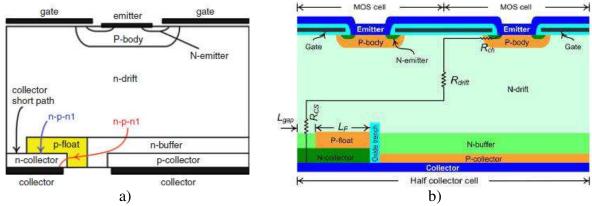

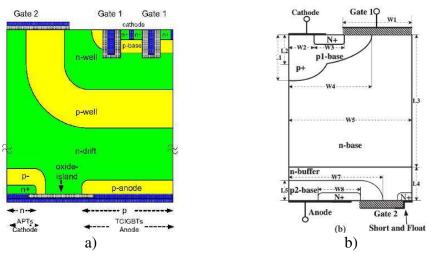

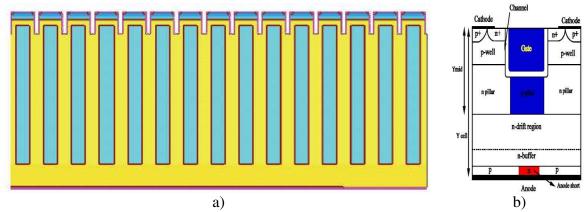

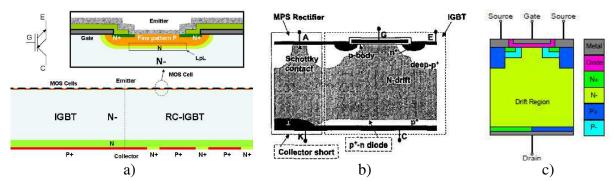

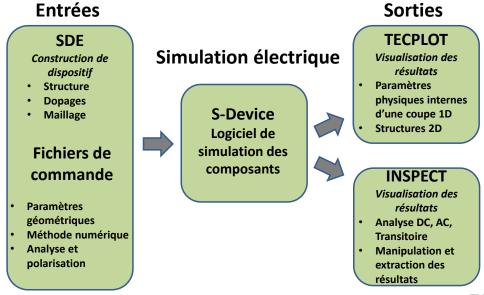

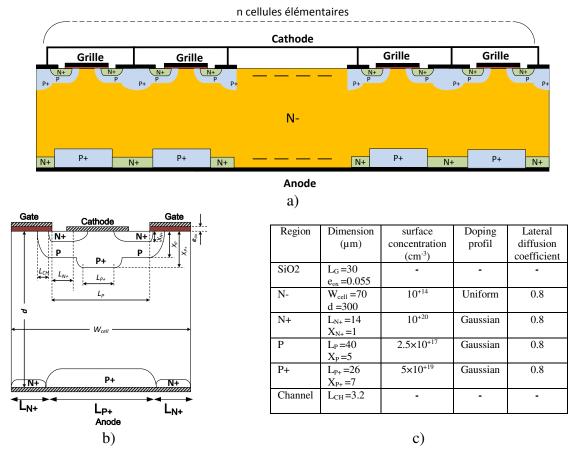

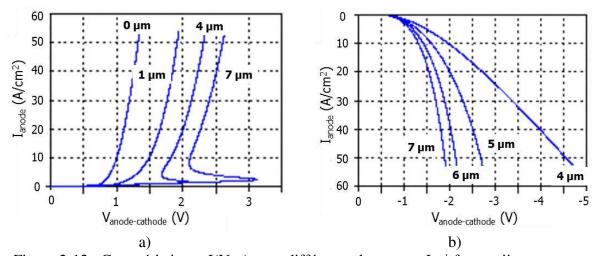

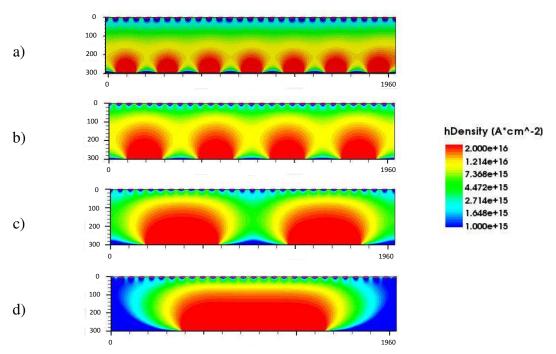

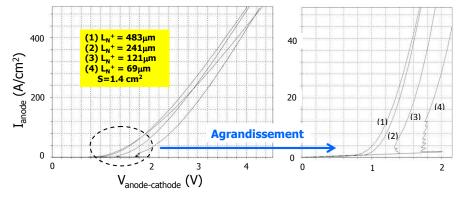

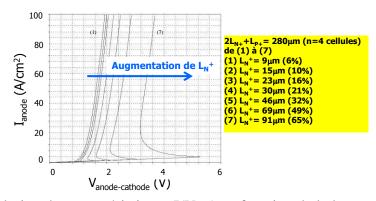

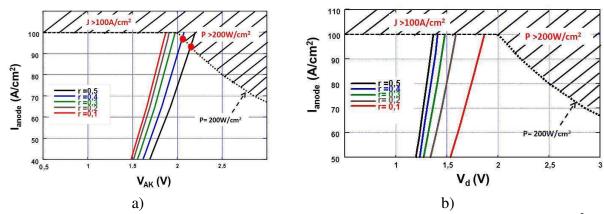

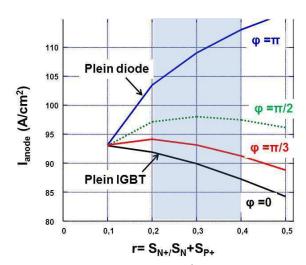

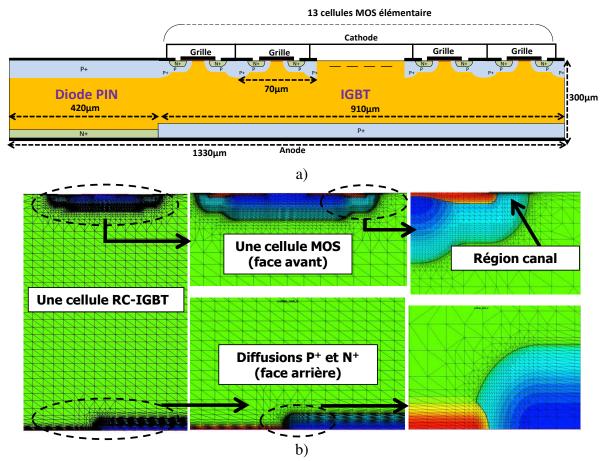

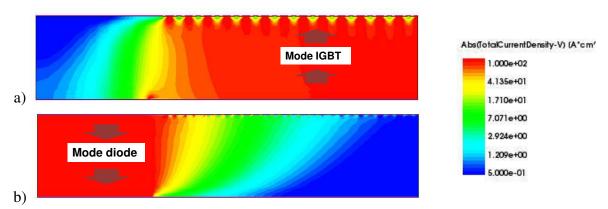

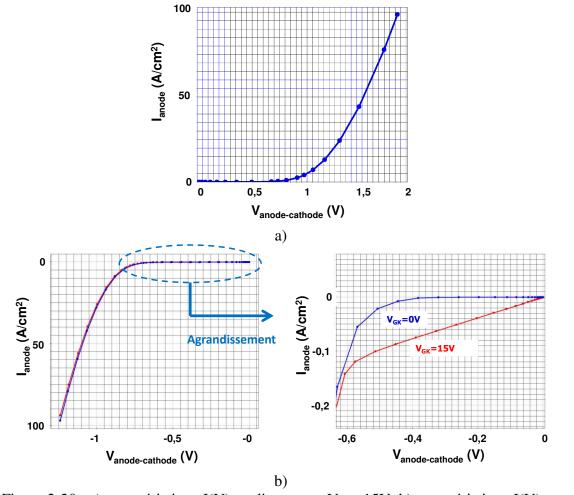

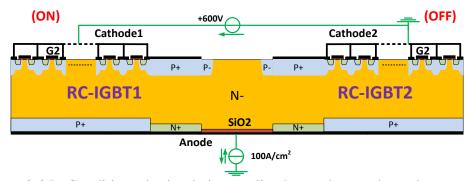

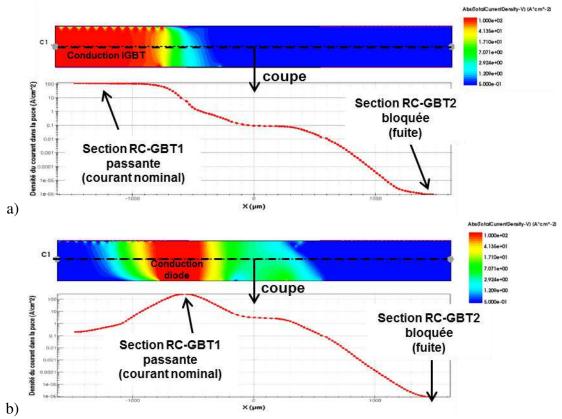

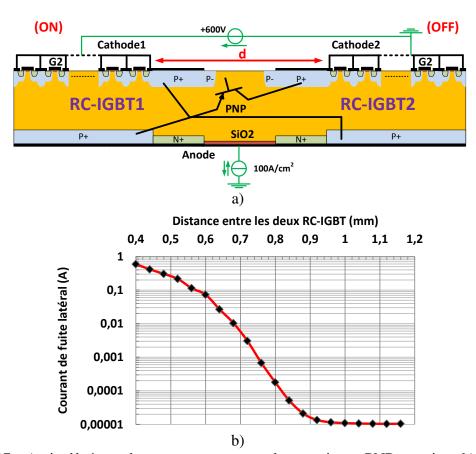

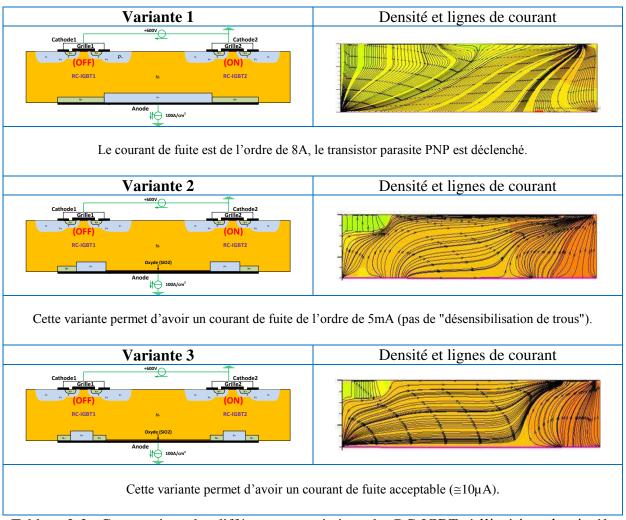

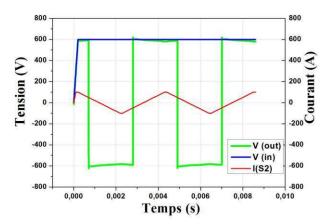

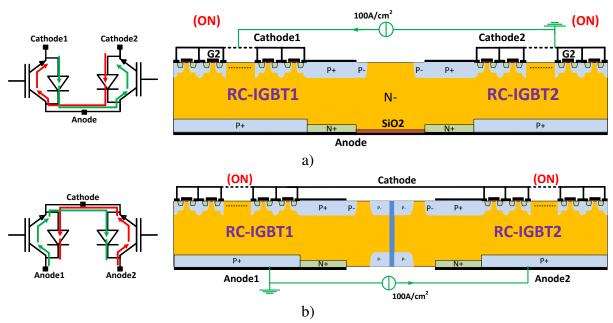

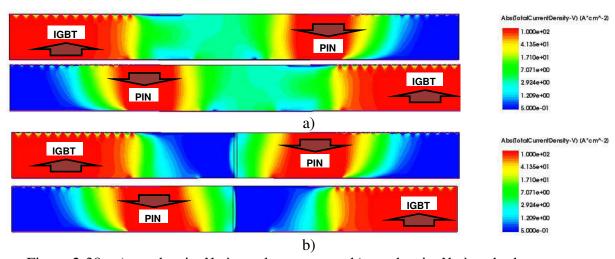

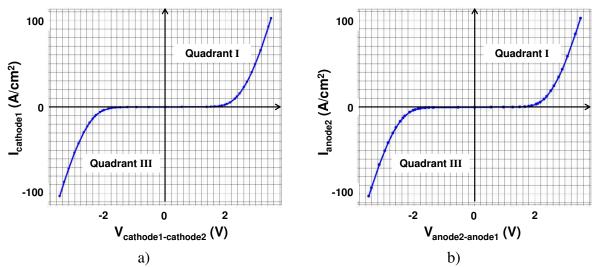

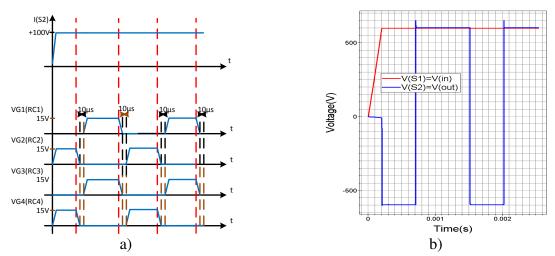

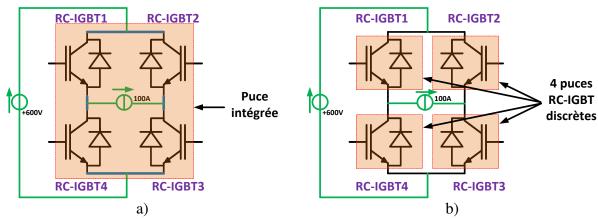

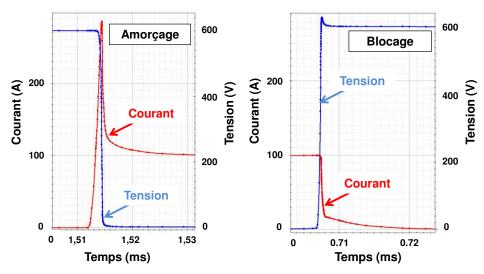

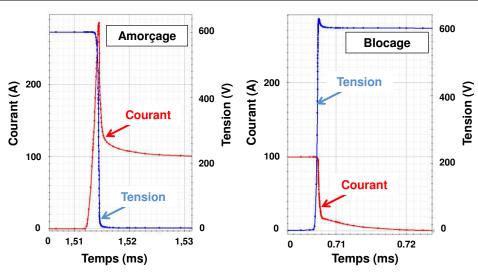

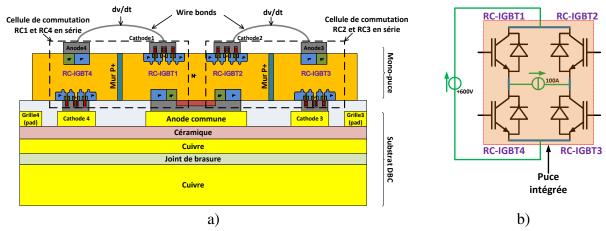

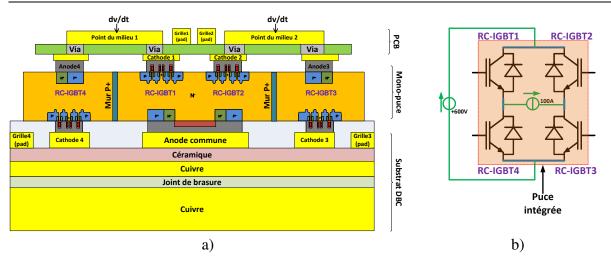

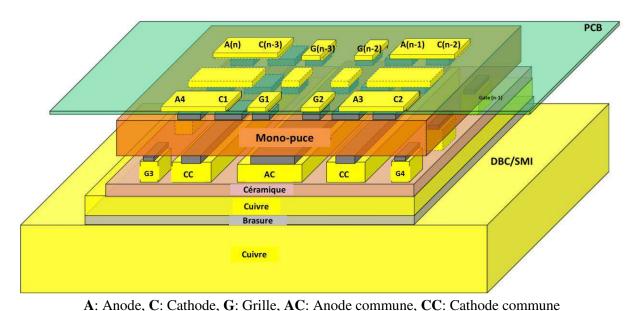

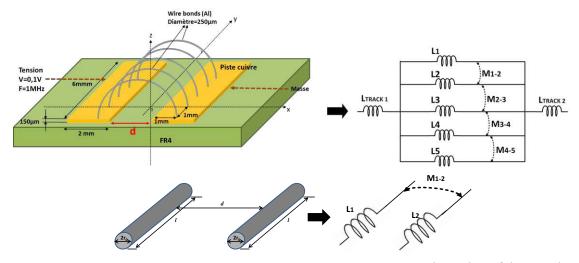

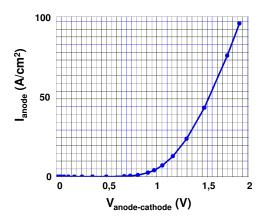

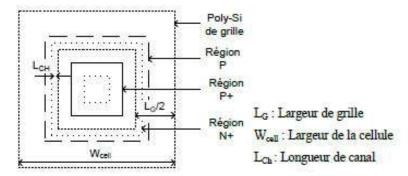

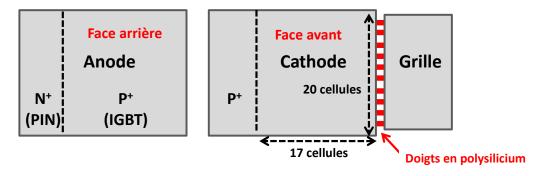

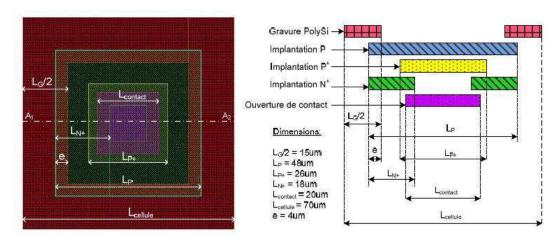

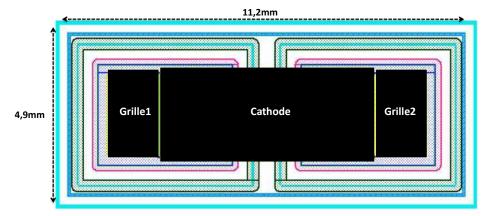

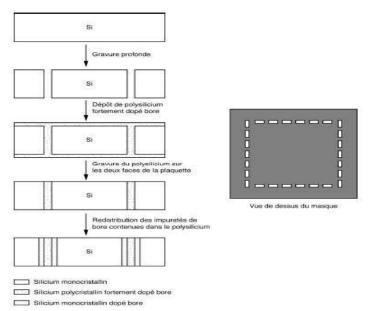

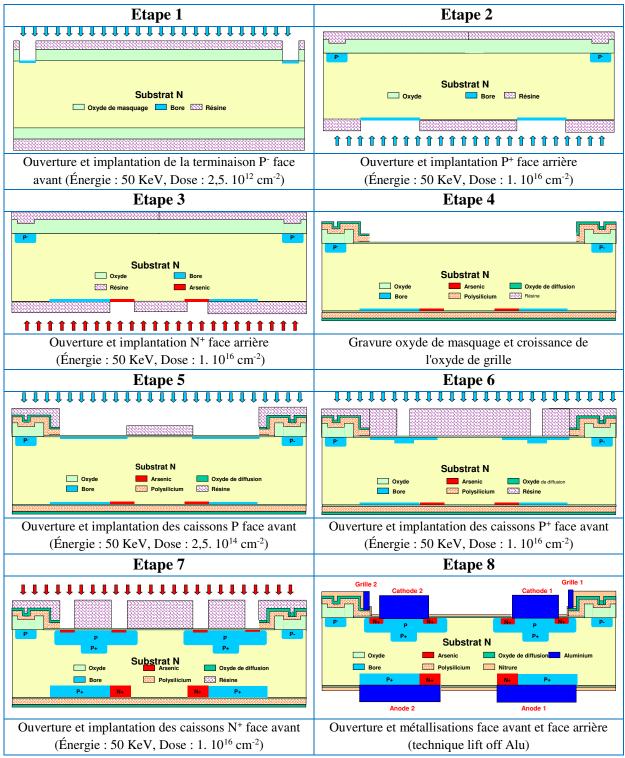

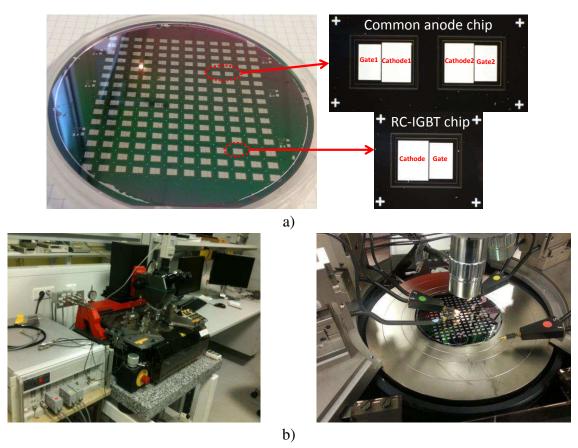

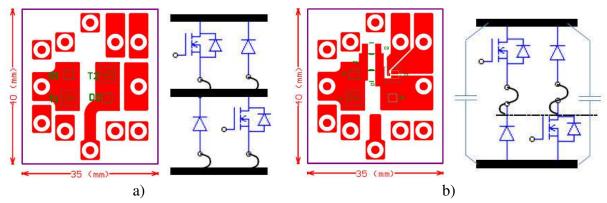

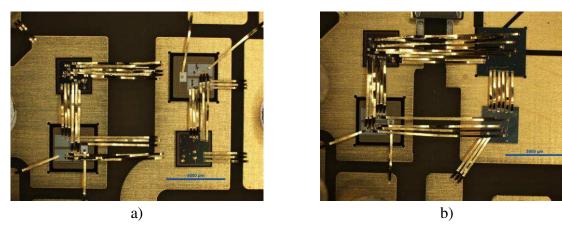

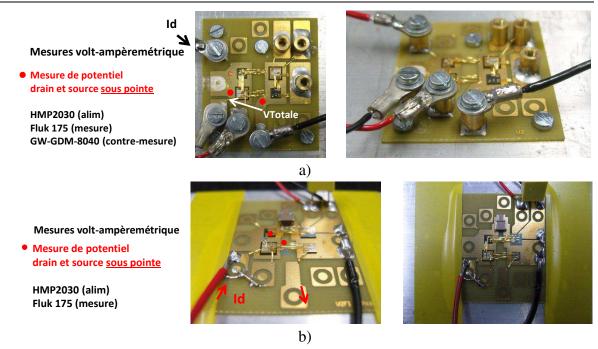

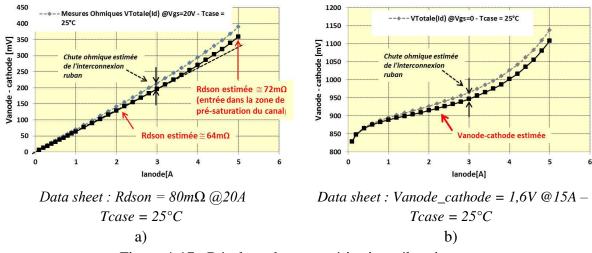

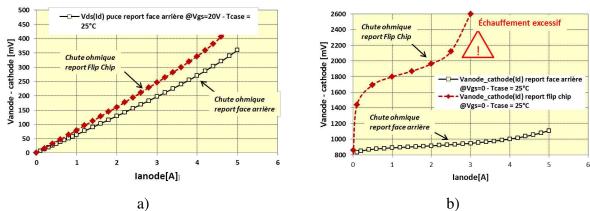

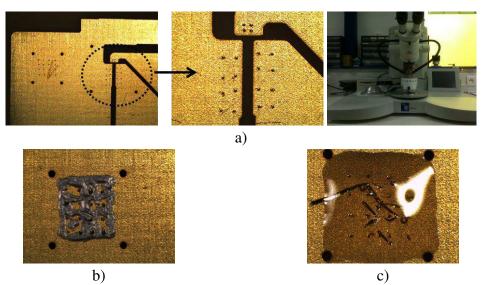

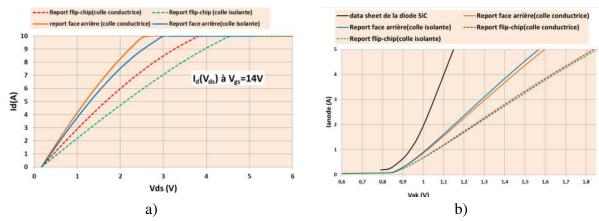

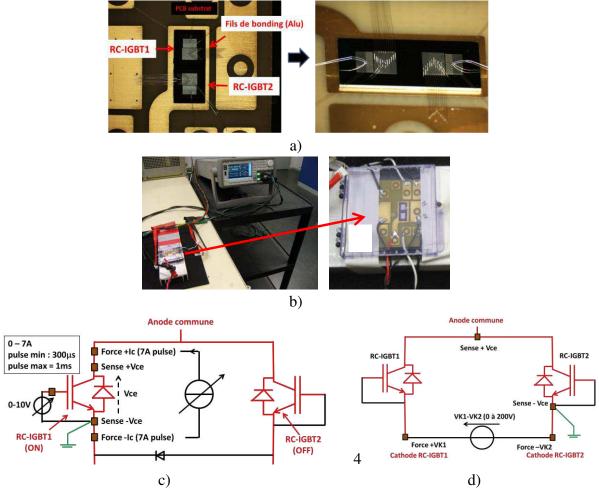

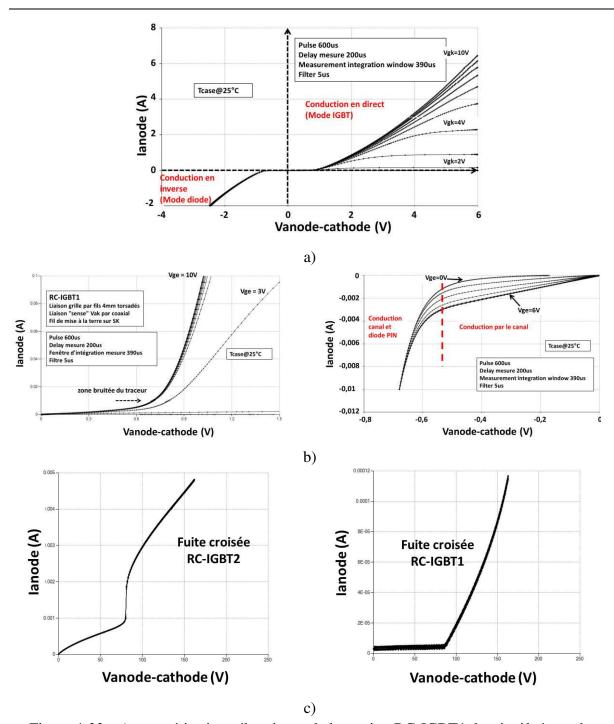

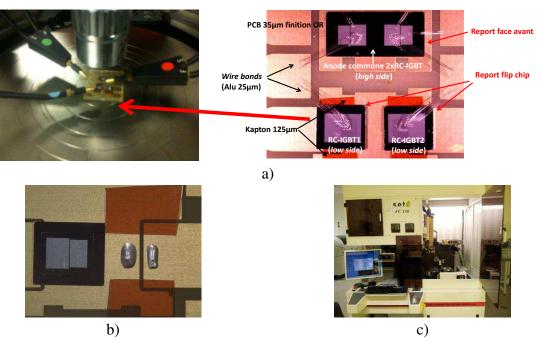

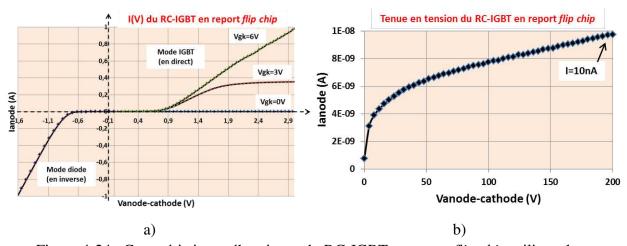

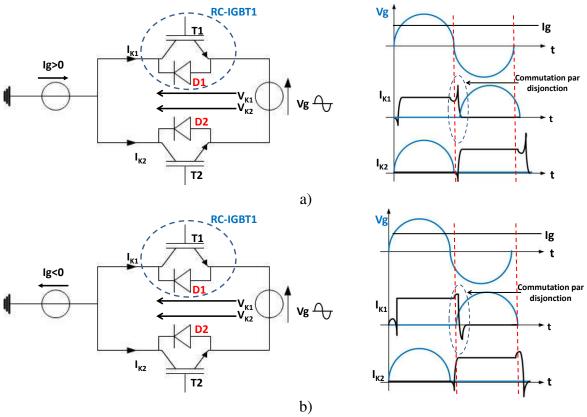

Les briques technologiques qui constituent cette filière permettent en plus de la réalisation technologique de composants conventionnels de puissance (MOS, IGBT, Thyristors...) la réalisation de fonctions plus complexes telle que l'isolation par mur P<sup>+</sup> traversant [52]. La Figure 1-30 montre un exemple de type de structure intégrée par la voie de l'intégration fonctionnelle correspondant au schéma électrique de détection et de protection contre les court-circuits.