# Évaluation des effets des neutrons atmosphériques sur l'électronique embarqué en avionique et recherche de solutions de durcissement

Sébastien Renard

#### ▶ To cite this version:

Sébastien Renard. Évaluation des effets des neutrons atmosphériques sur l'électronique embarqué en avionique et recherche de solutions de durcissement. Autre. Université Sciences et Technologies - Bordeaux I, 2013. Français. NNT: 2013BOR15253. tel-01015741

### HAL Id: tel-01015741 https://theses.hal.science/tel-01015741

Submitted on 27 Jun 2014

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

## **THÈSE**

#### PRÉSENTÉE A

## L'UNIVERSITÉ BORDEAUX 1

ÉCOLE DOCTORALE DES SCIENCES PHYSIQUE ET DE L'INGENIEUR

#### Par **Sébastien Renard**

POUR OBTENIR LE GRADE DE

**DOCTEUR**

SPÉCIALITÉ: **ELECTRONIQUE**

Evaluation des effets des neutrons atmosphériques sur l'électronique embarquée en avionique et recherche de solutions de durcissement.

Directeur de recherche: Pascal FOUILLAT

Soutenue le : 9 décembre 2013

#### Devant la commission d'examen formée de :

| M. PORTAL, Jean-Michel | Professeur à l'Université d'Aix-Marseille         | Rapporteur            |

|------------------------|---------------------------------------------------|-----------------------|

|                        |                                                   |                       |

| M. BONNAUD, Olivier    | Professeur à l'Université de Rennes 1             | Rapporteur            |

| M. FOUILLAT, Pascal    | Professeur à l'Université de Bordeaux 1           | Directeur de thèse    |

| M. POUGET, Vincent     | Chercheur CNRS à l'Université de Montpellier 2    | Co-Directeur de thèse |

| M. LEWIS, Dean         | Professeur à l'Université de Bordeaux 1           | Invité                |

| M. DARRACO, Frédéric   | Maître de conférence à l'Université de Bordeaux 1 | Invité                |

À Lætitia

#### **REMERCIEMENTS**

Je souhaite remercier l'ensemble de l'équipe de recherche, et particulièrement son responsable : Dean Lewis, qui m'a accueillie au sein du laboratoire IMS.

Monsieur Pascal Fouillat qui a su garder un œil attentif à mes problématiques malgré un emploi du temps complexe. Je remercie également Monsieur Vincent Pouget, sans qui ma thèse n'aurait jamais atteint ce point d'aboutissement. Monsieur Frédéric Darracq qui a su me faire partager sa vision de la science et me donner du recul sur mes recherches.

Je prends le temps de remercier les différents partenaires qui ont pu intervenir lors de ce projet : Didier Regis, Guillaume Hubert, Christian Chatry et Dominique Bellin.

Mes remerciements vont aussi à mes proches, tout particulièrement à Laetitia, la femme qui m'a supporté pendant ces quatre années. Je remercie mes parents et mon frère qui se sont montrés conciliants et ont su m'encourager dans les moments de doutes.

Un grand merci à ceux qui ont partagé mon quotidien dans la salle laser du laboratoire : Camille Larue, Emeric Farraud, Issam El Moukhtari, Kai Shao, Adèle Morisset, Nogayé M'Bayé et Mehdi Rebai. Mais je remercie également ceux sans qui le café n'aurait pas eu le même goût : Raphaël Roder, François Le Henaff, Nicolas Martin, Mathieu Vallet, Mickaël Gilles et Jérôme Le Gall.

Mes derniers remerciements, mais pas les moindres, iront à ceux qui m'ont permis de m'essayer au métier d'enseignant : Bertrand Le Gal, Yannick Bornat, Yannick Deshayes, Dominique Dallet et Francis Rodes.

Enfin, si vous lisez cette thèse et que j'ai oublié de vous remercier, sachez que j'en suis désolé.

## Table des matières

|                | TION GENERALE<br>TRE 1 : ETAT DE L'ART DES ENVIRONNEMENTS RADIATIFS, D |    |

|----------------|------------------------------------------------------------------------|----|

| ET DES MOY     | YENS DE TEST                                                           | 14 |

| I.1. INT       | TRODUCTION                                                             | 15 |

| I.2. L'I       | ENVIRONNEMENT RADIATIF                                                 | 15 |

| <i>I.2.1</i> . | L'environnement spatial                                                |    |

| I.2.2.         | L'environnement terrestre                                              |    |

| I.2.2.1        | Profondeur atmosphérique et rigidité magnétique                        | 19 |

| I.2.2.2        | Spectres des neutrons atmosphériques                                   | 20 |

| I.3. L'I       | INTERACTION NEUTRON-MATIERE                                            | 24 |

| I.3.1.         | L'interaction Ion-Silicium                                             | 24 |

| I.3.1.1        | . Description du phénomène                                             | 24 |

| I.3.1.2        | Pouvoir d'arrêt et transfert d'énergie linéique                        | 25 |

| <i>I.3.2</i> . | L'interaction Neutron-Matière                                          | 26 |

| I.3.2.1        | . L'interaction Neutron-Silicium                                       | 26 |

| I.3.2.2        | L'interaction Neutron-Matière                                          | 27 |

| <i>I.3.3</i> . | L'interaction Proton-Matière                                           | 27 |

| I.4. LE        | S EFFETS A EVENEMENT SINGULIER (SEE)                                   | 28 |

| I.4.1.         | Les Phénomènes mis en œuvre                                            | 28 |

| I.4.1.1        | . La collection de charge                                              | 28 |

| I.4.1.2        | Notion de charge critique et modèle RPP                                | 29 |

| I.4.2.         | Les différents SEE                                                     |    |

| I.4.2.1        | . Les SEU, MBU et MCU                                                  | 31 |

| I.4.2.2        | Les SEFI                                                               | 32 |

| I.4.2.3        | Les SEL et SEB                                                         |    |

| I.5. LE        | S TESTS                                                                | 33 |

| I.5.1.         | La courbe de section efficace                                          |    |

| I.5.2.         | Les équipements de test                                                |    |

| I.5.2.1        | Les sites en altitude                                                  | 34 |

| I.5.2.2        | Les accélérateurs de particules                                        | 35 |

| I.5.2.3        | Les réacteurs à neutrons                                               | 36 |

| I.5.2.4        | Les faisceaux laser impulsionnel                                       |    |

| I.5.           | .2.4.1. L'interaction laser-silicium                                   |    |

| I.5.           | .2.4.2. Equivalence entre ion lourd et impulsion laser                 |    |

| I.5.           | 2.4.3. Avantages et inconvénients du test sous faisceau laser          | 41 |

| I.5.3.         | Les méthodes de test                                                   |    |

| I.5.3.1        |                                                                        |    |

| I.5.3.2        | 1                                                                      |    |

| I.5.3.3        | Calcul du SER                                                          | 43 |

| 154            | Les SDRAMs faces aux SEEs                                              | 44 |

| I.5.5. Les MRAMs faces aux SEEs                                                          | 46      |

|------------------------------------------------------------------------------------------|---------|

| I.5.6. Les processeurs faces aux SEEs                                                    | 48      |

| I.6. LES OUTILS DE SIMULATION                                                            | 53      |

| I.6.1. GEANT4                                                                            | 53      |

| I.6.2. SRIM                                                                              | 54      |

| I.6.3. OMERE                                                                             | 55      |

| I.6.4. L'injection de fautes                                                             |         |

| I.7. CONCLUSION                                                                          |         |

|                                                                                          |         |

| II. CHAPITRE 2 : DEVELOPPEMENT DES SYSTEMES ET DES METHODOLOGIES DE TI                   | EST. 57 |

| II.1. Introduction                                                                       | 58      |

| II.2. PRESENTATION DES COMPOSANTS A EVALUER                                              | 58      |

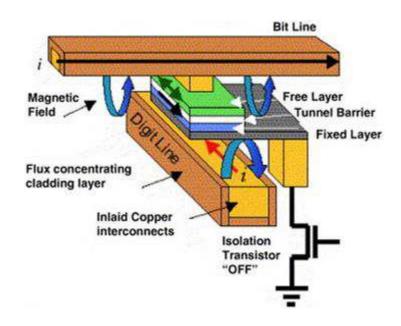

| II.2.1. La mémoire magnétique MRAM EV2A16A                                               | 58      |

| II.2.1.1. Rappel sur la technologie magnétique                                           | 58      |

| II.2.1.2. Caractéristiques techniques propre à la mémoire EV2A16A                        | 59      |

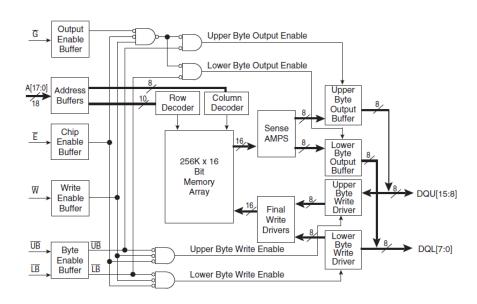

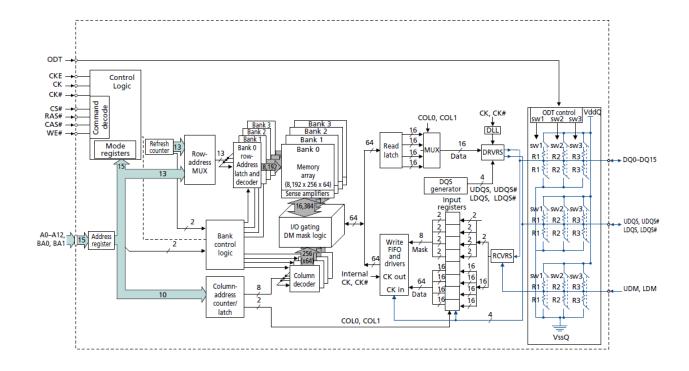

| II.2.2. La mémoire dynamique SDRAM MT47H32M16                                            | 60      |

| II.2.2.1. Caractéristiques techniques de la mémoire SDRAM                                | 60      |

| II.2.2.2. Usinage de la mémoire SDRAM                                                    | 61      |

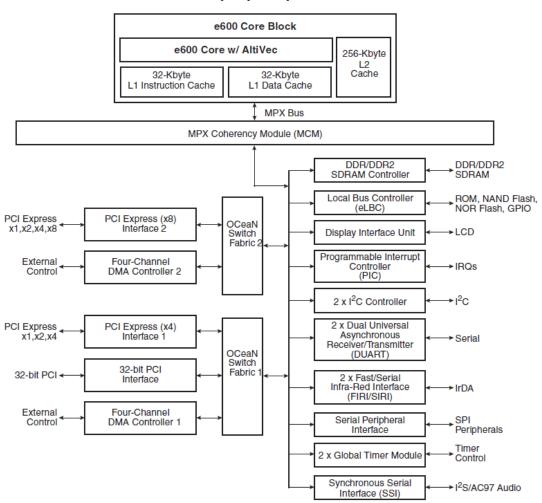

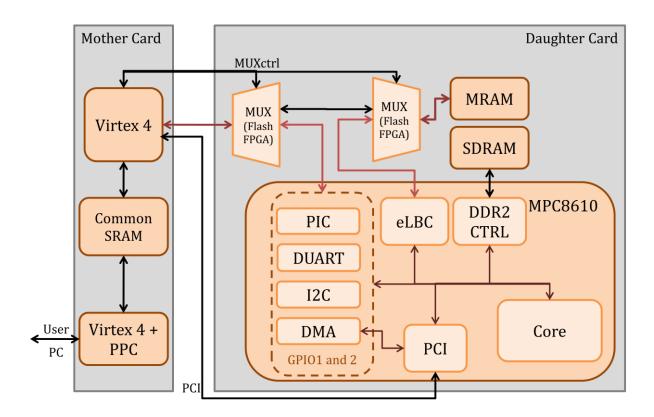

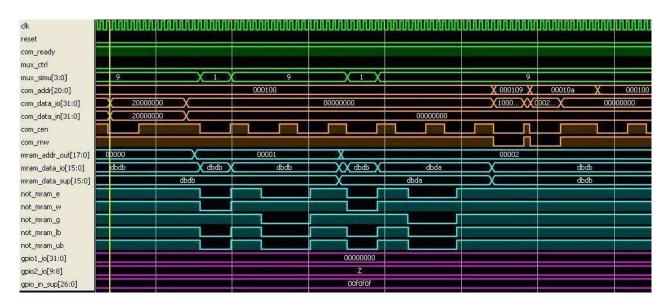

| II.2.3. Le PowerPC MPC8610                                                               | 63      |

| II.2.3.1. Blocs de contrôle de périphériques du MPC8610                                  | 63      |

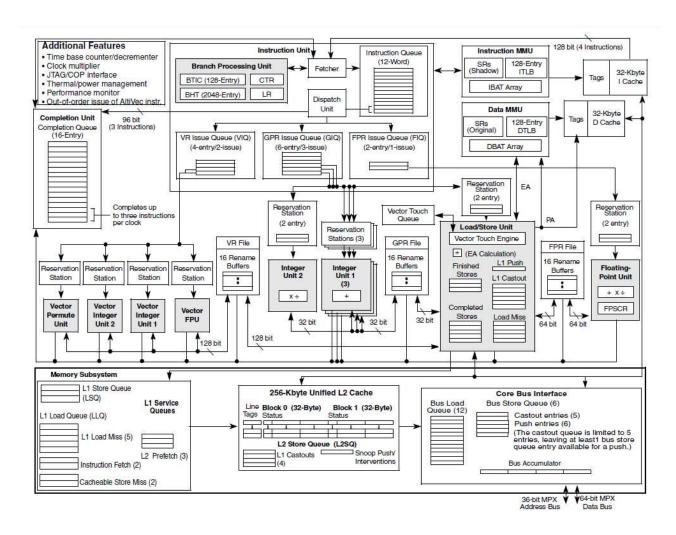

| II.2.3.2. Description du cœur du MPC8610                                                 | 64      |

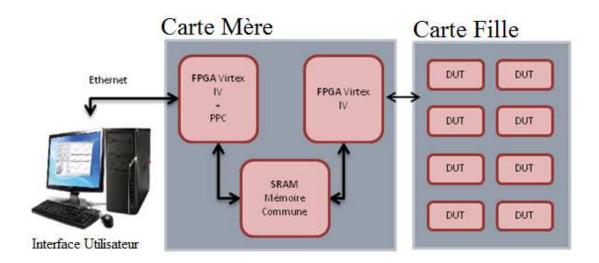

| II.3. LA PLATEFORME DE TEST                                                              | 66      |

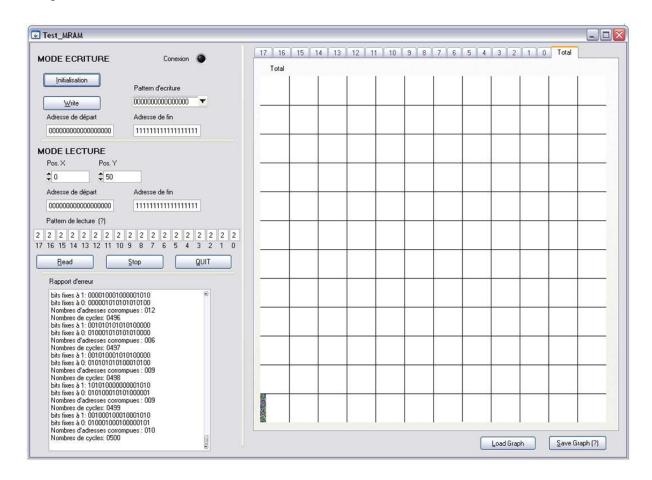

| II.3.1. L'interface utilisateur                                                          | 66      |

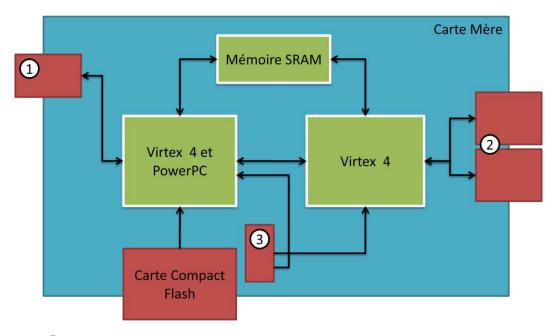

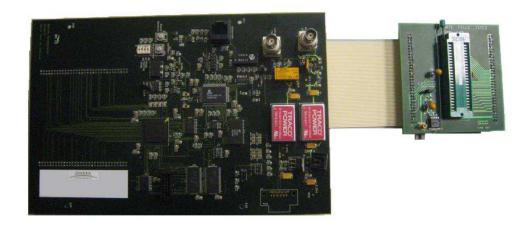

| II.3.2. La carte mère                                                                    | 68      |

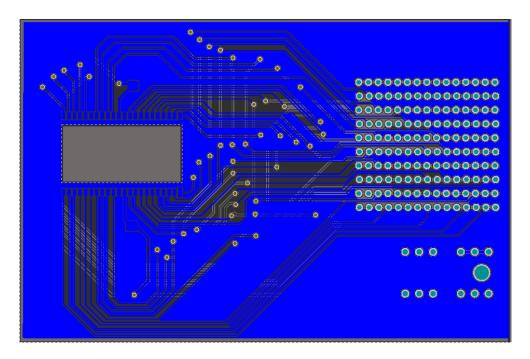

| II.3.3. Les cartes filles                                                                | 70      |

| II.3.3.1. Les cartes filles mémoires                                                     | 71      |

| II.3.3.2. La carte fille PowerPC                                                         | 71      |

| II.4. LES METHODES DE TEST                                                               | 73      |

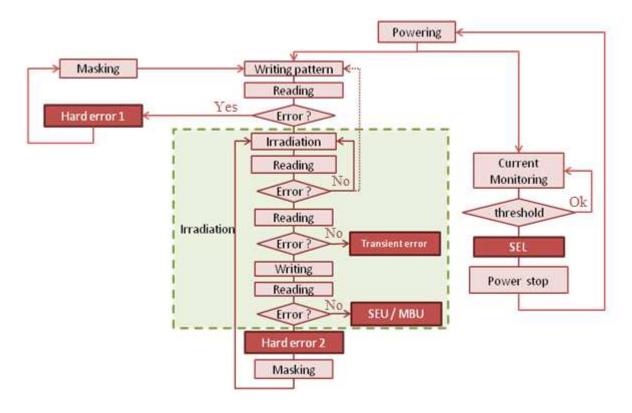

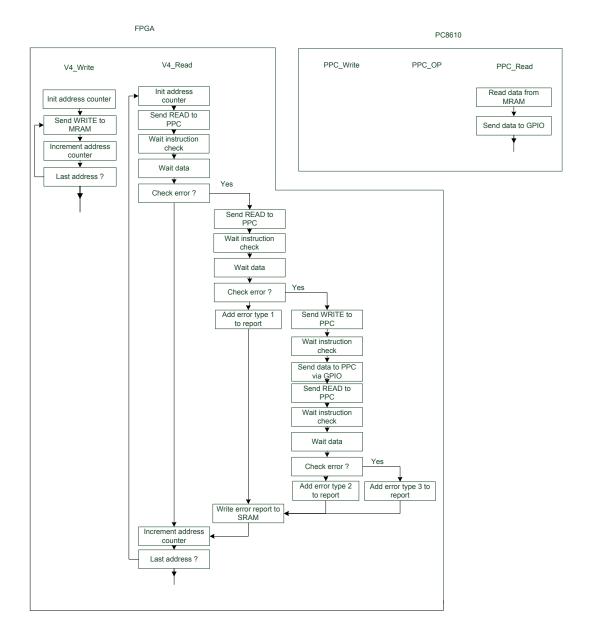

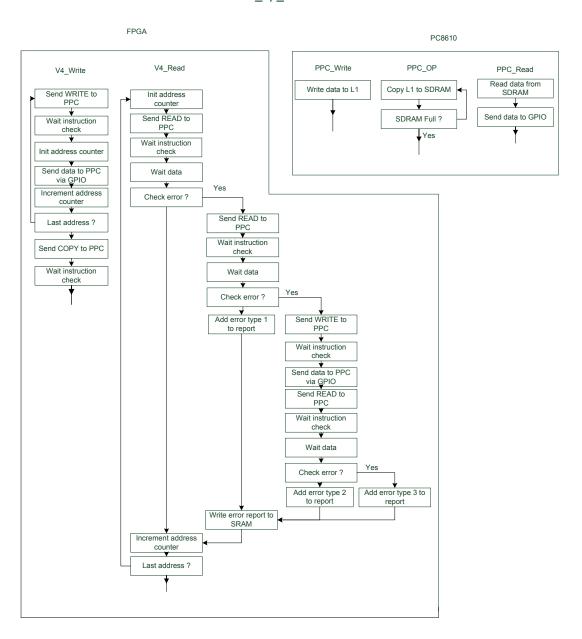

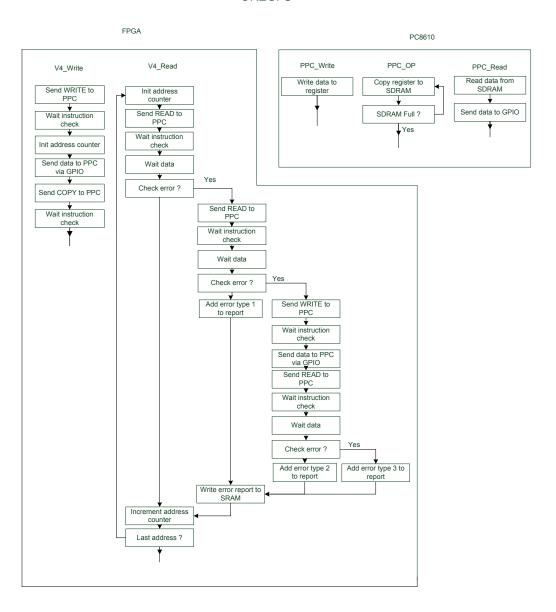

| II.4.1. Le programme de test des mémoires                                                |         |

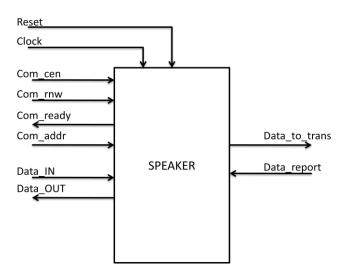

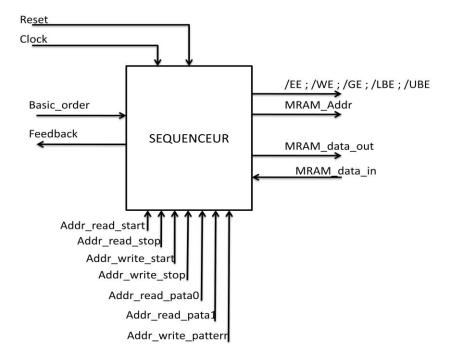

| II.4.1.1. Les entrées et sorties du FPGA communiquant avec la mémoire sous test          |         |

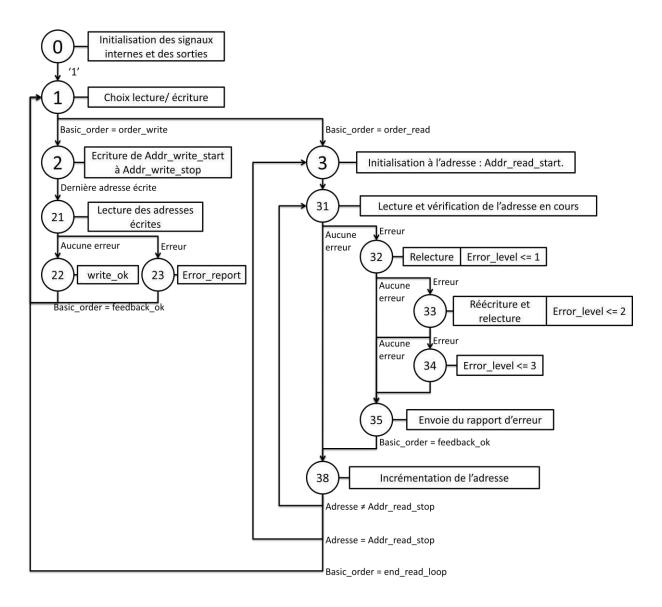

| II.4.1.2. Les protocoles de test des mémoires                                            |         |

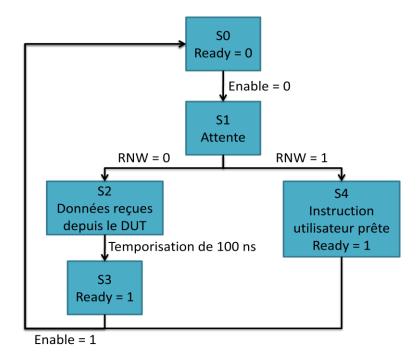

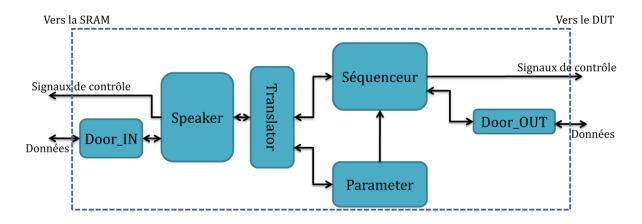

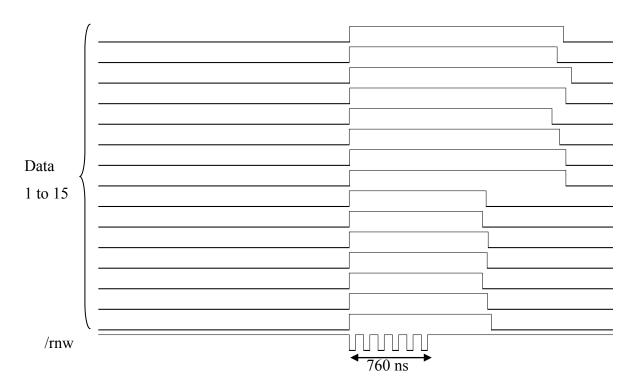

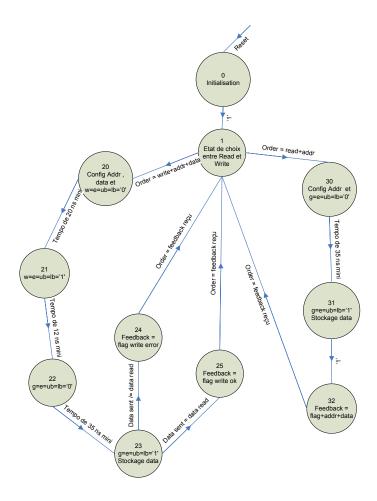

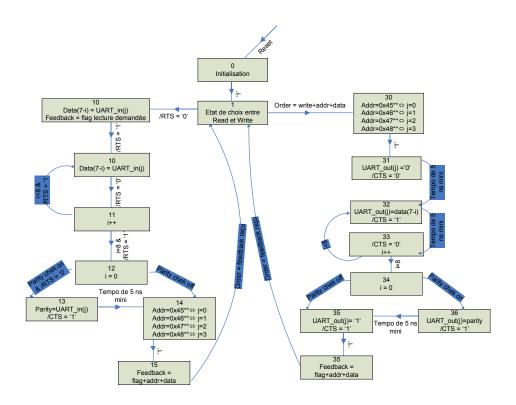

| II.4.1.3. Le module VHDL de pilotage de la MRAM                                          |         |

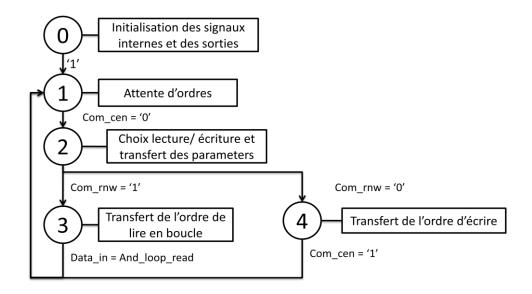

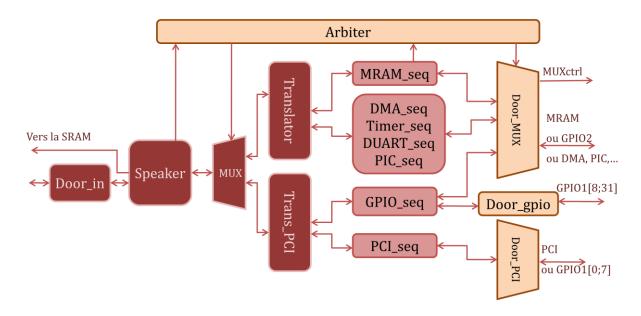

| II.4.1.3.1. Le sous-module Speaker                                                       | 76      |

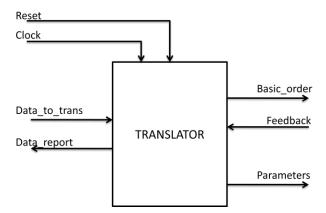

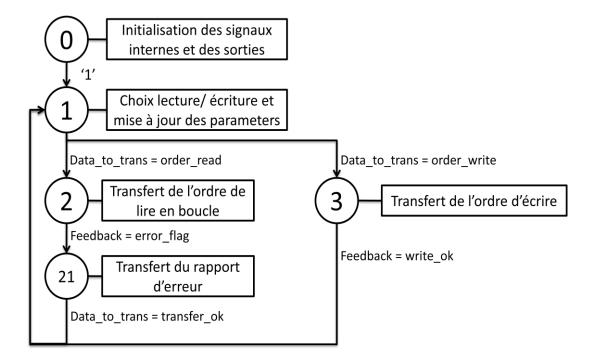

| II.4.1.3.2. Le sous-module Translator                                                    | 77      |

| II.4.1.3.3. Le sous-module Parameter                                                     | 78      |

| II.4.1.3.4. Le sous-module Séquenceur                                                    | 80      |

| II.4.1.3.5. Rapport de synthèse du programme de pilotage de la MRAM sur Virtex XC4VLX40  | 81      |

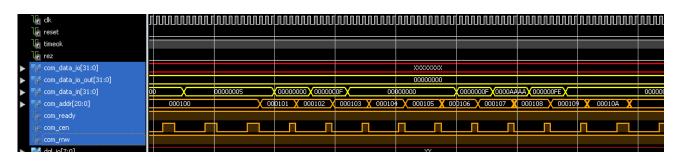

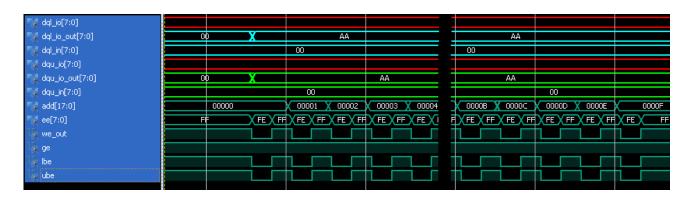

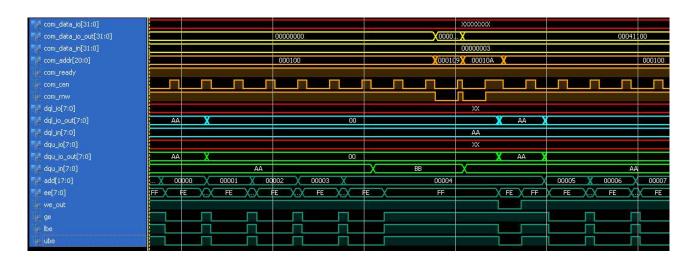

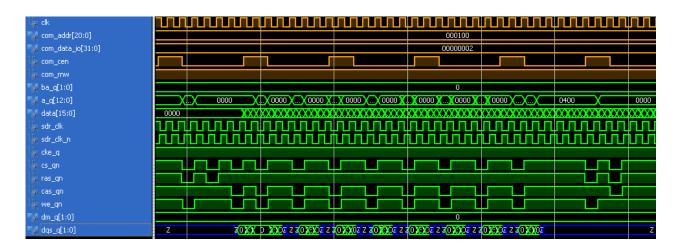

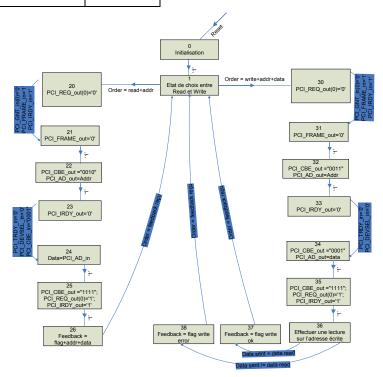

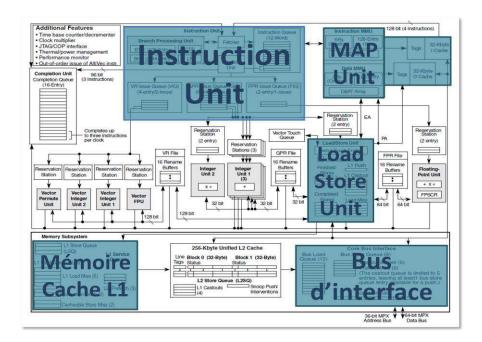

| II.4.1.4. Simulation du programme de pilotage de la MRAM                                 | 82      |

| II.4.1.5. Implémentation du module de test sur la carte mère Virtex 4                    | 84      |

| II.4.1.6. Module de pilotage de la SDRAM                                                 |         |

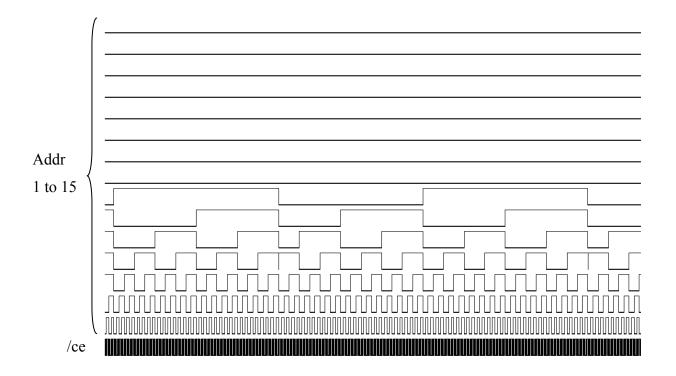

| II.4.1.6.1. Schéma Bloc du programme                                                     | 86      |

| II.4.1.6.2. Rapport de synthèse du programme de pilotage de la SDRAM sur Virtex XC4VLX40 |         |

| II.4.1.6.3. Simulation du programme de pilotage de la SDRAM                              | 87      |

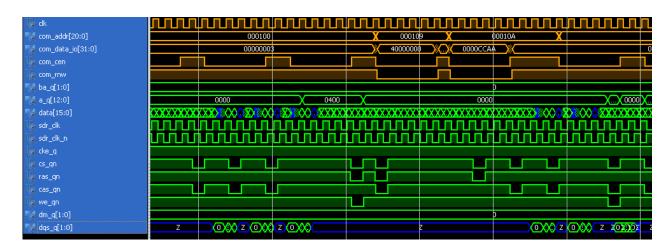

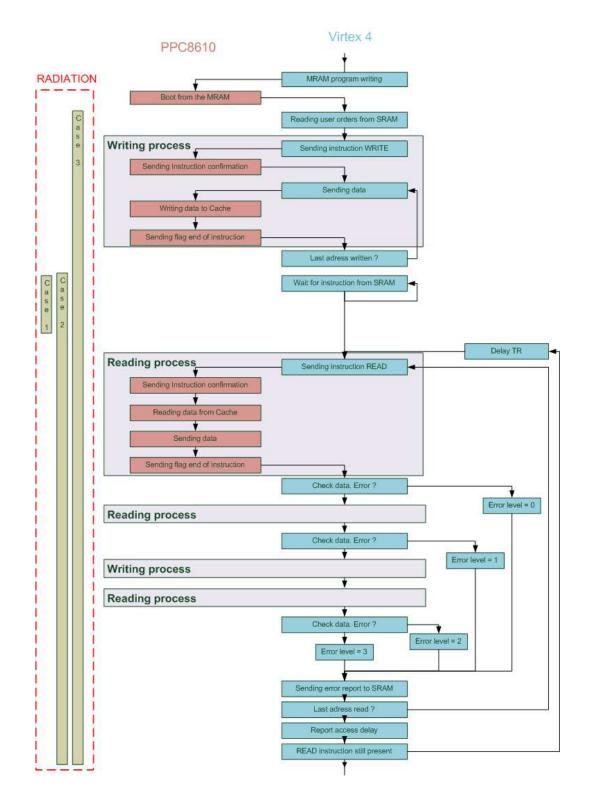

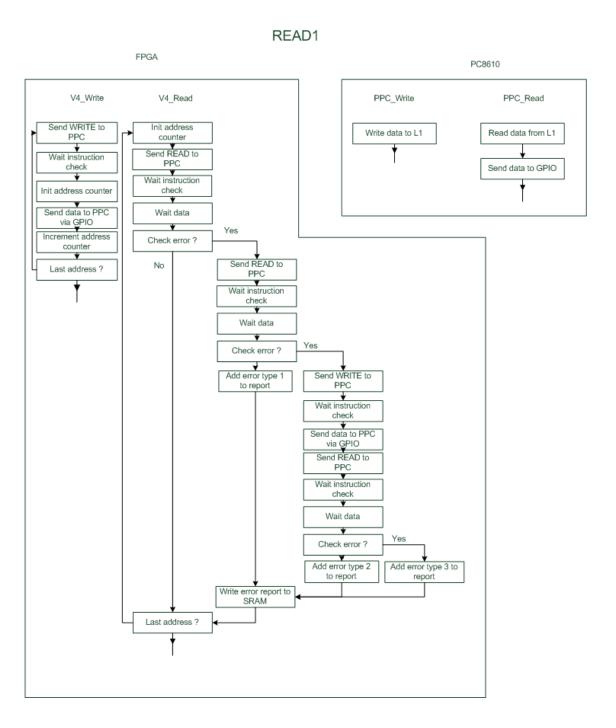

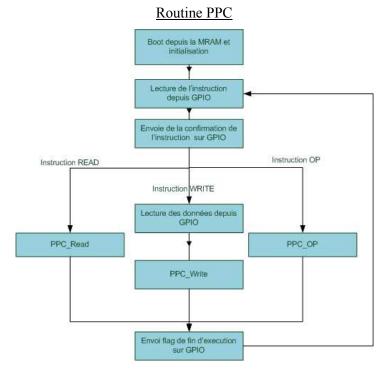

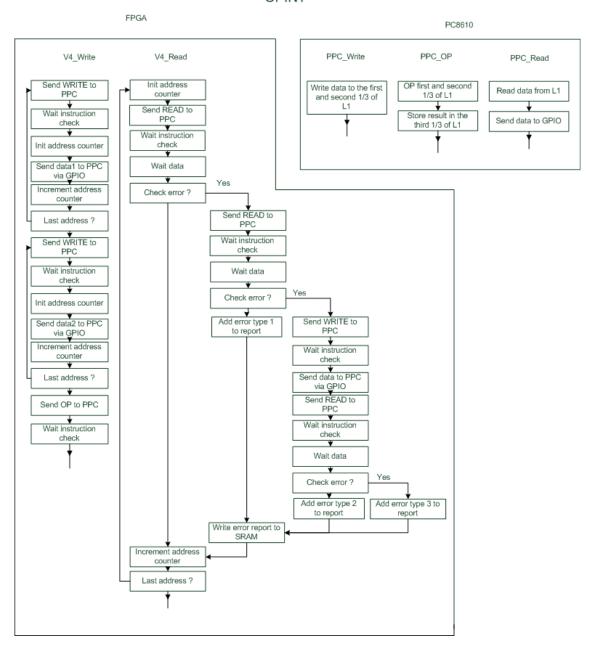

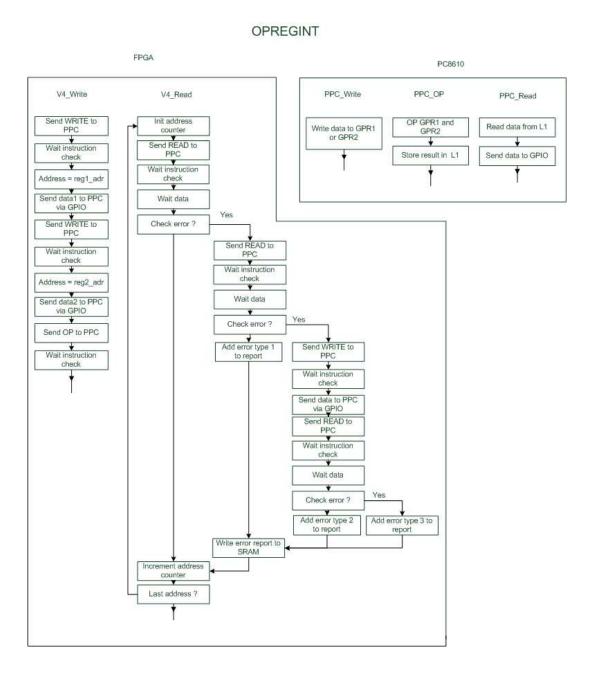

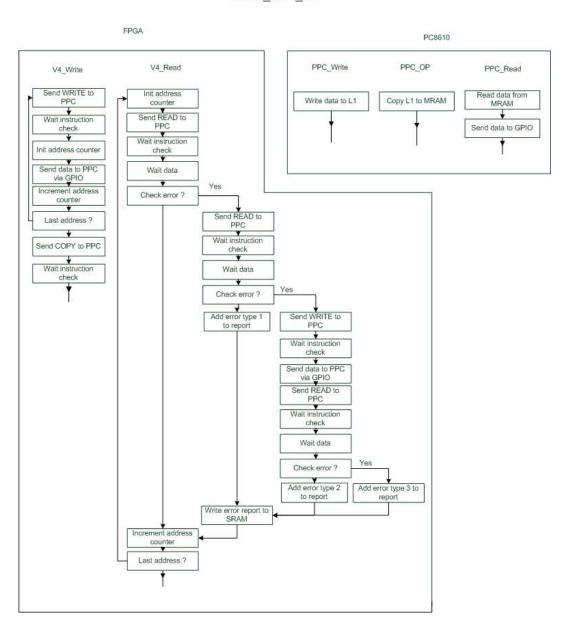

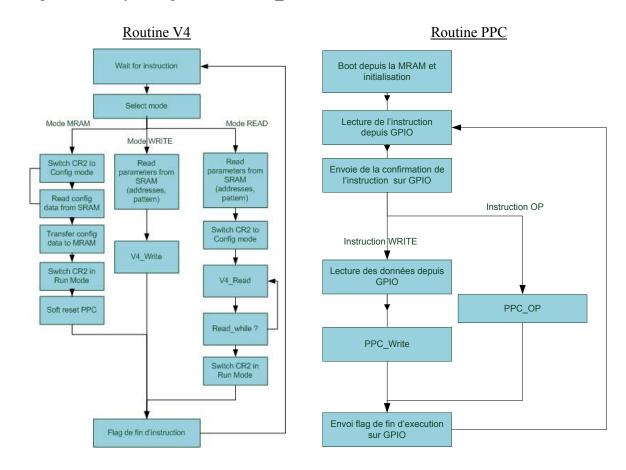

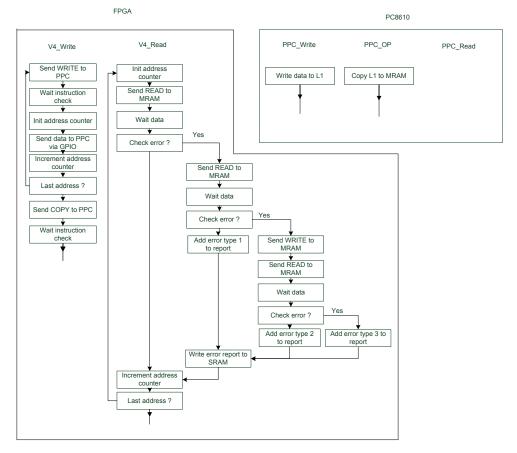

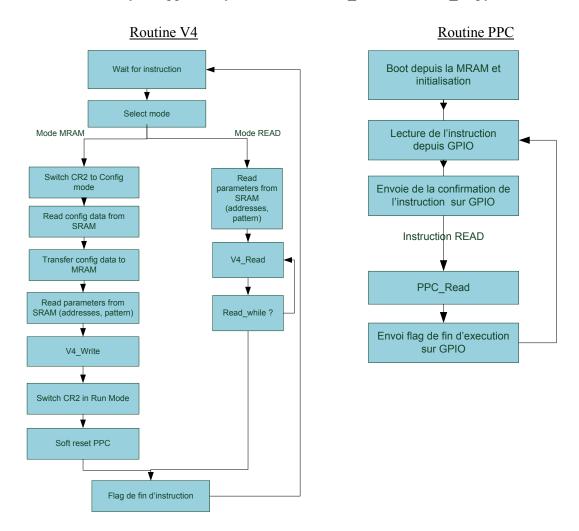

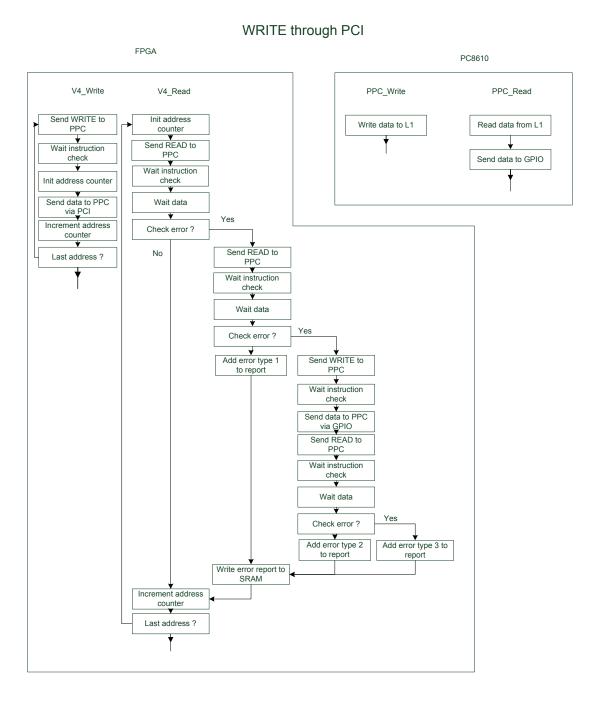

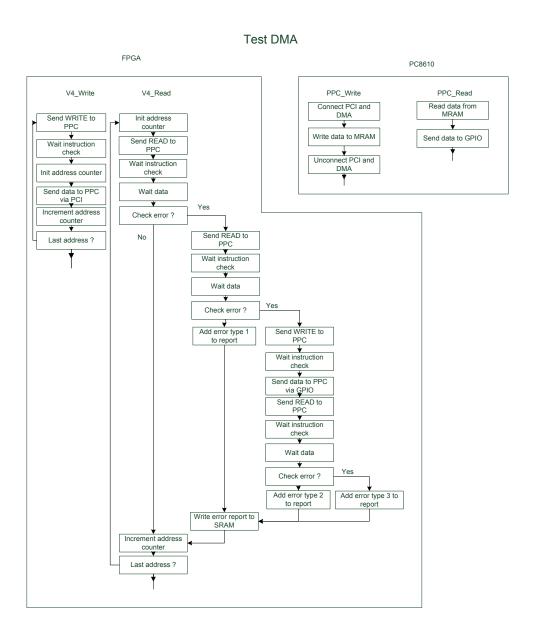

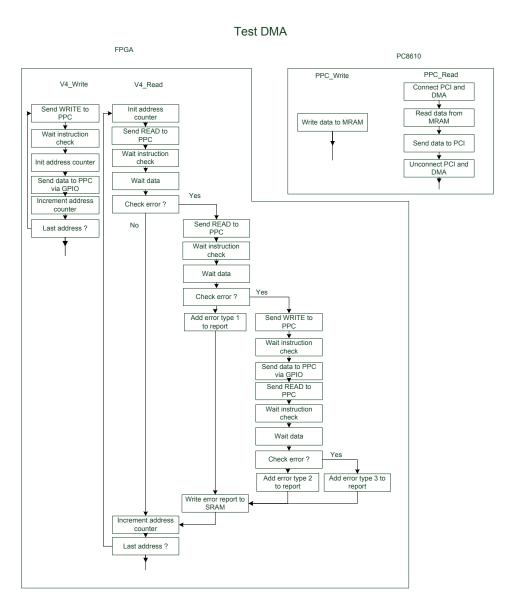

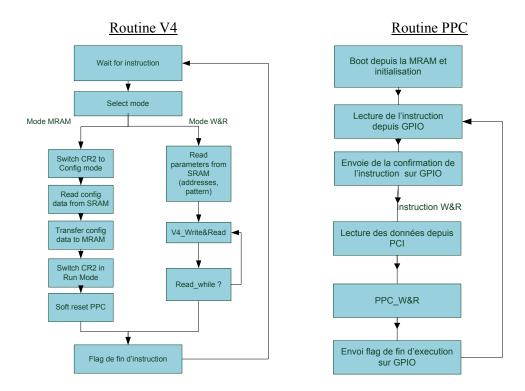

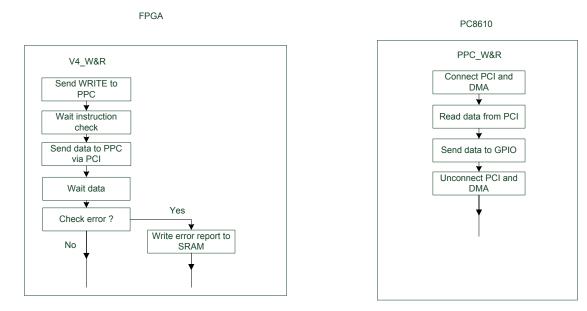

| II.4.2. Le module de pilotage du PowerPC                                                          | 89  |

|---------------------------------------------------------------------------------------------------|-----|

| II.4.2.1. Les entrées et sorties du FPGA communiquant avec la carte fille PowerPC                 | 89  |

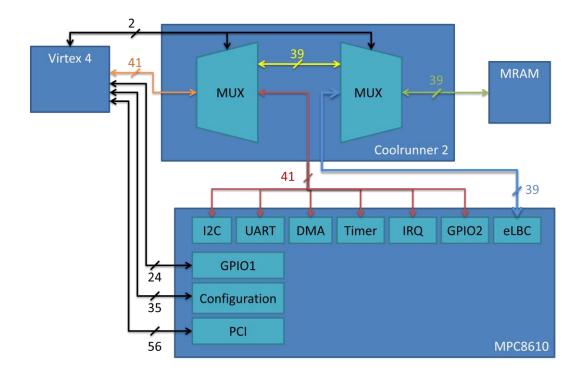

| II.4.2.2. Protocole de test du PowerPC                                                            | 89  |

| II.4.2.3. Schéma bloc du module de pilotage                                                       | 91  |

| II.4.2.3.1. Le sous-module MRAM_seq                                                               | 93  |

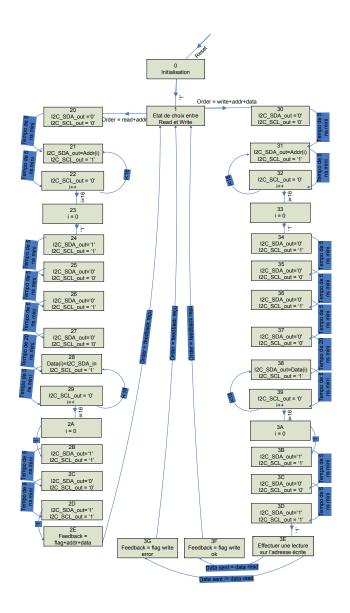

| II.4.2.3.2. Le sous-module I2C_seq                                                                |     |

| II.4.2.3.3. Le sous-module DUART_seq                                                              |     |

| II.4.2.3.4. Le sous-module PCI_seq                                                                |     |

| II.4.2.3.5. Le sous-module Arbiter                                                                |     |

| II.4.2.4. Rapport de synthèse du programme de pilotage du MPC8610 sur Virtex XC4VLX40             |     |

| II.4.2.5. Simulation du programme de pilotage du MPC8610  II.4.3. Les routines de test du PowerPC |     |

|                                                                                                   |     |

| II.4.3.1. Routines élémentaires du cœur E600                                                      |     |

| II.5. CONCLUSION                                                                                  |     |

| III. CHAPITRE 3 : ETUDE D'UNE D'UNE MEMOIRE STATIQUE BULK DE TECHNOI 90 NM 105                    |     |

| III.1. INTRODUCTION                                                                               |     |

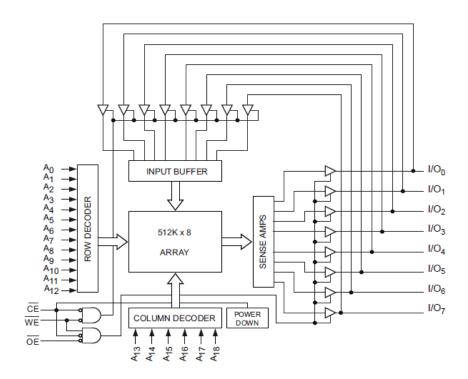

| III.2. PRESENTATION DE LA SRAM CY62148E55                                                         |     |

| III.2.1. Caractéristiques techniques                                                              |     |

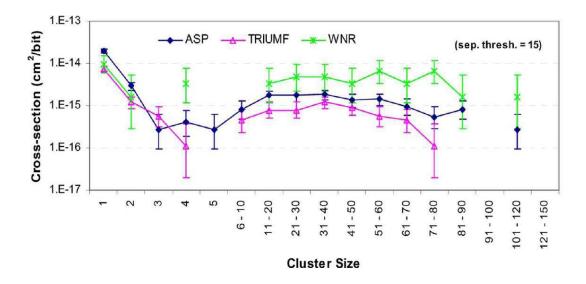

| III.2.2. Résultats de précédents tests effectués                                                  |     |

| III.3. ANALYSES ET TESTS PAR FAISCEAU LASER                                                       |     |

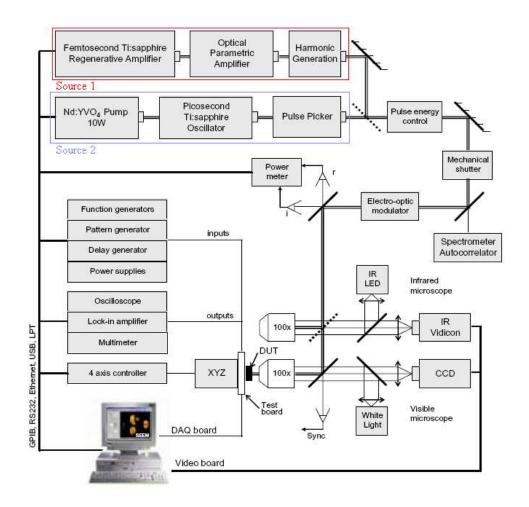

| III.3.1. Présentation du banc de test laser de la plateforme ATLAS                                | 111 |

| III.3.2. Plateforme de test                                                                       | 113 |

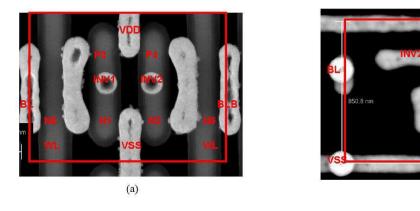

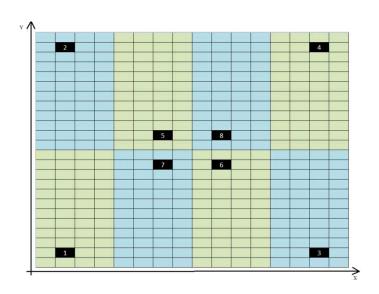

| III.4. METHODE DE DESCRAMBLING                                                                    | 114 |

| III.4.1. Mise en place du test laser                                                              | 114 |

| III.4.2. Le Descrambling                                                                          | 115 |

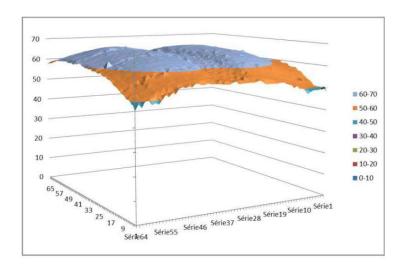

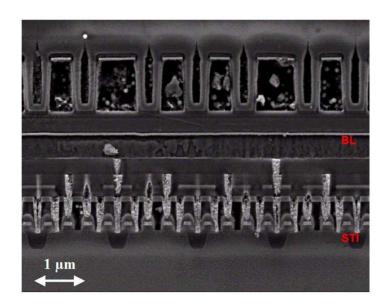

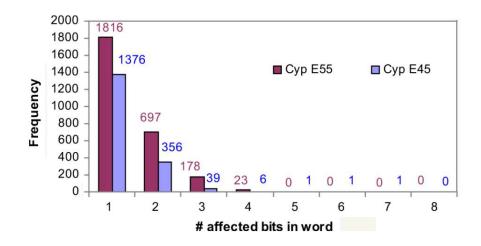

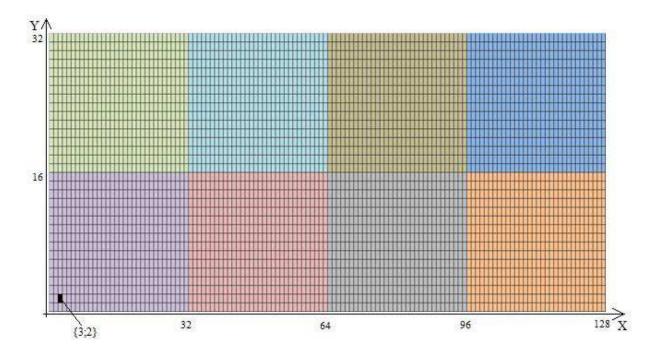

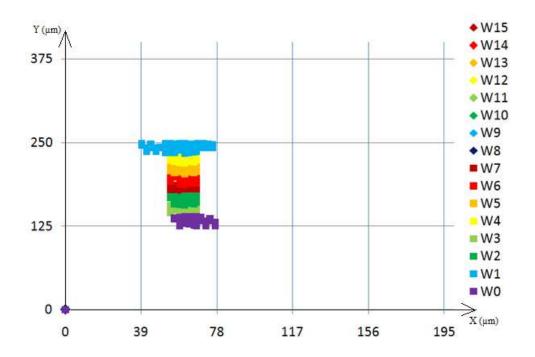

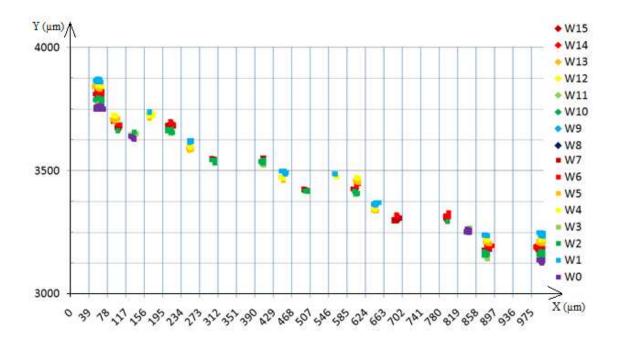

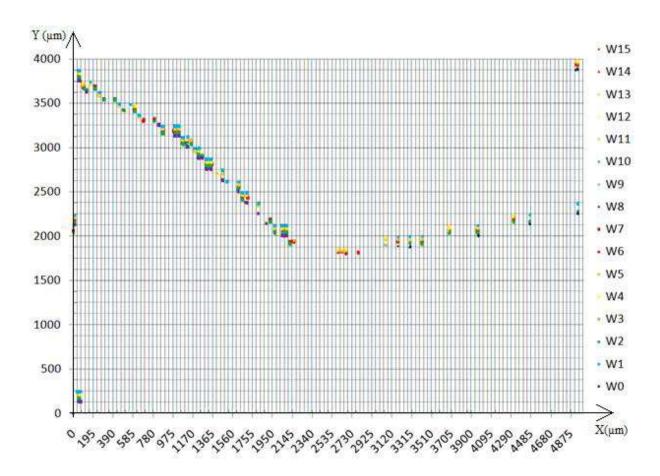

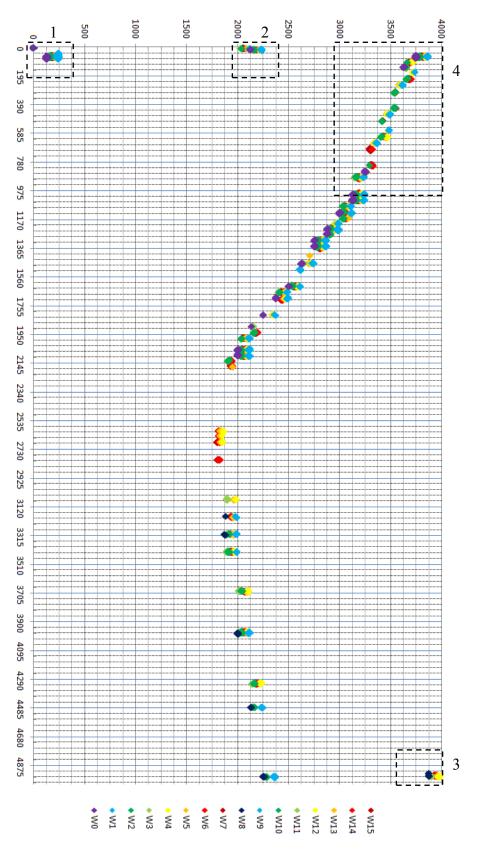

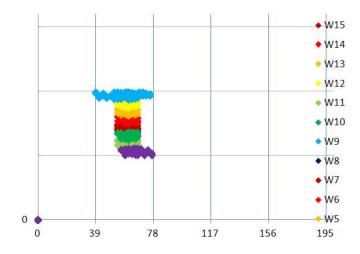

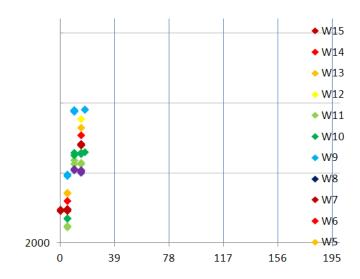

| III.5. RESULTATS DU DESCRAMBLING                                                                  | 116 |

| III.5.1. Recherche d'énergie seuil sur les échantillons non-fonctionnels                          | 116 |

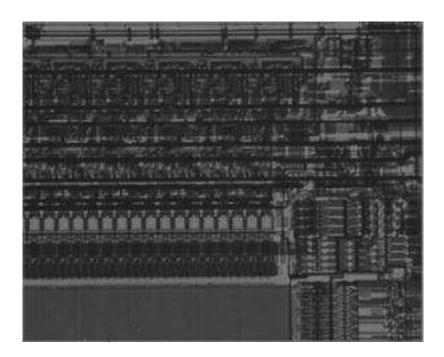

| III.5.2. Descrambling de l'échantillon fonctionnel                                                | 117 |

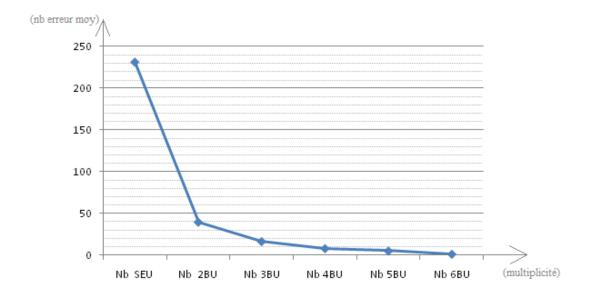

| III.5.3. Statistiques des différents profils d'erreurs                                            | 121 |

| III.6. CONCLUSION                                                                                 | 124 |

| CONCLUSION ET PERSPECTIVES                                                                        | 125 |

| RÉFÉRENCES BIBLIOGRAPHIQUES                                                                       | 128 |

| ANNEXES                                                                                           | 135 |

| Annexe A: Equations d'un faisceau Gaussien et de taux de generations                              | 136 |

| ANNEXE B: AFFECTATIONS DES PATTES DU VIRTEX 4 POUR LES MODULES VHDL DE PILOTAGE                   | 137 |

| ANNEXE C: PROTOCOLES ET ROUTINES DE TESTS DU POWERPC MPC8610                                      | 142 |

| ANNEXE D : REPRESENTATIONS SUPPLEMENTAIRES DU PLAN MEMOIRE DE LA SRAM CY62148E55                  |     |

Introduction générale

La fiabilité des circuits électroniques utilisés dans les équipements avioniques se doit d'être optimale. Outre le succès de missions, c'est de la sécurité des personnes et de vies humaines dont il est question. Il est donc primordial qu'aucune défaillance ne vienne perturber le fonctionnement du système en vol.

Or, depuis le milieu des 60s, on sait que des particules naturellement présentent dans l'environnement spatial sont susceptibles d'engendrer des dysfonctionnements [BRY66]. Par la suite, la diminution constante de la largeur des nœuds technologiques a rendu les systèmes électroniques sensibles aux particules atmosphériques. Cet environnement radiatif terrestre naturel est plus agressif aux altitudes de vol qu'au sol, car le flux diminue à mesure qu'il pénètre dans l'atmosphère. Des normes radiations ont donc été mise en place pour garantir le bon fonctionnement des équipements avioniques. Elles imposent de mesurer la sensibilité des composants électroniques face aux particules naturelles.

Cette étude se focalise sur les composants numériques complexes tels que les mémoires intégrées et les processeurs. Ces deux types de systèmes électroniques sont très répandus au niveau du sol et constituent le cœur de l'unité de vol d'un avion. Pour caractériser expérimentalement ces composants face aux rayonnements naturels, on utilise couramment des accélérateurs de particules. Ceux-ci reproduisent le rayonnement avec toutefois un facteur d'accélération. Ces équipements ont malheureusement un coût élevé, une accessibilité faible et des contraintes d'utilisation lourdes. C'est pourquoi des outils complémentaires, tels que les faisceaux lasers pulsés, ont été développés. Ils permettent d'émuler l'effet des radiations naturelles en injectant un courant photoélectrique dans les composants à tester.

Cette thèse s'inscrit dans le cadre du projet de recherche et développement : PROSEU. Son objectif est la caractérisation de la sensibilité d'une unité de vol face à l'environnement radiatif atmosphérique naturel. Cette unité de vol se compose d'un PowerPC et de deux mémoires intégrées : une dynamique et une magnétique. L'étape finale de ce projet est la réalisation de solution de durcissement réduisant la sensibilité du système selon des contraintes en performances, poids et coûts imposées.

Le premier chapitre présente le contexte de notre étude. L'environnement radiatif terrestre y est décrit, ainsi que les fluctuations des paramètres qui l'influencent. Les phénomènes d'interaction entre les différentes particules et les matériaux qui composent les circuits électroniques sont expliqués. L'interaction entre les faisceaux laser et le silicium est

également exposée et comparée à celle avec les particules. Le chapitre présente ensuite les équipements de test existants tels que les accélérateurs de particules ou les sites en altitudes. Un état de l'art des tests effectués sur des composants similaires à ceux de notre étude est fait. Enfin, le chapitre se clos sur un bref tour d'horizon des logiciels de simulation disponibles.

Le second chapitre s'attache à expliquer le développement des plateformes et des protocoles de tests nécessaires à notre étude. Il commence donc par une présentation du PowerPC et des mémoires étudiés. S'en suit la description hardware et software des plateformes de tests. Le détail de la communication entre l'interface utilisateur jusqu'au composant sous test est fait. Les programmes de pilotage, et donc les méthodes de test qui y sont liées, sont expliqués dans ce chapitre.

Le troisième chapitre se concentre lui sur l'étude d'une mémoire en particulier. Une première implémentation des programmes exposés en chapitre deux est faite. Toutefois, un problème matériel nous a contraints à changer de système de test et de mémoire à évaluer. Cette nouvelle mémoire statique et cette nouvelle plateforme de test sont donc brièvement présentés. Des résultats de test sous faisceau laser sont donnés. Ils portent sur le décodage de la mémoire, l'évaluation de sa sensibilité et plusieurs statistiques sur les patterns d'erreurs découverts.

I.Chapitre 1 : Etat de l'art des environnements radiatifs, de leurs effets et des moyens de test

#### I.1. Introduction

L'effet des ions lourds sur l'électronique embarquée a été découvert dans le début des années 1980. Toutefois, les particules de l'environnement radiatif naturel n'avaient encore qu'une influence limitée de par la faible intégration des composants électroniques. La technologie suivant la loi de Moore, en 1996 des tests ont démontré la sensibilité de systèmes électroniques aux neutrons [Obe96]. Dans le même temps, la part d'électronique embarquée en avionique n'a cessé de croître, réduisant les commandes hydrauliques et augmentant la part des commandes électriques et le nombre de capteurs. Dès lors, il est devenu indispensable de connaître le comportement des composants avioniques soumis au milieu radiatif terrestre. Le but de ce chapitre est de familiariser le lecteur avec ce que sont les effets à événement singulier, leurs causes et leurs conséquences.

Ce chapitre décrit un état de l'art de l'effet des neutrons atmosphériques sur l'électronique embarquée à l'avionique. Dans un premier temps seront présentés les environnements spatial et terrestre avec leurs flux de particules. Puis les mécanismes d'interaction entre les particules et les composants électroniques seront exposés. L'interaction laser-matière sera également expliquée. Les équipements expérimentaux permettant d'effectuer les tests seront ensuite présentés. Les principaux étant des accélérateurs de particules ou des bancs laser. Un catalogue des effets des événements singuliers sera exposé. Et enfin, nous présenterons un état de l'art de la sensibilité des composants étudiés et de composants qui leurs sont similaires.

#### I.2. L'environnement radiatif

#### I.2.1. L'environnement spatial

Avant de pouvoir décrire l'environnement radiatif terrestre, il est indispensable de décrire sa source : l'espace. L'environnement spatial est de loin le plus contraignant. Il est régi par trois grandes composantes : les rayons cosmiques, les ceintures de radiation et les éruptions solaires.

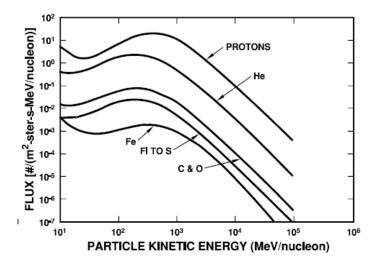

Les rayons cosmiques, Figure 1, sont d'origine galactique et extragalactique. Ils comportent tous les éléments du tableau de Mendeleïev dans un état d'ionisation avancé. Ces particules possèdent une énergie pouvant atteindre  $10^{12}$  GeV. Parmi ces particules, environ 1% sont des ions lourds ( $Z \ge 3$ ). Bien que moins nombreux, ils possèdent un pouvoir

d'ionisation important et représentent donc une composante significative de l'environnement spatial.

Figure 1 : Spectre en énergie des rayons cosmiques. [MEY74]

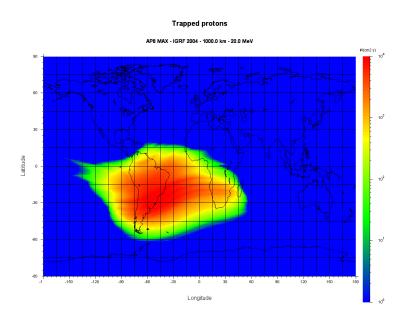

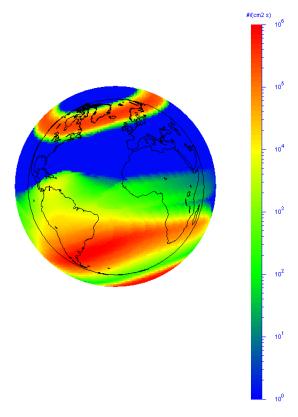

Les ceintures de radiation, découvertes par James Van Hallen en 1958, sont constituées de particules chargées légères piégées dans la magnétosphère : essentiellement des protons et des électrons. Les particules des deux ceintures, internes et externes, possèdent des énergies allant de quelques keV jusqu'à plusieurs centaines de MeV. Par ailleurs, la différence de 11° entre l'axe de rotation terrestre et l'axe de son dipôle magnétique entraîne un affaissement de la magnétosphère. Cette « anomalie de l'Atlantique Sud », en Figure 2, déséquilibre le flux de protons piégés dans les ceintures de Van Hallen qui devient très important à des altitudes relativement basses dans cette zone.

Figure 2: Visualisation de l'anomalie de l'Atlantique Sud via OMERE.

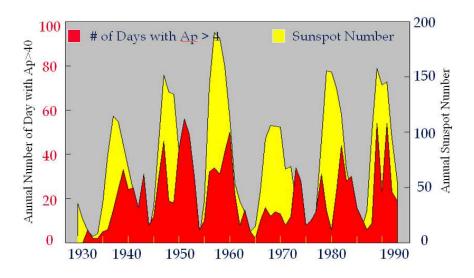

Les éruptions solaires sont des événements pouvant durer quelques heures ou quelques jours. Elles possèdent un flux très élevé d'électrons, de protons, de particules alpha et également d'ions lourds. Outre leurs intenses participations en apport de particules, ces événements jouent également un autre rôle. En effet, le vent solaire interagit avec les ions des rayons cosmiques et influence la dynamique des ceintures de Van Hallen. Des études sur le long terme montrent que l'activité solaire, en Figure 3, est cyclique avec une période de 11 ans.

Figure 3 : Cycle des éruptions solaires et des tempêtes magnétiques [BAR97].

#### I.2.2. L'environnement terrestre

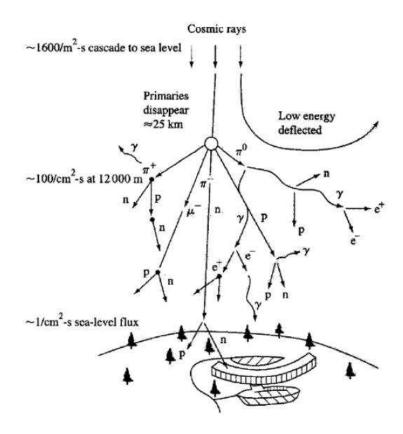

L'atmosphère terrestre est donc en interaction continuelle avec les ceintures de radiations et les rayons cosmiques tous deux modulés par les éruptions solaires qui apportent elles aussi leur lot de particules. Les particules chargées les moins énergétiques sont repoussées par la magnétosphère. Les ions lourds, quant à eux, viennent interagir avec l'atmosphère, principalement l'azote et l'oxygène, créant ainsi une « cascade » de particules secondaires, en Figure 4.

Figure 4 : Schéma de la cascade de particules secondaires. [ZIE96]

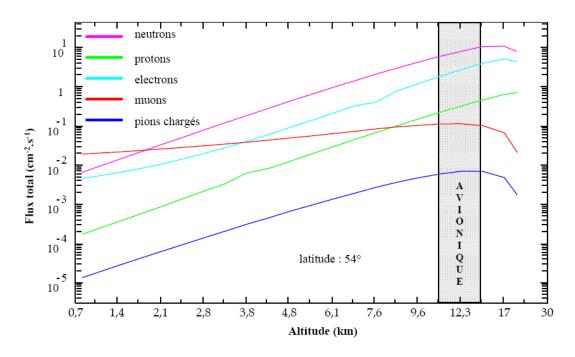

Ces particules sont : des neutrons, des protons, des électrons, des muons et des pions. La Figure 5 montre les flux de ces particules en fonction de l'altitude, pour une latitude de 54°. Aux altitudes avioniques, ce sont donc les neutrons et les électrons qui prédominent le spectre de particules. Cependant, si les électrons peuvent entraîner des défaillances sur les composants électroniques sur le long terme par effet de dose, ils n'entrent pas en compte dans les mécanismes d'ionisation qui seront développés par la suite. Les neutrons, quant à eux, joueront un rôle prépondérant dans les défaillances de systèmes électroniques.

Figure 5 : Spectre des particules secondaires. [LUU09]

#### *I.2.2.1. Profondeur atmosphérique et rigidité magnétique*

Il apparaît indispensable de connaître le comportement du spectre des neutrons atmosphériques dans les différentes régions du globe. Habituellement, les coordonnées spatiales utilisées sont l'altitude et la latitude. Toutefois, les géophysiciens préféreront utiliser la profondeur atmosphérique, exprimée en g/cm², à la place de l'altitude et le « vertical rigidity cutoff » exprimé en GV, à la place de la latitude.

La profondeur atmosphérique peut s'exprimer en fonction de l'altitude, A en pieds selon la formule suivante, d'après [NOR96] :

$$x = 1033 \times e^{-[0.4534 - (1.17 \times 10^{-9})] \frac{A - 1.05 \times 10^{5}}{1000}} \Big|^{3.58} \times \frac{A}{1000}$$

(1)

Par ailleurs, le vertical rigidity cutoff peut s'exprimer en première approximation, d'après [STO30], par :

$$R_{s} = \frac{M}{R^{2}} \times \frac{\cos^{4} \lambda}{(1 + \sqrt{1 - \sin \varepsilon . \sin \phi . \cos^{3} \lambda})^{2}}$$

(2)

Où M est le moment dipolaire terrestre, R la distance jusqu'au centre de ce dipôle en rayons terrestres,  $\lambda$  la latitude géomagnétique,  $\epsilon$  l'angle au zénith,  $\Phi$  l'azimut mesuré depuis l'axe du nord magnétique. L'équation (2) montre que pour n'importe quels angles d'azimut et de zénith, la rigidité magnétique diminue lorsque la latitude magnétique augmente. Ceci

implique que les particules pénètrent plus facilement aux pôles qu'à l'équateur. La rigidité magnétique peut également être reliée à l'énergie d'une particule :

$$R = \frac{A}{\rho} \times \sqrt{E^2 + 2.M_0.E} \tag{3}$$

Où A est la masse de la particule en amu,  $\rho$  la charge de la particule, E est l'énergie de la particule en MeV et Mo vaut 931 MeV. La rigidité magnétique d'une particule augmente avec son énergie, l'équation (3) montre que seules les particules de hautes énergies pourront traverser les régions à forte rigidité magnétique.

Toutefois cette approximation ne permet qu'une compréhension théorique des phénomènes. Shea et Smart [SS84] ont calculé un coefficient RS (vertical rigidity cutoff) plus précis sur l'ensemble de la surface du globe, mais les calculs devant être menés en tout point pour chaque direction, cette approche pratique n'est pas utilisable. En revanche, le code CREME (Cosmic Ray Effects on Microelectronics) développé par Adam et al. [ADA92] permet, par la combinaison de la théorie de Störmer et les calculs de Shea et Smart, de calculer le comportements des particules en fonction de la rigidité magnétique. Le code modifie ainsi la fluence des particules en fonction de leurs énergies.

#### *I.2.2.2.* Spectres des neutrons atmosphériques

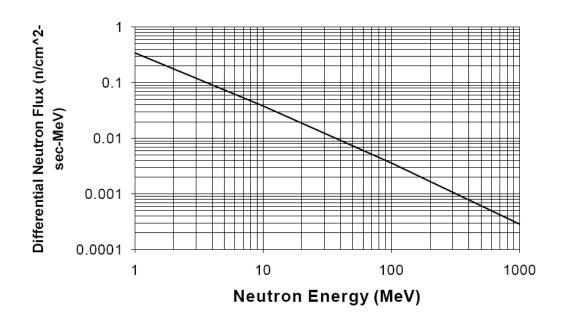

Le spectre des neutrons atmosphériques peut être représenté en fonction de l'énergie de chaque particule comme en Figure 6.

Figure 6 : Flux différentiel de neutrons mesuré à 40,000 ft et à 45° Nord

L'énergie d'un neutron peut être supérieure à 1 GeV. Ces mesures, effectuées par Hewitt et al. [HEW78], se sont vues confirmées par la suite [WIL91] avec parfois un plateau entre 30 et 70 MeV avant de poursuivre en décroissance.

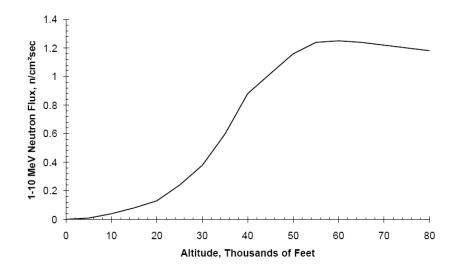

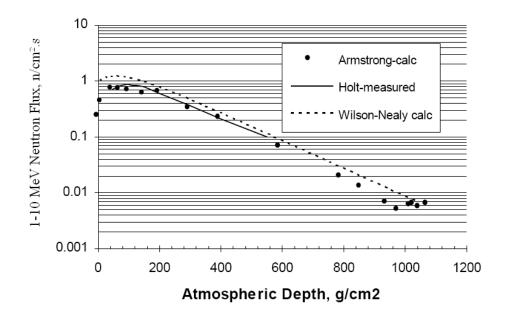

Le flux de neutrons varie avec l'altitude, visible en Figure 7. Tout d'abord, dans les premières couches de l'atmosphère la production de neutrons dépend de l'interaction avec les rayons cosmiques. Puis le nombre de neutrons diminue au fur et à mesure que la couche d'air à traverser augmente. Il en résulte un maximum appelé : maximum de Pfotzer se trouvant à environ 60,000 pieds.

Figure 7: Flux des neutrons 1-10 MeV à 45° Nord [NOR93a]

Le flux de neutrons 1-10 MeV est communément représenté, il faut toutefois remarquer que Normand et Baker ont vérifié que le flux des neutrons 10-100 MeV est régi par le même comportement [NOR93b].

Comme précédemment expliqué, l'altitude peut être remplacée par la profondeur atmosphérique (Figure 8).

Figure 8 : Flux de neutron 1-10 MeV [ADA92]

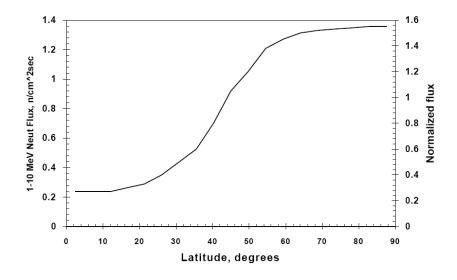

Par ailleurs, les rayons cosmiques ne pénétrant pas en tous points de la magnétosphère avec la même énergie, il apparaît normal que le flux de neutrons, qui en découlent, dépende de la latitude, visible en Figure 9.

Figure 9 : Flux de neutrons 1-10 MeV à 35,000 ft [NOR93a]

La figure 9 montre l'influence du champ magnétique terrestre sur les flux de neutrons atmosphériques. En effet, seuls les ions les plus énergétiques pourront pénétrer au niveau de l'équateur, alors que la plupart des particules traverseront la magnétosphère aux nivaux des pôles. Ce résultat est en accord avec les équations (2) et (3).

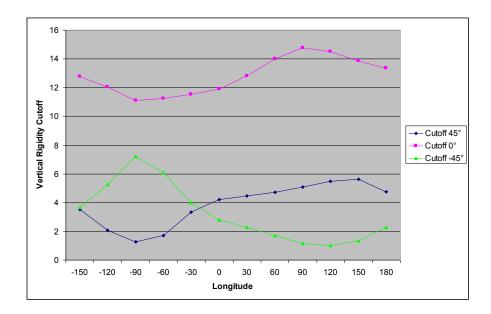

Mais le flux de neutrons est également différent en fonction de la longitude. La Figure 10 représente la rigidité magnétique calculée par [NYM09] en fonction de la longitude pour des Latitudes de 45°, 0° et -45°. La rigidité évoluant, le flux de rayons cosmiques pénétrant l'atmosphère diffère également et le flux de neutrons s'en trouve modifié.

Figure 10: Rigidité magnétique en 2005 selon [NYM09].

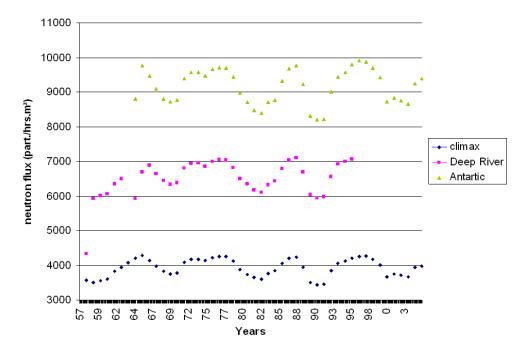

Un dernier phénomène qui impacte le flux de neutrons atmosphériques est le cycle d'éruptions solaires. Pour évaluer l'influence de ce cycle, il est possible de tracer les relevés effectués par [TAK07], en Figure 11, en différents points du globe :

Figure 11 : Flux de neutrons horaire moyenné sur un mois.

Pour plus de clarté, il est utile de présenter les coordonnées géographiques des trois lieux de mesure consignées dans le Tableau 1 :

| Lieu        | Latitude (°) | Longitude (°) | Altitude (m) | Vertical Cutoff (GV) |

|-------------|--------------|---------------|--------------|----------------------|

| Climax      | 39.37        | -106.18       | 3400         | 3.03                 |

| Deep River  | 46.10        | -77.5         | 145          | 1.02                 |

| Antarctique | -77.9        | 166.6         | 48           | 0.01                 |

Tableau 1: Coordonnées de trois des centres de mesures de [TAK07].

L'influence du coefficient RS est parfaitement visible sur la figure 11, plus il est faible et plus les flux de neutrons sont marqués. De plus, la comparaison des figures 11 et 3 amène à la conclusion que les ces flux sont amoindris lorsque l'activité solaire est intense. Ceci s'explique par le fait que, lors des éruptions solaires, les rayons cosmiques doivent combattre les particules issues du vent solaire. Ces rayons ayant perdu de leur énergie, ils engendrent moins de particules secondaires lors de leur interaction avec l'atmosphère.

#### I.3. L'interaction Neutron-Matière

Pour comprendre en quoi les neutrons représentent une menace pour les systèmes électroniques, il faut tout d'abord explorer l'effet des particules chargées sur un semi-conducteur.

#### I.3.1. L'interaction Ion-Silicium

#### *I.3.1.1. Description du phénomène*

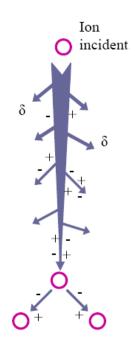

L'ion lourd est l'un des meilleurs candidats à la perturbation d'un système électronique. Il interagit avec les électrons et les atomes de la structure cristalline du semiconducteur par interaction électromagnétique coulombienne. Les processus de dépôt d'énergie sont l'ionisation et l'excitation des atomes.

L'interaction avec un électron est la plus probable. Si l'énergie transférée à l'électron est suffisante pour l'extraire du potentiel atomique, il y a alors ionisation. Cette ionisation directe est localisée autour de la trace de l'ion, la portée d'une interaction ionisante étant de l'ordre de 0.5 nm [EQU88]. L'électron participe au rayonnement  $\delta$  si l'énergie qu'il a captée lui permet d'ioniser à son tour d'autres atomes. Ces rayons  $\delta$  contribuent à l'extension radiale de la trace d'ionisation, leur parcours pouvant atteindre plusieurs microns.

$$R = \kappa T^{\alpha} \tag{4}$$

où R est le parcours moyen en  $\mu m$ ,  $\kappa$  vaut 0.0183  $\mu m/keV$  dans le silicium, T est l'énergie cinétique en keV et  $\alpha$  est compris entre 1,5 et 1,75.

L'ion cède son énergie au milieu lors de sa propagation, réduisant ainsi l'extension radiale de sa trace. Lorsque son énergie approche les quelques keV par nucléons, l'ion capture des électrons et son état d'ionisation diminue. Il interagit également avec les atomes, excitant la structure cristalline qui émet alors des phonons optiques. Ces atomes peuvent rester durablement hors de leur position d'équilibre, ils sont alors susceptibles d'engendrer d'autres défauts dans le réseau cristallin.

Figure 12 : Trace d'un ion dans le silicium [LUU09]

#### I.3.1.2. Pouvoir d'arrêt et transfert d'énergie linéique

La perte d'énergie de l'ion par interaction avec les électrons est appelée pouvoir d'arrêt électronique. Il peut s'exprimer par la formule de Bethe [CHE96] :

$$\left| \frac{dE_i}{dz} \right| = \frac{1}{4.\pi \cdot \varepsilon_0^2} \cdot \frac{N \cdot e^4}{m_e \cdot C^2} \cdot \frac{Z_i^2}{\beta^2} \cdot \left[ \ln \left( \frac{2 \cdot m_e \cdot C^2}{I} \cdot \beta^2 \right) - \ln \left( 1 - \beta^2 \right) - \beta^2 \right]$$

(5)

avec : dEi/dz : variation d'énergie linéique le long d l'axe de propagation,  $J.m^{-1}$

$\epsilon_0$  : permittivité du vide, 8,85.10  $^{\!-12}$   $C^2.J^{\!-1}.m^{\!-1}$

N : densité électronique du milieu, environ 7.10<sup>29</sup> m<sup>-3</sup> pour le silicium

e : charge d'un électron, 1,6.10<sup>-16</sup> C

$m_e$ : masse au repos de l'électron,  $9,1.10^{-31}\ kg$

C : vitesse de la lumière dans le vide, 3.10<sup>8</sup> m.s<sup>-1</sup>

Z<sub>i</sub> : nombre de charge de l'ion (numéro atomique en cas d'ionisation totale)

$\beta = V/C$ , où V est la vitesse de l'ion

I : potentiel d'ionisation moyen des électrons, environ 170 eV pour le silicium

Le pouvoir d'arrêt est donc proportionnel au carré de la charge de l'ion incident et dépend également de sa vitesse. L'équation (5) est une approximation, pour une meilleure précision, essentiellement pour les faibles énergies, il convient d'utiliser des tables [ZIE80] ou des logiciels [SRI00] dédiés. Le pouvoir d'arrêt s'exprime couramment en MeV.cm².mg⁻¹, obtenu à partir de :

$$\left| \frac{dE_i}{\rho . dz} \right| = \frac{10^4}{\rho} . \frac{dE_i}{dz} \tag{6}$$

ou en pC.µm<sup>-1</sup>, obtenu à partir de :

$$\left| \frac{dE_i}{dz} \right| = \frac{0.16}{E_p} \cdot \left| \frac{dE_i}{dz} \right| \tag{7}$$

Le pouvoir d'arrêt traduit l'énergie perdue par unité de longueur. Le Transfert d'Energie Linéique (LET) est défini en intégrant le spectre des rayons  $\delta$  jusqu'à une énergie maximum.  $L_{100\text{ev}}$  est ainsi l'énergie perdue par unité de longueur en ne prenant en compte que les rayons  $\delta$  d'énergie inférieure ou égale à 100 eV. Toutefois, l'usage identifie le LET au pouvoir d'arrêt, c'est-à-dire  $L_{\infty}$ .

#### I.3.2. L'interaction Neutron-Matière

#### I.3.2.1. L'interaction Neutron-Silicium

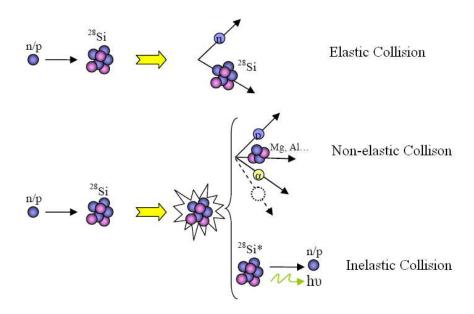

Les neutrons, contrairement aux ions, ne sont pas chargés. Ils ne possèdent donc pas de LET et n'ionisent donc pas la matière, du moins pas directement. En revanche, ils interagissent avec les noyaux, les neutrons thermiques (E <1 eV) entrent en collision avec l'isotope <sup>10</sup>B, et les neutrons rapides (100keV< E < 1 MeV) avec les atomes de silicium. Pour des énergies supérieures à quelques MeV, les collisions inélastiques et les réactions de fragmentation du noyau doivent être prises en compte.

Chapitre 1 : Etat de l'art des environnements radiatifs, de leurs effets et des moyens de test

Figure 13 : Schéma d'interaction Neutron-Silicium [LUU09]

Les collisions élastiques déplacent les atomes de silicium, il en résulte, sur le long terme, une dégradation des performances du semi-conducteur. En revanche les collisions non-élastiques sont des réactions nucléaires. Elles génèrent des particules secondaires : des neutrons, des particules alpha et des ions. Ils peuvent, à leurs tours, interagir avec le silicium et l'ioniser, tout comme le ferait un ion lourd par ionisation directe. L'ionisation étant donc indirecte, il n'est pas possible de parler du pouvoir d'arrêt d'un neutron. L'ionisation dépend alors de la nature de l'ion créé et de l'énergie cinétique qu'il a emmagasinée. Il est alors nécessaire de faire appel à des bases de données pour modéliser l'interaction neutron-silicium.

#### *I.3.2.2.* L'interaction Neutron-Matière

Si l'interaction d'un neutron avec un atome de silicium est susceptible de créer un ion de recul issu des atomes se trouvant avant le silicium dans le tableau de Mendeleïev, les neutrons peuvent également interagir avec tous les autres atomes présents dans l'environnement du semi-conducteur. Ces atomes pouvant être les dopants intrinsèques du semi-conducteur ou des impuretés, dont la nature est moins bien maîtrisée. Mais ils peuvent également être des atomes provenant du boîtier des puces de circuits intégrés [WRO08]. Il ne faut donc pas limiter les études de sensibilité au circuit seul, mais bien au système dans son ensemble.

#### I.3.3. L'interaction Proton-Matière

Une autre particule très présente dans l'atmosphère est le proton. Même si la densité du flux de proton est très inférieure à celle du flux de neutron, il n'en reste pas moins une

menace sérieuse pour les composants électroniques [REFatrouver]. En effet, le proton étant chargé, il peut ioniser le silicium qu'il traverse. Et, si son énergie est suffisante, il peut engendrer des particules secondaires suite à une collision non-élastique avec un noyau.

Au-delà d'une énergie de 50 MeV, le proton crée la même perturbation qu'un neutron sur un composant électronique. Si son énergie est inférieure à 50 MeV, l'ionisation qu'il laisse le long de sa trace devient non-négligeable devant l'effet d'éventuelles particules de recul [REFatrouver].

#### I.4. Les effets à événement singulier (SEE)

#### I.4.1. Les Phénomènes mis en œuvre

#### *I.4.1.1.* La collection de charge

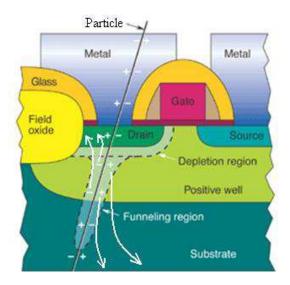

La figure 13 permet d'expliquer les phénomènes mis en jeu lors d'un SEE. Les paires électron-trou générées dans la zone de charge d'espace sont séparées par le champ électrique. Les porteurs sont alors accélérés jusqu'à atteindre la zone où ils sont majoritaires, c'est le phénomène de dérive. Un transitoire de courant inverse est alors généré dans la jonction. C'est ce transitoire qui est susceptible d'engendrer un SEE.

Les lignes de potentiels normalement confinées à la zone de charge espace se déploient dans le substrat. Le champ électrique gagne alors en volume, amplifiant la collection par dérive. Ce phénomène est le funneling [HSI81] (de l'anglais funnel : entonnoir). Ainsi, si la densité de porteurs générés est importante devant la concentration en atomes dopants ionisés dans la zone de charge espace, la colonne de charge peut écranter le champ initial. La différence de potentiel entre les régions N et P se répartit le long de la trace d'ionisation.

Les porteurs non-soumis à un champ électrique diffusent dans le semi-conducteur. Ils peuvent être collectés si cette diffusion les amène sous l'influence de la zone de charge espace. Dans le cas contraire, ils se recombinent après plusieurs microns de parcours autour du point d'impact de l'ion.

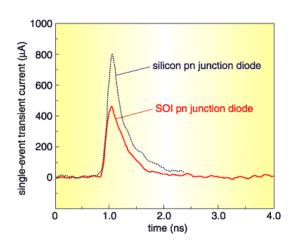

Figure 14 : Mécanisme de génération d'un courant transitoire parasite.

Ces trois phénomènes de collection entraînent donc la création d'un courant. L'amplitude de ce courant transitoire est directement liée aux nombres de charges collectées. La Figure 14 montre ainsi que dans une technologie SOI l'amplitude du courant est amoindrie par rapport à celui d'un transistor dans une technologie bulk de dopage similaire. En effet, la technologie SOI, où le volume du substrat est fortement limitée, réduit l'effet funneling et les porteurs collectés par effet de diffusion.

Figure 15 : Courant de collection lors d'un événement transitoire [LUU09].

#### I.4.1.2. Notion de charge critique et modèle RPP

La notion de charge critique permet d'exprimer la sensibilité d'une cellule mémoire. Cela suppose qu'une cellule donnée basculera dans son état logique complémentaire si la charge apportée à un nœud électrique sensible est supérieure à la charge critique :  $Q_c$ . Ce paramètre est un indicateur de sensibilité, il permet donc la comparaison de circuits, selon leurs technologies ou leurs géométries.

Il faut toutefois noter que cette notion occulte tous les aspects dynamiques de la collection de charges.

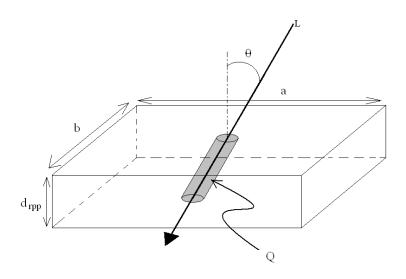

Fondé sur la notion de charge critique, le modèle RPP (rectangular parallelepiped) suppose que tout ion ayant généré, dans le volume sensible qu'est le RPP, une charge supérieure à Qc induira un SEU [PIC78].

Figure 16 : Géométrie du modèle RPP [POU00].

Le modèle RPP possède plusieurs avantages. Tout d'abord, il simplifie la modélisation de la sensibilité en limitant le nombre de paramètres : 1 paramètre électrique  $(Q_c)$  et 3 paramètres géométriques  $(a,\ b,\ d_{rpp})$ . Par ailleurs, il permet de traiter simplement la dépendance angulaire en extrapolant les résultats en incidence normale au cas d'un flux isotrope.

Il n'y aura alors un SEU que si le LET (en pC/ $\mu$ m) de l'ion est supérieur à Qc/d<sub>rpp</sub>. Donc pour un LET seuil L<sub>0</sub>, l'équation (8) est obtenue:

$$Q_c = L_0.d_{rpp} \tag{8}$$

Cependant, dans la plupart des cas, la charge critique n'est pas connue et la profondeur du volume est une estimation grossière de la réalité physique. Pour faciliter les comparaisons, la profondeur de zone sensible est arbitrairement fixée par défaut à 1 µm. Ce choix constitue la limitation principale de ce modèle. Il paraît en effet peut compatible de figer un volume sensible tout en prenant en compte la contribution d'une collection par diffusion lors d'un impact éloigné de la zone de charge espace.

#### I.4.2. Les différents SEE

Tout d'abord, et dans un souci de compréhension, les termes anglophones seront conservés pour la plupart des effets à événement singulier, ou Single Event Effects. Le tableau suivant récapitule les types SEEs les plus connus:

**Tableau 2: Single Event Effects usuels.**

| Abréviation | Nom complet                       | Définition                                                       | Destructif? |

|-------------|-----------------------------------|------------------------------------------------------------------|-------------|

| SEU         | Single Event Upset                | Changement d'état logique dans une cellule mémoire.              | non         |

| MBU         | Multiple Bit Upset                | Plusieurs SEU causés par une seule particule                     | non         |

| MCU         | Multiple Cell Upset               | Un MBU concentré dans<br>un mot logique                          | non         |

| SET         | Single Event Transient            | Apparition d'un courant transitionnel parasite                   | non         |

| SEFI        | Single Event Functional Interrupt | Blocage de systèmes<br>numériques complexes                      | non         |

| SEL         | Single Event Latchup              | Augmentation du courant due à une jonction <b>pnpn</b> parasite. | oui         |

| SEB         | Single Event Burnout              | Emballement thermique destructif                                 | oui         |

| SEGR        | Single Event Gate Rupture         | Rupture de grille du diélectrique                                | oui         |

De manière générale, un SEE peut se produire lors du dépôt de charge dans un système électronique par ionisation directe ou indirecte. Si les SEEs destructifs ne peuvent être endigués, les non-destructifs peuvent, eux, être corrigés. Il est alors utile de connaître au mieux les risques que court le système et comment le protéger.

Bien que les premières suggestions sur la possibilité qu'une particule puisse induire des effets sur un circuit microélectronique aient été faites en 1962. Il fallut attendre 1975 pour observer le premier SEE.

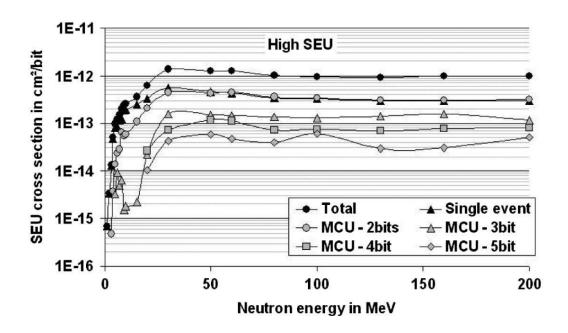

#### I.4.2.1. Les SEU, MBU et MCU

Ces trois types de SEEs sont ceux qui seront le plus souvent rencontrés dans notre étude, il apparaît utile d'en faire une définition précise.

Une définition raisonnable d'un SEU est : « Un Single Event Upset est le changement d'état logique d'un bit dans un élément numérique qui a été causé soit par une ionisation directe due à une particule traversante, soit par une ionisation produite par une particule de recul chargée émise suite à une réaction nucléaire induite près de l'élément. Le plus souvent, l'Upset n'est pas destructif et peut être corrigé s'il est détecté. » [STA95]

Les Multiple Bit Upset, ou MBU, sont plusieurs SEU engendrés par une même particule. Cette particule peut être un ion lourd ionisant plusieurs cellules le long de sa trace ou via ses rayons deltas sur des structures très intégrées. Mais cela peut également être un neutron qui, via plusieurs particules de recul, impacte différentes cellules parfois très éloignées.

Le Multiple Cell Upset, ou MCU, est un cas particulier de MBU où toutes les cellules mémoire impactées appartiennent au même mot logique. Cette particularité rend les MCU menaçants pour tout circuit numérique, les codes de correction d'erreur classiques ne pouvant corriger ou même détecter les cellules corrompues. Remarquons que certaines SEFI peuvent générer des erreurs assimilables à des MCU, mais n'ayant pas la même cause physique.

#### *I.4.2.2.* Les SEFI

Une définition raisonnable du SEFI est : « Un Single Event Function Interrupt est un SEU qui survient dans un système complexe tel que son système de contrôle est corrompu, menant ainsi à un fonctionnement inapproprié. »

Essayer de fournir un catalogue exhaustif des SEFI existantes serait vain. Toutefois, illustrons le concept par plusieurs exemples sur des composants électroniques usuels.

Dans des composants de type mémoire, une SEFI peut survenir dans la logique d'adressage et ainsi corrompre une ou plusieurs lignes ou colonnes de cellules. Un unique impact de particule engendre alors une erreur ressemblant à un MCU ou une combinaison de MCU. Le profile de ces SEFI varie en fonction de la structure de la mémoire [Gue12]

Dans un composant de type micro-processeur, chaque registre de configuration ou d'adressage est une source potentielle de SEFI.

#### I.4.2.3. Les SEL et SEB

Une définition raisonnable du SEL est : « Un Single Event Latchup est le dysfonctionnement d'un circuit dû à l'ionisation locale créée par un ion traversant ou une

réaction nucléaire. Le SEL peut être destructif ou non-destructif. Dans les technologies CMOS, un SEL peut créer un appel de courant endommageant les liaisons filaires (ou le semi-conducteur lui-même) si le circuit n'est pas protégé par un système de limitation de courant. Le SEL peut être un sérieux problème, car celui-ci persiste tant que l'alimentation du circuit touché n'est pas régulée. » [STA95]

#### I.5. Les tests

#### I.5.1. La courbe de section efficace

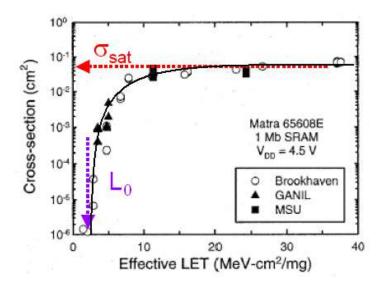

La section efficace permet de mesurer la sensibilité du circuit à tester (DUT) aux SEEs. Elle représente la surface sensible apparente du DUT :

$$\sigma_m(\phi) = \frac{N_e(\phi)}{\phi} \tag{9}$$

où  $\sigma_m$  est la section efficace en cm², Ne le nombre de SEEs en fonction de la fluence  $\Phi$  (en cm²) qui représente le nombre de particules incidentes par unité de surface durant la totalité du test.  $\sigma_m$  s'exprime aussi en barn, 1 barn =  $10^{-24}$  cm².

Les flux de particules sont considérés comme homogènes. La probabilité d'occurrence d'un SEE en une position donnée est perçue comme une variable stochastique. Plus la fluence est importante plus la section efficace est déterminée avec précision. La section efficace réelle peut ainsi s'écrire :

$$\sigma_r = \lim_{\phi \to \infty} \left( \frac{N_e(\phi)}{\phi} \right) \tag{10}$$

La mesure de la section efficace se fait pour plusieurs valeurs de LET, valeur modifiée en changeant d'énergie ou de type d'ions.

Figure 17 : Courbe de section efficace pour une mémoire bulk de 1 Mbits [FER04].

Les mesures sont souvent ajustées par une distribution de Weibull :

$$\sigma_{w}(L) = \begin{cases} \sigma_{sat}.(1 - e^{-\left(\frac{L - L_{0}}{W}\right)^{s}}) & pourL > L_{0} \\ 0 & pourL \le L_{0} \end{cases}$$

(11)

où  $\sigma_{sat}$  est la section efficace de saturation,  $L_0$  le LET seuil, W représente la largeur de la courbe et S est un paramètre de forme.  $L_0$  et  $\sigma_{sat}$  permettent de comparer les sensibilités des différents circuits ou systèmes testés.

En accélérateur de particules, le réglage du LET possède initialement une incertitude de 2% [ZAJ99]. De plus, le LET est une valeur moyenne, deux ions identiques frappant une même épaisseur ne déposeront pas la même énergie.

#### I.5.2. Les équipements de test

#### *I.5.2.1.* Les sites en altitude

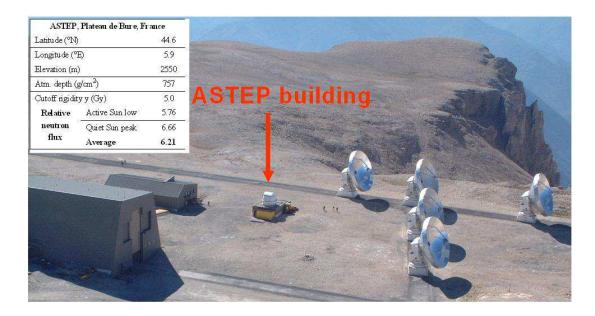

Pour réduire la durée des tests, une première solution consiste à les réaliser en environnement naturel, mais à une altitude élevée. En effet, le flux de neutrons étant plus important, les tests seront plus rapides qu'au niveau de la mer et leurs résultats statistiques s'en trouveront plus précis.

L'un de ces sites est français : l'ASTEP (Altitude See Test European Platform).

Figure 18: Plateforme ASTEP [AUT07].

#### I.5.2.2. Les accélérateurs de particules

Les accélérateurs de particules sont les instriments les plus couramment utilisés pour évaluer la sensibilité d'un circuit aux effets des radiations en milieu hostile. Le DUT est placé sous un faisceau d'ions de type, de charge et d'énergies connues. Son fonctionnement est contrôlé lors de l'irradiation pour détecter le nombre de SEEs. Le Tableau 3 donne un aperçu d'équipements existants.

Tableau 3: Liste non-exhaustive des accélérateurs de particules [BEZ04].

| Equipement       | Type d'accélérateur | Particules (et leurs énergies) |  |

|------------------|---------------------|--------------------------------|--|

| UCL, Belgique    | Cyclotron           | Ions lourds (> 10 MeV/n)       |  |

| OCL, Beigique    | Cyclotion           | Protons (< 65 MeV)             |  |

| JYFL, Finlande   | Cyclotron           | Ions lourds (> 10 MeV/n)       |  |

|                  | Cyclotion           | Protons (< 45 MeV)             |  |

| LBL, USA         | Cyclotus            | Ions lourds (> 10 MeV/n)       |  |

| LBL, USA         | Cyclotron           | Protons (< 55 MeV)             |  |

| PSI-OTIS, Suisse | Cyclotron           | Protons (< 63 MeV)             |  |

| PSI-HIF, Suisse  | Cyclotron           | Protons (< 300 MeV)            |  |

| CPO, France      | Synchrocyclotron    | Protons (< 200 MeV)            |  |

| TRIUMPH, Canada  | Cyclotron           | Protons (< 520 MeV)            |  |

| GANIL, France    | Cyclotron           | Ions lourds (> 100 MeV/n)      |  |

| TAMU, USA        | Cyclotron           | Ions lourds (> 1 GeV/n)        |  |

| GSI, Allemagne   | Cyclotron           | Ions lourds (> 1 GeV/n)        |  |

| CNPI, Russie     | Synchrocyclotron    | Protons (< 1 GeV)              |  |

Si ces accélérateurs sont couramment utilisés, ils n'en possèdent pas moins plusieurs inconvénients. En effet, les tests doivent se dérouler dans des chambres à vide, le composant sous test (DUT) doit donc être contrôlé à distance. Autre inconvénient, les faisceaux irradient la globalité de la carte de test, il est donc impossible de connaître l'endroit exact où à frapper la particule qui a provoqué un SEE. Enfin, deux autres soucis qui ne manquent pas d'irriter les industriels : le prix et l'accessibilité de ces structures. Entre 500\$ et 1000\$ de l'heure [LBN00] avec des réservations de plusieurs mois à l'avance.

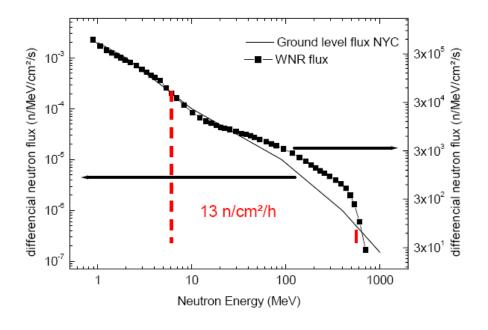

#### *I.5.2.3.* Les réacteurs à neutrons

Les neutrons n'étant pas des particules chargées, il est impossible de les accélérer via le champ magnétique d'un cyclotron. Des réacteurs à neutrons sont donc utilisés. Le plus puissant réacteur, situé au Los Alamos Neutron Science Center (LANSCE), accélère des protons jusqu'à 84% de la vitesse de la lumière. Lorsque ceux-ci frappent une cible de tungstène, des neutrons sont produits. Un compteur dans la chambre de test mesure le flux de neutrons.

Outre le fait que le LANSCE possède le plus puissant réacteur à neutrons, celui-ci est également très apprécié car il reproduit fidèlement le spectre d'énergie des neutrons atmosphériques naturels, avec un flux plus important. Une heure de test dans ce réacteur correspond à 15 753 années au niveau du sol.

Figure 19 : Spectre d'énergie des neutrons au LANSCE comparé au spectre au sol de New York [BAG07].

Bien entendu, il existe d'autres réacteurs à neutrons, certains d'entre eux ne produisent en revanche qu'un flux mono-énergétique de neutrons. Voici une liste des plus connus :

| Tableau 4: Liste non-exhaustive des réacteurs à neutrons [BAG07]. | • |

|-------------------------------------------------------------------|---|

|-------------------------------------------------------------------|---|

| Equipement                       | Energie   |

|----------------------------------|-----------|

| CEA, Valduc en France            | 14 MeV    |

| Delft Univ. Of Tech, Pays-Bas    | 14 MeV    |

| Svedberg Lab., Suède             | < 180 MeV |

| CYCLONE, Belgique                | < 80 MeV  |

| Inst. Paul Scherrer, Suisse      | <150 MeV  |

| Indiana Univ. Cyclotron Facility | < 160 MeV |

| Crocker Nuclear Lab, UC Davis    | < 65 MeV  |

| Boeing Radiation Effects Lab.    | 14 MeV    |

| Texas A&M                        | 14 MeV    |

| Triumf, Vancouver au Canada      | < 500 MeV |

# *I.5.2.4.* Les faisceaux laser impulsionnel

## I.5.2.4.1. L'interaction laser-silicium

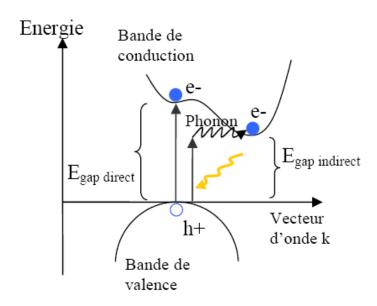

Dans un semi-conducteur, un photon dont l'énergie est supérieure à la largeur de la bande interdite (gap) peut être absorbé par un électron, le faisant passer de la bande de valence (BV) à la bande de conduction (BC). C'est l'effet photoélectrique d'absorption interbande.

Figure 20: Absorption de gap direct et indirect [LUU09]

IL existe deux manières pour un électron qui a absorbé un photon de passer de la BV à la BC.

L'absorption directe, qui nécessite que l'énergie du photon soit supérieure à la largeur de la bande interdite. Elle sera donc, pour le silicium, supérieure à  $E_{gdirect} = 3.41$  eV et sa longueur d'onde sera elle inférieure à 365 nm.

Une absorption indirecte est toutefois possible. En effet, pour un photon absorbé dont l'énergie est comprise entre  $E_{\text{gdirect}}$  et  $E_{\text{gindirect}}$ , l'électron peut également absorber un phonon pour atteindre la BC. La longueur d'onde maximum est alors donnée par :

$$\lambda_{gindirect} = \frac{\overline{h.C}}{E_{gindirect}} = 1110 \quad nm \tag{12}$$

Ces absorptions génèrent donc des paires électron-trou. Les électrons présents dans la BC peuvent eux aussi absorber des photons, les faisant ainsi accéder à des niveaux d'énergie plus importants, c'est l'auto-absorption. Ils retombent ensuite dans le bas de la bande par décroissance phononique (thermalisation). Ce processus est également possible pour les trous de la BV. Elle dépend directement du niveau de dopage.

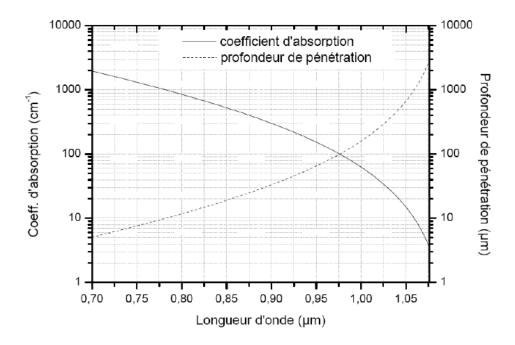

Figure 21 : Coefficient d'absorption et profondeur de pénétration dans du Si dopé P (<10<sup>17</sup> cm<sup>-3</sup>) [GER93]

Pour des champs élevés, des non-linéarités apparaissent. Ce nouveau phénomène d'absorption traduit la possibilité pour un électron d'absorber deux photons

simultanément. C'est l'absorption deux photons (ou TPA) qui doit être différenciée de l'auto-absorption. L'absorption TPA n'est possible que pour des intensités de faisceau très élevées, générées uniquement en régime impulsionnel.

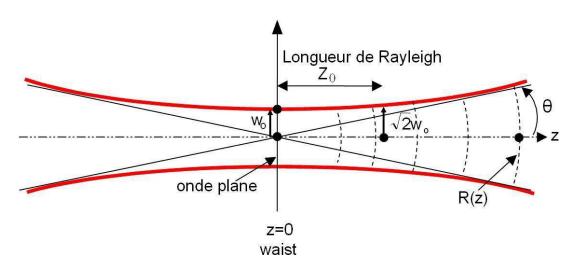

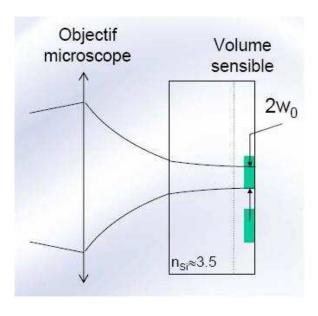

Le modèle le plus couramment utilisé pour décrire la structure transverse d'un faisceau laser est le faisceau gaussien [POU00] (équations en annexe). Dans la figure 22, le trait gras représente le rayon du faisceau (i.e. la frontière où l'intensité du faisceau est  $e^2$  fois plus faible qu'en son centre), Wo est le rayon minimal, Zo est le paramètre confocal situant la zone de transition entre un comportement d'onde quasi-plane et d'onde quasi-sphérique, et  $\theta$  est la divergence du faisceau.

Figure 22: Propagation d'un faisceau gaussien

## I.5.2.4.2. Equivalence entre ion lourd et impulsion laser

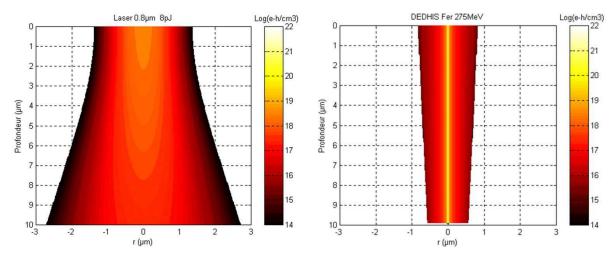

Les interactions ion-silicium et laser-silicium peuvent être comparées via leurs taux de génération de paires électron-trou exprimés en cm<sup>-3</sup>. Ces deux interactions seront considérées comme équivalentes si elles génèrent dans le volume de silicium la même quantité de porteurs de charge.

Figure 23 : Comparaison des distributions spatiales des paires électron-trou pour a) une impulsion laser et b) un ion fer [POU00]

Dans la figure 23 extraite de [POU00], les interactions dues à un ion Fe et une impulsion laser sont comparées. Un modèle gaussien linéaire a été utilisé pour l'impulsion laser, et le modèle DEDHIS (version améliorée du modèle cylindrique proposée par Vincent Pouget) est utilisé pour représenter la trace de l'ion. Bien que ces deux traces génèrent la même quantité de paires électron-trou, leurs profils s'avèrent très différents. L'impulsion laser est nettement plus étendue en volume, avec une densité maximale de charges sur l'axe environ 1000 fois plus faible, et une rapide décroissance en profondeur contrairement au taux de génération beaucoup plus uniforme observé le long de la trace de l'ion (l'échelle logarithmique amplifie artificiellement l'effet différentiel).

A partir de ces deux taux de génération, et en approximant le volume sensible à un parallélépipède rectangle de surface infinie et de profondeur d (méthode RPP vue ci dessus), l'approche ERPP permet de donner une équivalence entre les charges déposées dans ce volume. Par intégration du taux de génération sur le volume, il ressort [POU00] :

$$L_E = T.E_L.\frac{E_p}{E_{\gamma}}.\frac{1 - e^{-\alpha.d}}{d}$$

(13)

avec  $L_E$  étant le LET laser équivalent,  $E_L$  l'énergie de l'impulsion laser, et Ep l'énergie nécessaire à la création d'une paire électron-trou. Cette approche est bien entendue soumise aux mêmes limitations que le modèle RPP lui-même. C'est-à-dire la définition d'une profondeur arbitraire de volume sensible, profondeur à définir pour chaque technologie. Il est alors possible de définir un coefficient ERPP de proportionnalité entre le LET laser et le Let de l'ion:

$$L_E = K_e^d . E_L \tag{14}$$

Le tableau suivant donne les coefficients d'ERPP pour une profondeur  $d=1\mu m$ , dans le silicium, pour différentes énergies  $E_L$  exprimées en pJ.

Tableau 5: Coefficient d'ERPP dans le Silicium [POU00].

|                                                         | $\lambda = 0.8 \mu m$ | $\lambda = 1 \mu m$ | $\lambda = 1.06 \ \mu m$ |

|---------------------------------------------------------|-----------------------|---------------------|--------------------------|

| L <sub>E</sub> en MeV.cm <sup>2</sup> .mg <sup>-1</sup> | 3.85                  | 0.37                | 0.066                    |

| L <sub>E</sub> en MeV.μm <sup>-1</sup>                  | 0.89                  | 0.087               | 0.015                    |

I.5.2.4.3. Avantages et inconvénients du test sous faisceau laser

Tout d'abord, l'avantage premier du test sous faisceau laser est sa plus grande facilité d'accès comparée à un accélérateur de particule. Mais sa plus grande force est très certainement sa capacité à cartographier les défauts du DUT. Alors qu'un test en accélérateur irradiera le circuit dans son ensemble, le test laser permettra d'associer chaque réponse aux stimuli à une localisation.

En revanche, le test sous faisceau laser possède plusieurs limitations, la première étant qu'il n'est qu'une imitation de l'effet de particules ionisantes sur le DUT, et par conséquent que la possibilité d'une équivalence stricte avec un faisceau d'ion n'est pas encore démontrée. Bien que le test laser s'avère être un outil pertinent pour comparer la sensibilité de deux composants électroniques, un test final sous accélérateur de particules sera toujours nécessaire pour valider le comportement du circuit dans un environnement radiatif.

Le test sous faisceau laser est donc un excellent complément au test en accélérateur de particules, mais ne le remplace pas.

## I.5.3. Les méthodes de test

### *I.5.3.1.* Les normes de tests

Les tests de sensibilité aux radiations sont soumis à plusieurs normes. Dans le cas de l'étude de la sensibilité des systèmes électroniques embarqués à l'avionique, une norme doit être retenue :

**-JESD89A:** "Measurement and Reporting of Alpha particles and Terrestrial Cosmic Ray-induced Soft Errors in Semiconductor Devices". Publiée en octobre 2006 par JEDEC, cette norme décrit les différentes méthodes de tests pour évaluer le SER (Soft Error Rate) d'un composant soumis à l'environnement terrestre. Ce SER s'exprime en FIT (Failure In

Time). Un FIT correspond à une erreur toutes les 10<sup>9</sup> heures. Le seuil de fiabilité est fixé à 2000 FIT/Mbit.

Elle couvre les tests RTSER (Real Time SER) qui concernent les tests en temps réel et en environnement naturel, ainsi que les tests ASER (Accelerate SER) qui sont les tests menés en accélérateur de particules ou réacteur à neutrons.

Toutefois, si JESD89A est la seule norme, d'autres textes aiguilleront le testeur dans sa tâche, tels que l'ESCC25100 et l'ESCC22900 de l'ESA (European Space Agency) ou le TC107 d'IEC (International Electrotechnical commission).

## *I.5.3.2. Méthode de tests statiques et dynamiques*

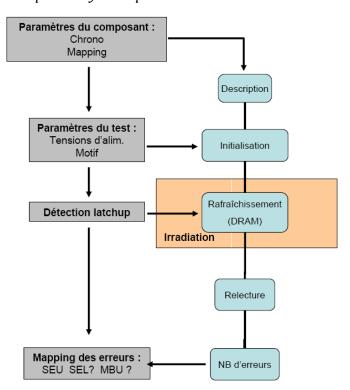

Le test statique est le plus simple. Le DUT est alimenté puis configuré selon un motif (tout à 1, tout à 0, damier...). Il est laissé dans une position de repos durant toute la durée de l'irradiation. Seuls des composants comme les DRAMs, qui nécessitent un rafraichissement régulier, subissent une modification. Une fois l'irradiation terminée, une relecture permet de comparer les bits qui ont été modifiés. La section efficace est alors calculée en fonction de la fluence.

Figure 24 : Diagramme de test statique [BAG07].

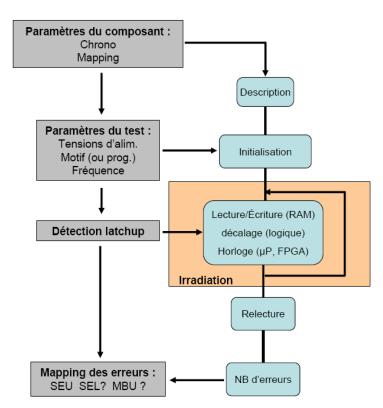

Le test dynamique est assez proche du test statique. Il se différencie par le fait que le DUT « travaille » durant l'irradiation. Une mémoire sera lue et écrite. Un processeur tournera sur une application. Et une relecture permettra de compter le nombre d'erreurs par rapport aux données attendues. Le test dynamique apporte la possibilité d'étudier l'influence de la fréquence de travail. De plus, un processeur pourra uniquement être testé avec une méthode dynamique.

Figure 25 : Diagramme de test dynamique [BAG07].

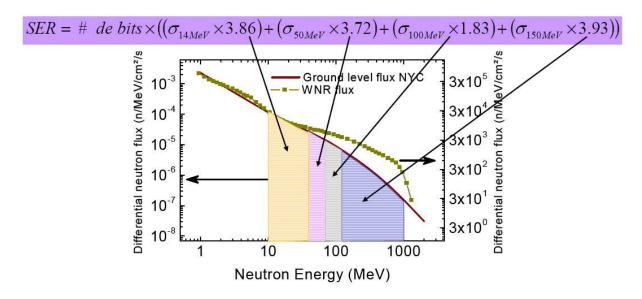

## I.5.3.3. Calcul du SER

Pour les mesures de SER sous flux de neutrons, quatre énergies sont recommandées par la norme JESD89A dans le cas des flux mono-énergétiques : 14 MeV, 50 MeV, 100 MeV et 150 MeV. Des tests sous réacteur doivent être menés à chaque énergie, de manière à calculer la section efficace qui leur est liée. Il est ensuite possible de calculer le SER du composant.

Figure 26: Formule du SER [BAG07].

La formule est cependant différente pour le flux de neutrons disponible au LANSCE. Celui balayant l'ensemble du spectre énergétique, un seul test et donc une seule mesure de section efficace suffit pour calculer le SER.

$$SER[Upset/h] = \sigma[cm^2/bit] \times 13[/cm^2/h] \times N_{bits}$$

(15)

Toutefois, à partir d'une certaine énergie, les tests ne sont plus effectués avec des neutrons. En effet, pour des énergies supérieures à 50 MeV, l'ionisation directe engendrée par les protons est négligeable devant l'ionisation indirecte de leurs particules secondaires qu'ils créent à l'instar des neutrons. Les protons étant plus faciles à manipuler grâce à leur charge, ils sont alors privilégiés pour réaliser des tests de sensibilité aux neutrons atmosphériques.

## I.5.4. Les SDRAMs faces aux SEEs

Les cellules DRAMs peuvent voir leur valeur logique modifiée par une particule ionisante, qu'elle soit primaire ou secondaire. La charge déposée par cette particule est capable de forcer la charge du condensateur intégré ou de la décharger en perturbant le transistor qui lui est lié. Par ailleurs, [NOR06] constate que les DRAMs sont plus sensibles aux neutrons thermiques que d'autres composants de même niveau technologique. Cette sensibilité semble toutefois diminuer avec la réduction de la longueur de grille. Il encourage cependant les fondeurs à multiplier les tests sous flux de neutrons thermiques pour en quantifier les effets.

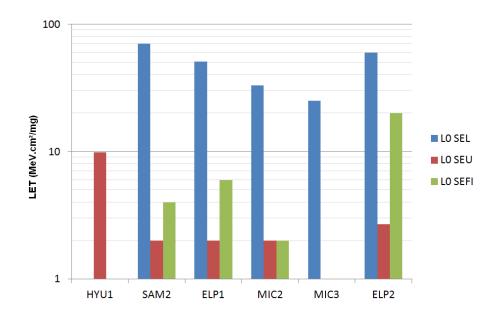

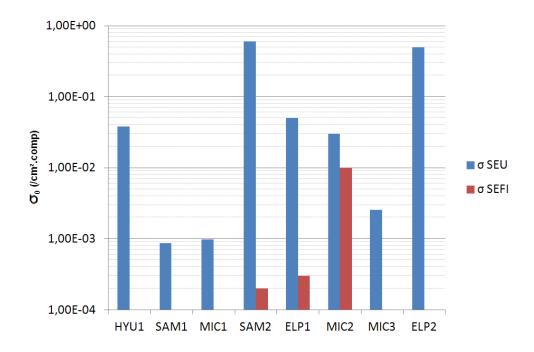

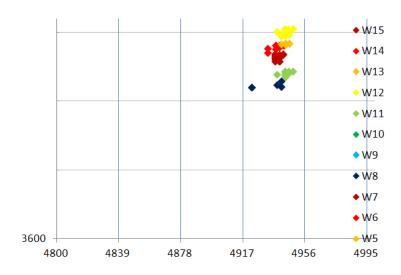

Le Tableau 6 récapitule les références de mémoires SDRAMS testées. Leurs étiquettes sont utilisées dans la Figure 27 et la Figure 28 pour une lecture plus aisée.

| Année | Composant       | Fabricant | Techno. | Equipement | Etiquette |

|-------|-----------------|-----------|---------|------------|-----------|

| 2000  | HY57V654020B    | Hyundai   |         | TAM        | HYU1      |

| 2006  | K4S510432M      | Samsung   |         | BREL       | SAM1      |

| 2006  | MT48LC128M4A2   | Micron    |         | BREL       | MIC1      |

| 2007  | K4T1G044QA-ZCD5 | Samsung   | 90 nm   | IUCF/TAM   | SAM2      |

| 2007  | EDE1104AB-50-E  | Elpida    | 90 nm   | IUCF/TAM   | ELP1      |

| 2007  | MT47H128M8HQ-3E | Micron    | 80 nm   | TAM        | MIC2      |

| 2007  | MT48LC16M16A    | Micron    |         | BNL        | MIC3      |

| 2008  | EDS5108ABTA     | Elpida    |         | NRL/TAM    | ELP2      |

Tableau 6: Extrait des Compendia [OBR08], [ALL08] et [OBR09].

Dans la Figure 27, les LET sont exprimés en [MeV.cm²/mg]. Elle montre la tendance qu'à le LET seuil à diminuer au fur et à mesure que le nœud technologique se rétrécie.

Figure 27: LET seuil des mémoires SDRAMS mesurés [OBR08], [ALL08] et [OBR09].

Dans la Figure 28, les sections efficaces sont exprimées en cm<sup>-2</sup> par composant, pour des fluences de 1.10<sup>7</sup> part/cm<sup>2</sup>. L'évolution de la section efficace est d'une part due à la réduction de la taille des cellules mémoires et donc de la surface physique pour une capacité logique égale. D'autre part elle est due à la réduction de la tension d'alimentation qui facilite la corruption de point mémoire. L'augmentation de la section efficace SEFI peut s'expliquer par l'augmentation de la fréquence de travail des composants. Ces deux dernières figures éclairent sur les tendances et les ordres de grandeurs des deux paramètres principaux lors de l'évaluation de la sensibilité d'un composant.

Figure 28 : Section efficace des mémoires SDRAMS mesurés [OBR08], [ALL08] et [OBR09].

# I.5.5. Les MRAMs faces aux SEEs

Les MRAMs sont souvent présentées comme l'avenir des mémoires. Non-volatiles, avec un degré d'intégration similaire aux SDRAMs et une consommation moindre, elles cumulent bien des qualités. Mais leur principe physique différent des mémoires classiques, comment réagissent elles face aux environnements radiatifs ?

Les travaux menés sur les MRAMs dans ce domaine sont prometteurs. En effet, lors des mesures menées par T. R. Oldham consignées dans [OBR08], aucun SEU ni SEFI n'ont été détectés lors de l'irradiation de la MRAM MR2A16A de Freescale sous un flux de protons de 89 et 198 MeV à l'IUCF. De la même manière, [KAT09] montre l'immunité d'une MRAM de 1 Mbit à des ions lourds de LET allant jusqu'à 69 MeV.cm²/mg, ainsi qu'à dose d'ionisation totale de 1 Mrad.

D'autres mesures ont été menées par [NUN08] sur une MRAM MR2A16A. Elles incluent des tests sous flux d'ions lourds, de protons d'énergie 200 MeV et sous faisceau laser.

| Ion                            | Facility | Energy (MeV)              | LET<br>(MeV.cm <sup>2</sup> /mg) | Range<br>(µm) |

|--------------------------------|----------|---------------------------|----------------------------------|---------------|

| $^{13}C^{4+}$                  | UCL      | 131                       | 1.2                              | 266           |

| <sup>22</sup> Ne <sup>1+</sup> | UCL      | 235                       | 3.3                              | 199           |

| $^{40}Ar^{12+}$                | UCL      | 372                       | 10.1                             | 119           |

| $^{58}Ni^{17+}$                | UCL      | 500                       | 21.9                             | 85            |

| $^{83}Kr^{25+}$                | UCL      | 756                       | 32.4                             | 92            |

| <sup>208</sup> Pb              | GANIL    | 5037<br>(24.22 MeV/nucl.) | 72.5                             | 250           |

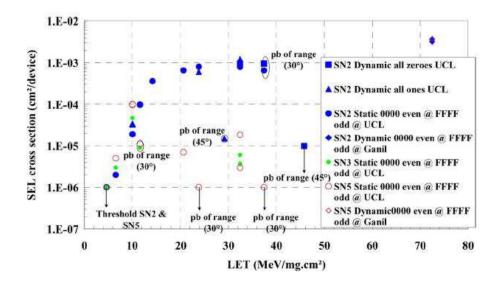

Figure 29 : Ions lourds utilisés lors des tests de [NUN08].

Figure 30 : Section Efficace SEL de la MR2A16A selon [NUN08].(Une flèche signifie l'absence de SEL)

Des SELs ont donc été détectés lors des tests sous flux d'ions lourds. Les relevés de courants révèlent que les pics d'intensité des 784 événements recensés sont centrés autour de 70 mA.

En revanche, aucun SEL, ni SEU, n'a était détecté lors de l'irradiation sous protons de 200 MeV par [NUN08].

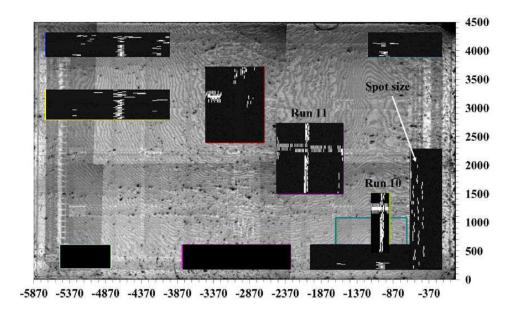

Les tests sous faisceau laser, qui permettent une cartographie des événements, révèlent que les zones sensibles de la MRAM ne sont pas les cellules elles-mêmes, mais la logique périphérique qui les entoure et permet l'adressage des données.

Figure 31 : Cartographie des SELs de la MR2A16A [NUN08]. (Dimensions en  $\mu m)$

# I.5.6. Les processeurs faces aux SEEs

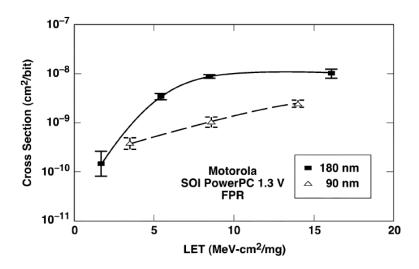

Les travaux de [IRO06] donnent un bon aperçu des tendances des comportements des microprocesseurs utilisant la technologie SOI (Silicon On Insulator) vis-à-vis des SEUs. Il a été montré que grâce à leur volume sensible amoindri, les systèmes en technologie SOI possédaient des sections efficaces de saturation d'un ordre de grandeur inférieur à celles des systèmes en technologie Bulk plus classiques. En effet, la technologie SOI permet de réduire de manière significative l'effet de collection par diffusion des paires électron-trou générées par les particules ionisantes.

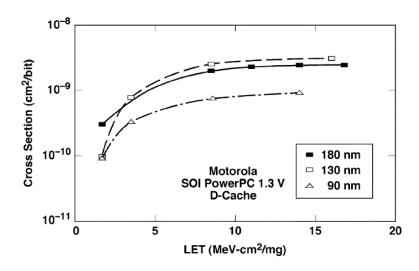

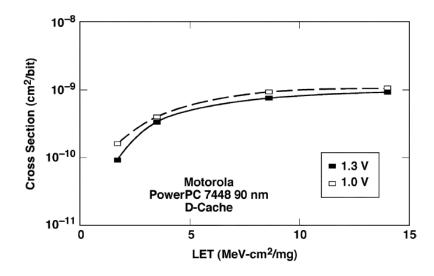

[IRO06] évalue la sensibilité aux SEU d'un PowerPC de Motorola de technologie SOI 90 nm et le compare aux PowerPCs de générations précédentes (130 et 180 nm). Trois mesures sont menées :

**-D-Cache Measurement :** La D-Cache, initialisée avec un pattern connu, est réécrite avec un pattern distinct du premier lors de l'irradiation. Le comptage des SEUs se fait lors de la relecture.

**-Register Measurements :** Le processeur effectue une boucle infinie contenant une unique instruction. Elle s'interrompt toute les demi-secondes pour écrire une copie des registres dans la mémoire physique. Une comparaison est effectuée après irradiation avec le pattern de référence.

PowerPC Techno. (nm) Alimentation (V) Fréquence max (MHz) 7455 180 1000 1.6 7455 180 1.3 800 7457 130 1.3 1200 7457 130 1.1 1000 7448 90 1.3 1600 7448 90 1.0 1000

Tableau 7: Résumé des PowerPC Motorola testé par [IRO06].

Les tests sont effectués sous un flux d'ions lourds : <sup>20</sup>Ne et <sup>40</sup>Ar de LET initial respectivement 1.7 et 3.8 MeV.cm<sup>2</sup>/mg.

Figure 32: Section efficace FPR pour les Motorola 7448 et 7455 [IRO06].

Figure~33: Section~efficace~D-Cache~pour~les~Motorola~7448, 7455~et~7457~[IRO06].

La section efficace par bit diminue donc avec la diminution de taille de grille en technologie SOI.

Figure 34 : Effet de l'alimentation sur la section efficace D-Cache du 7448 [IRO06].

En revanche, la technologie SOI n'empêche pas la section efficace d'augmenter avec la diminution de la tension d'alimentation de cœur.

Tableau 8: Résumé des composants mesurés par [IRO06].

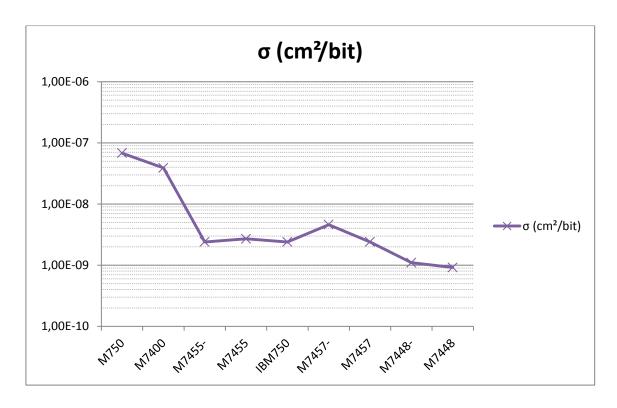

| Composant     | Techno. (nm) | Epaisseur du film de Si (nm) | Alimentation (V) |

|---------------|--------------|------------------------------|------------------|

| Motorola 750  | 290          | Bulk                         | 2.5              |

| Motorola 7400 | 200          | Bulk                         | 1.8              |

| Motorola 7455 | 180          | 110                          | 1.3              |

| Motorola 7455 | 180          | 110                          | 1.6              |

| IBM 750FX     | 130          | 117                          | 1.4              |

| Motorola 7457 | 130          | 55                           | 1.1              |

| Motorola 7457 | 130          | 55                           | 1.3              |

| Motorola 7448 | 90           | 55                           | 1.0              |

| Motorola 7448 | 90           | 55                           | 1.3              |

La Figure 35 montre les résultats obtenus lors des mesures des composants listés dans le Tableau 8. On peut y constater les mêmes tendances qu'expliquer précédemment sur la Figure 28.

Figure 35 : Section efficaces des composants mesurés par [IRO06].

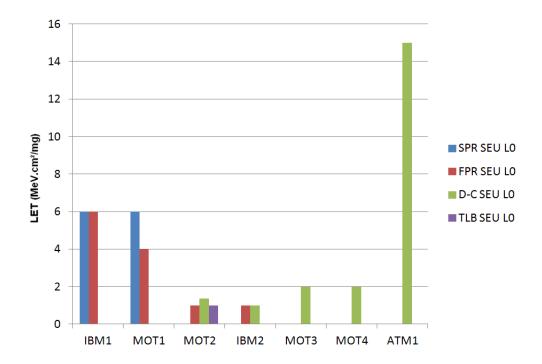

Le Tableau 9 consigne un ensemble microprocesseurs 32 bits précédemment testés sous flux d'ions lourds.

Composant **Fabricant** Equipement Etiquette Année Fonction 2001 PPC750 CPU IBM TAM IBM1 2001 PPC750 CPU **IBM** UCD/IUCF 2001 XPC750 CPU Motorola TAM MOT1 2001 XPC750 CPU Motorola UCD/IUCF 2001 PowerPC 7455 CPU **IUCF** Motorola MOT2 PowerPC 7455 2001 CPU Motorola TAM2001 PowerPC 750Fx CPU **IBM IUCF** IBM2 2001 PowerPC 750Fx CPU TAM **IBM** 2002 PowerPC 7457 CPU TAM Motorola MOT3 PowerPC 7448 TAM 2006 PowerPC Motorola MOT4 2006 SPARTSC695F Processor Atmel TAM ATM1

Tableau 9: Extrait des Compendia [OBR08] et [ALL08].

Les microprocesseurs et les PowerPC doivent être testés en fonction de l'application qu'ils exécutent. Ainsi chaque test va mettre en exergue les erreurs liées à un bloc particulier, tels que les registres de configuration, l'unité arithmétique ou la mémoire cache.

Glossaire d'abréviations: SPR = Special purpose register

Chapitre 1 : Etat de l'art des environnements radiatifs, de leurs effets et des moyens de test

FPR = Floating point register

D-C = Data cache

TLB = Translation Lookaside Buffer

La Figure 36 montre les LET seuils pour chacun des processeurs et ce pour différents blocs testés. La mémoire cache est le bloc le plus simple à tester et elle représente la majeur partie de la surface du composant. Elle est donc souvent le bloc testé en priorité.

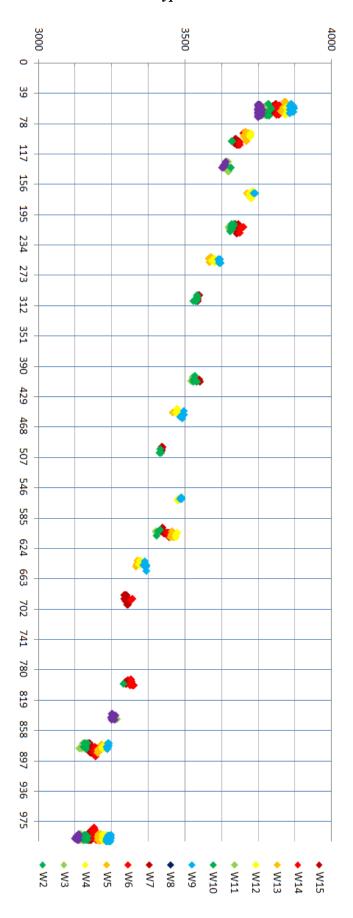

Figure 36: LET seuil des composants extrait des compendia [OBR08] et [ALL08].

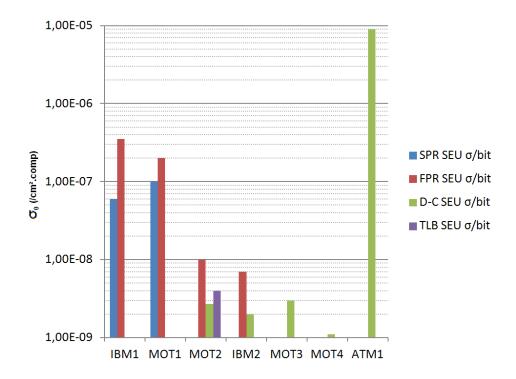

La Figure 37 expose les sections efficaces des composants des compendia, avec le détail par bloc testés. Les sections efficaces sont exprimées en cm<sup>-2</sup> par composant, pour des fluences de 1.10<sup>7</sup> part/cm<sup>2</sup>.

Figure 37: Sections efficaces des composants extraits des compendia [OBR08] et [ALL08].

## I.6. Les outils de simulation

Plusieurs outils de simulation ont été développés depuis la découverte des SEEs dans les années 1970. Si ces outils ne peuvent caractériser avec certitude la fiabilité d'un composant, ils permettent souvent une prédiction fiable de sa sensibilité aux phénomènes radiatifs.

## I.6.1. GEANT4

GEANT4 (GEometry ANd Tracking) est un ensemble d'outils permettant de simuler le passage de particules à travers la matière. C'est la dernière version de l'outil GEANT développé en 1974 par le CERN. Il intègre plusieurs paramètres comme : la trace, la géométrie, les modèles physiques et les collisions. L'approche physique est très complète comprenant à la fois les interactions électromagnétiques, hadroniques et optiques. Elle inclut également une large gamme de particules, matériaux et éléments avec des énergies pouvant aller de 250 eV jusqu'à quelques TeV.

GEANT4 a été conçu pour expliquer les modèles physiques utilisés, gérer des géométries complexes et s'adapter de manière optimale pour différentes applications. Ce bouquet de logiciel est le résultat d'une collaboration mondiale entre physiciens et informaticiens. Il a été créé en exploitant les connaissances en programmation orientée objet et implémenté en langage C#.

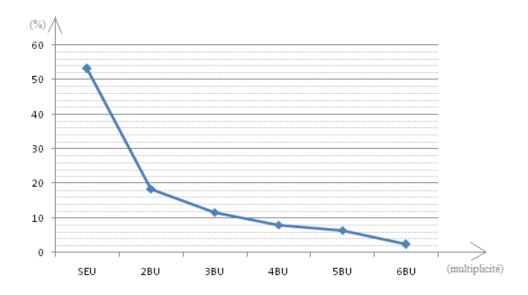

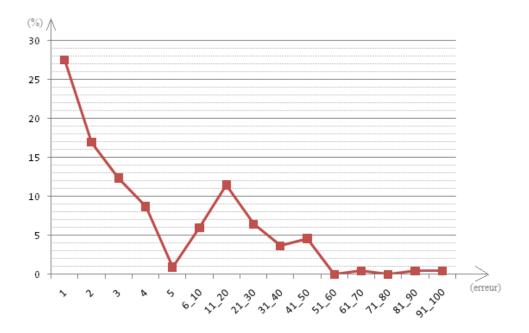

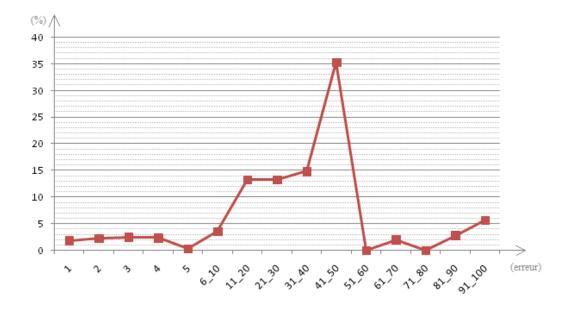

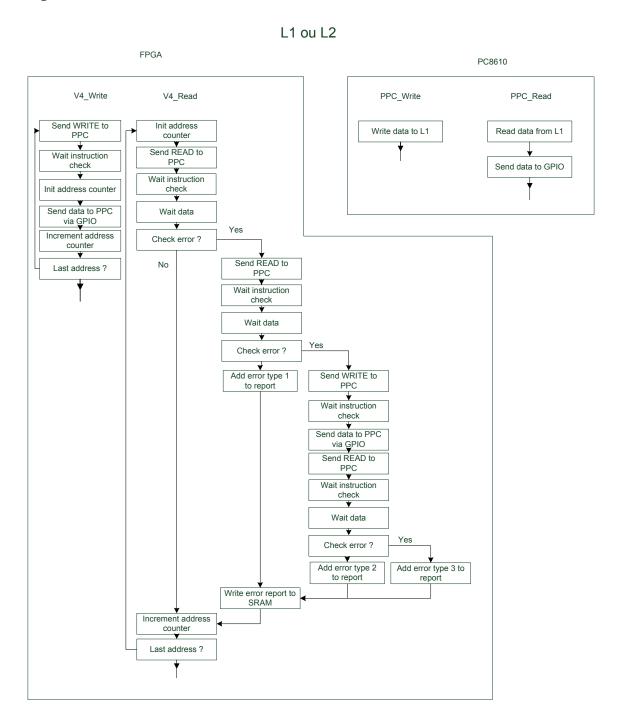

## *I.6.2. SRIM*