# Study and improvement of radiation hard monolithic active pixel sensors of charged particle tracking

Xiaomin Wei

#### ▶ To cite this version:

Xiaomin Wei. Study and improvement of radiation hard monolithic active pixel sensors of charged particle tracking. Other [cond-mat.other]. Université de Strasbourg, 2012. English. NNT: 2012STRAE044. tel-00953382

## HAL Id: tel-00953382 https://theses.hal.science/tel-00953382

Submitted on 28 Feb 2014

HAL is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

N° d'ordre: xxxx

#### École Doctorale de Physique et Chimie-Physique de l'Université de Strasbourg

UDS - IPHC - CNRS/IN2P3

# **THÉSE**

Présentée pour obtenir le grade de

### Docteur de l'Université de Strasbourg

Discipline : Électronique, Électrotechnique et Automatique

Spécialité : Instrumentation et Microélectronique

par

### **Xiaomin WEI**

# Study and Improvement of Radiation Hard Monolithic Active Pixel Sensors for Charged Particle Tracking

Soutenue publiquement le 18 décembre 2012 devant le jury:

Directeur de thèse: Yann HU Professeur, UDS, Strasbourg, France

Co-directeur de thèse: Deyuan GAO Professeur, NPU, Xi'an, China

Rapporteur externe: Michel PAINDAVOINE Professeur, UB, Dijon, France

Rapporteur externe: Guican CHEN Professeur, XJTU, Xi'an, China

Examinateur: Christine HU-GUO Ingénieur, IPHC, Strasbourg, France

Examinateur: Tingcun WEI Professeur, NPU, Xi'an, China

# **Contents**

| Content | ts       |                                                  | II  |

|---------|----------|--------------------------------------------------|-----|

| List of | Figures  |                                                  | IV  |

| List of | Tables . |                                                  | X   |

| Acknov  | vledgm   | ents                                             | XI  |

| Résumé  | Ş        |                                                  | XII |

|         |          |                                                  |     |

| 1 Intro | oductio  | n                                                | 1   |

| 1.1     | Char     | ged Particle Tracking in HEP                     | 1   |

|         | 1.1.1    | High Energy Physics                              |     |

|         | 1.1.2    | Particle Detection                               | 2   |

|         | 1.1.3    | Charged Particle Tracking                        | 3   |

| 1.2     | Dete     | ector Technologies for Charged Particle Tracking | 7   |

|         | 1.2.1    | Microstrip Detector                              | 8   |

|         | 1.2.2    | Hybrid Pixel Sensors                             | 9   |

|         | 1.2.3    | Charge-Coupled Device                            | 10  |

|         | 1.2.4    | DEPleted Field Effect Transistors                | 12  |

|         | 1.2.5    | Monolithic Active Pixel Sensors                  | 13  |

| 1.3     | App      | lications of MAPS in HEP                         | 14  |

|         | 1.3.1    | Why MAPS?                                        | 14  |

|         | 1.3.2    | Example of HEP experiments – STAR experiment     | 15  |

| 1.4     | Wor      | k Proposal and Thesis Layout                     | 18  |

| 2 Mai   | n Radia  | ntion Effects on MAPS                            | 21  |

| 2.1     | HEP      | Radiation Environment                            | 21  |

| 2.2     | Intro    | duction to Radiation                             | 22  |

|         | 2.2.1    | Type of Radiation                                | 22  |

|         | 2.2.2    | Radiation Quantities                             | 23  |

| 2.3     | Radi     | ation Effects on MAPS                            | 24  |

|         | 2.3.1    | Radiation Effects in different materials         | 24  |

|         | 2.3.2    | Main Radiation Effects on MAPS                   | 27  |

| 2.4     | Cond     | clusion                                          | 36  |

| 3 Rad   | iation I | Hardness Study on MAPS                           | 37  |

| 3.1     | Princ    | ciple of MAPS                                    | 37  |

| 3.2     | Char     | racteristics of MAPS                             | 42  |

|         | 3.2.1    | Charge Collection Efficiency                     | 42  |

|         | 3.2.2    | Charge to Voltage Conversion Gain                | 42  |

|         | 3.2.3    | Noise                                            | 44  |

|         | 3.2.4    | Spatial Resolution                               | 46  |

|         | 3.2.5    | Time Resolution                                  | 47  |

|         | 3.2.6    | Detection Efficiency                             |     |

|         | 3.2.7    | Radiation Tolerance                              | 48  |

| 3 3     | Radi     | ation Hard Study of MAPS                         | 48  |

#### Contents

|    | 3.3.1     | Introduction to SB pixel                               | 49   |

|----|-----------|--------------------------------------------------------|------|

|    | 3.3.2     | Primary Radiation Hardness Evaluation                  | 49   |

|    | 3.3.3     | Non-ionizing Radiation Hard Study                      | 56   |

|    | 3.3.4     | Ionizing Radiation Hard Design                         |      |

|    | 3.3.5     | Conclusion                                             |      |

| 4  | Improveme | ent of the MAPS Radiation Hardness by Memory Design    | 69   |

|    | 4.1 Fast  | Readout MAPS                                           | 69   |

|    | 4.1.1     | Architecture                                           | 69   |

|    | 4.1.2     | Pixel and Discriminator                                | 70   |

|    | 4.1.3     | Zero Suppression                                       | 74   |

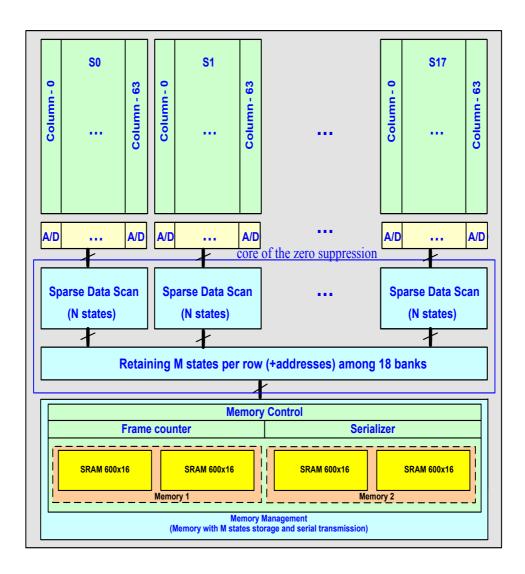

|    | 4.1.4     | Performance                                            |      |

|    | 4.2 Rad   | iation Tolerance of the Fast Readout MAPS              | 79   |

|    | 4.3 Des   | ign of Radiation Hard SRAM                             | 82   |

|    | 4.3.1     | Introduction to SRAM                                   | 82   |

|    | 4.3.2     | Analysis of Prevailing Radiation Hard Design Method    |      |

|    | 4.3.3     | Prototype Design                                       |      |

|    | 4.4 Des   | ign of Radiation Hard SRAM with enhanced SEU tolerance |      |

|    | 4.4.1     | Circuit Design                                         |      |

|    | 4.4.2     | Experimental Results                                   | 109  |

|    | 4.5 Prop  | oosal of a Dual-Port Memory Based on a 2T Cell         |      |

|    | 4.5.1     | Proposal of using DRAM Cell                            |      |

|    | 4.5.2     | Design of a 2T Cell                                    |      |

|    | 4.5.3     | Design of a Memory Based on the 2T Cell                |      |

|    | 4.6 Con   | clusion                                                |      |

| 5  | MAPS Rac  | diation Hardness with New Available Processes          | 121  |

|    | 5.1 MA    | PS with High Resistivity Epitaxy Process               | 121  |

|    |           | PS using a Small Feature Size Process                  |      |

|    | 5.3 MA    | PS with 3D Integrated Technology                       | 125  |

|    | 5.3.1     | Introduction to 3D Integrated Technology (3DIT)        | 125  |

|    | 5.3.2     | Advantages of MAPS using 3DIT                          |      |

|    | 5.3.3     | MAPS using 3DIT                                        |      |

|    | 5.4 Con   | clusion                                                | 129  |

| 6  |           | and Perspectives                                       |      |

| Bi |           |                                                        |      |

|    | 0 1 1     |                                                        |      |

|    |           | nd Communications                                      | 1/12 |

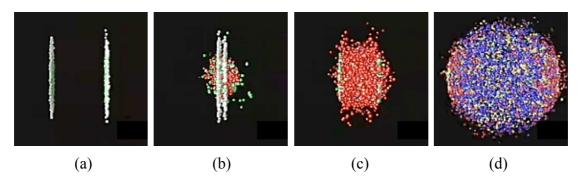

| Fig. 1-1. Heavy Ion Collisions at RHIC. (a) Ions about to collide, (b) Ion collision, (c) |

|-------------------------------------------------------------------------------------------|

| Quarks, gluons freed, (d) Plasma created. [2]                                             |

| Fig. 1-2. Elementary particles in the Standard Model                                      |

| Fig. 1-3. Schematic view of particles going through a particle detector consisting four   |

| sub-detectors including tracking chamber, electromagnetic calorimeter                     |

| hadron calorimeter and muon chamber from inside to outside. [3]                           |

| Fig. 1-4. Detection of a pentquark                                                        |

| Fig. 1-5. Stopping power for positive muons in copper as function of $\beta\gamma$ [5]    |

| Fig. 1-6. Energy loss for electrons, muons, pions, protons, deuterons and alpha           |

| particle in air [4]5                                                                      |

| Fig. 1-7. View of a silicon microstrip detector                                           |

| Fig. 1-8. View of a hybrid pixel sensor                                                   |

| Fig. 1-9. Cross section view of charge coupled device                                     |

| Fig. 1-10. Transport of charge packets in CCD. The charge packets are transported as      |

| processes (a)-(f) under the timing of the phase control (g)                               |

| Fig. 1-11. Structure of DEPFET pixel [17]                                                 |

| Fig. 1-12. Schematic of charge sensing element in MAPS. [9]                               |

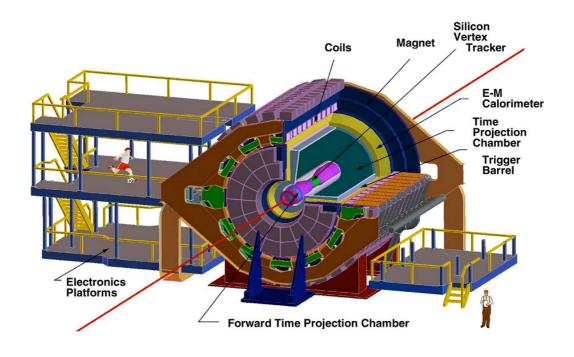

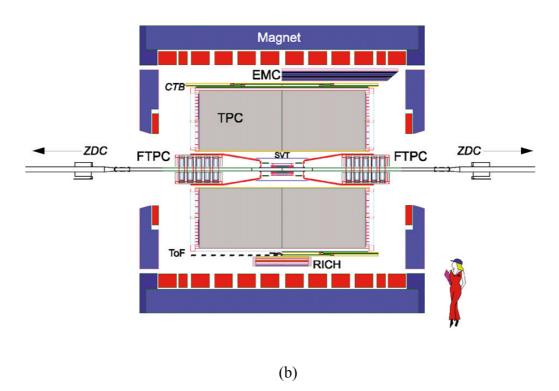

| Fig. 1-13. STAR detector. (a) perspective view, (b) Cross section view as configured      |

| in 2001. [23]                                                                             |

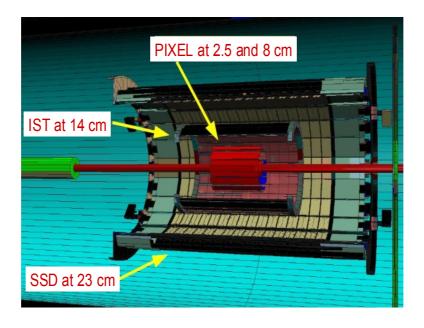

| Fig. 1-14. STAR Heavy Flavor Tracker                                                      |

|                                                                                           |

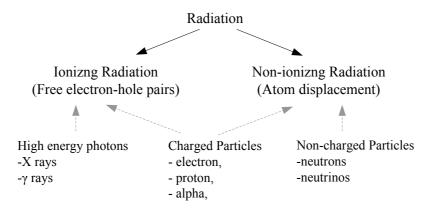

| Fig. 2-1. Type of radiation 22                                                            |

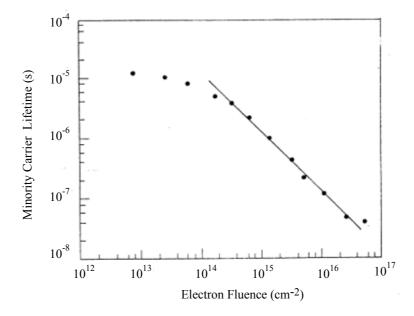

| Fig. 2-2. Minority carrier lifetime of holes in N-type silicon caused by 1 MeV            |

| electron irradiation. [33]                                                                |

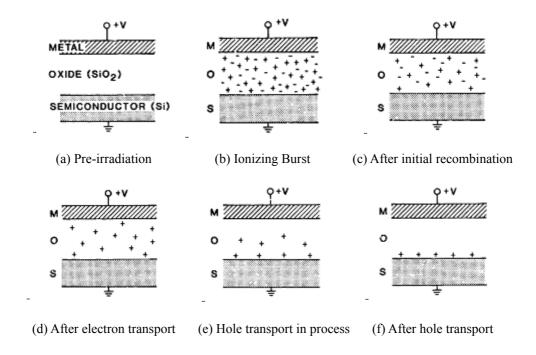

| Fig. 2-3. Illustration of initial recombination, hole transport and long-term trapping    |

| near SiO2/Si interface.[34]26                                                             |

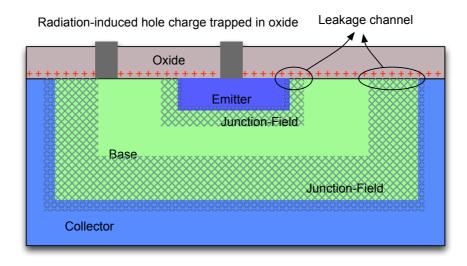

| Fig. 2-4. Schematic of radiation induced charge traps and leakage channel in a bipola     |

| transistor                                                                                |

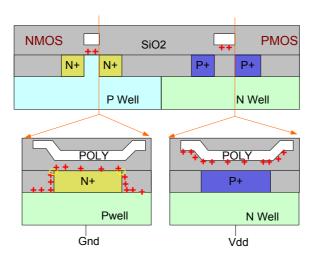

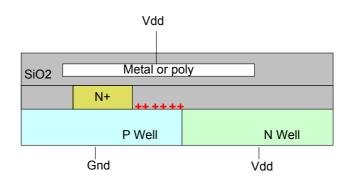

| Fig. 2-5. Schematic of TID-induced positive charge in NMOS and PMOS transistors           |

| The lower ones are the cross sections of the upper ones in the lined place.29             |

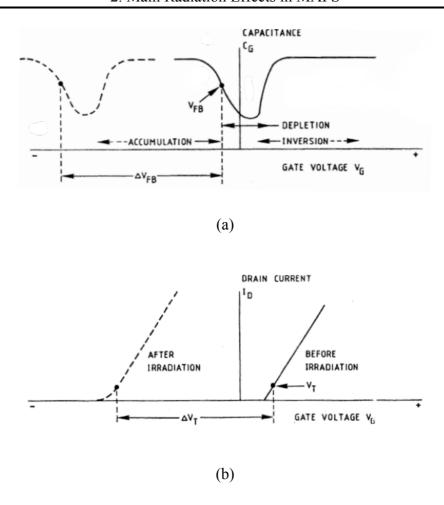

| Fig. 2-6. Typical variation of capacitance (a) and drain current (b) with gate voltage    |

| showing the shifts in flatband and in threshold voltage due to rapped charge              |

| (no interface states) [33]30                                                              |

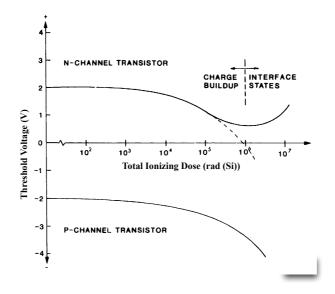

| Fig. 2-7. The effects of ionizing radiation (gamma) on the threshold voltage of MOS       |

| transistors [34]30                                                                        |

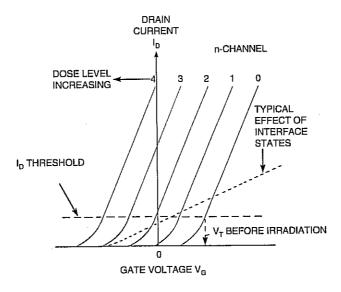

| Fig. 2-8. Typical drain current (ID) versus gate voltage (VG)       |                           |

|---------------------------------------------------------------------|---------------------------|

| subjected to the increasing radiation dose.[33]                     | 31                        |

| Fig. 2-9. Radiation-induced leakage path between n-diffusion        | and n-well in CMOS        |

| technology.                                                         | 32                        |

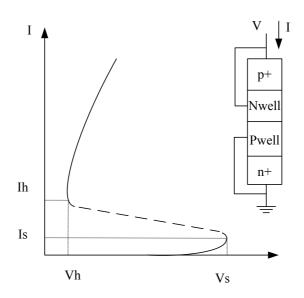

| Fig. 2-10.Parasitic SCR in an CMOS inverter                         | 34                        |

| Fig. 2-11.I-V characteristic of a silicon rectifier                 | 34                        |

| Fig. 3-1. Simplified block diagram of primary MAPS.[27]             | 37                        |

| Fig. 3-2. Sketch of the structure of MAPS for charged 1             | particle tracking. The    |

| charge-collecting element is an n-well/ p-epitaxy                   | diode. Because of the     |

| difference in doping levels (about three orders of a                | magnitude), the p-well    |

| and the p++ substrate act as reflective barriers. The               | generated electrons are   |

| collected by the n-well. [27]                                       | 38                        |

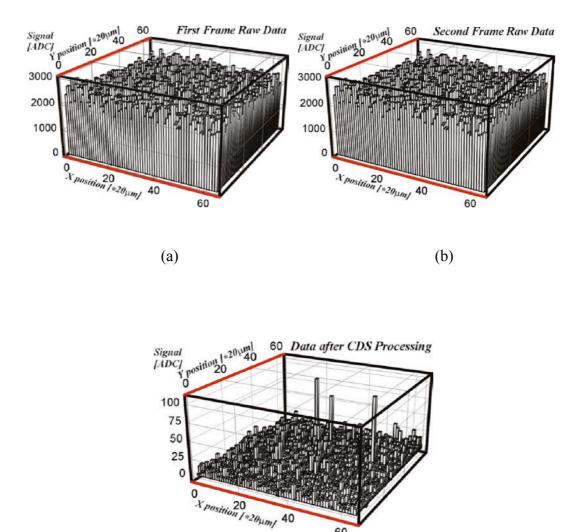

| Fig. 3-3. Correlated double sampling. (a) the first frame raw       | v data, (b) the second    |

| frame raw date, (c) the data after CDS processing [27               | <sup>'</sup> ]40          |

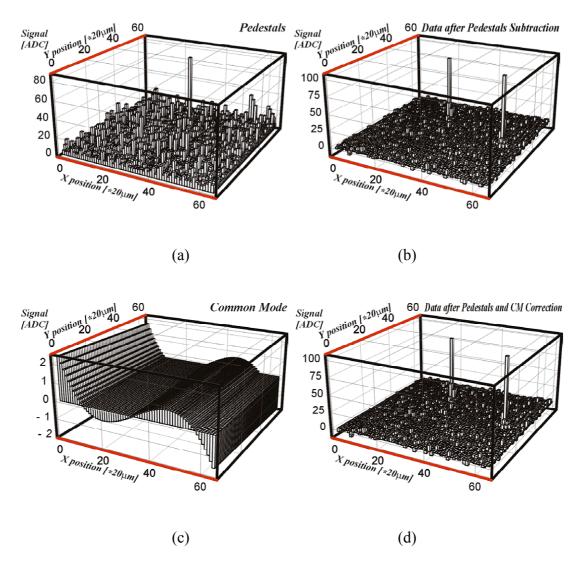

| Fig. 3-4. Data processing after CDS. (a) Pedestals, (b) Data after  | er pedestals subtraction  |

| (c) Common mode shift calculated for the analyzed                   | d event, (d) Data after   |

| pedestals and common mode shift subtraction.[27]                    | 41                        |

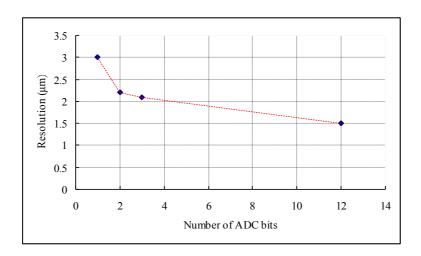

| Fig. 3-5. Resolution versus with number of ADC bits (MIMOS          | A I) [39]46               |

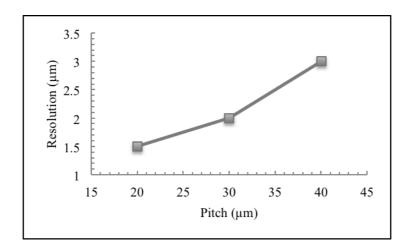

| Fig. 3-6. The spatial resolution of MAPS as a function the          | • •                       |

| 9).[40]                                                             | 47                        |

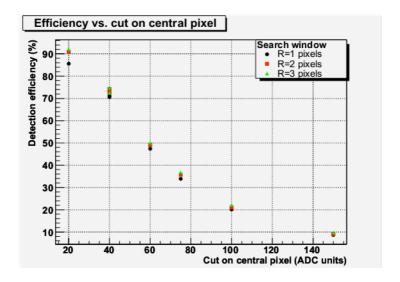

| Fig. 3-7. Detection efficiency as a function of the cuts applied    | on the pixel signal and   |

| search window radius.[41]                                           | 48                        |

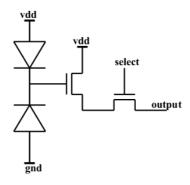

| Fig. 3-8. Scheme of a self-biased pixel.                            | 49                        |

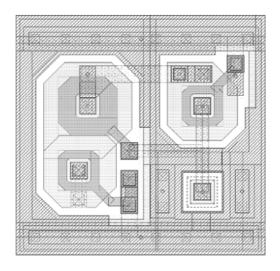

| Fig. 3-9. Single pixel layout with enclosed NMOS transistors a      | and n-well/p-epi charge   |

| sensing diode                                                       | 50                        |

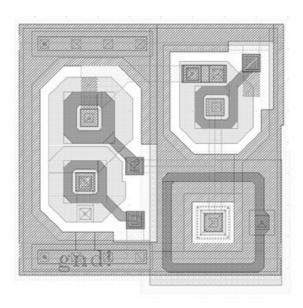

| Fig. 3-10. Single pixel layout with enclosed NMOS transis           | stors and n-well/p-epi    |

| charge sensing diode designed for radiation hardnes                 | s test with poly-silicon  |

| belt around the diode.                                              |                           |

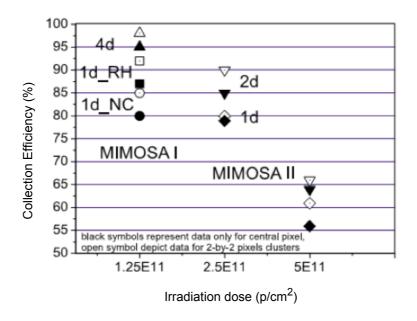

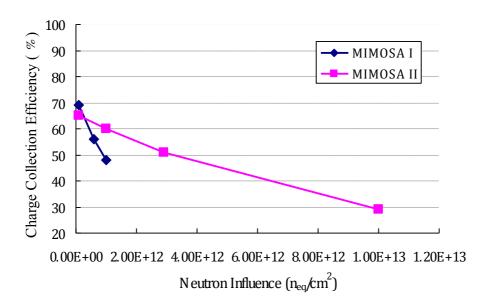

| Fig. 3-11. Collected charge (normalized to the initial sample       | e measurements) after     |

| irradiation with protons for MIMOSA I and MIMOS                     | A II, for different pixel |

| configuration implemented inside.[42]                               | 52                        |

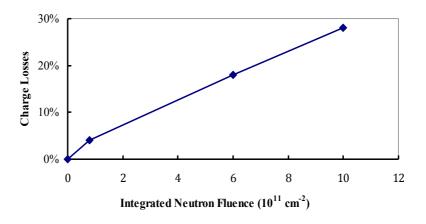

| Fig. 3-12. Collected charge losses as a function of neutron flue 52 | ence[42]. (MIMOSA I)      |

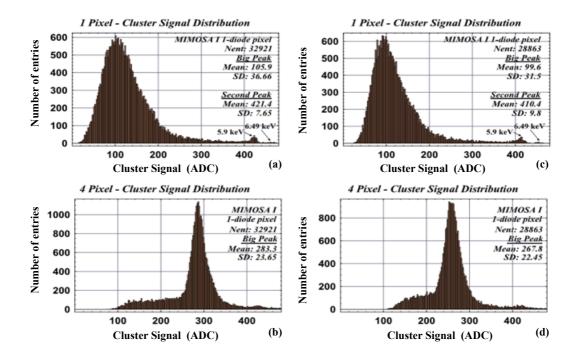

| Fig. 3-13. Sensor response to a 55Fe X-ray source. The              | e signal pulse-height     |

| distribution is shown before (a,b) and after (c,d) a dos            | se of 100 kRads 10keV     |

| photons. Plots (a) and (c) corresponds to the seed p                | oixel. Plots (b) and (d)  |

| corresponds to a cluster of 4 pixels including the see              | ed one [42]. (MIMOSA      |

| I)53                                                                                      |

|-------------------------------------------------------------------------------------------|

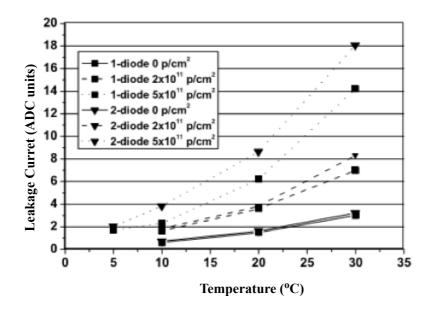

| Fig. 3-14. Increase of leakage current after irradiations with 30 MeV/c protons           |

| measured as a function of temperature [42]. (MIMOSA II)54                                 |

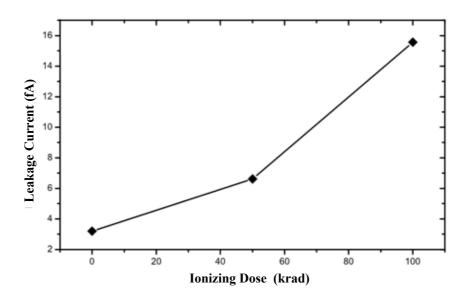

| Fig. 3-15. Variation of the leakage current as a function of the irradiation dose with 10 |

| keV photons (MIMOSA I prototype, measured at 0 oC).[42]54                                 |

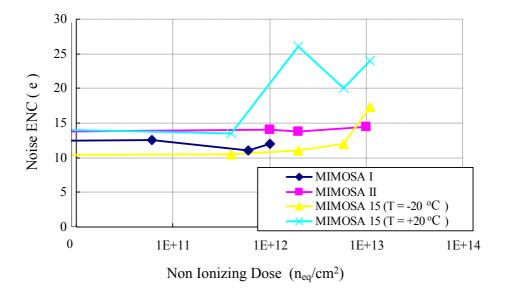

| Fig. 3-16. Noise as a function of neutron fluence [42]. (MIMOSA I)55                      |

| Fig. 3-17. Variation of the leakage current before (a) and after 10 keV photons           |

| irradiations as a function of temperature (MIMOSA 3). The post irradiation                |

| measurements were done 24 h after irradiation (b), after 3 weeks of room                  |

| temperature annealing (c) and after another 24 h annealing at 100 oC (d).                 |

| [42]55                                                                                    |

| Fig. 3-18. Charge collection efficiency of MIMOSA I and MIMOSA II as a function           |

| of the neutron fluence. [40]                                                              |

| Fig. 3-19. Noise as a function of the irradiation dose.[40]                               |

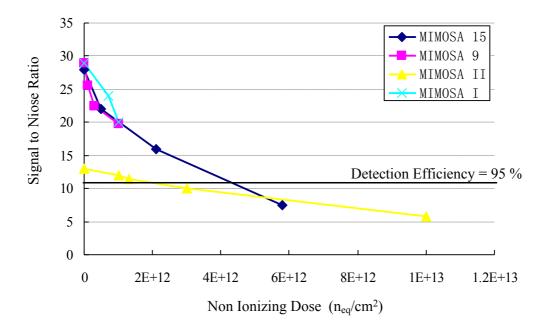

| Fig. 3-20. Signal to noise ratio as a function of irradiation dose.[40]59                 |

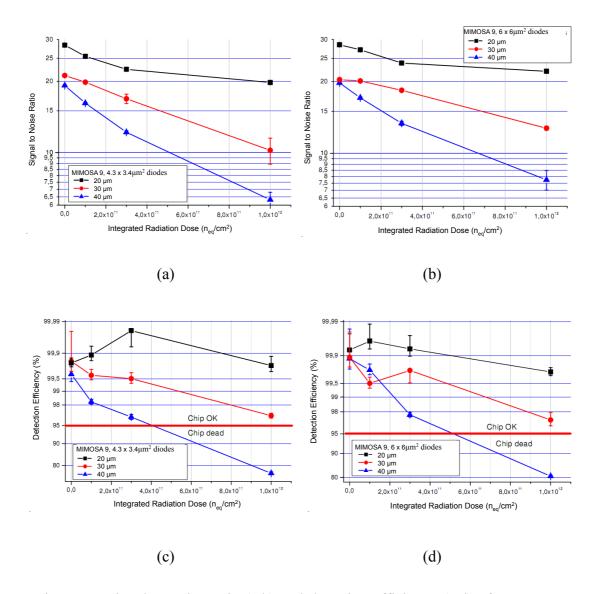

| Fig. 3-21. Signal to noise ratio (a,b) and detection efficiency (c,d) of MIMOSA 9 as a    |

| function of the radiation dose, the pixel pitch and the diode size. Note that             |

| the big diode size of the pixel with 30 $\mu$ m pitch is 5 × 5 $\mu$ m2. The data was     |

| taken at T= -20 oC and fclk = 2.5 MHZ. [40]60                                             |

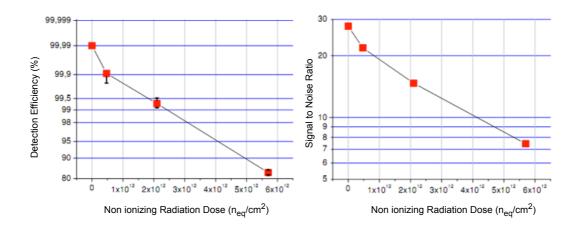

| Fig. 3-22. Signal over noise ratio and detection efficiency of MIMOSA 15 as a             |

| function of the radiation dose. (T = - 20 oC, $\tau$ int = 0.7 ms.)[40]61                 |

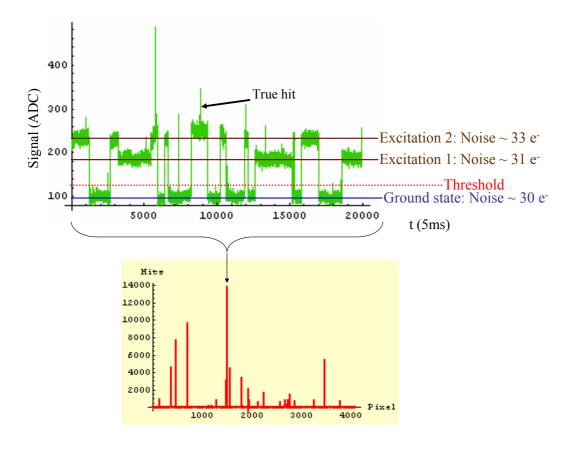

| Fig. 3-23. Random Telegraphy Signal (RTS) on MIMOSA II after an irradiation with          |

| 1013 neq/cm2 at a temperature of 40 °C and an integration time of 3.3 ms.                 |

| [40]62                                                                                    |

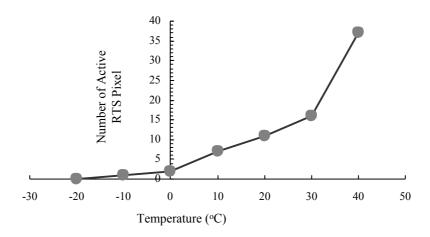

| Fig. 3-24. The number of RTS-pixels as a function of temperature.[40]63                   |

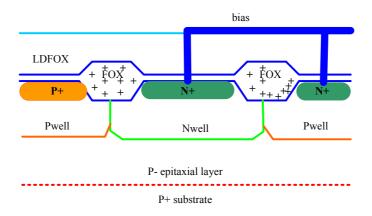

| Fig. 3-25. The positive charge built in standard pixel                                    |

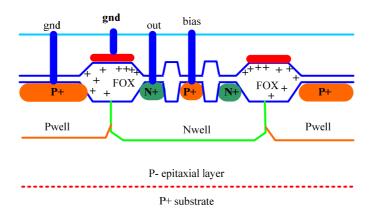

| Fig. 3-26. A proposed radiation hard pixel with dummy poly shielding64                    |

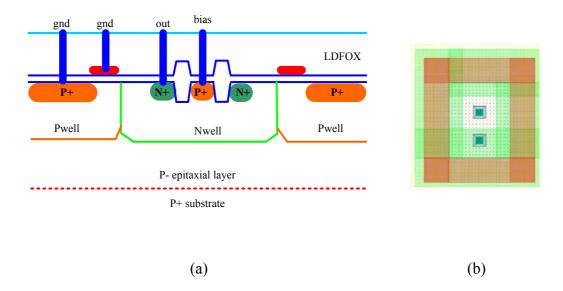

| Fig. 3-27. A radiation hard pixel with annular pseudo-poly-gate. (a) Cross section        |

| view, (b) Layout view65                                                                   |

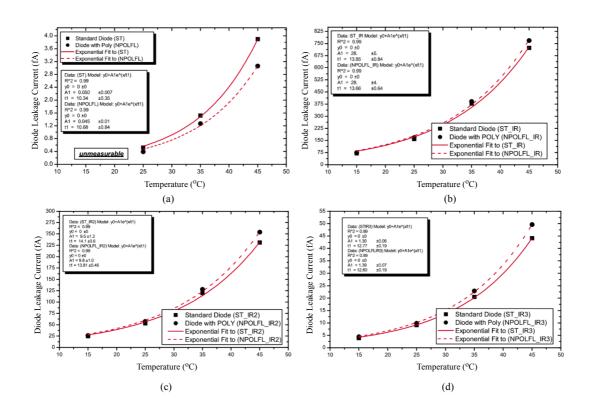

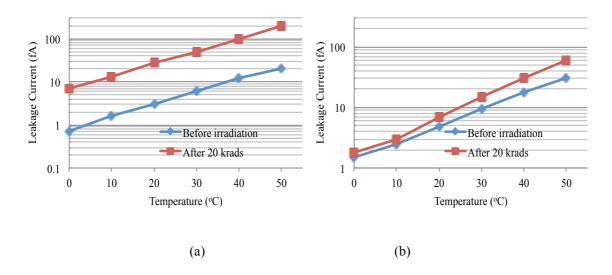

| Fig. 3-28. The leakage currents for standard (a) and radiation hard diode (b) as a        |

| function of temperature before and after receiving the ionizing radiation                 |

| dose of 20 kRad. (MIMOSA 11 with 4 ms of integration time)[41]65                          |

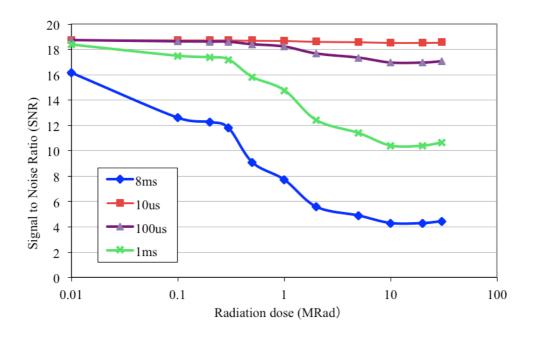

| Fig. 3-29. SNR versus irradiation with different integration time.[48]                    |

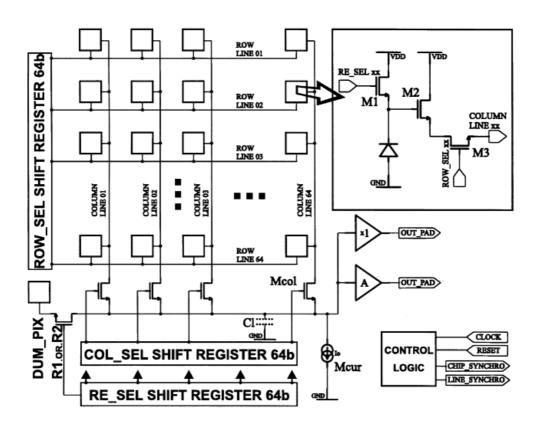

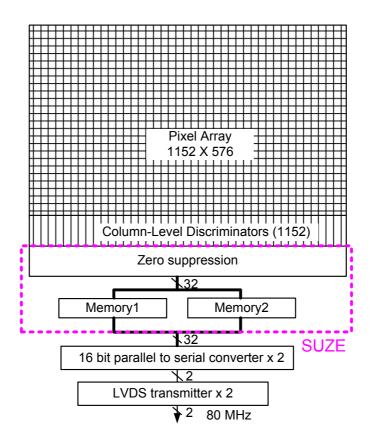

| Fig. 4-1. Schematic of a fast readout MAPS (MIMOSA 26)70                                  |

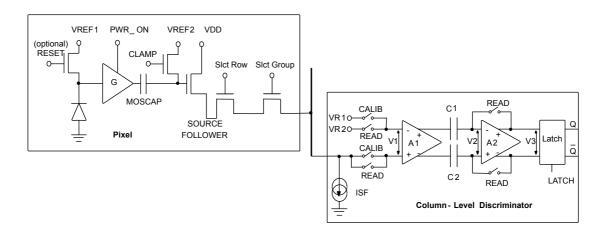

| Fig. 4-2. Topology of a pixel and a discriminator71                                       |

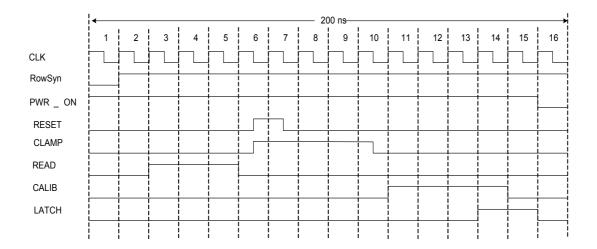

| Fig. 4-3. Timing Sequence of Pixel and Discriminator in Fig. 3-3371                       |

| Fig. 4-4. Schematic of in-pixel amplifier. (a) Common source amplifier (b) Improved       |

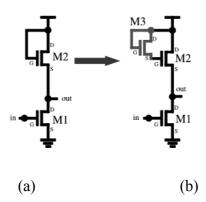

| amplifier.[54]73                                                                           |

|--------------------------------------------------------------------------------------------|

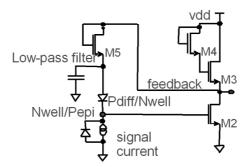

| Fig. 4-5. Improved amplifier with a negative feedback and self-biased sensing              |

| element.[55]                                                                               |

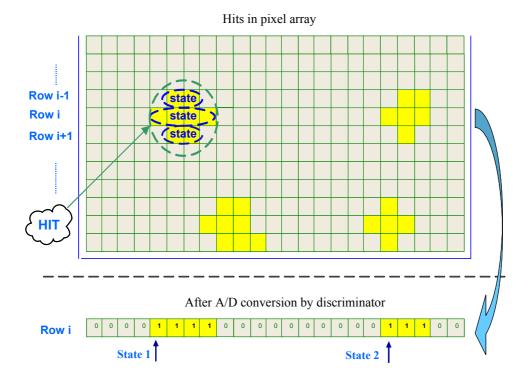

| Fig. 4-6. A sketch map of hits in pixel array.                                             |

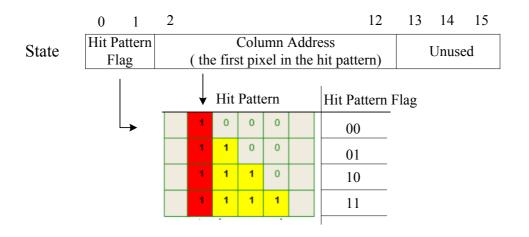

| Fig. 4-7. Encoding format of a state.                                                      |

| Fig. 4-8. Encoding format of a status.                                                     |

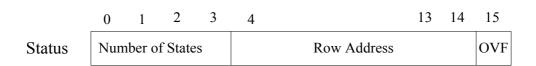

| Fig. 4-9. Block diagram of the MAPS readout chain with zero suppression76                  |

| Fig. 4-10. Response of a group of 288 discriminators connected to the pixel array [22      |

| 55]77                                                                                      |

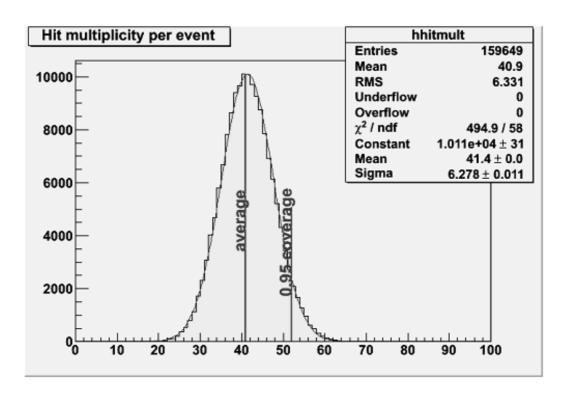

| Fig. 4-11. Number of pixels per frame with a noise fluctuation passing a discriminator     |

| threshold of 6 times of the average noise.[55]                                             |

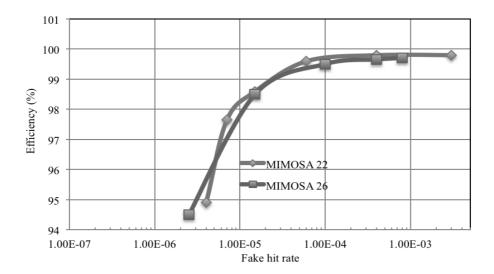

| Fig. 4-12. Variation of the detection efficiency with the fake hit rate.[22, 55]79         |

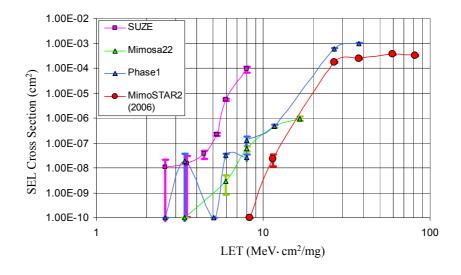

| Fig. 4-13. SEL cross-sections of MimoSTAR2, Phase1, MIMOSA 22 and SUZE80                   |

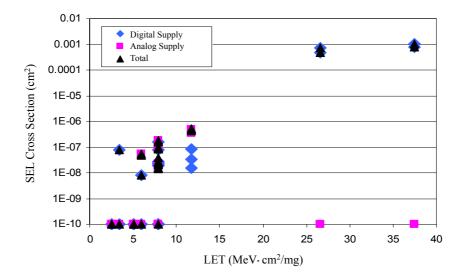

| Fig. 4-14. SEL cross-section measured for MIMOSA 22 with distinction between               |

| latchup events registered on the analog and digital power supplies81                       |

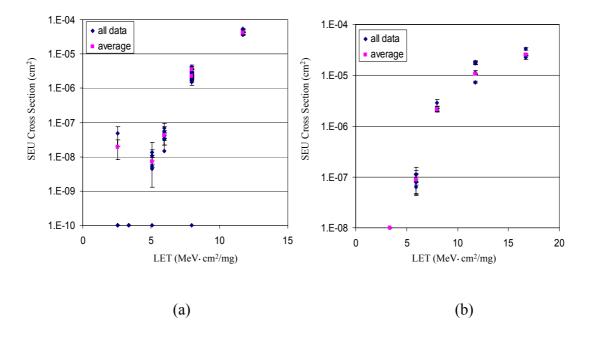

| Fig. 4-15. SEU cross-section measured for Phase1 (a) and MIMOSA 22 (b). Points a           |

| 1E-10 (Phase1) and 1E-8 (MIMOSA 22) indicate measurements that                             |

| yielded no errors81                                                                        |

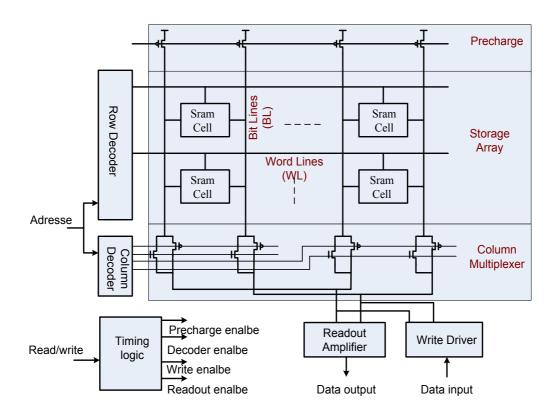

| Fig. 4-16. A simplified block diagram of SRAM                                              |

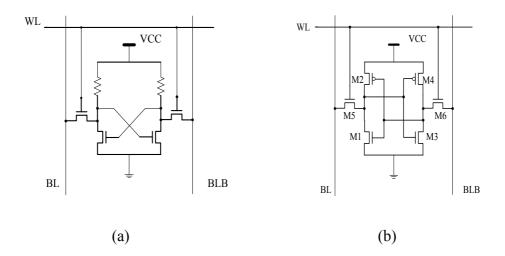

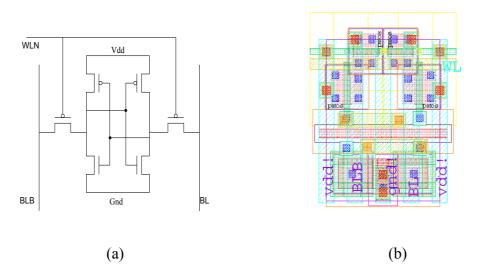

| Fig. 4-17. SRAM cell. (a) 4T2R (b) 6T                                                      |

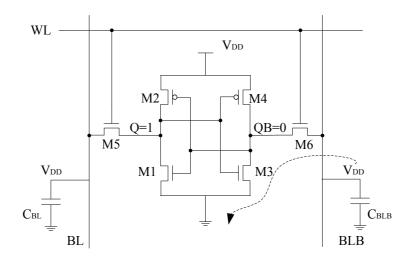

| Fig. 4-18. Read operation of a SRAM cell                                                   |

| Fig. 4-19. Write operation of a SRAM cell                                                  |

| Fig. 4-20. Scheme of the TMR technique                                                     |

| Fig. 4-21. Scheme of the EDAC technique                                                    |

| Fig. 4-22. Standard 6T-Cell, (a) Schematic, (b) Layout                                     |

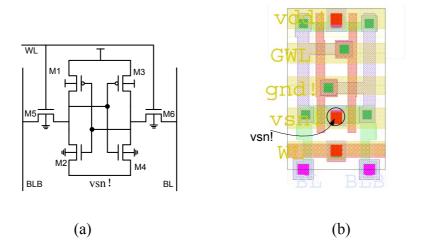

| Fig. 4-23. SRAM cell with PMOS pass gate transistors, (a) schematic, (b) layout90          |

| Fig. 4-24. Reverse-Body Bias 6T SRAM cell. (a) Schematic (b) Layout. The sources           |

| of two pull-down transistors are connected to a voltage (vsn!), which is                   |

| higher than ground91                                                                       |

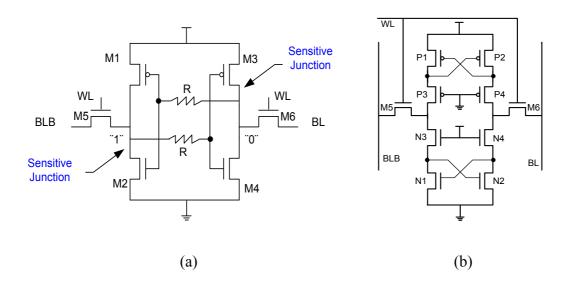

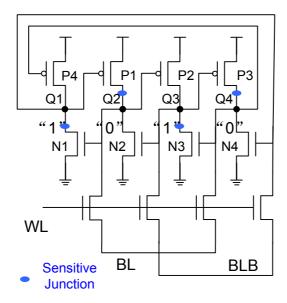

| Fig. 4-25. SRAM cell harden by resistor, (a) resistor on gate, (b) 10T cell92              |

| Fig. 4-26. SEU hard SRAM cell DICE.                                                        |

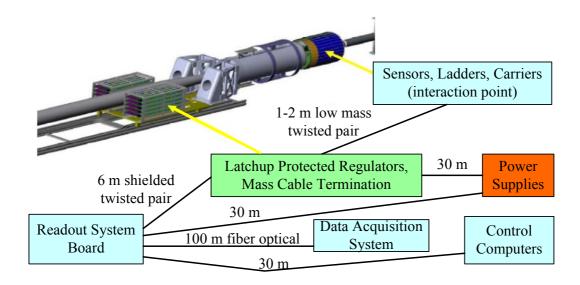

| Fig. 4-27. Readout system for the PIXEL detector in STAR experiment. [80]95                |

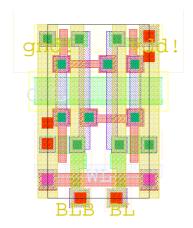

| Fig. 4-28. Layout of the radiation hard SRAM cell                                          |

| Fig. 4-29. Layout of the SRAM array of $4 \times 4$ cells                                  |

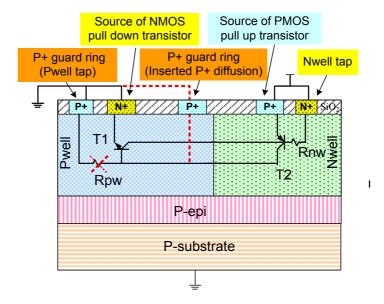

| Fig. 4-30. Cross-section of the radiation hard SRAM cell                                   |

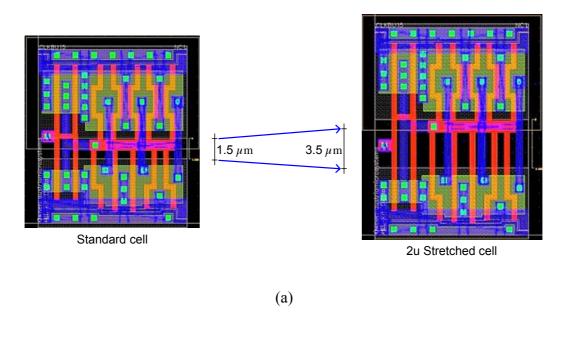

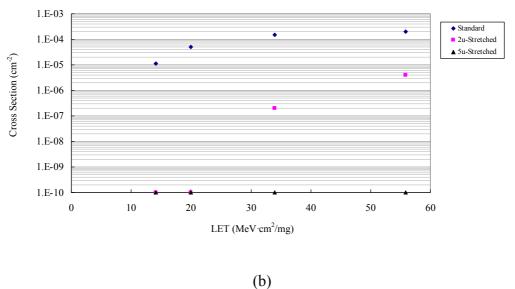

| Fig. 4-31. SEL test results of the standard, $2\mu$ -stretched and $5\mu$ -stretched logic |

| libraries. The cross-section of 10-10 cm-2 indicates that no latchup events                |

| were observed at the points. [81]                                                          |

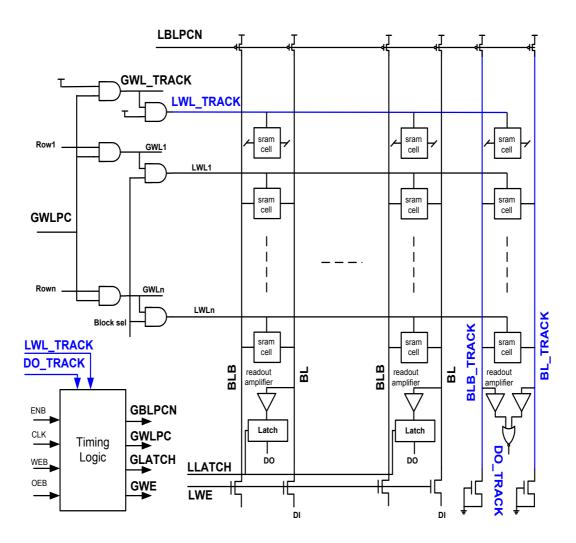

| GWL_TRACK and LWL_TRACK signals track the timing information of word lines, and the DO_TRACK signal reflects the timing information of |

|----------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                                        |

| 1.7.1.                                                                                                                                 |

| bit lines                                                                                                                              |

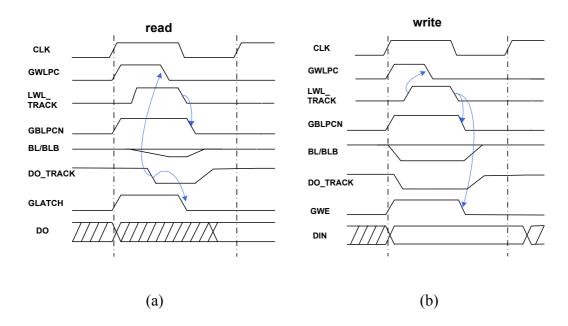

| Fig. 4-33. Timing sequence of the presented SRAM. (a) The timing sequence of a                                                         |

| read operation. The negative edge of DO_TRACK is used to disable                                                                       |

| GWLPC and GLATCH, and the negative edge of LWL_TRACK is used to                                                                        |

| enable GBLPCN. (b) The timing sequence of a write operation. The                                                                       |

| positive edge of LWL_TRACK is used to disabled GWLPC, and the                                                                          |

| negative edge of LWL_TRACK is used to disable GWE and to enable                                                                        |

| GBLPCN                                                                                                                                 |

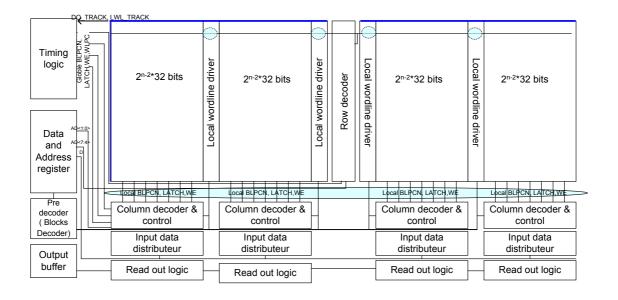

| Fig. 4-34. Architecture of the SRAM                                                                                                    |

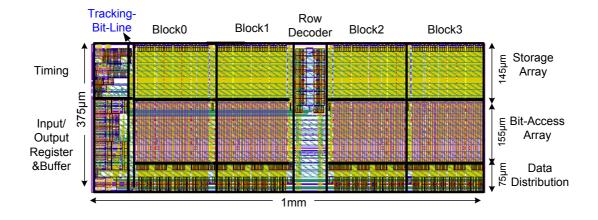

| Fig. 4-35. Layout of the SRAM                                                                                                          |

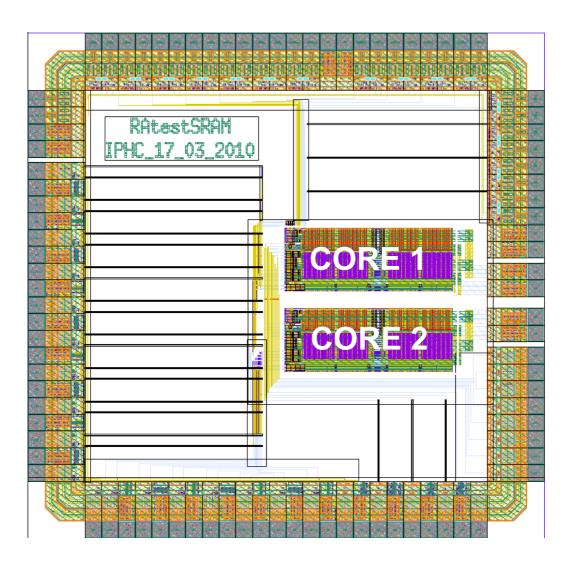

| Fig. 4-36. Layout of Prototype Chip                                                                                                    |

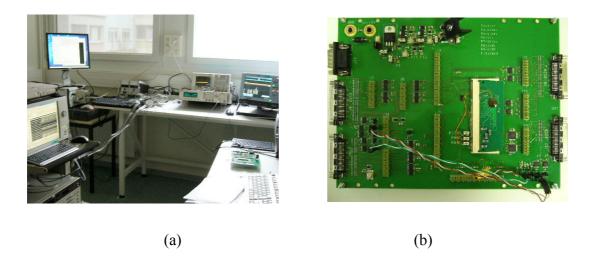

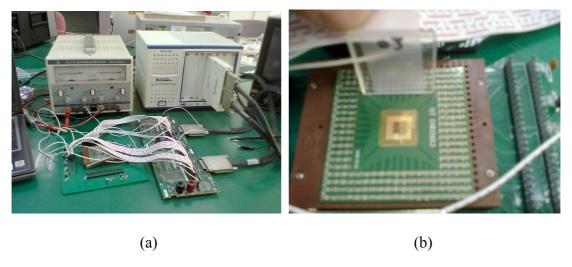

| Fig. 4-37. Test of the prototype chip. (a) Test environment, (b) Test board                                                            |

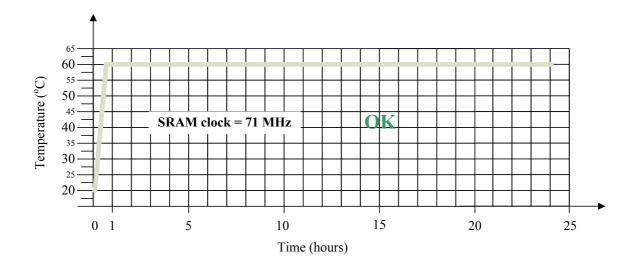

| Fig. 4-38. SRAM temperature test results                                                                                               |

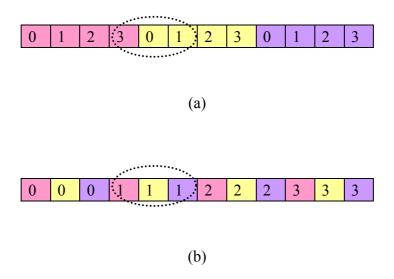

| Fig. 4-39. The distributions of storage data, (a) general, (b) bit interleaving. Three                                                 |

| 4-bit data are taken for example                                                                                                       |

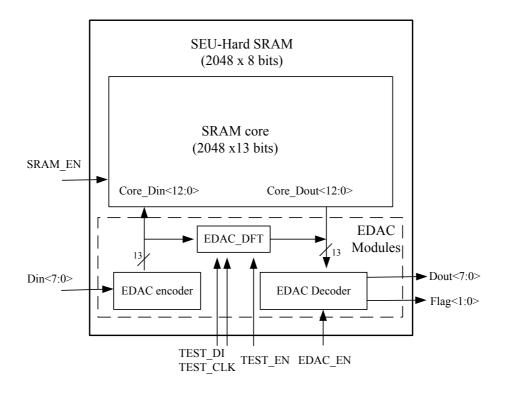

| Fig. 4-40. Block Diagram of SEU Hard SRAM                                                                                              |

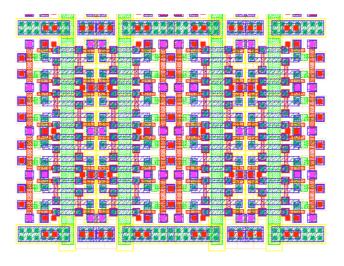

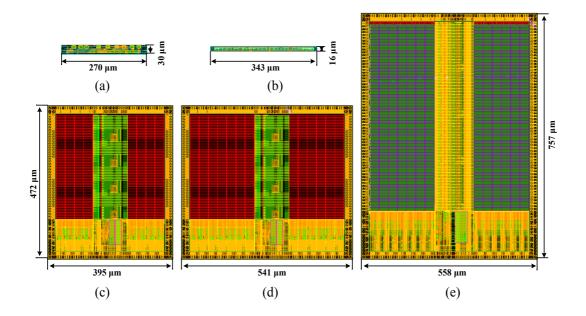

| Fig. 4-41. Layouts of the SRAM components. (a) SEL hardened EDAC decoder, (b)                                                          |

| SEL hardened EDAC encoder, (c) standard 2048 × 8 bit SRAM, (c)                                                                         |

| standard 2048 × 13 bit SRAM, (d) SEL hardened 2048 × 13 bit SRAM. 109                                                                  |

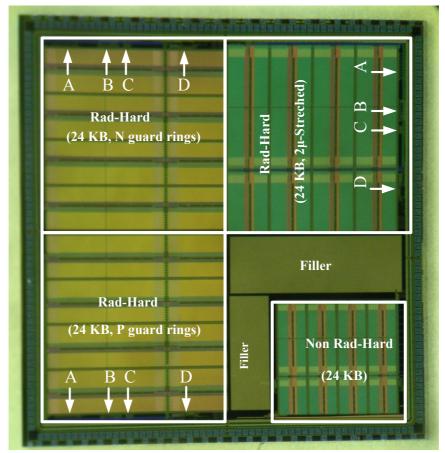

| Fig. 4-42. Micrograph of the prototype chip. A non-radiation hard SRAM is realized                                                     |

| on the bottom right corner. The other three SRAMs are hardened by the                                                                  |

| EDAC algorithm, the 2μ-stretched logic library and the radiation hard                                                                  |

| SRAM cells (with P+ guard ring layout, N+ guard ring layout or                                                                         |

| 2μ-stretched layout)                                                                                                                   |

| Fig. 4-43. Test of the prototype chip. (a) Test environment, (b) Chip under test 111                                                   |

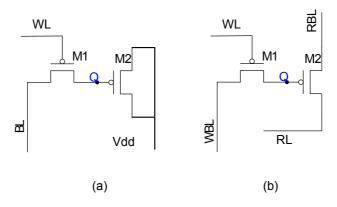

| Fig. 4-44. Proposed 2T memory cells. (a) Single port cell (b) Duel port cell113                                                        |

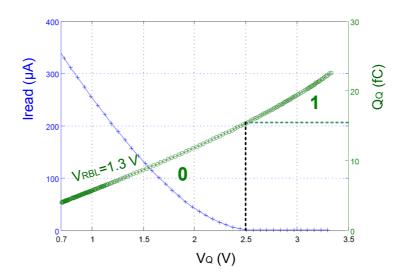

| Fig. 4-45. Read operation current and storage charges versus voltage of storage node.                                                  |

| 114                                                                                                                                    |

| Fig. 4-46. Layout of the proposed dual port DARM cell                                                                                  |

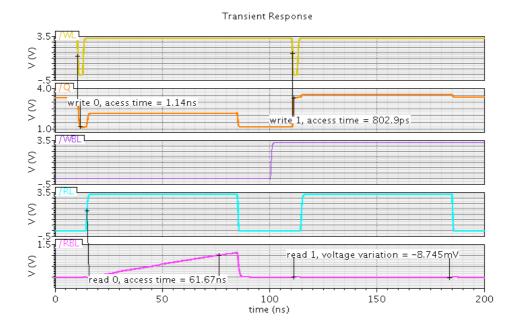

| Fig. 4-47. Simulation results of read and write operation                                                                              |

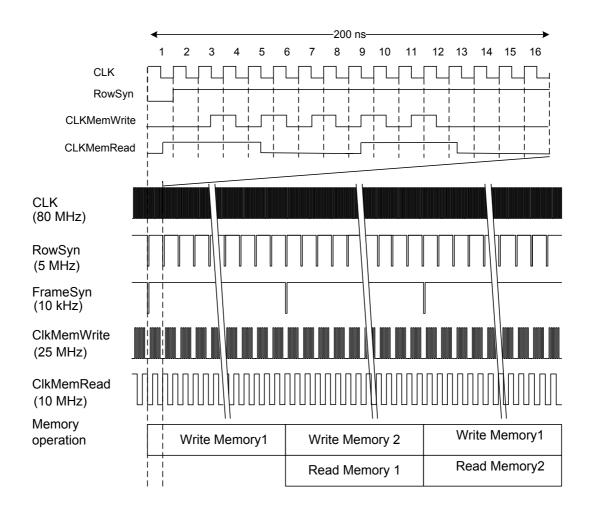

| Fig. 4-48. Memory control sequence                                                                                                     |

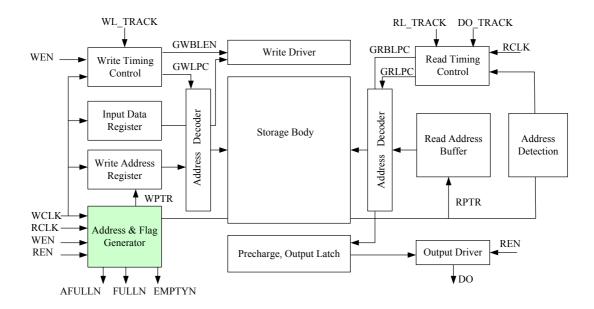

| Fig. 4-49. Block diagram of the FIFO                                                                                                   |

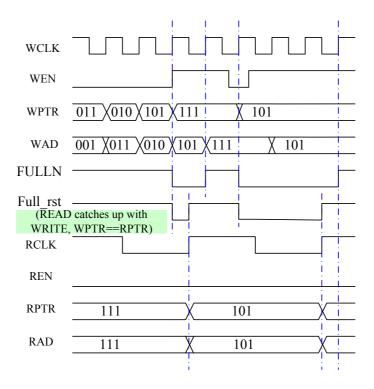

| Fig. 4-50. Generation of full signal (FULLN).                                                                                          |

| <u> </u>                                                                                                                               |

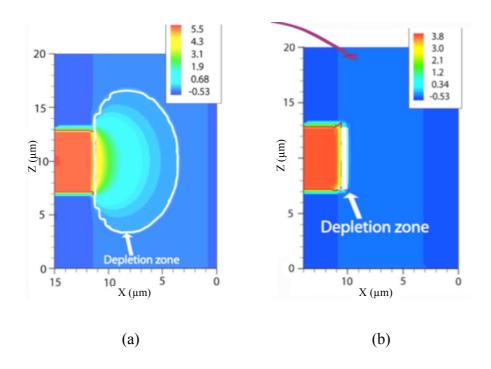

| P-epi, (b) Standard resistivity (19Ωcm) P-epi. [91]                                     |

|-----------------------------------------------------------------------------------------|

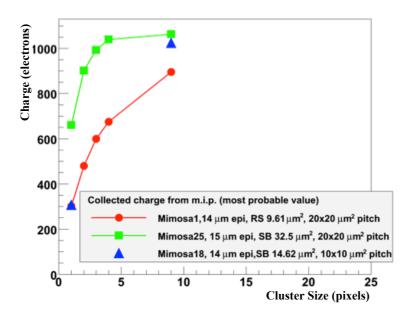

| Fig. 5-2. Charge collection from MIP in several chips [91]                              |

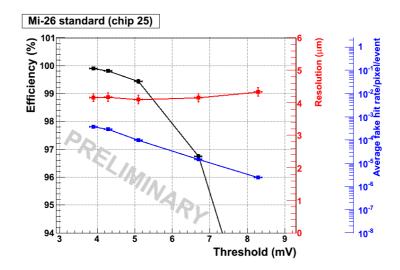

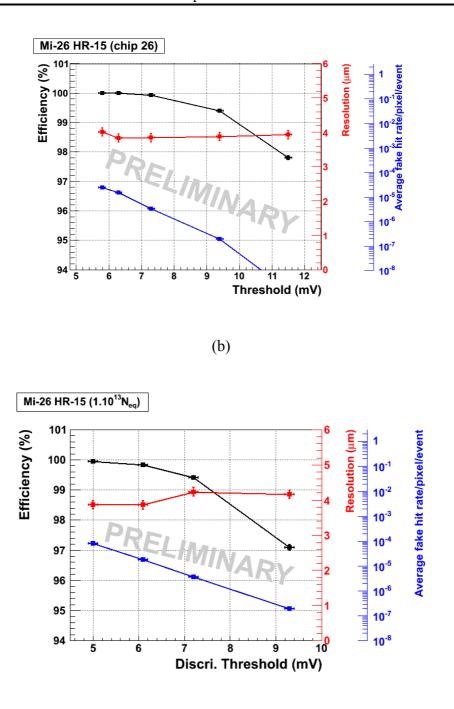

| Fig. 5-3. Beam test results for MIMOSA 26. (a) Standard, (b) HR-15, (c) HR-15           |

| irradiated with 1013 neq/cm2. [95]                                                      |

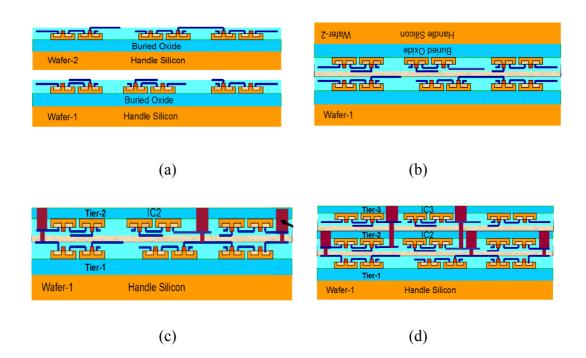

| Fig. 5-4. Illustration a three-tier chip fabricated by via after bonding. (a) Fabricate |

| individual tiers, (b) Invert, align, and bond wafer 2 to wafer 1, (c) Remove            |

| handle silicon form wafer 2, etch 3D Vias, deposit and CMP tungsten, (d)                |

| Invert, align and bond wafer 3 to wafer 2/1 assembly, remove wafer 3                    |

| handle wafer, form 3D Vias form tier 2 to tier 3. [99]126                               |

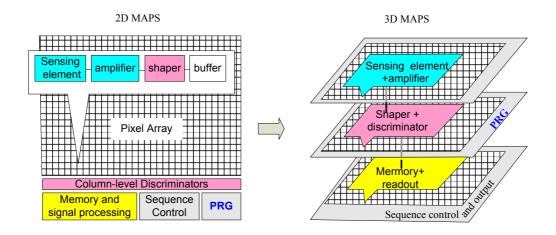

| Fig. 5-5. An architecture of 3D MAPS with 3 tiers conversion from an architecture of    |

| 2D MAPS                                                                                 |

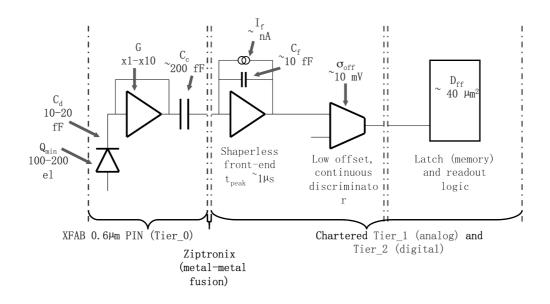

| Fig. 5-6. Block diagram of a proposed architecture using 3DIT.[103]128                  |

# **List of Tables**

| Table 1-1 Compare of the attractive detectors                                        | 14        |

|--------------------------------------------------------------------------------------|-----------|

| Table 1-2 Main Features and Specifications of PIXEL detector                         | 18        |

| Table 2-1 Particle rate and fluence for several experiments at the position of the i | nner most |

| pixel layer. [ <u>26</u> ]                                                           | 21        |

| Table 3-1 List of compared chips                                                     | 57        |

| Table 3-2 List of some pixel matrices in MIMOSA 9                                    | 60        |

| Table 4-1 Error location of a 5-bit Hamming Code                                     | 89        |

| Table 4-2 Main characteristics of the required SRAM                                  | 94        |

| Table 4-3 SRAM internal signal name description                                      | 99        |

| Table 4-3 Area comparison of the modules in SRAM                                     | 109       |

| Table 4-4 Timing parameter comparison of SRAM with and without EDAC                  | 110       |

| Table 5-1 Depletion depth of p-type resistivity epitaxy with different voltages      | 121       |

| Table 5-2 Signal to noise ratio of MIMOSA 26 with several processes.                 | 123       |

# **Acknowledgments**

As this thesis is approaching the end, I would like to express my sincere gratitude to all my supervisors, colleagues, friends, and families who have supported and helped me during the passed five years.

First of all, I would like to express my endless gratitude to my supervisors, Prof. Yann Hu at University of Strasbourg and Prof. Deyuan Gao at Northwestern Polytechnical University. I am deeply influenced by their careful work, diligence, specialist knowledge and wisdom. I also would like to thank Prof. Tingcun Wei who leads me to enter the gate of microelectronics and makes me have an interest in the mixed-signal circuit design. His research spirit and methods are impressing.

I sincerely appreciate Dr. Christine Hu-Guo, Dr. Wojteck Dulinski, Dr. Jerome Baudot and Dr. Marc Winter for providing me the proper means and environment to proceed with my work.

I own my gratitude to Andrei Dorokhov, Min Fu, Guy Doziere, and Gilles Claus for their help on device simulation and circuit test. I appreciate Frederic Morel, Gregory Bertolone, Sylviane Molinet and Christian Illinger for their supports on the problems about the EDA tools and the work computers. I would like to thank Mariusz Jankowski, Claude Colledani, Olave Torheim, Jerome Nanni, Isabelle Valin, Abdelkader Himmi, Xiaochao Fang, Wu Gao, Quan Sun, Ying Zhang, Yunan Fu, Jia Wang, Liang Zhang, Renzhuo Wan and other colleagues in IPHC for providing me a wonderful and warm academic atmosphere.

I am also grateful to Ran Zheng, Feng Li, Nan Chen, and other colleagues in Northwestern Polytechnical University for their help and support during this work.

Many thanks to my friends Anna Winter, Jia Ling, Yu Liu, Fan Yang, Ying Zhang and Guangyan Du for their help and accompanying during my living in France. I especially thank Anna Winter for her care and encouragement all the time and her great help of the French writing in this thesis.

I should not forget to thank the China Scholarship Council (CSC) for their financial support during my study in France.

Last but not least, I am extremely grateful to my families for their selfless supports and endless love.

Xiaomin WEI Xi'an, China October 15, 2012

### Résumé

Les capteurs monolithiques actifs à pixels (Monolithic Active Pixel Sensors, MAPS) sont de bons candidats pour être utilisés dans des expériences en Physique des Hautes Énergies (PHE) pour la détection des particules chargées, car ils offrent un compromis avantageux entre leur résolution spatiale, leur budget de matière, leur tolérance aux rayonnements et leur vitesse de lecture. Les MAPS sont directement exposés aux particules produites dans les expériences de PHE, y compris aux hadrons, aux leptons et à des noyaux légers. Le taux des réactions de particules traversant les MAPS se situe entre  $10^6$  cm<sup>-2</sup>·s<sup>-1</sup> et  $10^8$  cm<sup>-2</sup>·s<sup>-1</sup>. La dose intégrée du rayonnement ionisant et la fluence du rayonnement non-ionisant peuvent varier, respectivement, de quelques dizaines de kRads à plusieurs MRads par an et de  $10^{10}$  n<sub>eq</sub>/cm<sup>2</sup> à  $10^{15}$  n<sub>eq</sub>/cm<sup>2</sup>. Les MAPS, soumis à une irradiation intense dans leur l'environnement, doivent conserver leurs performances à la reconstruction de la trajectoire des particules chargées. Dans cette thèse, nous avons étudié et amélioré la tolérance des MAPS aux radiations. Les principales étapes du travail sont résumés comme suit :

- 1. Les effets des rayonnements sur les MAPS sont étudiés non seulement en fonction du type de rayonnement (non-ionisant et ionisant), mais prennent aussi en compte la composition des matériaux (semi-conducteur, conducteur et diélectrique) ainsi que les fonctionnalités et le câblage intégrés dans le capteur. Le rayonnement non-ionisant induit principalement des déplacements d'atomes. La dose du rayonnement dans la majorité des expériences en PHE engendre seulement des déplacements mineurs dans les conducteurs et les diélectriques, mais réduit la durée de vie des porteurs minoritaires dans les semi-conducteurs. Le rayonnement ionisant génère des paires électrons-trous dans les matériaux. Les principaux effets ionisants sont des effets d'une particule isolée (Single Event Effects, SEE) et des effets de dose ionisante intégrée (Total Ionizing Dose, TID) dus aux paires électron-trou déposées respectivement dans les semi-conducteurs et les diélectriques. Les circuits CMOS (Complementary Metal Oxide Semiconductor) dans les MAPS sont vulnérables tant aux effets SEE qu'aux effets TID. De plus, les diodes qui détectent la charge sont sensibles à la réduction de la durée de vie des porteurs minoritaires ainsi qu'aux courants de fuite générés par irradiation.

- 2. Le progrès dans la conception des MAPS radiorésistants est étudié. Au cours des dernières années, les effets des rayonnements non-ionisants et les effets TID ont été évalués à l'aide d'irradiations soigneusement sélectionnées utilisant des protons, des neutrons et des rayons X mous. En outre, les performances en termes d'efficacité de détection et de rapport signal sur bruit (Signal to Noise Ratio, SNR) ont été mesurées dans des expériences réelles avec faisceau de particules. Les résultats de ces tests démontrent que les effets non-ionisants conduisent principalement à la diminution de l'efficacité de collection de charge tandis que les effets ionisants induisent surtout une augmentation du bruit électronique. Des baisses de SNR et d'efficacité de détection des particules ont été observées avec les deux types de

rayonnement pour ces raisons. En sélectionnant une épaisseur de la couche épitaxiée adéquate et en optimisant la densité des diodes, les MAPS ont atteint une efficacité de détection de 99,5% après une dose de rayonnement non-ionisant allant jusqu'à 2×10<sup>12</sup> n<sub>eq</sub>/cm² (resp.10<sup>13</sup> n<sub>eq</sub>/cm²) pour une température de fonctionnement de 30°C (resp. 0°C). Les effets TID dans les MAPS ont été atténués par des techniques de conception spécifiques de durcissement au rayonnement et un design auto-biaisé de pixel. En outre, certains résultats de tests indiquent que la tolérance TID peut être améliorée en réduisant le temps d'intégration des MAPS, temps qui est égal au temps de lecture dans la plupart des designs des MAPS. La tolérance TID pourrait atteindre 1 MRad avec un temps d'intégration de 200 μs et près de 10 MRad avec un temps d'intégration de 10 μs. Par conséquent, l'amélioration de la tolérance TID de MAPS, passe par l'implémentation d'une lecture rapide.

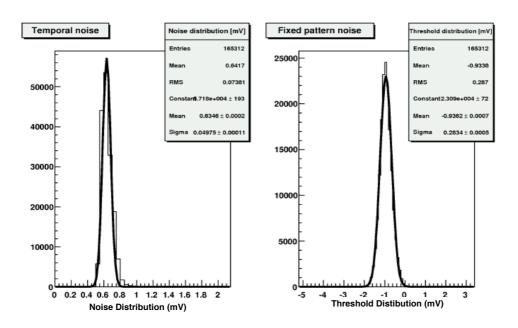

3. Avec les exigences d'une vitesse de lecture élevée et d'une haute tolérance TID, des MAPS de lecture rapide ont été conçus en intégrant un bloc de compression de données et deux cœurs SRAM (Static Random Access Memory) IP (Intellectual Property). Toutefois, la tolérance au rayonnement de ces deux cœurs n'est pas aussi élevée que pour les autres parties dans les MAPS et limite sensiblement la tolérance au rayonnement de la puce MAPS entière. Notamment, la SRAM est sensible aux effets SEE, y compris aux effets d'événement latchup (Single Event Latchup, SEL) et de perturbation par particule isolée (Single Event Upset, SEU). Par conséquent, trois mémoires résistantes au rayonnement sont conçues pour les puces MAPS présentes et futures.

En analysant les stratégies existantes de durcissement aux rayonnements, une SRAM radiorésistante est conçue pour remplacer les cœurs SRAM IP incorporés dans les MAPS. Dans ce but, la cellule SRAM standard à six transistors est choisie et durcie par augmentation de la marge au bruit statique (Static Noise Margin, SNM) de la cellule et par ajout d'anneaux de garde de type P+ dans le schéma d'implantation. Dans la conception du câblage périphérique de la mémoire SRAM est incorporée une bibliothèque de logiciels de conception radiotolérante par accroissement de la distance entre transistors NMOS et PMOS donnée par une bibliothèque de logique standard. La commande de synchronisation interne de la SRAM est durcie par un design de synchronisation auto-adaptatif. Enfin, la SRAM radiorésistante est implémentée et testée dans un procédé standard CMOS - 0,35 µm. La SRAM est adaptée pour fonctionner avec des fréquences allant jusqu'à 80 MHz, des tensions d'alimentation de 2,9 V à 3,3 V et des températures de 0 à 60 °C. La tolérance aux rayonnements de la SRAM est évaluée et comparée à des résultats de test d'irradiation antérieurs. La tolérance aux effets SEU et TID est comparable et même meilleure que la tolérance des autres circuits sur les MAPS. La tolérance à l'effet SEL est supérieur à 56 MeV·cm<sup>2</sup>/mg, à comparer à 5,2 MeV·cm<sup>2</sup>/mg avant l'amélioration. La SRAM a été développée pour être intégrée dans le capteur ULTIMATE qui équipera bientôt l'expérience STAR (Solenoidal Tracker At RHIC (Relativistic Heavy Ion Collider)).

Récemment, des procédés avec taille réduite des grilles des transistors (comme des procédés de  $0.18~\mu m$  et  $0.13~\mu m$ ) ont aussi été utilisés pour la conception de MAPS. Les effets TID et les effets SEL sont atténués grâce à l'épaisseur réduite à de

l'oxyde de la grille et la baisse de la tension d'alimentation. Toutefois, les effets SEU s'aggravent beaucoup en raison de la charge critique SEU réduite, qui diminue avec la tension d'alimentation. Outre les techniques de durcissement aux rayonnement déjà utilisées dans la SRAM avec un procédé de 0,35 μm, un algorithme de détection et correction d'erreurs (Error Detection And Correction, EDAC) est implémenté dans la SRAM conçue avec un procédé de 0,18 μm afin d'améliorer encore la tolérance au SEU. Avec l'adoption de l'approche EDAC, une perturbation d'une bit peut être corrigée automatiquement et des perturbations de deux bits peuvent être détectées et signalées. Bien que la surface de la SRAM soit augmentée d'environ 60% par l'algorithme EDAC, la densité de bits de cette nouvelle SRAM est plus élevée que celle de la SRAM réalisée en technologie 0,35 μm en raison de la gravure plus fine – et donc plus dense – du procédé 0,18 μm. Le temps d'accès de la SRAM inférieur à 10 ns, est augmentée d'environ 3 ns à cause de la procédure EDAC. Par conséquent, la SRAM convient pour des MAPS équipant des expériences en PHE.

A l'avenir, quand les MAPS seront développés pour une plus grande précision et une plus grande zone de détection, plus de données devront être traitées par des mémoires. Dans ce cas, une mémoire radiorésistante plus petite sera préférable, en particulier en cas de procédé de 0,35 μm. Dans cette thèse, une mémoire à double accès avec cellule-2T originale est conçue et évaluée pour les puces MAPS futures. La cellule-2T proposée est constituée de seulement deux transistors PMOS. La surface de la cellule est de 4,55 × 5,45 μm², qui ne représente que 67% de la surface de la cellule SRAM du procédé 0,35 μm conçue dans cette thèse. En outre, la cellule-2T est exempte d'effet SEL et a une immunité élevée contre les effets TID. La tolérance SEU est améliorée en optimisant le compromis entre la charge critique et la vitesse de lecture. Une mémoire à double accès basée sur la cellule-2T a été conçue selon les exigences des MAPS. Le temps d'accès en lecture est de 100 ns et celui en écriture est de 10 ns. Par conséquent, la mémoire à double accès basée sur la cellule-2T est un choix potentiel pour le développement futur des MAPS.

4. La tolérance aux rayonnements des MAPS avec des nouveaux procédés disponibles est étudiée. (a) Des procédés de couche épitaxiée de haute résistivité sont privilégiés. La haute résistivité de la couche permet sa déplétion presque complète, conduisant à une efficacité de collection de charge élevée. En raison du champ de dérivation associé à la déplétion, l'effet des pièges dus aux dommages non-ionisants s'atténue entraînant une amélioration de la tolérance aux rayonnements. Dans le test d'irradiation, la tolérance aux rayonnements non-ionisants a atteint plus de  $3 \times 10^{13}$ n<sub>eq</sub>/cm<sup>2</sup> à 30°C pour les MAPS basées sur une résistivité de la couche épitaxiée excédant 1 kΩ·cm. (b) Un procédé de 0,18 μm avec un puits P profond et une couche épitaxiée de haute résistivité est utilisé. La tolérance aux effets TID et SEL est améliorée grâce à un oxyde de grille plus mince et une tension d'alimentation plus basse. Les effets SEU peuvent être atténués par la SRAM radiorésistante équipée d'algorithme EDAC. (c) Actuellement, des technologies intégrées en trois dimensions (3D), qui intègrent deux ou plusieurs couches (feuilles) de dispositifs semi-conducteurs dans une même puce par amincissement, collage et interconnexion, offrent plus de possibilités de conception des circuits et d'optimisation des procédés

- de MAPS. Les MAPS utilisant la technologie 3D intégrée (3D Integrated Technology, 3DIT) sont susceptibles d'atteindre une haute résolution spatiale, une vitesse de lecture accrue, une tolérance aux rayonnements élevée et une peut-être consommation d'énergie faible. Dans les puces 3D, la tolérance aux rayonnements peut bénéficier à la fois de l'optimisation du procédé et de la vitesse de lecture élevée.

- 5. Une conclusion de cette thèse et les perspectives des travaux futurs sont exposées. La tolérance aux rayonnements de MAPS aux effets non-ionisants et aux effets TID a atteint plus de 10<sup>13</sup> n<sub>eq</sub>/cm² and 1 MRad, respectivement. La tolérance aux effets TID devrait être encore améliorée grâce aux nouveaux procédés disponibles. La tolérance SEE sera améliorée par les mémoires radiorésistantes conçues dans cette thèse. À l'avenir, des designs d'architecture plus évolués incorporant les nouveaux procédés disponibles peuvent être conçus pour une tolérance plus élevée aux rayonnements. En outre, les SEE dans les procédés de couche épitaxiée de haute résistivité doivent encore être étudiés et les puces MAPS intégrées avec les mémoires présentées dans cette thèse doivent être expérimentées davantage.

### **Abstract**

This thesis was proposed by the CMOS image sensor group in IPHC for charged particle tracking in high energy physics experiments. Monolithic active pixel sensors (MAPS) are attractive candidates for this application since their good trade-off between spatial resolution, material budget, radiation tolerance, and readout speed. Under the harsh environmental radiations of the high energy physics experiments, radiation tolerance of MAPS based on the commercial CMOS processes still need to be improved. This thesis focuses on the study and improvement of the MAPS radiation hardness.

Both non-ionizing radiation effects and ionizing radiation effects should be considered for MAPS, especially for charge sensing diodes and the MOS transistors. In the past, the MAPS radiation tolerance has been improved by selecting a proper epitaxial layer thickness, optimizing the diode density on epitaxy thickness, using radiation-hardening layout techniques and reducing the charge integration time.

With the requirements of higher radiation tolerance and higher readout speed, fast readout MAPS are conceived. However, the radiation tolerance of the SRAM IP cores built in fast readout MAPS chips is not as high as the tolerance of the other circuits and mitigates the radiation tolerance of the whole MAPS chip. Therefore, three radiation hard memories are designed in this thesis for the present and future MAPS chips. Firstly, a radiation hard SRAM prototype is realized by a full-custom designed radiation hard 6T SRAM cell, an SEL (Single Event Latchup) hardened logic library and a TID (Total Ionizing Dose) hardened timing. The tolerance to the SEU (Single Event Upset) effects and TID effects of the prototype chips is better than that of the other circuits in the MAPS. The tolerance to the SEL effect is estimated above 56 MeV·cm<sup>2</sup>/mg as compared with 5.2 MeV·cm<sup>2</sup>/mg before the improvement. Secondly, a prototype of radiation hard SRAM with enhanced SEU tolerance is implemented with an EDAC algorithm and a bit-interleaving storage since the SEU effects become worrying when the fabrication process is migrated to smaller feature size. Thirdly, a dual-port memory with an original 2T-cell is proposed and evaluated for higher bit density and higher radiation tolerance.

Recently, some new processes are available for MAPS chips. The tolerance of MAPS chips to non-ionizing radiation effects and TID effects can be further improved. In the future, advanced architecture designs with the new available processes can be conceived for higher radiation tolerance. Moreover, the single event effects in high resistivity epitaxy processes are still need to be studied and the MAPS integrated with the developed memories should be further experimented.

**Key Words:** High Energy Physics Experiments, Monolithic Active Pixel Sensors (MAPS), Radiation Effects, Radiation Hardening, Static Random Access Memory (SRAM)

## 1 Introduction

Human beings sense the world by the faculties of hearing, sight, smell, touch, taste, and equilibrium directly. Sensors help human to recognize the world as these faculties but in an extended range. The charged particles in high energy physics (HEP) experiments are not visible for human eyes. Kinds of sensors are employed to detect the particle information. Monolithic active pixel sensors (MAPS) are the silicon detectors developed for charged particle tracking in HEP experiments. In this chapter, charged particle tracking and detector technologies are introduced firstly. Then, the applications of MAPS in HEP are presented. Finally, the doctoral work is proposed in brief and the layout of the thesis is given.

#### 1.1 Charged Particle Tracking in HEP

#### 1.1.1 High Energy Physics

Human beings were exploring the universe for understanding its formation and nature ever since. The Big Bang model proposed by Georges Lemaitre is a prevailing theory of the early development of the universe in modern physics. It explains that the universe originated from singular point with an extremely hot and dense. With the expanding and cooling of the system evolution, new particles and matter were produced until to our current universe. [1]

Particle collision at high energy allows us to reconstruct the phenomenon after the Big Bang universe in laboratory, so as to enhance our vision on the original of our universe and the fundamental matter. Two biggest on going accelerators RHIC (Relativistic Heavy Ion Collider) and LHC (Large Hadron Collider) and near future ILC (International Linear Collider) aim to this target, as well as to find something new beyond.

Fig. 1-1. Heavy Ion Collisions at RHIC. (a) Ions about to collide, (b) Ion collision, (c) Quarks, gluons freed, (d) Plasma created. [2]

Here we take the RHIC as an example to explain the particle collision as shown in Fig.1-1. In RHIC, ions of gold, one of the heaviest common elements, were primarily used. Two beams of gold ions from opposite direction are collided when they're traveling at nearly the speed of light, called relativistic speed. When the ions collide at such high speeds, interesting things happen. The collision "melts" the protons and neutrons and liberates their constituent quarks and gluons. Just after the collision, thousands of particles form as the collision zone cools off. Each of the particles provides a clue as to what occurred inside the collision zone. Physicists sift through those clues for interesting information.[2]

#### 1.1.2 Particle Detection

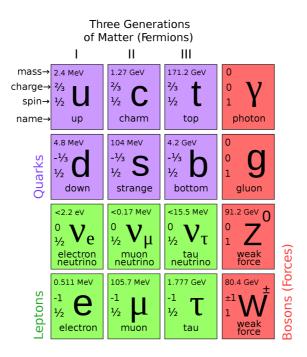

The fundamental particles are shown in Fig. 1-2. The particles are classified into fermions and bosons according the spins of the particles. Fermions are with half-integer spin and obey Fermic-Dirac statistic. The Standard Model recognizes two types of elementary fermions: quarks and leptons. In all, the model distinguishes 24 different fermions: 6 quarks (up u, down d, strange s, charm c, bottom b and top t) and 6 leptons (electron e, muon  $\mu$ , tau  $\tau$ , electron neutrino  $\nu_e$ , muon neutron  $\nu_\mu$  and tau neutrino  $\nu_\tau$ ), each with a corresponding anti-particle. Bosons are with integer spin and obey Bose-Einstein statistics. The bosons are the carriers of weak, strong, gravity and electromagnetic forces. The fundamental bosons are photon ( $\gamma$ ), gluon (g), and weak force ( $\nu$ ,  $\nu$  and  $\nu$

Fig. 1-2. Elementary particles in the Standard Model

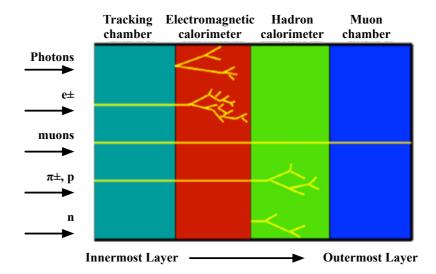

Fig. 1-3. Schematic view of particles going through a particle detector consisting four sub-detectors including tracking chamber, electromagnetic calorimeter, hadron calorimeter and muon chamber from inside to outside.

[3]

The particles can be detected only through their interaction with matter [4]. In the HEP experiments, a particle detector generally consists of several types of detectors in order for detecting certain types of particles or characterizing their motion. Fig. 1-3 presents a typical schematic view of particles going through a particle detector. The particle detector consists of four sub-detectors including tracking chamber, electromagnetic calorimeter, hadron calorimeter and muon chamber from inside to outside. The tracking of charged particles (such as e $\pm$ ,  $\pi\pm$ , p, and  $\mu$ ) can be detected by ionization in tracking chamber. The electromagnetic calorimeter can be used for the energy measurement of charged particles and photons. Hadron calorimeter measures the energy of hadrons. Additionally, hadron calorimeter provides an indirect measurement of the presence of non-interacting, uncharged particles such as neutrinos. Muon chamber is used to identify muons by detecting them outside of the iron of the hadron calorimeter due to the long penetration length of muons. The detectors work together for an advanced data acquisition including particle trajectories, particle velocity, energy, and so on. Subsequent physics analysis allows final statements to be made about the collision.

### 1.1.3 Charged Particle Tracking

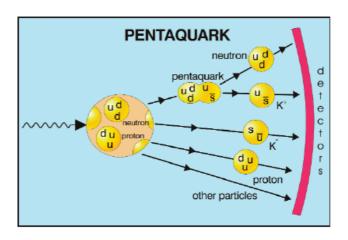

During the particle tracking, the information we get from detector is almost the final-state particles, as shown in Fig. 1-4. Some short-lived particles cannot be detected directly. We infer what actually happened in the initial collision based on working backwards in time. Hence the more precisely the final-state particles are measured, the more accurately we can determine the parameters of the initial state.

Generally, the innermost detector should provide most precise measurements including particle production positions, particle momentum and particle trajectories to the outer detectors. The particle production positions reveal the presence of long-lived particles and the final-state of short-lived particles. The particle momenta are complimentary to calorimeter at low energy. The association of particle trajectories with calorimeter energy deposits and muon hits allows global pattern recognition of physics objects.

Fig. 1-4. Detection of a pentquark

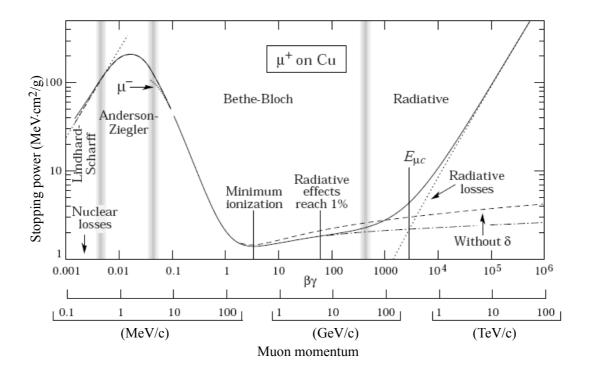

Fig. 1-5. Stopping power for positive muons in copper as function of  $\beta \gamma$  [5].

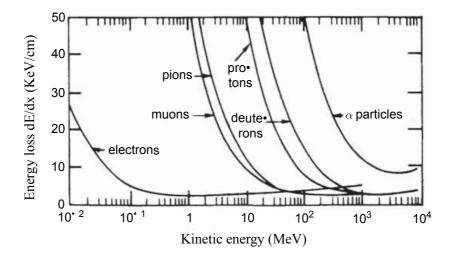

Fig. 1-6. Energy loss for electrons, muons, pions, protons, deuterons and alpha particle in air [4].

The detection of a charged particle is based on the energy loss of the charged particle, which is described by stopping power dE/dx. The stopping power is related with the category of impinging particle and properties of the absorber. Fig. 1-5 shows stopping power for positive muons in copper as function of the relativistic factor  $\beta\gamma$ . Fig 1-6 shows the ionization energy loss for electrons, muons, pions, protons, deuterons and alpha particles in air. The average energy loss of charged particles by ionization and excitation is given by Bethe-Bloch equation. For the most concerned particle in the tracking detection - minimal ionizing particles (MIP, a particle with an energy corresponding to the minimum of the energy loss rate), the stopping power can be expressed as,

$$-\frac{dE}{dx} = Kz^2 \frac{Z}{A} \frac{1}{\beta^2} \left[ \frac{1}{2} \ln \frac{2m_e c^2 \beta^2 \gamma^2 T_{\text{max}}}{I^2} - \beta^2 - \frac{\delta(\beta \gamma)}{2} \right] [\underline{6}]$$

where

dE/dx has units of MeV·cm<sup>2</sup>/g;

x is  $\rho$ s, where  $\rho$  is the material density, s is the path length;

z is the charge of the incident particle in terms of electron charge;

A and Z are the atomic number and mass of the absorber;

$$K/A = 4\pi N_A r_e^2 m_e c^2/A = 0.307 MeV \cdot g^{-1} \cdot cm^2$$

for A = 1g mol<sup>-1</sup>;

$m_e c^2 = 0.510$  MeV, electron mass times squared speed of light;

$$r_e = \frac{e^2}{4\pi m_e c^2} = 2.817 \times 10^{-13}$$

cm is the classical electron radius;

$N_A = 6.022 \times 10^{23} \,\text{mol}^{-1}$  is Avogadro's number;

I is the mean excitation energy in units of eV;

$\beta = v/c$  is the velocity of the particle in units of speed of light;

$$\gamma = 1/\sqrt{1-\beta^2}$$

is the Lorentz factor;

$\delta(\beta \gamma)$  is the density effect correction to ionization energy loss;

$$T_{\text{max}} = \frac{2m_e c^2 \beta^2 \gamma^2}{1 + 2\gamma m_e/M + (m_e/M)^2}$$

is the maximum energy loss in a single collision,

where M is the mass of the incident particle.

The loss energy triggers an electronic signal in a sensor. Then the electronic signals can be processed in advance to give the position and energy information, which helps to provide the gravity of the impinging particles. The particle production positions and particle trajectories are reconstructed by combining the detected position and physics analysis. The particle momentum needs to be calculated according to the tracking information. Generally, the tracker is placed in a magnetic field to distinguish the charged particles and neutral particles. The charged particles follow a curved trajectory in the magnetic field. Thus the particle momentum can be obtained by

$$p_{T} = 0.3BR$$

,

where  $p_T$  is transverse momentum in Gev/c. B is the axial magnetic field in T. R is the radius of curvature in m. [4] The only required parameter radius R can be known by several points along particle trajectory.

Actually, the particle tracking is much complicated due to many effects such as other energy losses, multiple Coulomb scattering and so on.

The Bethe-Bloch equation gives only the average energy loss of charged particles by ionization and excitation. Strong fluctuations around the average energy loss exist. This behavior follows Landau distribution for thin absorber and tends toward Gaussian distribution for thick absorber.

In addition, a charged particle may divert from straight path due to multiple Coulomb scattering effects. It is caused by collisions with atomic electrons. The distribution of scattering angles is described by Moliere's theory.

The root mean square of the projected scattering-angles distribution is given by

$$\theta_{rms}^{proj} = \sqrt{\theta^2} = \frac{13.6 MeV}{\beta cp} z \sqrt{\frac{x}{X_0}} [1 + 0.038 \ln(x/X_0)] [4],$$

where p is the momentum in MeV/c,  $\beta c$  is the velocity, and z is the charge of the scattered particle.  $x/X_0$  is the thickness of the scattering medium, measured in units of the radiation length.

$$X_0 = \frac{A}{4\alpha N_A Z^2 r_e^2 \ln(183Z^{-1/3})} [\underline{4}],$$

where Z and A are the atomic number and the atomic weight of the absorber respectively. Therefore, thin and low mass detector is preferred in precision particle tracking.

#### 1.2 Detector Technologies for Charged Particle Tracking

For charged particle tracking, there are many detector technologies such as multiwire proportional chambers, planar drift chambers, cylindrical wire chambers, micropattern gaseous detectors, scintillating fibre trackers, and semiconductor track detectors. For the innermost vertex detector, semiconductor detectors are good choices due to their dramatic merit on spatial resolution and the smallness of the ionization energy.

Silicon detector is the most popular semiconductor detector in high energy physics experiments due to the cost, resolution, and detection efficiency. Silicon is a material wildly existing in the nature and wildly used in very large scale integrated circuit (VLSI) design and the fabrication technologies are mature. As a result, the cost is low. With the decreasing of feature size of modern VLSI technologies, the spatial resolution will be improved. The energy for one electron-hole pair generation is about 3.6 eV for silicon, which is relative small in the semiconductor materials. The small ionization energy is helpful for a high energy resolution. In addition, the electron/hole lifetime in intrinsic silicon is in order of microsecond, which is a proper readout period.

The principle of silicon detector is based on ionizing interaction of the impinging particles. The detection procedure includes four steps. First of all, the charged particles interact with the detector active medium and transfer part of energy to the detector. Secondly, the medium absorbs the energy and then charge carriers are created. The number of generated charges depends on the absorbed energy and the energy required for generating one electro-hole pair. The later is related with the band gap of a marital. Thirdly, the charge carries are transported across the detector volume and collected by an electrode. Not all the created charge can be collected. Hence the charge collection efficiency should be evaluated. The charge collection efficiency is related with the charge diffusion path, charge collection speed, the electron/hole lifetime and so on. To get high efficient, the charges should be collected before their combination. Finally, the collected charge should be amplified and processed by electronic circuits. The readout circuits are the interface between the detectors and the data acquisition system. The actual particle position is obtained after data processing such as calculation of the gravity center of the charge collection.

The silicon detectors have undergone a great development in HEP experiments. Silicon pad detector, microstrip detector, silicon drift detector are ever very popular technologies for vertex detection. The requirements of HEP experiments are still pushing the silicon detectors for high granularity, low material budget, high radiation tolerance, and high readout speed. New detector techniques such as hybrid pixel sensors, charged coupled device (CCD), DEPleted Field Effect Transistor (DEPFET), MAPS are developed. In addition, sensors using SOI technology and 3D integrated technology are being developed. [7-9] Some detector technologies are introduced as follow.

#### 1.2.1 Microstrip Detector

Microstrip detectors were proposed in early 1980's and have been used as position sensitive devices in many particle physics experiments requiring high precision tracking such as DELPHI (DEtector with Lepton, Photon and Hadron Identification) experiment vertex detector, ATLAS (A Toroidal LHC Apparatus) semiconductor tracker, and PHENIX vertex detector.

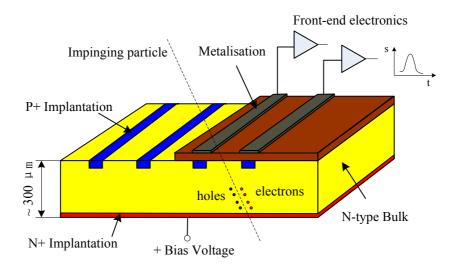

Fig. 1-7. View of a silicon microstrip detector

Microstrip detector can be seen as strip diodes on a plane. Fig. 1-7 shows the structure. The detector is formed from a high resistance n-type silicon bulk with p+ strip implementations as collection electrons and n+ implantation for bias. The typical thickness of the silicon bulk is about 300  $\mu$ m. A bias voltage is required to deplete bulk region for charge collection. This voltage is about 10 to 35 V in the PHENIX multiplicity vertex detector [10]. The created electric field guides the generated charge to the cathodes, namely the p+ strips. Each strip is connected to a channel of front-end readout electronics by micro-bonding. In some detectors, some of the trips are just left floating, which transfer the charge information by coupling, to get high spatial resolution without increasing readout channel. The microstrip detectors usually are segmented in width of 10  $\mu$ m to 50  $\mu$ m and length of several centimeters. The readout chips can be bounded on one side or on both sides of a detector.

The microstrip detectors can provide very good spatial resolution as few microns in one dimension. In order to achieve two-dimension position information, one solution is to mount two planes of microstrip detectors back to back by placing the strips in two directions. Obviously, this solution will increase the material budgets. The other solution is the double-side silicon microstrip detector [11]. N-type diffusion strips are implanted onto the backside of a detector, which should have some angle with respect to the p-type strips on topside. In addition, the n-type strips on n-type

bulk should be separated by p-type channel stoppers. In both case, only single track can be unambiguously reconstructed. Multiple tracks will produce ghost tracks. To conquer this disadvantage, several microstrip planes should be combined. Moreover, track-finding algorithms are required to distinguish the ambiguities partially or fully.

In short, microstrip detectors can achieve good spatial resolution [12] but make hit reconstruction ambiguous. In addition, the microstrip detectors require high voltage in order to deplete the sensitive region. That results in high power consumption. In some extent, additional cooling facilities, namely additional material, are required.

#### 1.2.2 Hybrid Pixel Sensors

Due to the good time resolution and high hadron radiation tolerance, the hybrid pixel sensors are widely considered in high energy physics experiment. Especially, the hybrid pixel sensors are advanced a lot by the requirements of the LHC experiments.

Fig. 1-8. View of a hybrid pixel sensor

Hybrid pixel sensors integrate the detector and readout circuits together by flip-chip bonding technique. The detector part can be seen as subdividing the strips in microstrip detector into many pieces. The readout channels are bonded vertically on the detector. Primarily, one active region corresponds to one readout channel. The active region and the corresponding readout channel consists one pixel. In such case, the spatial resolution is usually determined by the size of the readout circuits. To get higher spatial resolution, an idea is to implant several active regions in one pixel. Only one of the regions is connected to the readout circuits, the others work as the floating strips in microstrip detectors. Fig.1-8 shows a view of a hybrid pixel sensor.

As pixel detectors, the hybrid pixel sensors produce unambiguous position information. Since each pixel has its own readout circuits, the fully parallel readout is realized. Moreover, the small pixel area leads to low detector capacitance and low leakage current, which means large signal to noise ratio. However, the millions of bonding connections are quite complex, and the large number of readout channels lead to large power consumption of electronics.

#### 1.2.3 Charge-Coupled Device

The charge-coupled device (CCD) was invented in 1969 at Bell Labs by Willard Boyle and George E. Smith. Using the CCD, the first solid-state video camera was built in 1970. In the following decades, the performances of CCDs such as quantity efficiency, fill factor, resolution, noise, readout speed and so on get a great development. CCD cameras are developed and widely used in industry and scientific discovery. In HEP experiments, CCD has been successfully used in vertex detector of the SLD experiment at the SLAC's Linear Collider. The detector consists of more than 300 million pixels with pitch size of 20 um. The frame readout time is about 200 ms.

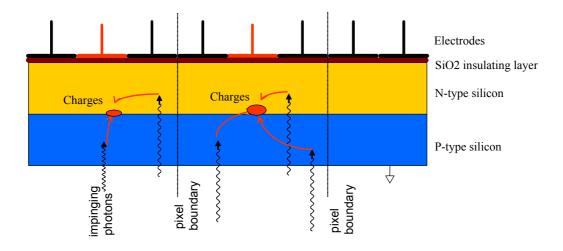

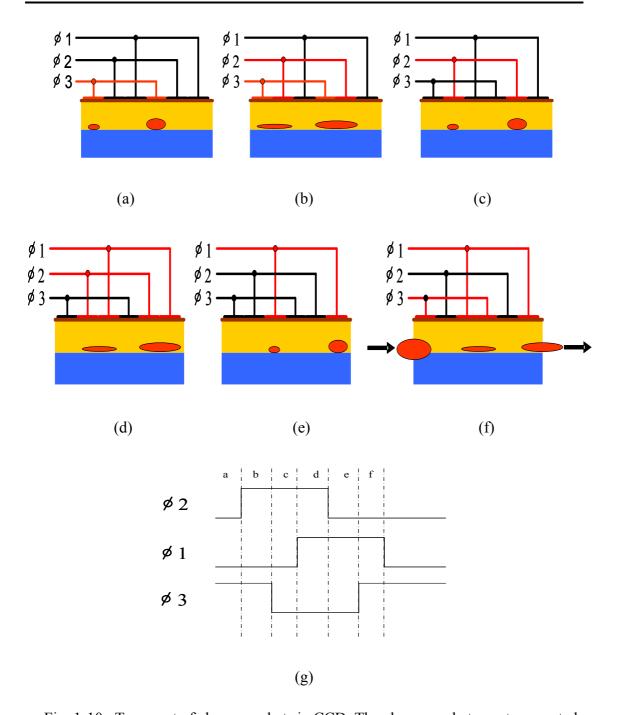

The basic structure of CCDs is shown in Fig. 1-9. The pixels are formed by the structures like MOS capacitors. The electrons generated by impinging particles will be attracted towards the most positive potential in the device where the 'charge-packets' are created. The charge-packets can be moved out with the most positive potential moving by controlling the voltage potential of the gates. Fig. 1-10 shows the process of charge transportation and the phases of the controlling gates [13]. The operation principles are to transfer the charges in order and then to measure the charges in a special cell used for readout. Finally, the measured signal is amplified by the special cell.

Fig. 1-9. Cross section view of charge coupled device

Fig. 1-10. Transport of charge packets in CCD. The charge packets are transported as processes (a)-(f) under the timing of the phase control (g).

The CCD sensors can provide good quality imaging with high readout speed. The resolution is also high enough for the HEP experiments. However, the CCD process is complex and not easy to integrate with more functions, such as analog to digital conversion and digital single processing. Moreover, since the input charge in HEP experiments is much less than visible light imaging, the CCD sensors can not provide low enough noise at room temperature. Thus, some facilities to cool down the chips are required. Furthermore, the CCD process has lower hadron irradiation tolerance than CMOS process.

#### 1.2.4 **DEPleted Field Effect Transistors**

DEPleted Field Effect Transistor (DEPFET) is a new type of active pixel particle detectors. DEPFET technology has been used in an inner detector in Belle II experiment, and it is one of candidates for ILC experiments [14-16].

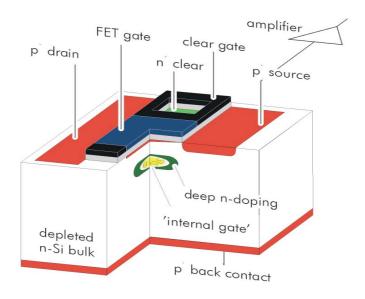

Fig. 1-11. Structure of DEPFET pixel [17]

DEPFET pixel structure is shown in Fig. 1-11. The main element is a MOSFET with a deep n-doping underneath the transistor channel, which is regarded as an internal gate. The bulk is fully depleted during the work of the detector. The electron-hole pairs are created in the bulk when a charged particle is traversing. While the holes drift to the p back contact, the electrons are moved to the internal n+ gate. The internal gate collects and stores the charges. As a result, the potential of the internal gate is changed. Consequently, a variation of channel current of the MOSFET is induced due to the potential change. Thus, the signal is read out by the MOSFET, which is also the first amplification stage of the readout electronics. During the process, the signal charge is not destructed. Hence, multiple and selective readout operations are allowed. The signal must be reset by a positive voltage at the "clear" terminal, which is n+ diffusion on the surface of bulk. The readout can be performed either in a voltage or in current mode.

DEPFET detector is full sensitivity over the whole bulk. Moreover, low noise can be achieved due to the small capacitance of the internal gate, and there is no reset noise because of the complete clearing of signal charge. Therefore, a high signal to noise ratio can be obtained. In addition, DEPFET detector can be thinned down to 50  $\mu$ m for achieving low material budgets. A 64 × 128 DEPFET pixel prototype shows noise values of 225 e- and frame readout time of 18 ms [14].

#### 1.2.5 Monolithic Active Pixel Sensors

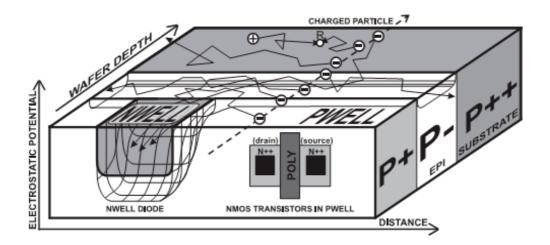

Since 1990s, CMOS active pixel sensors (APS) have been intensely developed and widely used in digital cameras [18]. In 1997, a near 100% fill factor CMOS active pixel sensor was proposed for charged particle tracking [19]. The epitaxial layer is used as sensing volume. In 1999, monolithic active pixel sensors (MAPS) were implemented by IPHC-Strasbourg group for MIP detection. The MAPS are intended to be used in STAR experiments and are being improved for future HEP experiments including CBM, ILC and so on.

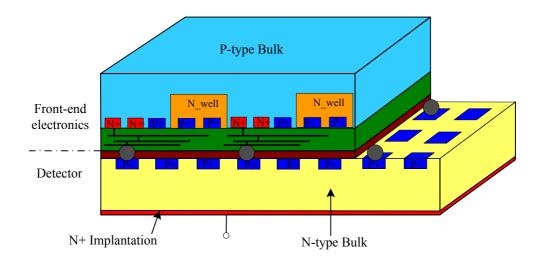

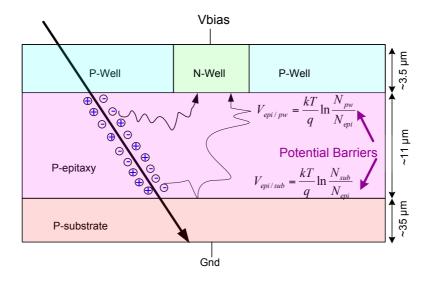

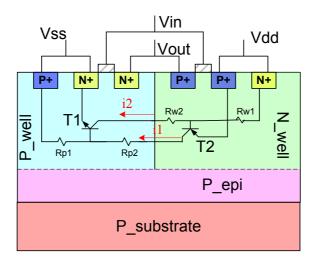

Fig. 1-12. Schematic of charge sensing element in MAPS. [9]

MAPS are based on standard CMOS processes with twin tubs on a 10-20  $\mu m$  thick epitaxial layer. The sensing elements of MAPS are N-well/P-epitaxy diodes. Fig.1-12 shows the cross section of a pixel. When a charged particle traverses through the sensing element, electron-hole pairs are generated along the track by ionizing interaction. The generated electrons thermally diffused in epitaxial layer owning to the two potential barriers formed by lightly doped P-epitaxy, highly doped P-well and highly doped P-substrate. When the electrons enter into the depletion region of the sensing diode, the electrons move towards N-well quickly due to the presence of the electric field. The collected charges are integrated on the junction capacitor of the sensing diode, and then read out by the circuits on the same substrate. The fill factor can achieve 100% if there is no additional N-well in pixel. In addition, the chip generally can be thinned down to about 50 um  $\sim$  100  $\mu m$  to satisfy the material budgets in the HEP experiments. As a result, the material budget is in order of  $0.1 X_0$

The detection performances of MAPS have been demonstrated by a series of MIMOSA (Minimum Ionizing particle MOS Active pixel sensor) chips [20-22]. The spatial resolution can achieve  $1\sim2$  µm; the readout speed can achieve 35 µs per frame; the equivalent input noise is about 20 e<sup>-</sup> to 30 e<sup>-</sup>.

#### 1.3 Applications of MAPS in HEP

#### 1.3.1 **Why MAPS?**

In the high energy physics experiments, the detectors are developed for high spatial resolution, high readout speed, high radiation tolerance, and low material budgets. To detect the short-lived particles, the detectors are placed quite close to the interaction point (primary vertex). Thereby, the impinging particle density is quite high. Thus, enormous number of particle collisions should be observed and high accuracy is preferred. In order to get high accuracy, high spatial resolution (high granularity) is desired. The high granularity will lead to abundant data to be processed. (Generally, the actual granularity should be compromised with the whole sensing area.) Considering the enormous number of particle collisions, high readout speed is essential. In addition, the scattering when a particle traverses through the sensor layers may influence the particle's trajectory. Hence, the mass of the material, namely material budgets, should be low enough to achieve the required accuracy. Moreover, the detector should be survived under the irradiation of the particles.

Requirements of Future PIXEL **MAPS** Detector **Topics** Hybrid **CCD** (2012)**STAR CMB ILC** Material Few 0.1% ~1% X0 ~0.1% X0 ~0.1% X0 ~0.3% X0 budget X0**Spatial** ~30 µm  $\sim$ 1-2  $\mu$ m  $\sim 5 \mu m$  $\sim$ 2-3  $\mu$ m  $\sim 1-2 \mu m$  $\sim 1-2 \mu m$ resolution Time ~ 25 μs、  $\sim 200 \ \mu s$  $\sim 100 \text{ ns}$  $\sim 25 \text{ ns}$  $\sim 50 \ \mu s$  $\sim 35 \ \mu s$ ~ 100 µs resolution  $\sim 10^{15}$  $\sim 10^{10}$  $\sim 10^{12}$  $\sim \! 10^{15}$  $\sim 10^{12} - 10^{13}$  $\sim \! 10^{13}$ Radiation  $n_{eq}/cm^2$ hardness  $n_{eq}/cm^2$  $n_{eq}/cm^2$  $n_{eq}/cm^2$  $n_{eq}/cm^2$  $n_{eq}/cm^2$

Table 1-1 Compare of the attractive detectors

In the prevailing detector technologies, hybrid pixel sensor, CCD, DEPFET and MAPS are the potential ones for future high energy physics experiments. The DEPFET requires a very special process and MPI is the only producer of this device although it has very good performances. The rests are compared in Table 1-1. The hybrid technology has the disadvantages on material budgets and spatial resolution. Due to the two layers for sensors and readout circuits and the connections between them, hybrid pixel sensors are much thicker than that can be done in a CCD or MAPS

technology. In addition, the readout channels make the pixel size of hybrid sensor much greater than that in the other technologies. The CCD sensors are much susceptive to hadron irradiation. Since the charge is transferred from one pixel to another in CCD sensor, the charge in the end row of a CCD chip may be transferred through more than 1000 pixels for a 1000×1000 array. Sum of the loss in charge transfer produces large signal losses and signal sharing. In addition, CCD requires a low temperature operation environment, which means mass budgets due to cooling facilities. MAPS can achieve trade-off between spatial resolution, material budget, radiation tolerance, and readout speed. Thereby, MAPS are very attractive in future high energy physics experiment for particle tracking, such as STAR, CBM and ILC.

#### 1.3.2 Example of HEP experiments – STAR experiment

STAR experiment is significantly introduced in this thesis since MAPS are intended to be used in the upgrade of STAR experiment in the near future and the research in this thesis is mostly concerned in the STAR experiment.

STAR, short for solenoidal tracker at RHIC, is one of the four experiments constructed at RHIC. The primary physics task of STAR is to study the formation and characteristics of the quark-gluon plasma (QGP), which is a hot and dense state as the matter in the moments after Big Bang. In this state, mesons and baryons are no longer existed as hadrons but as plasma of quarks and gluons. It is believed that this state has been existed for a few microseconds when matter started to be formed. In STAR experiment, Au particles or protons are accelerated to near relativistic speeds from opposite directions and are collided in the center of STAR detector. The matter produced in the collision can be investigated by studying the dynamics of the produced particles and the interaction of the medium with penetrating probes. The STAR experiment features detector systems for high precision tracking, momentum analysis, and particle identification [23].

Fig.1-13 shows the STAR detector. The heart of the STAR detector includes the silicon vertex tracker (SVT) and time projection chamber (TPC) for detection of trajectory and stopping power, respectively. The SVT consists of three cylindrical layers of silicon drift detectors at the radius of approximately 7, 11, and 15 cm. For three layers, the total average radiation length is below 6%. The SVT is used for accuracy position detection. The particle momentum will be provided by the track curvature in the magnetic field. The TPC is a gaseous detector. It is used for three-dimensional imaging of the ionization trail left along the path of charged particles. It helps distinguish particles with different masses or charges. It was improved by a silicon strip detector (SSD) at radius of 23 cm. The SSD is built in double-side silicon strip technology. It can achieve resolution of 20 µm in the transverse plane. The total radiation length of SSD is bout 1%. For the particle energy measurement, the electromagnetic calorimeter is outside of the TPC. To extend the tracking to the forward region, a radial-drift TPC is installed for complete azimuthal coverage and symmetry. To get the particle momenta, all above are installed in a large solenoid magnet, where the operating field is about 0.5T. The presented STAR

detector allows for the primary vertex with a precision of approximately  $100 \mu m$  and secondary decay vertices with precision of about  $500 \mu m$ .

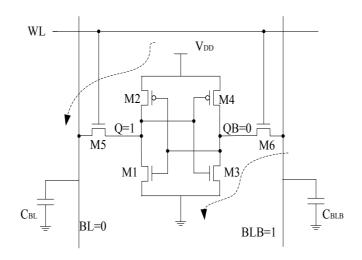

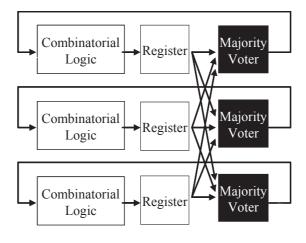

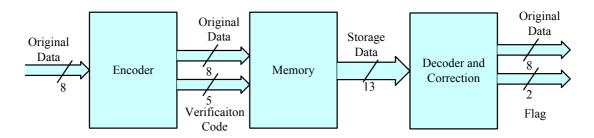

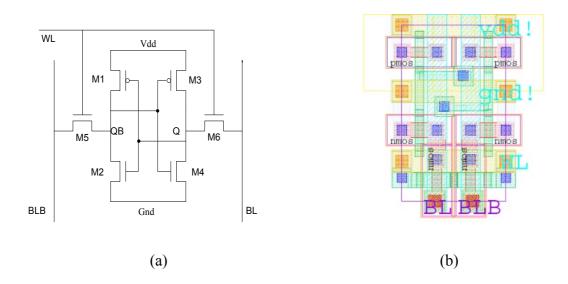

(a)