# Application d'un langage de programmation de type flot de données à la synthèse haut-niveau de système de vision en temps-réel sur matériel reconfigurable

Sameer Ahmed

## ▶ To cite this version:

Sameer Ahmed. Application d'un langage de programmation de type flot de données à la synthèse haut-niveau de système de vision en temps-réel sur matériel reconfigurable. Autre. Université Blaise Pascal - Clermont-Ferrand II, 2013. Français. NNT: 2013CLF22334. tel-00844399

# HAL Id: tel-00844399 https://theses.hal.science/tel-00844399

Submitted on 15 Jul 2013

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

$N^{\circ}$  d'ordre : D.U.2334 EDSPIC : 605

## Université Blaise Pascal - Clermont-Ferrand II

## ÉCOLE DOCTORALE SCIENCES POUR L'INGÉNIEUR DE CLERMONT-FERRAND

## Thèse

présentée par

### Sameer Ahmed

pour obtenir le grade de

## Docteur d'Université

SPÉCIALITÉ: VISION POUR LA ROBOTIQUE

# Application of a Dataflow Programming Language to the High Level Synthesis of Real-Time Vision Systems on Reconfigurable Hardware

Soutenue publiquement le 24 Janvier 2013 devant le jury:

| Μ. | Greg Michaelson     | Rapporteur         |

|----|---------------------|--------------------|

| Μ. | Hassan Rabah        | Rapporteur         |

| Μ. | Dominique Ginhac    | Examinateur        |

| Μ. | Julien Dubois       | Examinateur        |

| Μ. | Jean Pierre Derutin | Examinateur        |

| Μ. | François Berry      | Examinateur        |

| Μ. | Jocelyn Sérot       | Directeur de thèse |

# Abstract

Field Programmable Gate Arrays (FPGAs) are reconfigurable devices which can outperform General Purpose Processors (GPPs) for applications exhibiting parallelism. Traditionally, FPGAs are programmed using Hardware Description Languages (HDLs) such as Verilog and VHDL. Using these languages generally offers the best performances but the programmer must be familiar with digital design. This creates a barrier for the software community to use FPGAs and limits their adoption as a computing solution.

To make FPGAs accessible to both software and hardware programmers, a number of tools have been proposed both by academia and industry providing high-level programming environment. A widely used approach is to convert C-like languages to HDLs, making it easier for software programmers to use FPGAs. But these approaches generally do not provide performances on the par with those obtained with HDL languages. The primary reason is the inability of C-like approaches to express parallelism. Our claim is that in order to have a high level programming language for FPGAs as well as not to compromise on performance, a shift in programming paradigm is required. We think that the dataflow/actor programming model is a good candidate for this.

This thesis explores the adoption of dataflow/actor programming model for programming FPGAs. More precisely, we assess the suitability of CAPH, a domain-specific language based on this programming model for the description and implementation of stream-processing applications on FPGAs. The expressivity of the language and the efficiency of the generated code are assessed experimentally using a set of test bench applications ranging from very simple applications (basic image filtering) to more complex realistic applications such as motion detection, Connected Component Labeling (CCL) and JPEG encoder.

**Keywords:** Dataflow programming, stream-processing applications, FPGA, computer vision.

# Résumé

Les circuits reconfigurables de type FPGA (Field Programmable Gate Arrays) peuvent désormais surpasser les processeurs généralistes pour certaines applications offrant un fort degré de parallélisme intrinsèque. Ces circuits sont traditionnellement programmés en utilisant des langages de type HDL (Hardware Description Languages), comme Verilog et VHDL. L'usage de ces langages permet d'exploiter au mieux les performances offertes par ces circuits mais requiert des programmeurs une très bonne connaissance des techniques de conception numérique. Ce pré-requis limite fortement l'utilisation des FPGA par la communauté des concepteurs de logiciel en général.

Afin de pallier cette limitation, un certain nombre d'outils de plus haut niveau ont été développés, tant dans le monde industriel qu'académique. Parmi les approches proposées, celles fondées sur une transformation plus ou moins automatique de langages de type C ou équivalent, largement utilisés dans le domaine logiciel, ont été les plus explorées. Malheureusement, ces approches ne permettent pas, en général, d'obtenir des performances comparables à celles issues d'une formulation directe avec un langage de type HDL, en raison, essentiellement, de l'incapacité de ces langages à exprimer le parallélisme intrinsèque des applications. Une solution possible à ce problème passe par un changement du modèle de programmation même. Dans le contexte qui est le notre, le modèle flot de données apparaît comme un bon candidat.

Cette thèse explore donc l'adoption d'un modèle de programmation flot de données pour la programmation de circuits de type FPGA. Plus précisémment, nous évaluons l'adéquation de CAPH, un langage orienté domaine (*Domain Specific Language*) à la description et à l'implantation sur FPGA d'application opérant à la volée des capteurs (*stream processing applications*). L'expressivité du langage et l'efficacité du code généré sont évaluées expérimentalement en utilisant un large spectre d'applications, allant du traitement d'images bas niveau (filtrage, convolution) à des applications de complexité réaliste telles que la détection de mouvement, l'étiquetage en composantes connexes ou l'encodage JPEG.

Mots-clefs: Modèle flot de données, FPGA, traitement d'images, vision par ordinateur.

Dedicated to my father

# Contents

| 1 | Inti      | roduct                   | ion                                      | 1  |  |

|---|-----------|--------------------------|------------------------------------------|----|--|

| 2 | Rec       | Reconfigurable Computing |                                          |    |  |

|   | 2.1 FPGAs |                          |                                          |    |  |

|   |           | 2.1.1                    | FPGA Architecture                        | 10 |  |

|   |           |                          | 2.1.1.1 Logic Block                      | 10 |  |

|   |           |                          | 2.1.1.2 Routing Architecture             | 11 |  |

|   |           |                          | 2.1.1.3 Input and Outputs                | 13 |  |

|   |           |                          | 2.1.1.4 Others blocks                    | 13 |  |

|   |           | 2.1.2                    | Programming FPGAs                        | 15 |  |

|   | 2.2       | High 1                   | Level Synthesis (HLS) for FPGAs          | 16 |  |

|   | 2.3       | Dataf                    | low Programming                          | 18 |  |

|   |           | 2.3.1                    | Dataflow Programming Model               | 18 |  |

|   |           | 2.3.2                    | Dataflow Programming Languages           | 19 |  |

|   |           | 2.3.3                    | Dataflow Programming Languages for FPGAs | 20 |  |

|   |           |                          | 2.3.3.1 CAL (Caltrop Actor Language)     | 20 |  |

|   |           |                          | 2.3.3.2 Canals                           | 22 |  |

|   |           |                          | 2.3.3.3 StreamIT                         | 23 |  |

|   |           |                          | 2.3.3.4 FPGA Brook                       | 25 |  |

|   |           | 2.3.4                    | Conclusion                               | 27 |  |

| 3 | The       | c CAP                    | H language                               | 29 |  |

|   | 3.1       | CAPI                     | I Types                                  | 31 |  |

|   |           | 3.1.1                    | Base Types                               | 31 |  |

|   |           | 3.1.2                    | Structured Types                         | 31 |  |

|   |           |                          | 3.1.2.1 Arrays                           | 32 |  |

|   |           |                          | 3.1.2.2 DC (Data/Control) Type           | 32 |  |

|   | 3.2       | Progra                   | am Structure                             | 33 |  |

|   |           | 3.2.1                    | Type Declarations                        | 33 |  |

|   |           | 3.2.2                    | Global Declarations                      | 33 |  |

|   |           | 3.2.3                    | I/O Declarations                         | 34 |  |

|   |           | 3.2.4                    | Actor Declarations                       | 34 |  |

|   |           |                          | 3.2.4.1 Examples                         | 36 |  |

VIII

|   |     | 3.2.5 Network Declarations               |  |  |  |  |  |  |  |  |  |

|---|-----|------------------------------------------|--|--|--|--|--|--|--|--|--|

|   | 3.3 | Tools and design flow                    |  |  |  |  |  |  |  |  |  |

|   |     | 3.3.1 Graph Visualizer                   |  |  |  |  |  |  |  |  |  |

|   |     | 3.3.2 Reference Interpreter              |  |  |  |  |  |  |  |  |  |

|   |     | 3.3.3 Compiler                           |  |  |  |  |  |  |  |  |  |

|   |     | 3.3.3.1 Front-End                        |  |  |  |  |  |  |  |  |  |

|   |     | 3.3.3.2 Elaboration                      |  |  |  |  |  |  |  |  |  |

|   |     | 3.3.3.3 Back-Ends                        |  |  |  |  |  |  |  |  |  |

|   |     |                                          |  |  |  |  |  |  |  |  |  |

| 4 |     | e VHDL Backend 45                        |  |  |  |  |  |  |  |  |  |

|   | 4.1 | Data Representation                      |  |  |  |  |  |  |  |  |  |

|   |     | 4.1.1 Data/Control Encoding              |  |  |  |  |  |  |  |  |  |

|   |     | 4.1.2 Token Insertion                    |  |  |  |  |  |  |  |  |  |

|   | 4.0 | 4.1.3 Token Removal                      |  |  |  |  |  |  |  |  |  |

|   | 4.2 | VHDL Code Generation                     |  |  |  |  |  |  |  |  |  |

|   |     | 4.2.1 VHDL code for the dataflow network |  |  |  |  |  |  |  |  |  |

|   | 4.9 | 4.2.2 VHDL code for the sub actor        |  |  |  |  |  |  |  |  |  |

|   | 4.3 | Dimensionning FIFOs                      |  |  |  |  |  |  |  |  |  |

|   |     | 4.3.1 FIFO size                          |  |  |  |  |  |  |  |  |  |

|   |     | 4.3.2 Actual FIFO Implementation         |  |  |  |  |  |  |  |  |  |

| 5 | Exa | amples 61                                |  |  |  |  |  |  |  |  |  |

|   | 5.1 | Arithmetic                               |  |  |  |  |  |  |  |  |  |

|   | 5.2 | One-pixel delay                          |  |  |  |  |  |  |  |  |  |

|   | 5.3 | One-line delay                           |  |  |  |  |  |  |  |  |  |

|   | 5.4 | 1x3 Convolution                          |  |  |  |  |  |  |  |  |  |

|   | 5.5 | 3x3 Convolution                          |  |  |  |  |  |  |  |  |  |

|   | 5.6 | Functions                                |  |  |  |  |  |  |  |  |  |

|   |     | 5.6.1 Global Functions                   |  |  |  |  |  |  |  |  |  |

|   |     | 5.6.2 External Functions                 |  |  |  |  |  |  |  |  |  |

|   |     |                                          |  |  |  |  |  |  |  |  |  |

| 6 |     | blications 87                            |  |  |  |  |  |  |  |  |  |

|   | 6.1 | Compiling CAPH Programs on FPGA          |  |  |  |  |  |  |  |  |  |

|   | 6.2 | Motion Detection Application             |  |  |  |  |  |  |  |  |  |

|   |     | 6.2.1 Objective                          |  |  |  |  |  |  |  |  |  |

|   |     | 6.2.2 Principle                          |  |  |  |  |  |  |  |  |  |

|   |     | 6.2.3 Implementation                     |  |  |  |  |  |  |  |  |  |

|   |     | 6.2.4 Performance Results                |  |  |  |  |  |  |  |  |  |

|   | 6.3 | Connected Component Labeling             |  |  |  |  |  |  |  |  |  |

|   |     | 6.3.1 Objective                          |  |  |  |  |  |  |  |  |  |

|   |     | 6.3.2 Principle                          |  |  |  |  |  |  |  |  |  |

|   |     | 6.3.3 Implementation                     |  |  |  |  |  |  |  |  |  |

|   |     | 6.3.4 Experimental Results               |  |  |  |  |  |  |  |  |  |

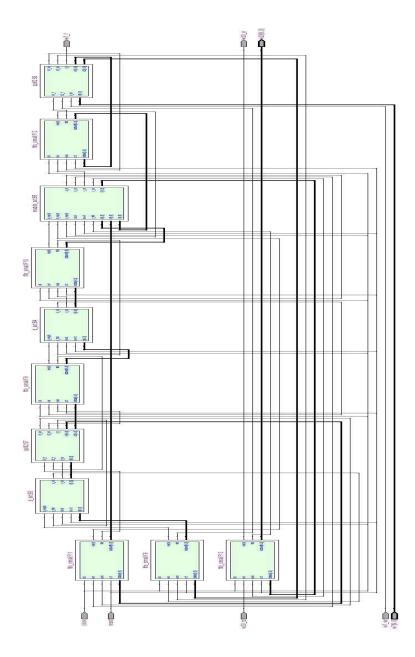

|   | 6.4 | JPEG Encoder                             |  |  |  |  |  |  |  |  |  |

|   |     | 6.4.1 Objective                          |  |  |  |  |  |  |  |  |  |

|   |     | 6.4.2 Principle 115                      |  |  |  |  |  |  |  |  |  |

Contents

|   |                                          | 6.4.2.1      | Discrete Cosine Transformation (DCT) | 115 |  |

|---|------------------------------------------|--------------|--------------------------------------|-----|--|

|   |                                          | 6.4.2.2      | Quantization                         | 117 |  |

|   |                                          | 6.4.2.3      | ZigZag Scan                          | 118 |  |

|   |                                          | 6.4.2.4      | Run Length Encoding                  | 119 |  |

|   | 6.4.3                                    | САРН і       | mplementation                        | 119 |  |

|   | 6.4.4                                    | Experim      | nental Results                       | 131 |  |

|   |                                          | 6.4.4.1      | Final Results                        | 133 |  |

|   |                                          | 6.4.4.2      | Performance Results                  | 137 |  |

| 7 | Conclusio                                | $\mathbf{n}$ |                                      | 143 |  |

| A | A Matlab Code for JPEG Encoder           |              |                                      |     |  |

| В | B Handwritten VHDL code for JPEG Encoder |              |                                      |     |  |

X Contents

# List of Figures

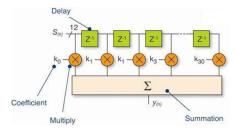

| 2.1  | Implementation of 32 tap FIR filter on FPGA                                   | 9  |

|------|-------------------------------------------------------------------------------|----|

| 2.2  | Implementation of 32 tap FIR filter on a classical processor                  | 10 |

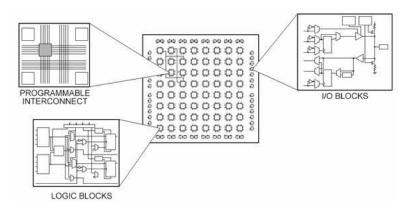

| 2.3  | Generic FPGA architecture                                                     | 10 |

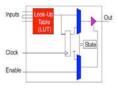

| 2.4  | Generalized FPGA Logic Element                                                | 11 |

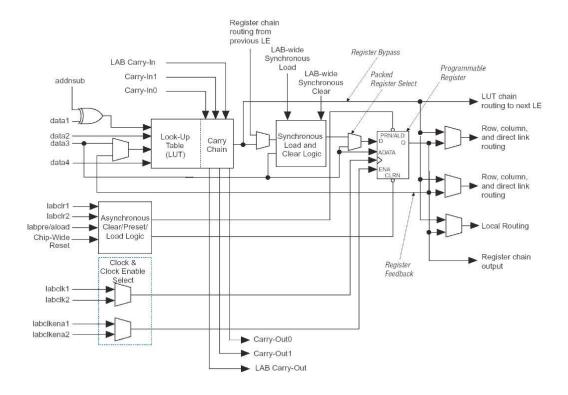

| 2.5  | Altera Cyclone II Logic Element [1]                                           | 12 |

| 2.6  | FPGA routing technology                                                       | 12 |

| 2.7  | FPGA routing modeling                                                         | 13 |

| 2.8  | Typical I/O pad from the Altera Stratix                                       | 13 |

| 2.9  | Typical application for each Stratix memory blocks and Stratix floor-planning | 14 |

| 2.10 | Altera Stratix II DSP Block [2]                                               | 15 |

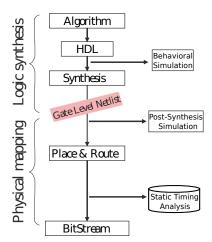

| 2.11 | FPGA design implementation steps                                              | 15 |

| 2.12 | Von Neumann vs dataflow execution model                                       | 19 |

| 2.13 | CAL dataflow network                                                          | 21 |

| 2.14 | Canals dataflow network                                                       | 23 |

| 2.15 | StreamIT dataflow network                                                     | 25 |

| 2.16 | FPGA Brook dataflow network                                                   | 26 |

| 3.1  | The structured stream representation of a 4x4 image                           | 33 |

| 3.2  | The image after application of a one-pixel delay per line                     | 39 |

| 3.3  | A dataflow network involving three actors                                     | 40 |

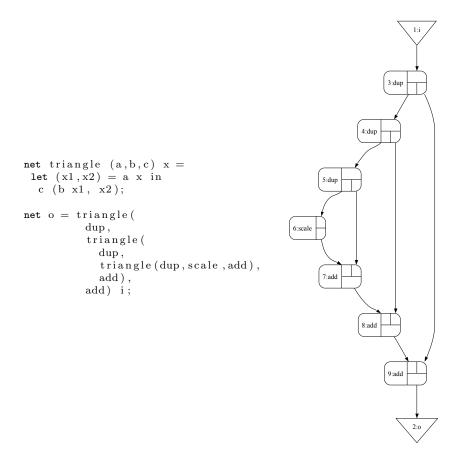

| 3.4  | A higher-order wiring function in CAPH                                        | 41 |

| 3.5  | Building complex graph patterns using higher-order wiring functions           | 41 |

| 3.6  | CAPH Toolset                                                                  | 42 |

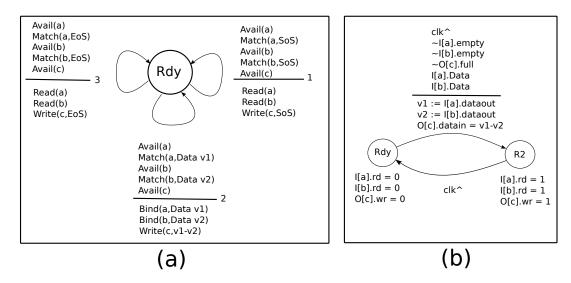

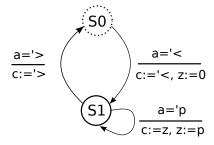

| 4.1  | Finite state machine diagram for token insertion process                      | 48 |

| 4.2  | Token insertion and removal                                                   | 48 |

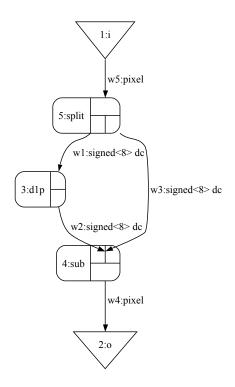

| 4.3  | Graph of dx Example                                                           | 49 |

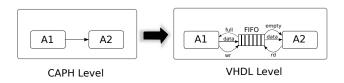

| 4.4  | CAPH to VHDL transition of actor connectivity                                 | 52 |

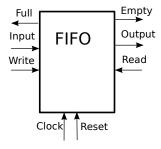

| 4.5  | FIFO Architecture                                                             | 53 |

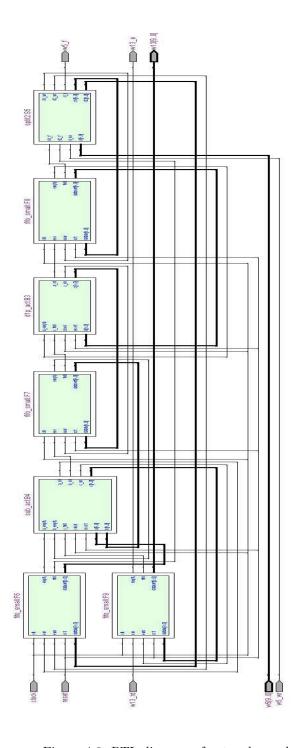

| 4.6  | RTL diagram of network graph                                                  | 54 |

| 4.7  | Intermediate Representation (IR) for the sub actor and transformation of the  |    |

|      | second rule $\dots$                                                           | 56 |

| 4.8  | RTL diagram of sub actor                                                      | 58 |

XII List of Figures

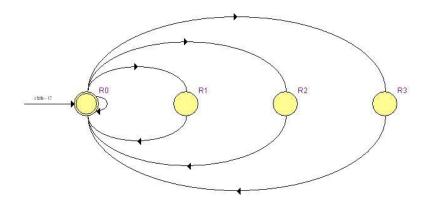

| 4.9  | State machine generated by sub actor                                                                                                                        |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4.10 | Annotation generated by the SystemC code                                                                                                                    |

| 5.1  | One-pixel delay actor state diagram                                                                                                                         |

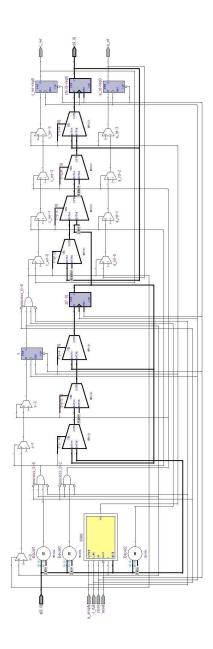

| 5.2  | RTL view of d1p actor                                                                                                                                       |

| 5.3  | One-line delay actor state diagram                                                                                                                          |

| 5.4  | RTL view of d1l actor                                                                                                                                       |

| 5.5  | Dataflow graph of 1x3 Convolution example                                                                                                                   |

| 5.6  | RTL view of maddn actor                                                                                                                                     |

| 5.7  | RTL view of network file for 1x3 Convolution                                                                                                                |

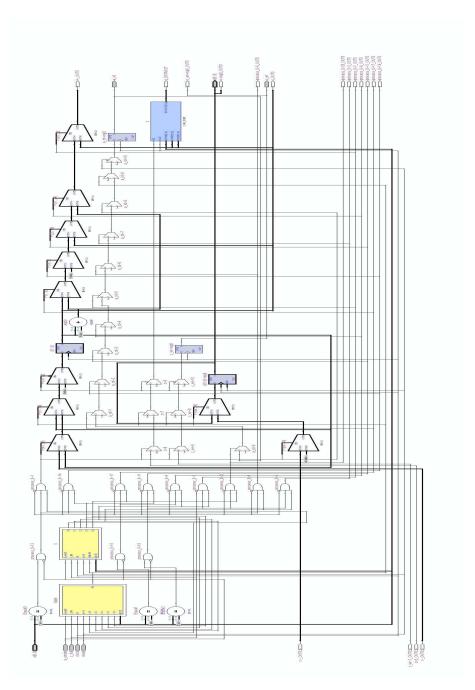

| 5.8  | Dataflow graph of 3x3 Convolution application                                                                                                               |

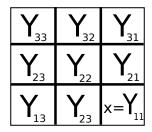

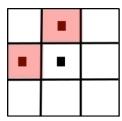

| 5.9  | Neighborhood of current pixel x                                                                                                                             |

| 5.10 | RTL view of 3x3 Convolution application $\dots \dots \dots$ |

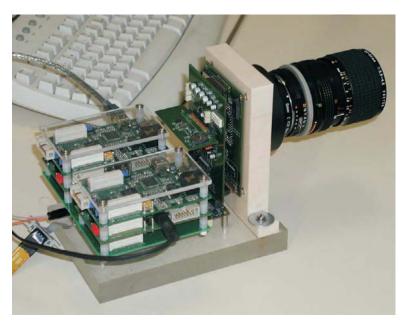

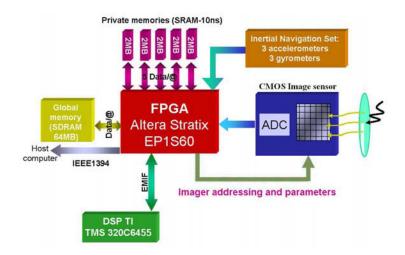

| 6.1  | SeeMOS smart camera                                                                                                                                         |

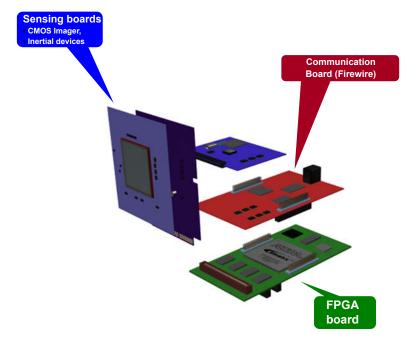

| 6.2  | SeeMOS camera, developed at LASMEA                                                                                                                          |

| 6.3  | Hardware architecture of the SeeMOS platform                                                                                                                |

| 6.4  | Different cards forming the heterogeneous SeeMOS platform                                                                                                   |

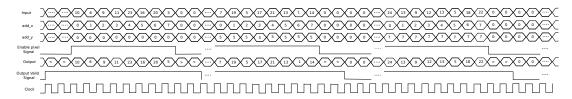

| 6.5  | FPGA I/O                                                                                                                                                    |

| 6.6  | Structured stream generation for 8x8 image                                                                                                                  |

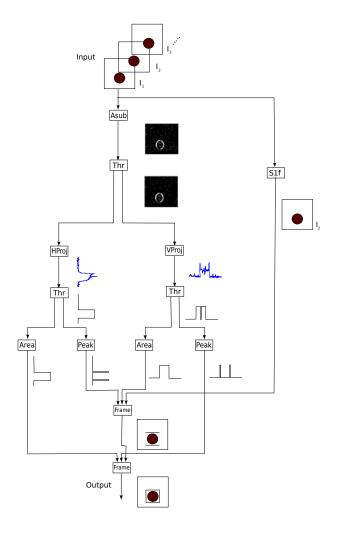

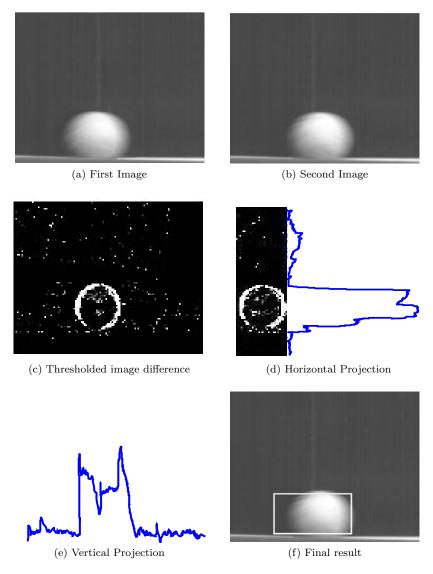

| 6.7  | Different steps of motion detection application                                                                                                             |

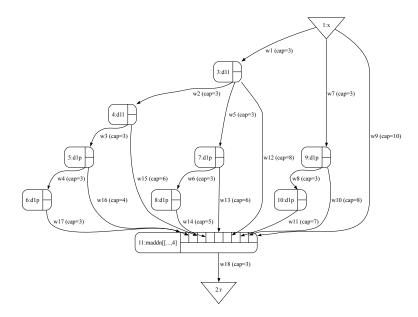

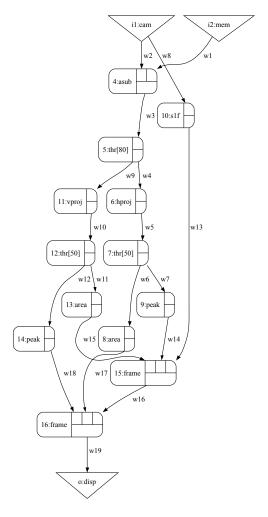

| 6.8  | Dataflow graph of motion detection application                                                                                                              |

| 6.9  | Motion detection application results                                                                                                                        |

| 6.10 | 4-Pixel Connectivity                                                                                                                                        |

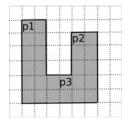

| 6.11 | Label merging in U-Shaped Object                                                                                                                            |

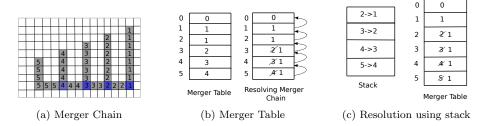

| 6.12 | Merger chain and its resolution                                                                                                                             |

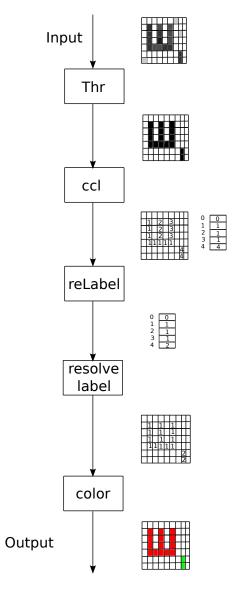

| 6.13 | Different steps of CCL application                                                                                                                          |

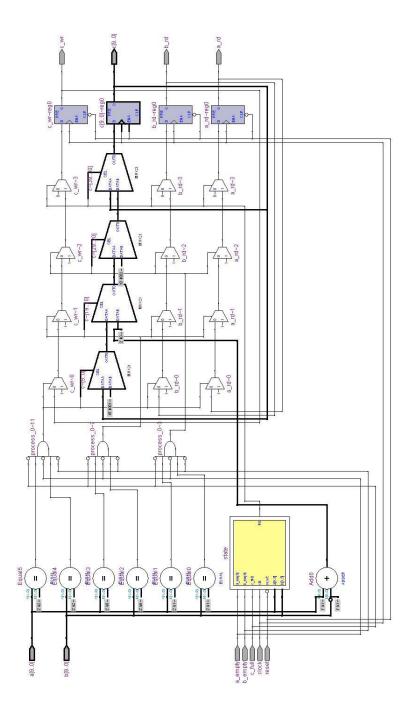

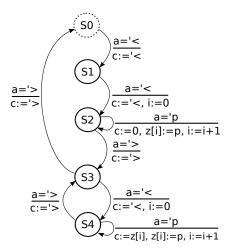

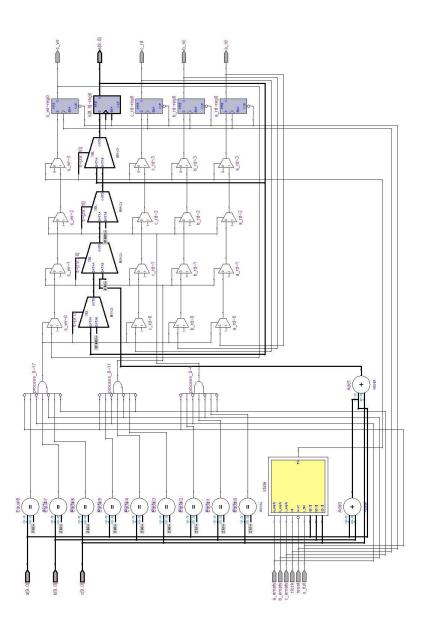

| 6.14 | Dataflow Graph of CCL application                                                                                                                           |

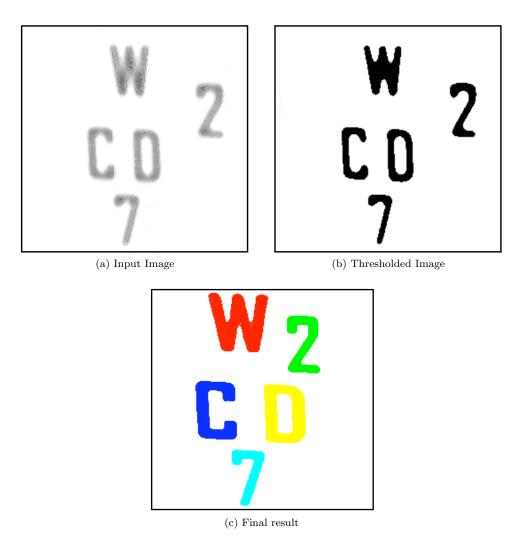

| 6.15 | CCL application results                                                                                                                                     |

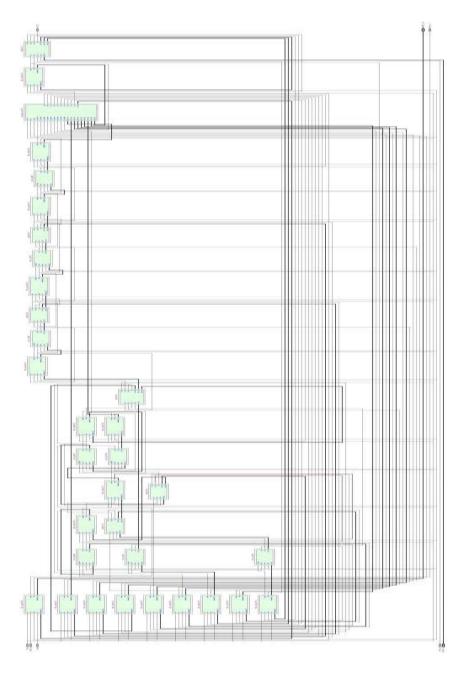

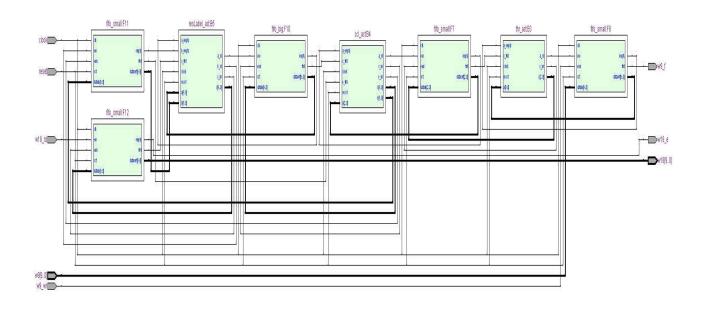

| 6.16 | RTL view of CCL application                                                                                                                                 |

| 6.17 | FPGA floorplan of CCL application                                                                                                                           |

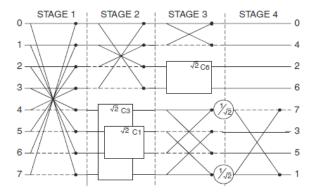

|      | Loeffler Algorithm to compute DCT                                                                                                                           |

| 6.19 | The Butterfly Block                                                                                                                                         |

| 6.20 | The Rotator Block                                                                                                                                           |

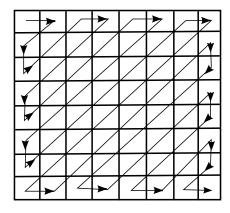

| 6.21 | Zig<br>Zag Scan Pattern                                                                                                                                     |

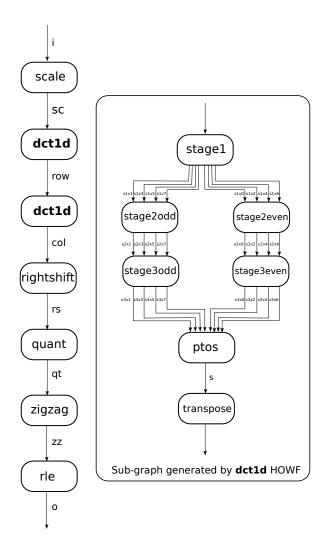

| 6.22 | Dataflow graph of JPEG encoder application                                                                                                                  |

# List of Tables

| 2.1  | Dataflow Languages for FPGAs                                      |

|------|-------------------------------------------------------------------|

| 3.1  | Builtin operators on scalar types                                 |

| 5.1  | Examples summary                                                  |

| 6.1  | Characteristics of the FPGA device used in SeeMOS smart camera 91 |

| 6.2  | Motion Detection Application Performance Results                  |

| 6.3  | CCL Application Performance Results                               |

| 6.4  | DCT (Altera)                                                      |

| 6.5  | Quantization + Zigzag Ordering (Altera)                           |

| 6.6  | Run Length Encoding (Altera)                                      |

| 6.7  | DCT (Xilinx)                                                      |

| 6.8  | Quantization + Zigzag Ordering (Xilinx)                           |

| 6.9  | Run Length Encoding (Xilinx)                                      |

| 6.10 | All parts (Altera)                                                |

| 6.11 | All parts (Xilinx)                                                |

XIV List of Tables

|              | 1 |  |  |  |  |

|--------------|---|--|--|--|--|

| l<br>Chapter | 1 |  |  |  |  |

# Introduction

Field Programmable Gate Arrays (FPGAs) are reconfigurable devices used for implementation of digital logic circuits. In the past decade, there has been a tremendous increase in the capacity of FPGAs. Moreover, many applications exhibiting parallelism, when implemented on FPGAs can outperform General Purpose Processors (GPPs). An example of such a class of applications is stream-processing applications. These applications operate on continuous streams of data and require high computing power. Furthermore, most of the computationally demanding tasks in these applications show parallelism. This makes FPGAs, a good candidate for implementing these applications.

FPGAs are programmed with *Hardware Description Languages* (HDLs) such as Verilog and VHDL. These languages provide the best performances in terms of area and speed. But, since these languages were designed for hardware designers, one has to acquire expertise in digital design to use them. From a programming point of view, this means that the FPGA programming community is limited to hardware experts. A desirable objective, to enlarge this community -and therefore the use of FPGA- is to make programming accessible to both hardware as well as software programmers.

To make this possible, a lot of tools have been proposed, both from academia and industry to provide high-level programming environment for FPGAs. The most commonly used approach, is to convert C-like languages into (V)HDL. Since C is widely used by the software community, this makes it easier for software programmer to program FPGAs. But this shift comes at a cost. As discussed earlier, HDLs provide best performances which is crucial for large applications. C-like approaches have to compromise on these performances. There are many reasons for this. The primary reason is the incapability of C-like languages to express parallelism in applications, which is the main factor of performance gain on FPGAs. Since C is intrinsically sequential, the task to identify parallelism is left to the compiler. In the current state-of-the-art this cannot be fully accomplished in an automatic way.

This means that in order to have a high level programing model for FPGA as well as not to compromise on performance, a shift in programming paradigm is required. In other words, it is crucial to reduce the gap between the *programming* model (as viewed by the programmer) and *implementation* model (as implemented in target hardware). The *Dataflow/actor* programming models, seem to be good candidate for this.

This thesis explores the adoption of a dataflow/actor programming model for programming stream-processing applications on FPGAs. More precisely, it investigates whether applications can be implemented at higher level using this model without compromising on performance. CAPH [3], a domain specific language based on the dataflow/actor programming model, is used to evaluate the aforementioned. The development and implementation of CAPH was independent of this thesis work. The main contribution of the thesis lies in the experimental benchmark of CAPH. First, a set of simple applications are developed to test whether it is feasible to use CAPH for programming FPGAs, more specifically to test whether it improves programmer efficiency or not. The results reported here show that CAPH can be used to efficiently implement applications for FPGAs at a higher abstraction level. In the second step, the performance of CAPH is evaluated by using more complex applications (Motion Detection Application, Connected Component Labeling (CCL) and JPEG encoder). For the last application results are also compared with direct VHDL implementation as well as another popular dataflow language CAL. The comparison with the former is used to prove the gain in

expressivity offered by a higher level language does not come at the price of a reduced efficiency.

The main research contribution of this thesis is to evaluate CAPH for programming image processing applications on FPGAs, this includes:

- At start, development of simple image processing applications in CAPH.

- Later, a benchmark of complex image processing applications implemented in CAPH.

- The experimental results of one application (JPEG encoder) are compared with handwritten VHDL and another popular dataflow language CAL on two different FPGA platforms.

The overall organization of the thesis is as follows:

Chapter 2 starts by introducing FPGAs, their architecture and the reason for their current emergence in the reconfigurable computing domain. Programming issues, which are the main obstacle to their widespread acceptance are described. Several state of the art C-like approaches to this problem are described and the reason why these approaches fail to meet the required performance are explained. Then, the Dataflow/actor programming model is proposed as an alternative programming model and a introduction to the dataflow programming model is given. Since this model was initially designed to program dataflow machines, some of the earlier and most famous languages based on this model to program dataflow machines are described. The recent and renewed interest in this model is due to the emergence of FPGAs. The reason for the natural coherence of this model for programming FPGAs are outlined. This chapter will also describe some languages based on the dataflow programming model for programming FPGAs.

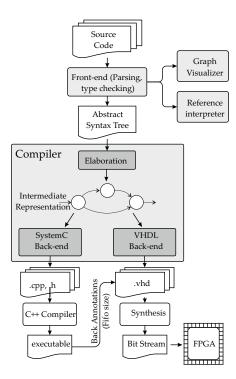

Chapter 3 gives an overview of the CAPH language. The main constructs of the language are illustrated with examples. Like other dataflow/actor based languages, applications are described at two levels: one to describe the behavior of each actor and the other the interconnections between the actors. The distinguished features of CAPH in describing these two levels, as compared to the other languages discussed in the previous chapter, are also highlighted. We also describe the design flow of the compiler and how this flow is supported by tools offered by the CAPH language.

Chapter 4 discusses the main issues related to the generation of VHDL code from CAPH programs. First of all, the representation of stream tokens is described at the hardware level. The process of adding control tokens to the input stream and the encoding technique used to distinguish them from data tokens is explained. With the help of small examples, an analysis of the VHDL code generated for each CAPH statement/construct is conducted. This covers the code generated for both the actor(s) and network parts. Issues related to FIFOs (used to connect actors) are also discussed, since this is an important aspect of dataflow/actor model.

Chapter 5 focuses on some programming features introduced by CAPH distinct from the basic programming constructs described in chapter 3. This chapter is divided into three parts. The first part focuses on expressing arithmetic operations. The use of built-in library operators provided by CAPH and the implementation of more complex operators are demonstrated. The second part describes some memory-related features, which play an important role in image

processing applications, as used by many applications in the next chapter. The implementation of a feature at the CAPH level as well as the resource utilization of the resulting VHDL design are explained in detail. Finally, the functional features of CAPH are analyzed with the help of examples which help to access their utility in improving application expressivity.

Chapter 6 starts by introducing the target platform we used to test CAPH applications on FPGA. Then it moves to demonstrate the effectiveness of the CAPH language both in terms of expressivity and performance. These are validated by describing the implementation of several test bench applications. These applications include motion detection, connected component labeling and parts of a JPEG encoder. Each application/experiment is described as follows: first an introduction and the main objective of the implemented algorithm are given, then its formulation in CAPH is described and finally, for the target FPGA, both resource consumption (Logic Elements (LEs), memory bits, Digital Signal Processing (DSP) blocks etc.) and performance (max. clock frequency, frame per second (FPS)) are given. For the last application (i.e. the JPEG encoder parts), a comparative analysis is also made with a direct VHDL implementation and another dataflow language CAL.

Chapter 7 concludes the thesis, by highlighting the original ideas explored and giving some directions for future research work.

# Reconfigurable Computing

Reconfigurable computing (RC) refers to the ability for a system to provide some form of hardware reprogrammability. By using RC, the same hardware can be changed to execute different applications [4]. This innovative development of hardware for an unlimited amount of reuse by re-programming led to a new field where many different hardware algorithms can execute on a single hardware, as many different software algorithms can run on a conventional microprocessor. Although the field of reconfigurable computing is not new [5], the recent surge in the field is due to rapid development of FPGAs [6].

### 2.1 FPGAs

With the increase in application complexity there is a constant need for more computing power, especially for applications like video processing, image recognition and processing etc. The situation becomes more complex, when considering the factors like power consumption, manufacturing cost and time to market. To keep on increasing processing power and decreasing the aforementioned factors is a challenging task. Single high performance microprocessors simply cannot meet the performance requirement for the computationally intensive applications. The above problems with conventional microprocessors have led to the recent interest in FPGAs. The decrease in performance gain of conventional microprocessor, in addition to considerable cost of their power requirement has left a vacuum to be filled by any other cost-effective technology and FPGAs seem to fill this gap.

Figure 2.1: Implementation of 32 tap FIR filter on FPGA

In fact, due to their reconfigurable architecture, FPGAs perform hardware optimizations of resources for an application as opposed to traditional processors. This results in the hardware configuration of the FPGA according to the application. On the contrary, the traditional processor has a fixed architecture and relies on a high clock frequency or duplication of processing cores. For example, considering a signal processing algorithm FIR filter for 32 samples, an FPGA performs massive parallelism with a pipeline of 32 registers (Fig. 2.1) and produces output at each clock cycle. On the other hand, implementation on a traditional processor with an arithmetic and logic unit (ALU) will perform 32 iterations to produce the same result (Fig. 2.2).

2.1. FPGAs

Figure 2.2: The implementation is known as a multiply-and-accumulate or MAC-type implementation. This is almost certainly the way a FIR filter would be implemented on a classical processor.

It is therefore easy to understand that apart from the possibility of reconfiguration of the FPGA hardware, FPGA works in "space" while a traditional processor works in "time". In the next section, we describe the internal structure of an FPGA emphasizing the characteristics of different modules.

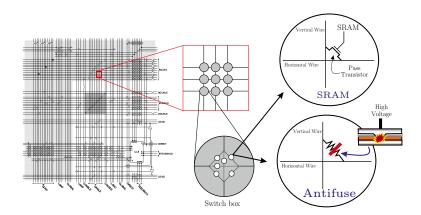

### 2.1.1 FPGA Architecture

FPGAs are components invented by Xilinx in the early 1980s [7] and improve the characteristics of the CPLD (Complex Programmable Logic Device) type circuits. The most common FPGA architecture consists of an array of logic blocks (called Configurable Logic Block (CLB) or Logic Array Block (LAB) depending on the vendor), I/O pads, and routing channels as shown in Fig. 2.3. Generally, all the routing channels have the same width (number of wires). Multiple I/O pads may fit into the height of one row or the width of one column in the array.

Figure 2.3: Generic FPGA architecture

With the passage of time, the basic architecture of FPGA has evolved to include more specialized programmable logic blocks. These include embedded memory, arithmetic logic (multiplier or Digital Signal Processing (DSP) blocks), high speed I/O and even embedded microprocessors. In the sections below, these main blocks are presented.

#### 2.1.1.1 Logic Block

Since their invention in 1980's, FPGAs have used a large variety of structure for logic block. A simplified architecture of a programmable logic block is shown in Fig. 2.4. It consists of

programmable combinational logic, a flip-flop or latch and carry chain logic. The output of the block is either the output of the combinational logic or the output of the flip-flop. The logic block in commercial FPGAs is much more flexible than this simple one. The most common way to implement the combinational logic is a look-up table (LUT), which acts as a memory with N address lines and  $2^N$  memory locations. In order to implement a specific function, the truth table has to be loaded into the memory. Because of area efficiency, most commercial FPGAs use four-input LUTs. Many FPGAs combine logic blocks to form a cluster in order to reduce the cost of routing. A special faster routing named "regional routing" is provided to connect logic blocks inside a cluster. This helps implementing larger functions inside a cluster where routing is the "speed bottleneck". For example, in the Altera Stratix family [8], each logic block consists of 4-input LUTs and 10 logic blocks are combined to form a cluster called Logic Array Block (LAB). Later Altera Stratix families use a mini-cluster known as Adaptive Logic Module (ALM) [9]. Each ALM consists of eight input adaptive look-up table (LUT), two dedicated embedded adders, and four dedicated registers. On the Xilinx side, the mini-cluster is called a Slice. Virtex 6 Slices consist of four look-up tables, eight registers, wide function multiplexer and carry logic [10]. The association of two slices is called a Configurable Logic Block (CLB).

Figure 2.4: Generalized FPGA Logic Element

#### 2.1.1.2 Routing Architecture

Logic Array blocks (LABs), DSP blocks, memory blocks and I/Os need to be connected through routing. Generally, the FPGA routing is unsegmented. That is, each wiring segment spans only one logic block before it terminates in a switch box (Fig. 2.6). By turning on some of the programmable switches within a switch box, longer paths can be constructed. For higher speed interconnect, some FPGA architectures use longer routing lines that span multiple logic blocks.

12 2.1. FPGAs

Figure 2.5: Altera Cyclone II Logic Element [1]

Figure 2.6: FPGA routing technology. There are two main approaches to configure the routing network. First, SRAM-based (Static RAM) where the configuration bitstream is stored in a classical SRAM. Since SRAM is volatile and cannot keep data without a power source, such FPGAs must be programmed (configured) upon startup. The majority of FPGAs use this routing approach. Second is the antifuse-based approach, where each device does not conduct current initially, but can be "burned" to conduct current (the antifuse behavior is thus opposite to that of the fuse, hence the name). The antifuse-based FPGAs cannot be reprogrammed since there is no way to return a burned antifuse into the initial state.

Whenever a vertical and a horizontal channel intersect, there is a switch box. In this architecture, when a wire enters a switch box, there are three programmable switches that allow it to connect to three other wires in adjacent channel segments. The pattern or topology of switches used in this architecture is the planar or domain-based switch box topology. In

this switch box topology, a wire in track number one connects only to wires in track number one in adjacent channel segments, wires in track number 2 connect only to other wires in track number 2 and so on.

Based on the switch and wire, interconnect routes can be modeled as RC networks (Fig. 2.7). The modeling explains why the placement is often a crucial point in a design. The routing length causes time delays in the path.

Figure 2.7: FPGA routing modeling

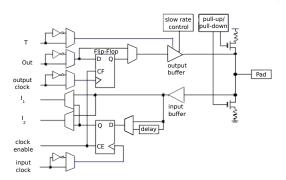

#### 2.1.1.3 Input and Outputs

Input and output blocks are used to connect an FPGA with external devices. Similar to dedicated logic blocks, FPGAs also include dedicated I/O hardware (for example, for DDR (double data rate) memories). In the Altera Stratix device, each I/O pin has an I/O element (IOE) which is located at the end of LAB rows and columns. Each IOE contains a bidirectional I/O buffer and six registers for registering input, output, and output-enable signals. There are also high speed serial interface channels which support up to 840 Mbps transfer rates.

Figure 2.8: Typical I/O pad from Altera Stratix. FPGAs provide support for dozens of I/O standards (TTL, CMOS, LVDS etc.) which are grouped in banks.

#### 2.1.1.4 Others blocks

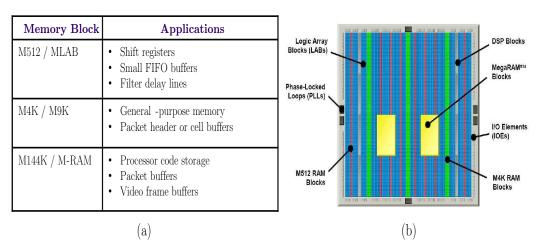

Apart from the previously described blocks, most of the latest FPGAs also integrate two other dedicated blocks : embedded memory blocks and dedicated arithmetic blocks.

### (a) Memory blocks

The circuitry inside logic blocks can be used for memory but they are inefficient for creating memories of large depth. So, FPGA vendors started providing SRAM blocks within the architecture. The classical ways to use memory inside FPGAs are:

14 2.1. FPGAs

- Register File

- Shift-register block

- ROM and waveform generation

- First-in-First-Out memory

In the Altera Stratix, it is a TriMatrix memory (Fig. 2.9, consisting of three type of RAM blocks: M512, M4K and M-RAM blocks). M512 blocks consist of 512 bits plus parity (576 bits). They can be configured with aspect ratio from 512x1 to 32x18. M4K blocks consist of 4K bits plus parity (4,608 bits). They can be configured with aspect ratio from 4Kx1 to 128x36. Finally, the M-RAM blocks consist of 512K bits plus parity (589,824 bits). These blocks can be configured with aspect ratio from 64Kx8 to 4Kx144. The memory sizes of different range facilitate the best size to be selected for the application needs without wasting many resources.

Figure 2.9: (a) Typical application for each Stratix memory blocks; (b) Stratix floor-planning [11]

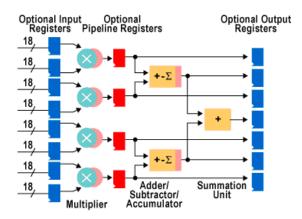

#### (b) Arithmetic blocks

Logic blocks can be used to perform any operation with the help of carry chain logic and adders but for complex operations it takes more area, delay and power. To overcome this, FPGAs have started including dedicated blocks for arithmetic operations. These blocks can perform addition/subtraction, multiplication and multiply-accumulate (MAC) operations. The Xilinx device consists of 18x18 bit multipliers and Altera device contains DSP blocks. Altera DSP blocks are more flexible than Xilinx multipliers, they can also perform accumulator function along with multiplication. These DSP blocks can be configured to eight 9x9 bit multiplier, four 18x18 multiplier or one 36x36 multiplier. These blocks also contain 18-bit input shift register (Fig. 2.10).

Figure 2.10: Altera Stratix II DSP Block [2]

This section gave an insight into different parts of an FPGA from an architectural perspective along with benefits obtained as compared to traditional processor. The next step is to implement an application to gain the benefits claimed by the device. The next section describes in detail the design flow to implement an application on an FPGA.

## 2.1.2 Programming FPGAs

To implement a design on FPGA, the design flow consist of several steps as shown in Fig. 2.11. First, the design is described using Hardware Description Languages (HDLs), such as VHDL [12] or Verilog [13]. This hardware description is synthesized and simulated to make sure it gives the intended behavior. The synthesis step takes this description and generates a gate level representation for the FPGA. It actually represents the design in terms of basic building blocks on FPGAs. The output of this design is a netlist<sup>1</sup> in EDIF (electronic design interchange format). Gate level simulation is performed to test that the design is synthesized correctly.

Figure 2.11: FPGA design implementation steps

In the next stage, the synthesized netlist is mapped on to the actual FPGA target. This is accomplished in two steps. In the *mapping* step, the components to perform logic are selected on the FPGA. They consist of selecting one LUT for simple operations or combination of LUTs

<sup>&</sup>lt;sup>1</sup>A textual description of a circuit diagram

for complex operations. In the *place and route* step, these mapped components are assigned to particular logic blocks on the FPGA and routing is performed to connect these components. This step takes into account the timing requirement for placement and routing of critical paths. In the last step, the configuration file is generated to program the FPGA. Apart from the first step (specifying the design using HDLs), all other steps are performed by CAD tools, usually provided by FPGA vendors. Since a typical user is only directly involved in the first step, we focus on this step in sequel.

Even with modern HDLs such as VHDL [12] or Verilog [13], describing a design is often a daunting task, because it requires a very good knowledge of concepts and techniques which are specific to hardware design. This is a great hurdle to the wide spread acceptance of FPGAs to software programmer community. To overcome this problem, several higher level programming languages have been proposed in recent past. Some of these will be discussed in next section.

## 2.2 High Level Synthesis (HLS) for FPGAs

The most commonly used source input for high level synthesis is based on standard languages such as ANSI C/C++ [14] and SystemC [15]. In the C-based High-level synthesis languages, the code is analyzed, constrained architecturally, and scheduled to create a register transfer level hardware design language (HDL), which is then synthesized to the gate level by the use of a logic synthesis tool. The goal of HLS is to let software programmers efficiently build and verify hardware design, by giving them better control over optimization of their design architecture. This is achieved by facilitating the programmers to describe the design using higher level tool, where the tool does the RTL implementation. Numerous languages have been proposed by different research teams. In the sequel, some of them are listed:

- Impulse-C [16] by Impulse Accelerated Technologies, is a C-based language for writing applications with the help of a library of functions to describe parallel processes. The communication between processes is based on a stream-based model. Existing VHDL designs can also be used with the help of external functions.

- Handle-C [17] is C-based hardware language provided by Celoxica. It provides statements to define parallel processing elements (par) and constructs for communication between them. It also supports flexible width variables, signals and bit-manipulation operations.

- Mitrion-C [18] is also a C-based hardware language by Mitrionics, to write code for FPGA applications. It is a ANSI-C based functional language which means that parallelism is expressed implicitly. The code written in Mitrion-C is converted to code for the Mitrion Virtual Processor (MVP) which is a reconfigurable soft-core processor.

- The Carte-C [19] development environment provides a library of pre-synthesized hardware functions to write programs. Users can also integrate their own VHDL/Verilog macros.

- Stream-C [20], by Los Alamos National Laboratory, is based on the Communicating Sequential Process (CSP) [21] model of computation. It was developed for implementing stream based applications on FPGAs. It consist of annotations for process, stream and signal. A process is independently executing an object consisting of C routines and signals synchronize execution of processes. Streams are used to associate inputs/outputs with each process. With the help of steam information, the compiler generates a process graph.

- SA-C [22] is functional, single assignment language. The compiler generates a dataflow graph of the application before generating FPGA code. SA-C does not include pointers, recursion and while-loops.

- SPARK [23] is high-level language which convert C code to VHDL. It is targeted for multimedia and image processing applications. For computational intensive blocks it performs optimizations such as loop unrolling and code motion to increase instruction level parallelism.

- The DWARV [24] C-to-VHDL generator converts C code into VHDL. The conversion process includes several phases of analysis, transformations and optimizations. It has limited C constructors, which include if statements and arithmetic and logic operations over a scalar or one dimensional array of scalar data.

- Mobius [25] is a domain specific, concurrent programming language based on the CSP model of communication. It has a Pascal-like syntax. The processes execute concurrently and exchange data through unidirectional channels.

All of the above languages are C-based except Mobius, nevertheless all expose parallelism by either providing statement-level annotations or relying on compiler to extract parallelism. In the former case, code has to be rewritten, as in case of Stream-C or SA-C. For the later, the compiler has to identify parallelism. In the current state-of-the-art, this cannot be done in a fully automatic way and the programmer is required to put annotations (pragmas) in the code to help the compiler. Finally, the code generally has to undergo various optimizations and transformations before the actual HDL generation. These optimizations and transformations vary from high level parallelization techniques to low level scheduling. The low level optimizations can be beneficial to any algorithm, but the high level optimizations are specifically suggested in the context of one field and would not give performance gains in other domains [24]. Moreover, with some of the existing tools (e.g. Handle-C, Impulse-C), transformations and optimizations require inputs from the programmer [26], who therefore must have a good knowledge of digital design.

All this makes the development of easy to use and efficient programming environments for FPGAs a challenging task [27]. In particular, one can question the use of the C language as a good basis for such an environment. In fact, as C was initially designed for single core architectures, it cannot efficiently be used as a language for expressing parallel computations. Based on this constraint, the research community has started working on domain specific languages (DSLs) for programming FPGAs [28, 29]. By restricting the class of target platforms and embedding some informations which cannot be easily expressed in a more general purpose language, DSLs offer the opportunity to reach an acceptable expressivity versus performance trade off. For this the gap between the programming model (as viewed by the programmer) and execution model (as implemented on the target hardware) must be reduced. The dataflow model of computation (MoC) has several properties making this possible. It is described in next section.

## 2.3 Dataflow Programming

## 2.3.1 Dataflow Programming Model

The dataflow programming model came into emergence in 1970s with the advent of dataflow architectures which were designed with the objective to exploit massive parallelism [30]. Because of the parallel execution of dataflow programs, these machines were able to overcome the von Neumann architecture bottlenecks [31, 32, 33]. The two major objections to the von Neumann model were the use of a global program counter and global memory [34]. From the start, it was widely acknowledged that imperative languages were not adapted to program machines based on this model [35]. Specific languages – namely dataflow languages—were designed in this context [30, 36]. After the emergence of dataflow architectures in 1970s, the research into the field of dataflow languages slowed after mid-1980s. The reason was unavailability of cost-effective dataflow hardware [37].

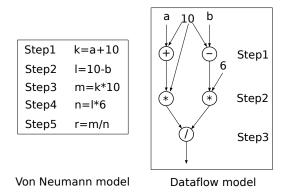

The name dataflow comes from the conceptual notion that a program in a dataflow computer is a directed graph and that data "flows" between instructions, along its arcs [38]. A program written in dataflow programming language is compiled to a dataflow graph – the "machine language" of dataflow computers [39]. There is no notion of a single point or locus of control - nothing corresponding to the program counter. The nodes of the graph are operators or "instructions". The arrows between the nodes represent data dependencies. Data flows as tokens along the arcs. Incoming arrows that flow toward a node are input to that node and outgoing arrows are output from that node. Whenever a node has all the required data on input, the node is fireable. As a result, it removes the data tokens from input, performs its operation, and places new data tokens on output. It then waits to become fireable again. By this method, nodes are executed as soon as input data becomes available. This stands in contrast to the von Neumann execution model, in which an instruction is only executed when the program counter reaches it, regardless of whether or not it can be executed earlier than this. This model exploits parallelism by executing nodes in a pipeline fashion. A node starts execution as soon as the data is available at the input(s). Fig. 2.12 shows a small program and the corresponding dataflow graph, arrows represent arcs and circles represent instruction nodes. Under the von Neumann execution model, this program would execute sequentially in five steps. In the first step, a and 10 are added and result is stored in k. In second step, b is subtracted from 10 and result is stored in 1. The third step will multiply k with 9 and store result in m. Similarly, the fourth step will multiply 1 with 6 and store result in n. The last step will divide m by n and result is stored in r. The same program is executed in three steps under the dataflow execution model. The first step performs the addition and subtraction operations simultaneously, as soon as data is available for their execution. Similarly, both multiplication operations are performed in the second step. Finally, in the third step the division operation is performed.

Figure 2.12: Von Neumann vs dataflow execution model

In the Dataflow model, nodes represent units of computation and edges represent FIFO communication channels. By changing the regularity and determinism of the communication pattern, as well as the amount of buffering allowed on the channels, different variants of the dataflow model can be developed. One of the most widely used is Synchronous Dataflow (SDF) [40]. In this model, the numbers of data items produced and consumed by one node at each execution is constant and known at compile time. So, the amount of buffering needed can be determined statically. Many variations of SDF have been defined, including cyclo-static dataflow [41, 42] and multi dimensional synchronous dataflow [43].

Though it was defined before the advent of reconfigurable architectures, the Dataflow MoC appears to be well suited for writing applications targeting FPGAs. In particular, it exploits the inherent concurrency in the algorithm without requiring the programmer to make it explicit. Moreover, the DFG representation of an application is in close resemblance with many image and signal processing algorithms which are represented graphically using block diagrams. This makes dataflow model a natural choice for these applications targeting FPGAs. In [44], authors emphasize the importance of stream architectures and dataflow design techniques to address concurrent design as compared to conventional general purpose languages. These languages are not well suited for representing parallel architectures. One possible solution is to add concurrent constructs but this is not natural and effects readability and programmer productivity. On the other hand, relying completely on the compiler to extract parallelism is not possible in the current state of the art. This advocates for a shift towards the dataflow model. In fact, the recent renewed interest in stream or dataflow programming can be viewed as a consequence of the development of reconfigurable computing (RC)/FPGAs, since this model provides a natural way to program these devices. There are several new languages and the area currently attracts considerable attention from academia and industry. Some of the languages will be introduced in section 2.3.3.

### 2.3.2 Dataflow Programming Languages

Several programming languages have been designed based on the dataflow programming model. Many of them rely on the concept of *single assignment* variables, i.e. variables which can only be assigned once. This concept avoids the Von Neumann model memory problems and a program is better suited for translation to DFGs.

Some of the popular early dataflow programming languages are:

- Textual Dataflow Language (TDFL) [35], developed in 1975, is considered to be the first dataflow language. A program in TDFL consist of series of modules (called procedures in some languages). Each module then consists of statements that can be assignments, conditional statements or calls to another module. Iterations are not directly supported but modules can call themselves iteratively.

- LAU [45] was developed in 1976 for the LAU static dataflow architecture by the computer structure group of Onera-Cert in France. It was a single assignment language. It provided explicit parallelism through the *expand* keyword.

- Lucid [46], the best known of all dataflow languages, was not originally developed as a dataflow language, but as a functional language to enable formal proofs. The objective was to write real-life program in a purely declarative style to enable verification. But later Lucid's functional and single assignment semantics established it to be a dataflow language [47].

- Id [48] was developed to write operating systems but without sequential controls and memory cells. Thus the language had single assignment and was block structured and expression based.

- There are several 'Manchester Languages' including DCBL [49], SISAL [50] and LAPSE [51] developed for the Manchester dataflow machine [52].

#### 2.3.3 Dataflow Programming Languages for FPGAs

In this section, we will discuss some of the dataflow programming languages closely related to our work, namely include CAL, Canals, StreamIT and FPGA Brook. The CAPH language, which also belongs to this category, and on which our work is based, will be described separately in chapter 3.

#### 2.3.3.1 CAL (Caltrop Actor Language)

CAL [53, 54], a dataflow/actor-oriented language is based on the Actor model of computation [55] for dataflow systems. The basic concepts of CAL have a natural resemblance to these systems. A dataflow model is described in CAL by a set of independent actors and their connections (called a network of actors).

An actor has a set of input and outputs which are used to communicate with other actors by exchanging data tokens. State variables are used to keep track of the internal state of an actor. The behavior of an actor is described using a set of actions. There must be at least one action in an actor. In the case of more than one action, CAL provides scheduling concepts to control the execution order of actions. The execution of an action depends on its internal state and the values available at input. During execution, an action can do all or any one of the following: change the state variable(s), read values from input and write values at output. It is also important to note that action execution is an atomic operation. At a time, only one action will be in execution.

A simple example of a CAL increment actor is given in listing 2.1, it has one input port t and one output port s, all of type integer [56]. This actor contains one action that consumes

one token from input port, and produces one token on the output port. This action will execute when data token is available at input port.

Listing 2.1: A Simple increment actor in CAL

```

actor Inc() integer t \Rightarrow integer s: action [a] \Rightarrow [inc] do inc := a + 1; end end

```

In the above example, it is also possible to use a type variable T to create generic a type actor. The advantage is to declare actors with different types from one generic actor instead of writing a separate actor for each type.

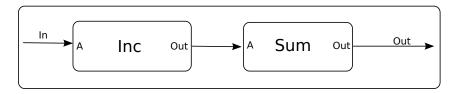

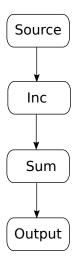

In order to implement an application, CAL actors are connected to each other to form a network of actors. This is done by connecting the input and output ports of actors with each other. The connections are made with the help of FIFOs. CAL does not provide any explicit scheduling between actors, which means that the resulting system is entirely self-scheduling based on the actual flow of tokens. The declaration of a network of actors consisting of two actors, inc and sum, as shown in Fig. 2.13 is given in listing 2.2.

Figure 2.13: CAL dataflow network

Listing 2.2: CAL network declaration

```

network Sum () In => Out:

entities

inc = Inc();

sum = Sum();

structure

In --> inc.A;

inc.Out --> sum.A;

sum.Out --> Out;

end

```

CAL takes care of low level communication details (e.g. message passing protocols) which helps designers to focus on actors and their connection to form a network. However, designers are provided control over connection communication parameters like length of FIFOs and the type of data exchanged.

When generating hardware implementations from networks of CAL actors, each actor is translated separately, and the resulting RTL descriptions are connected using FIFOs. Actors interact with FIFOs using a handshake protocol, which allows them to sense when a token is available or when a FIFO is full.

CAL has been selected by ISO/IEC for the definition of new MPEG standard called Reconfigurable Video Coding (RVC) [57]. All tools related to CAL are available under Orcc (Open RVC-CAL Compiler) [58] which is an update of the previous set of tools available under the Open Dataflow environment (OpenDF for short) [56]. It contains back ends for the generation of HDL [59], C [60] and Java [61]. MPEG Reconfigurable Video Coding framework has been implemented using CAL [62, 63]. CAL has many similarities with the CAPH language used in this thesis. Some elements of comparison are given in section 6.4.

#### 2.3.3.2 Canals

Canals [64, 65], another dataflow language is based on *nodes* and *links*. The former consists of kernels and networks and latter is channel used to connected the nodes. Kernels are the basic computing unit of the Canals language. A kernel performs computation on input data and results are written on output. A kernel consist of three sections: an obligatory work block, a section for variable declarations and a section to initialize specific operations. Actual computations are performed inside a work block by using the *Canals Kernel Language*. This is a sequential language having syntax similar to many programming languages. All variables declared inside a kernel are local and cannot be accessed from outside. The values of these variables are changed during the execution of a kernel.

A new kernel is defined by using keyword kernel along with unique name and data types of input and output. The number of inputs read and the number of outputs written during the execution of kernel are specified by get and put keywords in the header of the work block. For example, work get 1 put 1 in the header means that during the execution the kernel will read one value from input and write one value at the output. The code for a simple kernel declaration in Canals named inc, with input data type dt1 and output data type dt2 and consuming one element from input and producing one element at output during execution, is given in listing 2.3.

Listing 2.3: A Simple increment kernel declaration in Canals

```

kernel dt1 -> dt2 inc

{

variable dt1 myIn;

variable dt2 myOut;

work get 1 put 1 {

myIn = get();

myOut = myIn + 1 ;

put(myOut);

}

}

```

The data types dt1 and dt2 are specified using the keyword datadef.

Channels are memory buffers used to store data between connected kernels. A channel is specified using the channel keyword along with a name and a data type. The capacity of the channel is described in the body. Canals also provides one pre-defined channel type called a generic-channel. It is an unbounded FIFO queue for any defined data type. Furthermore, in order to distribute and collect data, channels support scatter and gather operations. The former is used to distribute data from one input channel to many output channels and the latter is used to collect data from many channels.

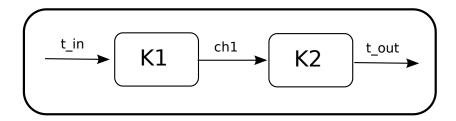

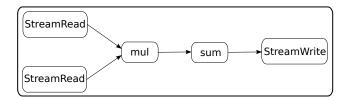

In order to form a working application, a network is defined using the network keyword. A network is defined by giving it a name and data types of input and output. Elements are added to a network by using the statements add-network, add-channel, add-kernel, add-scatter and add-gather. After adding these elements, they are connected by connect statements. The connect statements must form at least one valid data flow path between an incoming data port and an outgoing data port which are donated by NETWORK-IN and NETWORK-OUT respectively. Other networks can also be added into a network. Although there can be many networks, there is always one top-level network defined as network void -> void. This top-level network acts as starting point for Canals program. An example of a network shown in Fig. 2.14 is defined in Canals as given in listing 2.4.

Figure 2.14: Canals dataflow network

Listing 2.4: Network declaration in Canals

```

network t_in -> t_out N

{

add_channel ch1 < generic_channel >;

add_kernel K1 < inc >;

add_kernel K2 < sum >;

connect NETWORK_IN -> K1 -> ch1 -> K2 -> NETWORK_OUT;

}

```

The Canals compiler first generates a behavioral model, a mapping model and an architecture model from the input code. All three are then combined to form an implementation model which is platform independent. This model is used by different backends to generate code with the help of Hardware Abstraction Layer (HAL) which contains the communication mechanism for the target architecture.

The MPEG Reconfigurable Video Coding framework has been implemented in Canals [64]. In [65], the JPEG encoder was implemented on an Altera FPGA using the Canals back end for FPGA.

#### 2.3.3.3 StreamIT

StreamIT [66, 67] is an architecture-independent programming language for implementing high-performance streaming applications, by introducing stream-specific abstractions. This basic computational unit is called a filter. To build an application filters are connected through streams. StreamIt is based on the synchronous data flow (SDF) MoC but differs from this model by introducing multiple execution steps for filters, an option for declaring the

input/output rate of filter to be dynamic, teleport messaging<sup>2</sup>, peeking (i.e. reading elements from input queue without deleting) and allowing filters to input and output a number of elements during initialization.

A filter consists of a single input channel and single output channel. Each filter is completely independent of the others and all communications between filters take place through input and output channels. It consists of two stages of execution: initialization and steady state. During initialization, the parameters to a filter are resolved to constants and the init function is called. During steady state execution, the work function is called repeatedly. It is also possible to write a prework function which is called once between init and work [68]. The work function repeatedly executes as soon as sufficient data is available on its input FIFO (queue). It reads data from its input queues using pop operations, writes data to its output queue using push operations and can also inspect inputs without removing them from the FIFO using a peek operation. The number of elements to push, pop or peek is declared in the declaration section of the work function. The example of an increment filter in StreamIT is given in listing 2.5.

Listing 2.5: A simple increment filter in StreamIT

```

int->int filter inc () {

int result;

init {

result = 0;

}

}

work push 1 pop 1 {

result = pop()+1;

push(result);

}

}

```

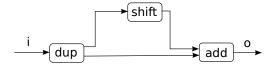

In StreamIT an application is build by connecting filters into stream graphs. To accomplish this, three hierarchical stream primitives are provided: pipeline, splitjoin, and feedbackloop [69]. The pipeline structure creates a serial composition of streams by connecting inputs and outputs of filters to each others. A splitjoin specifies parallel streams that diverge from a common splitter and merge into a common joiner<sup>3</sup>. And a feedbackloop structure creates a cycle in the stream graph. The add keyword is used to instantiate and add a new filter to current stream graph. A simple stream graph as shown in Fig. 2.15, consisting of four filters in a pipeline can be written as in listing 2.6:

$<sup>^2\</sup>mathrm{To}$  send a message from a filter's work function to change a parameter in another filter

<sup>&</sup>lt;sup>3</sup>It is implemented with the help of data reordering primitives e.g.duplicate,roundrobin

Figure 2.15: StreamIT dataflow network

Listing 2.6: Network declaration in StreamIT

```

int -> int pipeline Main() {

add Source();

add inc();

add sum();

add Output();

}

```

StreamIt was originally designed for the RAW<sup>4</sup> (Reconfigurable Architecture Workstation) machine [70], but more recently it has been used to introduce Optimus, an optimizing synthesis compiler for streaming applications on FPGAs [69]. It generates efficient Verilog HDL by performing many optimizations. These optimizations include Queue Allocation, Queue Access Fusion and Flip-Flop Elimination which effect space (area) and time (throughput) of the generated circuit. The first optimization reduces the size of the FIFO queues, the second fuses multiple queue operations into a single wider one and last identifies and eliminates redundant registers. The filters are synthesized using hardware templates and all templates are connected using FIFOs. The set of experiments implemented using this Optimus compiler includes: FFT (Fast Fourier Transform), parallel adder, bubble sort, merge sort, inverse DCT (Discrete Cosine Transform), DES (Data Encryption Standard) and matrix multiply [69].

#### 2.3.3.4 FPGA Brook

FPGA Brook is a streaming programming language based on the programming languages Brook [71] and GPU brook [72]. The former is used to target multiprocessors [73] and the latter is a variant specifically designed for GPUs [74]. In [75], Brook is used to target applications on FPGAs by using the open source GPU brook compiler [72]. This version, called FPGA Brook, extends the Brook syntax to include streams and kernels. Computations are performed by kernels on input streams. Streams are collections of the data same as arrays but the elements are mutually independent. Streams are declared using characters < and > instead of square brackets. A kernel can exploit data-level parallelism by operating on individual stream

<sup>&</sup>lt;sup>4</sup>A tiled multicore architecture

elements as all are independent of each other. Data-level parallelism can also be achieved by instantiating different instances of a kernel, each working on a part of the input stream. This is called kernel replication and is implemented using the speedup pragma statement. A special reduction kernel uses several elements of the input stream to produce one element of the output stream. There are also many stream operators for transforming input streams. For example, the StreamReapeat operator creates an output stream by repeating elements of the input stream. A stencil operator selects several elements of the input stream to create the output stream. StreamRead and StreamWrite operators are used to read (resp. write) input (resp. output) to/from memory. Although, Brook is based on the C programming language, it limits the usage of many features of the C language to make it easier for the compiler to analyze programs and extract parallelism [76]. The example of a simple increment filter in FPGA Brook is given in listing 2.7. The network depicted in Fig. 2.16 can be defined in FPGA Brook as given in listing 2.8.

Figure 2.16: FPGA Brook dataflow network

Listing 2.7: A Simple increment kernel in FPGA brook

```

kernel void inc (int a<>, int c<>)

{

c = a+1;

}

```

Listing 2.8: Network declaration in FPGA brook

```

void main ()

{

int Astr < 1,N >, Tstr < 1,N >, ystr < 1,N >;

int A[1][N], R[1][N];

streamRead (Astr, A);

inc (Astr, Istr);

sum (Istr, Rstr);

streamWrite (Rstr, R);

}

}

```

FPGA Brook does not directly generate HDL code for FPGA implementation. Instead the design flow consist of two steps. In the first step, the program written in FPGA Brook is converted to C code using C2H directives. C2H [77] is Altera's high level synthesis tool which converts C-like code to HDL. The first step converts kernels to C2H functions to be implemented as hardware accelerators and also generates SOPC system description. In the second step, Verilog HDL is generated from this code using C2H. The Verilog code is then synthesized into FPGA logic by the Quartus II CAD tool [78] to produce the FPGA programming file, which can then be used to program the FPGA device.

Applications implemented in FPGA Brook include FIR Filter, Two-Dimensional Convolution, Zigzag Ordering in MPEG-2, Inverse Quantization in MPEG-2, Saturation in MPEG-2 and Mismatch Control in MPEG-2 [76].

#### 2.3.4 Conclusion

Table 2.1 summarizes the difference between the languages described in the previous section. Two of the languages (Canals and FPGA Brook) can only generate HDL code for a specific target, so they cannot be called "generic" programming languages for FPGAs. Out of the other two languages, CAL code has to undergo some changes to be executed on Altera FPGA. Furthermore, all these languages rely on some textual language or graphical tool to describe networks which is often a complicated task for big applications.

CAPH is introduced in the next chapter with the objective to overcome these limitations. The following characteristics of CAPH differentiate it from other related languages described in the previous section.

CAPH generates efficient VHDL code as compared to other languages (results of the comparison with one language (CAL) will be presented in chapter 6). But this efficiency comes at the cost of expressivity at the language level. The CAPH languages offers less features compared to CAL. So this efficiency is the result of a trade off with expressivity.

CAPH is based on formal semantics, which describes by a mathematical model all the possible computations performed by the language. The advantages of using this approach for CAPH are two fold. First, the transformation from high-level CAPH code to hardware-level VHDL code is described formally. It helps generate accurate VHDL code based on mathematical modeling of formal semantics. Second, the reference interpreter of the language is developed in a systematic way which is used to evaluate the accuracy of results generated by backend code.

In CAPH, it is possible to describe arbitrarily complex data structures as well as actor descriptions operating on these values. This means it can describe and operate on non-regular and/or variable-size data structure. The objective is to target a large domain of applications instead of restricting them to signal or image processing. This is achieved by separating the tokens into two categories: *data tokens*(having actual values) and *control tokens*(used as structuring delimiters).

The CAPH network sub-language is a small functional language which makes it easier to describe complex dataflow graphs using a set of functional equations. It offers a better way to describe application as compared to explicitly describing actor connections, even with the help of graphical interface. This will be further illustrated with the help of complex examples in next chapter.

|                 | CAL              | Canals            | StreamIt             | FPGA Brook        | CAPH          |

|-----------------|------------------|-------------------|----------------------|-------------------|---------------|

| Computing Unit  | Actor            | Kernel            | Filter               | Kernel            | Actor         |

| Dataflow MoC    | Dynamic Dataflow | Synchronous       | Synchronous Dataflow | Static Dataflow   | Dynamic       |

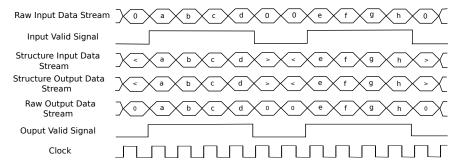

|                 |                  | Dataflow          |                      |                   | Dataflow      |