# Nouvelles méthodes pseudo-MOSFET pour la caractérisation des substrats SOI avancés

Amer El Hajj El Hajj Diab Diab

#### ▶ To cite this version:

Amer El Hajj El Hajj Diab Diab. Nouvelles méthodes pseudo-MOSFET pour la caractérisation des substrats SOI avancés. Autre. Université de Grenoble, 2012. Français. NNT: 2012GRENT060. tel-00796613

### HAL Id: tel-00796613 https://theses.hal.science/tel-00796613

Submitted on 4 Mar 2013  $\,$

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

## UNIVERSITÉ DE GRENOBLE

### THÈSE

Pour obtenir le grade de

### DOCTEUR DE L'UNIVERSITÉ DE GRENOBLE

Spécialité : NANO ELECTRONIQUE ET NANO TECHNOLOGIES (NENT)

Arrêté ministériel : 7 août 2006

Présentée par

### Amer EL HAJJ DIAB

Thèse dirigée par **Sorin CRISTOLOVEANU** et codirigée par **Irina IONICA**

préparée au sein du Laboratoire IMEP-LAHC dans l'École Doctorale EEATS

## Nouvelles méthodes pseudo-MOSFET pour la caractérisation des substrats SOI avancés

(Novel pseudo-MOSFET methods for the characterization of advanced SOI substrates)

Thèse soutenue publiquement le **10 Décembre 2012**, devant le jury composé de :

M. Olivier BONNAUD

Professeur, Université de Rennes (Président, Rapporteur)

Mme. Daniela MUNTEANU

Directrice de Recherche CNRS, IM2NP Marseille (Rapporteur)

M. Francisco GÁMIZ PÉREZ

Professeur, Université de Granada (Membre)

M. Daniel DELPRAT

Manager advanced R&D, Soitec (Membre)

M. Sorin CRISTOLOVEANU

Directeur de Recherche CNRS, IMEP-LAHC (Directeur de thèse)

Mme. Irina IONICA

Maître de conférences, IMEP-LAHC/INPG (Co-encadrante de thèse)

To my parents, brother, sister and my secret love

### TABLE OF CONTENTS

| ACKNOWLEDGEMENTS                                                                              | 5        |

|-----------------------------------------------------------------------------------------------|----------|

| LIST OF ACRONYMS                                                                              | 7        |

| LIST OF SYMBOLS                                                                               |          |

| LIST OF CONSTANTS                                                                             | 10       |

| GENERAL INTRODUCTION                                                                          | 11       |

| CHAPTER I: INTRODUCTION TO SOI MATERIALS AND DEVICES                                          | 13       |

| INTRODUCTION                                                                                  | 14       |

| 1. SOI DEVICES                                                                                | 15       |

| 1.1 SOI technology: an answer to scaling and diversity in Moore's law                         | 15       |

| 1.2 Advantages of the SOI technology                                                          |          |

| 1.3 SOI MOSFETs                                                                               |          |

| 1.3.1 Partially depleted transistors: PD MOSFETs                                              | 20       |

| 1.3.2 Fully depleted transistors: FD MOSFETs                                                  |          |

| 1.4 Innovative SOI transistors                                                                |          |

| 1.4.1 Multi-gate transistors                                                                  |          |

| 1.4.1.1 Double-gate (DG) transistors                                                          |          |

| 1.4.1.2 Triple-gate transistors                                                               | =4       |

| 1.4.1.3 Four-gate (G4-FET) transistors                                                        | 25       |

| 1.4.2 Gate-All-Around (GAA) transistors                                                       |          |

| 1.4.3   Tri-dimensional nanowires (3D NWs)                                                    |          |

| 2. SOI MATERIALS                                                                              |          |

| 2.1 State-of-the-art                                                                          |          |

| 2.2 Fabrication methods                                                                       |          |

| 2.2.1 SIMOX technology                                                                        |          |

| 2.2.2 SOI by wafer bonding                                                                    |          |

| 2.2.2.1 BESOI                                                                                 |          |

| 2.2.2.2 ELTRAN                                                                                |          |

| 2.2.2.3 Unibond (Smart-Cut <sup>™</sup> process)                                              |          |

| 2.2.3 Silicon-On-Nothing (SON)                                                                | ວວ<br>າ6 |

| 2.2.3 Shicon-On-Nothing (SON)                                                                 | 30<br>   |

|                                                                                               |          |

| 2.2.4.1       Silicon-On-Sapphire         2.2.4.2       Insulation by Porous Oxidized Silicon |          |

| 2.2.4.3 Zone Melting Recrystallization and Epitaxial Layer Overgrowth                         |          |

|                                                                                               |          |

| 2.3 Novel semiconductor on insulator structures                                               |          |

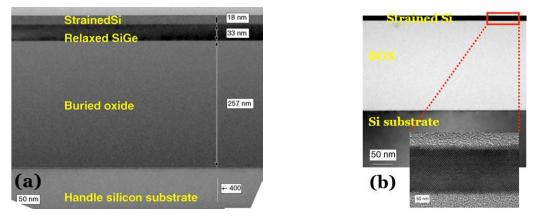

| 2.3.1 Strained SOI materials                                                                  |          |

| 2.3.2 Hybrid orientation technologies                                                         |          |

| 2.3.3 Germanium-On-Insulator                                                                  | 40       |

| 2.3.4 Other semiconductor, BOX and substrate materials                                        |          |

| 2.3.4.1 Conductive film materials                                                             | 41       |

| 2.3.4.2 BOX and substrate materials                                                           |          |

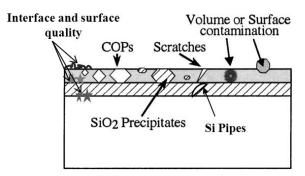

| 2.4 Defects of SOI material                                                                   |          |

| CONCLUSION                                                                                    | 43       |

| REFERENCES CHAPTER I                                                                          | 44       |

|                                                                                               | • • •    |

| CHAPTER II: ELECTRICAL CHARACTERIZATION OF SOI SUBSTRATES | 47       |

|-----------------------------------------------------------|----------|

| INTRODUCTION                                              | 48       |

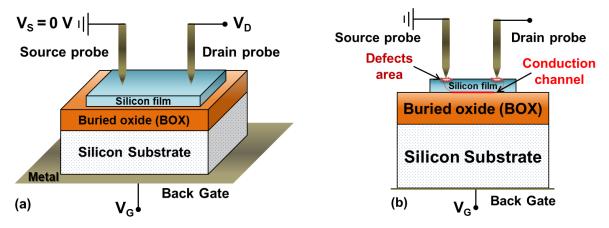

| 1. PSEUDO-MOSFET PRINCIPLE AND OPERATION                  | 49       |

| 1.1 Overview                                              | 40       |

| 1.2 Point-contact Ψ-MOSFET technique                      |          |

| 1.2.1 Sample preparation                                  | 52       |

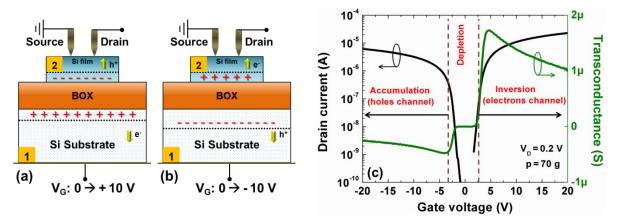

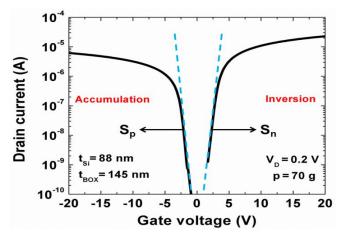

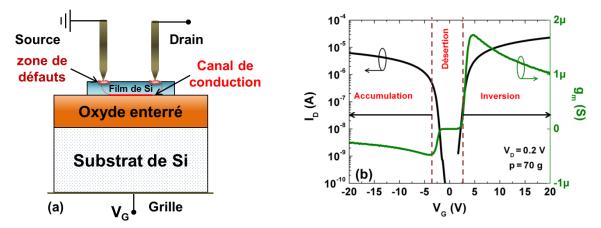

| 1.2.2 Typical $I_D-V_G$ in $\Psi$ -MOSFET configuration   | 52       |

| 1.2.3 Substrate effect                                    | 55       |

| 1.2.4 Influence of probe pressure                         | 50<br>56 |

| 1.3 Extraction methods of the electrical parameters       | 57       |

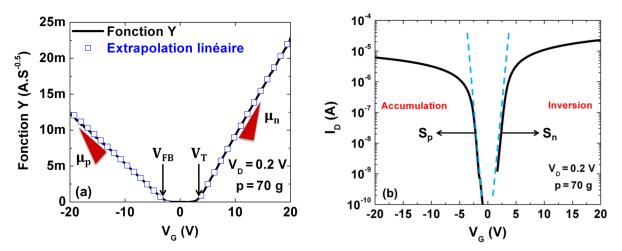

| 1.3.1 Threshold voltage and flat-band voltage             |          |

| 1.3.2 Carrier mobility                                    | 60       |

| 1.3.3 Mobility reduction factor and series resistance     | 62       |

| 1.3.4 Subthreshold swing and interface traps density      | 62       |

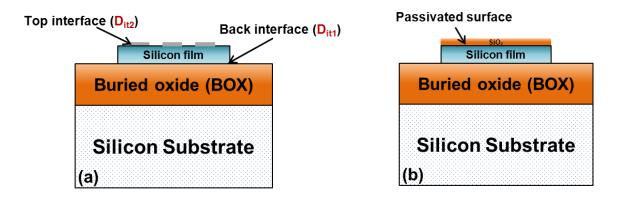

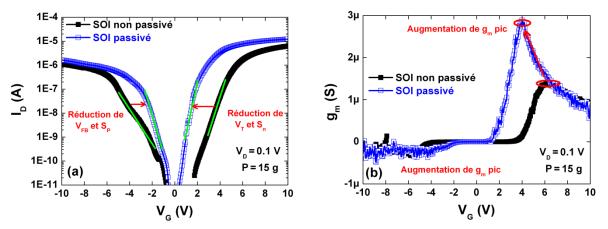

| 1.4 Impact of the top interface in thin SOI films         |          |

| 1.5 Revisited Ψ-MOSFET models                             | 67       |

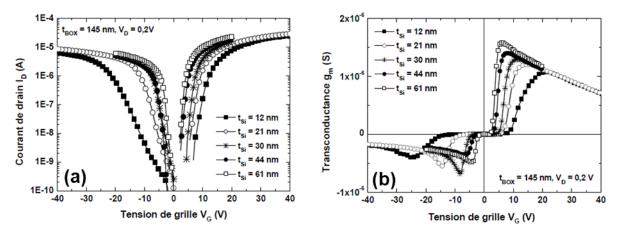

| 2. CHARACTERIZATION OF ULTRA AND EXTRA THIN SOI WAFERS    | 69       |

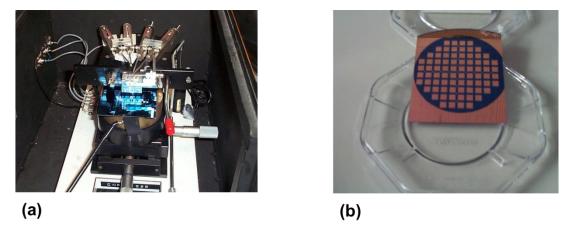

| 2.1 Experimental conditions                               |          |

| 2.1.1 Sample preparation                                  |          |

| 2.1.2 Measurement system                                  |          |

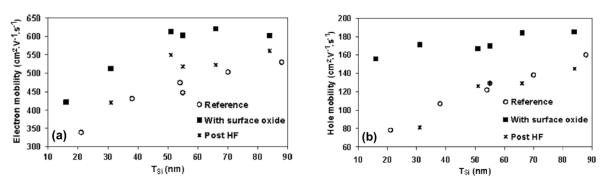

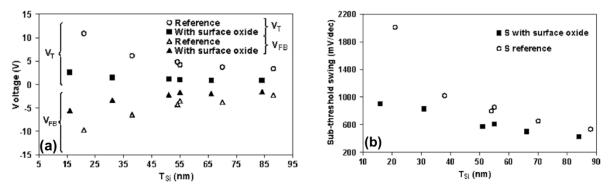

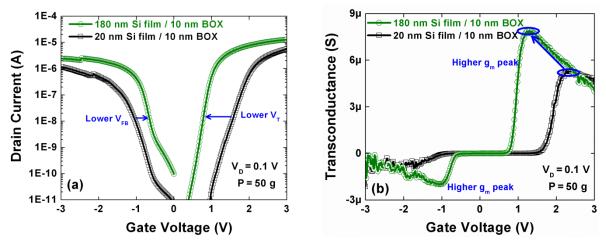

| 2.2 Results obtained on UT/ET SOI                         | 71       |

| 3. LOW-TEMPERATURE Ψ-MOSFET MEASUREMENTS                  | 74       |

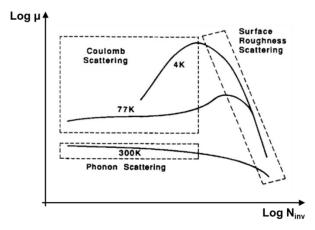

| 3.1 Interest of low-temperature measurements              | 74       |

| 3.2 Experimental set-up                                   |          |

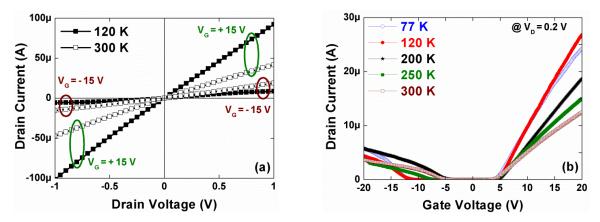

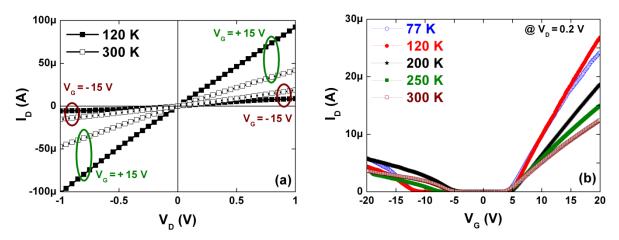

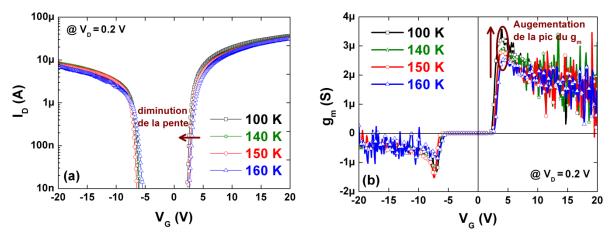

| 3.3 Drain current variation with temperature              | 75       |

| 3.4 Extracted parameters                                  |          |

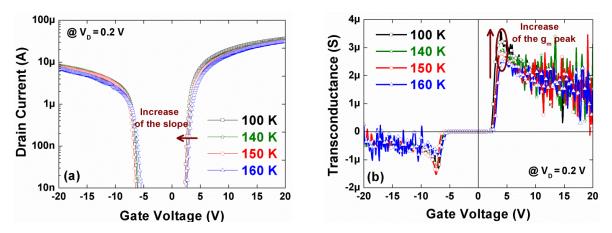

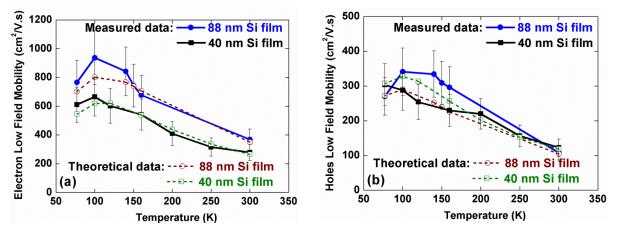

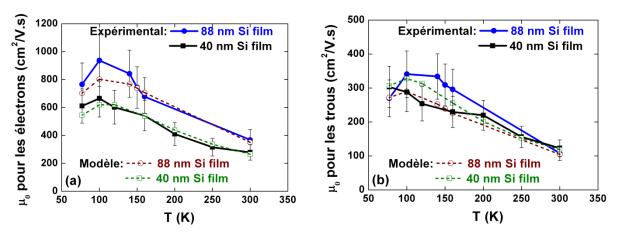

| 3.4.1 Carrier mobility                                    |          |

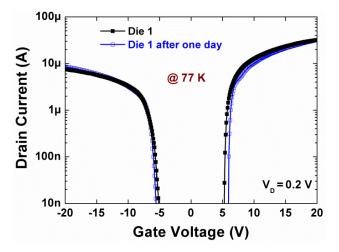

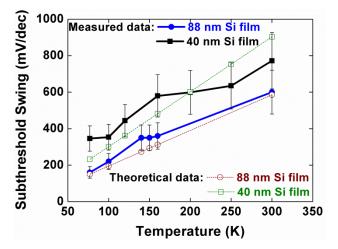

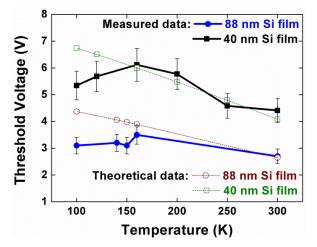

| 3.4.2 Subthreshold swing and threshold voltage            | 82       |

| CONCLUSION                                                | 86       |

| REFERENCES CHAPTER II                                     | 87       |

| CHAPTER III: NOVEL DEVELOPMENTS OF Ψ-MOSFET METHOD        | 89       |

| INTRODUCTION                                              | 90       |

| 1. LOW-FREQUENCY NOISE MEASUREMENTS ON BARE SOI WAFERS    | 91       |

| 1.1 Why noise measurements?                               | 91       |

| 1.2 Overview of the electronic noise                      | 91       |

| 1.2.1 Fundamentals of noise                               | 92       |

| 1.2.2 Different sources of noise in MOS transistor        | 93       |

| 1.2.2.1 White noise                                       | 93       |

| 1.2.2.2 Excess noise                                      |          |

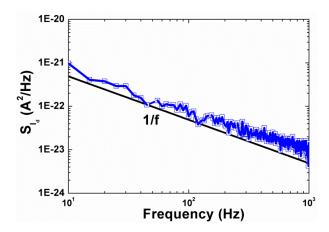

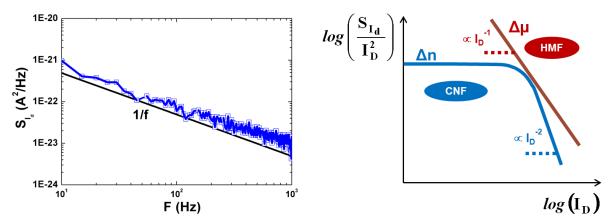

| 1.3 LFN on SOI wafers                                     |          |

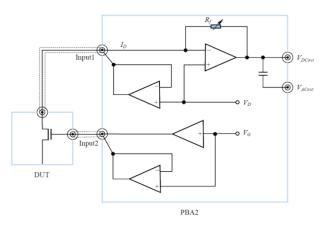

| 1.3.1 LFN in Ψ-MOSFET: experimental set-up                |          |

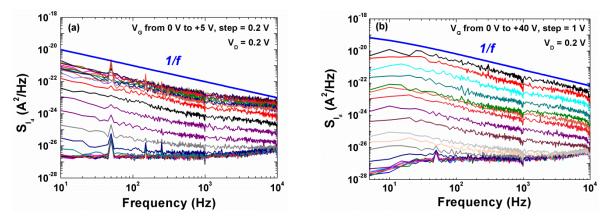

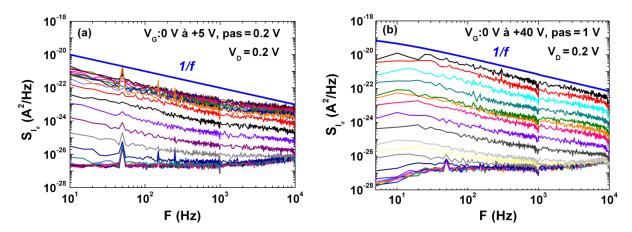

| 1.3.2 Experimental results                                |          |

| 1.3.2.1 <i>1/f</i> noise behavior                         |          |

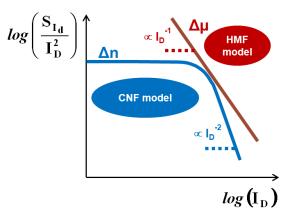

| 1.3.2.2 Noise model: CNF or HMF?                          |          |

| 1.3.2.3 Probe pressure impact on LFN                      | 103      |

| 1.3.2.4 D <sub>it</sub> extraction                        | 104      |

| 1.3.2.5 Impact of the surface preparation on LFN          | 105      |

| 1.3.2.6 Feasibility of LFN on extra-thin SOI structures                        | 107 |

|--------------------------------------------------------------------------------|-----|

| 1.4 Conclusion of section 1                                                    |     |

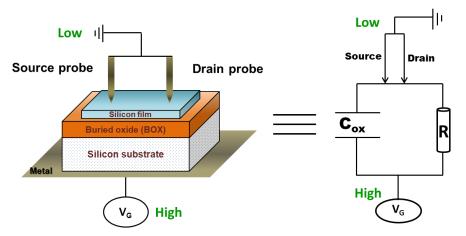

| 2. SPLIT C-V MEASUREMENT IN Ψ-MOSFET CONFIGURATION                             |     |

| 2.1 Split C-V technique and principle                                          | 109 |

| 2.2 Interest of split C-V for SOI wafer characterization                       |     |

| 2.3 Extension of $\Psi$ -MOSFET for split <i>C</i> - <i>V</i> measurements     |     |

| 2.3.1 Method and experiment                                                    |     |

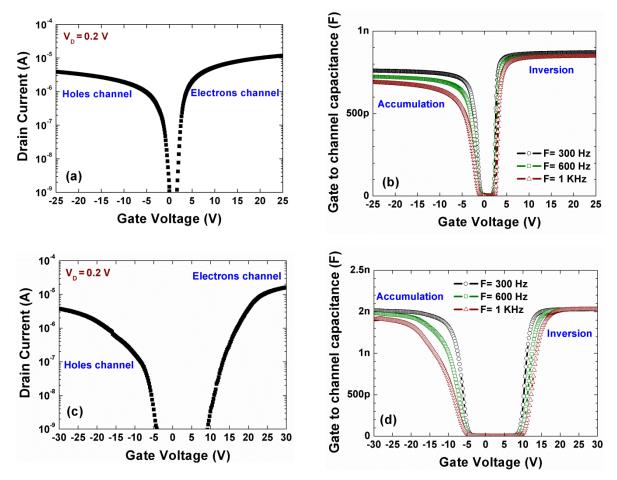

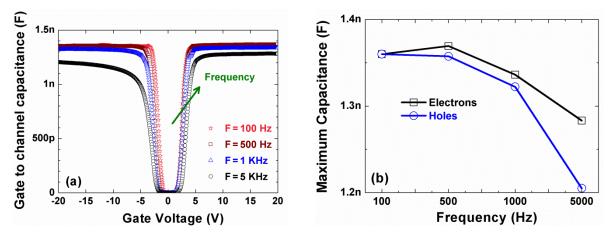

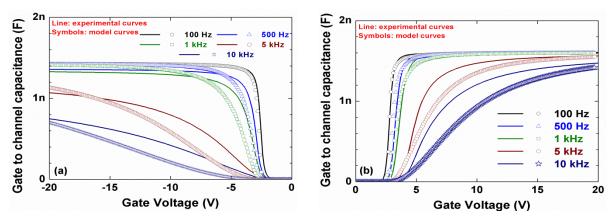

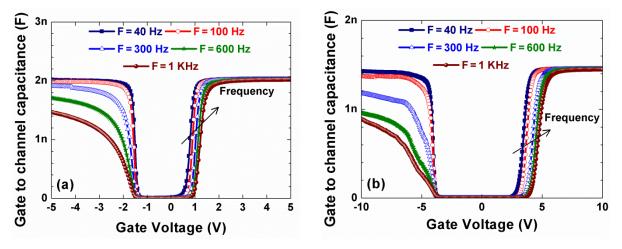

| 2.3.2 Experimental C-V curves                                                  |     |

| 2.4 Impact of experimental conditions on <i>C-V</i> measurements               |     |

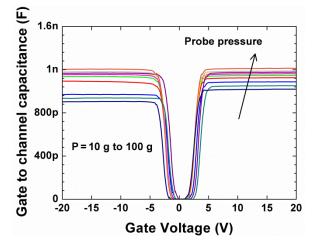

| 2.4.1 Probe pressure impact on <i>C</i> - <i>V</i> curves                      |     |

| 2.4.2 Frequency effects                                                        |     |

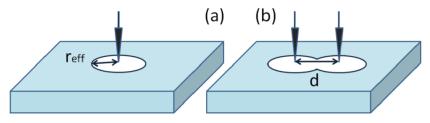

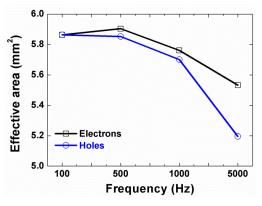

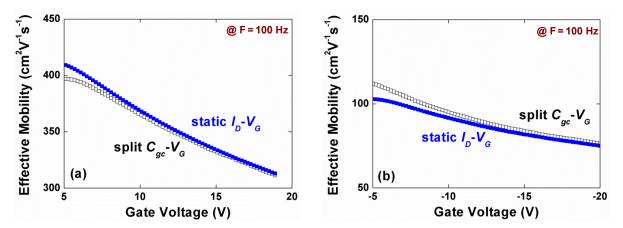

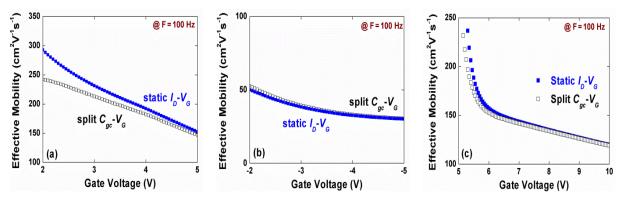

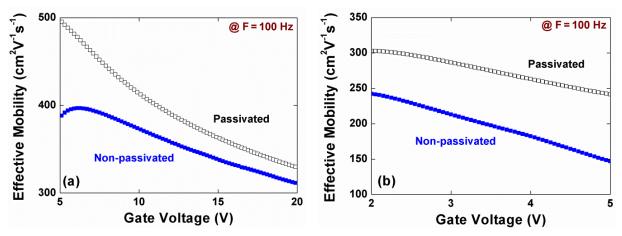

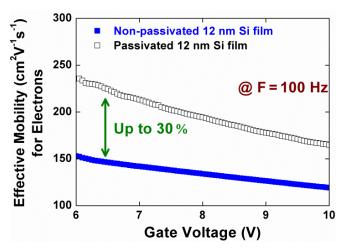

| 2.5 Extraction of $\mu_{\text{eff}}$ by split <i>C-V</i> technique             | 118 |

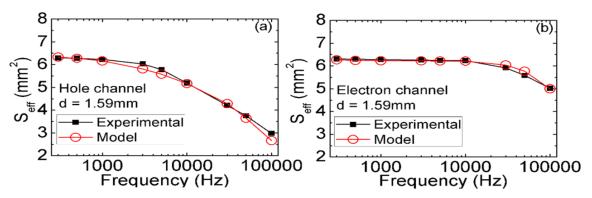

| 2.5.1 Adapted methodology to extract µ <sub>eff</sub>                          |     |

| 2.5.2 Applications of µ <sub>eff</sub> extraction for advanced SOI structures  | 120 |

| 2.6 Conclusion of section 2                                                    | 123 |

| CONCLUSION                                                                     |     |

| REFERENCES CHAPTER III                                                         | 125 |

| CHAPTER IV: INNOVATIVE APPLICATIONS OF PSEUDO-MOSFET                           | 127 |

| INTRODUCTION                                                                   | 128 |

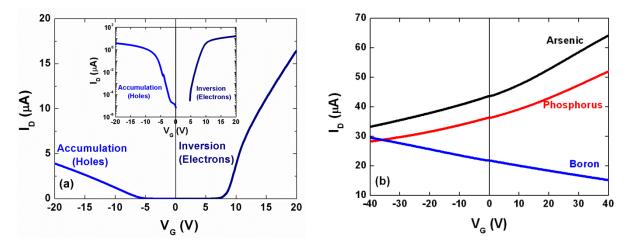

| 1. CHARACTERIZATION OF HEAVILY DOPED SOI WAFERS                                | 129 |

| 1.1 From undoped to doped SOI                                                  | 129 |

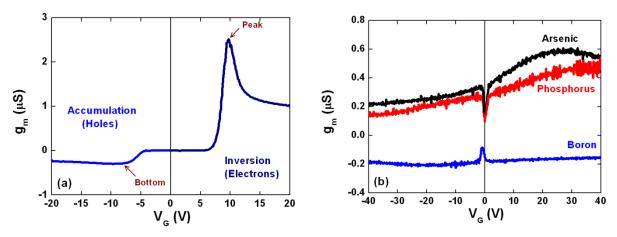

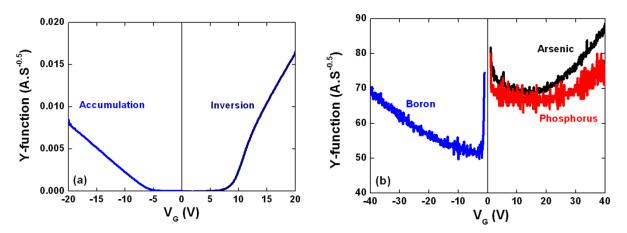

| 1.2 Ψ-MOSFET characterizations                                                 |     |

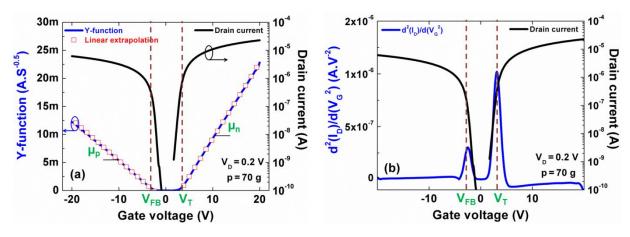

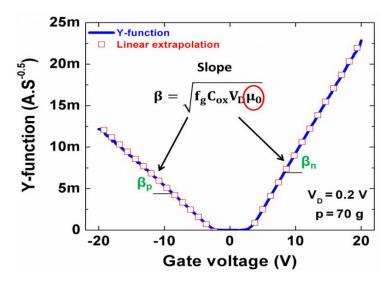

| 1.2.1 Y-function                                                               |     |

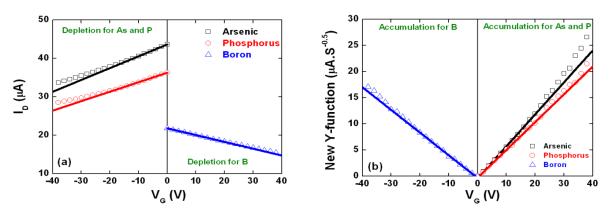

| 1.3 Revised model for parameter extraction in HD SOI                           | 131 |

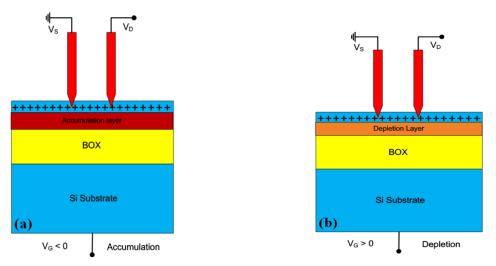

| 1.3.1 Volume conduction                                                        |     |

| 1.3.2 Surface accumulation                                                     | 133 |

| 1.3.3 Extracted parameters                                                     |     |

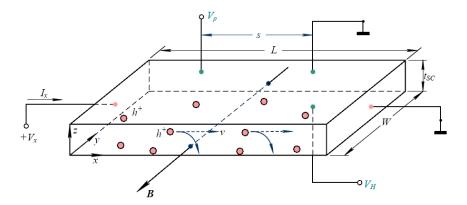

| 1.3.3.1 Van der Pauw and Hall effect                                           |     |

| 1.3.3.2 Comparison of Ψ-MOSFET, Van der Pauw and Hall effect results           | 137 |

| 1.4 Conclusion of section 1                                                    | 138 |

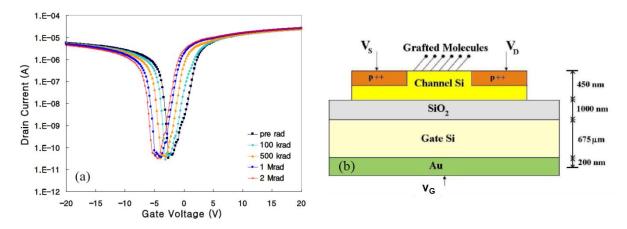

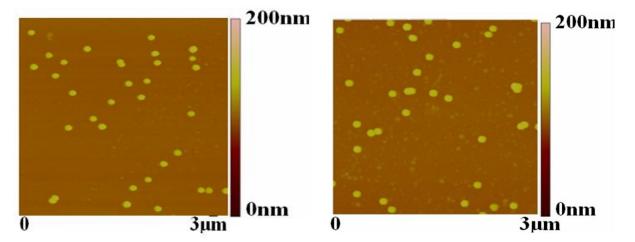

| 2. SOI-BASED SENSOR FOR GOLD NANOPARTICLES DETECTION                           | 140 |

| 2.1 SOI as a detection platform                                                | 140 |

| 2.2 Gold nanoparticles detection by Ψ-MOSFET                                   |     |

| 2.2.1 Fabrication steps of SOI sensors                                         |     |

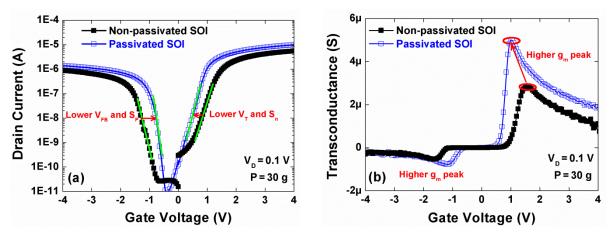

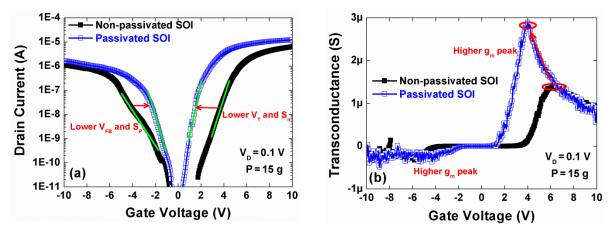

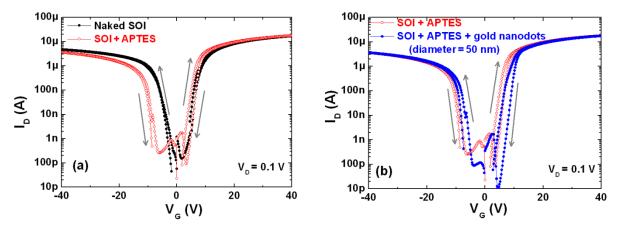

| 2.2.2 Sensor response                                                          |     |

| 2.2.2.1 Reproducibility                                                        |     |

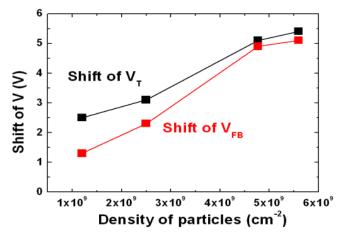

| 2.2.2.2 Impact of particle size and density                                    |     |

| 2.2.2.3 Sensitivity improvement                                                |     |

| 2.3 Conclusion of section 2                                                    |     |

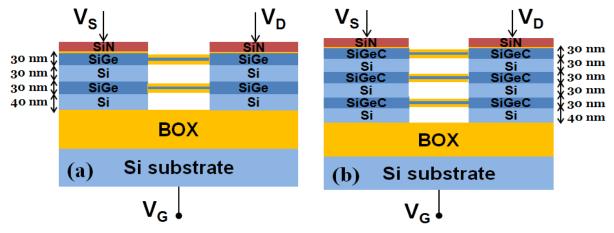

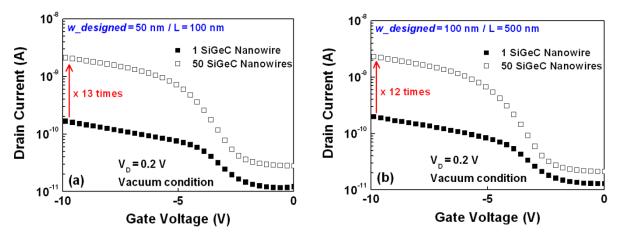

| 3. V-MOSFET CHARACTERIZATION OF 3D VERTICALLY STACKED SIGE AND SIGEC NANOWIRES | 149 |

| 3.1 Overview                                                                   |     |

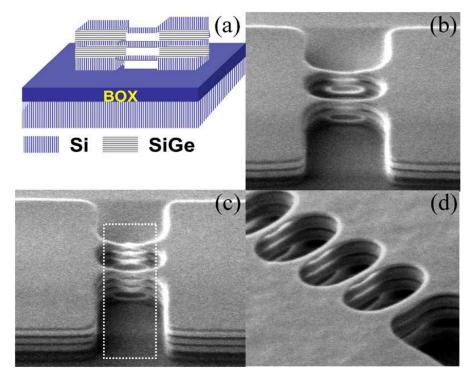

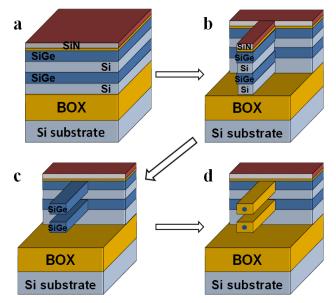

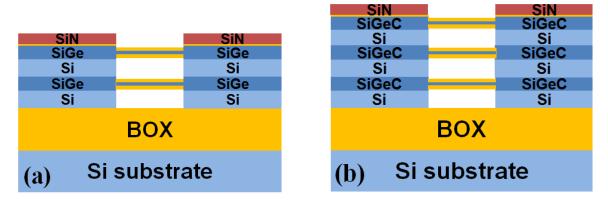

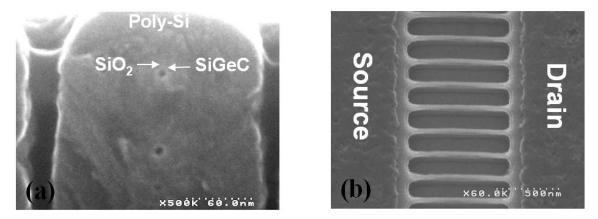

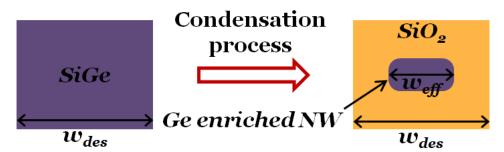

| 3.2 Fabrication process                                                        | 151 |

| 3.3 Electrical transport properties of SiGe NWs                                |     |

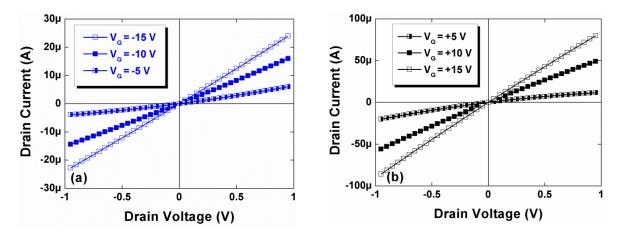

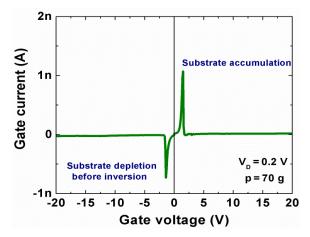

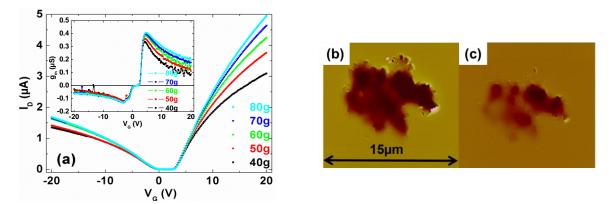

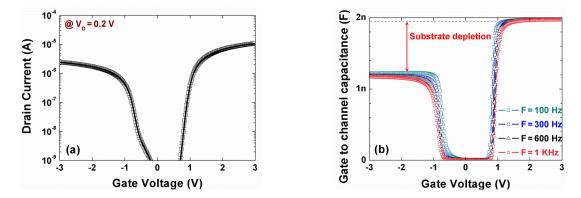

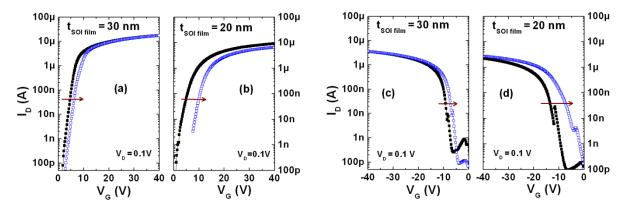

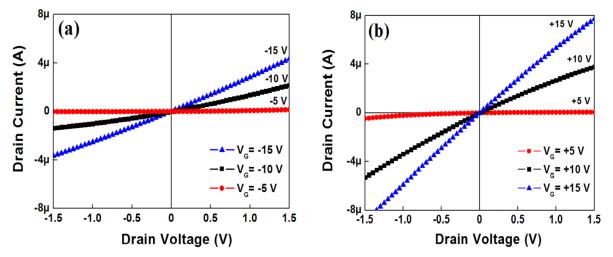

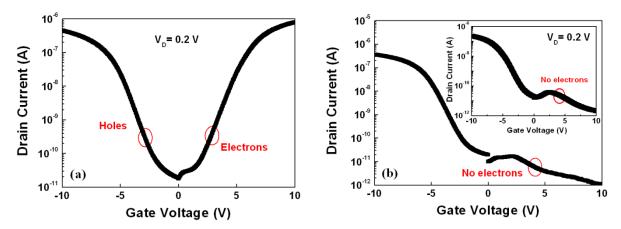

| 3.3.1 Basic characteristics                                                    | 154 |

| 3.3.2 Carrier transport and impact of series resistance                        |     |

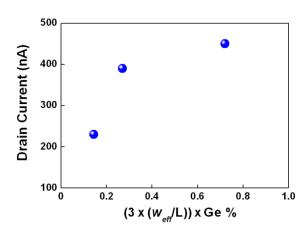

| 3.3.2.1 Hole carrier transport and mobility                                    | 157 |

| 3.3.2.2 Impact of series resistance                                            |     |

| 3.3.3 Low-temperature measurements                                             | 160 |

| 16 |

|----|

| 16 |

| 16 |

| 16 |

| 16 |

| 17 |

| 17 |

| 17 |

| 17 |

| 17 |

| 17 |

| 17 |

| 18 |

| 18 |

| 18 |

| 18 |

| 18 |

| 19 |

| 19 |

| 19 |

|    |

## Acknowledgements

A major research project like this is never the work of a single person. The contributions of many different people, in their different ways, have made this possible. I would like to express my appreciation especially to the following.

First, I would like to particularly express my gratitude and my thanks to my supervisors. Sorin Cristoloveanu and Irina Ionica, my dear thesis supervisors, who had allowed me to develop positively towards independent thinking and led me to adopt my subject, something essential in the world of research. Thank you for having always supported me, encouraged me and corrected my papers/my presentations several times... Sorin, my professor in the "three things", I learned a lot from you not only in SOI but also in project management, conference organization, scientific human relations and many other things.

Irina, I will be always your "jeune padawan", I am deeply grateful for your help in the research, presentation, paper/thesis writing, moral and teaching levels during these three years. You were always near me for any help I needed. I appreciate a lot your personality, kindness, your humor and your ability to listen and understand people, your way of thinking and dealing with things. Sorin and Irina, no words can express my thanks for you both!

For Gérard Ghibaudo, my third non official supervisor, what I can say! Thanks are not enough. It has always been very simple and motivating to work with you, your kindness, your humanity and your loyalty make you one of the persons that I respect most. Of course, I will not forget your great and deep knowledge in the semiconductor area and thank you for sharing a part of it with me.

I would like to express my gratitude to the committee of this thesis: Prof. Olivier Bonnaud, Prof. Francisco Gámiz Pérez, Dr. Daniela Munteanu and Manager advanced R&D Daniel Delprat. I am honored by their participation to my Ph.D. defense and their expert judgment of my work.

My collaboration with Soitec<sup>™</sup> engineers and scientists was much appreciated: Carlos Mazuré, Frédéric Allibert, Daniel Delprat and William Van Den Daele ("I will always remember Bonjour Madame every morning"). Next, I'd like to thank the French Ministry of National Education and the doctoral school EEATS (University of Grenoble and Grenoble Institute of Technology), for offering me a chance to conduct this Ph.D. thesis research and for their financial support (Allocation de Recherche) during the three years. I would also like to thank our collaborators, Akiko Ohata, Young-Ho Bae, Crisitina Fernández "pseudo-MOSFET girl", my friend Noel Rodriguez, Emeline Saracco and Jean-François Damlencourt for providing me many insightful discussions as well as the help in paper's preparing and other technical problems. Additionally, I'd like to acknowledge people at IMEP-LAHC laboratory for giving me help and support during experiments: Jan Chroboczek, Xavier Mescot, Martine Gri. Thanks to Fanyu Liu, Luca Pirro, Mehdi Daanoune and Sofiane Sirajeddine for the good work that we did and we will continue to do together.

I would like also thank all my friends "Ph.D. students" at IMEP-LAHC laboratory, my present and my ex office colleagues (A286), all the members of the laboratory IMEP-LAHC council, IMEP technical and administration staff and my foreign, French and Lebanese friends in Grenoble/France.

Special thanks to my professor Bilal Beydoun in the Lebanese University for introducing me to the world of nanotechnology.

Finally, loving thanks to my parents Abla & Ahmad, brother Assem and sister Katia. Without their support and motivation, my achievements would have been incomplete. I love you all.

## List of acronyms

| Acronym Nomination |                                                   |  |

|--------------------|---------------------------------------------------|--|

| MOS                | Metal oxide semiconductor                         |  |

| MOSFET             | Metal oxide semiconductor field effect transistor |  |

| Ψ-MOSFET           | Pseudo-MOSFET                                     |  |

| BOX                | Buried oxide                                      |  |

| CMOS               | Complementary metal oxide semiconductor           |  |

| SOI                | Silicon-On-Insulator                              |  |

| HD SOI             | Heavily-doped Silicon-On-Insulator                |  |

| VDP                | Van der Pauw                                      |  |

| NWs                | Nanowires                                         |  |

| GAA                | Gate-All-Around                                   |  |

| Low-T              | Low-temperature                                   |  |

| 1D, 2D and 3D      | One, two and tri-Dimensional                      |  |

| NP                 | Nanoparticles                                     |  |

| APTES              | Amino-Propyl-Tri-Ethoxy-Silane                    |  |

| AFM                | Atomic force microscopy                           |  |

| PD                 | Partially depleted                                |  |

| FD                 | Fully depleted                                    |  |

| SIMOX              | Separation by IMplantation of OXygen              |  |

| BESOI              | Bond-and-Etch-back Silicon-On-Insulator           |  |

| ELTRAN             | Epitaxial Layer TRANsfer                          |  |

| ITOX               | Internal Thermal OXidation                        |  |

| MLD                | Modified Low Dose                                 |  |

| UT                 | Ultra-thin                                        |  |

| ET                 | Extra-thin                                        |  |

| h+                 | Hole                                              |  |

| e-                 | Electron                                          |  |

| LFN                | Low-frequency noise                               |  |

| RTS                | Random Telegraph Signal                           |  |

| G-R                | Generation-recombination                          |  |

| CNF                | Carrier number fluctuation                        |  |

| HMF                | Hooge mobility fluctuation                        |  |

## List of symbols

| Symbol                                 | Unit                             | Description                                         |

|----------------------------------------|----------------------------------|-----------------------------------------------------|

| ID                                     | А                                | Drain current                                       |

| I <sub>D,corr</sub>                    | А                                | Corrected drain current from series resistance      |

| Is                                     | А                                | Source current                                      |

| $I_G$                                  | А                                | Gate current                                        |

| Iacc                                   | А                                | Accumulation current                                |

| $I_{vol}$                              | А                                | Volume current                                      |

| $V_D$                                  | V                                | Drain voltage                                       |

| $V_S$                                  | V                                | Source voltage                                      |

| $V_{G}$                                | V                                | Back-gate voltage                                   |

| VT                                     | V                                | Threshold voltage                                   |

| $V_{FB}$                               | V                                | Flat-band voltage                                   |

| S                                      | V.dec <sup>-1</sup>              | Subthreshold swing                                  |

| $\mathbf{S}_{\mathbf{n}}$              | V.dec <sup>-1</sup>              | Subthreshold swing for electrons                    |

| $\mathbf{S}_{\mathbf{p}}$              | V.dec <sup>-1</sup>              | Subthreshold swing for holes                        |

| PSD, S(f)                              | W.Hz <sup>-1</sup>               | Power spectral density                              |

| $\mathbf{S}_{\mathbf{I}_{\mathbf{d}}}$ | A <sup>2</sup> .Hz <sup>-1</sup> | Drain current power spectral density                |

| $S_{V_g}$                              | V <sup>2</sup> .Hz <sup>-1</sup> | Gate voltage power spectral density                 |

| $\mathbf{S_{V_{fb}}}$                  | V².Hz <sup>-1</sup>              | Flat-band voltage power spectral density            |

| $\mathrm{S_{I_d}/I_D}^2$               | Hz-1                             | Normalized power spectral density                   |

| $\mathbf{S}_{	ext{eff}}$               | mm <sup>2</sup>                  | Effective surface                                   |

| D <sub>it</sub>                        | cm <sup>-2</sup> /eV             | Interface trap density                              |

| D <sub>it1</sub>                       | cm <sup>-2</sup> /eV             | Interface trap density at film-BOX (back) interface |

| D <sub>it2</sub>                       | cm <sup>-2</sup> /eV             | Interface traps density at top interface            |

| μ <sub>o</sub>                         | cm <sup>2</sup> /V.s             | Low-field mobility                                  |

| . $\mu_{\rm eff}$                      | cm <sup>2</sup> /V.s             | Effective mobility                                  |

| $\mu_n$                                | $cm^2/V.s$                       | Low-field electrons mobility                        |

| $\mu_{\rm p}$                          | $cm^2/V.s$                       | Low-field holes mobility                            |

| $\mu_{vol}$                            | cm <sup>2</sup> /V.s             | Volume mobility                                     |

| $\mu_{s}$                              | cm <sup>2</sup> /V.s             | Accumulation mobility                               |

| $\mu_{\rm H}$                          | $cm^2/V.s$                       | Hall mobility                                       |

| μ <sub>Ph</sub>                        | $cm^2/V.s$                       | Low-field mobility limited by phonon scattering     |

| $\mu_{\rm sr}$                         | $cm^2/V.s$                       | Low-field mobility limited by surface roughness     |

| μ <sub>C</sub>                         | $cm^2/V.s$                       | Low-field mobility limited by phonon scattering     |

| R <sub>SD</sub>                        | Ω                                | Series resistance between source and drain          |

| $\mathbf{R}_{\Box}$                    | Ω                                | Sheet resistance                                    |

| G                                      | $\Omega^{-1}$                    | Electrical conductance                              |

| $\mathbf{g}_{\mathrm{m}}$              | S                                | Transconductance                                    |

| g <sub>m</sub><br>f                    | Hz                               | Frequency                                           |

| ${f f_g}{f T}$                         | unitless                         | Geometrical factor in pseudo-MOSFET                 |

| Ť                                      | K                                | Temperature                                         |

| Symbol                              | Unit                 | Description                                             |

|-------------------------------------|----------------------|---------------------------------------------------------|

| C <sub>Si</sub> , C <sub>film</sub> | F.cm <sup>-2</sup>   | Surface silicon film capacitance                        |

| C <sub>it1</sub>                    | F.cm <sup>-2</sup>   | Surface traps density capacitance at film-BOX interface |

| C <sub>it2</sub>                    | F.cm <sup>-2</sup>   | Surface traps density capacitance at top interface      |

| Cox                                 | F.cm <sup>-2</sup>   | Surface oxide capacitance/BOX capacitance per unit area |

| $C_{dep}$                           | F.cm <sup>-2</sup>   | Dynamic depletion capacitance                           |

| C <sub>gc</sub>                     | F.cm <sup>-2</sup>   | Gate-to-channel capacitance                             |

| $C_{\mathrm{gb}}$                   | F.cm <sup>-2</sup>   | Gate-to-bulk capacitance                                |

| C <sub>max</sub>                    | F                    | Maximum value of the gate-oxide capacitance             |

| $C_{\mathrm{sub}}$                  | F.cm <sup>-2</sup>   | Depleted substrate capacitance                          |

| ρ                                   | $\mathrm{cm.}\Omega$ | Electrical resistivity                                  |

| $\theta_1$                          | V-1                  | First order mobility attenuation factor                 |

| $\theta_2$                          | V-1                  | Second order mobility attenuation factor                |

| фғ                                  | V                    | Fermi level potential                                   |

| φ <sub>fb</sub>                     | V                    | Work function difference between Si film and substrate  |

| Qox                                 | С                    | The fixed charge in the buried oxide                    |

| Q <sub>dep</sub>                    | С                    | Depletion charge                                        |

| Qinv                                | С                    | Inversion charge                                        |

| $\mathbf{Q}_{\mathrm{acc}}$         | С                    | Accumulation charge                                     |

| E <sub>G</sub>                      | eV                   | Band gap                                                |

| $\mathbf{E}_{\mathrm{eff}}$         | V/cm                 | Effective transversal electric field                    |

| Nt                                  | cm <sup>-3</sup> /eV | Volume trap density                                     |

| Nit                                 | cm <sup>-2</sup> /eV | Surface trap density in the oxide                       |

| N <sub>inv</sub>                    | cm-2                 | The concentration of carriers in the inversion layer    |

| N <sub>A</sub>                      | cm <sup>-3</sup>     | Acceptor impurities concentration                       |

| ND                                  | cm <sup>-3</sup>     | Donor impurities concentration                          |

| $N_{\mathrm{film}}$                 | cm <sup>-3</sup>     | Doping level in the silicon film                        |

| $\mathbf{N}_{	ext{sub}}$            | cm <sup>-3</sup>     | Doping level in the substrate                           |

| $n_i, n_i(T)$                       | cm <sup>-3</sup>     | Intrinsic carrier density                               |

| t <sub>Si</sub>                     | nm                   | Silicon film thickness                                  |

| t <sub>BOX</sub>                    | nm                   | Buried oxide thickness                                  |

| WD                                  | nm                   | Width of the depletion layer                            |

| р                                   | g                    | Pseudo-MOSFET probe pressure                            |

## List of constants

| Symbol         | Value/Unit                         | Description                  |  |

|----------------|------------------------------------|------------------------------|--|

| k              | 1.38×10 <sup>-23</sup> J/K         | Boltzmann constant           |  |

| q              | $1.602 \times 10^{-19}$ C          | Elementary charge            |  |

| ε <sub>0</sub> | $8.85 \times 10^{-12} \text{ F/m}$ | Vacuum permittivity          |  |

| Esi            | 11.8 × $\varepsilon_0$ F/m         | Silicon permittivity         |  |

| ESiO2          | $3.9 \times \varepsilon_0 F/m$     | Silicon dioxide permittivity |  |

## **General introduction**

Since the era of portable multimedia, Smartphones and other state-of-the-art applications, the demand for smaller, smarter and deeper processors was accelerated, pulling behind it all the microelectronics industry and intensifying the rhythm of the technological research. In this challenging context of evolution of microelectronics, the use of Silicon-On-Insulator (SOI) substrates instead of bulk silicon opens new avenues for innovation, delivering performance, power and miniaturization. Indeed, SOI technology can overcome some of the major issues of bulk silicon technology (*e.g.* device isolation is less complex thanks to the presence of the buried oxide). Moreover, SOI devices offer a much better electrostatic control of the channel thanks to advanced architectures (*e.g.* multi-gate transistors).

In order to take full advantage of all SOI benefits, the SOI wafers must be of an excellent electrical quality. In this highly competitive field, the aim of this thesis is to contribute to the analysis and to the optimization of advanced SOI substrates by the development of innovative methods of electrical characterization and new physical models, starting from the classical, well-known pseudo-MOSFET ( $\Psi$ -MOSFET) configuration.

This manuscript is composed of four chapters: one on the review of SOI technology, the second about  $\Psi$ -MOSFET characterization technique and its developments, the third on innovative electrical methods and the last on the use of  $\Psi$ -MOSFET configuration for more exotic applications in nanoelectronics.

The first chapter will cover Semiconductor-On-Insulator (SOI) materials and devices as well as their characteristics. In the first section, we will introduce SOI technology and transistor structures fabricated on SOI substrate. We will concentrate on partially depleted (PD) and fully depleted (FD) SOI MOSFETs by presenting their principles and challenging issues. Finally, we will show some innovative SOI-based technology architectures. In the second section, the state-of-the art of SOI material technology and the fabrication methods are discussed. We also introduce novel semiconductor on insulator structures emerged from SOI technologies. Finally, we will present the defects of SOI materials. In the second chapter, we start from the classical well known  $\Psi$ -MOSFET characterization method for SOI materials. Firstly, we describe the principles, standard operation and classical parameters extraction for  $\Psi$ -MOSFET. In second section we wanted to know whether it is possible to extend the  $\Psi$ -MOSFET to advanced SOI substrates with ultra-thin film and/or BOX. Furthermore, the main question of the third section is: can we also extend  $\Psi$ -MOSFET at low temperature?

In the third chapter, we investigate the possibility to expand the range of  $\Psi$ -MOSFET from classical I-V measurements to other types of characterizations. The first track followed concerns the low frequency noise measurements. Is it possible to measure low-frequency noise in  $\Psi$ -MOSFET configuration? Furthermore, is it reasonable to apply MOS-like models to these measurements and extract material parameters? The second road taken drove us to *C*-*V* measurements in  $\Psi$ -MOSFET. Would a split *C*-*V* technique be possible for SOI in  $\Psi$ -MOSFET? Is the effective mobility extraction possible here, as it is in MOSFETs?

In the last chapter, we let our imagination run towards exotic uses of  $\Psi$ -MOSFET. Would it be possible to apply  $\Psi$ -MOSFET to heavily doped SOI films and could we obtain parameters such as the doping level? The SOI in  $\Psi$ -MOSFET is sensitive to the environment, but could it be used as a reliable sensor? We will present the answer to this question for gold nanoparticle detection. Finally the paradigm of  $\Psi$ -MOSFET is based on the use of back gate. Can this configuration be suitable for 3D vertically-stacked nanowires? Would the conduction through these nanowires be controlled by a back-gate as it is in  $\Psi$ -MOSFET? Could one obtain electrical parameters concerning the NWs from this kind of measurements?

The main answers to these questions will be developed chapter after chapter and synthetized in the general conclusion. During this Ph.D., some doors were opened albeit further investigations are needed; they will be presented as perspectives.

## <u>Chapter I</u>:

## Introduction to SOI materials and devices

### Introduction

This chapter introduces Semiconductor-On-Insulator (SOI) materials and devices as well as their characteristics.

In the first section, the motivations and the advantages of SOI structure for building transistors are shown. Then we discuss SOI devices by presenting successively the partially depleted (PD) and fully depleted (FD) transistors; finally, some innovative architectures based on SOI technology are described.

In the second section, we give an overview of the state of art of SOI technology and fabrication methods, followed by an introduction to new SOI-like materials. The defects of SOI material are also discussed.

#### 1. SOI devices

# **1.1 SOI technology: an answer to scaling and diversity in Moore's law**

The use of Silicon-On-Insulator (SOI) components is technically imperative in diverse domains of the electronics. Here are some examples: very low consumption circuits, in particular for laptops, telephones, tablets, game consoles, computers, watches; very fast microprocessors intended for PCs and servers; Radio Frequency circuits for wireless communication; average and high-voltage circuits for the lighting or engines command control; high temperature circuits for the oil, automobile and the aeronautics industries; hardened circuits for the space and the defense.

Silicon-On-Insulator is gaining momentum as bulk complementary metal oxide semiconductor (CMOS) technology is confronted with scaling, power and performance challenges. The miniaturization driven by Moore's Law requires doubling the density of transistors per unit area every two years. This law has very strong economic implications and makes the market very beneficial for the most powerful microelectronic integrated circuit manufacturers. The topic is hot, being situated at the crossing of two Moore avenues: continuing the scaling and diversity.

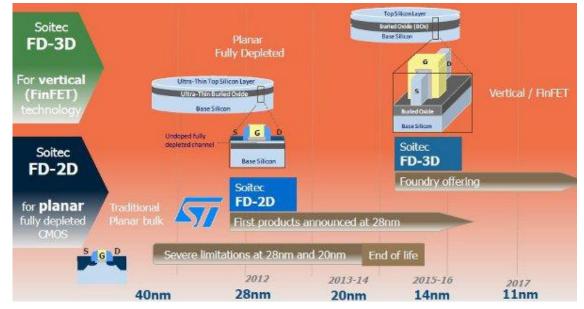

The milestones of the scaling are measurable in nanometers for the transistor feature size and in billions for the number of transistors in a System-On-Chip (SOC). SOI is certainly able to take us far beyond the current status. SOI circuits are denser, smaller, and faster. This is why the device miniaturization is more efficient and comfortable if transistors are fabricated "On Insulator". In addition, an effort to gain a stronger foothold in the coming fully depleted (FD) CMOS era: the world leader for SOI manufacturing (Soitec) is already providing SOI wafers to both planar two-Dimensional FD (FD-2D) and tri-Dimensional FD (FD-3D FinFET) customers for the next technological nodes (Figure I-1).

The diversity side of the Moore's law departs from the traditional forms of scaling. This route is imposed by the need for enriched circuit functionality. SOI is flexible for the co-integration of heterogeneous technologies and multi-functional devices. Skilled circuit design can take advantage of multiple gates, independently biased, to reduce the transistor count for a given logic function or to elaborate new schemes of operation. Some innovative SOI devices will be illustrated later.

On the other hand, SOI circuits naturally offer low-power consumption without fundamentally disrupting the current CMOS process and design infrastructure [1]. A comparison of state-of-the-art bulk and SOI circuits provides unquestionable evidence. The main advantages of SOI technology will be discussed in the next sub-sections.

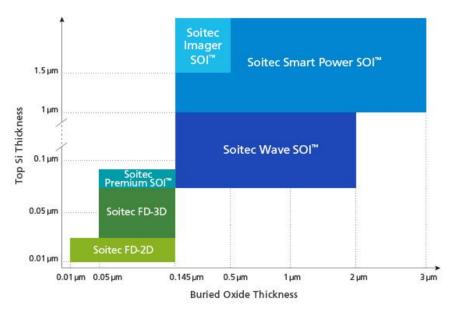

Figure I-1: SOI wafer roadmap from Soitec for next technological nodes [2].

The superior performances of SOI devices justify additional cost, which moreover is decreasing under the influence of the increase of the volume of markets. Finally, there is wide space for further improvements enabling a massive increase of the SOI segment in the global market for integrated circuits.

#### 1.2 Advantages of the SOI technology

The main originality of the SOI transistor compared with the silicon bulk transistor comes from the presence of the buried oxide (BOX) under the Si film. By isolating the thin silicon film from the substrate, we limit the parasitic effects associated with it that may damage the good function of devices. Indeed, in a MOSFET there is only the superficial layer of silicon, with a thickness of 0.006-0.1  $\mu$ m (that is to say less than 0.01 % of the total thickness of the silicon wafer), which is really useful for the transport of carriers [3]. The rest of the Si wafer (99.99 %) is

responsible for the undesirable parasitic effects, which can be avoided by calling a solution such as SOI.

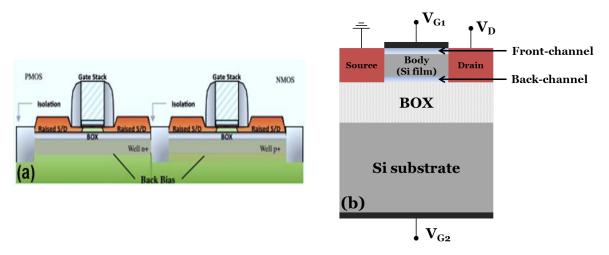

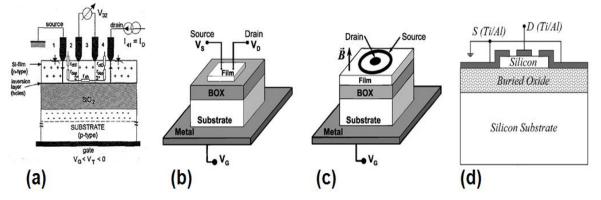

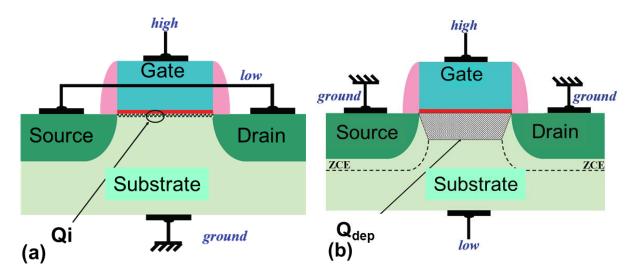

A schematic configuration cross section of a metal oxide semiconductor (MOS) transistor built in SOI is shown in Figure I-2a. An interesting specificity of SOI transistor is the possibility of applying simultaneously front-gate voltage ( $V_{G_1}$ ) and back-gate voltage ( $V_{G_2}$ ) to the gates G1 (front-gate) and G2 (back-gate). According to the bias applied to the gates G1 and G2, the body of the transistor can accommodate two conduction channels: the front-channel at the film/gate oxide interface and the back-channel at the film/BOX interface (Figure I-2b).

*Figure I-2: SOI MOS transistor cross section (a) of schematic architecture [4], (b) of the transistor.*

The SOI transistors, thanks to their structure, present advantages with respect to bulk MOSFETs. Below we expose some of these advantages.

*Immunity against radiations:* historically, there have been three reasons for developing and using SOI. In the 1970's and 1980's, radiation hardness of integrated circuits was the main motivation for choosing these new substrates. Transistors with thin SOI film are exceptionally tolerant to the transient effects of the ionizing irradiations. The majority of charges generated in the Si substrate would be stopped by the buried oxide, thus reducing the current surge in the active film. Besides, compared with silicon bulk, SOI possesses superior immunity for the induced degradation by hot carriers.

**Device and structure isolation:** SOI chips consist of millions of singletransistor islands dielectrically isolated from each other and from the underlying silicon substrate. The entire transistor body (the source, the drain, and the channel in between) is isolated from the Si substrate and from every other transistor by means of the buried oxide below, and by a combination of thermally grown and deposited oxide above and on the sides of the transistor.

The lateral isolation makes inter-device separation in SOI free of complicated schemes of trench or well formation. The overall technology and circuit design are, in this respect, highly simplified and result in more compact Very-Large-Scale Integration chips compared to Si bulk circuit concept and design. On the other hand, the vertical isolation protects the thin active silicon layer (Si film) from most parasitic effects induced by the Si bulk substrate: leakage currents, radiation-induced photocurrents, *latch-up* effects between contiguous devices, *etc*.

**Reduction of parasitic capacitances:** the source and drain regions spread out down to the buried oxide so that the junctions between source/drain and the Si body do not present more than a lateral side and minimized surface [3]. It results a strong reduction of the current leakage and the junction capacitances. This offers the opportunity to fabricate CMOS circuits with lower power dissipation in standby and operating modes, improved speed, and wider temperature range.

**Reduction of short-channel effects (SCEs):** the limited extension of drain and source regions makes SOI MOS transistors less sensitive to the shortchannel effects, induced by the charge sharing between gate and junctions. Indeed, the surfaces of the source/drain junctions depend only on the film thickness, the depleted zones are less spread and the SCEs decrease. Furthermore, the possibility of bias by the back-gate offers an additional way for controlling the short-channels effects.

*Low voltage and low power (LV/LP) circuits:* it is especially in this very competitive domain that SOI expresses its full potential. A low voltage applied to the gate is desirable to switch the transistor from the off state to the on state, leading to the need for a low subthreshold swing (S). Only the SOI offers almost ideal slope in weak inversion (S  $\approx$  60 mV/decade at room temperature), and thus the possibility of lowering the threshold voltage (V<sub>T</sub>) around 0.2 to 0.3 V. The low leakage currents minimize the dissipated power in static mode, while the dynamic power is saved by the decrease of parasitic capacitances and of power supply voltage.

A gain in performance of about 20-30 % as compared to bulk-silicon circuits is systematically observed during operation with similar voltage power, whereas

operation at similar low power dissipation yields higher the gain by more than two times. In other words, SOI circuits of n generation and bulk-Si circuits from the next generation (n + 1) perform comparably [5]. This argument is strong enough for major companies to include SOI technology in their strategy. IBM, Sony, AMD, Sharp, STMicroelectronics, *etc.*, are currently fabricating commercial SOI-enhanced PC processors and mobile communication devices.

The main disadvantage which the SOI had to undergo is the fact that the enumeration of this impressive list of advantages was not enough for perturbing the fast and continuous progress of the silicon technology. Moreover, the presence of the BOX asks to take into account other phenomena (*e.g.*, floating body, self-heating, BOX and Si-SiO<sub>2</sub> interface quality) which can affect the operating of SOI devices.

In the following sub-sections of this chapter we will describe the traditional technologies (PD and FD) of SOI MOSFETs and give examples of innovative SOI device architectures. The aim of these examples is to show how the SOI can improve performance.

#### **1.3 SOI MOSFETs**

The two technologies, which we denote now FD for fully depleted and PD for partially depleted are specific for "film On Insulator" structures, such as SOI or GeOI. PD technology is closer to the Si bulk technology in terms of electrical behavior, but does not have as many advantages as the FD technology in terms of reduced shortchannel effects.

For a MOS transistor, there are different operating regimes (weak and strong inversion, depletion and accumulation). When we bias the gate in inversion mode, the majority carriers are pushed away from the oxide/semiconductor interface to create a depletion zone and then an inversion layer. Once the inversion regime appears, the depletion zone freezes and possesses a maximal width ( $W_{Dmax}$ ). It is expressed by the following relationship [6]:

$$W_{Dmax} = \sqrt{\frac{4\varepsilon_{Si}\phi_{F}}{qN_{A,D}}} = \sqrt{\frac{4\varepsilon_{Si}kT}{q^{2}N_{A,D}}\ln\left(\frac{N_{A,D}}{n_{i}(T)}\right)}$$

(I-1)

where  $\varepsilon_{Si}$  is the silicon permittivity, q is the elementary charge, k is the Boltzmann constant, T is the temperature,  $\phi_F$  is the Fermi level potential,  $n_i(T)$  is the intrinsic carrier density and  $N_{A,D}$  is the impurities concentration for acceptors ( $N_A$ ) or donors ( $N_D$ ).

In the case of SOI MOSFET, there are two MOS stacks, the first one corresponding to metal gate/gate oxide/Si film and the second to Si film/BOX/Si substrate. In that case, it is possible according to  $W_{Dmax}$  and to the film thickness ( $t_{Si}$ ) to distinguish the two modes (PD and FD) for SOI transistors:

- The PD mode, or **partially depleted**, corresponds to a film thickness  $t_{Si}$  superior two times to the maximal depletion width  $W_{Dmax}$ . In that case, there is a part of the film which will be 'neutral' (no space charge region can cover this part). Thus, the condition of PD mode can be written as  $t_{Si} > 2W_{Dmax}$ .

- The FD mode, or **fully depleted**, is obtained in case of  $t_{Si} < 2W_{Dmax}$ . The depletion zones overlap and the potential of both interfaces interacts by coupling.

The FD and PD modes depend only on the intrinsic carrier density, on the impurities concentration and on the temperature. Therefore, they are really specific to the semiconductor material used. To give an example,  $W_{Dmax}$  for a Si film with a doping concentration level ( $N_A = 10^{17}$  cm<sup>-3</sup>), at room temperature (T = 300 K), is almost equal to 100 nm. The future generations of SOI transistors for the advanced nodes must be made on FD SOI to keep all the advantages of short-channel effects control ([7], [8]).

Notice that the previous analysis corresponds to long channels. In short channel transistors, the depletions of the source/drain are added to the depletion of the gate modifying the actual doping and leading to two-dimensional (2D) effects [9].

#### 1.3.1 Partially depleted transistors: PD MOSFETs

As previously mentioned, in this case the depletion zones do not overlap and the electric potentials of the two interfaces (gate oxide/Si film and Si film/BOX) remain independent. This situation is very similar for the electrical operating to the architecture of bulk silicon transistors. The Si film must be inevitably doped to reduce the depletion width so to decrease the short-channel effects. Nevertheless, in PD films there are additional effects named "floating-body effects". In Si-bulk architecture, if majority carriers are created during the operating of the transistor, they can be evacuated by the substrate because it is directly connected to ground. On the other hand, in the case of a PD SOI transistor, the film potential is not fixed; it is then floating. The film potential is determined by the capacitances related to source and drain, by the front and back gate and also by the current which circulates in the channel. In most of the cases, the parasitic effects appear because of created majority carriers excess which cannot be evacuated from the Si film. Below are the most frequently encountered "floating-body effects":

- The kink effect occurs in strong longitudinal field due to high drain voltage (V<sub>D</sub>). Majority carriers are then produced by impact ionization and increase the body potential. The potential increase has the impact of decreasing the threshold voltage (V<sub>T</sub>) and increasing the drain current (I<sub>D</sub>) [10].

- The parasitic bipolar transistor effect appears at strong V<sub>D</sub> when a strong majority carrier density is accumulated, the body potential becomes high enough so that the PN (body-Source) junction turns on. The NPN (Source/film/Drain) bipolar transistor is activated. The drain current increases, it is the second kink effect.

- The **transient effects** (variations of body potential, threshold voltage, and current) occur during the switching of transistors [11]. When the gate is switched on, majority carriers are expelled from the depletion region (instantly formed by capacitive coupling) and collected in the neutral body, giving rise to a drain current 'overshoot'. The drain current decreases gradually with time during electron-hole recombination. A reciprocal 'undershoot' occurs when the gate is switched from strong to weak inversion: the drain current increases with time as the majority carriers are generated and allow the depletion depth to shrink. The amplitude of current overshoot or undershoot is proportional to the difference between the final and initial body charges, and the transient duration depends on the generation-recombination rate in the film volume, at interfaces and on the edges.

- The **Gate-Induced Floating Body Effect** (GIFBE) effect [12] occurs for very thin gate oxides and at strong gate voltage; the leakage currents by tunnel effect can be important, leading to body charping, a variation of the film potential (even for low drain current) and an increase of the drain current.

In order to face all these floating-body effects and to ameliorate the transistor performances, FD technology presented in the next sub-section was found suitable to replace the PD technology.

#### 1.3.2 Fully depleted transistors: FD MOSFETs

Unlike PD technology, full depletion appears when the depletion regions cover the whole transistor body (*i.e.*; the film thickness). The depletion charge is constant and cannot extend further when the gate bias increases. There is no neutral zone.

In SOI MOSFETs, two inversion channels can be activated, one at the front Si-gate oxide interface and the other at the back Si-BOX interface. A better coupling is then obtained between the gate bias and the inversion charge, leading in particular to an increase of the drain current. Besides, the front and back surface potentials become inter-related [3]. The interface coupling means that the electrical characteristics of one channel vary with the bias applied to the opposite gate. In practice, the front gate measurements may include contributions from the BOX and from the BOX/bulk Si interface, and highly depend on the back gate bias.

This FD technology presents numerous advantages:

- The possibility to non-dope the conduction channel enables increasing the mobility compared with a PD SOI transistor.

- Short-channel effects are largely reduced if t<sub>si</sub> is very small ([7], [8]).

- Lower threshold voltage compared to Si bulk technologies allows low power consumption applications.

- The subthreshold slope (S) is reduced due to the replacement of the dynamic depletion capacitance ( $C_{dep}$ ) by a fixed Si film capacitance ( $C_{Si} = \epsilon_{Si}/t_{Si}$ ).

Nevertheless FD SOI transistors have several issues especially in the case of ultra-thin films:

- Very sensitive threshold voltages to the ultra-thin Si film uniformity (especially for  $t_{Si}$  < 10 nm).

- Defect coupling in FD MOSFETs means that carriers flowing at one interface are influenced by the presence of defects at the opposite interface.

- A mobility variation with the film thickness [13].

- Self-heating conveyed by the low thermal conductivity of the BOX.

- Drain-induced virtual substrate biasing (DIVSB) effect is due to the lateral penetration of the electric field into the BOX and underlying substrate. The fringing field causes an increase in the potential at the film-BOX interface; by consequence the front-channel threshold voltage and subthreshold slope are lowered [14].

To ameliorate the electrical behavior (lower  $V_T$ , steeper S, higher mobility, *etc.*) of SOI transistors, several innovative structures based on this technology were proposed.

#### 1.4 Innovative SOI transistors

The SOI structure and the advanced development of the film layer transfer technology allow the conception of transistors with innovative architectures and with improved performances. In this sub-section, we show various SOI-based architectures.

#### 1.4.1 Multi-gate transistors

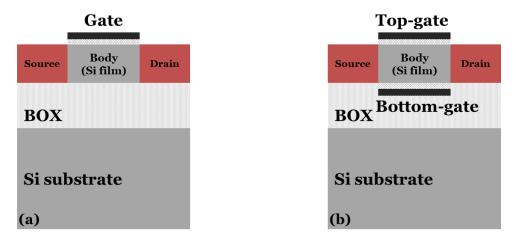

Transistors with multi-gate are innovative architectures but with more complicated technological steps compared to SOI single-gate transistors (Figure I-3a). Their basic structure is the same as that of FD SOI: an extremely thin silicon film and a relatively thick buried oxide on a silicon substrate are always part of the structure. The number, shape and the location of the gates improve the gate control over the channel and isolate it from parasitic effects which can appear in single-gate architectures. Components with multi-gates will lead microelectronics industry into the near future. These components present several advantages when the gate length becomes shorter than 25 nm.

#### 1.4.1.1 Double-gate (DG) transistors

The conception of double-gate transistors appeared as a solution for the penetration of the electric field in the BOX for ultra-thin SOI transistors. The addition of the second gate under the silicon blocks the penetration of the electric field and offers a better control of the channel (Figure I-3b). The presence of the back-gate increases the channel surface conduction and favors the volume inversion, thus, the drain current is increased compared with the single-gate SOI transistor (Figure I-3a). The substhreshold slope and the short-channel effects are also improved [15].

Figure I-3: (a) Conventional thin film SOI MOSFET, (b) SOI MOSFET with top and bottom gate (DG MOSFET).

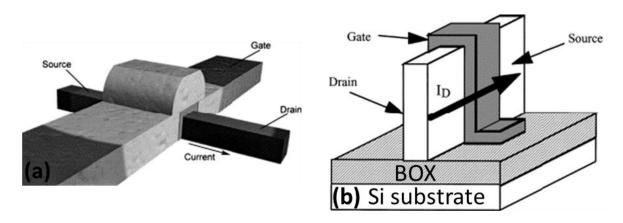

#### 1.4.1.2 Triple-gate transistors

In triple-gate (Figure I-4a) or FinFET (Figure I-4b) transistors, the gate recovers the three faces of the Si 'fin', forming then three channels. The upper channel could be deactivated by using a thicker oxide, forming a semi-vertical double-gate transistor. The current is horizontal, but controlled by two vertical gates, which can be possibly biased independently. Because of the FinFET configuration, the coupling effects are tri-dimensional (3D): 'lateral' coupling between the opposite

gates, the 'vertical' coupling between channels and the substrate voltage and the 'longitudinal' coupling between the drain and the channel. Nevertheless, the performances are excellent thanks to the strengthening of the gate role. In general, FinFET transistors are made on bulk Si, but their structure and operation, in fully depleted regime, are similar to their cousins on SOI (Figure I-4b).

Figure I-4: (a) triple-gate SOI MOSFET, (b) SOI FinFET structure [16].

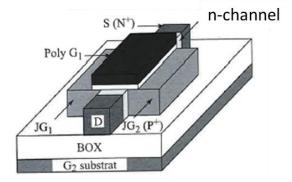

#### 1.4.1.3 Four-gate (G4-FET) transistors

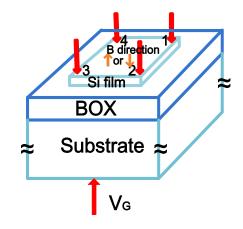

The four-gate (G4-FET) transistor (Figure I-5) has four independently biased gates [17]. The source and the drain are doped N<sup>+</sup> and the body is N type, as in a transistor in accumulation mode. We form on sides two P<sup>+</sup> junctions which play the role of lateral gates. These gates allow modulating the effective width of the transistor while the usual MOS gates, situated in front and back face, govern the accumulation or the depletion of the carriers. G<sup>4</sup>-FET combines MOSFET and JFET (junction field-effect transistor) operating types where every gate can cut the current. The published results [17] show that G<sup>4</sup>-FET turns out to be a useful and new transistor, with a high flexibility in the modulation of the subthreshold slope, threshold voltage and noise.

Figure I-5: Configuration of the n-channel G4-FET [17].

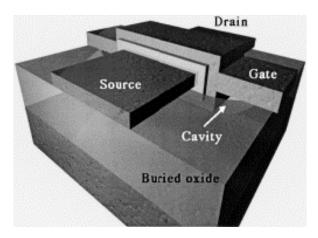

#### 1.4.2 Gate-All-Around (GAA) transistors

The Gate-All-Around (GAA) transistor (Figure I-6) possesses a unique gate which surrounds the body, rectangular or circular. The electrostatic control being ideal, this transistor, called also 'nanowire MOSFET', turns out to be the most scalable. A recent variant is the transistor without junction ('junctionless' FET) where the source, the drain and the body have all a very high doping [18]. It is in fact a resistance the center part of which is surrounded by a gate able to cut the current by full depletion. This implies a technological compromise between strong doping (>> 10<sup>19</sup> cm<sup>-3</sup>) and low diameter (< 5 nm).

Figure I-6: Gate-All-Around (GAA) MOSFET [16].

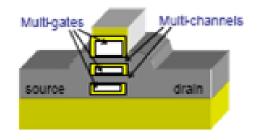

#### 1.4.3 Tri-dimensional nanowires (3D NWs)

Another alternative to increase the on-current at the end of roadmap is the fabrication of multi-gate and multi-channel superposed structures working in parallel (Figure I-7). Components are made by iterations using the Silicon-On-Nothing (SON) technology, which can give rise to very good performances [19].

Figure I-7: Schematic representation of multi-gate and multi-channel MOSFET.

#### 2. SOI materials

The zoology of architectures of SOI devices previously shown represents different answers to efficient scaling. Obviously, the condition for efficient scaling is the use of high quality SOI wafers. In this section we will show different SOI materials and the technologies of fabrication. We will resume the best technological choices in order to obtain high quality SOI materials.

#### 2.1 State-of-the-art

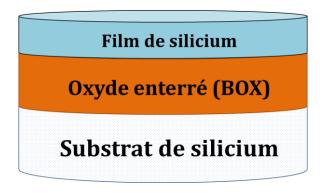

The Semiconductor-On-Insulator is a new generation of materials for an alternative technology to traditional "bulk" substrates used in the microelectronics industry. The SOI substrates are composed of a buried oxide (BOX) inserted between the active silicon layer (Si film) on which electronic components are made, and the silicon substrate which serves for mechanical support (Figure I-8) [3].

Figure I-8: Schematic representation of SOI structure.

SOI technology has been developed in the 1960-1970s. The first SOI substrate was the Silicon-On-Sapphire (SOS) which used the sapphire ( $Al_2O_3$ ) as an insulator [20]. This technology has been used for long time in niche applications such as spacecraft and military electronics, because it improves the resistance of the integrated circuits against ionizing radiation. The use of SOS was limited due to their high cost and material issues.

Thanks to the advance in the technology and especially the patent of the Smart-Cut<sup>™</sup> process [21], the SOI material was able to prove itself and to enter the

world of microelectronics industry. Below we discuss the different fabrication methods of SOI wafers.

#### 2.2 Fabrication methods

The main problem to fabricate an SOI wafer comes up when a crystalline silicon layer must be deposited on top of an insulator, usually an oxide sitting on top of a silicon wafer. Ideally both the silicon layer and the oxide layer should be defectfree, stress-free and uniform in thickness, and should display excellent interface properties.

There are numerous methods for manufacturing SOI wafers ([3], [5]). In this section, we briefly describe the most relevant techniques that have been developed and we focus on the technological approaches that gained commercial significance. It is possible to separate them into two main groups: the formation of buried oxide layer by implantation through the substrate (SIMOX: Separation by IMplantation of OXygen) and wafer bonding (BESOI: Bond-and-Etch-back SOI, ELTRAN: Epitaxial Layer TRANsfer and Smart Cut<sup>TM</sup>).

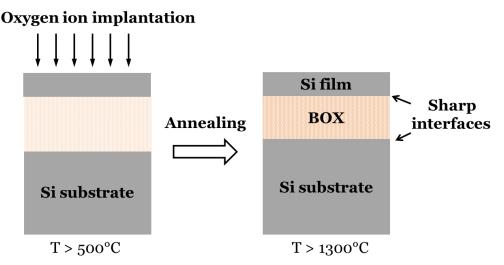

#### 2.2.1 SIMOX technology

In 1966 the first publications reported the attempt to form silicon dioxide  $(SiO_2)$  by oxygen (O) implantation into silicon [22]. However, it was not until the late 1970's that the SIMOX process was actually developed and demonstrated for the fabrication of MOS devices with SOI structure [23].

The principle of SIMOX material formation is quite simple, and consists of the synthesis of a buried layer of  $SiO_2$  by oxygen ions implantation beneath the surface of a silicon wafer. The silicon oxide is made by internal oxidation during the deep implantation of oxygen ions at high doses (in the order of  $2 \times 10^{18}$  ions.cm<sup>-2</sup>), at high energies (200 KeV) and at temperatures close to 600°C [5]. After implantation, very high temperature annealing (~ 1300°C) is required (Figure I-9) to restore film cristallinity.

Figure I-9: The principle of SIMOX: a heavy-dose oxygen implantation into silicon followed by a very high temperature annealing step produces a buried layer of silicon dioxide, below a thin single-crystal Si film [24].

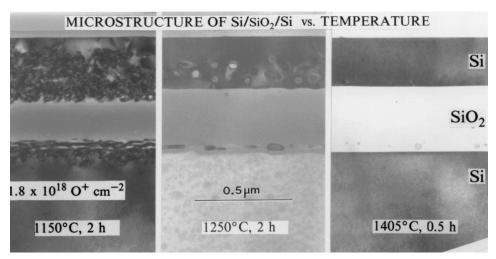

Figure I-10 shows the annealing impact by changing the time and by increasing the temperature (from 11150°C to 1250°C and then to 1405°C). The aim of this annealing is to induce the reaction between oxygen ions and silicon in order to form SiO<sub>2</sub>, to eliminate the high density of precipitates and residual defects and finally to obtain atomically sharp and planar interfaces between the near-surface regions of Si and the buried oxide (Figure I-10). A single-crystal but highly defective silicon overlayer (Si film) above the oxide is obtained.

Figure I-10: Evolution of SIMOX microstructure with annealing temperature and time [25].

The first wafers obtained by SIMOX technology with high implanted dose presented numerous crystalline defects in the active Si layer as well as numerous roads of BOX leakage, harmful defects for the good electric properties of the SOI. Several advances consisted in modifying the implanters to improve the crystalline quality of SIMOX substrate. Due to these advances and to the fact that the wafer cost is a strong function of the implant dose, the SIMOX "low dose" was achieved. The implant parameters, mainly the energy (120 KeV), dose ( $1-4 \times 10^{17}$  ions.cm<sup>-2</sup>) and temperature ( $600^{\circ}$ C), were used to improve and also to engineer the SIMOX structure and interface properties [5]. The lower oxygen dose needed implies a considerable gain in processing time and wafer cost. In addition, it enabled the drastic limitation of the dislocation density (reduced to  $10^{6}$  cm<sup>-2</sup>) in the Si layer (with thickness between 170 and 215 nm) [26]. A continuous planar buried oxide (between 80 and 200 nm thickness) was obtained. Low dose implantation has the benefit of reduced implantation damage and as a direct consequence fewer defects are present in the final annealed wafers [27].

In addition, it is possible to obtain thinner films and buried oxides [28] by variation of the oxygen implanted dose, energy and the annealing temperature. One concern with the thinner BOX is a higher probability of Si pipes that electrically short the Si film to the substrate. Another SIMOX process called ITOX (Internal Thermal OXidation) is effective in reducing the density of dislocations and Si pipes in the BOX [29]. By oxidizing an SOI wafer at 1350°C, a small fraction of the oxygen spreads through the Si film and re-acts at the film/BOX interface (instead of oxidizing the Si film). This internal oxidation ameliorates the quality of the SiO<sub>2</sub> with electrical properties comparable to those obtained from a thermal oxide.

SIMOX technology presents several disadvantages such as cost and processing time, crystalline defects, BOX quality and thickness scaling limitation of BOX and Si film, *etc*.

#### 2.2.2 SOI by wafer bonding

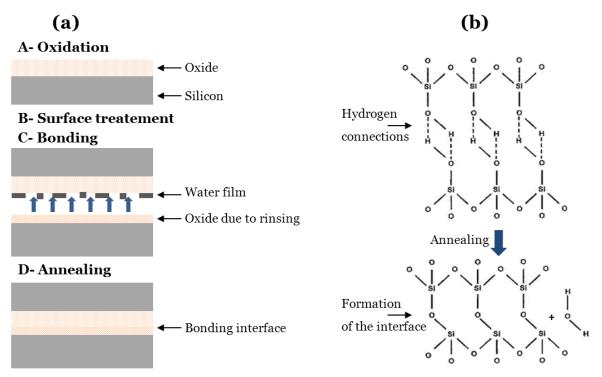

Wafer bonding (WB) is another mature SOI technology. It was first proposed in the 1980's at Bell laboratories and IBM ([30], [31]). Wafer bonding method consists in putting in contact two substrates having an excellent surface state [32]. It is then possible to bond Si-Si, SiO<sub>2</sub>-Si and SiO<sub>2</sub>-SiO<sub>2</sub>. In the case of the SOI (Figure I-11aA), we have one substrate with oxidized surface (which will represent later the insulator) and another substrate (with or without surface oxidation). Both substrates are cleaned in an RCA solution [33] followed by a water rinse in order to eliminate any possible contamination: particles, organic, or metallic (Figure I-11aB). The surface cleaning makes the non-oxidized substrate "hydrophilic" and water (H<sub>2</sub>O) molecules are able to fix on the surface during the rinsing. After putting in contact both substrates (Figure I-11aC), OH molecules related to the hanging connections of Si form a very thin film of water (~ 2 nm) by making hydrogen connections (Figure I-11b). A high-temperature stabilization annealing (for example, 1100°C for the standard Unibond), allows then to break the connections of Si-OH for the benefit of Si-O-Si connections (Si-O-H + H-O-Si  $\rightarrow$  Si-O-Si + H-O-H). After further heating of the samples a complete closure of the interface (Figure I-11b) occurs by coupling the remaining interface hydroxyl species and diffusion of the hydrogen into the Si (Figure I-11aD).

Figure I-11: Principle of the (a) hydrophilic bonding, (b) formation of interface bonding.

Generally, the bonding interface is placed below the BOX, far from the silicon film (where the components will be made).

The essential advantage of wafer bonding is to supply almost unlimited combinations of film and BOX thicknesses, which are attractive for the manufacturing of sensors and power circuits. On the other hand, its limitation is the practical difficulty to produce ultrathin films (< 100 nm), with uniform thickness, low stress, and excellent crystallinity. By using this principle of bonding, three techniques

were developed (described in the following sub-sections) as variants for the thinning down of the Si film.

#### 2.2.2.1 BESOI

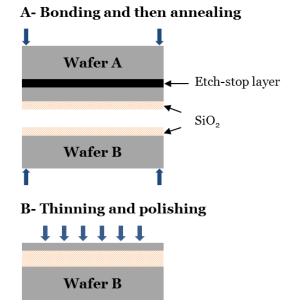

The Bond-and-Etch-back SOI (BESOI) technique relies on the hydrophilic bonding described previously. The specificity of this technique is the thinning down of the upper wafer, by mechanical polishing followed by mechanico-chemical polishing and/or by sacrificial oxidations (Figure I-12). Etch-stop layers can be introduced before bonding as for example a selective doping (junction  $P^+/P^-$  or P/N) or a different structure (SiGe, *etc.*) [32]. However, we to note that this technique presents disadvantages, in particular mechanical constraints and poor uniformity of the film thickness [3]. Thus, it is mainly used for the applications which require thick Si film (several micrometers thickness). Further, this method is relatively expensive because of the use of two wafers for the manufacturing of one SOI wafer.

*Figure I-12: Schematic representation of BESOI process. Bonding and annealing (A) of wafer A and wafer B are carried out, then the upper wafer A is thinned and polished (B) [5].*

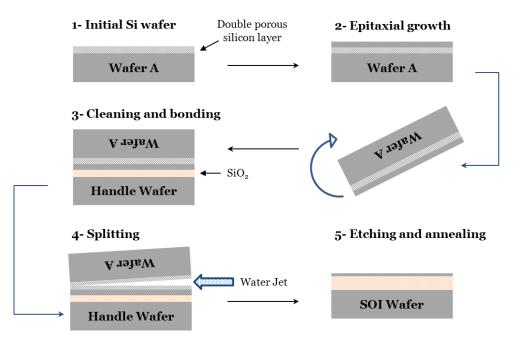

#### 2.2.2.2 ELTRAN

The Epitaxial Layer TRANsfer (ELTRAN) technique is another approach that combines the formation of a porous layer and wafer bonding to produce a material with good film thickness uniformity. This technique was developed by Canon in 1990 for the industrial production of SOI wafers [34]. A donor Si substrate 'Wafer A' undergoes an electrolytic attack making the Si surface porous (Figure I-13). Two successive epitaxial steps, first of porous silicon followed by single-crystal silicon allow forming a layer of non-porous silicon with high crystalline quality. The porous silicon wafer with the epitaxial layer film is then oxidized and bonded to another wafer 'Handle Wafer'. The fracture is made by means of a high-power water jet along the planar porous layers which are mechanically more fragile, leading to a more uniform cleavage. After wafers splitting, the residual porous Si on the SOI wafer is etched away, and the newly exposed SOI wafer surface is smoothed by a second application of hydrogen annealing at about 1100°C.

The wafer 'A' that donated the epitaxial film can be reclaimed, polished if necessary, and then reutilized. The crystal quality of the SOI material obtained by wafer bonding and etch-back is, in principle, as good as that of the starting silicon wafer. The control of film thickness is challenging.

Figure I-13: Schematic representation of ELTRAN process for SOI wafer manufacturing [34].

2.2.2.3 Unibond (Smart-Cut<sup>™</sup> process)

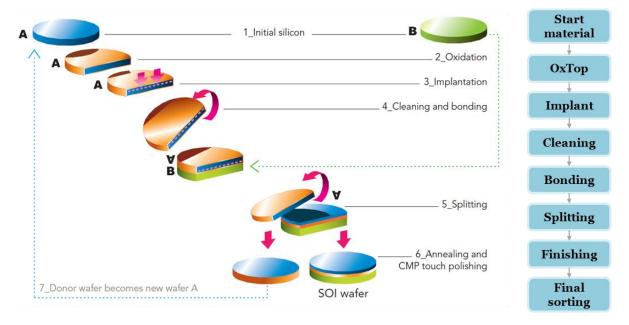

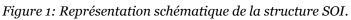

In the 1990s, a revolutionary process of wafer separation, named Smart-Cut<sup>TM</sup>, was invented by Michel Bruel from CEA-Leti (France-Grenoble) [35] and constitutes the technological exclusivity of the company Soitec (France-Bernin). The key step of the Smart-Cut<sup>TM</sup> process is the implantation of hydrogen for splitting the wafers (Figure I-14).

First the 'donor wafer' A undergoes a thermal oxidation to form an oxide which will serve as a BOX. Its thickness is easily adjustable by the control of oxidation. Then, a dose of hydrogen between  $3 \times 10^{16}$  and  $1 \times 10^{17}$  cm<sup>-2</sup> is implanted through this oxide. The hydrogen engenders micro-cavities (zone in dashed lines on Figure I-14). These are going to allow defining a plan of the fracture. The 'donor wafer' and 'Handle wafer' B are then cleaned to eliminate particles and contaminations on surface. This stage also allows returning both surfaces hydrophilic. The two wafers are aligned and putted in contact so that the bonding is made on the entire surface. During the bonding of wafers A and B (Figure I-14) and of the annealing that follows, the pressure of hydrogen molecules (H<sub>2</sub>) in micro-cavities increases. H<sub>2</sub> propagates then in micro-cavities and provokes a horizontal fracture which leads to a natural separation of wafers. This separation takes place, not at the bonding interface, but in the region defined by the localization of hydrogen micro-cavities.

Figure I-14: Schematic illustration of the fabrication steps for a standard Unibond SOI wafer with Smart-Cut<sup>TM</sup> process described by Soitec [36].

After this step, the surface roughness is of the order of some nanometers. It is important to underline that one of the advantages of this technique is to be able to reuse wafer A: the process is called "refresh".

To improve the crystalline quality of the transferred layer, some fracture processes use at present the co-implantation of hydrogen-helium. The implanted dose varies between  $2.5 \times 10^{16}$  and  $5 \times 10^{16}$  cm<sup>-2</sup>. Helium implanted after the hydrogen

fills the voids and provides most of the pressure that causes separation of a Si film from the bulk substrate. In addition, the helium improves the quality of the fracture. A better quality of the film and a reduction in the production cost are obtained.

The extraordinary potential of the Smart-Cut<sup>TM</sup> approach is evidenced by several essential key benefits [5]:

- i. The thinning step can be achieved without any limitations.

- ii. The donor wafer (A) undergoes only the removal of a thin Si surface layer and can be recycled several times. The quality of this mother wafer must be excellent, while that of the wafer B, used primarily for mechanical support, is not critical. Therefore, the Smart-Cut<sup>TM</sup> is almost mono-wafer, with a low cost for the wafer B. This translates into competitive production costs.

- iii. Conventional implantation and annealing equipments are used, even for the manufacturing of 12 inch wafers, which is not the case of SIMOX where only maximum 8 inch wafers can be obtained.

- iv. The silicon film and the BOX thicknesses are adjustable (*via* the implantation energy of hydrogen and oxidation time) in a wide range  $(t_{Si} = 0.01 \text{ to } 1.5 \text{ microns and } t_{BOX} = 0.01 \text{ to } 5 \text{ microns})$  in order to adapt to most architectures of integrated components: ultra-thin CMOS, power transistors or sensors with thick films.

- v. The crystal quality, defect density and characteristics of the Si film are excellent, while the buried oxide keeps the usual properties of the thermal oxide. The fact that the bonding interface is below the BOX improves the Si film quality.

The Smart-Cut<sup>™</sup> wafer manufacturing technology gives Soitec the flexibility to tailor SOI substrates to meet most demanding design specifications and to cover the full range of applications for microelectronics markets (Figure I-15). Note that the Smart-Cut<sup>™</sup> is universal in the sense of adaptability to a variety of materials. These new products (showed in the next section) allow Soitec to answer the expectation of the microelectronics market subjected to the technological nodes defined by the ITRS (International Technology Roadmap for Semiconductors) and to invest new market shares still dominated by the Si bulk technology.

*Figure I-15: Soitec's Unibond SOI wafers with wide flexibility in top Si and buried oxide thicknesses to meet the industry's most rigorous requirements [37].*

#### 2.2.3 Silicon-On-Nothing (SON)

The Silicon-On-Nothing (SON) technology was invented in 2000 to realize localized SOI regions favoring the cohabitation of SOI and bulk Si circuits [38]. On a isolated bulk wafer, is epitaxied in predefined regions, a stack of sacrificial SiGe and Si layers. The selective etching of the SiGe leaves a vacuum ('Nothing') under the Si film. This space is filled by a dielectric to form "integrated" SOI in silicon. The thin layer of Si can also be used for the fabrication of Gate-All-Around transistors. The SON process allows the buried dielectric (which may be an oxide but also an air gap) to be fabricated locally in dedicated parts of the chip, which may present advantages in terms of cost and facility of System-On-Chip integration.

The innovative SON process enables fabrication of SOI-like structures on bulk substrates with well-controlled and extremely thin buried oxide (10 to 30 nm) and silicon films (5 to 20 nm). The very thin layers in the SON transistor allow good control of the short-channel effects (SCEs) and excellent electrical performances [38].

#### 2.2.4 Other SOI technologies

#### 2.2.4.1 Silicon-On-Sapphire

The Silicon-On-Sapphire (SOS) is the godfather of the SOI family. The epitaxial growth of a silicon film on a bulk sapphire  $(Al_2O_3)$  substrate gives rise to

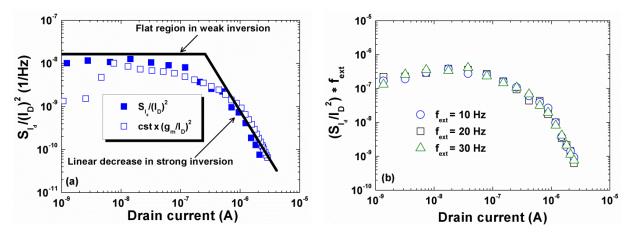

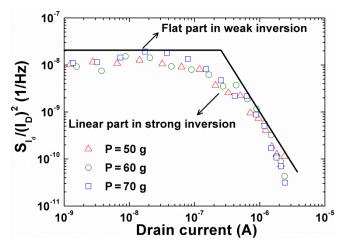

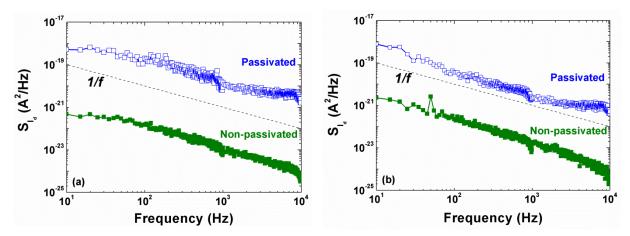

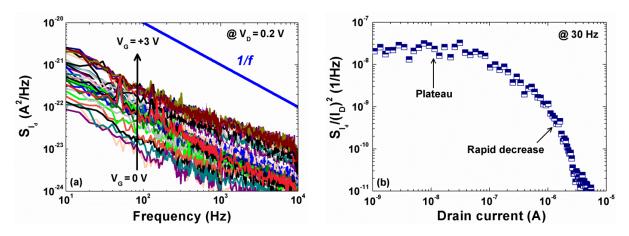

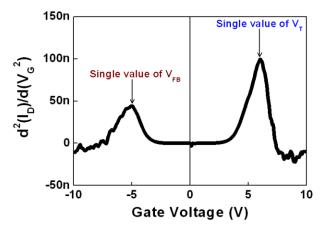

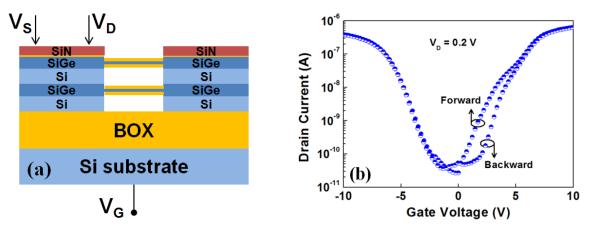

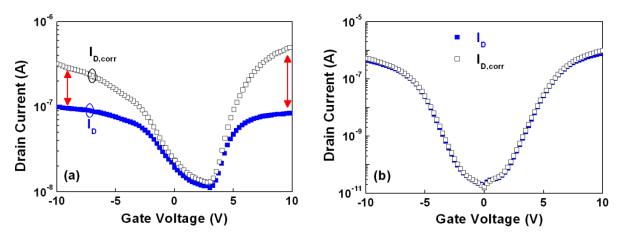

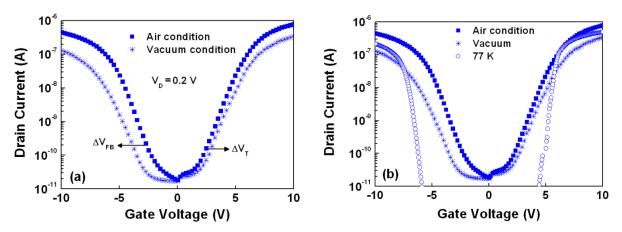

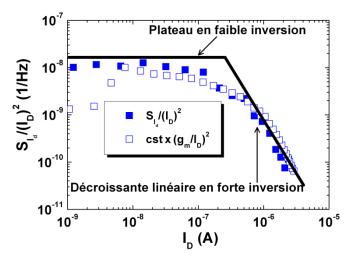

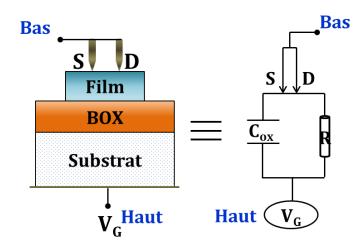

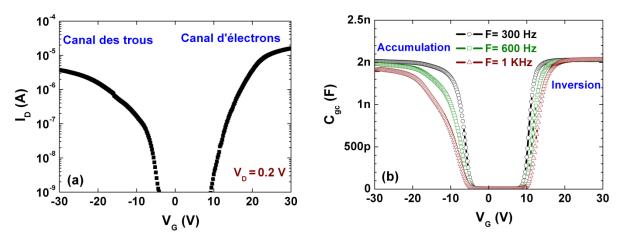

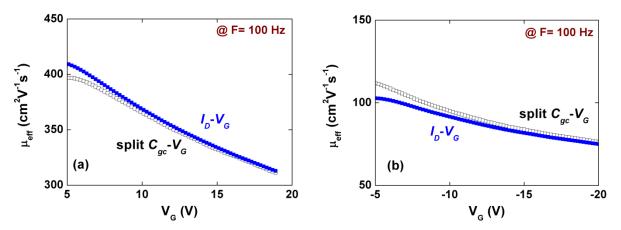

small Si islands that finally coalesce. The interface transition region contains numerous crystallographic defects, mainly stacking faults, due to the lattice mismatch and aluminum contamination from the sapphire substrate. The electrical properties are affected by the lateral stress, difference in thermal expansion, in depth inhomogeneity of SOS films, and interface traps [20].