# Co-design of integrated Power Amplifier-Antenna Modules on Silicon Technologies for the Optimization of Power Efficiency

Juan Pablo Guzman Velez

#### ▶ To cite this version:

Juan Pablo Guzman Velez. Co-design of integrated Power Amplifier-Antenna Modules on Silicon Technologies for the Optimization of Power Efficiency. Electromagnetism. Télécom Bretagne, Université de Bretagne Occidentale, 2013. English. NNT: . tel-00794765

# HAL Id: tel-00794765 https://theses.hal.science/tel-00794765

Submitted on 26 Feb 2013

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

N° d'ordre : 2013telb0266

#### Sous le sceau de l'Université Européenne de Bretagne

# Télécom Bretagne

En habilitation conjointe avec l'Université de Bretagne Occidentale

École Doctorale - SICMA

# Co-design of integrated PA (Power Amplifier) - Antenna Modules on silicon Technologies for the optimization of power efficiency

#### Thèse de Doctorat

Mention : Sciences pour l'Ingénieur

Présentée par Juan Pablo Guzman

Département : Micro-ondes

Laboratoire: Lab-STICC - Pôle: Micro-ondes, Optoélectronique et Matériaux

Directeurs de thèse : Christian Person, Michel Ney

Soutenue le 23 Janvier 2013

#### Jury:

#### **Rapporteurs**

M. Christophe Delavaud

M. Ronan Sauleau

**Examinateurs**

M. Yves Quere

M. Eric Kerherve M. Michel Ney M. Christian Person

Invités

M. Christophe Calvez M. Romain Pilard

- Ingénieur R&D HDR, CEA LETI

- Professeur, Université de Rennes 1, IETR

- Maître de Conférences, Université de Bretagne Occidentale, LabSTICC

- Professeur, Université de Bordeaux, IMS - Professeur, Télécom Bretagne, Lab-STICC

- Professeur, Télécom Bretagne, Lab-STICC

- Ingénieur R&D, Autocruise-TRW, Plouzané - Ingénieur R&D, ST Microelectronics, Crolles

#### Acknowledgments

First of all, I would like to express my thanks to Christian Person and Michel Ney for their invaluable support and guidance

Next, I would like to thank all examiners for taking their time to read and evaluate my thesis. I would also like to show my appreciation to Christophe Calvez and Shoaib Muhammad as encouraging partners who help me at some stages of my thesis and provided valuable inputs.

Prototype fabrication and measurement were also very important and for this matter I can't skip thanking Guy Chuiton, Raymond Jezequel, Serge Pinel, Camilla Karnfelt and Pascal Coant.

I would also like to thank Nejdat Demirel, Nathalie Deltimple and Eric Kerherve from IMS Bordeaux, for their help concerning the Power Amplifier presented in this thesis and for their welcome at my short but pleasant stay at IMS labs.

And last but not least, all the people at "Département Micro-ondes", in Telecom Bretagne and at Brest, with whom the daily life would not have been the same.

# **Table of Contents**

| Rés | sumé  |             |                                                                    | 1        |

|-----|-------|-------------|--------------------------------------------------------------------|----------|

| 1)  | Co    | ntex        | te et Application                                                  | I        |

| 2)  | Éta   | t de        | l'art des systèmes dans la bande 60 GHz                            | III      |

| 3)  | Sol   | utio        | n antenne SoC → vers l'amélioration du rendement global du système | IV       |

| 4)  | Sol   | utio        | n antenne SiP → vers des solutions de haut gain                    | IX       |

| 5)  | An    | tenn        | e doublement alimentée pour une amélioration du rendement du PA    | . XIII   |

| 6)  | Co    | nclus       | ions Générales                                                     | . XVI    |

| 7)  | Tra   | ıvau        | cà réaliser dans le futur                                          | XVII     |

| Gei | neral | l Int       | roduction                                                          | <b>1</b> |

| Cho | aptei | r 1 -       | State of the Art of 60 GHz Transmission Systems                    | 1        |

| 1)  | Int   | rodu        | ction                                                              | 1        |

| 2)  | The   | e <b>60</b> | GHz band and its opportunities                                     | 2        |

|     | 2.a)  | The         | 60 GHz band and its regulation                                     | 2        |

|     | 2.b)  | Unl         | icensed Band, what does this imply                                 | 3        |

|     | 2.c)  | Wh          | y the 60 GHz band?                                                 | 3        |

|     | 2.d)  | App         | lications                                                          | 5        |

|     | 2.e)  |             | enuation factors (losses in the 60 GHz band)                       |          |

|     | 2.f)  |             | Budget                                                             |          |

|     | 2.g)  |             | nmercially Available Solutions at 60 GHz                           |          |

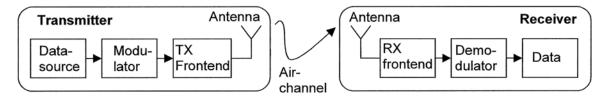

| 3)  | Ge    |             | Transmission Chain and Front End location                          |          |

|     | 3.a)  |             | nplete Tx-Rx Chain                                                 |          |

|     | 3.b)  |             | hnological Possibilities                                           |          |

|     |       | -           | Silicon → Bulk or SOI (Silicon on Insulator)?                      |          |

|     | 3.b   | ,           | Active Devices: the transistor                                     |          |

|     | 3.c)  |             | sive Devices: Transmission Lines, Inductors and Capacitors         |          |

|     | 3.c   | ,           | Transmission lines:                                                |          |

| ح.  | 3.c   | •           | Inductances and Capacitors                                         |          |

| 4)  |       |             | Amplifiers                                                         |          |

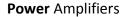

|     | 4.a)  |             | distortion sources                                                 |          |

|     | 4.a   | ,           | How to measure the performance of a PA?                            |          |

|     | 4.a   | •           | PA Topologies                                                      |          |

|     | 4.b)  | ιyp         | ical PA amplification curve                                        | ∠ /      |

|     | 4.c)  | PA    | Stages                                         | 28   |

|-----|-------|-------|------------------------------------------------|------|

|     | 4.0   | :.i)  | PA impedance matching stages                   | 28   |

|     | 4.d)  | PA    | State of the Art                               | 30   |

| 5   | ) An  | tenn  | a in the 60 GHz band                           | 32   |

|     | 5.a)  | Ant   | enna Performance                               | 33   |

|     | 5.a   | a.i)  | System on Chip or SoC                          | 33   |

|     | 5.a   | a.ii) | System in Package or SiP                       | 40   |

| 6   | ) Fro | ont-E | nd Transmitters (Whole Tx chain)               | 49   |

| 7   | ) Co  | nclus | sions                                          | 52   |

| Ch  | apte  | r 2   | - Integrated Silicon based antenna: toward SoC | (Co- |

| int | egra  | tion  | and Co-design Scenarios)                       | 53   |

| 1   | ) Th  | e 60  | GHz Power Amplifier on SOI                     | 53   |

|     | 1.a)  | РА    | on SOI description                             | 53   |

|     | 1.b)  | PA    | Performance                                    | 54   |

|     | 1.c)  | Cor   | nprehensive analysis of the PA                 | 56   |

|     | 1.d)  | Co-   | integration and Co-design scenarios            | 57   |

|     | 1.0   | (i.b  | Co-integration scenario                        | 57   |

|     | 1.0   | d.ii) | Co-design scenario                             | 57   |

| 2   | ) An  | tenn  | a design for Co-Integration                    | 58   |

|     | 2.a)  | Slot  | t on an infinite ground plane (no substrate)   | 58   |

|     | 2.b)  | Lov   | vering the input impedance                     | 59   |

|     | 2.c)  | Slot  | t on a finite ground plane (no substrate)      | 62   |

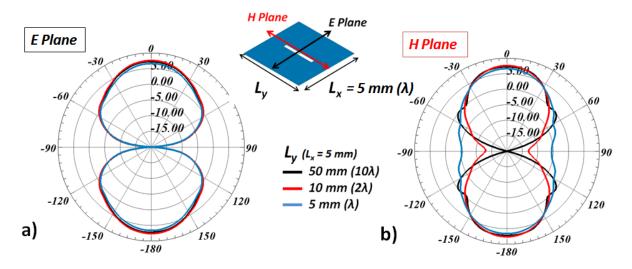

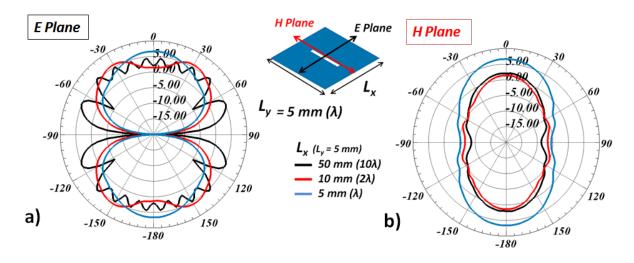

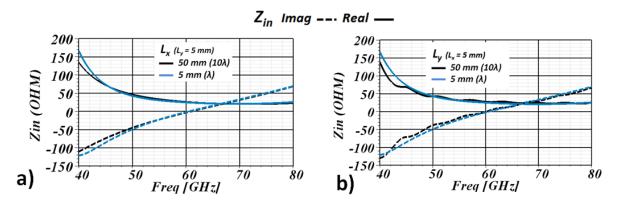

|     | 2.0   | c.i)  | Size study of finite ground                    | 63   |

|     | 2.d)  | Add   | ding the substrate                             | 65   |

|     | 2.0   | (i.b  | W <sub>slot</sub> as impedance controller      | 65   |

|     | 2.0   | (ii.b | Ground size as impedance controller            | 66   |

|     | 2.e)  | Fina  | al 50 $\Omega$ antenna configuration           | 69   |

|     | 2.€   | e.i)  | Radiation performance                          | 71   |

| 3   | ) An  | tenn  | a Design for Co-design with PA                 | 73   |

|     | 3.a)  | Tra   | nsistor output stage configuration             | 73   |

|     | 3.b)  | A 1   | 5 $\Omega$ input impedance antenna             | 74   |

|     | 3.c)  | Fina  | al Antenna configuration                       | 77   |

| 4   | ) Glo | obal  | energy budget                                  | 78   |

| 5   | 50    | Ω Αι  | ntenna Measurement                             | 79   |

|     | 5.a)  | S11   | . Measurement                                  | 80   |

| 5                                      | 5.b)                                                                       | Gaiı                                                       | n Measurement                                                                                                                                                                                                                                                                                                                                     | 83                                   |

|----------------------------------------|----------------------------------------------------------------------------|------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|

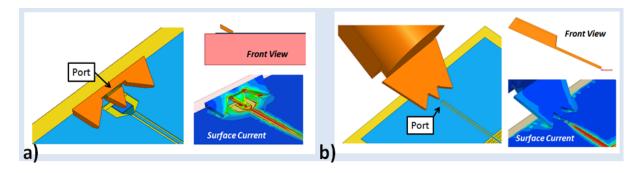

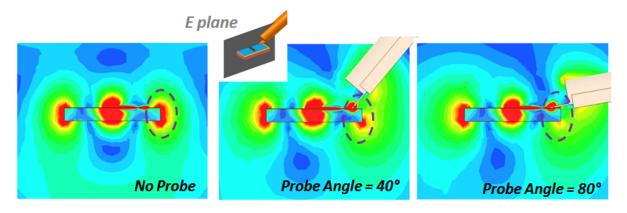

| 5                                      | 5.c)                                                                       | Pro                                                        | be angle incidence                                                                                                                                                                                                                                                                                                                                | 86                                   |

|                                        | 5.c                                                                        | .i)                                                        | Probe coupling: broadside or backside effect?                                                                                                                                                                                                                                                                                                     | 88                                   |

|                                        | 5.c                                                                        | .ii)                                                       | Probe distance                                                                                                                                                                                                                                                                                                                                    | 90                                   |

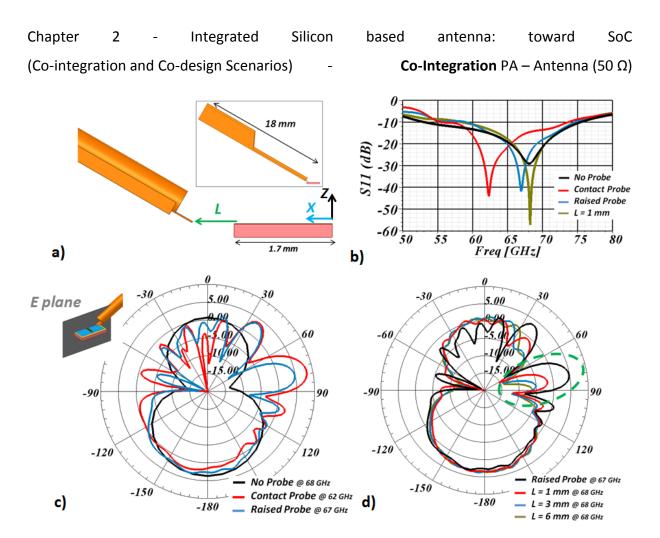

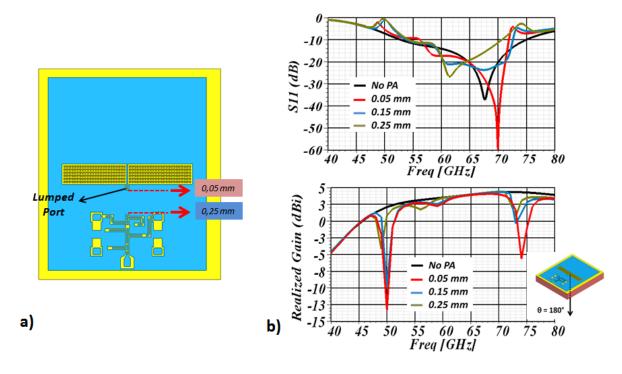

| 6)                                     | Co-                                                                        | -Inte                                                      | gration PA – Antenna (50 Ω)                                                                                                                                                                                                                                                                                                                       | 91                                   |

| 6                                      | 5.a)                                                                       | Sim                                                        | ulation of Co-integrated PA + Antenna                                                                                                                                                                                                                                                                                                             | 92                                   |

|                                        | 6.a                                                                        | .i)                                                        | Parametric study PA – Slot distance                                                                                                                                                                                                                                                                                                               | 92                                   |

|                                        | 6.a                                                                        | .ii)                                                       | The PA coupled resonating elements                                                                                                                                                                                                                                                                                                                | 94                                   |

| 7)                                     | Co-                                                                        | -desi                                                      | gn of PA and Antenna (15 $\Omega$ )                                                                                                                                                                                                                                                                                                               | 97                                   |

| 8)                                     | Me                                                                         | easur                                                      | ing Integrated PA-Antenna                                                                                                                                                                                                                                                                                                                         | 98                                   |

| 8                                      | 3.a)                                                                       | Sup                                                        | port Selection                                                                                                                                                                                                                                                                                                                                    | 99                                   |

| 8                                      | 3.b)                                                                       | S11                                                        | Measurement                                                                                                                                                                                                                                                                                                                                       | 100                                  |

|                                        | 8.b                                                                        | .i)                                                        | Measurement bench description (45 to 75 GHz)                                                                                                                                                                                                                                                                                                      | 101                                  |

|                                        | 8.b                                                                        | ii)                                                        | S11 Measurement                                                                                                                                                                                                                                                                                                                                   | 103                                  |

| 8                                      | 3.c)                                                                       | Sup                                                        | port impact on Antenna performance                                                                                                                                                                                                                                                                                                                | 104                                  |

| 8                                      | 3.d)                                                                       | Gaiı                                                       | n Measurements                                                                                                                                                                                                                                                                                                                                    | 108                                  |

| 9)                                     | Coi                                                                        | nclus                                                      | ions                                                                                                                                                                                                                                                                                                                                              | 111                                  |

| CI                                     |                                                                            |                                                            | Dialactria Dagametar Antonner CiD calutions for a                                                                                                                                                                                                                                                                                                 |                                      |

| Lnap                                   | oter                                                                       | ' 3 I                                                      | Dielectric Resonator Antenna: SiP solutions for e                                                                                                                                                                                                                                                                                                 | enhanced                             |

| •                                      |                                                                            |                                                            | ce                                                                                                                                                                                                                                                                                                                                                |                                      |

| •                                      | orm                                                                        | nan                                                        | -                                                                                                                                                                                                                                                                                                                                                 | 112                                  |

| erf                                    | orm<br>Int                                                                 | <i>nan</i><br>rodu                                         | ce                                                                                                                                                                                                                                                                                                                                                | 112<br>112                           |

| 1)<br>2)                               | orm<br>Int                                                                 | n <i>an</i><br>rodu<br>e die                               | ction:                                                                                                                                                                                                                                                                                                                                            | 112<br>112<br>112                    |

| 1)<br>2)                               | orm<br>Int                                                                 | rodu<br>e die                                              | ction:lectric resonator antenna or DRA                                                                                                                                                                                                                                                                                                            | 112112112113                         |

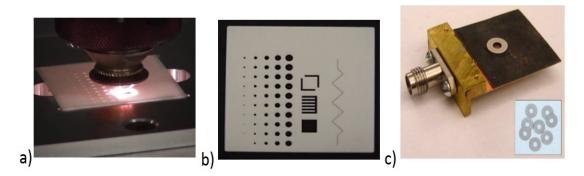

| 2)                                     | Internal                                                                   | rodu<br>rodu<br>e die<br>DRA<br>Fab                        | ction:                                                                                                                                                                                                                                                                                                                                            | 112112112113116                      |

| 2)                                     | Into<br>Into<br>The<br>P.a)                                                | rodu<br>rodu<br>e die<br>DRA<br>Fab<br>Hov                 | ction: lectric resonator antenna or DRA A state of the art rication of Dielectric Resonator Antennas                                                                                                                                                                                                                                              | 112112112113116                      |

| 2)                                     | Internal The Page 12. (a) Page 12. (b) Page 12. (c)                        | rodu<br>rodu<br>e die<br>DRA<br>Fab<br>Hov                 | ction: lectric resonator antenna or DRA A state of the art rication of Dielectric Resonator Antennas v does the DRA works                                                                                                                                                                                                                         | 112112113116119                      |

| 2)                                     | Internal (1) (1) (1) (1) (1) (1) (1) (1) (1) (1)                           | rodu<br>e die<br>DRA<br>Fab<br>Hov<br>.i)                  | ction:  lectric resonator antenna or DRA  A state of the art  rication of Dielectric Resonator Antennas                                                                                                                                                                                                                                           | 112112113116119123                   |

| 2) 2 2 2                               | Internal (1) (1) (1) (1) (1) (1) (1) (1) (1) (1)                           | rodu<br>e die<br>DRA<br>Fab<br>Hov<br>.i)                  | ction:  lectric resonator antenna or DRA                                                                                                                                                                                                                                                                                                          | 112112113116119123                   |

| 2) 2 2 2                               | Internal (1) (1) (1) (1) (1) (1) (1) (1) (1) (1)                           | rodu<br>e die<br>DRA<br>Fab<br>Hov<br>.i)<br>.ii)          | ction:  lectric resonator antenna or DRA                                                                                                                                                                                                                                                                                                          | 112112113116119123123                |

| 2) 2 2 2                               | Internal (1) (1) (1) (1) (1) (1) (1) (1) (1) (1)                           | rodu<br>e die<br>DRA<br>Fab<br>Hov<br>.i)<br>.ii)<br>.iii) | ction:  lectric resonator antenna or DRA                                                                                                                                                                                                                                                                                                          | 112112113116119123123125             |

| 2) 2 2 2                               | Internal (1.a) (2.b) (2.c) (2.c) (2.c) (2.d) (2.d) (2.d)                   | rodu<br>e die<br>DRA<br>Fab<br>Hov<br>.i)<br>.ii)<br>.iii) | ction:  lectric resonator antenna or DRA  A state of the art  rication of Dielectric Resonator Antennas  v does the DRA works  Resonant modes in a cylindrical DR.  Mode selection  Resonance frequency of the TM₁1  ecting the excitation element  DR + Slot → Initial performances                                                              | 112112113116119123123125126          |

| 2) 2 2 2 2 2                           | Internal (1.a) (2.b) (2.c) (2.c) (2.c) (2.d) (2.d) (2.d)                   | rodu e die DRA Fab Hov .ii) .iii) Sele l.ii)               | ction:  lectric resonator antenna or DRA.  A state of the art                                                                                                                                                                                                                                                                                     | 112112113116119123125126127          |

| 2) 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 | Internal (1.a) (2.b) (2.c) (2.c) (2.c) (2.d) (2.d) (2.d) (2.d) (2.d) (2.d) | rodu e die DRA Fab Hov .i) .ii) .iii) Sele l.ii) l.iii)    | ction:  lectric resonator antenna or DRA  A state of the art  rication of Dielectric Resonator Antennas  v does the DRA works  Resonant modes in a cylindrical DR.  Mode selection  Resonance frequency of the TM <sub>11</sub> ecting the excitation element  DR + Slot → Initial performances  Finite ground plane effect  The substrate effect | 112112113116119123125126127130       |

| 2) 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 | Internal (1.a) (2.b) (2.c) (2.c) (2.d) (2.d) (2.d) (2.d) (2.d) (2.e)       | rodu e die DRA Fab Hov .ii) .iii) Sele l.ii) DRA DRA       | ction:  lectric resonator antenna or DRA                                                                                                                                                                                                                                                                                                          | 112112113116119123125125126127129130 |

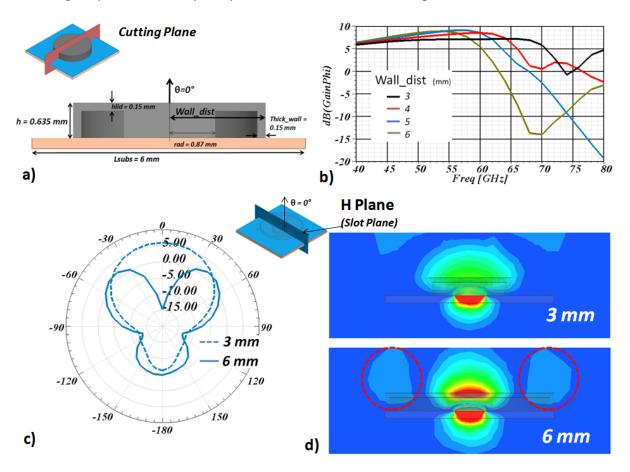

| 2.1                   | h.i) DR position shift impact                                     | 134 |

|-----------------------|-------------------------------------------------------------------|-----|

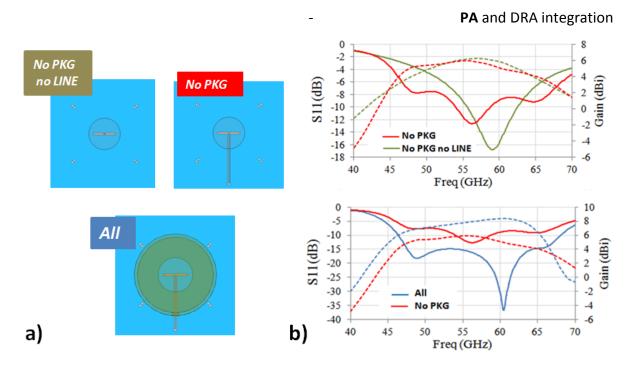

| 3) PA                 | A and DRA integration                                             | 136 |

| 3.a)                  | 1 <sup>st</sup> DR incorporated in Package solution               | 138 |

| 3.a                   | a.i) Conclusions                                                  | 141 |

| 3.b)                  | 2nd packaged solution $ ightarrow$ solving the DR alignment issue | 141 |

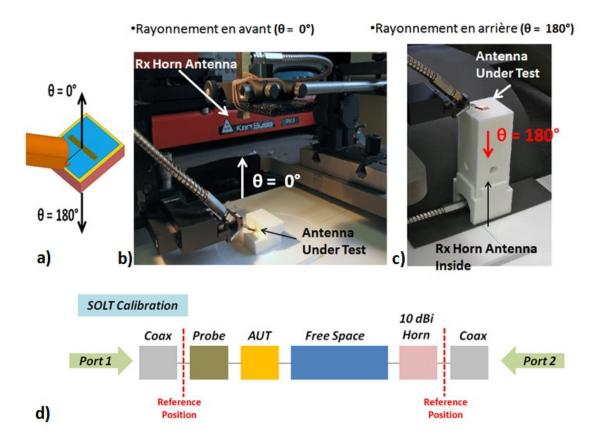

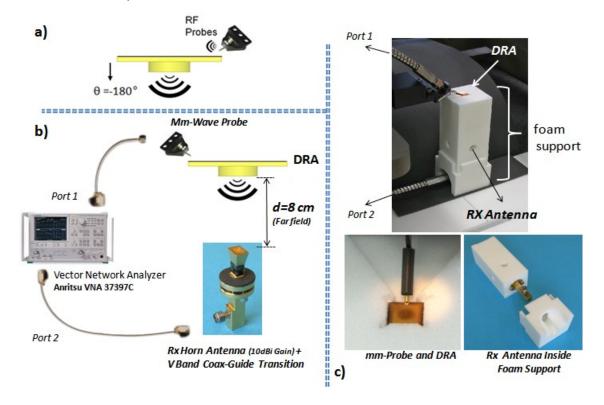

| 3.1                   | b.i) Backside radiation measurement bench                         | 144 |

| 3.1                   | b.ii) Measurement results                                         | 145 |

| 3.1                   | b.iii) Silicon Chip integration                                   | 146 |

| 3.1                   | b.iv) Conclusions                                                 | 149 |

| 3.c)                  | 3rd packaged solution → completely packaged solution              | 150 |

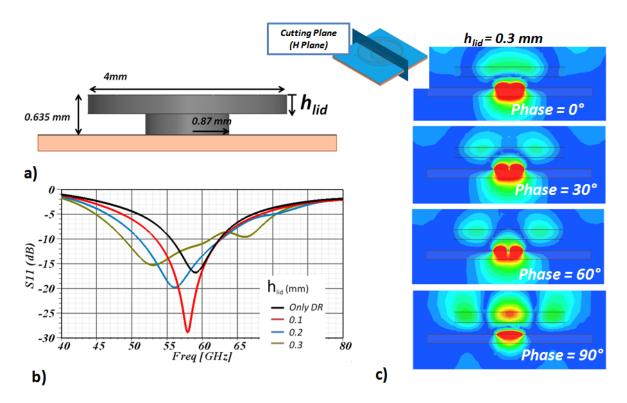

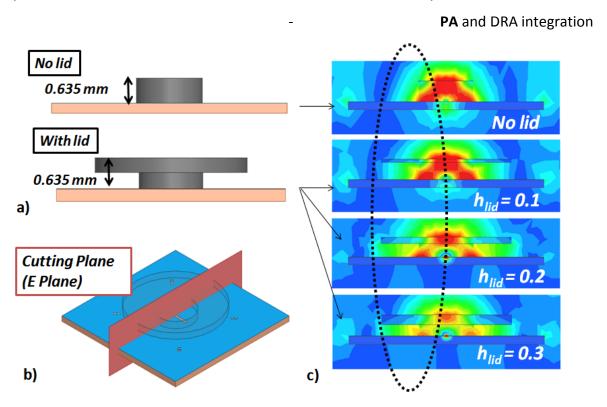

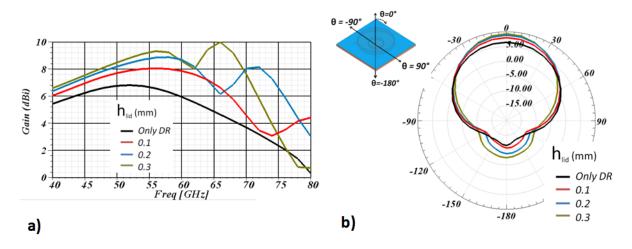

| 3.0                   | c.i) The lid effect                                               | 152 |

| 3.0                   | c.ii) The wall effect                                             | 155 |

| 3.0                   | c.iii) The CPW coupling mechanism                                 | 156 |

| 3.d)                  | 4 <sup>th</sup> solution → eliminating interconnections           | 161 |

| 4) Co                 | onclusions                                                        | 166 |

| _                     | r 4 - Multi-feed antenna for PA-Antenna<br>ement                  |     |

|                       | troduction                                                        |     |

| •                     | ulti PA solution                                                  |     |

| 2, ivi                | Multi-feed antenna for Multi-PA solution                          |     |

| 2.a)<br>2.b)          | Coupling constraint                                               |     |

| 2.c)                  | Vectorial addition                                                |     |

| 2.d)                  | The impact of field rotation                                      |     |

| ,                     | RA for multi-feed PA-antenna solutions                            |     |

| 3.a)                  | Multiple lateral DR feed configuration                            |     |

| ,                     | dapted feed for multi-fed DRA                                     |     |

| 4.a)                  | HTCC Packaging technology                                         |     |

| 4.b)                  | DR Multilayer Fabrication                                         |     |

| 4.c)                  | Single Feed Waveguide Fed DR                                      |     |

| 4.a)                  | Waveguide to SIW                                                  |     |

| 4.b)                  | Waveguide dimensioning and performance                            |     |

| 4.c)                  | Multi feed DR                                                     |     |

| 4.d)                  | SIW excitation                                                    | 188 |

| 4.e)                  | PA incorporation constraints                                      | 191 |

| <b>5</b> \ <b>6</b> - |                                                                   |     |

| 5) Co                 | onclusions                                                        | 194 |

| General Conclusions | 195 |

|---------------------|-----|

| Future Work         | 197 |

| References          | 198 |

| Publications        | 205 |

# Résumé

## 1) Contexte et Application

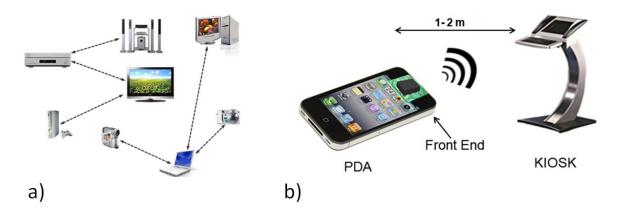

Dans le cadre des communications numériques sans fil, la vitesse d'échange de données (débit) reste toujours une des caractéristiques qui limite la performance du système. Une diminution des temps d'échange est donc nécessaire pour l'amélioration de la performance et l'introduction des nouvelles applications. Celles comme « Wireless HD » rendent possible la transmission sans fil de vidéo non-compressée » à haute définition (débit = 4 Gbps) « Kiosk Downloading » permettrait l'échange de données à haut débit (1-2 Gbps) sur une courte portée (1-2 m).

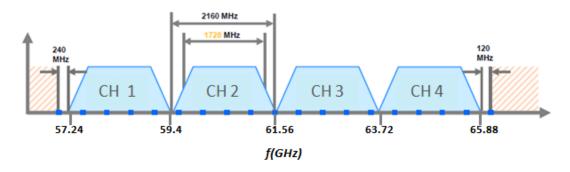

Selon Shannon (Eq. 1), la capacité du canal (débit) dépend du niveau de bruit dans le canal (S/N) ainsi que de la bande passante disponible (B). Prenant ce dernier en compte, une bande passante plus importante, disponible sur la bande 60 GHz (7 GHz), devrait augmenter le débit par rapport aux solutions existantes.

$$C = B \times log_2 \left(1 + \frac{s}{N}\right)$$

Eq. 1

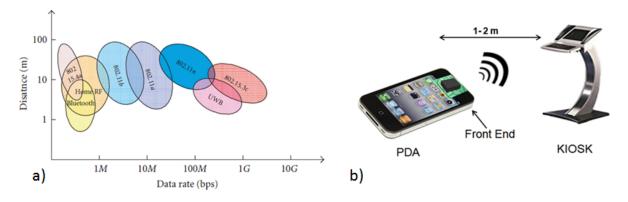

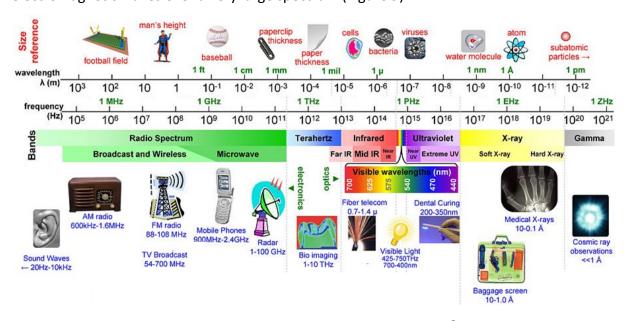

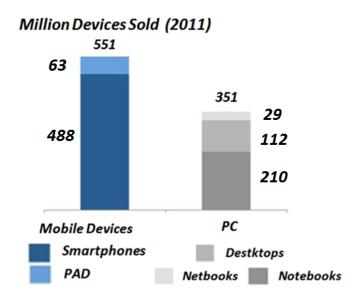

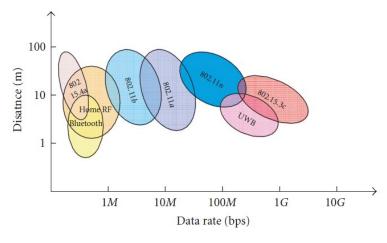

Le débit de plusieurs protocoles est montré à la Figure 1 a). On peut repérer une augmentation du débit entre différents standards; par exemple, Bluetooth (< 1 Mbps), Wifi ou 802.11 (10-100 Mbps) ou 802.15.3c (< 1 Gbps). En partie cela peut être expliqué par la bande passante attribuée à chaque standard: Bluetooth (1 MHz), Wi-Fi (22 MHz) et 802.15.3c (2.1 GHz). Il faut noter que cette bande passante est par canal et ne couvre pas toute la bande attribuée aux standards. Avec un débit si important, comme c'est le cas de 802.15.3c (1 Gbps), on pourrait envisager des solutions de transmission numérique de vidéo rapide. Par exemple, un téléchargement d'un film (qualité DVD  $\approx 5$  Gb) en quelques instants (5 s). Une nouvelle façon pour l'utilisateur d'emprunter des films. Il devra juste se rendre à un kiosque avec son PDA (Personal Digital Assistant) et réaliser le téléchargement en quelques secondes. C'est ce qu'on appelle « Kiosk Downloading » et c'est l'application visée dans ce travail.

Figure 1: a) Débits et besoins pour les standards WLAN et WPAN. [1] b) Application "Kiosk Downloading"

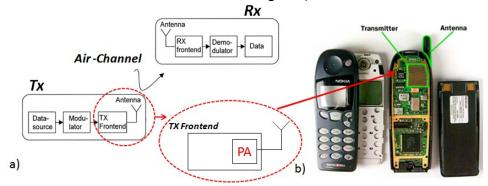

L'introduction de l'application visée permet de repérer les trois éléments qui constituent la liaison de communication : le transmetteur (PDA), le récepteur (Kiosk) et entre eux, l'interface aérienne. Dans cette thèse, les efforts vont être centrés sur le transmetteur, et plus spécifiquement sur les derniers éléments de la chaine de transmission (Figure 2): le PA (Amplificateur de Puissance selon l'abréviation anglaise) et l'antenne.

Figure 2 : a) Les trois composants de la chaine de Tx-Rx (Transmetteur – Air – Récepteur) [2] and b) Module Transmetteur-Antenne d'un téléphone portable <sup>1</sup>

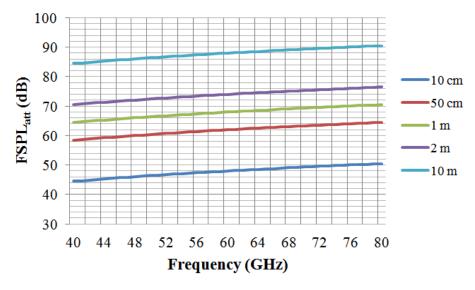

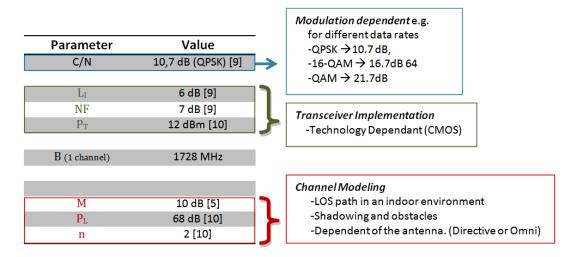

Toutefois, les solutions PA-Antenne du transmetteur vont être soumises aux contraintes liées à l'interphase aérienne. Parmi elles, une des plus importantes pour le système transmetteur est l'atténuation de l'énergie à 60 GHz due à l'espace libre. Elle atteint – 74 dB (2 m de séparation entre récepteur et transmetteur) qui devra être compensé par le gain des éléments actifs (PA) et l'antenne. En fait, un niveau maximum de gain est imposé pour le PA de 13.7 dBm (en Europe) limitant sa contribution pour le gain du système (Tx) global et imposant un gain de 6 – 7 dBi pour l'antenne. Cette valeur a été obtenue en prenant en compte les niveaux de bruit du système ajoutés par les différents composants de la chaine (i.e. bruit thermique, codage, bruit dans le récepteur etc.).

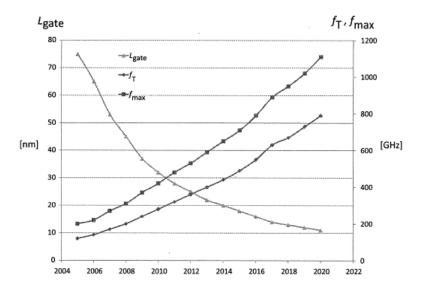

#### 1.b.) Choix technologique

La réalisation des éléments actifs (transistors) qui comprennent le PA ont besoin d'un substrat semi-conducteur. La sélection parmi les semi-conducteurs existants (Si, GaAs ou InP) dépend en grand partie de contraintes comme le prix et la fréquence de fonctionnement. D'un côté, le silicium offre un prix de fabrication plus bas par rapport aux autres technologies. Et cette différence de coût devrait augmenter, dû aux investissements faits ces dernières années autour du silicium [2]. D'un autre coté, la fréquence d'opération a été un des facteurs avantageant le silicium. Mais ce n'est plus le cas. Selon l'ITRS (International Technology Roadmap for Semiconductors), le silicium peut dès maintenant rivaliser avec les autres technologies même au-delà des 100 GHz [3]. C'est donc le silicium qui permettra d'obtenir une solution bas coût et également performante.

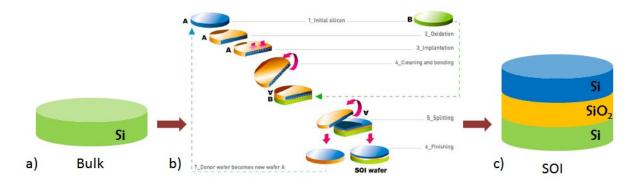

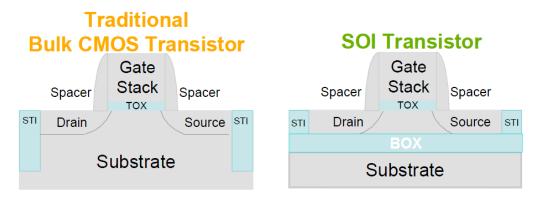

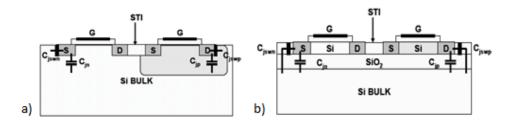

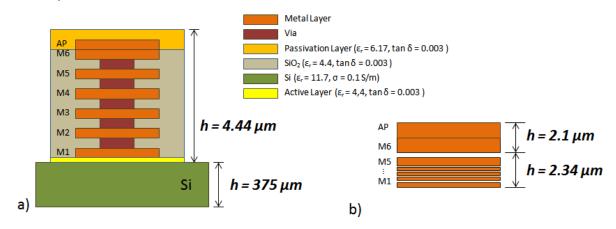

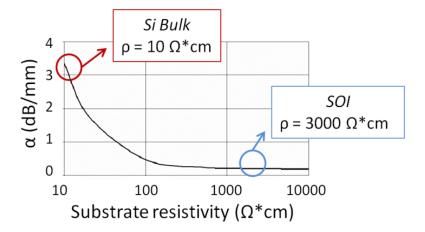

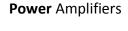

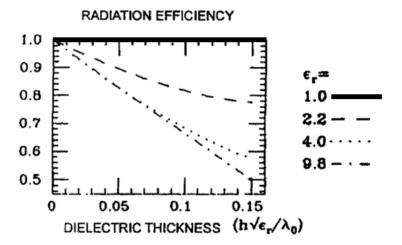

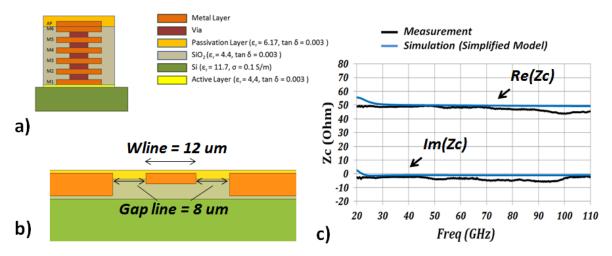

Le silicium, lui aussi, offre deux possibilités. Il existe le Si Bulk qui présente une résistivité au niveau du substrat de  $10~\Omega$  cm et le Si SOI avec  $3000~\Omega$  cm. Cette différence a un grand effet notamment sur l'efficacité du système. Comme exemple, l'atténuation d'une ligne coplanaire (CPW) est montrée dans la Figure 30. Une différence de 3 dB peut être aperçue pour la ligne entre le "Bulk" et le SOI. Par conséquent, le SOI a été choisi.

-

<sup>&</sup>lt;sup>1</sup> http://www.electronics.howstuffworks.com

# 2) État de l'art des systèmes dans la bande 60 GHz

L'étude de l'état de l'art des systèmes dans la bande 60 GHz a été divisée en deux parties, une dédiée au PA et l'autre aux antennes.

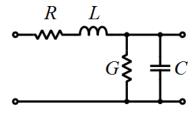

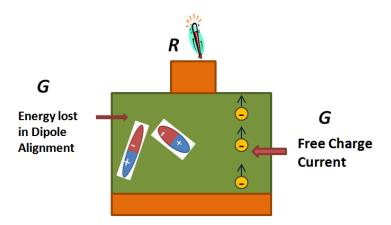

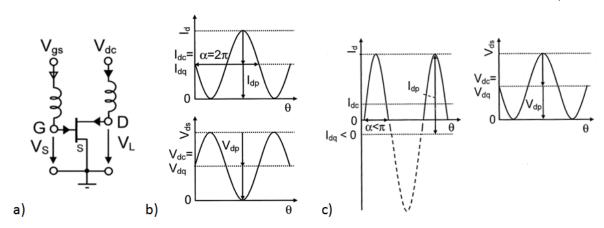

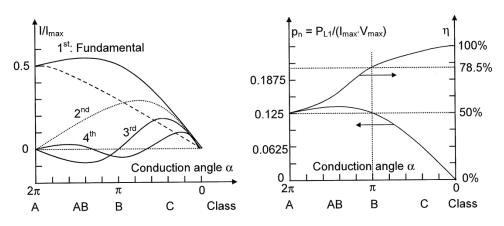

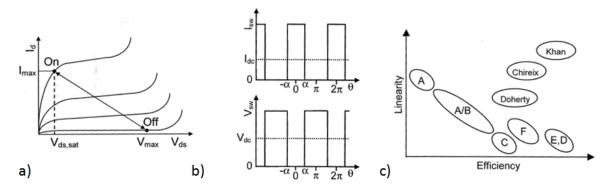

#### 2.a) Le PA: état de l'art

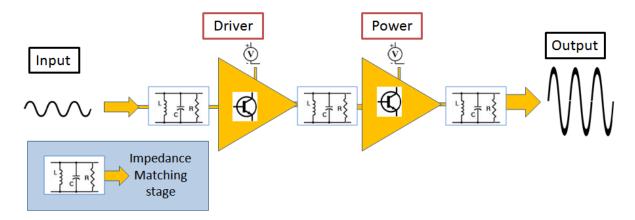

Un amplificateur de puissance (PA) consiste en un enchainement de plusieurs transistors (responsables de l'effet d'amplification) liés par des circuits d'adaptation d'impédance. Ces circuits permettent de transmettre un maximum d'énergie entre les différents étages d'amplification ainsi que l'entrée et la sortie. Un schéma simplifié pour un amplificateur de puissance à deux étages est montré en Figure 40. Les circuits d'adaptation amènent des pertes, dues aux éléments passifs. Ils jouent donc un rôle important dans l'efficacité du PA. L'état de l'art des amplificateurs de puissance dans la bande de 60 GHz est résumé dans la Table 2. Les paramètres comme le PAE (Power Added Efficiency), le niveau d'alimentation (Power Supply), la dissipation de puissance (power dissipation) et le nombre d'étapes (Stages) y sont montrés.

De cette première partie, les conclusions suivantes ont été tirées.

- On préfèrera une configuration coplanaire pour les lignes de transmission.

- ♣ La taille complète du design du PA semble occuper une surface totale de 1 mm². (En incluant les plots de RF (Radio Frequency) et d'alimentation)

- ♣ D'habitude, les PA's ont de 2 à 3 étages d'amplification, ce qui implique 3 ou 4 circuits d'adaptation. Une augmentation d'environ 10% est observée entre le PAE de Bulk et SOI.

#### 2.b ) L'antenne: état de l'art

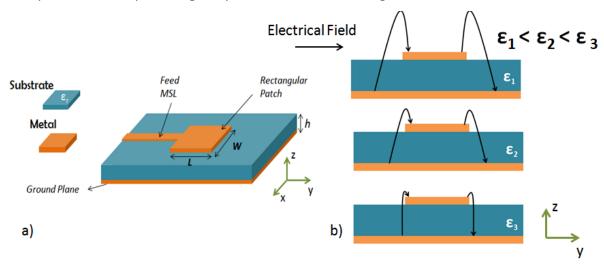

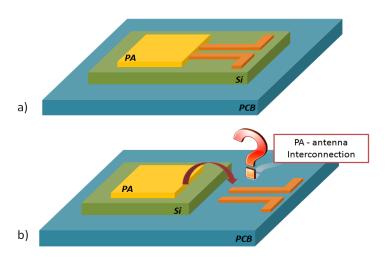

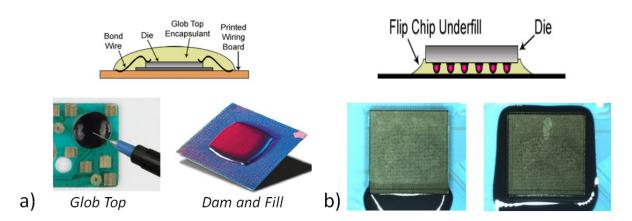

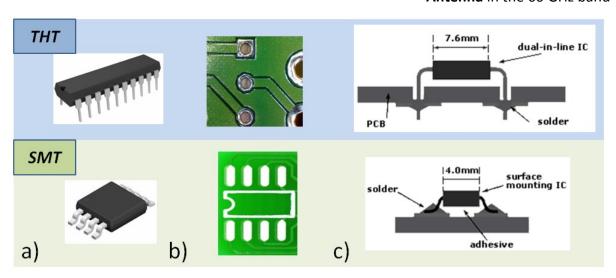

Deux stratégies ont été observées concernant la conception d'antennes dans la bande millimétrique. Dans le premier cas, les antennes se trouvent intégrées dans la métallisation de la technologie. C'est-à-dire que l'antenne reposera sur le substrat (Silicium, dans notre application) et sera intégrée au même moment que les circuits actifs. Ceci s'appelle « Système on Chip ou SoC ». L'antenne, dans ce cas là, se trouve affectée par les propriétés électriques du substrat comme la permittivité et conductivité. D'un autre coté, quand l'antenne est indépendante des circuits et peut être conçue comme faisant partie du boitier, on parle alors de « System in Package ou SiP ». Ce dernier permet d'avoir une plus grande souplesse au moment de choisir l'antenne mais met en évidence aussi une des problématiques des circuits à haute fréquence (60 GHz) : les interconnexions (Figure 54).

Les performances des antennes sont évaluées au moyen de plusieurs paramètres, parmi lesquels se trouvent la bande passante, le gain ou l'efficacité. Un état de l'art pour chacun des deux cas a été fait et il est montré par la suite.

#### 2.b.i) **SoC**

Pour le SoC, (Table 3), les conclusions suivantes ont été tirées:

♣ En regardant le gain, on peut se rendre compte que des valeurs négatives sont communes. Quelques antennes montrent des valeurs positives comme 2,3 ou 4,2. Ce sont des solutions qui ajoutent un plan de métallisation à l'arrière en l'utilisant

comme un plan réflecteur. Ce qui est intéressant, c'est l'efficacité des 82 % fournie [21], due à l'utilisation du SOI. Les valeurs de gain sont toutefois insuffisantes pour notre application.

- ♣ Les antennes sur substrat semblent être bien adaptées concernant notre besoin de bande passante (8 GHz). Une bande passante de 10 GHz en moyenne peut être observée dans le tableau 2.

- $\clubsuit$  Une impédance d'entrée de 50  $\Omega$  semble aussi être un cas général. Ceci est logique à cause des bancs de mesure qui imposent telle valeur. Une basse impédance (4.4 et 20  $\Omega$ ) ainsi qu'une impédance complexe ont été aussi trouvées. Une configuration CPW ou CPS est surtout utilisée.

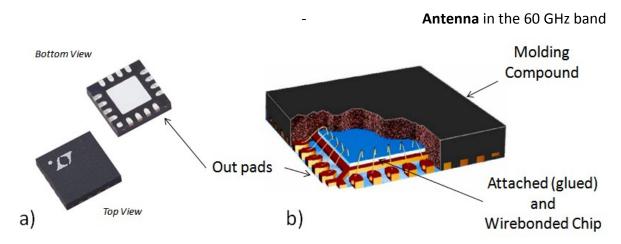

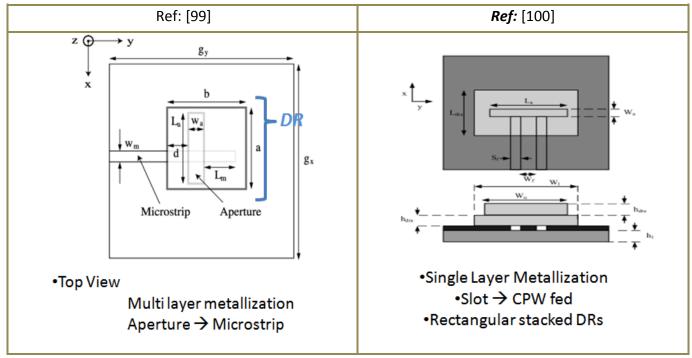

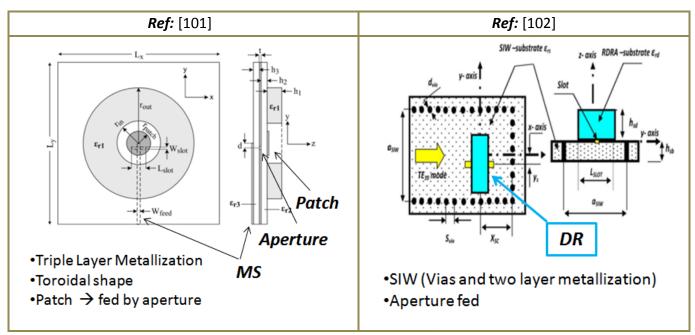

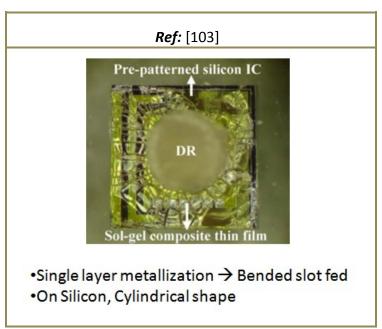

#### 2.b.ii) SiP

Pour le SiP (Table 4), les conclusions suivantes ont été tirées

- ♣ Tout de suite, une des différences importantes est visible entre les deux approches (SoC et SiP). Une valeur plus importante de gain est obtenue pour les configurations qui prennent en compte le boitier. Les niveaux de 5, 8 et 10 dBi sont maintenant possibles. L'efficacité a tout de même aussi augmenté, essentiellement due à l'utilisation des substrats à faibles pertes.

- Malgré la souplesse donnée par les interconnexions, les pertes liées à leur incorporation dans la conception devront être étudiées afin de les quantifier. Un effet de désadaptation d'impédance peut être aussi introduit par les interconnexions.

- ♣ La bande passante reste tout à fait acceptable et maintient même un niveau supérieur par rapport aux besoins. Une valeur de 12% (8 GHz @ 60 GHz) est envisageable.

# 3) Solution antenne SoC → vers l'amélioration du rendement global du système

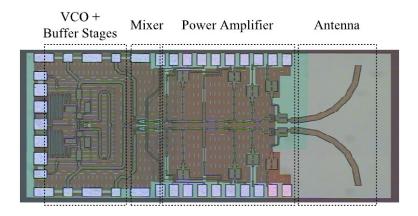

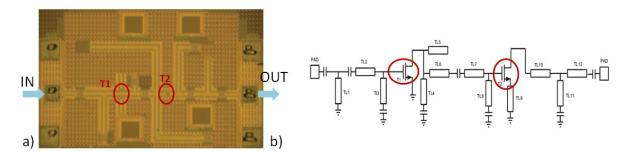

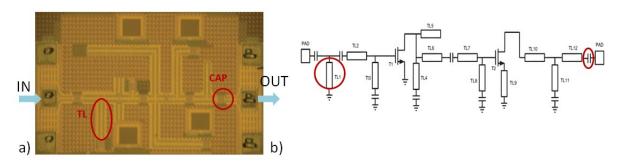

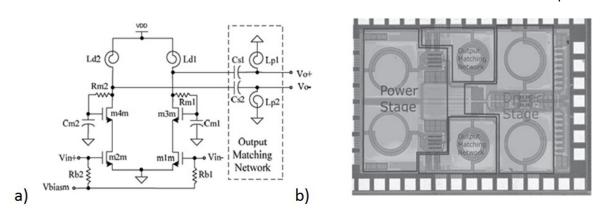

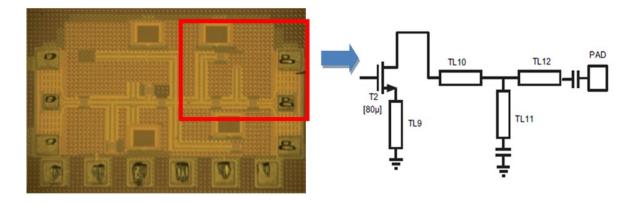

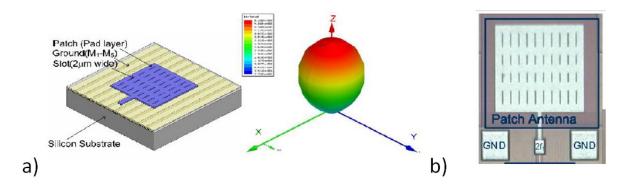

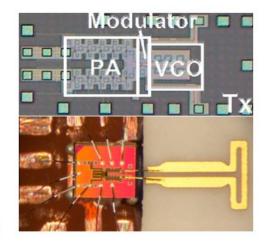

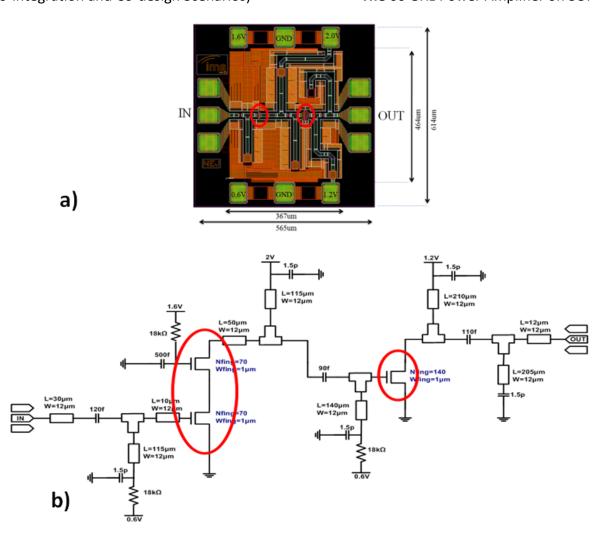

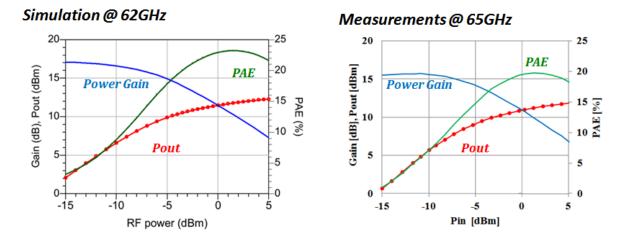

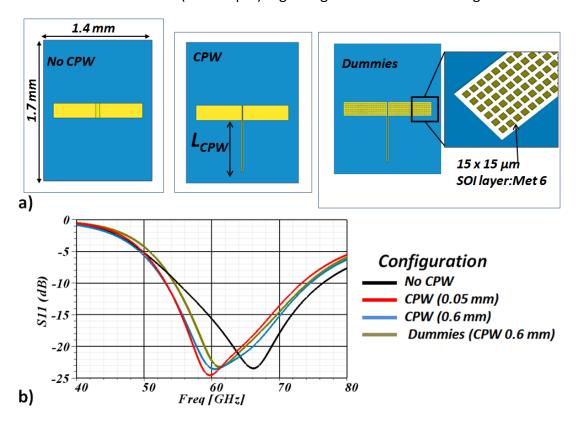

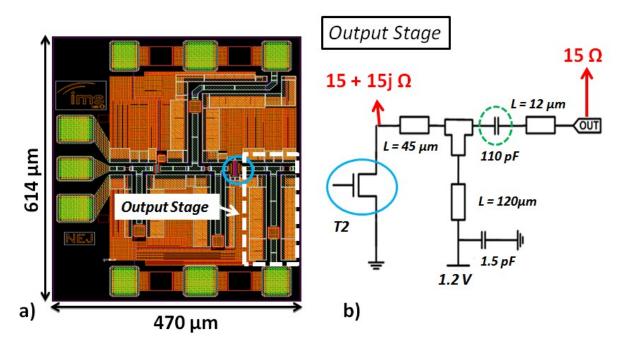

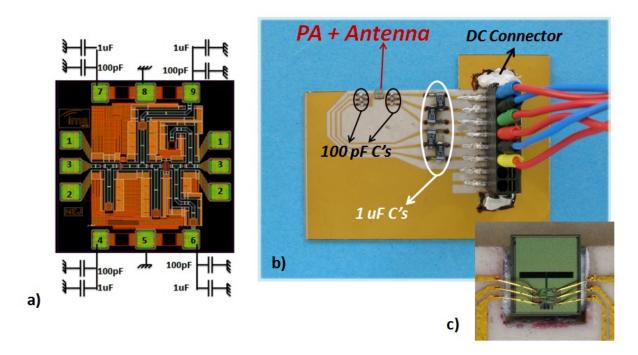

Pour cette partie de notre recherche il y a eu une coopération proche avec IMS (Laboratoire de l'Intégration du Matériau au Système situé à Bordeaux). L'amplificateur de puissance (PA) présenté dans ce chapitre a été développé par ce laboratoire. Le PA est basé sur la technologie SOI à 65 nm de ST Micro-électronics et est montré à la Figure 70. Cette technologie permet de viser une solution d'antenne de haute efficacité à cause de la haute valeur de la conductivité du substrat comme expliqué auparavant.

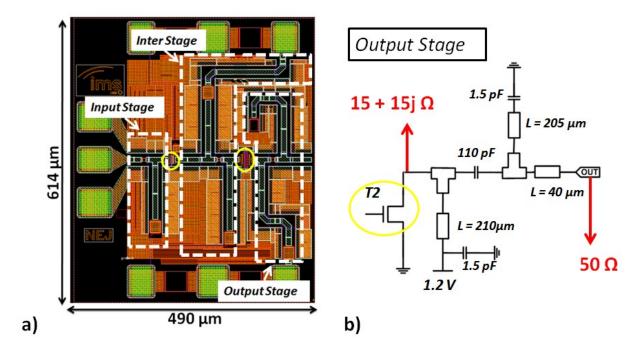

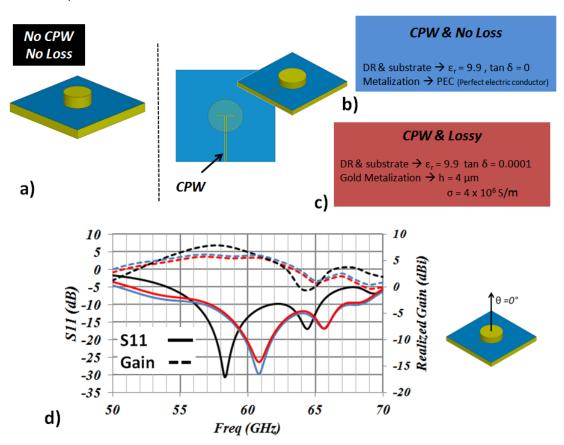

L'approche SoC permet seulement une « simple » intégration de l'antenne (une fois que l'impédance et le mode ont été adaptés), mais aussi lui offre de nouvelles possibilités vis-àvis des modifications des conditions d'adaptation PA-Antenne. La puce du PA illustré à la Figure 6, montre les différentes étapes d'adaptation nécessaires pour créer le chemin entre l'entrée et la sortie en liant les transistors. Ces étapes permettent une adaptation d'impédance vitale pour une transmission maximale de puissance. Mais malgré ce rôle, ces étapes d'adaptation ajoutent des pertes provenant des éléments passifs comme les lignes de transmission. Un niveau de perte de 0.7, 1.8 et 0.8 dB est attendu pour l'étape d'entrée, milieu et sortie respectivement. Une amélioration du rendement du PA peut donc être envisagée si les pertes insérées par les étapes d'adaptation sont enlevées.

Le schéma de la dernière étape (l'étape de sortie) est montré de façon plus détaillée. Deux valeurs d'impédances peuvent être repérées dans deux endroits différents du PA : une impédance de 50  $\Omega$  (impédance vue à la sortie du PA) et une impédance de 15 + 15j (à la sortie du transistor). Cette première impédance de 50  $\Omega$  est habituellement utilisée dû à l'impédance imposée par les bancs de mesures. Mais si l'élément à la sortie ne nécessite pas une adaptation de 50  $\Omega$ , une partie du circuit peut être supprimée et on obtiendra une augmentation du rendement comme résultat. Deux antennes vont être donc montrées dans cette section : une adaptée aux 50  $\Omega$  (approche de Co-Intégration) et l'autre à une impédance plus basse de 15  $\Omega$  pour une solution plus efficace (approche de Co-Conception). A cause de la configuration de l'étage de sortie, son enlèvement complet n'est pas possible puisqu'il joue un rôle partiel sur l'alimentation du PA. De cette façon, une impédance de 15  $\Omega$  (souligné en vert dans la Figure 70), à la place de celle de 15 + 15 j  $\Omega$  à la sortie du PA, devient l'impédance imposée à l'antenne.

#### 3.a) Conception de l'antenne basse impédance (50 $\Omega$ et 15 $\Omega$ )

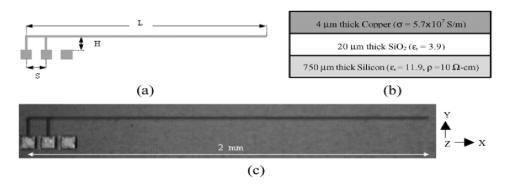

Pour la conception de l'antenne, deux caractéristiques importantes ont été déjà extraites : une impédance d'entrée de 50  $\Omega$  (et aussi 15  $\Omega$ ) et une configuration d'accès coplanaire (CPW). Une antenne qui est habituellement utilisée sous ce genre de conditions est la fente [14], [20], [37]. A cause de la configuration coplanaire de l'accès, la fente semble l'élément rayonnant le plus adapté car il s'agit tout simplement d'une ouverture dans un plan de métallisation.

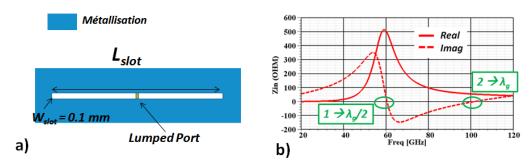

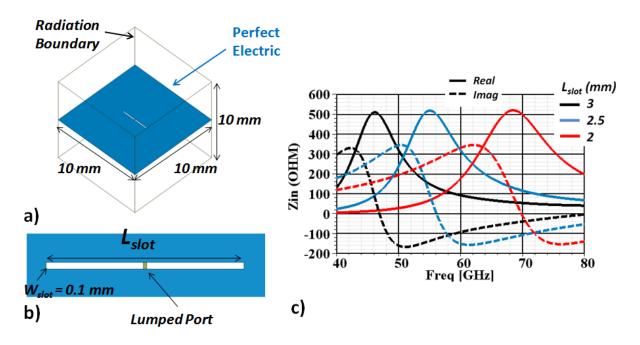

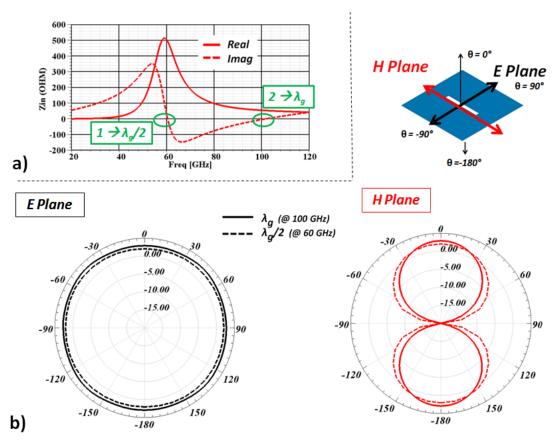

#### 3.a.i) Modes et impédances correspondantes pour une fente

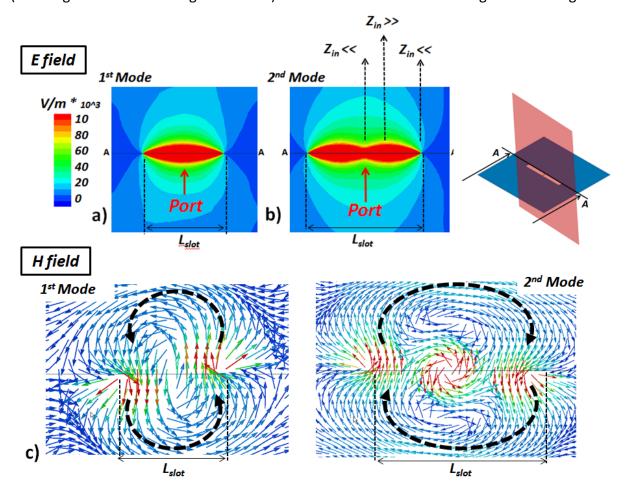

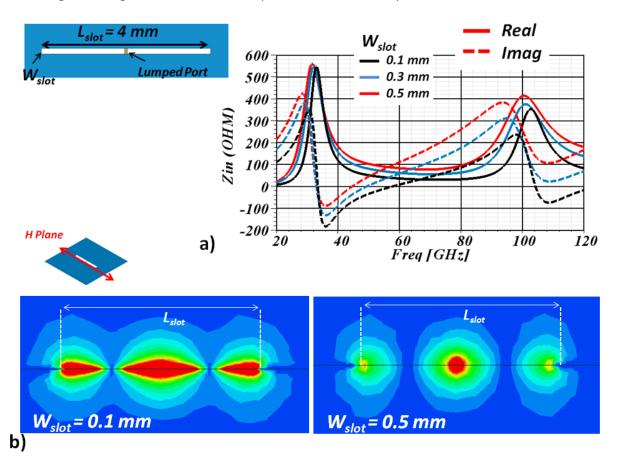

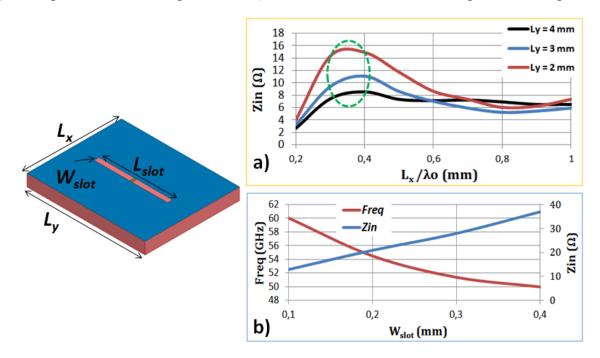

Dans la Figure 3, l'impédance pour les deux premiers modes de la fente sont montrés. Le premier a une fréquence de 60 GHz qui correspond à une valeur de  $\lambda/2$  ( $\lambda$  = 5 mm @ 60 GHz) pour L<sub>slot</sub>, soit 2.5 mm. Ensuite, le deuxième mode ( $\approx \lambda$ ) se retrouve à 100 GHz. Une claire différence est immédiatement visible, une impédance de 500  $\Omega$  pour le premier mode qui contraste avec celle de 60  $\Omega$  pour le deuxième. C'est donc le deuxième mode qui sera utilisé. Bien sûr, L<sub>slot</sub> doit être modifié pour faire descendre ce mode de 100 GHz à 60 GHz. Le substrat n'a pas été inclus dans la configuration présentée.

Figure 3 : a) Impédance d'entrée pour une fente (deux modes)

Cette haute impédance est expliquée par le champ éléctrique dans la fente montrée dans la Figure 73. Pour le premier mode, on peut repérer une présence maximale de champ dans la partie centrale de la fente (position du port). Maintenant, pour le deuxième mode, une absence de champ est visible au même endroit. Cette différence explique la différence d'impédance entre les deux modes.

Le rayonnement des deux modes est globalement semblable, sauf pour une différence de gain d'environ d'un dBi. Ceci peut aussi être expliqué par les champs magnétiques. On peut

observer, que pour le premier mode, le champ est lié entre les deux endroits où le champ est maximum (souligné par la flèche blanche). Ce phénomène est aussi observé pour le deuxième mode entre les champs maxima aux extrémités de la fente. Dans ce mode, un nouveau maximum au centre est aussi observé.

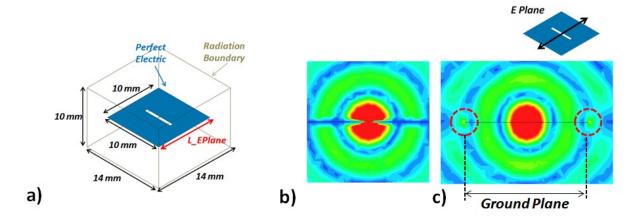

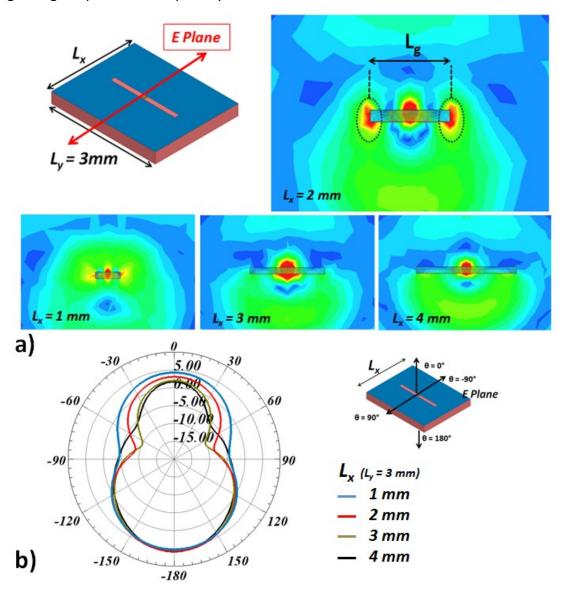

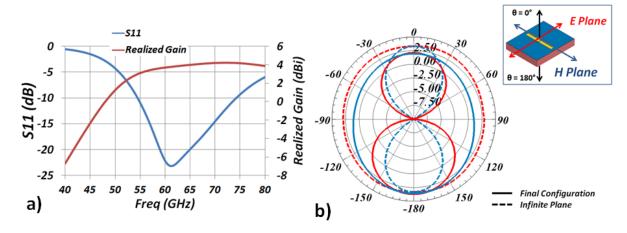

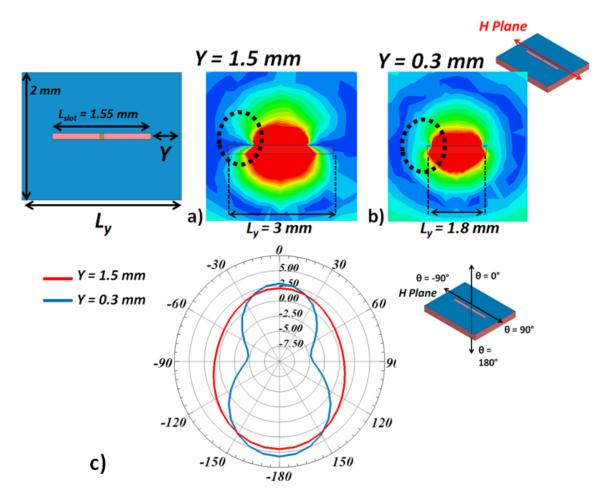

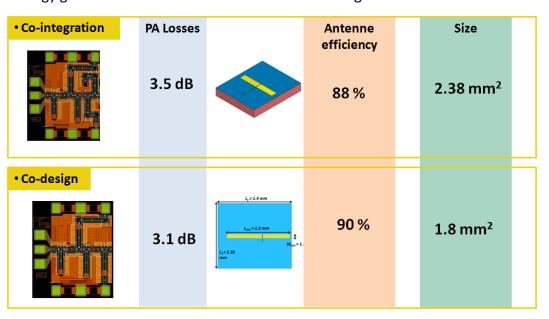

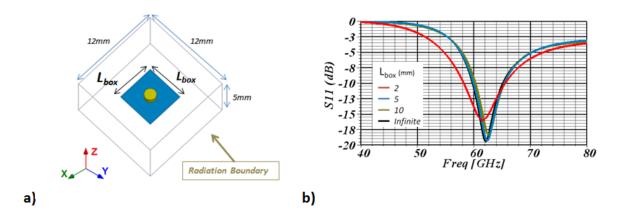

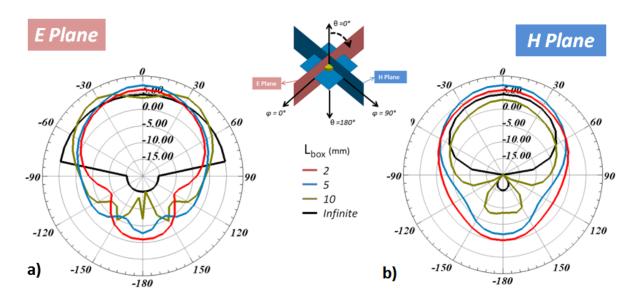

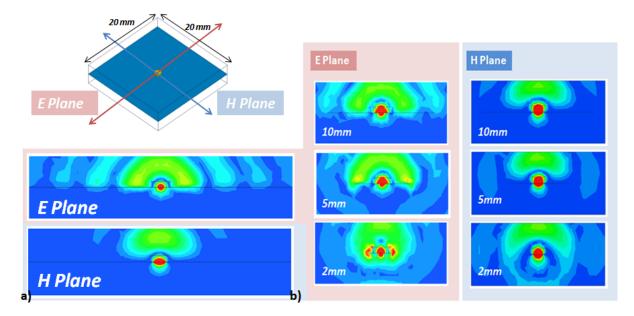

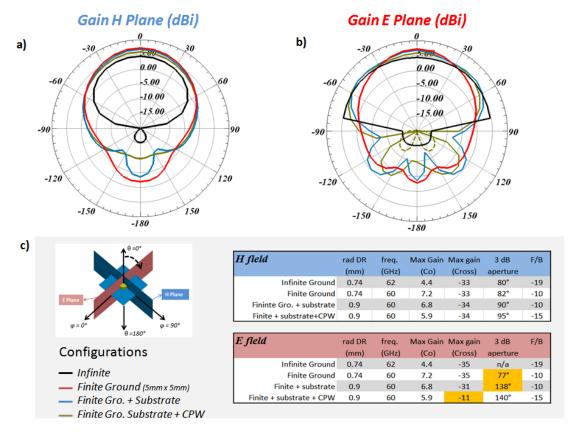

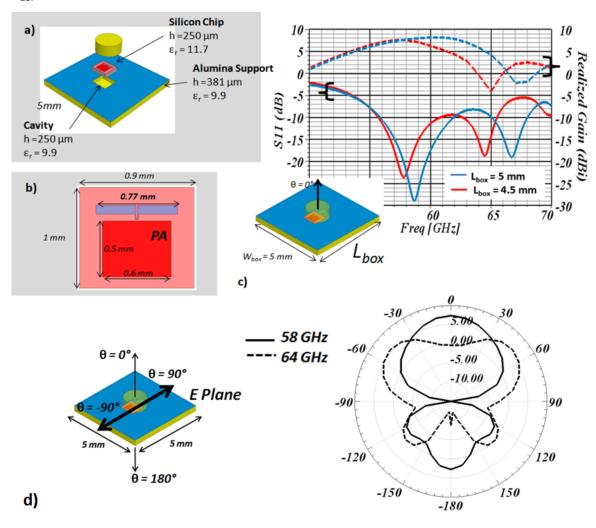

#### 3.a.ii) Performances finales de l'antenne (Co-intégration et Co-conception)

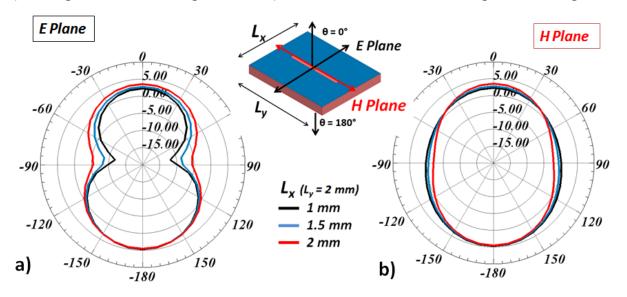

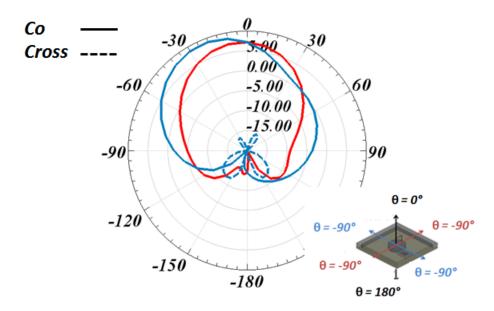

L'étude présentée précédemment comprenait un plan métallique infini. Un plan de masse fini doit être introduit pour une solution réalisable. La dimension du plan de masse a un effet important sur l'impédance et aussi pour le rayonnement de l'antenne. Par exemple, dans la Figure 79, on peut observer comment, pour certaines dimensions du plan de masse, ces bords se couplent au rayonnement de la fente. En maîtrisant ces effets, et d'après l'addition du substrat, une configuration finale est obtenue et sa performance peut être observée dans la Figure 84. Une bande passante (ROS < 2 dB) de 19.8 GHz a été obtenue, avec un gain minimum de 3 dBi dans l'ensemble de la bande adaptée et une valeur maximale de 4.2 dBi ( $\theta$  = 180°). Une taille finale de 2.38 mm² et une efficacité de 89% sont aussi obtenues par simulation. L'effet du substrat est aussi visible dans le diagramme de rayonnement. En insérant le substrat, la configuration perd sa symétrie et les valeurs du gain en  $\theta$  = 180° et  $\theta$  = 0° deviennent par conséquent différentes. Ces résultats contrastent avec ceux obtenus pour une configuration seulement fente (sans substrat) comme celle de la Figure 73.

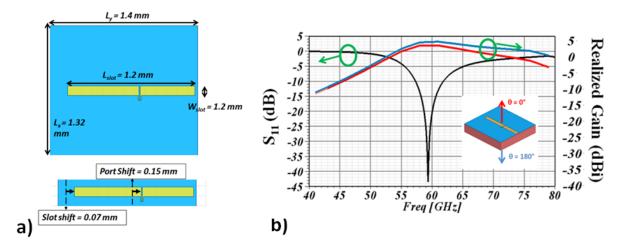

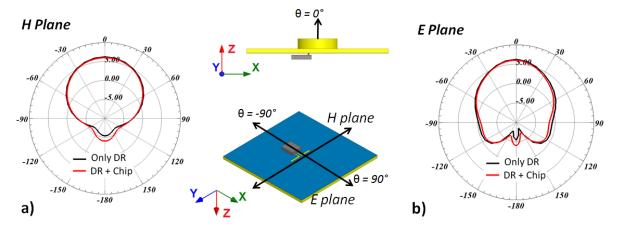

Pour le cas du Co-design et comme signalé auparavant, une impédance encore plus basse est nécessaire. Une telle impédance est aussi atteignable avec la configuration « fente sur plan de masse fini ». Par conséquent, la taille ainsi que la performance de l'antenne ont été modifiées. Maintenant, pour une taille de 1.68 mm<sub>2</sub>, on a réussi à obtenir une bande passante de 4.8 GHz (ROS < 2 dB) et un gain maximum de 3.4 dBi @  $\theta$  = 180°. Le diagramme de rayonnement se comporte essentiellement de la même manière que celui de l'antenne à 50  $\Omega$  avec un rayonnement omnidirectionnel dans le plan H et avec des zéros à  $\theta$  = 90° et  $\theta$  = -90° dans le plan E.

#### 3.b) Mesures de l'antenne à $50 \Omega$

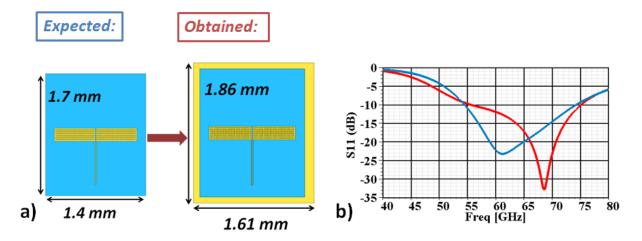

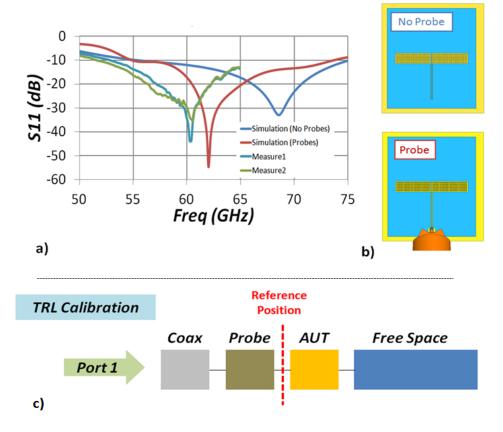

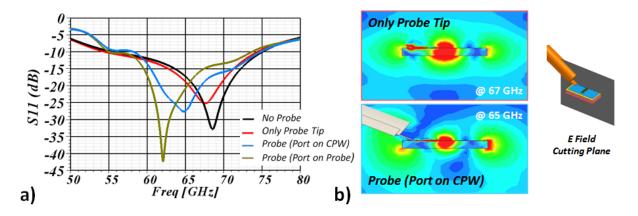

Puisque les dimensions de l'antenne sont vraiment importantes pour une résonnance à 60 GHz et une bonne adaptation, un procédé de coupage a été demandé à l'usine. Cependant, les dimensions obtenues sont différentes de celles attendues. Ce changement fait décaler la fréquence de résonance de 7 GHz, soit une résonance à 67 GHz. L'antenne fabriquée, ainsi que ses réponses en adaptation pour deux mesures sont montrées dans la Figure 93. Malgré la modification de taille, une résonance à 60 GHz est toujours obtenue. Pour pouvoir expliquer le décalage par rapport aux résultats de simulation (qui prennent en compte les nouvelles dimensions), un autre élément doit être introduit dans la configuration de la simulation : la sonde de mesure.

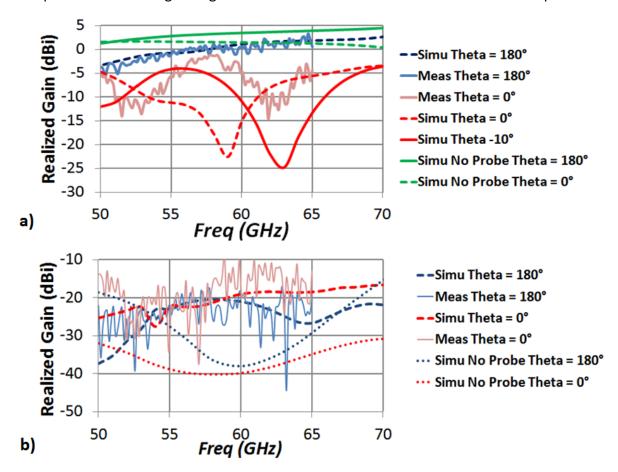

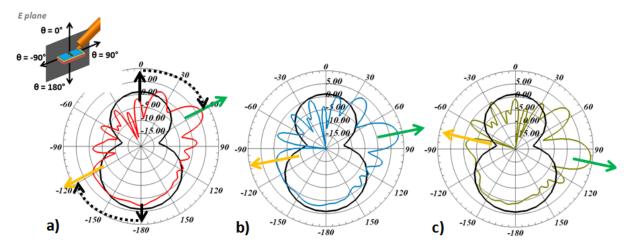

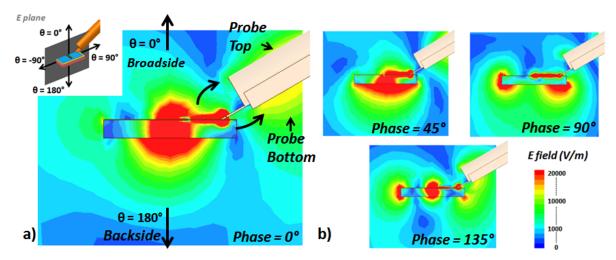

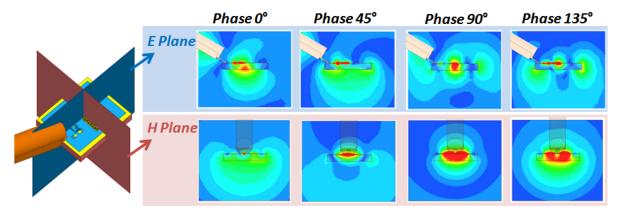

La sonde est maintenant incorporée dans la simulation. Le couplage avec l'antenne peut être observé dans la Figure 96. Le champ autour de la sonde montre que le couplage a lieu pardessus comme par-dessous. Il va donc transformer le rayonnement de l'antenne. D'une part, le diagramme de rayonnement change particulièrement autour de  $\theta=80^\circ$ , où une augmentation de niveau est observée de plus de 20 dB par rapport au niveau de la configuration «antenne seule». Cette relocation d'énergie va, par conséquent, modifier le diagramme de rayonnement. Une baisse d'intensité de 2 et 3 dB selon  $\theta=180^\circ$  (arrière) ainsi que une variation plus importante vers la direction normale (10 et 20 dB respectivement pour  $\theta=0^\circ$  et  $\theta=10^\circ$ ). D'autre part, une augmentation de la polarisation croisée est aussi observée entre les deux configurations. Les mesures montrées dans la

Figure 99, concordent avec les modifications induites par la présence de la sonde. C'est-à-dire, une diminution de la puissance dans la direction normale est obtenue et un haut niveau de polarisation croisée a été aussi mesuré (non montrée). Ces mesures ont permis de valider l'antenne.

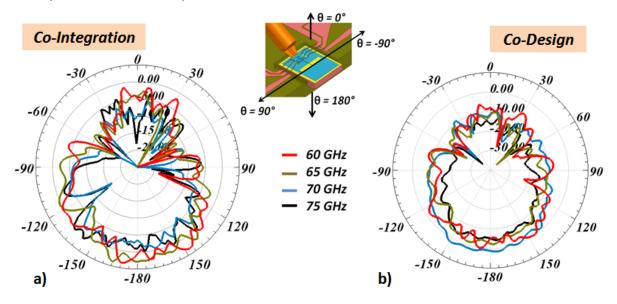

#### 3.c) Co-intégration PA – Antenne (50 $\Omega$ )

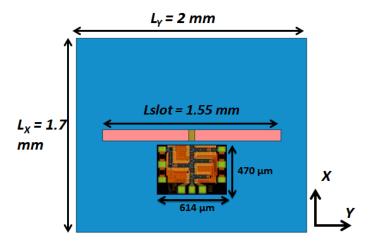

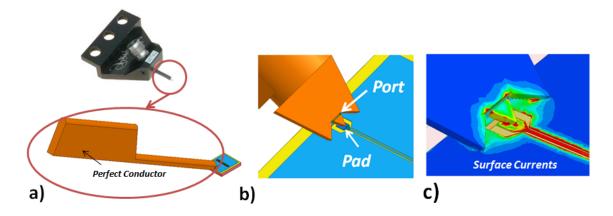

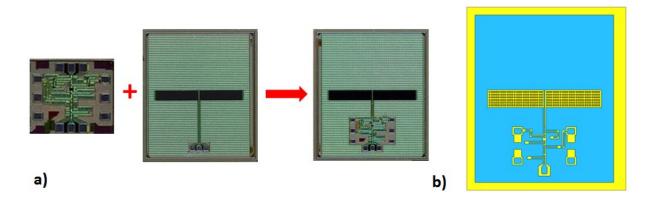

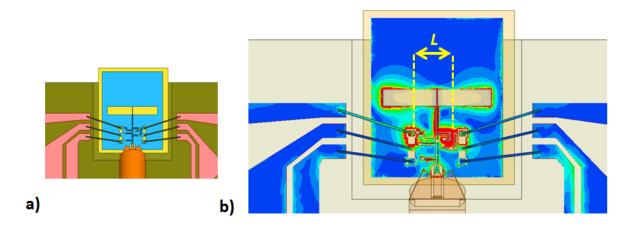

Après la conception de l'antenne et sa validation, on remarque que la taille de l'antenne (1.86 x 1.61 mm²) fait plusieurs fois celle du PA (0.614 x 0.565 mm²). Pour limiter la taille globale du système (PA-Antenne), le PA est incorporé dans la métallisation de l'antenne. Cette opération est possible grâce à la configuration coplanaire du PA qui rend une grande partie du PA comme métallisation et par conséquent compatible avec la configuration de la métallisation de l'antenne. Une ligne de 50  $\Omega$  est utilisée pour lier l'antenne au PA et elle permet d'avoir un certain degré de liberté pour la position du PA par rapport à la fente rayonnante. Pour la simulation, l'agencement du PA a été inséré dans la métallisation de l'antenne et cette configuration est simulée par un simulateur électromagnétique 3D. Ce simulateur ne peut pas prendre en compte l'effet des transistors, c'est-à-dire, l'amplification du PA. Pour le prendre en compte, un simulateur de circuit est nécessaire mais il ne permettra pas d'évaluer l'interaction électromagnétique entre les deux parties. Pour notre étude, cette interaction est primordiale. Par conséquent, la configuration pour le simulateur 3D a été choisie.

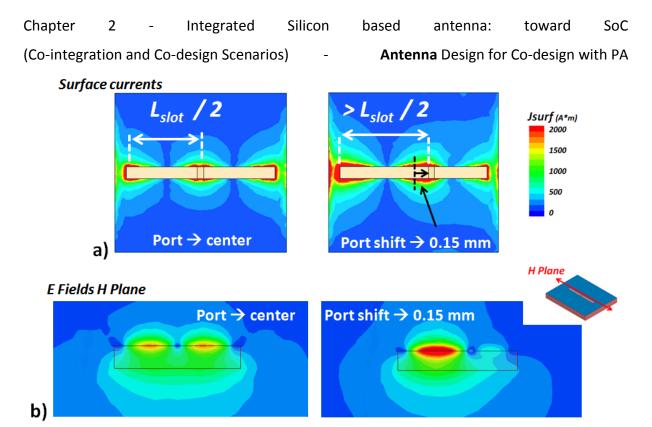

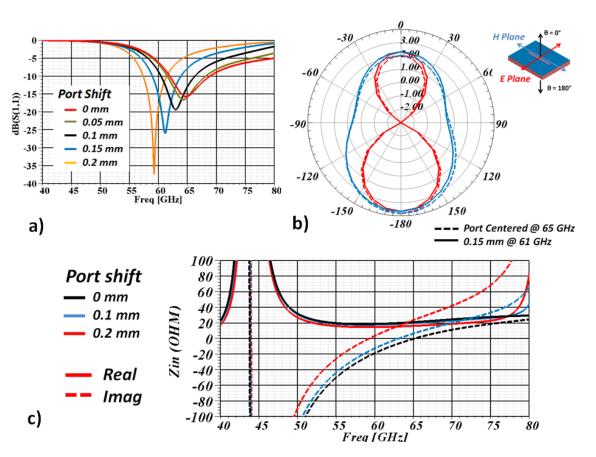

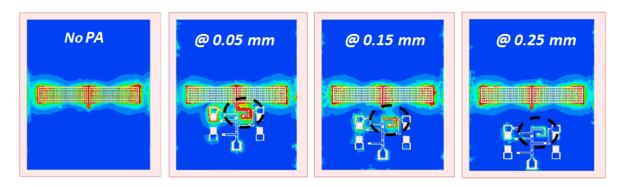

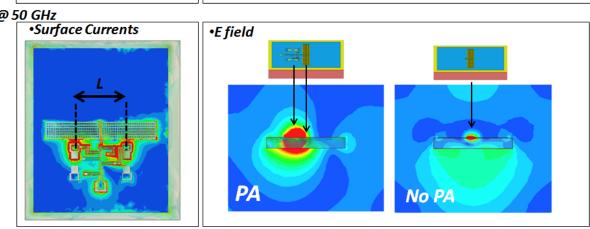

Malgré la compatibilité de la disposition de la métallisation entre le PA et l'antenne, des effets de couplage sont trouvés par simulation. Le niveau de couplage diminue avec l'augmentation de la distance entre le PA et la fente. Cette réduction est visible dans les courbes du gain réalisé. Pour comprendre le couplage, le courant surfacique dans la métallisation est montré à 50 et 74 GHz. On peut repérer un fort niveau de courant dans des éléments du PA. Les plots et lignes du PA entrent en résonance et génèrent une composante destructive pour le rayonnement de l'antenne. Une chute de 16 et 9 dB est observée dans le gain respectivement à 50 et 74 GHz (Figure 106).

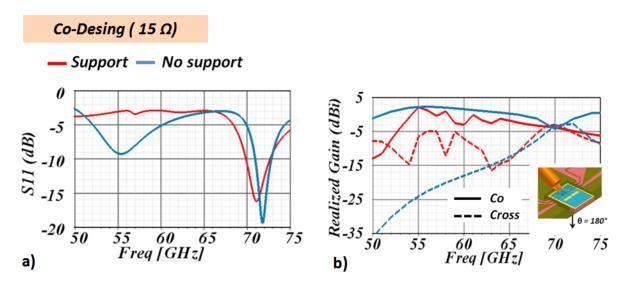

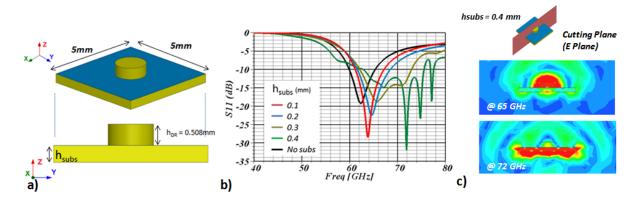

#### 3.d) Co-conception PA - Antenne (15 $\Omega$ )

De la même façon que pour l'antenne de  $50~\Omega$ , la réalisation a débouché sur une augmentation de la taille totale de l'antenne. L'impédance d'entrée a donc été modifiée. Une impédance de  $25~\Omega$  a été obtenue au lieu de celle attendue de  $15~\Omega$ . Le changement en adaptation, ainsi que la configuration PA-Antenne sont montrés dans la Figure 111. Un décalage vers le bas de la fréquence de résonance (la résonance à 60~GHz est maintenant à 57~GHz) et une diminution de l'adaptation sont montrés par la courbe du S11. Le layout du PA est ensuite incorporé et le S11 également montré. Une nouvelle résonance est immédiatement observée à 72~GHz. Comme précédemment, il s'agit d'une résonance provenant des éléments du PA. Malgré ces changements, un gain de 3~dB est obtenu dans toute la bande.

Ces derniers résultats nous ont permis d'obtenir les réponses pour les deux configurations de PA -Antenne. L'influence du PA, ainsi que la taille de l'antenne ont été étudiés. Maintenant, les résultats de mesures seront présentés.

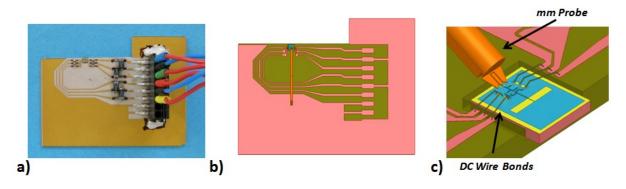

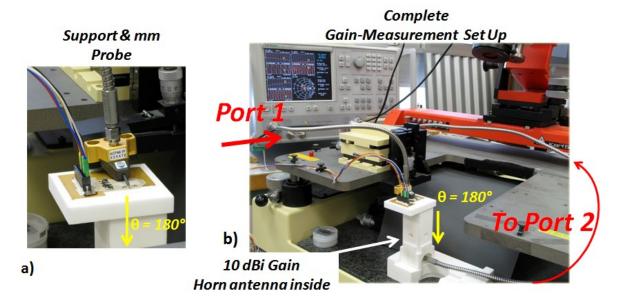

#### 3.e) Mesures: S11 et gain

Dans la Figure 112 a, le circuit d'alimentation DC du PA est montré. Ce circuit comprend le connecteur DC, les capacitances de découplage, le substrat de support et finalement des fils de connexion en or. Ces derniers sont montrés en détail dans la Figure 112 b. Une colle non-

conductrice et de basse permittivité est utilisée pour fixer la puce au support. Le support va permettre aussi de tenir le circuit pendant les mesures, rendant possible la position de la sonde d'une façon fiable. La réponse d'adaptation est d'abord mesurée pour les deux cas : Co-intégration et Co-Conception.

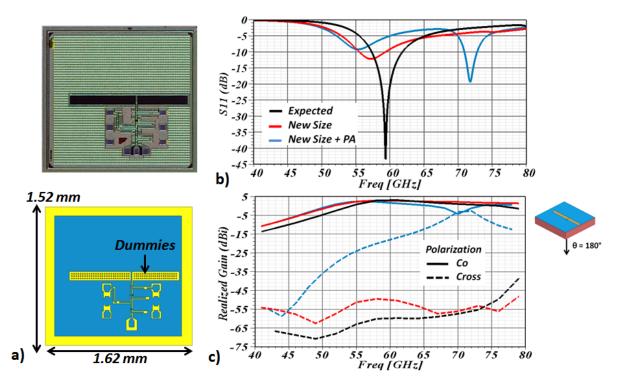

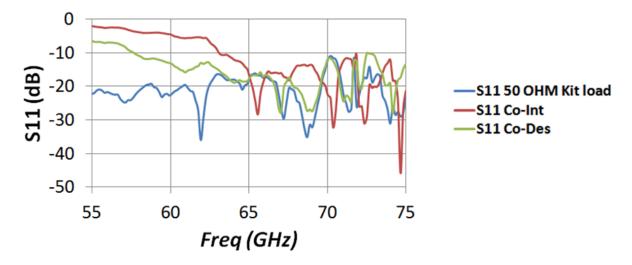

La mesure et la simulation du S<sub>11</sub> du PA isolé, c'est-à-dire sans aucune stratégie de cointégration, est montrée à la Figure 114. Un décalage est observé d'autour de 6 GHz pour une fréquence de résonance visée de 60 GHz. Même avec une modification du modèle du transistor qui a rapproché les résultats de simulation de ceux des mesures, une fréquence de résonance de 62 GHz est obtenue. Ce décalage est tout de suite observé dans les mesures de Co-intégration et de Co-conception. Une fréquence de résonance de 65 GHz est obtenue. Ces résultats nous ont permis de valider le fonctionnement correct du circuit d'alimentation DC. Ce décalage aura un grand impact sur les mesures de gain présentées ensuite.

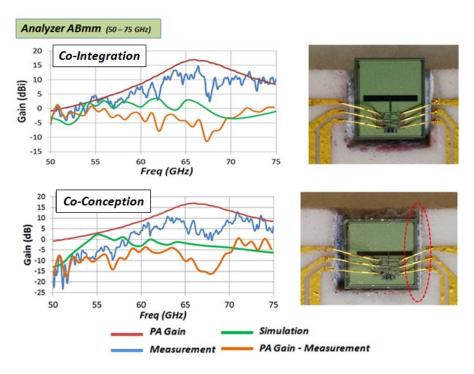

A cause du décalage obtenu en fréquence, l'analyseur utilisé jusqu'à présent (fréquence maximal de 65 GHz) a été remplacé par un autre analyseur qui opère jusqu'à 75 GHz. Les résultats de simulation inclus prennent en compte le support, la sonde, les fils de connexion et le support. La structure simulée peut être observée dans la Figure 112 b) pour le cas de la co-intégration.

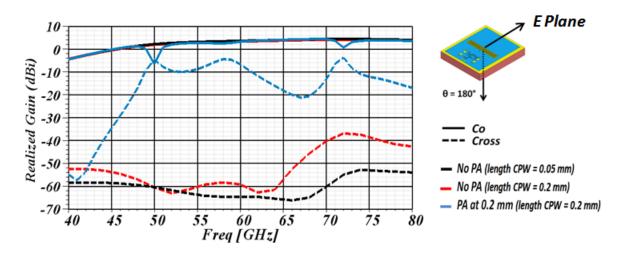

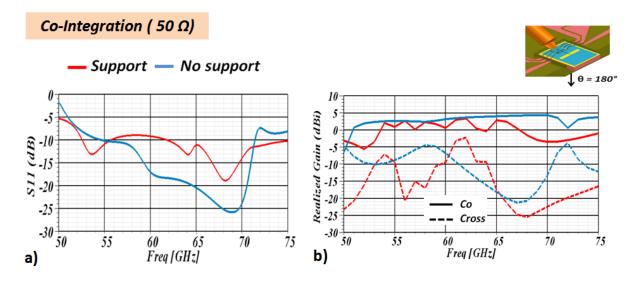

D'après les résultats du gain présentés dans la Figure 4, le transfert d'énergie du PA à l'antenne est évident. Une augmentation du gain d'environ 15 dB a été mesurée pour le cas de la co-intégration à 65 GHz. Une valeur plus faible est obtenue pour la co-conception. Ceci est expliqué par les résultats de simulation et aussi par la position finale de la puce par rapport aux parois du support. Elle se trouve en contact avec le support et la frontière de l'antenne est modifiée selon les caractéristiques du support comme sa permittivité. Cette nouvelle position est soulignée dans la Figure 4.

Une chute inattendue est aussi observée dans les deux cas au moment de l'amplification maximale du PA.

Un niveau de 15 dB est immédiatement suivi par une descente de gain atteignant2 ou 3 dB. On peut constater que le gain «mesuré » de l'antenne (PA Gain – Measurement: ligne orange) et la simulation (ligne verte) montrent une plus grande divergence entre 65 et 70 GHz. Bien qu'on voie une différence entre gain du PA (ligne rouge) et mesure (ligne bleue), cette chute importante n'a pas pu être précisément expliquée.

Une des explications possibles vient peut être du fait que la simulation simultanée des éléments passifs et actifs n'est pas possible, comme mentionné auparavant. L'existence des transistors est négligée et leur réaction à la présence d'un champ électrique extérieur comme celui de l'antenne n'est pas pris en compte. À mesure que le PA transfère l'énergie à l'antenne, elle est davantage rayonnée et, par conséquent, il aura plus de champ externe sur les transistors. Ceci pourrait expliquer les résultats obtenus en mesure. Les valeurs simulées et mesurées retrouvent leurs concordances dans la partie haute de la bande (70 à 75 GHz) pour les deux cas.

Figure 4 : Mesure de gain pour la Co-Intégration et la Co-Conception (50 - 75 GHz) Vue détaillée de la puce collée et connectée par fils.

Ces résultats présentent la dernière étape de notre travail par rapport aux solutions SoC. Les limites de simulation des éléments passifs et actifs on été exposés. Une amélioration du rendement a été aussi obtenue avec une stratégie de co-conception. Les pertes liées à l'étape de sortie ont été diminuées, passant de 0.8 dB à 0.4 dB et par conséquent une amélioration de 11% pour les pertes totales liées aux éléments passifs du PA. Par contre, le niveau de gain visé pour notre application (6 dBi) est toujours inatteignable avec cette stratégie SoC (4 dBi obtenu) et c'est pour cela que les solutions SiP vont être poursuivies et présentées plus tard.

## 4) Solution antenne SiP → vers des solutions de haut gain

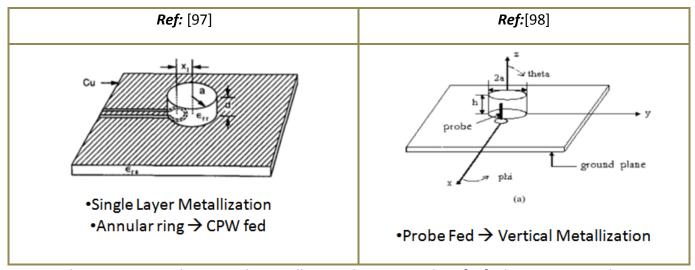

D'après les solutions présentées dans l'état de l'art pour des systèmes SiP, une solution semblait être intéressante due aux possibilités de haut gain et aux compatibilités avec des technologies de « packaging ».

#### 4.a) L'antenne basée sur le résonateur diélectrique ou DRA

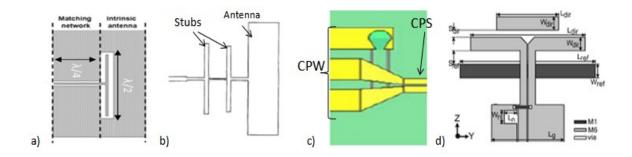

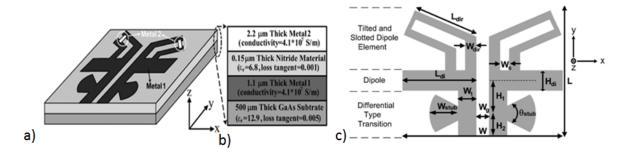

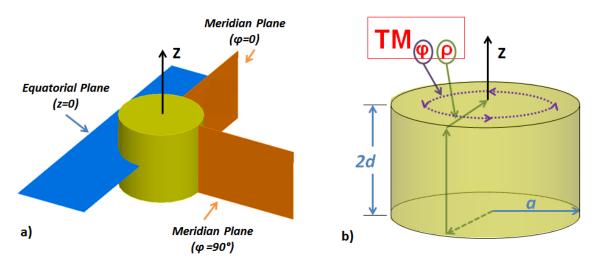

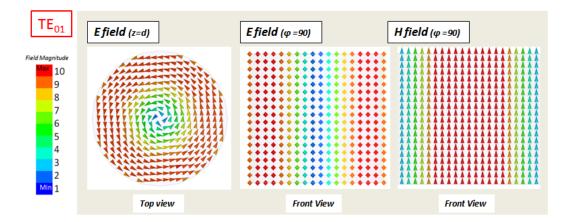

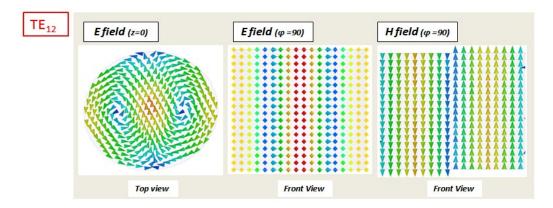

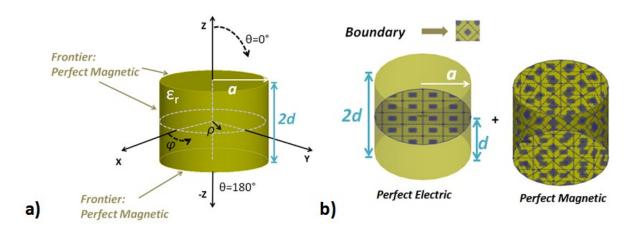

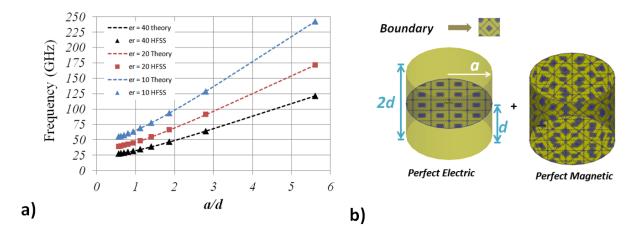

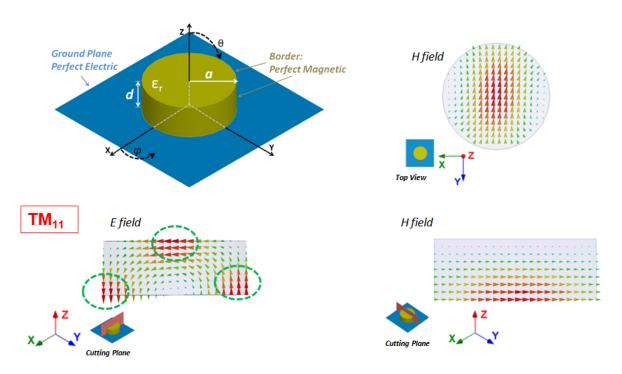

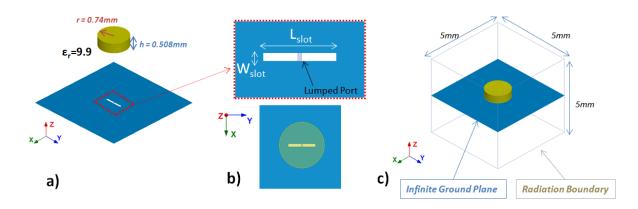

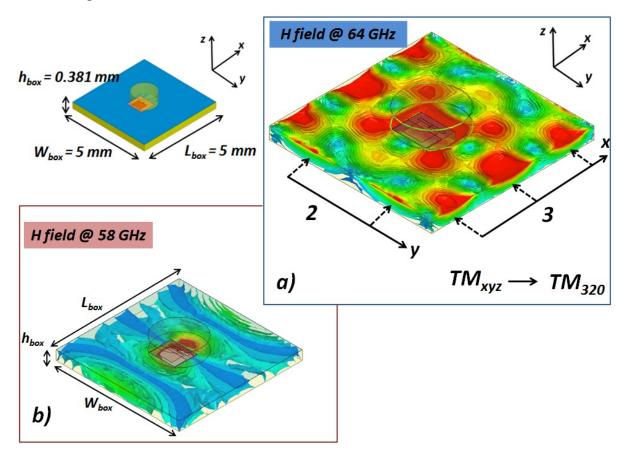

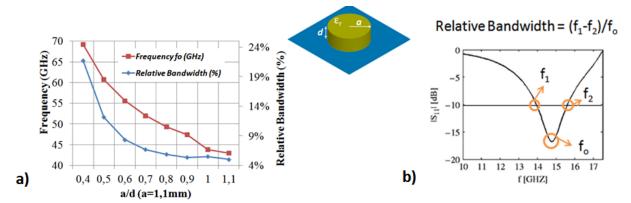

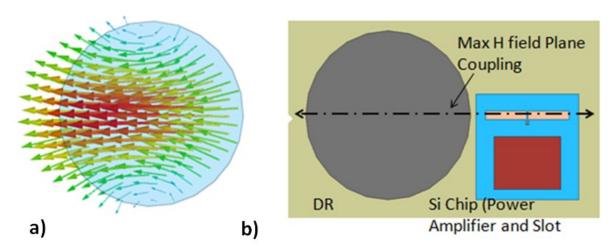

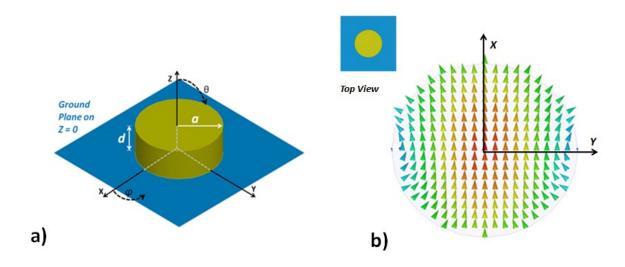

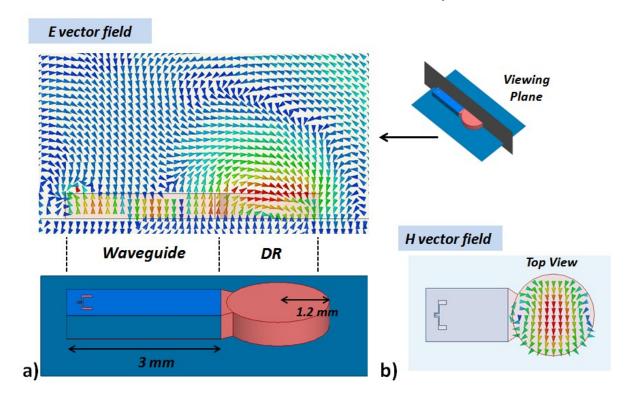

L'antenne basée sur résonateur diélectrique ou DRA d'après l'abréviation anglaise (Dielectric Resonator Antenna) est donc choisie. Une DRA est composée de deux éléments : le résonateur diélectrique et l'élément d'excitation. Celui-ci va transférer de l'énergie guidée (par exemple par une ligne coplanaire) pour générer les champs électromagnétiques dans la cavité. Le rayonnement de l'antenne est obtenu grâce à la distribution des champs qui déborde à l'extérieur de la cavité. Les champs peuvent s'exprimer par des modes qui ont un rayonnement propre. Dans notre cas, le mode TM<sub>11</sub> a été choisi car il possède le facteur de qualité le plus bas et, en conséquence, la plus large bande passante.

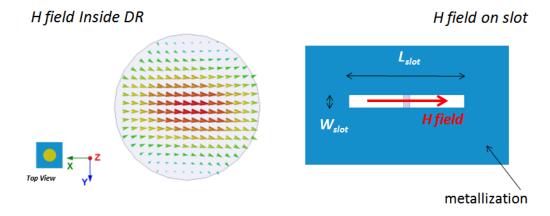

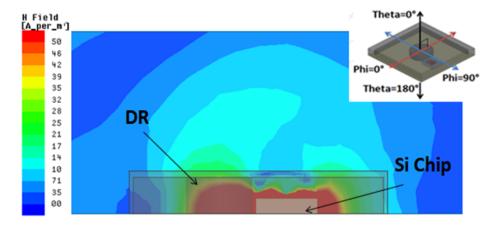

Le champ H du TM<sub>11</sub> (pour une cavité cylindrique) est montré dans Figure 137, ainsi que l'élément excitant. L'excitation du mode du DR se fait à partir d'une fente non résonante qui partage la distribution du champ magnétique (distribuée linéairement tout au long de sa

longueur) avec celle du DR. De cette façon, la fente doit être mise sous le DR au centre pour une correcte excitation. Cette excitation a été déjà validée dans [100] and [101].

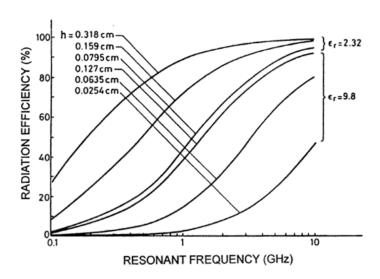

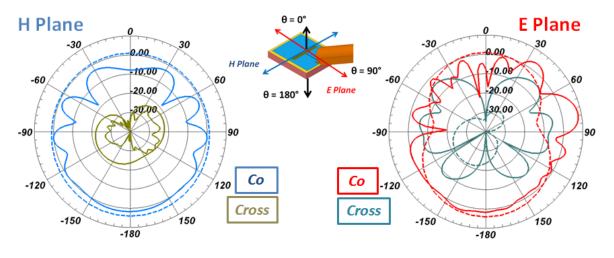

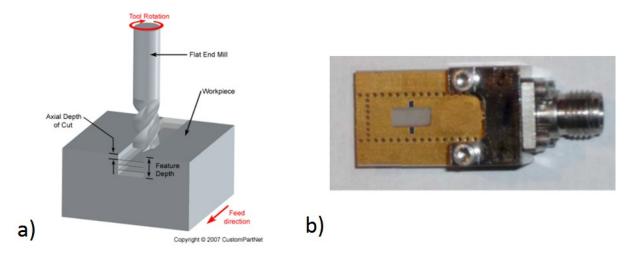

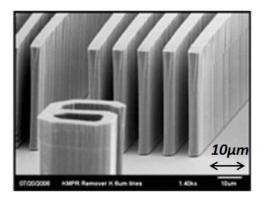

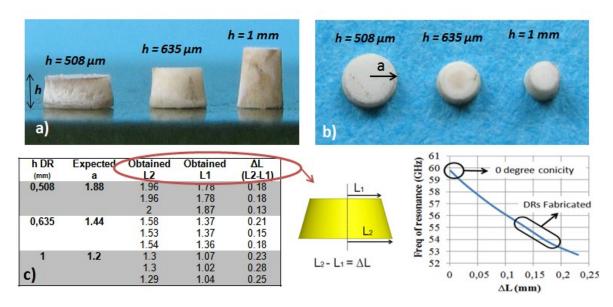

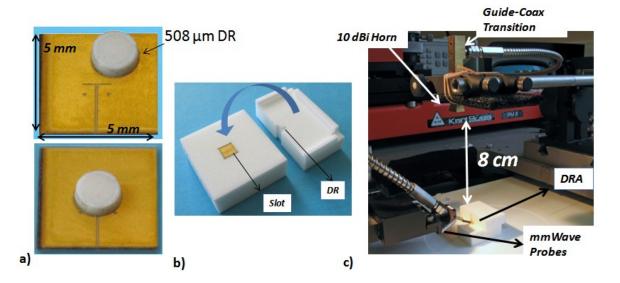

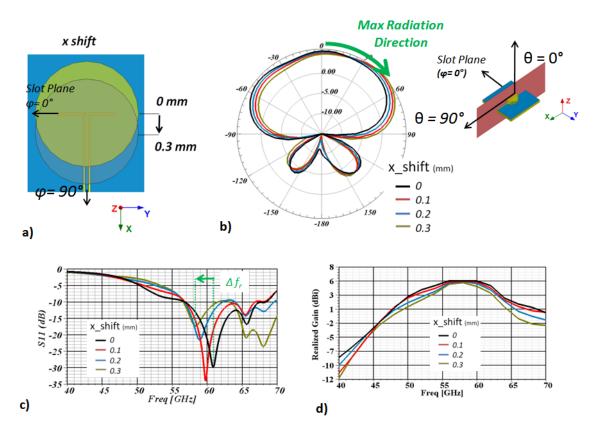

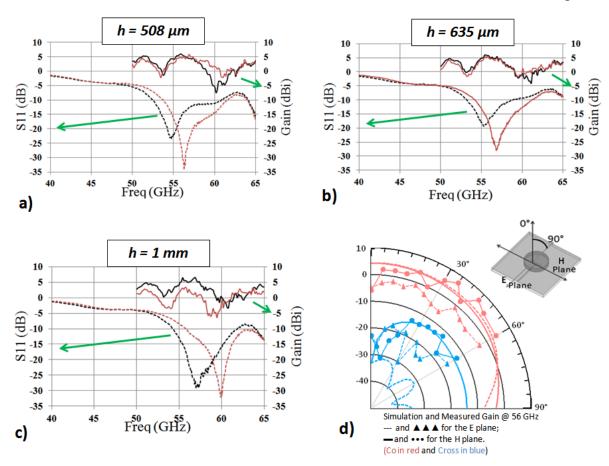

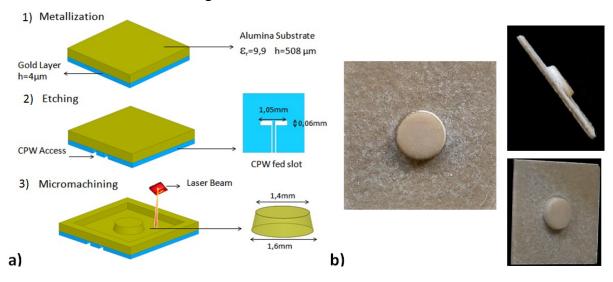

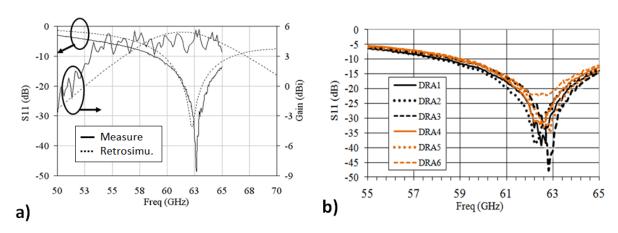

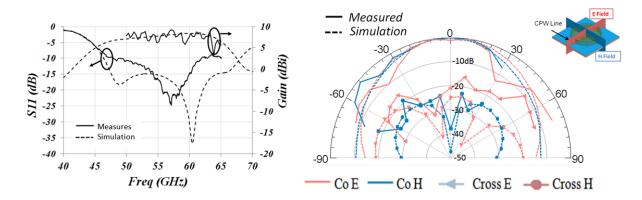

#### 4.b) DR Fabrication et mesures (Validation du DRA)

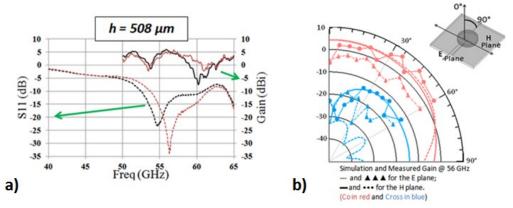

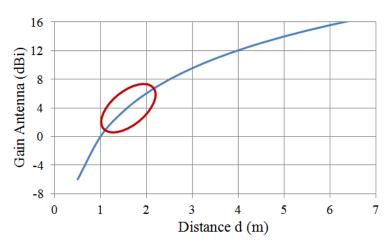

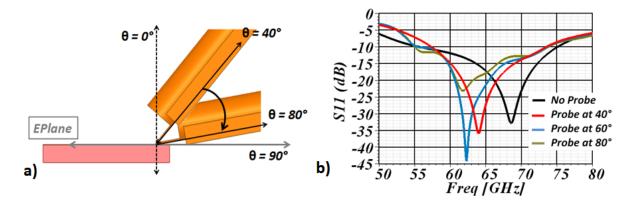

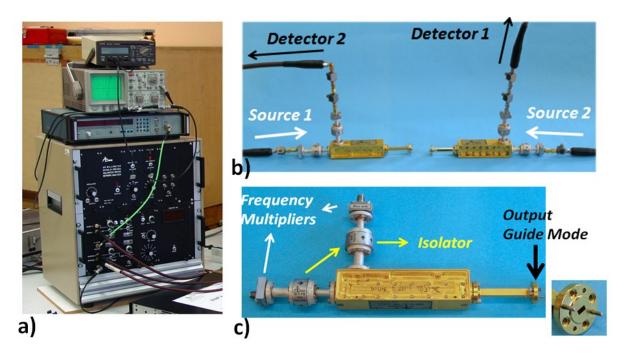

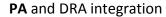

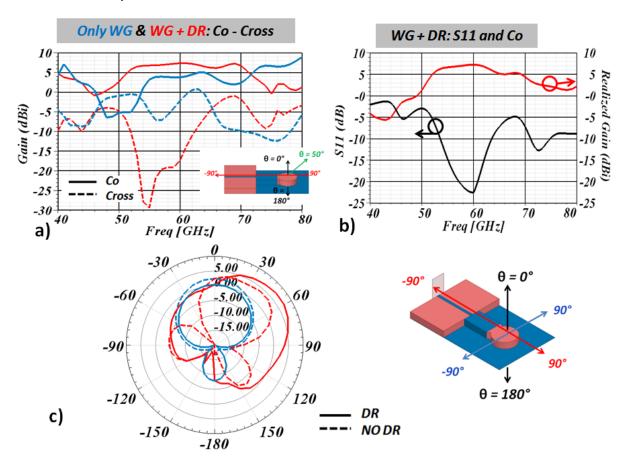

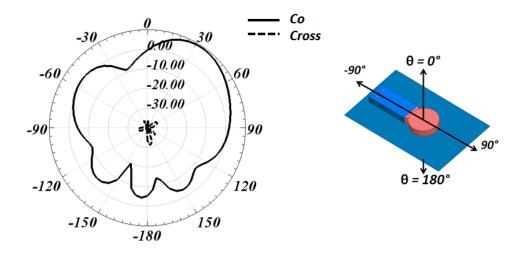

Neuf échantillons ont été fabriqués au laboratoire et peuvent être observés dans la Figure 146. Trois épaisseurs différentes du substrat disponible ont permis d'obtenir trois groupes de cavités diélectriques avec des hauteurs différentes (h = 0.508 mm, 0.635 mm et 1 mm). La fréquence de résonance de la cavité dépend de son rayon comme de sa hauteur. Une diminution du rayon est nécessaire pour garder la même fréquence de résonance si la hauteur augmente. Une valeur de 0.1 mm pour W<sub>slot</sub> et de 0.9 mm pour L<sub>slot</sub> ont été utilisés pour les mesures. Après l'usinage par laser, une forme conique a été trouvée à la place de la forme cylindrique attendue. Cette conicité provoque une diminution de la fréquence de résonance de 3 ou 4 GHz en simulation. Les résultats de simulation ont été corroborés par des mesures comme le montre la Figure 5. Seules deux mesures d'un des échantillons de 0.508 mm de hauteur sont montrées. Des oscillations sont visibles sur les mesures de gain produites par des réflexions sur le banc de mesure. Une haute valeur de gain est obtenue malgré ces réflexions avec valeurs entre 5 et 6 dBi dans la bande adaptée (S11 < -10dB). Le gain est aussi mesuré par une fréquence fixe pour une variation de 0° à 60° dans deux plans orthogonaux. Un niveau plus faible est trouvé pour le plan E par rapport à celui du plan H et est expliqué par la présence de la sonde millimétrique dans ce plan. Un bon accord entre les mesures et la simulation est observable pour la co-polarisation comme pour la crosspolarisation dans les deux plans. Par conséquent, le DR est ainsi validé.

Figure 5 a) Adaptation et gain pour deux échantillons de 0.508 mm et b) diagramme du gain @ 56 GHz.

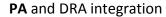

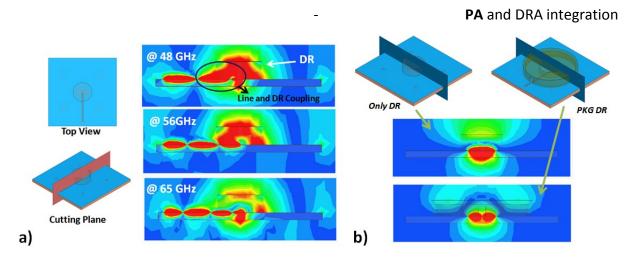

#### 4.c) Intégration du PA et DRA

Après la validation du DR, l'intégration avec le PA doit être étudiée. Dans les sections suivantes, plusieurs configurations sont présentées dans lesquelles différentes possibilités d'interconnexion et « packaging » sont explorées.

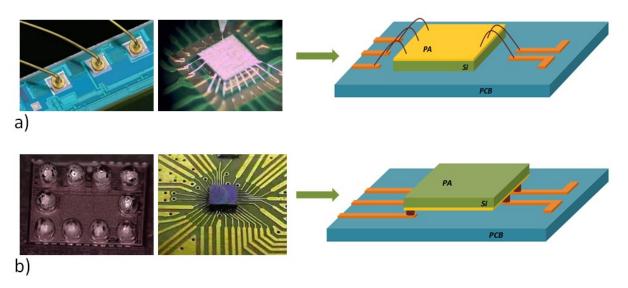

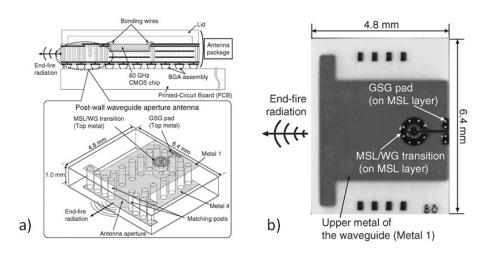

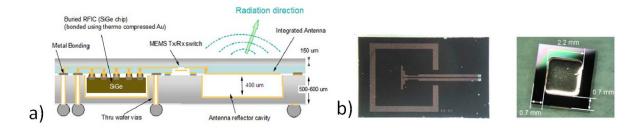

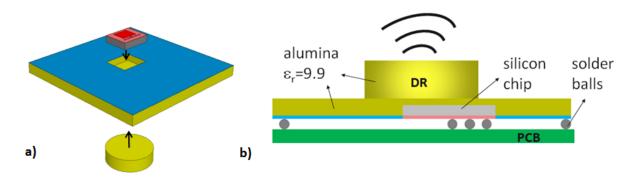

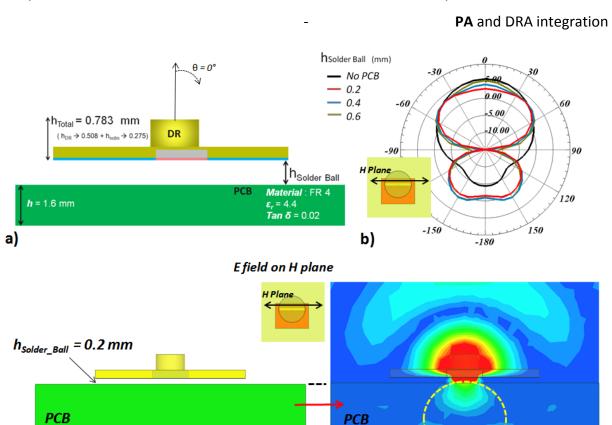

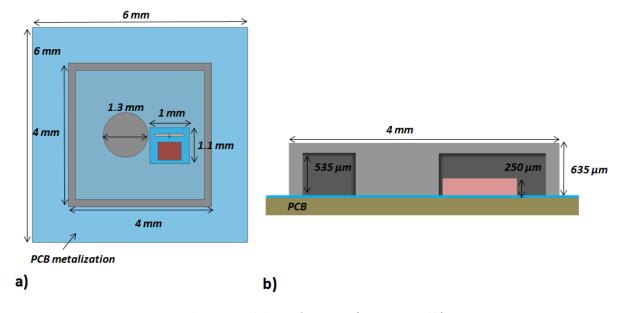

#### 4.c.i) 1ere Solution: Incorporation du PCB et ses interconnexions

Cette configuration est illustrée dans la Figure 152. La configuration proposée est basée sur l'intégration d'élément excitant (la fente) dans la structure de la technologie SOI. La puce sera introduite dans une cavité faite au niveau du substrat d'alumine. Une fois insérée, le DR est positionné par-dessus. Ici, on profite de la taille réduite de la fente grâce à la haute permittivité du silicium qui permet d'atteindre une surface comparable à celle du PA (0.5  $\mu$ m x 0.6  $\mu$ m). Ensuite, le PCB est aussi introduit au moyen des interconnexions. Ces sont des « solder balls » qui permettent d'envoyer le signal DC pour l'alimentation du PA ainsi que le

signal de 60 GHz. Une solution quasi encapsulée est donc présentée. Pour compléter l'encapsulage, comme on verra plus loin, une protection de l'environnement est nécessaire. Cette solution a été validée par simulations et quelques conclusions ont pu être tirées. Premièrement, le DRA conserve toujours ses bonnes performances : un haut gain (6dBi) et une assez large bande passante (6 GHz @ ROS <2) malgré le changement de la position de la fente par rapport au DR. Deuxièmement, l'impact du PCB sur le rayonnement est visible pour lequel, dépendant de la hauteur des « solder balls », une quantité importante est rayonnée vers le substrat diminuant ainsi le gain. Finalement, le DR comme élément indépendant de la configuration ajoute une difficulté au moment de l'aligner avec la fente. Par conséquent, un décalage en fréquence ainsi qu'une chute de gain peuvent être générés par un défaut de positionnement. Une seconde solution est donc présentée pour contourner le problème ci-dessus.

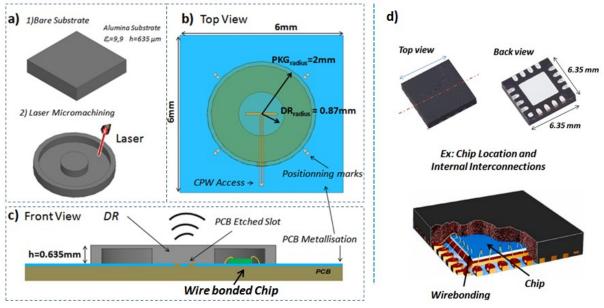

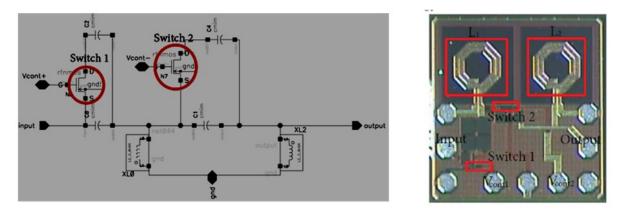

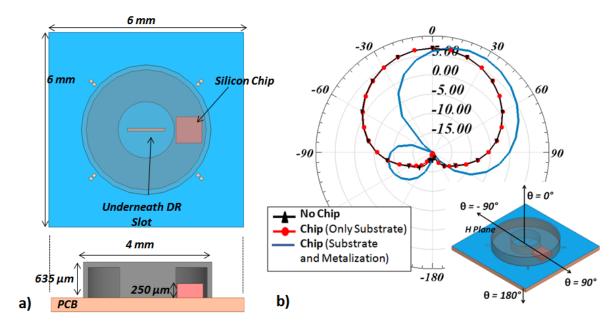

#### 4.c.ii) 2ème solution: une solution DR-fente auto-alignée

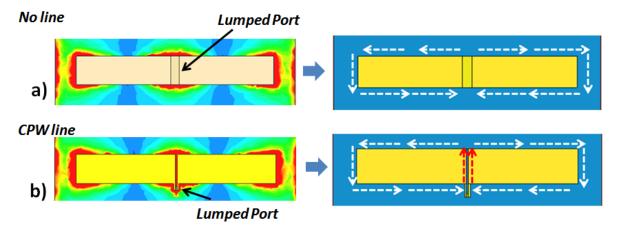

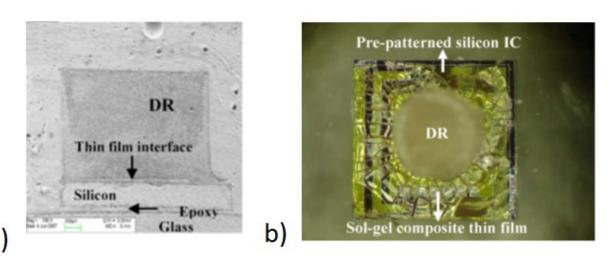

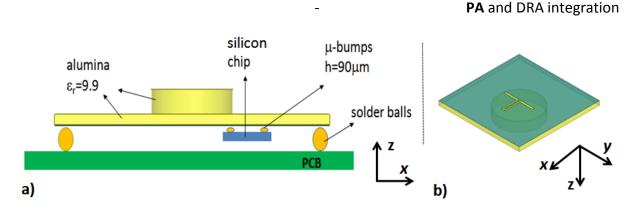

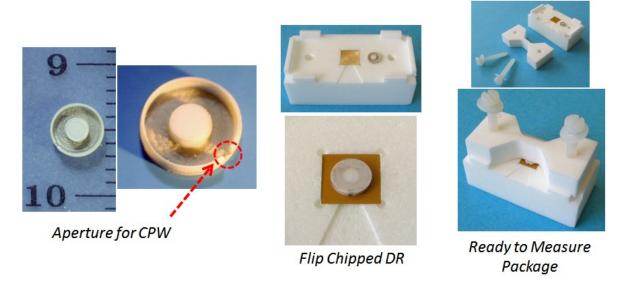

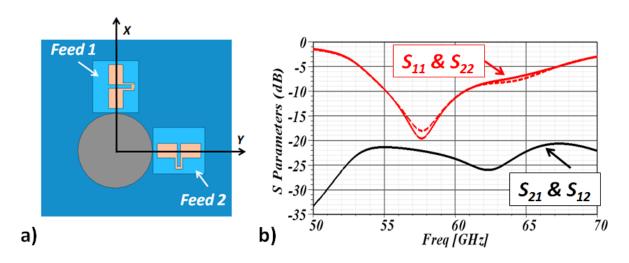

Pour maximiser le couplage et le transfert d'énergie de la fente au DR, l'alignement doit être assuré. Une nouvelle solution est donc présentée, où le DR et la fente sont fabriqués par le même procédé d'élaboration. De cette manière, le positionnement est assuré par la méthode de fabrication et non au moment de mesurer la configuration. Le procédé est montré à la Figure 155. Une fente miniature est gravée à l'arrière du substrat où le DR sera usiné ensuite par laser. Les échantillons obtenus sont aussi montrés. Une ligne coplanaire de  $50~\Omega$  est aussi gravée dans la métallisation utilisée par la fente.

Avec cette solution, une nouvelle configuration d'intégration du PA doit être introduite car la fente fait maintenant partie du DR. La Figure 156 montre cette configuration. La puce est maintenant connectée à la fente par le moyen de «  $\mu$ -solder balls » (hauteur h=90 $\mu$ m). Ils servent à établir la connexion pour le signal de 60 GHz. D'autres « solder balls » d'une hauteur plus importante sont utilisés comme support et pour l'alimentation DC. Une bonne isolation électrique est attendue entre l'antenne et la puce grâce au plan métallique de la fente qui se trouve entre les deux.

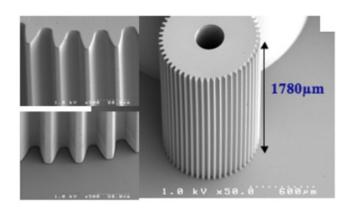

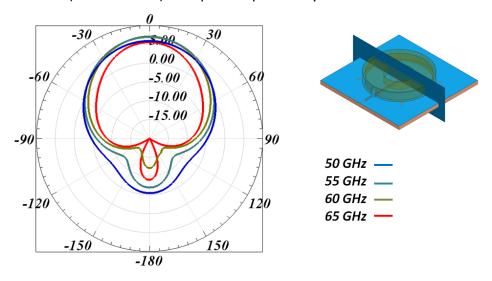

Comme auparavant, la forme finale cylindrique attendue du DRA a été modifiée et une forme conique la remplace. Cette fois-ci, un décalage en fréquence vers le haut est obtenu. Les mesures et la simulation dans la Figure 159 montrent un bon accord avec une bande passante de 6.4 GHz et un gain maximal de 5.4 dBi . Un rendement minimum de 59% est obtenu aussi dans la bande adaptée de l'antenne avec une valeur maximale de 95% @ 61.3 GHz. Six échantillons ont été mesurés pour déterminer la répétitivité et la fiabilité de l'usinage par laser. Le coefficient de réflexion de ces six échantillons montre une différence maximale de 0.6 GHz avec un rayon minimal de 1.54 mm et maximal de 1.59. Ces valeurs peuvent être réduites si d'autres techniques de fabrication sont utilisées comme par exemple un usinage par laser à haute puissance ou des techniques de moulage par injection.

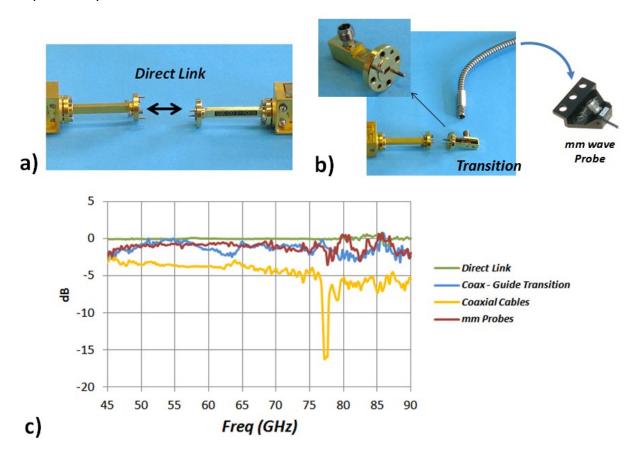

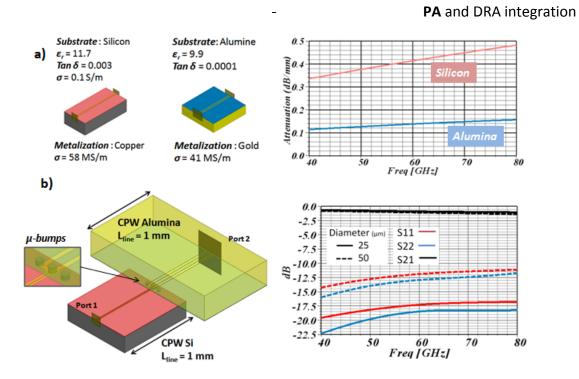

#### 4.c.iii) Pertes des interconnexions

Pour l'intégration de la puce, comme présenté dans les pages précédentes, les interconnexions sont faites au moyen des "μ-bumps". Cette interconnexion présente un changement d'impédance et un mode pour la liaison entre les deux lignes coplanaires. Un changement d'impédance et de mode ajoute des pertes au système. Pour quantifier le niveau de pertes qu'on pourrait attendre, la configuration montrée dans la Figure 160 est proposée. Les deux lignes coplanaires (sur alumine et sur silicium) exhibaient des pertes respectivement de 0.15 dB et de 0.4 dB. Ensuite, une simulation des deux lignes liées par les "μ-bumps" est faite. Aujourd'hui, le pitch des "μ-bumps" selon [40] atteint les 50 et 100 μm

pour des diamètres respectivement de 25 ou 50  $\mu$ m. Pour obtenir les pertes ajoutées par l'interconnexion, les pertes de lignes sont déduites de la valeur du S21 obtenue pour la configuration complète. Un niveau de perte de 0.44 et de 0.24dB est donc obtenu pour des diamètres respectivement de 100 et 50  $\mu$ m.

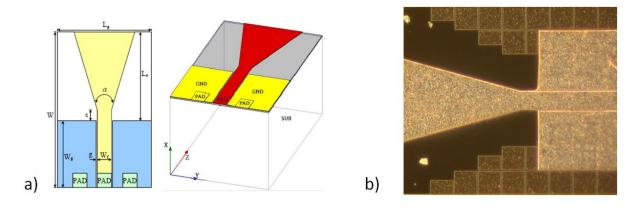

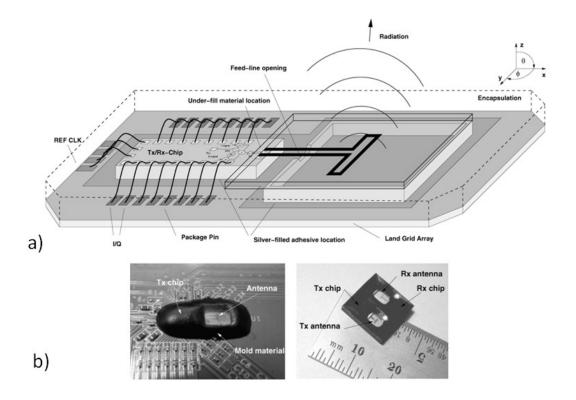

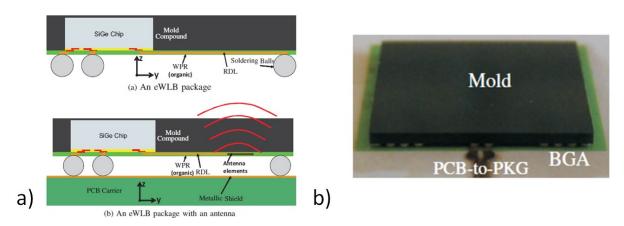

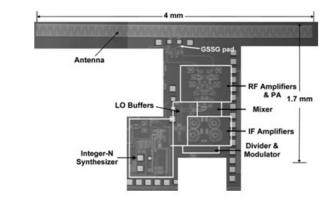

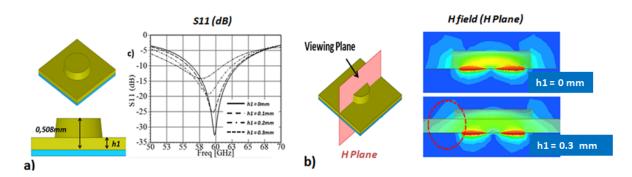

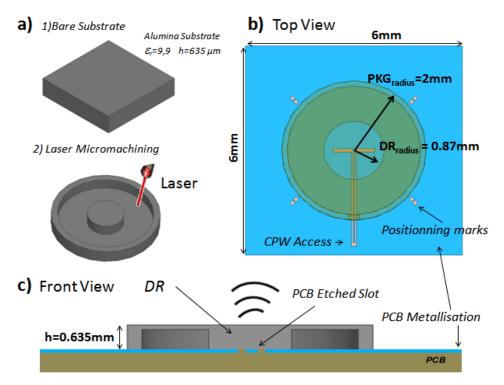

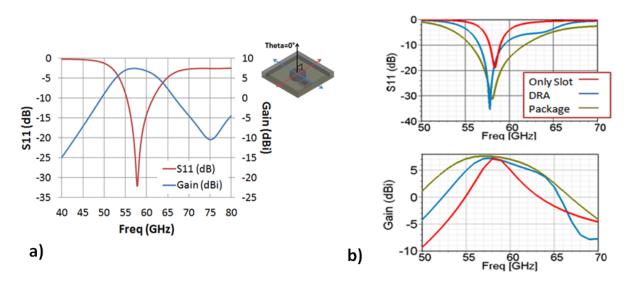

#### 4.c.iv) 3ème solution: solution complètement encapsulée

Dans les solutions présentées antérieurement, la puce ne se trouve pas dans une configuration complètement encapsulée. L'utilisation des "bumps" comme support mécanique ne remplit pas la définition d'une solution intégralement encapsulée. Selon [41], l'encapsulage pour des circuits intégrés doit assurer une connexion électrique, un support mécanique, une protection environnementale et un chemin de conductivité thermique pour la dissipation de la chaleur. Dans les solutions précédentes, la connexion électrique et aussi le support mécanique sont intégrés aux configurations. Dû à la basse puissance de travail, la dissipation de puissance peut être négligée. Par contre, la protection environnementale n'a pas été toujours prise en compte. Pour ceci, une nouvelle solution est maintenant présentée et montrée dans la Figure 6. L'antenne devient une partie de l'encapsulage.

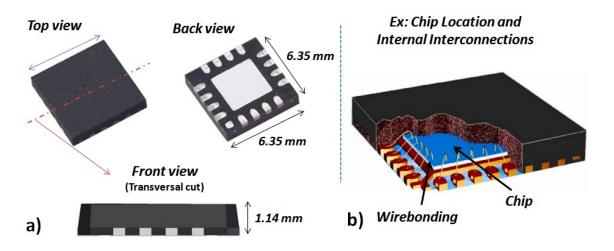

Figure 6 : a) Procédé de fabrication b) Vue d'en haut c) Vue de face (PCB, Antenne et intégration de la chip) et d) exemple de mise en boîtier QFN (utilisation industrielle<sup>2,3</sup>)

L'antenne et le package sont usinés par laser en même temps à partir d'un substrat d'alumine. Le package est donc « flip-chipped » sur le PCB où une fente a été gravée précédemment. L'antenne-boitier pourra ensuite héberger la chip qui peut être interconnectée au CPW de la fente par bonding (comme montré dans la figure) ou par des  $\mu$ -bumps. On peut comparer cette mise en boîtier à celle QFN d'utilisation industrielle où les interconnections électriques ainsi que la protection environnementale se font de manière similaire. Comme avantage, notre mise en boîtier inclut l'antenne. L'ensemble fait

\_

<sup>&</sup>lt;sup>2</sup> http://www.pcb-3d.com/models/

<sup>&</sup>lt;sup>3</sup> http://www.obs.u-bordeaux1.fr

maintenant une taille globale de 36mm<sup>2</sup>, une taille comparable aux QFN qui mesurent 40 et 57 mm<sup>2</sup> [42]. L'antenne et le boîtier usinés sont montrés dans la Figure 174.

Comme nous l'avons vu, l'usinage du boitier par le laser a modifié la forme du DRA et les parois externes. Ces modifications ont été prises en compte par retro-simulation et les résultats sont montrés dans la Figure 175. Un assez bon accord est trouvé entre la simulation et les mesures. Un décalage en fréquence de 3 GHz est visible pour la réponse du S11. Il peut être expliqué par le désalignement de la fente par rapport au DR. De fortes ondulations sont aussi repérées, probablement produites par des signaux réfléchis par le banc de mesure. Pourtant, un bon niveau de gain (> 5 dBi) est trouvé dans la bande adaptée. Le problème de désalignement de la fente par rapport au DR est de retour dans cette solution et c'est pour cela qu'une nouvelle configuration est présentée ci-après.

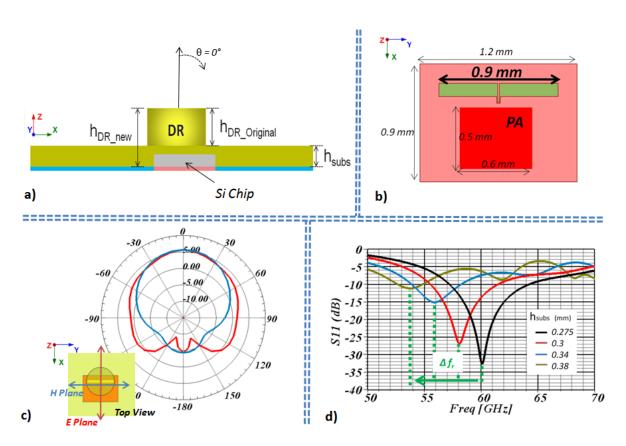

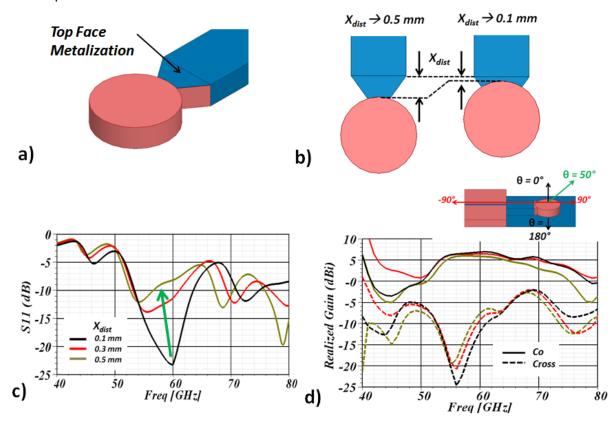

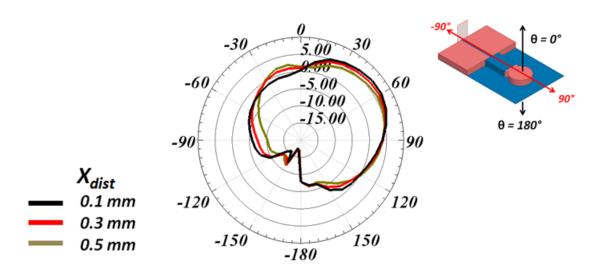

# 4.c.v) 4ème solution: Réduction de l'impact du désalignement fente-DR et les pertes des interconnections

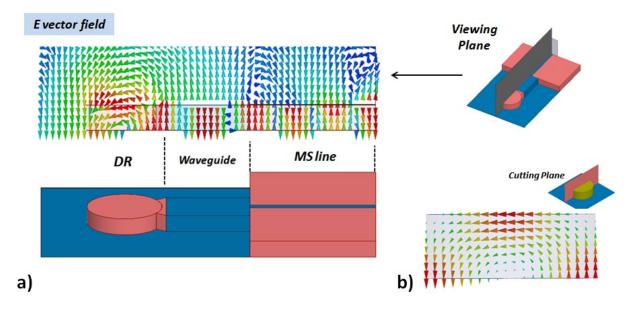

Dans la solution précédente, une très haute précision est nécessaire pour le positionnement de la fente et le DR. Un décalage en fréquence de 3GHz peut être attendu avec une séparation de 5 µm entre le plan métallique de la fente et le DR. Ce résultat montre l'importance de l'interphase d'air entre les deux éléments. Une excitation latérale est maintenant introduite, où la fente d'excitation reste intégrée dans le silicium mais positionnée à coté du DR, générant ainsi un couplage latéral. Cette configuration est montrée à la Figure 177. La position de la fente doit être assurée de telle façon qu'elle corresponde au champ magnétique du mode TM<sup>11</sup> (Figure 178).

La même stratégie de boitier est utilisée malgré le changement de forme (circulaire à rectangulaire). Cette configuration présente aussi un avantage au niveau des interconnections où, à la différence du cas précédent, la fente et le PA n'ont pas besoin de connexions. Une connexion sur le silicium est suffisante et de cette manière les pertes par interconnexion peuvent être réduites.

L'interaction entre la fente et le DR est visualisée à la Figure 179. Le champ magnétique est montré dans un plan qui coupe la structure par la zone de champ maximum. Une concentration significative du champ est trouvée dans le DR et contribue de façon significative au rayonnement global de la configuration. L'effet du DR et du boitier est aussi évident dans les courbes de gain. Trois configurations ont été étudiées : i) fente seule, ii) fente + DRA et iii) fente + DRA + boitier. Dans cette configuration la fente passe d'un état non-résonant à un état résonant; pour cela une partie du rayonnement proviendra de la fente et peut être visualisée pour une haute valeur de gain avec la première configuration. À mesure qu'on ajoute les autres éléments, la bande passante s'améliore, passant de 2 à 6 GHz. Ce comportement est aussi présent pour le gain, qui pour la configuration complète arrive à avoir un niveau de 6 dBi dans toute la bande.

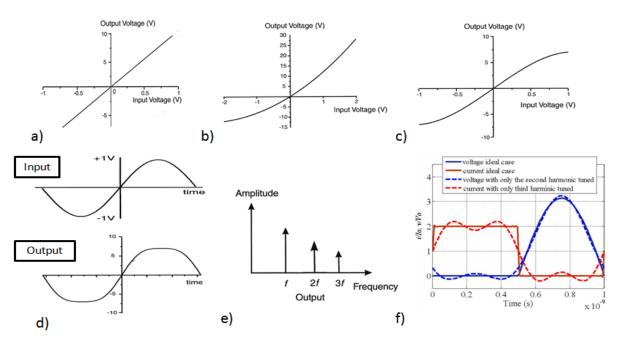

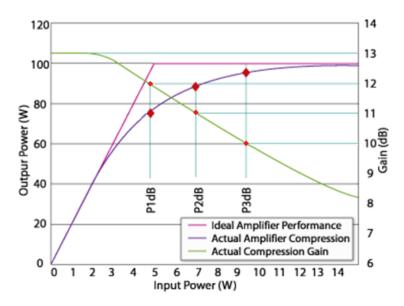

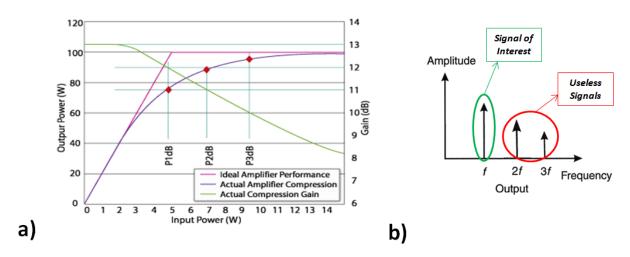

# 5) Antenne doublement alimentée pour une amélioration du rendement du PA

Dans la section 4, les éléments passifs ont été repérés comme une des sources des pertes du PA. Mais elle n'est pas la seule. Dans la Figure 183, la courbe du gain du PA est montrée par rapport à la puissance d'entrée. Deux régions d'amplification sont montrées par la courbe mauve. Une région de gain linéaire jusqu'à 3W de puissance d'entrée et après un gain asymptotique qui fait que la courbe de gain (courbe verte) descend à mesure que la

puissance d'entrée augmente. Cette baisse dans le gain dans la deuxième région est due à l'effet de la saturation du PA qui ajoutera des harmoniques supérieures au signal de sortie. L'énergie totale sera donc redistribuée dans les différentes harmoniques et le signal d'intérêt aura moins de puissance à mesure que les harmoniques augmentent. Ce sont, en fait, ces signaux supplémentaires ajoutés à la saturation du PA qu'on visera à réduire en utilisant l'antenne en plus de son rôle d'élément rayonnant.

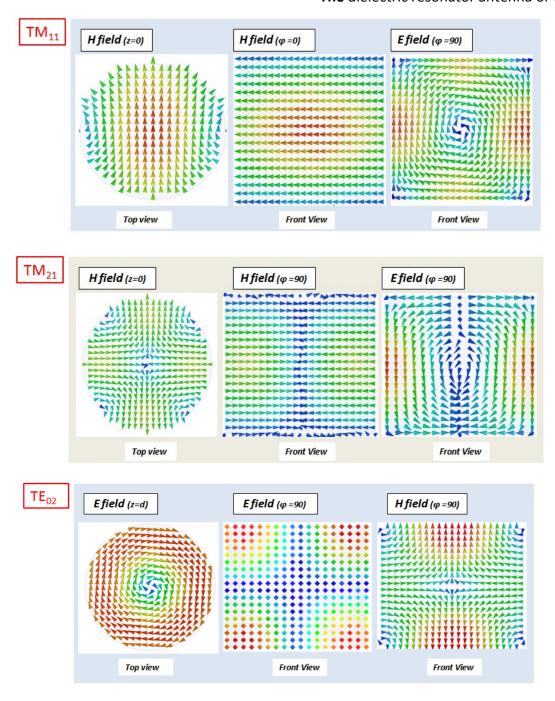

#### 5.a) Multi PA solution

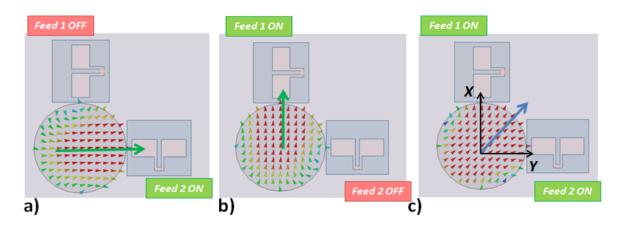

Pour éviter la saturation, le PA est limité à travailler dans la région linéaire. De cette façon, une réponse de haut gain et haute linéarité est possible. Le seul problème avec cette région d'opération est la basse puissance de sortie. Une augmentation de cette puissance de sortie peut être envisagée si, à la place d'utiliser un seul PA, un deuxième PA est ajouté à la configuration. Deux PA en parallèle de puissance réduite mais fonctionnant dans la zone linéaires vont s'additionner pour avoir un seul signal de sortie de haute puissance et toujours en fonctionnement linéaire, évitant ainsi les harmoniques. L'antenne sera dans ce cas, non seulement un élément rayonnant mais elle fera aussi l'addition des signaux des deux PA indépendants.

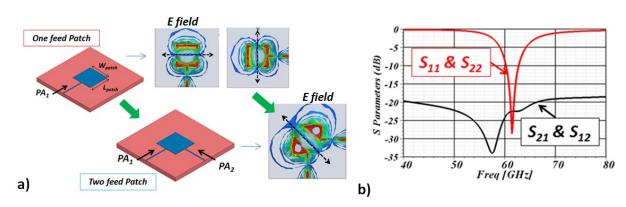

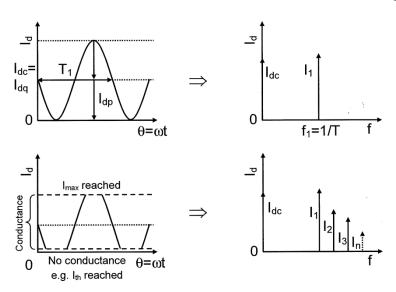

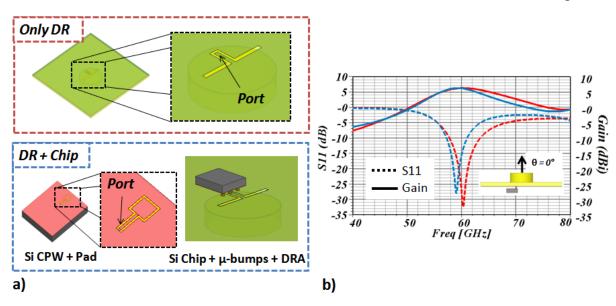

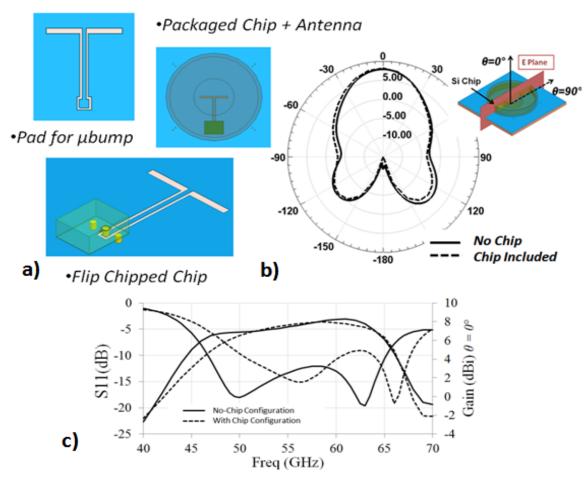

#### 5.a.i) Contraintes et conséquences d'une alimentation multiple

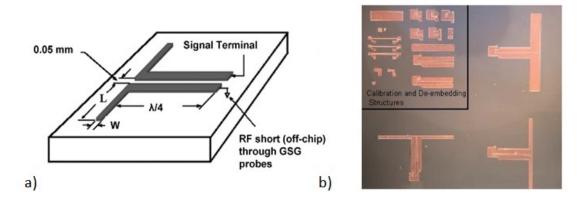

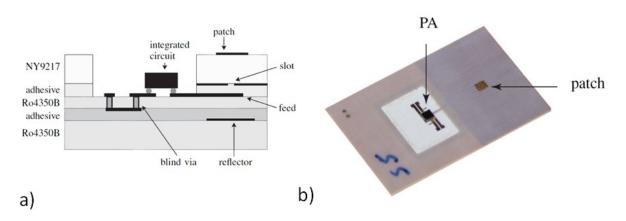

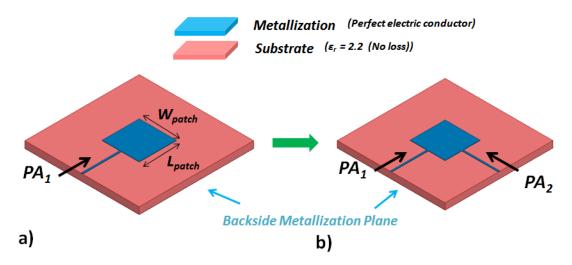

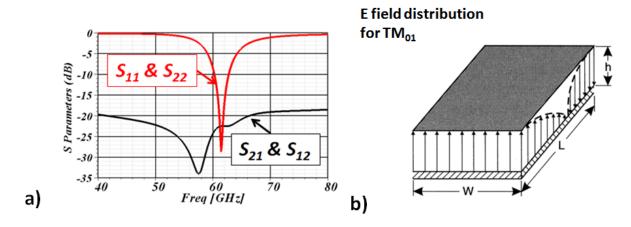

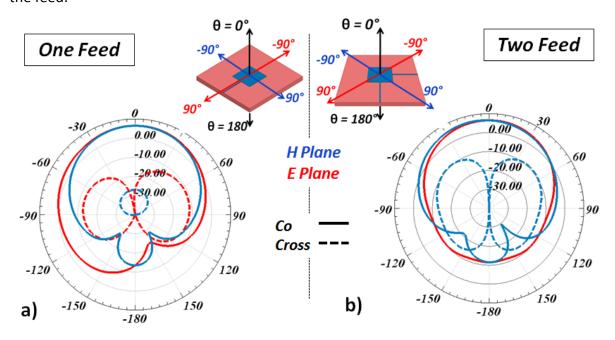

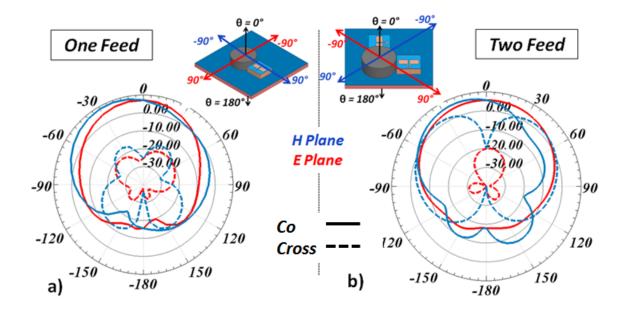

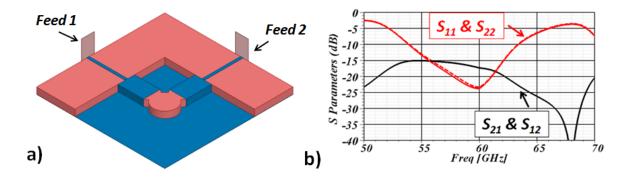

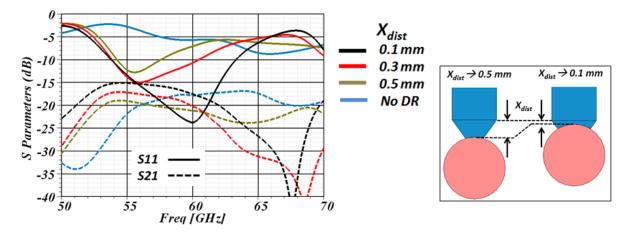

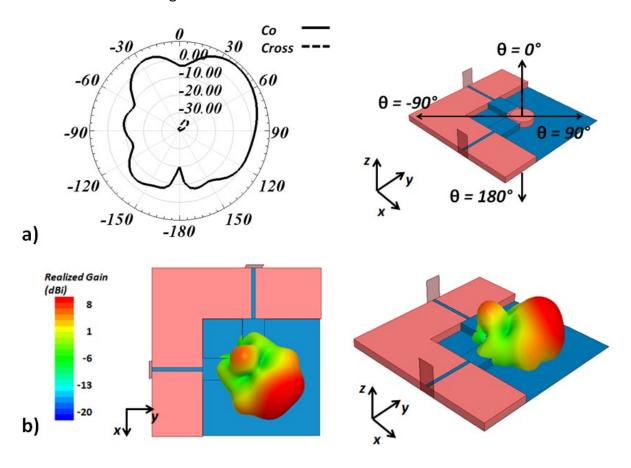

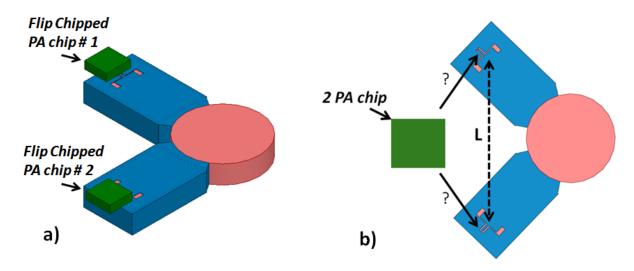

Une configuration initiale d'un patch multi-alimenté est présentée à la Figure 7 qui permettra d'établir les possibles conséquences et contraintes pour les antennes multi-alimentées. Les PA vont donc partager la même antenne et à partir de là, un problème d'isolation entre les sources devient évident. L'isolation entre les multiples alimentations de l'antenne devient désormais une des contraintes de la configuration. L'isolation, elle, sera montrée par des paramètres S de transmission de l'antenne et une valeur de -20 dB devra être assurée. Dans le cas de patchs, une valeur de -23 dB est obtenue dans la fréquence de résonance (61 GHz).

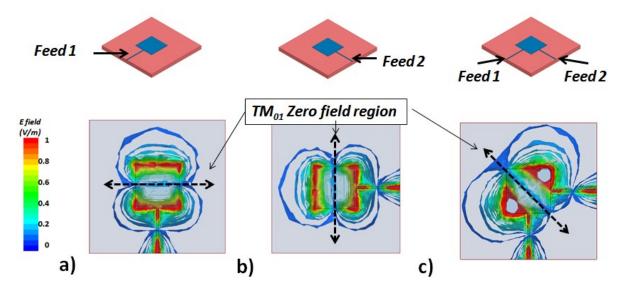

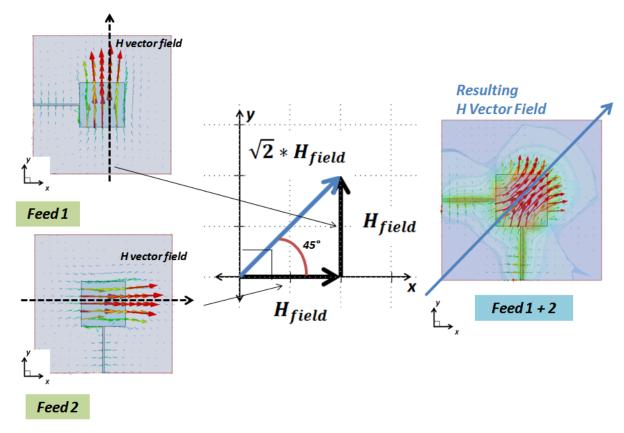

Figure 7 : a)Passage d'une seule alimentation à deux alimentations et le champ E dans le substrat. b) S Paramètres pour la configuration des deux alimentations

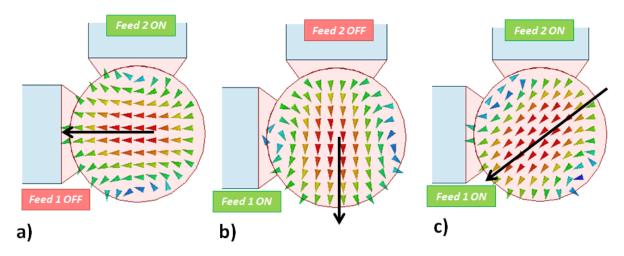

Un deuxième changement est visible aussi dans la polarisation de l'antenne. Il est illustré par la rotation du champ E dans le substrat dans la Figure 184. Initialement, les champs sont montrés pour des configurations d'alimentation simple où une orthogonalité entre les deux cas est observée. Au moment d'alimenter simultanément l'antenne par les deux ports, l'addition des champs produit une rotation du champ de 45° qui se traduit par une rotation de la polarisation linéaire de l'antenne.

En identifiant maintenant les contraintes que peuvent avoir les solutions d'antenne à multiples alimentations, une technologie de mise en boîtier sera introduite et les possibilités pour la réalisation d'un DRA de multiple alimentation présentées.

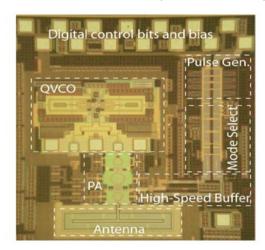

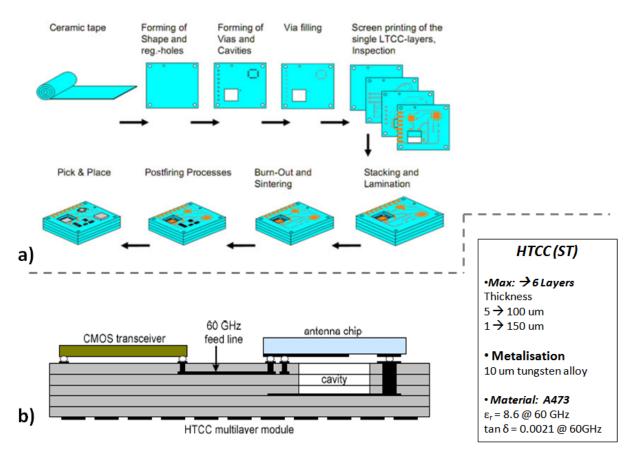

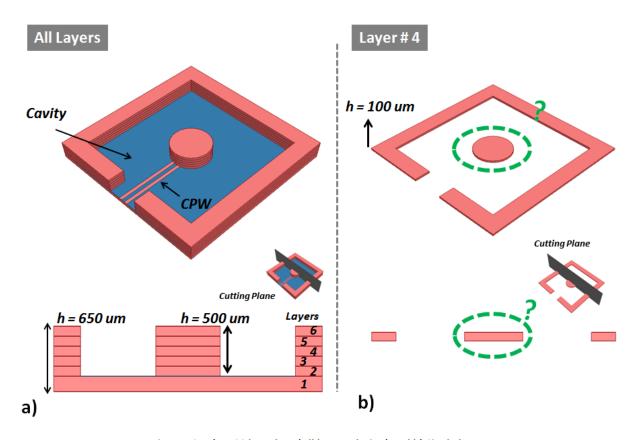

# 5.b) Technologie de mise en boîtier HTCC et ses possibilités pour l'usinage du DRA

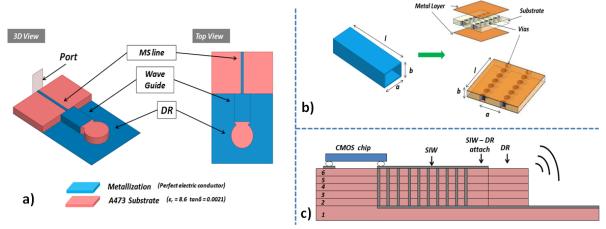

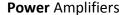

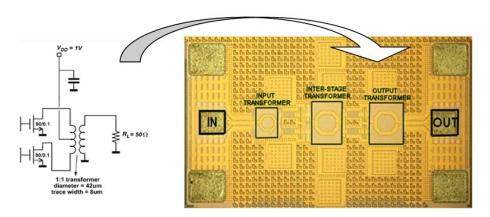

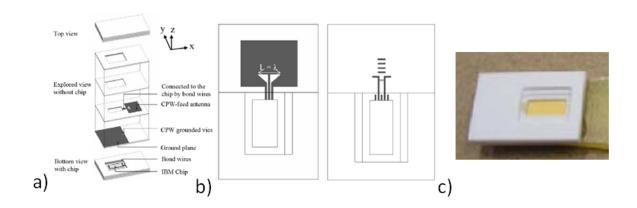

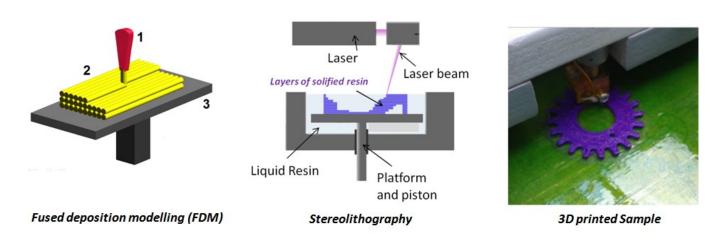

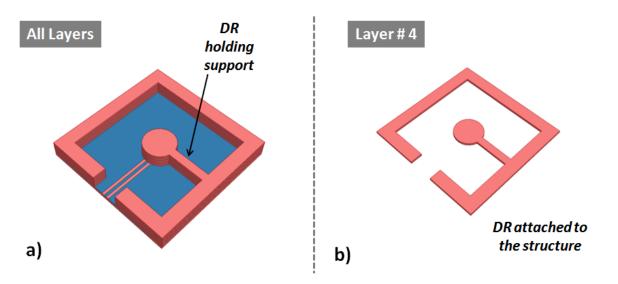

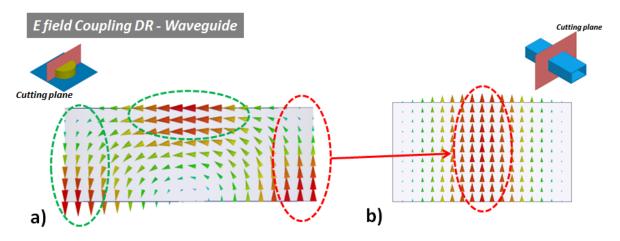

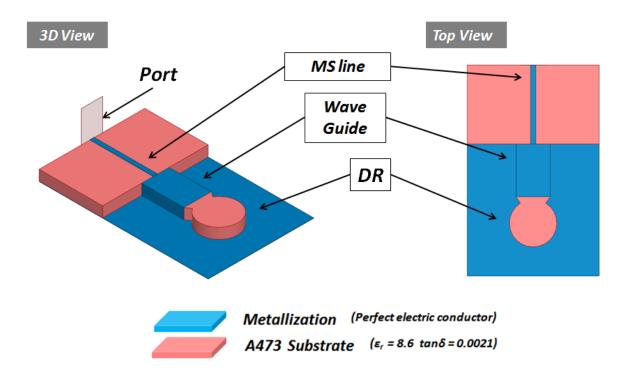

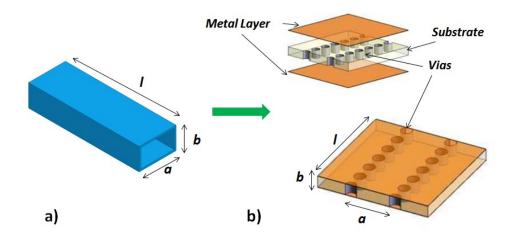

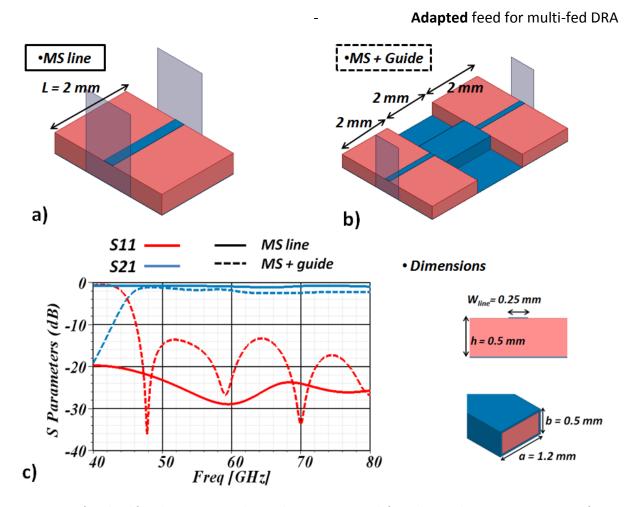

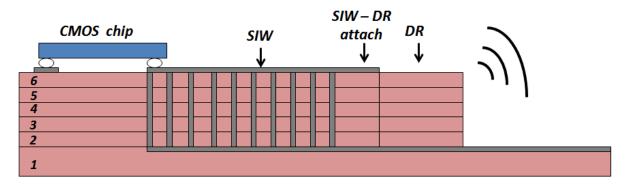

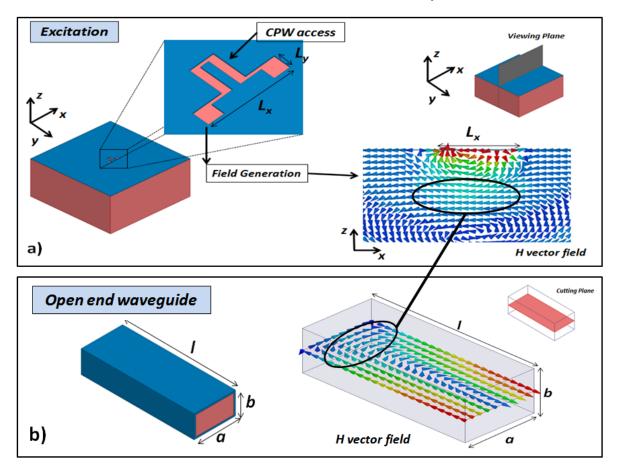

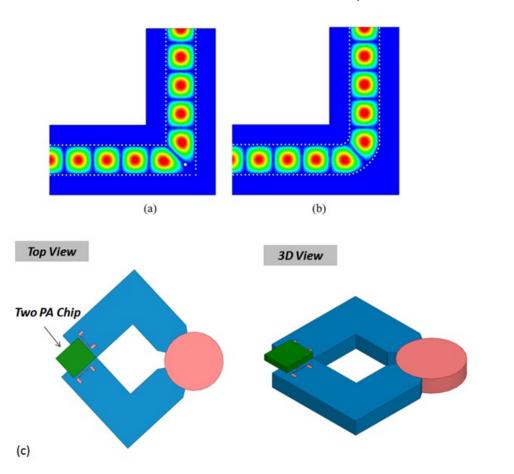

LTCC ou HTCC (Low or High Temperature Co-Fired Ceramics) est une technologie pour la mise en boîtier en région millimétrique. Elle permet l'intégration de circuits actifs avec des éléments passifs. Elle offre donc des possibilités intéressantes pour nos solutions PA et antenne. Ces technologies consistent en l'empilement de plusieurs couches de céramique qui peuvent ou pas être métallisées. Pour le cas du HTCC, la céramique offre une permittivité de 8.6 et un tan  $\delta$  = 0.0021 @ 60 GHz. Ces valeurs permettent de penser à la fabrication de l'antenne à partir du matériel même, par exemple une antenne DR. Un des inconvénients pour l'usinage d'une DRA (par exemple celle de la section 5 avec une excitation par-dessous) c'est l'imposition d'une liaison entre tous les éléments pour chacune des couches dans lesquelles est divisée la structure. Pour certaines couches du DR, le cylindre restera isolé du reste de la structure et sa position finale ne pourra pas être assurée lors de l'empilement final. C'est pour cela qu'une nouvelle excitation pour le DR est présentée. Cette fois-ci, une excitation latérale du DR est réussie par le moyen d'une guide d'onde (Figure 8 a). Le guide d'onde montré est impossible à usiner dans la technologie multicouche dû à l'impossibilité d'élaborer la métallisation verticale pour les parois de la guide. Un guide d'onde dont les parois sont construites par des trous métallisés (« vias »), aussi nommé SIW (Substrate Integrated Waveguide), peut être utilisé tel que présenté à la Figure 8 c).

Figure 8 : a) DR excité latéralement par un guide d'onde, b) Guide d'onde et SIW (Substrate Integrated Waveguide) et c)

Solution d'intégration

#### 5.c) Double alimentation pour un DR