## Architectures matérielles pour filtres morphologiques avec des grandes éléments structurants

Jan Bartovsky

#### ▶ To cite this version:

Jan Bartovsky. Architectures matérielles pour filtres morphologiques avec des grandes éléments structurants. Autre [cs.OH]. Université Paris-Est; Západočeská univerzita (Pilsen, République tchèque), 2012. Français. NNT: 2012PEST1060 . tel-00788984

## HAL Id: tel-00788984 https://theses.hal.science/tel-00788984

Submitted on 15 Feb 2013

HAL is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

#### UNIVERSITE PARIS-EST: Ecole doctorale MSTIC

and

#### University of West Bohemia in Pilsen

### **THESIS**

to obtain the Doctor of Philosophy degree of the University Paris-Est with specialization in Computer Sciences

# Hardware Architectures for Morphological Filters with Large Structuring Elements

## Jan Bartovský

presented on November 14<sup>th</sup> 2012

#### Composition of the Examination Committee:

| Michal KOZUBEK     | Professor, Masaryk University Brno | Reviewer   |

|--------------------|------------------------------------|------------|

| Olivier DÉFORGES   | Professor, INSA Rennes             | Reviewer   |

| Mohamed AKIL       | Professor, ESIEE Paris             | Director   |

| Vjačeslav GEORGIEV | V Assoc. professor, UWB Pilsen     | Director   |

| Eva DOKLÁDALOV     | Á Assoc. professor, ESIEE Paris    | Examinator |

| Petr DOKLÁDAL      | Research engineer, ARMINES Paris   | Examinator |

| Václav MATOUŠEK    | Professor, UWB Pilsen              | Examinator |

| Michel BILODEAU    | Research engineer, ARMINES Paris   | Examinator |

# **Abstract**

Bartovský, J. Hardware Architectures for Morphological Filters with Large Structuring Elements. University Paris-Est, University of West Bohemia. Directors: Mohamed Akil, Vjačeslav Georgiev.

This thesis is focused on implementation of fundamental morphological filters in the dedicated hardware. The main objective of this thesis is to provide a programmable and efficient implementation of basic morphological operators using efficient dataflow algorithms considering the entire application point of view.

In the first part, we study existing algorithms for fundamental morphological operators and their implementation on different computational platforms. We are especially interested in algorithms using the queue memory because their implementation provides the sequential data access and minimal latency, the properties very beneficial for the dedicated hardware. Then we propose another queue-based arbitrary-oriented opening algorithm that allows for direct granulometric measures. Performance benchmarks of these two algorithms are discussed, too.

The second part presents hardware implementation of the efficient algorithms by means of stream processing units. We begin with a 1-D dilation unit, then thanks to the separability of dilation we build up 2-D rectangular and polygonal dilation units. The processing unit for arbitrary-oriented opening and pattern spectrum is described as well. We also introduce a method of parallel computation using a few copies of processing units in parallel, thereby speeding up the computation. All proposed processing units are experimentally assessed in hardware by means of FPGA prototypes, and the performance and FPGA occupation results are discussed.

In the third part, the proposed units are employed in two diverse applications illustrating thus their capability of addressing performance-demanding, low-power embedded applications.

The main contributions of this thesis are: 1) new algorithm for arbitrary-oriented opening and pattern spectrum, 2) programmable hardware implementation of fundamental morphological operators with large structuring elements and arbitrary orientation, 3) performance increase obtained through multi-level parallelism. Results suggest that the previously unachievable, real-time performance of these traditionally costly operators can be attained even for long concatenations and high-resolution images.

## Keywords

Mathematical morphology, morphological filter, hardware implementation, algorithm, FPGA.

## Résumé

Bartovský, J. Architectures matérielles pour filtres morphologiques avec des éléments structurants de grande taille. Université Paris-Est, L'Université de Bohême de l'Ouest. Directeurs: Mohamed Akil, Vjačeslav Georgiev.

Le sujet de cette thèse concerne l'architecture matérielle et la mise en oeuvre de filtres morphologiques, basés sur des itérations d'érosions/dilatations. L'objectif principal de cette thèse est de proposer une mise en oeuvre efficace et programmable de ces opérateurs en utilisant des algorithmes en flot de données tout en tenant compte des besoins applicatifs globaux.

Dans la première partie, nous étudions les algorithmes existants d'opérateurs morphologiques et leur réalisation sur différentes plates-formes informatiques. Nous nous intéressons plus particulièrement à un algorithme de dilatation basé sur une file d'attente car il permet de réaliser l'accès séquentiel aux données avec une latence minimale, ce qui est très favorable pour le matériel dédié. Nous proposons ensuite un autre algorithme basé aussi sur une file d'attente réalisant l'ouverture morphologique directionnelle, pour angle arbitraire, et qui permet d'obtenir directement des mesures de granulométrie.

La deuxième partie présente la mise en oeuvre matérielle des algorithmes efficaces au moyen d'unités de traitement à flot de données. Nous commençons par l'unité de dilatation 1-D, puis grâce à la séparabilité de la dilatation nous construisons des unités 2-D rectangulaire et polygonale. L'unité de traitement pour l'ouverture directionnelle et de son spectre est aussi décrite. Nous présentons également une méthode de parallélisation de calcul en dupliquant des unités de traitement. Toutes les unités de traitement proposées sont évaluées expérimentalement par la réalisation des prototypes à base de circuits programmables (FPGA). Les résultats en termes d'occupation de surface et de vitesse de traitement sont également discutés.

Dans la troisième partie, les unités de calcul proposées sont utilisées dans deux applications différentes, illustrant ainsi leur capacité de répondre aux exigeances des applications embarquées a basse consommation.

Les principales contributions de cette thèse sont : i) la proposition d'un nouvel algorithme d'ouverture directionnelle à angle quelconque, ii) la réalisation des architectures matérielles dédiées et programmables d'opérateurs morphologiques pour de grands éléments structurants et à angle quelconque ; iii) l'exploitation de plusieurs niveaux de parallélisme afin d'améliorer les performances. Les performances obtenues permettent de faire du temps-réel et de concaténer plusieurs opérateurs sur des images à haute résolution.

#### Mots clefs

Morphologie mathématique, filtre morphologique, la mise en oeuvre du matériel, algorithme, FPGA.

## Anotace

Bartovský, J. Číslicové architektury morfologických filtrů s velkými strukturujícími elementy. Univerzita Paris-Est, Západočeská univerzita v Plzni. Vedoucí: Mohamed Akil, Vjačeslav Georgiev.

Tato práce se zabývá implementací základních morfologických filtrů v číslicových obvodech. Hlavním úkolem této práce je vytvořit programovatelné a efektivní číslicové implementace základních morfologických operátorů za použití výpočetně efektivních algoritmů. Důležitým hlediskem je chování celé aplikace složené z více operátorů.

V první části jsou prostudovány existující algoritmy základních morfologických operátorů a jejich realizace na vhodných výpočetních platformách. Z existujících algoritmů se pro implementaci dilatace jako nejvhodnější jeví algoritmy využívající paměť fronty. Důvodem jsou vhodné vlastnosti pro číslicové obvody, sekvenční přístup k datům a minimální latence. Posléze navrhneme a popíšeme vlastní algoritmus morfologického otevření využívající stejnou paměť fronty, který umožňuje výpočet pod libovolným úhlem a přímý výpočet granulometrie. Výkonnostní parametry obou dvou algoritmů jsou zde diskutovány.

Druhá část obsahuje popis obvodové implementace těchto algoritmů ve formě výpočetních jednotek. Napřed vytvoříme 1-D jednotku dilatace, pomocí které díky rozložitelnosti dilatace vytvoříme 2-D jednotku dilatace pomocí obdélníků a polygonů. Návrh výpočetní jednotky algoritmu orientovaného otevření a spektra vzorů je také uveden v této části. Abychom dosáhli vyššího výpočetního výkonu, použijeme metodu paralelního výpočtu, která využívá několika kopií použitých výpočetních jednotek pracujících ve stejném čase. Všechny navržené výpočetní jednotky byly experimentálně ověřeny v číslicových obvodech typu FPGA, výsledky výpočetního výkonu a potřebné plochy čipu jsou diskutovány.

Ve třetí části jsou navržené výpočetní jednotky použity ve dvou různých aplikacích, čímž ilustrují svoji využitelnost v embedded aplikacích vyžadujících velmi velký výpočetní výkon a zároveň nízkou spotřebu.

Hlavní přínosy této práce jsou následující: 1) vlastní algoritmus morfologického otevření a spektra pod libovolným úhlem, 2) číslicová implementace základních morfologických operátorů filtrů s velkými a libovolně orientovanými strukturujícími elementy, 3) zvýšení výpočetního výkonu díky víceúrovňovému paralelnímu výpočtu. Dosažené výsledky ukazují, že výpočet těchto náročných operátorů v reálném čase, kterého dosud nebylo možné docílit, je nejen dosažitelný ale i udržitelný pro dlouhé zřetězené filtry a vysoké rozlišení zpracovávaných obrazů.

#### Klíčová slova

Matematická morfologie, morfologický filtr, obvodová implementace, algoritmus, FPGA.

# Acknowledgment

I am glad to express hearty appreciation to my thesis directors Mohamed Akil and Vjačeslav Georgiev for their time, patience, consideration, and support by thoughts and motivation. Their kind and selfless help in both thought and bureaucratic crises was highly appreciated.

I am very grateful to my thesis advisors Eva Dokládalová and Petr Dokládal for their tremendously kind, insight, endless support. Without their everyday effort in enhancing my work the thesis could not have been completed in time.

I am very thankful to Michel Bilodeau who accepted me into the FREIA project, and thereby opened the doors to the Centre of Mathematical Morphology for me.

I am grateful to Michel Couprie, Thierry Grandpierre, Laurent Perroton, Hugues Talbot, Eric Llorens, Christine Auger, and the other members of the A3SI team at ESIEE Paris for friendly welcome and nice working environment.

My internship in the Centre of Mathematical Morphology was very inspiring and fruitful. The credit goes to all the staff: Fernand Meyer, Dominique Jeulin, Serge Beucher, Étienne Decenciére, Jesús Angulo, Beatriz Marcotegui, Petr Matula, Guillaume Thibault, Catherine Moysan, and the others.

I would like to thank all my fellow students and colleagues Václav Kraus, Aleš Krutina, Radek Šalom, Michael Holík, Martin Poupa, Nicolas Ngan, Imran Taj, Ramzi Mahmoudi, Rostom Kachouri, Jeoffroy Marbeaux, Oussama Feki, Xiwei Zhang, Vincent Morard, Santiago Velasco, and many others.

I should also thank the members of examination committee Olivier Déforges, Michal Kozubek, and Václav Matoušek for their time necessary to read and understand the manuscript.

The most eminent thanks goes to my parents who were unconditionally encouraging me during the entire university study to achieve the goals I can be proud of.

# Glossary

### List of Symbols

$\alpha$  Orientation of the line SE

$\varphi$  Closing

Complementation operator

$\delta$  Dilation  $\varepsilon$  Erosion

I, f Discrete image

Q Set of rational numbersmod Remainder of integer division

$\gamma$  Opening

X, Y Set

$\mathbb{Z}$  Set of integer numbers

$\zeta$  Serial concatenation of operators

AQ Array of Queues B Structuring element l Length of the SE

$N \times M$  Width×height of the image

Q Queue

$W \times H$  Width×height of the SE

$\mathcal{O}_{\mathrm{image}}$  () Computational complexity against the whole image

$\mathcal{O}()$  Computation complexity

#### List of Abbreviations

$n ext{-D}$   $n ext{-Dimension(al)}$  ALU Arithmetic Logic Unit AR Average pixel Rate

ASF $^{\lambda}$   $\lambda$ -order Alternate Sequential Filter ASIC Application-Specific Integrated Circuit

bpp Bits Per Pixel

BRAM Block RAM memory

CAM Content Addressable Memory

CCT Connected Component Tree

CPU Central Processing Unit

DMA Direct Memory Access

FIFO First In First Out

FPGA Field-Programmable Gate Array

FPS Frame-Per-Second ratio

FREIA Framework for Embedded Image Applications

FSM Finite State Machine

GPP General-Purpose Processor GPU Graphics Processing Unit HDTV High-Definition Television

HGW Dilation algorithm proposed by van Herk, and Gil and Werman

HW Hardware

LUT Look-Up Table

MMB Mathematical Morphology Blocks MPMC Multi-port Memory Controller

PLB Peripheral Local Bus

PoC Processor-on-chip

PRR Partial-Result Reuse

RAM Random Access Memory

SE Structuring Element

SIMD Simple Instruction, Multiple Data

SoC System-on-chip

SSE Streaming SIMD Extension

TEMAC Tri-Mode Ethernet Media Access Controller

UHDTV Ultra High-Definition Television VFBC Video Frame Buffer Controller

VHDL Very-high-speed integrated circuits Hardware Description Language

VLIW Very Long Instruction Word

# Contents

| 1 | Intr | oduction  | n                                                     | 1          |

|---|------|-----------|-------------------------------------------------------|------------|

|   | 1.1  | Applicat  | tions of Mathematical Morphology                      | 2          |

|   |      | 1.1.1 V   | Vision Application Constraints                        | 3          |

|   | 1.2  | Roles of  | Dedicated Hardware for Vision Applications            | 4          |

|   | 1.3  | Contribu  | utions of the Thesis                                  | 5          |

|   | 1.4  | Outline   |                                                       | 6          |

| 2 | Fun  | damenta   | al Operators of Mathematical Morphology               | 9          |

|   | 2.1  | Erosion   | and Dilation                                          | 10         |

|   |      | 2.1.1     | Composition of Structuring Elements                   | 13         |

|   | 2.2  | Opening   | g and Closing                                         | 14         |

|   | 2.3  | Alternat  | ting Sequential Filters                               | 14         |

|   | 2.4  | Granulo   | emetry and Pattern Spectrum                           | 16         |

| 3 | Sta  | te of the | e Art                                                 | 21         |

|   | 3.1  | Advance   | es of Basic Morphology Algorithms                     | 22         |

|   |      | 3.1.1 1   | I-D Dilation Algorithms                               | 22         |

|   |      | 3.1.2     | 2-D Dilation Algorithms                               | 24         |

|   |      | 3.1.3     | I-D Opening Algorithms                                | 26         |

|   |      | 3.1.4     | 2-D Opening Algorithms                                | 28         |

|   |      | 3.1.5     | Choice of Algorithm for Hardware Implementation       | 28         |

|   | 3.2  | Advance   | es in Morphology Implementation                       | 29         |

|   |      | 3.2.1     | General-purpose Processors                            | 29         |

|   |      | 3.2.2     | Graphics Processing Units                             | 30         |

|   |      | 3.2.3 I   | Dedicated Hardware                                    | 31         |

|   | 3.3  | Conclus   | ions                                                  | 38         |

| 4 | Alg  | orithm l  | Description                                           | 41         |

|   | 4.1  | 1-D Dila  | ation Algorithm                                       | 41         |

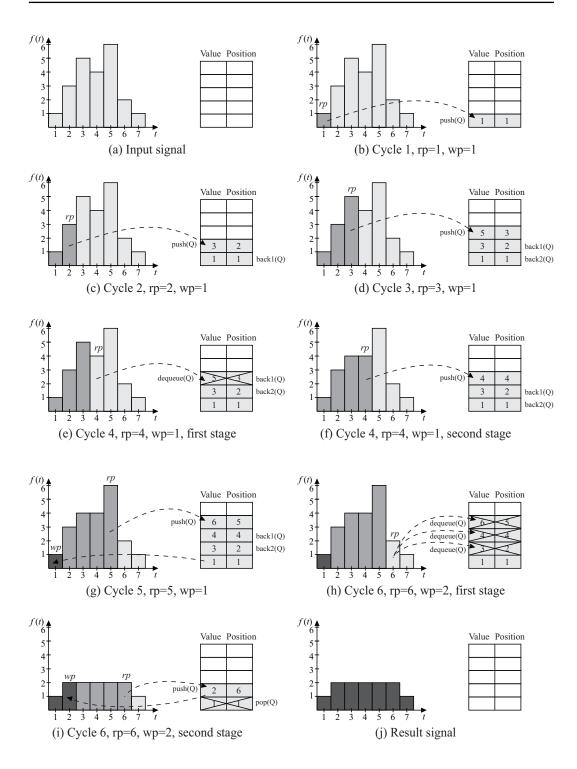

|   |      | 4.1.1 I   | Illustration of <i>Dokládal</i> Algorithm Run         | 44         |

|   | 4.2  | 2-D Dila  | ation by Rectangular SE                               | 46         |

|   |      | 4.2.1 1   | I-D Vertical Dilation                                 | 48         |

|   |      | 4.2.2     | 2-D Algorithm for Rectangles                          | 49         |

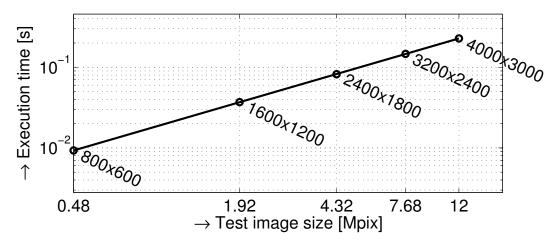

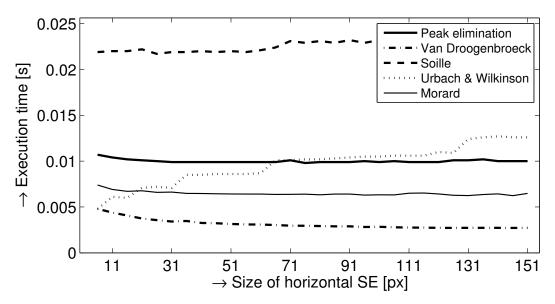

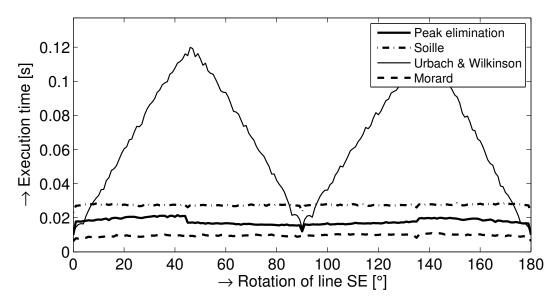

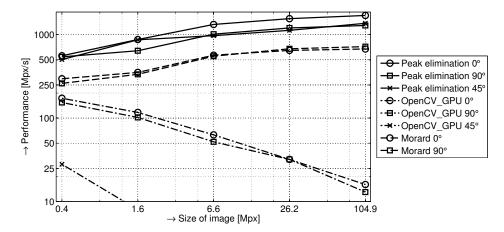

|   |      | 4.2.3     | GPP Experimental Results of <i>Dokládal</i> Algorithm | 49         |

|   | 4.9  | Dolmon    | al CE                                                 | <b>E</b> 6 |

XII Contents

|   |     | 4.3.1            | Oblique 1-D Structuring Element                                 | 6 |

|---|-----|------------------|-----------------------------------------------------------------|---|

|   |     | 4.3.2            | Translation-Variant SEs on 8-connected Grid 5                   | 7 |

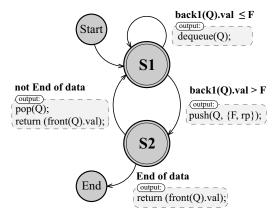

|   | 4.4 | 1-D O            | pening Algorithm                                                | 8 |

|   |     | 4.4.1            | Illustration of Streaming Peak Elimination Algorithm Run 6      | 1 |

|   |     | 4.4.2            | Pattern Spectrum from Opening 65                                | 3 |

|   |     | 4.4.3            | Arbitrary SE Orientation                                        | 4 |

|   |     | 4.4.4            | Experimental Results of Streaming Peak Elimination Algorithm 69 | 9 |

|   | 4.5 | Conclu           | sions                                                           | 4 |

| 5 | Har | $\mathbf{dware}$ | Implementation 77                                               | 7 |

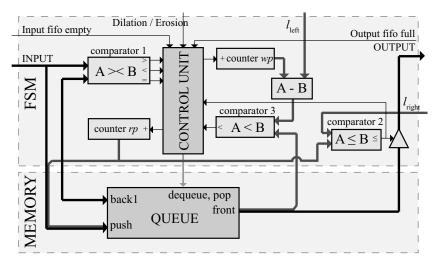

|   | 5.1 | 1-D D            | ilation Architecture                                            | 8 |

|   |     | 5.1.1            | Horizontal Architecture                                         | 9 |

|   |     | 5.1.2            | Vertical Architecture                                           | 0 |

|   |     | 5.1.3            | Reducing the Impact of Data Dependency 83                       | 1 |

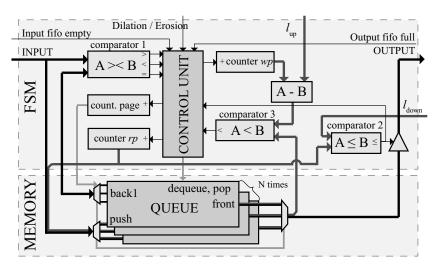

|   | 5.2 | 2-D R            | ectangular Dilation Architecture                                | 3 |

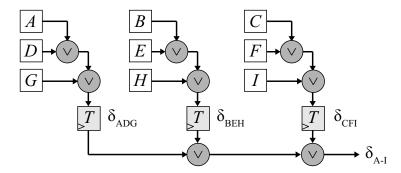

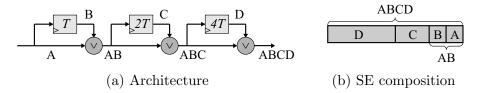

|   |     | 5.2.1            | Parallel Rectangle Architecture                                 | 6 |

|   |     | 5.2.2            | Conclusions                                                     | 9 |

|   | 5.3 | 2-D P            | olygonal Dilation Architecture                                  | 0 |

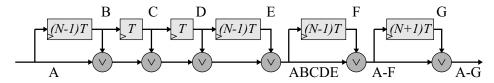

|   |     | 5.3.1            | 1-D Line Unit Architecture                                      | 0 |

|   |     | 5.3.2            | Polygon Unit Architecture                                       | 2 |

|   |     | 5.3.3            | Parallel Polygon Architecture                                   | 4 |

|   |     | 5.3.4            | Conclusions                                                     | 6 |

|   | 5.4 | 1-D Sy           | vnchronous Dilation Architecture 9'                             | 7 |

|   |     | 5.4.1            | Conclusions                                                     | 1 |

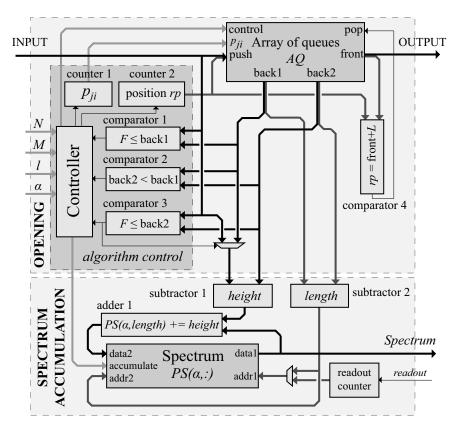

|   | 5.5 | 1-D O            | pening and Spectrum Architecture                                | 1 |

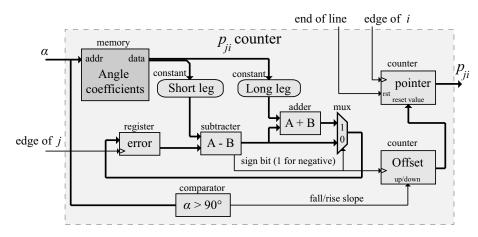

|   |     | 5.5.1            | Arbitrary Orientation                                           | 2 |

|   |     | 5.5.2            | Conclusions                                                     | 6 |

|   | 5.6 | Conclu           | sions                                                           | 6 |

| 6 | Imp | olemen           | tation Results 109                                              | 9 |

|   | 6.1 | Rectar           | ngle Dilation Unit                                              | 1 |

|   | 6.2 | Polygo           | on Dilation Unit                                                | 4 |

|   | 6.3 | 1-D Sy           | vnchronous Dilation Unit                                        | 5 |

|   | 6.4 | Openia           | ng and Spectrum Unit                                            | 6 |

|   | 6.5 | Compa            | arison of the Proposed Implementations                          | 7 |

|   | 6.6 | Compa            | arison with Existing Implementations                            | 9 |

|   |     | 6.6.1            | Comparison Using Alternating Sequential Filters 12              | 1 |

|   | 6.7 | Conclu           | asions                                                          | 2 |

| $\mathbf{Conte}$ | ents | XIII |

|------------------|------|------|

|                  |      |      |

| 7  | App    | olicatio   | ons                                                    | 125 |

|----|--------|------------|--------------------------------------------------------|-----|

|    | 7.1    | A Platform | 125                                                    |     |

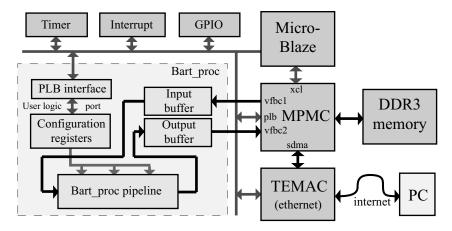

|    |        | 7.1.1      | Top-level Platform Description                         | 126 |

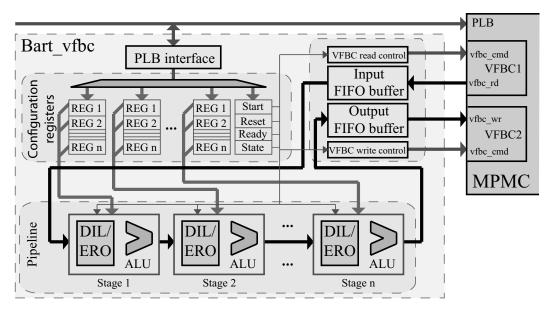

|    |        | 7.1.2      | Bart_proc Peripherals                                  | 128 |

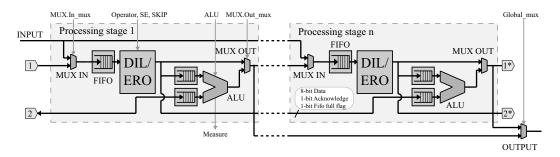

|    |        | 7.1.3      | Bart_proc Pipeline                                     | 129 |

|    |        | 7.1.4      | FREIA Interface                                        | 130 |

|    |        | 7.1.5      | FREIA Performance Evaluation                           | 131 |

|    | 7.2    | Classif    | fication of Particles Recorded by the Timepix Detector | 133 |

|    |        | 7.2.1      | Classification Using Morphological Characteristics     | 133 |

|    |        | 7.2.2      | Method Description                                     | 134 |

|    |        | 7.2.3      | Hardware Architecture                                  | 138 |

|    | 7.3    | Conclu     | isions                                                 | 141 |

| 8  | Gen    | eral C     | onclusions and Perspectives                            | 143 |

|    | 8.1    | Perspe     | ectives                                                | 145 |

| Pι | ıblica | ations     |                                                        | 147 |

| Bi | bliog  | raphy      |                                                        | 149 |

# 1 Introduction

#### Contents

| 1.1 | Applications of Mathematical Morphology             | 2 |

|-----|-----------------------------------------------------|---|

|     | 1.1.1 Vision Application Constraints                | 3 |

| 1.2 | Roles of Dedicated Hardware for Vision Applications | 4 |

| 1.3 | Contributions of the Thesis                         | 5 |

| 1.4 | Outline                                             | 6 |

In this thesis we focus on hardware implementation of fundamental algorithms of mathematical morphology. Mathematical morphology is a popular image processing framework providing a complete set of tools for filtering, multi-scale image analysis, or pattern recognition. It has been used in a number of applications, including biomedical and medical imaging, video surveillance, industrial control, video compression, stereology or remote sensing since its very first appearance in the late 1960's, see [Matheron 1975] [Serra 1988] [Serra 1992].

Considering the hardware implementation context, several different trends have been observed. A recent technological advance of imaging sensors stimulated the development of applications by means of high-resolution images that became a standard. This trend of increasing resolution is widely expected to carry on, such as UHDTV [ITU-R 2012], the public broadcasting of which may be ready by 2016. Needless to say large images impose challenging requirements on the computation platform in terms of both performance and memory.

On the other hand, the industrial context often induces severe real-time constraints on applications. As these demanding image-interpretation applications requires a high correct-decision liability, robust but costly multi-criteria and/or multi-scale analyses are used. Provided that slow image processing may deteriorate some industrial production, the latency and computational performance are of high interest in this context.

In embedded systems, the most important concerns are low power consumption (and consequently low heat dissipation) and small resources occupation, which allows for better embedding. All these considerations combined together infer overwhelming requirements on the architecture of polyvalent processing units addressing many different contexts.

2 1. Introduction

### 1.1 Applications of Mathematical Morphology

Examples of the most frequent morphology operators and their applications follow below.

- Filters: Filters are low-level vision operators and serve either to eliminate noise that deteriorates an image by some undesired artifacts [Heijmans 1997] [Serra 1992] [Maragos 2005], or to simplify image topology in order to make further processing easier. Morphological filters are commonly used in preprocessing stage of many complex higher-level operators, such as image compression and image segmentation [Gorpas 2009].

- Granulometry: Granulometry (so-called size distribution) measures distribution of object size in a population of objects [Matheron 1975] [Maragos 1989]. It can be considered as an ordered set of operators—sieves—each of which allows only objects larger than a given size to pass. [Urbach 2004] used granulometry of an inner cell texture for automatic diatom cell identification and classification. [Bagdanov 2002] utilized granulometry in genre classification of printed documents, and more recently [Karas 2012b] took advantage of arbitrary-oriented granulometries for rotation detection of music sheet scans.

- Image enhancement: Image enhancement is a common technique to improve some visual features with respect to different criteria, e.g., contrast enhancement, toggle mapping [Serra 1989]. For another examples, [Zhang 2011] detected microaneurysms on eye fundus images, and [Wei 2007] used a multiscale top-hat transformation to locally increase contrast of orthopaedic X-ray images, which were then easier to read.

- Classification: In general, classification aims at identifying to which of a set

of classes a new observation belongs. Mathematical morphology has been

mainly used in classification of images (or sections of images) with respect to

spatial features. [Moore 2007] used mathematical morphology for the classification of astronomical objects, both for star/galaxy differentiation and

galaxy morphology classification.

- Segmentation: Segmentation is another key tool of image processing applied to a large number of problems. For example, see contouring blobs of proteins in an electrophoresis gel, separation of overlapping grains, both [Beucher 1992].

- Statistical learning: A selected set of morphological operators can be separately applied to an image and used as a vector of descriptors for pixelwise statistical learning, see [Vapnik 1995] for the domain introduction. [Cord 2007] devised a method for segmentation of random textures using a vector of 126 morphological descriptors.

#### 1.1.1 Vision Application Constraints

From the applications in literature we can recognize the most common constraints shared among various vision applications as follows:

- Real-time processing: We understand as real-time processing the capability of processing data at a rate at least equal to the acquisition/input data rate. This constraint is closely related to performance, however, the exact value depends on a given application. For example, the common video camera formats specify the minimum frame-per-second (fps) performance to 25, 30, etc., respectively; pixel detectors take from 30 to 100 fps; and for highend industrial applications, even more diverse values (1–1000 fps) may be encountered. Clearly, the values above reflect complexity of applications; however, the higher performance of computation platform helps us to meet the application-specific real-time constraint.

- Latency: The excessive latency of computation has two main implications on an application. First, the larger latency usually implies the larger memory requirements, either as an image storage (input, intermediate, output) or as a working memory. Second, the excessive latency may be limiting for certain applications that need results as soon as possible for further processing, e.g., iterative reconstruction, etc.

- High-definition resolution: The resolution of images varies within a large range from a small resolution 256×256 of the pixel detector, through distinct video format resolutions (nowadays standards 640×480–1920×1080, or even UHDTV 7680×4320), up to industrial sensors with resolution of tens of megapixels. The high resolution impacts computation performance, so it is more challenging to achieve real-time processing, and memory requirements. In non-destructive testing by machine vision, searching for small defects (orders of micrometers) in large-size pieces (orders of square meters), one easily encounters extreme resolution requirements.

- Reliability, power consumption: In certain industrial applications such as road monitoring and obstacle detection [Beucher 1995] or track autonomous following [Marion 2004], high system reliability and low power consumption are very important constraints. This constraint is typical for all embedded systems.

All these constraints combined together infer overwhelming (and even sometimes contradictory) requirements on the computational platform. We recognize three general computation platforms suitable for such vision applications: general-purpose processor (GPP, so-called CPU), graphics processing unit (GPU), and dedicated hardware. The conveniences of these platforms for vision applications are discussed in the following section.

4 1. Introduction

### 1.2 Roles of Dedicated Hardware for Vision Applications

Probably the most popular and common computation platform is a general-purpose processor that appears in a variety of general-purpose computing devices: personal computers, multi-core workstations, or many-core clusters. Despite the wide spread, and recent technological advances, the performance of the GPP is rather low given some complex vision application as it is partly sacrificed in favor of large universality. The computation is carried out sequentially in a GPP (there are exceptions like the SIMD instruction set, superscalar CPUs etc.).

The second platform suitable for vision applications is graphics processing unit (GPU). A GPU consists of many light-weight processors interconnected in given hierarchy, each of which executes several threads of the application code. Hence, this platform provides some parallelism via many threads being computed at the same time. However, the threads are processed sequentially, and the inter-thread communication is penalizing. The GPU platforms can achieve higher performance than GPP for applications that takes advantage of thread-wise parallel computation, thus weakening universality.

The dedicated hardware (we focus chiefly on FPGAs, however, the following holds true for ASICs as well) goes even farther. It provides the designer by a large amount of logic resources (that carry out arithmetic, logic operations, etc.) and interconnection resources, and let him to decide the way how the processing architecture should be assembled. Such an approach results in a great opportunity for parallelism of different kinds (spatial, temporal) that leads to the highest performance for certain applications. These target applications are supposed to involve rather dense numerical computation per datum with less conditional jumps and context switching, such as digital filters, video coding/decoding, etc.. Obviously, most vision applications (including mathematical morphology) satisfies the first presumption. In order to comply with the latter, we have to beware of very complex applications or applications that need large diversity of operators.

Notice that for changing the computation context, like in the case of complex or general-purpose applications, the dedicated hardware must be either reconfigured, see [Hauck 2007] or [Gokhale 2010] for FPGA reconfiguration, or it must possess computation resources for every used context and programmable interconnection. Either way, it results in inefficient hardware utilization.

The dedicated hardware is a platform that can address each one of the application constraints mentioned above. On the other hand, the real power of this platform can only be exploited, above all, in single-purpose applications, which attain efficient resources utilization. We see mainly two target application groups of dedicated hardware as follows:

• High-performance single-purpose applications: That is applications demanding a huge computational power tailored to only one purpose. Then dedicated hardware allows for real-time processing even in the most demanding appli-

cations, for which the other platforms are not powerful enough. Dedicated hardware is definitely capable of improving the overall performance.

• Low-power embedded applications: The other group of dedicated hardware applications stand on the opposite side of performance scale. For low-power embedded applications the computational performance is not the main measure, but it is power consumption or resources occupation. In this field dedicated hardware is better choice than other platforms thanks to low power and area demands.

Considering the other two constraints, hardware platforms improves them as well. The hardware platform clearly allows a designer to devise an architecture with zero additional latency, or an architecture supporting large images with no penalization (unless all resources are used). On the other hand, dedicated hardware can hardly constitute a general-purpose computation platform for a complete set of vision applications. Large polyvalence of applications would gravely reduce computation performance due to inefficient utilization of hardware resources.

#### 1.3 Contributions of the Thesis

The aim of the thesis is to propose hardware implementation of adaptable processing units for vision applications based on mathematical morphology. The thesis develops in three main stages: algorithms of mathematical morphology, hardware implementation of processing units, and applications.

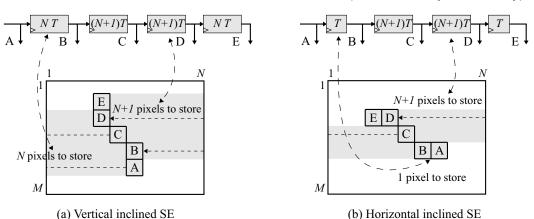

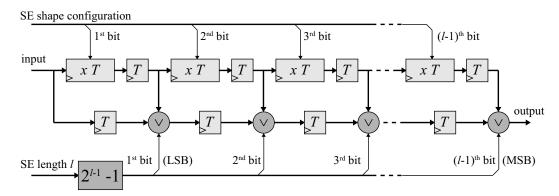

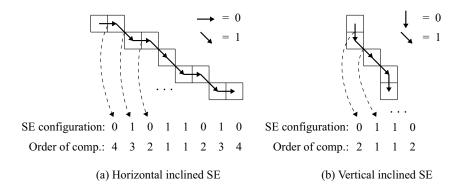

First, we evaluate algorithms for low-level mathematical morphology and recognize the *Dokládal* algorithm (published in [Dokládal 2011]) to be the best choice for hardware implementation. As the first contribution, we enrich the family of supported structuring elements by inclined lines that can form regular polygons. For the inclined lines the computation of dilation proceeds along an inclined discrete line the coordinates of which are determined using Bresenham line algorithm [Bresenham 1965]. A similar approach was used by [Soille 1996] and [Morard 2011] but our solution preserves sequential access to data whatever the inclination angle, a very beneficial property of the algorithm.

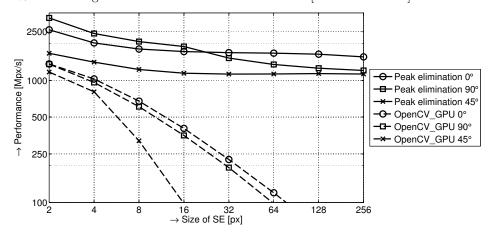

After that we propose an original algorithm for arbitrary-oriented 1-D opening and pattern spectrum called *streaming peak elimination*. Even though opening is commonly obtained as a concatenation of erosion and dilation, direct computation of opening is faster and easier to implement. The proposed algorithm is targeted to hardware and GPU implementation. The performance benchmark reveals that our algorithm outperforms all other algorithms using graphics cards.

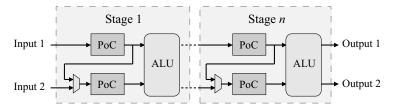

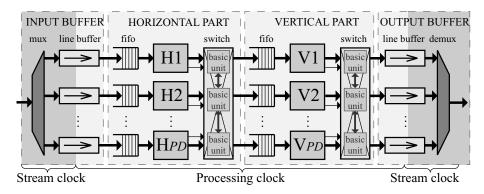

Second, we propose the dedicated hardware implementation of the *Dokládal* algorithm as a fully programmable 1-D dilation processing unit supporting different orientations, which is used as a building brick in concatenations of any length. This *inter-operator parallelism* is illustrated on the 2-D rectangular and polygonal dilation processing units. Then, we introduced a method of parallel computation that

6 1. Introduction

uses a few copies of processing units in parallel, each of which however processes its dataflow sequentially. This *intra-operator parallelism* almost linearly increases the performance of both rectangular and polygonal processing units. Compared to other recent architectures, our processing units outperform the others for structuring elements larger than  $3\times3$ . The difference is even more evident in the case of compound operators, for instance serial filters.

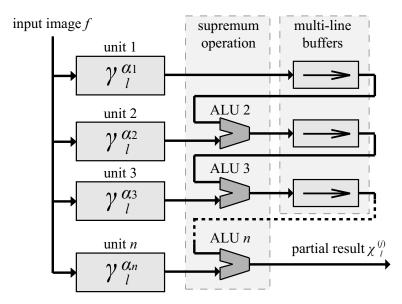

In a later part, we implemented the *streaming peak elimination* algorithm as a fully programmable 1-D opening and pattern spectrum processing unit supporting arbitrary orientation. This processing unit allows for *inter-operator parallelism* of complex morphological operators demanding multiple orientation analysis, such as oriented pattern spectra or image enhancement.

Third, we utilize the proposed processing units in two applications. We integrate the units into the FREIA (Framework for Embedded Image Applications, [FREIA 2011]) platform that is supposed to address the most computation performance demanding vision applications. From the FREIA viewpoint, the main contribution of the proposed architectures is efficient computation of large and oriented SEs. The second application classifies high-energy particles recorded by the Timepix detector. We show that a basic classification of particle shapes can be realized in a streaming manner in an embedded device using the proposed processing units.

Considering performance of the designed computing units, this scalable and programmable computing platform allows us to obtain previously unachievable, real-time performances for the traditionally costly morphological operators. Along with ability to implement large SEs without decomposition, it opens the accessibility of advanced morphological operators in industrial systems. The number of examples includes the on-line production control, aging material defectoscopy, etc. Thanks to its high degree of universality, it shall allow application developers to utilize this framework instead of an expensive ad-hoc development.

#### 1.4 Outline

The rest of the manuscript is organized as follows. Chapter 2 recalls the basic terminology of image processing and fundamental operators of the mathematical morphology.

In Chapter 3, we present the review of the literature on advances in basic morphology algorithms, chiefly dilation and opening, and decides which algorithm has the most pleasant properties for hardware implementation. We also outline advances in morphology implementation. We discuss especially in detail existing implementations on general-purpose processors, graphics processing units, and dedicated hardware.

Chapter 4 is devoted to the thorough description of the selected morphological algorithm used in implementation later. We also propose an original algorithm for

1.4. Outline 7

morphological opening in this chapter. Performance benchmarks of these algorithms with respect to other state-of-the-art algorithms are mentioned using different computation platforms.

In Chapter 5, we present hardware implementation of basic morphological operators using efficient algorithms that have been chosen in the previous chapters. The proposed programmable processing units can be used as basic bricks to build up more complex operators. We also shows how to speed up the performance by introducing two levels of parallelism. Chapter 6 presents experimental performance and FPGA implementation results of the proposed processing units with respect to various properties. The proposed architectures are also compared with other state-of-the-art hardware implementations in order to evaluate the contribution.

Chapter 7 contains description of two practical applications that utilizes the proposed processing units. The purpose of this work is to illustrate usability of the units both high-performance and low-power, embedded applications. Finally, chapter 8 concludes the manuscript and outlines the perspectives and the undergoing work.

# 2 Fundamental Operators of Mathematical Morphology

#### Contents

| 2.1 | Erosion and Dilation                      |           |  |  |

|-----|-------------------------------------------|-----------|--|--|

|     | 2.1.1 Composition of Structuring Elements | 13        |  |  |

| 2.2 | Opening and Closing                       | 14        |  |  |

| 2.3 | Alternating Sequential Filters            | 14        |  |  |

| 2.4 | Granulometry and Pattern Spectrum         | <b>16</b> |  |  |

In the following sections, we review the basic image processing terminology used in the thesis. The definition of the most important morphological operations follows below.

First of all, we focus on a discrete (digital) image. The transformation of continuous image into discrete image is called digitalization and consists of sampling (i.e., discretization of spatial coordinates) and value quantization. Let X be a countable set called support, and Y a countable set of defined values. We consider a family of discrete images I an application of some function  $f: X \to Y$  where X is usually a rectangular domain,  $X \subset \mathbb{Z}^2$  or  $X \subset \mathbb{Z}^3$ . An element  $x \in X$  is called an image point. Depending on the definition of the support X, we call an image point a pixel if  $X \subset \mathbb{Z}^2$ , or a voxel if  $X \subset \mathbb{Z}^3$ . The value y of a pixel x is defined as y = f(x). We can further specify the type of image according to the set of image values Y. We call f a binary image if Y contains exactly two elements. The grey-scale images consider  $Y \subset \mathbb{Z}$ , or even Y being a subset of a set of floating-, fixed-point numbers (such sets are countable). In general, all image operations  $\Xi: I \to I, g = \xi(f)$  can be broken down with regard to the influence scope into three basic types:

- Pixel operations. The output g(x) depends only on the input at the very same position f(x), it is independent of all other pixels in the image. For instance, threshold, contrast addition, subtraction, stretching are pixel operations.

- Neighborhood (local) operations. The output g(x) depends on a given set of input pixels  $f(\mathcal{P}(x))$ ;  $\mathcal{P}(x) \subset X$  ( $\mathcal{P}(X)$  is a subset of X) often surrounding x, hence called a neighborhood of x. The examples of neighborhood operations are, e.g., various filters (morphological, smoothing, Laplacian), convolution, gradient, sharpening, etc.

- Global operations. The output g(x) depends on the entire input image f(X). The global operations are designed to reflect some statistical information of the image, e.g., distance transformation, histogram equalization, or they

extract some hierarchical information, e.g., connected components trees, segmentation, scene parsing.

Morphological operators aim at extracting some relevant spatial information from an image, see [Serra 1982, Matheron 1975] for extensive information. Since the image is considered to be a set X, it can be achieved by probing the image with another set of a known shape. Hereafter, we call the probe  $Structuring\ Element$  (SE), in other literature sometimes called window or kernel. The shape of the SE has very significant influence on the result of any morphological operation, and therefore, the choice of the shape and size is often made according to some a priori knowledge of the image geometry.

Although a SE may be generally n+1-dimensional for n-dimensional images, we focus on n-dimensional SEs. These SEs are referred to as flat because they have only 2 dimensions in the case of 2-dimensional image, which is the most common. The n+1-dimensional SEs are called volumic, non-flat, or gray-scale, and omitted in this memory due to high computation complexity and restricted usage. Regardless the type, each SE is equipped by an origin that allows positioning of the SE at a given point of an image.

#### 2.1 Erosion and Dilation

The erosion and dilation are fundamental operations of mathematical morphology; they answer to the most obvious question while probing an image (the following questions quote [Soille 2003]).

The binary dilation answers the question "Does the structuring element hit the set?". The result set contains the points where the answer is affirmative. The binary dilation of a set X by a SE B is denoted by  $\delta_B(X)$  and it is defined as

$$\delta_B(X) = \{x \mid \widehat{B}(x) \cap X \neq \emptyset\}$$

(2-1)

where the SE B is considered to be flat, i.e.,  $B \subset \mathbb{Z}^2$  (translation-invariant), equipped with an origin  $x \in B$ . The transposed SE  $\widehat{B}$  is equal to the geometric reflection of B around the origin

$$\widehat{B} = \{x \mid -x \in B\}. \tag{2-2}$$

The binary dilation can be also defined by means of Minkowski set addition, such as

$$\delta_B X = X \oplus B = \bigcup_{b \in B} X_b \tag{2-3}$$

where for set X and element b, the subscript  $X_b$  denotes translation of X by b.

This latter definition allows for direct extension to gray-scale images (functions). The definition of the gray-scale dilation by a flat SE also exists in two versions. First, the extension to functions of the Minkowski set addition, such as

$$[\delta_B(f)](x) = \left[\bigvee_{b \in B} f_b\right](x) \tag{2-4}$$

where  $f_b$  denotes translations of f by vectors  $b \in B$ . The second definition is obtained by extension to functions of the set intersection/inclusion given by

$$[\delta_B(f)](x) = \Lambda\{v \in Y \mid \widehat{B} + v \ge f\}. \tag{2-5}$$

The implementation of the gray-scale dilation essentially consists of searching the maximum of f within the scope of B such as

$$[\delta_B(f)](x) = \max_{b \in B} [f(x+b)]$$

(2-6)

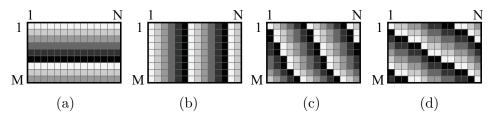

The example of an image dilated by SEs of various sizes is displayed in Fig. 2.1. At first sight, the light regions, which have high gray-level values, are stretched out.

(a) Input image

(b) Dilation by  $11\times11$  (c) Dilation by  $21\times21$  (d) Dilation by  $31\times31$

**Figure 2.1:** Example of images processed by dilation with various SEs. (a) input image f, (b) dilated by SE  $11\times11$ , (c) dilated by SE  $21\times21$ , (d) dilated by SE  $31\times31$ .

The output of the binary erosion is a set of points where the answer to "Does the structuring element fit the set?" is positive. The binary erosion of a set X by a structuring element B is denoted by  $\varepsilon_B(X)$  and it is defined a

$$\varepsilon_B(X) = \{ x \mid B(x) \subset X \} \tag{2-7}$$

where the SE B is considered to be flat equipped with an origin  $x \in B$ . The binary erosion can be also defined by means of Minkowski set addition, such as

$$\varepsilon_B X = X \ominus B = \bigcap_{b \in \widehat{B}} X_b \tag{2-8}$$

where for set X and element b, the subscript  $X_b$  denotes translation of X by b.

This latter definition allows for direct extension to gray-scale images (functions). The definition of the gray-scale erosion by a flat SE also exists in two versions. First, the extension to functions of the Minkowski set addition, such as

$$[\varepsilon_B(f)](x) = \left[ \bigwedge_{b \in \widehat{B}} f_b \right](x), \tag{2-9}$$

where  $f_b$  denotes translations of f by vectors  $b \in B$  computed as f(x+b). The second definition is obtained by extension to functions of the set intersection/inclusion given by

$$[\varepsilon_B(f)](x) = \forall \{v \in Y \mid B + v < f\}. \tag{2-10}$$

The implementation of the gray-scale erosion essentially consists of searching the minimum of f within the scope of B such as

$$[\varepsilon_B(f)](x) = \min_{b \in \widehat{B}} [f(x+b)]$$

(2-11)

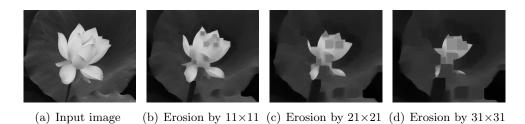

The example of erosion by SEs of various sizes is displayed in Fig. 2.2. Erosion expands the dark regions as those have small gray-level value.

**Figure 2.2:** Example of images processed by erosion with various SEs. (a) input image f, (b) eroded by SE  $11\times11$ , (c) eroded by SE  $21\times21$ , (d) eroded by SE  $31\times31$ .

Both dilation and erosion share some important properties. First of all, they are dual operation to each other. It means that an erosion of an image is equal to complementation of the dilation of the complemented image (and the other way around). Complementation is a basic set operator, and complementation of some image f, denoted as  $\mathbb{C}f$ , is defined for each pixel x as the maximum value of the data type used for storing the pixel  $t_{\text{max}}$  minus the value of image f at position x, such as

$$Cf(x) = t_{\text{max}} - f(x). \tag{2-12}$$

From the implementation point of view, one can omit dealing with an erosion if he has a dilation and some light-weighted, efficient complementation operator C,

$$\delta_B(f) = \mathcal{C}_{\widehat{B}}\mathcal{C}(f). \tag{2-13}$$

Dilation and erosion also form an adjunction pair

$$\delta(X) \le Y \Leftrightarrow X \le \varepsilon(Y). \tag{2-14}$$

The adjunction is necessary to obtain properties allowing for combining dilation and erosion to form filters.

Other properties are increasingness, ordering relations, invariance to translation, distributivity, etc., the thorough description of which can found in [Soille 2003].

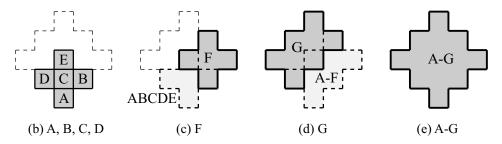

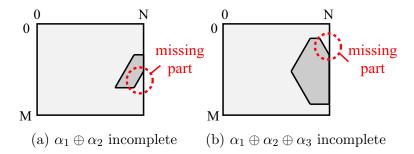

#### 2.1.1 Composition of Structuring Elements

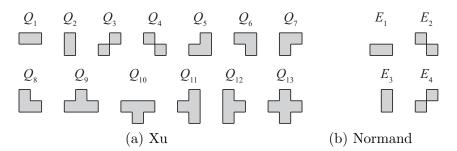

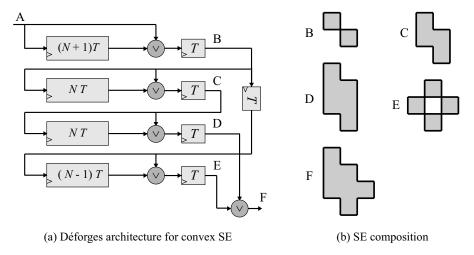

The last, and very important, property of erosion and dilation is SE composition (sometimes referred to as SE decomposition). The composition property claims that a sequence of dilations (or erosions) is equivalent to only one operation by the SE equal to the Minkowski addition  $\oplus$  of both original SEs, see (2-15). This property is very useful because it allows us to compose more spatially complex SEs using elementary SEs that often decreases the order of computation complexity. Figure 2.3 displays the composition of rectangle, hexagon, and octagon from lines. This decomposition is often used to approximate circle SEs.

**Figure 2.3:** Examples of regular polygon SE composition: (a) rectangle, (b) hexagon, (c) octagon.

**Figure 2.4:** Classes of primitive SEs. Any 8-convex polygon SE is decomposable into either: (a) Xu class, or (b) Normand class while using union along with  $\oplus$ .

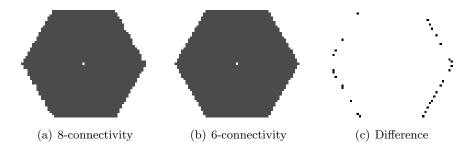

Another principle of SE decomposition was proposed by [Xu 1991] (similar to [Zhuang 1986]). It claims that any 8-convex polygon (convex on 8-connectivity grid, hence 8-convex) is decomposable into a class of 13 nontrivial indecomposable convex polygonal SEs  $Q_1 - Q_{13}$  shown in Fig. 2.4 (a). [Normand 2003] reduces the class of shapes to only four 2-pixel SEs, see Fig. 2.4 (b), by allowing the union operator to take place in SE decomposition. For instance,  $Q_{12}$  by Xu is obtained as  $(E_3 \oplus E_3) \cup E_4$  by Normand.

### 2.2 Opening and Closing

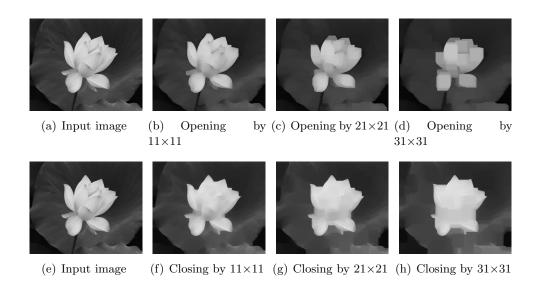

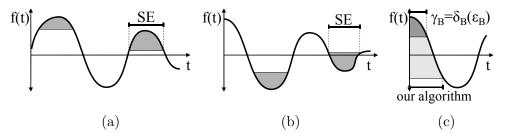

Concatenations of a dilation and an erosion form elementary filters called opening and closing, see Fig. 2.5.

The binary opening preserves the whole set of the SE if the SE fits into an image. The binary opening by a flat SE B is denoted by  $\gamma_B(X)$  and defined as

$$\gamma_B(X) = \bigcup_x \{B(x) \mid B(x) \subseteq X\}. \tag{2-16}$$

The gray-scale opening is defined as the union of all SEs that fit under the graph of a function f such as

$$\gamma_B(f) = \vee \{B + v \le f\},\tag{2-17}$$

and it can be implemented by

$$\gamma_B(f) = \delta_{\widehat{B}}[\varepsilon_B(f)]. \tag{2-18}$$

The result of the binary closing filter does not contain any point of SEs that fit the background set. The binary closing of a set X by a flat SE B is denoted by  $\varphi_B(X)$  and defined as

$$\gamma_B(X) = \mathbb{C}\left[\bigcup_x \{B(x) \mid B(x) \subseteq \mathbb{C}X\}\right].$$

(2-19)

The gray-scale closing is defined as

$$\gamma_B(f) = \Lambda\{\widehat{B} + v \ge f\},\tag{2-20}$$

and it can be implemented by

$$\varphi_B(f) = \varepsilon_{\widehat{B}}[\delta_B(f)]. \tag{2-21}$$

The opening and closing are dual operations according to the complementation  $\mathbb{C}$ , such as

$$\varphi_B(f) = \mathbb{C}\gamma_{\widehat{B}}\mathbb{C}(f) \tag{2-22}$$

## 2.3 Alternating Sequential Filters

From opening and closing, one forms alternating filters obtained as  $\gamma\varphi$ ,  $\varphi\gamma$ ,  $\gamma\varphi\gamma$  and  $\varphi\gamma\varphi$ . The number of combinations obtained from two filters is rather limited. Other filters can be obtained by combining two *families* of filters. This leads to morphological Alternating Sequential Filters (ASF), originally proposed by [Sternberg 1986], and studied in [Serra 1988], Chapter 10. In general, it is a family of operators parameterized by some  $\lambda \in \mathbb{Z}^+$ , obtained by alternating concatenation

**Figure 2.5:** Example of images processed by opening and closing with various SEs. (a) (e) input image f, (b) opening by SE  $11\times11$ , (c) opening by SE  $21\times21$ , (d) opening by SE  $31\times31$ , (f) closing by SE  $11\times11$ , (g) closing by SE  $21\times21$ , (h) closing by SE  $31\times31$ .

of two families of increasing and decreasing filters  $\{\xi_i\}$  and  $\{\psi_i\}$ , respectively, such that  $\psi_n \leq \ldots \leq \psi_1 \leq \xi_1 \leq \ldots \leq \xi_n$ .

The most known ASF are those based on openings and closings, obtained by taking  $\psi = \gamma$  and  $\xi = \varphi$ :

$$ASF^{\lambda} = \gamma^{\lambda} \varphi^{\lambda} \dots \gamma^{1} \varphi^{1} \tag{2-23}$$

starting with a closing, and

$$ASF^{\lambda} = \varphi^{\lambda} \gamma^{\lambda} \dots \varphi^{1} \gamma^{1} \tag{2-24}$$

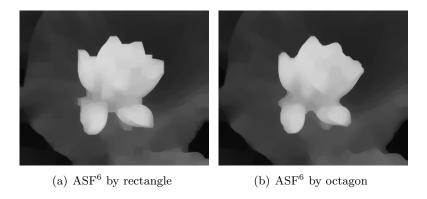

starting with an opening, the example of which for different orders is shown in Fig. 2.6.

**Figure 2.6:** Example of images processed by ASF of various orders with a rectangular SE. (a) input image f, (b) ASF<sup>1</sup>, (c) ASF<sup>3</sup>, (d) ASF<sup>5</sup>.

#### 2.4 Granulometry and Pattern Spectrum

Another application of opening and closing is called granulometry, or pattern spectrum. The concept of granulometry was introduced by [Matheron 1975] in a study of porous materials. Let  $\Psi = (\psi_{\lambda})_{\lambda > 0}$  be a family of image transformations depending on a parameter  $\lambda$ . This family constitutes granulometry if and only if it forms a decreasing family of openings, that is

$$\forall \lambda \ge 0, \qquad \psi_{\lambda} \text{ is an opening}$$

(2-25)

$$\forall \lambda \geq 0, \qquad \psi_{\lambda} \text{ is an opening}$$

(2-25)

$\forall \lambda \geq 0, \mu \geq 0, \qquad \lambda \geq \mu \Rightarrow \psi_{\lambda} \leq \psi_{\mu}$  (2-26)

The above definition does not require the opening  $\psi_{\lambda}$  to be a morphological opening. Algebraic granulometries, e.g., granulometry by area, based on algebraic openings are also valid, see [Serra 1988]. However, we will focus on a morphological granulometry hereafter.

The family  $\Gamma = (\gamma_{\lambda})_{{\lambda}>0}$  of openings by homothetics  ${\lambda}B = \{{\lambda}b|b \in B\}, {\lambda} \geq 0$ , of B is a granulometry if and only if B is convex. In more practical way it means that provided a convex primary grain B, the family of openings with all the scales of B is a granulometry.

The granulometric analysis of a set f is often presented as a sieving process, fis sieved through a set of sieves with increasing mesh size. Each opening removes more than the previous one. In order to quantify the rate of sieving f, a measure m(f) is used. In the most cases, m(f) measures the sum of all pixels remaining in f. The measure constitutes a granulometric curve of f with respect to granulometry  $\Gamma = (\gamma_{\lambda})_{{\lambda}>0}$  such as

$$G_{\Gamma}(f) = m(\gamma_{\lambda}(f)) - m(\gamma_{\lambda-1}(f)). \tag{2-27}$$

The pattern spectrum is an operator very similar to the morphological granulometric curve, but it was defined in different way in [Maragos 1989]. Let  $S_{\lambda B}$ :  $\mathbb{R}^2 \to \mathbb{R}$  be a single value of the pattern spectrum, parameterized by a SE  $B \subset \mathbb{R}^2$ and its size  $\lambda$ , defined as

$$S_{\lambda B}(f) = -\frac{d}{d\lambda} \|\gamma_{\lambda B} f\|; \quad f: \mathbb{R}^2 \to \mathbb{R}. \tag{2-28}$$

Since we are interested in discrete images with bounded support  $X \subset \mathbb{Z}^2, X =$  $[1, M] \times [1, N]$ , the discrete value of  $S_{\lambda B}$  is transformed to

$$S_{\lambda B}(f) = \sum_{X} (\gamma_{\lambda B} f - \gamma_{(\lambda+1)B} f); \quad f: D \to \mathbb{R},$$

(2-29)

considering the pattern spectrum step  $d\lambda = 1$ .

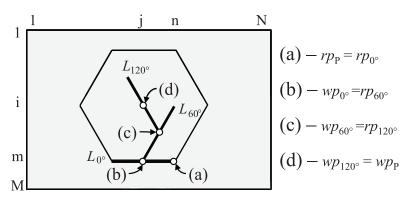

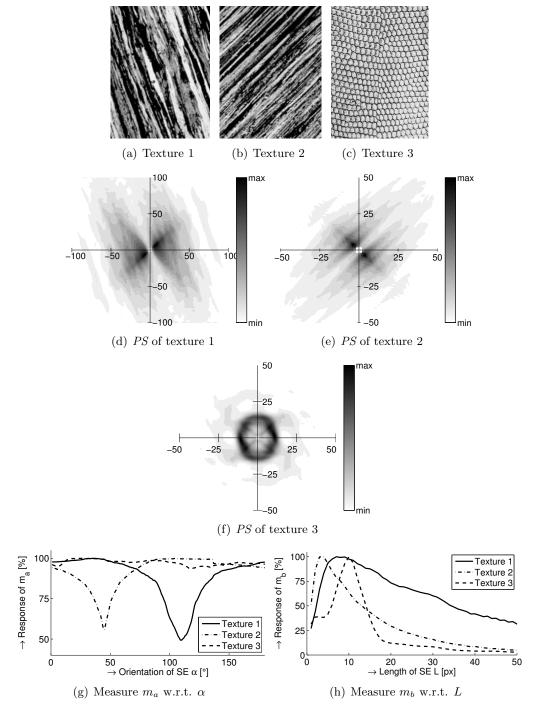

In the following definitions, we consider  $\gamma_l^{\alpha}$  be the opening by a line SE  $L_l^{\alpha}$ . This SE has a shape of a discrete line of length l rotated by angle  $\alpha$  from the positive x-axis counterclockwise ( $\gamma_i^{\alpha}$  is also called *linear opening*) and is commonly used for extracting information about orientation of objects. Using this SE we obtain

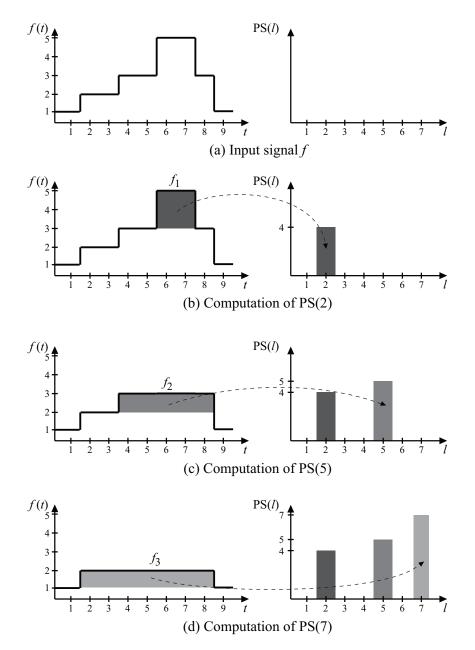

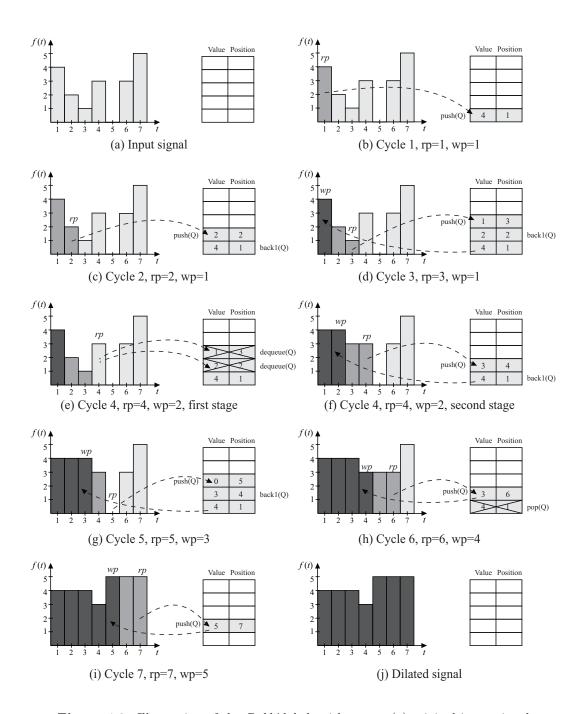

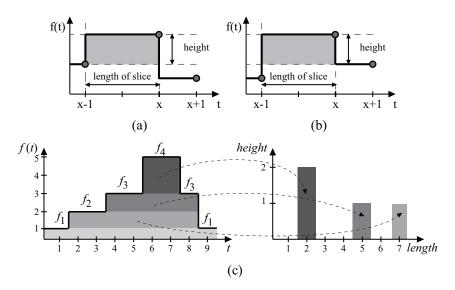

**Figure 2.7:** Example of 1-D signal f and creation of the pattern spectrum PS(l).

the equation for the oriented pattern spectrum  $PS: \mathbb{Z}^2 \to \mathbb{R}$  in (2-30). Such a pattern spectrum PS of an anisotropic texture is the size distribution expectancy of a 1-D signal obtained by intersection with a randomly drawn straight line. The expectancy is approximated by the frequency count.

$$[PS(\alpha, l)](f) = \sum_{X} \left( \gamma_l^{\alpha} f - \gamma_{l+1}^{\alpha} f \right). \tag{2-30}$$

Figure 2.7 shows an intuitive representation of the pattern spectrum PS(l) on 1-D signal f, so only the length of the SE l is variable. We start by computing the

first element  $PS(1) = \sum (\gamma_1 f - \gamma_2 f)$ . Since neither  $\gamma_1$  nor  $\gamma_2$  changes the signal f, see Fig. 2.7 (a), PS(1) remains empty. Then we go one step further, we compute  $\gamma_3 f$  and subtract that from already computed  $\gamma_2 f$ . As we can see in Fig. 2.7 (b),  $\gamma_3$  cuts off the signal cord  $f_1$ , the area of which is the result of the sum of the two openings in PS(2). Note that the length of the eliminated cord is 2 (equal to the length of the SE l=2) but PS contains its area 4. In the next two steps, i.e., for  $l=\{3,4\}$ , the PS contains zero values as both openings return the same signals. For l=5 in Fig. 2.7 (c), the subtraction of  $\gamma_5 f$  and  $\gamma_6 f$  results in the area of the 5-pixel-wide cord labeled  $f_2$  that goes to PS(5). The openings  $\gamma_7$  and  $\gamma_8$  reveals the 7-pixel-wide cord in Fig. 2.7 (d).

In conclusion, this operator decomposes the original signal into a set of signal cords obtained as the residue in the equation (2-30) above (cords of length l). They are represented as a discrete histogram of the sum of their area so that the area of a cord of length l contributes to the l-th bin.

The oriented linear opening  $\gamma_l^{\alpha}$  can be used for the detection of local orientation (orientation field)  $\zeta_l \colon \mathbb{Z}^2 \to [0, 180)$  by looking for angle  $\alpha$  that causes the greatest response of  $\gamma_l^{\alpha}(f)$  at each point as

$$\zeta_l(f) = \arg\max_{\alpha \in [0,180)} \gamma_l^{\alpha}(f). \tag{2-31}$$

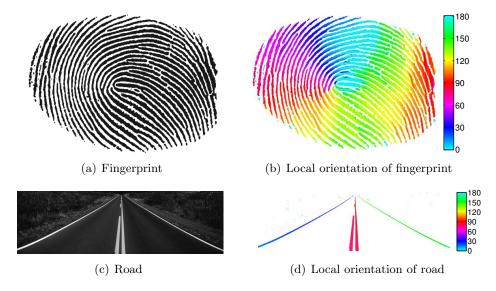

Examples of  $\zeta_l$  applications are shown in Fig. 2.8. The first application shows the local orientation of elongated papillary lines of the fingerprint, the second example determines the orientation of the road lines in the image of a road.

Figure 2.8: Extraction of local orientation on (a) a fingerprint and (b) a road image.

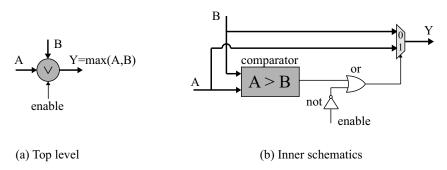

Another operator  $\chi: \mathbb{Z}^2 \to \mathbb{R}$  may also take advantage of  $\gamma_l^{\alpha}$  for image restoration by taking a pixel-wise supremum of openings by different angles in each pixel

$$\chi_l(f) = \bigvee_{\alpha \in [0,180)} \gamma_l^{\alpha}(f) \tag{2-32}$$

The last two operators are rather application-oriented. They demonstrate the feasible applications of linear openings with arbitrary orientation.

# 3 State of the Art

#### Contents

| 3.1 Adv | rances of Basic Morphology Algorithms           |

|---------|-------------------------------------------------|

| 3.1.1   | 1-D Dilation Algorithms                         |

| 3.1.2   | 2-D Dilation Algorithms                         |

| 3.1.3   | 1-D Opening Algorithms                          |

| 3.1.4   | 2-D Opening Algorithms                          |

| 3.1.5   | Choice of Algorithm for Hardware Implementation |

| 3.2 Adv | rances in Morphology Implementation             |

| 3.2.1   | General-purpose Processors                      |

| 3.2.2   | Graphics Processing Units                       |

| 3.2.3   | Dedicated Hardware                              |

| 3.3 Con | clusions                                        |

This chapter surveys the state of the art of mathematical morphology from two different perspectives. At first, algorithmic advances of the low-level morphological operators dilation and erosion in literature are reviewed. Dilation and erosion are the fundamental and most common operators; they are utilized in almost every application that concerns mathematical morphology. Also, many complex morphological operators and methods are composed of various concatenations of these basic operations.

Later, we outline major previous contributions to implementation of the mathematical morphology on different platforms. We are interested in three platforms most suitable for complex image processing applications: general-purpose processors (GPP, CPU), graphics processing unit (GPU), and dedicated hardware (chiefly FPGA).

In the following paragraphs, we use the  $\mathcal{O}()$  notation to express the asymptotic computation complexity (sometimes called time complexity, or big O notation) of an algorithm as proposed by [Knuth 1976]. The computation complexity stands for a number of atomic instructions that must be executed to apply a given algorithm on a single pixel in dependence on some quantity, size criterion n. Asymptotic property means that we are only interested in the order of complexity, e.g., the algorithm of  $\mathcal{O}(100n^2) \equiv \mathcal{O}(n^2)$  has far lower complexity than the algorithm of  $\mathcal{O}(0.01n^3) \equiv \mathcal{O}(n^3)$ . Hereafter, the quantity criterion n is the size of the SE. On some special occasions, for instance when algorithm is of  $\mathcal{O}(1)$  and we want do express the influence of image borders, we use the complexity against the size of the image. That is denoted by  $\mathcal{O}_{\text{image}}()$  and should be comparable to  $\mathcal{O}_{\text{image}}(MN)$  for  $\mathcal{O}(1)$ . For further reading and examples of algorithm analysis see [Leiss 2007, Knuth 1997].

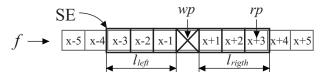

Also, a few terms concerning the latency should be noted as we will use them in the thesis. The latency is a measure expressed in a number of data samples, e.g., pixels. We define the latency introduced by the dependence of the result on future data samples as operator latency. For example the max filter  $y_i = \max(x_{i-2}, x_{i-1}, x_i, x_{i+1}, x_{i+2})$  has operator latency 2, defined by the distance between  $x_i$  and  $x_{i+2}$ . Operators with non-zero operator latency are sometimes referred to as non-causal. We define as algorithm latency any additional latency introduced by the algorithm, e.g., the necessity to perform a reverse scan on data, computing intermediate results, etc. Last, computing latency measures the impact of the implementation on computation. For instance, the polyadic max from the example above can either be executed sequentially on a sequential machine, in a pipeline, or entirely in parallel on a dedicated hardware. The system latency, or simple latency, in the usual sense is the sum of these three terms.

### 3.1 Advances of Basic Morphology Algorithms

The mathematical morphology itself has been studied since its first appearance to improve efficiency and enrich applicability. The development of algorithms attracted a large portion of mathematicians' attention throughout the whole time. It is worthy to recall that the efficiency of an algorithm directly affects its usability whenever the processing time is the main concern.

The following paragraphs present advances of two essential low-level morphological algorithms, dilation and opening. The most efficient dilation algorithms are based on the SE decomposition to a set of basic, more easily optimized shapes. A special attention is paid to the n-D SE decomposition into 1-D SE because the 1-D algorithms obtain the most significant gain in the overall performance.

#### 3.1.1 1-D Dilation Algorithms

The simplest method to compute dilation is the exhaustive search for maximum in the scope of SE B according to definition (2-6). This naive solution tends to need a large number of comparisons, which are on most platforms diadic (with two operands). The number of comparisons is considered as a metric of algorithm complexity, so the naive algorithm has complexity  $\mathcal{O}(l)$  as it has to carry out l-1 comparisons for an l pixel long SE. Such complexity suggests that the naive algorithm is inefficient for any large SEs. [Pecht 1985] proposed a method to decrease the complexity based on logarithmic SE decomposition, thereby achieving  $\mathcal{O}(\lceil \log_2(l) \rceil)$  complexity.

The first 1-D algorithm that reduced complexity to a constant is often referred to as HGW (it was published simultaneously in two papers: [van Herk 1992] and [Gil 1993]). The computation complexity is constant, i.e., of  $\mathcal{O}(1)$ , which means the upper bound of the computation time is independent of the SE size. The HGW algorithm uses two buffers g(x) and h(x), which are divided into segments of the SE

length l. Each segment of the first buffer is filled by the forward propagation of local maxima (3-1) (within the scope of a segment), whereas the second buffer stores the reverse propagation (3-2). The result  $y(x) = \delta_B f(x)$  is obtained by merging both buffers such as (3-3).

$$g(x) = \begin{cases} f(x) & \text{if } x \mod l = 0\\ \max(g(x-1), f(x)) & \text{otherwise} \end{cases}, x = [0..N-1]$$

(3-1)

$$g(x) = \begin{cases} f(x) & \text{if } x \mod l = 0\\ \max(g(x-1), f(x)) & \text{otherwise} \end{cases}, x = [0..N-1]$$

$$h(x) = \begin{cases} f(x) & \text{if } (x+1) \mod l = 0\\ \max(h(x+1), f(x)) & \text{otherwise} \end{cases}, x = [N-1..0]$$

(3-1)

$$y(x) = \max(g(x + (l-1)/2), h(x - (l-1)/2)), x = [0..N - 1]$$

(3-3)

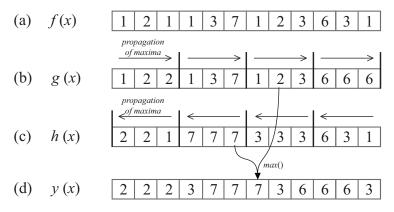

An example of the HGW algorithm run for l = 3, N = 12 is illustrated in Fig 3.1. First, the original signal (a) is forward scanned to compute the forward propagation of maxima in buffer q(x) (b). Notice that the maxima do not propagate beyond the segment of l pixels, see for instance the first segment. The second buffer h(x) (c) is computed in the same way while backward scanning f(x). Finally, the two buffers are merged into the output signal by pixel-wise maximum such as  $y(x) = \max(g(x+1), h(x-1)).$

**Figure 3.1:** Illustration of the HGW algorithm run with SE B long l = 3 px: (a) input signal f(x), (b) forward propagation buffer g(x), (c) backward propagation buffer h(x), (d) output signal  $y(x) = \delta_B f(x)$ .

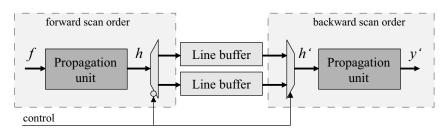

The simplified description above does not correctly handle all the possible cases (e.g., when  $N \mod l \neq 0$ , border pixels), but rather presents the major drawback of this algorithm, the requirement of two data scans: forward and reverse (so-called causal and anti-causal). The unlike scans impose significant restrictions to the implementation on platforms with limited memory management (e.g., dedicated hardware) and infer high latency, especially in the vertical direction. [Gil 2002] proposed an improved version of HGW that lowered the number of comparisons per element, but at the cost of increased memory usage and implementation complexity.

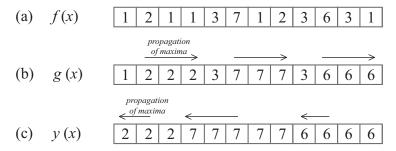

[Lemonnier 1995] proposes another algorithm of  $\mathcal{O}(1)$  that also identifies local extrema and propagates their values. This algorithm does not divide f(x) into segments, but propagates the maxima of f(x) as long as it is covered by the SE

B instead. At first step, the algorithm forward propagates all local maxima by k = (l-1)/2 pixels storing results in a buffer g(x), see Fig 3.2 (b) for example of l = 5, k = 2, N = 12. We notice that each local maximum is propagated only 2 pixels rightwards. The second step backward propagates maxima of the buffer g(x) for the maximal distance of k pixels leftwards, see Fig 3.2 (c). Again, the limiting forward and reverse scans are needed for every non-causal SEs. Although this algorithm needs only 2 max operations per pixel, its implementation results in a large number of if statements to properly treat all boundary conditions.

**Figure 3.2:** Illustration of the Lemonnier algorithm run with SE B long l=5 px: (a) input signal f(x), (b) forward propagation of maxima in g(x), (c) output signal  $y(x) = \delta_B f(x)$ .

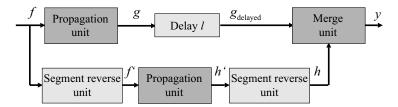

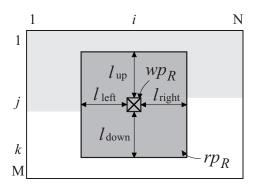

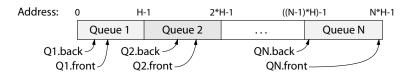

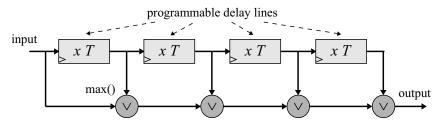

[Lemire 2006] proposes a fast stream-processing algorithm  $\mathcal{O}(1)$  for causal line SEs. It replaces the line buffers of previous algorithms by a more specific memory structure—double-ended FIFO (queue). This algorithm uses two queues of length W in order to store the pixels that form locally monotonous signal (i.e., monotonously increasing and decreasing). Although it produces both erosion and dilation simultaneously, has lower memory requirements and zero latency, it works with causal SEs only. This downside was solved later in [Dokládal 2011] who proposed another queue-based algorithm (see Section 4.1 for further description of his algorithm). The advantages of these queue-based algorithms are low memory requirements, zero latency, and strictly sequential access to data.

Table 3.1 sums up the most important properties of the 1-D dilation algorithms mentioned above.

#### 3.1.2 2-D Dilation Algorithms

As mentioned before, 2-D dilation can be obtained by composition of 1-D dilation. However, this often used technique covers only a limited family of shapes, such as rectangles, diamonds. In the following we will present the overview of algorithms that allow us to obtain more complex 2-D SEs.

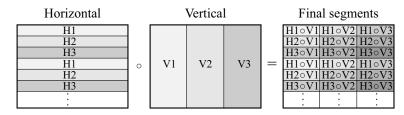

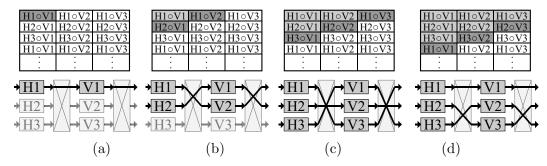

[Soille 1996] propose an approach to approximate circles and polygons by using SE decomposition into a set of line SEs rotated by different angles. The complete dilation by a polygon requires several iterations over the image. Each line SE is computed by the fast 1-D HGW algorithm oriented by the desired angle. The

| Algorithm         | SE type | Comparisons          | Algorithm | Data   | Working |

|-------------------|---------|----------------------|-----------|--------|---------|

|                   |         | per pixel            | latency   | memory | memory  |

| Naive 1-D         | User    | l-1                  | 0         | N      | 0       |

| HGW               | Sym     | 3 - 4/l              | 1         | N      | 2l      |

| Lemire            | Causal  | 3                    | 0         | 0      | 2l      |

| Lemmonier         | Sym     | $NC(\mathcal{O}(1))$ | N         | N      | N       |

| Van Droogenbroeck | Sym     | $NC(\mathcal{O}(1))$ | 0         | N      | N+G     |

| Buckley           |         |                      |           |        |         |

| Dokládal          | User    | 3                    | 0         | 0      | 2l      |

TABLE 3.1: COMPARISON OF FAST 1-D DILATION ALGORITHMS.

Sym = symmetric SE; User = User-defined SE; l = length of a 1-D SE; N = line size; G = number of gray levels; NC = not communicated.

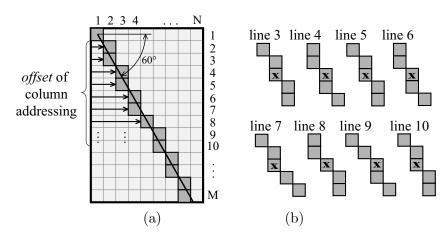

orientation of the SE is achieved through image partition into discrete lines (parallel, with no overlap), along which the HGW operates. The main drawback of such an image partition is that the result SE is translation variant; the shape of the SE varies along the discrete line. The translation variance, which makes that the adjunction is not verified, may introduce undesired artifacts to many application, such as filters.

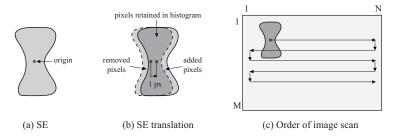

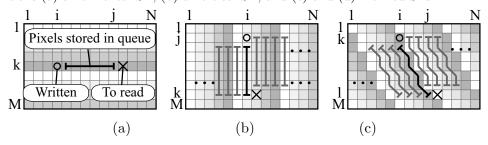

In [Van Droogenbroeck 1996] the authors proposed an algorithm for arbitrary-shaped 2-D SEs that takes advantage of a histogram to compute the dilation of pixels covered by the SE scanning the image. As the SE slides over the image by 1 px long translation, the histogram is not computed all over again from scratch, but only updated instead. The update of the histogram consists of removing pixels that are no longer covered by the SE (see the left-hand side of the SE in Fig. 3.3 (b)), and adding new pixels that become covered at the current position (see the right-hand side of the SE in Fig. 3.3 (b)). The SE does not slide over an image in the common scan order, it uses a horizontal zigzag pattern instead, see Fig. 3.3 (c). Typical complexity (for a square SE) of this algorithm is  $\mathcal{O}(H \log_2(G))$ , but this algorithm suffers from usage of the histogram (which does not allow for high-precision numbers) and non-causal zigzag image scan.

**Figure 3.3:** Histogram-based algorithm for arbitrarily shaped SEs: (a) example of SE, (b) SE translation by 1 px, (c) horizontal zigzag scanning pattern.

Recently, [Urbach 2008] propose an algorithm for arbitrary-shaped 2-D flat SEs

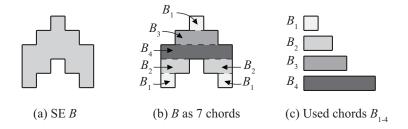

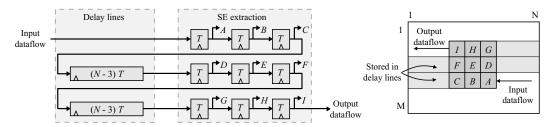

based on decomposition of the SE into a set of  $N_c$  elementary line SEs called chords, see Fig. 3.4 (b). The whole set of chords ( $N_c = 4$  chords in the case of Fig. 3.4) is computed for every pixel and stored in a look-up table. The result is then computed by taking a maximum from the values of all chords (stored in the look-up table) corresponding to the shape of the SE. Although the computation time is independent of the image content, a large look-up table (easily dozens of chords for each pixel) and non-optimized search of the maximum from the look-up table are the limiting factors for hardware implementation.

Table 3.2 outlines overview of the 2-D dilation algorithms described above.

**Figure 3.4:** Chords decomposition algorithm: (a) example of SE, (b) SE chords decomposition, (c) set of chords  $B_{1-4}$  to be computed for each pixel.

| Algorithm          | SE type | Complexity                | Algorithm | Data   | Working        |

|--------------------|---------|---------------------------|-----------|--------|----------------|

|                    |         | per pixel                 | latency   | memory | memory         |

| Naive 2-D          | User    | $\mathcal{O}(WH)$         | 0         | MN     | 0              |

| Urbach-            | User    | $\mathcal{O}(N_c +$       | MN        | MN     | $NH \log_2(W)$ |

| Wilkinson          |         | $\log_2(L_{max}(C))$      |           |        |                |

| Van Droogenbroeck- | User    | $\mathcal{O}(H\log_2(G))$ | 0         | NH     | WHG            |

| Talbot             |         |                           |           |        |                |

| Dokládal           | Rect    | $\mathcal{O}(1)$          | 0         | 0      | 2(W+NH)        |

| (SE decomposition) |         |                           |           |        |                |

Table 3.2: Comparison of fast 2-D dilation algorithms.

Rect = rectangular SE; User = User-defined SE;  $N \times M$  = image size;  $W \times H$  = SE size; G = number of gray levels;  $L_{max}(C)$  = maximum chord length,  $N_c$  = number of chords.

#### 3.1.3 1-D Opening Algorithms

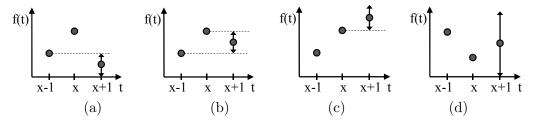

1-D opening algorithms can be divided into three classes: (i) two-stage algorithms, (ii) direct computation, and (iii) connected component trees (CCT). The last-named approach is very complex containing several advanced techniques such as building CCT, computation of attributes, image restitution, and is mentioned just for completeness. The description of CCT algorithms can be found in [Salembier 1998] [Menotti 2007] [Wilkinson 2008] [Matas 2008].

The two-stage algorithms stem from a concatenation of erosion and dilation,

such as

$$\gamma_B(f) = \delta_{\widehat{R}}[\varepsilon_B(f)]. \tag{3-4}$$

where the hat  $\hat{B} = \{x | -x \in B\}$ , which may be difficult to achieve efficiently for some shapes of SEs. Also this approach demands two scans of input image. These two downsides can be overcome by the direct computation.

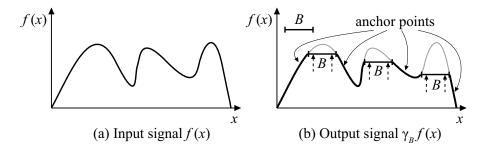

**Figure 3.5:** Illustration of opening algorithm using anchors. Anchors are those points of the signal that are not changed by opening: (a) input signal f(x), (b) output signal  $\gamma_B f(x)$ .

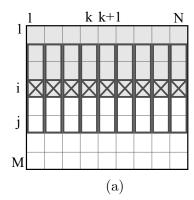

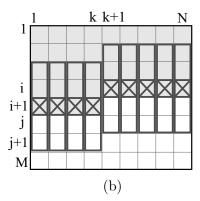

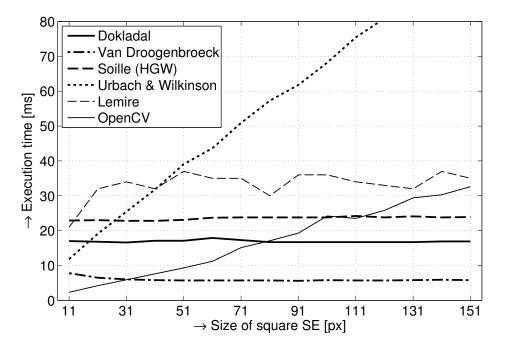

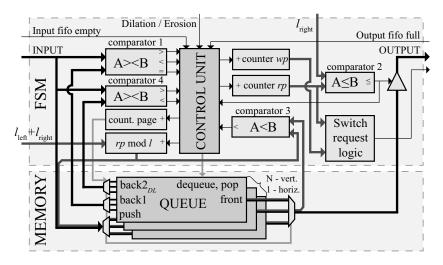

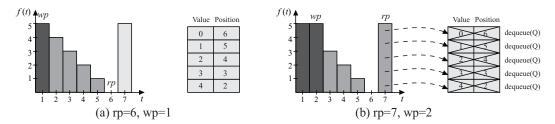

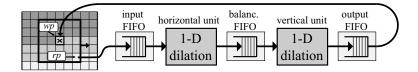

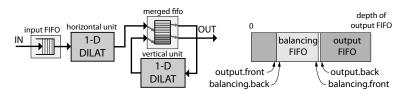

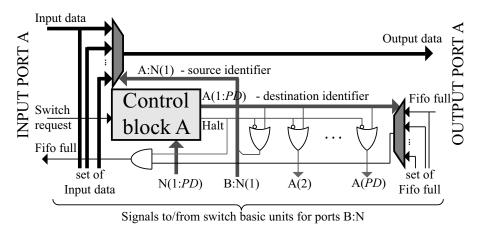

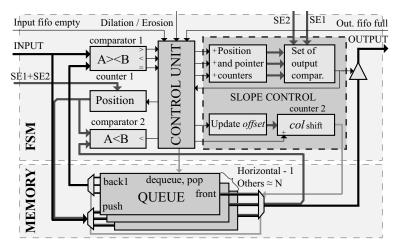

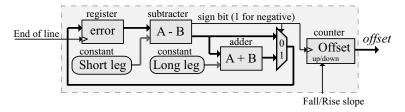

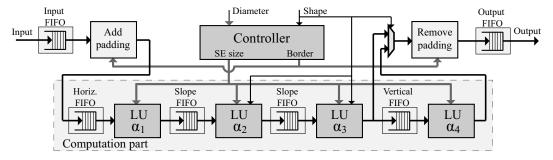

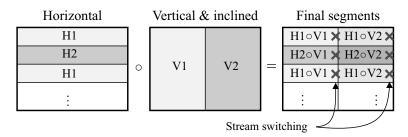

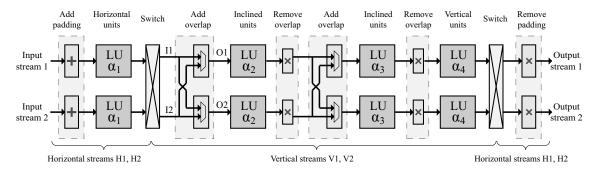

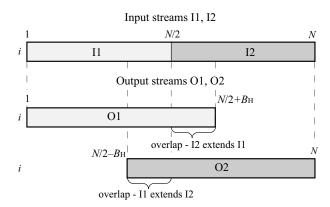

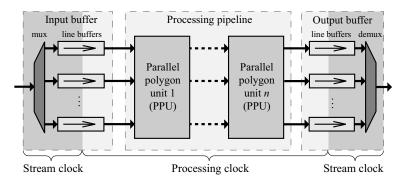

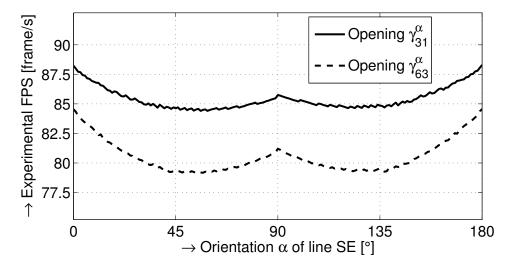

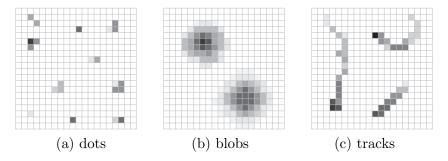

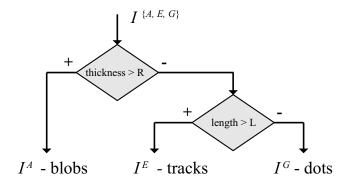

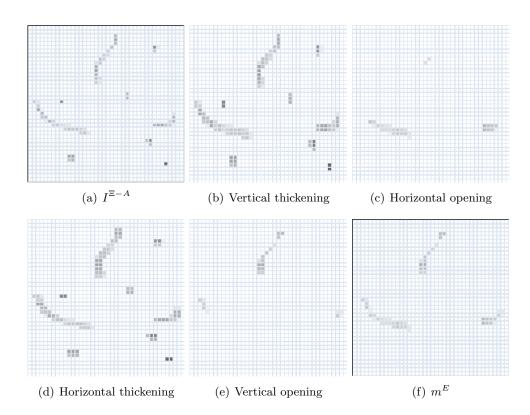

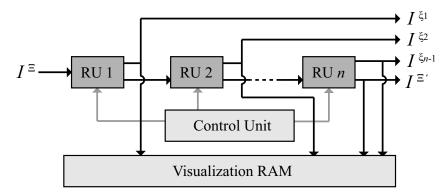

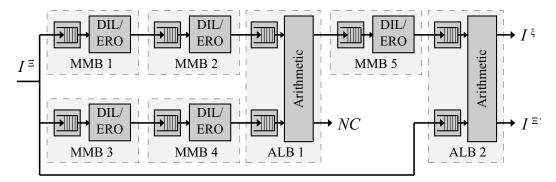

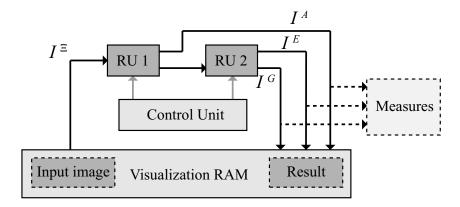

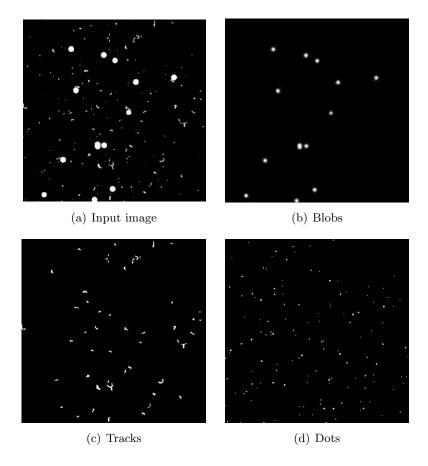

One direct approach was introduced in [Van Droogenbroeck 2005]. The authors brought in a new notion of anchors, the points that are not changed by the opening operation, i.e., f(a) is an anchor if  $f(a) = \gamma_B f(a)$ . In order to decide whether a pixel is an anchor or not, 6 different signal patterns are to be tested. All pixels between two anchors are replaced by the value of anchors. This tends to a rather complex code (however,  $\mathcal{O}(1)$ ), large memory demands, random access to data, and due to the use of a histogram, the high-precision data are very penalizing. Therefore, this algorithm is suitable for neither the GPU nor dedicated hardware implementation. On the other hand, it is still the fastest solution for opening on general-purpose processor platforms, which cope with random memory accesses and complex code much better.