# Modélisation, caractérisation et analyse de systèmes de PLL intégrés, utilisant une approche globale puce-boîtier-circuit imprimé

Manohiaina Ranaivoniarivo

#### ▶ To cite this version:

Manohiaina Ranaivoniarivo. Modélisation, caractérisation et analyse de systèmes de PLL intégrés, utilisant une approche globale puce-boîtier-circuit imprimé. Autre. Université Paris-Est, 2011. Français. NNT: 2011PEST1045. tel-00779319

### HAL Id: tel-00779319 https://theses.hal.science/tel-00779319

Submitted on 22 Jan 2013

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# UNIVERSITÉ PARIS-EST ÉCOLE DOCTORALE MSTIC

#### Thèse de Doctorat Electronique Optronique et Systèmes

#### par Manohiaina RANAIVONIARIVO

# MODELING, CHARACTERIZATION AND ANALYSIS OF INTEGRATED PLL SYSTEMS USING A GLOBAL CHIP-PACKAGE-BOARD APPROACH

Soutenue le 15 décembre 2011

#### Membres du Jury:

DIRECTION ET ENCADREMENT:

Odile PICON Professeur, ESYCOM, Université de Paris Est - Marne la Vallée

Sidina WANE Dr.-Ing., Principal, NXP Semiconducteurs Caen

RAPPORTEURS:

Raymond QUÉRÉ Professeur, XLIM, Université de Limoges

Junwu TAO Professeur, ENSEEIHT-Laplace, INPT, Université de Toulouse

EXAMINATEURS:

Fadhel GHANNOUCHI Professeur, Director of iRadio Laboratory, University of Calgary

Zhuoxiang REN Professeur, Université Paris-VI Pierre et Marie Curie

Patrice GAMAND HDR.-Ing, General Manager ICRF, NXP Semiconducteurs Caen

$\mathrel{<\!\!\!<} \dots$  cherchez, et vous trouverez ;  $\dots \mathrel{>\!\!\!\!>}$  Luc XI, 9

#### REMERCIEMENTS

En trois ans et plusieurs mois de thèse sur un thème large mais précis, j'ai dû je pense comme tout autre thésard connaître des hauts et des bas, des très haut et des très bas aussi bien techniquement que personnellement... Et il ne suffit pas forcément de chercher pour trouver la réponse adaptée à une problématique donnée, pour obtenir la réponse à la question posée.

Ce travail de thèse est ma propre réponse, mon interprétation du sujet. Je n'aurais pas pu le réaliser sans l'aide, l'assistance et les encouragements de certaines personnes. Pour cela, je leur dis, je vous dis merci.

Tout d'abord, je tiens à remercier messieurs Raymond Quéré et Junwu Tao qui ont bien voulu rapporter cette thèse et qui ont donné leur avis favorable afin que je puisse soutenir mon travail et obtenir le titre de Docteur de l'Université de Paris Est.

Je remercie aussi tous les membres de mon jury qui ont accepté d'accorder un peu de leur temps pour s'intéresser à mes travaux.

Cette thèse CIFRE a été réalisée à travers une collaboration entre l'Université de Paris-Est - Marne la Vallée et NXP Semiconducteurs Caen.

Coté académique, j'exprime ma profonde reconnaissance à madame Odile Picon, mon directeur de thèse, pour m'avoir fait confiance tout au long de cette thèse, pour ses multiples conseils et recommandations, ses efforts côté administratifs afin que la soutenance se déroule pour le mieux. Je remercie aussi madame Elodie Richalot, pour ses précieuses remarques et recommandations, d'avoir bien voulu revoir mon manuscrit minutieusement ainsi que pour sa sincérité technique.

Toujours dans le cadre de mon encadrement, je pense que je pourrais écrire tout un chapitre de thèse pour adresser mes remerciement à mon encadrant en entreprise : monsieur Sidina Wane. Pour faire court, merci pour tout Sidina.

Côté NXP, je tiens à remercier en premier lieu, monsieur Patrice Gamand qui a transmis mon CV à NXP et qui a donc pu rendre possible cette thèse CIFRE. Je le remercie aussi d'avoir pu mettre à ma disposition tous les moyens humains, matériels et financiers afin que mon intégration et mes travaux se déroulent pour le mieux au sein de NXP.

Je remercie aussi vivement les responsables de groupes qui m'ont accueillie et fait confiance : madame Dominique Lohy et madame Christine Dufour pour Corp. I&T ainsi que monsieur Alain Cousin et monsieur Patrice Gamand pour l'ICRF.

Merci à tous mes collègues pour les échanges technique et non technique qui ont facilités ces 3 ans et demi.

Un grand merci et bravo aux assistantes : mesdames Sylvie Cach de l'UPE, Marie José Moréno pour l'ICRF, et Oranne Potier pour Corp I&T. Pleines de talents, d'efficacité et de gentillesse, beaucoup de choses n'auraient pas pu se faire sans leurs interventions.

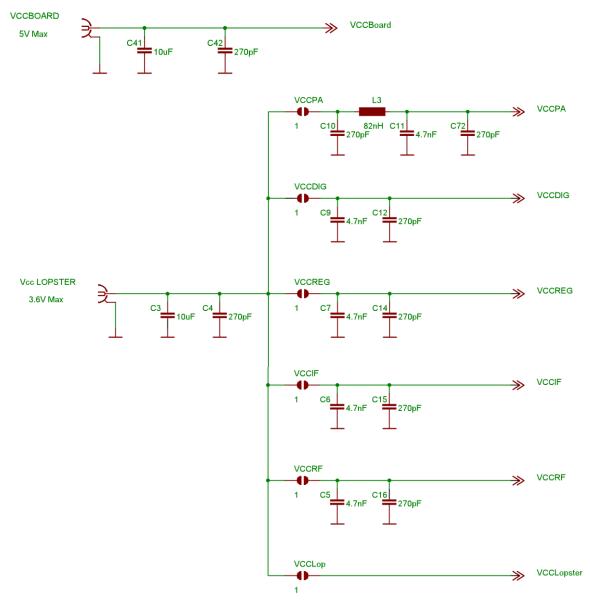

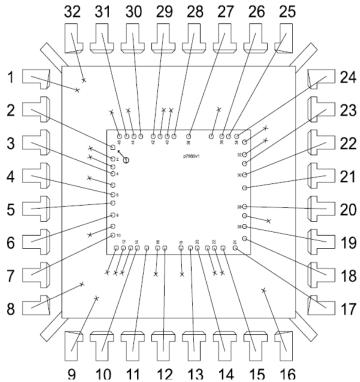

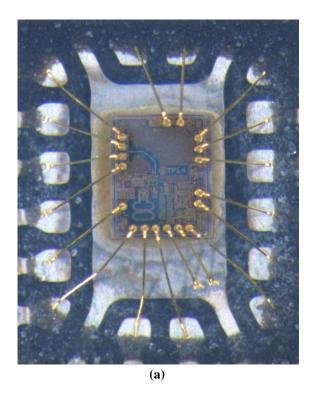

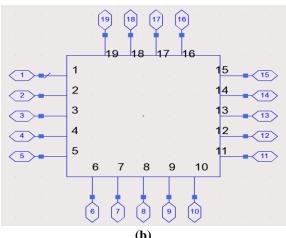

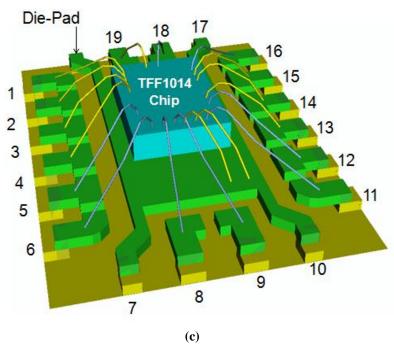

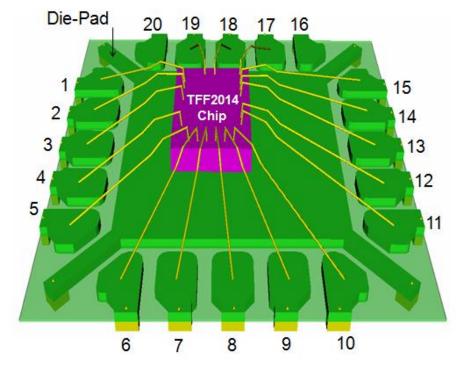

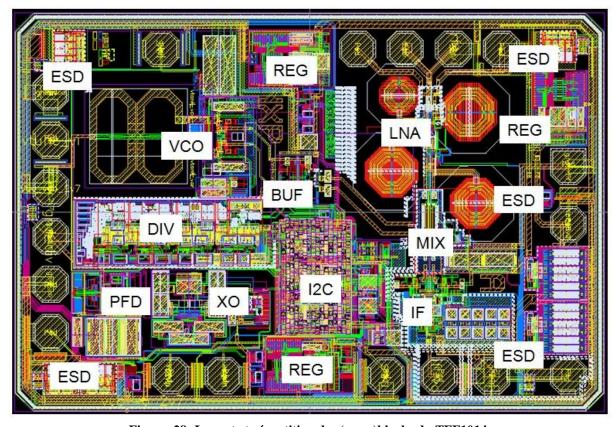

Un merci spécial pour les personnes qui m'ont aidée techniquement. Concernant le projet LoPSTer, merci à Olivier Aymard, Sebastien Darfeuille, Mathieu Périn, Alexis Legrontec et Laurent Monge. Pour le projet TFF1014, merci à Pascal Philippe, Eric Thomas, Serge Bardy, Celine Barbier-Petot, François Moreau et bien sûr Sidina Wane.

Afin d'avoir rendu possible et avec qualité mes résultats de mesure, merci à messieurs Dominique Lesenechal et Philippe Descamps.

Merci à monsieur Stéphane Protat de l'université de ne pas avoir ménagé ses efforts pour les simulations EM.

Merci aux personnes du CAD/IT d'avoir débugué à plusieurs reprises mes jobs : Samuel Mabire pour Sonnet, Laurent Langlais pour UNIX, Bertrand Cesbron pour Matlab et Jean François Aupée pour les problèmes de quotas.

Merci à mes voisins de bureau, Eric Lehouelleur, François Moreau, Eric Thomas, qui m'ont aidée sur parfois des broutilles IT, mais qui m'ont énormément rendu service.

Merci aussi à mes collègues thésards de NXP: Hugues Kampé, Magali Duplessis, Mathieu Périn, Laure Rolland du Roscoat, Bilal El Kassir, Pierre Guillot et Sandeep Kowlgi. Les trucs et astuces techniques, conseils donnés et réconforts m'ont bien servis, fait rire, et remonté le moral en des temps parfois assez difficiles.

Des remerciements un peu plus personnels maintenant...

Je voudrais remercier les copains du FPMA Caen, pour ces après midis et soirées de rigolade, de piété, et de reconstruction du monde et de Madagascar à n'en plus finir. Qui sait, peut être qu'un jour, nous nous y retrouveront tous « ho an'i Tanindrazana »!

Un grand merci aussi à l'équipe Alpha Hérouville, pour leur gentillesse, leur accueil et surtout pour certaines séances qui m'ont fait un bien fou.

Merci à mes professeurs de Physique/Chimie du collège et du lycée : messieurs Tida et Molliex, qui ont su attiser ma curiosité et m'ont donné goût aux sciences de l'ingénieur.

Enfin, je remercie du fond du cœur ma famille, qui m'a épaulée durant toutes ces années. Merci à mes parents Mamy et Michelle Ranaivoniarivo, qui, grâce à leur soutient indéfectible, leurs encouragements, leurs privations, m'ont permis de finir enfin mes études dans une certaine sérénité. Merci à Loharanontsoa Moreau et toute sa petite famille pour leur soutient et leur disponibilité. Merci à Walid Galal El Dine pour ces années pas faciles, mais on y est maintenant!

Merci à vous aussi, qui prenez le temps de lire ce manuscrit.

#### **ABSTRACT**

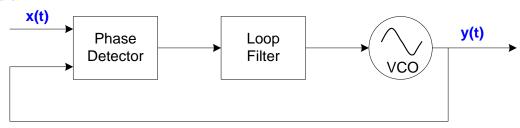

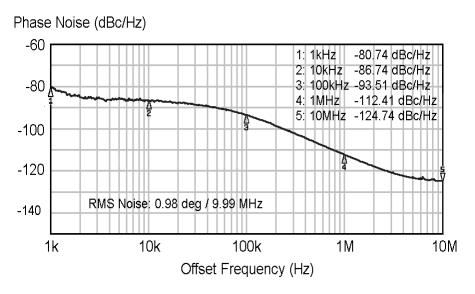

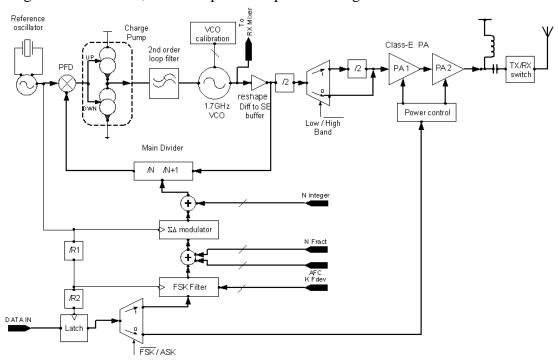

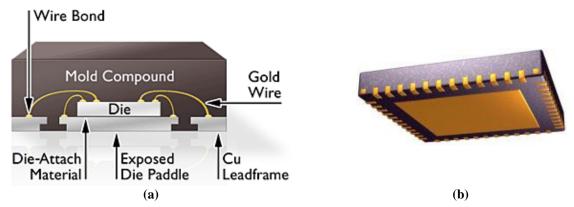

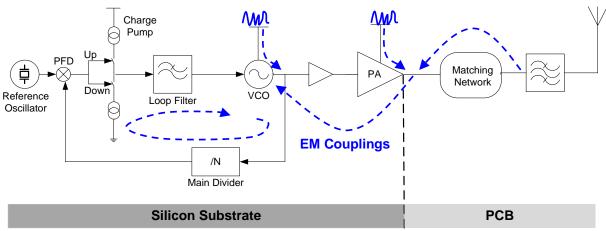

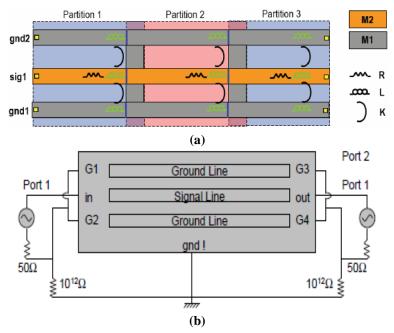

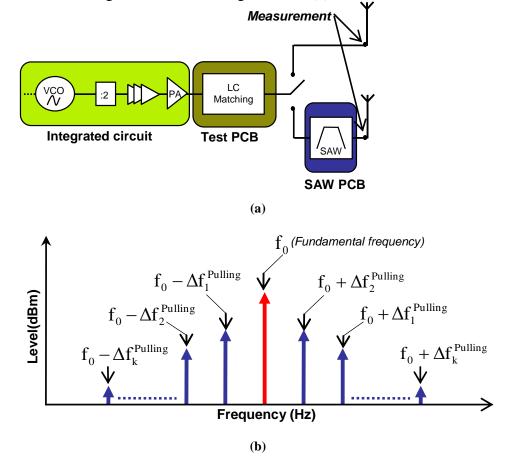

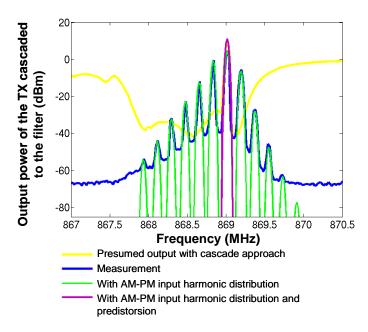

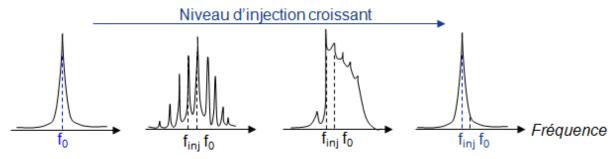

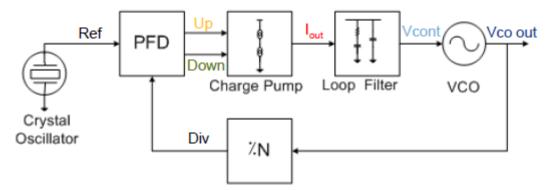

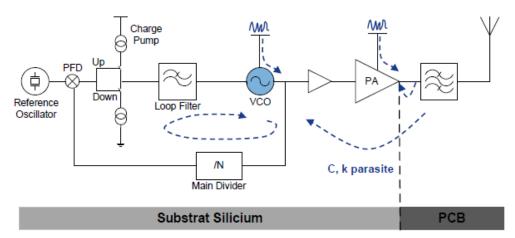

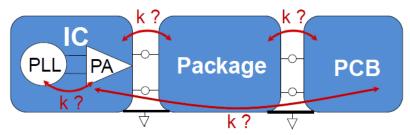

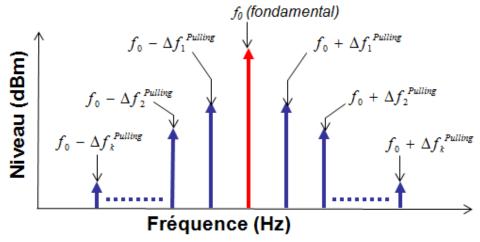

This thesis work focuses on characterization, modeling and analysis of «Pulling» and «Pushing» phenomena in Phase Locked Loops (PLL) based on a global approach where distributed effects of electromagnetic couplings at different integration levels (chip-level, assembly-level, board or PCB-level) are taken into account.

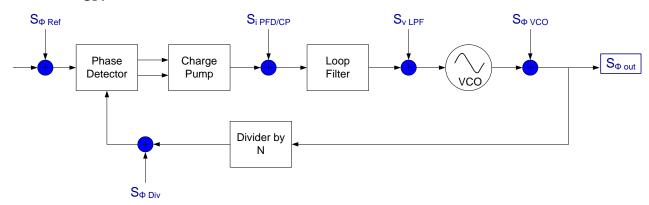

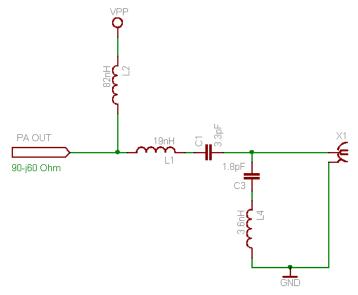

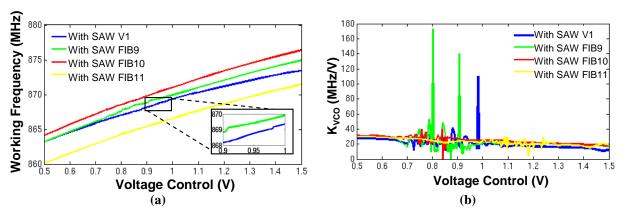

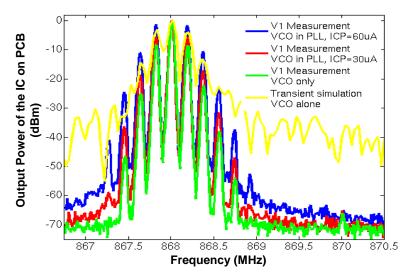

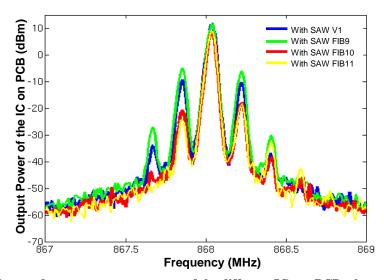

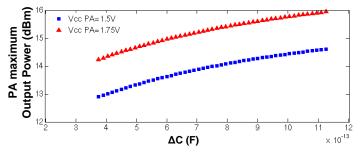

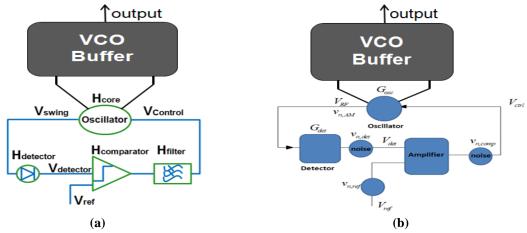

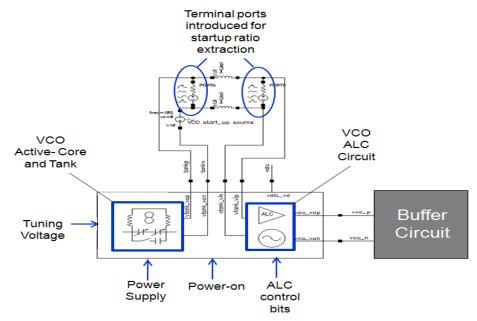

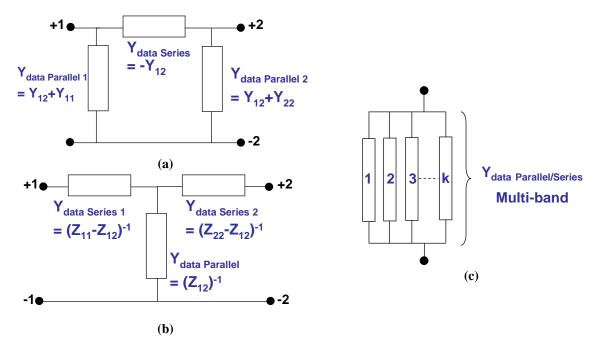

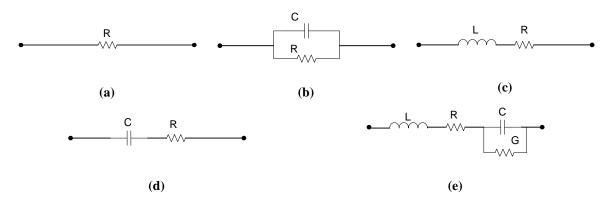

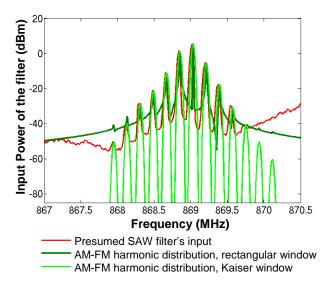

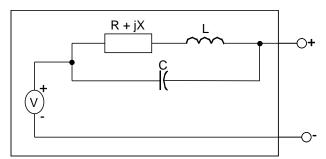

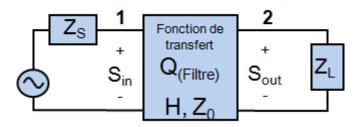

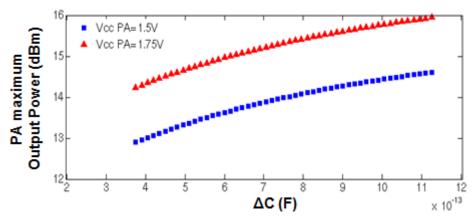

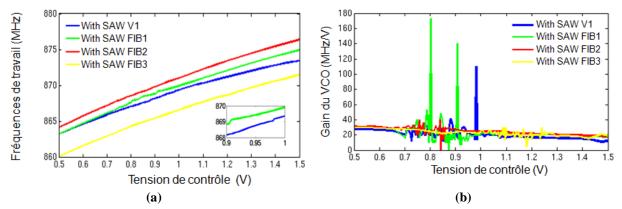

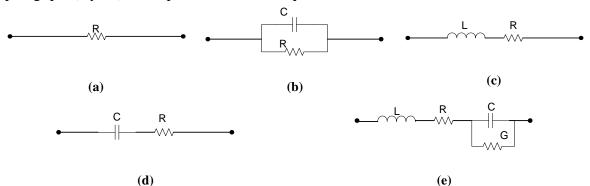

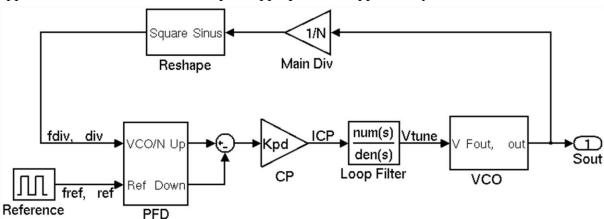

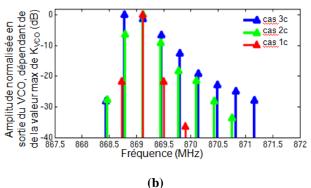

The modeling approach adopts a hybrid methodology where the analysis of electromagnetic couplings combined with broadband equivalent circuit synthesis (compatible with library models of active components) is coupled with dynamic behavioral representations. The derived behavioral representations properly capture the effects of nonlinearities both at component scale (non-linear characteristic of varicap devices as function of control voltages) and at function block level (non-uniform gain  $K_{VCO}$  of VCO circuits depending on frequency).

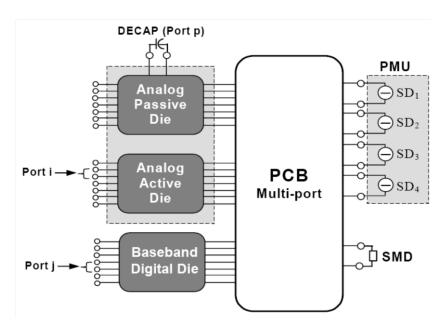

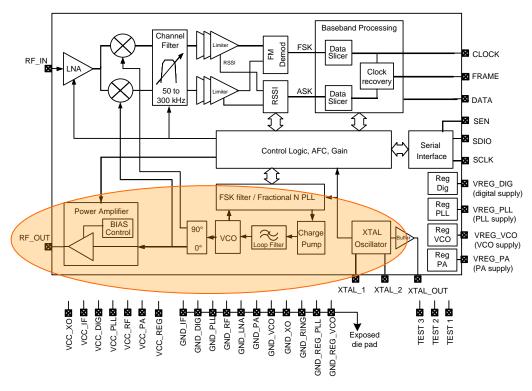

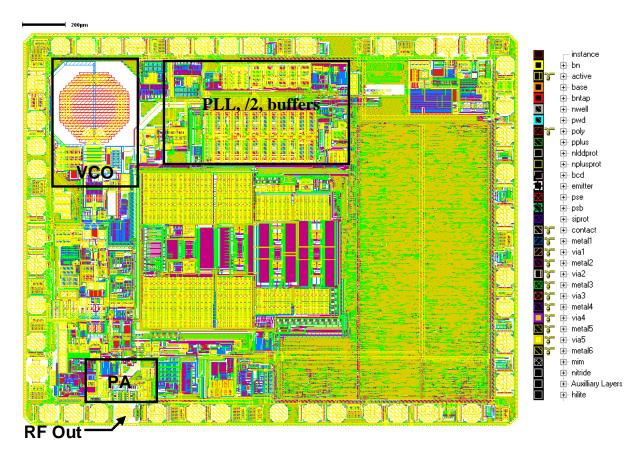

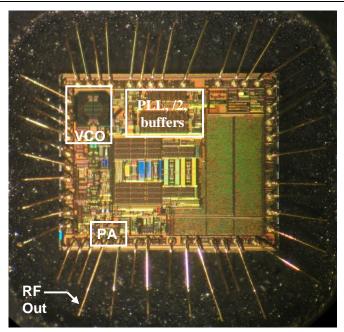

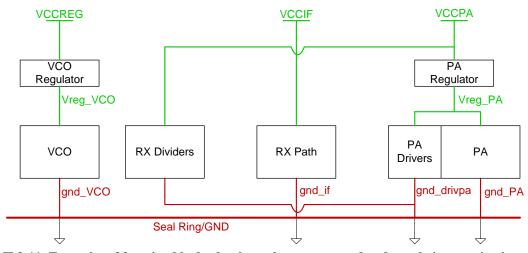

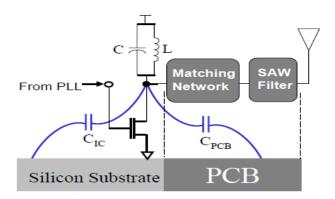

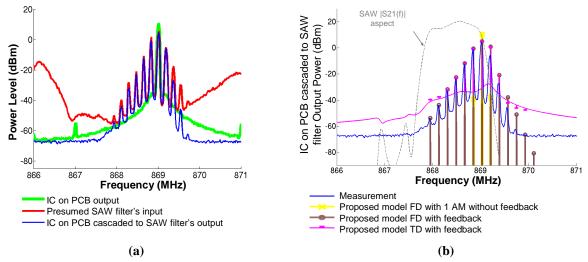

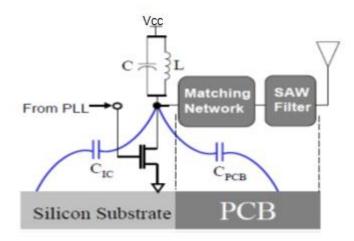

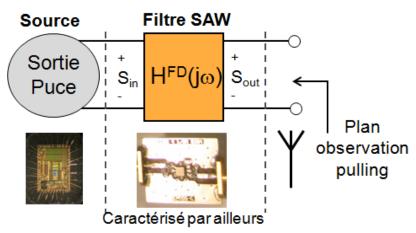

The hybrid methodology renders possible the assessment of competitive effects resulting from «Pulling» and «Pushing» phenomena at chip level (*influence of the PLL*, *effects of the power amplifier*, *power integrity*, *or ground reference distribution*, *etc.*.), and the distortions induced by components external to the chip at package and board levels (*such as components on PCB: SAW filters, decoupling capacitors, matching networks*).

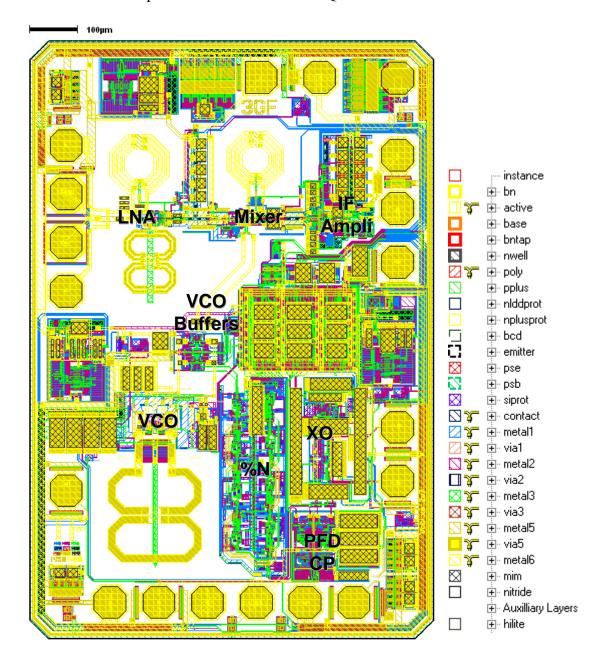

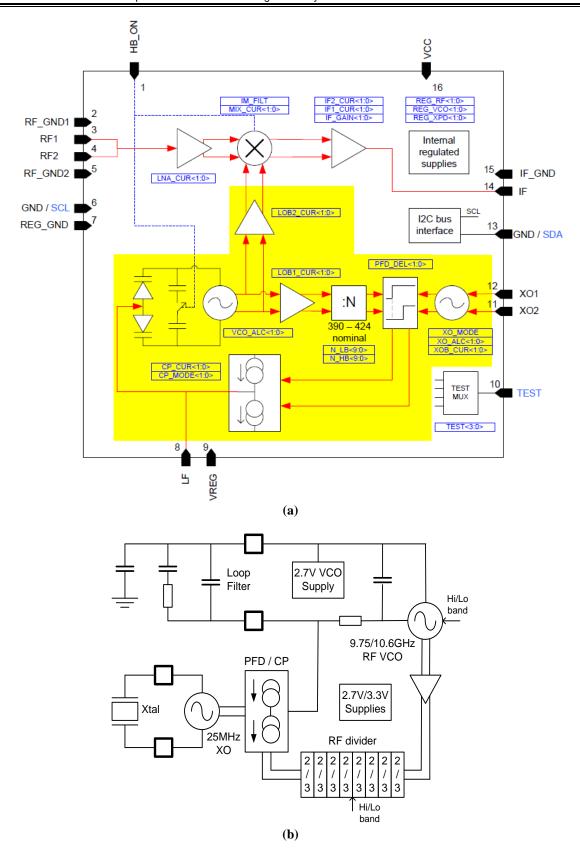

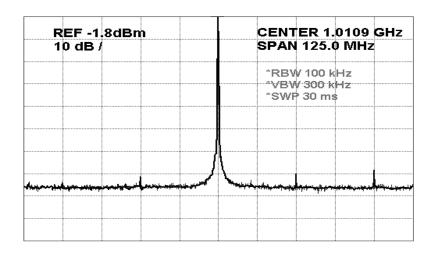

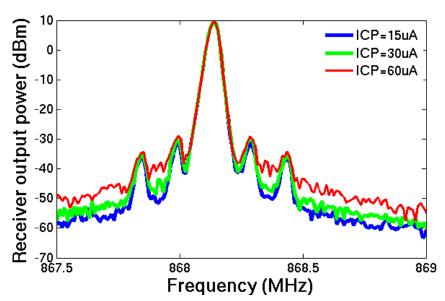

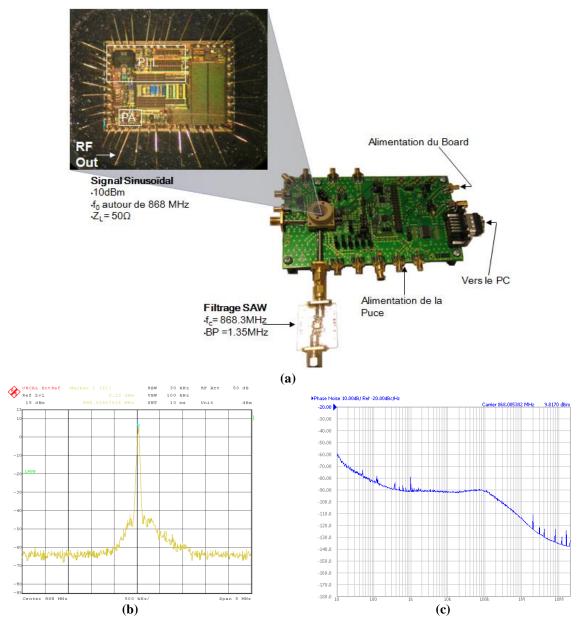

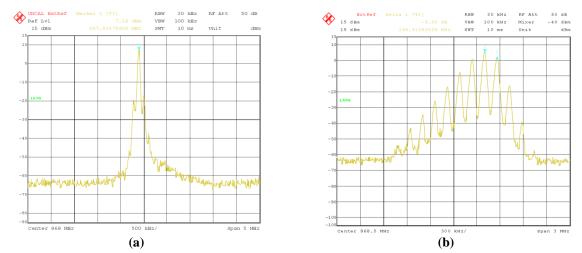

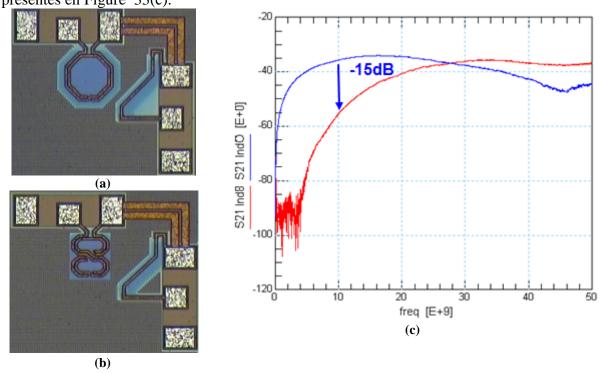

The proposed approach is used for the study and design of two types of circuits developed by NXP-Semiconductors: an application related to automotive security and immobilization (an RF low power transceiver Integrated Circuit, *PLL running around* 1.763GHz), and a satellite receiver (*PLL operating at low power for LNB circuits working at* 9.75/10.6 GHz).

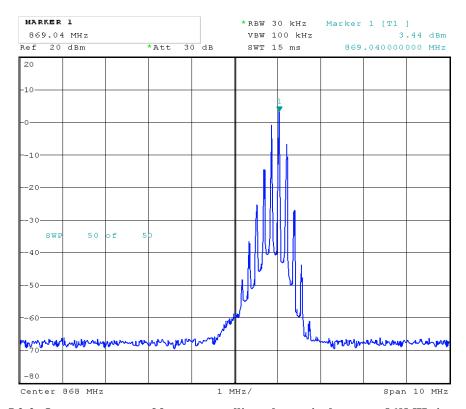

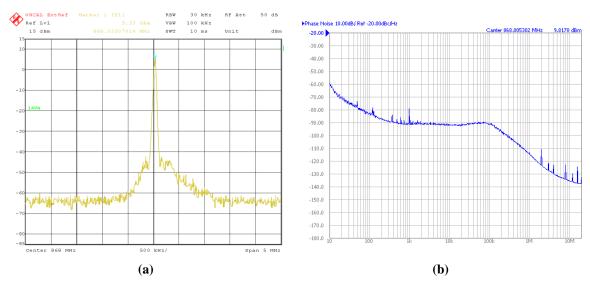

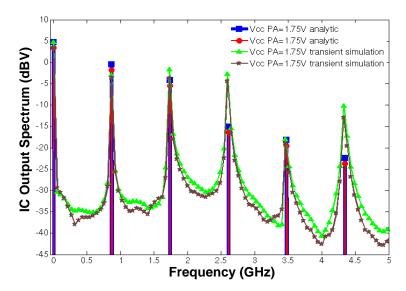

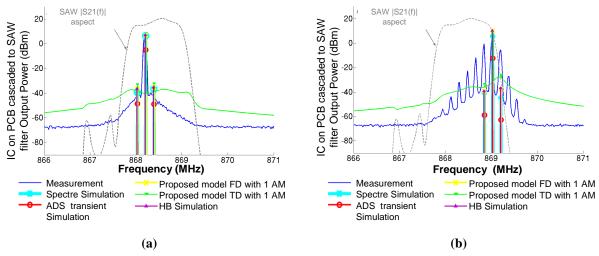

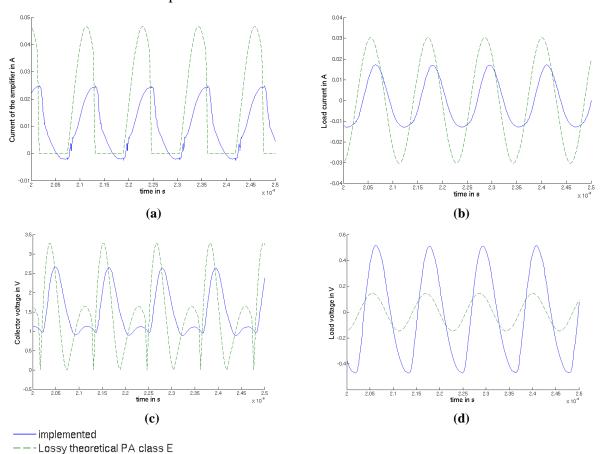

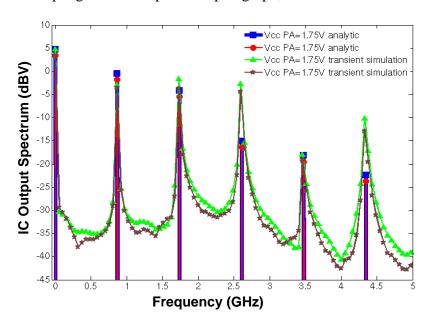

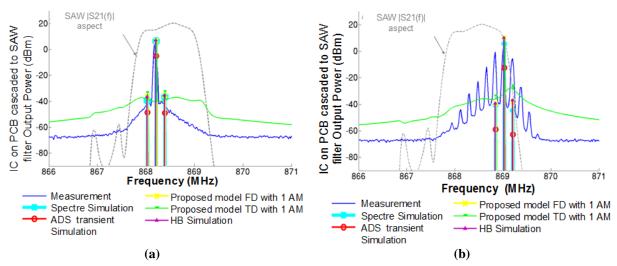

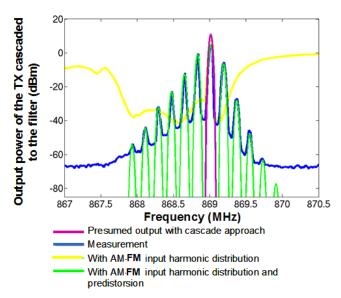

The obtained modeling results are validated by correlation with experimental data and by comparison with different time-domain and frequency-domain simulation tools results (ADS-Harmonic Balance, ADS-Shooting solutions, Cadence-Spectre).

**Key-Words:** PLL, VCO, Pulling and Pushing Effects, Electromagnetic Couplings, Chip-Package-Board Co-Simulation, Hybrid Methodologies, Behavioral Modeling.

# RÉSUMÉ

Cette thèse porte sur la caractérisation, la modélisation et l'analyse des phénomènes de «Pulling» et de «Pushing» dans les systèmes de boucles à verrouillage de phase (PLL), utilisant une approche globale où les effets de couplages électromagnétiques aux différents niveaux d'intégration (niveau puce, niveau assemblage, niveau report sur PCB) sont pris en compte de manière distribuée.

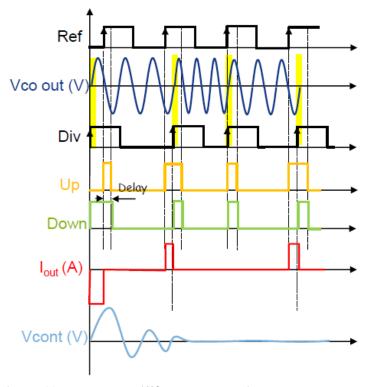

L'approche de modélisation adopte une méthodologie hybride où l'analyse des couplages électromagnétiques combinée à des schémas équivalents large-bande (compatibles avec les modèles de composants actifs disponibles dans les librairies) est couplée à des représentations comportementales dynamiques. Les représentations comportementales développées permettent de capturer des effets de non-linéarités tant au niveau composant (caractéristique non-linéaire des Varicap en fonction des tensions de contrôle) qu'au niveau block de fonction (gain  $K_{VCO}$  non uniforme de l'oscillateur contrôlé en tension (VCO) en fonction de la fréquence).

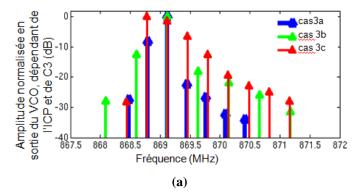

Cette méthodologie hybride permet l'évaluation d'effets compétitifs résultant de phénomènes de «pulling» et de «Pushing» au niveau de la puce (influence de la PLL, effets de l'amplificateur de puissance, intégrité des alimentations ou distribution des références de masse, etc.) , et des distorsions induites par des éléments extérieurs à la puce (exemple de composants sur PCB : Filtre SAW, capacités de découplages, réseaux d'adaptation).

L'approche proposée est utilisée pour l'étude et la conception de deux types de circuits développés par NXP-Semi-conducteurs pour des applications liées à la sécurité automobile (*PLL fonctionnant aux alentours de 1.736GHz*) et à la réception satellitaire (*PLL de faible consommation fonctionnant à 9.75/10.6 GHz pour les circuits LNB*).

Les résultats de modélisation obtenus sont validés par corrélations avec les données expérimentales et par comparaison avec les résultats obtenus de différents outils (ADS Harmonic-Balance/Transient de Agilent, Spectre de Cadence).

Mots clés : PLL, VCO, Effets de Pulling et de Pushing, Couplages Electromagnétiques, Cosimulation Puce-Boîtier-Circuit imprimé, Méthodologies Hybrides, Modélisation comportementale.

# **Table of Contents:**

| REMERCIEMENTS                                                                      | 5         |

|------------------------------------------------------------------------------------|-----------|

|                                                                                    |           |

|                                                                                    | _         |

| ABSTRACT                                                                           | <u> 7</u> |

|                                                                                    |           |

| RÉSUMÉ                                                                             | <u>9</u>  |

|                                                                                    |           |

| GENERAL INTRODUCTION                                                               | 23        |

|                                                                                    |           |

| CHAPTER I:                                                                         | 29        |

|                                                                                    |           |

| LINEAR AND NON-LINEAR TECHNIQUES FOR BEHAVIORAL MODELING OF PLL SYSTEMS            | 29        |

| I.0. Introduction                                                                  | 31        |

| I.1. Overview of State of the Art of Non-Linear Techniques for PLL Mod             |           |

| •                                                                                  |           |

| I.1.1. General considerations                                                      |           |

| Baseband and Passband signals                                                      |           |

| Modulation                                                                         |           |

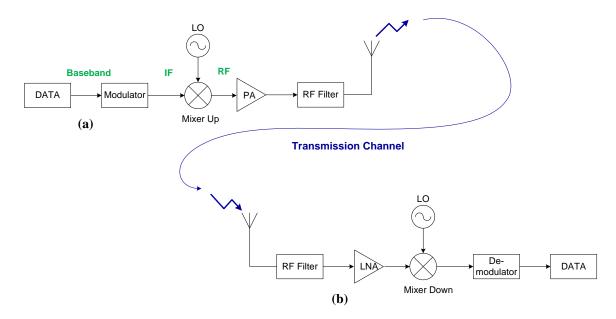

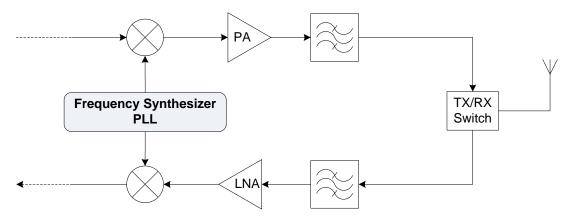

| b. RF Transmitter-Receiver systems                                                 |           |

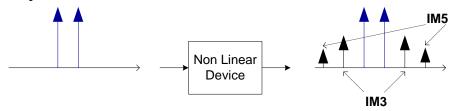

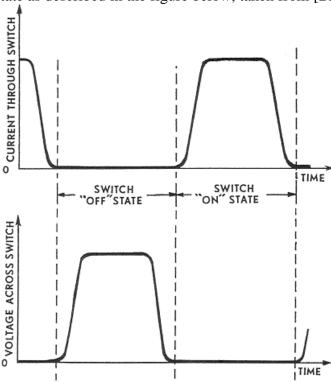

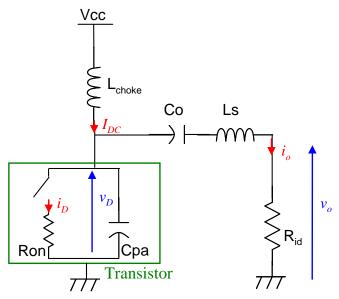

| c. The Power Amplifier                                                             |           |

| d. Phase Locked Loop Fundamentals                                                  |           |

| I.1.2. Small-Signal Analysis and Large-Signal Analysis                             |           |

| a. Small-Signal Analysis                                                           |           |

| b. Large-Signal Analysis                                                           |           |

| I.1.3. Behavioral Modeling Techniques                                              |           |

| I.1.4. Power-Series and Volterra Modeling                                          |           |

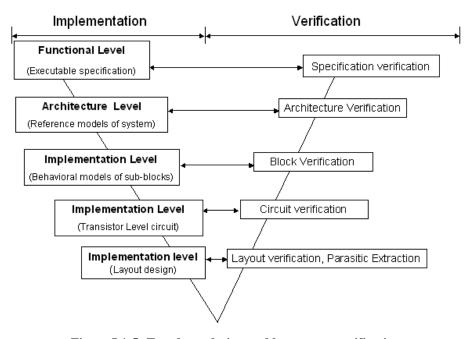

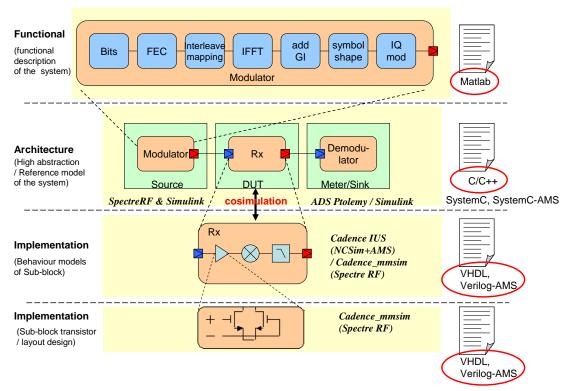

| I.1.5. Hybrid Models and Co-simulation                                             | 41        |

| I.1.6. Measurement Techniques                                                      | 43        |

| I.2. Simplification of PLL Systems for Design Specification: Predictive Challenges | 44        |

| I.2.1. State of the Art Design of Methodology Challenges for PLL Systems           | 44        |

| I.2.2. PLL Design Specifications: Importance of Spurs, Pulling and Pushing E       |           |

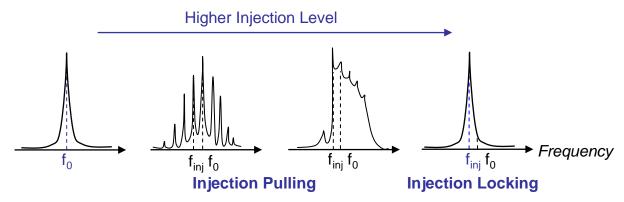

| a Available Techniques for Pulling Modeling and analysis                           | 17        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Spice-like simulations                                                                                                                                                        | 47                                                   |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Analytical Method                                                                                                                                                             | 48                                                   |

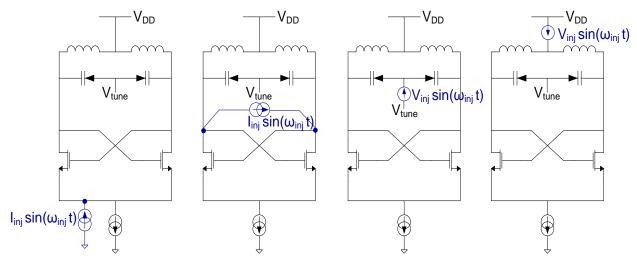

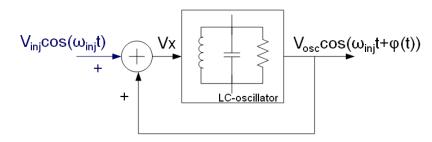

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | LC Oscillator Circuit and Injection                                                                                                                                           | 48                                                   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Perturbation Projection Vector (PPV)                                                                                                                                          | 49                                                   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Injection pulling in Phase-Locked Oscillators                                                                                                                                 |                                                      |

| h                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | b. Proposed Solutions in the Literature                                                                                                                                       |                                                      |

| ~                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Positive use of injection-locking                                                                                                                                             |                                                      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Pulling effects reduction                                                                                                                                                     |                                                      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | T dilling chools reduction                                                                                                                                                    |                                                      |

| 1.3. 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Context and Originality of the Proposed Contribution                                                                                                                          | 51                                                   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                               |                                                      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | .1. Motivation                                                                                                                                                                |                                                      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | .2. The Derived Methodology for Pulling Issues Analysis                                                                                                                       |                                                      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | a. To Model Sensitive Active Blocks:                                                                                                                                          |                                                      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | b. To tackle Co-Simulation Analysis:                                                                                                                                          |                                                      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | c. To account for EM Couplings:                                                                                                                                               |                                                      |

| 1.3.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | .3. The Challenges                                                                                                                                                            | 53                                                   |

| а                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | a. Simulation and Co-Simulation Challenges:                                                                                                                                   | 53                                                   |

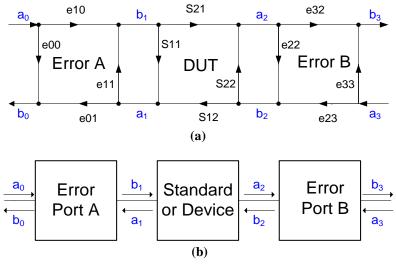

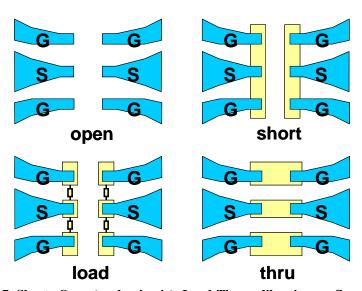

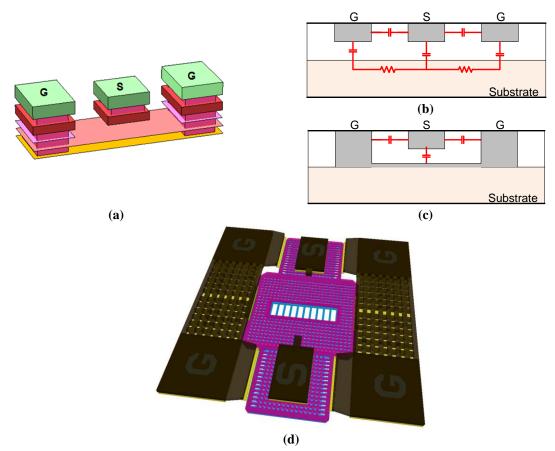

| b                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | b. Measurement/Characterization Challenges:                                                                                                                                   | 53                                                   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | -                                                                                                                                                                             |                                                      |

| I.4. A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Applications Description                                                                                                                                                      | 55                                                   |

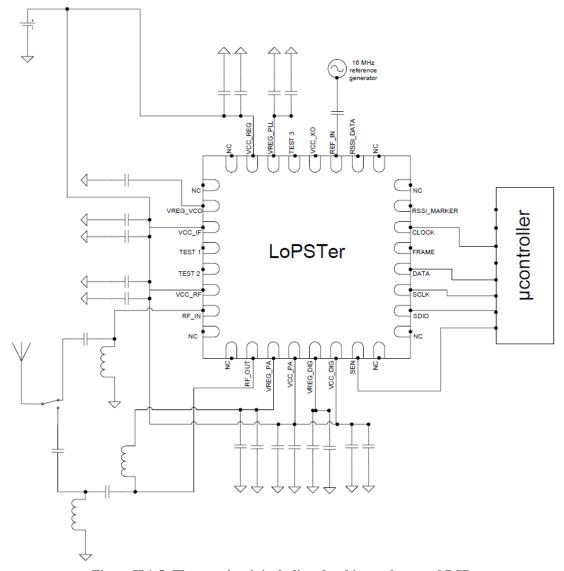

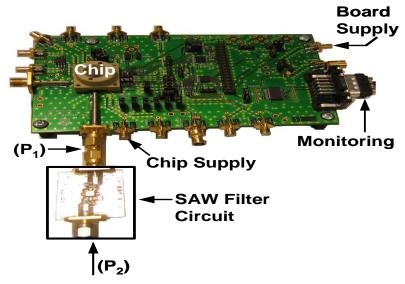

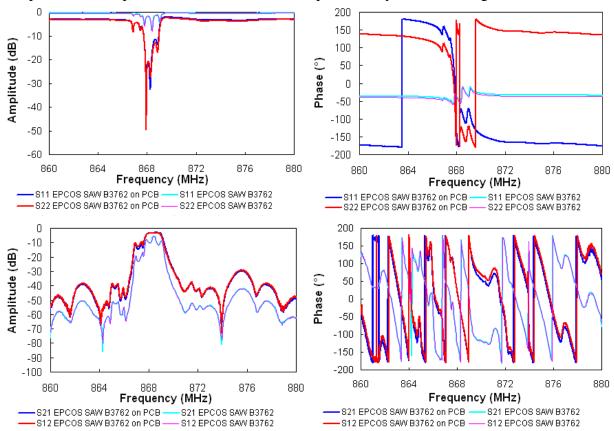

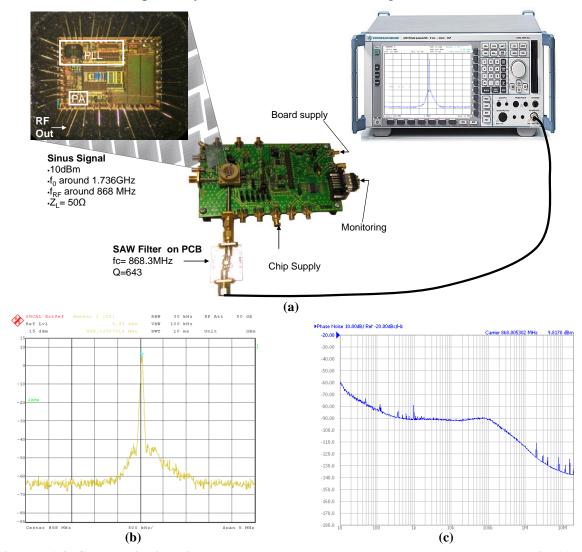

| 1.4.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | .1. An Automotive Car Access Transceiver Application around 868                                                                                                               | BMHz: the                                            |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | PSTer                                                                                                                                                                         |                                                      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | a. The LoPSTer's Description and the Automotive Specifications for the LoPSTer.                                                                                               |                                                      |

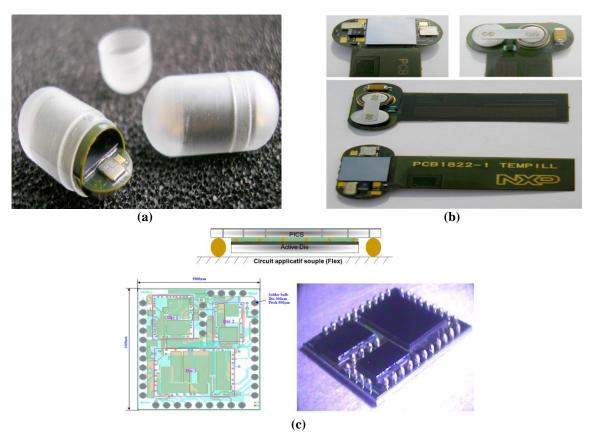

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | b. The LoPSTer in an Edible Capsule for Continuous Measurement of                                                                                                             |                                                      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Temperature                                                                                                                                                                   |                                                      |

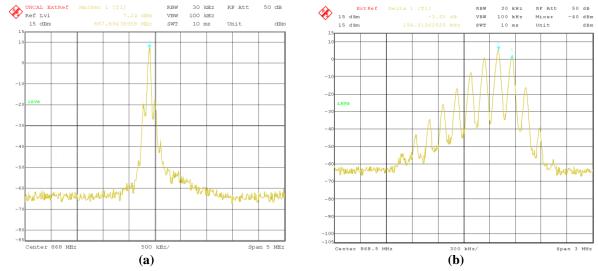

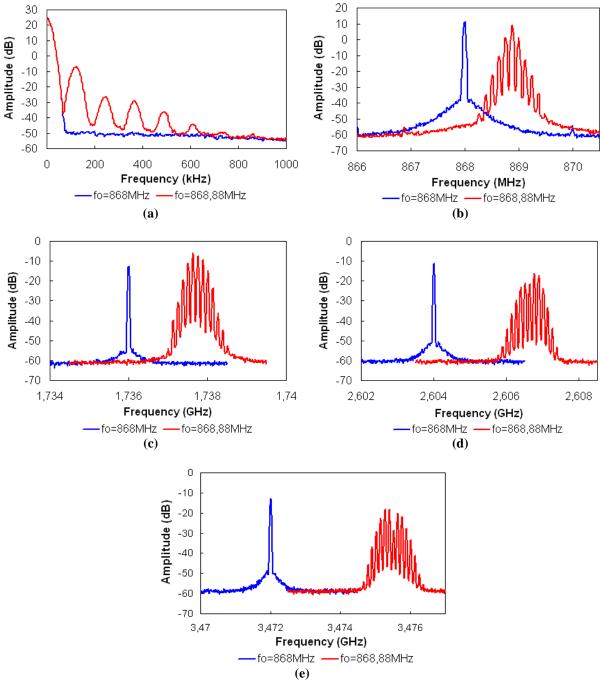

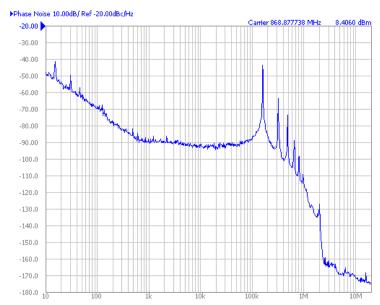

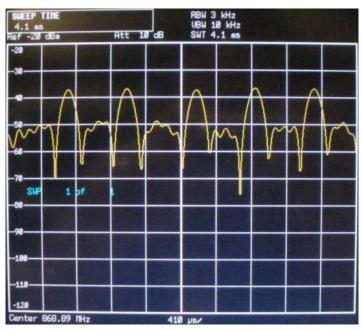

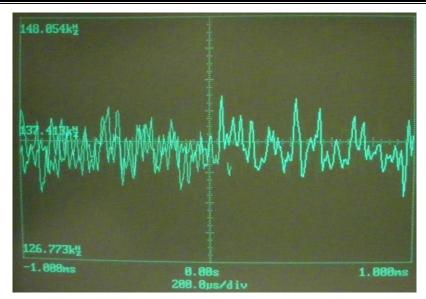

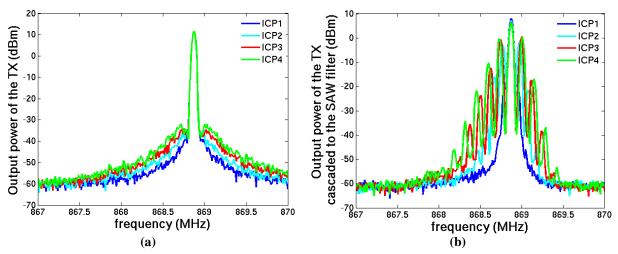

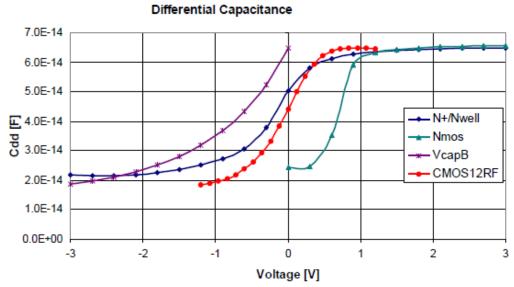

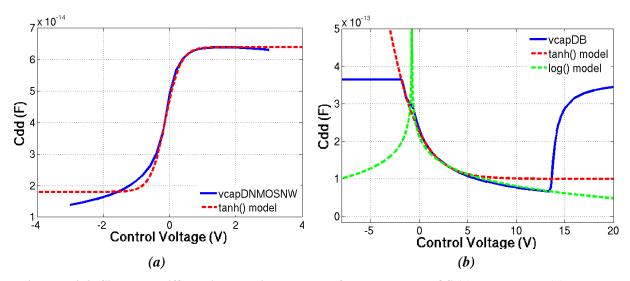

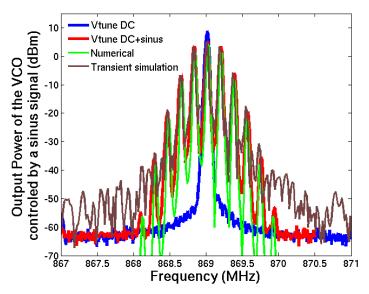

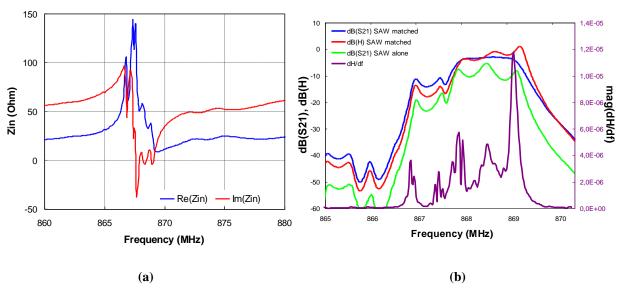

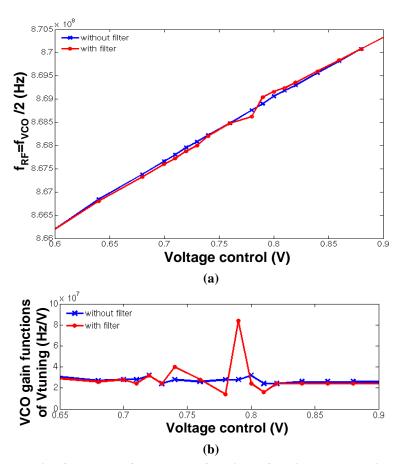

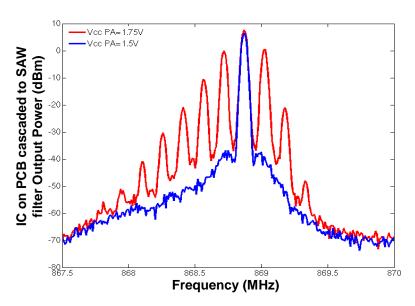

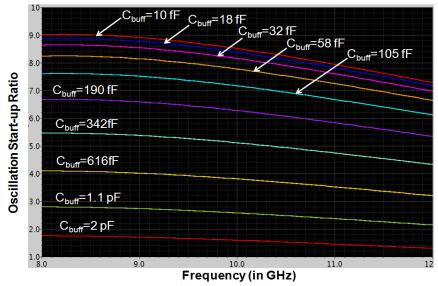

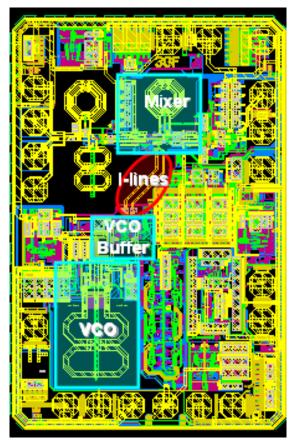

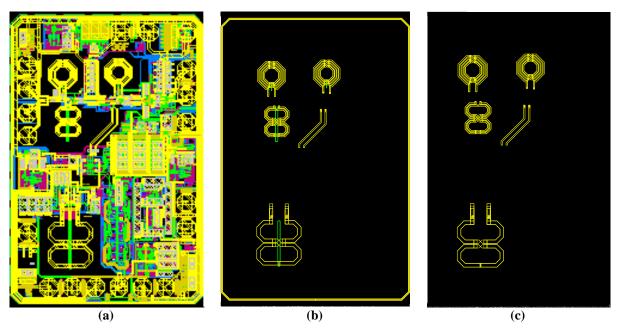

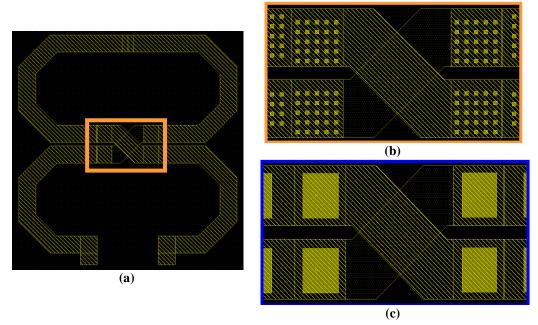

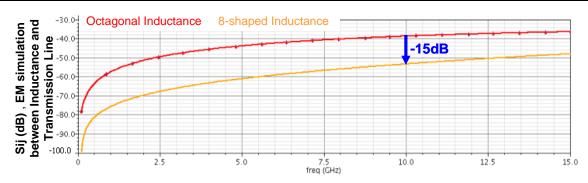

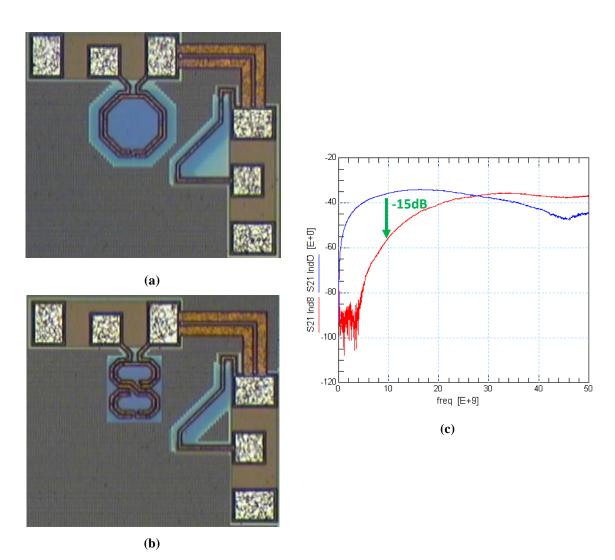

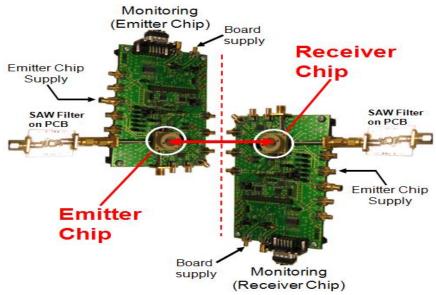

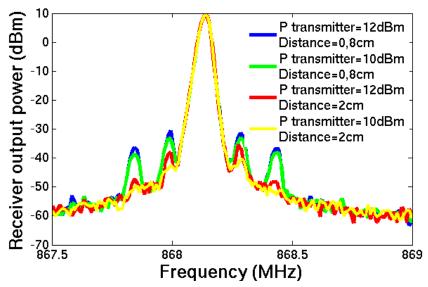

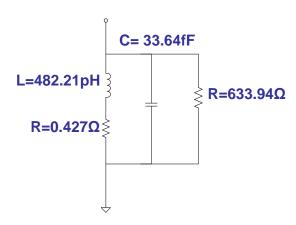

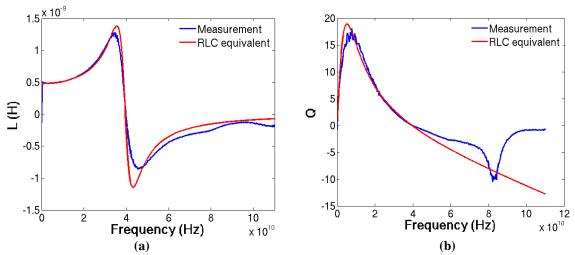

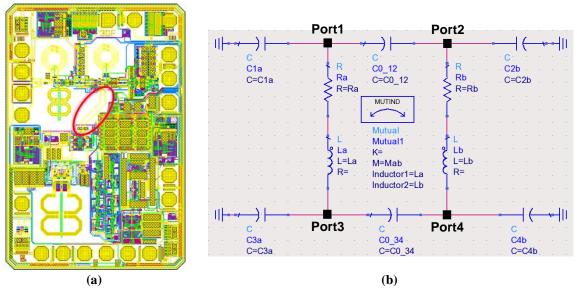

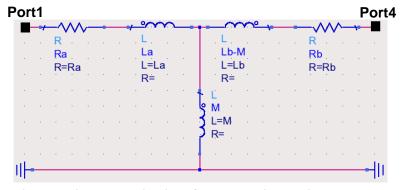

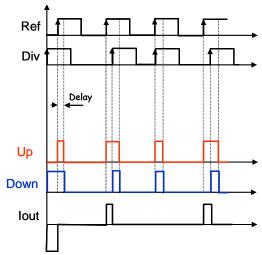

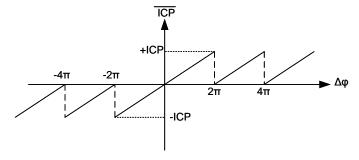

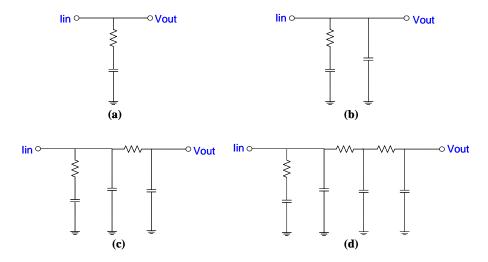

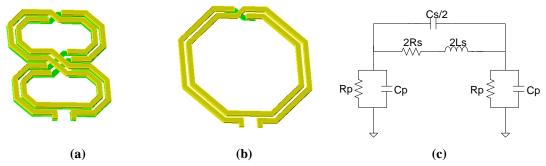

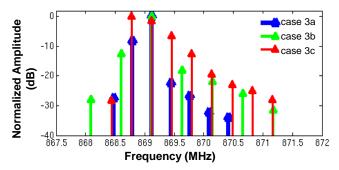

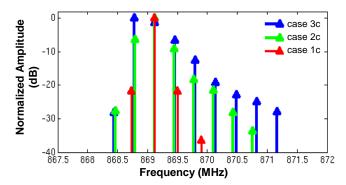

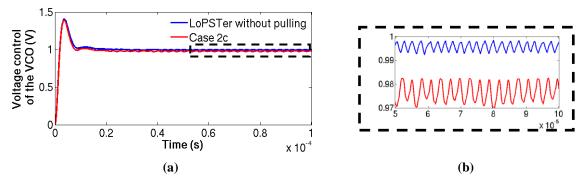

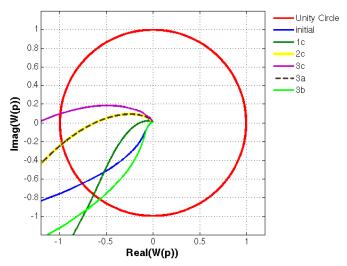

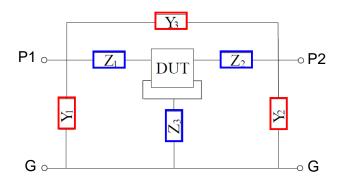

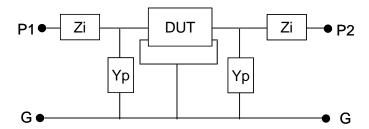

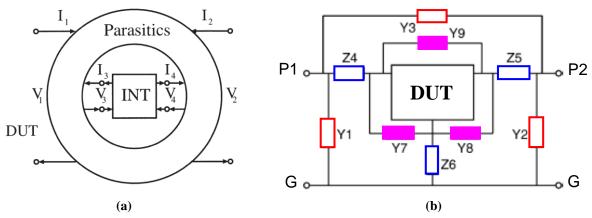

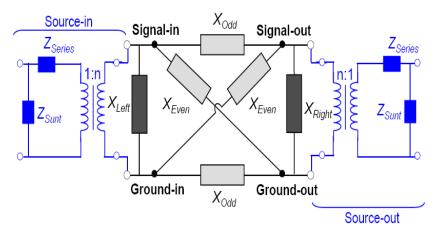

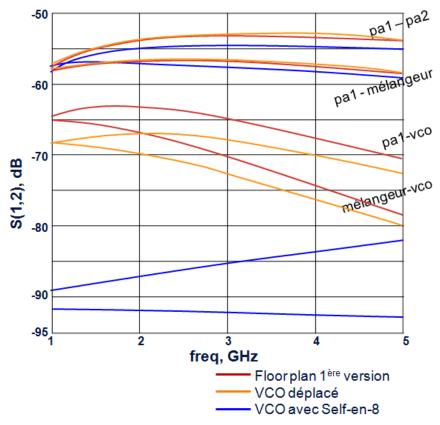

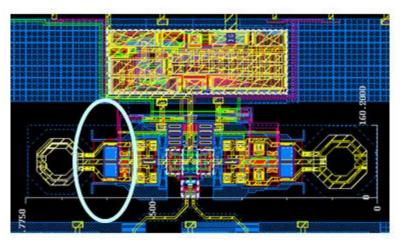

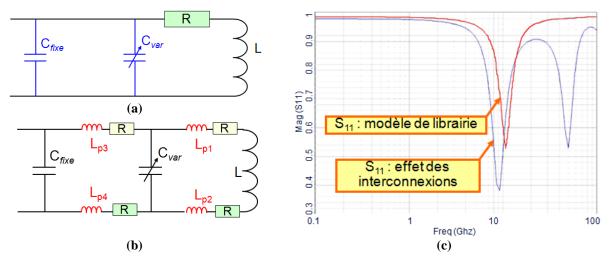

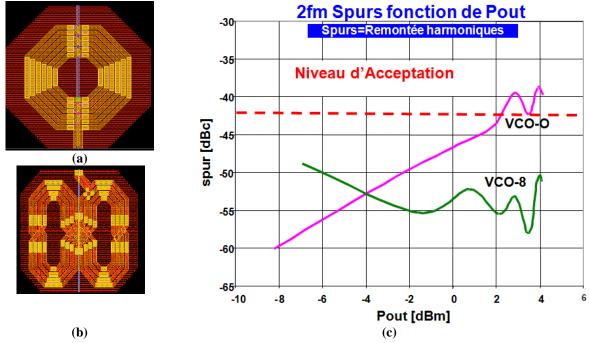

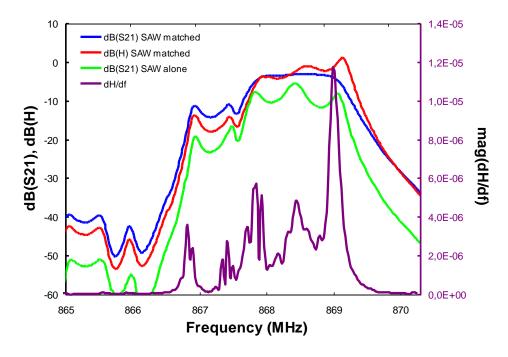

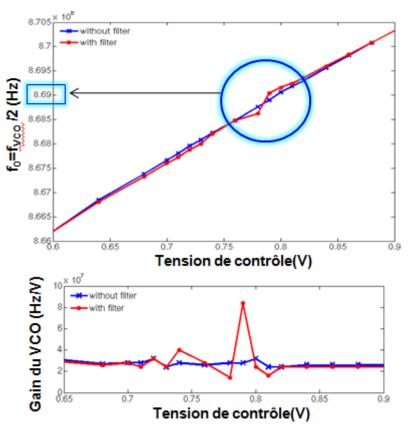

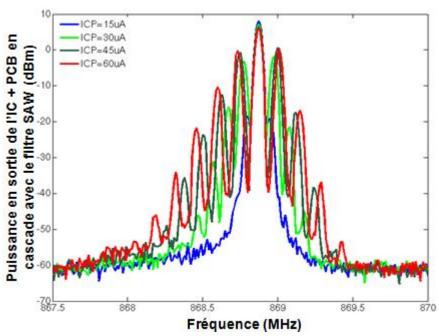

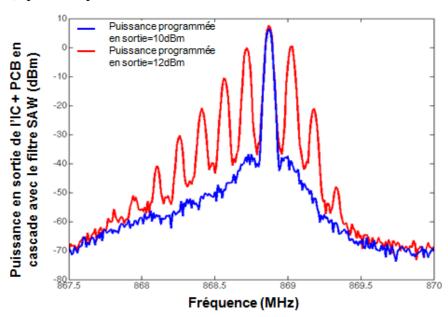

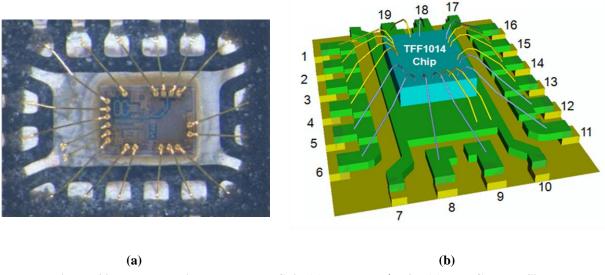

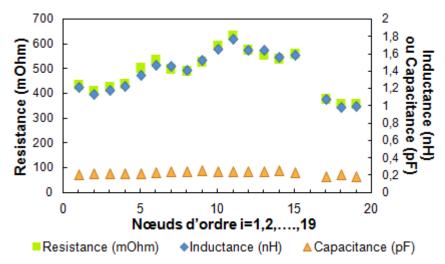

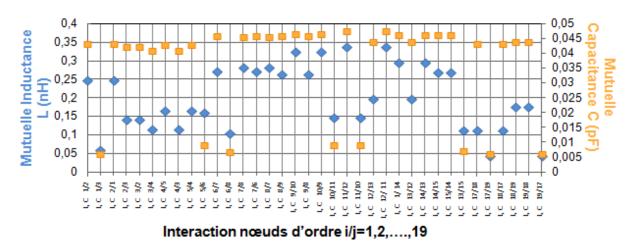

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | .2. A Microwave Down-Converter for Satellite TV Application around 10-                                                                                                        |                                                      |