# Scheduling Tasks over Multicore machines enhanced with acelerators: a Runtime System's Perspective

Cédric Augonnet

#### ▶ To cite this version:

Cédric Augonnet. Scheduling Tasks over Multicore machines enhanced with acelerators: a Runtime System's Perspective. Distributed, Parallel, and Cluster Computing [cs.DC]. Université Bordeaux 1, 2011. English. NNT: . tel-00777154

# HAL Id: tel-00777154 https://theses.hal.science/tel-00777154

Submitted on 17 Jan 2013

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

#### N° d'ordre: 4460 UNIVERSITÉ DE BORDEAUX 1

# ÉCOLE DOCTORALE DE MATHÉMATIQUES ET INFORMATIQUE

# **THÈSE**

présentée pour obtenir le grade de

**DOCTEUR**

Spécialité : Informatique

# Scheduling Tasks over Multicore machines enhanced with Accelerators: a Runtime System's Perspective

## par Cédric AUGONNET

soutenue le 9 Décembre 2011

#### Après avis de :

| M. Albert        | COHEN          | Directeur de recherche INRIA    | Rapporteur         |

|------------------|----------------|---------------------------------|--------------------|

| M. Jean-François | <b>M</b> EHAUT | Professeur des Universités      | Rapporteur         |

|                  |                |                                 |                    |

|                  | Devant la co   | mmission d'examen composée de : |                    |

| M. Henri         | BAL            | Professeur des Universités      | Examinateur        |

| M. Albert        | COHEN          | Directeur de recherche INRIA    | Rapporteur         |

| M. David         | Goudin         | Ingénieur Chercheur au CEA      | Examinateur        |

| M. Jean-François | Mehaut         | Professeur des Universités      | Rapporteur         |

| M. Raymond       | NAMYST         | Professeur des Universités      | Directeur de Thèse |

| M. Jean          | ROMAN          | Professeur à l'IPB              | Président          |

Maître de Conférences

Directeur de Thèse

THIBAULT

M. Samuel

À Camille,

# Remerciements

Au terme de ce périple qu'est la thèse, je souhaite remercier toutes celles et ceux qui m'ont permis de parcourir ce chemin tortueux. Je remercie en premier lieu mes encadrants pour m'avoir guidé pendant ces quatre dernières années. Merci Raymond de m'avoir donné l'opportunité de travailler sur un tel sujet et de m'avoir encadré tout au long de cette aventure, depuis mon premier stage en licence jusqu'á la fin de ma thèse. Merci Samuel d'avoir toujours été là pour me faire prendre le recul nécessaire afin de canaliser un enthousiasme quelque peu débordant. Je suis d'ailleurs particulièrement fier d'avoir été ton premier thésard. Je tiens aussi à remercier les autres membres de mon jury, que j'ai eu la chance de recontrer à différentes reprises au cours de ce périple : Henri Bal – dont le cours aura suscité en moi une véritable passion pour le calcul parallèle –, David Goudin et Jean Roman. Je remercie particulièrement Jean-François Mehaut et Albert Cohen pour avoir accepté et pris le temps relire mon manuscrit.

Une thèse, c'est avant tout un travail d'équipe. Merci donc aux membres de Runtime d'avoir rendu ce travail possible et de m'avoir supporté malgré un handicap administratif flagrant (pardon Sylvie!). Merci à celles et ceux qui ont participé à l'aventure StarPU et qui m'ont permis d'avancer bien plus que je ne l'aurais imaginé: Samuel, Raymond, Nathalie, Nicolas, François, Ludovic, Sylvain, Olivier ... Et bonne chance aux personnes qui reprendront le flambeau! Je remercie également Alexandre, Denis, Emmanuel, Marie-Christine, Olivier et Pierre-André pour leurs conseils avisés. Merci aux autres personnes avec lesquelles j'ai pu partager les joies de la thèse: Babeth la spécialiste des makis, Bertrand le marathonien, Broq l'homme le plus drôle du monde, Diak mon co-bureau invisible, Jéjé le sosie officiel de Michael Lonsdale, Paulette et ses compils de Thunderdome, et enfin Stéphanie à qui je dois certainement 3000 euros chez Nespresso. Par ailleurs, je tiens à m'excuser auprès de mes différents co-bureaux pour leur avoir infligé mes frasques musicales, un fouillis sans nom, et ma décoration à base de poneys. Qui aurait cru qu'on puisse chauffer un bureau à l'aide de BLAS3?

Merci aussi aux personnes avec qui j'ai eu la chance de collaborer à Bordeaux et dans les projets ProHMPT, MediaGPU, PEPPHER, ou encore celles qui m'ont accueilli à l'Université du Tennesse Knoxville et d'Urbana-Champaign. Merci notamment à Emmanuel, Hatem, Mathieu et Stan de m'avoir ouvert les portes de l'ICL.

Je pense également à mes amis qui ont rendu cette période un peu plus légère. Merci à Cécile, Cyril, Amélie et Christophe pour les soirées Wii/Master System 2 sur fond de Rhum et Tequila. Spécial big up à Juliette et François qui ont toujours été présents dans les moments importants, et ce malgré la distance. Merci aussi à eux (et à Camille) pour m'avoir supporté en tant que colocataire : il en fallait du courage pour tolérer ma boite à meuh, ma carte musicale Coca-Cola,

et mes moultes décorations des plus seyantes! Au passage, une caresse à Babouch mon chat d'adoption, pour ces longues heures passées sur mes genoux pendant que je m'affairais à rédiger ce document! Merci enfin aux geeks de l'ENS Lyon qui m'ont fait découvrir l'informatique et la Guinness: Dain, Grincheux, Julio, Kaisse, Louloutte, Nanuq, Nimmy, Stilgar, TaXules, Tchii, Theblatte, Tonfa, Vinz, Youpi et Zmdkrbou.

Parceque sans eux je n'en serais probablement pas arrivé là: merci à mes parents d'avoir toujours pris sur eux pour me soutenir, malgré la distance. J'espère que vous ne m'en voulez pas

trop pour toutes ces fêtes de Noël passées à travailler entre le saumon et la bûche ; ou pour cette

époque durant laquelle je découvrais Internet tout en vous empêchant de recevoir le moindre

coup de fil (une petite pensée au passage pour tous les autres parents victimes du forfait AOL 99

francs illimité). Merci à mon autre famille pour sa grande générosité et pour m'avoir fait apprécier

les joies du Sud-Ouest. Merci Michel pour toutes nos discussions, pour les leçons de conduite, et

pour avoir sacrifié à maintes reprises votre réserve de champagne, afin d'accompagner les moments importants. Merci Geneviève pour tous les croissants, pains au chocolat (ou chocolatines !)

et autres bouteilles de Jurançon. Merci à Julie et Jerry, et à Charlotte et Jean-Clément pour m'avoir

accueilli si souvent : que c'est bon d'être une pièce rapportée dans ces conditions !

Enfin plus que quiconque, je tiens vraiment à remercier Camille, qui a toujours été là pour moi. Merci pour tout cet amour, cette douceur, et ce réconfort! Merci à toi pour les sacrifices consentis, et pour tout ce temps passé à me soutenir malgré mes innombrables absences. Je te suis infiniment reconnaissant de m'avoir ouvert les yeux sur ce que sont les vrais bonheurs de la vie, que tu rends chaque jour un peu plus belle.

# **Abstract**

Multicore machines equipped with accelerators are becoming increasingly popular in the High Performance Computing ecosystem. Hybrid architectures provide significantly improved energy efficiency, so that they are likely to generalize in the Manycore era. However, the complexity introduced by these architectures has a direct impact on programmability, so that it is crucial to provide portable abstractions in order to fully tap into the potential of these machines. Pure offloading approaches, that consist in running an application on regular processors while offloading predetermined parts of the code on accelerators, are not sufficient. The real challenge is to build systems where the application would be spread across the entire machine, that is, where computation would be dynamically scheduled over the full set of available processing units.

In this thesis, we thus propose a new task-based model of runtime system specifically designed to address the numerous challenges introduced by hybrid architectures, especially in terms of task scheduling and of data management. In order to demonstrate the relevance of this model, we designed the StarPU platform. It provides an expressive interface along with flexible task scheduling capabilities tightly coupled to an efficient data management. Using these facilities, together with a database of auto-tuned per-task performance models, it for instance becomes straightforward to develop efficient scheduling policies that take into account both computation and communication costs. We show that our task-based model is not only powerful enough to provide support for clusters, but also to scale on hybrid manycore architectures.

We analyze the performance of our approach on both synthetic and real-life workloads, and show that we obtain significant speedups and a very high efficiency on various types of multicore platforms enhanced with accelerators.

# Résumé

Les machines multicœurs équipées d'accélérateurs deviennent de plus en plus populaires dans le domaine du Calcul Haute Performance. Les architectures hybrides réduisent la consommation énergétique de manière significative et sont donc amenées à se généraliser dans l'ère du manycœur. Cependant, la complexité induite par ces architectures a un impact direct sur leur programmabilité. Il est donc indispensable de fournir des abstractions portables afin de tirer pleinement parti de ces machines. Les approches qui consistent à exécuter une application sur des processeurs généralistes et à ne déporter que certaines parties prédéterminées du calcul sur des accélérateurs ne sont pas suffisantes. Le véritable défi consiste donc à concevoir des environnements où les applications sont réparties sur l'intégralité de la machine, c'est-à-dire où les différents calculs sont ordonnancés dynamiquement sur la totalité des unités de calcul disponibles.

Dans cette thèse, nous proposons donc un nouveau modèle de support exécutif fondé sur une abstraction de tâche et spécifiquement conçu pour répondre aux nombreux défis en termes d'ordonnancement de tâches et de gestion de données. La plate-forme StarPU a été conçue lors de cette thèse afin de démontrer la pertinence de ce modèle. StarPU propose une interface expressive permettant d'accéder à un ordonnancement flexible, fortement couplé à une gestion de données efficace. À l'aide de cet environnement et en associant les différentes tâches avec des modèles de performance auto-calibrés, il devient par exemple très simple de concevoir des stratégies d'ordonnancement prenant en compte les temps de calcul et les surcoûts liés aux mouvements de données. Nous montrons que notre modèle fondé sur un paradigme de tâche est suffisamment puissant pour exploiter les grappes de calcul d'une part, et les architectures *manycœurs* hybrides d'autre part.

Nous analysons les performances obtenues non seulement grâce à des tests synthétiques, mais aussi à l'aide d'applications réelles. Nous obtenons ainsi des accélérations substantielles, ainsi qu'une très bonne efficacité parallèle sur différents types de plates-formes multicœurs, dotées d'accélérateurs.

# **Contents**

| In | trodu | ıction   |                                                          | 23 |

|----|-------|----------|----------------------------------------------------------|----|

|    | Hyb   | rid acc  | elerator-based computing                                 | 23 |

|    | Goa   | ls and ( | Contributions of this thesis                             | 23 |

|    | Orga  | anizatio | on of this document                                      | 25 |

| 1  | Con   | text an  | d Motivation                                             | 27 |

|    | Cha   | pter Ab  | ostract                                                  | 28 |

|    | 1.1   | Many     | core and Accelerator-based Architectures                 | 28 |

|    |       | 1.1.1    | Accelerating compute boards: from ASICs to GPU computing | 28 |

|    |       | 1.1.2    | Computing with Graphic Processing Units                  |    |

|    |       | 1.1.3    | From specialized cores to hybrid manycore processors     |    |

|    |       | 1.1.4    | Discussion                                               |    |

|    | 1.2   | Progra   | amming models                                            |    |

|    |       | 1.2.1    | Multithreading                                           | 37 |

|    |       | 1.2.2    | Message passing                                          | 38 |

|    |       | 1.2.3    | Data parallelism                                         |    |

|    |       | 1.2.4    | Task parallelism                                         | 39 |

|    | 1.3   | Progra   | amming Environments                                      | 41 |

|    |       | 1.3.1    | Low-level Vendor Toolkits                                | 41 |

|    |       | 1.3.2    | Era of libraries                                         | 43 |

|    |       | 1.3.3    | Generating compute kernels for accelerators              | 44 |

|    |       | 1.3.4    | Coordination languages                                   | 45 |

|    |       | 1.3.5    | Autotuning Frameworks                                    | 47 |

|    | 1.4   | Sched    | ulers                                                    | 48 |

|    | 1.5   | Data r   | nanagement support                                       | 50 |

|    |       | 1.5.1    | Support for explicitly managed memory                    | 50 |

|    |       | 1.5.2    | Virtually Distributed Shared memory (VDSM)               | 50 |

|    | 1.6   | Runtii   | me systems for accelerator-based platforms               | 51 |

|    |       | 1.6.1    | Cell-specific runtime systems                            | 51 |

|    |       | 1.6.2    | Runtime systems specifically designed for Linear Algebra |    |

|    |       | 1.6.3    | Generic runtime systems for hybrid platforms             | 53 |

|    | 1.7   | Discus   | ssion                                                    | 55 |

#### **CONTENTS**

| I | Cor | ntribut | tion                                                                | 57      |

|---|-----|---------|---------------------------------------------------------------------|---------|

| 2 |     |         | ed paradigm for Accelerator-Based platforms                         | 59      |

|   | Cha |         | bstract                                                             |         |

|   | 2.1 | _       | gramming model based on tasks and explicit data registration        |         |

|   |     | 2.1.1   | Task parallelism                                                    |         |

|   |     | 2.1.2   | Explicit data registration                                          |         |

|   | 2.2 |         | tarPU runtime system from a user's point of view                    |         |

|   |     | 2.2.1   | Programming model overview                                          |         |

|   |     | 2.2.2   | A tasking model enabling heterogeneous scheduling                   |         |

|   |     | 2.2.3   | Registering data to StarPU                                          |         |

|   |     | 2.2.4   | Expressing dependencies                                             |         |

|   |     | 2.2.5   | Implicit data-driven dependencies for sequentially consistent codes |         |

|   | 2.3 | Efficie | ent asynchronous data management                                    |         |

|   |     | 2.3.1   | MSI Coherency Protocol                                              |         |

|   |     | 2.3.2   | Decentralized asynchronous data management                          | <br>77  |

|   |     | 2.3.3   | Memory Allocation Cache                                             |         |

|   |     | 2.3.4   | Memory reclaiming                                                   | <br>80  |

|   | 2.4 | Relax   | ing the data coherency model                                        |         |

|   |     | 2.4.1   | Scratch access mode                                                 | <br>81  |

|   |     | 2.4.2   | Reduction access mode                                               | <br>82  |

|   |     | 2.4.3   | Elements of Implementation                                          | <br>85  |

|   | 2.5 | Execu   | ıtion of a Task within StarPU                                       | <br>85  |

|   |     | 2.5.1   | Enforcing explicit dependencies                                     |         |

|   |     | 2.5.2   | Enforcing data-driven implicit dependencies                         | <br>88  |

|   | 2.6 | A gen   | neric execution model                                               | <br>89  |

|   |     | 2.6.1   | Supporting CPU cores                                                |         |

|   |     | 2.6.2   | Supporting GPU devices                                              | <br>90  |

|   |     | 2.6.3   | Supporting the Cell processor                                       | <br>91  |

|   | 2.7 | Discu   | ssion                                                               |         |

| 3 | Sch | edulin  | g Strategies                                                        | 95      |

|   | Cha | pter Al | bstract                                                             | <br>96  |

|   | 3.1 | Sched   | luling tasks in heterogeneous accelerator-based environments        | <br>96  |

|   |     | 3.1.1   | Dealing with heterogeneous processing capabilities                  | <br>97  |

|   |     | 3.1.2   | Impact of data transfers                                            | <br>97  |

|   | 3.2 | A gen   | neric scheduling engine                                             | <br>98  |

|   |     | 3.2.1   | No single perfect scheduling strategy exists                        | <br>98  |

|   |     | 3.2.2   | A Flexible API to design portable Scheduling Strategy as plug-ins   | <br>99  |

|   |     | 3.2.3   | Use case: implementing the greedy strategy                          | <br>102 |

|   | 3.3 | Sched   | luling hints: a precious help from the application                  | <br>103 |

|   |     | 3.3.1   | Task priorities                                                     |         |

|   |     | 3.3.2   | Performance Models                                                  |         |

|   | 3.4 | Sched   | luling strategies relying on performance models                     | <br>105 |

|   |     | 3.4.1   | Strategies based on the sustained speed of the processing units     |         |

|   |     | 3.4.2   | Predicting performance using per-task performance modesl            | <br>106 |

|   |      | CON                                                                | ΓENTS |

|---|------|--------------------------------------------------------------------|-------|

|   |      | 3.4.3 HEFT: Minimizing termination time                            | 107   |

|   |      | 3.4.4 Dealing with inaccurate or missing performance models        | 109   |

|   | 3.5  | Auto-tuned performance models                                      | 110   |

|   |      | 3.5.1 History-based models                                         | 110   |

|   |      | 3.5.2 Regression-based models                                      | 112   |

|   |      | 3.5.3 How to select the most appropriate model?                    | 113   |

|   |      | 3.5.4 Sharpness of the performance prediction                      |       |

|   | 3.6  | Integrating data management and task scheduling                    |       |

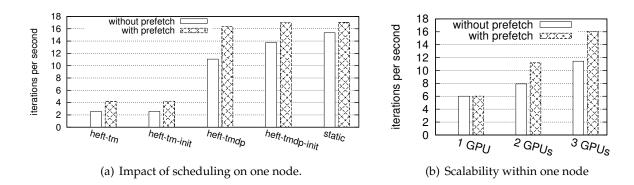

|   |      | 3.6.1 Data prefetching                                             |       |

|   |      | 3.6.2 Predicting data transfer time                                |       |

|   |      | 3.6.3 Non-Uniform Memory and I/O Access on hierarchical machines   |       |

|   |      | 3.6.4 Using data transfer time prediction to improve data locality |       |

|   | 3.7  | Taking other criteria into account                                 |       |

|   | 0.7  | 3.7.1 Reducing Power consumption                                   |       |

|   |      | 3.7.2 Optimizing memory footprint and data bandwidth               |       |

|   | 3.8  | Confining applications within restricted scheduling domains        |       |

|   | 3.9  | Toward composable scheduling policies                              |       |

|   |      | Discussion                                                         |       |

|   | 3.10 | Discussion                                                         | 123   |

| 4 |      | nularity considerations                                            | 125   |

|   |      | pter Abstract                                                      |       |

|   | 4.1  |                                                                    |       |

|   |      | 4.1.1 Dealing with embarrassingly parallel machines                |       |

|   |      | 4.1.2 Dealing with computation power imbalance                     |       |

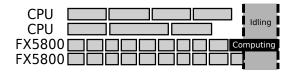

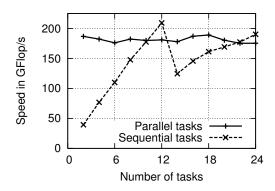

|   | 4.2  | Parallel tasks                                                     |       |

|   |      | 4.2.1 Beyond flat parallelism                                      |       |

|   |      | 4.2.2 Supporting parallel tasks in StarPU                          | 128   |

|   |      | 4.2.3 Parallelizing applications and libraries                     | 129   |

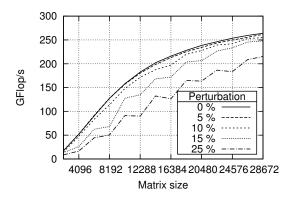

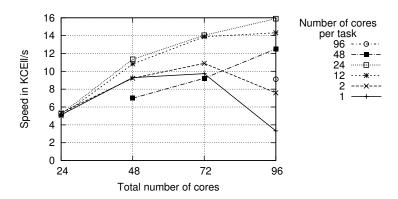

|   |      | 4.2.4 A practical example: matrix multiplication                   | 130   |

|   | 4.3  | Scheduling parallel tasks                                          | 132   |

|   |      | 4.3.1 Taking machine hierarchy into account                        | 132   |

|   |      | 4.3.2 Scheduling strategies for parallel tasks                     | 133   |

|   |      | 4.3.3 Dimensioning parallel tasks                                  |       |

|   | 4.4  | Toward divisible tasks                                             |       |

|   | 4.5  | Discussion                                                         | 136   |

| 5 | Tow  | vard clusters of machines enhanced with accelerators               | 139   |

| 0 |      | pter Abstract                                                      |       |

|   | 5.1  | Adapting our task-based paradigm to a cluster environment          |       |

|   | 5.2  | Managing data in an MPI world enhanced with accelerators           |       |

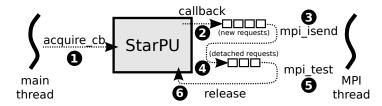

|   | 5.3  | A library providing an MPI-like semantic to StarPU applications    |       |

|   | 0.0  | 5.3.1 Main API features                                            |       |

|   |      | 5.3.2 Implementation overview                                      |       |

|   | 5.4  | Mapping DAGs of tasks on clusters                                  |       |

|   | J.4  | 5.4.1 A systematic methodology to map DAGs of tasks on clusters    |       |

|   |      | ,                                                                  |       |

|   |      | 5.4.2 The starpu_mpi_insert_task helper                            | 143   |

## **CONTENTS**

|    | 5.5 | 5.4.3 Example of a five-point stencil kernel automatically distributed over MPI 5.4.4 Implementation overview | 147<br>148 |

|----|-----|---------------------------------------------------------------------------------------------------------------|------------|

| 6  |     | ougging and Performance analysis tools                                                                        | 151        |

|    | Cha | pter Abstract                                                                                                 |            |

|    | 6.1 | Performance analysis tools                                                                                    | 151        |

|    |     | 6.1.1 Offline tools                                                                                           |            |

|    |     | 6.1.2 Online tools                                                                                            |            |

|    | 6.2 | Performance counters                                                                                          |            |

|    | 6.3 | Case Study: Optimizing the TPACF cosmological data analysis benchmark                                         | 154        |

|    | 6.4 | Automatically Predicting theoretical execution time upper-bounds                                              | 157        |

|    | 6.5 | Discussion                                                                                                    | 159        |

| II | Eva | aluation                                                                                                      | 161        |

| 7  | Exp | erimental Validation                                                                                          | 163        |

|    |     | pter Abstract                                                                                                 | 163        |

|    | 7.1 | Experimental platforms                                                                                        |            |

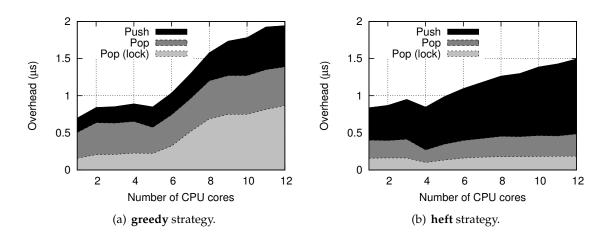

|    | 7.2 | Task scheduling overhead                                                                                      |            |

|    | 7.3 | QR decomposition                                                                                              |            |

|    |     | 7.3.1 The PLASMA and the MAGMA libraries                                                                      |            |

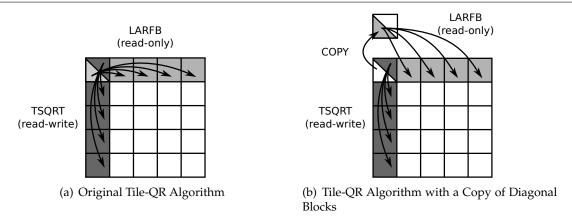

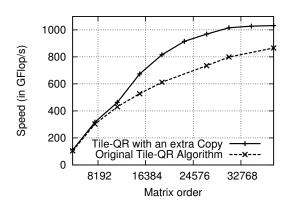

|    |     | 7.3.2 Improvement of the Tile-QR algorithm                                                                    | 167        |

|    |     | 7.3.3 Impact of the scheduling policy                                                                         |            |

|    |     | 7.3.4 Communication-avoiding QR decomposition                                                                 |            |

|    | 7.4 | Cholesky decomposition over MPI                                                                               |            |

|    | 7.5 | 3D Stencil kernel                                                                                             |            |

|    | 7.6 | Computing $\pi$ with a Monte-Carlo Method                                                                     |            |

|    | 7.7 | Computational Fluid Dynamics: Euler 3D equation                                                               |            |

|    |     | 7.7.1 Scalability of the CFD benchmark on a manycore platform                                                 | 179        |

|    |     | 7.7.2 Efficiency of the CFD benchmark on a Hybrid platform                                                    |            |

|    | 7.8 | Discussion                                                                                                    | 181        |

| 8  |     | fusion                                                                                                        | 183        |

|    | Cha | pter Abstract                                                                                                 |            |

|    | 8.1 | Integration of StarPU within the computing ecosystem                                                          |            |

|    | 8.2 | Real-Life Applications enhanced with StarPU                                                                   |            |

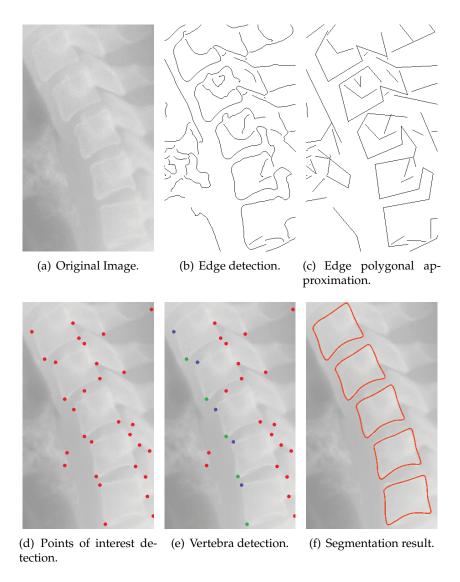

|    |     | 8.2.1 Vertebra Detection and Segmentation in X-Ray images                                                     |            |

|    |     | 8.2.2 Accelerating a query-by-humming music recognition application                                           | 185        |

|    | 8.3 | Libraries                                                                                                     |            |

|    |     | 8.3.1 A hybrid implementation of LAPACK mixing PLASMA and MAGMA                                               |            |

|    |     | 8.3.2 StarPU-FFT                                                                                              |            |

|    | 8.4 | Support for compilers and programming environments                                                            |            |

|    |     | 8.4.1 Adding StarPU back-ends for annotation-based language extensions                                        | 190        |

|    |                          |                      | CONT                                                                                    | ENTS                                                              |

|----|--------------------------|----------------------|-----------------------------------------------------------------------------------------|-------------------------------------------------------------------|

|    | 8.5<br>8.6               | 8.5.1<br>8.5.2       | Automatic kernel generation with HMPP                                                   | <ul><li>. 192</li><li>. 193</li><li>. 193</li><li>. 194</li></ul> |

| Co | Con<br>Pers              | tributic<br>spective | ad Future Challenges onseses                                                            | . 199                                                             |

| A  | Full                     | imple                | mentation of Cholesky decomposition                                                     | 203                                                               |

| В  | <b>Tun</b><br>B.1<br>B.2 | Tunin                | ear and non-linear regression-based models g linear models with the Least Square method |                                                                   |

| C  | Bibl                     | liograp              | hy                                                                                      | 211                                                               |

| D  | Pub                      | lication             | ns                                                                                      | 227                                                               |

# **List of Figures**

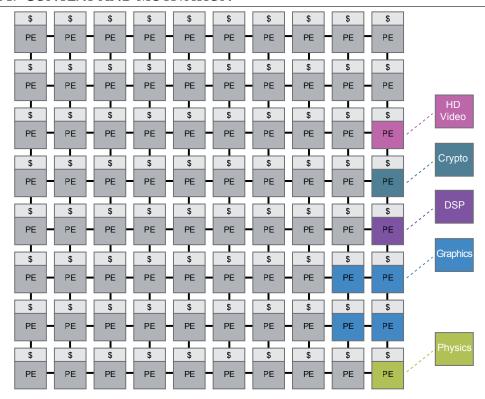

| 1.1  | Intel Terascale Tile Arrangement                                                               |

|------|------------------------------------------------------------------------------------------------|

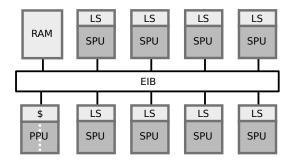

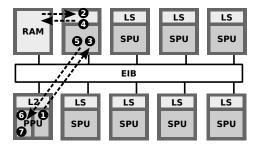

| 1.2  | Architecture of the Cell Processor                                                             |

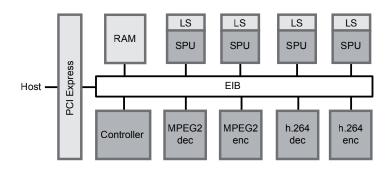

| 1.3  | Spurs Engine                                                                                   |

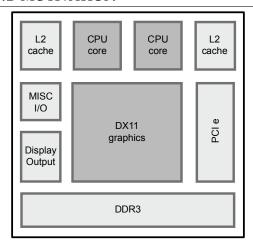

| 1.4  | AMD Fusion Arrangement                                                                         |

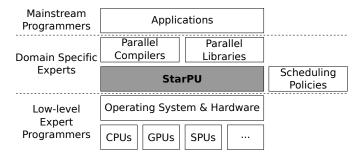

| 2.1  | Runtime Systems play a central role in Hybrid Platforms                                        |

| 2.2  | Adding two vectors with StarPU                                                                 |

| 2.3  | Examples of data interfaces                                                                    |

| 2.4  | Memory nodes and data interfaces                                                               |

| 2.5  | Example of a matrix-vector product using data filters                                          |

| 2.6  | Code of a filter partitioning a vector into multiple sub-vectors                               |

| 2.7  | Example of data partitioning and its hierarchical representation                               |

| 2.8  | A simple task DAG                                                                              |

| 2.9  | Explicit dependencies between task structures                                                  |

| 2.10 | Explicit dependencies with tags                                                                |

|      | Example of code relying on implicit data-driven dependencies                                   |

| 2.12 | Accessing the arguments of task $C$ in Figure 2.11                                             |

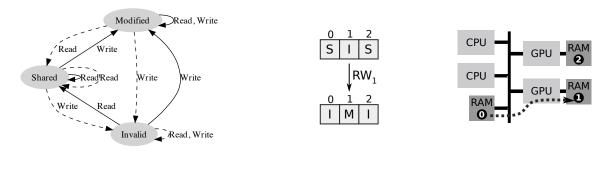

|      | The MSI coherency protocol                                                                     |

| 2.14 | Example of method to transfer a vector between a CUDA device and host memory 78                |

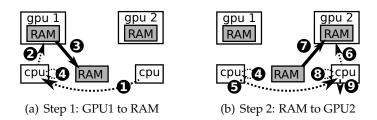

| 2.15 | Implementing GPU-GPU transfers with chained requests                                           |

| 2.16 | Codelets implementing the data accumulator used on Figure 2.17 83                              |

| 2.17 | Dot product based on data reductions                                                           |

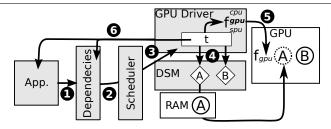

| 2.18 | Overview of the path followed by a task within StarPU                                          |

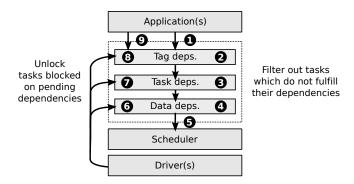

| 2.19 | Detailed view of the different steps required to enforce dependencies 86                       |

| 2.20 | Driver for a CPU core                                                                          |

| 2.21 | Offloading tasks with the Cell Runtime Library (Cell-RTL)                                      |

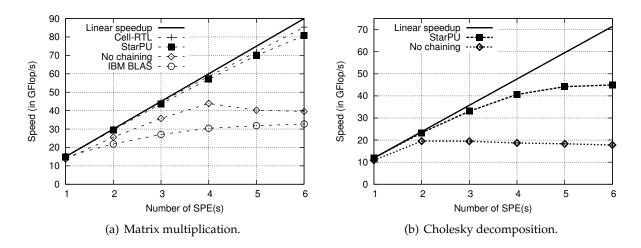

| 2.22 | Scalability of StarPU on the Cell processor                                                    |

| 3.1  | A pathological case with a greedy scheduling strategy                                          |

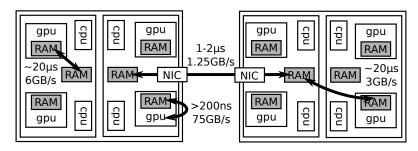

| 3.2  | Typical performance of the different types of memory interconnects                             |

| 3.3  | Data Structure describing a scheduling strategy in StarPU                                      |

| 3.4  | All scheduling strategies implement the same queue-based interface                             |

| 3.5  | Associating each worker with a condition variable                                              |

| 3.6  | Workload distribution in a hybrid environment                                                  |

| 3.7  | Examples of scheduling strategies offering different level of support for task priorities. 104 |

## LIST OF FIGURES

| 3.8  | Impact of priorities on Cholesky decomposition                                      | . 104 |

|------|-------------------------------------------------------------------------------------|-------|

| 3.9  | Practical example of the Weighted-Random Strategy.                                  |       |

| 3.10 | The Heterogeneous Earliest Finish Time Strategy                                     |       |

|      | Simplified code of the push method used in the <b>heft-tm</b> strategy              |       |

|      | Post execution hook of the <b>heft-tm</b> strategy                                  |       |

|      | Signature of a matrix-vector multiplication task                                    |       |

|      | Performance feedback loop                                                           |       |

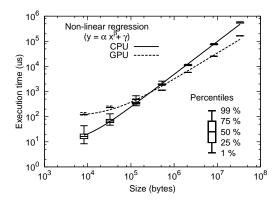

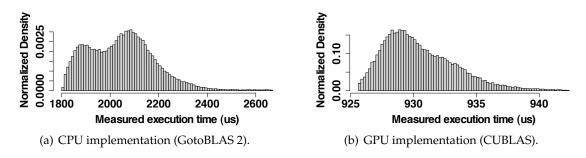

| 3.15 | Performance and regularity of an STRSM BLAS3 kernel depending on granularity.       | . 113 |

|      | Distribution of the execution times of a STRSM BLAS3 kernel                         |       |

| 3.17 | Impact of performance model inaccuracies                                            | . 115 |

| 3.18 | Example of NUIOA effects measured during the sampling procedure                     | . 118 |

| 3.19 | Extending the HEFT strategy to minimize energy consumption                          | . 120 |

|      | Example of overlapping scheduling domains                                           |       |

| 3.21 | Composing scheduling policies                                                       | . 122 |

|      |                                                                                     |       |

| 4.1  | Parallel programming paradigms.                                                     |       |

| 4.2  | Hybrid DAG with parallel tasks                                                      | . 128 |

| 4.3  | Original CPU driver.                                                                | . 129 |

| 4.4  | CPU driver supporting parallel tasks                                                |       |

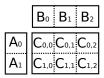

| 4.5  | Product of two tiled matrices                                                       |       |

| 4.6  | Code of the Parallel Matrix Product kernel in SPMD mode                             |       |

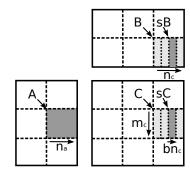

| 4.7  | Parallel Matrix Product Algorithm.                                                  |       |

| 4.8  | Product of two matrices with a small number of tasks                                |       |

| 4.9  | Implementing parallel tasks by submitting task duplicates to multiple workers       | . 133 |

| 5.1  | Code of a MPI Ring using detached calls to increment a variable                     | . 143 |

| 5.2  | Implementation of the detached send operation.                                      |       |

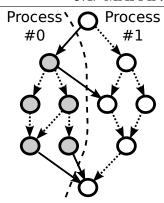

| 5.3  | Example of task DAG divided in two processes                                        | 145   |

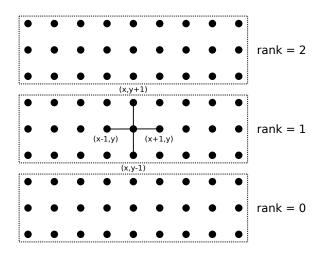

| 5.4  | Five-point stencil kernel distributed over MPI                                      | 146   |

| 5.5  | Implementation of a five-point stencil kernel over MPI                              |       |

|      |                                                                                     |       |

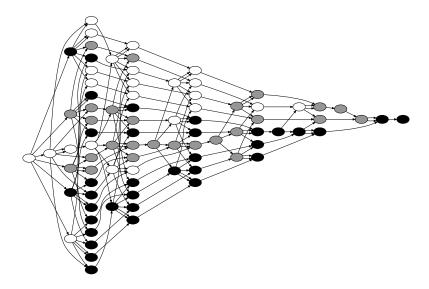

| 6.1  | DAG obtained after the execution of a Cholesky decomposition                        |       |

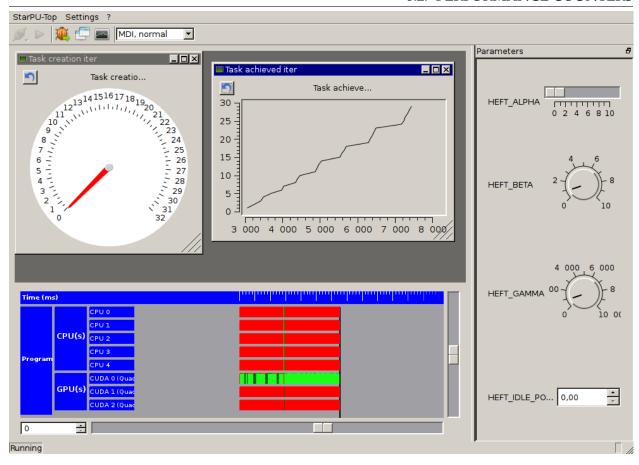

| 6.2  | StarPU-Top controlling interface                                                    |       |

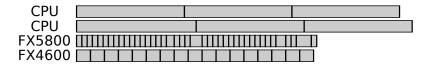

| 6.3  | Vite Trace obtained with a naive port of the TPACF benchmark on StarPU              |       |

| 6.4  | Impact of loop unrolling on the TPACF benchmark                                     |       |

| 6.5  | Comparison between actual performance and theoretical boundaries                    |       |

| 6.6  | Comparing the actual execution time with the theoretical bound                      | . 158 |

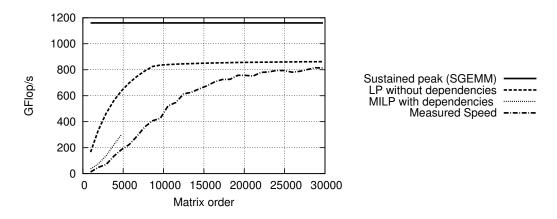

| 7.1  | Task scheduling overhead on ATTILA                                                  | 165   |

| 7.2  | Modification of the Tile-QR Algorithm to increase the amount of parallelism         |       |

| 7.3  | Duplicating the diagonal blocks to save parallelism on MORDOR                       |       |

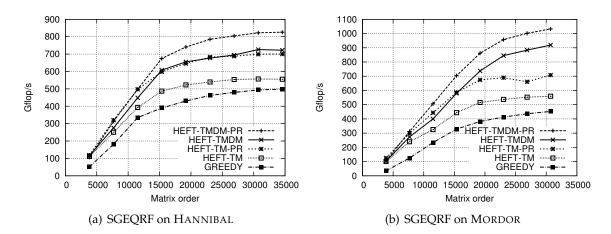

| 7.4  | Impact of the scheduling policy on the performance of a QR decomposition            |       |

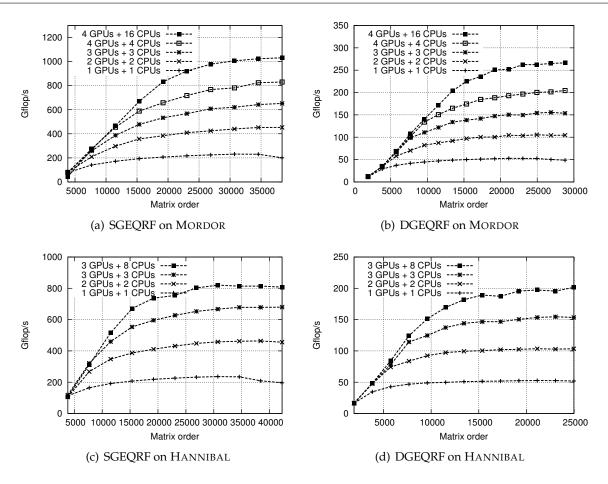

| 7.5  | Scalability of the QR decomposition with respect to the number of processing units. |       |

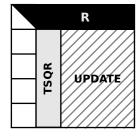

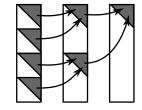

| 7.6  | Communication-Avoiding QR (CAQR) algorithm                                          |       |

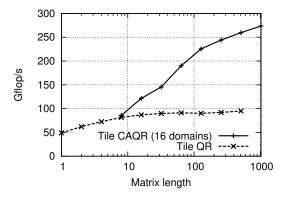

| 7.7  | Performance of Tile CAQR for tall and skinny matrices                               |       |

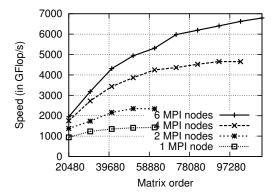

| 7.8  | Strong scalability of a Cholesky decomposition over a cluster                       |       |

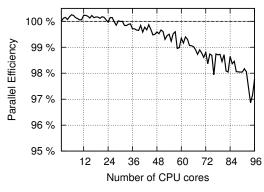

| 79   | Performance of a Stencil kernel over multiple CPUs                                  | 175   |

## LIST OF FIGURES

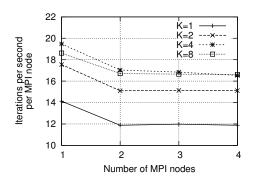

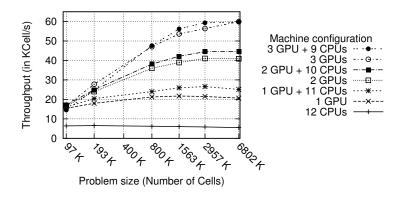

| 7.10 | Throughput of a Stencil kernel over a cluster of machines with multiple GPUs (AC). 175                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7.11 | Computing $\pi$ with a Monte Carlo method                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

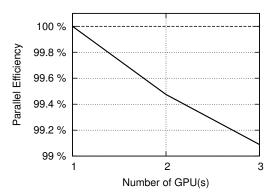

| 7.12 | Parallel efficiency of the Monte-Carlo method implemented with reductions 178                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 7.13 | Speedup of the Monte-Carlo method implemented with Reductions 178                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

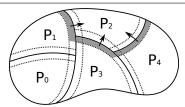

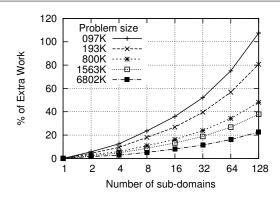

| 7.14 | Parallelizing the CFD benchmark by dividing into sub-domains 179                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|      | Strong scalability of the CFD benchmark                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|      | Parallelization overhead of the CFD benchmark                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 7.17 | Throughput of the CFD kernel on a Hybrid machine                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 0.1  | P. 1.1. ( 1.10 at 1.10 |

| 8.1  | Berkeley's classification of scientific computing problems into dwarfs 184                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 8.2  | Integration of StarPU within the computing ecosystem                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 8.3  | Illustration of the whole segmentation framework                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

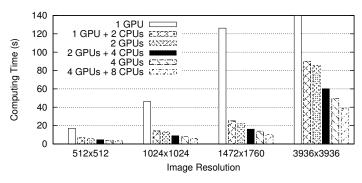

| 8.4  | Performance of recursive edge detection on hybrid platforms                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 8.5  | Screenshot of the SIMBALS music recognition library                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 8.6  | Example of 2D FFT performed with StarPU's FFT library                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 8.7  | Example of code using the Mercurium source-to-source compiler 191                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|      | The last of Diff. 1 and  |

|      | Initializing StarPU and registering data                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|      | A codelet implementing the <i>sgemm</i> kernel                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| A.3  | Actual implementation of the tile Cholesky hybrid algorithm with StarPU 206                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

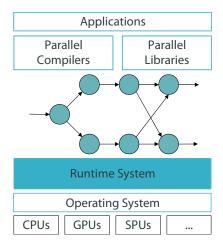

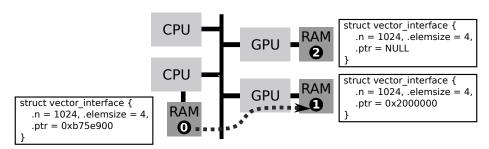

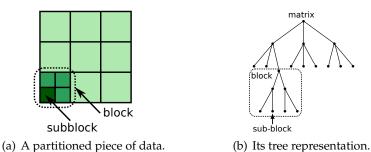

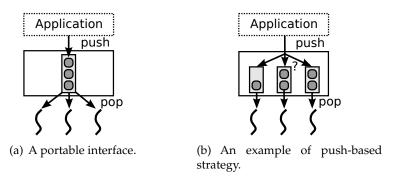

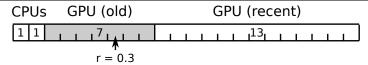

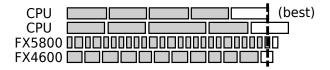

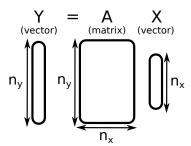

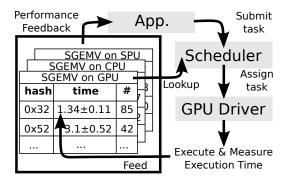

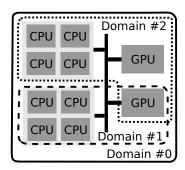

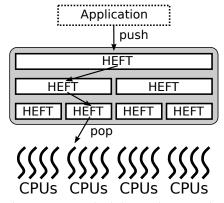

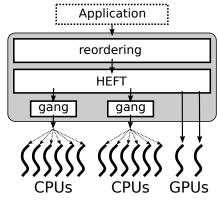

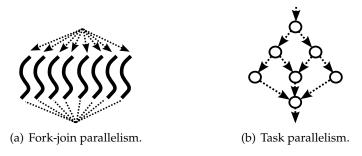

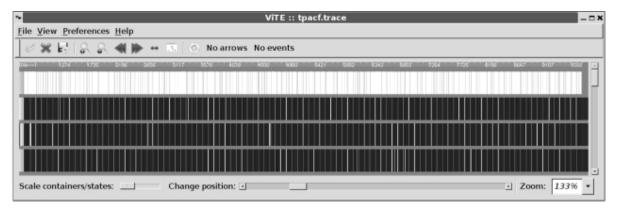

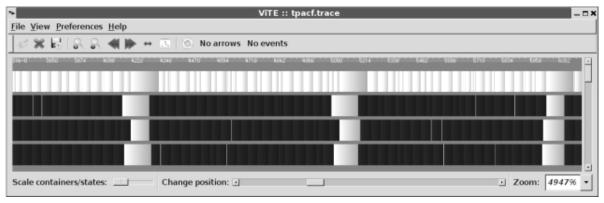

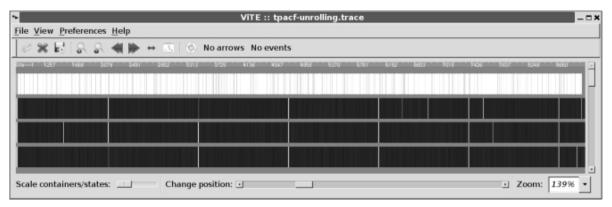

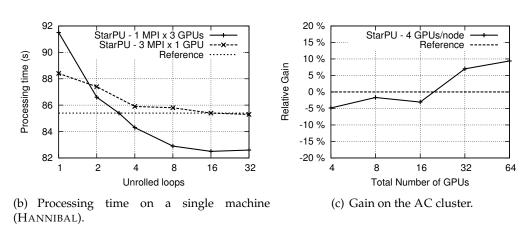

# **List of Tables**