## Design of a low noise, limited area and full on-chip power management for CMOS pixel sensors in high energy physics experiments

Jia Wang

### ► To cite this version:

Jia Wang. Design of a low noise, limited area and full on-chip power management for CMOS pixel sensors in high energy physics experiments. Other. Université de Strasbourg; Northwestern Polytechnical University (Chine), 2012. English. NNT: 2012STRAE006. tel-00758209

## HAL Id: tel-00758209 https://theses.hal.science/tel-00758209

Submitted on 28 Nov 2012

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

$N^{o}$  d'ordre: xxxx

École Doctorale de Physique et Chimie-Physique de l'Université de Strasbourg

UDS - IPHC - CNRS/IN2P3

# THÈSE

présentée pour obtenir le grade de

Docteur de l'Université de Strasbourg

Discipline : Électronique, Électrotechnique et Automatique Spécialité : Instrumentation et Microélectronique

par

## Jia WANG

## Design of a low noise, limited area and full on-chip power management for CMOS pixel sensors in high energy physics experiments

Soutenue publiquement le 3 Septembre 2012 devant le jury:

| Directeur de thèse:    | YANN HU           | Professeur, UDS, Strasbourg, France    |

|------------------------|-------------------|----------------------------------------|

| Co-directeur de thèse: | DEYUAN GAO        | Professeur, NPU, Xi'an, China          |

| Rapporteur externe:    | PATRICK GARDA     | Professeur, UPMC, Paris, France        |

| Rapporteur externe:    | YU-SHAN LI        | Professeur, Xidian Univ., Xi'an, China |

| Examinateur:           | DOMINIQUE KNITTEL | Professeur, UDS, Strasbourg, France    |

| Examinateur:           | TINGCUN WEI       | Professeur, NPU, Xi'an, China          |

$N^{o}$  d'ordre: xxxx

Doctoral School of Physics, Chemistry-Physics - ED 182

UDS - IPHC - CNRS/IN2P3

# THESIS

Presented to obtain the degree of

Doctor of Philosophy in University of Strasbourg

Discipline : Electronics, Electrotechnics and Automation Speciality : Instrumentation and Microelectronics

by

## Jia WANG

## Design of a low noise, limited area and full on-chip power management for CMOS pixel sensors in high energy physics experiments

Submitted publicly before 3 September 2012 to the jury:

| Director of thesis:    | YANN HU           | Professor, UDS, Strasbourg, France    |

|------------------------|-------------------|---------------------------------------|

| Co-director of thesis: | DEYUAN GAO        | Professor, NPU, Xi'an, China          |

| Referee:               | PATRICK GARDA     | Professor, UPMC, Paris, France        |

| Referee:               | YU-SHAN LI        | Professor, Xidian Univ., Xi'an, China |

| Examiner:              | DOMINIQUE KNITTEL | Professor, UDS, Strasbourg, France    |

| Examiner:              | TINGCUN WEI       | Professor, NPU, Xi'an, China          |

Better to light a candle than to curse the dark.

$-Chinese \ proverb$

4\_\_\_\_\_

# Contents

| Τa            | able o                 | of cont       | ents                                                                                                    | i    |

|---------------|------------------------|---------------|---------------------------------------------------------------------------------------------------------|------|

| $\mathbf{Li}$ | st of                  | Figure        | es                                                                                                      | iv   |

| $\mathbf{Li}$ | st of                  | tables        |                                                                                                         | ix   |

| A             | cknov                  | wledge        | ments                                                                                                   | x    |

| Re            | ésum                   | é             |                                                                                                         | xiii |

| $\mathbf{A}$  | bstra                  | $\mathbf{ct}$ |                                                                                                         | xix  |

| 1             | Intr                   | oducti        | on                                                                                                      | 1    |

|               | 1.1                    | Resear        | rch background                                                                                          | 1    |

|               |                        | 1.1.1         | High energy physics (HEP)                                                                               | 1    |

|               |                        | 1.1.2         | Silicon detector topologies                                                                             | 6    |

|               |                        | 1.1.3         | Power distribution challenges in the detectors                                                          | 12   |

|               | 1.2                    | Propos        | sed work                                                                                                | 13   |

|               | 1.3                    | Thesis        | overview                                                                                                | 14   |

|               | Bibl                   | iograph       | y                                                                                                       | 16   |

| <b>2</b>      | $\mathbf{C}\mathbf{M}$ | OS piz        | xel sensors                                                                                             | 19   |

|               | 2.1                    | CPS s         | tructure                                                                                                | 19   |

|               |                        | 2.1.1         | Correlated double sampling $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots$      | 23   |

|               | 2.2                    | Sensor        | requirements in HEP experiments                                                                         | 25   |

|               |                        | 2.2.1         | Material budget                                                                                         | 25   |

|               |                        | 2.2.2         | Spatial resolution                                                                                      | 26   |

|               |                        | 2.2.3         | Readout speed $\ldots$ | 26   |

|               |                        | 2.2.4         | Radiation tolerance                                                                                     | 27   |

|               | 2.3                    | New d         | levelopments on CPS                                                                                     | 27   |

|   |      | 2.3.1   | Fast readout speed                                                                                          | 27 |

|---|------|---------|-------------------------------------------------------------------------------------------------------------|----|

|   |      | 2.3.2   | 3D vertical integration technologies                                                                        | 27 |

|   | 2.4  | Power   | management                                                                                                  | 29 |

|   |      | 2.4.1   | Research on power management techniques                                                                     | 33 |

|   |      | 2.4.2   | Radiation tolerance                                                                                         | 37 |

|   |      | 2.4.3   | Low power consumption $\ldots \ldots \ldots$ | 37 |

|   |      | 2.4.4   | Low noise and low silicon area                                                                              | 38 |

|   | 2.5  | Conclu  | usions                                                                                                      | 38 |

|   | Bibl | iograph | y                                                                                                           | 39 |

| 3 | Alte | ernativ | ve power distribution approaches                                                                            | 43 |

|   | 3.1  | The se  | blution of power distributions                                                                              | 43 |

|   | 3.2  | Serial  | powering                                                                                                    | 44 |

|   |      | 3.2.1   | Structures and implementation of the serial powering                                                        | 44 |

|   |      | 3.2.2   | Performances achieved                                                                                       | 46 |

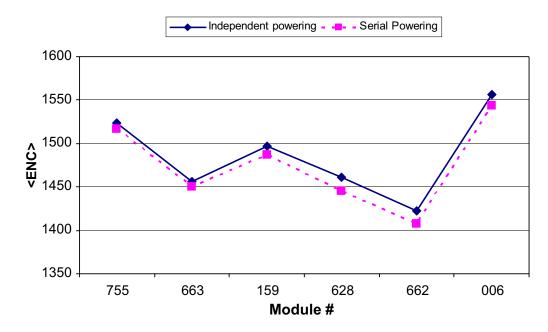

|   | 3.3  | DC-D    | C conversion powering                                                                                       | 47 |

|   |      | 3.3.1   | Buck DC-DC converter with air-core inductors                                                                | 48 |

|   |      | 3.3.2   | Switched capacitor DC-DC converter                                                                          | 50 |

|   |      | 3.3.3   | Piezoelectric transformers                                                                                  | 51 |

|   | 3.4  | Comp    | arison of serial powering and DC-DC conversion                                                              | 53 |

|   | 3.5  | The p   | ower distribution proposed for CPS                                                                          | 53 |

|   | 3.6  | Conclu  | usions                                                                                                      | 57 |

|   | Bibl | iograph | y                                                                                                           | 58 |

| 4 | Rad  | liation | effects and radiation hardening by design                                                                   | 61 |

|   | 4.1  | Introd  | uction                                                                                                      | 62 |

|   | 4.2  | Ionizir | ng radiation                                                                                                | 62 |

|   |      | 4.2.1   | Total ionizing dose effects                                                                                 | 63 |

|   |      | 4.2.2   | Single-event effects (SEE)                                                                                  | 68 |

|   | 4.3  | Non-io  | onizing radiation or displacement damage                                                                    | 71 |

|   | 4.4  | Radia   | tion hardening by design                                                                                    | 72 |

|   |      | 4.4.1   | Hardening against TID effects                                                                               | 72 |

|   |      | 4.4.2   | Hardening against SEE                                                                                       | 73 |

|   | 4.5  | Conclu  | usions                                                                                                      | 77 |

|   | Bibl | iograph | y                                                                                                           | 78 |

| <b>5</b> | Des   | ign of   | linear regulator for clamping voltage, RegVclamp                                                                                                                    | 83    |

|----------|-------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

|          | 5.1   | Introd   | luction                                                                                                                                                             | . 83  |

|          | 5.2   | The re   | egulator topologies                                                                                                                                                 | . 86  |

|          |       | 5.2.1    | Frequency compensation based on current buffer                                                                                                                      | . 87  |

|          |       | 5.2.2    | Nested-Miller compensation (NMC)                                                                                                                                    | . 88  |

|          |       | 5.2.3    | Damping-factor-control frequency compensation                                                                                                                       | . 89  |

|          |       | 5.2.4    | Buffer impedance attenuation                                                                                                                                        | . 91  |

|          |       | 5.2.5    | Pole-zero cancelation                                                                                                                                               | . 92  |

|          | 5.3   | Linear   | regulator for clamping voltage, RegVclamp                                                                                                                           | . 93  |

|          |       | 5.3.1    | Design considerations at system level                                                                                                                               | . 94  |

|          |       | 5.3.2    | The proposed reference generator RegVclamp                                                                                                                          | . 98  |

|          |       | 5.3.3    | Measurement results and discussions                                                                                                                                 | . 101 |

|          | 5.4   | Conclu   | usions                                                                                                                                                              | . 109 |

|          | Bibl  | iograph  | ly                                                                                                                                                                  | . 110 |

| 6        | Des   | ign of   | linear regulator for analog supply voltage, RegVdda                                                                                                                 | 113   |

|          | 6.1   | Design   | $\mathbf{n} \text{ considerations } \ldots $ | . 113 |

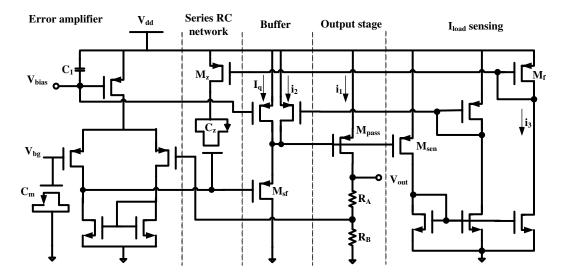

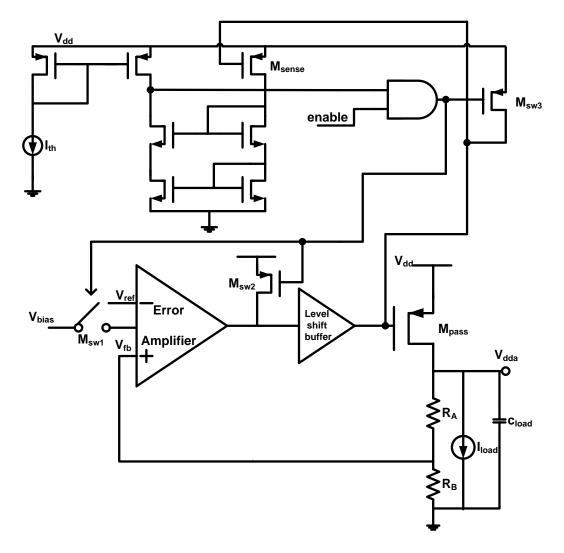

|          | 6.2   | Circui   | t design $\ldots$                                                                  | . 114 |

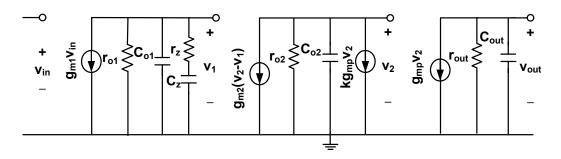

|          |       | 6.2.1    | Stability analysis                                                                                                                                                  | . 116 |

|          |       | 6.2.2    | Dropout voltage and PSR                                                                                                                                             | . 120 |

|          | 6.3   | Exper    | imental results and discussions                                                                                                                                     | . 120 |

|          | 6.4   | Optim    | nization design of RegVdda                                                                                                                                          | . 128 |

|          | 6.5   | Conclu   | usions                                                                                                                                                              | . 130 |

|          | Bibl  | iograph  | ly                                                                                                                                                                  | . 131 |

| Co       | onclu | isions a | and perspectives                                                                                                                                                    | 133   |

|          | Bio   | graphy   | 7                                                                                                                                                                   | 137   |

# List of Figures

| 1    | Schéma de le HFT et le PXL équipée par les puces CPSs                                                  | xiv |

|------|--------------------------------------------------------------------------------------------------------|-----|

| 2    | La distribution de puissance pour les CPS dans un «ladder»                                             | xiv |

| 3    | Diagramme simple de la gestion de l'alimentation dans le CPS                                           | xv  |

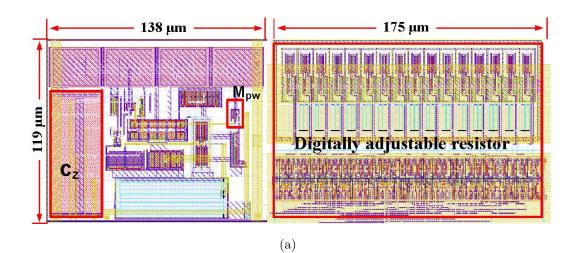

| 4    | Disposition des RegVclamp (a) et RegVdda (b)                                                           | xvi |

| 1.1  | Elementary particles and their interaction in Standard Model                                           | 3   |

| 1.2  | Phase diagram of nuclear matter as a function of the temperature and the                               |     |

|      | baryonic density.                                                                                      | 3   |

| 1.3  | Schematic view of the heavy ion collision with time evolution. $\ldots$ $\ldots$ $\ldots$              | 4   |

| 1.4  | The bird's eye view of LHC at CERN.                                                                    | 5   |

| 1.5  | The bird's eye view of RHIC.                                                                           | 5   |

| 1.6  | The bird's eye view of Tevatron                                                                        | 6   |

| 1.7  | The layout of STAR detector and the cutting view showing the inner de-                                 |     |

|      | tector [6]. $\ldots$  | 7   |

| 1.8  | The architecture of hybrid pixel sensor [8]                                                            | 8   |

| 1.9  | Structure of CCD and the operation timing                                                              | 9   |

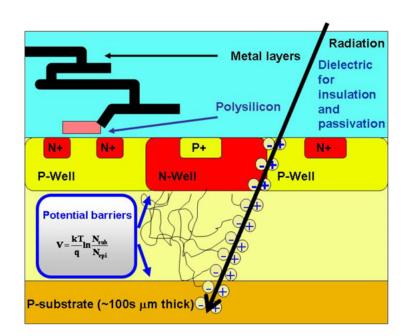

| 1.10 | Schematic cross-section of a CMOS pixel sensor [16]                                                    | 10  |

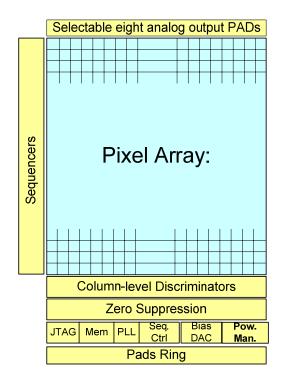

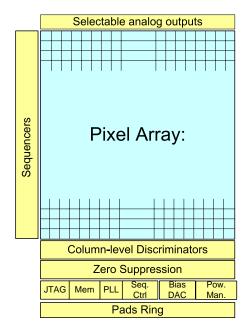

| 1.11 | Structure of CPS chip                                                                                  | 11  |

| 2.1  | Structure of current CPS chip                                                                          | 20  |

| 2.2  | Simplified pixel topology [1]. $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ | 21  |

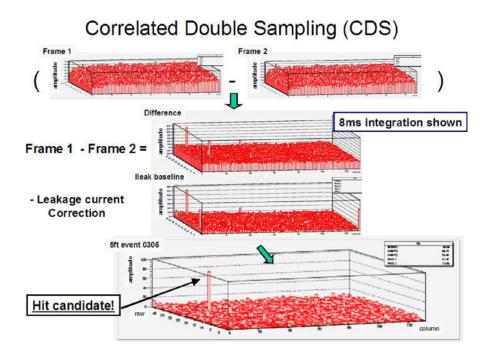

| 2.3  | Signal extraction with CDS operation for early CPS chips [13]                                          | 24  |

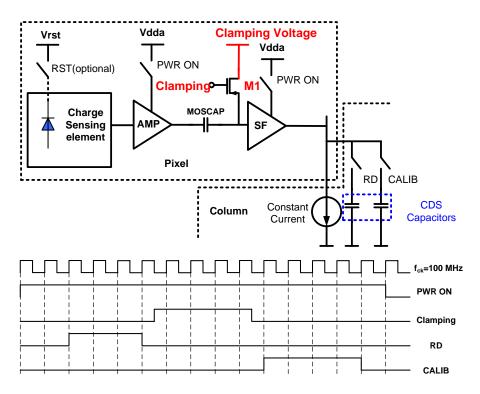

| 2.4  | Block diagram and timing of CDS operation [14].                                                        | 25  |

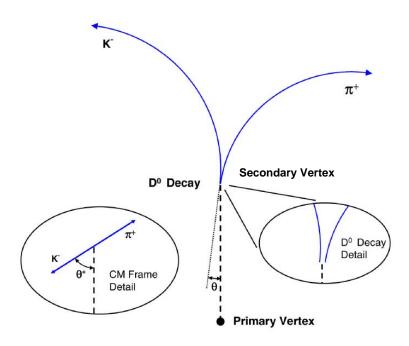

| 2.5  | Diagram of $D^0$ decaying                                                                              | 26  |

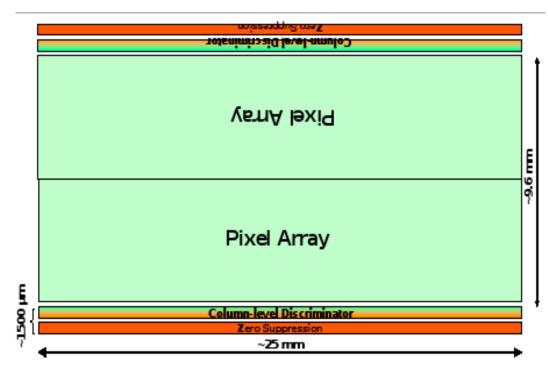

| 2.6  | Diagram of two sided readout.                                                                          | 28  |

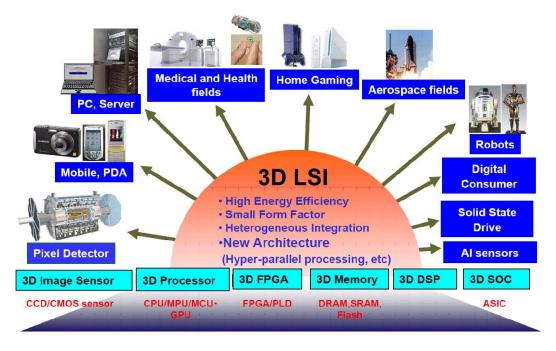

| 2.7  | Potential applications of 3D technology [20]                                                           | 29  |

| 2.8  | Transforming 2D into 3D.                                                                               | 30  |

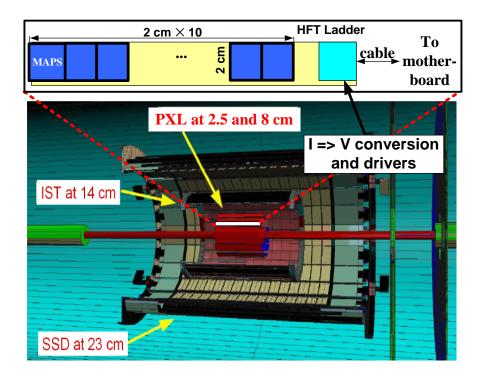

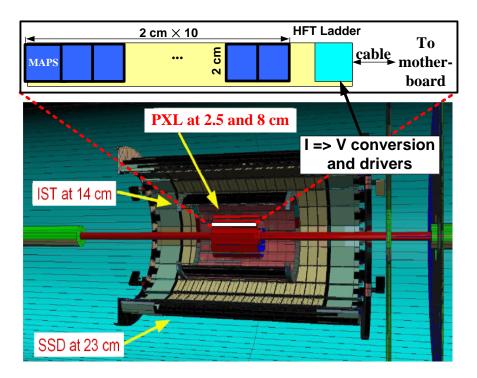

| 2.9  | Diagram of the HFT and one ladder                                                                      | 31  |

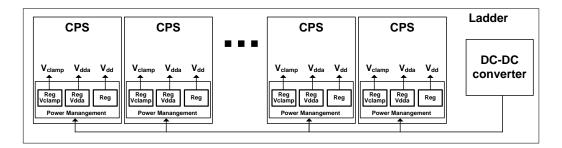

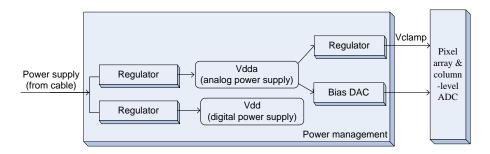

| 2.10 | Block diagram of power management in CPS                                                               | 31  |

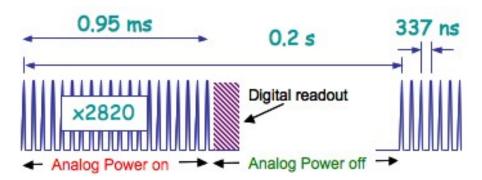

| 2.11 | Power cycling options of ILC bunch timing [22]                                | 32 |

|------|-------------------------------------------------------------------------------|----|

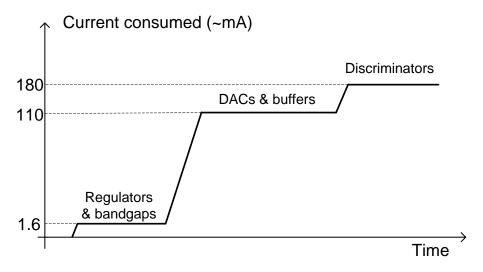

| 2.12 | Current consumed by CPS during the startup                                    | 32 |

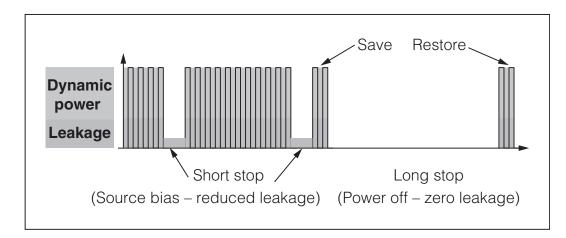

| 2.13 | Pulse width modulation activity/inactivity sequence over time [23]            | 34 |

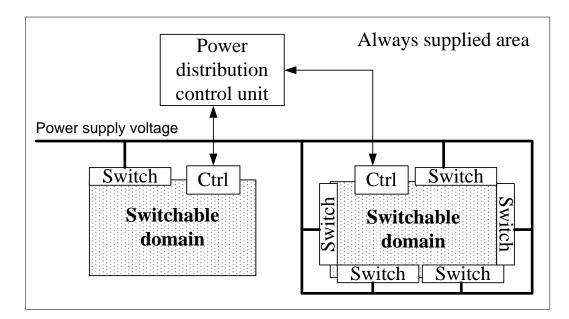

| 2.14 | Power gating using one switch or several switches                             | 35 |

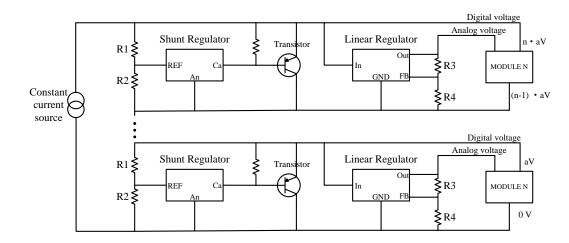

| 3.1  | Scheme of a serial powering without shown AC-coupling of signal. (The         |    |

|      | module voltage is assumed about aV.)                                          | 44 |

| 3.2  | Sketch of alternative serial powering implementations in a two-module con-    |    |

|      | figuration with three ROICs. A single shunt regulator and shunt transistor    |    |

|      | external to the ROICs (a). Parallel shunt regulators and shunt transistors,   |    |

|      | one each in each ROIC (b). A single external shunt regulator combined         |    |

|      | with parallel shunt transistors, one in each ROIC (c). [1]                    | 45 |

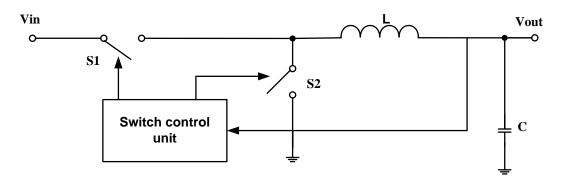

| 3.3  | The comparison of the noise between independent powering and serial pow-      |    |

|      | ering [1]                                                                     | 47 |

| 3.4  | Architecture of buck converter.                                               | 48 |

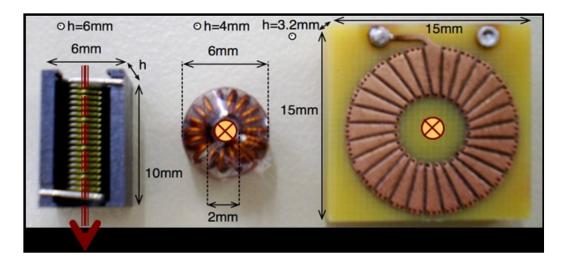

| 3.5  | Solenoid (left), air core toroid (center), PCB toroid (right) [8]             | 49 |

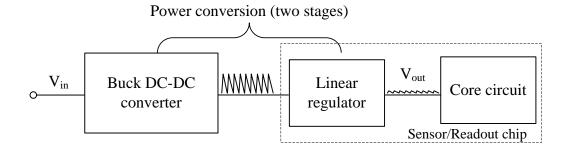

| 3.6  | Post-regulator built-in the low-noise electronics.                            | 50 |

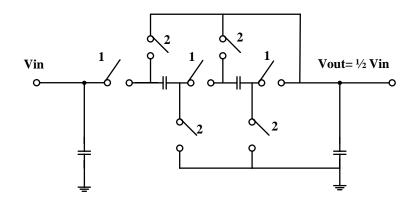

| 3.7  | Simplified schematic diagram of a divide-by-two charge pump, "1" and "2"      |    |

|      | represent "charging" and "discharging" phase, respectively.                   | 51 |

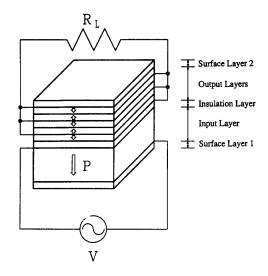

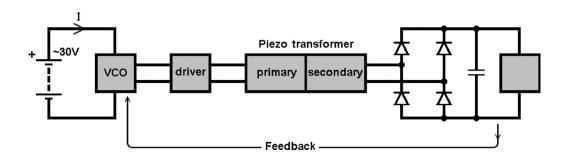

| 3.8  | Piezoelectric transformer construction [16]                                   | 52 |

| 3.9  | Sketch of a four-terminal piezoelectric transformer used as a DC-DC con-      |    |

|      | verter powering a module [1]                                                  | 53 |

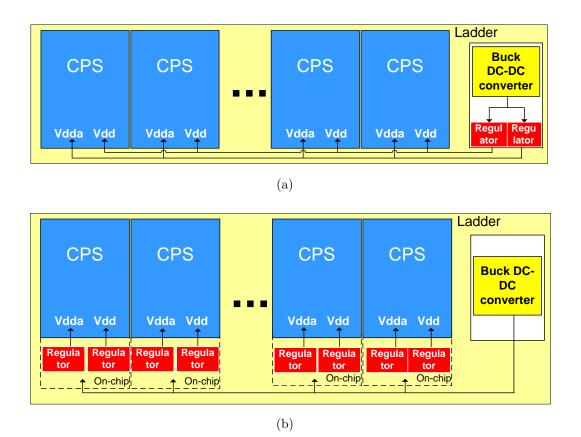

| 3.10 | Schemes of the power distribution for CPS chips in a ladder: employing        |    |

|      | discrete regulators (Reg) (a) and on-chip regulators (Reg) (b). $\ldots$ .    | 55 |

| 3.11 | Power distribution for CPS in a ladder                                        | 56 |

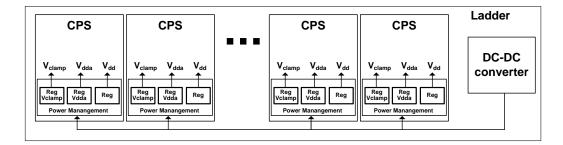

| 4.1  | Classification of radiation [1].                                              | 61 |

| 4.2  | Band diagram of an MOS capacitor with a positive gate bias. Illustrated       |    |

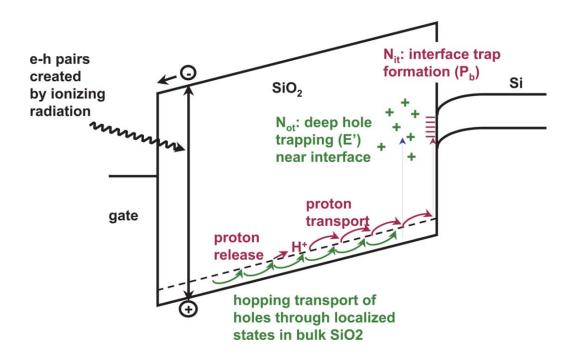

|      | are the main processes for radiation-induced charge generation [2]            | 63 |

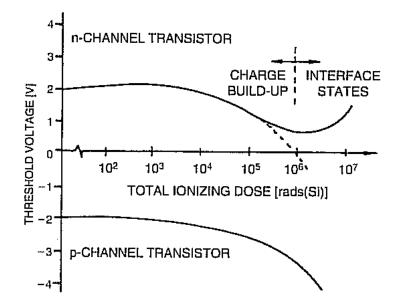

| 4.3  | Threshold voltage shift of NMOS and PMOS transistors versus dose [5].         | 65 |

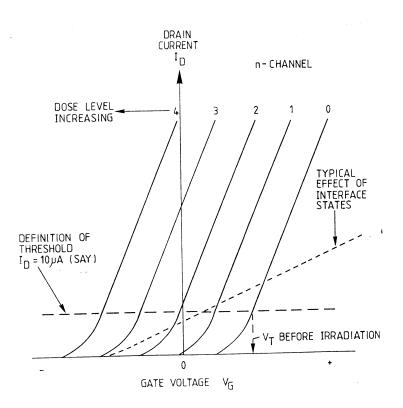

| 4.4  | Drain current of NMOS transistors with increasing dose level [7].             | 66 |

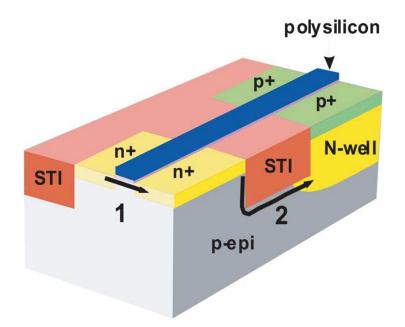

| 4.5  | Possible leakage pathes in a shallow-trench isolation technology [10]         | 67 |

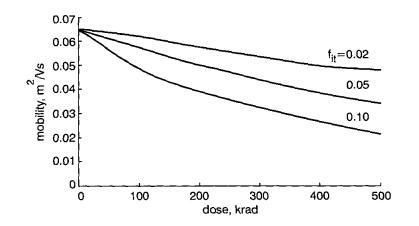

| 4.6  | Variation of mobility of surface channel with increasing dose and three       |    |

|      | different generation efficiencies of interface trap charge [11]               | 68 |

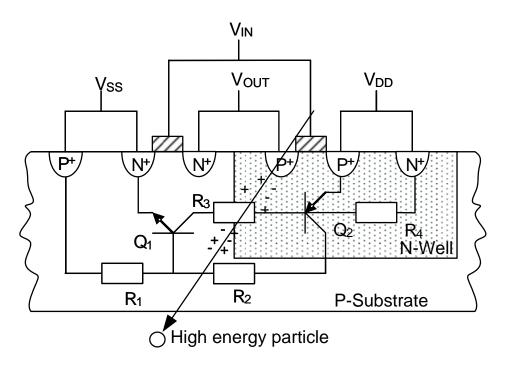

| 4.7  | Principle of SEL in an inverter illustrating charges induced by a single high |    |

|      | energy particle.                                                              | 70 |

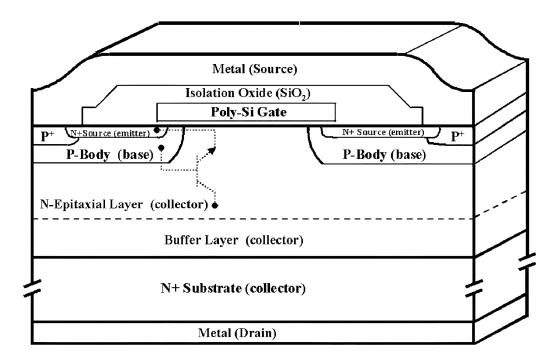

| 4.8  | Cross section of n-channel power MOSFET [17].                                 | 71 |

|      |                                                                               |    |

### LIST OF FIGURES

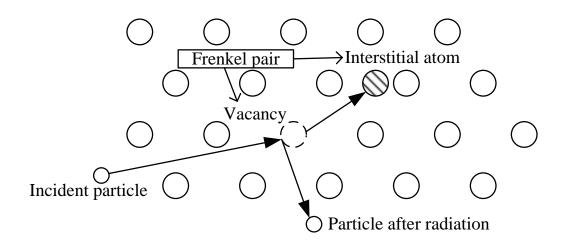

| 4.9  | Atom displacement damage.                                                                                     | 72  |

|------|---------------------------------------------------------------------------------------------------------------|-----|

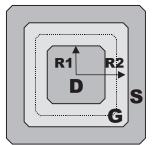

| 4.10 | Layout of the enclosed layout transistor [24]                                                                 | 73  |

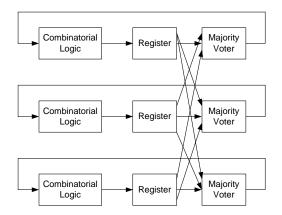

|      |                                                                                                               | 74  |

|      |                                                                                                               | 75  |

|      |                                                                                                               | 75  |

|      |                                                                                                               | 76  |

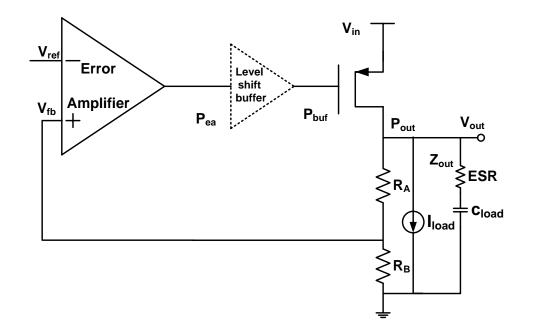

| 5.1  | Block diagram of traditional linear regulator with buffer depicting the main                                  |     |

|      | poles and zeros                                                                                               | 84  |

| 5.2  | An example of frequency compensation based on employing buffer [8]                                            | 88  |

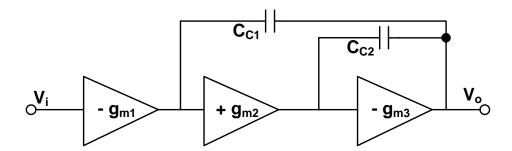

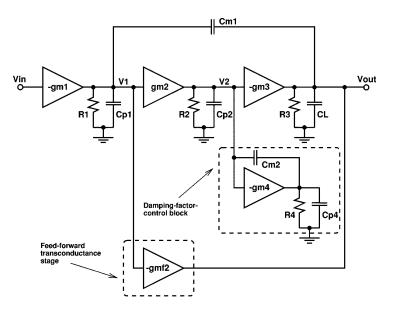

| 5.3  | A three-stage amplifier with nested Miller compensation                                                       | 89  |

| 5.4  | Block diagram of a multi-stage amplifier with damping-factor-control fre-                                     |     |

|      | quency compensation [14]. $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$                      | 90  |

| 5.5  | Buffer with dynamically-biased shunt feedback [17]                                                            | 92  |

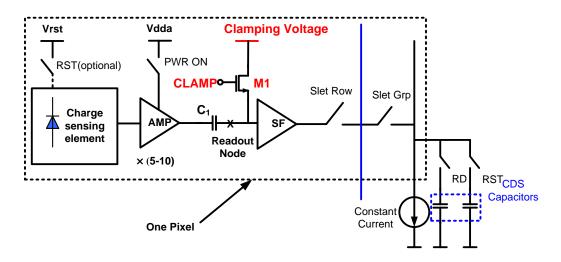

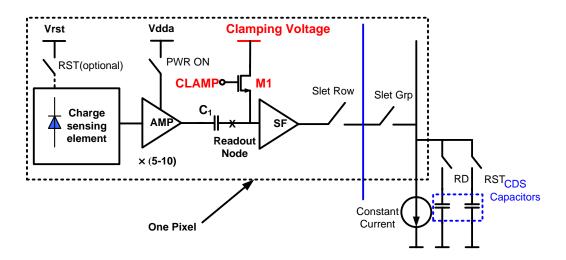

| 5.6  | Pixel topology [21]. $\ldots$                                                                                 | 94  |

| 5.7  | The block diagram of the proposed regulator depicting the equivalent re-                                      |     |

|      | sistors and capacitors of each stage and the main noise sources. $\ldots$ .                                   | 96  |

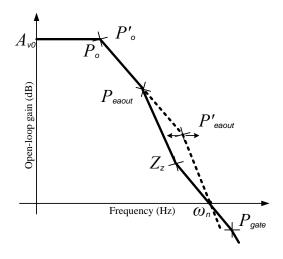

| 5.8  | The pole-zero location of the regulator before (dashed line) and after (solid                                 |     |

|      | line) compensation. $\ldots$ | 96  |

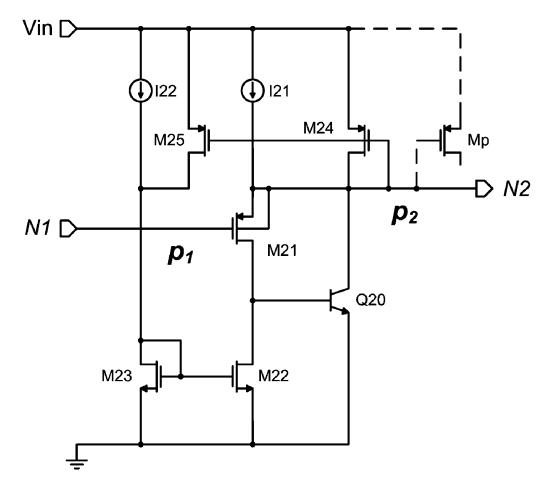

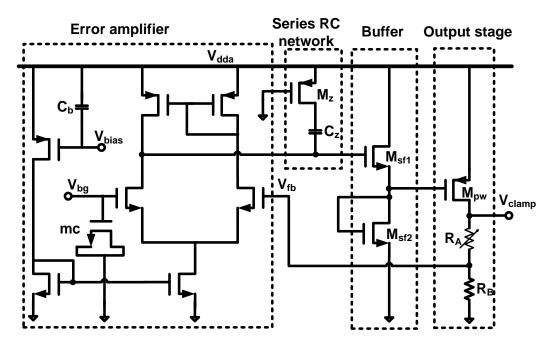

| 5.9  | Schematic diagram of the RegVclamp.                                                                           | 99  |

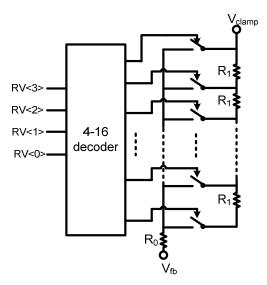

| 5.10 | The digitally adjustable resistor $R_A$                                                                       | .00 |

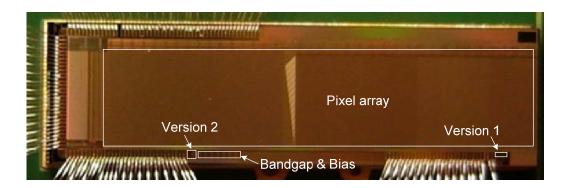

| 5.11 | Microphotograph of the MIMOSA22-HRE chip                                                                      | .00 |

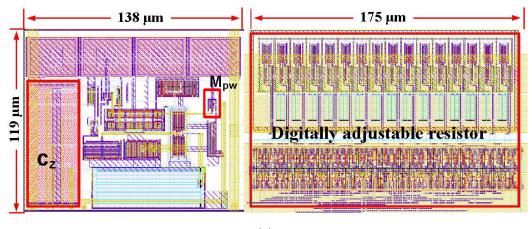

| 5.12 | Layout of the version 1 (a) and version 2 (b)                                                                 | .02 |

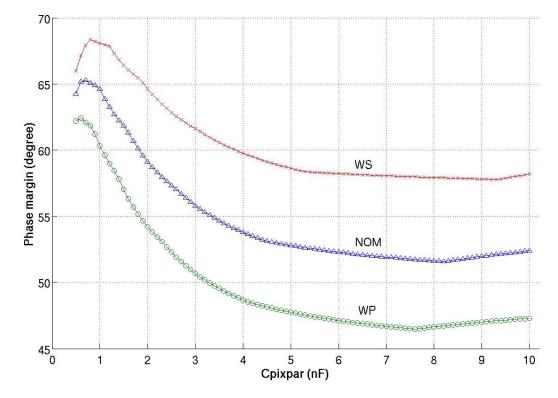

| 5.13 | Simulated results of phase margin with respect to the load capacitor 1                                        | .03 |

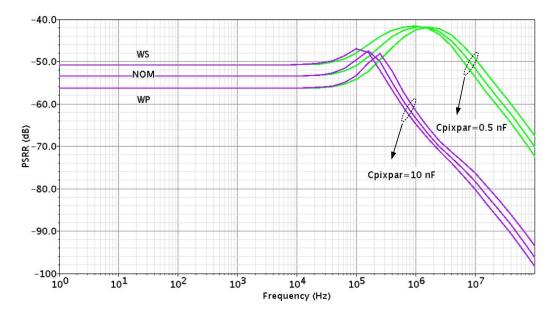

| 5.14 | Simulated results of PSRR with capacitance of 0.5 nF and 10 nF 1                                              | .03 |

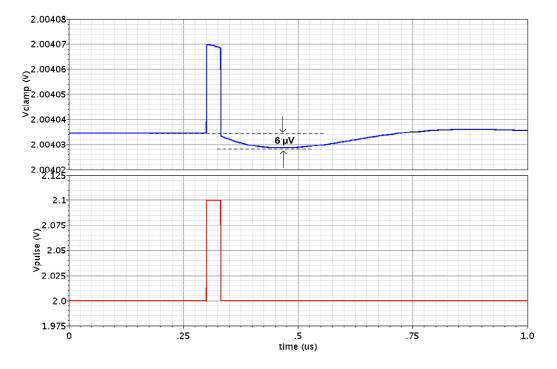

| 5.15 | Simulated output voltage during the clamping operation                                                        | .04 |

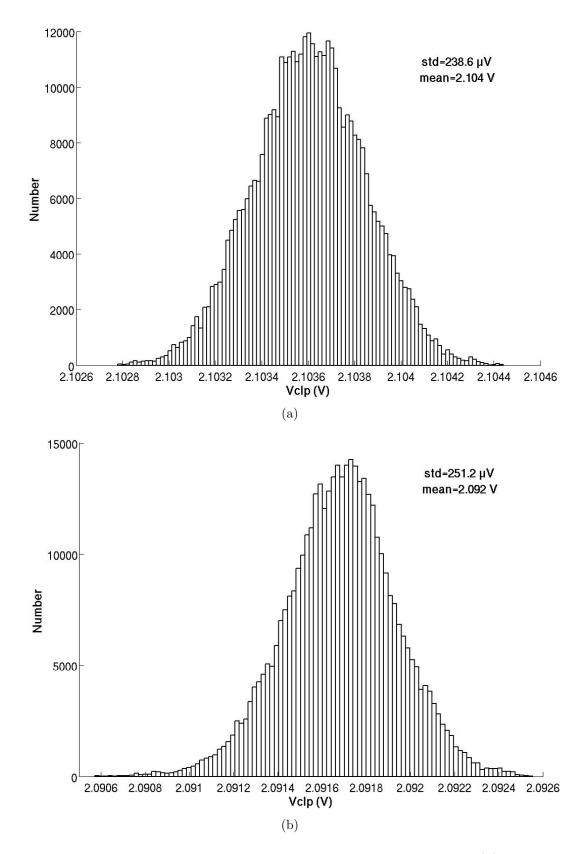

| 5.16 | Histograms of the clamping voltage refer to version $1$ (a) and version $2$ (b) $1$                           | .05 |

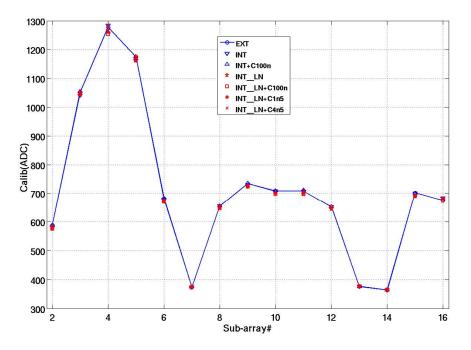

| 5.17 | Calibration results with different reference generators and load capacitances.1                               | .06 |

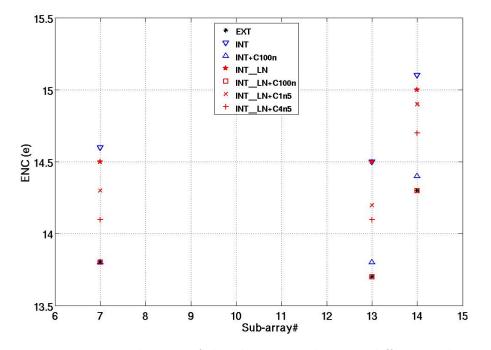

| 5.18 | Measured noise of the clamping voltage in different sub-arrays                                                | .07 |

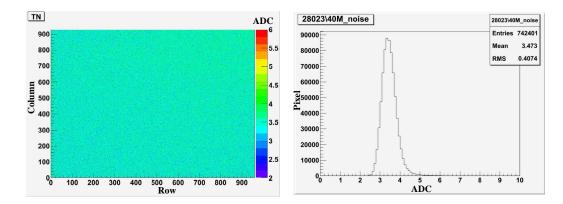

| 5.19 | Distribution of the pixels noise in ULTIMATE at 40 MHz clock frequency                                        |     |

|      | (left) and Histogram of pixel noise in ADC unit (right) (1 ADC unit= $4.15$                                   |     |

|      | $e^{-}$ ) [28]                                                                                                | .08 |

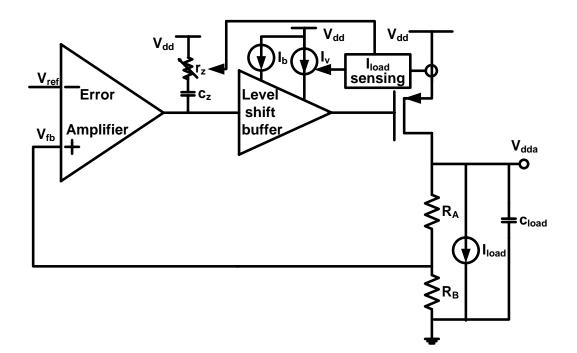

| 6.1  | Block diagram of RegVdda.                                                                                     | .14 |

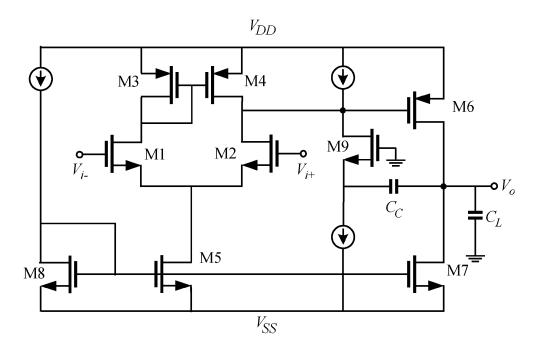

| 6.2  | Implementation of the proposed regulator                                                                      | 15  |

| 6.3  | Equivalent small-signal model of the proposed regulator (open-loop). $\ldots$ 1                               | 15  |

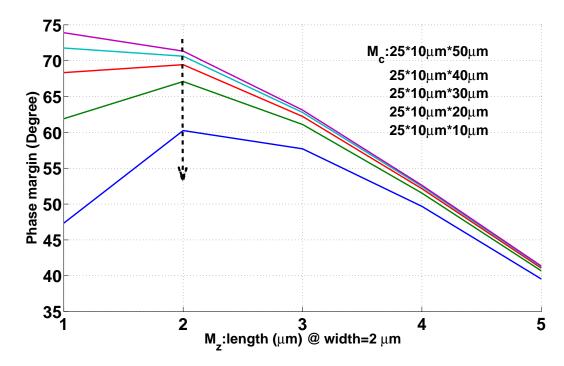

| 6.4  | Optimization of $M_z$ and $M_c$                                                                               | .18 |

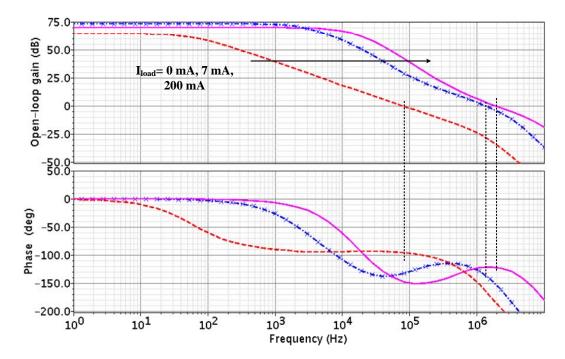

| 6.5  | Open-loop frequency responses at load current of 0 mA, 7 mA and 200 mA $$   |  |

|------|-----------------------------------------------------------------------------|--|

|      | when load capacitance is 200 nF                                             |  |

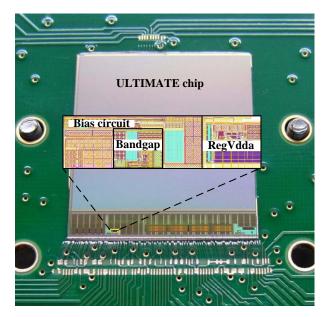

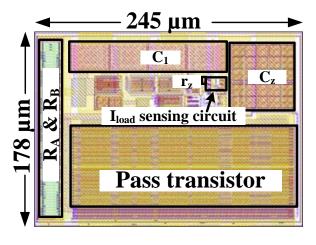

| 6.6  | ULTIMATE chip micrograph (a) and layout of the regulator RegVdda (b). $121$ |  |

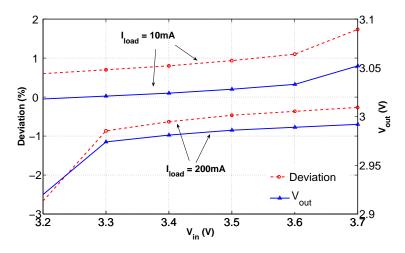

| 6.7  | Measured line and load regulation. $\ldots$                                 |  |

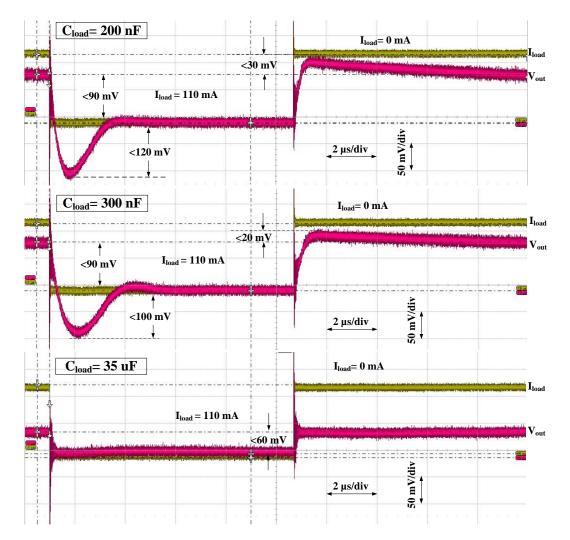

| 6.8  | Transient response when the load current varies with different load capac-  |  |

|      | itances. $(I_{load} (\text{Yellow}), V_{out}(\text{Red}))$                  |  |

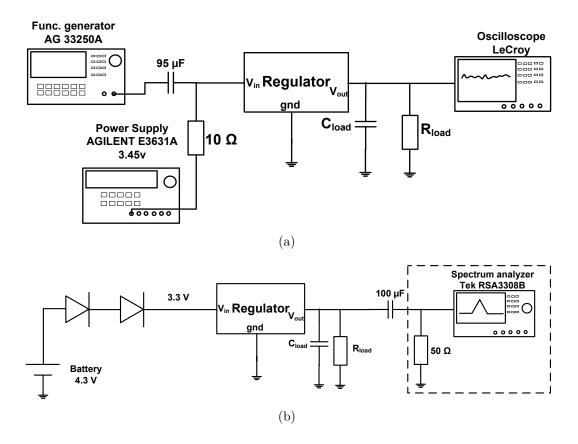

| 6.9  | Measurement setup of PSR (a) and output noise (b)                           |  |

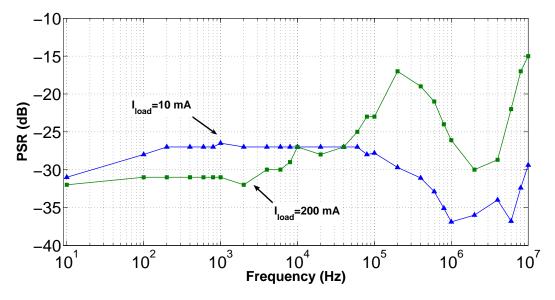

| 6.10 | Measured PSR                                                                |  |

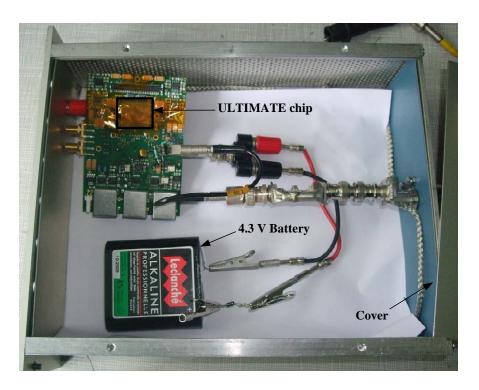

| 6.11 | Tested chip and battery are placed in the metal box for shielding 125       |  |

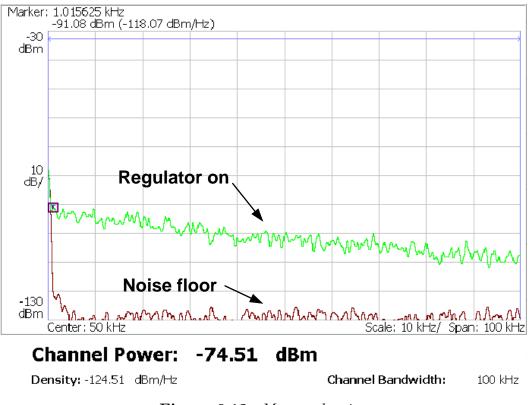

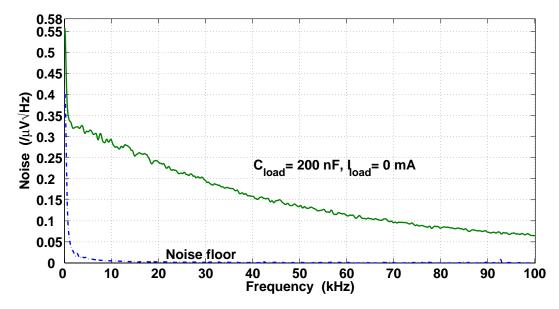

| 6.12 | Measured noise                                                              |  |

| 6.13 | Measured output noise spectrum density                                      |  |

| 6.14 | Implementation of the current limiter                                       |  |

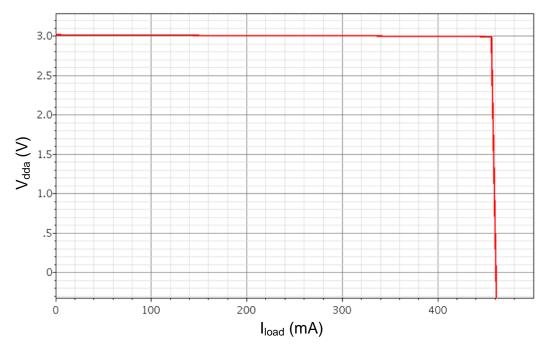

| 6.15 | Simulated results of current limiter in nominal corner                      |  |

| 6.16 | Simulated results of $V_{dda}$ versus $V_{dd}$                              |  |

# List of Tables

| 1.1 | Force and their carries                                                            |

|-----|------------------------------------------------------------------------------------|

| 1.2 | The performance comparisons of CPS with the competitions                           |

| 2.1 | Radiation dose and fluence of HEP experiments                                      |

| 3.1 | Features of IP and alternative approaches [1]                                      |

| 5.1 | Design specifications of RegVclamp                                                 |

| 5.2 | Performances comparison of the two versions                                        |

| 6.1 | Design specifications of RegVdda                                                   |

| 6.2 | The performance comparisons of the proposed work and reported work $~$ . $. ~ 127$ |

### Acknowledgements

It is a pleasure to thank all the persons who help me in my doctor living and study during the past five years. They make this thesis possible. Firstly, I would like to thank China Scholarship Council (CSC) for funding my two-year study in University of Strasbourg, France and Institut Pluridisciplinaire Hubert Curien (IPHC), Strasbourg, for providing me the opportunity to join in the wonderful research group of CMOS pixel sensors.

I would like to express my endless gratitude to both of my supervisors, Prof. Yann Hu from University of Strasbourg and Prof. Deyuan Gao from Northwestern Polytechnical University. They taught me how to independently research and to be a real researcher. I am deeply influenced by their careful work, diligence, specialist knowledge and wisdom. I also would like to thank Prof. Tingcun Wei who leads me to enter the gate of microelectronics and makes me have an interest in the analog circuit design. His research spirit and methods have made great impact on me, since I was a beginner. I also got very helpful writing suggestions from him when I wrote my Ph.D. thesis.

I gratefully acknowledge Dr. Christine Hu-Guo, Dr. Isabelle Valin, Dr. Andrei Dorokhov, Dr. Mariusz Jankowski and Dr. Hung Pham for their fruitful discussions. Thank them for giving me help in the circuit design and measurement. I also thanks for their wonderful written suggestions about writing English. I appreciate Kimmo Jaaskelainen, Mathieu Goffe, Frederic Morel and Gregory Bertolone for their help of circuit fabrication and measurement. I gratefully thank Jerome Nanni and Guy Doziere for their help of learning French and my living in France. I also would like to thank Xiaochao Fang and Ying Zhang for their help of reviewing my thesis and submitting defense documents for me. I appreciate Marc Winter, Claude Colledani, Wojciech Dulinski, Abdelkader Himmi, Sylviane Molinet, Christian Illinger, Gilles Claus, Ying Zhang, Min Fu, Liang Zhang, Wei Zhao, Zhan Shi, Yang Zhou, Yunan Fu and other colleagues in IPHC for providing me a wonderful and warm academic atmosphere. I would like to thank Xiaomin Wei, Dr. Renzhuo Wan and Dr. Fan Yang for their kind care when I broke my finger. During I wrote this thesis, I also got help from Dr. Wu Gao, Ran Zheng, Feng Li, Limin Han and other classmates in Northwestern Polytechnical University. Thank for their helpful comments and suggestions.

Last but not least, I am extremely grateful to my grandparents, parents, wife and sister. They are the impulse source during my five years doctoral work and my life. Thanks for their selfless supports and endless love. They make me persist my research when I face challenges and problems. I especially thank my wife for her patience, understanding and encouragement which help me to overcome each difficulty. Thank the true love for making us together!

> Jia Wang Xi'an, China May 22, 2012

### Résumé

Capteurs à pixels CMOS (CPS, aussi appelés capteurs monolithiques à pixels actifs) offrent un compromis attirant entre le budget matériel, la tolérance au rayonnement, la consommation d'énergie et la granularité. L'autre avantage est que les CPS peuvent être émincés à 50  $\mu$ m, ce qui est utile pour diminuer le budget matériel. Le CPS est un bon choix pour détecter les particules chargées dans les détecteurs de vertex. Par exemple, les puces CPSs va équiper le détecteur PXL en «heavey flavor tracker» (HFT) de «Solenoidal Tracker at RHIC (STAR) experiments» (illustré à la figure 1.).Une série des puces CPSs appelées MIMOSA (« Minimum Ionising particle MOS Active sensor») ont été conçus et évalués par le groupe de micro-électronique à l'IPHC (Institut Pluridisciplinaire Hubert Curien), Strasbourg, France, depuis les années 1990. Ce travail de thèse est une partie de la conception des CPS à l'IPHC et dédiée à la gestion de l'alimentation. Ce bloc fournit les tensions nécessaires à les autres circuits, tels que la matrice de pixels et les discriminateurs, etc.

La stratégie de distribution de puissance pour les CPS est d'abord recherchée. Comme l'approche traditionnelle, les alimentations sont indépendantes. Ils échouent. Puisque plus de capteurs va équiper dans le détecteur, le nombre des côles a fortement augmenté. Le budget de matériel ne peut pas satisfaire à l'exigence. En outre, il y aura plus de l'énergie consommé par les côles. Par conséquent, l'efficacité énergétique des systèmes de détection est réduite à une valeur inacceptable. Il y a principalement deux approches alternatives, telles que les alimentations en série et la conversion DC-DC. Puisque les alimentations en série ne sont pas compatibles avec la conception récente des CPS, la conversion DC-DC est utilisée. Comme le montre la figure 2, un convertisseur abaisseur «Buck» DC-DC fournit des alimentations à plusieurs puces de capteurs. Puis, la tension de sortie entre dans la gestion de l'alimentation de chaque puce CPS, où les tensions d'alimentation analogique et numérique sont générées. En outre, il y a quelque tensions critiques utilisées dans les puces CPSs. Les références de tension doivent être à faible bruit en raison du très faible signal détecté. Des cbles sont nécessaires si ces tensions sont fournies extérieurement. Toutefois, les puces CPSs sont montées à proximité dans le «ladder». La diaphonie apparaît parmi les puces de détection. Le bruit peut être injecté

Figure 1: Schéma de le HFT et le PXL équipée par les puces CPSs.

Figure 2: La distribution de puissance pour les CPS dans un «ladder»..

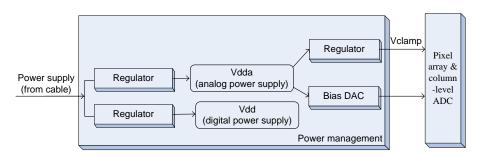

Figure 3: Diagramme simple de la gestion de l'alimentation dans le CPS.

dans les références de tension. Le condensateur de filtrage peut être utilisé pour diminuer le bruit. Toutefois, le budget de matériel est augmenté et la conception «ladder» est compliquée. En conséquence, certaines tensions critiques sont générées dans la gestion de l'alimentation comme l'indique la figure 3.

Le régulateur à faible chute de tension (LDR) est un élément essentiel dans le système d'alimentation. Le bruit et la taille limitent l'application de l'alimentation à découpage, bien qu'elle puisse atteindre un rendement élevé. En outre, il est difficile d'intégrer un inducteur ou un grand condensateur dans la puce. Le LDR comporte généralement une faible chute de tension, un faible bruit et une petite taille. Puisque les circuits analogiques sont sensibles au bruit, les LDRs sont utilisés pour fournir la tension d'alimentation analogique et les références de tension. Afin d'augmenter le rendement élevé, le convertisseur à capacités commutées est utilisé. Le LDR peut également supprimer le bruit de commutation du convertisseur d'abaisseur DC-DC. Toutefois, certains défis sont portés à la conception LDR dans les CPS. La stabilité doit être analysée attentivement, parce que tout élément extérieur n'est pas autorisé en vue de réaliser la conception de sur-puce pleinement. En outre, le bruit et la consommation de l'alimentation devraient être faible. La tolérance au rayonnement doit être également concernée. Deux LDRs sont conçus et évalués dans ce travail de thèse (illustré à la figure 4.). Un régulateur dit «RegVclamp» est utilisé pour fournir la tension de «clamping», qui est utilisé pour le fonctionnement à double échantillonnage corrélé. L'autre régulateur dit RegVdda est utilisé pour fournir la tension d'alimentation analogique.

Une structure basée sur l'annulation de pôle-zéro et l'optimisation de la conception est proposée afin de satisfaire toutes les exigences. Les deux régulateurs sont vérifiés par les deux prototypes. Le RegVclamp est intégré dans MIMOSA22HRE afin d'offrir la tension de clamping à la puce du capteur. Les résultats des mesures montrent que seulement 5,8% du bruit est augmenté par le RegVclamp, qui peut satisfaire à l'exigence du bruit. Il est également vérifié par la puce ULTIMATE, dans lequel la capacité parasite

(b)

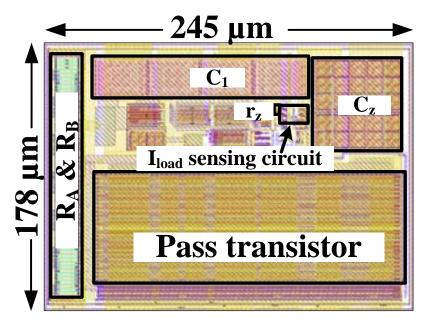

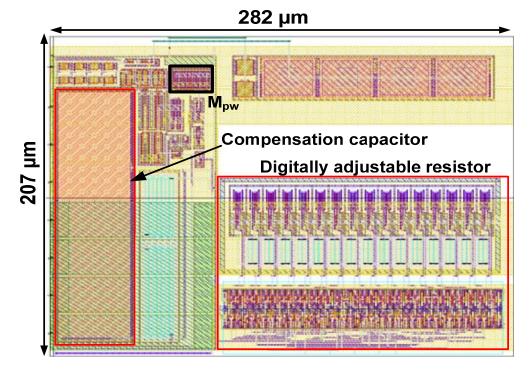

Figure 4: Disposition des RegVclamp (a) et RegVdda (b).

aux exigences des puces CPSs.

est différente avec MIMOSA22HRE. La plupart de capacité de charge de RegVclamp vient de la capacité parasite. Il est d'environ 0,5 nF dans le MIMOSA22HRE et 5 nF dan l'ULTIMATE. Les résultats démontrent que le RegVclamp peut travailler avec un large éventail de capacités de charge. Ainsi, il peut être réutilisé dans les puces CPSs avec les matrices de pixels différents. L'ENC («Equivalent Noise Charge») du pixel est inférieure à 15  $e^-$ , lorsque la tension de «clamping» est fournie par RegVclamp. Il peut satisfaire

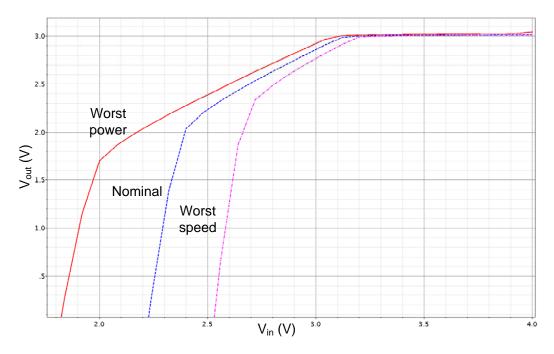

Afin de générer la tension d'alimentation analogique, le RegVdda est conçu. Puisque le courant de charge varie dans une large gamme, tous les pôles et les zéros sont réglables pour garantir la stabilité. Une nouvelle structure est proposée. Une résistance et un condensateur sont connectés en série, qui introduit un zéro dans le demi-plan de gauche. En outre, deux rétroactions de courant sont utilisées pour adapter la valeur de la résistance dans le réseau série et la transconductance du tampon à la mi-étape. Ainsi, tous les pôles et les zéros déplacent à la même direction que le pôle de sortie fait. Le condensateur de compensation utilisé est diminué dans ce régulateur. En outre, le transistor de sortie travaille dans la région à faible inversion et la région linéaire à faible charge et à charge élevée respectivement. Ainsi, la dimension du transistor de sortie est diminuée et le courant de polarisation est aussi diminué. Afin d'atteindre la tolérance au rayonnement, le circuit est fabriqué dans un procédé à la couche épitaxiale avec haute-résistance. En outre, chaque transistor est entouré par l'anneau de garde. Le RegVdda a été intégré dans la puce ULTIMIATE comme un circuit optionnel. Les résultats des mesures montrent que ce régulateur est stable dans la gamme du courant de charge (0 - 200 mA) lorsque la capacité de charge est de 200 nF et 300 nF. Le «power supply rejection» (PSR) est au-dessus de 20 dB à la fréquence de 1 MHz. Le bruit testé est d'environ 65  $nV/\sqrt{Hz}$ à la fréquence de 100 kHz. Toutefois, la chute de tension est de 0,3 V à cause du petit transistor de sortie. Afin de diminuer la chute de tension, un régulateur optimisé a été conçu et il peut fournir jusqu'à 300 mA du courant de charge. Un limiteur de courant a été concu pour protéger le régulateur et les autres blocs des CPS. Un comparateur de courant est conçu afin de comparer le courant détecté et le courant de seuil. La sortie sera égale à «0» si le courant de charge est supérieur à 460 mA. Il permet de couper le courant d'alimentation. Ce régulateur optimisé est intégré dans le MIMOSA30. Les résultats simulés montrent que la chute de tension est inférieure à 200 mV. La performance PSR est également meilleure. La stratégie de gestion de l'alimentation pour CPS est également étudiée. Différent avec l'électronique grand public, les CPS sont limités par le procédé de fabrication. Toutefois, quelques stratégies de gestion de l'alimentation sont basées sur le processus. En outre, la performance est plus importante que la consommation

d'énergie. Ainsi, le compromis entre la performance et la consommation d'énergie devrait être considérée. Une gestion de l'alimentation basée sur les états de travail est proposée dans les CPS. Les alimentations des blocs inutilisés sont coupées dans l'état de veille. Dans le développement du futur, le convertisseur à capacités commutées sera conçu et intégré dans la gestion de l'alimentation. La tolérance aux radiations des transistors de très grande taille sera analysée et testée.

## ABSTRACT

What are the elementary particles and how did the universe originate are the main driving forces in the high energy physics. In order to further demonstrate the standard model and discover new physics, several detectors are built for the high energy physics experiments. CMOS pixel sensors (CPS) can achieve an attractive tradeoff among many performance parameters, such as readout speed, granularity, material budget, power dissipation, radiation tolerance and integrating readout circuitry on the same substrate, compared with the hybrid pixel sensors and charge coupled devices. Thus, the CPS is a good candidate for tracking the charged particles in vertex detectors and beam telescopes.

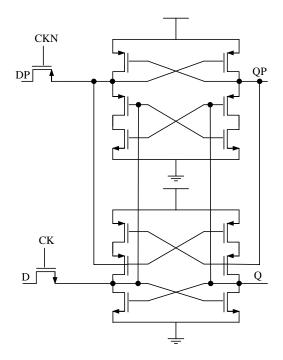

The power distribution becomes an important issue in the future detectors, since a considerable amount of sensors will be installed. Unfortunately, the independent powering has been proved to fail. In order to solve the power distribution challenges and to provide noiseless voltages, this thesis focuses on the design of a low noise, limited area, low power consumption and full on-chip power management in CPS chips. The CMOS pixel sensors are firstly introduced drawing the design requirements of the power management. The power distribution dedicated to CPS chips is then proposed, in which the power management is utilized as the second power conversion stage. Full on-chip regulators are proposed to generate the power supply voltages and the reference voltage required by correlated double sampling operation.

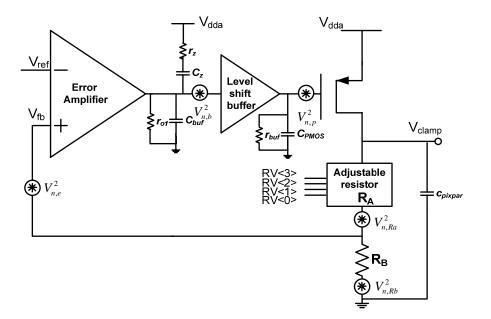

Two full on-chip regulators have been designed and measured. One regulator provides the reference voltage required by correlated double sampling operation, functioning as a reference generator. It is implemented by a three-stage linear regulator. As the mid-stage, the buffer isolates the high output impedance of error amplifier from the large input capacitor of pass transistor with the aim of pushing the relevant poles to high frequency and improving the transient response. Moreover, a series RC network is employed to introduce a zero compensating the phase. The generator is stable with the load capacitance of 0.5 nF - 10 nF, without any external elements. The average noise value amounts to  $\leq 15e^-$  ENC (equivalent noise charge) at 20° and 40 MHz readout clock frequency, when the clamping voltage is internally generated. The output voltage is programmable at the voltage step of 20 mV for testing flexibility. The chip area is about 313  $\mu m \times 119 \ \mu m$ .

Based on the reference generator, a linear regulator is designed to provide the analog supply voltage. Since the current required by CPS chips varies in a large range, a novel structure is proposed. All the poles and zeros are adaptable to move as the output pole does, which is implemented by a current sensing circuit and a current feedback circuit. The measurement results demonstrate that the regulator can be stable in the full range of the load current with the estimated parasitic capacitor in CPS. The power supply rejection at high frequency is also improved due to the large bandwidth. The measured noise is 340  $nV/\sqrt{Hz}$  and 65  $nV/\sqrt{Hz}$  at 1 kHz and 100 kHz, respectively, when the load capacitor is about 200 nF. The quiescent current is 147 mA and 314 mA at the load current of 0 and 200 mA, respectively.

Two prototypes have verified these regulators. They can meet the requirements of CPS. Moreover, the power management techniques and the radiation tolerance design are also presented in this thesis.

**Keywords:** CMOS pixel sensors (CPS), Full on-chip, Linear regulator, Low noise, Low dropout (LDO) regulator, Monolithic active pixel sensors (MAPS), Power management.

# Chapter 1

# Introduction

The integrated circuits have been developing rapidly since 1958 when the first integrated circuit was invented by Jack Kilby. They have been essential in our living from the portable electronics to the large electronic instruments. Silicon is also a good material for sensing due to its proper energy gap. For example, the complementary metal-oxide semiconductor (CMOS) imaging sensors have been widely used in digital cameras for sensing the visual light. Moreover, the doped silicon can react with high energy particles and left electron-hole pairs while they traverse the silicon. In order to rebuild the trace and measure the energy of the high energy particles, the sensor chips are also essential to be employed in high energy physics experiments.

In this chapter, the research background will be presented at first. Then the doctoral work is proposed in brief. At last the layout of this thesis is given.

### 1.1 Research background

### 1.1.1 High energy physics (HEP)

High energy physics (HEP), also called particle physics or elementary particle physics, is looking for the smallest constituents of matter (elementary particles) and for the fundamental forces between them. As called, atoms were considered as the fundamental building blocks of all forms of matter until the beginning of  $20^{th}$  century. The experiments of Rutherford and the others proved that atoms were composed of protons, neutrons and electrons in 1900's. The atoms consist of mostly empty space with electrons surrounding a dense central nucleus made up of protons and neutrons. By the early 1960s, as accelerators reached higher energies, a hundred or more types of particles were discovered

| Force           | Gauge Boson      |

|-----------------|------------------|

| Strong          | Gluon (g)        |

| Electromagnetic | $Photon(\gamma)$ |

| Weak            | $W^{\pm}, Z$     |

| Gravity         | Graviton $(G)$   |

Table 1.1: Force and their carries.

in many series experiments [1]. Nucleus are thought to be composed of quarks. It is still an unanswered question that what are the fundamental particles. It becomes more clear when "Standard Model" was built late in the last century, which should be further proved by further experiments. Modern particle physics research focus on the subatomic particles, including atomic constituents and particles produced by radioactive and scattering processes. The atomic constituents contain electrons, protons and neutrons. Some particles can be produced in the radioactive and scattering processes, such as photons, neutrinos and muons. They also interest the particle physicists.

The fundamental forces refer to the interactions between fundamental particles. It is considered that Strong Force, Weak Force, Electromagnetism and Gravity are the four different types of forces in the nature. These forces can be regarded as being transmitted through the exchange of particles, which are called gauge bosons. The carriers of the four forces are shown in Table 1.1.

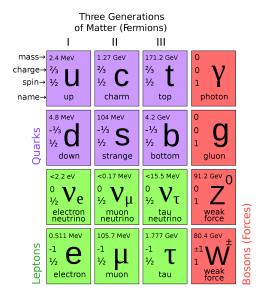

#### 1.1.1.1 Standard model

In 1970s, the "Standard Model" was built to describe the role of the fundamental particles and the interactions between them [2]. In this model, the considered fundamental particles are divided into two classes according to the spin value, the fermions and the bosons, as shown in figure 1.1. The fermions have half integer spin while the bosons have an integer spin. The bosons are the carrier particles of weak, strong, gravity and electromagnetic forces. The fermions contain quarks and leptons, which are considered as the fundamental constituents of matter. Each particle has its corresponding anti-particle having the same properties except the opposite charge and opposite sign of the quantum numbers, so 6 quarks and 6 leptons are included. Moreover, quarks usually cannot be observed in nature and have to combine to form hadrons.

The Standard Model has successfully explained many experimental results and predicted a lot of phenomenons in the past few years. However, it still needs to be further developed and demonstrated by more experiments.

Figure 1.1: Elementary particles and their interaction in Standard Model.

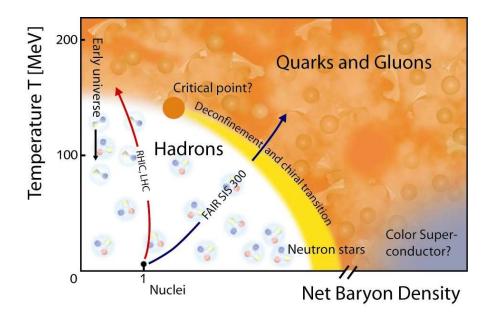

Figure 1.2: Phase diagram of nuclear matter as a function of the temperature and the baryonic density.

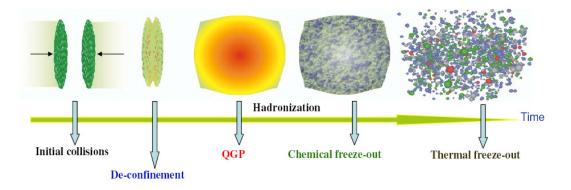

Figure 1.3: Schematic view of the heavy ion collision with time evolution.

As a part of the Standard Model, Quantum ChromoDynamics (QCD) is the universally accepted theory to describe the strong interactions, which happen among the quarks, gluons and nucleons [3]. However, the non-perturbative aspects of QCD are still not well understood, as well as the explaining of the quark confinement. According to the phase diagram in figure 1.2, the hadronic matter is expected to enter a deconfined phase, when the temperature and/or baryonic density increase. The deconfined phase may have plasma characteristics. The quarks become free over a large volume. This phase is called Quark-Gluon Plasma (QGP). Its occurrence has been predicted by QCD. However, it has not been observed in the experiments yet. QGP is also expected to occur in the universe after a few microseconds of Big Bang and the neutron stars nowadays. Therefore, studying the formation and characteristics of QGP allows us to well understand non-perturbative aspects of strong interaction, early universe and many astrophysical processes.

It is believed that QGP can be reproduced in the reaction zone of a heavy ion collision, which is the only way to reproduce QGP in laboratory. As shown in figure 1.3, a volume of hot and dense matter called fireball are produced in the initial collisions and then deconfinement evolved to thermal QGP. The main experiments related to QGP are operated at Brookhaven National Laboratory (BNL), New York in USA and at Conseil Européene pour la Recherche Nucléaire) (CERN), Geneva in Switzerland.

#### 1.1.1.2 HEP experiments

In order to verify the Standard Model and search the new physics beyond it, HEP experiments have been built. The QGP is also expected to be reproduced and observed in the HEP experiments. The main idea of HEP experiments is to accelerate, collide two particles and observe what comes out and try to guess what was in [4]. Unlike the other

Figure 1.4: The bird's eye view of LHC at CERN.

Figure 1.5: The bird's eye view of RHIC.

physics experiments where a theory can be verified by a single measurement, a variety of simultaneous studies are used in the high energy physics experiments to draw strong conclusions. Thus, a great amount of elementary particles such as electrons or hadrons are accelerated by the accelerator and periodically collided [5]. The accelerator is composed of the source, the electric field and the magnetic field. Then the tracks and energy of the particles produced in the collisions are measured and stored with kinds of detectors. The aims of the detectors are to find the tracks of the particles, measure their energy and identify them. Especially, some of them have to be near to the point of the particles' interactions. The dedicated colliders for high energy physics experiments have been built and operated already, for example, the Brookhaven National Lab's relativistic heavy ion collider (RHIC), the large hadron collider (LHC) at CERN (shown in figure 1.4) and the Tevatron in Fermi National Accelerator Laboratory (shown in figure 1.6), which was shut down in September 2011.

In order to detect the particles at a full coverage, the detector is formed as a barrel.

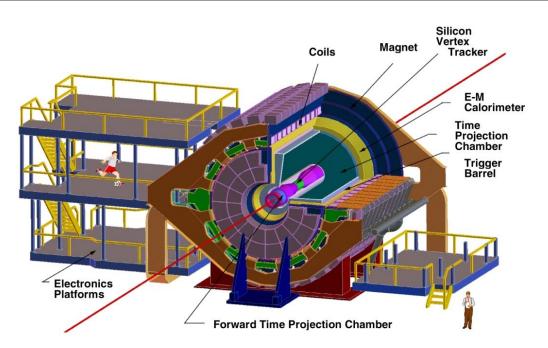

Figure 1.6: The bird's eye view of Tevatron.

This barrel is composed of several subsystems to track different particles. As an example, the layout of the Solenoidal Tracker At RHIC (STAR) detector is depicted in figure 1.7 [6]. The detector is composed of Silicon Vertex Tracker (SVT), Time Projection Chamber (TPC), Trigger Barrel, ElectroMagnetic Calorimeter (EMC), Magnet and Coils. The SVT tracks the charged particles close to the interaction region. It should be precise sufficient to locate the primary interaction vertex and identify the secondary vertices. The large volume TPC also tracks the charged particles and identifies them with SVT using ionization energy loss. The Trigger Barrel acquires the data from multiple detectors. EMC measures the transverse energy of events and trigger on and measure high transverse momentum photons, electrons and electromagnetically decaying hadrons. The Magnet and Coils create a strong magnetic field in order to analyze the momentum of charged particles. The maximum value is about 0.5 T.

### 1.1.2 Silicon detector topologies

Full-custom detectors are required in the HEP experiments due to the extreme environment, which are usually composed of many layers. The vertex detector is the detector nearest to the collision point, which detects and records the position of the charged particles when they pass through. Almost all the physical results rely heavily on the performance of vertex detectors [7]. Since very high spatial resolution, high readout speed and low material budget are required by vertex detector, silicon detectors are usually used in the vertex detector. The charged particles can be detected by the silicon detectors due to the electron/hole pairs induced by them. The collision produces many particles in a very short period of time. Thus, the vertex detector works in a harsh radiation environment.

The silicon sensors that are most commonly used in vertex detectors are hybrid pixel detectors, microstrip detectors, charge coupled devices, Si drift detectors, pad detectors and CMOS pixel sensors. The hybrid pixel detectors, charge coupled devices and CMOS pixel sensors are introduced in detail in following sections.

Figure 1.7: The layout of STAR detector and the cutting view showing the inner detector [6].

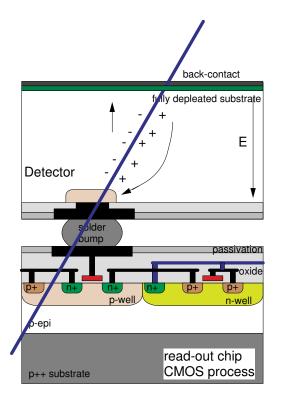

### 1.1.2.1 Hybrid pixel detectors

Hybrid pixel detectors are composed of two parts: the sensor chip and the readout chip, as shown in figure 1.8 [8]. The sensor detects the signal and transfers it to the readout chip. The sensor chip is built on the high-resistivity silicon substrate. Its active volume is fully depleted by applying an appropriate voltage to the back side. This structure can achieve high spatial resolution and good radiation hardness. The readout chip is usually based on the standard CMOS technology and they can be highly optimized to achieve high readout speed. Combining these two layers, the detectors can achieve attractive radiation hardness, spatial resolution and readout speed. Hybrid pixel detectors have been successfully employed in the pixel detectors for HEP experiments such as WA97, which is a heavy ion experiment to study Pb-Pb collisions at the CERN Omega spectrometer [9]. They are also currently used in ATLAS, ALICE and CMS for LHC experiments with the pixel size of 50  $\mu s \times 400 \ \mu s$ , 50  $\mu s \times 425 \ \mu s$ , 150  $\mu s \times 150 \ \mu s$ , respectively [10] [11] [12]. They are the promising candidates employed in the pixel detectors for HEP experiments owing to their excellent radiation hardness.

However, the hybrid pixel detectors have some disadvantages which limit their applications in HEP experiments. The bump-bonding flip-chip bonding techniques are usually used to connect the sensor chip and the readout chip [13] and each pixel cell of sensor has

Figure 1.8: The architecture of hybrid pixel sensor [8].

its own readout circuit. They are connected via the bump bond. The minimum pixel size is thus limited by the readout electronics and the bump size. The interconnection is also very complex. Moreover, the material budget is high due to the thickness of the sensor chip, bumps and the readout chip. Since large voltage is applied to the sensor, hybrid pixel detectors also suffer high power consumption.

#### 1.1.2.2 Charge coupled devices (CCD)

The charge coupled devices were invented in 1970 by Willard Boyle and George Smith at Bell Laboratories, USA [14] [15]. CCDs have found their applications in the cameras, scanners, cell phones and personal computers in the following years. Most of the imaging devices utilize CCDs as the visual light sensors. They are also used in the space imaging and in high energy physics experiments for tracking particles. As the vertex detectors of NA32 at CERN, the SPS and SLD are equipped with CCDs owning to their high spatial resolution and thin thickness.

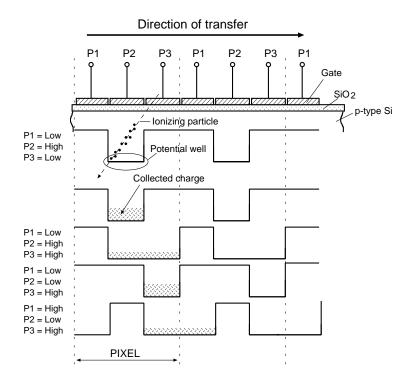

CCD is an array of MOS capacitors tightly covering on the substrate. A pixel is composed of three gates, as shown in figure 1.9. Only one gate voltage is high while the other two are low. Thus, a potential well forms. The charged particle induces electron/hole

Figure 1.9: Structure of CCD and the operation timing.

pairs in the depleted layer under the gate, when it traverses the device. Electrons are collected and stored in the potential well. Then the charges stored in one capacitor can be transferred in the channel of the adjacent device by a appropriate voltage consequence at their gate nodes. The signal is serially read out leading to relatively low readout speed. This will be worsened for a larger pixel array.

The main structures of CCD are the surface-channel and buried-channel. The buriedchannel is mostly used, which is not compatible with standard CMOS technology. The gate voltage to transfer the charge is usually high to 10 V. Thus, CCDs can not be integrated on the same substrate with readout circuitry.

Since the performances of CCDs depend on the perfect charge transferring, they are very sensitive to the radiation damage. This drawback limits their applications in the high energy physics experiments.

#### 1.1.2.3 CMOS pixel sensors or Monolithic active pixel sensors

In the early 1990s CMOS sensors were used in visual imaging such as the commercial cameras, video recorders and so on. They can be fabricated in the standard commercial CMOS technology. Thus the sensing elements and the readout circuitry can be integrated

Figure 1.10: Schematic cross-section of a CMOS pixel sensor [16].

on the same substrate. They decrease the cost and the chip area. They rapidly develop in the consumer electronics and they are predicted to replace CCD in the future. The CMOS pixel sensors (CPS) were firstly proposed to detect the charged particles in 1999 in IPHC - Strasbourg, France. They have been verified and proved by a series of prototypes called Minimum Ionizing particle MOS Active pixel sensors (MIMOSA) [17]. The test results demonstrated that they had promising features for charged particle tracking. The crosssection of a CMOS pixel sensor is shown in figure 1.10 [16]. Different with the standard substrate in VLSI technology, the substrate is highly doped as  $p^{++}$  and the lightly doped epitaxial layer is thicken. The photodiode is formed by the junction between the pepitaxial layer and the N-well. The electron/hole pairs are generated along the trajectory of the ionizing particle when it traverses the sensor. Recombination finishes very quickly in the substrate, so the particles in the p-epitaxial moves to the highly doped n-well. The current can be integrated by the revers-biased diodes through thermal diffusion during about 100 ns.

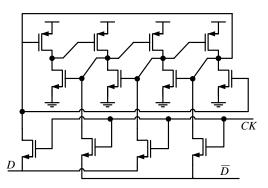

The structure of CPS is shown in figure 1.11. CPS are composed of a pixel array, column-level discriminator, bias DACs, power management/regulators, phase locked loop (PLL), zero suppression, memories, sequencer and sequencer controller. The pixel array takes the most of area in CPS. The pixel cell integrates the current induced by the ionizing particle and pre-amplifies the signal. The output analog voltage is digitalized by the discriminator, which is a comparator in fact. When the signal amplitude is higher

Figure 1.11: Structure of CPS chip.

than the threshold, the output is "1". It indicates that one particle may traverse this pixel. Its position can be reconstructed by dedicated algorithms in the following data analysis procedure. To improve the readout speed, the digitalization is parallel done in column level. The aim of zero suppression is to delete the information of the pixel not hit. Thus, the speed and power consumption is significantly decreased. The regulators generate the low-noise reference voltage and the power supply voltage on chip, which is the main work in these thesis. The bias DACs generate bias voltages for other blocks. Utilizing the JTAG interfaces, the bias voltage and current can be adapted to get the optimized value and make tests flexible. The PLL generates the reading clock. The sequencer and sequencer controller provide the correct timing in successive mode.

The comparison of CPS with CCD and hybrid pixel sensors is shown in Table 1.2. CPS can offer an attractive trade-off among the granularity, material budget, readout speed, radiation tolerance and power consumption. The material budget can be further decreased since the sensor chip can be thinned down to 50  $\mu m$ . The hardening by design (HBD) has improved the radiation tolerance in CMOS process. This technology can meet the requirements of most of the high energy physics experiments. Consequently, CPS is a good choice of the sensors used in vertex detectors.

| CPS and competitions | CPS | Hybrid pixel sensors | CCD |

|----------------------|-----|----------------------|-----|

| Granularity          | +   | -                    | +   |

| Material budget      | +   | -                    | +   |

| Readout speed        | +   | ++                   | -   |

| Radiation tolerance  | +   | ++                   | -   |

| Power consumption    | +   | -                    | +   |

Table 1.2: The performance comparisons of CPS with the competitions

#### **1.1.3** Power distribution challenges in the detectors

The independent powering is used in the recent detectors. Each electronics (sensor/readout circuit) is powered directly from power supply located remotely by its own cables. The length of the cables can be longer than dozens of meters. There maybe more than one cable for one electronics, e.g., the analog supply voltage, digital supply voltage and bias voltage. In order to decrease the material in the active volume, thinner cables are used. The resistance of the cables cannot be ignored. Moreover, the electronics requires high current while working. Much power is burnt by the cables due to the unwanted resistive heating  $I^2R_{cable}$ . This problem also influences the cooling system. The detectors will be equipped with more sensors in the future, which make the things worse. The independent powering has been proved failed for the future detectors [18]. The reasons are listed as follows:

- 1. Lack of space to place cables. The cables increase with the number of electronics. For example, the channels increase by a factor of 2-10 in the SLHC. Since the vertex detector is close to beam, the space is limited by the radius of the detector. Moreover, it is impossible to place all the cables in the detector if extreme low material budget is required.

- 2. Increase of the material budget. It is undoubted that the material budget increases when a large amount of cables are placed in the active material. However, the material budget is required low enough to decrease the multiple scattering, which impacts the momentum and the resolution of the low-momentum particles.

- 3. Low power efficiency. As mentioned above, the resistive heating significantly increases with the number of the cables. The cables consume higher than 50% of the total power, for example, the power efficiency of the Pixels detector for ATLAS in LHC is only 20%.

Consequently, power distribution becomes a large challenge in the detectors. The new schemes must be designed for the future detectors to decrease the number of the cables. Furthermore, any electronics in the power distribution must be able to work in the harsh radiation and magnetic environment due to close the interaction point.

### 1.2 Proposed work

This doctor work is one part of the development of CPS. The goal is to build a power management in the CPS. All the voltages required are generated on-chip. Therefore, the pad number is decreased as well as the cable number. The noise and power performances are also improved. Furthermore, the power distribution for CPS was analyzed and proposed. Two full-custom regulators, supplying clamping voltage and analog power supply voltage, were designed and verified. The strategies of the power management in CPS were also analyzed. The radiation tolerance technology was also researched.

The work proposed in this thesis focuses on the linear regulator design in the power management of CPS. These regulators are fully integrated on-chip. Any external elements are not allowed due to the limitation of the space on the ladder and the material budget. In the other hand, CPS will contain more pixels to improve the spatial resolution. The parasitic capacitance is very large, which is proportional to the size of pixel array. Thus, the stability of the regulators must be carefully designed. However, the topologies replying on the external compensation elements can not be applied in these two regulators. Since the signal induced by the charged particles is very weak, low noise is also required and the power supply rejection must be high. Moreover, the power consumption is limited by the cooling system and the detector requirements.

A novel compensation strategy was proposed to guarantee the stability. A series RC network was employed to introduce a zero. Moveover, the main poles and zeros were adaptable by the current feedback. It is easy to be realized. The compensation elements area were decreased, compared with the other schemes. Low extra current is required in this scheme.

A programmable resistance is employed in the feedback resistor network to compensate the process fluctuation and temperature variation. Its value can be adapted by the standard joint test action group (JTAG) interfaces.

## 1.3 Thesis overview

The power requirement of the CPS is firstly presented. As one part of the CPS design, this work dedicates to the power management. It is also helpful to the power distribution. This thesis is organized as follows:

In Chapter 2, CPS are introduced in detail, including their structure, the requirements of the HEP experiments and their power specifications. The power distribution topologies for CPS are proposed and discussed. This chapter also gives the power requirements of CPS, which must be fulfilled by the power management design. Moreover, the possible power management strategy for CPS is given in order to further decrease the power consumption.

In Chapter 3, the alternative power distributions are presented. As the conventional scheme, the independent powering has been demonstrated failed in the future detectors. Many works addressing this problem have been reported. The state art of the power distributions is presented. These approaches can be summarized as two fundamental approaches [18]: (1) Serial powering the sensors/readout circuits using a recycle current. (2) Parallel powering with local DC-DC conversion. The power is transmitted at high DC voltage and low current. Each topology is presented in detail. The advantages and disadvantages are summarized. According to the analysis, the power distribution for CPS is proposed.

Since the sensor chips work in high radiation environment, the radiation effects and radiation hardening techniques are presented in Chapter 4. The hardening by design (HBD) is focused on in order to achieve good radiation tolerance in standard CMOS process.

In Chapter 5, a linear regulator is proposed in the power management to provide the clamping voltage for correlated double sampling in CPS chip. The linear regulator is briefly introduced at the beginning. The regulator topologies are summarized then. The design specifications are presented according to the requirements of CPS. The load capacitor and load current are introduced in detail, since they influence the stability and noise performance. Circuit implementation is presented in detail. The simulation and experimental results are given to validate the design at last.

In Chapter 6, the other linear regulator named RegVdda is presented. It is utilized to supply power to the analog circuit. In order to guarantee the stability with the load current in a large range, a novel compensation strategy is proposed. The compensation capacitance is remarkably decreased. The simulation and measurement results are also given.

Finally, this thesis work is summarized and the perspectives are given.

## Bibliography

- [1] N. Mistry, "A brief introduction to particle physics," Laboratory for elementary particle physics, Cornell University, Tech. Rep.

- [2] B. Mueller, "The physics of the quark-gluon plasma," in *Lecture Notes in Physics, Berlin Springer Verlag*, ser. Lecture Notes in Physics, Berlin Springer Verlag, vol. 225, 1985.

- [3] A. Ranjan and V. Ravishankar, "Introduction to quark-gluon plasma," Indian J.Phys., vol. 84, no. 1, pp. 11–40, 2010.

- [4] M. Pimenta, "Experiments in high energy physics: A brief introduction," in *The Physical Universe: The Interface Between Cosmology, Astrophysics and Particle Physics*, ser. Lecture Notes in Physics, Berlin Springer Verlag, J. D. Barrow, A. B. Henriques, M. T. V. T. Lago, & M. S. Longair, Ed., vol. 383, 1991, pp. 275–280.

- [5] K. T. Pozniak, "Electronics and photonics for high-energy physics experiments," in *Proceedings of SPIE 5125*, vol. 91, 2003.

- [6] K. Ackermann and et al., "Star detector overview," Nuclear Instruments and Methods in Physics Research A, vol. 499, pp. 624–632, 2003.

- [7] P. Weilhammer, "Overview: silicon vertex detectors and trackers," Nuclear Instruments and Methods in Physics Research A, vol. 453, pp. 60–70, 2000.

- [8] M. Szelezniak, "Development of pixel detectors with integrated microcircuits for the vertex detector in the star experiment at the rhic collider," Ph.D. dissertation, University of Strasbourg, Feb. 2008.

- [9] G. D. Hallewell, "The present status of pixel detector development for high energy physics collider applications," Nuclear Instruments and Methods in Physics Research Section A: Accelerators, Spectrometers, Detectors and Associated Equipment, vol. 383, no. 1, pp. 44 – 54, 1996, development and Application of Semiconductor Tracking Detectors. [Online]. Available: http://www.sciencedirect.com/science/article/pii/S0168900296006201

- [10] G. Aad, E. Abat, J. Abdallah, and et al., "The ATLAS experiment at the CERN large hadron collider," *Journal of Instrumentation*, vol. 3, p. S08003, Auguest 2008.

- [11] K. Aamodt, A. A. Quintana, and R. Achenbach, "The ALICE experiment at the CERN LHC," *Journal of Instrumentation*, vol. 3, p. S08002, Auguest 2008.

- [12] S. Chatrchyan, G. Hmayakyan, V. Khachatryan, and et al., "The CMS experiment at the CERN LHC," *Journal of Instrumentation*, vol. 3, p. S08004, Auguest 2008.

- [13] H. Chen, K. Liang, Q. Zeng, X. Li, Z. Chen, Y. Du, and R. Wu, "Flip-chip bonded hybrid CMOS/SEED optoelectronic smart pixels," *Optoelectronics, IEE Proceedings* -, vol. 147, no. 1, pp. 2–6, feb 2000.

- [14] W. S. Boyle and G. E. Smith, "Charge coupled semiconductor devices," Bell System Technical Journal, vol. 49, p. 587, 1970.

- [15] Sharma, "A look at CCD sensors..." in What Digital Camera Magazine, November 1997, pp. 54–56.

- [16] R. Turchetta and et al., "CMOS monolithic active pixel sensors (MAPS): Developments and future outlook," *Nuclear Instruments and Methods in Physics Research A*, vol. 582, pp. 866–870, 2007.

- [17] IPHC, Tech. Rep. [Online]. Available: http://www.iphc.cnrs.fr/ Pictures-of-Mimosa-chips.html

- [18] M. Weber, "Power distribution for SLHC trackers: Challenges and solutions," Nuclear Instruments and Methods in Physics Research Section A: Accelerators, Spectrometers, Detectors and Associated Equipment, vol. 592, no. 1-2, pp. 44 – 55, 2008. [Online]. Available: http://www.sciencedirect.com/science/article/pii/S016890020800483X

## Chapter 2

## CMOS pixel sensors

CMOS pixel sensors are also called monolithic pixel sensors (MAPS), since they integrate the sensing element and the readout circuitry on the same substrate. They are fabricated by standard process and can be thinned down to 50  $\mu m$ . Thus, low cost and low material budget are achieved. CPS are not only widely used in visual imagining but also are good choices to track the charged particles in HEP experiments. This chapter will introduce CPS in detail. At first, the structure of CPS is presented. Each block in CPS is introduced. Secondly, the power requirements of the high energy physics experiments are discussed. Finally, the power specifications of CPS are given.

## 2.1 CPS structure

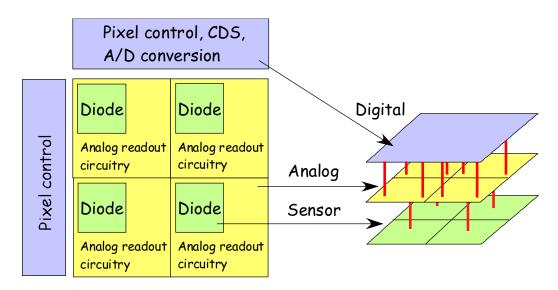

CPS have developed fast in the past a few years. A series of prototypes called MIMOSA (Minimum Ionizing particle MOS Active pixel sensor) has been designed and measured in Institut Pluridisciplinaire Hubert Curien (IPHC), Strasbourg, France, since 1999 [1]. The measurements have demonstrated that CPS is a promising candidate for charged particle tracking and it can be also used in biology imaging [2]. Charge collection efficiency was the main driving force in the first years. Different technologies were tested in order to find a proper process for CPS fabrication. The radiation tolerance was also analyzed. In recent years, the driving force comes from the physics domain. CPS chips usually are full-customer to fulfill the requirements of different detectors. The design effort is developing the chip architecture and fast column-parallel readout. The recent structure is significantly different with the previous chips. For example, the output is analogue signal in MIMOSA 1-21 from 2001 to 2006. The output is digital and correlated double sampling (CDS) operation is complemented in latter CPS chips. As shown in figure 2.1, CPS are

Figure 2.1: Structure of current CPS chip.

composed of pixel array, row sequencers, column-level discriminators, zero-suppression, bias DAC, power management/regulators and joint test action group (JTAG) in their recent versions. The function of each block is listed as follows:

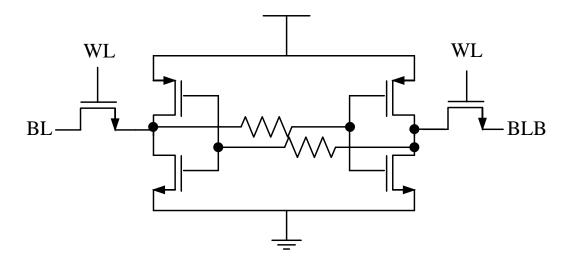

• Pixel array: sensing and pre-amplifying the signal induced by the charged particles. Unlike the simple three-transistor pixel used in visual imagining, pixel used for HEP experiments is more complex. It consists more transistors, as shown in figure 2.2. One pixel is composed of sensing element, pre-amplifier, a correlated double sampling (CDS) circuitry, source follower and so on. The sensing element, which is implemented by Psub-Nwell diode, collects electrons. Thus, the voltage at the diode decreases when the particle hits this pixel or one nearby. The pitch of the diode is decided by the charge collection efficiency and the equivalent noise charge (ENC). Obviously, large diode can improve charge collection. However, the ENC is increased since large diode increases the input node capacitance. For a typical pixel size of 30  $\mu m \times 30 \ \mu m$ , the optimum diode size was found to be approximately 15  $\mu m^2$ . Pixel with multiple charge collecting diodes (up to four diodes per pixel) is also tested. It is demonstrated failed due to introducing very large input node capacitance [3]. As a consequence, only one diode is usually used in recent pixel.

The self-biased structure (SB) takes the place of simple reset due to simplifying the pixel architecture and eliminating the pedestal inherent to pixel operation [4].

Figure 2.2: Simplified pixel topology [1].