# Réseaux d'interconnexion flexible pour architecture reconfigurable dynamiquement

Ludovic Devaux

#### ▶ To cite this version:

Ludovic Devaux. Réseaux d'interconnexion flexible pour architecture reconfigurable dynamiquement. Traitement du signal et de l'image [eess.SP]. Université Rennes 1, 2011. Français. NNT: 2011REN1E005. tel-00746290

## HAL Id: tel-00746290 https://theses.hal.science/tel-00746290

Submitted on 28 Oct 2012

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

$N^o$  d'ordre : 2011REN1E005

### THÈSE / UNIVERSITÉ DE RENNES 1

sous le sceau de l'Université Européenne de Bretagne

### pour le grade de DOCTEUR DE L'UNIVERSITÉ DE RENNES 1

Mention : Traitement du signal et télécommunications

Ecole doctorale MATISSE

présentée par

### Ludovic Devaux

préparée à l'unité de recherche (6074 IRISA UMR) (Institut de Recherche en Informatique et Systèmes Aléatoires)

Flexible interconnection networks for dynamically reconfigurable architectures

Thèse soutenue à Lannion le 24 novembre 2011

devant le jury composé de :

M. Frederic Pétrot

Professeur, ENSIMAG / président

M. Fernando Moraes

Professeur, PUCRS / rapporteur

M. Jean-philippe Diguet

Directeur de recherche CNRS, UBS / rapporteur

M. Fabrice Muller

Maître de conférence, UNS / examinateur

M. Daniel Chillet

Maître de conférence, ENSSAT / examinateur

M. Didier Demingy

Professeur, IUT Lannion / directeur de thèse

M. Sébastien Pillement

Maître de conférence

IUT Lannion / co-directeur de thèse

**Abstract**: Dynamic and partial reconfiguration allows to dynamically allocate the tasks constituting an application in the reconfigurable regions of an FPGA. However, dynamic management of the tasks directly impacts the communications since tasks are not always implemented at the same place in the FPGA. So, the communication architecture must support high flexibility and significant qualities of service (guaranteed bandwidth and/or latency).

In this PhD, several interconnection architectures were studied and evaluated regarding their compliance with a dynamically reconfigurable system implemented in FPGA. This study led to the proposal of the DRAFT network that fully supports this concept. This network uses some specificities of the dynamically reconfigurable systems to reduce its hardware resources consumption. Furthermore, if several constraints are verified, the performances are not influenced by the dynamic allocation of the tasks. A network generator, DRAGOON, is also presented in order to implement and simulate the DRAFT network.

Following the realization and characterization of this network which was compared with two very popular networks, its integration inside a system was studied. Consequently, a standard interface was designed in order to ease the interconnection of elements such as microprocessors. Considering the degree of complexity of the hardware parts of a reconfigurable system, an OS is often used to act as an abstraction layer. So, a service allowing to realize communications between the various elements of a system while providing a complete abstraction of the DRAFT network was designed in hardware.

Considering the various constraints on the use of DRAFT, the OCEAN network was proposed. This network allows a simple interconnection of the elements constituting a system with great flexibility. For this purpose, the OCEAN network is based on two sub-networks, one being dedicated to data transfers, while the other ensures its control. OCEAN network lies on dynamically created communication paths following applicative requirements. This network particularly targets ASIC implementations

All these networks were validated and characterized through experiments and implementations in FPGA. Results demonstrate the adequacy between proposed networks and the actual needs, also with the support of complex applications using dynamic reconfiguration. The OCEAN network even proposes an evolution toward future dynamic architectures.

**Keywords:** network-on-chip - FPGA - dynamic reconfiguration - flexible - ASIC

**Résumé :** La reconfiguration dynamique partielle permet de placer dynamiquement les tâches d'une application dans des zones reconfigurables d'un FPGA. Cependant, la gestion dynamique des tâches impacte les communications du fait que les tâches ne sont pas toujours allouées au même endroit dans le FPGA. Ainsi, l'architecture d'interconnexions doit supporter une grande flexibilité et un large éventail de qualité de service (bande passante ou latence garantie).

Dans cette thèse, plusieurs architectures d'interconnexion ont été étudiées et évaluées en fonction de leur compatibilité avec un système reconfigurable dynamiquement implémenté sur FPGA. Cette étude a conduit à proposer le réseau DRAFT qui supporte pleinement ce concept. Ce réseau utilise certaines spécificités des systèmes reconfigurables dynamiquement actuels pour réduire sa consommation de ressources. De plus, si certaines contraintes sont vérifiées, les performances ne sont pas affectées par l'allocation dynamique des tâches. Un générateur de réseaux, DRAGOON, est aussi présenté afin d'implémenter et de simuler le réseau DRAFT.

Suivant la réalisation et la caractérisation du réseau DRAFT qui a été comparé à deux réseaux très populaires, son intégration au sein d'un système a été étudiée. C'est ainsi qu'une interface standard a été développée afin de faciliter l'interconnexion d'éléments tels que des processeurs. Etant donné le degré de complexité des parties matérielles d'un système reconfigurable, un OS est souvent utilisé pour en permettre l'abstraction. Ainsi, un service de communication permettant de réaliser des échanges entre les différents éléments d'un système tout en ayant une abstraction totale du réseau DRAFT a été conçu matériellement.

Considérant les différentes contraintes liées à l'utilisation de DRAFT, le réseau OCEAN a été proposé. Ce réseau permet une simplification de l'interconnexion des éléments d'un système avec une très grande souplesse d'utilisation. Ce réseau est pour cela basé sur deux sous- réseaux, l'un étant dédié au transport des données tandis que l'autre en assure le contrôle. Le réseau OCEAN repose sur des chemins de communication créés dynamiquement en fonctions des besoins. Ce réseau dynamique vise plutôt une cible ASIC.

L'ensemble des réseaux proposés ont été validés et caractérisés au travers d'expériences et d'implantations sur FPGA. Les résultats montrent une adéquation avec les besoins actuels, et le support efficace de la dynamicité des applications complexes. Le réseau OCEAN propose même une évolution pour de futures architectures dynamique.

Mots-clés: réseau sur puce - FPGA - reconfiguration dynamique - flexible - ASIC

## **Summary**

| In                          | trodu                                     | ction                           |                                | 1  |  |  |

|-----------------------------|-------------------------------------------|---------------------------------|--------------------------------|----|--|--|

| 1                           | Stat                                      | State of the art - Definitions  |                                |    |  |  |

|                             | 1.1                                       | Dynar                           | mic Reconfiguration            | 12 |  |  |

|                             |                                           | 1.1.1                           | General definition             | 12 |  |  |

|                             |                                           | 1.1.2                           | Xilinx partial reconfiguration | 13 |  |  |

|                             | 1.2                                       | Defini                          | tions                          | 18 |  |  |

|                             |                                           | 1.2.1                           | Communication architecture     | 18 |  |  |

|                             |                                           | 1.2.2                           | NoC parameters                 | 19 |  |  |

|                             |                                           | 1.2.3                           | Network performances           | 23 |  |  |

|                             | 1.3                                       | Interc                          | onnection architectures        | 25 |  |  |

|                             |                                           | 1.3.1                           | Bus based interconnections     | 26 |  |  |

|                             |                                           | 1.3.2                           | Static NoCs                    | 28 |  |  |

|                             |                                           | 1.3.3                           | Flexible NoCs                  | 38 |  |  |

|                             | 1.4                                       | Synth                           | esis of the chapter            | 39 |  |  |

| 2                           | The                                       | DRAF1                           | Γ network                      | 41 |  |  |

|                             | 2.1                                       | Object                          | tives and motivations          | 42 |  |  |

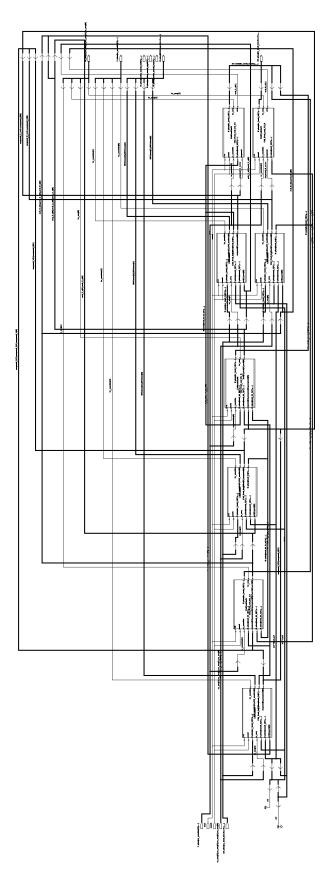

|                             | 2.2                                       | 2 Topology of the DRAFT network |                                |    |  |  |

|                             | <ul><li>2.3 Router architecture</li></ul> |                                 |                                |    |  |  |

|                             |                                           |                                 |                                |    |  |  |

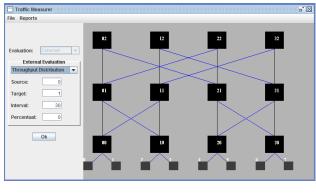

| 2.5 The DRAGOON environment |                                           | RAGOON environment              | 58                             |    |  |  |

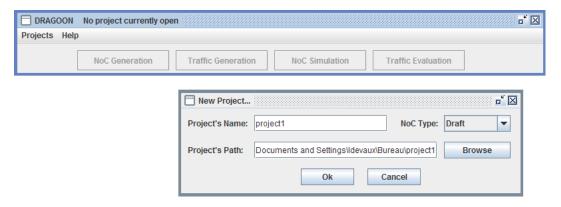

|                             |                                           | 2.5.1                           | DRAGOON main interface         | 59 |  |  |

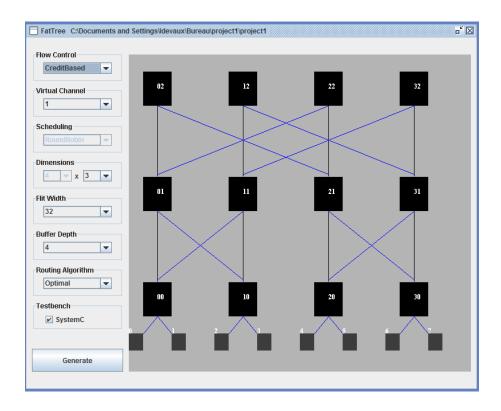

|                             |                                           | 2.5.2                           | The NoC generator              | 60 |  |  |

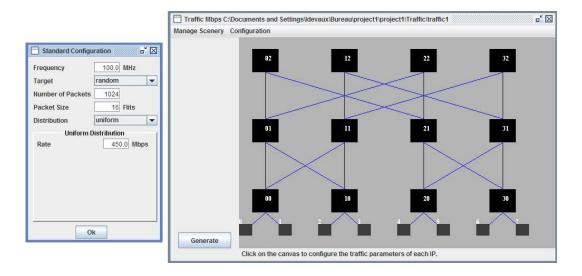

|                             |                                           | 2.5.3                           | The traffic generator          | 62 |  |  |

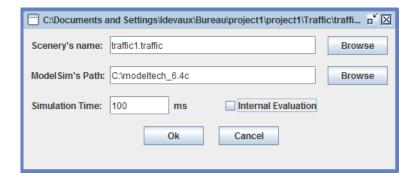

|                             |                                           | 2.5.4                           | The NoC simulator              | 63 |  |  |

|                             |                                           | 2.5.5                           | The traffic evaluator          | 63 |  |  |

|                             | 2.6                                       | DRAFT                           | Cimplementation advices        | 64 |  |  |

vi Summary

|   | 2.7  | DRAFT                             | integration: interface DRAFT/AHB        | 67  |

|---|------|-----------------------------------|-----------------------------------------|-----|

|   | 2.8  | DRAFT                             | communication service                   | 70  |

|   | 2.9  | Synthe                            | esis of the chapter                     | 75  |

| 3 | Towa | ard nev                           | w flexible NoCs                         | 77  |

|   | 3.1  | Objecti                           | ives and motivations                    | 78  |

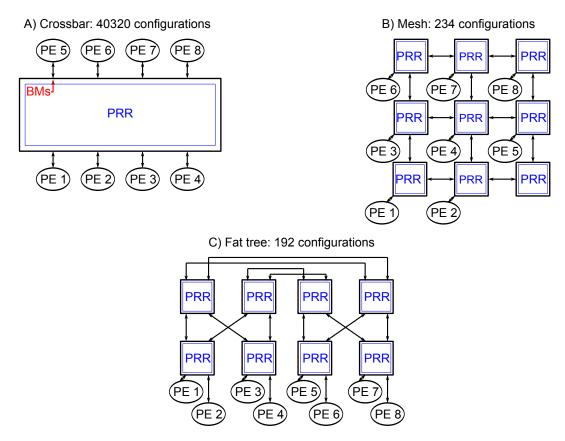

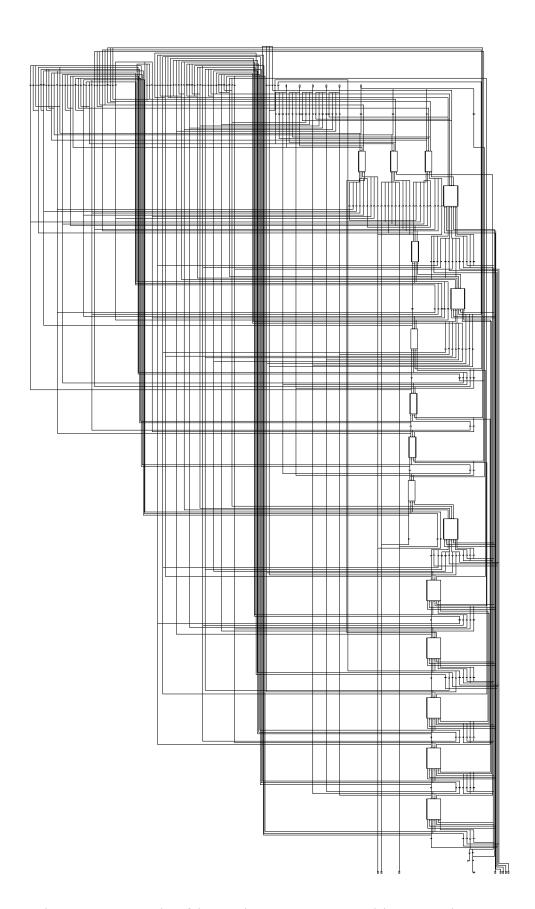

|   | 3.2  | Topolog                           | gy of the R2NoC network                 | 79  |

|   | 3.3  | R2NoC                             | switch architecture                     | 82  |

|   | 3.4  | R2NoC                             | Routing and Flow Control                | 83  |

|   | 3.5  | Constra                           | aints of the R2NoC network              | 86  |

|   | 3.6  | Motiva                            | tions for the OCEAN network             | 87  |

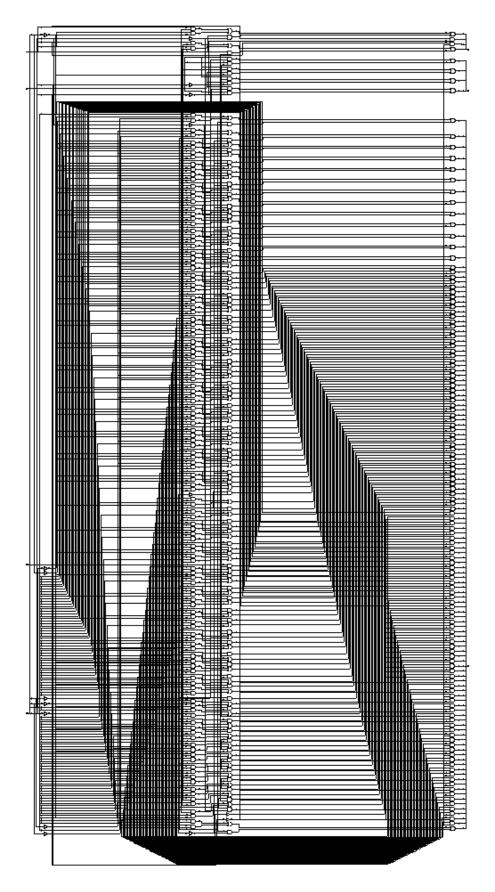

|   | 3.7  | Topolog                           | gy of the OCEAN networks                | 89  |

|   | 3.8  | The da                            | ta network                              | 90  |

|   |      | 3.8.1                             | Communication principles and interfaces | 90  |

|   |      | 3.8.2                             | Data switches                           | 90  |

|   |      | 3.8.3                             | Discussions over the data network       | 93  |

|   | 3.9  | The co                            | ntrol network                           | 94  |

|   |      | 3.9.1                             | Operation principles and interfaces     | 94  |

|   |      | 3.9.2                             | OCEAN Routing algorithm                 | 96  |

|   |      | 3.9.3                             | Control switches                        | 99  |

|   | 3.10 | Variatio                          | ons of the OCEAN network                | 102 |

|   |      | 3.10.1                            | OCEAN v4.0                              | 103 |

|   |      | 3.10.2                            | OCEAN v3.1 and v4.1                     | 104 |

|   | 3.11 | Discus                            | sions concerning the OCEAN networks     | 107 |

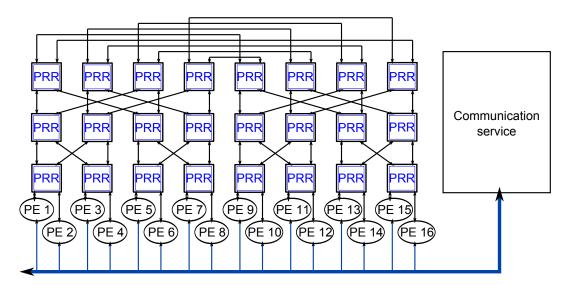

|   | 3.12 | OCEAN                             | I test platform                         | 108 |

|   | 3.13 | Synthe                            | esis of the chapter                     | 112 |

| 4 | Resu | ılts and                          | d comparisons                           | 115 |

|   | 4.1  | Objecti                           | ives                                    | 116 |

|   | 4.2  | Experir                           | mental conditions                       | 117 |

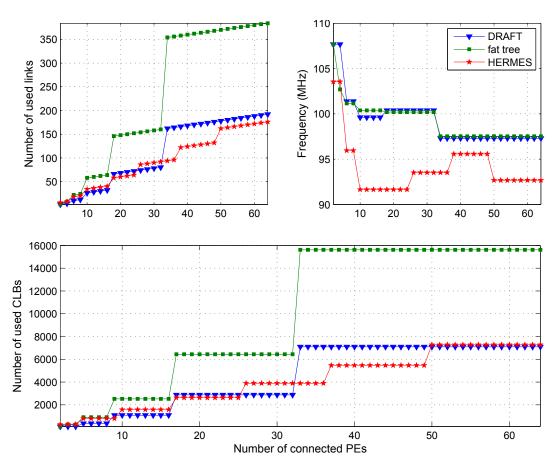

|   | 4.3  | DRAFT performances and comparison |                                         | 120 |

|   |      | 4.3.1                             | Hardware resources consumptions         | 120 |

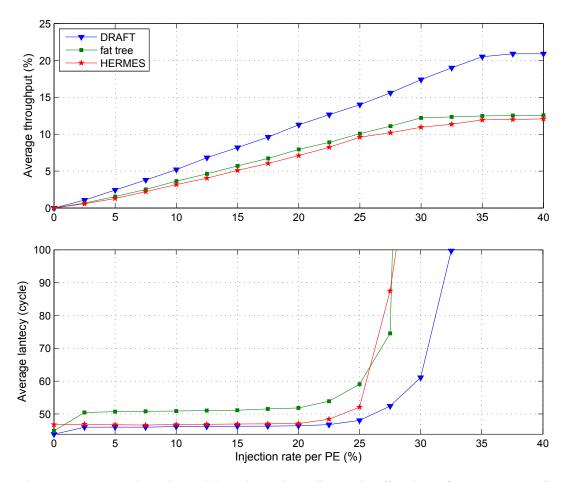

|   |      | 4.3.2                             | Network performances                    | 121 |

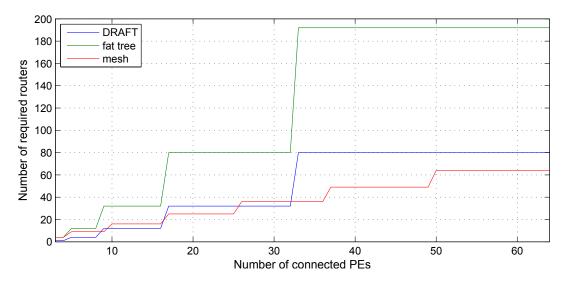

|   |      | 4.3.3                             | The scalability                         | 123 |

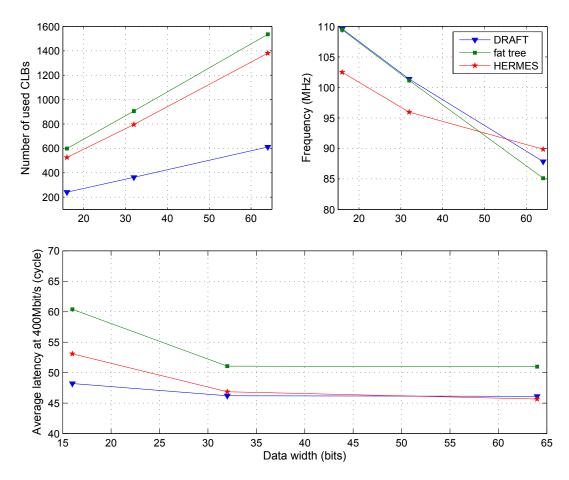

|   |      | 4.3.4                             | The data width                          | 124 |

Summary

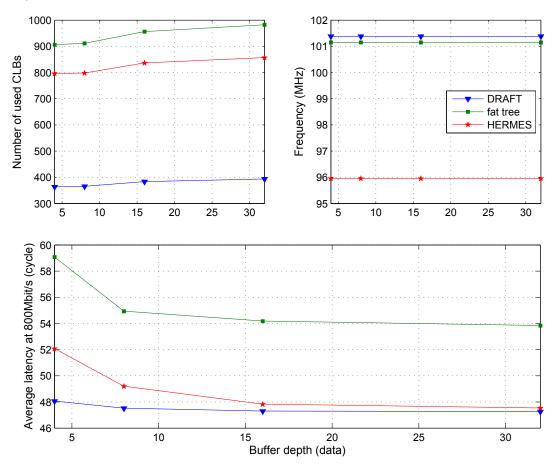

|     |                               | 4.3.5   | Buffer depth                           | 126 |  |

|-----|-------------------------------|---------|----------------------------------------|-----|--|

|     |                               | 4.3.6   | Types of data traffics                 | 127 |  |

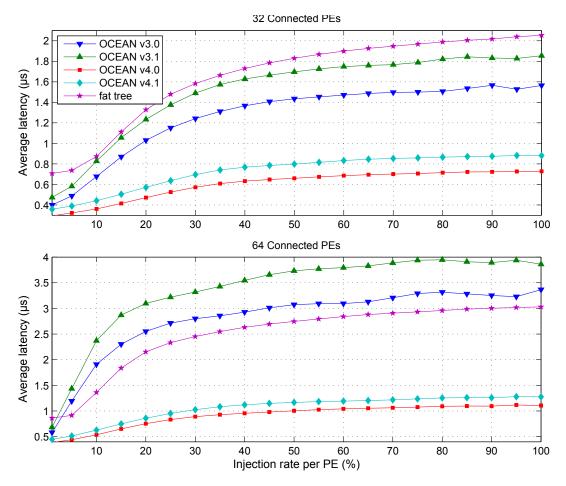

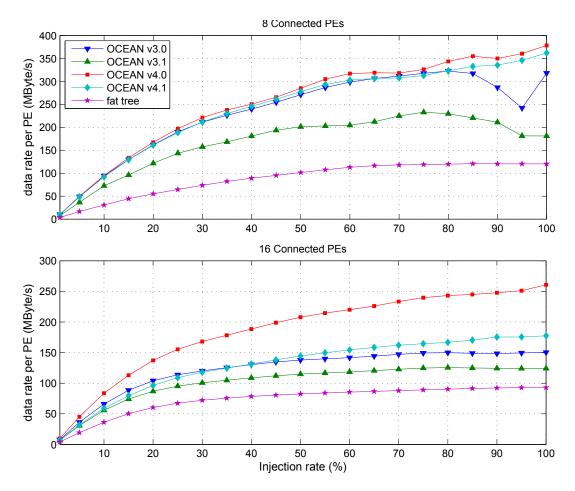

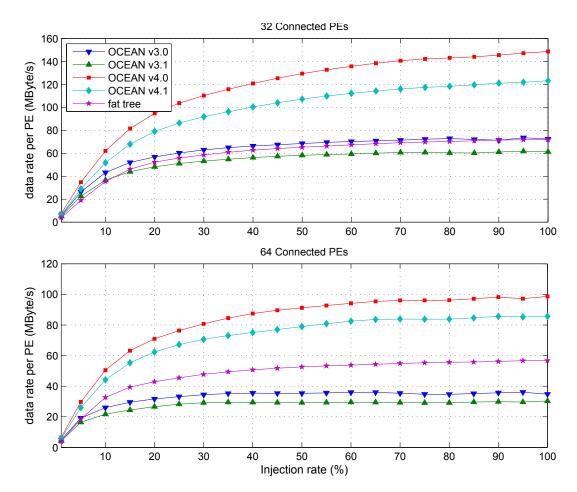

|     | 4.4                           | Ocean   | performances and comparison            | 128 |  |

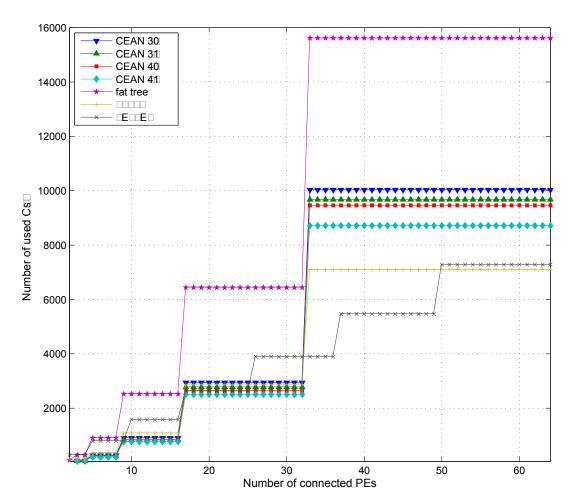

|     |                               | 4.4.1   | Hardware resources consumption         | 128 |  |

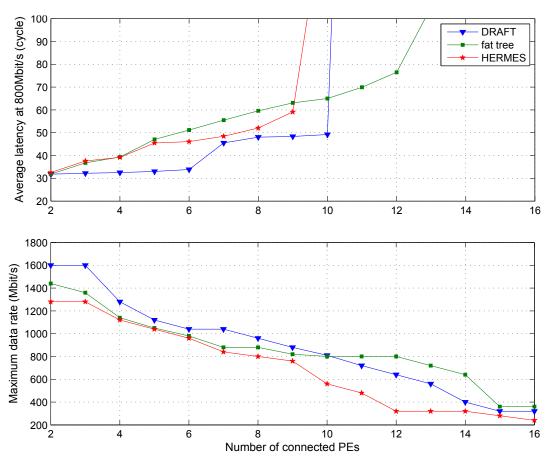

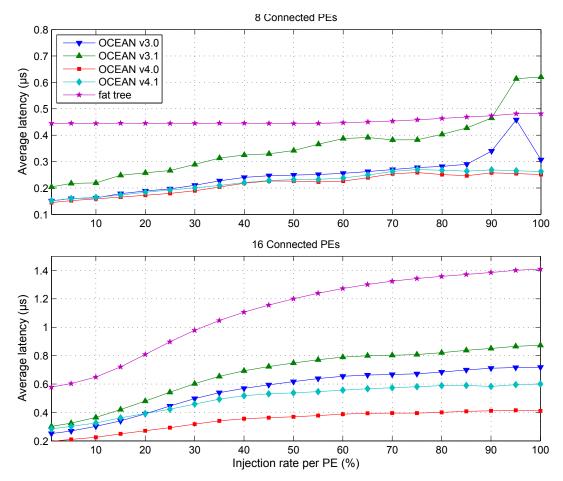

|     |                               | 4.4.2   | Network performances                   | 130 |  |

|     |                               | 4.4.3   | FPGA validation                        | 136 |  |

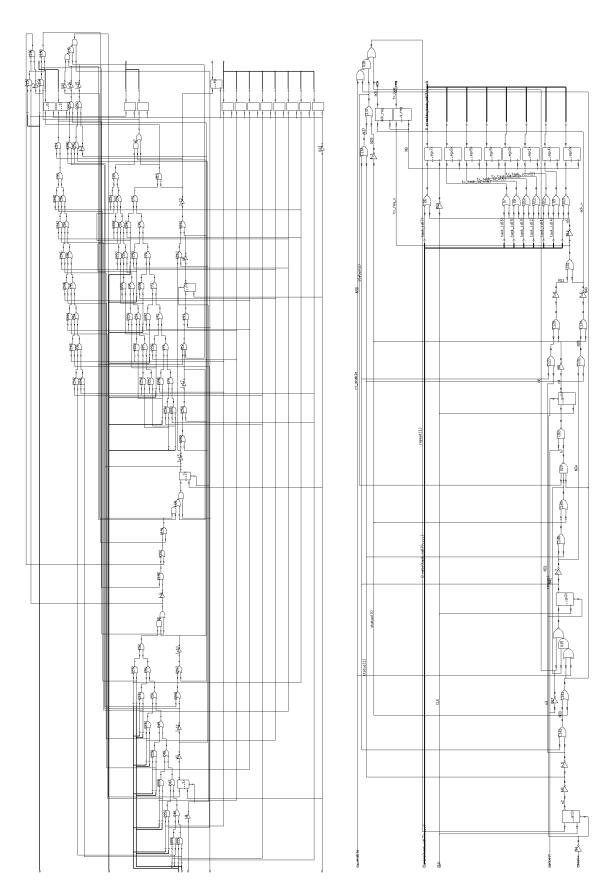

|     |                               | 4.4.4   | ASIC implementation                    | 137 |  |

|     | 4.5                           | Synthe  | sis of the chapter                     | 139 |  |

| Co  | Conclusion and perspectives   |         |                                        |     |  |

| Bib | Bibliographic references      |         |                                        |     |  |

| Pe  | Personal publications         |         |                                        |     |  |

| Ар  | Appendix                      |         |                                        |     |  |

| A   | Simulation files from DRAGOON |         |                                        | 165 |  |

| В   | In si                         | tu char | acterization platform                  | 169 |  |

|     | B.1                           | Need o  | f an In-Situ characterization platform | 169 |  |

| С   | R2N                           | oC mea  | sured performances                     | 173 |  |

| D   | ASIC                          | imple   | mentation of OCEAN                     | 177 |  |

## **Abbreviations and Acronyms**

**AHB** Advanced High-performance Bus

AMBA Advanced Microcontroller Bus Architecture

API Application Programming Interface

ASIC Application-Specific Integrated Circuit

BM Bus Macro

CAD Computer Assisted Design

**CLB** Configurable Logical Block

CMOS Complementary Metal Oxide Semiconductor

**DCM** Digital Clock Manager

**DMA** Direct Memory Access

**DPR** Dynamic and Partial Reconfiguration

**DRAFT** Dynamic Reconfiguration Adapted Fat-Tree

**DRAGOON** Dynamically Reconfigurable Architectures compliant Generator and simulatOr Of Network

**DSP** Digital Signal Processor

FIFO First In First Out

FOSFOR Flexible Operating System FOr Reconfigurable devices

FPGA Field Programmable Gate Array

FSM Finite State Machine

GALS Globally Asynchronous Locally Synchronous

ICAP Internal Configuration Access Port

IO Input Output

IP Intellectual Property

$\mathbf{LUT}$  Look Up Table

**NI** Network Interface

NoC Network-on-Chip

**OCEAN** On-Chip Efficiently Adaptive Network

**OPB** On-chip Peripheral Bus

**OS** Operating System

**PE** Processing element

**PLB** Processor Local Bus

PRR Partially Reconfigurable Region

**QoS** Quality of Service

R2NoC Reconfigurable Routers based Network-on-Chip

RAM Random Access Memory

**RSoC** Reconfigurable System-on-Chip

${f RTL}$  Register Transfer Level

SoC System-on-Chip

**UART** Universal Asynchronous Receiver Transmitter

VC Virtual Chanel

VHDL VHSIC Hardware Description Language

VHSIC Very-High-Speed Integrated Circuits

VLSI Very Large Scale Integration

Since the very beginning of electronics in 1904, (year of "electronic tube" invention, the ancestor of the transistor), the complexity of electronic systems never ended increasing. Over the years, more and more powerful systems were created. Indeed, this computing power, which can be expressed as the number of operations per time unit, continuously increases along with the needs of our modern society. This research of more computing power led to the miniaturization process. The objective is simple, since the speed of an electron is constant in a metal wire or in a transistor, miniaturization reduces their length so that the electrons reach more rapidly their destinations. So, each operation to be realized takes less and less time in a smaller and smaller electronic system. It is then possible to realize more operations in the same time unit. The fact that electronic systems are now ubiquitous in our life is a direct consequence of this research of computing performances.

A digital electronic system is always composed of the same sets of elements. First are the computing elements that can be processors running user defined software algorithms, or blocks performing all the processing of some incoming data in hardware. If the function computed by latter blocks can be modified, they are called reconfigurable. The second set concerns the storage capacities. Indeed, every application requiring an electronic system embeds computing elements that process data. Consequently these data should be memorized in order for the processing elements to pick them up before processing, and then to store results. Finally, the last set concerns the communication. In every system, a communication medium is required to make the interconnection of the computing element(s) and the storage one(s). Furthermore, interfaces are also necessary in order for the system to take information (data) from their environment. These interfaces are often considered as computing elements providing data by the communication architecture. For convenience purpose, every interconnected element, either processors, computing blocks, memories, and communication interfaces are denominated as Processing Elements (PEs) since they participate to the processing of the overall application. First digital electronic systems were composed of one PE per chip. However, following the miniaturization process, chips have started to embed all the elements required to run the application.

Thus, a single circuit can now embed one or several processors, computing blocks, memories, communication architectures and interfaces. Communications were usually realized through metal wires. This is the definition of a System-on-Chip (SoC).

There are several ways to implement a SoC. The first one consists in designing the system directly in silicon. The resulting chip is then dedicated to the originally aimed application even if an embedded microprocessor can bring a certain flexibility: software codes can evolve in the time. This implementation way, called Application-Specific Integrated Circuit (ASIC) guarantees high performances but no flexibility in the sense that no change can happen to the hardware architecture of the application. The second way to implement a SoC consists in configuring a general purpose architecture. The principle is simple: the architecture embeds logical resources that can be configured to realize a function in hardware. Using these configurable resources and the interconnection wires between them, it is possible to produce the behaviour of all the elements constituting a SoC. At the cost of a loss in performances, the flexibility is thus increased. Some chips like the Programmable Array Logics (PALs) are one time programmable, they are usually used as chips performing a permanent function but at a lower cost than ASICs. Indeed, they do not embed sufficient programmable resources to implement a complete application. Most of SoCs are implemented using reconfigurable chips called Field Programmable Gate Arrays (FPGAs). FPGAs have the particularity that embedded hardware resources are programmed at boot time. So, depending on the configuration that is applied to the FPGA at the power-up, different applications can be implemented on the same chip. This leads to the definition of a Reconfigurable System-on-Chip (RSoC).

Originally FPGAs were mostly used to prototype ASIC implementations. However, their reconfiguration ability leads them to be used inside industrial finite products. Reconfiguration of a chip is a key feature of present and future systems. Indeed, when an application requires a wide range of performances that can only be attained through hardware implementation, the reconfiguration takes all its sense. The reconfiguration is particularly useful at design time in order to reduce the financial and temporal costs to verify the proper behaviour of the system: one or several reconfigurable chips are used. PEs can then be configured inside these chips and reconfigured if an unexpected behaviour is detected. If chips were not reconfigurable, then each time an error is detected a new chip would be designed. With a reconfigurable circuit, the new PE is configured instead of the previous faulty one, thus saving both time and money. If originally reconfigurable circuits were used for design assistance purpose, they have demonstrated their interest in real life applications. Indeed they allow the system to evolve in the time. Thanks to the reconfiguration, PEs can be updated without any human direct intervention on the system, and furthermore without changing any physical element (board, chip, etc.). Completely

changing the behaviour of a system in order to re-use its components, providing a better Quality of Service (QoS) reconfiguring a PE for fault tolerance purpose are also key functionalities that are allowed thanks to the reconfiguration ability of the chips.

Originally, the reconfiguration of a chip requires halting the execution of the whole chip in order to configure every one of their logical elements. This is called the static or total reconfiguration. This is the case for most of current and past FPGAs. However, steady technological, scientific, commercial, financial, and finally human evolutions lead desired application to become more and more complex every day. This complexity attains such a level that required hardware resources to support these applications overcome the capacity of present chips. More and more, single chips are not powerful enough to handle present applications. This is why several technological ways are explored. Facing the problem of the resources limitations, three main paths are followed by both researchers and industrials:

- the conception and design of larger and larger chips embedding more and more configurable resources,

- the use of several chips in parallel allowing to multiply the actions that can be realized at a time,

- and the dynamic reconfiguration ability of the circuits.

The conception of larger and larger chips leads to more and more complex designs. Designs become then both hard to debug and to maintain. This leads to the proposal of new Computer Assisted Design (CAD) tools in order to ease both the conception and the maintenance of complex applications. However, the use of several chips is based on the parallelism of the applications. Indeed, following the observation that usually applications are composed of several functions, it is possible to improve performances processing these functions at the same time while using several chips of reduced size. However, new mechanisms are required to guarantee a valid behaviour of the application while exploiting as much as possible the parallelism. Thus, both an Operating System (OS) and CAD tools are required in order to give to the designer an abstraction of the physical components and their operation that steadily becomes more complex.

A new feature appeared recently in the world of FPGAs. This is the Dynamic and Partial Reconfiguration (DPR). Originally motivated by the constant increase of SoCs' complexity, the DPR of an FPGA consists in the possibility to reconfigure not only the whole chip at boot time, but only a part of embedded logical resources during the execution of the application. If previously more and more complex applications required larger and larger SoCs (and thus chips), the DPR offers the possibility to

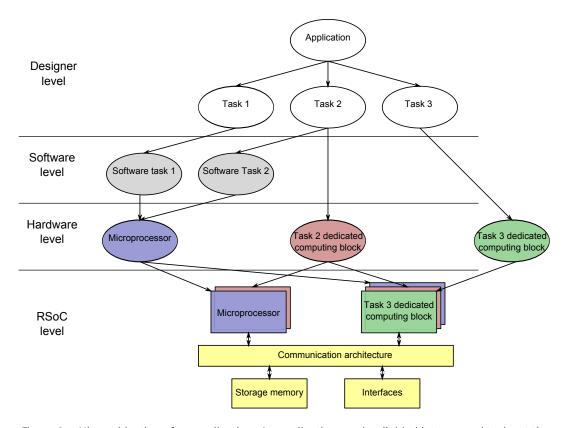

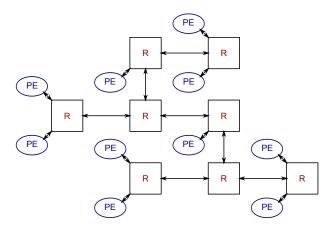

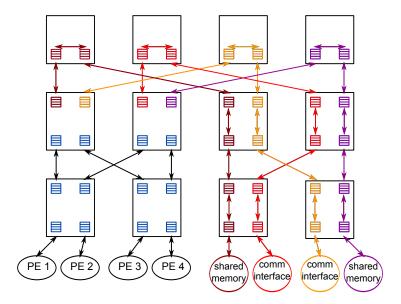

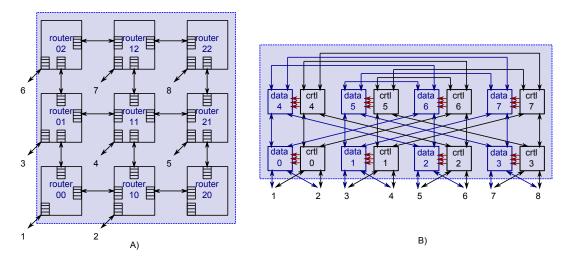

sequentialize the applications. Indeed, every application can be divided into several tasks. These tasks can be processed either in software (running on a hardware processor), or directly in hardware using a computing block. As illustrated in Figure 1, storage elements, communication interfaces and an interconnection architecture may also be required for the whole RSoC to operate properly. However, if the size of the RSoC is too limited to implement the microprocessor and the two computing blocks at a time, the DPR offers the possibility to swap a hardware element by another one. Obviously, the DPR is efficient only if all the tasks do not need to be executed simultaneously. In this example, all logical resources that are used by both the microprocessor and the computing block dedicated to the task 3 can be dynamically allocated at a different time to a different computing block: the one dedicated to the task 2.

Figure 1: Hierarchization of an application. An application can be divided into several tasks at the designer level. Some tasks can then be implemented in software, or directly in hardware. Software implemented tasks are processed on a hardware processor while hardware implemented ones lead to dedicated computing blocks. All these hardware elements are allocated inside a RSoC along with storage and communication elements. The resources are shared in the time.

The DPR allows reducing the size of the RSoCs, and thus their complexity. However, this concept of dynamic hardware implementation of the tasks has a significant

impact over both the design and the functioning of a SoC. Indeed, the allocation of hardware components of an application needs now to be scheduled, and their placement must be controlled. Furthermore, it also impacts the communication architecture. From the communication architecture point of view, every interconnected element has specific communication requirements in terms of amount of data that must be transferred, and of maximum time allowed to transfer these data. In SoCs, it was possible to design a communication architecture optimally considering the communication requirements inherent to each PE. However, due to the DPR, PEs can be exchanged by others with different communication needs. Furthermore the same PE is not guaranteed to be always located at the same place in the RSoC. Indeed there is no obstacle for a PE to be relocated at a new place depending on the applicative context. All of this avoids any possibility for the resulting data traffic or the communication infrastructure to be predicted at design time.

If computing elements perform all the operations and make all the decisions, most of present digital systems are limited by their interconnection [33]. Until the late 1990s, the traditional way of interconnecting PEs such as computing blocks, microprocessors and memories was to use dedicated links to minimize latencies or shared buses for simplicity. With subsequent increases in number of interconnected PEs on a single chip along with the length and delay of wires to cross a chip, it has become important to share on-Chip interconnect bandwidth in a more structured way. This leads to the notion of Networks-on-Chip (NoCs). Since then, numerous NoCs have been proposed but the introduction of the DPR in RSoCs reveals a lack of flexibility for lot of them. Communication architectures thus become a major problem when designing RSoCs. This is why the research work presented in this report proposes new flexible interconnection architectures. This work took place into the scope of a PhD financed by the Agence Nationale de la Recherche (ANR) through the Flexible Operating System FOr Reconfigurable devices (FOSFOR) project.

### **Applicative context**

#### **DPR compliant FPGAs**

The three main FPGA manufacturers are Xilinx, Altera and Atmel. There are also small societies that take advantage of niche markets like Achronix. Achronix provides asynchronous FPGAs where resources are distributed in small tiles working in pipelined fashion [1]. However, only a small range of FPGAs are currently available and the support of the DPR is not foreseen in their business plan. Atmel devices propose large varieties of FPGAs with a regular intrinsic structure [14]. However, when compared with Altera and Xilinx devices, the number of reconfigurable resources

is too limited to handle the implementation of large and complex applications. At present time, Xilinx is the market leader concerning FPGAs. Xilinx is at the origin of the first FPGAs supporting DPR: the XC6200. However, DPR is only supported by Xilinx software tools since the ISE 9.1 and ISE 9.2 design suits [73] targeting the Virtex II Pro FPGA. Even though, DPR could only be realized through early access add-ons to these software tools. Much more series of dynamically reconfigurable devices were proposed by Xilinx through the Virtex IV, V, VI, and the most recent one VII [116], [117], [125], [123]. The first versions of ISE have evolved and now the versions 12 and 13 offer the DPR ability to every designer without any add-on (at the cost of the appropriate license) [122], [124]. Furthermore, the PlanAhead software that is part of the ISE/EDK suit [121] offers interesting possibilities to designers to control which PE should be dynamically reconfigurable.

From the beginning Xilinx has felt the interest of the DPR and invested a lot of time, money, and manpower to offer viable devices to industrials and academics. Since the DPR becomes a real market with growing interests and earnings, Altera recently announced their first FPGAs supporting DPR [36]. In Stratix IV series, only the input/outputs were already dynamically reconfigurable [8]. The programmable resources inside the FPGA were not dynamically reconfigurable [9]. This is not the case for the Stratix V series that is announced by Altera. Every programmable resource is dynamically reconfigurable, just like Xilinx FPGAs [10]. The use of the DPR is proposed to designers through the well known Quartus II design suit [10] on the same model as for Xilinx ISE/EDK recent versions. Altera recently published an article presenting the interest of systems using DPR in order to reconfigure the hardware architecture without rebooting the OS, even if it runs on an on-chip processor [62]. It is particularly interesting to notice that Altera's vision of applications using DPR is very similar to Xilinx's.

At the beginning of this PhD, only Xilinx devices were compliant with DPR. This is why in this report, only Xilinx architectures are considered.

#### The FOSFOR project

The FOSFOR project aims to reconsiderate the structure of an OS which is usually software, centralized, and static. The OS proposed by the FOSFOR project should be flexible and distributed even if proposing an homogeneous interface from the application point of view. For this purpose, the DPR ability of modern FPGA should be applied to complex RSoCs and completely supported by the FOSFOR OS. In these complex RSoCs, tasks can be either statically or dynamically implemented, and even allocated in software or hardware. The FOSFOR project proposes mechanisms of virtualization of the various services constituting an OS. This way, through

these services, applicative tasks can be processed and can communicate without any knowledge about their implementation (software or hardware) nor about their location. More precisely, the FOSFOR project considers three fundamental services of an OS: the scheduling and placement of the tasks, the communication and the memory management. More than expected theoretical results, the FOSFOR project aims to demonstrate the viability of presented concepts through a demonstrator. This demonstrator is a hardware platform representative from future embedded applications [38].

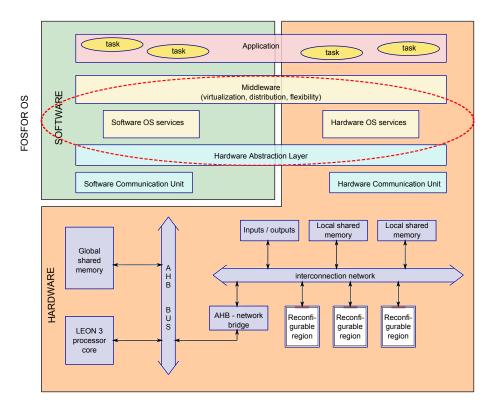

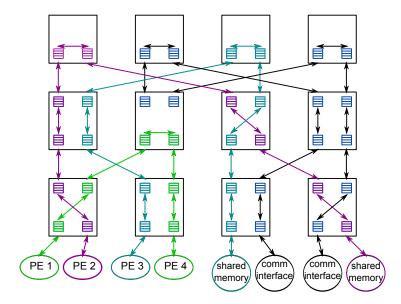

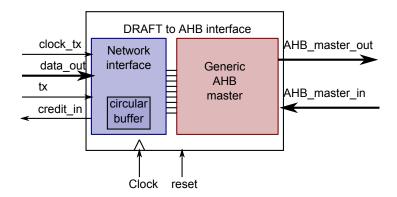

Figure 2: Presentation of the FOSFOR environment. Constituted of two parts (software and hardware), the FOSFOR OS provides an abstraction of these two parts to the application. The services of the OS are distributed both in software and in hardware. Through an hardware abstraction layer and control interfaces, the OS manages the hardware platform. This platform consists in a LEON 3 processor core, a shared memory connected to the processor through an AHB bus, and reconfigurable regions interconnected by a network. PEs corresponding to hardware tasks are dynamically implemented in the reconfigurable regions.

The FOSFOR environment presented in Figure 2 is constituted of the FOSFOR OS whose services are distributed both in hardware and software. Through the specific block called middleware, the OS is able to make the relation between its various services and to provide a uniformized interface to the application. Through the middleware, the application is executed without any knowledge of where the tasks are

implemented (software or hardware). Through the hardware abstraction layer, the OS manages the execution of the tasks allocating them on the LEON 3 processor (if software) or inside the reconfigurable regions. Allocated tasks always have the possibility to communicate together through the AHB bus and the interconnection network. They can also communicate with the FOSFOR OS through software command units (if allocated on the LEON 3 processor), or the hardware one (if allocated in a reconfigurable region).

#### Objectives and contributions of this work

The contribution of this PhD, lies in the proposal of an innovative interconnection architecture. The proposed network should be compliant with the DPR paradigm while being flexible supporting heterogeneous environments (software and hardware implemented tasks). Furthermore, since it could be integrated in the FOSFOR platform, this network should be able to efficiently interconnect the various PEs of the FOSFOR demonstrator. The demonstrator is only representative from future applications, this is why the proposed network should be as scalable as possible. Finally, the integration of proposed interconnection architecture should be eased providing a network with standardized interfaces.

However, the research works that took place during this PhD do not aim only in providing a communication architecture to the FOSFOR project. Much more contributions are expected. So, the second contribution should be to ease the use of the proposed interconnection network through a dedicated generation and characterization environment. This environment should provide to the designers an easy way to parameterize and generate the network. Furthermore, using this environment, the designer should easily receive estimations of the performances that are expected to be obtained from chosen configuration.

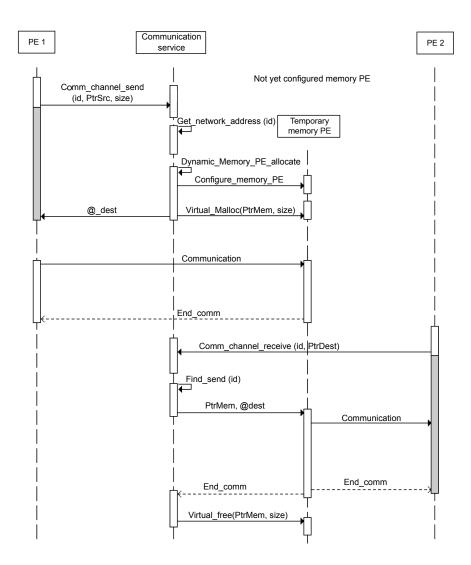

In order to ease the use of proposed interconnection network, an efficient communication manager is proposed. This manager should give to the tasks that wish to communicate an abstraction of the hardware components. Through this manager that acts as an OS communication service, tasks should be able to communicate in an heterogeneous platform without taking care about if they are statically or dynamically allocated, and even software or hardware implemented. Their location inside the platform should not even be known by the tasks. the challenge with this communication service is then to make communicate the same way hardware and software tasks. Furthermore, the communication service should provide efficient mechanisms in order to take into account communication cases that can be induced by the DPR ability of the RSoC. For example, the communication service should provide answers to improve the communications when a task requests to send data to a non-allocated

one. Even if proposed outside of the scope of the FOSFOR project, it would be interesting for this communication service to be compliant with the FOSFOR OS.

Finally, considering the lack of flexibility of present interconnection networks, along with their limited scalability, the other main contribution of this PhD is to propose a NoC with very high network performances. This network should present a reduced cost in order to be scalable enough to fit future large scale applications. Furthermore, along with high bandwidth and low latency, this network should be flexible enough to support the DPR of PEs with a significant increase in QoS. Finally, since the need of performances is not reserved only to RSoCs, this network must be fully compliant with future flexible ASIC implementations.

#### Organization of the report

This report is organized in four chapters. Chapter 1 provides an overview of current dynamically reconfigurable architectures. FPGAs supporting DPR are presented along with the available design flows. Furthermore, the advantages and drawbacks of the DPR are also explained in this chapter. Then, before presenting some of the existing interconnection architectures, definitions are stated concerning every aspect of the conception and characterization of an interconnection architecture. Using these definitions also with the constraints induced by the DPR, existing interconnection architecture are detailed and discussed.

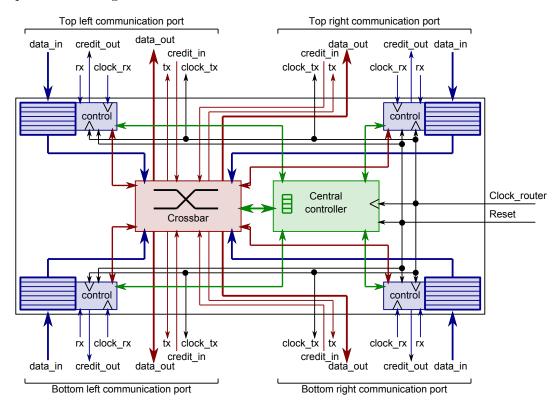

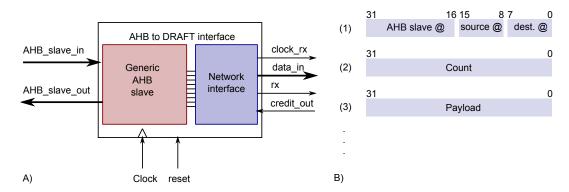

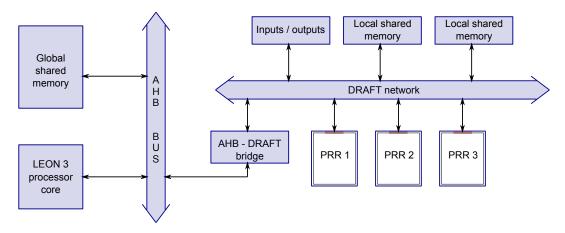

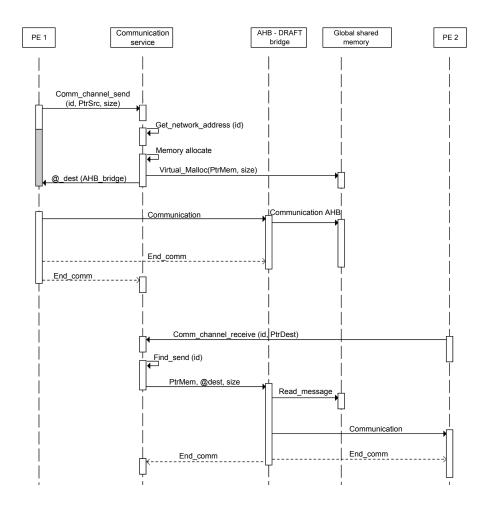

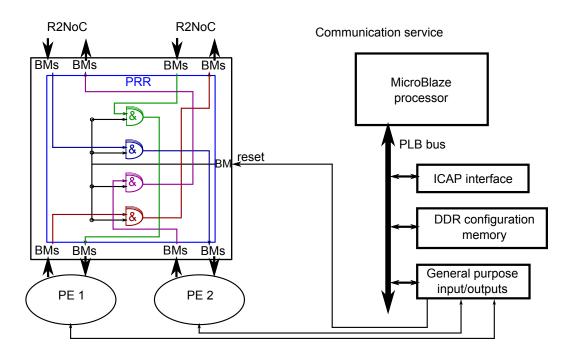

In Chapter 2, the DRAFT Network-on-Chip designed for the FOSFOR project is presented. Using both the constraints of the DPR and previously presented NoCs, the particular topology of the DRAFT network is investigated. Next, the various tools to make easier the use of DRAFT are detailed. Indeed, first is presented the DRAGOON environment that allows to parameterize, generate, and simulate networks. Then, a bridge making the relation between DRAFT and an AHB bus is detailed. This bridge is particularly useful providing a standardized and largely used interface. This allows for example the integration of DRAFT inside the FOSFOR demonstrator. Finally, a communication service acting as an overlayer to the DRAFT network is proposed. This communication service provides efficient mechanisms to manage communications in heterogeneous applications (hardware and software) using DPR.

In Chapter 3, the R2NoC and OCEAN networks are presented. R2NoC is an innovative NoC that uses the DPR ability of the FPGAs to provide high level performances with a reduced cost. Constraints and technological drawbacks of R2NoC are presented in this chapter. This leads to the definition of the OCEAN network which is a high performances, scalable, flexible, and easy to use NoC. This network auto-reconfigures its structure to provide maximum bandwidth and minimum laten-

cies to the communications. As presented in this chapter, OCEAN aims both DPR compliant FPGAs and future flexible ASIC implementations. In order to evaluate the performances of OCEAN, a simulation environment is detailed.

In Chapter 4, characterizations of the proposed networks are presented. Experimental conditions are first detailed. Next, DRAFT and OCEAN characterizations are provided. All these networks are compared with existing and popular networks that we characterized in exactly the same conditions. Finally, ASIC implementation results of the OCEAN network are presented.

Finally, the last chapter concludes this work and proposes further researches.

## **Chapter 1**

## **State of the art - Definitions**

| 1.1 | Dynan  | Dynamic Reconfiguration        |    |  |  |  |

|-----|--------|--------------------------------|----|--|--|--|

|     | 1.1.1  | General definition             | 12 |  |  |  |

|     | 1.1.2  | Xilinx partial reconfiguration | 13 |  |  |  |

| 1.2 | Defini | tions                          | 18 |  |  |  |

|     | 1.2.1  | Communication architecture     | 18 |  |  |  |

|     | 1.2.2  | NoC parameters                 | 19 |  |  |  |

|     | 1.2.3  | Network performances           | 23 |  |  |  |

| 1.3 | Interc | onnection architectures        | 25 |  |  |  |

|     | 1.3.1  | Bus based interconnections     | 26 |  |  |  |

|     | 1.3.2  | Static NoCs                    | 28 |  |  |  |

|     | 1.3.3  | Flexible NoCs                  | 38 |  |  |  |

| 1.4 | Synth  | esis of the chapter            | 39 |  |  |  |

This chapter aims to give an overview of modern dynamically reconfigurable architectures. Both reconfigurable devices and reconfiguration techniques are presented. Following this presentation, a terminology is proposed in order to define every parameter influencing the conception of an interconnection architecture. Characterization metrics are also defined. Following these definitions, most popular interconnection architectures are presented and confronted to the dynamic reconfiguration paradigm.

#### 1.1 Dynamic Reconfiguration

#### 1.1.1 General definition

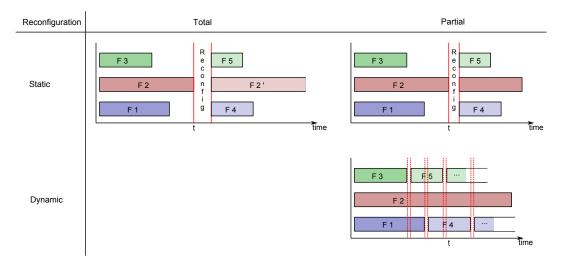

The dynamic reconfiguration consists in the possibility to change only one part of the chip while the other parts continue their execution. This is also called the DPR. This reconfiguration is based on the observation that in most applications, several functions do not need to be executed at the same time. This leads to a temporal partition of the application. Following this temporal partition, the idea is then to configure in the chip only the functions that need to be executed. At the end of their execution, they can be removed, freeing resources to dynamically configure another function. DPR significantly reduces the number of required hardware resources, and thus the size of the chips. The difference between the various reconfiguration types are presented in Figure 1.1.

Figure 1.1: Presentation of the various reconfiguration types. Two short functions F1 and F3 are reconfigured respectively by functions F4 and F5. The reconfiguration occurs at last at the instant "t". A longer function F2 is configured and needs more than "t" to complete its execution.

In the static and total reconfiguration, at reconfiguration times all functions are

halted and removed. The reconfiguration delay is quite long because the entire chip is reconfigured. The function F2 is un-allocated and reconfigured (equivalent to a reset) in instance F2'. If specific mechanisms were not foreseen, the execution of F2' starts from the beginning and all actions performed by F2 are lost. The static partial reconfiguration provides significant improvements compared with the total one. Since it is a static reconfiguration all functions are halted at the reconfiguration time, but only the functions that need to be reconfigured are un-allocated. This way, the reconfiguration time is shorter: only the needed resources are reconfigured. At the end of the reconfiguration process, F2 can resume its execution. The dynamic total reconfiguration does not make sense since every function is reconfigured. It is then similar to the static total reconfiguration. Finally, the dynamic partial reconfiguration lead for the functions that finished their execution to be reconfigured at once without disturbing the execution of the others. The reconfiguration process is shorter than for other reconfiguration types since only the needed functions are reconfigured at a time and longer functions are not halted. Thus DPR allow to best use the temporal partition of the application limiting the delays for reconfiguration purpose while ensuring that other functions are not impacted at all.

First industrial and academic applications using DPR were presented since 2001 [20], [49]. However, only the proposal of first chips proposing a DPR ability could demonstrate the viability of these applications since 2005 [82]. In latter article, issues were presented in order for the DPR to be more and more interesting for both industrials and academics. Issues were notably the creation of design flows supporting the DPR, larger scale FPGAs, and more FPGA vendors providing this functionality. Furthermore complex applications requiring DPR already exist like the real time video processing [28] and also automotive applications that are now part of our daily life [19].

#### 1.1.2 Xilinx partial reconfiguration

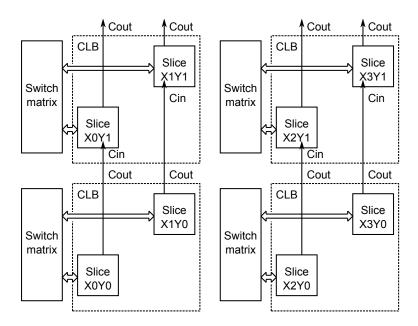

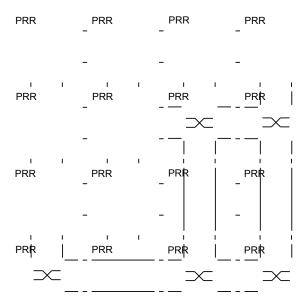

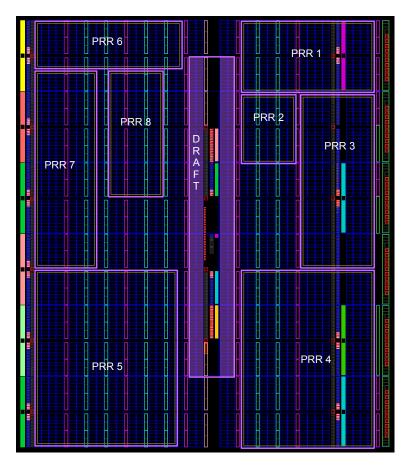

Xilinx DPR occurs in specific regions called Partially Reconfigurable regions (PRRs) [26]. These regions are statically defined before place and route phase of the implementation. Partial reconfiguration can only occur inside these regions, thus distinguishing the dynamic parts from the static ones of the FPGA. Inside a PRR, every Configurable Logical Block (CLB) is dynamically reconfigurable, thus forming the smallest reconfigurable zones. As presented in Figure 1.2, these blocks are constituted of two regions so called slices. CLBs are arranged in column, allowing embedded slices to communicate with directly upper neighbours or with other parts of the chip through the switch matrices.

In Xilinx Virtex V series, each slice is constituted of four 6-inputs Look Up Tables

Figure 1.2: Diagram of the resources embedded in Xilinx FPGAs. CLBs, composed of two slices, are the smallest reconfigurable entities. CLBs are arranged in column: each slice can communicate with upper neighbour one. Switch matrices allow the communication between a CLB and other resources (CLBs, input/outputs, etc.) located in different regions of the chip.

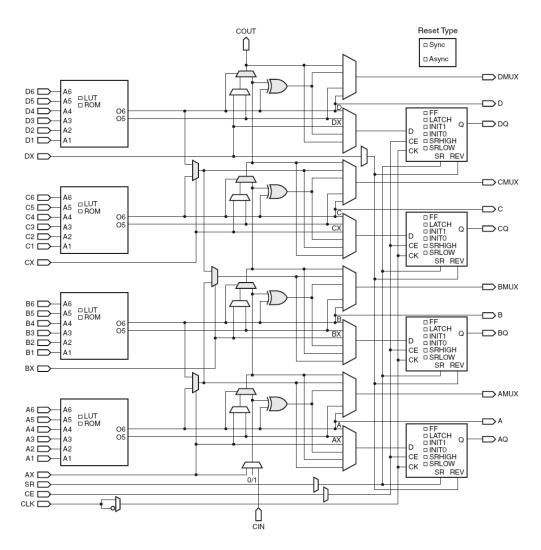

(LUTs) that are generators of logic-functions, four registers (called FF), multiplexers, and combinatorial logics. The diagram from a single slice is presented in Figure 1.3. Some LUTs support extra functions: storing data using distributed Random Access Memory (RAM), or shifting data with 32 bits registers [118].

During the DPR process, the function implemented inside the LUTs, the data in registers, the connexion of the multiplexers, and the switch matrix of a CLB are all reconfigured. A PRR can embed specific resources like RAM blocks (BRAMs) allowing 36 Kbits data storage each, and DSP blocks that are specific signal processing oriented units. This allows users to implement dynamically a complete PE using all required resources. The configuration of a PRR is realized through a bit file called partial bitstream. In order to reconfigure a PRR, a partial bitstream is loaded inside a specific interface called Internal Configuration Access Port (ICAP) [117]. Partial bitstreams are generated at compile time for every PRR regarding every possible configuration they can take. This way, each partial bitstream configures a whole PRR. This means that it is not possible to dynamically reconfigure only a part of a PRR, the whole PRR is reconfigured. However, if a resource has the same configuration in the novel configuration as in the previous one, then it is not affected by the reconfiguration process. This means that no glitch can occur, thus disrupting its behaviour [73].

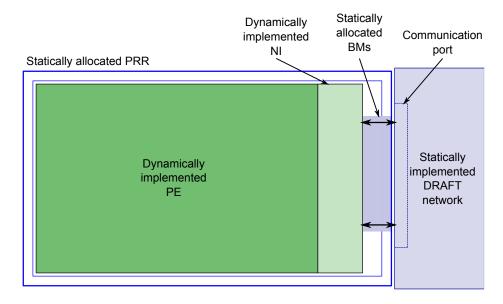

The communication between resources embedded inside a PRR and those from

Figure 1.3: Diagram of a single slice composed of four LUTs (LUT/ROM boxes of the left side), four registers (FF boxes of the right side), multiplexers and combinatorial logics. This diagram is issued from [118].

the static defined part of the FPGA are realized through interfaces called Bus Macros (BMs). BMs are statically defined inside the PRRs. Each BM acts as a bridge between dynamic and static parts of the FPGA. A single BM is implemented using a full slice [115].

Using Xilinx ICAP interface through the genuine controller provided by Xilinx usually leads to long reconfiguration delays. Indeed reconfiguration times from the decade to several hundreds of milliseconds are commonly encountered depending on the size of the PRRs. As an example, the dynamic reconfiguration of a PRR requiring a bitstream of 22KB takes 11.3ms. However, for many applications with hard real time constraints, such delays are not acceptable. This is why several

works proposed optimized ICAP controllers leading to reconfiguration delays from the decade to several hundreds of microseconds [72], [35]. With such rapid ICAP controllers, expected reconfiguration times are between 50-60 $\mu$ s for a 22KB partial bitstream. However, such rapid ICAP controllers can only be implemented at the cost of a massive BRAM usage. Obviously, dynamically reconfiguring a PRR using Xilinx genuine ICAP controller is much faster than reconfiguring statically the whole FPGA.

Along with researches leaded in order to improve the dynamic reconfiguration process, there are many studies aiming to better control this process. Indeed, usually the DPR of a PRR is initiated by a software code running on an on-chip implemented processor like a MicroBlaze or a powerPC [92]. However, some researches aim to improve this DPR initiation through an object oriented control running along with an OS like linux [45] or OS4RS [75], [88].

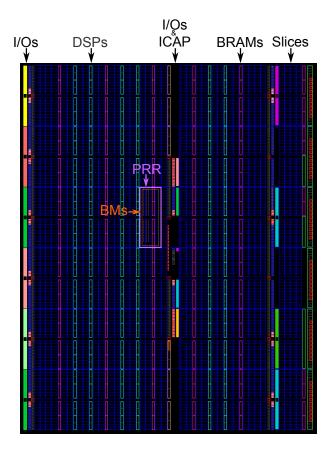

Many works like [18] take advantage of the new possibilities that are, or should be, offered by the DPR. This way, placement of the PEs and of the PRRs is a key research topic. Virtex II pro FPGAs were only compliant with 1D placement of the PRRs [57]. This means that when reconfiguring a PRR, the whole column was impacted. Consequently it was not possible to place two PRRs in the same columns of resources. Presently, the 2D placement of the PRRs is fully supported. This means that PRRs are defined as rectangular arrays that can be placed everywhere in the FPGA matrix. Several PRRs can thus be placed in the same column of resources. Concerning PEs, like PRRs they can be placed in 2D in the FPGA. When a PE is dynamically implemented in a PRR, concerning the overall application, it leads to the 3D placement where the third coordinate is the time [17]. Due to their column based repartition of the resources, Xilinx FPGAs are not homogeneous in 2D, thus constraining the placement of the PEs. For example, the organization of a Xilinx FPGA also with placement of a PRR are depicted in Figure 1.4. Indeed, PEs are then implemented as arrays that can be swapped depending on the moment they are scheduled to be executed [105]. The online placement of the PEs in the PRRs was investigated through several studies like [4] [5]. As a result of these works, a high flexibility is provided to the applications because the initial placement of the PEs can evolve depending on the applicative context. However, the flexibility concerning the placement of the PEs directly impacts the communication architecture since it must support this dynamic adaptation of the overall architecture.

The DPR proposed by Xilinx presents several advantages and constraints. The first constraint lies in the number of PRRs that can be reconfigured at a time. Starting from the Virtex V series, Xilinx DPR compliant FPGAs embed two ICAP ports. However they can not operate at the same time. Partial bitstreams can be forwarded to the ICAP controllers in parallel, but the effective reconfigurations will

Figure 1.4: Internal structure of a Xilinx Virtex V FPGA. Resources are distributed in columns. Resources (slices and BRAMs) included inside the defined PRR can be dynamically and partially reconfigured.

happen sequentially. So, two PRRs can not be reconfigured in parallel, but the presence of a second ICAP interface allows to save time considering the transfers of the partial bitstreams [117].

In every Xilinx Virtex FPGAs, partial bitstream are encrypted. Indeed, analyzing the bitstreams would give information on involved resources starting from their configuration bits as well as the implemented functions. However, this indispensable industrial protection is also a major constraint for researchers because it is not possible to generate online a partial bitstream. Since bitstreams are encrypted, and since FPGAs are not homogeneous in 2D, a small change between two configurations can not be realized in situ: both configurations are to be generated at compile time and stored in memory. Thus, this industrial protection has a dramatic effect regarding the number of partial bitstreams to generate and then to store in complex applications. Until the Virtex IV series, the addresses of the PRRs could be read at the beginning of the partial bitstreams. This way, the addresses of a given partial bitstream could be modified, and then the partial bitstream could be applied on

another PRR. This leads to the relocation of a PE. This is why basic PEs relocation and defragmentation could be realized [30]. Relocation were also realized using Xilinx more mature devices (XCV200) [42]. However, since the Virtex V series, Xilinx encrypted not only the payload of the partial bitstreams but also the addresses. This way addresses can not be modified and any relocation/defragmentation approach is thus impossible.

#### 1.2 Definitions

Sometimes in literature, researchers do not employ the same vocabulary. When characterizing a PE or a communication architecture, the definition that lies behind the performance metrics vary also quite often. This is why in this Section, all the needed parameters in the conception of a communication architecture and all metrics required for its complete characterization are defined. Definitions are issued from both [33] and [46] that are reference publications in the domain of the communication architectures. Obviously, all stated definitions are carefully respected in the remaining of this report.

#### 1.2.1 Communication architecture

A digital system is composed of three basic building blocks: logic, memory, and communication. Logic transforms and combines data, for example performing an arithmetic operation or making decisions. Memory stores data for later retrieval. Communication moves data from one location to another. The communication medium linking the various logic and memory blocks, along with its dedicated control, is called communication architecture. For a SoC, there are two main types of communication architectures: the buses and the Networks-on-Chip (NoCs). In this report, Processing Elements (PEs) are composed of both the logic and the memory blocks since they both participate to the processing of the data.

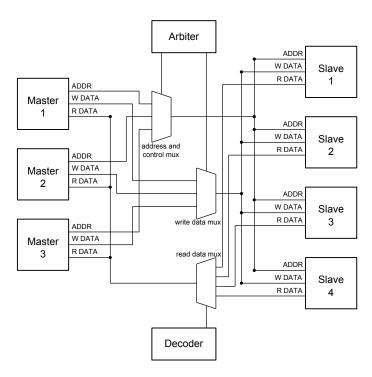

#### Bus

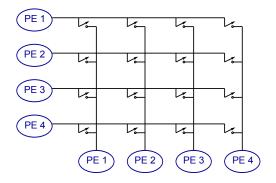

Communication architecture where interconnected elements (PEs) share a unique medium of communication. Buses were historically composed of a set of parallel wires with multiple connections. A bus is usually composed of data and address wires. Every PE requiring to communicate must reserve the bus. When no other PE uses the bus, data can be transmitted on the data wires while asserting the proper destination address on the corresponding wires. Every connected PE accesses both data and address wires so that only the one seeing its address on dedicated wires can read the data. In order to improve performances in complex systems, communication

1.2. Definitions

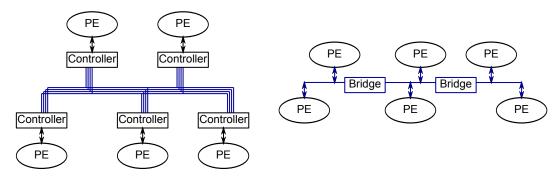

architectures were created using several buses in parallel: they are called multiple buses. This way several communications can occur at a time, one on each unitary bus. Furthermore, segmented buses were also created. Segmented buses are composed of several unitary or multiple buses serially linked by elements called bridges. Every bridge makes the relation between one bus and another one. Examples of multiple and segmented buses are provided in Figure 1.5. Further details are provided in Section 1.3.

Figure 1.5: Examples of a multiple bus (left) accessed through controllers, and of a segmented bus whose segments are interconnected by bridges.

#### **Network-on-Chip (NoC)**

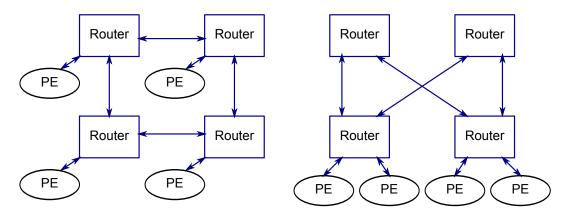

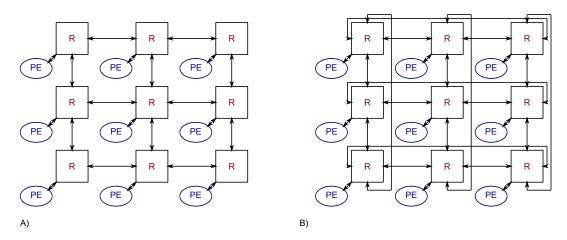

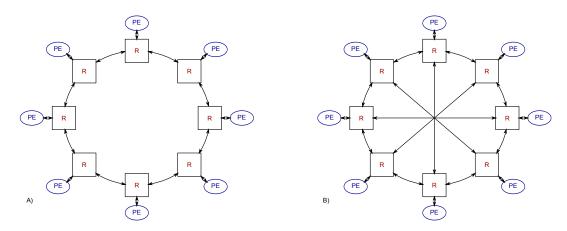

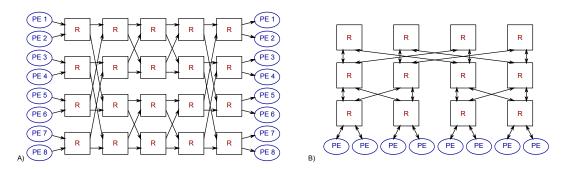

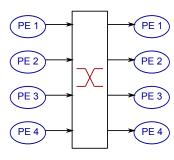

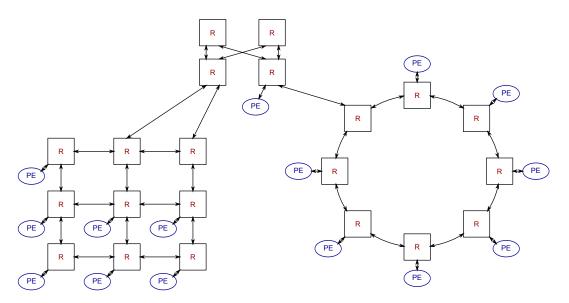

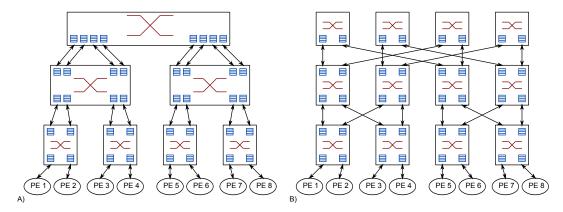

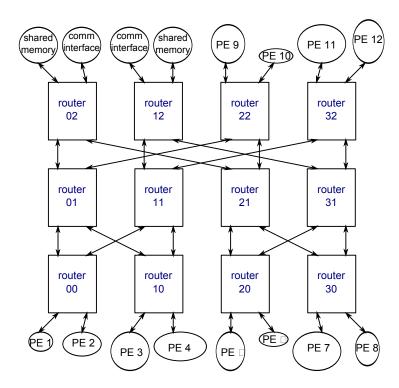

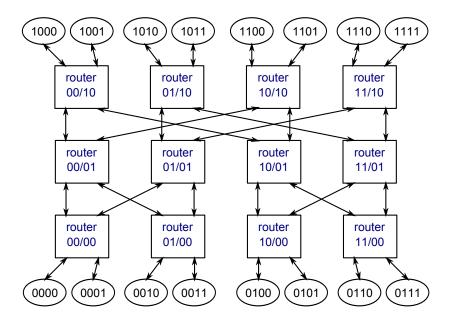

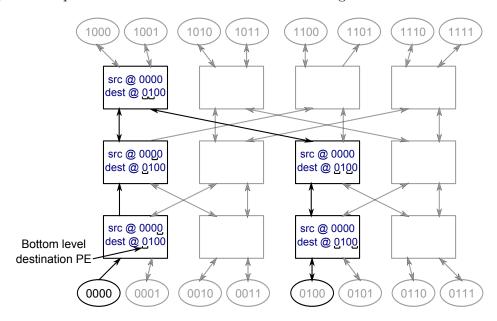

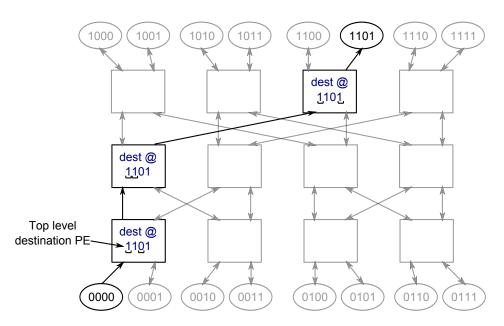

Networks-on-Chip are defined as a set of shared routing nodes and communication links. There are two types of networks: direct and indirect. In a direct network, each PE is connected to a dedicated routing node. In an indirect network, some of the routing nodes are linked with one or several PEs while remaining ones are only linked with neighbour routing nodes. Direct and indirect NoCs are presented in Figure 1.6. A network is defined by its topology, its routing techniques, its switching policy and its flow control.

#### 1.2.2 NoC parameters

#### Topology

The topology refers to the static arrangement of links and routing nodes in an interconnection network. The topology can be viewed as a road map. Data (like cars) are transmitted on links (like roads) from a routing node to another one (like intersections). Finally, the topology is not only the arrangement of the routing nodes and links, it is also the size of these links (width of the roads). The topology is the first choice when designing a network because the routing strategy and the flow control method are highly correlated with it. A topology is chosen regarding its cost and

Figure 1.6: Direct (left) and indirect (right) networks. In a direct network every router connects a PE while in an indirect one several routers do not connect directly any PE.

performance. The cost is defined as the number and the complexity of the routing nodes also with the density and length of involved links. Performance has two components: the bandwidth and the latency. A good topology is a trade off between the cost that should be minimized and the performance that should fit applicative requirements at minimum. Further details concerning topologies are provided in Section 1.3.

#### Routing

The routing method employed in a network determines the path taken by a data to reach its destination. If the topology is the road map of the network, routing is the next logical step: choosing one road to reach the destination. A good routing algorithm balances the load across the network links even in the presence of a non uniformly distributed data traffic. The more balanced is the load, the more performances will be close from ideal. A well designed routing algorithm also keeps the path length as short as possible in order to reduce the overall latencies of the data. There are three types of routing algorithms:

- Deterministic: the routing algorithm always chooses the same route for a specific couple source and destination PEs. This is for example the case of the XY algorithm: in an array of routers, like the direct network presented in Figure 1.6, data always travel on the X axis until they reach the column the destination PE is connected to. When in the proper column, they follow the Y axis reaching the line where the destination PE is located.

- Oblivious: this routing algorithm includes the deterministic routing as a subset, the choice of the path is made without considering any information about the network's present state. As an example, an oblivious but not deterministic

1.2. Definitions

algorithm consists, considering an indirect network like in Figure 1.6, in randomly choosing a path through upper level routers, then climbing down the structure of the network to reach the destination PE.

• Adaptive: the routing algorithm adapts itself considering the state of the network, for example avoiding congested areas. An example of adaptive routing is the turn model: data travel using a deterministic algorithm, but if they encounter a router that is already used for a communication, then they turn on another direction, thus reaching the destination through a different path (different lines and columns are used).

#### Circuit and packet switching

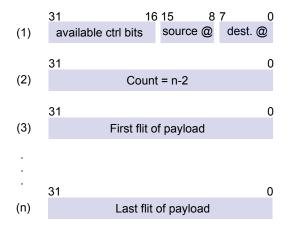

A network can be circuit switched or packet switched. In circuit switch, resources (links, buffers, etc.) are first allocated for a communication forming a reserved communication channel between the source and the destination PEs. When this channel is created, data can be transmitted (one or several packets of data). In circuit switch the routing node of the network are called switches while they are called routers in packet switch. In packet switch, data are injected inside the network with the destination address. The data path is allocated to this communication as packets advance inside the network. This is in packet switch that the flow control protocols presented in next section take all their sense. So, in packet switch, data are divided in one or several packets. Each packet can follow a different data path. For this purpose, usually each packet is composed of first sets of bits called flits that contain for example source and destination addresses, as well as other control informations (Cyclic Redundancy Check (CRC), etc.). These first flits are called header. Usually the header is followed by a flit called count since it contains the number of flits of data that are part of the packet. Data flits are called the payload.

#### Flow Control

The flow control protocol determines how resources of the network (links, buffers, etc.) are allocated. A good flow control method allocates these resources in an efficient manner so the network achieves a high fraction of its ideal bandwidth while delivering data with low predictable latencies. When two data arrive at a routing node for the same destination, the flow control method allocates resources to a communication while dealing with the other one. This way contentions are resolved. There are three main flow control methods: the store and forward, the virtual cut through, and the wormhole. In store and forward, every routing node stores the whole packet in its buffer before sending it to the following neighbour or the destination PE. In virtual cut through, the whole packet is also stored in a buffer of

the routing node until the whole packet is successfully transmitted, but flits are forwarded as soon as possible. In wormhole, only a small amount of flits are stored in a buffer. Flits are forwarded as soon as possible freeing a memory space in the buffer. This way, when a flit is forwarded, another can arrive. So, the packet is distributed over several routing nodes along its route like a worm.

A flow control protocol also manages the functioning of the buffers. One management protocol is based on credits. Each buffer has a counter indicating if further data can be received. Each time a flit is transmitted to next node (router or PE), the counter of considered buffer is incremented. Similarly, each time a flit arrives in the buffer, the counter is decremented. If the counter value is zero, the buffer is full and a signal indicates to previous node (router or PE) that no further data can be received. Another flow control protocol is the On/Off. A signal indicates to a previous node if it is allowed to transmit data. If the buffer storing incoming data contains more than a certain number of flits (called threshold), the "Off" signal is transmitted halting the communication in previous nodes. When the number of flits in the buffer becomes less than the threshold value, the "On" signal is asserted so that further flits can be received. Finally, another flow control protocol reducing the load of the buffers is the Ack/Nack (also called handshake). Each time a flit arrives in a router, if it can be stored in a buffer an acknowledgment (Ack) is sent. If no buffer is available, the flit is drop and a non-acknowledgment (Nack) is sent. When receiving a "Nack" signal, previous node sends the same flit again until it receives an "Ack".

#### **Traffic Patterns**

The Traffic pattern is the main concern when performances of a network are to be evaluated. Indeed, the topology of a network, the routing algorithm and the flow control methods react differently depending on the traffic pattern. A random traffic in which each source PE sends data with equal probability to each destination is the most commonly used traffic. A completely random traffic do not stress a network because, by making the traffic uniformly distributed, it balances data load inside the structure of the NoC even for topologies and routing algorithms that normally have very poor balance. Some very bad topologies and routing algorithms look good if only evaluated with a random traffic. To stress a topology or routing algorithm, permutation based traffic is typically used. In this pattern, each source PE sends all of its traffic to a single destination. Because load are then concentrated on individual source/destination pairs, permutations stress the load balance of topology and routing algorithm. In such a traffic, destination addresses are calculated from source addresses with a permutation or rotation of the bits.

1.2. Definitions

In addition with the choice of destination addresses that can notably be random or permutation based, the temporal distribution of the communication is also important. So, a PE sending all its data at a constant data rates forms a Uniform data traffic. The data rate can also vary in the time, reaching some peaks. Traffics patterns with data rates following a Normal temporal distribution are commonly encountered in applications. Another temporal distribution characterize the functioning of most memories. This is the burst transfers: data are grouped and transmitted sequentially without interruption. When all data are transmitted, periods of silence occur.

#### Deadlock, livelock and contention

Deadlock occurs in a network when a group of packets are unable to progress because they are waiting on another one to release resources (buffer, link, etc.). If a sequence of packets forms a cycle in the network, then the network is deadlocked. A deadlock is catastrophic because when few resources are occupied by deadlocked packets, other packets will block on these resources thus completely paralyzing the network. Furthermore the network would remain in this state until external intervention.

A closely related network pathology is livelock. In livelocks, packets continue on moving inside the network but without making progress toward their destinations. This becomes a concern for example when packets are allowed to take non minimal paths through the network. Livelocks are as dramatic as deadlocks for a network.

Contentions are defined as delays imposed to a packet in order to wait for a resource to be available. Contentions are not problematic like deadlocks and livelocks because the network recovers from contention without any external intervention. It recovers as soon as previous communication finishes or as soon as another path is found.

#### 1.2.3 Network performances

#### Latency

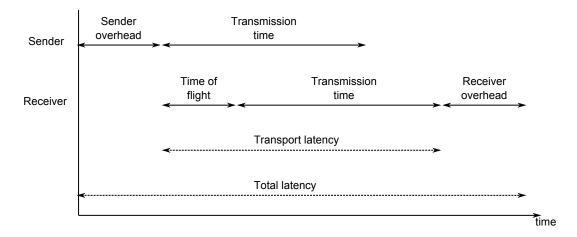

Latency is defined as the time elapsed between the moment the source PE sends the first bit of a data and the moment the destination PE receives the last bit of data. There are different types of latencies: the sender overhead, the time of flight, the transmission time, and the receiver overhead. These latencies are presented in Figure 1.7. The sender overhead corresponds to the time for the source PE to prepare the packets that are to be injected in the network. The time of flight is defined as the time for the first flit to cross the network, and thus to reach the destination PE. Time of flight usually depends on the traffic inside the NoC, so it may vary accordingly with the injected traffic. The transmission time corresponds

to the time taken by the whole packet of data to pass through the network. The transmission time do not include the time of flight. However, this time is highly linked with the size of the packet in terms of number of flits. The receiver overhead is defined as the time required by the destination PE to process the incoming data. The sum of the time of flight and the transmission time is denominated as transport latency. Transport latency thus corresponds to the time the packet spends inside the network. Finally, the total latency is defined as the sum of the transport latency and the sender/receiver overheads. Total latency represent from the PE point of view the total time required for communication purpose. Usually, in network characterization, only the transport latency is considered. This allows to extract the performances of the network alone, or interconnecting ideal PEs.

Figure 1.7: Presentation of the various delays constituting the total latency.

In the remaining of this report, the transport latency will always be considered under the appellation "latency".

#### Injection rate

The injection rate, also called offered traffic, is defined as the number of packets that are offered by every PE to the network. Offered traffic corresponds indeed to the number of packets each PE would like to inject in the network per unit of time. As in next section, offered traffic is often confronted to the accepted traffic, i.e. the number of data the network can accept. When the accepted traffic is less than the offered one, the network is not able to transfer all the data provided to it (this is the saturation). Injection rates are usually expressed in percentage, as a fraction of capacity which corresponds to the theoretical bandwidth of the network. If C is the capacity of a network,  $D_w$  the width in bits of the data lines, and F the operating

frequency of the NoC, then C is

$$C = D_w * F (1.1)$$

Then, if  $D_{offered}$  corresponds to the number of data bits per second offered to the network, then the injection rate  $I_r$ , in percentage, is

$$I_r = \frac{D_{offered} * 100}{C} \tag{1.2}$$

From this formula, PEs injecting packets using all the theoretical bandwidth of the network define an injection rate of 100%. Similarly PEs injecting data using only half of this theoretical bandwidth offer an injection rate of 50%.

#### **Throughput**

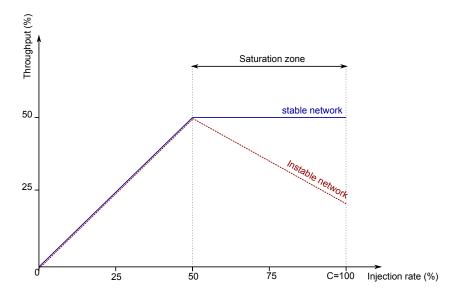

Throughput corresponds to the rate at which packets are delivered by the network. It is measured counting the number of packets that arrive at destination over a time interval. Usually presented in percentage as a fraction of network's total capacity, it is also sometime expressed as a data rate. Throughput represents the traffic that is accepted by the network. This is why throughput is usually contrasted with the injection rate (offered traffic). At traffic level less than saturation, accepted traffic is proportional to offered traffic. However, when the network saturates the accepted traffic either reaches a constant value or decreases. When a constant value is reached, the network is called stable because accepted traffic is ensured to fit the offered traffic until a maximum fraction of capacity. However, an accepted traffic decreasing when the network saturates reveals an instability of this network: accepted traffic feats the offered one until reaching a pick after which performances fall down. Stable and instable networks are presented in Figure 1.8

#### 1.3 Interconnection architectures

In previous sections, the impact of the DPR over the conception of Systems-on-Chip was presented. Keeping in view the large range of applications that have to be implemented, an interconnection architecture should support several constraints induced by the DPR. Current applications are very complex and their task graphs exhibit a large degree of parallelism. Thus, from the interconnection point of view, the architecture must provide the possibility to realize several communications in parallel. Furthermore, dynamic placement and scheduling of PEs in an FPGA require a high level of flexibility. So, neither the location of PEs nor the data traffic (uniform, permutation, etc.) can be predicted at compile time. These requirements of flexibility should be considered by the network topology and the routing algorithm, and thus

Figure 1.8: Presentation of the throughput compared with the injection rate for a stable (blue) and an instable (red) network.

the available network performances. An application is typically split into tasks, and there is no reason for every task to be implemented in homogeneously sized hardware PEs. Heterogeneously sized PEs are considered in this work. Furthermore the matrices of current FPGAs are highly heterogeneous when considering the 2D repartition of the resources. So, both heterogeneously sized PEs and heterogeneous FPGAs should be supported by the interconnection architecture. Finally, a communication architecture should present an interesting trade off between the implementation cost (used resources) and performances. Since a large range of applications is considered, network performances can be sparingly privileged.

Some existing interconnection architectures are now presented. Considering the very large amount of different architectures that were proposed in research, this presentation can not be comprehensive. However, most popular interconnection are presented and confronted to the constraints induced by the DPR.

### 1.3.1 Bus based interconnections

Buses are very popular in present on-Chip circuits. Since the sizes of most affordable FPGAs are still limited in terms of CLBs number, the number of PEs constituting an application is also limited. This is why Xilinx proposes bus based interconnection architecture directly accessible from the ISE/EDK design environments. Thus, both the Processor Local Bus (PLB) and the On-chip Peripheral Bus (OPB) are available from these tools. These two buses provide high level performances with a reduced cost. They are quite simple to implement into the scope of an application thanks

to the ISE/EDK environments and to their well documented interfaces [120], [119]. Furthermore, thanks to the ISE/EDK environments, many IP cores are available to be connected to these buses: MicroBlaze or PowerPC processors, memory controllers, communication interfaces like PCI bridges, etc.

Others largely used bus based interconnections are the Advanced High-performance Bus (AHB) that is inherited from Advanced Microcontroller Bus Architecture (AMBA) [40], and the Wishbone bus [89]. Both AHB and Wishbone buses are open source. Wishbone is provided by OpenCores while AHB is accessible through the GRLIB library also with many IP cores that can be directly interconnected: LEON 3 processor, memory controllers, etc. AHB provides high level performances as demonstrated in [12]. Considering these bus based interconnections along with their design environment and existing compliant IP cores (PEs), designing complete applications is substantially eased.

Several others bus based interconnections were proposed as NECoBus that is very close from AMBA [13]. Some of them are used on-Chip like in 8032 or ARM processors [112]. However, as every bus based interconnections, they suffer of a poor scalability resulting in a fall of performances when the number of interconnected cores increases. Furthermore, even if currently DPR is realized through statically implemented interfaces, all these buses were foreseen to operate only with statically allocated PEs.

Some buses have been designed in order to present both improved scalability and higher performances. Segmented buses with different clocks per segment were presented in 1999 [84]. This is the Globally Asynchronous Locally Synchronous (GALS) approach. Each segment has a dedicated clock reference allowing synchronous data transfers. The clock adaptation between the various segments is realized through the use of bridges. This way, the overall interconnection architecture seems asynchronous. As demonstrated through an ASIC implementation, the proposed bus presents interesting performances. Following the same idea, another segmented bus was proposed for high performance compliance purpose in 2002 [102]. Finally, the HIBI interconnection network was designed. Indeed, HIBI is based on segmented buses and uses also the GALS approach [99]. Following the GALS approach, a fully asynchronous bus was proposed in 2003 [56]. Latter bus is expected to provide better performances than synchronous based ones because it does not take care about propagation delays nor the parasitic effects that affect the physical layers of the chips. Unfortunately, no comparison with synchronous buses was presented.

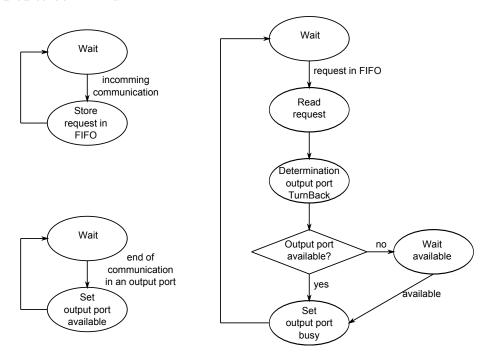

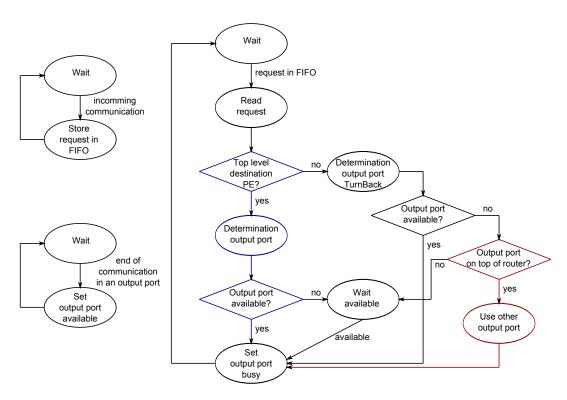

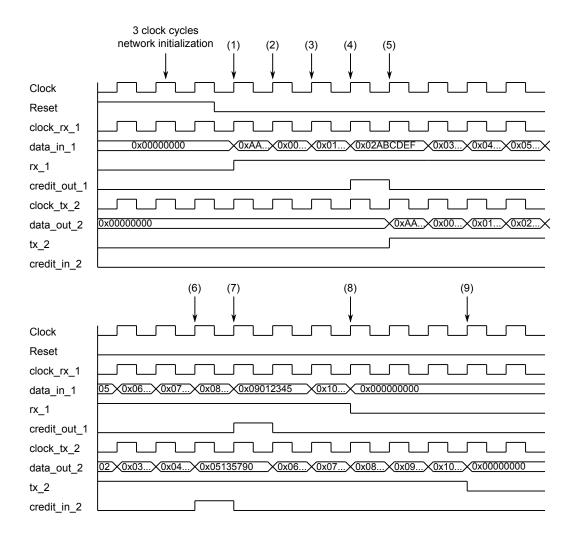

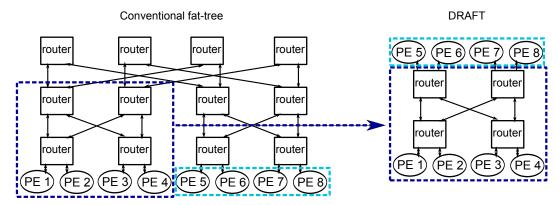

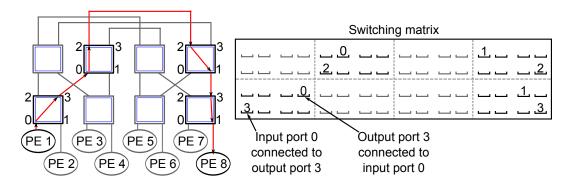

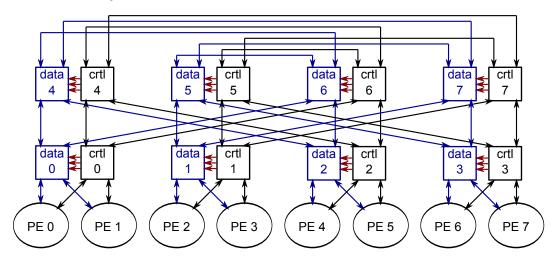

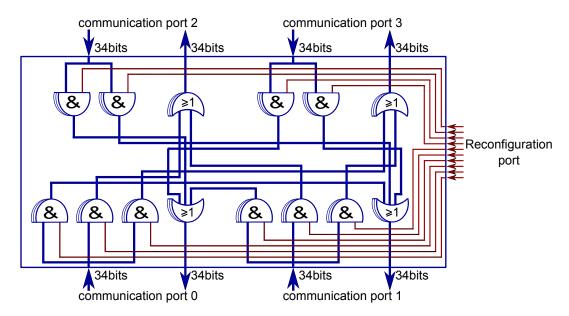

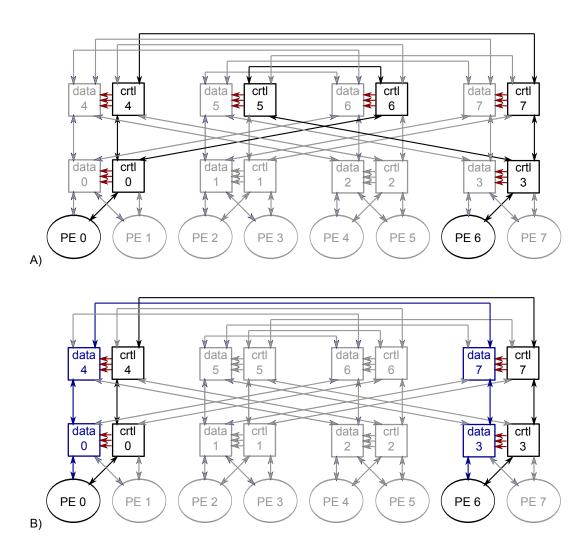

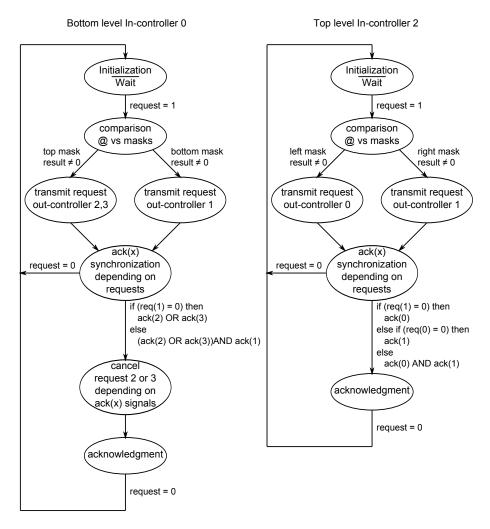

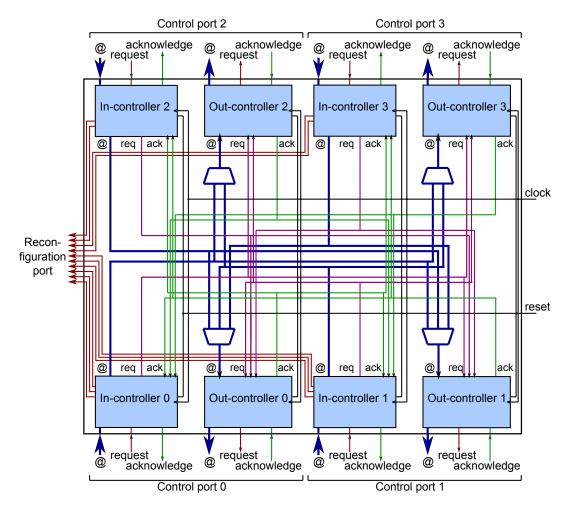

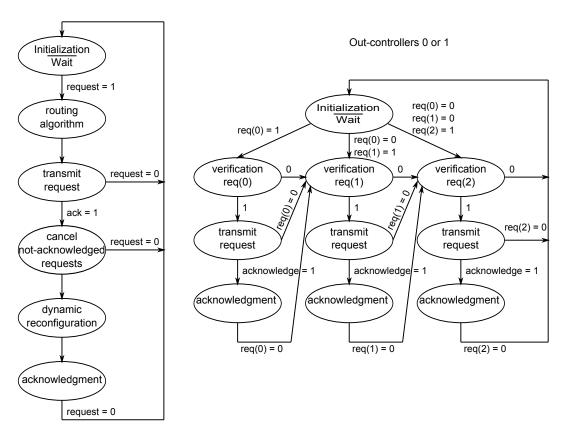

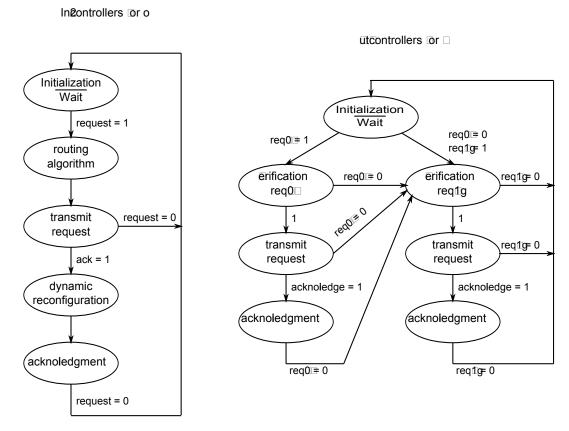

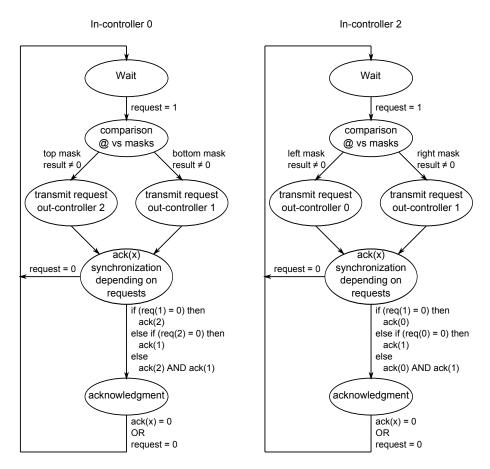

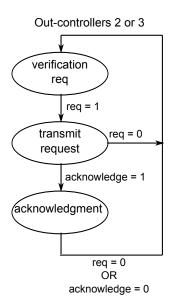

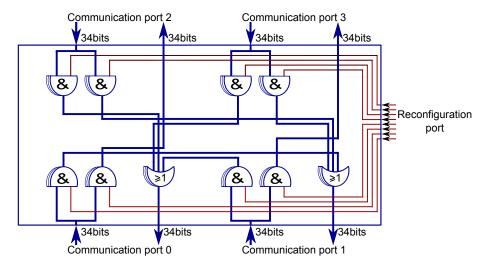

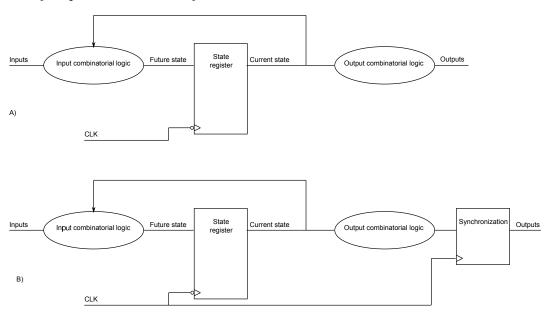

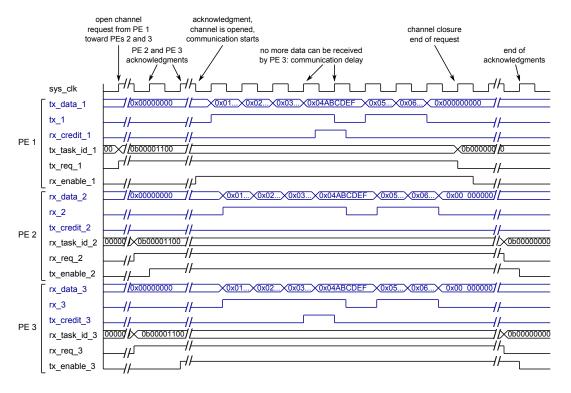

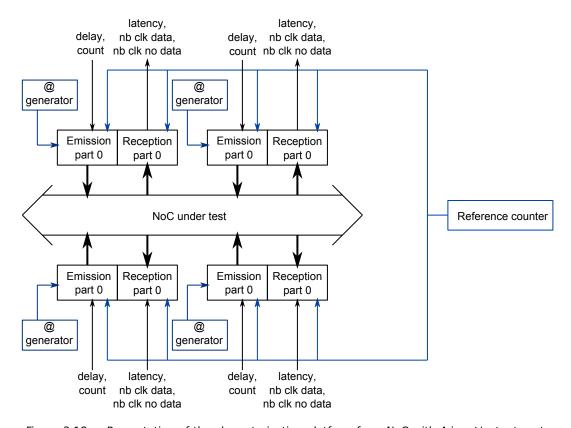

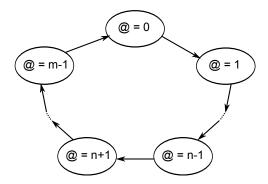

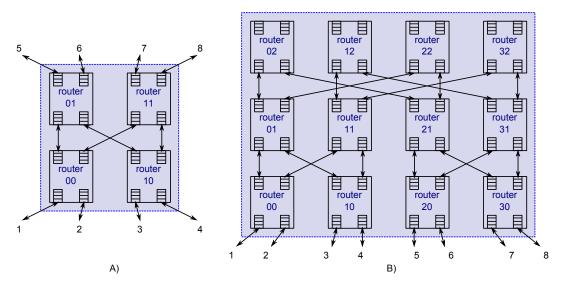

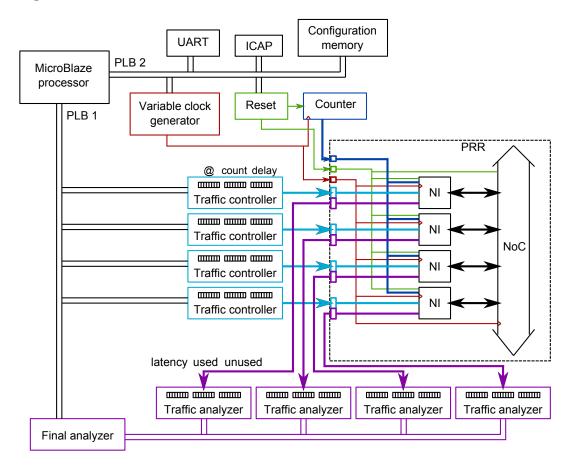

More researches were lead in order to design efficient buses. This is the case of the bus presented in 2009 in [87], or of FLEXBUS [103]. However the introduction of the DPR paradigm in the on-Chip design methodology has lead to DPR oriented buses. This is the case for example for ReCoBus [64] which is defined as a shared