# Développement de nouveaux procédés d'isolation électrique par anodisation localisée du silicium

Ahmed Garbi

#### ▶ To cite this version:

Ahmed Garbi. Développement de nouveaux procédés d'isolation électrique par anodisation localisée du silicium. Autre. INSA de Lyon, 2011. Français. NNT: 2011ISAL0072 . tel-00694394

# HAL Id: tel-00694394 https://theses.hal.science/tel-00694394

Submitted on 4 May 2012

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

No d'ordre: 2011-ISAL-0072 Année 2011

# **THESE**

Présentée devant

# L'INSTITUT NATIONAL DES SCIENCES APPLIQUEES DE LYON

Pour obtenir le grade de

#### **DOCTEUR**

ECOLE DOCTORALE : Electronique, Electrotechnique, Automatique (EEA)

SPECIALITE : Dispositifs de l'Electronique Intégrée

Par

### **Ahmed GHARBI**

# Développement de nouveaux procédés d'isolation électrique par anodisation localisée du silicium

Soutenue le 08 juillet 2011 devant la Commission d'Examen

**BARBIER Daniel** Professeur, INSA de Lyon Président du jury **NASSIOPOULOU** Androula Directeur de recherche, IMEL, Grèce Rapporteur Professeur, Université de Tours VENTURA Laurent Rapporteur **HALIMAOUI** Aomar Ingénieur STMicroelectronics Examinateur SOUIFI Abdelkader Professeur, INSA de Lyon Directeur de thèse **REMAKI Boudjemaa** Maître de conférence-HDR, Univ. Lyon 1 Directeur de thèse

> Cette thèse a été préparée à l'Institut des Nanotechnologies de Lyon (INL) Cofinancement CNRS-STMicroelectronics

Order No.: 2011-ISAL-0072 Year 2011

# **THESIS**

Submitted to

## NATIONAL INSTITUTE OF APPLIED SCIENCE OF LYON

For the degree of

#### PhD DOCTOR

DOCTORAL SCHOOL: Electronique, Electrotechnique, Automatique (EEA)

SPECIALITY: Integrated Electronic Devices

Ву

### **Ahmed GHARBI**

# Development of a new process for electrical isolation of ULSI CMOS circuits based on local anodization of silicon

Defended on July 8th, 2011

**BARBIER Daniel** Professor, INSA Lyon President NASSIOPOULOU Androula Research Director, IMEL, Greece Reporter **VENTURA Laurent** Professor, University of Tours Reporter **HALIMAOUI** Aomar **Engineer STMicroelectronics** Examiner SOUIFI Abdelkader Professor, INSA Lyon Director of thesis **REMAKI Boudjemaa** Assistant Professor-HDR, Univ. Lyon 1 Director of thesis

This project has been performed at the Lyon Institute of Nanotechnology (INL) in the frame of CNRS/STMicroelectronics partnership

# INSA Direction de la Recherche - Ecoles Doctorales - Quinquennal 2011-2015

| SIGLE                                                                                  | ECOLE DOCTORALE                                               | NOM ET COORDONNEES DU RESPONSABLE                                                       |

|----------------------------------------------------------------------------------------|---------------------------------------------------------------|-----------------------------------------------------------------------------------------|

| CHIMIE                                                                                 | CHIMIE DE LYON http://www.edchimie-lyon.fr                    | M. Jean Marc LANCELIN Université de Lyon – Collège Doctoral                             |

|                                                                                        |                                                               | Bât ESCPE<br>43 bd du 11 novembre 1918                                                  |

|                                                                                        | Insa : R. GOURDON                                             | 69622 VILLEURBANNE Cedex Tél: 04.72.43 13 95 directeur@edchimie-lyon.fr                 |

| <b>E.E.A.</b> <u>ELECTROTECHNIQUE</u> , <u>AUTOMATIQUE</u>                             |                                                               | M. Gérard SCORLETTI Ecole Centrale de Lyon                                              |

|                                                                                        | Secrétariat : M.C. HAVGOUDOUKIAN                              | 36 avenue Guy de Collongue<br>69134 ECULLY<br>Tél : 04.72.18 60 97 Fax : 04 78 43 37 17 |

|                                                                                        | eea@ec-lyon.fr                                                | Gerard.scorletti@ec-lyon.fr                                                             |

| E2M2 EVOLUTION, ECOSYSTEME, MICROBIOLOGIE, MODELISATION http://e2m2.universite-lyon.fr |                                                               | Mme Gudrun BORNETTE CNRS UMR 5023 LEHNA Université Claude Bernard Lyon 1                |

|                                                                                        | Insa : H. CHARLES                                             | Bât Forel 43 bd du 11 novembre 1918 69622 VILLEURBANNE Cédex                            |

|                                                                                        |                                                               | Tél: 04.72.43.12.94<br><u>e2m2@biomserv.univ-lyon1.fr</u>                               |

| EDISS                                                                                  | INTERDISCIPLINAIRE SCIENCES-<br>SANTE                         | M. Didier REVEL                                                                         |

| EDISS                                                                                  | http://ww2.ibcp.fr/ediss                                      | Hôpital Louis Pradel<br>Bâtiment Central<br>28 Avenue Doyen Lépine                      |

|                                                                                        | Sec : Safia AIT CHALAL<br>Insa : M. LAGARDE                   | 69677 BRON Tél: 04.72.68 49 09 Fax:04 72 35 49 16 Didier.revel@creatis.uni-lyon1.fr     |

|                                                                                        | INFORMATIQUE ET                                               | M. Johannes KELLENDONK                                                                  |

| INFOMATHS                                                                              | MATHEMATIQUES http://infomaths.univ-lyon1.fr                  | Université Claude Bernard Lyon 1<br>LIRIS - INFOMATHS                                   |

|                                                                                        |                                                               | Bâtiment Nautibus                                                                       |

|                                                                                        |                                                               | 43 bd du 11 novembre 1918<br>69622 VILLEURBANNE Cedex                                   |

|                                                                                        |                                                               | Tél: 04.72. 43.19.05 Fax 04 72 43 13 10                                                 |

|                                                                                        | MATERIAUX DE LYON                                             | infomaths@bat710.univ-lyon1.fr M. Jean-Yves BUFFIERE                                    |

| Matériaux                                                                              |                                                               | Secrétaire : Mériem LABOUNE                                                             |

|                                                                                        |                                                               | INSA de Lyon<br>École Doctorale Matériaux                                               |

|                                                                                        |                                                               | Mériem LABOUNE                                                                          |

|                                                                                        |                                                               | Bâtiment Antoine de Saint-Exupéry<br>25bis Avenue Jean Capelle                          |

|                                                                                        |                                                               | 69621 VILLEURBANNE                                                                      |

|                                                                                        |                                                               | Tel: 04 72 43 71 70<br>Fax: 04 72 43 72 37                                              |

|                                                                                        |                                                               | ed.materiaux@insa-lyon.fr                                                               |

| MEGA                                                                                   | MECANIQUE, ENERGETIQUE, GENIE<br>CIVIL, ACOUSTIQUE (ED n°162) | M. Philippe BOISSE<br>Secrétaire : Mériem LABOUNE                                       |

|                                                                                        |                                                               | Adresse:                                                                                |

|                                                                                        |                                                               | INSA de Lyon<br>École Doctorale MEGA                                                    |

|                                                                                        |                                                               | Mériem LABOUNE                                                                          |

|                                                                                        |                                                               | Bâtiment Antoine de Saint-Exupéry<br>25bis Avenue Jean Capelle                          |

|                                                                                        |                                                               | 69621 VILLEURBANNE                                                                      |

|                                                                                        |                                                               | Tel : 04 72 43 71 70<br>Fax : 04 72 43 72 37                                            |

|                                                                                        |                                                               | mega@insa-lyon.fr                                                                       |

|                                                                                        | ScSo*                                                         | Site web: http://www.ed-mega.com                                                        |

| ScSo                                                                                   | <u>Jeno</u>                                                   | M. OBADIA Lionel<br>Université Lyon 2                                                   |

|                                                                                        | M. OBADIA Lionel                                              | 86 rue Pasteur                                                                          |

|                                                                                        | Sec : Viviane POLSINELLI                                      | 69365 LYON Cedex 07<br>Tél: 04.78.69.72.76 Fax: 04.37.28.04.48                          |

|                                                                                        | Insa: J.Y. TOUSSAINT                                          | <u>Lionel.Obadia@univ-lyon2.fr</u>                                                      |

<sup>\*</sup>ScSo : Histoire, Geographie, Aménagement, Urbanisme, Archéologie, Science politique, Sociologie, Anthropologie

# Résumé

La miniaturisation extrême des dispositifs CMOS est une des préoccupations majeures de l'industrie microélectronique. Il a fallu donc chercher des solutions innovantes pour répondre aux défis de cette miniaturisation soit en proposant de nouvelles architectures de circuits soit en utilisant de nouveaux matériaux ou aussi de nouveaux procédés de fabrication. Par exemple, la fabrication de l'oxyde permettant l'isolation électrique entre les transistors a nécessité sans cesse d'être améliorée. Ainsi, on est passé du procédé d'isolation par oxydation localisée de silicium (LOCOS) au procédé d'isolation par tranchées (STI) qui est utilisée maintenant pour la technologie la plus avancée en production. En STI, une gravure localisée des tranchées dans le substrat de silicium est réalisée. Cette étape est suivie d'une oxydation et d'un dépôt de silice. Le procédé se termine par une planarisation par polissage mécanochimique (CMP). L'avantage de ce procédé est lié à la possibilité d'isoler les dispositifs avec des tranchées profondes de manière quasi-anisotrope alors que dans le cas du LOCOS, le procédé est isotrope, ce qui limite la profondeur de l'isolation au risque de consommer le silicium des zones actives par extension latérale du processus d'oxydation. Cependant, pour les technologies en développement, le STI commence à montrer quelques limitations.

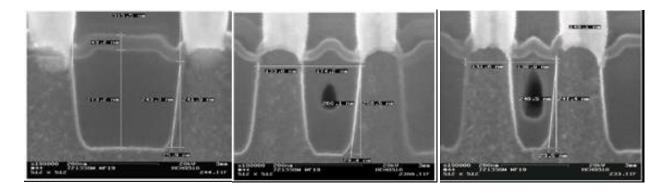

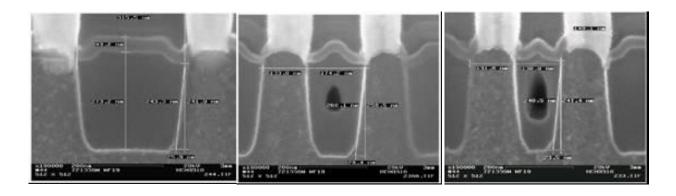

Le premier problème, qui est illustré à la Figure 1, est lié au remplissage par la silice de tranchées de moins en moins larges. En effet, lorsqu'on diminue la largeur des tranchées, leur remplissage par la silice devient incomplet laissant des cavités d'air (Voiding). Le deuxième problème est lié à l'étape de planarisation qui conduit à un "surpolissage" des zones les plus larges (Dishing). De nouvelles approches sont envisagées pour remplacer le procédé STI. L'anodisation électrochimique est une piste prometteuse. En effet, cette technique utilisant un électrolyte à base d'acide fluorhydrique (HF) permet de rendre localement poreux le silicium en profondeur. Un recuit oxydant permet ensuite de transformer le silicium poreux en silice. Dans cette approche (Si poreux), la silice permettant l'isolation est obtenue par oxydation et non pas par dépôt ce qui écarte tout risque de voiding et limite l'extension latérale. Par ailleurs, cette approche ne nécessite aucune étape de CMP, éliminant ainsi le problème de dishing. Cette technique proposée a constitué le point de départ de nos travaux de thèse qui s'est focalisée sur deux axes principaux : d'une part la maîtrise du procédé d'anodisation électrochimique pour la formation du silicium poreux et d'autre part l'optimisation du procédé d'oxydation.

**Figure 1** Image MEB illustrant une limitation du procédé STI quand on diminue la largeur des tranchées (voiding)

Dans le premier chapitre de ce mémoire de thèse, nous nous présentons le contexte du sujet travers une brève introduction sur l'évolution de la microélectronique et sa course continue pour la miniaturisation. On y trouve ainsi un rappel sur les réalisations importantes qui ont marqué l'histoire dans ce domaine telles que les premiers transistors commercialisés en 1954 puis l'invention des circuits intégrés (ICs) suite au développement du procédé de fabrication planaire en 1959 jusqu'à l'apparition du premier microprocesseur en 1971 [Sif04, Gil90]. Il est à noter que ce dernier exploit a lancé vraiment la croissance de l'industrie microélectronique et a ouvert la voie à la réalisation de microprocesseurs de hautes performances et de meilleure fiabilité, soutenue par la maturation du processus de fabrication et la miniaturisation continue des transistors. En effet, cette miniaturisation permet d'obtenir des ICs (i) plus rapides (fréquence de fonctionnement plus élevée), (ii) moins chers à fabriquer comme il est possible de monter plus de circuits sur une plaque de silicium et (iii) de consommation plus faible car les porteurs de charge ont tout simplement une distance plus courte à parcourir. Dans ce contexte, Gordon Moore, l'un des fondateurs d'Intel, a prédit que le nombre de transistors sur une plaque de silicium doublerait tous les deux ans [Moo75]. Cette prédiction, connue aussi sous la dénomination loi de Moore, a tenu bon pendant plus de quatre décennies et devrait être valable pour au moins une autre. Cette évolution impose de trouver des solutions à de nombreux et difficiles problèmes technologiques. Par exemple, la miniaturisation du transistor MOS nécessitait la réduction de l'épaisseur de son oxyde de grille (à base d'oxyde thermique de silicium SiO<sub>2</sub>) pour maintenir les mêmes performances du dispositif (Loi de Dennard) [Den74]. Toutefois, pour les technologies les plus avancées, comme la longueur de grille a diminué en dessous de 130 nm, l'épaisseur d'oxyde de grille a dû être réduite d'environ 2 nm. Cela semble être une limitation fondamentale car le courant de fuite (courant tunnel grille-canal) devient très élevé (aussi grand que le courant de fuite source-drain à l'état bloqué du transistor qui est d'environ 10 nA/ $\mu$ m² [Wol99]) rendant impossible la réalisation des MOS de haute performance. Pour cette raison, il a fallu remplacer le dioxyde de silicium par les matériaux high-k (matériaux de grande permittivité diélectrique) tels que l'oxyde d'aluminium Al $_2$ O $_3$  ( $\epsilon$  = 9), l'oxyde de zirconium ZrO $_2$  ( $\epsilon$  = 25) et l'oxyde d'hafnium HfO $_2$  ( $\epsilon$  = 24), ce qui permet d'obtenir les mêmes capacités avec de plus grandes épaisseurs physiques. De la même façon, le procédé de fabrication de l'oxyde d'isolation entre les transistors PMOS et NMOS dans une technologie CMOS a subi lui aussi des améliorations pour résoudre certaines limitations indiquées ci-dessus. On est passé ainsi du LOCOS au STI pour arriver à d'autres alternatives telles que l'approche Si poreux.

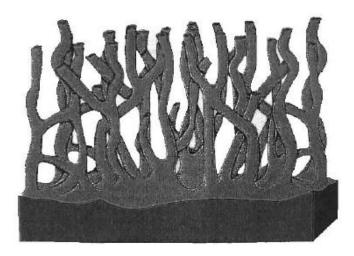

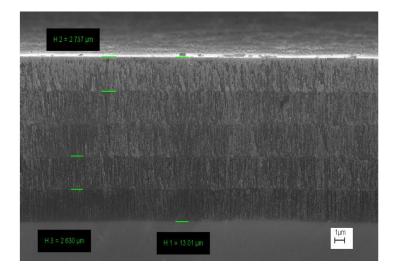

Dans une deuxième partie de ce premier chapitre, nous nous intéressons au silicium poreux qui est un matériau nanostructuré composé d'un réseau de cristallites de Si et de pores interconnectés. On présente tout d'abord les conditions expérimentales permettant sa formation. Le Si poreux est tout simplement obtenu en appliquant une polarisation positive (anodisation) à une plaque de silicium immergée dans de l'acide fluorhydrique (HF), ce qui conduit à une réaction entre les porteurs libres électroniques (les trous) et les ions négatifs fluor F⁻ à l'interface semiconducteur/électrolyte, puis une dissolution d'atomes de silicium du réseau du substrat. Dans le cas du silicium de type-n, l'apport de trous pourrait être assuré par illumination (photogénération de trous) ou application d'une forte tension d'anodisation. Certaines mesures doivent être prises en considération pour assurer une bonne expérience d'anodisation électrochimique, notamment une bonne homogénéité en profondeur de la couche poreuse (même diamètre de pore et même épaisseur de couche) avec une meilleure reproductibilité (un bon contrôle de la porosité et de l'épaisseur) d'une manip à l'autre, surtout quand il s'agit d'une porosofication profonde (> 2μm).

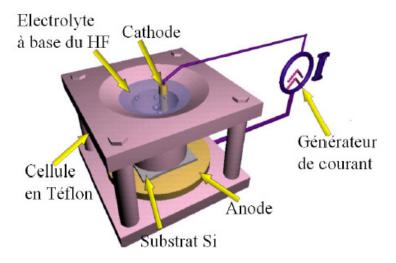

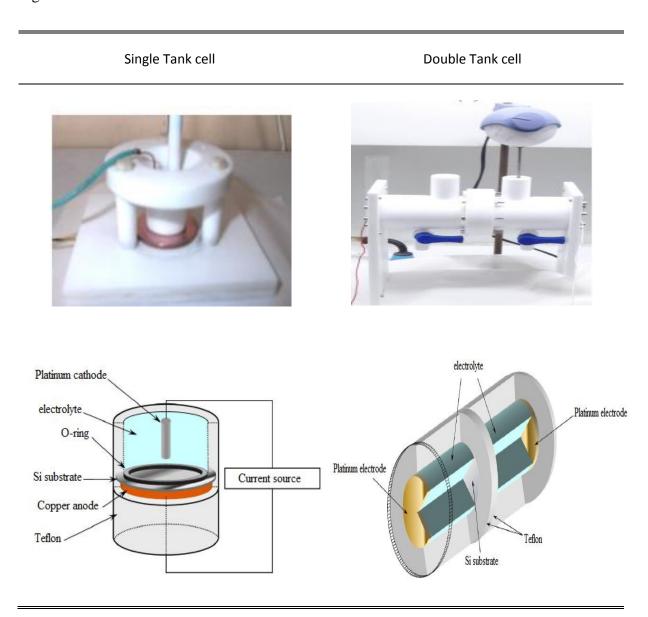

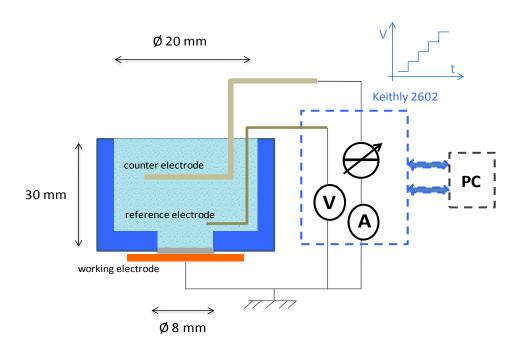

Par exemple, la cathode de platine (ou d'or) dans une cellule d'anodisation simple bain (Figure 2), qui est utilisé dans ce travail, devrait être de même taille, colinéaire et assez loin de l'anode du silicium afin d'obtenir une distribution de lignes de potentiel plus uniforme et assurer donc une gravure électrochimique homogène [Leh02]. De plus, au cours de la réaction d'anodisation, il y a dégagement gazeux de bulles de dihydrogène qui se collent à la surface de silicium et s'accumulent au fond des pores où se produit la réaction de dissolution, ce qui pourrait empêcher la progression de la gravure et induire une inhomogénéité latérale et/ou en profondeur. La solution à ce problème est d'ajouter un agent mouillant (communément l'éthanol) à la solution de HF qui favorise l'infiltration de l'électrolyte et donc l'élimination

de gaz. D'autre part, il est généralement conseillé d'utiliser un agitateur mécanique pour accélérer la libération de ces bulles de dihydrogène ou encore de remplacer le régime d'anodisation continu (courant continu appliqué) par un mode pulsé qui permet la régénération des ions fluore F dans les pores pendant les temps de repos et évite alors toute diminution de la concentration locale de HF et maintient une vitesse de gravure homogène [Hou96, Pop05]. Pour certaines applications, le contrôle de la température pendant l'anodisation électrochimique s'avère aussi essentiel et un système d'échangeur de chaleur devrait donc être intégré. Il a été démontré [Leh02] par exemple que la densité de courant d'électropolissage varie en fonction de la température selon un comportement de type Arrhenius avec une énergie d'activation de 0,345 eV pour du silicium de type-p anodisé avec une concentration de HF de 1 à 10%. Guillermain [Gui07] a également révélé que la température ambiante n'est pas le meilleur choix pour une bonne homogénéité de la couche poreuse. A basse température, la viscosité de l'électrolyte augmente ce qui conduit à une meilleure mouillabilité et facilite donc la libération du digydrogène. En outre, la vitesse de gravure diminue avec la température (vitesse de gravure à -40 °C est presque 30 à 100 fois inférieure à celle à la température ambiante pour une même porosité) et permet ainsi non seulement un contrôle précis de l'épaisseur mais aussi une bonne homogénéité de la couche poreuse puisque l'électrolyte trouverait le temps de se régénérer. Setzu et al. [Set98] ont aussi signalé une diminution importante de la rugosité de l'interface Si/Si poreux en diminuant la température concluant ainsi que c'est un bon moyen pour obtenir du Si poreux de bonne qualité de point de vue structural.

Figure 2 Cellule d'anodisation électrochimique simple-bain

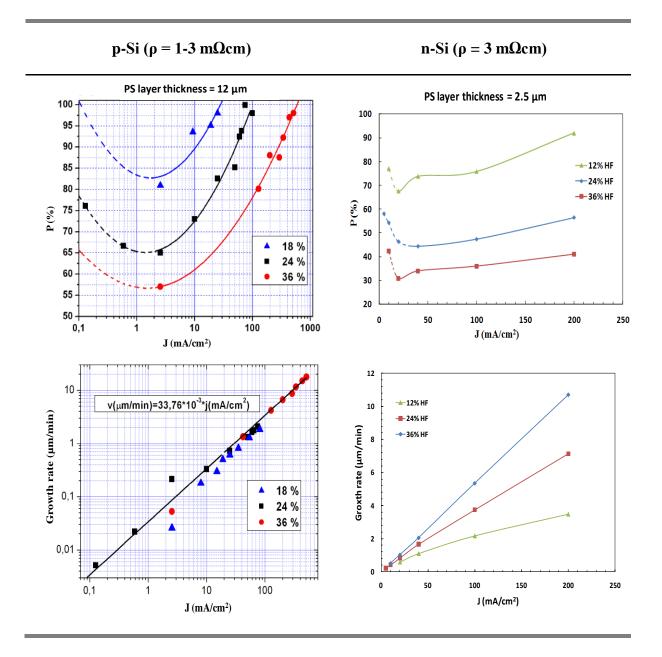

Par la suite, nous donnons un aperçu des principales propriétés structurales du Si poreux (porosité, surface spécifique, taille des pores, épaisseur de la couche) et les méthodes qui permettent leur caractérisation en soulignant leur variation avec les paramètres d'anodisation (concentration HF, densité de courant, type et niveau de dopage du substrat).

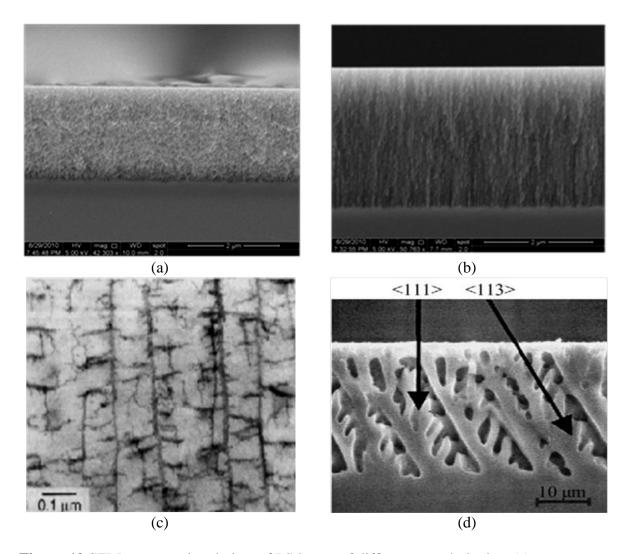

Le Si poreux peut prendre différentes formes morphologiques (spongieuse, colonnaire...) qui sont principalement déterminées par le type et le niveau de dopage du substrat initial. La taille moyenne des pores (ou des nanocristallites) peut varier du micromètre à quelques nanomètres. On peut alors distinguer du macroporeux (taille de pore comprise entre 0.1-1µm), du méso-poreux (structure colonnaire fortement anisotrope avec un diamètre de pore de quelques dizaines de nanomètre) et du nanoporeux (structure spongieuse avec un réseau aléatoire de pores de quelques nanomètre de diamètre). Il faut aussi mentionner que chaque nanocristallite conserve la structure cristalline du substrat initial avec la même orientation [Bar84]. On note également que pour le Si de type-n faiblement dopé, l'orientation cristallographique semble avoir un effet significatif sur la morphologie de la couche poreuse [Fol02,Lev93]. Il en résulte des macropores qui ne sont pas forcément perpendiculaire à la surface mais qui croissent plutôt selon la direction des plans cristallins <100> et <113> [Ron99], ce qui donne une morphologie finale sous forme d'un pore principale dans l'une de ces deux directions avec des branches dans les autres directions. La distribution en taille des pores peut être déterminée à l'aide des mesures d'absorption de gaz [Her87] ou avec la microspectroscopie Raman [Bru97, Isl01] ou par des mesures de rayon X [Bel96,Leh93].

La surface spécifique d'une couche poreuse représente toute la surface interne de cette couche par unité de masse ou par unité de volume [Roq94]. Elle peut être déterminée à partir de mesures d'absorption de gaz [Bom88] ou par comparaison de la vitesse de gravure du silicium poreux dans le HF avec celle du substrat de silicium [Hal94]. La surface spécifique du Si poreux peut varier de 50 à 1000 m²/cm³.

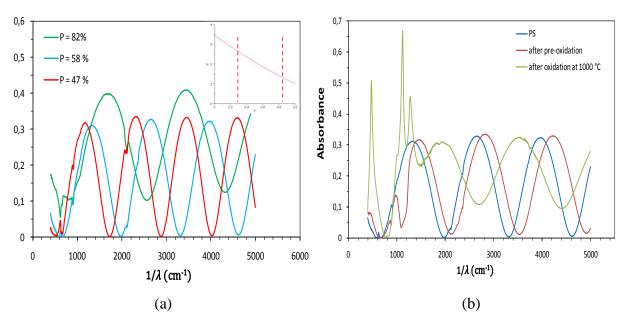

La porosité d'une couche poreuse est définie comme la fraction volumique du vide. Elle peut varier de 30% à 90% et peut être déterminée par gravimétrie ou par mesure de l'indice de réfraction en FTIR (spectroscopie infrarouge à transformée de Fourier). Il est à noter que la porosité augmente avec la densité de courant d'anodization et diminue en augmentant la concentration de HF. Cependant, il a été observé qu'à faible densité de courant, la porosité augmente quand la densité de courant diminue. Ceci peut être expliqué par la

dissolution chimique qui commence à devenir importante par rapport à la dissolution électrochimique à faible courant [Nyc06]. D'autre part, la porosité dépend aussi de la concentration de dopants du substrat. Pour des même conditions d'anodisation (densité de courant et concentration en HF), les couches nanoporeuses obtenues par exemple à partir du silicium de type-p faiblement dopé sont reconnu comme étant de plus grande porosité que les couches mesoporeuse ou macroporeuse [Leh00].

Quant à la vitesse de formation du Si poreux (ou vitesse de gravure électrochimique), elle varie quasi linéairement avec le courant sauf pour le cas du Si de type-n faiblement dopé où elle est reste constante mais elle diminue avec la concentration de HF. Il faut mentionner également que cette vitesse d'attaque dépend peu de la concentration de dopage du substrat sauf pour le type-n moyennement et fortement dopé où elle croît en diminuant la densité de courant.

Toute application du Si poreux nécessite une bonne compréhension de la formation de ce matériau permettant ainsi une maîtrise parfaite de ses propriétés avec les paramètres d'anodisation. Le deuxième chapitre de ce manuscrit s'attache à l'étude de l'une des propriétés qui est la dépendance de la formation du Si poreux avec la concentration de dopants. Pour cela, une analyse détaillée des caractéristiques courant-tension I-V est menée sur le Si durant son anodisation électrochimique.

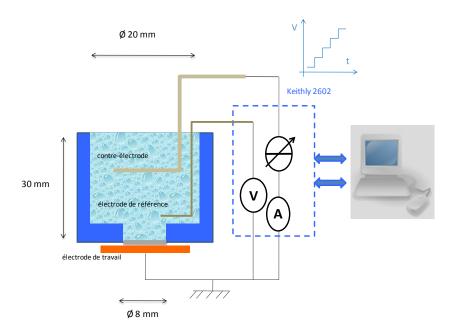

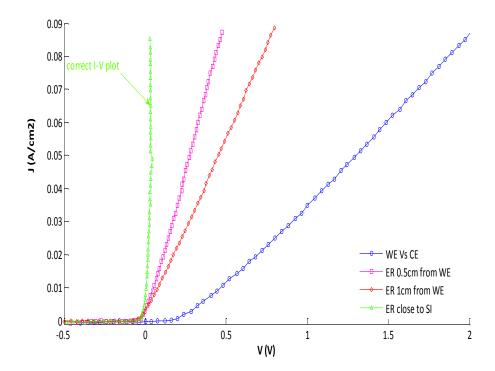

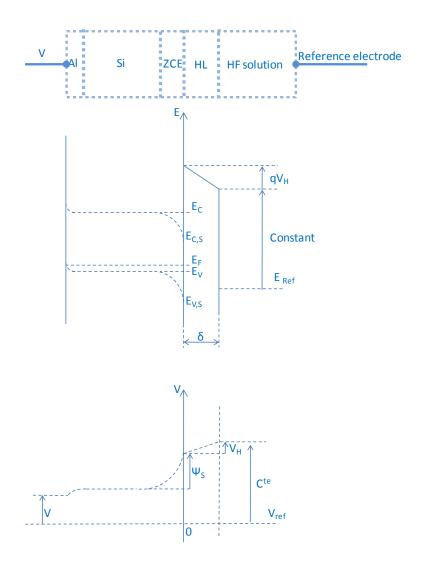

Notre dispositif expérimental est représenté sur la Figure 3. La surface de l'échantillon de silicium en contact avec l'électrolyte est de 0,5 cm² (0,8 cm de diamètre) et la contre-électrode est une grille de platine (ou or) cylindrique, parallèle et assez loin de l'électrode de silicium. Pour relever des caractéristiques I-V dans un milieu électrochimique, un montage bipolaire simple avec deux électrodes ne sera pas suffisant. Il permet uniquement de relever la différence de potentiel entre les deux électrodes, et non le potentiel de chaque électrode (par rapport à une référence commune), en général nécessaire pour une interprétation fiable et complète. Comme une couche de Helmholtz peut être formée sur l'électrode de platine et peut modifier considérablement son potentiel en fonction du temps [Bar80, Shy96], les caractéristiques I-V enregistrées seront en quelque sorte faussées et ne donneront pas la bonne information sur l'électrode de silicium (distribution de potentiel de la jonction silicium/électrolyte) qui nous intéresse. Pour cette raison, une troisième électrode, qui est une électrode de référence Ag/AgCl, est utilisé. Le courant est donc fourni entre l'électrode de travail et la contre-électrode, et le potentiel de l'électrode de travail est mesuré par rapport à

l'électrode de référence en utilisant un sourcemètre Keithley 2602 contrôlé par un programme Labview via une carte GPIB. La connexion électrique ainsi obtenue peut être considérée comme similaire au montage quatre pointes utilisé dans la caractérisation de dispositifs électroniques. Le deuxième avantage de l'électrode de référence est qu'elle peut être placée au plus près de la contre électrode, ce qui permet de s'affranchir de la chute de potentiel dans l'électrolyte qui pourrait devenir importante par rapport à la tension appliquée. D'autre part, le contact face arrière silicium/plaque de cuivre doit être ohmique. Il est assuré par un dépôt d'aluminium sous vide suivie d'un recuit thermique rapide à 700 °C sous atmosphère d'azote. Dans le cas du silicium faiblement dopé, un fort dopage de la face arrière des échantillons est aussi effectué.

Figure 3 Connexion électrique de la cellule d'anodisation électrochimique

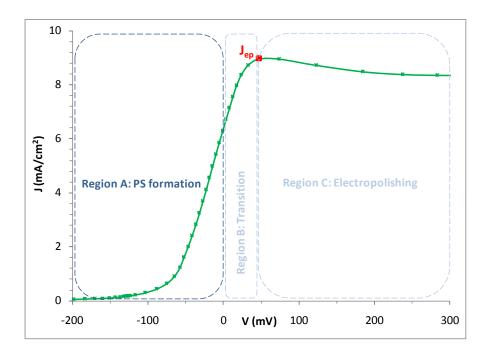

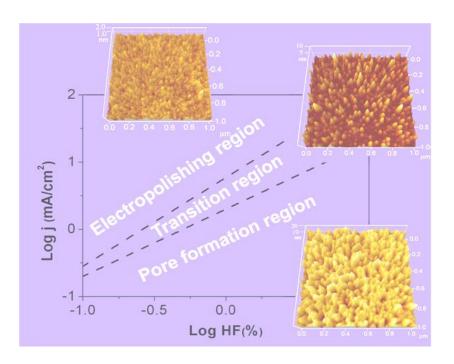

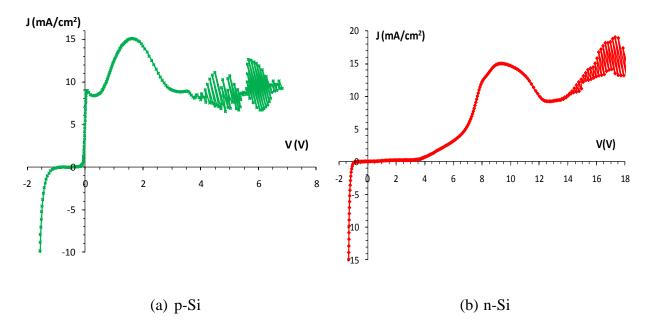

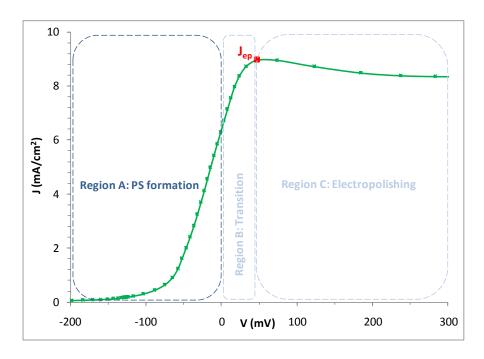

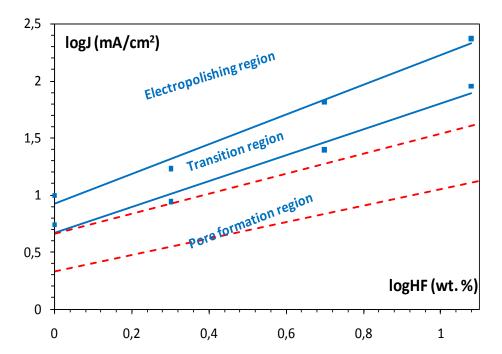

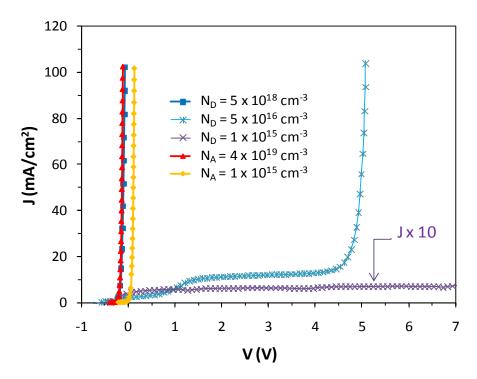

D'après la caractéristique I-V montrée à Figure 4, on peut distinguer trois régimes d'anodisation électrochimique : le régime de porosofication (ou de formation de pores), le régime d'électroplissage (aucune nanostructuration de la surface) et le régime de transition qui est une compétition entre la porosofication et l'électroplolissage. Ces régimes dépendent de la concentration de HF et de la densité de courant appliquée. Par exemple, la formation de Si poreux se fait à forte concentration de HF et à faible densité de courant tandis que l'électroploissage se produit à forte densité de courant et à faible concentration de HF.

**Figure 4** Caractéristique I-V de l'anodisation électrochimique de silicium montrant les trois régimes de porosofication, électropolissage et transition

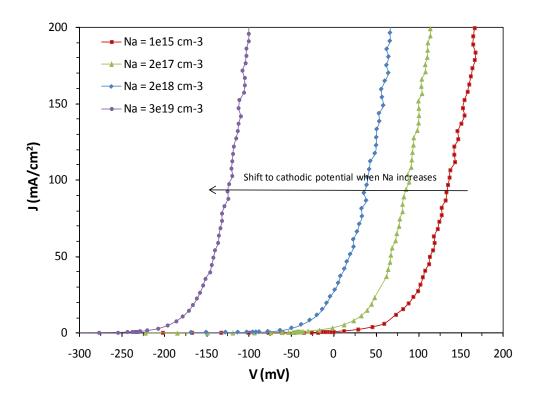

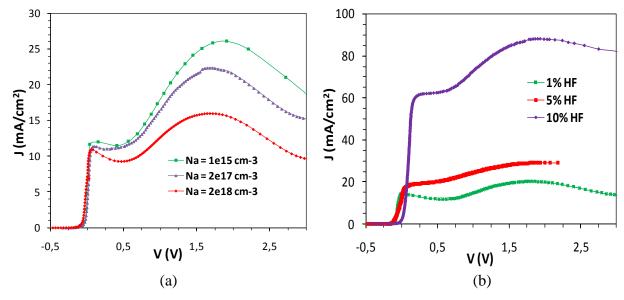

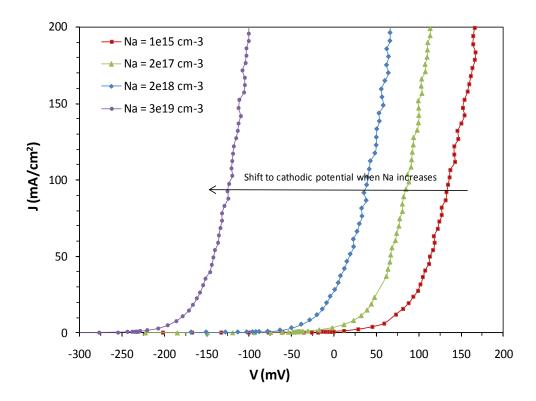

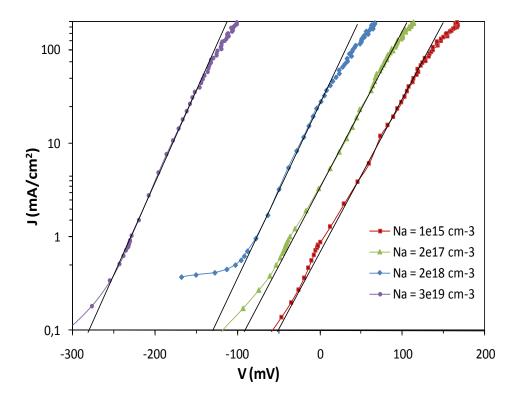

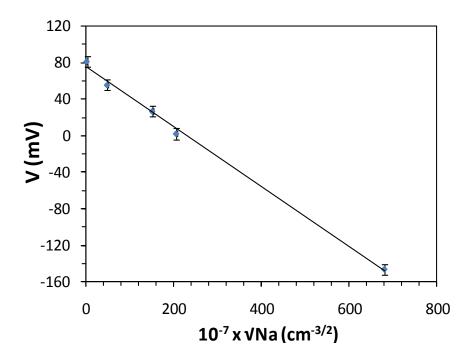

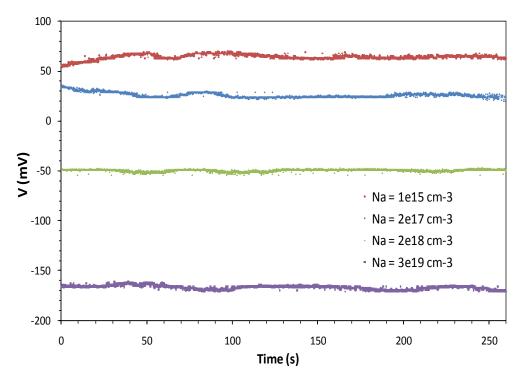

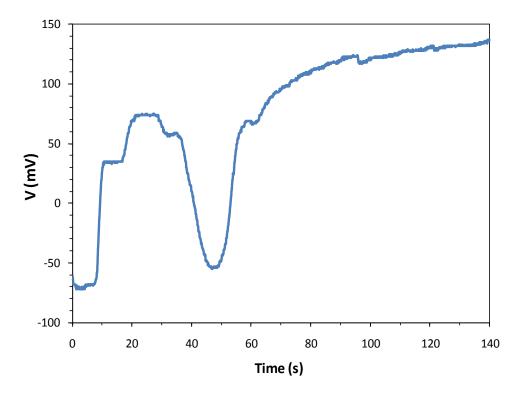

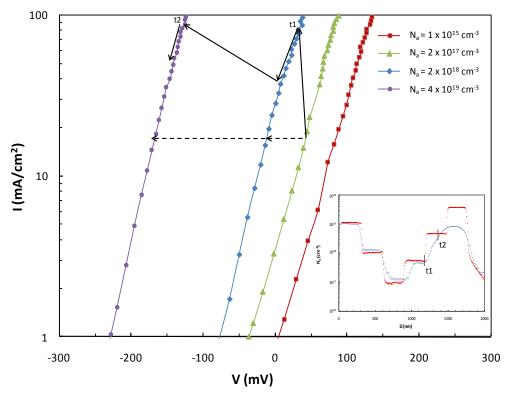

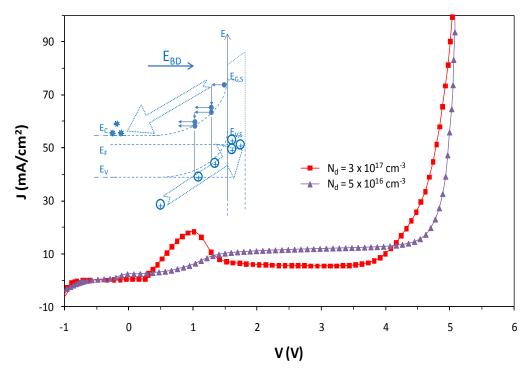

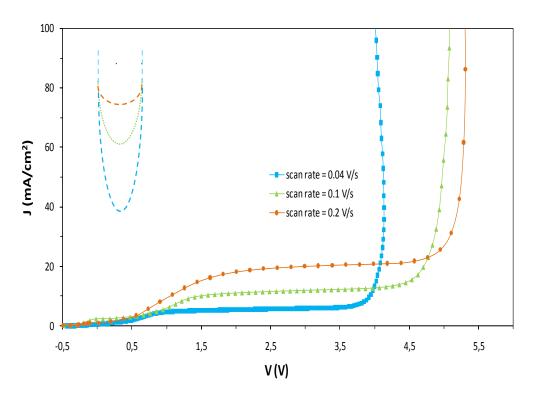

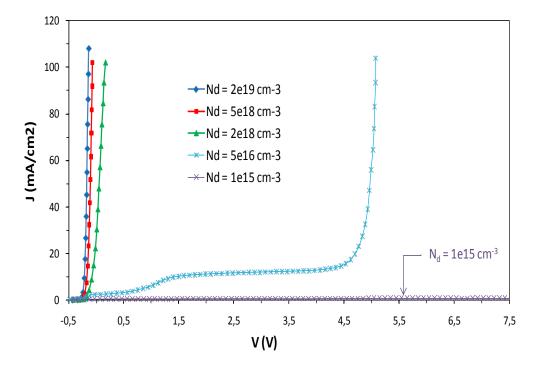

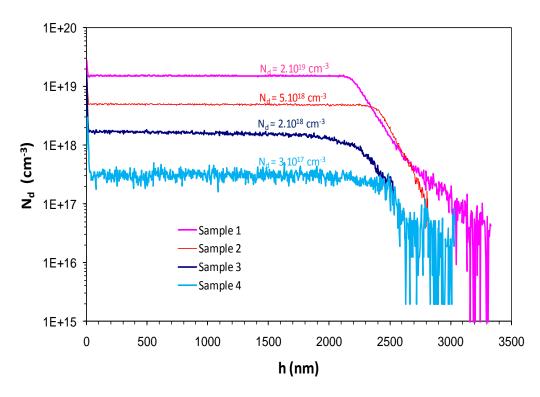

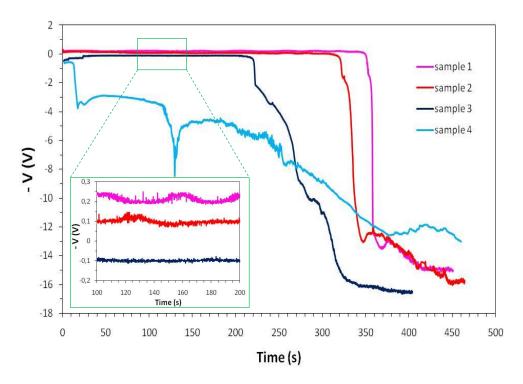

On s'intéresse dans ce travail au régime de formation du Si poreux. Pour le Si de typep, la représentation semi-logarithmique des caractéristiques I-V montre, sur un intervalle de 1 à 100 mA/cm<sup>2</sup>, une variation linéaire de la densité de courant en fonction de la tension avec une pente de 59 mV/décade, en accord avec un contact classique métal/semiconducteur de pente (kT/q) x Ln(10) (où q est la charge élémentaire, k la constante de Boltzmann et la T température absolue). Ce résultat révèle, comme suggéré par plusieurs auteurs [Gas89, Leh00 et Smi92], que le courant au cours de la porosofication de p-Si est déterminé par une émission thermoïonique des trous à travers une barrière Schottky à la surface de la zone de silicium déplètée. Cependant, cela n'explique pas le décalage observé des caractéristiques I-V vers les tensions négatives quand la concentration de dopage du substrat augmente (Figure 5). Gaspard et al. [Gas89] ont attribué ce décalage à une augmentation de la chute de potentiel à travers la couche d'Helmholtz présente à l'interface électrolyte/silicium. Cet effet a été modélisé avec succès en considérant la capacité due à la couche d'Helmholtz en série avec la zone déplétée dans le silicium. Cette approche a été vérifiée expérimentalement et a été à l'origine du développement d'une technique simple d'extraction du profil de dopage dans le silicium de type-p par voie électrochimique. En effet, au cours de l'anodisation d'un échantillon de Si type-p présentant des variations de concentration en dopants en marches d'escalier, les variations de tensions enregistrées peuvent être converties en concentrations de dopants utilisant la relation ci-mentionnée, et l'échelle de temps d'anodisation en profondeur connaissant la vitesse de gravure.

**Figure 5** Caractéristiques I-V de l'anodisation du silicium de type-p dans le HF pour différents concentrations de dopage du substrat

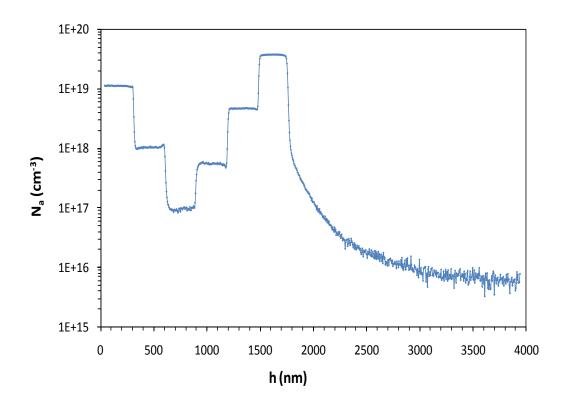

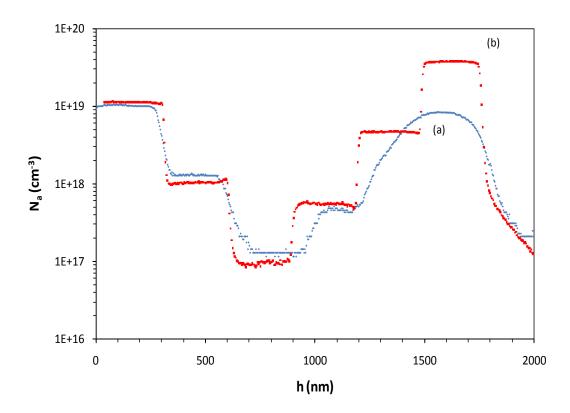

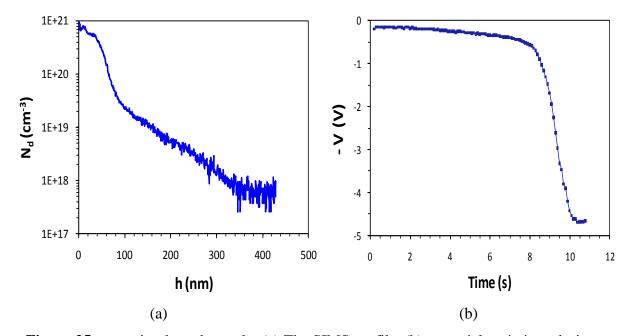

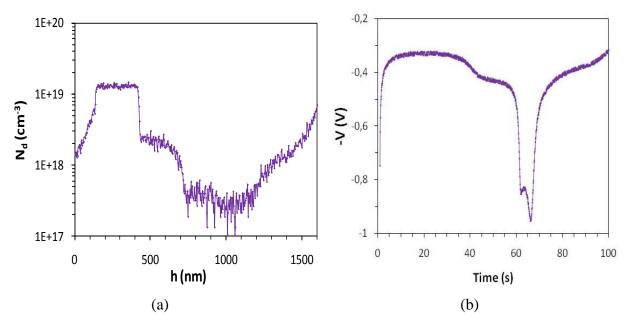

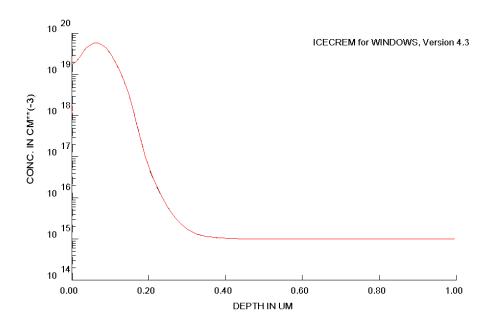

Le profil de dopage obtenu est représenté à la Figure 6 et comparé au profil mesuré avec l'analyse SIMS (spectroscopie de masse d'ions secondaires). Un très bon accord entre la technique électrochimique et la mesure SIMS est obtenu pour la partie descendante du profil (les trois premières marches). On montre également que la résolution en profondeur de cette technique est liée au niveau du dopage et s'approche de celle du SIMS pour les fortes concentrations avec une valeur estimée de 60 nm/décade. Cependant, la technique présente quelques limitations. Elle est d'une part limitée au Si de type-p. D'autre part, elle ne peut pas fournir le bon profil de dopage lorsque le niveau de concentration des impuretés à analyser est inférieure à celui de la couche sous-jacente (partie ascendante du profil où les concentrations de dopage mesurées par la méthode électrochimique ne suivent plus les variations en marche d'escalier). Ce dernier problème peut être expliqué par l'inhomogénéité du front de gravure de la réaction électrochimique.

**Figure 6** Profil de dopage d'un échantillon déterminé par (a) la technique Si poreux et (b) l'analyse SIMS

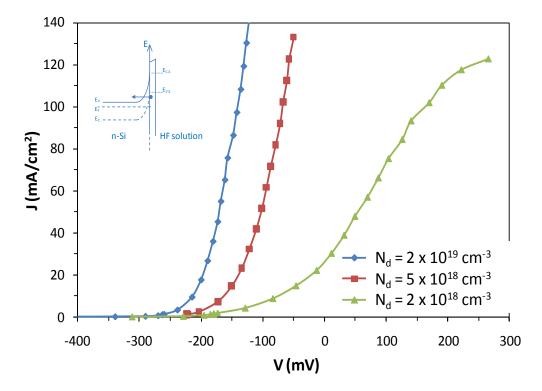

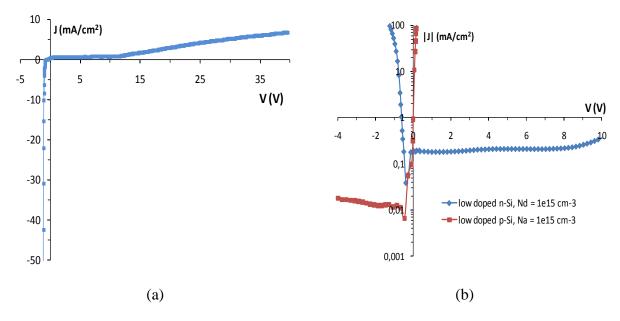

En ce qui concerne l'anodisation du Si de type-n en obscurité, la jonction Si/électrolyte étant en inverse, le passage de courant donnant lieu à la formation du Si poreux ne se produit qu'après claquage de la région de charge d'espace à la surface de l'électrode par un fort champ électrique fournissant ainsi les trous nécessaires à la dissolution du silicium. En fonction de la concentration de dopage et de la tension appliquée, on peut distinguer deux mécanismes de transport de charge à l'origine de ce claquage: l'effet tunnel et l'effet d'avalanche. Les caractéristiques I-V pour le n-Si ont montré elles-aussi un décalage vers les tensions négatives quand la concentration de dopage augmente. Par contre, on n'a pas pu quantifier ce décalage sur toute la gamme de concentration étudiée ce qui rend impossible d'appliquer la technique de profilométrie décrite précédemment au silicium de type-n. D'autant plus, le potentiel d'anodisation, à densité de courant constante et pour une concentration de dopage donnée, n'est pas fixe au cours du temps car il est affecté par un claquage prématuré dû à une rugosité très importante de l'interface Si/Si poreux.

Après avoir étudié la formation du Si poreux, nous nous intéressons dans **le troisième chapitre** à son oxydation. Nous essayons d'optimiser les conditions d'anodisation et d'oxydation permettant d'obtenir un Si poreux oxydé localisé de bonne qualité diélectrique.

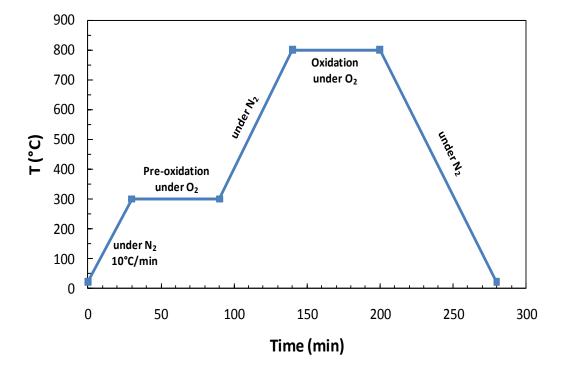

L'oxydation est réalisée dans un four SEMCO standard à oxydation sèche sous pression atmosphérique. Pour oxyder le Si poreux, nous avons utilisé un procédé d'oxydation à deux étapes similaire à celui décrit par plusieurs groupes [Bom88, Lin86 et Mol05]. Dans ce procédé, le Si poreux subit d'abord une étape primordiale de pré-oxydation à des températures assez basses (environ 300 °C) afin de stabiliser sa structure initiale contre toutes transformations irréversibles lors d'un traitement thermique élevé. En effet, pour des températures supérieures à 400 °C, une désorption des atomes d'hydrogène couvrant la couche interne se produit, ce qui entraîne la migration en surface des atomes de silicium et l'effondrement des pores [Gup88]. On se retrouve alors avec une structure composée de larges pores entourés par de murs de silicium très épais dont l'oxydation complète devient très difficile, voire impossible. La pré-oxydation permet donc de résoudre ce problème en couvrant toute la surface interne du Si poreux par une mince couche d'oxyde thermique (1-3 nm d'épaisseur) qui vient stabiliser la texture contre toute restructuration à haute température. En revanche, il est bien évident que cette étape de pré-oxydation n'est pas aussi suffisante pour assurer l'oxydation complète de la couche poreuse, même si un long temps d'oxydation est appliqué. En fait, la température n'est pas assez élevée pour permettre la diffusion de l'oxygène à travers la couche superficielle d'oxyde formée. Pour cela, une deuxième étape d'oxydation à des températures plus élevés est réalisée.

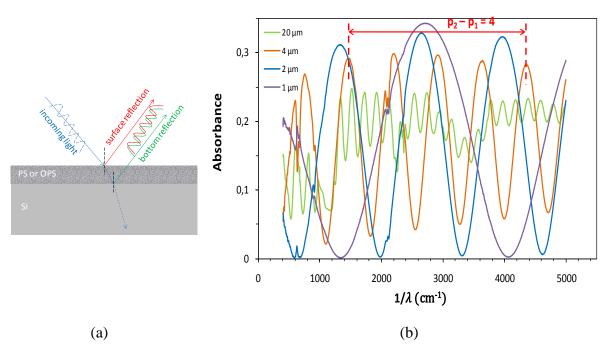

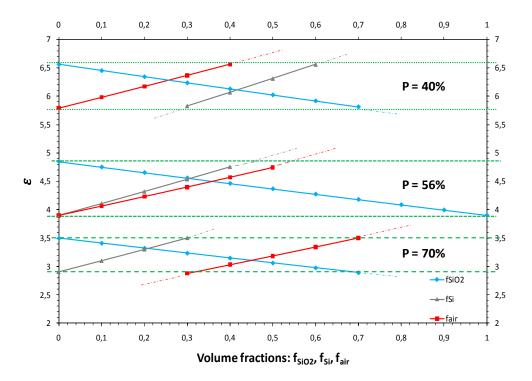

Pour cette étape, l'obtention du Si poreux totalement oxydé (c'est-à-dire n'ayant pas de résidu de Si) et non poreux dépend du choix des paramètres d'anodisation (densité de courant et concentration de HF...) et d'oxydation (température et temps d'oxydation). Le tableau cidessous (Table 1) présente la composition (en Si, SiO<sub>2</sub> et air) de l'oxyde final de plusieurs échantillons obtenus après différents temps et températures d'oxydation et à partir du Si poreux de différentes porosités. Cette composition est donnée sous formes de fractions volumiques calculées à partir de la mesure (par spectroscopie FTIR) de l'indice de réfraction de la couche du Si poreux oxydé et en s'appuyant sur le modèle de Landau-Lifshitz-Looyenga des milieux effectifs. La fraction oxydée, définie comme le pourcentage de silicium de la couche poreuse ayant oxydé, est aussi donnée.

Table 1 Résultats des mesures par spectroscopie FTIR

|         |     | Conditions d  | 'oxydation   | Mesures FTIR |                            |           |                 |  |

|---------|-----|---------------|--------------|--------------|----------------------------|-----------|-----------------|--|

| éch. n° | P % | (T,t)         | $t_{ox}(nm)$ | $f_{SiO2}$   | $\mathbf{f}_{\mathbf{Si}}$ | $f_{air}$ | ξ <sub>ox</sub> |  |

| 1       | 82  | (1000°C,1h)   | 120          | 0.38         | 0                          | 0.62      | 1               |  |

| 2       | 73  |               |              | 0.62         | 0                          | 0.38      | 1               |  |

| 3       | 58  |               |              | 0.87         | 0.03                       | 0.1       | 0.92            |  |

| 4       | 47  |               |              | 0.84         | 0.16                       | 0         | 0.7             |  |

| 5       | 46  | (1000°C,2h)   | 125          | 0.85         | 0.15                       | 0         | 0.7             |  |

| 6       | 65  |               |              | 0.39         | 0.18                       | 0.43      | 0.5             |  |

| 7       | 60  | (800°C,1h) 50 | 50           | 0.56         | 0.15                       | 0.29      | 0.62            |  |

| 8       | 50  |               |              | 0.62         | 0.22                       | 0.15      | 0.55            |  |

| 9       | 58  | (800°C,2h)    | 52           | 0.54         | 0.18                       | 0.27      | 0.57            |  |

| 10      | 57  | (800°C,4h)    | 55           | 0.56         | 0.18                       | 0.26      | 0.58            |  |

Il est bien clair d'après ce tableau que la cinétique d'oxydation du Si poreux dépend à la fois de la température et du temps d'oxydation. On peut remarquer que la fraction oxydée  $\xi_{ox}$  augmente avec la température et sature après 1 heure d'oxydation à 800 °C ou à 1000 °C. Une valeur de saturation de 0,5 à 0,6 (échantillons n° 8, 9 et 10) est enregistrée à 800 °C tandis qu'une oxydation totale ( $\xi_{ox} = 1$ ) est obtenue à 1000 °C (échantillons n° 1, 2 et 3). Cependant, il paraît qu'une oxydation totale de la couche poreuse ne puisse être atteinte que si la porosité initiale est suffisamment élevée. Par exemple, pour les échantillons n° 4 et 5,  $\xi_{ox}$ vaut seulement 0,7 après 1 h ou 2 h d'oxydation à 1000 °C et le matériau final est composé uniquement de silicium et de dioxyde de silicium sans air. Compte tenu du taux d'expansion volumique du SiO<sub>2</sub>, une porosité d'environ 56% (échantillon n° 3) est un optimum théorique corroboré par l'expérience pour assurer une oxydation complète du Si poreux (avoir un oxyde final sans Si résiduel qui pourrait dégrader les propriétés d'isolation électrique et thermique) et obtenir un oxyde avec une porosité minimale. Un oxyde poreux n'est pas préférable car il pourrait provoquer des problèmes lors de processus de fabrication ultérieurs (capture des impuretés et gravure rapide au HF). D'autre part, une telle porosité permet aussi d'éviter toute déformation possible du silicium et le développement des défauts causés par le taux

d'expansion du dioxyde de silicium. Il a été démontré en fait que le Si poreux subit un changement de volume après oxydation (expansion si la porosité est inférieure à 56% et contraction si supérieur) qui pourrait introduire des contraintes élastiques [Barl86, Hol83]. Enfin, il est à noter que même une porosité initiale de 56% ne peut pas éviter un caractère un peu poreux de l'oxyde final avec la présence de cavités d'air nanométriques en raison de la nature chaotique de la structure initiale du poreux. Par conséquent, un recuit à haute température pourrait être envisagé afin d'obtenir un oxyde dense similaire au SiO<sub>2</sub> thermique. Cette dernière étape de densification, telle que proposée par certains auteurs [Bom88, Yon87], est réalisée par un écoulement visqueux de silice et exige des températures supérieures à 1000° C. Pour des raisons de limitation de la température de notre four, nous n'avons pas accompli cette étape.

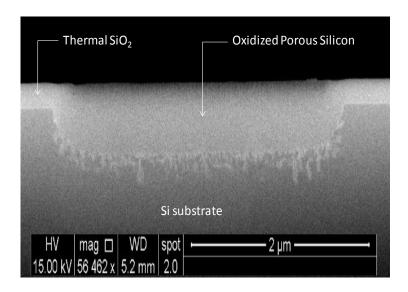

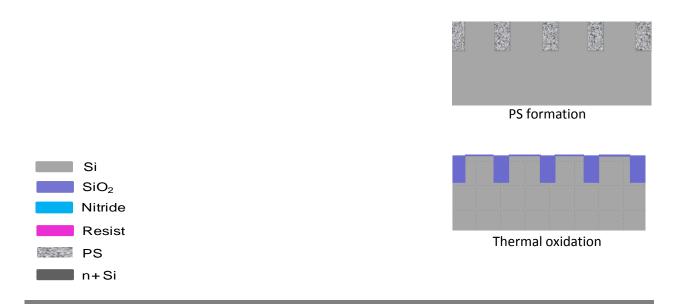

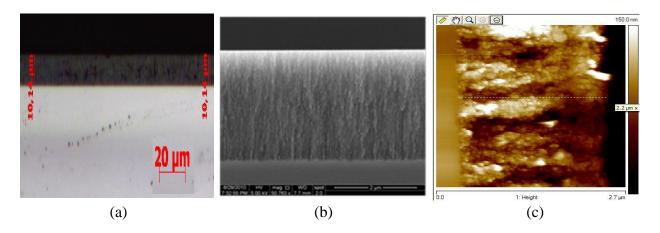

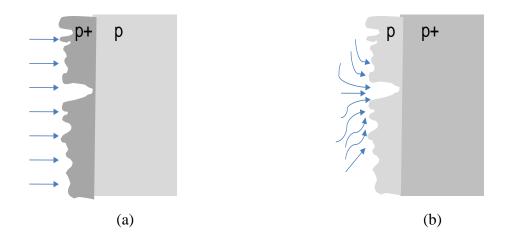

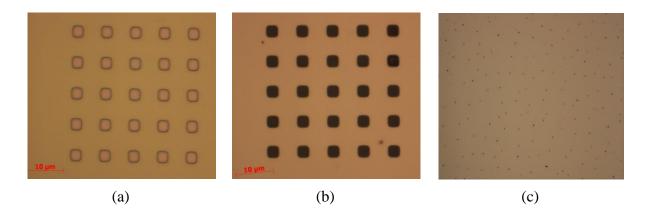

Dans une deuxième partie du chapitre 3, nous mettons en évidence la formation localisée du silicium poreux oxydé (Figure 7) en exploitant la propriété de dépendance de la formation du Si poreux avec la concentration de dopage, déjà étudié au premier chapitre. En effet, un choix judicieux du potentiel d'anodisation permet de rendre poreux sélectivement des régions fortement dopées implantées dans un substrat de silicium faiblement dopé (sans recours à un masque). Ces régions sont ensuite transformées en oxyde par un recuit oxydant.

Par ailleurs, nous donnons quelques recommandations utiles pour la fabrication d'un oxyde final localisé relativement plan et uniforme, tirant profit des études d'optimisation de formation du Si poreux et son oxydation bien contrôlée détaillées ci-avant (dans les parties précédentes). A titre d'exemple, il semble que le silicium de type-n est mieux adapté à être utilisé que le type-p dans la mesure où il présente une plus grande sélectivité pour la formation du Si poreux et qu'il montre moins de variation de la porosité avec la densité de courant ce qui permet d'obtenir une structure poreuse plus homogène en profondeur et d'avoir des résultats plus reproductibles. De plus, outre le réglage des paramètres d'anodisation pour obtenir une porosité de 56%, il est conseillé d'utiliser un régime potentiostatique pour l'anodisation avec une tension appliquée suffisamment faible pour éviter le claquage de la surface de silicium.

Figure 7 Image MEB: formation localisée du silicium poreux oxydé

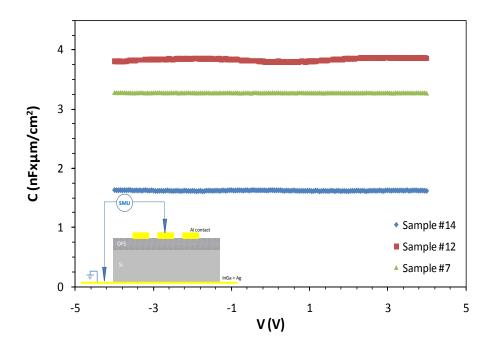

Enfin, on a pu montrer également que la composition du Si poreux oxydé peut être aussi déterminée à partir des mesures électriques capacité-tension C-V complémentaires. Alors que dans le FTIR, on mesure l'indice de réfraction, avec les mesures C-V, on détermine la constante diélectrique de la couche du Si poreux oxydé. Par ailleurs, nous avons montré, à partir de la caractérisation I-V que le Si poreux oxydé peut être considéré comme un bon isolant diélectrique, présentant une résistivité électrique assez élevée ( $\rho = 2.10^{13}~\Omega cm$ ) et un courant de fuite raisonnable (de l'ordre de 1  $\mu m/cm^2$  à une polarisation de 10V).

En conclusion, le Si poreux est un matériau très intéressant qui offre des propriétés prometteuses conduisant à une grande variété d'applications. Dans ce travail, nous nous sommes intéressés à la propriété de dépendance de la formation du Si poreux avec la concentration de dopants. Grâce à l'étude des caractéristiques I-V au cours de l'anodisation électrochimique, il a été constaté que cette dépendance est contrôlée, pour le silicium de typep, par la chute de potentiel à travers la couche de Helmholtz qui est présente à l'interface Schottky électrolyte/silicium polarisée en direct.

Ce dernier résultat a été à l'origine du développement d'une méthode très simple de profilométrie des impuretés dans le silicium de type-p à l'aide de l'anodisation électrochimique. En effet, il a été démontré que pendant l'anodisation à courant constant d'un échantillon de Si de type-p présentant une variation de concentration en dopants en marches d'escalier, les variations de la tension d'anodisation pouvaient être converties en variations de concentration de dopage grâce au modèle ''Schottky + Helmoltz'', et l'échelle de temps

d'anodisation en échelle de profondeur connaissant la vitesse de gravure. Nous avons exploité cette propriété pour former localement du Si poreux oxydé apportant ainsi une précieuse avancée à notre objectif de départ. En effet, nous avons pu vérifier que lorsqu'une plaque de Si avec des régions de différentes concentrations de dopage est anodisée à potentiel constant bien choisi, le courant de dissolution ne circule que dans les zones de dopage les plus élevées et par conséquent le Si poreux est uniquement formé dans ces zones. Nous avons également essayé d'optimiser les procédés d'anodisation et d'oxydation afin d'obtenir un oxyde final de bonne qualité. Néanmoins, la formation du Si poreux oxydé dépend de plusieurs paramètres au cours des trois principales étapes de sa fabrication: l'implantation ionique, l'anodisation électrochimiques et l'oxydation. Par conséquent, il sera nécessaire d'optimiser encore mieux chacune de ces étapes afin d'obtenir un oxyde final présentant des propriétés diélectriques fiables comparable à celles de l'oxyde obtenu par CVD qui est utilisé en STI. Ensuite, pour confirmer la faisabilité de la technique Si poreux pour les technologies CMOS au-delà de 65 nm, des transistors MOS doivent être réalisés puis caractérisés et comparées à ceux fabriquées par STI.

# **Contents**

| GENERAL INTRODUCTION                                        | 1  |

|-------------------------------------------------------------|----|

| CHAPTER 1: STATE OF THE ART                                 | 5  |

| INTRODUCTION                                                |    |

| 1. MINIATURIZATION                                          |    |

| 1.1. MICROELECTRONICS EVOLUTION                             |    |

| 1.2. Miniaturization: a few key figures                     | 9  |

| 1.3. MOSFET SCALING                                         | 10 |

| 2. LIMITATIONS AND CHALLENGES OF SCALING                    | 12 |

| 2.1. Ultrathin oxide: high-k material                       |    |

| 2.2. FIELD OXIDE: CMOS ISOLATION                            | 15 |

| 2.2.1 LOCOS                                                 | 15 |

| 2.2.2 STI                                                   | 16 |

| 2.2.3 STI by PS approach                                    | 18 |

| 2.3. SOI                                                    | 20 |

| 3. POROUS SILICON: FABRICATION, PROPERTIES AND APPLICATIONS | 23 |

| 3.1. Anodization conditions and parameters                  | 24 |

| 3.1.1 Anodization cell                                      | 24 |

| 3.1.2 Electrolyte                                           | 26 |

| 3.1.3 Current density                                       | 27 |

| 3.1.4 Other experimental considerations                     | 30 |

| 3.2. STRUCTURAL PROPERTIES OF PS                            | 30 |

| 3.2.1 Microstructure                                        | 31 |

| 3.2.2 Specific surface area                                 | 33 |

| 3.2.3 Porosity                                              | 34 |

| 3.2.4 Growth rate                                           | 35 |

| 3.3. PS APPLICATIONS                                        | 37 |

| 3.3.1 Optical-optoelectronic applications                   | 38 |

| 3.3.2 Sensor applications                                   | 38 |

| 3.3.3 Micromachining applications                           | 38 |

| CONCLUSION                                                  | 40 |

| CHA           | PTER 2: Investigation of current-voltage                                    |     |

|---------------|-----------------------------------------------------------------------------|-----|

| CHAR          | ACTERISTICS OF SILICON IN HF SOLUTION                                       | .41 |

| INTRO         | DUCTION                                                                     | 43  |

| 1. EX         | PERIMENTAL SET UP                                                           | 44  |

| 1.1.          | EXPERIMENTAL CONDITIONS                                                     | 44  |

| 1.2.          | ELECTRICAL CONNECTION                                                       | 45  |

| 1.3.          | SAMPLE PREPARATION – BACK SIDE OHMIC CONTACT                                | 47  |

| 1.4.          | DESCRIPTION OF SAMPLES                                                      | 47  |

|               | NERAL CURRENT-VOLTAGE CHARACTERISTICS OF SILICON IN H                       |     |

| 2.1.          | ELECTROCHEMICAL REGIONS OF THE SI/HF SYSTEM                                 | 49  |

| 2.1           | .1 Cathaodic polarization                                                   | 50  |

| 2.1           | .2 Anodic polarization                                                      | 50  |

| 2.2.<br>PARAM | ANODIC DISSOLUTION REGIONS IN P-SI AND DEPENDENCE ON THE ANODIZATION METERS | 51  |

|               | IARGE EXCHANGE MECHANISM DURING PS FORMATION OF P-TYFON                     |     |

| 3.1.          | THE ANODIZATION POTENTIAL IS DETERMINED AT THE SI/HF INTERFACE              | 54  |

| 3.2.          | THE "SCHOTTKY BARRIER + HELMOLTZ LAYER" MODEL                               | 56  |

| 3.3.          | THE ANODIZATION POTENTIAL DEPENDENCE TOWARD THE DOPING ENTRATION.           | 59  |

|               | PLICATION: P-TYPE SILICON DOPING PROFILING USING ROCHEMICAL ANODIZATION     | 61  |

| 4.1.          | THE METHOD PRINCIPLE: POTENTIAL VARIATIONS DURING PS FORMATION              | 61  |

| 4.2.<br>PROFI | CONVERSION OF POTENTIAL VARIATIONS DURING ANODIZATION TO DOPING LING.       | 63  |

| 4.3.          | LIMITATION OF PROFILING METHOD BY ELECTROCHEMICAL ANODIZATION               | 65  |

|               | ARGE CARRIER TRANSFER DURING PS FORMATION OF N-TYPE                         |     |

| SILICO        | N                                                                           |     |

| 5.1.          | HIGHLY DOPED N-SI                                                           |     |

| 5.2.          | LOW DOPED N-SI                                                              |     |

| 5.3.          | MODERATELY DOPED N-SI                                                       | 70  |

|               | PLICATION: N-TYPE SILICON DOPING PROFILING USING ROCHEMICAL ANODIZATION     | 73  |

| CONCI         | USION                                                                       | 78  |

| PROP  | PERTIES                                                             | 79  |

|-------|---------------------------------------------------------------------|-----|

| INTRO | DUCTION                                                             | 81  |

| 1. PO | PROUS SILICON OXIDATION PROCESS                                     | 82  |

| 1.1.  | Pre-oxidation                                                       | 83  |

| 1.2.  | TOWARD A COMPLETE OXIDATION OF PS                                   | 84  |

| 1.2   | 2.1 OPS characterization using FTIR                                 | 84  |

| 1.2   | 2.2 Complementary characterization using CV measurements            | 90  |

| 2. FA | BRICATION OF LOCAL OPS                                              | 93  |

| 2.1.  | ELECTROCHEMICAL ANODIZATION                                         | 95  |

| 2.2.  | OXIDATION                                                           | 97  |

|       | ELECTRIC PROPERTIES OF OPS: INVESTIGATION OF CURAGE CHARACTERISTICS |     |

| 3.1.  | Pre-oxidized PS samples                                             | 100 |

| 3.2.  | OXIDIZED PS SAMPLES                                                 | 104 |

| CONCI | LUSION                                                              | 106 |

| GENI  | ERAL CONCLUSION                                                     | 109 |

| APPE  | ENDICES                                                             | 113 |

| REFE  | ERENCES                                                             | 118 |

# General introduction

Device miniaturization has become the main concern of the microelectronic industry from a long period of time. Therefore, researchers are always trying to find innovative solutions for technological challenges by proposing either new materials or new designs or new fabrication processes. For example, the oxide allowing the isolation between devices in an electronic chip has been also scaled down and has then exhibited different technological processes. The latest process which is widely used in the most advanced in-production CMOS (complementary metal oxide semiconductor) technologies is the STI (shallow trench isolation) process. It is based on three main steps: trench etching, filling with CVD (chemical vapor deposited) oxide and planarization by CMP (chemical mechanical polishing), and it came to replace the LOCOS (local oxidation of silicon) process which encountered a primary problem known as bird's beak encroachment that limits the circuit packing density.

However, for sub-65 nm technologies under development, STI begins to show some limitations: voiding and dishing. In fact, filling of narrow trenches with CVD oxide cannot be perfect and voids can possibly be left between active areas. In addition, CMP planarization may only work for the narrow gaps and leads to a non-planar surface that will not be well suited for further lithography steps. An alternative solution, which is based on local anodization of silicon and further oxidation of the formed porous silicon, is proposed to overcome these limitations of voiding and dishing. The approach, in which neither dry etching nor CMP are required, seems to be promising.

In this context, our PhD project is defined. It focuses on the study of porous silicon (PS) in order to take advantage of its interesting properties. The properties and characteristics of this material have been extensively investigated since its discovery six decades ago leading to a large variety of applications. In our work, we will rather interest in the properties of (i) PS formation dependence with silicon doping concentration and (ii) its high rate of oxidation for the application of electrical isolation.

The manuscript is divided into three chapters which are organized in the following manner.

The first chapter or the state of the art chapter introduces the main purpose of our work. It first focuses on the art of miniaturization in microelectronics through some key figures and examples of technological challenges. We describe in particular the different fabrication processes used for electrical isolation of CMOS devices and discuss their

limitations. We propose hence the PS method as an alternative solution that deserves investigation. The chapter also provides an introduction to PS with special emphasis putted on its properties and their dependence on the anodization parameters.

The second chapter is devoted to the well understanding of PS formation through the investigation of current-voltage characteristics of n- and p-type silicon electrodes during electrochemical anodization. It highlights the property of PS formation dependence with silicon doping concentration which is exploited for the application of doping profiling by electrochemical anodization.

The last chapter deals with the oxidation of PS. Electrical and optical characterizations are performed on oxidized PS in order to determine its structural and dielectric properties and thus optimize its fabrication process. A particular attention is also given to the fabrication of local oxidized PS.

# Chapter 1: State of the art

### **Introduction**

In this introductory chapter, we first present a brief summary of the microelectronic evolution and its continual need for miniaturization. We give some examples of important limitations and technological challenges for the most advanced technologies. This leads us to introduce both the FIPOS process which seems to be a promising alternative to the STI process in CMOS isolation, and the SOI technology based on PS formation which becomes to be intensively investigated by the semiconductor industry. In a second time, a special interest is given to the porous silicon material. After presenting experimental conditions allowing PS formation, we go through the structural properties of this material giving an overview of their characterization and underlining their dependence on the anodization parameters.

#### 1. Miniaturization

In this first part, we present a historical review of major devices and achievements in the field of the microelectronic industry which is still ruled up to now by the law of miniaturization or scaling.

#### 1.1. Microelectronics evolution

Since the "big-bang" of electronics in 1947 when J. Bardeen, W. Brattain, and W. Shockley discovered for the first time that when electrical contacts were applied to a crystal of germanium, the output power was larger than the input [Wei73], much research efforts of scientists and engineers have devoted to the developing of semiconductor devices. This quest led to the emergence of a new branch of electronics, called the semiconductor industry, which experienced tremendous growth over the following decade announced by the fabrication of several different types of innovative devices going from the first commercial silicon junction transistor produced by Texas Instruments in 1954 to the first MOS (metal oxide silicon) transistor built at Bell Labs in 1960 [Sif04].

The year 1959 was marked by the development of the planar process which resulted in the invention of integrated circuits (ICs). From that date, one could say that the capabilities of the transistor begun to be fully utilized with the large number of devices integrated within the silicon and the vast variety of circuit functions implemented. Later, the need of producing ICs with higher yield and hence lower cost, greater performance and enhanced reliability have pushed manufacturers to do efforts to improve the fabrication process and propose new logic-style families such as transistor-transistor logic (TTL), diode-transistor logic (DTL) in 1962 and complementary metal oxide semiconductor (CMOS) in 1963 [Pav08]. The increased complexity of ICs and the great requirement of developing circuits suitable for generalized applications instead of designing each IC to serve a single application have led then to the apparition of the first microprocessor in 1971 namely the 4004 with 2800 transistors and 60000 instructions per second [Gil90].

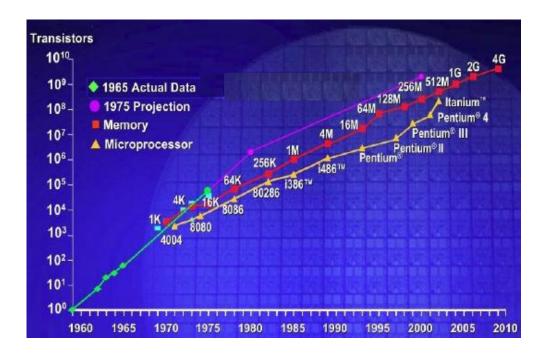

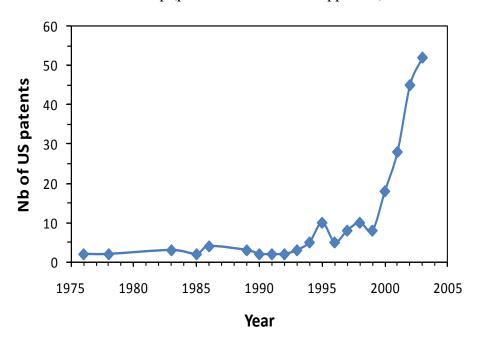

This achievement have boosted the growth of the semiconductor industry and opened the way to fascinating improvements of microprocessors with higher performance and higher reliability, driven by the maturation of the manufacturing process and supported by the continual scaling of transistors. In this context, Gordon Moore, one of the founders of Intel, predicted in 1965 that the number of transistors on a silicon wafer would double every eighteen months [Moo65] before altering his projection in 1975 to a doubling every two years [Moo75]. Anyway, this prediction, referred to as Moore's Law, has held good for more than four decades and is expected to hold true for at least another as illustrated in Figure 1.

**Figure 1** Illustration of Moore's law through the evolution of Intel microprocessors and memories<sup>1</sup>

### 1.2. Miniaturization: a few key figures

Device miniaturization has become then the major concern of the semiconductor industry for a long time. Indeed, it results in chips that are (i) faster (of higher operation frequency), (ii) cheaper to make as it is possible to fit more integrated circuits on a silicon wafer and (iii) of lower power consumption because the charge carriers have simply a shorter distance to move.

For example, the cost per bit of memory chips has halved every 2 years for successive generations of dynamic random access memories (DRAMs). The device speed has improved by a few orders of magnitude since 1959 and digital ICs are able now to perform numerical

<sup>&</sup>lt;sup>1</sup> According to the Intel web site: www.intel.com

computation at terabit-per-second rates. The energy dissipated per logic gate has decreased by over one million times since 1959 [Sze01].

The minimum device dimension of an integrated circuit, also called the minimum line width, has been reduced at an annual rate of about 13% i.e., a reduction of 30% every 3 years. The half-pitch (i.e., half the distance between identical features in an array of a memory cell), to which the name of the technology node is associated, was decreased for example from 0.8  $\mu$ m in the year 1989 to 0.13  $\mu$ m in 2002 and will shrink to 22 nm around 2015 according to the prediction of the International Technology Roadmap for Semiconductors (ITRS). The Table 1 below gives scaling examples of some physical and electrical parameters.

**Table 1** The technology generation from 1989 to 2002<sup>2</sup> and future scaling trends adapted from 2009 ITRS<sup>3</sup>

| Year of production                        | 1989 | 1999 | 2002 | 2010 | 2012 | 2015 | 2020  |

|-------------------------------------------|------|------|------|------|------|------|-------|

| Technology node                           | 800  | 180  | 90   | 45   | 32   | 22   | 12    |

| Physical gate length (nm)                 | -    | 130  | 50   | 18   | 22   | 15.3 | 10.7  |

| Equivalent gate oxide thickness: EOT (nm) | -    | -    | -    | 1.4  | 1.2  | 1.1  | 0.8   |

| Supply voltage: $V_{DD}(V)$               | 5    | 2    | 1.8  | 1    | 0.9  | 0.81 | 0.68  |

| Clock frequency (MHz)                     | 40   | 1200 | 1600 | 2500 | 4000 | 6600 | 12500 |

### 1.3. MOSFET scaling

Since the beginning of the microelectronics era, it was noticeable that the connections among active devices of a circuit presented an important obstacle for increasing circuit performance. The invention of the integrated circuit considerably alleviated interconnect-related problems by bringing the interconnects on-chip reducing then the interconnect length and thus decreasing significantly the delay and the power consumption. Over the next decades, on-chip interconnects were not the major focus of the IC design process, as performance improvements reaped from scaling the devices were much greater than any degradation caused by the interconnects [Pav08].

<sup>&</sup>lt;sup>2</sup> Intel microprocessors

<sup>&</sup>lt;sup>3</sup> According to the ITRS web site: www.itrs.net

Here, we try to take the example of the metal oxide semiconductor field effect transistor (MOSFET) as it is the dominant device in ULSI (ultra large scale integration) ICs and as it can be scaled to smaller dimensions than other types of devices [Sze01]. The table above gives an overview of this drastic scaling rate through the gate length.

Electrical characteristics of the MOS transistor can be described mainly by two parameters: the saturation current  $I_{ON}$  and the leakage current  $I_{OFF}$  [Web05]. A low current  $I_{OFF}$  will help limit the consumption and the static power dissipation ( $P_s = V_{DD} \, x \, I_{OFF}$ ) in a circuit while the operation frequency or the switching speed of logic gates will be governed by (i) the resistance and capacity of interconnection wires and (ii) the delay of the transistor  $\tau$  given by

$$\tau = \frac{V_{DD} \times C_{gate}}{I_{ON}}$$

where  $C_{gate}$  is the gate capacitance.

For the transistor device itself (without interconnections), It is noticeable that a high current  $I_{ON}$  allows a high switching frequency but it is not a sufficient condition. Indeed, according to the last equation and the expression of the drain current-voltage  $I_D$ - $V_D$  at saturation<sup>4</sup>, one can note that if the current increases by a variation of the gate capacitance  $C_{gate}$  (i.e. by reducing the gate oxide thickness or increasing the width W of the transistor), the intrinsic delay will remain constant. Scaling of the gate length L can however improve  $I_{ON}$  and thus  $\tau$ . It is on this simple principle which improves both the integration density and the performance of transistors that is based Moore's Law.

Nevertheless, reducing L is still associated with some unwanted parasitic or side effects referred to as short channel effects which mainly cause degradation of  $I_{OFF}$ . To avoid such a problem, Dennard [Den74] has proposed a scaling rule for optimizing the device performance which consists of scaling down all dimensions and voltages of the MOSFET so that the internal electric fields are kept the same. This constant field scaling is shown in Table 2 along with the real scaling used in the semiconductor industry [Sze06].

-

<sup>&</sup>lt;sup>4</sup>  $I_{ON} = I_{Dsat} = \mu C_{gate} \frac{W}{2L} V_{Dsat}^2$  where  $\mu$  is the carriers mobility, W and L are the gate width and length, respectively.

**Table 2** MOSFET scaling rules according to Dennard [Den74] and real scaling [Web05, Bak10, Ngu09]

|                                                   | Scaling factor             |                                 |  |  |  |  |

|---------------------------------------------------|----------------------------|---------------------------------|--|--|--|--|

| Parameter                                         | <b>Dennard's law</b> (α<1) | Actual $(\alpha < \lambda < 1)$ |  |  |  |  |

| Gate length, width: L,W                           | α                          | α                               |  |  |  |  |

| Gate oxide thickness: tox                         | α                          | α                               |  |  |  |  |

| Junction depth: X <sub>j</sub>                    | α                          | α                               |  |  |  |  |

| Substrate doping: N <sub>A</sub> , N <sub>D</sub> | $1/\alpha$                 | $\lambda/lpha^2$                |  |  |  |  |

| Electric field: E                                 | 1                          | $\lambda/lpha$                  |  |  |  |  |

| Supply voltage: $V_{DD}$                          | α                          | λ                               |  |  |  |  |

| ON current: I <sub>ON</sub>                       | 1                          | $\lambda^2/\alpha^2$            |  |  |  |  |

| Active power: P                                   | $lpha^2$                   | $\lambda^3/lpha$                |  |  |  |  |

| Transistor delay: τ                               | α                          | $\lambda^2/lpha$                |  |  |  |  |

## 2. Limitations and challenges of scaling

Challenges of new technologies beyond 100 nm include for example the formation of ultra shallow source/drain junction with low sheet resistance which can be achieved by employing low energy and high dosage ion implantation. In addition, as the dimension of the device size scales down, the delay time (RC) resulting from multilevel interconnection increases significantly and hence low speed operation is achieved. Consequently, to overcome this problem, both high-conductivity metals, such as copper Cu (1.7  $\mu\Omega$ cm compared with 2.7  $\mu\Omega$ cm of aluminum Al), and low-dielectric constant (low-k) insulators, such as organic (polyimide) or inorganic (fluorine doped oxide) materials should be used instead of the conventional Al and oxide [Sze01]. Another important issue is the gate material: since the mid-1970s, the metal (Al) MOSFET gate is replaced by the polysilicon gate [Wol99] that offers a self-aligned structure but as the gate lengths were scaled down, the resistance of the polysilicon lines became too large to be effective in their secondary role as a local interconnect (even when they were doped as heavily as possible). That's why it became necessary to use a metal silicide layer on top surface of the poly film. The Ti-silicide process

had then been widely used until it encountered limitations for deep sub-micron technologies because the sheet resistance of a  $TiSi_2$  line is found to increase with decreasing line width.  $CoSi_2$  and NiSi processes seem to be the promising candidates.

Many other important issues have also paid great attention when MOSFET scaling is in question in order to ensure a well optimized performance of the device. Among these issues, one can also mention tailoring of the channel doping profile in both lateral and vertical directions to control the threshold voltage, and adjusting the formation of the p/n-type wells and the drain structure to avoid parasitic effects and inter device leakage currents. For more details, it can be referred for example to [Wol99, Sze01]. In the following sections, we have chosen to discuss in more details scaling limitations related to two features: the gate oxide and the field oxide. In fact, the first is widely studied recently at least in our laboratory in the frame of several theses while the second will be useful to introduce the general context of our work.

# 2.1. Ultrathin oxide: high-k material

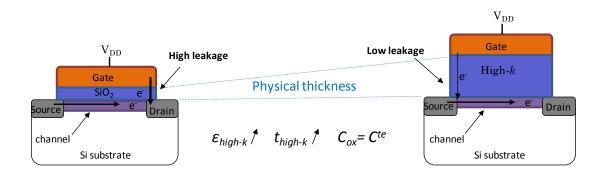

MOSFET transistors have been continually scaled since they were first introduced and hence the gate oxide, made by thermally grown silicon dioxide  $SiO_2$ , had also to be progressively thinner to maintain the device performance. However, for the most advanced technologies, since the gate length shrank below 130 nm, the gate oxide thickness had to be reduced around 2 nm. This seems to be a fundamental limitation because the gate-to-channel tunneling leakage current becomes very high (approximately as great as the off-state source-to-drain leakage current of about 10 nA/ $\mu$ m<sup>2</sup> [Wol99]) leading infeasible to build high performance logic MOSFETs.

For this reason, to allow the scaling of gate lengths (below 100 nm) and permit further miniaturization of devices, high-k dielectric materials such as aluminum oxide  $Al_2O_3$  ( $\epsilon=9$ ), tantalum pentoxide  $Ta_2O_5$  ( $\epsilon=26$ ), zirconium oxide  $ZrO_2$  ( $\epsilon=25$ ) and hafnium oxide  $HfO_2$  ( $\epsilon=24$ ) are suggested as alternative candidates for the gate dielectric to replace silicon dioxide. With these materials, thicker dielectric layers can be used resulting in less carrier tunneling with maintaining the same MOSFET capabilities (Figure 2). In fact, it can be possible to achieve the same equivalent oxide thickness EOT as required for  $SiO_2$ , according to:

$$C_{ox} = C_{high-k} \rightarrow \text{EOT} = \frac{\varepsilon_{ox}}{\varepsilon_{high-k}} \times t_{high-k}$$

where  $C_{ox}$ ,  $C_{high-k}$  are the gate oxide capacitances with  $SiO_2$  and the high-k dielectric, respectively,  $t_{high-k}$  is the thickness of the high-k dielectric,  $\epsilon_{ox}$  and  $\epsilon_{high-k}$  are the relative permittivities of  $SiO_2$  and the high-k, respectively. For example, a high-k gate insulator with a thickness  $t_{high-k}$  of 10 nm and a dielectric constant  $\epsilon_{high-k}$  of 20 will behave in the same way in a MOSFET as a  $SiO_2$  layer with a thickness of 2 nm.

Figure 2 Reducing the tunneling current using high-k material

However, one of the drawbacks of using high-k dielectrics is that if they are deposited directly on silicon they tend to have a high level of interface states [Sze06,Ngu09]. The interface states density can be reduced by growing a thin layer of silicon dioxide (1-2 atomic layers i.e. 0.8-1.6 nm thickness) on the silicon to passivate the surface. This interfacial layer will however limit the highest possible gate stack capacitance or, equivalently, the minimum achievable EOT value as this latter will never be less than that of the high-k layer according to the equation below:

$$\frac{1}{C_{equ}} = \frac{1}{C_{ox}} + \frac{1}{C_{high-k}} \rightarrow EOT = t_{ox} + \frac{\varepsilon_{ox}}{\varepsilon_{high-k}} \times t_{high-k}$$

A bilayer approach necessarily limits the use of high-k materials and let the scaling of the gate dielectric a greatest challenge to be investigated in order to find the ideal gate dielectric stack that seems to be the good compromise between many factors like compatibility with the actual fabrication process, reducing EOT and obtaining high quality Si/dielectric interface.

### 2.2. Field oxide: CMOS isolation

The dominant technology for MOSFET is the CMOS (complementary MOSFET) technology, in which both n-channel and p-channel MOSFETs (called NMOS and PMOS, respectively) are provided on the same chip. CMOS technology is particularly attractive for ULSI circuits because it has the lowest power consumption of all IC technologies. One of the tasks of CMOS miniaturization is to reduce the isolation distance between NMOS and PMOS. This isolation is of primary importance for suppressing leakage current between the devices (NMOS and PMOS) that must be kept electrically isolated from one another.

One of the simplest methods of isolation is to fabricate the CMOS such that a reverse-bias pn-junction is formed between the transistors. Oppositely doped regions (n-well adjacent to p-well) can be electrically isolated by tying the n-region to the most positive potential in the circuit and the p-region to the most negative. As long as the reverse-bias is maintained and the breakdown voltage is not exceeded for all operating conditions, a small reverse diode saturation current accounts for the leakage current. However, as this leakage current is directly proportional to the junction area, for relatively large p- and n-regions in modern devices, junction isolation alone becomes not adequate [Bak10]. Hence, a second method of isolation is proposed which is related to the formation of a thick dielectric region between transistors. The region without the thick dielectric, where transistors reside, is known as the active area. The relatively thick oxide that is formed between the active areas is called the field oxide (FOX). There are two general approaches of forming FOX regions which are extensively used in the semiconductor industry: LOCOS and STI.

# 2.2.1 LOCOS

Local oxidation of silicon (LOCOS) isolation was developed in the early 1970s and it remained, for its simplicity, the conventional isolation process for CMOS ICs during 30 years until these technologies reached the 0.35 µm generation [Fra04,Wol99]. In LOCOS, a silicon nitride layer (100-200 nm) is deposited and patterned over a thin pad oxide (10-50 nm) to define active and field oxide areas. The pad oxide serves as a stress relief layer; it diminishes the stress-induced dislocations that a thick nitride exerts in silicon. Nitride acts as a diffusion barrier for oxygen; areas under nitride will not be oxidized. LOCOS process flow is pictured in Table 3.

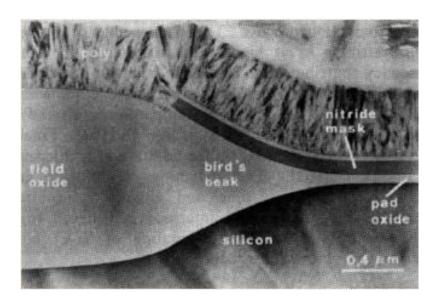

The primary limitation of LOCOS is the lateral extension of the oxide that encroaches into the active area and thereby reduces the achievable circuit packing density. This problem is known as bird's beak encroachment as the lateral oxide feature resembles in cross-section a bird's beak (Figure 3). A thinner pad oxide would help minimize bird's beak but at the expense of silicon damage from nitride stress.

Figure 3 TEM picture of a bird's beak obtained by using classical LOCOS [Cla84]

Moreover, LOCOS requires a high temperature and a long time process which can result in significant diffusion of previously introduced dopants. The resulting non planar topography is also a matter that makes subsequent optical lithography (depth-of-focus problems) and deposition steps not easy (e.g. in multi-level metallization for advanced ICs, via-hole etching and sputtering become difficult because holes will be of different depths). Recessed LOCOS [Fra04] with additional etching step had been used to make the surface more planar after oxidation resulting in approximately equal surface heights for oxide and silicon. The shallow trench isolation (STI) technology can avoid all these problems and has become the mainstream technology for isolation, precisely in IC generation beyond 0.35  $\mu$ m.

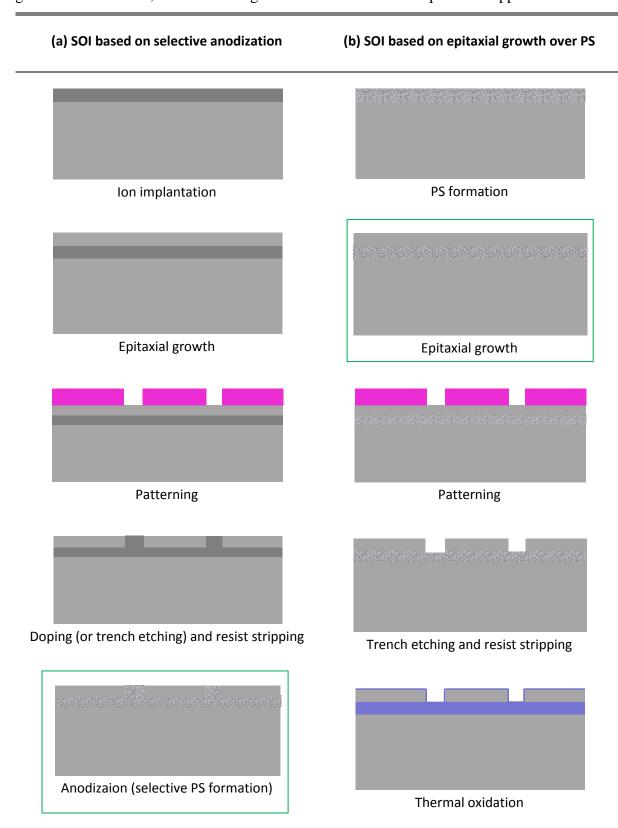

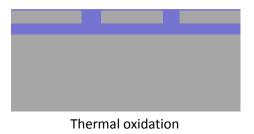

### 2.2.2 STI

Table 3 shows the process sequence of forming a shallow trench isolation structure. In STI, there are four main steps: after patterning, trenches are etched and filled with oxide deposited by CVD (chemical vapor deposition) to form the FOX region. CMP (chemical mechanical polishing) is finally used to remove the oxide on the nitride and to get a flat

surface. Due to its high resistance to polishing, the nitride acts as a stop-layer for the CMP process. After the polishing, the nitride layer and the oxide layer can be removed by phosphoric H<sub>3</sub>PO<sub>4</sub>, and hydrofluoric HF acids, respectively. It should be mentioned that the planarization step is helpful for subsequent patterning and planarization in the multilevel interconnection processes.

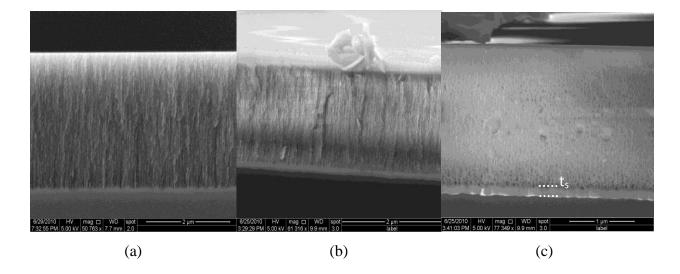

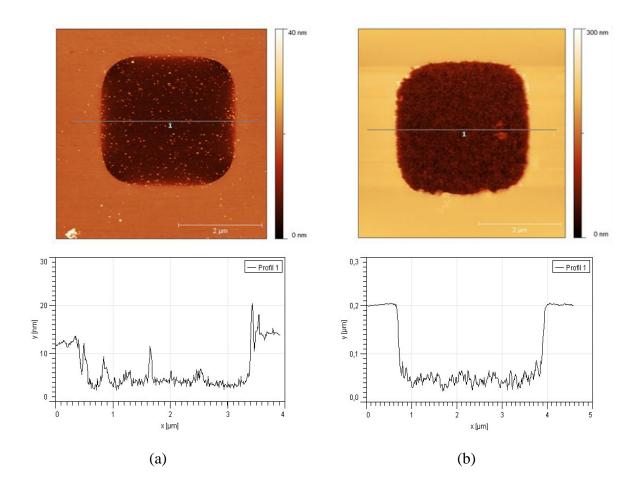

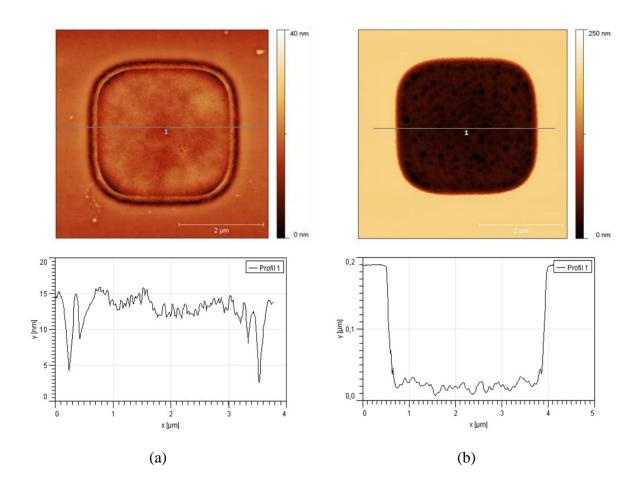

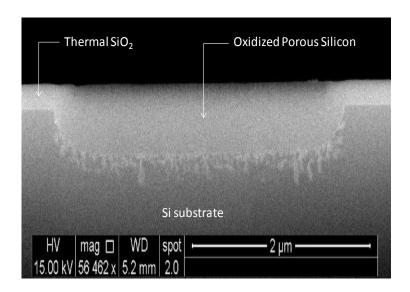

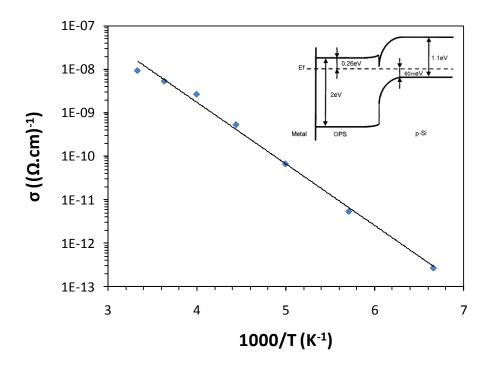

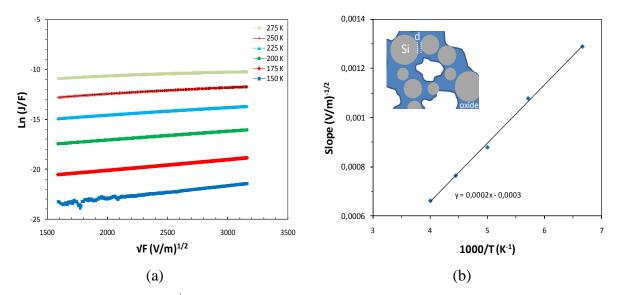

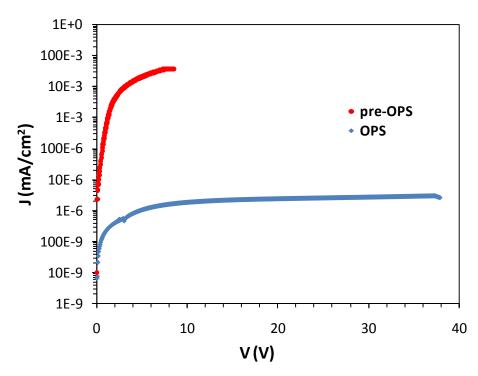

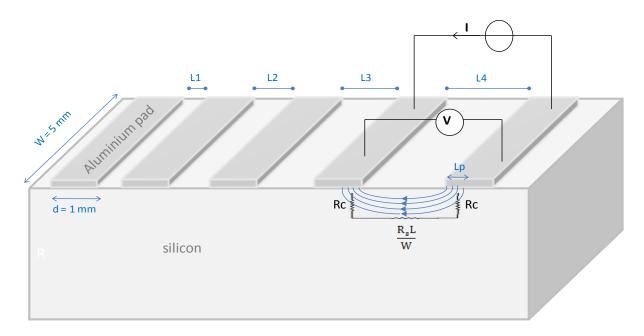

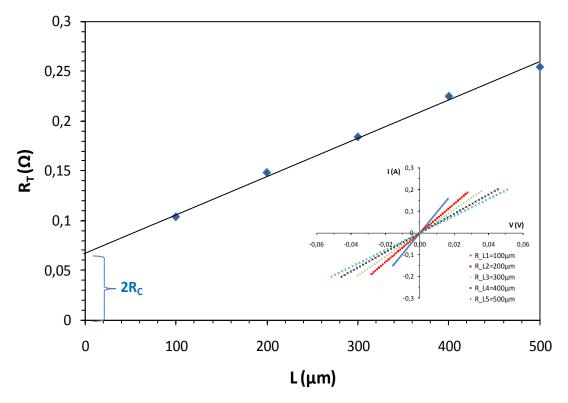

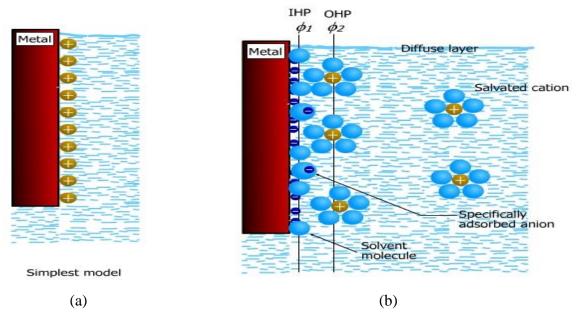

From a processing perspective, STI is complex but it has overcome LOCOS problems and brought interesting benefits to CMOS fabrication. Since the isolation material is deposited by CVD, it does not need high and long time temperature process. So, it has a relatively low thermal budget, avoids unwanted dopant diffusion and eliminates wasting area from bird's beak lateral extent. The process takes also advantage of CMP, which offers planarity of the final structure.