# Modes de défaillance induits par l'environnement radiatif naturel dans les mémoires DRAMs: étude, méthodologie de test et protection

A. Bougerol

# ▶ To cite this version:

A. Bougerol. Modes de défaillance induits par l'environnement radiatif naturel dans les mémoires DRAMs: étude, méthodologie de test et protection. Micro et nanotechnologies/Microélectronique. Université de Grenoble, 2011. Français. NNT: . tel-00611100

# HAL Id: tel-00611100 https://theses.hal.science/tel-00611100

Submitted on 25 Jul 2011

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# UNIVERSITÉ DE GRENOBLE

# **THÈSE**

Pour obtenir le grade de

# DOCTEUR DE L'UNIVERSITÉ DE GRENOBLE

Spécialité : Micro et Nano Électronique

Arrêté ministériel: 7 août 2006

Présentée par

# Antonin BOUGEROL

Thèse dirigée par Régis Leveugle

préparée au sein du Laboratoire TIMA dans l'École Doctorale «Électronique, Électrotechnique, Automatisme et Traitement du Signal»

Modes de défaillance induits par l'environnement radiatif naturel dans les mémoires DRAMs : étude, méthodologie de test et protection.

Thèse soutenue publiquement le **16 mai 2011**, devant le jury composé de :

# M. Régis LEVEUGLE

Professeur à l'Université de Grenoble, Grenoble-INP, Directeur de Thèse

#### M. Patrick GIRARD

Directeur de Recherche au CNRS, Université Montpellier II, Rapporteur

#### M. Jean-Michel PORTAL

Professeur à l'Université de Provence, Rapporteur

#### M. Pascal FOUILLAT

Professeur à l'Université Bordeaux I, Directeur de l'UMR IMS, Président

### **Mme Véronique FERLET-CAVROIS**

Ingénieur à l'ESA, Membre

# M. Florent MILLER

Ingénieur à EADS IW, Membre

# M. Patrick HEINS

Ingénieur à AIRBUS, Invité

"La valeur d'une idée dépend de son utilisation."

Thomas Edison

# Remerciements

Au terme de ces travaux effectués au sein du centre de recherche "EADS Innovation Works" (IW) du groupe EADS, à Suresnes, en collaboration avec le laboratoire TIMA de l'Université de Grenoble, je tiens à remercier :

Monsieur Régis LEVEUGLE, professeur à l'Université de Grenoble et directeur de cette thèse, pour la confiance qu'il m'a témoignée tout au long de cette étude, ses conseils judicieux et son entière disponibilité;

Messieurs Patrick GIRARD et Jean-Michel PORTAL, respectivement Directeur de Recherche au CNRS à Université Montpellier II et Professeur à l'Université de Provence, pour avoir accepté d'être rapporteur de ce travail et pour leurs commentaires pertinents ;

Monsieur Pascal FOUILLAT, Professeur à l'Université Bordeaux I et Directeur de l'UMR IMS, pour m'avoir fait l'honneur d'être président du jury ;

Madame Véronique FERLET-CAVROIS et Monsieur Patrick HEINS, experts radiations respectivement à l'Agence Spatiale Européenne (ESA) et à AIRBUS, pour avoir accepté de participer au jury et apprécié ce travail ;

Monsieur Florent MILLER, responsable de l'équipe "Semiconductor and Equipment Dependability" à EADS IW, pour son suivi et son aide précieuse tout au long de ce travail dans le cadre de mon activité d'ingénieur de recherche;

Madame Nadine BUARD, responsable du département "Electronic Systems" d'EADS IW pour son soutien, sa confiance, et sa participation à la soutenance ;

Monsieur Thierry CARRIERE, expert radiation chez ASTRIUM, pour m'avoir encouragé à me lancer dans cette aventure ;

Messieurs Rémi GAILLARD et Patrick POIROT, consultants, pour leurs conseils avisés;

L'ensemble des collègues avec lesquels il est (a été) particulièrement agréable de travailler : Richard DUFAYEL, Bruno FOUCHET, Nicolas GUIBBAUD, Sabrine HOUSSANY, Aurore LUU, Florian MOLIERE, Sébastien MORAND, Katell MOREAU, Vincent ROUET, Cécile WEULERSSE;

Ma famille, en particulier ma femme Laetitia.

# Table des matières

| REMERCIEMENTS                                                                                   | 5        |

|-------------------------------------------------------------------------------------------------|----------|

| TABLE DES MATIÈRES                                                                              | 7        |

| LISTE DES ACRONYMES                                                                             | 11       |

| INTRODUCTION                                                                                    | 13       |

| CHAPITRE I - CONTEXTE ET ÉTAT DE L'ART                                                          | 17       |

| I.A LES MÉMOIRES DYNAMIQUES                                                                     | 17       |

| I.A.1 Présentation générale                                                                     |          |

| I.A.1.1 La famille des DRAMs                                                                    |          |

| I.A.1.2 Performances.                                                                           |          |

| I.A.2 Cellules mémoire élémentaires                                                             |          |

| I.A.2.1 Principe du stockage                                                                    |          |

| I.A.2.2 Les différents types de capacité                                                        |          |

| I.A.3 Circuits périphériques                                                                    | 24       |

| I.A.3.1 Principe d'accès aux cellules                                                           | 24       |

| I.A.3.2 Circuits de redondance                                                                  | 28       |

| I.B Environnements radiatifs naturels et effets sur les circuits intégrés                       |          |

| I.B.1 Les environnements radiatifs naturels                                                     |          |

| I.B.1.1 L'environnement spatial                                                                 | 30       |

| I.B.1.2 L'environnement atmosphérique.                                                          | 32       |

| I.B.2 Mécanismes d'interaction physiques                                                        |          |

| I.B.2.1 Interactions ion-silicium.                                                              | 33       |

| I.B.2.2 Interactions neutron-silicium et collection de charges                                  | 34       |

| I.B.3 Les effets singuliers                                                                     |          |

| I.B.3.1 Les "Single Event Upsets"                                                               | 36       |

| I.B.3.2 Les "Single Event Functional Interrupts"                                                | 37       |

| I.B.3.3 SEL et autres effets                                                                    |          |

| I.C CARACTÉRISATION DE LA SENSIBILITÉ DES CIRCUITS INTÉGRÉS AUX EFFETS SINGULIERS               |          |

| I.C.1 Exigences de fiabilité                                                                    |          |

| I.C.2 Moyens de test classiques                                                                 |          |

| I.C.2.1 Tests radiatifs accélérés                                                               |          |

| I.C.2.2 Contraintes des tests radiatifs accélérés.                                              |          |

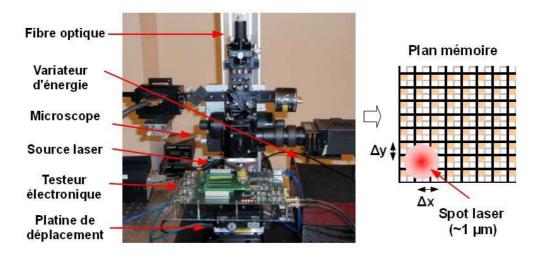

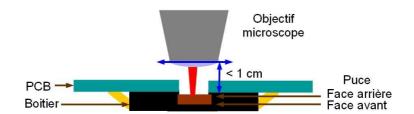

| I.C.3 Faisceaux laser impulsionnels  I.C.3.1 Mécanismes physiques d'interaction photon-silicium | 43       |

| I.C.3.2 Principe et contraintes du test laser                                                   | 43<br>44 |

| I.D Conclusion.                                                                                 |          |

| CHAPITRE II - ÉTUDE DES MODES DE DÉFAILLANCE DES PLANS MÉMOIRE DES D                            |          |

|                                                                                                 |          |

| II.A SENSIBILITÉ AUX RADIATIONS DES PLANS CAPACITÉ                                              |          |

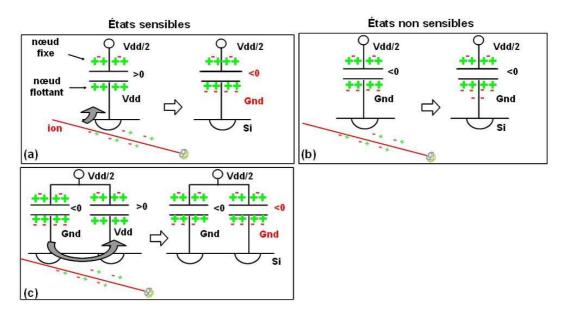

| II.A.1 Mécanismes de SEU induits par une particule ionisante                                    |          |

| II.A.1.1 SEU par decharge de la certule                                                         |          |

| II.A.1.2 Sizo par perturbation d'une righe de données                                           |          |

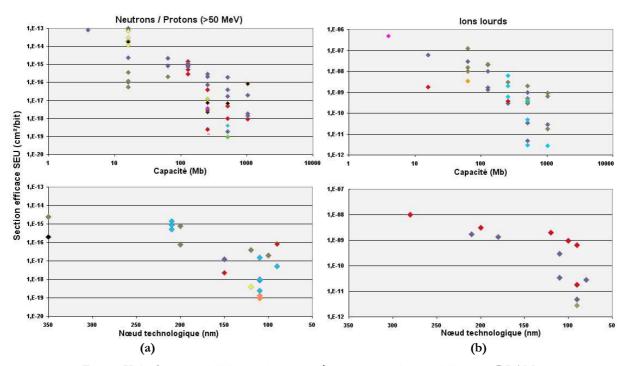

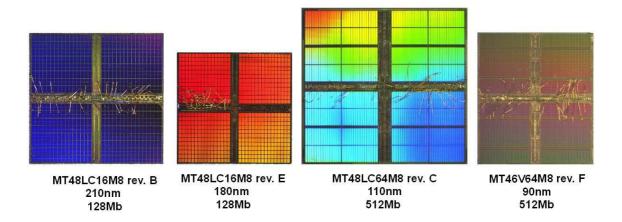

| II.A.2.1 Synthèse et analyse de données bibliographiques                                        |          |

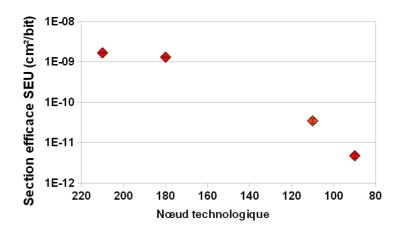

| II.A.2.2 Mesures réalisées sous faisceaux.                                                      |          |

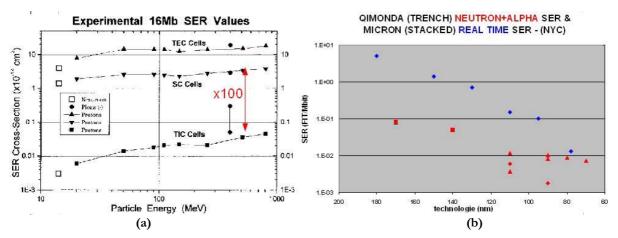

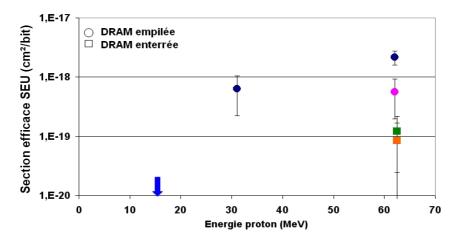

| II.A.3 Niveaux de sensibilité selon le type de cellules                                         |          |

| II.A.3.1 Synthèse et analyse de données bibliographiques                                        |          |

| II.A.3.2 Mesures réalisées sous faisceaux.                                                      |          |

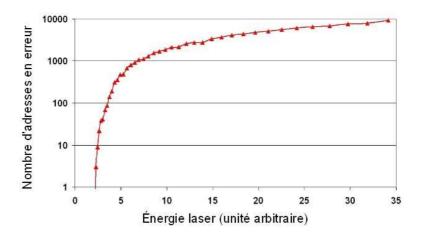

| II.B UTILISATION DU LASER SUR LES CELLULES DRAMS                                                | 60       |

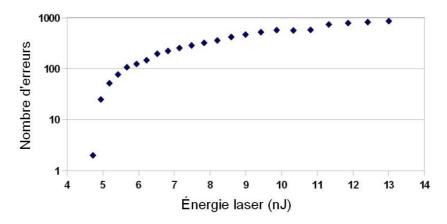

| II.B.1 Effets du laser sur les cellules DRAMs                                                   | 60       |

| II.B.1.1 SEUs induits par une impulsion laser                                                   | 60       |

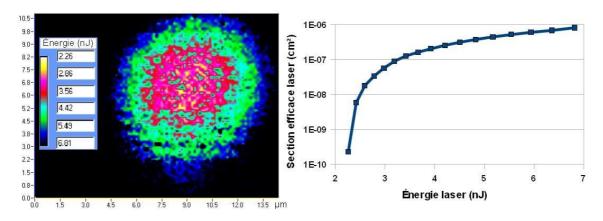

| II.B.1.2 Zone de sensibilité laser d'une cellule                                                |          |

| II.B.2 Informations technologiques révélées par laser                                           | 62       |

| II.B.2.1 Obtention du nœud technologique                                                                                                                                                                                                                                                                 |       |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| II.B.2.2 Obtention de l'agencement des cellules.                                                                                                                                                                                                                                                         |       |

| II.C DÉTERMINATION DU MOTIF DE TEST LE PLUS SENSIBLE.                                                                                                                                                                                                                                                    |       |

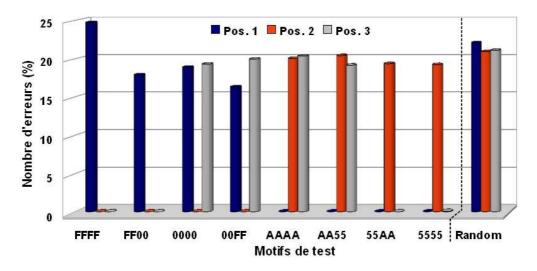

| II.C.1 Influence des motifs sur la sensibilité                                                                                                                                                                                                                                                           | 65    |

| II.C.1.1 Immunité des capacités DRAMs déchargées                                                                                                                                                                                                                                                         |       |

| II.C.1.2 Problèmes inhérents aux motifs "logiques"                                                                                                                                                                                                                                                       |       |

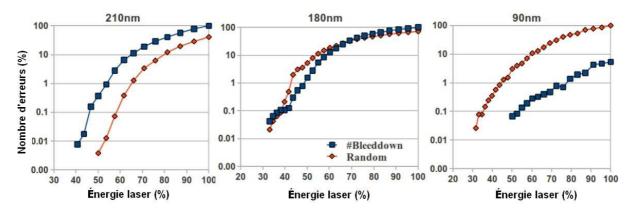

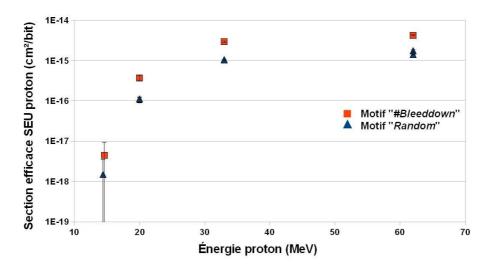

| II.C.2 Comparaison des sensibilités obtenues avec les motifs "#Bleeddown" et "Random"                                                                                                                                                                                                                    | 69    |

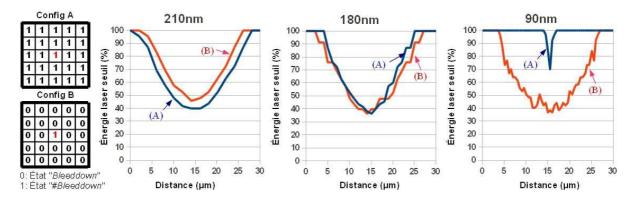

| II.C.2.1 Variation de sensibilité selon le mécanisme de collection ou de transfert de charges                                                                                                                                                                                                            |       |

| II.C.2.2 Résultats de tests laser et accélérés.                                                                                                                                                                                                                                                          |       |

| II.D Conclusion.                                                                                                                                                                                                                                                                                         | 74    |

| CHAPITRE III - ÉTUDE DES MODES DE DÉFAILLANCE DES CIRCUITS PÉRIPHÉRIQUE                                                                                                                                                                                                                                  | S DES |

| DRAMS                                                                                                                                                                                                                                                                                                    |       |

|                                                                                                                                                                                                                                                                                                          |       |

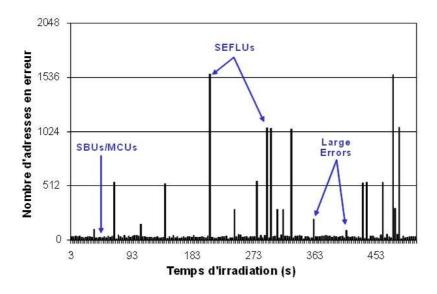

| III.A SENSIBILITÉ AUX RADIATIONS DES CIRCUITS PÉRIPHÉRIQUES DES DRAMS                                                                                                                                                                                                                                    |       |

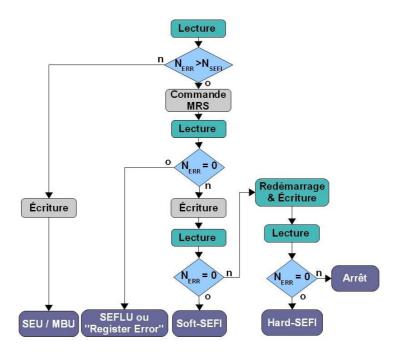

| III.A.1 Problématique des SEFIs dans les DRAMs                                                                                                                                                                                                                                                           |       |

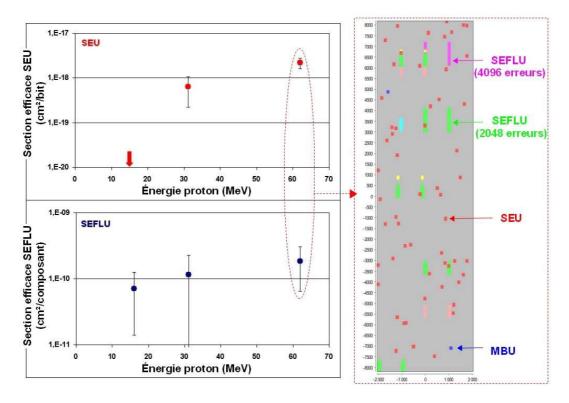

| III.A.1.1 Signatures d'événements SEFI en accélérateur                                                                                                                                                                                                                                                   |       |

| III.A.1.2 Problèmes liés à la caractérisation des SEFIs                                                                                                                                                                                                                                                  |       |

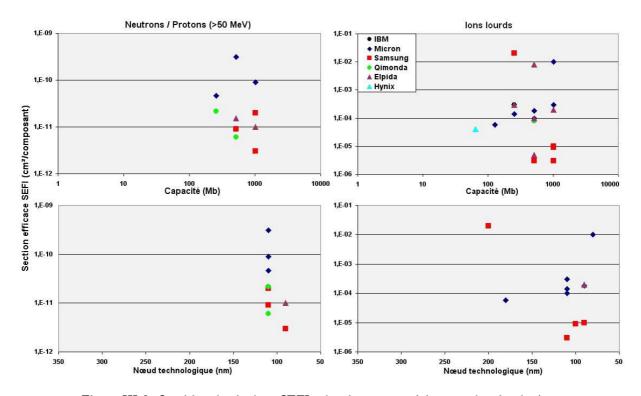

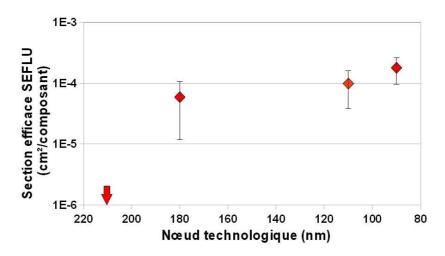

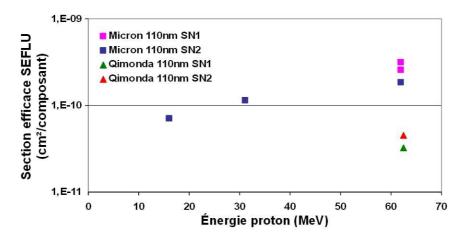

| III.A.2 Niveau de sensibilité et évolution avec l'intégration technologique                                                                                                                                                                                                                              |       |

| III.A.2.1 Synthèse de résultats bibliographiques                                                                                                                                                                                                                                                         |       |

| III.A.2.2 Tests expérimentaux aux ions lourds.                                                                                                                                                                                                                                                           |       |

| III.B UTILISATION DU LASER POUR L'ÉTUDE DES SEFIS                                                                                                                                                                                                                                                        |       |

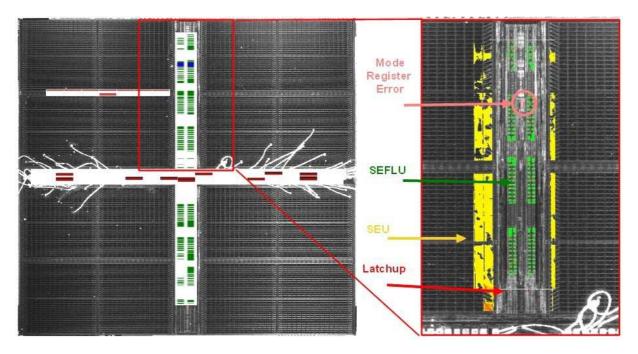

| III.B.1 Détermination des zones et des types de SEFIs                                                                                                                                                                                                                                                    |       |

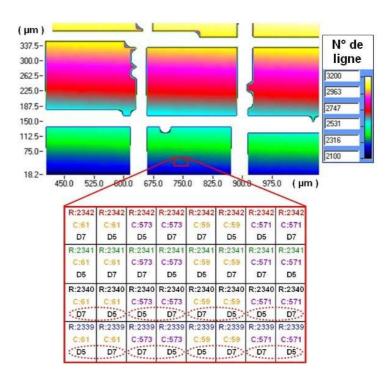

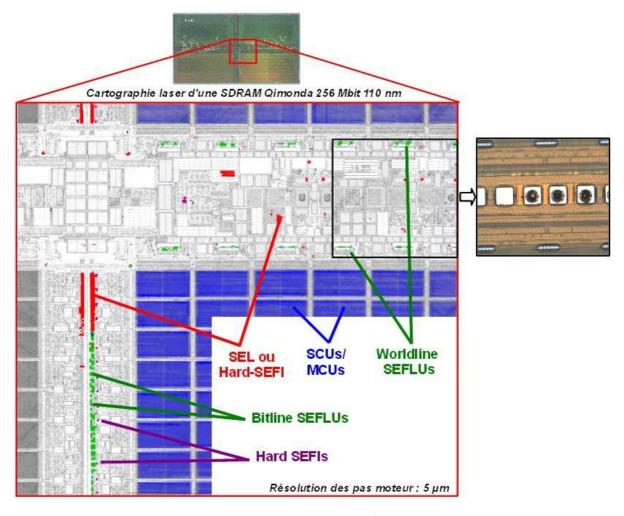

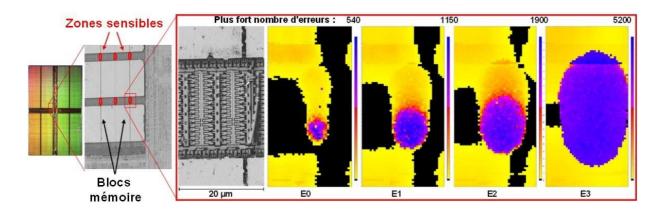

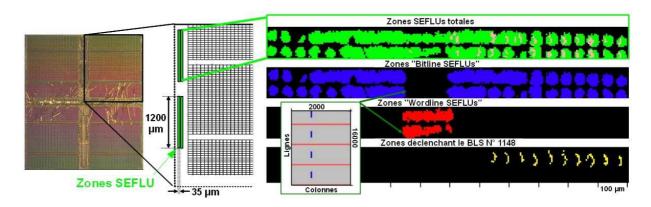

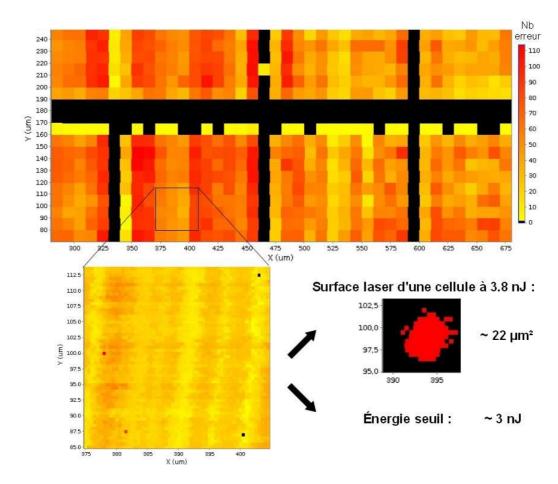

| III.B.1.1 Cartographie laser d'une SDRAM Qimonda 110 nm                                                                                                                                                                                                                                                  |       |

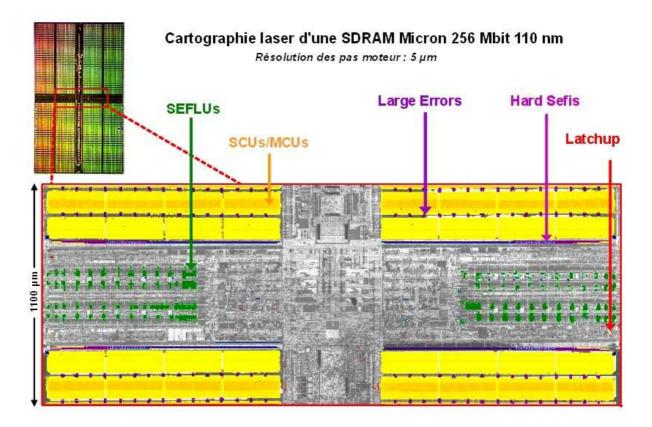

| III.B.1.2 Cartographie laser d'une SDRAM Micron 110 nm                                                                                                                                                                                                                                                   |       |

| III.B.2 Étude d'effets particuliers                                                                                                                                                                                                                                                                      |       |

| III.B.2.1 Les effets "Large Errors"                                                                                                                                                                                                                                                                      |       |

| III.C Proposition d'un nouveau modèle de fautes : les "Single Event Fuse-Latch Upsets".                                                                                                                                                                                                                  |       |

|                                                                                                                                                                                                                                                                                                          |       |

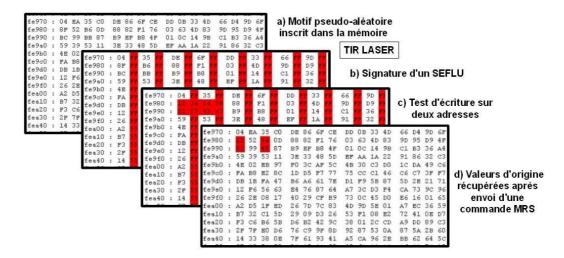

| III.C.1 Particularités des SEFLUsIII.C.1.1 Singularité comportementale des SEFLUs                                                                                                                                                                                                                        |       |

| III.C.1.2 Agencement des SEFLUs au sein de la mémoire                                                                                                                                                                                                                                                    |       |

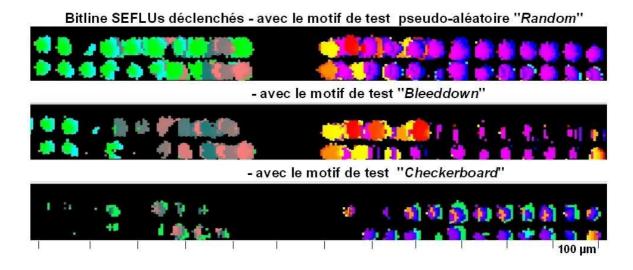

| III.C.2 Influence du motif de test sur la détection des SEFLUs                                                                                                                                                                                                                                           |       |

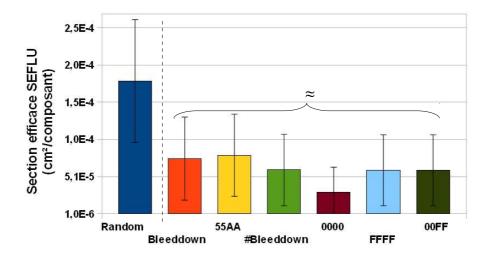

| III.C.2.1 Mesures en accélérateur de particules des sensibilités SEFLUs selon le motif de test                                                                                                                                                                                                           |       |

| III.D Conclusion                                                                                                                                                                                                                                                                                         |       |

|                                                                                                                                                                                                                                                                                                          |       |

| CHAPITRE IV - PROPOSITION D'UNE MÉTHODOLOGIE DE TEST                                                                                                                                                                                                                                                     | 105   |

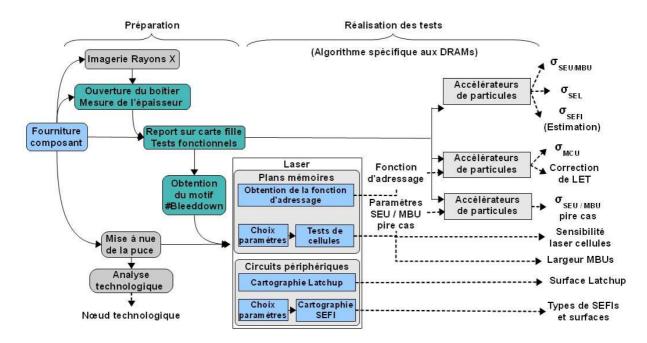

| IV.A Présentation de la méthodologie                                                                                                                                                                                                                                                                     | 104   |

| IV.A.1 Limites des méthodologies actuelles.                                                                                                                                                                                                                                                              |       |

| IV.A.2 Vue générale de la méthodologie                                                                                                                                                                                                                                                                   |       |

|                                                                                                                                                                                                                                                                                                          |       |

| IV.A.3 Prérequis liés aux équipements de test                                                                                                                                                                                                                                                            |       |

| 1 1 12 1 12 1 12 1 12 1 12 1 12 1 12 1 12 1 12 1 12 1 12 1 12 1 12 1 12 1 12 1 12 1 12 1 12 1 12 1 12 1 12 1 12 1 12 1 12 1 12 1 12 1 12 1 12 1 12 1 12 1 12 1 12 1 12 1 12 1 12 1 12 1 12 1 12 1 12 1 12 1 12 1 12 1 12 1 12 1 12 1 12 1 12 1 12 1 12 1 12 1 12 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 |       |

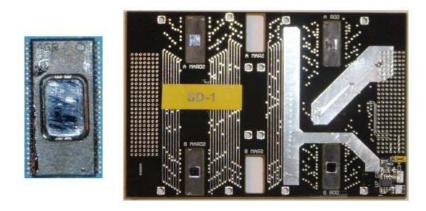

| IV.B.1 Analyses du composant                                                                                                                                                                                                                                                                             |       |

| IV.B.1.1 Imagerie aux rayons X                                                                                                                                                                                                                                                                           |       |

| IV.B.1.2 Mise à nue de la puce.                                                                                                                                                                                                                                                                          |       |

| IV.B.1.3 Analyse technologique                                                                                                                                                                                                                                                                           |       |

| IV.B.2.1 Ouverture du boîtier                                                                                                                                                                                                                                                                            |       |

| IV.B.2.2 Report et tests fonctionnels                                                                                                                                                                                                                                                                    |       |

| IV.B.2.3 Obtention du motif "#Bleeddown"                                                                                                                                                                                                                                                                 |       |

| IV.C RÉALISATION DES TESTS.                                                                                                                                                                                                                                                                              |       |

| IV.C.1 Tests laser des plans mémoire                                                                                                                                                                                                                                                                     |       |

| IV.C.1 Tests taser des plans memotre                                                                                                                                                                                                                                                                     |       |

| IV.C.1.2 Sensibilité laser des cellules                                                                                                                                                                                                                                                                  |       |

| IV.C.2 Tests laser des circuits périphériques.                                                                                                                                                                                                                                                           |       |

| IV.C.2.1 Tests de sensibilité aux SELs.                                                                                                                                                                                                                                                                  |       |

| IV.C.2.2 Cartographies SEFIs.                                                                                                                                                                                                                                                                            |       |

| IV.C.3 Tests en accélérateur de particules                                                                                                                                                                                                                                                               |       |

| IV D Conclusion                                                                                                                                                                                                                                                                                          | 132   |

|                                                                                                                                                                                                                                                                                                          | 1 7/  |

| CHAPITRE V - PROPOSITION D'UNE SOLUTION DE TOLÉRANCE AUX FAUTES.       | 135 |

|------------------------------------------------------------------------|-----|

| V.A TECHNIQUES DE PROTECTION USUELLES                                  | 135 |

| V.B DESCRIPTION DE LA TECHNIQUE PROPOSÉE                               | 136 |

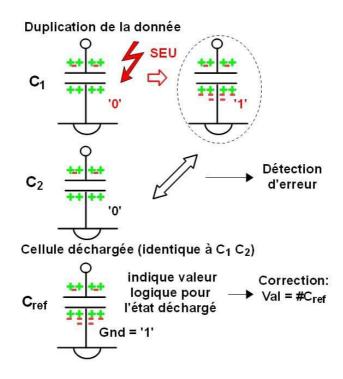

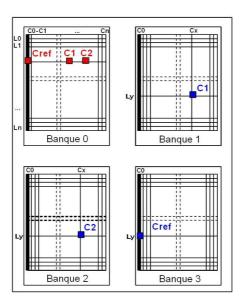

| V.B.1 Utilisation de la propriété d'insensibilité des cellules         | 136 |

| V.B.2 Possibilités d'implantation                                      | 138 |

| V.C MISE EN ŒUVRE ET VALIDATION                                        | 140 |

| V.C.1 Développement d'un contrôleur matériel tolérant aux fautesfautes | 140 |

| V.C.2 Tests laser et accélérés                                         | 141 |

| V.C.3 Performances                                                     | 142 |

| V.D CONCLUSION.                                                        | 143 |

| CONCLUSION GÉNÉRALE                                                    | 145 |

| PUBLICATIONS ET ACTIVITÉS                                              | 149 |

| RÉFÉRENCES                                                             | 151 |

| LISTE DES FIGURES                                                      | 159 |

| LISTE DES TABLEAUX                                                     | 160 |

# Liste des acronymes

| Terme     | Description                                       | Première occurrence |

|-----------|---------------------------------------------------|---------------------|

| BLS       | Bitline SEFLU                                     | Page 89             |

| COTS      | Commercial Off-The-Shelf                          | Page 39             |

| DDR SDRAM | Double-Data-Rate SDRAM                            | Page 18             |

| DRAM      | Dynamic Random Access Memory                      | Page 13             |

| DUT       | Device Under Test                                 | Page 45             |

| IEEE      | Institute of Electrical and Electronics Engineers | Page 53             |

| EADS      | European Aeronautic Defense and Space Company     | Page 13             |

| EASA      | European Aviation Safety Agency                   | Page 38             |

| FAA       | Federal Aviation Administration                   | Page 38             |

| IP        | Intellectual Property                             | Page 140            |

| JEDEC     | Joint Electron Devices Engineering Council        | Page 18             |

| LET       | Linear Energy Transfer                            | Page 34             |

| MBU       | Multiple Bit Upset                                | Page 36             |

| MCU       | Multi Cell Upset                                  | Page 36             |

| MRS       | Mode Register Set                                 | Page 88             |

| RAM       | Random Access Memory                              | Page 17             |

| SCU       | Single Cell Upset                                 | Page 36             |

| SDRAM     | Synchronous Dynamic Random Access Memory          | Page 18             |

| SEE       | Single Event Effect                               | Page 31             |

| SEFI      | Single Event Functional Interrupt                 | Page 14             |

| SEFLU     | Single Event Fuse-Latch Upset                     | Page 79             |

| SEL       | Single Event Latchup                              | Page 36             |

| SEM       | Scanning Electron Microscope                      | Page 21             |

| SER       | Soft Error Rate                                   | Page 41             |

| SET       | Single Event Transient                            | Page 36             |

| SEU       | Single Event Upset                                | Page 14             |

| SRAM      | Static Random Access Memory                       | Page 19             |

| UCL       | Université Catholique de Louvain                  | Page 42             |

| VHDL      | VHSIC Hardware Description Language               | Page 140            |

| WLS       | Wordline SEFLU                                    | Page 89             |

# Introduction

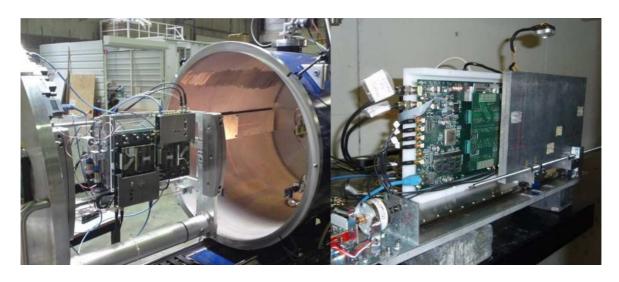

La forte compétition régnant au sein des marchés spatiaux et aéronautiques, ajoutée à l'augmentation des fonctionnalités souhaitées par les clients, impose de concevoir des systèmes de plus en plus performants, autonomes et complexes. Ces exigences impliquent l'accroissement des puissances de calcul des systèmes électroniques embarqués, et l'utilisation des composants les plus récents. Pour les fonctions nécessitant de la mémoire, les composants DRAMs (Dynamic Random Access Memory) offrent aux concepteurs de cartes électroniques les plus fortes capacités de stockage et de vitesse d'accès, à un faible coût par bit. Malheureusement, la fiabilité de ces composants n'est pas garantie pour les environnements sévères, car ils sont principalement destinés aux applications grand public. Or, au regard des enjeux économiques et humains, la sûreté de fonctionnement des systèmes spatiaux et aéronautiques est primordiale ; les composants utilisés dans les applications critiques doivent donc être testés pour évaluer les risques encourus et la nécessité de mettre en œuvre des techniques de protection. Parmi les sources d'erreurs, le rayonnement cosmique constitue une problématique majeure, traditionnellement évaluée par des essais en accélérateur de particules. Cependant les modes de défaillance étant de plus en plus variés à mesure que les composants évoluent, la complexité et la durée des tests augmentent, si bien qu'il devient difficile de les caractériser de manière exhaustive et à un coût acceptable avec ces seuls moyens. Des solutions complémentaires sont donc nécessaires, c'est pourquoi l'utilisation de faisceaux laser impulsionnels pour simuler l'effet des particules suscite un intérêt croissant.

Dans ce contexte, nos travaux effectués au centre de recherche d'EADS IW (European Aeronautic Defense and Space Company) traitent de cette problématique d'évaluation de la tenue aux radiations des DRAMs modernes. Les différents effets pouvant survenir au sein du composant ont pour cela été étudiés avec des expérimentations laser et en accélérateur de particules. Une méthodologie de test optimisée pour les besoins industriels a ensuite été élaborée, utilisant de manière complémentaire ces deux outils pour réduire la durée des tests et améliorer la précision des résultats. Une méthode innovante de correction d'erreurs est en outre proposée, fondée sur des propriétés particulières aux cellules DRAMs. Ces différents points sont développés autour de cinq chapitres.

Le chapitre I introduit le contexte et les principales notions qui seront utilisées par la suite. L'étude étant focalisée sur les DRAMs, la connaissance de leurs caractéristiques technologiques et architecturales est nécessaire. Les particules à considérer varient selon que l'on s'intéresse aux environnements spatiaux ou atmosphériques, aussi leurs caractéristiques et les effets parasites qu'ils produisent sur l'électronique embarquée sont présentés. Les méthodes de caractérisation classiques en accélérateur de particules et les normes décrivant les procédures de test sont également introduites, et confrontées aux caractéristiques des installations de test laser.

Le chapitre II décrit ensuite les travaux relatifs aux modes de défaillance spécifiques aux plans mémoire, principalement ceux liés au changement d'état d'un point de mémorisation, appelés SEU (Single Event Upset). Il s'agit dans un premier temps de comprendre les mécanismes physiques en jeu, et d'évaluer l'évolution de la sensibilité selon l'intégration technologique et le type de cellule employé. Ces mécanismes pouvant aussi être déclenchés par des impulsions laser, nous évaluerons les possibilités offertes par cet outil pour aider à caractériser la sensibilité des DRAMs. La précision spatiale et temporelle de l'injection de charges par laser peut en effet être mise à profit pour révéler diverses informations architecturales ; nous verrons lesquelles et leurs utilités. Par ailleurs, la question de l'influence des motifs de test sur la sensibilité perdure, si bien que l'étude de ce paramètre constituera un volet important de ce chapitre. Un des principaux objectifs sera de déterminer les conditions de tests permettant d'obtenir une mesure de sensibilité SEU la plus conservatrice.

Le chapitre III traite quant à lui des modes de défaillance dans les circuits périphériques, en particulier ceux induisant le dysfonctionnement de certaines parties du composant, appelés SEFI (Single Event Functional Interrupt). Nous verrons que cette problématique est croissante à mesure que les composants évoluent, et que de nouveaux défis se posent pour évaluer les risques associés. Le laser sera à nouveau utilisé pour déterminer les types d'effets provoqués par ces défaillances et les surfaces de sensibilité associées. Le plus important d'entre eux implique le mauvais adressage de certains secteurs du composant. Le laser a offert la possibilité d'étudier ce mode défaillance mal connu jusqu'à présent, et d'identifier les structures responsables. Des méthodes de caractérisation et de protection seront donc proposées.

À partir des connaissances acquises en étudiant ces effets parasites, une méthodologie complète de caractérisation a été élaborée, et est proposée au chapitre IV. Elle s'appuie sur l'utilisation du test laser en complément de l'accélérateur de particules afin d'optimiser le coût global et déterminer tous les modes de défaillance potentiels. Les mises en œuvre des étapes de préparation et de réalisation des tests seront décrites, afin, notamment, de servir de référence aux

futures normes internationales.

Pour finir, une nouvelle solution de tolérance aux fautes, basée sur la propriété particulière des cellules DRAMs d'être immune aux radiations pour un de leurs deux états de charge, sera dévoilée au chapitre V. Nous verrons que plusieurs implantations sont possibles et que leur rendement, c'est à dire le rapport du nombre de bits stockés sur le nombre de bits utiles, est particulièrement intéressant en comparaison des techniques classiques. Les résultats de campagnes de tests laser et en accélérateur de particules démontreront l'efficacité de la technique, et ces performances globales seront confrontées à celles des codes correcteurs existants.

# Chapitre I - Contexte et état de l'art

L'étude des modes de défaillance des mémoires dynamiques vis à vis des radiations suppose, à titre liminaire, d'introduire certaines données et notions fondamentales. Ainsi les caractéristiques des mémoires dynamiques sont d'abord présentées (I.A), suivies des environnements radiatifs auxquels elles sont susceptibles d'être exposées (I.B), et des techniques de caractérisation de sensibilité usuelles (I.C).

# I.A Les mémoires dynamiques

Les mémoires de la famille *Dynamie* RAM (*Random Access Memory*) sont largement utilisées car elles présentent de nombreux avantages, tant du point de vue de leur coût que de leurs performances qui n'ont cessé de croître depuis plus d'une quarantaine d'année (I.A.1). Ces avantages proviennent d'abord de la structure des cellules mémoire élémentaires, réduite à un transistor et un condensateur (I.A.2), mais également des performances des interfaces et circuits périphériques (I.A.3).

# I.A.1 Présentation générale

Les DRAMs sont principalement utilisés comme mémoire centrale des ordinateurs. Ce sont des mémoires "dynamiques" car il est nécessaire de rafraîchir leur contenu à intervalle régulier, et à "accès direct" car chaque emplacement mémoire est accessible avec un même temps de latence. Elles sont classées dans les mémoires "volatiles", ou "vives", car les informations ne peuvent être conservées sans alimentation électrique.

#### I.A.1.1 La famille des DRAMs

Le principe de la cellule DRAM est de stocker une information binaire dans un condensateur, accessible à travers un transistor. Il a été breveté en 1967 [DEN68], et trois ans plus tard, le premier circuit DRAM intégré contenant 1024 bits est commercialisé par la société Intel [LOJ07]. Les technologies ont par la suite énormément évolué, et de nombreuses déclinaisons sont

apparues avec des capacités et des performances toujours plus importantes.

Les DRAMs PMs (*Page Mode*), FPMs (*Fast Page Mode*) et EDOs (*Extended Data Out*) ont été les déclinaisons les plus répandues jusque dans les années 2000. Leurs différences d'un point de vue utilisateur résidaient surtout dans les modes d'accès proposés, notamment le mode "rafale" (*burst mode*) permettant d'adresser successivement plusieurs cellules mémoire sans temps de latence. La société IBM détient à l'époque la plus grosse part de marché. Néanmoins, ces composants étant asynchrones, les vitesses d'accès restent encore limitées.

L'évolution majeure a consisté à cadencer ces mémoires sur la même horloge que la carte mère. Ces DRAMs synchrones (SDRAM, *Synchronous DRAM*) sont alors polarisées à 3.3V et leurs fréquences de fonctionnement vont de 100 à 167 Mhz. Une donnée pouvant être transférée par coup d'horloge, leurs taux de transfert vont de 100 à 167 MT/s (million de transfert par seconde). Grâce à la définition de ces caractéristiques par le groupe de normalisation international JEDEC (*Joint Electron Devices Engineering Council*) [J21C], les SDRAMs se sont rapidement imposées sur le marché à partir des années 2000.

Ce groupe proposa quelques années plus tard une nouvelle évolution : la DDR-SDRAM (*Double Data Rate SDRAM*), polarisée à 2,5 V [J79]. À technologie identique et fréquence égale, elle permet de doubler la bande passante en faisant transiter les données sur les fronts montants et descendants de l'horloge. Pour des fréquences d'horloge allant de 100 à 200 Mhz, les taux de transfert vont ainsi de 200 à 400 MT/s.

La fréquence interne des puces pouvant difficilement dépasser 200 Mhz, l'évolution de la génération DDR2 [J79-2] a consisté à augmenter les fréquences externes (de 200 jusqu'à 400 Mhz), mais avec une fréquence interne deux fois plus faible. Les taux de transfert vont donc de 400 à 800 MT/s, et la tension d'alimentation diminue à 1,8V.

Pour la génération DDR3 [J79-3], les fréquences externes sont encore augmentées (de 400 jusqu'à 1066 Mhz), et les fréquences internes sont divisées par quatre. Les taux de transfert vont ainsi de 800 à 2133 MT/s, et la tension d'alimentation descend à 1,5V. La génération DDR4 commence en 2011 à sortir des laboratoires.

Il existe également des familles spécifiques pour les applications réseaux (Reduced Latency DRAM), vidéos (GDDR, ..., GDDR5, RAMDAC, Windows RAM, Rambus DRAM, etc.), et mobiles (Mobile SDRAM) [WWW01].

Enfin, on parle d'eDRAM (*embedded DRAM*) lorsque cette fonction mémoire est gravée avec d'autres circuits au sein d'une même puce [LOP05].

À l'heure actuelle, les plus importants fabricants sont dans l'ordre : Samsung, Hynix, Elpida, Micron, Nanya, Winbond, Promos, Etron et Renesas.

# I.A.1.2 Performances

Les performances actuelles des DRAMs sont présentées dans le tableau I-1 en comparaison des deux autres familles de mémoire couramment utilisées : les SRAMs (*Static RAM*) et les FLASHs.

Vitesse de Vitesse Type de Capacité Coût Volatile lecture d'écriture Avantages Inconvénients Mémoire par bit (MT/s)(MT/s)- Coût élevé **SRAM** Le plus - Faible Oui 144 Mb 1100 Faible capacité (QDR2) élevé consommation - Volatile Non volatile - Écriture lente **FLASH** Non 128 Gb 166 Lent (ms) Élevé - Très faible Effacement nécessaire (NAND) Nb. d'écriture limitée consommation **DRAM** -Faible coût Rafraîchissement Le plus Oui 8 Gb 2133 (DDR3) faible -Haute densité Volatile

Tableau I-1: Performances actuelles des familles DRAMs, SRAMs et FLASHs

Les SRAMs sont volatiles, mais conservent les informations sans rafraîchissement : elles sont "statiques" [PAV08]. Leur interface est relativement simple et les temps de lecture et d'écriture sont très rapides. En revanche, les cellules élémentaires occupant six transistors, les capacités proposées sont plus faibles et le coût par bit plus élevé que les deux autres technologies.

Les FLASHs sont non volatiles, ont une faible consommation en mode statique, et sont très intégrées puisque l'information est stockée dans la grille flottante d'un seul transistor [BRE08]. Des capacités allant jusqu'à 128 Gb sont actuellement proposées. En revanche, le processus d'écriture est lent, limité en nombre de cycles et nécessite une opération d'effacement de bloc préalable.

Les DRAMs sont volatiles et nécessitent d'être rafraîchies. Leurs avantages sont en revanche de combiner une densité élevée (jusqu'à 8 Gb), avec d'excellentes performances en temps d'accès.

Ainsi, sur un bus cadencé à 1066 Mhz, une DDR3 PC-2133 a un taux de transfert de 2133 MT/s, soit une bande passante de 16,67 Gio/s (Giga-octets) lorsqu'elles sont combinées en bus de 64 bits. Compte tenu de ces caractéristiques, les applications pour lesquelles les DRAMs sont les plus appropriées sont l'exécution du code d'un micro-processeur ou le stockage temporaire de trames vidéo ou de données de communication. Ces performances proviennent principalement de la structure des cellules mémoire élémentaires.

#### I.A.2 Cellules mémoire élémentaires

Environ 80 % de la surface d'une puce DRAM est constituée de cellules mémoire, dont la conception a beaucoup évolué au cours des dernières décennies.

# I.A.2.1 Principe du stockage

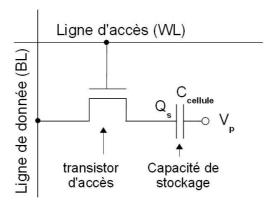

Les cellules mémoire DRAMs sont formées d'une capacité ( $C_{cellule}$ ) stockant une charge ( $Q_s$ ) et d'un transistor d'accès, comme illustré sur la figure I-1.

Figure I-1: Schématique d'une cellule élémentaire DRAM [MAL05]

On parle de cellule 1T/1C. Une ligne d'accès WL (*Wordline*) pilote le transistor d'accès, tandis que l'information transite sur une ligne de données BL (*Bitline*). De nombreux ouvrages décrivent en détail le fonctionnement de ces cellules [KEE08-MAL05-JAC04-JAC05], aussi nous ne résumons ici que leurs principales caractéristiques. Les capacités de stockage ont une armature polarisée à un potentiel commun : Vp. Ce potentiel était égal à la tension d'alimentation (Vcc) dans les premières générations, puis il a été défini à la moitié de celle-ci (Vcc/2) afin d'augmenter

la quantité de charges stockées.

La deuxième armature est le nœud de stockage, pouvant être polarisé à Vcc ou Gnd :

- Vcc : La cellule est dite chargée. La différence de potentiel aux bornes du condensateur est alors +Vcc/2 ; la charge stockée est donnée par l'équation suivante :

$$Q_s = \frac{Vcc}{2} \cdot C_{cell}$$

(Qs s'exprime en Coulomb, Vcc en Volt et Ccell en Farad)

- Gnd : La cellule est dite déchargée. La différence de potentiel aux bornes du condensateur est alors négative (-Vcc/2), la charge s'exprime donc :

$$Q_s = -\frac{Vcc}{2} \cdot C_{cell}$$

Différents courants de fuite amènent les cellules à se décharger, c'est pourquoi un mécanisme de rafraîchissement est nécessaire.

La densité des mémoires DRAMs a augmenté en moyenne d'un facteur 4 tous les trois ans depuis leur création, et cette tendance se poursuit actuellement. Cette augmentation remarquable a été rendue possible par l'amélioration de plusieurs domaines technologiques, incluant les processus de lithographie et de gravure, les techniques de déposition de couches fines, ainsi que l'amélioration de l'architecture des cellules. Le résultat est une meilleure optimisation d'utilisation de la surface de silicium.

# I.A.2.2 Les différents types de capacité

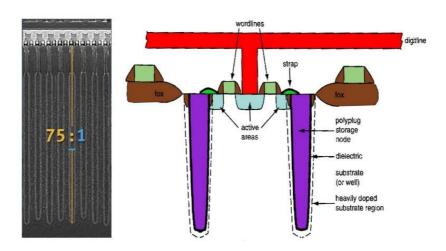

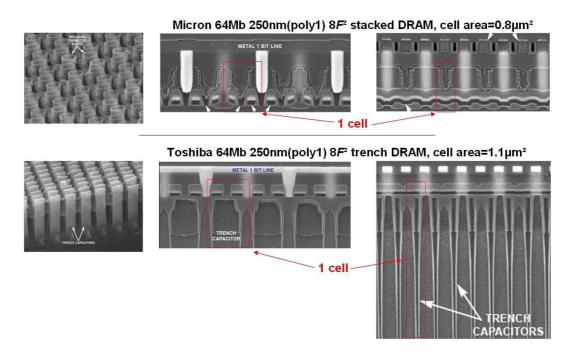

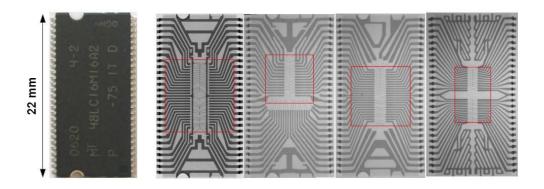

Avec la diminution de la surface des cellules, les fabricants durent utiliser la troisième dimension pour conserver un niveau de charge suffisamment élevé par rapport au bruit ambiant. Deux approches ont été adoptées : les capacités enterrées, ou "*Trench*" (IBM, Qimonda, etc.) et celles empilées, ou "*Stack*" (Samsung, Micron, Elpida, etc.). Chacune des architectures a grandement évolué depuis le milieu des années 90 [SUN08]. Néanmoins, le nombre de fabricants de cellules enterrées tend actuellement à diminuer.

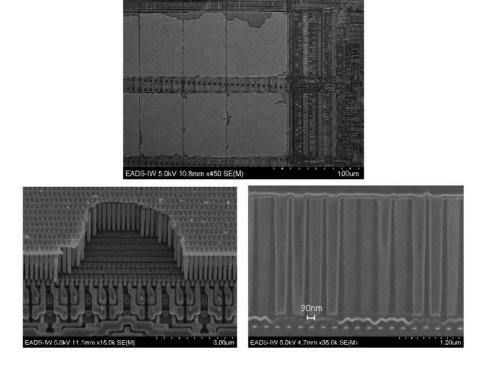

La figure I-2 montre une image SEM (Scanning Electron Microscope) et un schématique de deux cellules DRAMs enterrées. Celles-ci sont fabriquées en gravant des tranchées sur plusieurs

dizaines de micromètres dans le substrat de silicium, en recouvrant les parois d'un isolant électrique et en le remplissant ensuite de polysilicium dopé. La connexion avec le transistor d'accès est réalisée par un contact métallique, et le substrat sert de contact commun. Plus l'intégration augmente et plus la profondeur des tranchées est importante. Les cellules sont groupées par deux et partagent un même plot de connexion à la ligne de données.

Figure I-2: Photo SEM et schématique de cellules DRAMs enterrées [FUL01]

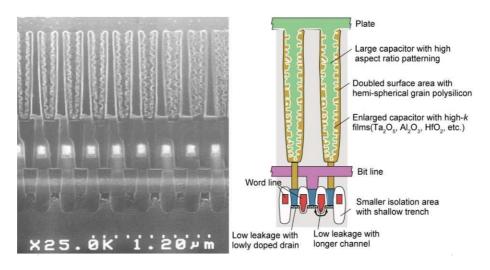

La figure I-3 montre un schématique et une photo SEM de cellules DRAMs empilées cylindriques en polysilicium HSG (*Hemi-Spherical Grain*) fabriquées en technologie 110 nm. Les condensateurs atteignent plusieurs dizaines de micromètres de hauteur, aussi doivent-ils être maintenus mécaniquement par un revêtement rigide et polarisé.

Figure I-3 : Photo SEM et schématique de cellules DRAMs empilées [WWW02-SUN08]

La difficulté de fabrication réside dans le fait que les condensateurs doivent être amincis à leur

base aux plus petites dimensions possibles du procédé de gravure pour être intercalés entre les lignes de données. Comme pour les cellules enterrées, celles empilées sont groupées par deux et partagent un même plot d'accès à une ligne de données. Quel que soit le type de cellule, nous verrons dans les chapitres suivants que leur contenu peut être altéré par des perturbations extérieures, de manière plus ou moins importante en fonction de la quantité de charge stockée et de la surface des cellules. Cette dernière dépend de la finesse de gravure et du type d'agencement.

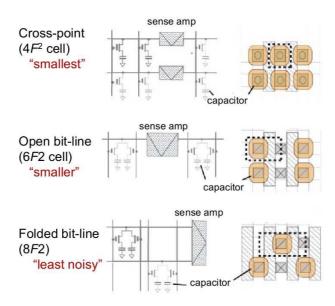

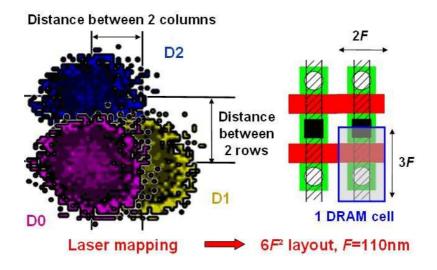

Il existe trois agencements possibles ("Cross Point", "Open Bitline" et "Folded Bitline"), illustrés sur la figure I-4. La surface des cellules s'exprime en fonction du nœud technologique F ( $4F^2$ ,  $6F^2$  et  $8F^2$ ). Une cellule en technologie 90 nm avec un agencement en  $6F^2$  a ainsi une surface de  $0.048 \, \mu \text{m}^2$ .

Figure I-4: Configurations d'agencement des matrices de cellules DRAMs [SUN08]

L'agencement "Folded Bitline" est le plus ancien et permet de s'affranchir des bruits de mode commun car les deux lignes de données sont côte à côte. Celui "Open Bitline" est actuellement le plus répandu et permet une plus forte densité. Enfin les cellules en "Cross Point" permettent en théorie une densité maximale, mais au prix d'une forte sensibilité aux bruits électromagnétiques. Aucun composant en production n'implante encore cet agencement.

La dimension du nœud technologique pour une DRAM est définie selon l'ITRS (*International Technologie Roadmap for Semiconductors*) comme étant la moitié du décalage (*Pitch*) entre deux métallisations de niveau 1 [ITRS09]. Le tableau I-2 donne à titre indicatif les nœuds

technologiques prédits par l'ITRS jusqu'en 2016, qui suivent les lois de Moore.

Tableau I-2: Prévisions de l'évolution des nœuds technologiques [ITRS00-ITRS09]

| Date de production | 1999 | 2000 | 2001 | 2002 | 2003 | ••• | 2009 | 2010 | 2011 | 2012 | ••• | 2015 | 2016 |

|--------------------|------|------|------|------|------|-----|------|------|------|------|-----|------|------|

| Technologie (nm)   | 180  | 150  | 130  | 120  | 110  |     | 52   | 45   | 40   | 36   | ••• | 25   | 22,5 |

Début 2011, les puces les plus avancées de la société Samsung sont produites en technologie 39 nm pour un agencement en  $6F^2$ , confirmant les prévisions des analystes.

La forte compétitivité régnant sur les marchés grand public oblige les fabricants à adopter les technologies de gravure les plus récentes. Le coût unitaire est ainsi diminué car un nombre de puces plus élevé peut être gravé par tranche de silicium (wafer). Les performances et la consommation électrique sont également améliorées à chaque génération technologique.

Cette course à l'intégration a comme conséquence la rapide obsolescence des composants, ce qui pénalise les industries comme le spatial et l'aéronautique dont les systèmes sont produits sur plusieurs décennies, si bien que des stocks stratégiques de lots entiers sont généralement constitués.

# I.A.3 Circuits périphériques

La partie périphérique des DRAMs inclut les interfaces, les signaux de contrôle, la logique d'accès aux cellules, le décodage d'adresses, l'alimentation [WEI00], la sélection du mode d'opération, la logique de gestion du rafraîchissement, de la redondance, etc. De nombreux ouvrages [KEE08-MAL05-JAC04-JAC05] détaillent amplement l'architecture de ces circuits. Nous ne présentons ici que ceux les plus sensibles aux agressions externes.

# I.A.3.1 Principe d'accès aux cellules

Le principe de la lecture est basé sur le transfert de charges avec la cellule et la ligne de données, provoquant une variation positive ou négative du potentiel de la ligne, qu'il suffit alors de mesurer.

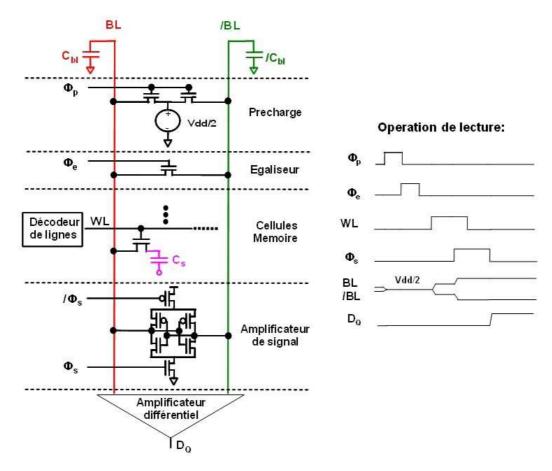

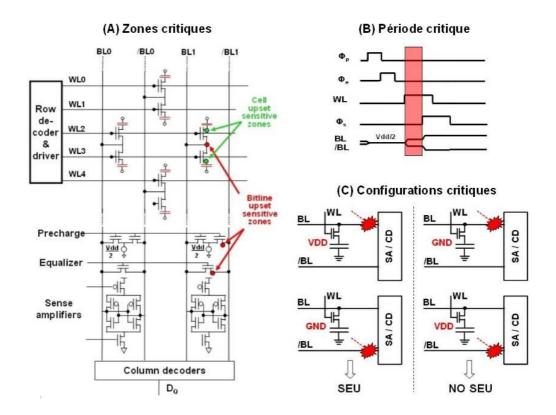

La figure I-5 montre un schéma du circuit de lecture avec un chronogramme des opérations.

Sont illustrés une cellule DRAM (Cs), sa ligne d'accès (WL), sa ligne de données (BL), celle de référence (/BL), l'amplificateur de signal (*Sense Amplifier*) et d'autres éléments nécessaires à cette opération.

La séquence effectuée pour lire le contenu d'une cellule commence par l'étape de précharge, qui consiste à imposer à BL et /BL une tension de référence (Vcc/2). Cette tension est ensuite égalisée par la mise en conduction d'un transistor dédié, et les capacités parasites C<sub>BL</sub> et C<sub>/BL</sub> maintiennent ces niveaux de tension un certain temps.

Figure I-5 : Schéma simplifié de la circuit de lecture d'une cellule DRAM

La ligne d'accès (WL) correspondant à la cellule souhaitée est ensuite sélectionnée, ce qui active simultanément toutes les cellules de la ligne : c'est l'étape d'activation. Un transfert de charges s'effectue alors entre la cellule mémoire et la ligne de données. Il en résulte une variation  $\Delta V$  de la tension sur BL qui dépend du rapport des capacités, dont l'équation est donnée ciaprès :

$$\Delta V = \frac{Vcc}{2} \cdot \frac{C_{cell}}{C_{cell} + C_{bitline}} \approx 100 mV$$

Afin d'obtenir la variation de tension la plus importante possible et de s'affranchir des bruits parasites, les fabricants cherchent à diminuer la capacité des lignes de données et à augmenter celle des cellules.

Lorsque le potentiel Vcc est stocké dans la cellule, la tension sur BL lors du transfert devient :  $Vcc/2 + \Delta V$ . Pour le potentiel Gnd, la variation est alors négative, et la tension sur BL est alors :  $Vcc/2 - \Delta V$ .

Pour augmenter la différence de tension entre BL et /BL, un amplificateur de signal (Sense Amplifier) détectant des variations de l'ordre du million d'électrons est activé. Les tensions sur BL et /BL sont alors amplifiées aux valeurs extrêmes (Vcc et Gnd).

Un amplificateur différentiel (*Differential Amplifier*) interprète au final cette information en une valeur logique ('1' ou '0'). Il est important pour la suite de noter qu'un état de charge donné sera traduit différemment selon que la cellule est connectée sur la borne positive ou négative de l'amplificateur différentiel. La relation entre valeur logique ('0' ou '1') et état de charge (chargé ou déchargé) diffère donc selon l'emplacement de la cellule.

Le décodeur de colonnes sélectionne au final la ligne de données souhaitée et l'information est transmise vers les amplificateurs (*Buffer*) de sortie.

L'opération de lecture est destructrice, mais la valeur est naturellement réécrite pendant l'étape d'amplification car les transistors d'accès restent ouverts. L'opération de rafraîchissement est par ailleurs similaire à cette opération de lecture.

# I.A.3.2 Architecture et fonctionnement général

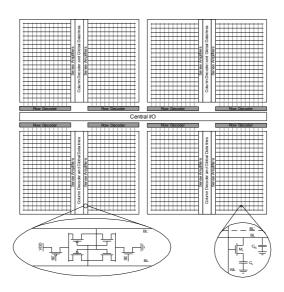

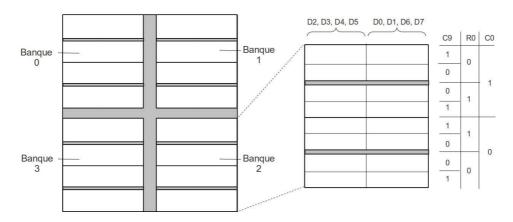

Les cellules mémoire sont groupées en blocs, typiquement constitués de 512 lignes et 512 colonnes. Le groupement de plusieurs blocs avec les circuits d'amplification et de précharge est appelé "banque". La puce est constituée de plusieurs banques et de circuits périphériques. Cette organisation en banques est une façon de limiter la longueur des lignes d'accès pour réduire les capacités parasites.

La figure I-6 illustre un agencement physique typique d'une mémoire DRAM. Les amplificateurs de signaux se trouvent en bordure des banques, et les entrées/sorties au milieu de la puce afin d'optimiser la distance à parcourir pour les signaux.

Figure I-6: Organisation typique d'une mémoire DRAM

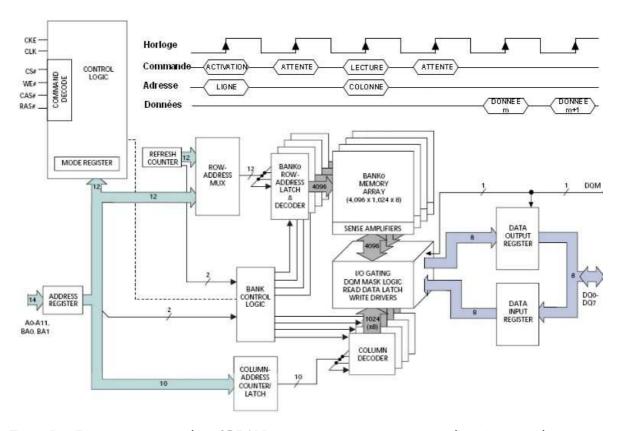

La description en blocs fonctionnels d'une SDRAM telle qu'indiquée dans la fiche technique d'un produit de la société Micron est donnée sur la figure I-7, avec un chronogramme des signaux d'interface lors d'une lecture. L'ensemble des deux figures permet d'expliquer simplement le fonctionnement du composant d'un point de vue utilisateur.

L'interface de la mémoire est composée d'un bus de données (DQ0-DQ7), d'un bus d'adresses (A0-A11, BA0-BA1), de signaux de commande (/CS, /WE, /RAS, /CAS) et d'une horloge (CLK). Les commandes sont prises en compte aux fronts montants de l'horloge. Le bus d'adresses est multiplexé pour les lignes et les colonnes afin de réduire le nombre de signaux, aussi la demande de lecture se fait en deux temps. Elle commence par la commande "activation", pendant laquelle les numéros de banque et de ligne sont positionnés sur le bus d'adresses, suivie de la commande "lecture" accompagnée du numéro de la première colonne souhaitée. Les informations sont disponibles sur le bus de données quelques coups d'horloge plus tard.

Les mémoires actuelles proposent plusieurs modes de fonctionnement, configurés par l'intermédiaire du registre de configuration (*Mode Register*). Parmi eux, on peut citer la possibilité d'accéder aux données en "rafale" (4 bits, 8 bits, page entière), de choisir le type d'accès (séquentiel ou aléatoire), le temps de latence, le temps de rafraîchissement, la mise en veille, etc.

Le registre de configuration permet en outre aux fabricants d'activer des modes de test spécifiques, appelés BIST (*Built-In Self Test*), utilisés pendant le test en usine [WON96-GIRA09].

Figure I-7: Blocs fonctionnels d'une SDRAM, et chronogramme des signaux d'interface lors d'une lecture

Enfin, le circuit de rafraîchissement est une autre fonction essentielle aux DRAMs. Celui-ci est basé sur un compteur désignant un numéro de ligne et s'incrémentant de manière automatique ou sur commande extérieure. Les normes stipulent des intervalles pour les commandes de rafraîchissement de 7,8 µs .

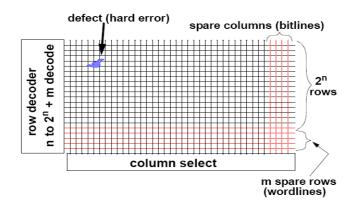

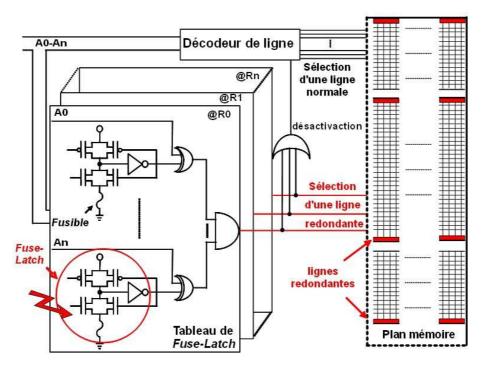

#### I.A.3.3 Circuits de redondance

La diminution de la taille des nœuds technologiques induit l'augmentation du nombre de défauts pendant la fabrication. Afin de maintenir des rendements de production satisfaisants, les fabricants intègrent des cellules supplémentaires destinées à remplacer celles qui sont défectueuses. Comme illustré sur la figure I-8, des lignes et des colonnes entières sont ajoutées au sein de chaque bloc. Un ordre de grandeur à titre indicatif est de 2 ou 4 lignes redondantes pour 512 lignes régulières. Les adresses logiques des cellules défectueuses sont identifiées pendant les

tests en usine. Le circuit de gestion de la redondance est alors paramétré afin que, lorsque ces adresses sont demandées, des cellules redondantes soient sélectionnées, et ce de manière transparente pour l'utilisateur [WIEN08].

Figure I-8 : Illustration d'une zone défectueuse et des lignes et colonnes de remplacement. [JAC05]

Les adresses défectueuses sont stockées dans des tableaux de fusibles, chaque fusible correspondant à un bit et définissant une valeur binaire selon qu'il est ouvert ou fermé. Ces fusibles sont brûlés, soit électriquement par le passage d'un fort courant, soit par l'utilisation d'un laser [PRA97]. Cette deuxième technique nécessite un circuit moins complexe mais une précision de plus en plus difficile à obtenir à mesure que la taille des transistors diminue.

Deux types d'architecture de comparaison d'adresses existent [MIW96] : les architectures parallèles et série. L'architecture série consiste à comparer successivement l'adresse demandée avec celles stockées dans les tableaux de fusibles. Elle est relativement peu coûteuse en surface mais lente face à un nombre important de comparaisons. C'est pourquoi l'architecture parallèle est de nos jours majoritairement adoptée : le délai de comparaison n'est alors plus pénalisant car toutes les adresses sont comparées simultanément.

Dans cette architecture, afin d'isoler les fusibles qui pourraient ne pas être correctement brûlés et causer une surconsommation de courant, ceux-ci sont généralement associés à des registres qui recopient l'information du fusible à la mise sous tension du composant, et pendant les réinitialisations (*Reset*). Ces structures associant un fusible et un registre sont appelées "*Fuse-Latch*" [REN94-HIDE09]. Du fait de leur nature d'élément bistable, le contenu des "*Fuse-Latchs*" peut être altéré par des perturbations externes et, comme nous le verrons dans les chapitres suivants, sont responsables de certains modes de défaillance.

# I.B Environnements radiatifs naturels et effets sur les circuits intégrés

Les environnements dans lesquels les véhicules spatiaux et les aéronefs évoluent sont hostiles pour l'homme mais également pour l'électronique embarquée. Parmi les sources de défaillance, on trouve les particules cosmiques dont la quantité et la nature diffèrent selon le milieu spatial ou atmosphérique. La présentation des environnements radiatifs naturels (I.B.1) sera suivie de l'explication des mécanismes d'interaction entre particules et circuits intégrés (I.B.2), et de celle des effets induits (I.B.3).

# I.B.1 Les environnements radiatifs naturels

Deux environnements doivent être distingués : l'environnement spatial et l'environnement atmosphérique, ce dernier étant protégé par la magnétosphère terrestre [ROC99, WRO02].

# I.B.1.1 L'environnement spatial

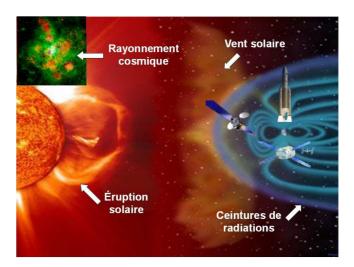

L'environnement spatial est le plus agressif au niveau des radiations, et l'homme ne pourrait pas y survivre sans protection. D'importants flux de particules fortement énergétiques provenant de diverses sources traversent ce milieu et les objets qui s'y trouvent (figure I-9).

Figure I-9: Illustration de l'environnement radiatif spatial

Les premières études émettant l'hypothèse selon laquelle les ions lourds seraient la cause de défaillances des circuits électroniques datent des années 1975 [BIND75]. Les principales composantes de cet environnement radiatif sont classées en quatre catégories suivant leur origine : les ceintures de radiations, le vent solaire, les éruptions solaires et le rayonnement cosmique. Le tableau I-3 indique leurs populations respectives : principalement des protons, des particules  $\alpha$  (alpha), des électrons et des ions lourds.

Tableau I-3: Tableau des populations de particules dans l'espace [BOUD95]

| Origine                | PARTICULES                                             | ÉNERGIES                                              | FLUX (cm <sup>-2</sup> s <sup>-1)</sup>                    |

|------------------------|--------------------------------------------------------|-------------------------------------------------------|------------------------------------------------------------|

| CEINTURES DE RADIATION | -Protons (Orbites basses)<br>-Électrons (Orbites géo.) | 99 % < 10 MeV<br>99 % < 2 MeV                         | 10 à 10 <sup>6</sup><br>10 <sup>-2</sup> à 10 <sup>7</sup> |

| VENT SOLAIRE           | -Protons<br>-Électrons<br>-Particules alpha            | < 100 keV<br>< qq. keV                                | 10 <sup>8</sup> à 10 <sup>10</sup>                         |

| ÉRUPTIONS<br>SOLAIRES  | -Protons<br>-Particules alpha<br>-Ions lourds          | 10 à 1000 MeV<br>10 à 100 MeV                         | 10 <sup>10</sup><br>100 à 1000                             |

| RAYONS<br>COSMIQUES    | -Protons (87 %)<br>-Particules α<br>-Ions lourds (1%)  | 100 à 10 <sup>6</sup> MeV<br>1 à 10 <sup>14</sup> MeV | 1 à 100 MeV<br>10 <sup>-4</sup> à 10 <sup>6</sup> MeV      |

L'énergie de ces particules s'exprime en électron-volt (eV), correspondant à l'énergie cinétique d'un électron accéléré depuis le repos par une différence de potentiel d'un volt. Les particules les plus énergétiques proviennent des éruptions solaires et du rayonnement cosmique. L'origine de ce dernier est étudiée depuis le début du XX° siècle, mais reste actuellement un mystère : il pourrait provenir de l'explosion de supernovas, de trous noirs ou bien de noyaux de galaxies actives. L'observatoire "Pierre Auger" mis en service en 2004 en Argentine devrait apporter des éléments de réponse dans les années à venir.

Les électrons et les protons sont principalement responsables des effets de dose cumulée, ou TID (*Total Ionizing Dose*), qui se traduisent par une dérive de certains paramètres électriques. Ces effet augmentent avec la fluence reçue et ne sont pas réversibles.

Les ions lourds, les particules  $\alpha$  et à nouveau les protons induisent des effets singuliers ou SEE (Single Event Effect), qui sont des effets non destructifs et réversibles induits par le passage d'une particule unique. Parmi eux, les SEUs (Single Event Upsets) et les SEFIs (Single Event Functional Interrupts) sont les événements qui nous intéresseront particulièrement.

# I.B.1.2 L'environnement atmosphérique

L'atmosphère terrestre est protégée de la plupart des rayons cosmiques par la magnétosphère qui les dévie vers les pôles, créant alors le phénomène d'aurore boréale.

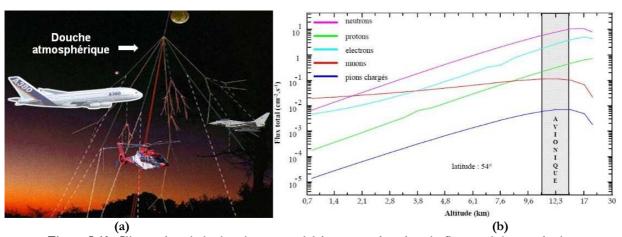

Néanmoins, certains protons sont suffisamment énergétiques pour traverser ce champ magnétique. L'interaction de ces particules avec les noyaux des éléments constituant l'atmosphère (80% d'azote et 20 % d'oxygène) produit des particules secondaires, qui elles-mêmes interagissent avec d'autres noyaux. C'est le phénomène de douche atmosphérique, illustré sur la figure I-10 (a).

Figure I-10 : Illustration de la douche atmosphérique et estimation du flux total des particules atmosphériques en fonction de l'altitude, d'après [BRI71-BRI78].

Les principaux produits secondaires créés sont des neutrons, des électrons, des protons, des muons et des pions chargés. Comme le montre la figure I-10 (b), hormis les muons, le flux total (toutes énergies confondues) pour chaque type de particules décroît avec l'altitude.

Les neutrons sont les particules les plus nombreuses quelle que soit l'altitude. Le flux exact est difficile à estimer et diffère légèrement selon les normes, mais la communauté s'accorde sur le fait qu'il varie avec l'altitude (facteur 300 entre le sol et 12 km) et la latitude (facteur 6 entre les pôles et l'équateur) [NOR93].

Les neutrons ont été identifiés depuis les années 1990 comme la cause principale d'événements singuliers dans les systèmes électroniques avioniques. Des études ont en effet montré que les taux d'erreurs observés à différentes altitudes et latitudes variaient de la même façon que le flux de neutron.

D'autres corrélations avec des expériences menées en laboratoire sont également venues

appuyer ces hypothèses. Ces particules sont donc actuellement considérées comme les plus préoccupantes pour l'électronique embarquée aux altitudes avioniques.

Les neutrons n'ont pas de pouvoir ionisant car ils sont électriquement neutres. En revanche, nous verrons au paragraphe I.B.2.2 qu'ils peuvent interagir avec les noyaux du réseau cristallin des composants traversés et générer ainsi des ions secondaires qui sont directement responsables des défaillances.

Parmi les autres sources de radiation naturelle, on trouve au niveau du sol du radon, un gaz radioactif provenant de la désintégration du radium, lui-même provenant de l'uranium présent naturellement dans la croûte terrestre.

Par ailleurs, l'émission de particules alpha par des constituants des boîtiers électroniques est une préoccupation récurrente de l'industrie micro-électronique. Les flux et les énergies de ces particules sont néanmoins bien moins importants que ceux rencontrés en altitude.

# I.B.2 Mécanismes d'interaction physiques

Les particules constituant les environnements radiatifs traversent la matière et interagissent avec ses atomes. On distingue les interactions ion-silicium ionisant la matière directement et celles neutron-silicium que le font indirectement.

#### I.B.2.1 Interactions ion-silicium

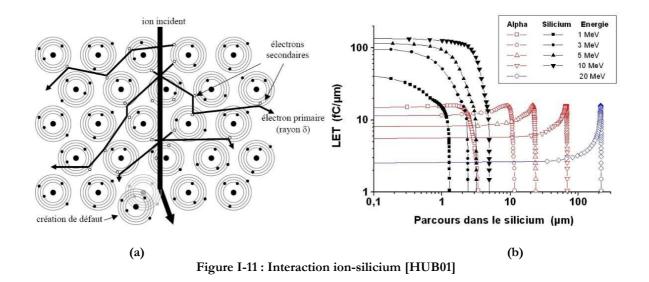

Lorsqu'une particule chargée pénètre dans la matière, elle interagit essentiellement sous l'effet des forces coulombiennes avec les particules chargées qui constituent les atomes du matériau [HUB01]. La probabilité d'un choc direct avec le noyau atomique est très faible alors que l'ion traverse un milieu comportant une forte population d'électrons. L'ion incident subit ainsi un grand nombre d'interactions avec les électrons au cours desquelles il perd progressivement de l'énergie. Ces électrons subissent d'abord une transition vers un état excité, c'est le phénomène d'ionisation, qui génère d'autres d'électrons qui, à leur tour, vont produire de nouvelles ionisations, comme illustré sur la figure I-11 (a).

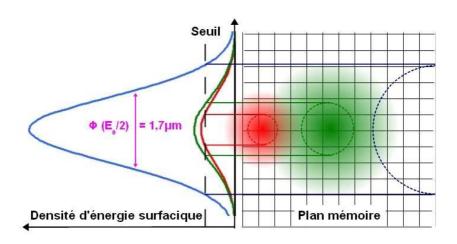

Ce mécanisme d'ionisation est donc responsable de la perte d'énergie de la particule chargée et de son ralentissement. Cette perte d'énergie dE/dx cédée par unité de longueur est appelée pouvoir d'arrêt ou LET (*Linear Energy Transfer*) et s'exprime en fC/µm, ou en MeV/(mg/cm²). Des exemples d'évolution du LET dans le silicium pour des ions silicium et alpha sont donnés sur la figure I-11 (b) pour différentes énergies initiales.

Malgré les interactions, la particule incidente est peu déviée car l'énergie qu'elle cède à chaque collision est faible devant son énergie initiale. Lors du passage d'une particule ionisante, il y a donc formation d'un canal très fortement ionisé de très faible diamètre (typiquement  $0,5~\mu m$ ) autour de la trace de l'ion.

# I.B.2.2 Interactions neutron-silicium et collection de charges

Les neutrons présents dans l'atmosphère n'ionisent pas directement la matière car ils sont électriquement neutres. Ils peuvent en revanche rencontrer le noyau d'un atome et engendrer des particules secondaires qui elles sont capable d'ioniser. La probabilité qu'une interaction ait lieu entre un neutron et un noyau est d'environ 5.10<sup>-6</sup> [HUB01].

Dans une technologie CMOS classique, les drains et sources des transistors sont implantés directement dans le substrat de silicium, et sont de ce fait vulnérables à la collection de charges parasites résultant du passage d'une particule. Deux mécanismes de collection de charges existent : la collection par aspiration (funneling) et la collection par diffusion [LAM06]. La première

résulte du passage de l'ion directement au travers de la jonction polarisée et de la zone de charge d'espace. La charge collectée dans ce cas correspond à une impulsion de courant très brève. Dans la collection par diffusion, les porteurs générés en dehors d'une zone de charge d'espace diffusent à partir de la trace de l'ion vers les zones de plus faible densité, avant d'être recombinés. Une partie peut donc atteindre le drain d'un transistor, apportant ainsi des charges parasites. Les courants collectés par ce mécanisme sont plus faibles, mais d'une durée plus importante.

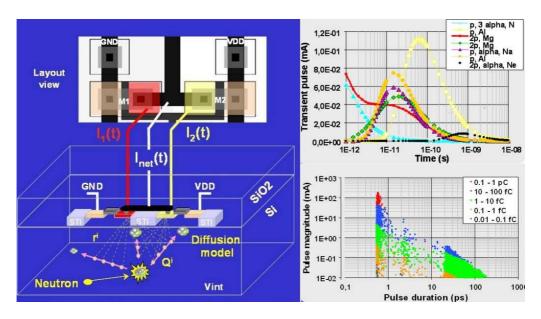

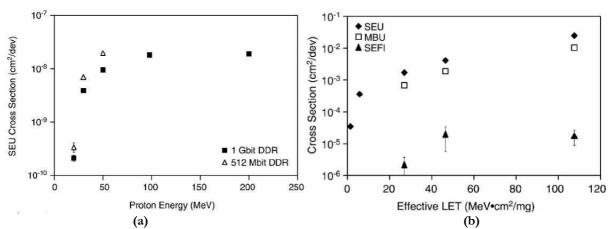

La figure I-12 illustre l'interaction d'un neutron avec un noyau de silicium proche d'une cellule CMOS inverseur (INV).

Figure I-12 : Illustration de l'interaction nucléaire neutron / silicium et allures d'une population de courants collectés par un drain 130 nm [HUB06-RUS07]

Dans cet exemple, la réaction nucléaire produit trois ions chargés. Les zones sensibles de cette structure sont les drains des deux transistors qui sont connectés, et dont le potentiel est flottant. La valeur totale des charges reçues par le nœud correspond à la somme des charges apportées par les trois ions et collectés par les deux drains.

Ces charges dépendent donc fortement de la localisation de l'interaction, des paramètres des ions et de la géométrie des drains. Un exemple de population de courants pouvant être collectés dans une technologie 130 nm [HUB06] est indiquée afin de montrer leur grande diversité en terme de durée et d'amplitude. Les effets au niveau fonctionnel résultant de la collection de ces charges parasites dépendent de l'allure des impulsions ainsi que de la fonction des transistors touchés.

#### I.B.3 Les effets singuliers

Les "effets singuliers" désignent les dysfonctionnements non destructifs et réversibles induits par une particule unique. Dans cette étude, nous nous intéresserons principalement aux SEUs (Single Event Upsets) et aux SEFIs (Single Event Functional Interrupts), mais évoquerons également le SEL (Single Event Latchup).

#### I.B.3.1 Les "Single Event Upsets"

Le pulse de tension généré par la collection de charges peut avoir des conséquences variées selon la fonction des transistors touchées.

Dans un composant analogique, le transitoire peut se propager jusqu'à la sortie et produire une impulsion ponctuelle. Cet effet est appelé SET (Single Event Transient).

Dans un composant logique, un transitoire généré dans une cellule combinatoire peut se propager. S'il n'est pas atténué ou masqué par une porte logique, il peut être capturé par un élément mémoire de type *Flip-Flop*, induisant une erreur pouvant induire des défaillances au niveau du système [LEV07].

Dans une fonction mémoire, l'effet est local et peut conduire au basculement de la structure, donc à l'inversion de l'information. On parle alors d'aléa logique, en anglais SEU (Single Event Upset), ou plus précisément SCU (Single Cell Upset) s'il s'agit d'une unique cellule mémoire. Le niveau de charge nécessaire pour induire un SCU est appelé charge critique (Qc). Ce changement accidentel d'état logique dans une mémoire est réversible (l'information peut être corrigée par une opération d'écriture) et ne conduit pas à la destruction du composant.

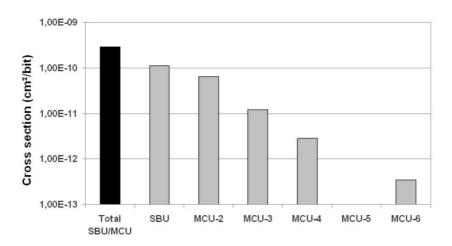

Cet effet de basculement peut se produire dans tout élément bistable comme les registres, les bascules, les "Fuse-Latchs", etc. Lorsque plusieurs cellules basculent suite au passage d'une unique particule, on parle d'événements multiples, ou MCU (Multiple Cell Upset). Si ces cellules appartiennent à une même adresse logique, l'effet est appelé MBU (Multiple Bit Upset).

Les condensateurs des DRAMs sont aussi altérés par la collection de charges, qui modifient le potentiel stocké et peut amener à l'inversion de l'information. Les mécanismes spécifiques aux DRAMs seront étudiés en détail dans le chapitre II.

#### I.B.3.2 Les "Single Event Functional Interrupts"

Les SEFIs (*Single Event Functional Interrupts*) désignent les conséquences du basculement d'un registre appartenant aux circuits périphériques d'un composant. Ce terme est en réalité assez imprécis et est employé pour différents effets dans plusieurs familles de composants.

Dans un microprocesseur, il désigne la perte de fonctionnalité d'une partie du composant qui n'exécute alors plus le programme, ni ne répond aux commandes extérieures, et est parfois nommé "hang". Une réinitialisation (Reset) ou une remise sous tension est alors nécessaire pour retrouver la fonctionnalité.

Dans un réseau de portes logiques programmables comme les FPGAs (Field Programmable Gate Array) où la configuration réside dans une matrice de cellules SRAMs, un SEFI désigne la modification de la fonction souhaitée suite à l'altération d'une ou plusieurs cellules de configuration, ou l'impossibilité d'activer certaines fonctionnalités du composant.

Dans un composant mémoire relativement complexe comme une DRAM ou une FLASH, cette classe d'effets englobe tous ceux se produisant dans les circuits périphériques. Ils peuvent amener à un mauvais adressage, à une perte de fonctionnalité de certains secteurs, ou au dysfonctionnement complet de la mémoire nécessitant une remise sous tension. L'étude approfondie des SEFIs dans les DRAMs est l'objet du chapitre III.

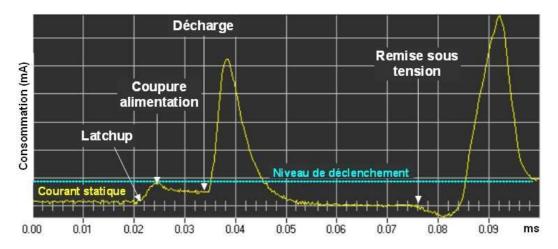

#### I.B.3.3 SEL et autres effets

Un autre effet important pouvant se produire dans les DRAMs est le SEL (Single Event Latchup) [BRU96], qui est la mise en conduction par un ion d'une structure thyristor parasite, entraînant le passage d'un courant important. Cet effet s'apparente à un court circuit et peut amener à la destruction du composant. Les composant sensibles à ce type de défaillance ne sont généralement pas retenus pour des applications spatiales, car les méthodes de protection sont chères et complexes.

Les DRAMs sont également sensibles aux phénomènes de bits collés (*Stuck Bit*) [SCH08] et de bits collés intermittents [CHU09]. Néanmoins, ces effets s'apparentent à des effets de dose qui sont en dehors du cadre de cette étude.

# I.C Caractérisation de la sensibilité des circuits intégrés aux effets singuliers

Ayant présenté les mémoires dynamiques et les environnements radiatifs dans lesquels elles sont susceptibles d'être utilisées, intéressons nous dans cette troisième section aux méthodes de caractérisation existantes. Ces caractérisations de sensibilité sont nécessaires pour s'assurer que les exigences de fiabilité des systèmes spatiaux et avioniques sont satisfaites (I.C.1). Les moyens de caractérisation au sol classiquement utilisés sont les accélérateurs de particules (I.C.2), mais des outils complémentaires comme les faisceaux laser impulsionnels deviennent de plus en plus attractifs (I.C.3).

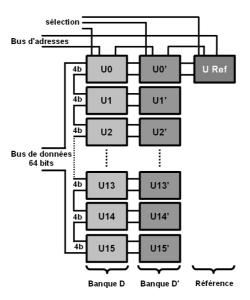

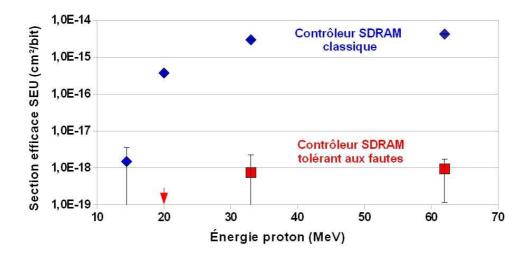

#### I.C.1 Exigences de fiabilité